Nexus 21 1066Mt S Interposer Users Manual NEX NEXVuDDR800M X

1066MTs Interposer to the manual 0f8e1930-12e6-4c16-8b9b-dc677d1a1114

2015-02-05

: Nexus-21 Nexus-21-1066Mt-S-Interposer-Users-Manual-494957 nexus-21-1066mt-s-interposer-users-manual-494957 nexus-21 pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 91

- 1.0 OVERVIEW

- 2.0 SOFTWARE INSTALLATION

- 3.0 CONNECTING to the NEX-DDR3INTR-THIN INTERPOSER

- 4.0 CLOCK SELECTION

- 5.0 CONFIGURING FOR READ / WRITE DATA ACQUISITION

- 5.1 A Note About the Different Data Groups

- 5.2 MagniVu Signals

- 5.3 Adjusting Input Thresholds for Proper Data Acquisition

- 5.4 DDR3 and DDR3SPA

- 5.5 Selecting B_DDR3E_XX Read Data Sample Points

- 5.6 Selecting B_DDR3D_XX Write Data Sample Points

- 5.7 B_DDR3D_XX Support Setup

- 5.8 Setting B_DDR3D_3A Read Data Sample Points

- 6.0 VIEWING DATA

- 7.0 HINTS & TIPS

- APPENDIX A – How DDR Data is Clocked

- APPENDIX B - Considerations

- APPENDIX C – 240-pin DDR3 DIMM Pinout

- APPENDIX D –Data Flow Through the Probes (coax cable to chan

- APPENDIX E – B_DDR3D_2D Support Pinout, DIMM Slot 0

- APPENDIX F – B_DDR3_2G Support Pinout, DIMM Slot 0 Auxiliary

- APPENDIX G – B_DDR3D_3A Support Pinout, DIMM Slot 1

- APPENDIX H – Data Group / Data Byte / Strobe Cross-Reference

- APPENDIX I – NEX-DDR3INTR-THIN Silkscreen

- APPENDIX J – Keep out area

- APPENDIX K – Simulation Model

- APPENDIX L - References

- APPENDIX M - Support

DDR3THIN-MN-XXX 1 Doc. Rev. 1.11

NEX-DDR3INTR-THIN

DDR3 800/1066MT/s Interposer

For use with the TLA7BB4 Logic Analyzer

Modules

Including these Software Support packages:

B_DDR3D_2D (Single/Dual/Quad Rank, single slot with Selective Clocking)

*B_DDR3D_2G (2 or 3 DIMM slots, two Rank @ 800MT/s)

*B_DDR3D_3A (2 DIMM slots, two Rank @ 1066MT/s)

* Optional Software

Copyright © 2007 Nexus Technology, Inc. All rights reserved.

Contents of this publication may not be reproduced in any form without

the written permission of Nexus Technology, Inc.

Brand and product names used throughout this manual are the trademarks

of their respective holders.

DDR3THIN-MN-XXX 2 Doc. Rev. 1.11

Product Warranty

Due to wide variety of possible customer target implementations, this product has a 30 day

acceptance period by the customer from the date of receipt. If the customer does not contact

Nexus Technology within 30 days of the receipt of the product, it will be said that the customer

has accepted the product. If the customer is not satisfied with this product, they may return it

within 30 days for a refund.

This Nexus Technology product has a warranty against defects in material and workmanship for a

period of 1 year from the date of shipment. During the warranty period, Nexus Technology will,

at its option, either replace or repair products proven to be defective. For warranty service or

repair, this product must be returned to the factory.

For products returned to Nexus Technology for warranty service, the Buyer shall prepay shipping

charges to Nexus Technology and Nexus Technology shall pay shipping charges to return the

product to the Buyer. However, the Buyer shall pay all shipping charges, duties, and taxes for

products returned to Nexus Technology from another country.

Nexus Technology warrants that its software and hardware designated by Nexus Technology for

use with an instrument will execute its programming instructions when properly installed on that

instrument. Nexus Technology does not warrant that the operation of the hardware or software

will be uninterrupted or error-free.

Limitation of Warranty

The foregoing warranty shall not apply to defects resulting from improper or inadequate

maintenance by the Buyer, Buyer-supplied software or interfacing, unauthorized modification or

misuse, operation outside of the environmental specifications for the product, or improper site

preparation or maintenance. NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. NEXUS

TECHNOLOGY SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF

MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

Exclusive Remedies

THE REMEDIES PROVIDED HERIN ARE BUYER’S SOLE AND EXCLUSIVE REMEDIES.

NEXUS TECHNOLOGY SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT,

SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON

CONTRACT, TORT OR ANY OTHER LEGAL THEORY.

Software License Agreement

IMPORTANT – Please read this license agreement carefully before opening the CD case. Rights

in the software are offered only on the condition that the customer agrees to all terms and

conditions of the license agreement. Opening the CD case indicates your acceptance of these

terms and conditions. If you do not agree to the licensing agreement, you may return the

unopened package for a full refund.

DDR3THIN-MN-XXX 3 Doc. Rev. 1.11

License Agreement

In return for payment for this product, Nexus Technology grants the Customer a SINGLE user

LICENSE in the software subject to the following:

Use of the Software:

- Customer may use the software on only one Tektronix mainframe logic analysis system at

any given time

- Customer may make copies or adaptations of the software (see Copies and Adaptations below

for more information)

- Customer may NOT reverse assemble or decompile the software

Copies and Adaptations:

- Are allowed for archival purpose only

- When copying for adaptation is an essential step in the use of the software with the logic

analyzer and/or logic analysis mainframe so long as the copies and adaptations are used in no

other manner. Customer has no right to copy software unless it acquires an appropriate

license to reproduce from Nexus Technology.

- Customer agrees that it does not have any title or ownership of the software, other than the

physical media.

Ownership:

- Customer acknowledges and agrees that the software is copyrighted and protected under the

copyright laws.

- Transfer of the right of ownership shall only be done with the consent of Nexus Technology.

Sublicensing and Distribution:

- Customer may not sublicense the software or distribute copies of the software to the public in

physical media or by electronic means or any other means without the prior written consent

of Nexus Technology.

Compliance with WEEE and RoHS Directives

This product is subject to European Union regulations on Waste Electrical and Electronics

Equipment. Return to Nexus Technology for recycle at end of life. Costs associated with the

return to Nexus Technology are the responsibility of the sender.

DDR3THIN-MN-XXX 4 Doc. Rev. 1.11

TABLE OF CONTENTS

1.0 OVERVIEW ........................................................................................................................... 9

1.1 General Information ............................................................................................................ 9

1.2 Software Package description..............................................................................................9

1.3 Eye size required ............................................................................................................... 11

2.0 SOFTWARE INSTALLATION........................................................................................... 11

3.0 CONNECTING to the NEX-DDR3INTR-THIN INTERPOSER ........................................ 12

3.1 General .............................................................................................................................. 12

3.2 B_DDR3D_2D Support..................................................................................................... 12

3.3 B_DDR3D_2G Support..................................................................................................... 12

3.4 B_DDR3D_3A Support..................................................................................................... 13

3.5 Short “LEASH” probes ..................................................................................................... 15

3.5.1 Samtec connector on the LEASH probe pins ............................................................ 16

3.5.2 LEASH probe to NEX-PRB1X/2X connection......................................................... 17

3.5.3 Alternate use of NEX-PRB1X or NEX-PRB2X probes ............................................ 17

3.6 Slot Numbering............................................................................................................. 18

3.7 Display Groups not in Tables 1,2 or 3............................................................................... 39

4.0 CLOCK SELECTION .......................................................................................................... 40

4.1 B_DDR3D_2D Clocking Selections ................................................................................. 40

4.2 B_DDR3D_2G Clocking Selections ................................................................................. 41

4.3 B_DDR3D_3A Clocking Selections ................................................................................. 43

5.0 CONFIGURING FOR READ / WRITE DATA ACQUISITION........................................ 44

5.1 A Note About the Different Data Groups.......................................................................... 44

5.2 MagniVu Signals ............................................................................................................... 44

5.3 Adjusting Input Thresholds for Proper Data Acquisition.................................................. 53

5.4 DDR3 and DDR3SPA ....................................................................................................... 53

5.5 Selecting B_DDR3E_XX Read Data Sample Points ........................................................ 53

5.6 Selecting B_DDR3D_XX Write Data Sample Points....................................................... 54

5.7 B_DDR3D_XX Support Setup.......................................................................................... 55

5.8 Setting B_DDR3D_3A Read Data Sample Points ............................................................ 62

6.0 VIEWING DATA................................................................................................................. 63

6.1 Viewing B_DDR3D_XX Data .......................................................................................... 63

6.2 Viewing Raw DDR3 Data using B_DDR3D_XX Supports......................................... 66

6.3 B_DDR3D_2A / 3A Mnemonics Description................................................................... 66

6.4 B_DDR3D_2G Mnemonics Description........................................................................... 66

6.5 Viewing Timing Data on the TLA .................................................................................... 67

7.0 HINTS & TIPS ..................................................................................................................... 69

7.1 Symbolic Triggering on a Command using B_DDR3D_XX Supports............................. 69

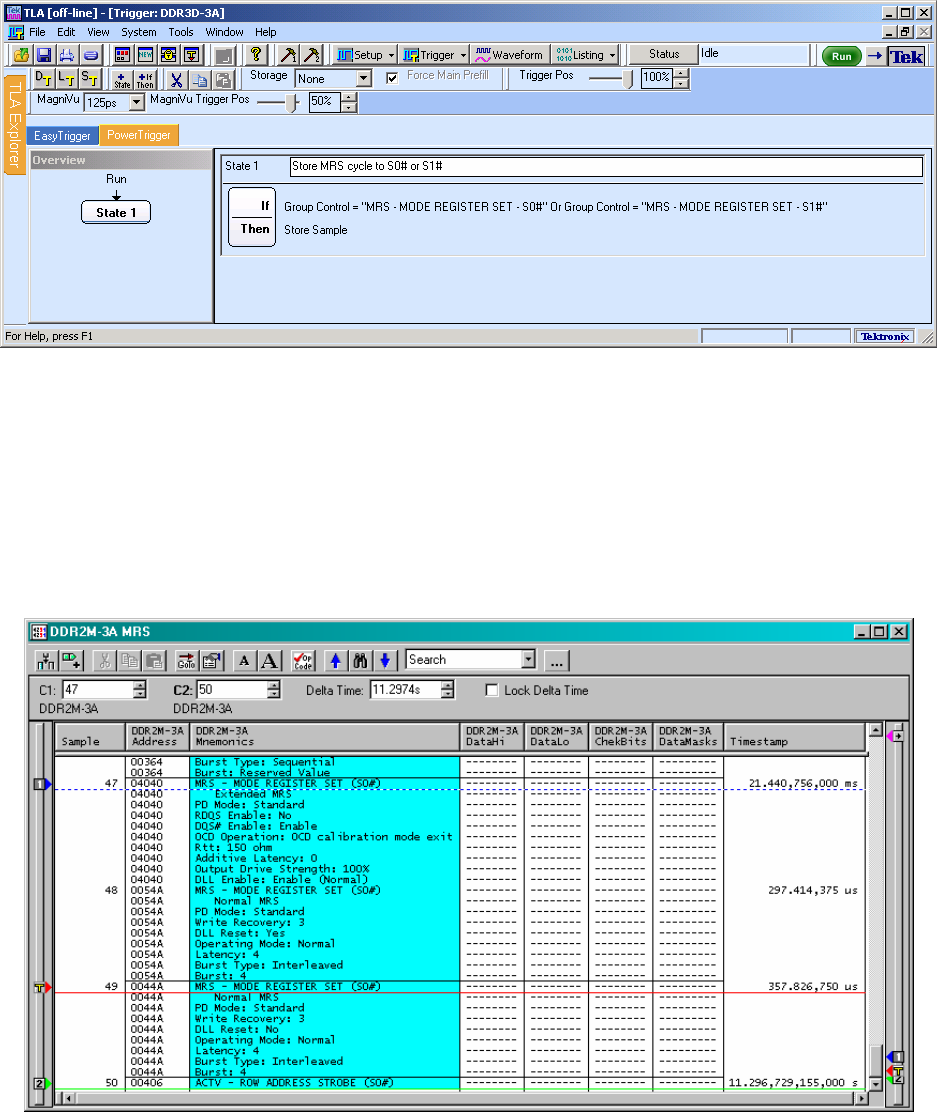

7.3 Capturing MRS (Mode Register Set) Cycles .................................................................... 70

7.4 Clock Capture quality........................................................................................................ 71

7.5 Thresholds ......................................................................................................................... 72

APPENDIX A – How DDR Data is Clocked ............................................................................... 73

A.1 Background....................................................................................................................... 73

A.2 DDR Acquisition - General .............................................................................................. 73

A.3 B_DDR3D_2D / 2G / 3A Data Acquisition ..................................................................... 74

APPENDIX B - Considerations.................................................................................................... 75

B.1 NEX-DDR3INTR-THIN Bus Loading............................................................................. 75

B.2 DIMM connector location for best quality signal capture................................................ 75

DDR3THIN-MN-XXX 5 Doc. Rev. 1.11

B.3 TLA7BB4 Module to module skew.................................................................................. 75

APPENDIX C – 240-pin DDR3 DIMM Pinout ........................................................................... 76

APPENDIX D –Data Flow Through the Probes (coax cable to channel) .................................... 78

APPENDIX E – B_DDR3D_2D Support Pinout, DIMM Slot 0.................................................. 80

APPENDIX F – B_DDR3_2G Support Pinout, DIMM Slot 0 Auxiliary Signals ....................... 82

APPENDIX G – B_DDR3D_3A Support Pinout, DIMM Slot 1 ................................................. 84

APPENDIX H – Data Group / Data Byte / Strobe Cross-Reference............................................ 86

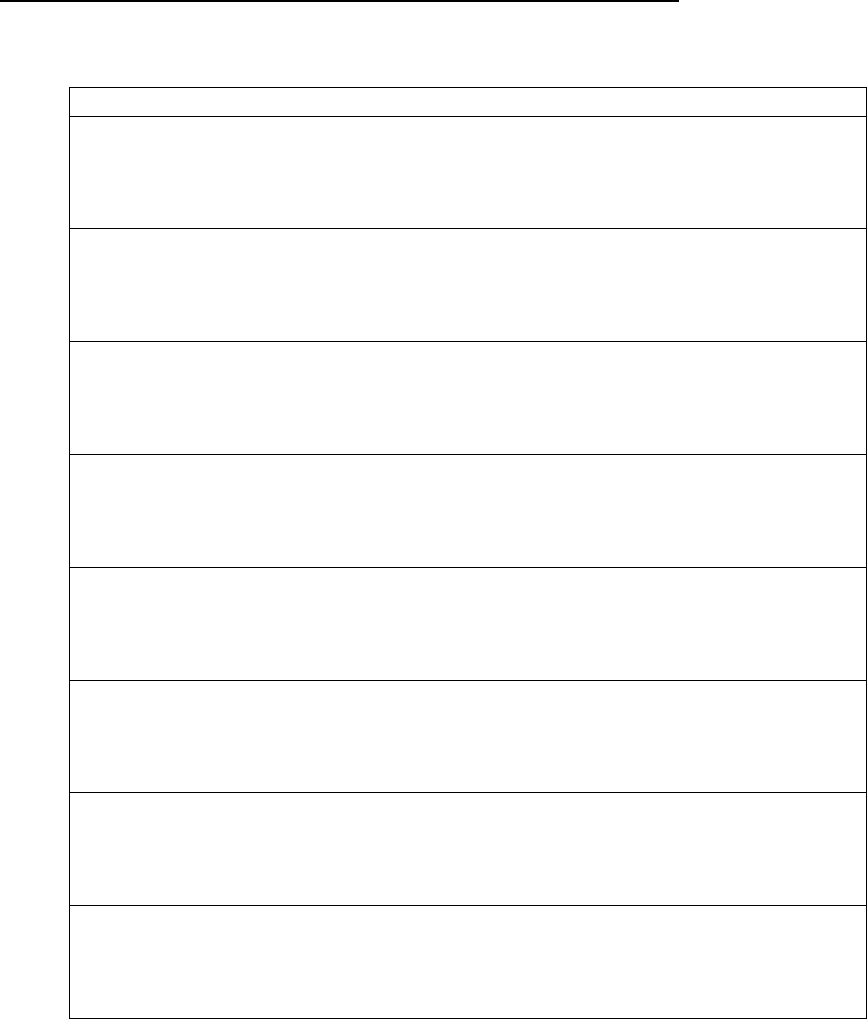

APPENDIX I – NEX-DDR3INTR-THIN Silkscreen................................................................... 87

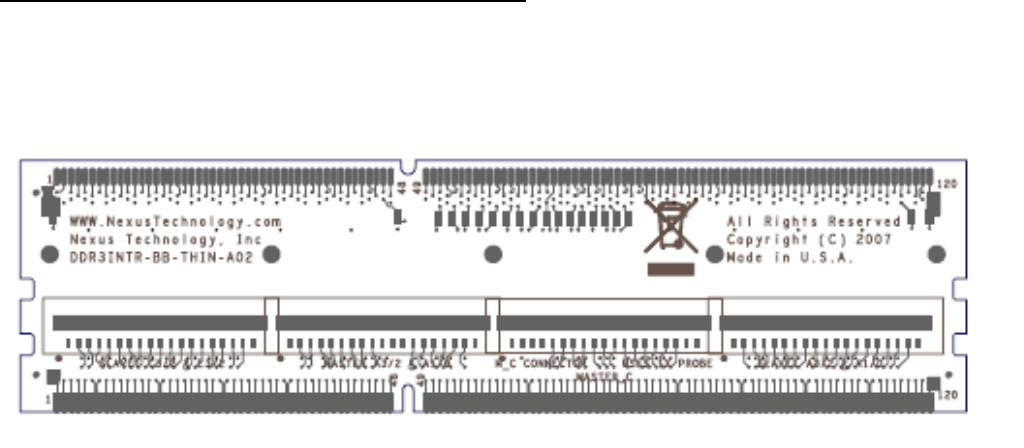

APPENDIX J – Keep out area ...................................................................................................... 88

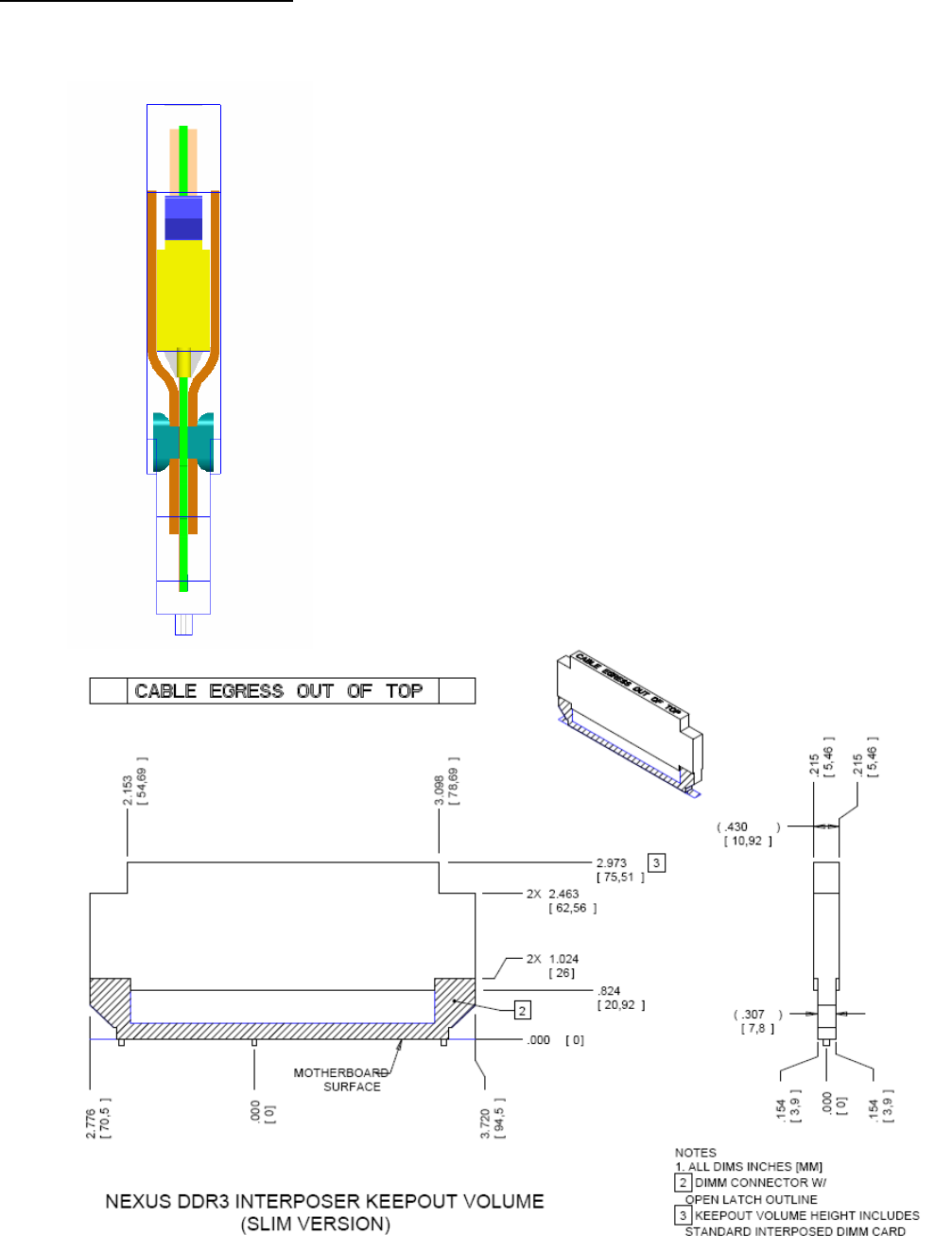

APPENDIX K – Simulation Model.............................................................................................. 89

APPENDIX L - References .......................................................................................................... 90

APPENDIX M - Support .............................................................................................................. 91

DDR3THIN-MN-XXX 6 Doc. Rev. 1.11

TABLE OF FIGURES

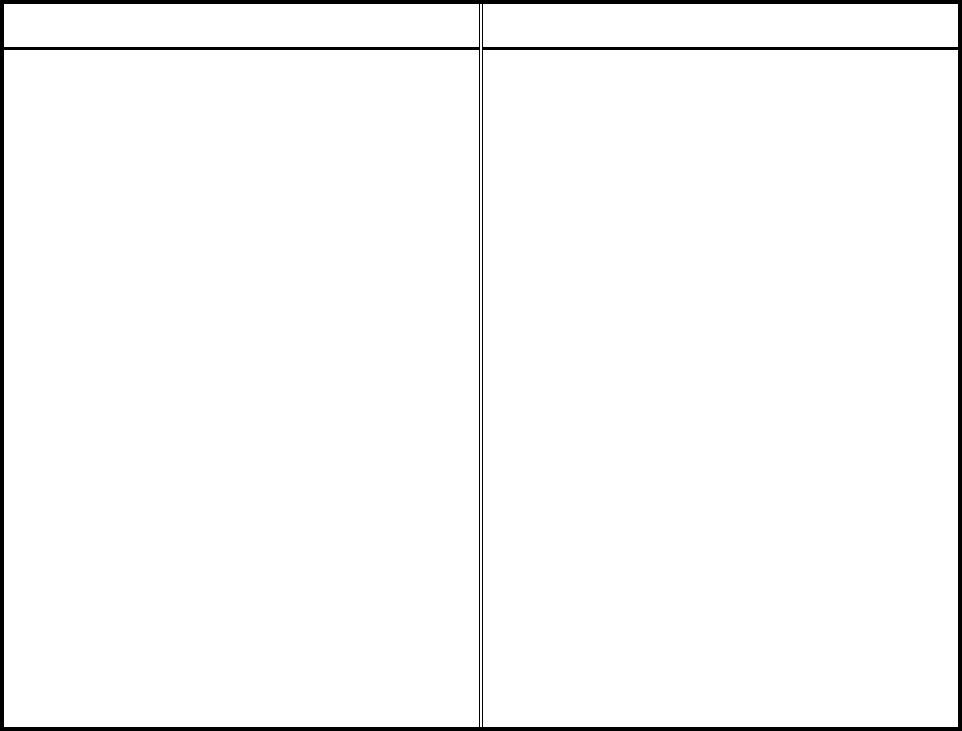

Figure 1 – Drawing of Interposer with probes attached ............................................................... 15

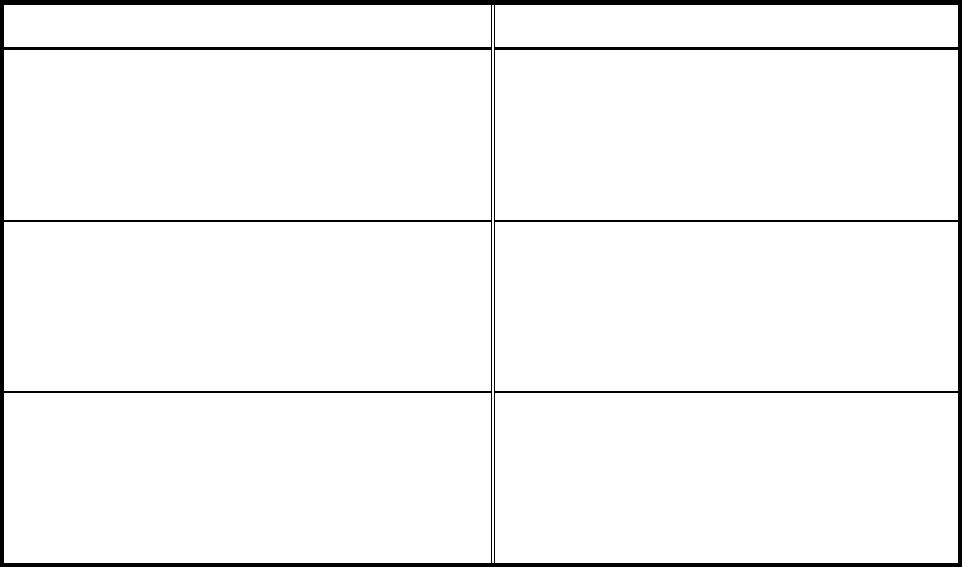

Figure 2 – Samtec connector on the LEASH probe...................................................................... 16

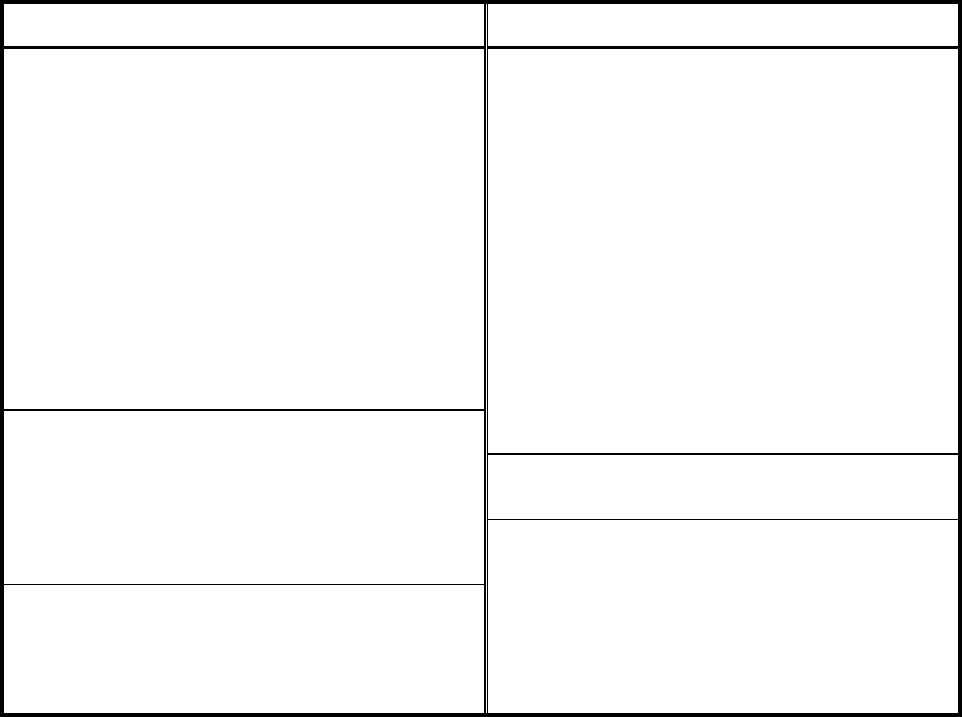

Figure 3 – LEASH probe to NEX-PRB1X/2X connection .......................................................... 17

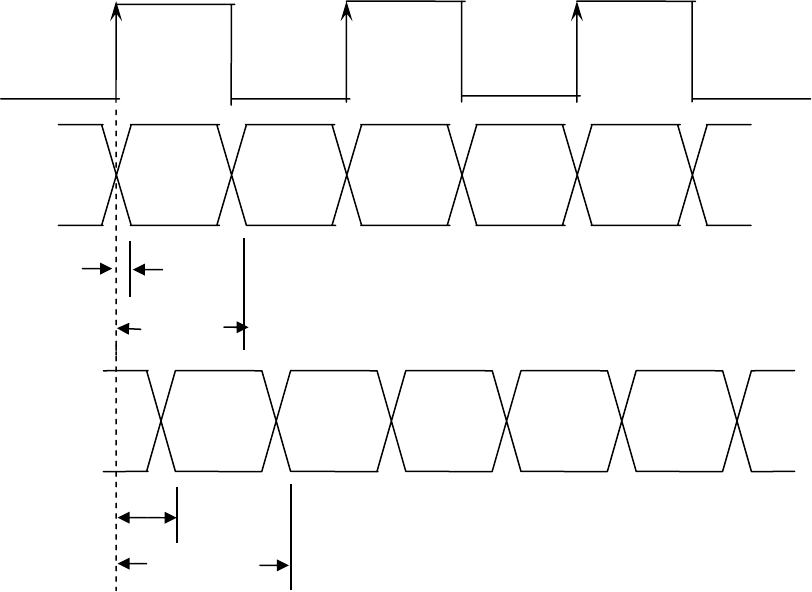

Figure 4 - Read Data Latency = CAS Latency + CAS Additive Latency + RDIMM (5+0+1) = 6

cycles) ........................................................................................................................................... 54

Figure 5 - Write Data Latency = CAS Write Latency + RDIMM (5+1) = 6 cycles..................... 54

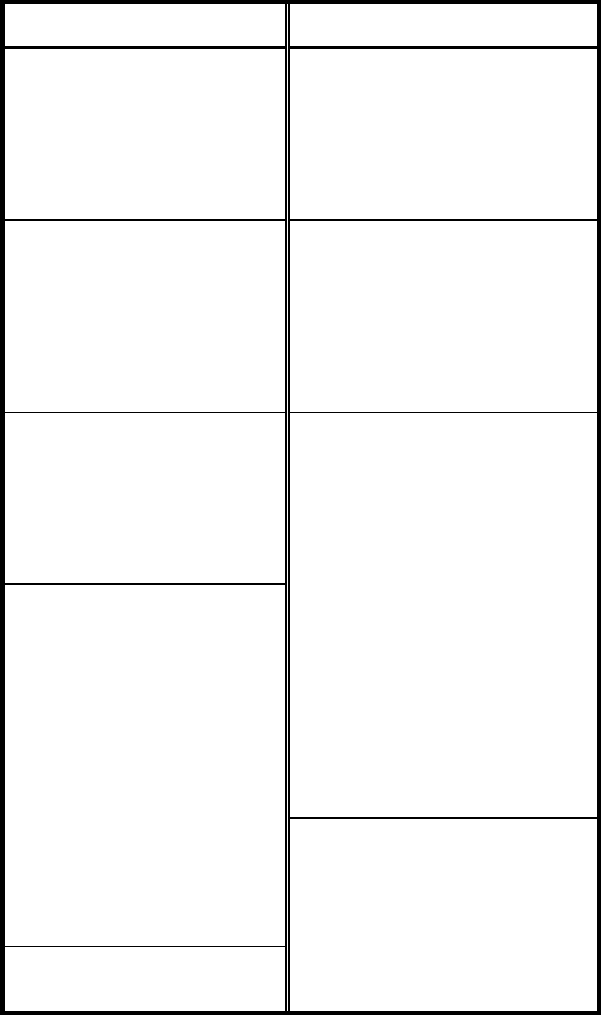

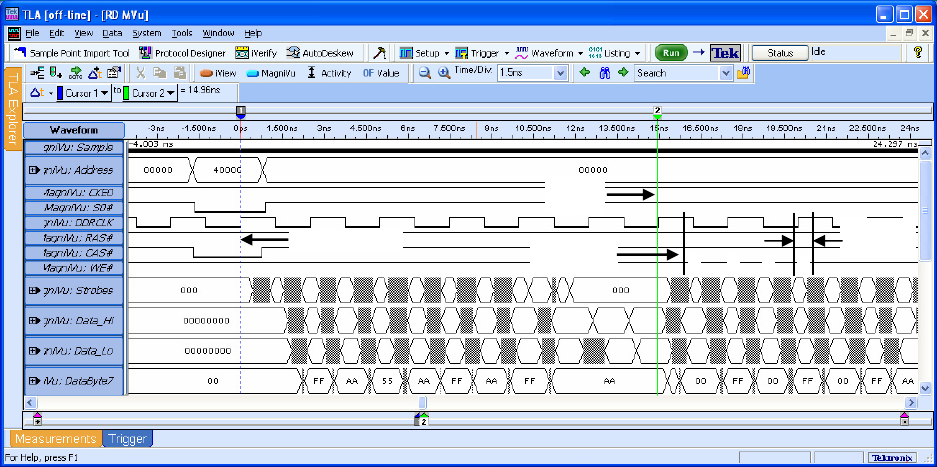

Figure 6 - Locating Minimum Valid B_DDR3D_XX Read Data Window ................................. 55

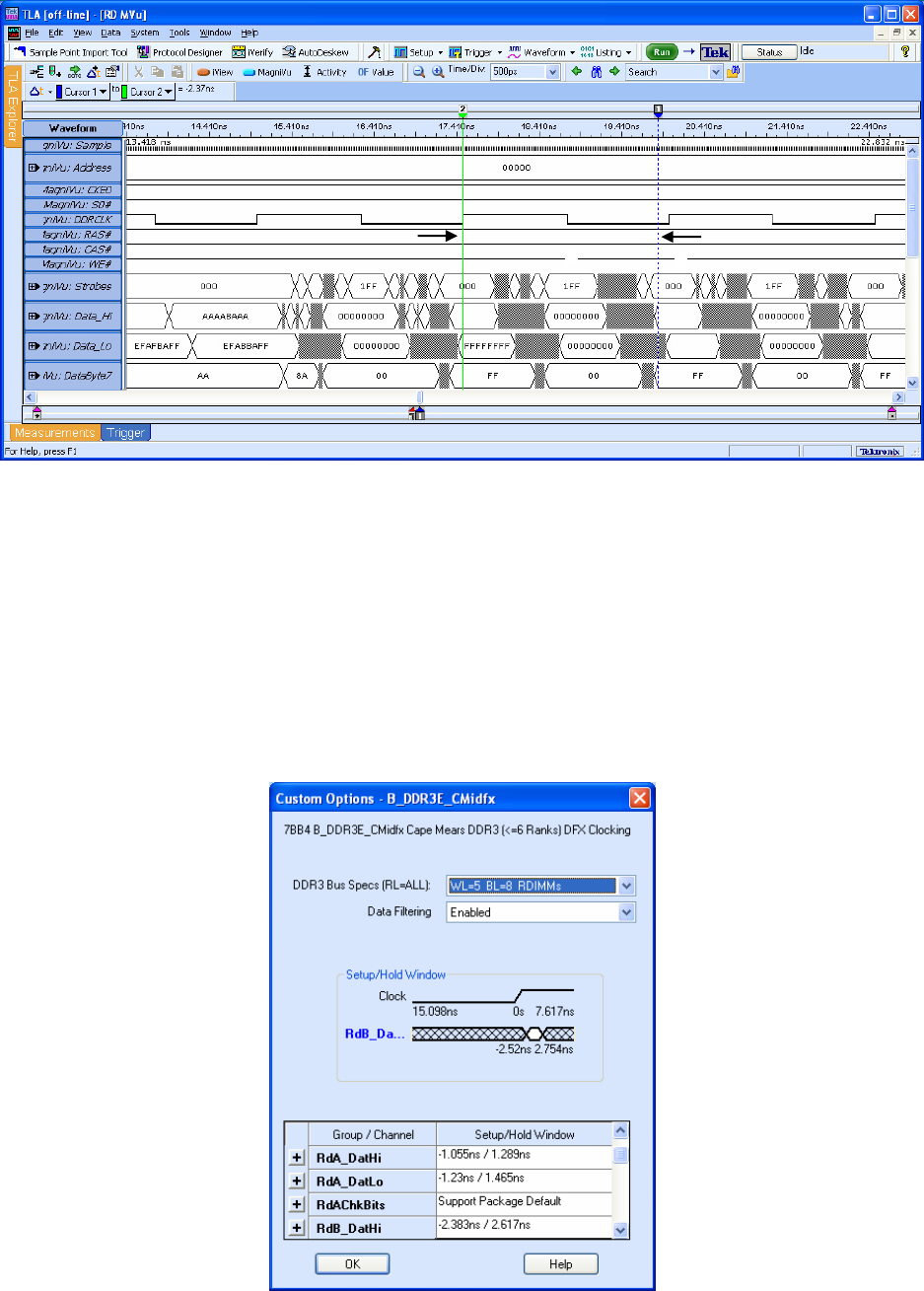

Figure 7 - Measuring B_DDR3D_XX RdA_DatHi / Lo Read Data Setup & Hold..................... 56

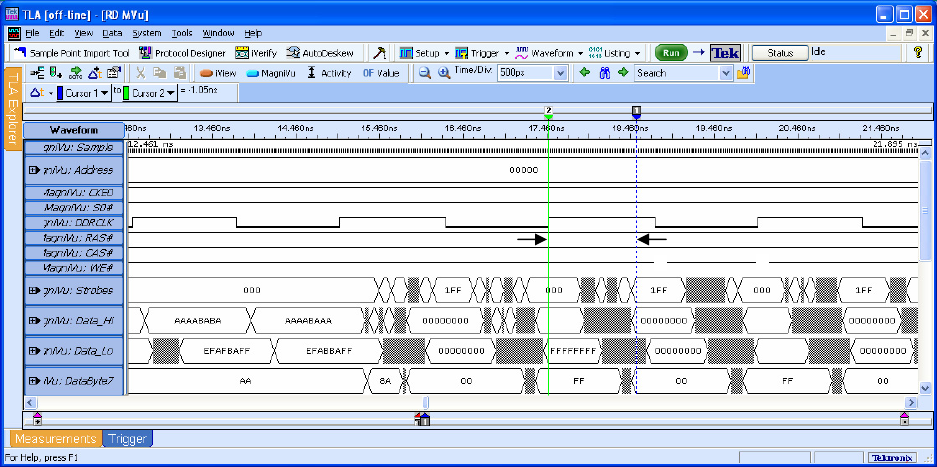

Figure 8 - Measuring B_DDR3D_XX RdB_DatHi / Lo Read Data Setup & Hold ..................... 57

Figure 9 - Setting B_DDR3D_XX RdA_DatHi / Lo and RdB_DatHi / Lo Sample Points ......... 57

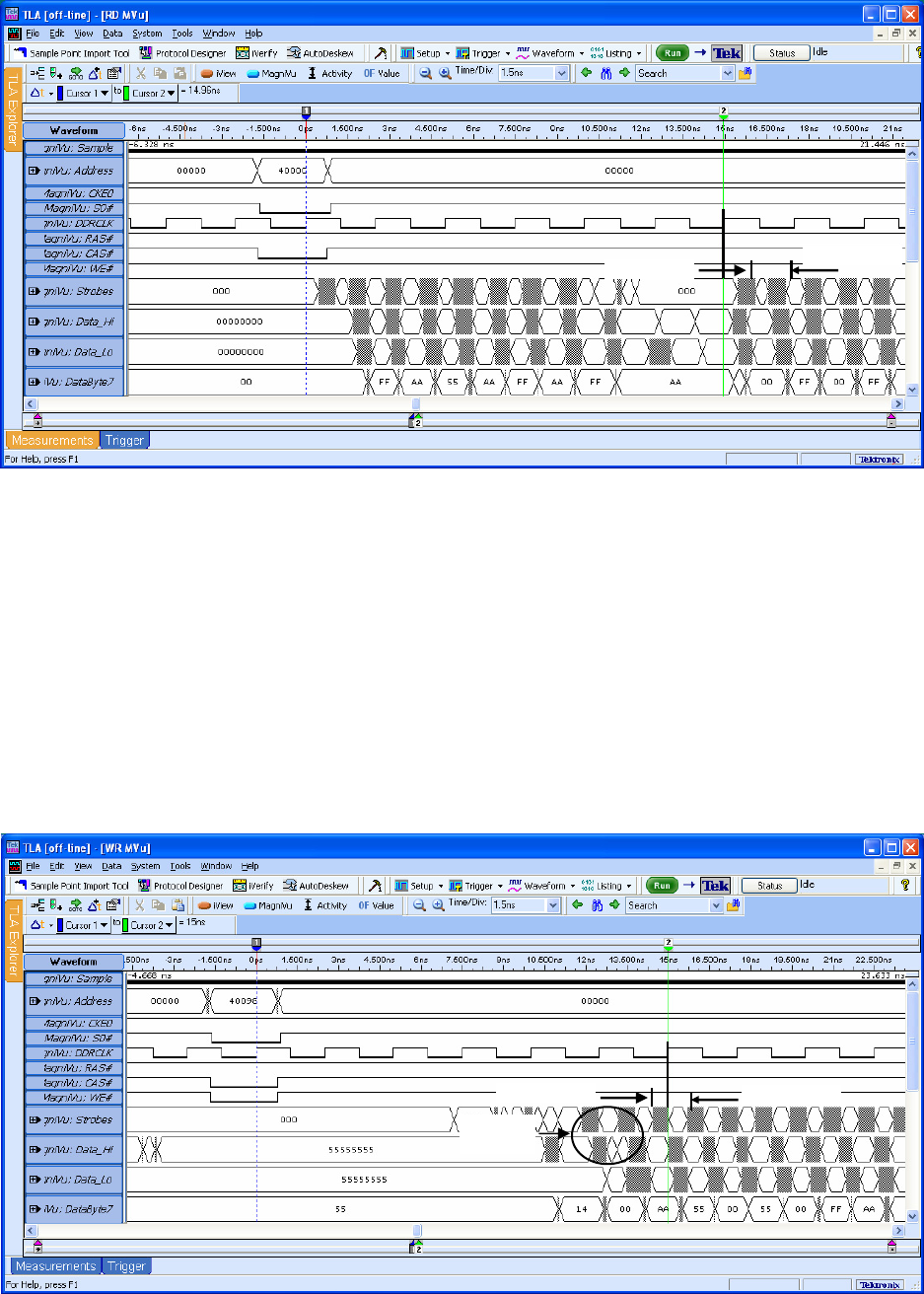

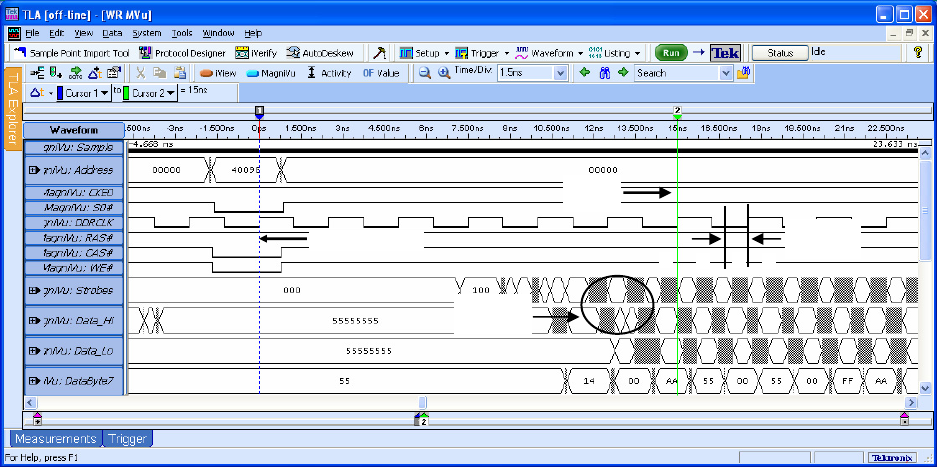

Figure 10 - Locating Minimum Valid B_DDR3D_XX Write Data Window .............................. 58

Figure 11 - Measuring B_DDR3D_XX WrA_DatHi / Lo Write Data Setup & Hold.................. 59

Figure 12 - Measuring B_DDR3D_XX WrB_DatHi / Lo Write Data Setup & Hold.................. 59

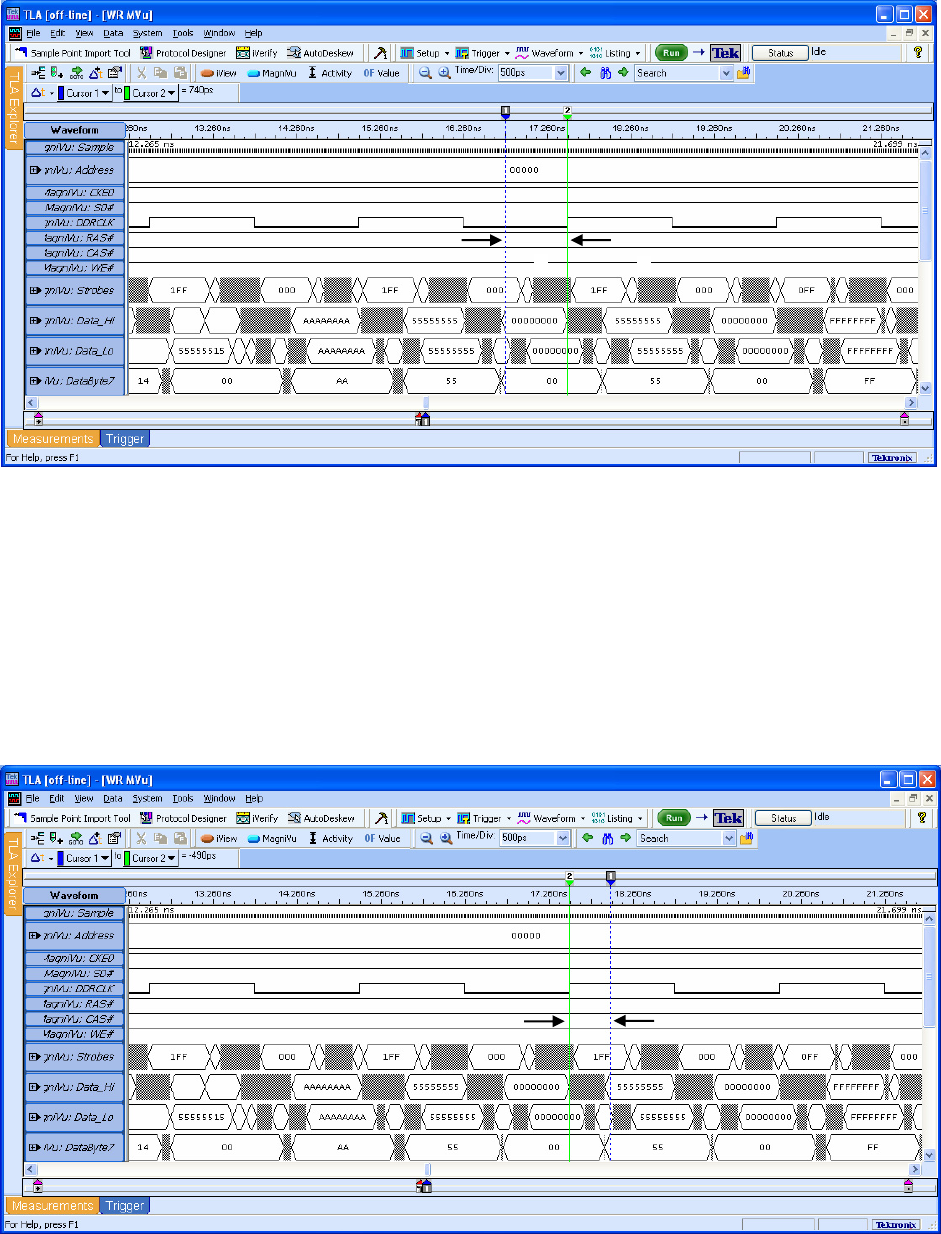

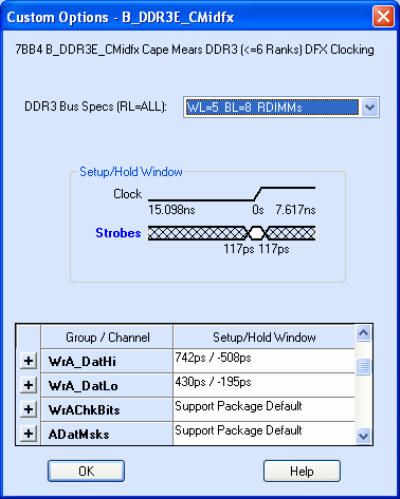

Figure 13 - Setting B_DDR3D_XX WrA_DatHi / Lo and WrB_DatHi / Lo Sample Points ...... 60

Figure 14 - Viewing Individual 8-bit Read Data Groups ............................................................. 61

Figure 15 - Setting Individual Setup & Hold Values for the 8-bit Read Data Groups................. 61

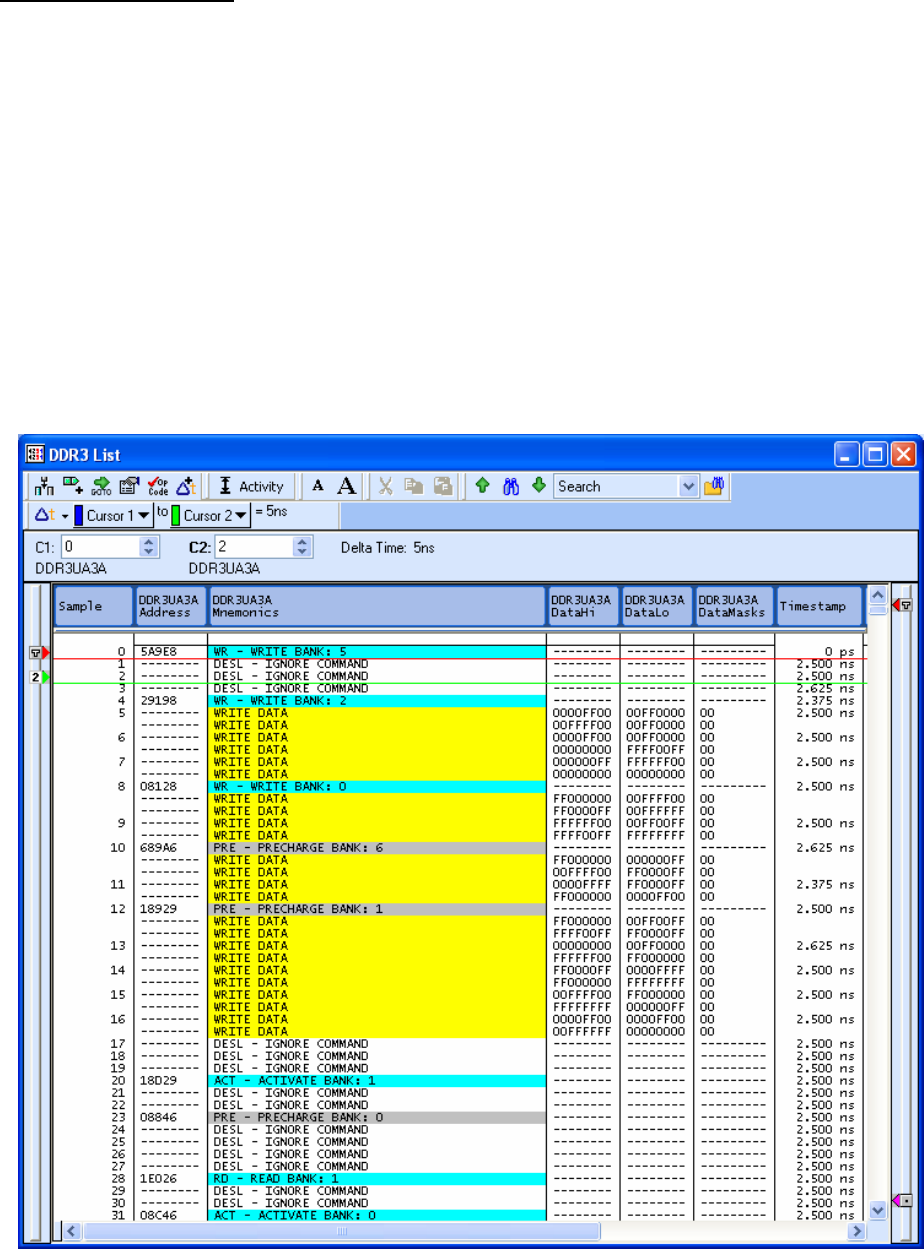

Figure 16 - B_DDR3D_XX Listing Display ................................................................................ 63

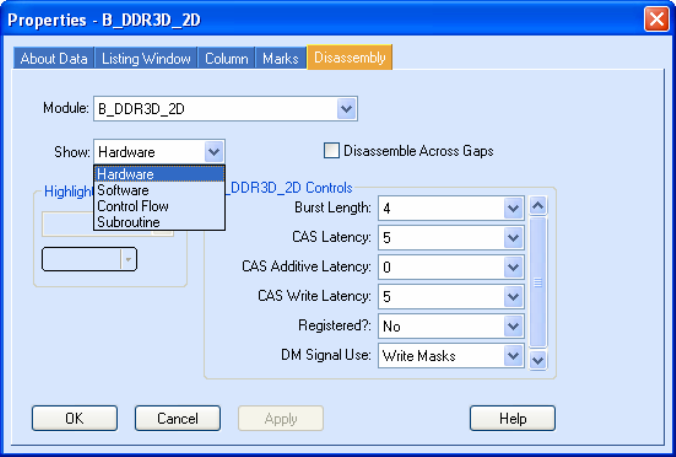

Figure 17 - Disassembly Properties .............................................................................................. 64

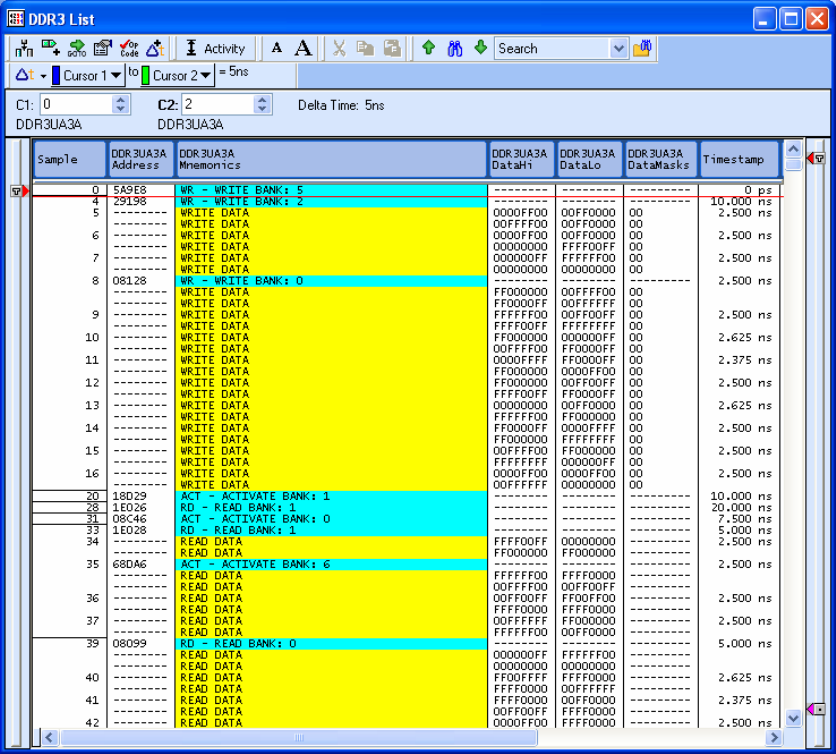

Figure 18 - B_DDR3D_XX Listing Display - Control Flow ....................................................... 65

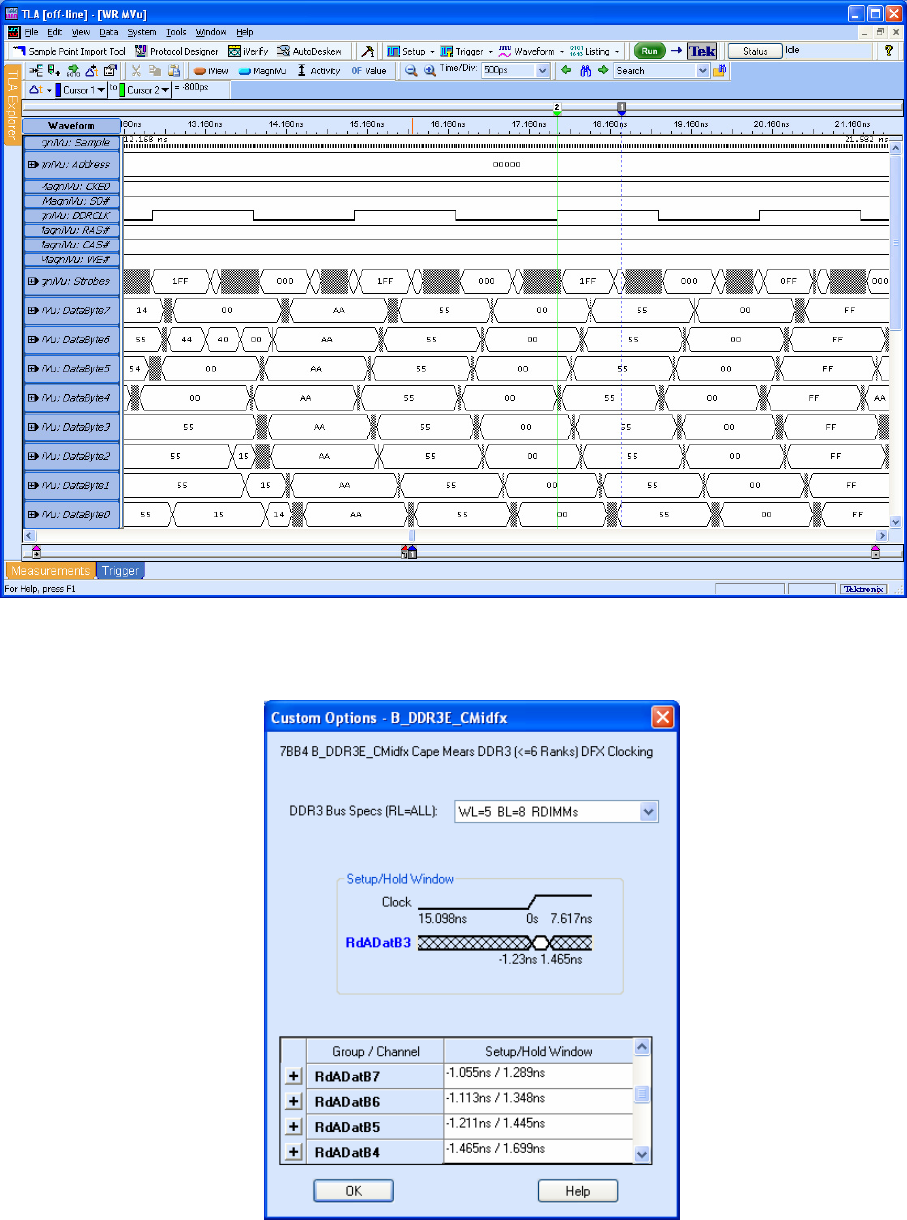

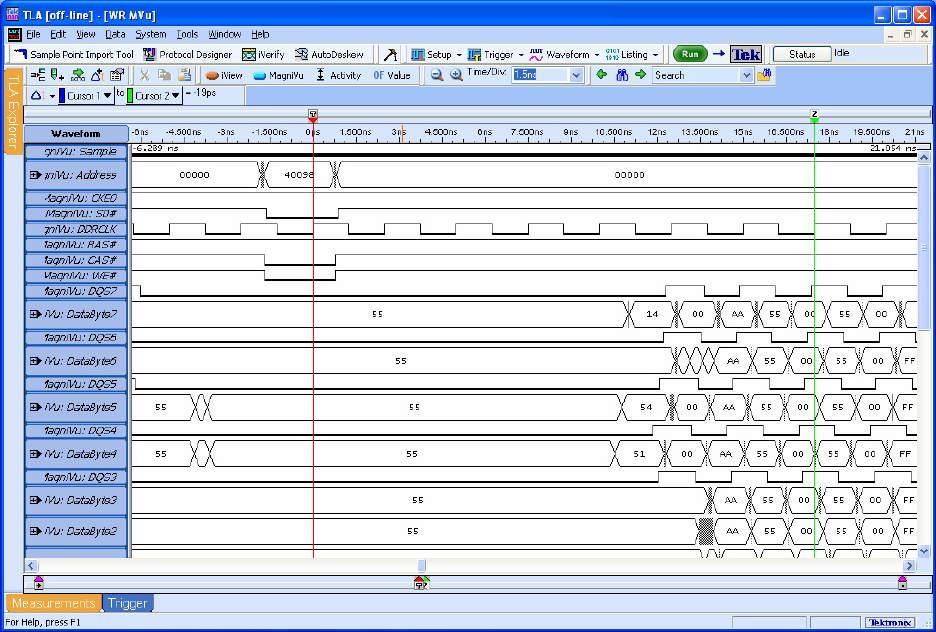

Figure 19 - B_DDR3D_XX MagniVu Display on TLA .............................................................. 68

Figure 20 - B_DDR3D_2D MRS Trigger .................................................................................... 71

Figure 21 - MRS Cycle Acquisition Disassembly........................................................................ 71

DDR3THIN-MN-XXX 7 Doc. Rev. 1.11

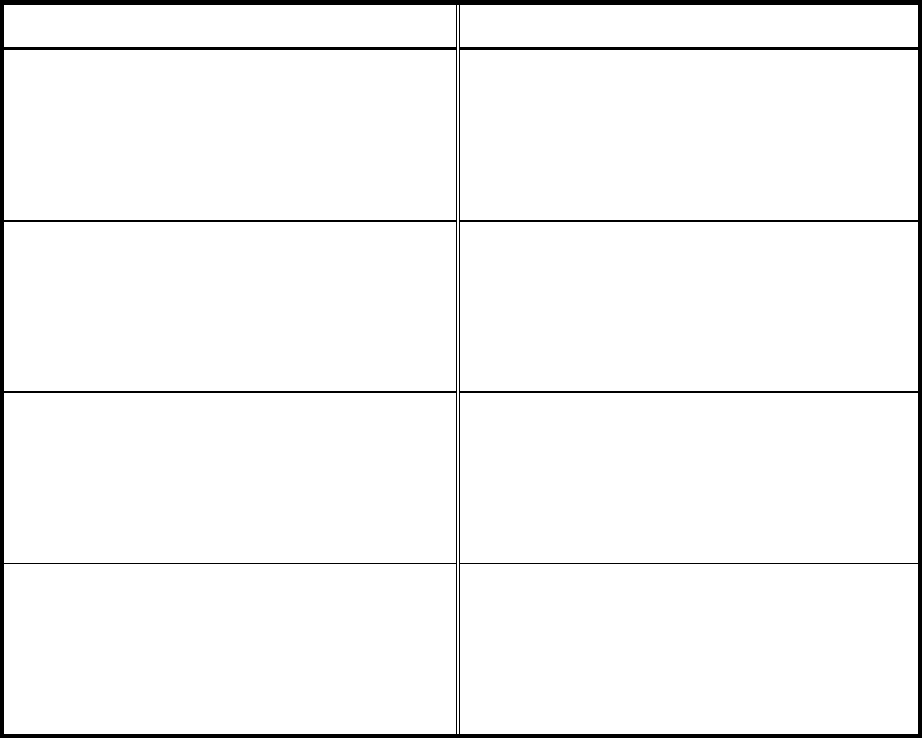

TABLE OF TABLES

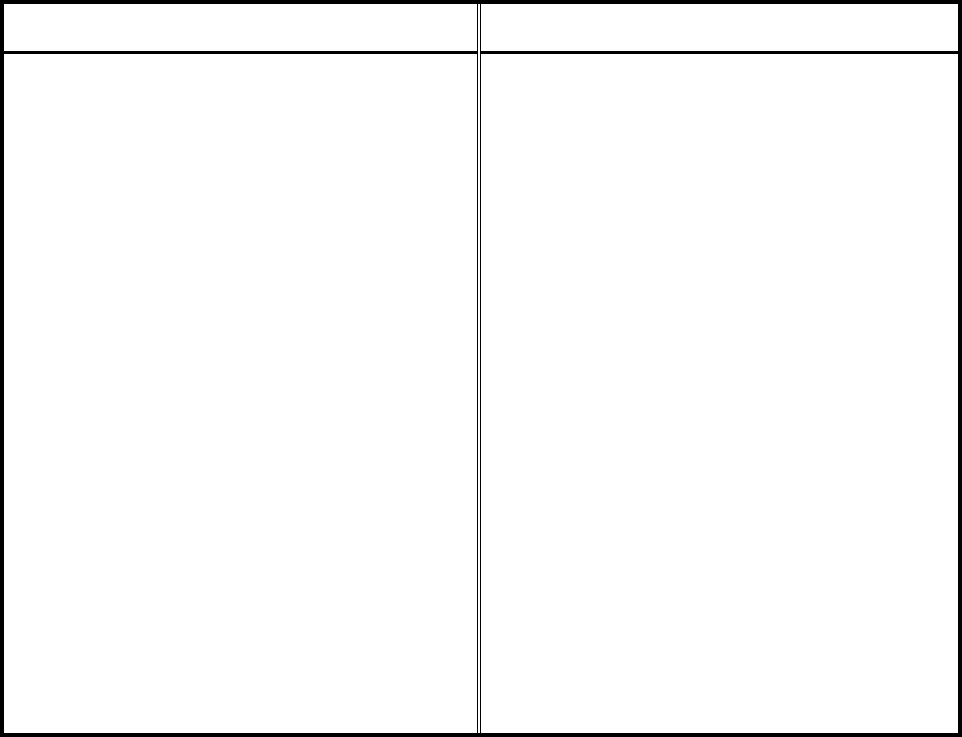

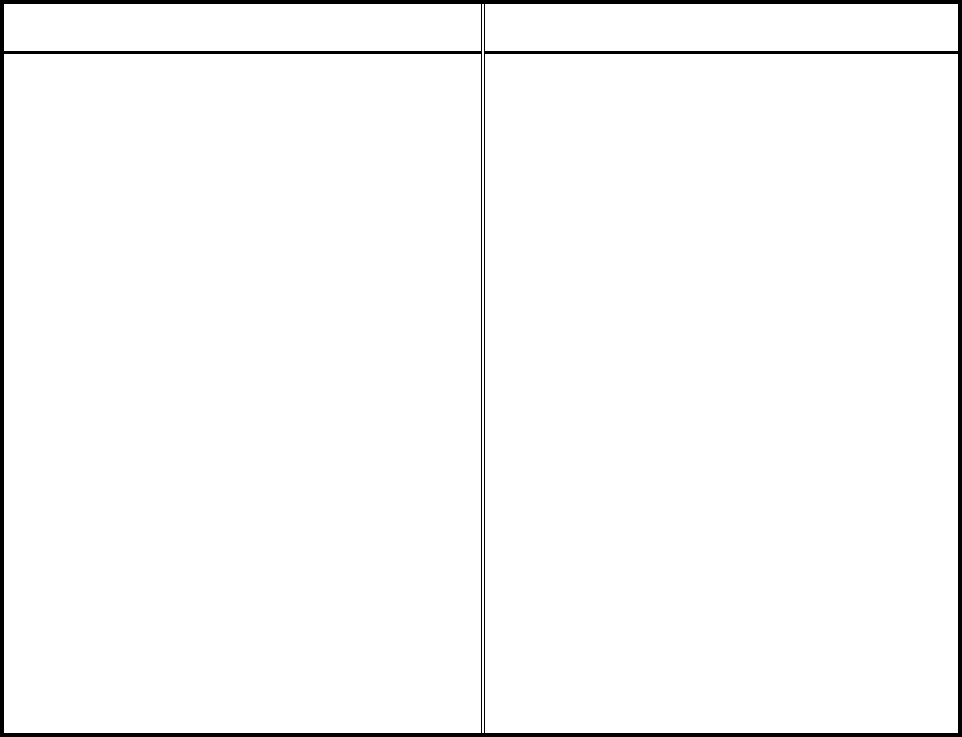

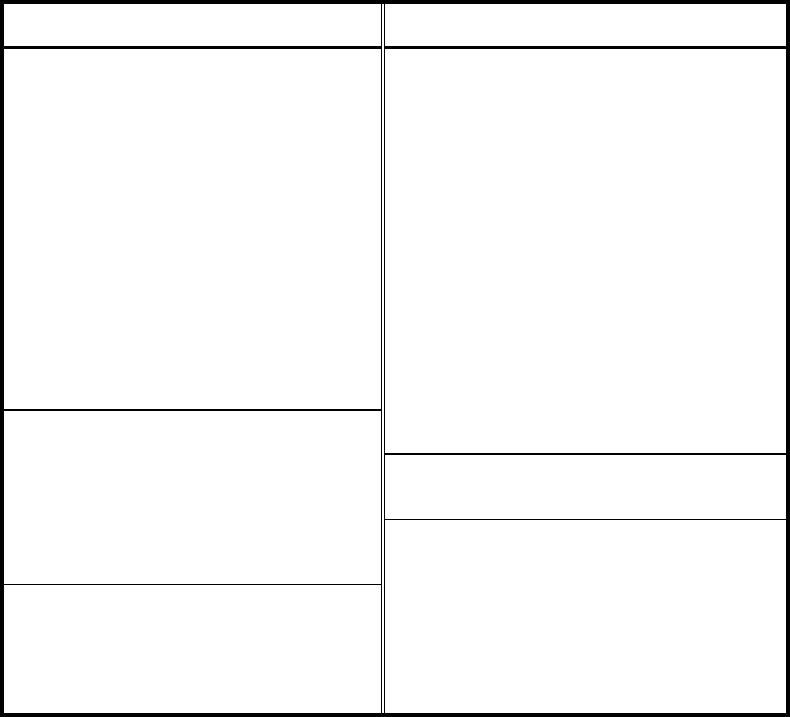

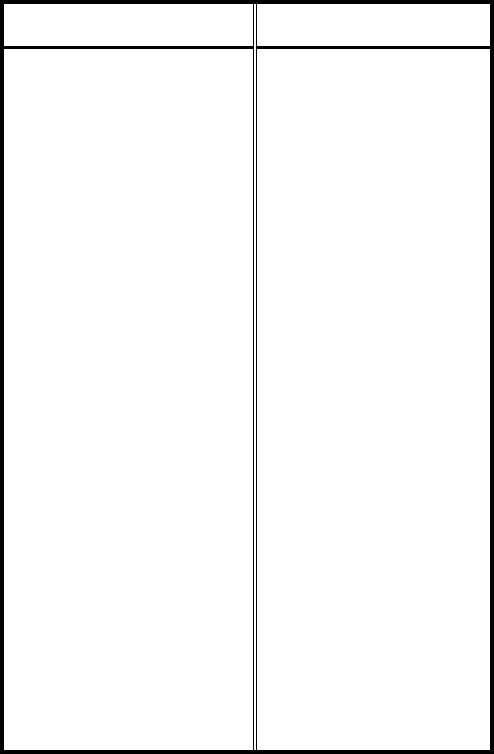

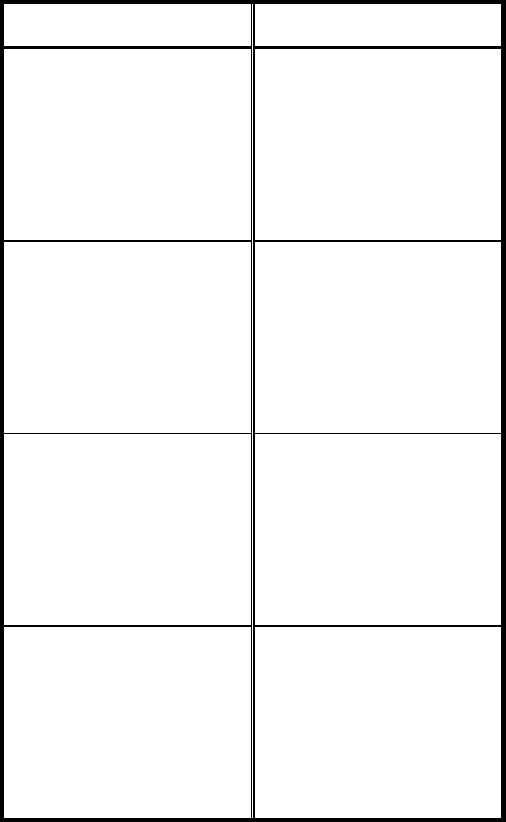

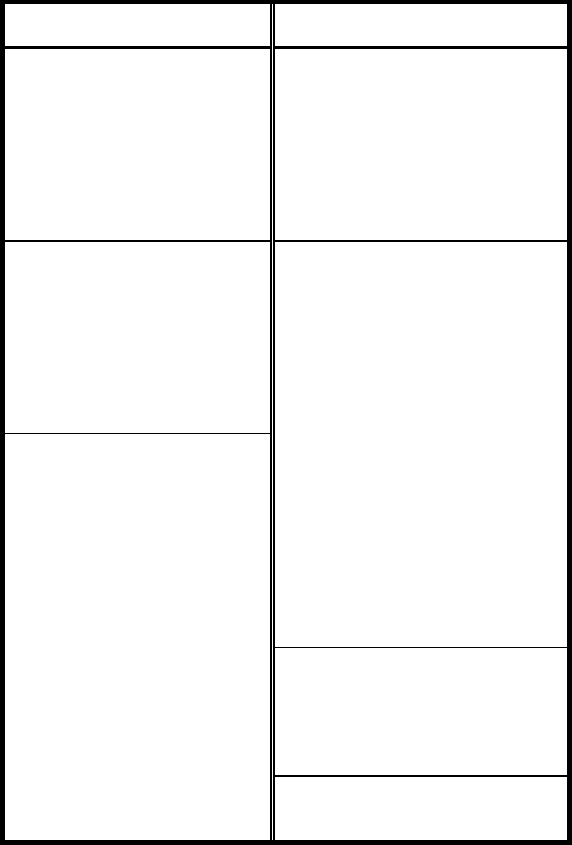

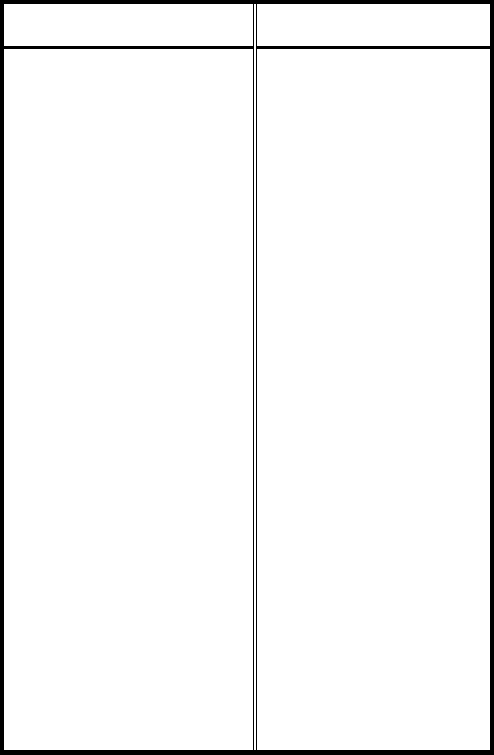

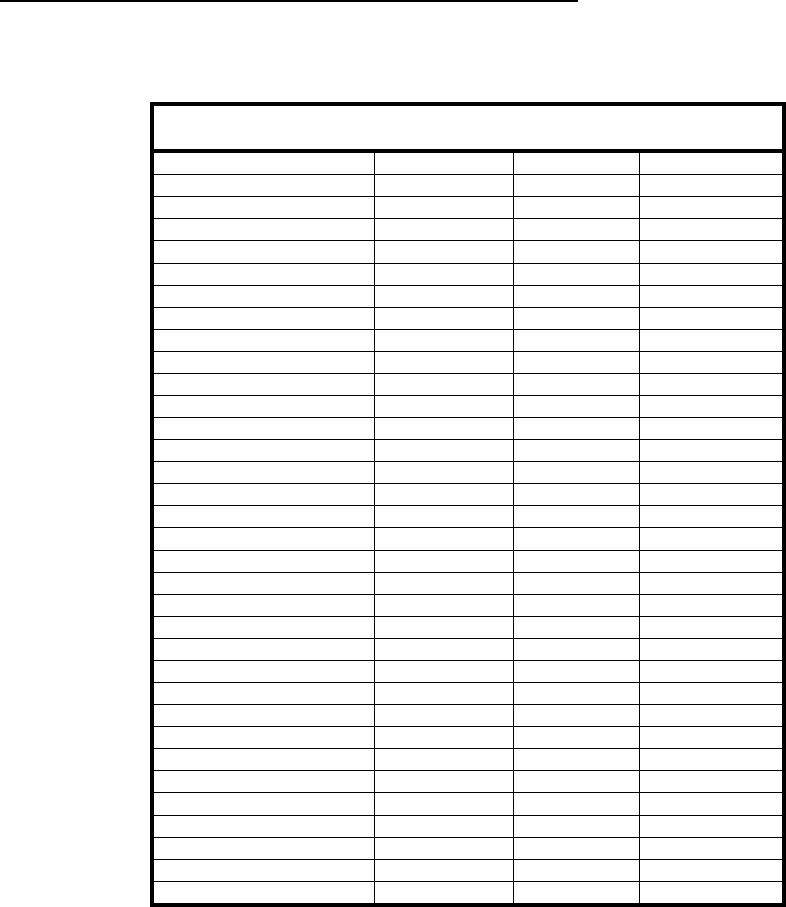

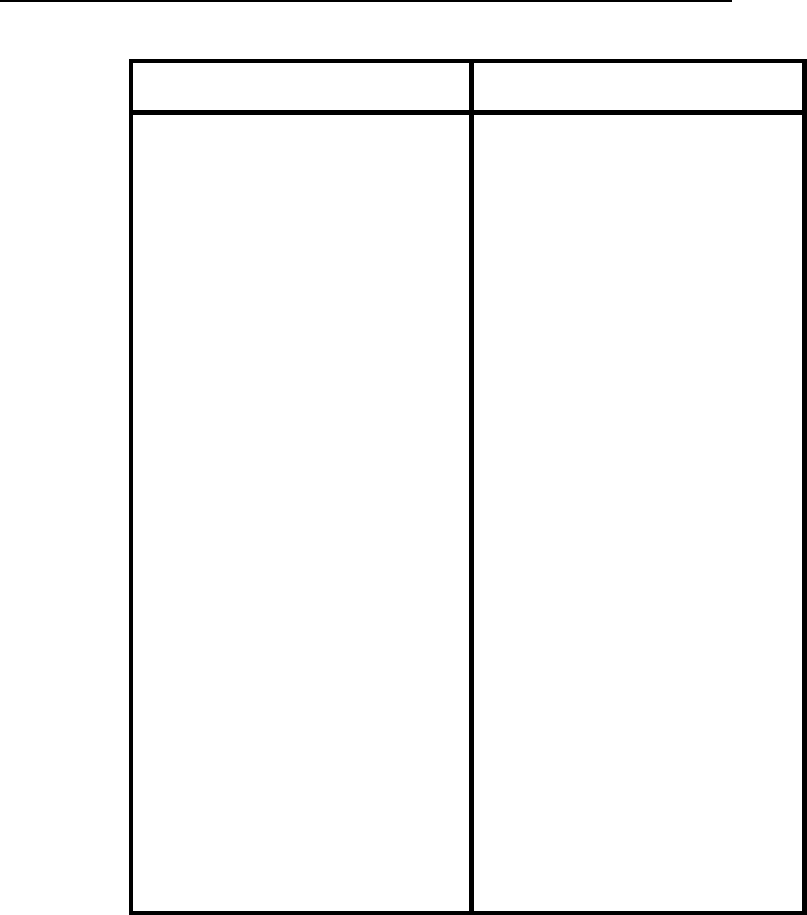

Table 1 - B_DDR3D_2D (<=1066MT/s Read and Write) TLA Channel Grouping.................... 19

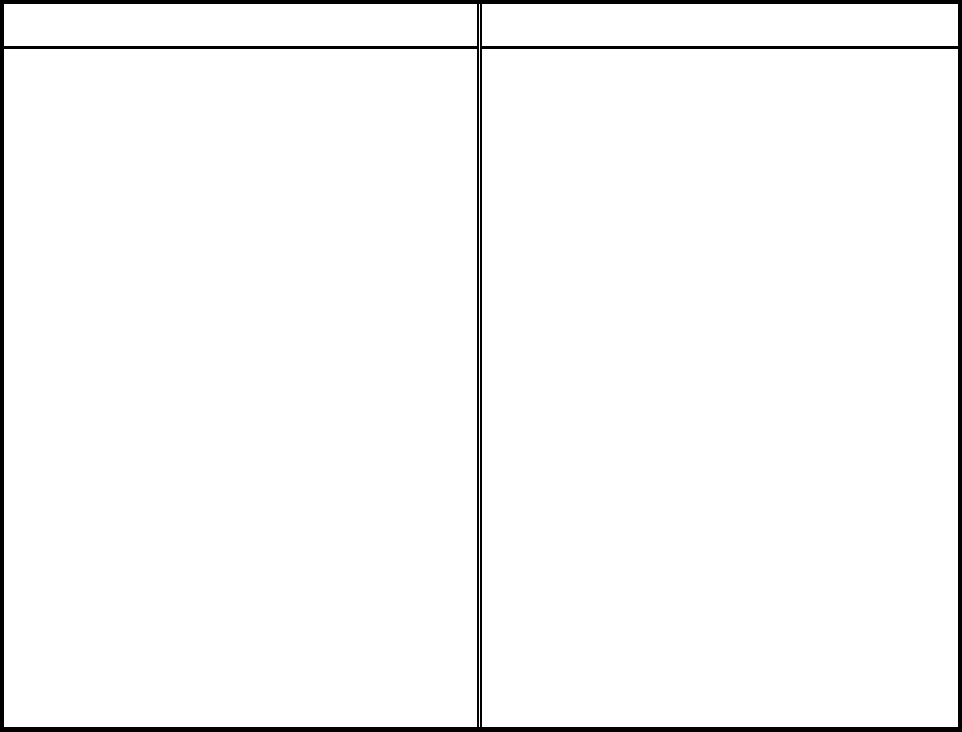

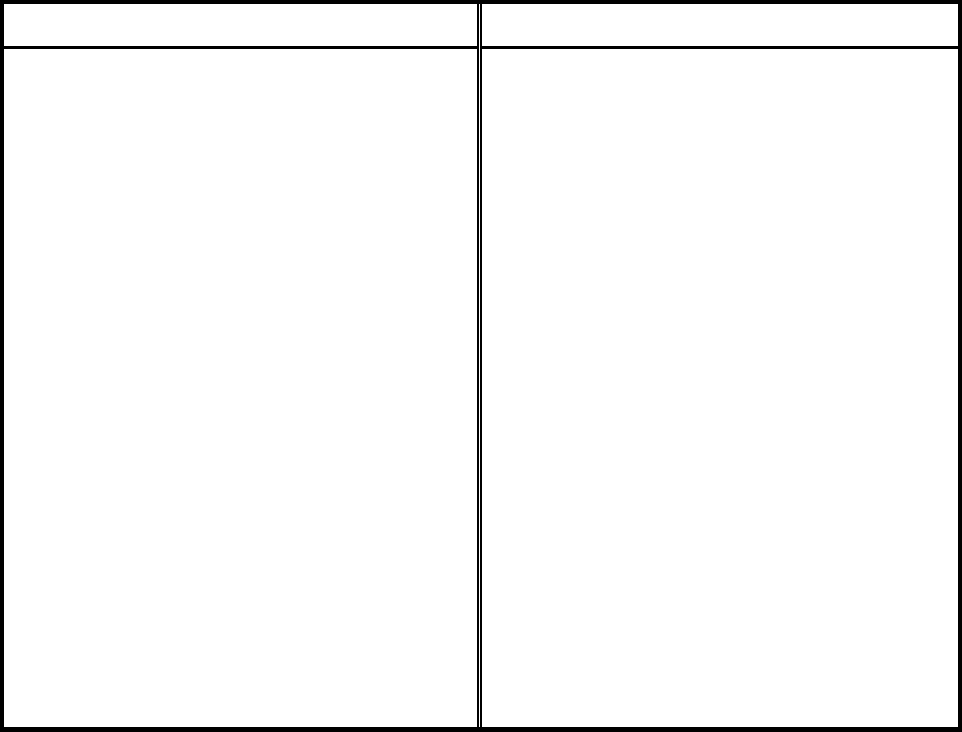

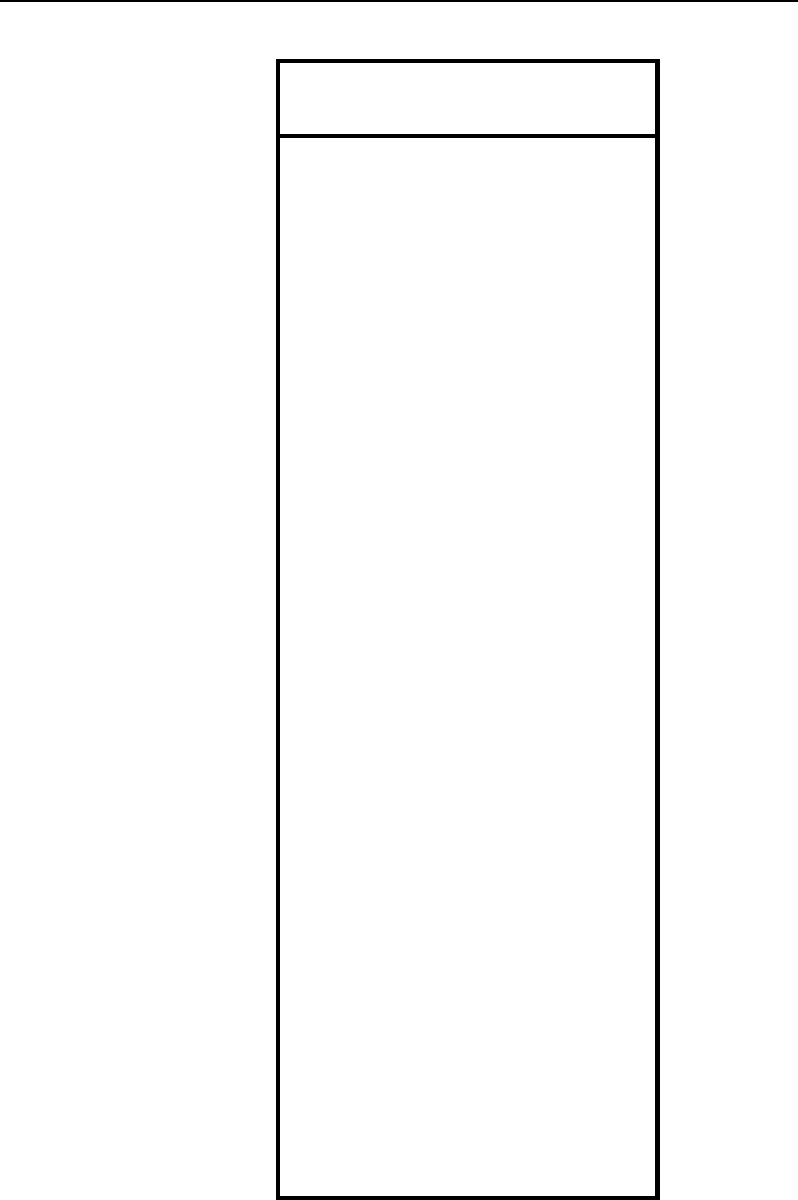

Table 2 - B_DDR3D_2G (<=1066MT/s Read and Write) TLA Channel Grouping.................... 25

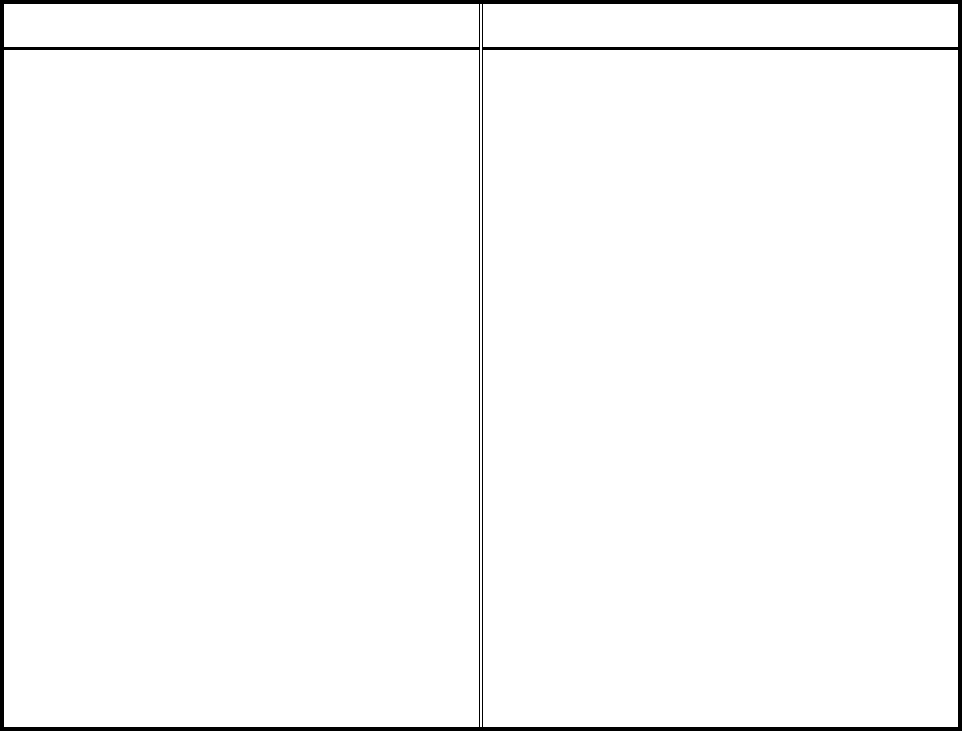

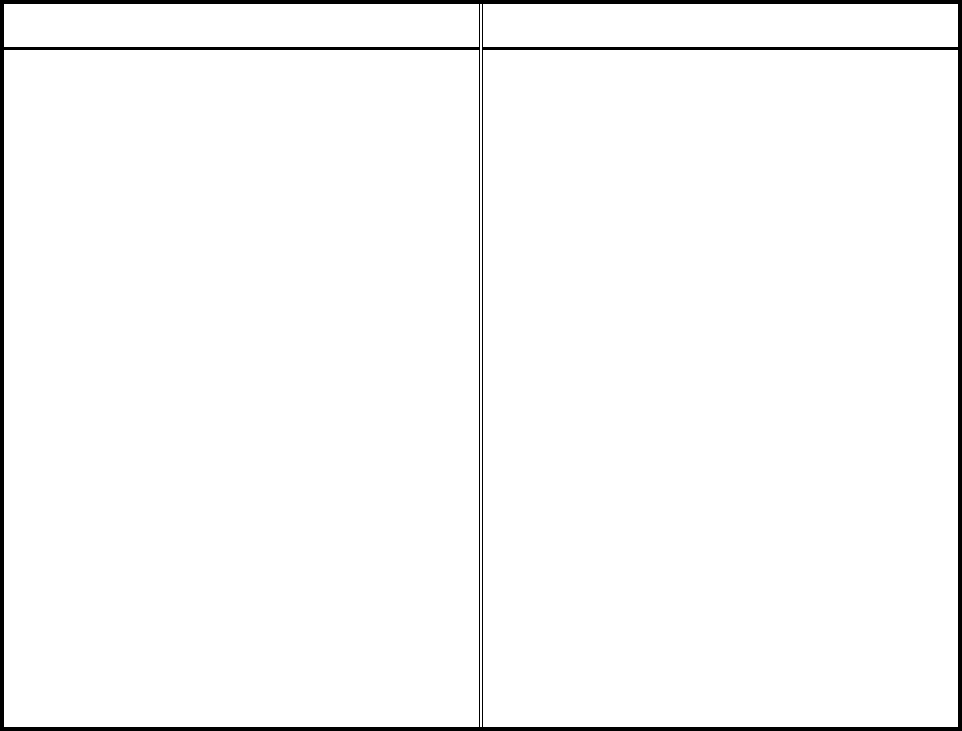

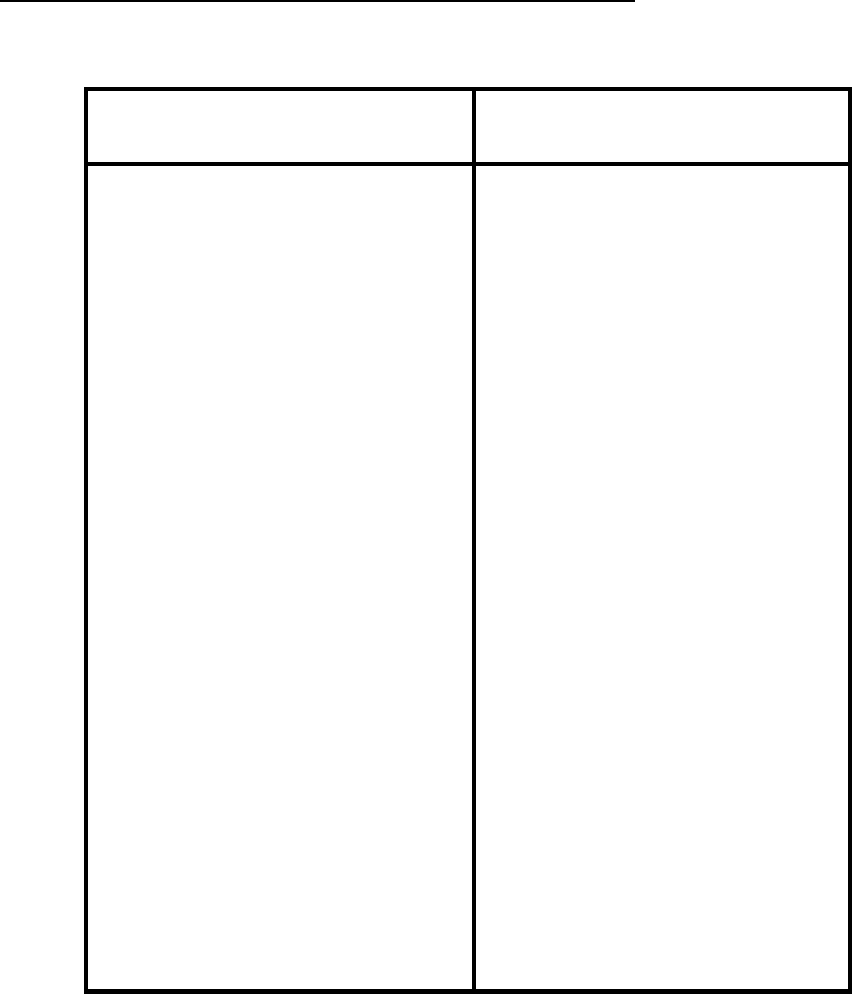

Table 3 - B_DDR3D_3A (<=1066MT/s Read and Write) TLA Channel Grouping.................... 31

Table 4 - B_DDR3D_2D/_2G TLA MagniVu Channel Grouping .............................................. 45

Table 5 - B_DDR3D_3A TLA MagniVu Channel Grouping ...................................................... 48

Table 6 - B_DDR3D_2A / 3A Mnemonics Definition................................................................. 66

Table 7 - B_DDR3D_2G Mnemonics Definition......................................................................... 67

Table 8 - B_DDR3D_2D / 3A Control Symbol Table ................................................................ 69

Table 9 - B_DDR3D_2G Control Symbol Table ........................................................................ 70

DDR3THIN-MN-XXX 8 Doc. Rev. 1.11

DDR3THIN-MN-XXX 9 Doc. Rev. 1.11

1.0 OVERVIEW

1.1 General Information

The DDR3 Interposer Products are designed for ease of use. Interposers extra signal trace

length, also an extra connector that might affect the quality of the system operation in some

systems.

• This Product is designed for capture of 1066MT/s or slower, and may only be used with

the Tektronix TLA7BB4 acquisition modules.

This product requires the use of the new NEX-PRB1X-T / PRB2X-T Low Profile Distributed

probes available from Nexus. Tektronix P68xx or P69xx probes can not be used.

This Interposer has been designed to provide a quick and easy connection to interface to a

Tektronix TLA7BB4 Logic Analyzer acquisition cards to a 240-pin DDR3 (Double Data Rate 3)

bus. Contact NEXUS Technology for other available DDR3 Products. The Nexus Technology

web site (www.NexusTechnology.com) contains information on the latest software release.

1.2 Software Package description

The NEX-DDR3INTR-THIN support includes the following software packages:

B_DDR3D_2D allows the user to acquire Read AND Write data from a single, dual or

quad rank DDR3 DIMM running 1066MT/s or less. This support requires 1ea. NEX-

PRB1X-T and 3ea. NEX-PRB2X-T Low Profile Distributed probes, and two merged

Tektronix TLA7BB4 acquisition cards. This support can use selective clocking to reduce

the number of Idle states acquired by the logic analyzer.

Optional software available for the NEX-DDR3INTR-THIN support includes the following

software packages:

B_DDR3D_2G allows the user to acquire Read AND Write data from a memory

channel made up of two or three DIMM slots with one or two rank DDR3 DIMMs

running 800MT/s or less. This is total disassembly for the 3 DIMM memory channel.

This support requires 2ea. NEX-PRB1X-T and 3ea. NEX-PRB2X-T Low Profile

Distributed probes, and two merged Tektronix TLA7BB4 acquisition cards. This support

also requires the NEX-PRBCOAX product. This support can be used with Single Rank

and Dual Rank DIMMs (will also support a single quad rank DIMM). Reads for the three

DIMMs must have a common data eye (over lap) of 330ps. No selective clocking

B_DDR3D_3A allows the user to acquire Read AND Write data from a memory channel

made up of two DIMM slots with single or dual rank DDR3 DIMMs running 1066MT/s

or less. This is total disassembly for the 2 DIMM memory channel. This support

requires 5ea. NEX-PRB1X-T and 3ea. NEX-PRB2X-T Low Profile Distributed probes,

and three merged Tektronix TLA7BB4 acquisition cards. This support also requires two

DDR3THIN-MN-XXX 10 Doc. Rev. 1.11

NEX-DDR3INTR-THIN Interposer products. This support can be used with Single

Rank and Dual Rank DIMMs.

Note that this manual uses some terms generically. For instance, references to the TLA700/7000

apply to all suitable TLA700/7000 Logic Analyzers, or PCs being used to control the TLA.

NEX-DDR3INTR-THIN refers to the B_DDR3D_2D/2G/3A software support packages.

Appendix G has a silk-screened print of the NEX-DDR3INTR-THIN Logic Analyzer Interposer

board. Referring to this drawing while reading the manual is suggested.

This manual assumes that the user is familiar with the DDR3 SDRAM Specification and the

Tektronix TLA Logic Analyzers. It is also expected that the user is familiar with the Windows

environment used with the TLA.

DDR3THIN-MN-XXX 11 Doc. Rev. 1.11

1.3 Eye size required

The Eye size (stable data) required at the input resistor to the Nexus passive probes (NEX-

PRB1X(-T) & NEX-PRB2X(-T)) is 330ps, and 0.2V. Capture accuracy may be affected if a

stable eye can not meet this requirement. . The eye is a perfectly shaped diamond with each side

equal distant from the center.

2.0 SOFTWARE INSTALLATION

To Install the NEX-DDR3INTR-THIN software support place the B_DDR3D_XX Install CD in

the CD drive of the TLA or the PC being used to control the TLA. Using Windows Explorer

select the CD, navigate to the support_software folder, select the folder of the support to be

installed (B_DDR3D_2D, B_DDR3D_2G or B_DDR3D_3A) and then run the .MSI file within

the folder. The selected software will be installed on the TLA’s hard disk.

To load the support into the TLA, first select the desired Logic Analyzer module (different

supports require different module counts) in the Setup window, select Load Support Package

from the File pull-down, then choose the software package name you are want to load and click

on Okay. Note that this support requires two or more merged modules and that the TLA

acquisition cards must be configured properly for the software to load.

DDR3THIN-MN-XXX 12 Doc. Rev. 1.11

3.0 CONNECTING to the NEX-DDR3INTR-THIN INTERPOSER

3.1 General

Care should be taken to support the weight of the acquisition probes so that the Logic Analyzer

Interposer board and/or target socket are not damaged.

3.2 B_DDR3D_2D Support

To acquire DDR3 Read and Write data at speeds up to 1066MT/s requires two merged

TLA7BB4 136-channel, with 1.4G state option, acquisition cards and the use of the

B_DDR3D_2D support software. The Master card will be in the lower numbered of the two

cards. Slave card #1 is in the adjacent high-numbered slots. The logic analyzer modules should

be connected to the DDR3 DIMM Interposer as follows using (1) NEX-PPRB1X-T probes and

three (3) NEX-PRB2X-T probes:

TLA Master

Connect the NEX-PRB1X-T “C” probe head to DDR3 Interposer’s LEASH (soldered-on

coax cable) that is attached to “M_C” position on the Interposer.

Connect the NEX-PRB2X-T A3/2 & A1/0 probe head to DDR3 Interposer’s LEASH

that is attached to “M_ A3/2 A1/0” position on the Interposer.

Match the label on the end of the NEX-PRB1X-T/2X-T probes with the labels on the

front of the Tektronix Logic Analyzer Master module and connect.

TLA Slave

Connect the NEX-PRB2X-T A3/2 & A1/0 probe head to DDR3 Interposer’s LEASH

that is attached to “S_ A3/2 A1/0” position on the Interposer.

Connect the NEX-PRB2X-T “C3/2” & “E3/2” probe head to DDR3 Interposer’s LEASH

that is attached to “S_C3/2 E3/2” position on the Interposer.

See Figure 1 for connections. Table 1 shows the Channel Grouping / Wiring for use with the

B_DDR3D_2D support.

3.3 B_DDR3D_2G Support

To acquire DDR3 Read and Write data from two or three DIMM slots, for total memory channel

disassembly, at speeds up to 800MT/s requires two merged TLA7BB4 136-channel, with 1.4G

state option, acquisition cards and the use of the B_DDR3D_2G optional support software. The

Master card will be in the lower numbered, of the two cards. Slave card #1 will be in the

adjacent high-numbered slots. This support requires an additional NEX-PRB1X-T (for a total of

2), and the NEX-PRBCOAX product. The logic analyzer modules should be connected to the

DDR3 DIMM Interposer as follows using (1) NEX-PPRB1X-T probes and three (3) NEX-

PRB2X-T probes, with the additional NEX-PRB1X-T connected to the NEX-PRBCOAX:

DDR3THIN-MN-XXX 13 Doc. Rev. 1.11

TLA Master

Connect the NEX-PRB1X-T “C” probe head to DDR3 Interposer’s LEASH (soldered-on

coax cable) that is attached to “M_C” position on the Interposer.

Connect the NEX-PRB2X-T A3/2 & A1/0 probe head to DDR3 Interposer’s LEASH

that is attached to “M_ A3/2 A1/0” position on the Interposer.

Connect the NEX-PRB1X-T “E” probe head to the NEX-PRBCOAX.

Note the leads 9- 12 of the NEX-PRBCOAX must be connected to the second slots Chip

Select lines (CS) near the second and third DIMM socket, usually on the back of the

mother board.

Match the label on the end of the NEX-PRB1X-T/2X-T probes with the labels on the

front of the Tektronix Logic Analyzer Master module and connect.

TLA Slave

Connect the NEX-PRB2X-T A3/2 & A1/0 probe head to DDR3 Interposer’s LEASH

that is attached to “S_ A3/2 A1/0” position on the Interposer.

Connect the NEX-PRB2X-T “C3/2” & “E3/2” probe head to DDR3 Interposer’s LEASH

that is attached to “S_C3/2 E3/2” position on the Interposer.

See Figure 1 for connections. Table 2 shows the Channel Grouping / Wiring for use with the

B_DDR3D_2G support.

3.4 B_DDR3D_3A Support

To acquire DDR3 Read and Write data from a two DIMM slots, for total memory channel

disassembly, at speeds up to 1066MT/s requires three merged TLA7BB4 136-channel, with

1.4G state option, acquisition cards and the use of the B_DDR3D_3A optional support software.

The Master card will be in the lower numbered, of the three cards. Slave card #1 will be in the

adjacent high-numbered slots. Slave card #2 will be in the adjacent low-numbered slots. This

support also requires two NEX-DDR3INTR-THIN Interposer products. The logic analyzer

modules should be connected to the DDR3 DIMM Interposer as follows using (5) NEX-

PPRB1X-T probes and three (3) NEX-PRB2X-T probes:

TLA Master

Connect the NEX-PRB1X-T “C” probe head to DDR3 Interposer’s LEASH (soldered-on

coax cable) that is attached to “M_C” position on the Interposer.

Connect the NEX-PRB2X-T A3/2 & A1/0 probe head to DDR3 Interposer’s LEASH

that is attached to “M_ A3/2 A1/0” position on the Interposer.

Match the label on the end of the NEX-PRB1X-T/2X-T probes with the labels on the

front of the Tektronix Logic Analyzer Master module and connect.

DDR3THIN-MN-XXX 14 Doc. Rev. 1.11

TLA Slave1

Connect the NEX-PRB2X-T A3/2 & A1/0 probe head to DDR3 Interposer’s LEASH

that is attached to “S_ A3/2 A1/0” position on the Interposer.

Connect the NEX-PRB2X-T “C3/2” & “E3/2” probe head to DDR3 Interposer’s LEASH

that is attached to “S_C3/2 E3/2” position on the Interposer.

TLA Slave2

Connect the NEX-PRB1X-T A3/2 D3/2 probe head to DDR3 Interposer’s LEASH that is

attached to “M_A3/2 A1/0” position on the second Interposer.

Connect the NEX-PRB1X-T A1/0 D1/0 probe head to DDR3 Interposer’s LEASH that is

attached to “S_A3/2 A1/0” position on the second Interposer.

Connect the NEX-PRB1X-T “C” probe head to DDR3 Interposer’s LEASH that is

attached to “M_C3/2 C1/0” position on the second Interposer.

Connect the NEX-PRB1X-T “E” probe head to DDR3 Interposer’s LEASH that is

attached to “S_C3/2 E3/2” position on the second Interposer.

See Figure 1 for connections. Table 3 shows the Channel Grouping / Wiring for use with the

B_DDR3D_3A support.

DDR3THIN-MN-XXX 15 Doc. Rev. 1.11

3.5 Short “LEASH” probes

The standard product includes 4 “LEASH” probes connected to this Interposer product. These

short probes are soldered directly onto the interposer and interface the Interposer to the Passive

probes that connect to the logic analyzer. These “LEASH” probes are to allow the user to easily

install and remove the Interposer product in their system with out the added weight of the

passive probe attached. There may be other probing options in the future. Contact Nexus for any

updates.

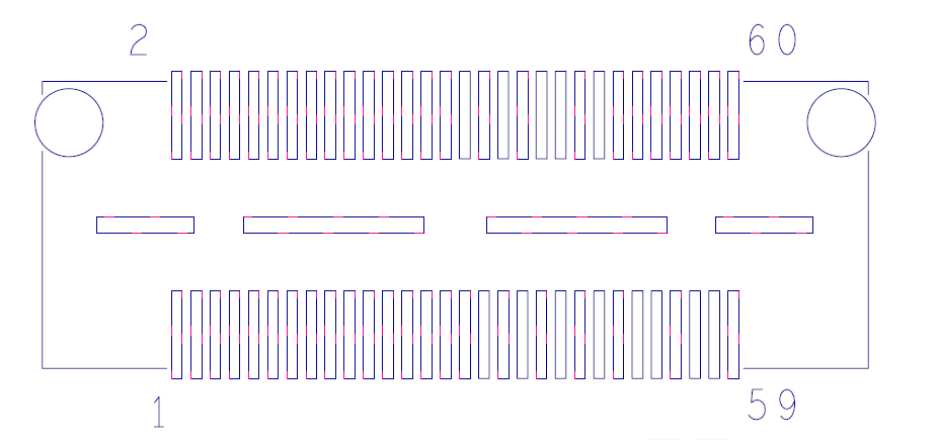

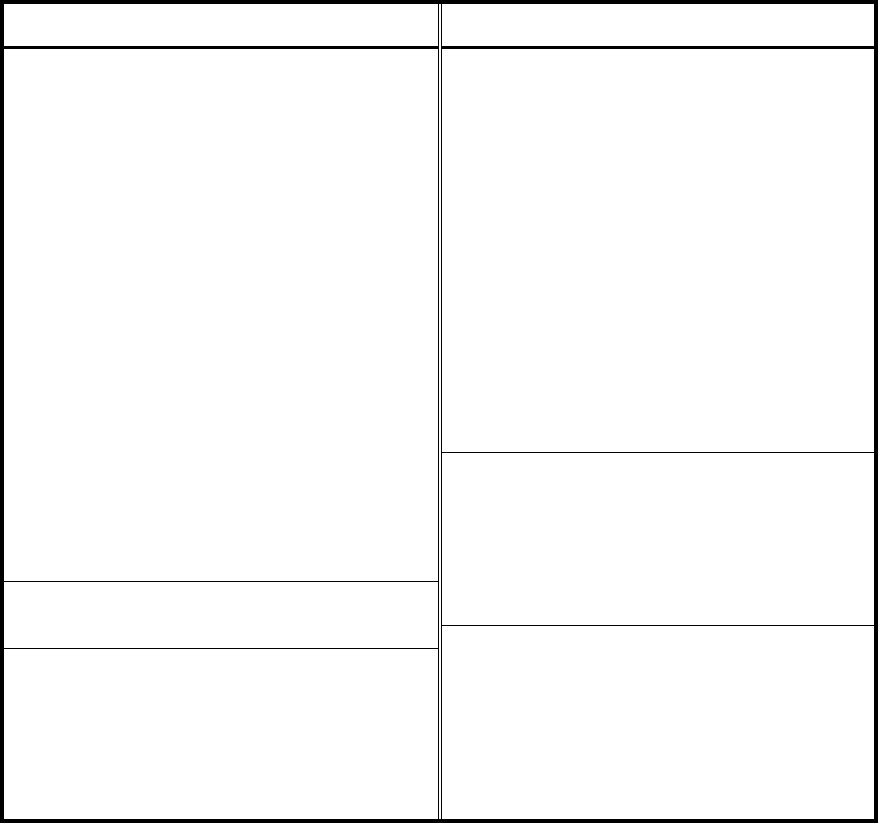

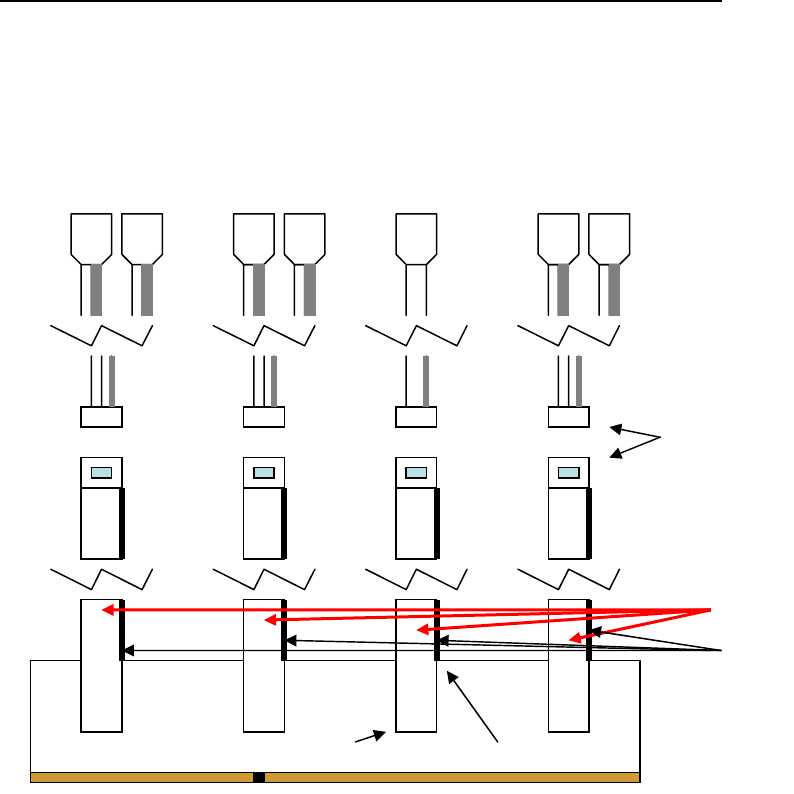

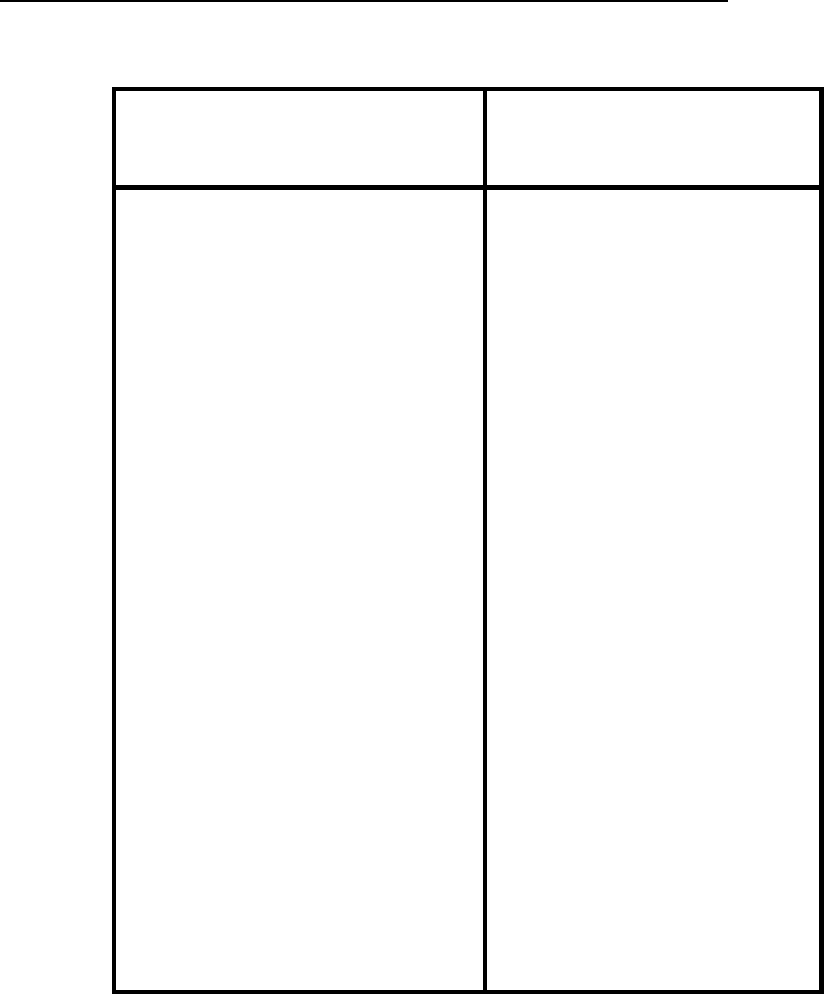

Figure 1 below shows the location on the Interposer of the LEASH probe connections.

Location of HCD connectors, right under metal compression plate, and probe tip board:

Figure 1 – Drawing of Interposer with probes attached

The four (4) each, 1 foot long, “LEASH” probes that are soldered onto the Interposer are in turn

connected to either a NEX-PRB1X-T or NEX-PRB2X-T probe. The NEX-PRB1X-T or NEX-

PRB2X-T probe in turn connects to the input of the logic analyzer modules. The connection

between the LEASH Probes and the logic Analyzer is a Samtec connector with a pin out as

shown below on the LEASH probe. Refer to 3.2 to determine if a NEX-PRB1X-T or NEX-

PRB2X-T connects to each LEASH probe.

PRB2

S_A3/2 A1/0 M_

PRB1PRB2PRB2

S_C3/2 M_A3/2 A1/0

DDR3THIN-MN-XXX 16 Doc. Rev. 1.11

The strain relief on the LEASH to NEXPRB1X/2X interface, while designed for bench handling,

can be damaged by twisting the coax cables. Bends of over 45 degrees in this area should be

avoided. The coax connection points, under any circumstances, are not to be bent.

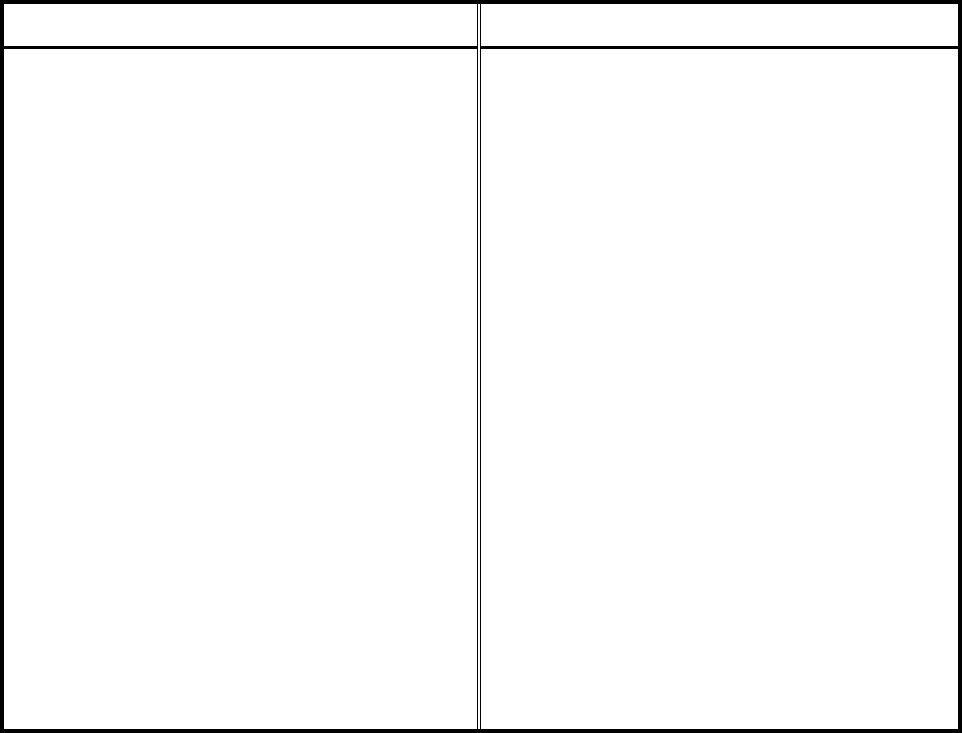

3.5.1 Samtec connector on the LEASH probe pins

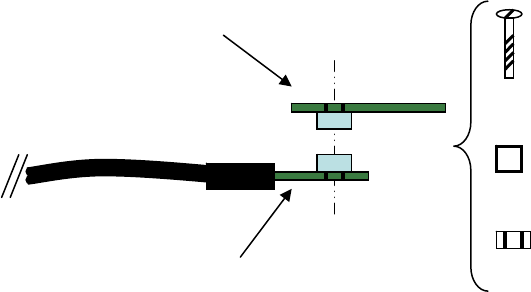

Figure 2 – Samtec connector on the LEASH probe

The LEASH probe connects to the NEX-PRB1X-T or NEX-PRB2X-T probe using two plastic

nuts and screws, with a plastic spacer between the two boards. These parts are supplied.

DDR3THIN-MN-XXX 17 Doc. Rev. 1.11

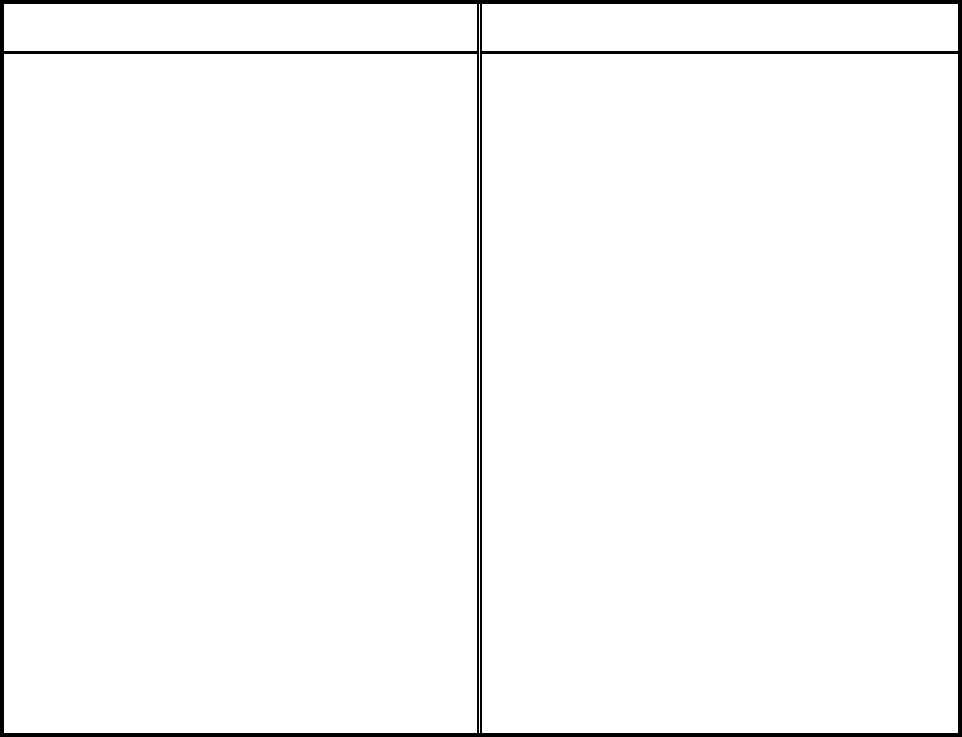

3.5.2 LEASH probe to NEX-PRB1X/2X connection

Figure 3 – LEASH probe to NEX-PRB1X/2X connection

3.5.3 Alternate use of NEX-PRB1X or NEX-PRB2X probes

The NEX-PRB1X or NEX-PRB2X can be used in place of the “-T” probes but will have to be

secured for long term connection by tie-wraps.

Two each plastic

Spacers

Screws

&

Nuts

Hold each probe

together

Transition board on the “LEASH”

Cable end

Probe tip on the NEX-PRB1X-T or

NEX-PRB2X-T

Interposer

here

DDR3THIN-MN-XXX 18 Doc. Rev. 1.11

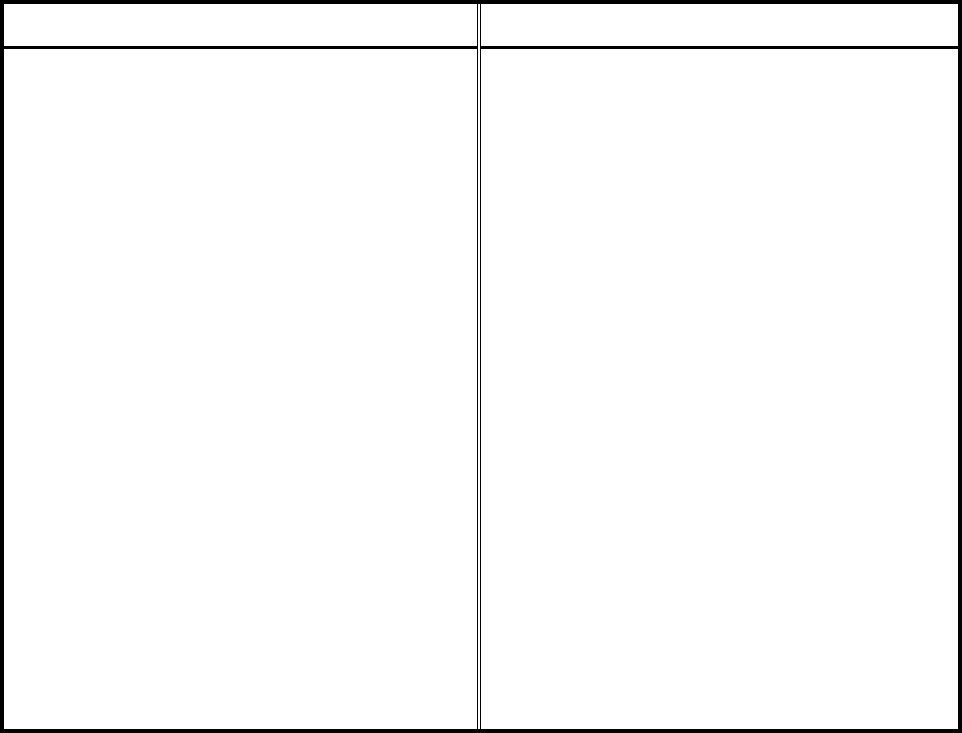

3.6 Slot Numbering

The Interposer must be installed in the furthest slot from the memory controller. For 1066MT/s

support only the two furthest slots may be used. Slots are named as shown below:

Slot naming for a three slot system

Memory controller

Slot C Slot B Slot A

S0-3#

CLKE0-

bS0-1#

bCLKE0-1

(from NEX-

PRBCOAX)

cS0-1#

cCLKE0-1

(from NEX-

PRBCOAX)

If only one slot is used it must be the furthest slot from the memory controller.

If two slots are used they must be the furthest slots from the memory controller.

Quad rank is only supported in the single slot configuration

Interposer in any two or three slot configuration must be in the furthest slot.

1066MT/s full channel support (B_DDR3D_3A) requires two interposers in the two

furthest slots from the memory controller.

DDR3THIN-MN-XXX 19 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

RdA_DatHi RD_A_DQ63 234 S_A2:0 RdA_DatLo RD_A_DQ31 156 M_A0:6

(Hex) RD_A_DQ62 233 S_A2:1 (Hex) RD_A_DQ30 155 M_A0:3

RD_A_DQ61 228 S_A2:5 RD_A_DQ29 150 S_C2:0

RD_A_DQ60 227 S_CK0 RD_A_DQ28 149 S_C2:1

RD_A_DQ59 115 S_A2:2 RD_A_DQ27 37 M_A0:4

RD_A_DQ58 114 S_A2:3 RD_A_DQ26 36 M_A0:1

RD_A_DQ57 109 S_A2:7 RD_A_DQ25 31 S_C2:2

RD_A_DQ56 108 S_A3:0 RD_A_DQ24 30 S_C2:3

RD_A_DQ55 225 S_A3:2 RD_A_DQ23 147 S_C2:4

RD_A_DQ54 224 S_A3:3 RD_A_DQ22 146 S_C2:5

RD_A_DQ53 219 S_A3:7 RD_A_DQ21 141 S_C3:2

RD_A_DQ52 218 S_A1:5 RD_A_DQ20 140 S_C3:3

RD_A_DQ51 106 S_A3:1 RD_A_DQ19 28 S_C2:6

RD_A_DQ50 105 S_A3:4 RD_A_DQ18 27 S_C2:7

RD_A_DQ49 100 S_A1:7 RD_A_DQ17 22 S_C3:1

RD_A_DQ48 99 S_A1:6 RD_A_DQ16 21 S_C3:4

RD_A_DQ47 216 S_A1:4 RD_A_DQ15 138 S_C3:6

RD_A_DQ46 215 S_A1:1 RD_A_DQ14 137 S_C3:7

RD_A_DQ45 210 S_A0:7 RD_A_DQ13 132 S_E3:4

RD_A_DQ44 209 S_A0:6 RD_A_DQ12 131 S_E3:1

RD_A_DQ43 97 S_A1:3 RD_A_DQ11 19 S_C3:5

RD_A_DQ42 96 S_A1:2 RD_A_DQ10 18 S_E3:7

RD_A_DQ41 91 S_A0:5 RD_A_DQ9 13 S_E3:3

RD_A_DQ40 90 S_A0:4 RD_A_DQ8 12 S_E3:2

RD_A_DQ39 207 S_A0:3 RD_A_DQ7 129 S_E3:0

RD_A_DQ38 206 S_A0:2 RD_A_DQ6 128 S_E2:7

RD_A_DQ37 201 M_C2:1 RD_A_DQ5 123 S_E2:3

RD_A_DQ36 200 M_C2:4 RD_A_DQ4 122 S_E2:2

RD_A_DQ35 88 S_A0:1 RD_A_DQ3 10 S_Q3

RD_A_DQ34 87 S_A0:0 RD_A_DQ2 9 S_E2:5

RD_A_DQ33 83 M_C2:6 RD_A_DQ1 4 S_E2:1

RD_A_DQ32 81 M_C2:7 RD_A_DQ0 3 S_E2:0

Table 1 - B_DDR3D_2D (<=1066MT/s Read and Write) TLA Channel Grouping

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘S’ in front of a TLA channel denotes the Slave card of the merged pair

DDR3THIN-MN-XXX 20 Doc. Rev. 1.11

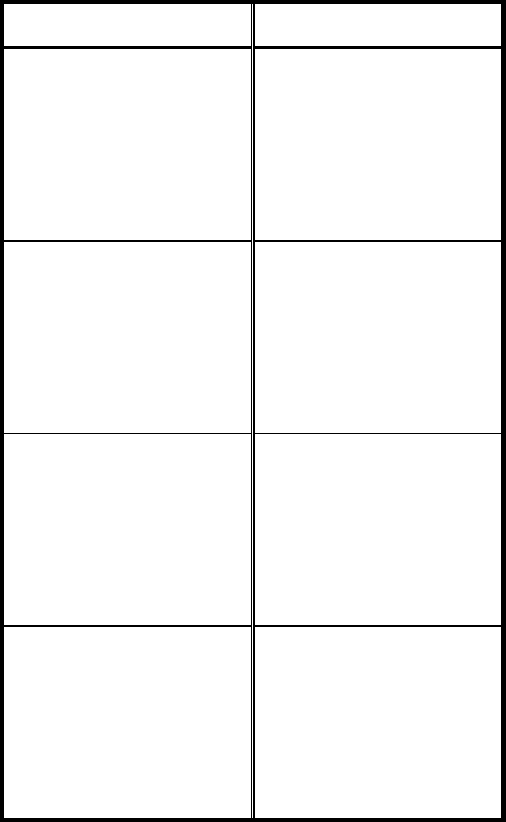

Group

Name

Signal

Name

DDR3

Pin#

TLA

Input

Group

Name

Signal

Name

DDR3

Pin#

TLA

Input

RdB_DatHi RD_B_DQ63 234 S_A2:0^1 RdB_DatLo RD_B_DQ31 156 M_A0:6^1

(Hex) RD_B_DQ62 233 S_A2:1^1 (Hex) RD_B_DQ30 155 M_A0:3^1

RD_B_DQ61 228 S_A2:5^1 RD_B_DQ29 150 S_C2:0^1

RD_B_DQ60 227 S_CK0^1 RD_B_DQ28 149 S_C2:1^1

RD_B_DQ59 115 S_A2:2^1 RD_B_DQ27 37 M_A0:4^1

RD_B_DQ58 114 S_A2:3^1 RD_B_DQ26 36 M_A0:1^1

RD_B_DQ57 109 S_A2:7^1 RD_B_DQ25 31 S_C2:2^1

RD_B_DQ56 108 S_A3:0^1 RD_B_DQ24 30 S_C2:3^1

RD_B_DQ55 225 S_A3:2^1 RD_B_DQ23 147 S_C2:4^1

RD_B_DQ54 224 S_A3:3^1 RD_B_DQ22 146 S_C2:5^1

RD_B_DQ53 219 S_A3:7^1 RD_B_DQ21 141 S_C3:2^1

RD_B_DQ52 218 S_A1:5^1 RD_B_DQ20 140 S_C3:3^1

RD_B_DQ51 106 S_A3:1^1 RD_B_DQ19 28 S_C2:6^1

RD_B_DQ50 105 S_A3:4^1 RD_B_DQ18 27 S_C2:7^1

RD_B_DQ49 100 S_A1:7^1 RD_B_DQ17 22 S_C3:1^1

RD_B_DQ48 99 S_A1:6^1 RD_B_DQ16 21 S_C3:4^1

RD_B_DQ47 216 S_A1:4^1 RD_B_DQ15 138 S_C3:6^1

RD_B_DQ46 215 S_A1:1^1 RD_B_DQ14 137 S_C3:7^1

RD_B_DQ45 210 S_A0:7^1 RD_B_DQ13 132 S_E3:4^1

RD_B_DQ44 209 S_A0:6^1 RD_B_DQ12 131 S_E3:1^1

RD_B_DQ43 97 S_A1:3^1 RD_B_DQ11 19 S_C3:5^1

RD_B_DQ42 96 S_A1:2^1 RD_B_DQ10 18 S_E3:7^1

RD_B_DQ41 91 S_A0:5^1 RD_B_DQ9 13 S_E3:3^1

RD_B_DQ40 90 S_A0:4^1 RD_B_DQ8 12 S_E3:2^1

RD_B_DQ39 207 S_A0:3^1 RD_B_DQ7 129 S_E3:0^1

RD_B_DQ38 206 S_A0:2^1 RD_B_DQ6 128 S_E2:7^1

RD_B_DQ37 201 M_C2:1^1 RD_B_DQ5 123 S_E2:3^1

RD_B_DQ36 200 M_C2:4^1 RD_B_DQ4 122 S_E2:2^1

RD_B_DQ35 88 S_A0:1^1 RD_B_DQ3 10 S_Q3^1

RD_B_DQ34 87 S_A0:0^1 RD_B_DQ2 9 S_E2:5^1

RD_B_DQ33 83 M_C2:6^1 RD_B_DQ1 4 S_E2:1^1

RD_B_DQ32 81 M_C2:7^1 RD_B_DQ0 3 S_E2:0^1

Table 1 – B_DDR3D_2D (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘S’ in front of a TLA channel denotes the Slave card of the merged pair

3. All signals on this page are stored in the TLA7BB4’s Prime memory and will not have a

MagniVu display value

DDR3THIN-MN-XXX 21 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

WrA_DatHi WR_A_DQ63 234 S_D2:0 WrA_DatLo WR_A_DQ31 156 M_D0:6

(Hex) WR_A_DQ62 233 S_D2:1 (Hex) WR_A_DQ30 155 M_D0:3

WR_A_DQ61 228 S_D2:5 WR_A_DQ29 150 S_C0:0

WR_A_DQ60 227 S_Q1 WR_A_DQ28 149 S_C0:1

WR_A_DQ59 115 S_D2:2 WR_A_DQ27 37 M_D0:4

WR_A_DQ58 114 S_D2:3 WR_A_DQ26 36 M_D0:1

WR_A_DQ57 109 S_D2:7 WR_A_DQ25 31 S_C0:2

WR_A_DQ56 108 S_D3:0 WR_A_DQ24 30 S_C0:3

WR_A_DQ55 225 S_D3:2 WR_A_DQ23 147 S_C0:4

WR_A_DQ54 224 S_D3:3 WR_A_DQ22 146 S_C0:5

WR_A_DQ53 219 S_D3:7 WR_A_DQ21 141 S_C1:2

WR_A_DQ52 218 S_D1:5 WR_A_DQ20 140 S_C1:3

WR_A_DQ51 106 S_D3:1 WR_A_DQ19 28 S_C0:6

WR_A_DQ50 105 S_D3:4 WR_A_DQ18 27 S_C0:7

WR_A_DQ49 100 S_D1:7 WR_A_DQ17 22 S_C1:1

WR_A_DQ48 99 S_D1:6 WR_A_DQ16 21 S_C1:4

WR_A_DQ47 216 S_D1:4 WR_A_DQ15 138 S_C1:6

WR_A_DQ46 215 S_D1:1 WR_A_DQ14 137 S_C1:7

WR_A_DQ45 210 S_D0:7 WR_A_DQ13 132 S_E1:4

WR_A_DQ44 209 S_D0:6 WR_A_DQ12 131 S_E1:1

WR_A_DQ43 97 S_D1:3 WR_A_DQ11 19 S_C1:5

WR_A_DQ42 96 S_D1:2 WR_A_DQ10 18 S_E1:7

WR_A_DQ41 91 S_D0:5 WR_A_DQ9 13 S_E1:3

WR_A_DQ40 90 S_D0:4 WR_A_DQ8 12 S_E1:2

WR_A_DQ39 207 S_D0:3 WR_A_DQ7 129 S_E1:0

WR_A_DQ38 206 S_D0:2 WR_A_DQ6 128 S_E0:7

WR_A_DQ37 201 M_C0:1 WR_A_DQ5 123 S_E0:3

WR_A_DQ36 200 M_C0:4 WR_A_DQ4 122 S_E0:2

WR_A_DQ35 88 S_D0:1 WR_A_DQ3 10 S_CK2

WR_A_DQ34 87 S_D0:0 WR_A_DQ2 9 S_E0:5

WR_A_DQ33 83 M_C0:6 WR_A_DQ1 4 S_E0:1

WR_A_DQ32 81 M_C0:7 WR_A_DQ0 3 S_E0:0

Table 1 – B_DDR3D_2D (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘S’ in front of a TLA channel denotes the Slave card of the merged pair

DDR3THIN-MN-XXX 22 Doc. Rev. 1.11

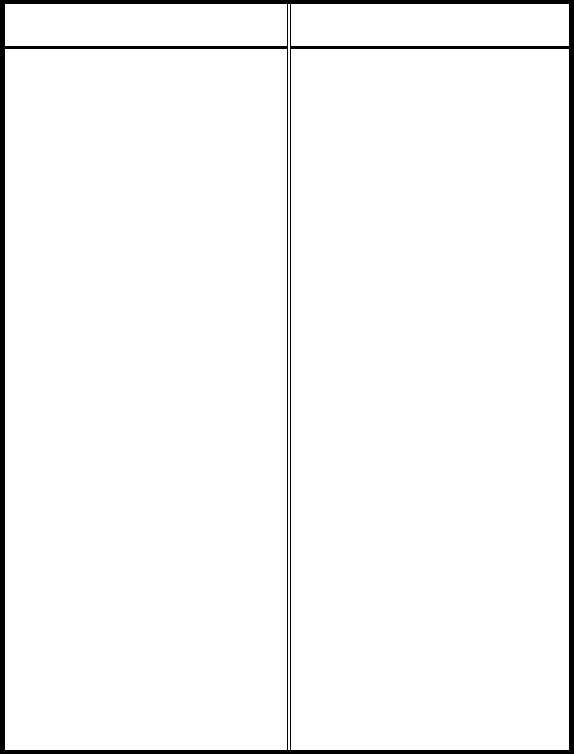

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

WrB_DatHi WR_B_DQ63 234 S_D2:0^1 WrB_DatLo WR_B_DQ31 156 M_D0:6^1

(Hex) WR_B_DQ62 233 S_D2:1^1 (Hex) WR_B_DQ30 155 M_D0:3^1

WR_B_DQ61 228 S_D2:5^1 WR_B_DQ29 150 S_C0:0^1

WR_B_DQ60 227 S_Q1^1 WR_B_DQ28 149 S_C0:1^1

WR_B_DQ59 115 S_D2:2^1 WR_B_DQ27 37 M_D0:4^1

WR_B_DQ58 114 S_D2:3^1 WR_B_DQ26 36 M_D0:1^1

WR_B_DQ57 109 S_D2:7^1 WR_B_DQ25 31 S_C0:2^1

WR_B_DQ56 108 S_D3:0^1 WR_B_DQ24 30 S_C0:3^1

WR_B_DQ55 225 S_D3:2^1 WR_B_DQ23 147 S_C0:4^1

WR_B_DQ54 224 S_D3:3^1 WR_B_DQ22 146 S_C0:5^1

WR_B_DQ53 219 S_D3:7^1 WR_B_DQ21 141 S_C1:2^1

WR_B_DQ52 218 S_D1:5^1 WR_B_DQ20 140 S_C1:3^1

WR_B_DQ51 106 S_D3:1^1 WR_B_DQ19 28 S_C0:6^1

WR_B_DQ50 105 S_D3:4^1 WR_B_DQ18 27 S_C0:7^1

WR_B_DQ49 100 S_D1:7^1 WR_B_DQ17 22 S_C1:1^1

WR_B_DQ48 99 S_D1:6^1 WR_B_DQ16 21 S_C1:4^1

WR_B_DQ47 216 S_D1:4^1 WR_B_DQ15 138 S_C1:6^1

WR_B_DQ46 215 S_D1:1^1 WR_B_DQ14 137 S_C1:7^1

WR_B_DQ45 210 S_D0:7^1 WR_B_DQ13 132 S_E1:4^1

WR_B_DQ44 209 S_D0:6^1 WR_B_DQ12 131 S_E1:1^1

WR_B_DQ43 97 S_D1:3^1 WR_B_DQ11 19 S_C1:5^1

WR_B_DQ42 96 S_D1:2^1 WR_B_DQ10 18 S_E1:7^1

WR_B_DQ41 91 S_D0:5^1 WR_B_DQ9 13 S_E1:3^1

WR_B_DQ40 90 S_D0:4^1 WR_B_DQ8 12 S_E1:2^1

WR_B_DQ39 207 S_D0:3^1 WR_B_DQ7 129 S_E1:0^1

WR_B_DQ38 206 S_D0:2^1 WR_B_DQ6 128 S_E0:7^1

WR_B_DQ37 201 M_C0:1^1 WR_B_DQ5 123 S_E0:3^1

WR_B_DQ36 200 M_C0:4^1 WR_B_DQ4 122 S_E0:2^1

WR_B_DQ35 88 S_D0:1^1 WR_B_DQ3 10 S_CK2^1

WR_B_DQ34 87 S_D0:0^1 WR_B_DQ2 9 S_E0:5^1

WR_B_DQ32 83 M_C0:6^1 WR_B_DQ1 4 S_E0:1^1

WR_B_DQ33 81 M_C0:7^1 WR_B_DQ0 3 S_E0:0^1

Table 1 – B_DDR3D_2D (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘S’ in front of a TLA channel denotes the Slave card of the merged pair

3. All signals on this page are stored in the TLA7BB4’s Prime memory and will not have a

MagniVu display value

DDR3THIN-MN-XXX 23 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

RdAChkBits RD_A_CB7 165 M_A1:5 WrAChkBits 4 WR_A_CB7 165 M_D1:5

(OFF) RD_A_CB6 164 M_A1:4 (OFF) WR_A_CB6 164 M_D1:4

RD_A_CB5 159 M_A1:0 WR_A_CB5 159 M_D1:0

RD_A_CB4 158 M_A0:7 WR_A_CB4 158 M_D0:7

RD_A_CB3 46 M_A1:6 WR_A_CB3 46 M_D1:6

RD_A_CB2 45 M_A1:3 WR_A_CB2 45 M_D1:3

RD_A_CB1 40 M_CK1 WR_A_CB1 40 M_Q0

RD_A_CB0 39 M_A0:5 WR_A_CB0 39 M_D0:5

RdBChkBits 4 RD_B_CB7 165 M_A1:5^1 WrBChkBits 4 WR_B_CB7 165 M_D1:5^1

(OFF) RD_B_CB6 164 M_A1:4^1 (OFF) WR_B_CB6 164 M_D1:4^1

RD_B_CB5 159 M_A1:0^1 WR_B_CB5 159 M_D1:0^1

RD_B_CB4 158 M_A0:7^1 WR_B_CB4 158 M_D0:7^1

RD_B_CB3 46 M_A1:6^1 WR_B_CB3 46 M_D1:6^1

RD_B_CB2 45 M_A1:3^1 WR_B_CB2 45 M_D1:3^1

RD_B_CB1 40 M_CK1^1 WR_B_CB1 40 M_Q0^1

RD_B_CB0 39 M_A0:5^1 WR_B_CB0 39 M_D0:5^1

ADatMsks A_DM7/DQS16 230 S_A2:4 BDatMsks 4 B_DM7/DQS16 230 S_A2:4^1

(BIN) A_DM6/DQS15 221 S_A3:6 (BIN) B_DM6/DQS15 221 S_A3:6^1

A_DM5/DQS14 212 S_A1:0 B_DM5/DQS14 212 S_A1:0^1

A_DM4/DQS13 203 M_C2:0 B_DM4/DQS13 203 M_C2:0^1

A_DM3/DQS12 152 M_A0:2 B_DM3/DQS12 152 M_A0:2^1

A_DM2/DQS11 143 S_CK3 B_DM2/DQS11 143 S_CK3^1

A_DM1/DQS10 134 S_E3:5 B_DM1/DQS10 134 S_E3:5^1

A_DM0/DQS9 125 S_E2:6 B_DM0/DQS9 125 S_E2:6^1

Table 1 – B_DDR3D_2D (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. ‘ # ‘ denotes a low-true signal

2. The ‘S’ in front of a TLA channel denotes the Slave card of the merged set

3. The ‘M’ in front of a TLA channel denotes the Master card of the merged pair

4. Signals in these groups are acquired using the TLA’s demux capability and will not have

a MagniVu display value

DDR3THIN-MN-XXX 24 Doc. Rev. 1.11

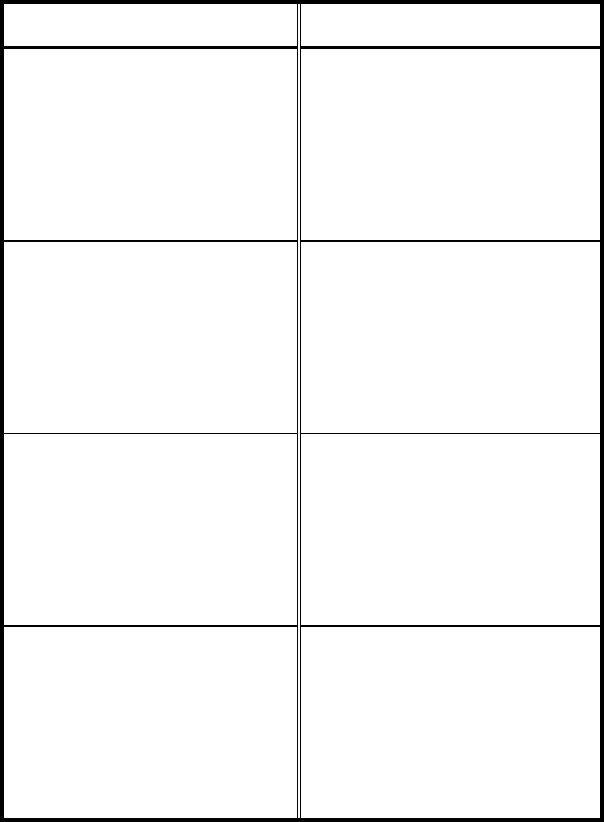

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Control 2 CKE1 169 M_A3:2 Address 2 BA2 52 M_A3:0

(SYM) CKE0 50 M_A3:1 (Hex) BA1 190 M_C3:7

S3# 49 M_C2:5 BA0 71 M_C1:6

S2# 48 M_C3:0 A15 171 M_CK0

S1# 76 M_C3:4 A14 172 M_A2:5

S0# 193 M_C3:3 A13 196 M_CK3

BA2 52 M_A3:0 A12/BC# 174 M_A2:4

BA1 190 M_C3:7 A11 55 M_A2:6

BA0 71 M_C1:6 A10/AP 70 M_C1:3

A15 171 M_CK0 A9 175 M_A2:1

A14 172 M_A2:5 A8 177 M_A2:0

A13 196 M_CK3 A7 56 M_A2:3

A12/BC# 174 M_A2:4 A6 178 M_C0:3

A10/AP 70 M_C1:3 A5 58 M_A2:2

RAS# 192 M_C3:6 A4 59 M_C0:5

CAS# 74 M_C3:5 A3 180 M_C1:0

WE# 73 M_C1:7 A2 61 M_Q1

Strobes DQS7 111 S_A2:6 A1 181 M_C1:1

(HEX) DQS6 103 S_A3:5 A0 188 M_C1:5

DQS5 94 S_CK1 Misc 2 MISC1

Placeholder

DQS4 85 M_C2:3 (OFF) MISC0

Placeholder

DQS3 34 M_A0:1 DDRCK0+/- 184/185 M_C1:4

DQS2 25 S_C3:0 Ungrouped DQS8 43 M_A1:2

DQS1 16 S_E3:6 DM8 161 M_A1:1

DQS0 7 S_E2:4 ERR_OUT#³ 53 M_A2:7

Unprobed All DQSx# RESET# 168 M_A3:6

DDRCK1+/- 63/64 TEST 167 M_A3:7

SA1 237 ODT0 195 M_C2:0

SDA 238 ODT1 77 M_C2:1

SA0 117 PAR_IN 68 M_C1:2

SCL 118

Table 1 – B_DDR3D_2D TLA Channel Grouping (cont’d.)

Notes:

1. ‘ # ‘ denotes a low-true signal

2. These signals are required for accurate acquisition and post-processing of acquired data

3. The ‘S’ in front of a TLA channel denotes the Slave card of the merged pair

4. The ‘M’ in front of a TLA channel denotes the Master card of the merged pair

5. Signals in these groups are acquired using the TLA’s demux capability and will not have

a MagniVu display value

DDR3THIN-MN-XXX 25 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

RdA_DatHi RD_A_DQ63 234 S_A2:0 RdA_DatLo RD_A_DQ31 156 M_A0:6

(Hex) RD_A_DQ62 233 S_A2:1 (Hex) RD_A_DQ30 155 M_A0:3

RD_A_DQ61 228 S_A2:5 RD_A_DQ29 150 S_C2:0

RD_A_DQ60 227 S_CK0 RD_A_DQ28 149 S_C2:1

RD_A_DQ59 115 S_A2:2 RD_A_DQ27 37 M_A0:4

RD_A_DQ58 114 S_A2:3 RD_A_DQ26 36 M_A0:1

RD_A_DQ57 109 S_A2:7 RD_A_DQ25 31 S_C2:2

RD_A_DQ56 108 S_A3:0 RD_A_DQ24 30 S_C2:3

RD_A_DQ55 225 S_A3:2 RD_A_DQ23 147 S_C2:4

RD_A_DQ54 224 S_A3:3 RD_A_DQ22 146 S_C2:5

RD_A_DQ53 219 S_A3:7 RD_A_DQ21 141 S_C3:2

RD_A_DQ52 218 S_A1:5 RD_A_DQ20 140 S_C3:3

RD_A_DQ51 106 S_A3:1 RD_A_DQ19 28 S_C2:6

RD_A_DQ50 105 S_A3:4 RD_A_DQ18 27 S_C2:7

RD_A_DQ49 100 S_A1:7 RD_A_DQ17 22 S_C3:1

RD_A_DQ48 99 S_A1:6 RD_A_DQ16 21 S_C3:4

RD_A_DQ47 216 S_A1:4 RD_A_DQ15 138 S_C3:6

RD_A_DQ46 215 S_A1:1 RD_A_DQ14 137 S_C3:7

RD_A_DQ45 210 S_A0:7 RD_A_DQ13 132 S_E3:4

RD_A_DQ44 209 S_A0:6 RD_A_DQ12 131 S_E3:1

RD_A_DQ43 97 S_A1:3 RD_A_DQ11 19 S_C3:5

RD_A_DQ42 96 S_A1:2 RD_A_DQ10 18 S_E3:7

RD_A_DQ41 91 S_A0:5 RD_A_DQ9 13 S_E3:3

RD_A_DQ40 90 S_A0:4 RD_A_DQ8 12 S_E3:2

RD_A_DQ39 207 S_A0:3 RD_A_DQ7 129 S_E3:0

RD_A_DQ38 206 S_A0:2 RD_A_DQ6 128 S_E2:7

RD_A_DQ37 201 M_C2:1 RD_A_DQ5 123 S_E2:3

RD_A_DQ36 200 M_C2:4 RD_A_DQ4 122 S_E2:2

RD_A_DQ35 88 S_A0:1 RD_A_DQ3 10 S_Q3

RD_A_DQ34 87 S_A0:0 RD_A_DQ2 9 S_E2:5

RD_A_DQ33 83 M_C2:6 RD_A_DQ1 4 S_E2:1

RD_A_DQ32 81 M_C2:7 RD_A_DQ0 3 S_E2:0

Table 2 - B_DDR3D_2G (<=1066MT/s Read and Write) TLA Channel Grouping

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘S’ in front of a TLA channel denotes the Slave card of the merged set

DDR3THIN-MN-XXX 26 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin#

TLA

Input

Group

Name

Signal

Name

DDR3

Pin#

TLA

Input

RdB_DatHi RD_B_DQ63 234 S_A2:0^1 RdB_DatLo RD_B_DQ31 156 M_A0:6^1

(Hex) RD_B_DQ62 233 S_A2:1^1 (Hex) RD_B_DQ30 155 M_A0:3^1

RD_B_DQ61 228 S_A2:5^1 RD_B_DQ29 150 S_C2:0^1

RD_B_DQ60 227 S_CK0^1 RD_B_DQ28 149 S_C2:1^1

RD_B_DQ59 115 S_A2:2^1 RD_B_DQ27 37 M_A0:4^1

RD_B_DQ58 114 S_A2:3^1 RD_B_DQ26 36 M_A0:1^1

RD_B_DQ57 109 S_A2:7^1 RD_B_DQ25 31 S_C2:2^1

RD_B_DQ56 108 S_A3:0^1 RD_B_DQ24 30 S_C2:3^1

RD_B_DQ55 225 S_A3:2^1 RD_B_DQ23 147 S_C2:4^1

RD_B_DQ54 224 S_A3:3^1 RD_B_DQ22 146 S_C2:5^1

RD_B_DQ53 219 S_A3:7^1 RD_B_DQ21 141 S_C3:2^1

RD_B_DQ52 218 S_A1:5^1 RD_B_DQ20 140 S_C3:3^1

RD_B_DQ51 106 S_A3:1^1 RD_B_DQ19 28 S_C2:6^1

RD_B_DQ50 105 S_A3:4^1 RD_B_DQ18 27 S_C2:7^1

RD_B_DQ49 100 S_A1:7^1 RD_B_DQ17 22 S_C3:1^1

RD_B_DQ48 99 S_A1:6^1 RD_B_DQ16 21 S_C3:4^1

RD_B_DQ47 216 S_A1:4^1 RD_B_DQ15 138 S_C3:6^1

RD_B_DQ46 215 S_A1:1^1 RD_B_DQ14 137 S_C3:7^1

RD_B_DQ45 210 S_A0:7^1 RD_B_DQ13 132 S_E3:4^1

RD_B_DQ44 209 S_A0:6^1 RD_B_DQ12 131 S_E3:1^1

RD_B_DQ43 97 S_A1:3^1 RD_B_DQ11 19 S_C3:5^1

RD_B_DQ42 96 S_A1:2^1 RD_B_DQ10 18 S_E3:7v

RD_B_DQ41 91 S_A0:5^1 RD_B_DQ9 13 S_E3:3^1

RD_B_DQ40 90 S_A0:4^1 RD_B_DQ8 12 S_E3:2^1

RD_B_DQ39 207 S_A0:3^1 RD_B_DQ7 129 S_E3:0^1

RD_B_DQ38 206 S_A0:2^1 RD_B_DQ6 128 S_E2:7^1

RD_B_DQ37 201 M_C2:1^1 RD_B_DQ5 123 S_E2:3^1

RD_B_DQ36 200 M_C2:4^1 RD_B_DQ4 122 S_E2:2^1

RD_B_DQ35 88 S_A0:1^1 RD_B_DQ3 10 S_Q3^1

RD_B_DQ34 87 S_A0:0^1 RD_B_DQ2 9 S_E2:5^1

RD_B_DQ33 83 M_C2:6^1 RD_B_DQ1 4 S_E2:1^1

RD_B_DQ32 81 M_C2:7^1 RD_B_DQ0 3 S_E2:0^1

Table 2 – B_DDR3D_2G (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘S’ in front of a TLA channel denotes the Slave card of the merged set

3. All signals on this page are acquired using the TLA’s demux capability and will not have

a MagniVu display value

DDR3THIN-MN-XXX 27 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

WrA_DatHi WR_A_DQ63 234 S_D2:0 WrA_DatLo WR_A_DQ31 156 M_D0:6

(Hex) WR_A_DQ62 233 S_D2:1 (Hex) WR_A_DQ30 155 M_D0:3

WR_A_DQ61 228 S_D2:5 WR_A_DQ29 150 S_C0:0

WR_A_DQ60 227 S_Q1 WR_A_DQ28 149 S_C0:1

WR_A_DQ59 115 S_D2:2 WR_A_DQ27 37 M_D0:4

WR_A_DQ58 114 S_D2:3 WR_A_DQ26 36 M_D0:1

WR_A_DQ57 109 S_D2:7 WR_A_DQ25 31 S_C0:2

WR_A_DQ56 108 S_D3:0 WR_A_DQ24 30 S_C0:3

WR_A_DQ55 225 S_D3:2 WR_A_DQ23 147 S_C0:4

WR_A_DQ54 224 S_D3:3 WR_A_DQ22 146 S_C0:5

WR_A_DQ53 219 S_D3:7 WR_A_DQ21 141 S_C1:2

WR_A_DQ52 218 S_D1:5 WR_A_DQ20 140 S_C1:3

WR_A_DQ51 106 S_D3:1 WR_A_DQ19 28 S_C0:6

WR_A_DQ50 105 S_D3:4 WR_A_DQ18 27 S_C0:7

WR_A_DQ49 100 S_D1:7 WR_A_DQ17 22 S_C1:1

WR_A_DQ48 99 S_D1:6 WR_A_DQ16 21 S_C1:4

WR_A_DQ47 216 S_D1:4 WR_A_DQ15 138 S_C1:6

WR_A_DQ46 215 S_D1:1 WR_A_DQ14 137 S_C1:7

WR_A_DQ45 210 S_D0:7 WR_A_DQ13 132 S_E1:4

WR_A_DQ44 209 S_D0:6 WR_A_DQ12 131 S_E1:1

WR_A_DQ43 97 S_D1:3 WR_A_DQ11 19 S_C1:5

WR_A_DQ42 96 S_D1:2 WR_A_DQ10 18 S_E1:7

WR_A_DQ41 91 S_D0:5 WR_A_DQ9 13 S_E1:3

WR_A_DQ40 90 S_D0:4 WR_A_DQ8 12 S_E1:2

WR_A_DQ39 207 S_D0:3 WR_A_DQ7 129 S_E1:0

WR_A_DQ38 206 S_D0:2 WR_A_DQ6 128 S_E0:7

WR_A_DQ37 201 M_C0:1 WR_A_DQ5 123 S_E0:3

WR_A_DQ36 200 M_C0:4 WR_A_DQ4 122 S_E0:2

WR_A_DQ35 88 S_D0:1 WR_A_DQ3 10 S_CK2

WR_A_DQ34 87 S_D0:0 WR_A_DQ2 9 S_E0:5

WR_A_DQ33 83 M_C0:6 WR_A_DQ1 4 S_E0:1

WR_A_DQ32 81 M_C0:7 WR_A_DQ0 3 S_E0:0

Table 2 – B_DDR3D_2G (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘S’ in front of a TLA channel denotes the Slave card of the merged set

DDR3THIN-MN-XXX 28 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

WrB_DatHi WR_B_DQ63 234 S_D2:0^1 WrB_DatLo WR_B_DQ31 156 M_D0:6^1

(Hex) WR_B_DQ62 233 S_D2:1^1 (Hex) WR_B_DQ30 155 M_D0:3^1

WR_B_DQ61 228 S_D2:5^1 WR_B_DQ29 150 S_C0:0^1

WR_B_DQ60 227 S_Q1^1 WR_B_DQ28 149 S_C0:1^1

WR_B_DQ59 115 S_D2:2^1 WR_B_DQ27 37 M_D0:4^1

WR_B_DQ58 114 S_D2:3^1 WR_B_DQ26 36 M_D0:1^1

WR_B_DQ57 109 S_D2:7^1 WR_B_DQ25 31 S_C0:2^1

WR_B_DQ56 108 S_D3:0^1 WR_B_DQ24 30 S_C0:3^1

WR_B_DQ55 225 S_D3:2^1 WR_B_DQ23 147 S_C0:4^1

WR_B_DQ54 224 S_D3:3^1 WR_B_DQ22 146 S_C0:5^1

WR_B_DQ53 219 S_D3:7^1 WR_B_DQ21 141 S_C1:2^1

WR_B_DQ52 218 S_D1:5^1 WR_B_DQ20 140 S_C1:3^1

WR_B_DQ51 106 S_D3:1^1 WR_B_DQ19 28 S_C0:6^1

WR_B_DQ50 105 S_D3:4^1 WR_B_DQ18 27 S_C0:7^1

WR_B_DQ49 100 S_D1:7^1 WR_B_DQ17 22 S_C1:1^1

WR_B_DQ48 99 S_D1:6^1 WR_B_DQ16 21 S_C1:4^1

WR_B_DQ47 216 S_D1:4^1 WR_B_DQ15 138 S_C1:6^1

WR_B_DQ46 215 S_D1:1^1 WR_B_DQ14 137 S_C1:7^1

WR_B_DQ45 210 S_D0:7^1 WR_B_DQ13 132 S_E1:4^1

WR_B_DQ44 209 S_D0:6^1 WR_B_DQ12 131 S_E1:1^1

WR_B_DQ43 97 S_D1:3^1 WR_B_DQ11 19 S_C1:5^1

WR_B_DQ42 96 S_D1:2^1 WR_B_DQ10 18 S_E1:7^1

WR_B_DQ41 91 S_D0:5^1 WR_B_DQ9 13 S_E1:3^1

WR_B_DQ40 90 S_D0:4^1 WR_B_DQ8 12 S_E1:2^1

WR_B_DQ39 207 S_D0:3^1 WR_B_DQ7 129 S_E1:0^1

WR_B_DQ38 206 S_D0:2v WR_B_DQ6 128 S_E0:7^1

WR_B_DQ37 201 M_C0:1^1 WR_B_DQ5 123 S_E0:3^1

WR_B_DQ36 200 M_C0:4^1 WR_B_DQ4 122 S_E0:2^1

WR_B_DQ35 88 S_D0:1v WR_B_DQ3 10 S_CK2^1

WR_B_DQ34 87 S_D0:0^1 WR_B_DQ2 9 S_E0:5^1

WR_B_DQ32 83 M_C0:6^1 WR_B_DQ1 4 S_E0:1^1

WR_B_DQ33 81 M_C0:7^1 WR_B_DQ0 3 S_E0:0^1

Table 2 – B_DDR3D_2G (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘S’ in front of a TLA channel denotes the Slave card of the merged set

3. All signals on this page are stored in the TLA7BB4’s Prime memory and will not have a

MagniVu display value

DDR3THIN-MN-XXX 29 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

RdAChkBits RD_A_CB7 165 M_A1:5 WrAChkBits 4 WR_A_CB7 165 M_D1:5

(OFF) RD_A_CB6 164 M_A1:4 (OFF) WR_A_CB6 164 M_D1:4

RD_A_CB5 159 M_A1:0 WR_A_CB5 159 M_D1:0

RD_A_CB4 158 M_A0:7 WR_A_CB4 158 M_D0:7

RD_A_CB3 46 M_A1:6 WR_A_CB3 46 M_D1:6

RD_A_CB2 45 M_A1:3 WR_A_CB2 45 M_D1:3

RD_A_CB1 40 M_CK1 WR_A_CB1 40 M_Q0

RD_A_CB0 39 M_A0:5 WR_A_CB0 39 M_D0:5

RdBChkBits 4 RD_B_CB7 165 M_A1:5^1 WrBChkBits 4 WR_B_CB7 165 M_D1:5^1

(OFF) RD_B_CB6 164 M_A1:4^1 (OFF) WR_B_CB6 164 M_D1:4^1

RD_B_CB5 159 M_A1:0^1 WR_B_CB5 159 M_D1:0^1

RD_B_CB4 158 M_A0:7^1 WR_B_CB4 158 M_D0:7^1

RD_B_CB3 46 M_A1:6^1 WR_B_CB3 46 M_D1:6^1

RD_B_CB2 45 M_A1:3^1 WR_B_CB2 45 M_D1:3^1

RD_B_CB1 40 M_CK1^1 WR_B_CB1 40 M_Q0^1

RD_B_CB0 39 M_A0:5^1 WR_B_CB0 39 M_D0:5^1

ADatMsks A_DM7/DQS16 230 S_A2:4 BDatMsks 4 B_DM7/DQS16 230 S_A2:4^1

(BIN) A_DM6/DQS15 221 S_A3:6 (BIN) B_DM6/DQS15 221 S_A3:6^1

A_DM5/DQS14 212 S_A1:0 B_DM5/DQS14 212 S_A1:0^1

A_DM4/DQS13 203 M_C2:0 B_DM4/DQS13 203 M_C2:0^1

A_DM3/DQS12 152 M_A0:2 B_DM3/DQS12 152 M_A0:2^1

A_DM2/DQS11 143 S_CK3 B_DM2/DQS11 143 S_CK3^1

A_DM1/DQS10 134 S_E3:5 B_DM1/DQS10 134 S_E3:5^1

A_DM0/DQS9 125 S_E2:6 B_DM0/DQS9 125 S_E2:6^1

Table 2 – B_DDR3D_2G (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. ‘ # ‘ denotes a low-true signal

2. The ‘S’ in front of a TLA channel denotes the Slave card of the merged set

3. The ‘M’ in front of a TLA channel denotes the Master card of the merged set

4. All signals on this page are stored in the TLA7BB4’s Prime memory and will not have a

MagniVu display value

DDR3THIN-MN-XXX 30 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Control 2 cCKE1 From Slot C M_E3:5 Address 2 BA2 52 M_A3:0

(SYM) cCKE0 From Slot C M_E3:4 (Hex) BA1 190 M_C3:7

bCLK1 From Slot B M_Q2 BA0 71 M_C1:6

bCLK0 From Slot B M_E1:7 A15 171 M_CK0

CKE1 169 M_A3:2 A14 172 M_A2:5

CKE0 50 M_A3:1 A13 196 M_CK3

cS1# From Slot C M_E2:6 A12/BC# 174 M_A2:4

cS0# From Slot C M_E2:2 A11 55 M_A2:6

bS1# From Slot B M_E0:4 A10/AP 70 M_C1:3

bS0# From Slot B M_E0:0 A9 175 M_A2:1

S3# 49 M_C2:5 A8 177 M_A2:0

S2# 48 M_C3:0 A7 56 M_A2:3

S1# 76 M_C3:4 A6 178 M_C0:3

S0# 193 M_C3:3 A5 58 M_A2:2

BA2 52 M_A3:0 A4 59 M_C0:5

BA1 190 M_C3:7 A3 180 M_C1:0

BA0 71 M_C1:6 A2 61 M_Q1

A15 171 M_CK0 A1 181 M_C1:1

A14 172 M_A2:5 A0 188 M_C1:5

A13 196 M_CK3 Strobes DQS7 111 S_A2:6

A12/BC# 174 M_A2:4 (HEX) DQS6 103 S_A3:5

A10/AP 70 M_C1:3 DQS5 94 S_CK1

RAS# 192 M_C3:6 DQS4 85 M_C2:3

CAS# 74 M_C3:5 DQS3 34 M_A0:1

WE# 73 M_C1:7 DQS2 25 S_C3:0

Misc 2 MISC1

Placeholder M_A3:5 DQS1 16 S_E3:6

(OFF) MISC0

Placeholder M_A3:4 DQS0 7 S_E2:4

DDRCK0+/- 184/185 M_C1:4 Ungrouped DQS8 43 M_A1:2

Unprobed All DQSx# 1_DQS8 43 S2_D3:2

DDRCK1+/- 63/64 DM8 161 M_A1:1

SA1 237 ERR_OUT#³ 53 M_A2:7

SDA 238 RESET# 168 M_A3:6

SA0 117 TEST 167 M_A3:7

SCL 118 ODT0 195 M_C2:0

ODT1 77 M_C2:1

PAR_IN 68 M_C1:2

Table 2 – B_DDR3D_2G (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. ‘ # ‘ denotes a low-true signal

2. These signals are required for accurate acquisition and post-processing of acquired data

3. The ‘S’ in front of a TLA channel denotes the Slave card of the merged set

4. The ‘M’ in front of a TLA channel denotes the Master card of the merged set

DDR3THIN-MN-XXX 31 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

RdA_DatHi RD_A_DQ63 234 S_A2:0 RdA_DatLo RD_A_DQ31 156 M_A0:6

(Hex) RD_A_DQ62 233 S_A2:1 (Hex) RD_A_DQ30 155 M_A0:3

RD_A_DQ61 228 S_A2:5 RD_A_DQ29 150 S_C2:0

RD_A_DQ60 227 S_CK0 RD_A_DQ28 149 S_C2:1

RD_A_DQ59 115 S_A2:2 RD_A_DQ27 37 M_A0:4

RD_A_DQ58 114 S_A2:3 RD_A_DQ26 36 M_A0:1

RD_A_DQ57 109 S_A2:7 RD_A_DQ25 31 S_C2:2

RD_A_DQ56 108 S_A3:0 RD_A_DQ24 30 S_C2:3

RD_A_DQ55 225 S_A3:2 RD_A_DQ23 147 S_C2:4

RD_A_DQ54 224 S_A3:3 RD_A_DQ22 146 S_C2:5

RD_A_DQ53 219 S_A3:7 RD_A_DQ21 141 S_C3:2

RD_A_DQ52 218 S_A1:5 RD_A_DQ20 140 S_C3:3

RD_A_DQ51 106 S_A3:1 RD_A_DQ19 28 S_C2:6

RD_A_DQ50 105 S_A3:4 RD_A_DQ18 27 S_C2:7

RD_A_DQ49 100 S_A1:7 RD_A_DQ17 22 S_C3:1

RD_A_DQ48 99 S_A1:6 RD_A_DQ16 21 S_C3:4

RD_A_DQ47 216 S_A1:4 RD_A_DQ15 138 S_C3:6

RD_A_DQ46 215 S_A1:1 RD_A_DQ14 137 S_C3:7

RD_A_DQ45 210 S_A0:7 RD_A_DQ13 132 S_E3:4

RD_A_DQ44 209 S_A0:6 RD_A_DQ12 131 S_E3:1

RD_A_DQ43 97 S_A1:3 RD_A_DQ11 19 S_C3:5

RD_A_DQ42 96 S_A1:2 RD_A_DQ10 18 S_E3:7

RD_A_DQ41 91 S_A0:5 RD_A_DQ9 13 S_E3:3

RD_A_DQ40 90 S_A0:4 RD_A_DQ8 12 S_E3:2

RD_A_DQ39 207 S_A0:3 RD_A_DQ7 129 S_E3:0

RD_A_DQ38 206 S_A0:2 RD_A_DQ6 128 S_E2:7

RD_A_DQ37 201 M_C2:1 RD_A_DQ5 123 S_E2:3

RD_A_DQ36 200 M_C2:4 RD_A_DQ4 122 S_E2:2

RD_A_DQ35 88 S_A0:1 RD_A_DQ3 10 S_Q3

RD_A_DQ34 87 S_A0:0 RD_A_DQ2 9 S_E2:5

RD_A_DQ33 83 M_C2:6 RD_A_DQ1 4 S_E2:1

RD_A_DQ32 81 M_C2:7 RD_A_DQ0 3 S_E2:0

Table 3 - B_DDR3D_3A (<=1066MT/s Read and Write) TLA Channel Grouping

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘M’ in front of a TLA channel denotes the Master card of the merged set

3. The ‘S’ in front of a TLA channel denotes Slave card #1 of the merged set

DDR3THIN-MN-XXX 32 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin#

TLA

Input

Group

Name

Signal

Name

DDR3

Pin#

TLA

Input

RdB_DatHi RD_B_DQ63 234 S_A2:0^1 RdB_DatLo RD_B_DQ31 156 M_A0:6^1

(Hex) RD_B_DQ62 233 S_A2:1^1 (Hex) RD_B_DQ30 155 M_A0:3^1

RD_B_DQ61 228 S_A2:5^1 RD_B_DQ29 150 S_C2:0^1

RD_B_DQ60 227 S_CK0^1 RD_B_DQ28 149 S_C2:1^1

RD_B_DQ59 115 S_A2:2^1 RD_B_DQ27 37 M_A0:4^1

RD_B_DQ58 114 S_A2:3^1 RD_B_DQ26 36 M_A0:1^1

RD_B_DQ57 109 S_A2:7^1 RD_B_DQ25 31 S_C2:2^1

RD_B_DQ56 108 S_A3:0^1 RD_B_DQ24 30 S_C2:3^1

RD_B_DQ55 225 S_A3:2^1 RD_B_DQ23 147 S_C2:4^1

RD_B_DQ54 224 S_A3:3^1 RD_B_DQ22 146 S_C2:5^1

RD_B_DQ53 219 S_A3:7^1 RD_B_DQ21 141 S_C3:2^1

RD_B_DQ52 218 S_A1:5^1 RD_B_DQ20 140 S_C3:3^1

RD_B_DQ51 106 S_A3:1^1 RD_B_DQ19 28 S_C2:6^1

RD_B_DQ50 105 S_A3:4^1 RD_B_DQ18 27 S_C2:7^1

RD_B_DQ49 100 S_A1:7^1 RD_B_DQ17 22 S_C3:1^1

RD_B_DQ48 99 S_A1:6^1 RD_B_DQ16 21 S_C3:4^1

RD_B_DQ47 216 S_A1:4^1 RD_B_DQ15 138 S_C3:6^1

RD_B_DQ46 215 S_A1:1^1 RD_B_DQ14 137 S_C3:7^1

RD_B_DQ45 210 S_A0:7^1 RD_B_DQ13 132 S_E3:4^1

RD_B_DQ44 209 S_A0:6^1 RD_B_DQ12 131 S_E3:1^1

RD_B_DQ43 97 S_A1:3^1 RD_B_DQ11 19 S_C3:5^1

RD_B_DQ42 96 S_A1:2^1 RD_B_DQ10 18 S_E3:7^1

RD_B_DQ41 91 S_A0:5^1 RD_B_DQ9 13 S_E3:3^1

RD_B_DQ40 90 S_A0:4^1 RD_B_DQ8 12 S_E3:2^1

RD_B_DQ39 207 S_A0:3^1 RD_B_DQ7 129 S_E3:0^1

RD_B_DQ38 206 S_A0:2^1 RD_B_DQ6 128 S_E2:7^1

RD_B_DQ37 201 M_C2:1^1 RD_B_DQ5 123 S_E2:3^1

RD_B_DQ36 200 M_C2:4^1 RD_B_DQ4 122 S_E2:2^1

RD_B_DQ35 88 S_A0:1^1 RD_B_DQ3 10 S_Q3^1

RD_B_DQ34 87 S_A0:0^1 RD_B_DQ2 9 S_E2:5^1

RD_B_DQ33 83 M_C2:6^1 RD_B_DQ1 4 S_E2:1^1

RD_B_DQ32 81 M_C2:7^1 RD_B_DQ0 3 S_E2:0^1

Table 3 – B_DDR3D_3A (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘M’ in front of a TLA channel denotes the Master card of the merged set

3. The ‘S’ in front of a TLA channel denotes Slave card #1 of the merged set

4. All signals on this page are stored in the TLA7BB4’s Prime memory and will not have a

MagniVu display value

DDR3THIN-MN-XXX 33 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

1_RdA_DatHi 1_RD_A_DQ63 234 S2_A0:0 1_RdA_DatLo 1_RD_A_DQ31 156 S2_D2:6

(Hex) 1_RD_A_DQ62 233 S2_A0:1 (Hex) 1_RD_A_DQ30 155 S2_D2:3

1_RD_A_DQ61 228 S2_A0:5 1_RD_A_DQ29 150 S2_E2:0

1_RD_A_DQ60 227 S2_CK1 1_RD_A_DQ28 149 S2_E2:1

1_RD_A_DQ59 115 S2_A0:2 1_RD_A_DQ27 37 S2_D2:4

1_RD_A_DQ58 114 S2_A0:3 1_RD_A_DQ26 36 S2_D2:1

1_RD_A_DQ57 109 S2_A0:7 1_RD_A_DQ25 31 S2_E2:2

1_RD_A_DQ56 108 S2_A1:0 1_RD_A_DQ24 30 S2_E2:3

1_RD_A_DQ55 225 S2_A1:2 1_RD_A_DQ23 147 S2_E2:4

1_RD_A_DQ54 224 S2_A1:3 1_RD_A_DQ22 146 S2_E2:5

1_RD_A_DQ53 219 S2_A1:7 1_RD_A_DQ21 141 S2_E3:2

1_RD_A_DQ52 218 S2_D1:5 1_RD_A_DQ20 140 S2_E3:3

1_RD_A_DQ51 106 S2_A1:1 1_RD_A_DQ19 28 S2_E2:6

1_RD_A_DQ50 105 S2_A1:4 1_RD_A_DQ18 27 S2_E2:7

1_RD_A_DQ49 100 S2_D1:7 1_RD_A_DQ17 22 S2_E3:1

1_RD_A_DQ48 99 S2_D1:6 1_RD_A_DQ16 21 S2_E3:4

1_RD_A_DQ47 216 S2_D1:4 1_RD_A_DQ15 138 S2_E3:6

1_RD_A_DQ46 215 S2_D1:1 1_RD_A_DQ14 137 S2_E3:7

1_RD_A_DQ45 210 S2_D0:7 1_RD_A_DQ13 132 S2_E1:4

1_RD_A_DQ44 209 S2_D0:6 1_RD_A_DQ12 131 S2_E1:1

1_RD_A_DQ43 97 S2_D1:3 1_RD_A_DQ11 19 S2_E3:5

1_RD_A_DQ42 96 S2_D1:2 1_RD_A_DQ10 18 S2_E1:7

1_RD_A_DQ41 91 S2_D0:5 1_RD_A_DQ9 13 S2_E1:3

1_RD_A_DQ40 90 S2_D0:4 1_RD_A_DQ8 12 S2_E1:2

1_RD_A_DQ39 207 S2_D0:3 1_RD_A_DQ7 129 S2_E1:0

1_RD_A_DQ38 206 S2_D0:2 1_RD_A_DQ6 128 S2_E0:7

1_RD_A_DQ37 201 S2_C2:1 1_RD_A_DQ5 123 S2_E0:3

1_RD_A_DQ36 200 S2_C2:4 1_RD_A_DQ4 122 S2_E0:2

1_RD_A_DQ35 88 S2_D0:1 1_RD_A_DQ3 10 S2_Q2

1_RD_A_DQ34 87 S2_D0:0 1_RD_A_DQ2 9 S2_E0:5

1_RD_A_DQ33 83 S2_C2:6 1_RD_A_DQ1 4 S2_E0:1

1_RD_A_DQ32 81 S2_C2:7 1_RD_A_DQ0 3 S2_E0:0

Table 3 – B_DDR3D_3A (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. These signals are acquired from the second DIMM slot

2. All signals on this page are required for accurate post-processing of acquired data

3. The ‘S2’ in front of a TLA channel denotes Slave card #2 of the merged set

DDR3THIN-MN-XXX 34 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin#

TLA

Input

Group

Name

Signal

Name

DDR3

Pin#

TLA

Input

1_RdB_DatHi 1_RD_B_DQ63 234 S2_A0:0^1 1_RdB_DatLo 1_RD_B_DQ31 156 S2_D2:6^1

(Hex) 1_RD_B_DQ62 233 S2_A0:1^1 (Hex) 1_RD_B_DQ30 155 S2_D2:3^1

1_RD_B_DQ61 228 S2_A0:5^1 1_RD_B_DQ29 150 S2_E2:0^1

1_RD_B_DQ60 227 S2_CK1^1 1_RD_B_DQ28 149 S2_E2:1^1

1_RD_B_DQ59 115 S2_A0:2^1 1_RD_B_DQ27 37 S2_D2:4^1

1_RD_B_DQ58 114 S2_A0:3^1 1_RD_B_DQ26 36 S2_D2:1^1

1_RD_B_DQ57 109 S2_A0:7^1 1_RD_B_DQ25 31 S2_E2:2^1

1_RD_B_DQ56 108 S2_A1:0^1 1_RD_B_DQ24 30 S2_E2:3^1

1_RD_B_DQ55 225 S2_A1:2^1 1_RD_B_DQ23 147 S2_E2:4^1

1_RD_B_DQ54 224 S2_A1:3^1 1_RD_B_DQ22 146 S2_E2:5^1

1_RD_B_DQ53 219 S2_A1:7^1 1_RD_B_DQ21 141 S2_E3:2^1

1_RD_B_DQ52 218 S2_D1:5^1 1_RD_B_DQ20 140 S2_E3:3^1

1_RD_B_DQ51 106 S2_A1:1^1 1_RD_B_DQ19 28 S2_E2:6^1

1_RD_B_DQ50 105 S2_A1:4^1 1_RD_B_DQ18 27 S2_E2:7^1

1_RD_B_DQ49 100 S2_D1:7^1 1_RD_B_DQ17 22 S2_E3:1^1

1_RD_B_DQ48 99 S2_D1:6^1 1_RD_B_DQ16 21 S2_E3:4^1

1_RD_B_DQ47 216 S2_D1:4^1 1_RD_B_DQ15 138 S2_E3:6^1

1_RD_B_DQ46 215 S2_D1:1^1 1_RD_B_DQ14 137 S2_E3:7^1

1_RD_B_DQ45 210 S2_D0:7^1 1_RD_B_DQ13 132 S2_E1:4^1

1_RD_B_DQ44 209 S2_D0:6^1 1_RD_B_DQ12 131 S2_E1:1^1

1_RD_B_DQ43 97 S2_D1:3^1 1_RD_B_DQ11 19 S2_E3:5^1

1_RD_B_DQ42 96 S2_D1:2^1 1_RD_B_DQ10 18 S2_E1:7^1

1_RD_B_DQ41 91 S2_D0:5^1 1_RD_B_DQ9 13 S2_E1:3^1

1_RD_B_DQ40 90 S2_D0:4^1 1_RD_B_DQ8 12 S2_E1:2^1

1_RD_B_DQ39 207 S2_D0:3^1 1_RD_B_DQ7 129 S2_E1:0^1

1_RD_B_DQ38 206 S2_D0:2^1 1_RD_B_DQ6 128 S2_E0:7^1

1_RD_B_DQ37 201 S2_C2:1^1 1_RD_B_DQ5 123 S2_E0:3^1

1_RD_B_DQ36 200 S2_C2:4^1 1_RD_B_DQ4 122 S2_E0:2^1

1_RD_B_DQ35 88 S2_D0:1^1 1_RD_B_DQ3 10 S2_Q2^1

1_RD_B_DQ34 87 S2_D0:0^1 1_RD_B_DQ2 9 S2_E0:5^1

1_RD_B_DQ33 83 S2_C2:6^1 1_RD_B_DQ1 4 S2_E0:1^1

1_RD_B_DQ32 81 S2_C2:7^1 1_RD_B_DQ0 3 S2_E0:0^1

Table 3 – B_DDR3D_3A (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. These signals are acquired from the second DIMM slot

2. All signals on this page are required for accurate post-processing of acquired data

3. The ‘S2’ in front of a TLA channel denotes Slave card #2 of the merged set

4. All signals on this page are stored in the TLA7BB4’s Prime memory and will not have a

MagniVu display value

DDR3THIN-MN-XXX 35 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

WrA_DatHi WR_A_DQ63 234 S_D2:0 WrA_DatLo WR_A_DQ31 156 M_D0:6

(Hex) WR_A_DQ62 233 S_D2:1 (Hex) WR_A_DQ30 155 M_D0:3

WR_A_DQ61 228 S_D2:5 WR_A_DQ29 150 S_C0:0

WR_A_DQ60 227 S_Q1 WR_A_DQ28 149 S_C0:1

WR_A_DQ59 115 S_D2:2 WR_A_DQ27 37 M_D0:4

WR_A_DQ58 114 S_D2:3 WR_A_DQ26 36 M_D0:1

WR_A_DQ57 109 S_D2:7 WR_A_DQ25 31 S_C0:2

WR_A_DQ56 108 S_D3:0 WR_A_DQ24 30 S_C0:3

WR_A_DQ55 225 S_D3:2 WR_A_DQ23 147 S_C0:4

WR_A_DQ54 224 S_D3:3 WR_A_DQ22 146 S_C0:5

WR_A_DQ53 219 S_D3:7 WR_A_DQ21 141 S_C1:2

WR_A_DQ52 218 S_D1:5 WR_A_DQ20 140 S_C1:3

WR_A_DQ51 106 S_D3:1 WR_A_DQ19 28 S_C0:6

WR_A_DQ50 105 S_D3:4 WR_A_DQ18 27 S_C0:7

WR_A_DQ49 100 S_D1:7 WR_A_DQ17 22 S_C1:1

WR_A_DQ48 99 S_D1:6 WR_A_DQ16 21 S_C1:4

WR_A_DQ47 216 S_D1:4 WR_A_DQ15 138 S_C1:6

WR_A_DQ46 215 S_D1:1 WR_A_DQ14 137 S_C1:7

WR_A_DQ45 210 S_D0:7 WR_A_DQ13 132 S_E1:4

WR_A_DQ44 209 S_D0:6 WR_A_DQ12 131 S_E1:1

WR_A_DQ43 97 S_D1:3 WR_A_DQ11 19 S_C1:5

WR_A_DQ42 96 S_D1:2 WR_A_DQ10 18 S_E1:7

WR_A_DQ41 91 S_D0:5 WR_A_DQ9 13 S_E1:3

WR_A_DQ40 90 S_D0:4 WR_A_DQ8 12 S_E1:2

WR_A_DQ39 207 S_D0:3 WR_A_DQ7 129 S_E1:0

WR_A_DQ38 206 S_D0:2 WR_A_DQ6 128 S_E0:7

WR_A_DQ37 201 M_C0:1 WR_A_DQ5 123 S_E0:3

WR_A_DQ36 200 M_C0:4 WR_A_DQ4 122 S_E0:2

WR_A_DQ35 88 S_D0:1 WR_A_DQ3 10 S_CK2

WR_A_DQ34 87 S_D0:0 WR_A_DQ2 9 S_E0:5

WR_A_DQ33 83 M_C0:6 WR_A_DQ1 4 S_E0:1

WR_A_DQ32 81 M_C0:7 WR_A_DQ0 3 S_E0:0

Table 3 – B_DDR3D_3A (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘M’ in front of a TLA channel denotes the Master card of the merged set

3. The ‘S’ in front of a TLA channel denotes Slave card #1 of the merged set

DDR3THIN-MN-XXX 36 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

WrB_DatHi WR_B_DQ63 234 S_D2:0^1 WrB_DatLo WR_B_DQ31 156 M_D0:6^1

(Hex) WR_B_DQ62 233 S_D2:1^1 (Hex) WR_B_DQ30 155 M_D0:3^1

WR_B_DQ61 228 S_D2:5^1 WR_B_DQ29 150 S_C0:0^1

WR_B_DQ60 227 S_Q1^1 WR_B_DQ28 149 S_C0:1^1

WR_B_DQ59 115 S_D2:2^1 WR_B_DQ27 37 M_D0:4^1

WR_B_DQ58 114 S_D2:3^1 WR_B_DQ26 36 M_D0:1^1

WR_B_DQ57 109 S_D2:7^1 WR_B_DQ25 31 S_C0:2^1

WR_B_DQ56 108 S_D3:0^1 WR_B_DQ24 30 S_C0:3^1

WR_B_DQ55 225 S_D3:2^1 WR_B_DQ23 147 S_C0:4^1

WR_B_DQ54 224 S_D3:3^1 WR_B_DQ22 146 S_C0:5^1

WR_B_DQ53 219 S_D3:7^1 WR_B_DQ21 141 S_C1:2^1

WR_B_DQ52 218 S_D1:5^1 WR_B_DQ20 140 S_C1:3^1

WR_B_DQ51 106 S_D3:1^1 WR_B_DQ19 28 S_C0:6^1

WR_B_DQ50 105 S_D3:4^1 WR_B_DQ18 27 S_C0:7^1

WR_B_DQ49 100 S_D1:7^1 WR_B_DQ17 22 S_C1:1v

WR_B_DQ48 99 S_D1:6^1 WR_B_DQ16 21 S_C1:4^1

WR_B_DQ47 216 S_D1:4^1 WR_B_DQ15 138 S_C1:6^1

WR_B_DQ46 215 S_D1:1^1 WR_B_DQ14 137 S_C1:7^1

WR_B_DQ45 210 S_D0:7^1 WR_B_DQ13 132 S_E1:4^1

WR_B_DQ44 209 S_D0:6^1 WR_B_DQ12 131 S_E1:1v

WR_B_DQ43 97 S_D1:3^1 WR_B_DQ11 19 S_C1:5^1

WR_B_DQ42 96 S_D1:2^1 WR_B_DQ10 18 S_E1:7^1

WR_B_DQ41 91 S_D0:5^1 WR_B_DQ9 13 S_E1:3^1

WR_B_DQ40 90 S_D0:4^1 WR_B_DQ8 12 S_E1:2^1

WR_B_DQ39 207 S_D0:3^1 WR_B_DQ7 129 S_E1:0^1

WR_B_DQ38 206 S_D0:2^1 WR_B_DQ6 128 S_E0:7^1

WR_B_DQ37 201 M_C0:1^1 WR_B_DQ5 123 S_E0:3^1

WR_B_DQ36 200 M_C0:4^1 WR_B_DQ4 122 S_E0:2^1

WR_B_DQ35 88 S_D0:1^1 WR_B_DQ3 10 S_CK2^1

WR_B_DQ34 87 S_D0:0^1 WR_B_DQ2 9 S_E0:5^1

WR_B_DQ32 83 M_C0:6^1 WR_B_DQ1 4 S_E0:1^1

WR_B_DQ33 81 M_C0:7^1 WR_B_DQ0 3 S_E0:0^1

Table 3 – B_DDR3D_3A (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘M’ in front of a TLA channel denotes the Master card of the merged set

3. The ‘S’ in front of a TLA channel denotes Slave card #1 of the merged set

4. All signals on this page are stored in the TLA7BB4’s Prime memory and will not have a

MagniVu display value

DDR3THIN-MN-XXX 37 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

RdAChkBits RD_A_CB7 165 M_A1:5 WrAChkBits 4 WR_A_CB7 165 M_D1:5

(OFF) RD_A_CB6 164 M_A1:4 (OFF) WR_A_CB6 164 M_D1:4

RD_A_CB5 159 M_A1:0 WR_A_CB5 159 M_D1:0

RD_A_CB4 158 M_A0:7 WR_A_CB4 158 M_D0:7

RD_A_CB3 46 M_A1:6 WR_A_CB3 46 M_D1:6

RD_A_CB2 45 M_A1:3 WR_A_CB2 45 M_D1:3

RD_A_CB1 40 M_CK1 WR_A_CB1 40 M_Q0

RD_A_CB0 39 M_A0:5 WR_A_CB0 39 M_D0:5

RdBChkBits 4 RD_B_CB7 165 M_A1:5^1 WrBChkBits 4 WR_B_CB7 165 M_D1:5^1

(OFF) RD_B_CB6 164 M_A1:4^1 (OFF) WR_B_CB6 164 M_D1:4^1

RD_B_CB5 159 M_A1:0^1 WR_B_CB5 159 M_D1:0^1

RD_B_CB4 158 M_A0:7^1 WR_B_CB4 158 M_D0:7^1

RD_B_CB3 46 M_A1:6^1 WR_B_CB3 46 M_D1:6^1

RD_B_CB2 45 M_A1:3^1 WR_B_CB2 45 M_D1:3^1

RD_B_CB1 40 M_CK1^1 WR_B_CB1 40 M_Q0^1

RD_B_CB0 39 M_A0:5^1 WR_B_CB0 39 M_D0:5^1

1_RdAChkBits 1_RD_A_CB7 165 S2_D3:5 1_RdBChkBits 4 1_RD_B_CB7 165 S2_D3:5^1

(OFF) 1_RD_A_CB6 164 S2_D3:4 (OFF) 1_RD_B_CB6 164 S2_D3:4^1

1_RD_A_CB5 159 S2_D3:0 1_RD_B_CB5 159 S2_D3:0^1

1_RD_A_CB4 158 S2_D2:7 1_RD_B_CB4 158 S2_D2:7^1

1_RD_A_CB3 46 S2_D3:6 1_RD_B_CB3 46 S2_D3:6^1

1_RD_A_CB2 45 S2_D3:3 1_RD_B_CB2 45 S2_D3:3^1

1_RD_A_CB1 40 S2_Q0 1_RD_B_CB1 40 S2_Q0^1

1_RD_A_CB0 39 S2_D2:5 1_RD_B_CB0 39 S2_D2:5^1

ADatMsks A_DM7/DQS16 230 S_A2:4 BDatMsks 4 B_DM7/DQS16 230 S_A2:4^1

(BIN) A_DM6/DQS15 221 S_A3:6 (BIN) B_DM6/DQS15 221 S_A3:6^1

A_DM5/DQS14 212 S_A1:0 B_DM5/DQS14 212 S_A1:0^1

A_DM4/DQS13 203 M_C2:0 B_DM4/DQS13 203 M_C2:0^1

A_DM3/DQS12 152 M_A0:2 B_DM3/DQS12 152 M_A0:2^1

A_DM2/DQS11 143 S_CK3 B_DM2/DQS11 143 S_CK3^1

A_DM1/DQS10 134 S_E3:5 B_DM1/DQS10 134 S_E3:5^1

A_DM0/DQS9 125 S_E2:6 B_DM0/DQS9 125 S_E2:6^1

Table 3 – B_DDR3D_3A (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. ‘ # ‘ denotes a low-true signal

2. The ‘M’ in front of a TLA channel denotes the Master card of the merged set

3. The ‘S’ in front of a TLA channel denotes Slave card #1 of the merged set

4. The ‘S2’ in front of a TLA channel denotes Slave card #2 of the merged set

5. Signals in these groups are acquired using the TLA’s demux capability and will not have

a MagniVu display value

DDR3THIN-MN-XXX 38 Doc. Rev. 1.11

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Control 2 CKE1 169 M_A3:2 Address 2 BA2 52 M_A3:0

(SYM) CKE0 50 M_A3:1 (Hex) BA1 190 M_C3:7

S3# 49 S2_C2:5 BA0 71 M_C1:6

S2# 48 S2_C3:0 A15 171 M_CK0

S1# 76 M_C3:4 A14 172 M_A2:5

S0# 193 M_C3:3 A13 196 M_CK3

BA2 52 M_A3:0 A12/BC# 174 M_A2:4

BA1 190 M_C3:7 A11 55 M_A2:6

BA0 71 M_C1:6 A10/AP 70 M_C1:3

A15 171 M_CK0 A9 175 M_A2:1

A14 172 M_A2:5 A8 177 M_A2:0

A13 196 M_CK3 A7 56 M_A2:3

A12/BC# 174 M_A2:4 A6 178 M_C0:3

A10/AP 70 M_C1:3 A5 58 M_A2:2

RAS# 192 M_C3:6 A4 59 M_C0:5

CAS# 74 M_C3:5 A3 180 M_C1:0

WE# 73 M_C1:7 A2 61 M_Q1

Strobes DQS7 111 S_A2:6 A1 181 M_C1:1

(HEX) DQS6 103 S_A3:5 A0 188 M_C1:5

DQS5 94 S_CK1 Misc 2 MISC1

Placeholder M_A3:5

DQS4 85 M_C2:3 (OFF) MISC0

Placeholder M_A3:4

DQS3 34 M_A0:1 DDRCK0+/- 184/185 M_C1:4

DQS2 25 S_C3:0 Ungrouped DQS8 43 M_A1:2

DQS1 16 S_E3:6 DM8 161 M_A1:1

DQS0 7 S_E2:4 ERR_OUT#³ 53 M_A2:7

Unprobed All DQSx# RESET# 168 M_A3:6

DDRCK1+/- 63/64 TEST 167 M_A3:7

SA1 237 ODT0 195 M_C2:0

SDA 238 ODT1 77 M_C2:1

SA0 117 PAR_IN 68 M_C1:2

SCL 118

Table 3 – B_DDR3D_3A TLA Channel Grouping (cont’d.)

Notes:

1. ‘ # ‘ denotes a low-true signal

2. These signals are required for accurate acquisition and post-processing of acquired data

3. The ‘M’ in front of a TLA channel denotes the Master card of the merged set

4. The ‘S’ in front of a TLA channel denotes Slave card #1 of the merged set

5. The ‘S2’ in front of a TLA channel denotes Slave card #2 of the merged set

6. Signals in these groups are acquired using the TLA’s demux capability and will not have

a MagniVu display value

DDR3THIN-MN-XXX 39 Doc. Rev. 1.11

3.7 Display Groups not in Tables 1,2 or 3

There are several groups in the List window that are not documented in the tables as these

groups are used only by the post-processing display software. To ensure correct data display

these groups must not be modified. These groups are:

• DataHi

• DataLo

• ChekBits

• Command

• DataMasks

• MRSAddr

DDR3THIN-MN-XXX 40 Doc. Rev. 1.11

4.0 CLOCK SELECTION

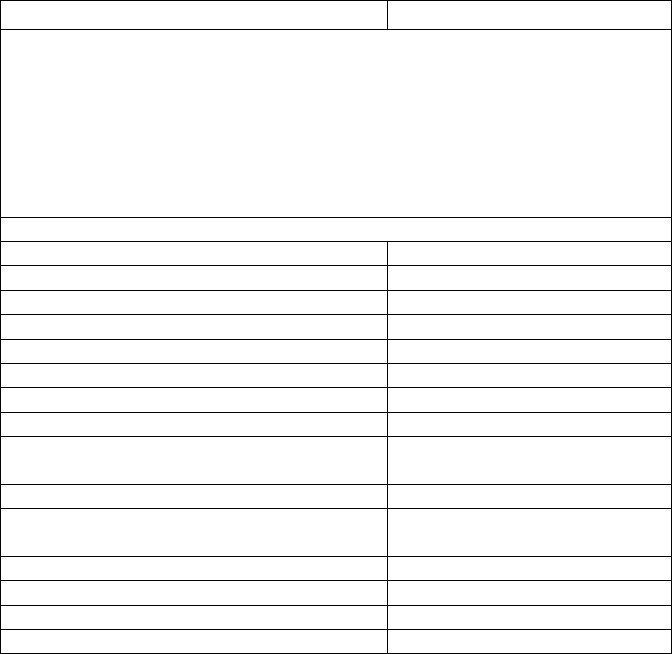

4.1 B_DDR3D_2D Clocking Selections

There are two clocking option fields available when using the B_DDR3D_2D support package.

These select fields permit the user to setup the TLA acquisition as follows:

SDRAM Clocking: – Permits selecting the Clocking Mode to be used to acquire DDR3

data. It is important to note that the selection chosen will force unused Chip Selects and

CKE1 into inactive states. The field choices are:

S0#; Every Rising Edge (default) – Clocks data using every rising edge of DDR

Clock 0. Forces CKE1 low and S1-3# high. No Idle Cycle filtering is done.

S0# & S1#; Every Rising Edge – Clocks data using every rising edge of DDR

Clock 0. Forces S2-3# high. No Idle Cycle filtering is done.

S0-3#; Every Rising Edge – Clocks data using every rising edge of DDR Clock

0. No Idle Cycle filtering is done.

S0#; Total L <=5 – utilizes Selective Clocking to reduce acquisition of Idle bus

states. Forces CKE1 low and S1-3# high.

S0# & S1#; Total L <=5 - utilizes Selective Clocking to reduce acquisition of

Idle bus states. Forces S2-3# high.

S0-3#; Total L <=5 - utilizes Selective Clocking to reduce acquisition of Idle bus

states.

S0#; Total L <=6

S0# & S1#; Total L <=6

S0-3#; Total L <=6

.

.

.

S0#; Total L <=25

S0# & S1#; Total L <=25

S0-3#; Total L <=25

The above selections reduce the number of Idle cycles stored by the acquisition

card to provide optimum use of the acquisition memory. Data is stored whenever

RAS# or CAS# is asserted low along with a valid Chip Select. After every

assertion of CAS# (paired with a valid Chip Select) samples are taken during the

next X DDR Clock cycles to ensure that all valid memory cycles have been

acquired. The acquisition then pauses and waits for the next Command. If CAS#

and a Chip Select are asserted during these X clock cycles the count is reset. The

X-clock cycle value is determined by adding the maximum Burst Length of 8

clock cycles to the selected maximum Read Latency. So for a selected Total

DDR3THIN-MN-XXX 41 Doc. Rev. 1.11

Latency of <= 5 cycles the support software will store a total of 13 clock cycles

worth of data after the Read or Write Command appears on the bus.

Refresh Cycles: – Permits choosing whether Refresh Cycles will be stored or not. The

field choices are:

Acquire (default) – Refresh Cycles will be stored.

Do Not Acquire – This mode will reduce the number of Refresh cycles stored by

the acquisition card to provide optimum use of the acquisition memory.

NOTE: This mode is disabled when the SDRAM Clocking choice is set to a