FPGA Surevyor III XC3S200 Board_Manual 3HA05 2.FPGA XC3S200F F4 Board Manual

FPGA_Surevyor-III_XC3S200F_F4_Board_Manual

3HA05-2.FPGA_Surevyor-III_XC3S200F_F4_Board_Manual

User Manual: Pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 18

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

1

FPGA Surveyor-III XC3S200F

FPGA Surveyor-III XC3S200F4

BoardManual

APEX INSTRUMENT CO., LTD.

77/9 1 10900 .:0-2939-2084 : 0-2939-2084

77/9 SOI LADPRAO 1 , LADPRAO ROAD , JOMPOL , JATUJAK DISTRICT , BANGKOK THAILAND 10900 TEL. 0-2939-2084 FAX.0-2939-2084

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

2

FPGA Surveyor-III XC3S200

FPGA Surveyor-III XC3S200F FPGA Surveyor-III XC3S200F4 FPGA

Logic Trainer 1 FPGA

200,000 400,000 Platform Flash PROM

Platform Flash PROM JTAG 20,000

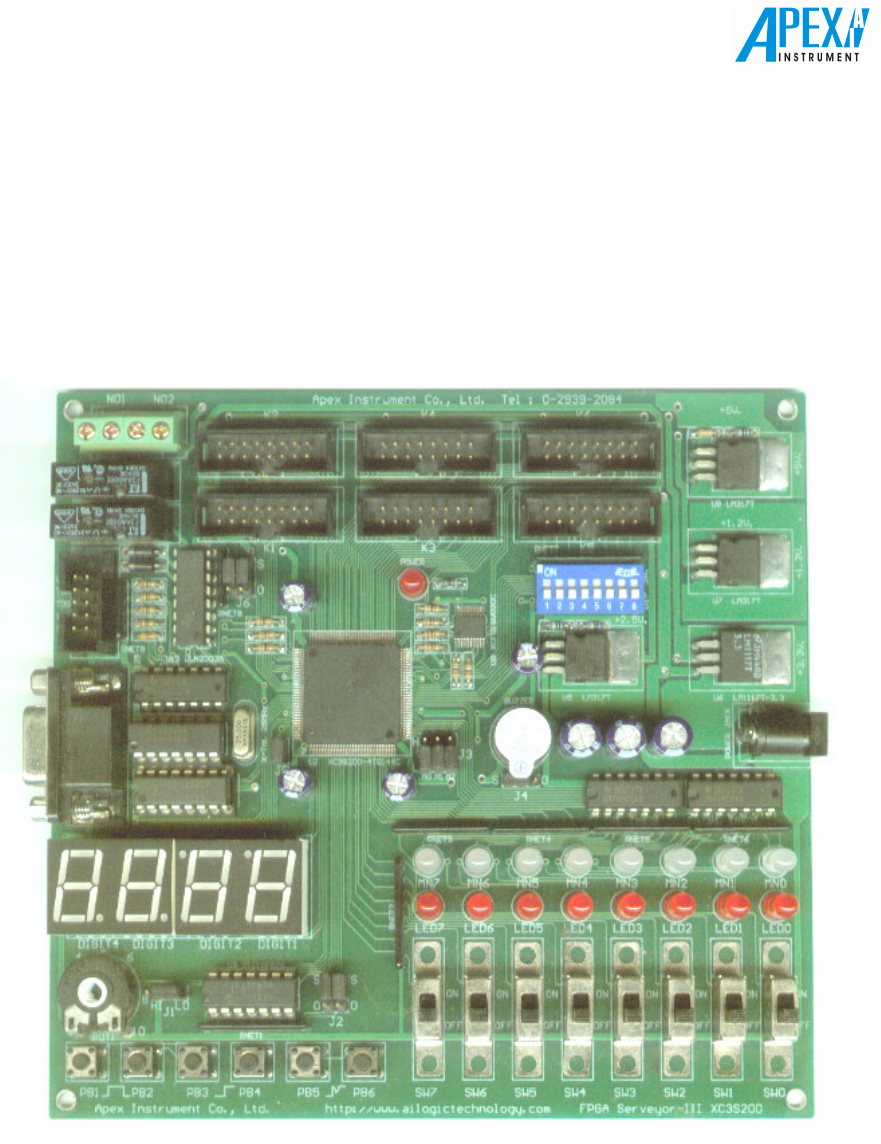

1 FPGA Surveyor-III XC3S200

FPGA Surveyor-III XC3S200

• FPGA Spatan-3 XC3S200-4TQ144C (XC3S400-4TQ144C F4)

• Platform Flash PROM XCF01SVO20C (XCF02VO20C F4)

• 7 Segment 4

• DIP Switch 8

• LED 3 8

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

3

• LED 2 8

• Logic Switch ( Slide Switch ) 8

• Switch One-Shot 2

• Switch Bounce 2

• Switch Bounceless 2

• 6 Expansion ports ( 48 Bits I/O )

• Relay 220 V/3A 2

• Clock generator :1100Hz 101KHz

• Buzzer 1

• 25 MHz Oscillator

FPGA Spartan-3 XC3S200

FPGA Spatan-3 RAM 216Kbits

12 DCM 4

• 200,000

• 18Kb block RAMs 12 216K bits( 18 F4)

• 18x18 hardware multiplier 12 ( 18 F4)

• Digital Clock Manager (DCM) 4

• Digitally Controlled Impedance (DCI)

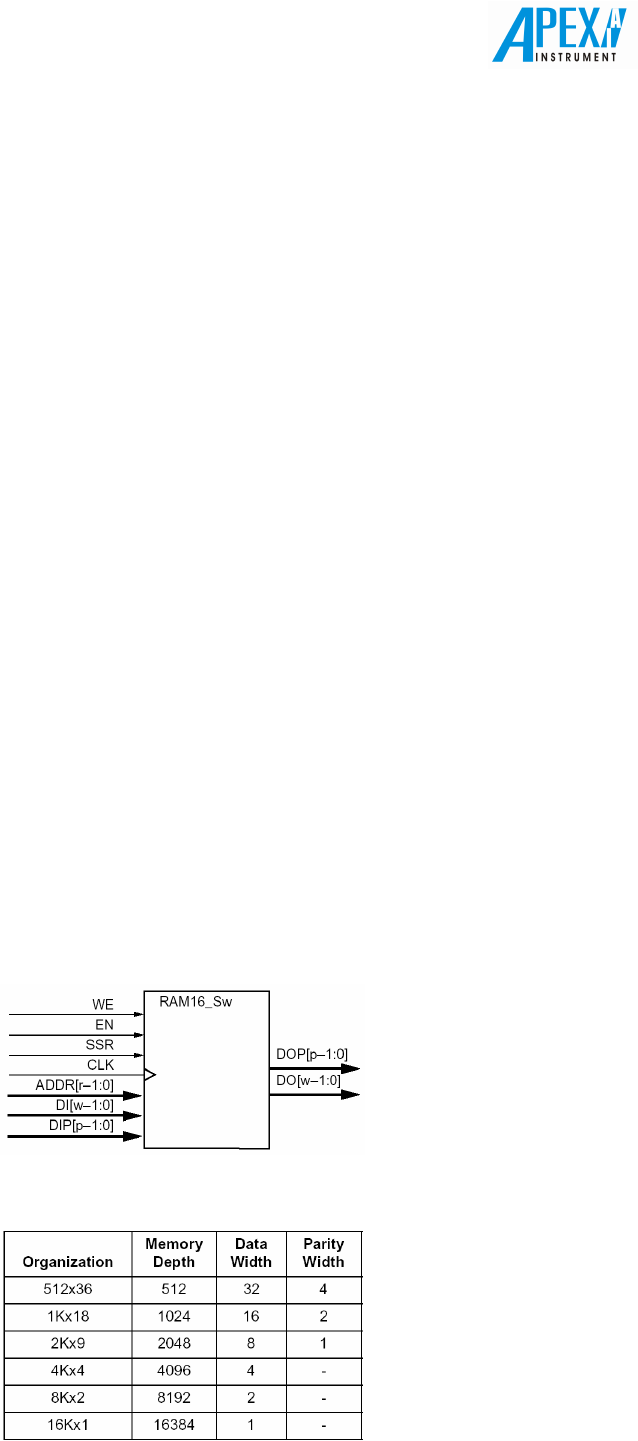

1.) 18Kb block RAM

18Kb block RAM 200 Mhz 12 Block RAM

RAM ROM 2 3

2 RAM Single Port

3 RAM Single Port Block RAM

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

4

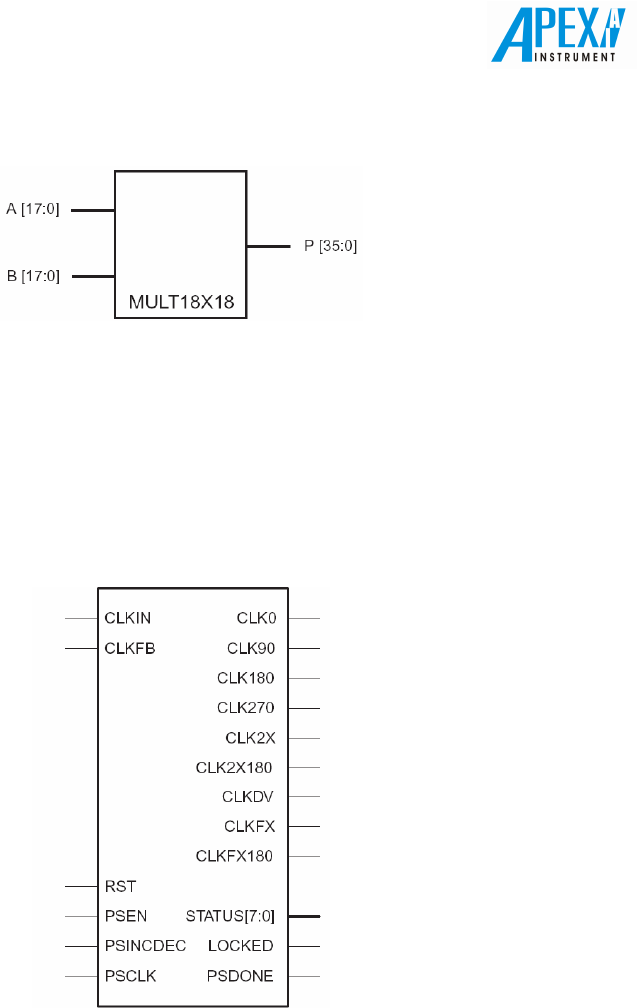

2.) 18x18 Hardware multiplier

18x18 hardware multiplier 18x18 4 12

4 18x18 hardware multiplier

3.) Digital Clock Manager

Digital Clock Manager (DCM)

4 DCM

Variable Clock DCM 5

5 DCM

DCM

• ( Clock Divider ) 1.5, 2,

2.5, 3, 3.5, 4, 4.5, 5, 5.5, 6, 6.5, 7, 7.5, 8, 9, 10, 11,12, 13, 14, 15, 16

• (Clock Doubler ) 2

• Digital Frequency Synthesizer ( DFS )

M/D M = 2 32 D = 1 32 Fin = 25 MHz Fout= 200 MHz

M=8 , D=1 DFS

10 11

• Delay-Locked Loop (DLL)

• Quadrant Phase Shift 90 , 180 270

• Fine Phase Shift 1/ 256

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

5

4.) Digitally Controlled Impedance (DCI)

Digitally Controlled Impedance (DCI) PCB

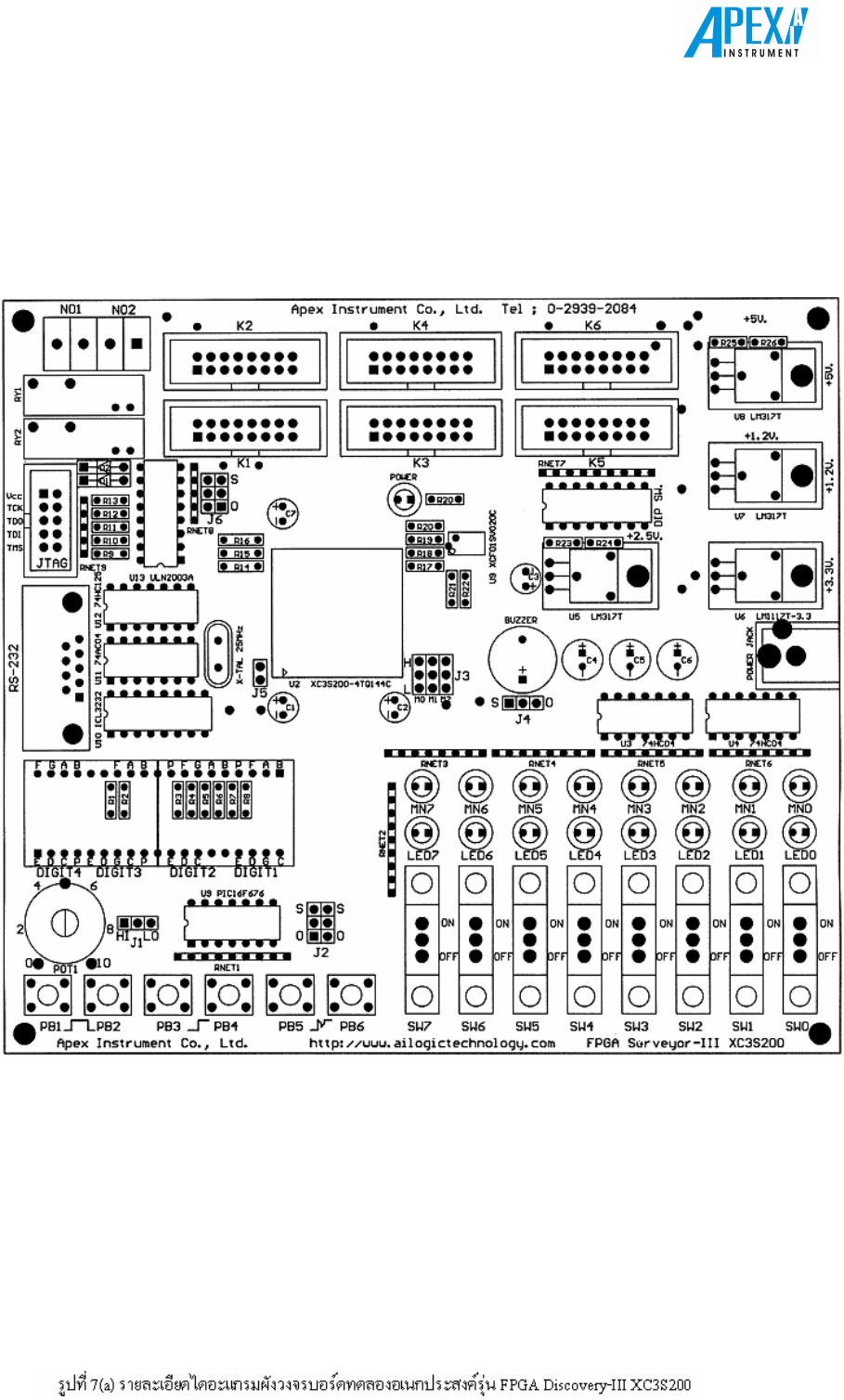

FPGA Survayer-III XC3S200 6

6 FPGA Survayer-III XC3S200

1.

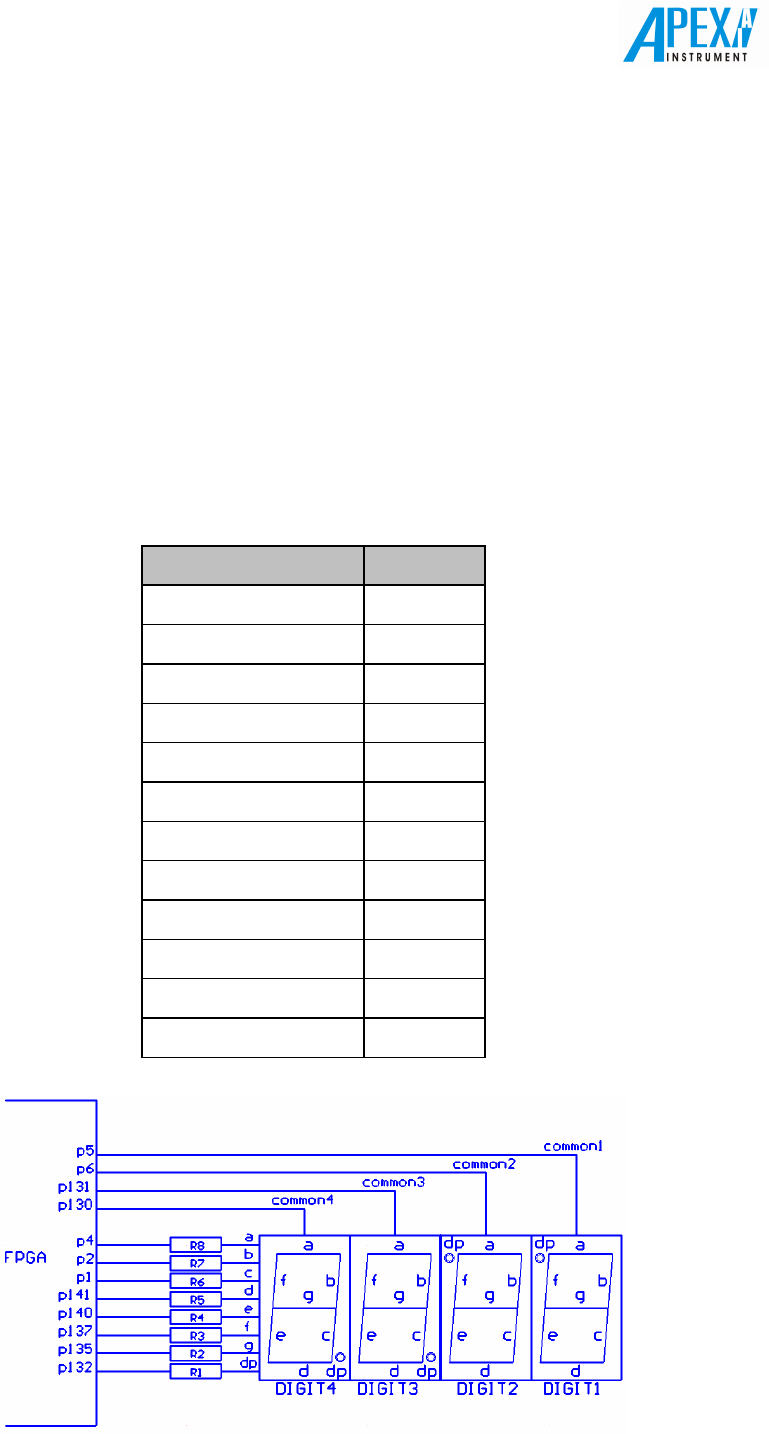

1.1) 7-Segment (DIGIT 1 DIGIT4)

(7-Segment ) 4 DIGIT1 DIGIT4 (Scan)

4 O/P FPGA 8 Data

4 (Common Cathode) 1

4

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

6

25 30 120

( 30 X 4 = 120 )

1

R1-R8 100 I/O FPGA

0

DIGIT2 DIGIT1 180

(.) DIGIT2 DIGIT1 : (Colon)

11:39 20o C

FPGA 1 7

1 FPGA

7-Segment FPGA Pin

a p4

b p2

c p1

d p141

e p140

f p137

g p135

dp () p132

DIGIT1 (Common1) p5

DIGIT2 (Common2) p6

DIGIT3 (Common3) p131

DIGIT4 (Common4) p130

7 7-Segment

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

7

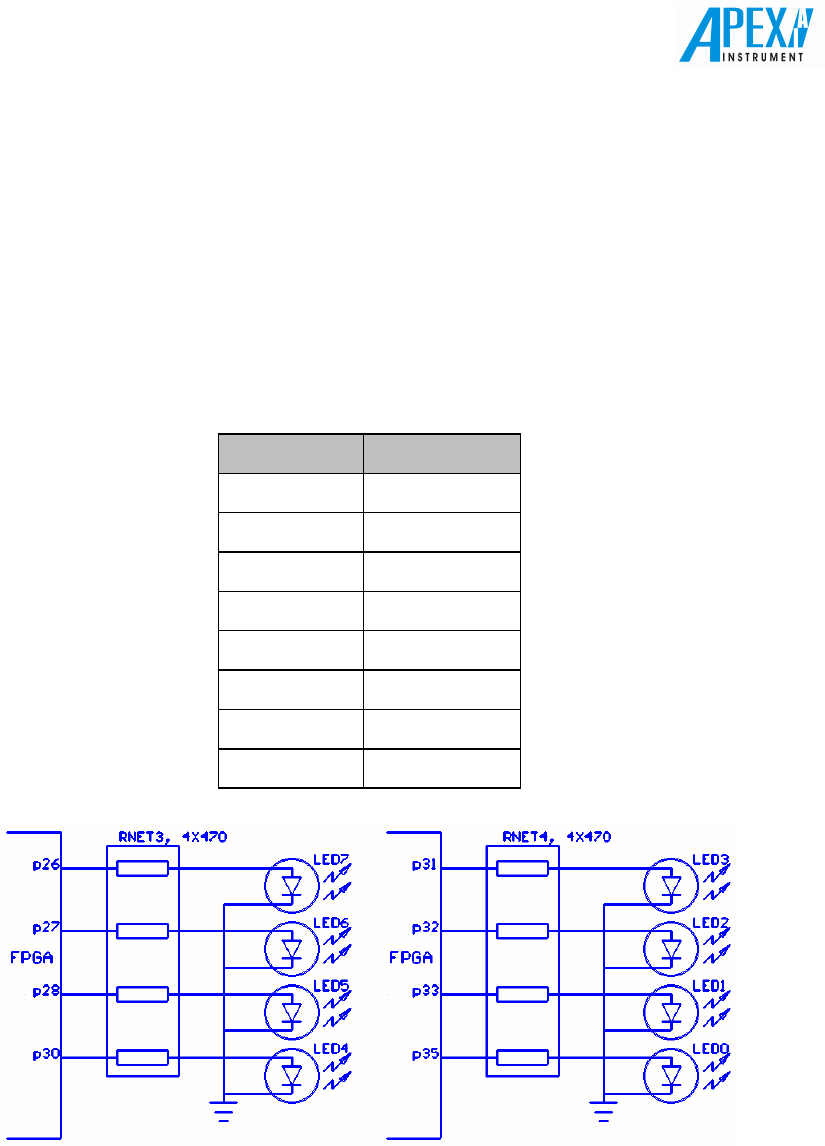

1.2 LED

1.) LED monitor ZLED0-LED7)

LED 8 LED1 LED8 (Cathode)

(I/O) FPGA ( R=470 4 ) RNET3

RNET4 High 1 LED

Low 0 LED LED Duty

Cycle LED (I/O) FPGA 2 8

2 LED (I/O) FPGA

LED FPGA Pin

LED0 P35

LED1 P33

LED2 P32

LED3 P31

LED4 P30

LED5 P28

LED6 P27

LED7 P26

8 LED monitor

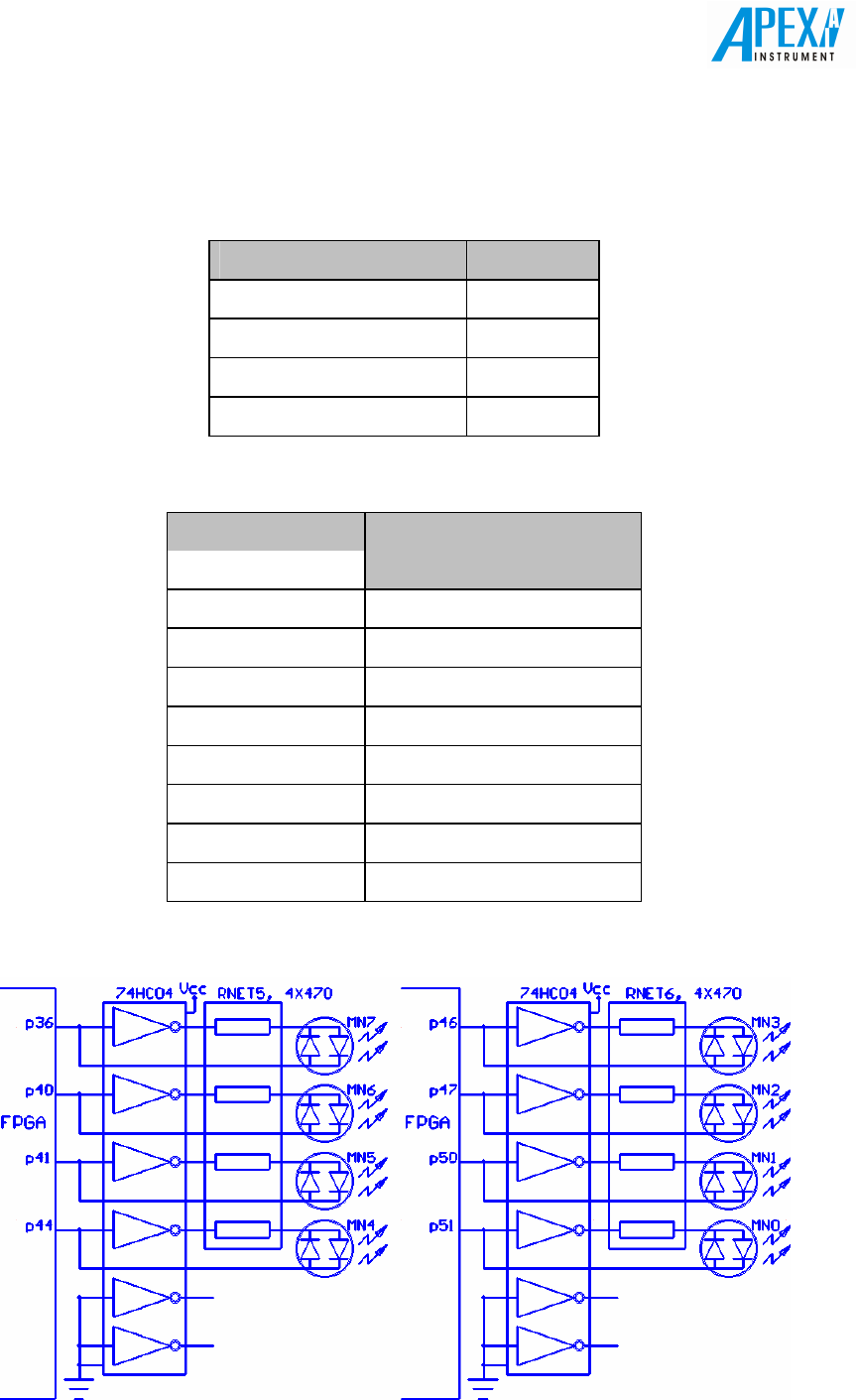

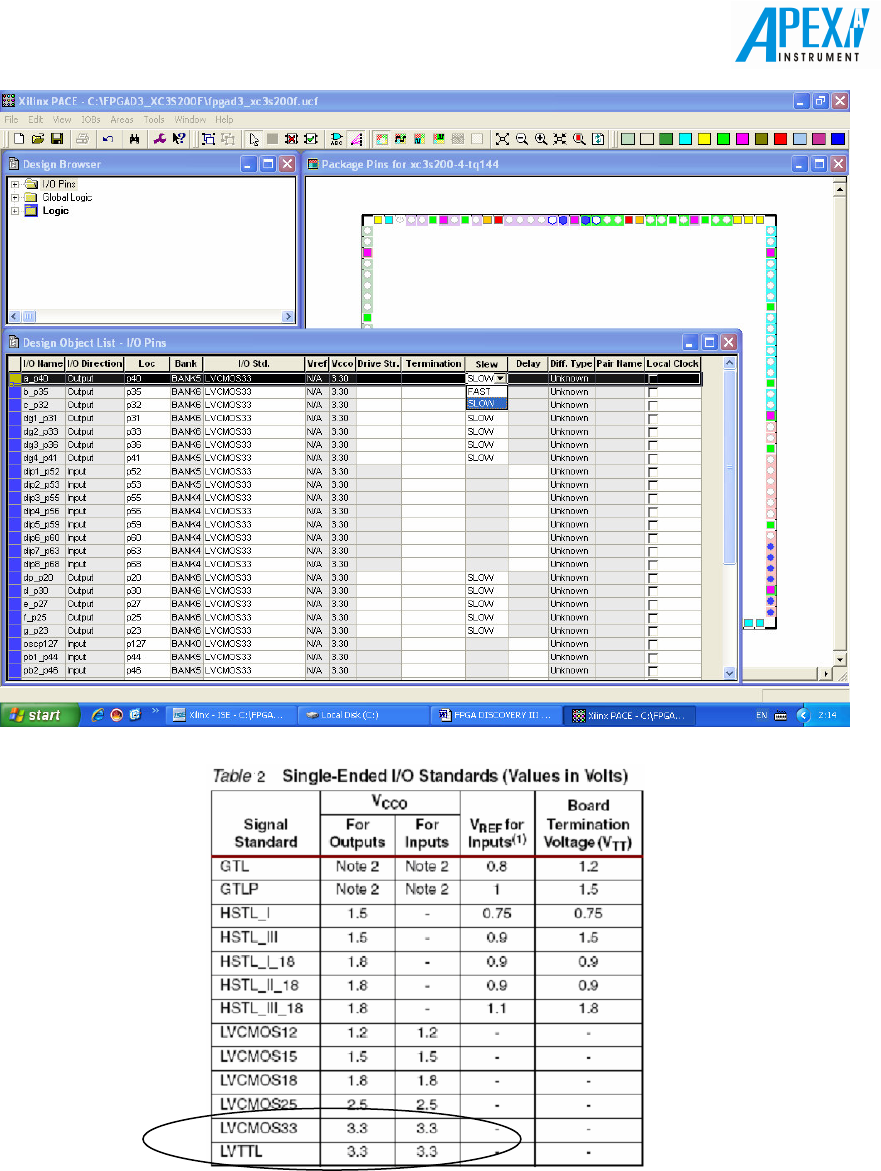

2.) Logic monitor ( MN0 MN7 )

LED High 1, Low 0 High impedance Z

LED MN0 MN0 Pin 1 MN0 Pin 2

MN0 Pin 1 1 MN0 Pin 2 0 MN0

Logic Monitor

High 1 Low 0

High impedance Z

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

8

FPGA 4

Logic monitor 9

3 LED

Logic Color

High 1 Red

Low 0 Green

High impedance Z Off

Pulse Orange

4 LED (I/O) FPGA

Bi-color LED

FPGA pin

MN0 P51

MN1 P50

MN2 P47

MN3 P46

MN4 P44

MN5 P41

MN6 P40

MN7 P36

9 Logic monitor

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

9

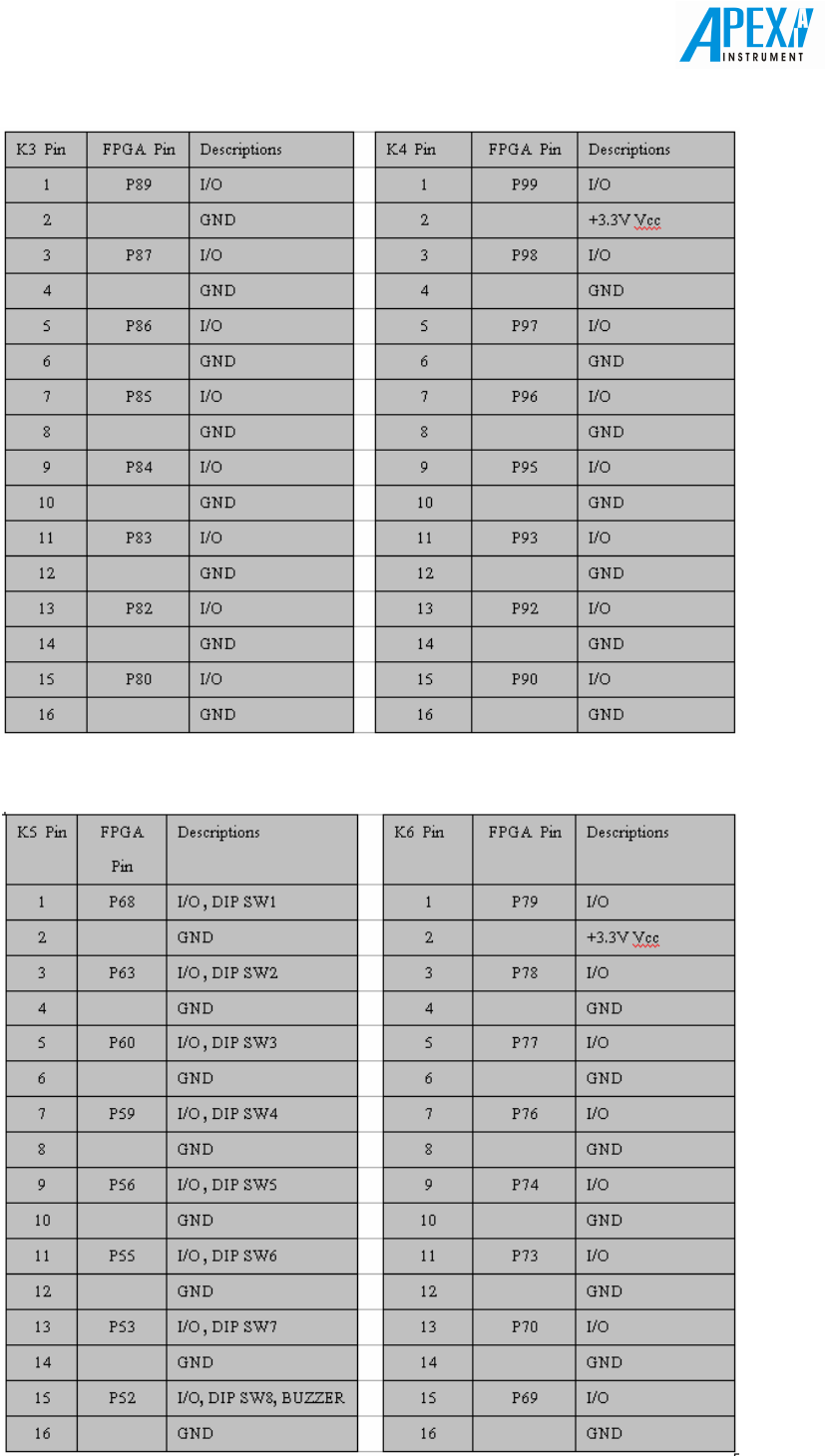

1.4 K1- K6

K1-K6

1 K1- K6

( Cross talk )

I/O 3.3 I/O

3.3 5 I/O 3.3

5 3.3 74HCxx

74ACxx 2 6 74HC125

3.3 5

220 10 mA

5 TTL 100 1

CMOS

TTL CMOS FPGA 10 Input 5

CPLD XC9500XL XC9572XL I/O CPLD 3.3

5 I/O

10 TTL CMOS FPGA

(Pulled up) Jumper J5

J5 I/O K1 K6

PCB

(Flat Cable) 40 10 15

(

) I/O FPGA Slow Slew Rate

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

10

Transmission Line effect PCB ()

PCB (2/nS) x (Rise time) O/P FPGA Fast

slew rate 1 nS Slow slew rate 3 nS

(2/nS) x 3 nS = 6 = 15

Terminate Spartan-3

Digitally Controlled Impedance (DCI)

Vcc 0.1 uF

10nF (Chip capacitor) Vcc

() Vcc AC

K1- K6 FPGA 5

5 K1- K6 FPGA

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

11

5 K1- K6 FPGA ()

5 K1- K6 FPGA ()

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

12

2.

2.1

( Dip Switch ) 8 OFF 1 (Active Low)

ON 0

6 FPGA ()

DIP SWITCH FPGA Pin

DIP1 P68

DIP 2 P63

DIP 3 P60

DIP 4 P59

DIP 5 P56

DIP 6 P55

DIP 7 P53

DIP 8 P52

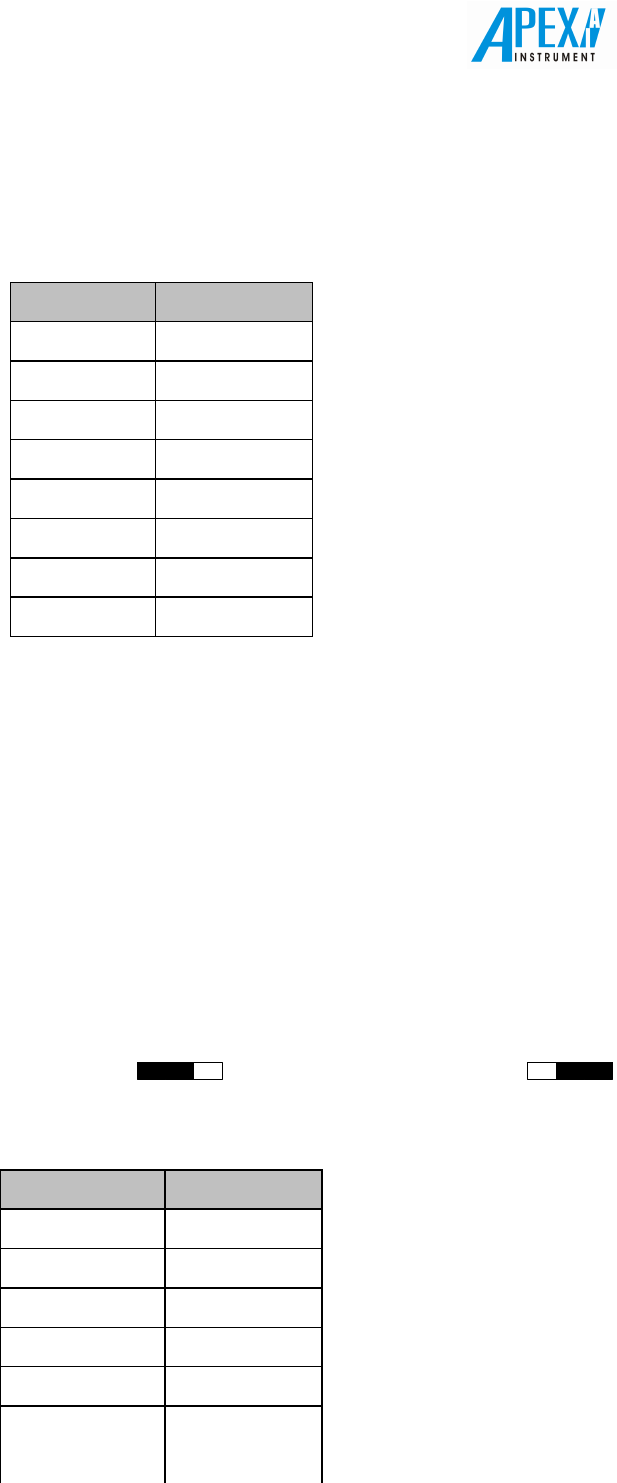

2.2 Variable clock generator

( Push botton Switch ) 6 PB1 PB6 Variable

clock generator (VRCLK) PIC16F676 11 PB1 PB2

One-shot push button switch 1

High 1

PB3 PB4 Bounce-less push button switch 1

High 1 Low 0

( Square Wave ) ( Bounce-less )

PB5PB6 Bounce push button switch PB1-PB6

FPGA 1 0 RNET1

Range selector of on board variable clock generator (J1) lock

generator 2 High Frequency ( 1 2 ) Low Frequency

( 2 3 ) POT1

7 FPGA

Pushutton CLK

FPGA Pin

PB1 OUT P8

PB2 OUT P10

PB3 OUT P11

PB4 OUT P12

PB5 P13

PB6 P14

VRCLK P7

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

13

12 Clock

2.3

(Oscillator socket) 1

74AC04 25 Mhz 330 1 15 pF 2

GCLK6 p127 FPGA

74AC04 3.3

1 Mhz 50 MHz FPGA Spartan-3 Digital Clock Manager (DCM)

4 DCM

2.4 Relay connector ( NO1, NO2 )

1 2 (RLY1, RLY2) 3A 250V 2

(NO) 1 2 P125 P124 FPGA I/O 1

3 K1 ( Jumper S) 1 2 Jumper O

2.5 JTAG connector

JTAG Cable) FPGA Flash PROM

2.6 Slide switch ( SW0 SW7 )

CPLD 1 0

FPGA Active Low R Slide switch Vcc

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

14

8 Slide switch FPGA

Slide switch FPGA Pin

SW7 P15

SW6 P17

SW5 P18

SW4 P20

SW3 P21

SW2 P23

SW1 P24

SW0 P25

3 RS-232C

RS-232C ICL3232 MAX3232 13 p128 p129 14

13 RS-232C

14 RS-232C FPGA

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

15

4. Misc

4.1 DC Adaptor input jack 7V 9V

+ -

4.2 Power switch

4.3 Power LED

4.4 JUMPER J2 Jumper PB5 PB6 FPGA ( S)

CMOS TTL 1

( R=4.7-10k) 0 1

CMOS Vcc Ground

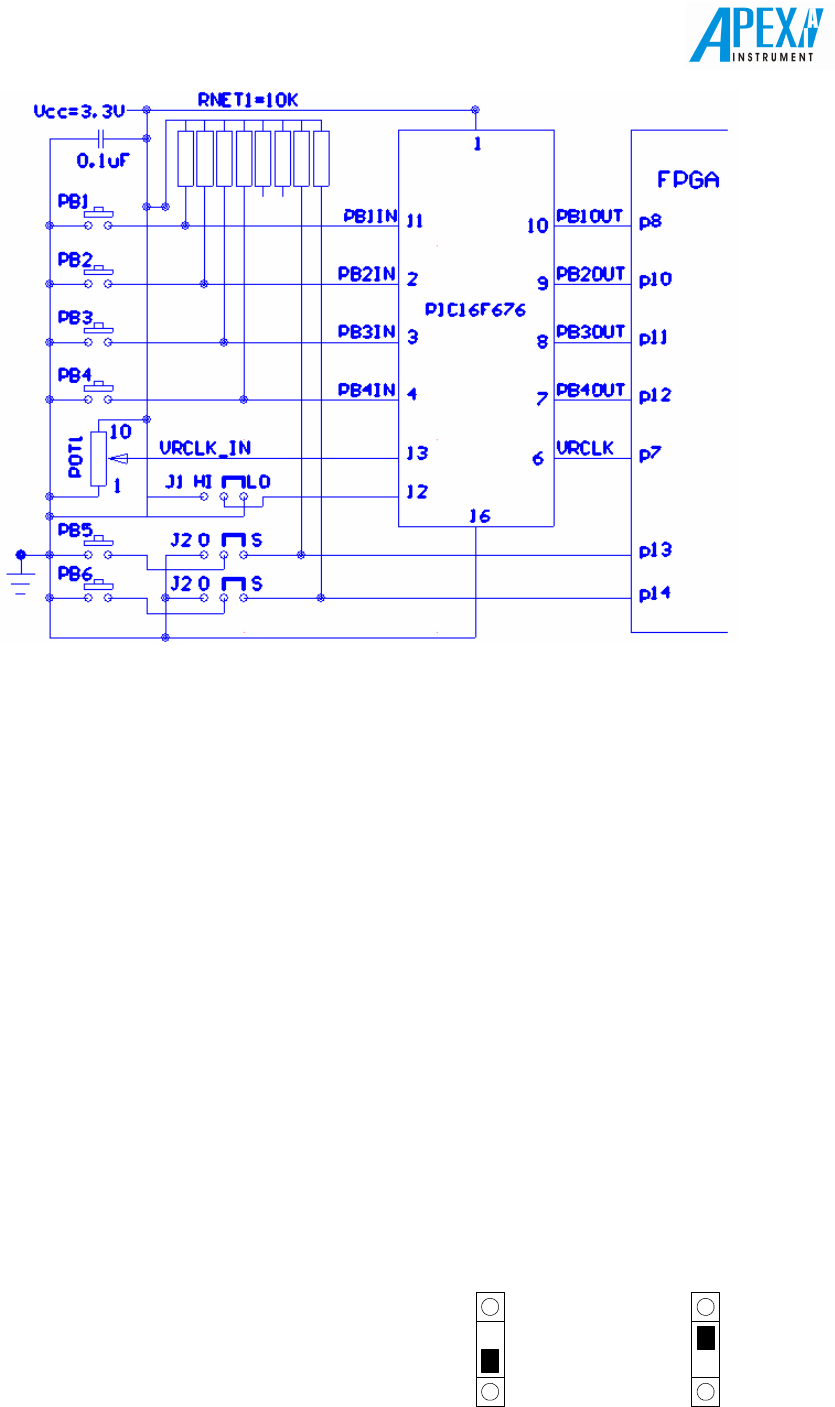

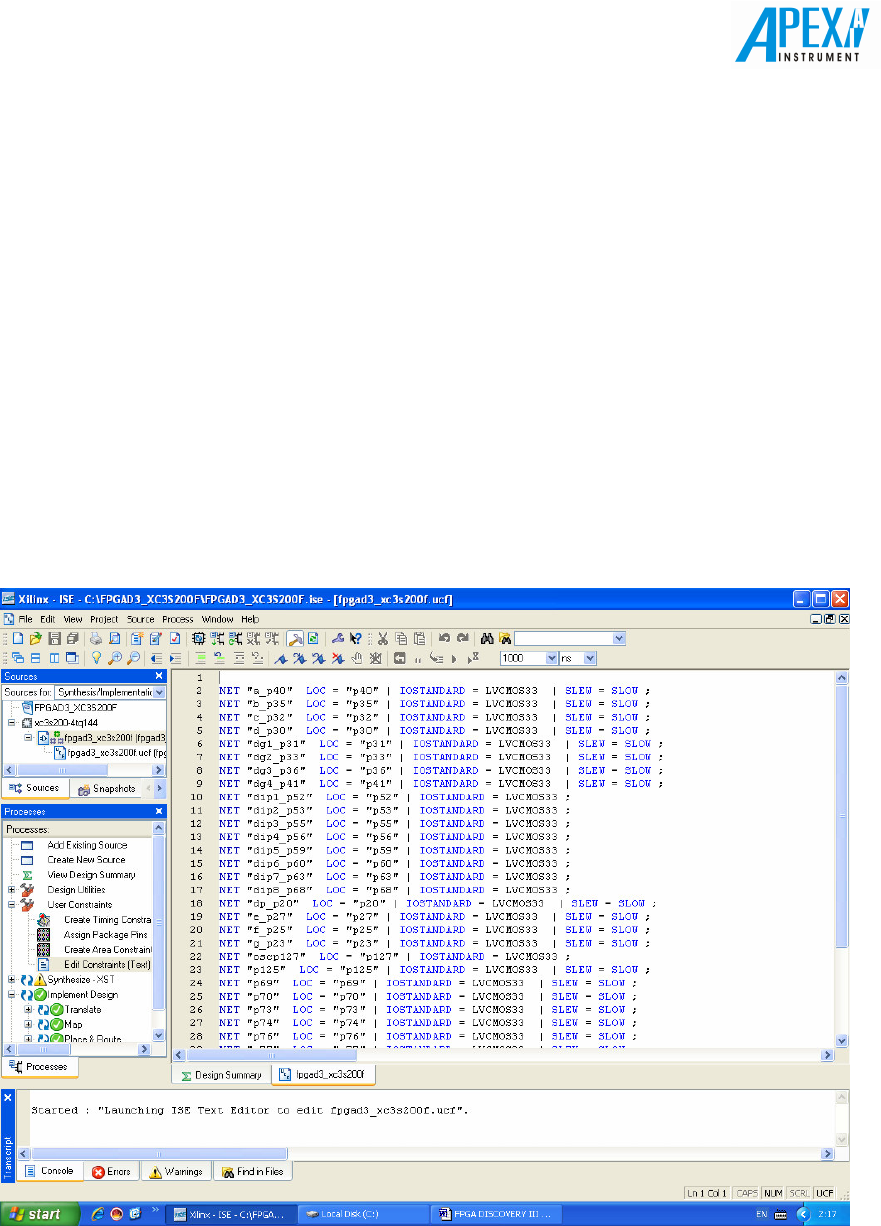

4.5 FPGA

Vcco 3.3V I/O 3.3V I/O 2

LVCMOS33 LVTTL 2 FPGA LVTTL (IOSTANDARD = LVTTL)

Slow slew Rate (SLEW = SLOW) Edit Constraints(Text)15 PACE 16

15 FPGA LVCMOS Slow slew Rate Edit Constraints(Text)

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

16

16 FPGA LVCMOS Slow slew Rate PACE

4.6 JTAG J1

JTAG (JTAG Cable) (Printer Port)

(Configuration data) FPGA Serial Flash PROM FPGA

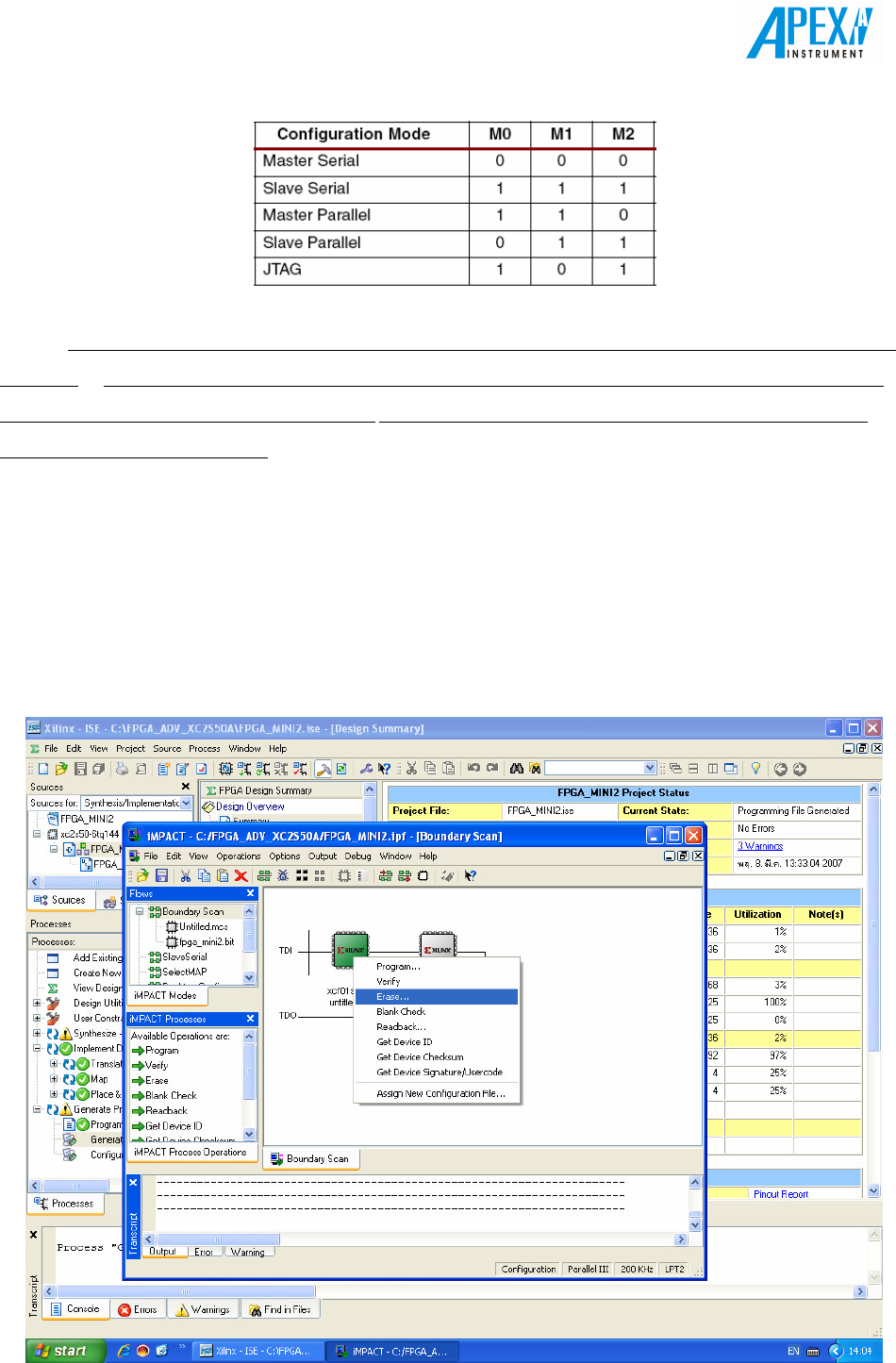

JTAG Mode (Boundary Scan Mode) Master Serial Mode Serial Flash

PROM FPGA Master Serial Mode Jumper J1 M0,

M1, M2 = 000 3 Xilinx (

) M0, M1 M2 JTAG

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

17

3 FPGA

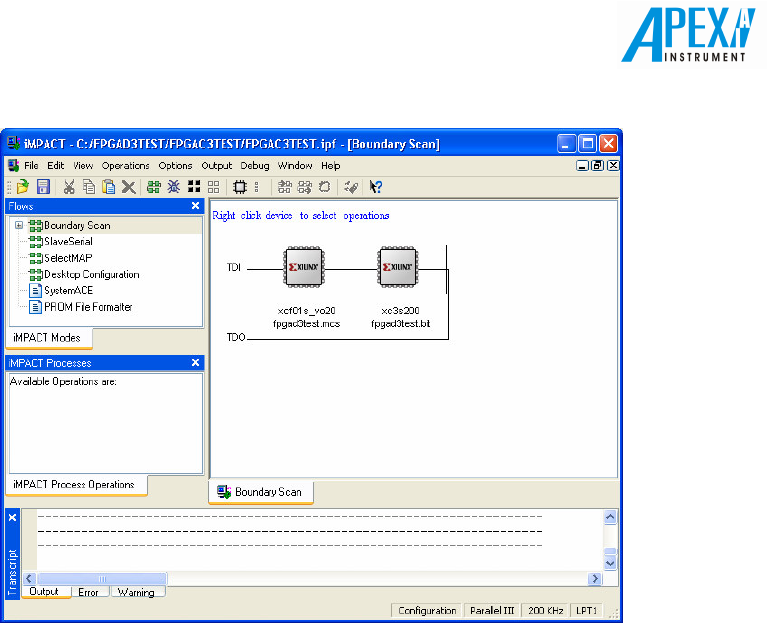

FPGA JTAG Flash PROM

17 Flash PROM FPGA (

) FPGA Master Serial Mode Flash PROM

FPGA Platform Flash PROM FPGA

JTAG Flash PROM FPGA

2 18

JTAG

Platform Flash PROM FPGA Master serial (M0 , M1 , M2 = 0)

FPGA Platform Flash PROM FPGA

17 Flash PROM FPGA JTAG

FPGA Surveyor-III XC3S200 Board Manual (Rev2.07/03/07)

18

18 Flash PROM FPGA