Configuration Guide For Display Drivers (ACPI And XML) 80 NB116 2 ACPI ON WINDOWS

User Manual: Pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 110 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- Configuration Guide for Display Drivers (ACPI and XML)

- Revision history

- Contents

- Figures

- Tables

- 1 Introduction

- 2 ACPI configuration for display drivers

- 3 Panel configuration format

- 4 Supported tag list

- 5 Panel configuration tag descriptions

- 6 Display hardware tag descriptions

- 7 Display features

- 8 Display interface-specific configurations

- 8.1 DSI interface configurations

- 8.1.1 Common DSI configurations

- 8.1.2 Display stream compression (DSC)

- 8.1.3 Init sequence timing

- 8.1.4 DSI DCS command configurations

- 8.1.5 Supported DCS commands

- 8.1.6 Special DCS commands

- 8.1.7 DSI interface timing overrides

- 8.1.8 DSI Video mode configuration

- 8.1.9 DSI Command mode configuration

- 8.1.10 DSI Command mode TE synchronization

- 8.1.11 Tear check threshold parameters

- 8.1.12 Dual DSI configuration

- 8.2 DSI Command mode configuration

- 8.3 eDP configuration

- 8.4 HDMI configuration

- 8.1 DSI interface configurations

- 9 Backlight configuration

- 10 ESD detection and recovery configuration

- 11 AD core configuration (preliminary)

- 12 Platform-specific GPIO configuration

- 13 Power-saving configuration

- 14 Sharpening configuration

- 15 Display-specific ACPI methods

- 15.1 _ROM method

- 15.2 ROM multipanel support

- 15.3 BLCP method

- 15.4 Panel calibration commands (PIGC, PPCC, PPGC, PGRT, PBRT, HSIC, PGMT)

- 15.4.1 Panel Inverse Gamma Correction (PIGC)

- 15.4.2 Panel Color Correction (PPCC)

- 15.4.3 Panel Gamma Correction (PGCT)

- 15.4.4 Panel Gamma Response Table (PGRT)

- 15.4.5 HSIC panel HSIC configuration table

- 15.4.6 Panel Gamut Mapping Table (PGMT)

- 15.4.7 Panel Backlight Response Table (PBRT)

- 15.4.8 Panel Linear Gamma Correction (PLGC)

- 15.4.9 Panel Wide Gamut Mapping Table (PWGM)

- 15.4.10 Panel Dithering Table (DITH)

- 16 Registry key entries

- 17 OLED power

- A Specifying the I2C connection in graphics.asl

- B Sample ACPI configuration for DCSbased backlight control

- C References

Qualcomm Technologies, Inc.

Confidential and Proprietary – Qualcomm Technologies, Inc.

NO PUBLIC DISCLOSURE PERMITTED: Please report postings of this document on public servers or websites to:

DocCtrlAgent@qualcomm.com.

Restricted Distribution: Not to be distributed to anyone who is not an employee of either Qualcomm Technologies, Inc. or its

affiliated companies without the express approval of Qualcomm Configuration Management.

Not to be used, copied, reproduced, or modified in whole or in part, nor its contents revealed in any manner to others without the

express written permission of Qualcomm Technologies, Inc.

Qualcomm is a trademark of Qualcomm Incorporated, registered in the United States and other countries. Other product and brand

names may be trademarks or registered trademarks of their respective owners.

This technical data may be subject to U.S. and international export, re-export, or transfer (“export”) laws. Diversion contrary to U.S.

and international law is strictly prohibited.

Qualcomm Technologies, Inc.

5775 Morehouse Drive

San Diego, CA 92121

U.S.A.

© 2013-2017 Qualcomm Technologies, Inc. All rights reserved.

Configuration Guide for Display Drivers

(ACPI and XML)

80-NB116-2 G

March 27, 2017

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 2

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

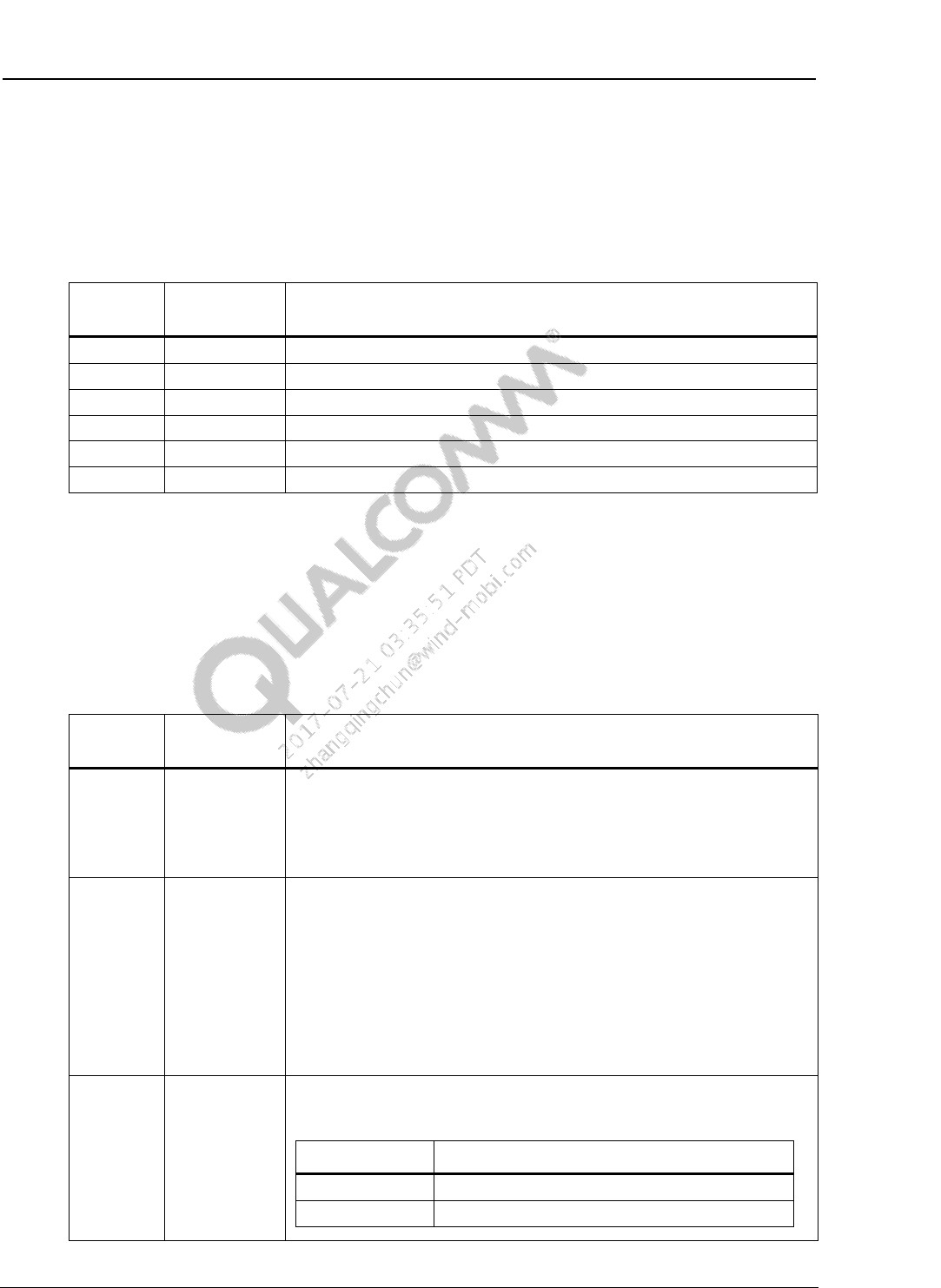

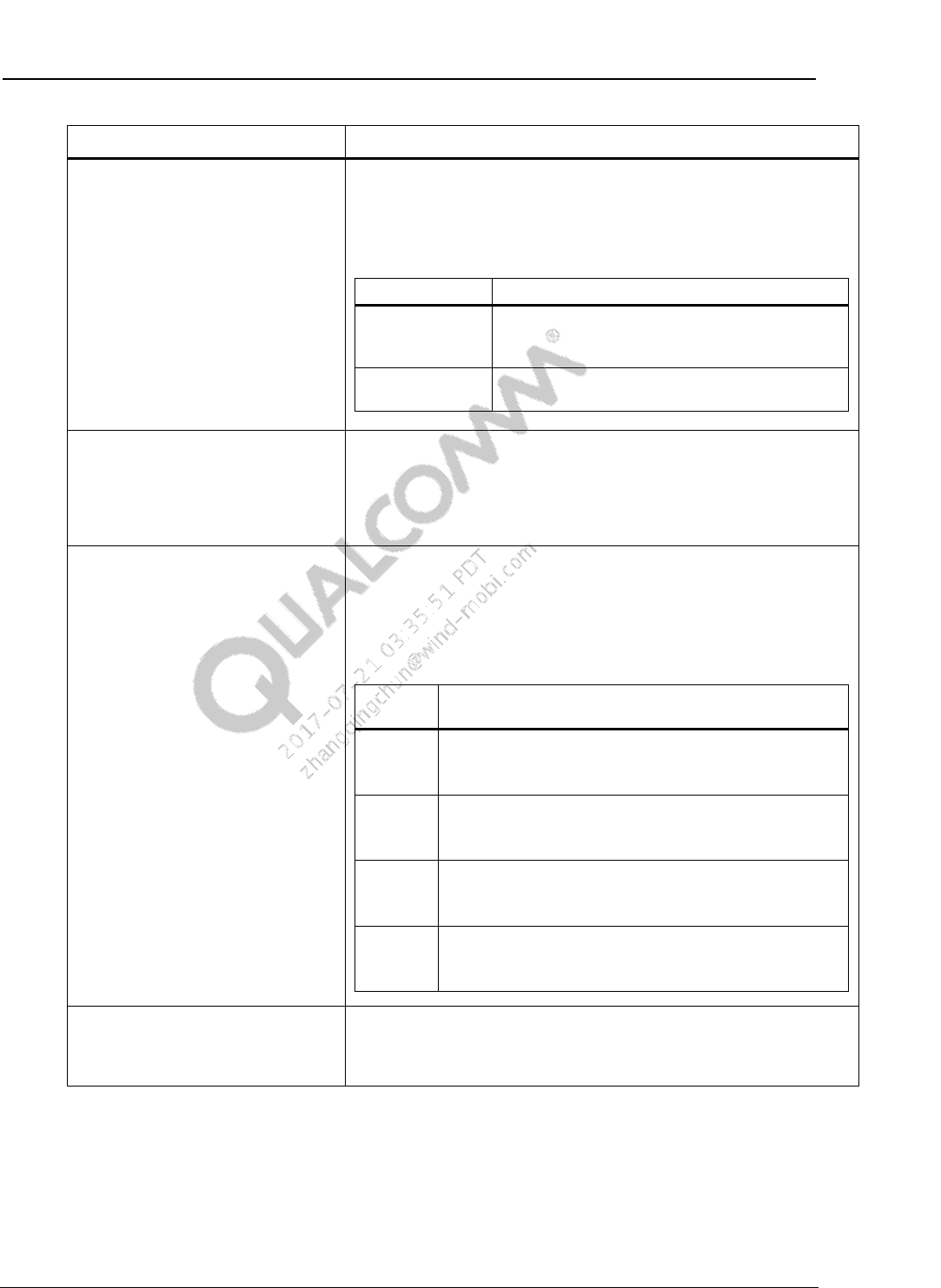

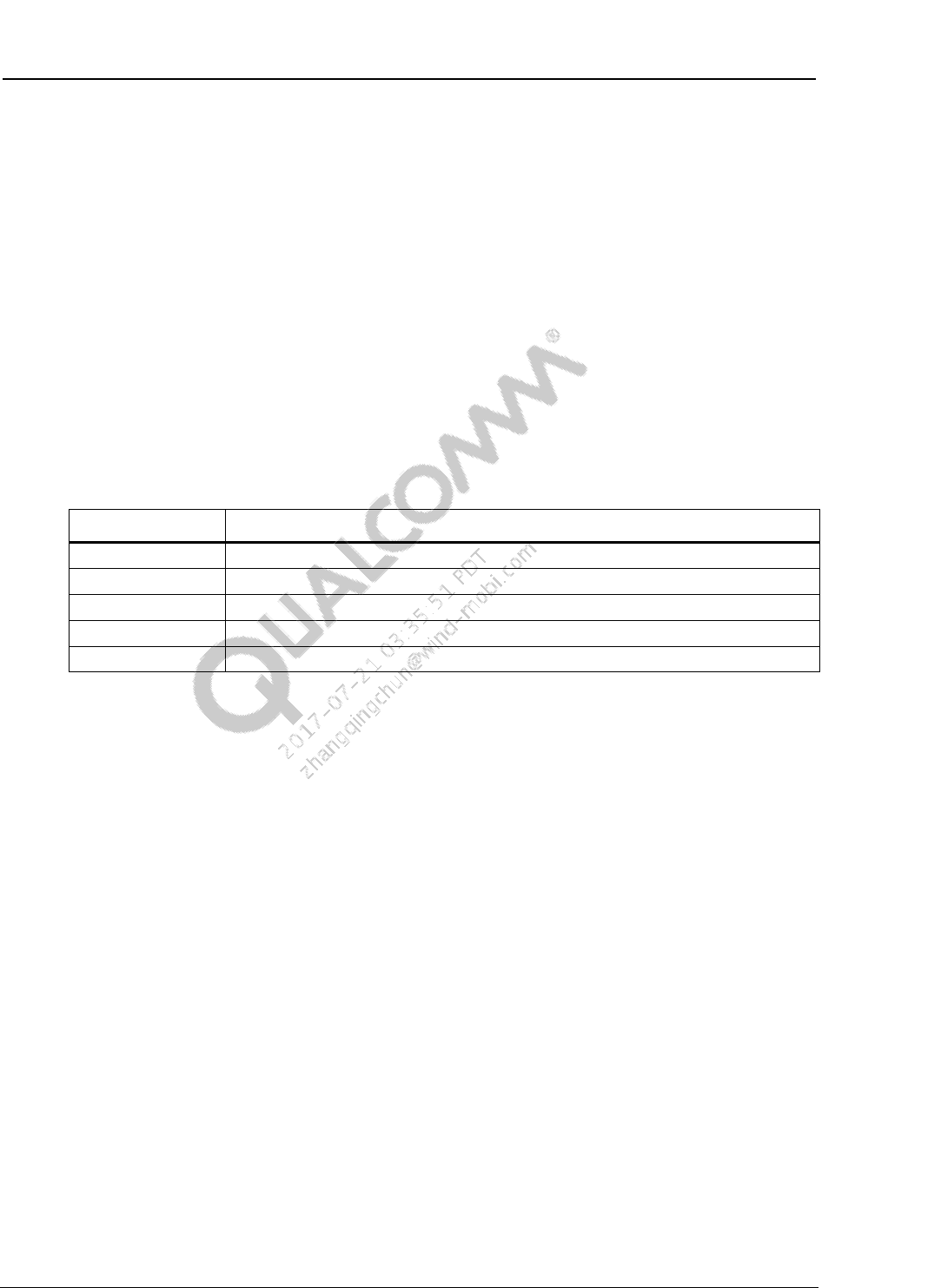

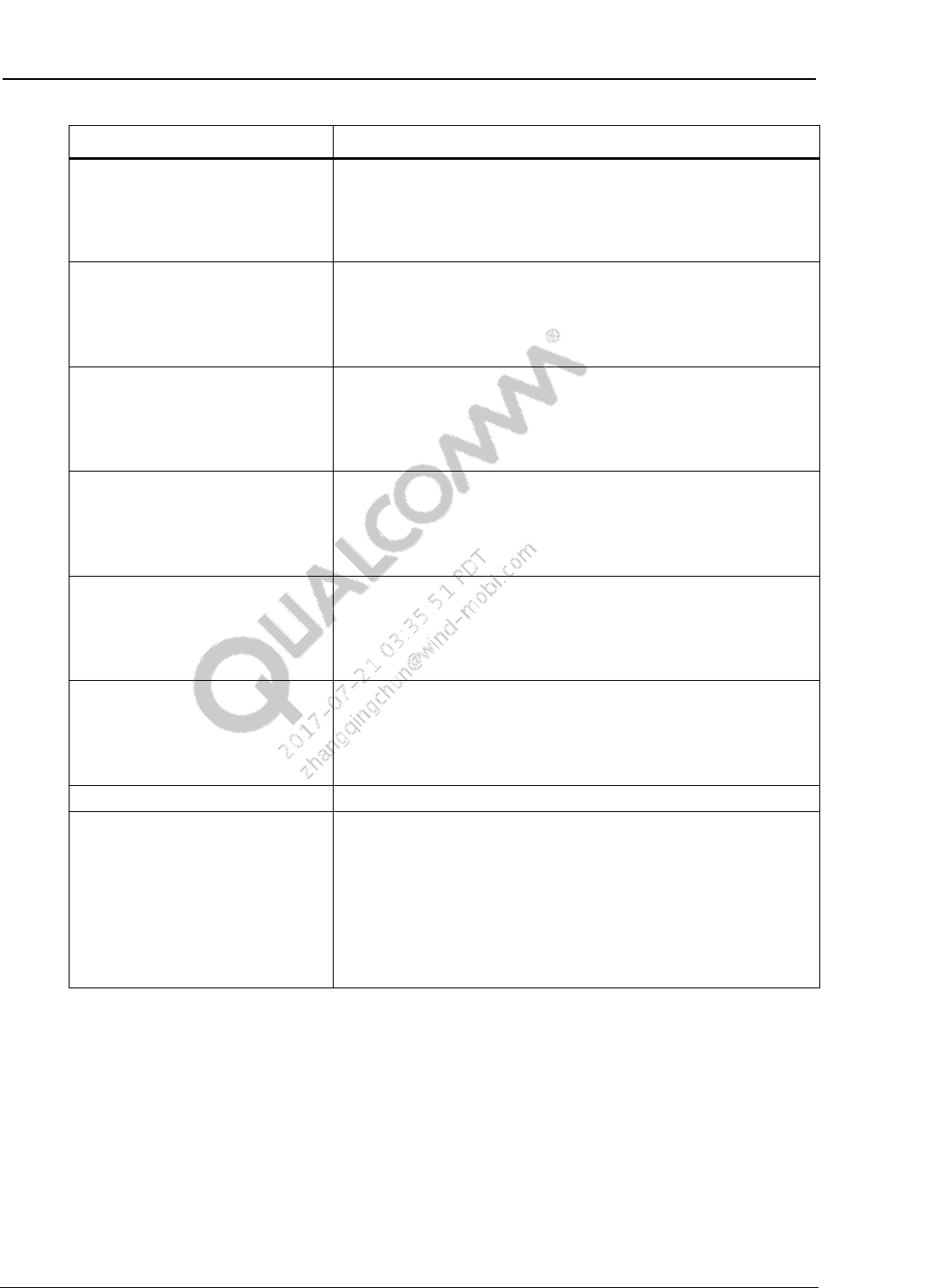

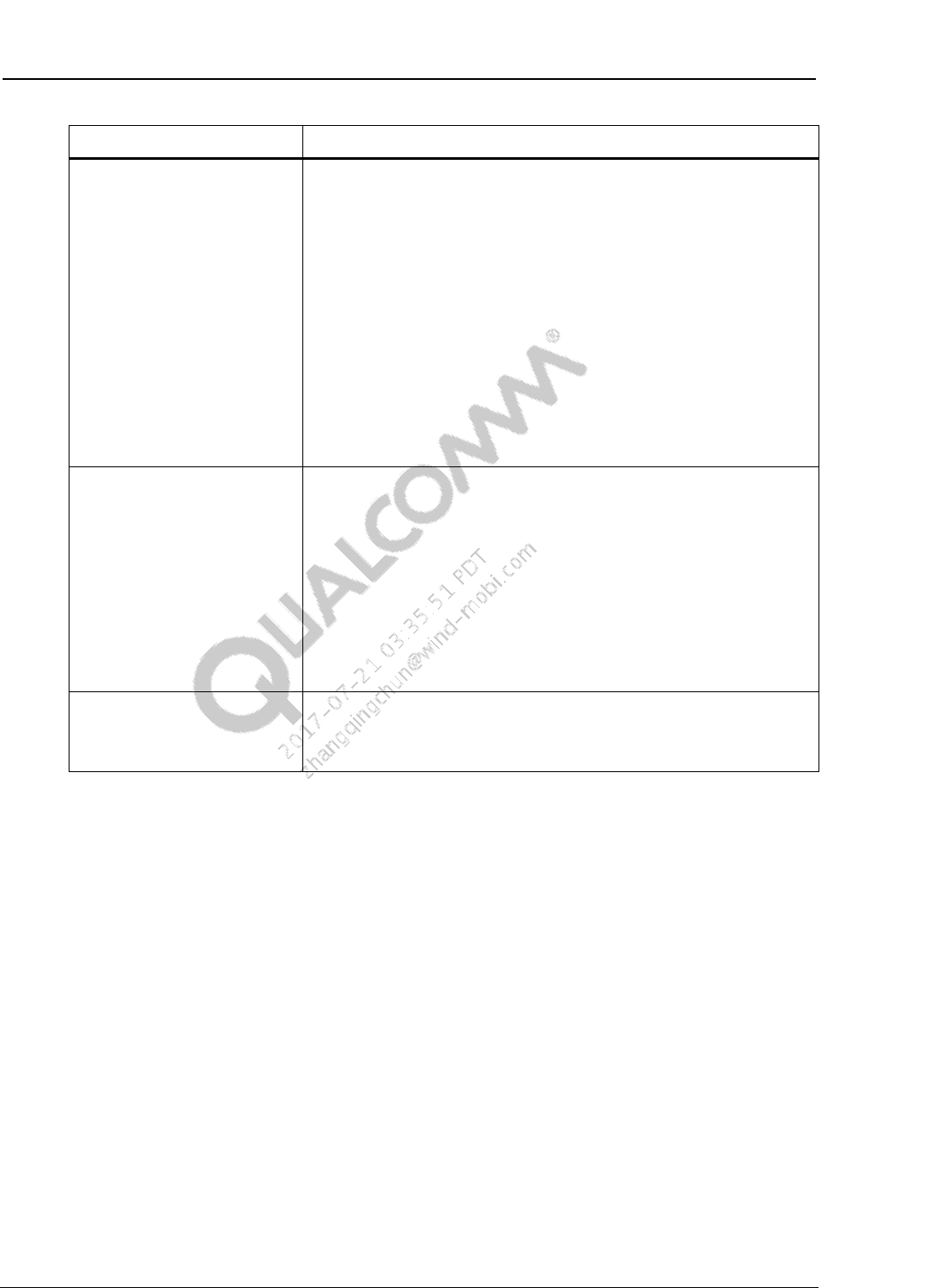

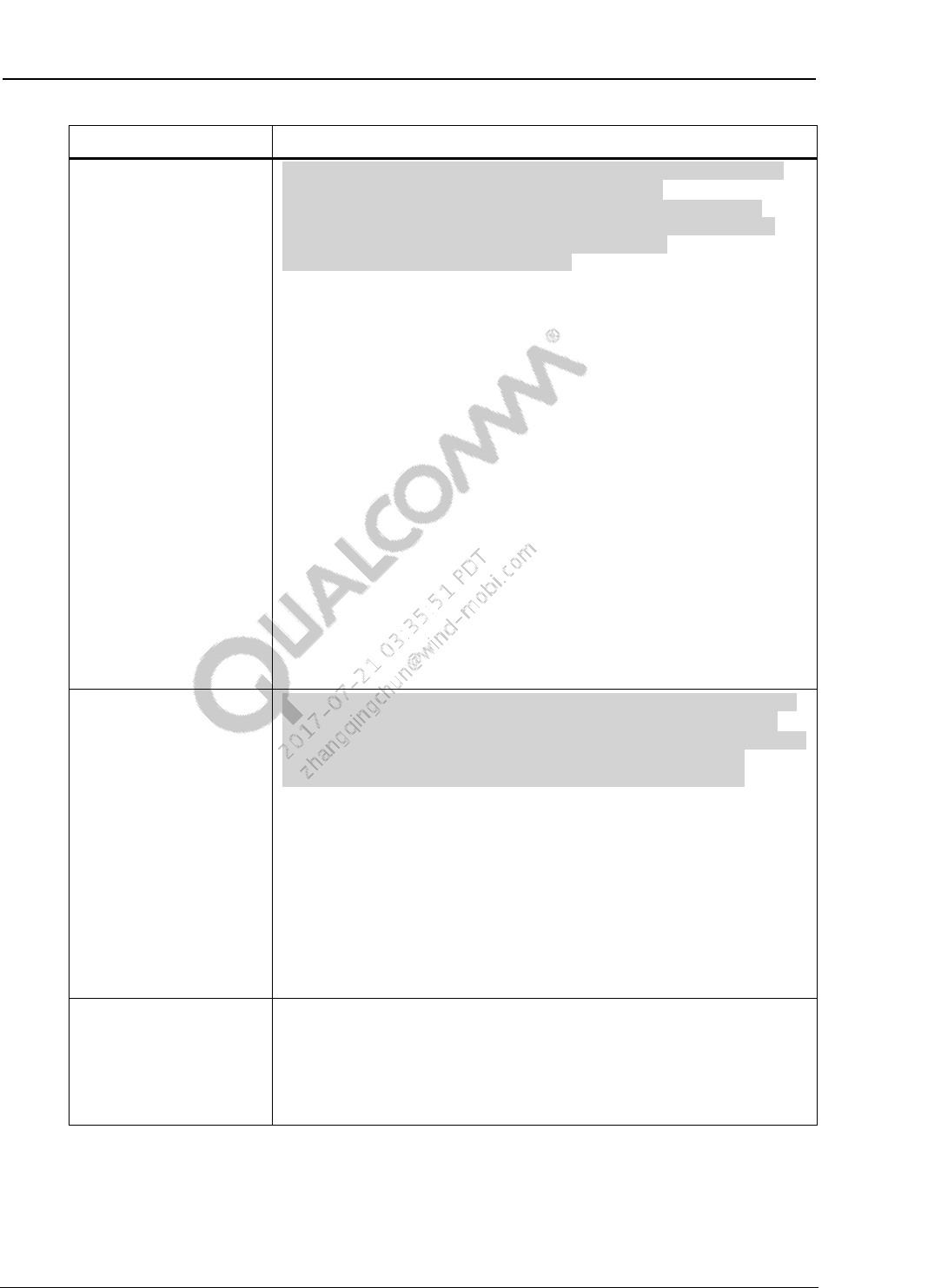

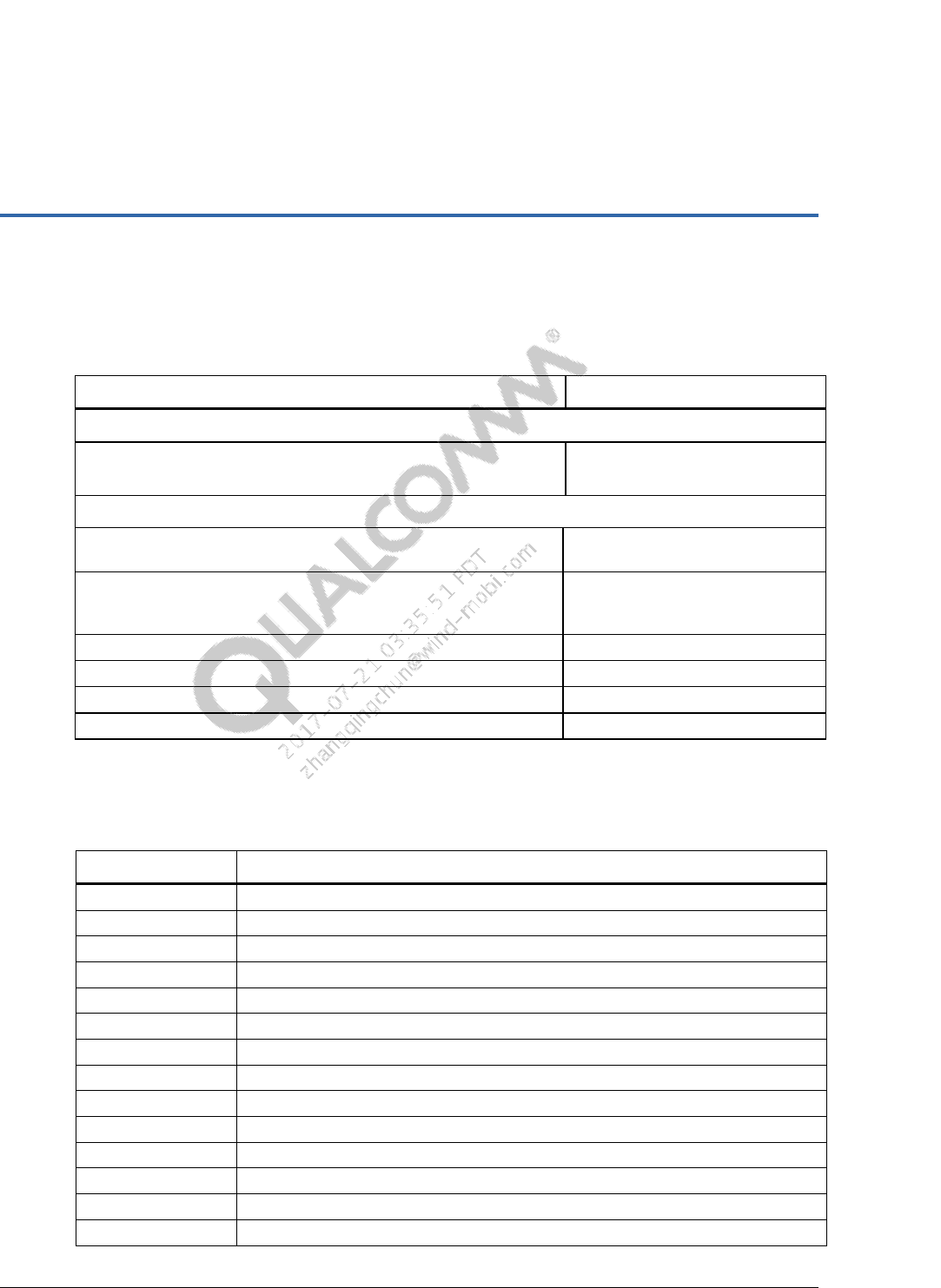

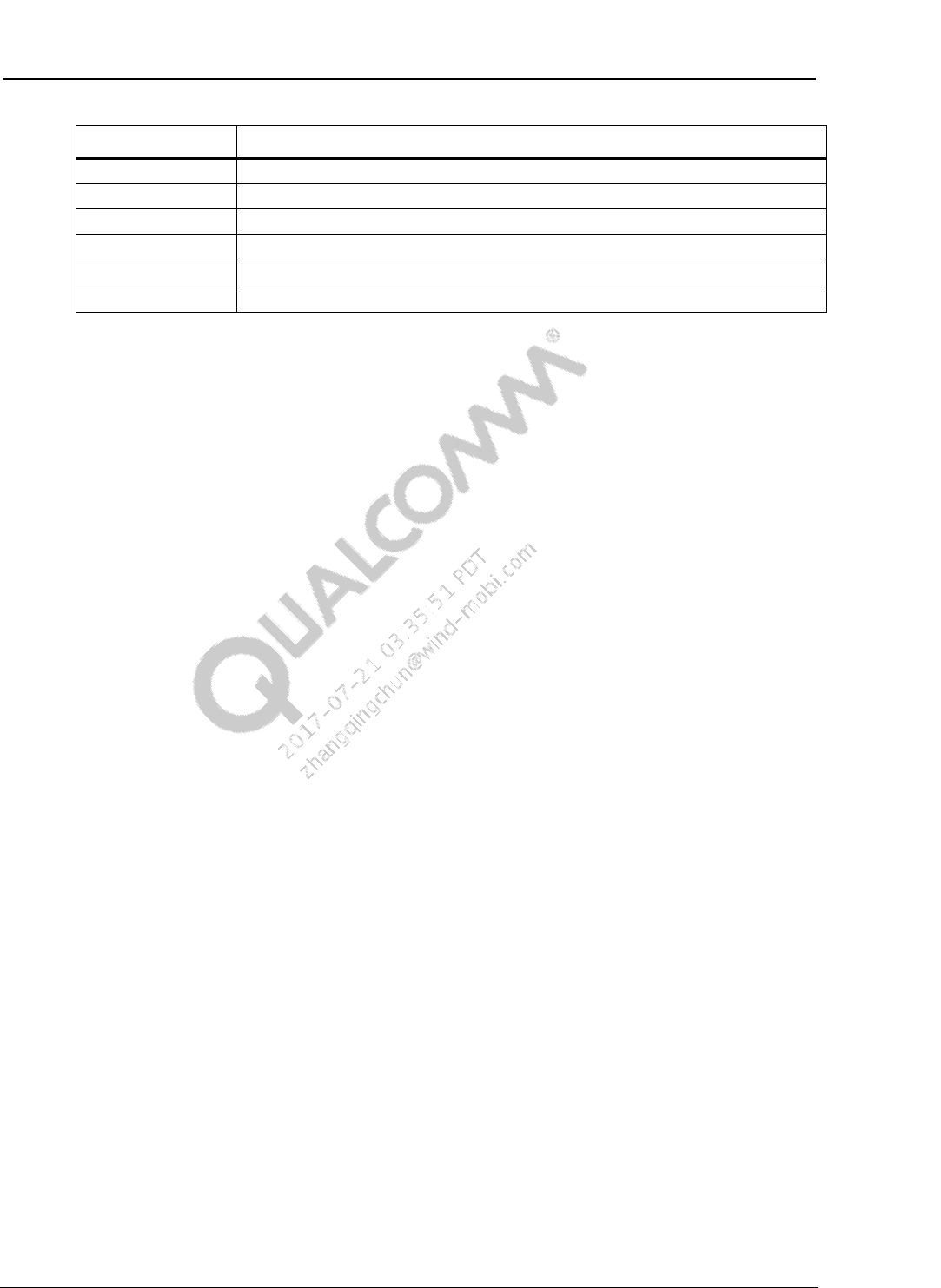

Revision history

Revision Date Description

A June 2013 Initial release

B April 2014 Updated Section 3.3 and Tables 4-1, 5-2, 5-4, 5-5, 6-1, 8-4, 8-6, 8-7, 8-8,

9-2, and 11-1; added Sections 5.2.3, 8.2, 9.3, Table 10-2, and Chapters

13 and 14

C February 2015 Updated Section 2.1 and Tables 4-1, 8-1, 8-6, and 9-2; added

Chapter 17

D March 2015 Updated Tables 4-1, 7-1, 8-6, and 8-7; added Section 8.1.11

E February 2016 Updated Tables 4-1, 7-1, 8-1, 8-9, and 17-1

F August 2016 Updated Sections 2.1, 3.3 and Tables 4-1, 7-1, and 8-1; added Table 8-2

and Section 12.1.1

G March 2017 Updated Table 4-1, 6-1, 7-1, 8-1, 8-2, and 9-4

Updated Sections 15.4.1, 15.4.2, 15.4.3, and 15.4.6

Added Sections 15.4.8, 15.4.9, and 15.4.10

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 3

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Contents

1 Introduction ...................................................................................................... 8

1.1 Purpose.......................................................................................................................... 8

1.2 Conventions .................................................................................................................. 8

1.3 Technical assistance ...................................................................................................... 8

2 ACPI configuration for display drivers .......................................................... 9

2.1 Panel configuration in the boot sequence ..................................................................... 9

3 Panel configuration format ........................................................................... 10

3.1 Tag syntax ................................................................................................................... 10

3.2 Special keyword tags .................................................................................................. 10

3.3 Supported data types ................................................................................................... 11

3.4 Limitations .................................................................................................................. 12

4 Supported tag list .......................................................................................... 13

5 Panel configuration tag descriptions .......................................................... 24

5.1 Informational fields ..................................................................................................... 24

5.2 EDID fields ................................................................................................................. 24

5.2.1 Static EDID fields ............................................................................................ 24

5.2.2 Detailed timing fields ...................................................................................... 25

5.2.3 EDID information ............................................................................................ 26

5.2.4 Dynamic EDID fields ...................................................................................... 26

5.3 Panel timings configuration ........................................................................................ 28

6 Display hardware tag descriptions .............................................................. 30

6.1 Common hardware configuration parameters ............................................................. 30

7 Display features ............................................................................................. 33

7.1 Display feature flags ................................................................................................... 33

8 Display interface-specific configurations.................................................... 35

8.1 DSI interface configurations ....................................................................................... 35

8.1.1 Common DSI configurations ........................................................................... 35

8.1.2 Display stream compression (DSC) ................................................................. 42

8.1.3 Init sequence timing ......................................................................................... 43

8.1.4 DSI DCS command configurations ................................................................. 44

8.1.5 Supported DCS commands .............................................................................. 45

8.1.6 Special DCS commands .................................................................................. 45

Configuration Guide for Display Drivers (ACPI and XML) Contents

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 4

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

8.1.7 DSI interface timing overrides ......................................................................... 46

8.1.8 DSI Video mode configuration ........................................................................ 47

8.1.9 DSI Command mode configuration ................................................................. 52

8.1.10 DSI Command mode TE synchronization ..................................................... 54

8.1.11 Tear check threshold parameters ................................................................... 55

8.1.12 Dual DSI configuration .................................................................................. 55

8.2 DSI Command mode configuration ............................................................................ 56

8.3 eDP configuration ....................................................................................................... 58

8.4 HDMI configuration ................................................................................................... 60

9 Backlight configuration................................................................................. 62

9.1 Common backlight configuration parameters ............................................................. 63

9.2 PWM (PMIC)-based backlight control ....................................................................... 64

9.3 Sample backlight configurations ................................................................................. 65

9.3.1 WLED configuration (1 WLED string) ........................................................... 65

9.3.2 LPG configuration ........................................................................................... 66

9.4 I2C-based backlight control ........................................................................................ 66

9.5 DSI DCS-based backlight control ............................................................................... 66

9.6 ACPI-based backlight control ..................................................................................... 67

9.7 CABL configuration ................................................................................................... 67

9.8 Advanced backlight configuration .............................................................................. 68

10 ESD detection and recovery configuration ............................................... 69

11 AD core configuration (preliminary) .......................................................... 70

12 Platform-specific GPIO configuration ........................................................ 71

12.1 GPIO configuration ................................................................................................... 74

13 Power-saving configuration ....................................................................... 75

14 Sharpening configuration ........................................................................... 78

15 Display-specific ACPI methods .................................................................. 79

15.1 _ROM method .......................................................................................................... 80

15.2 ROM multipanel support .......................................................................................... 80

15.3 BLCP method ........................................................................................................... 82

15.3.1 BLCP format for DSI DCS commands.......................................................... 83

15.3.2 BLCP format for I2C commands ................................................................... 83

15.4 Panel calibration commands (PIGC, PPCC, PPGC, PGRT, PBRT, HSIC, PGMT) 84

15.4.1 Panel Inverse Gamma Correction (PIGC) ..................................................... 85

15.4.2 Panel Color Correction (PPCC) ..................................................................... 86

15.4.3 Panel Gamma Correction (PGCT) ................................................................. 87

15.4.4 Panel Gamma Response Table (PGRT) ......................................................... 88

15.4.5 HSIC panel HSIC configuration table ........................................................... 90

15.4.6 Panel Gamut Mapping Table (PGMT) .......................................................... 90

15.4.7 Panel Backlight Response Table (PBRT) ...................................................... 92

15.4.8 Panel Linear Gamma Correction (PLGC) ..................................................... 94

Configuration Guide for Display Drivers (ACPI and XML) Contents

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 5

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

15.4.9 Panel Gamut Mapping Table (PWGM) ......................................................... 94

15.4.10 Panel Dithering Table (DITH) ..................................................................... 96

16 Registry key entries .................................................................................... 98

16.1 CABL ........................................................................................................................ 98

16.2 SBC ........................................................................................................................... 98

16.3 AVI Info Frame Packet ............................................................................................. 98

16.4 HDCP ........................................................................................................................ 99

17 OLED power ............................................................................................... 100

A Specifying the I2C connection in graphics.asl ......................................... 102

B Sample ACPI configuration for DCS-based backlight control ................ 103

C References ................................................................................................... 109

C.1 Related documents ................................................................................................... 109

C.2 Acronyms and terms ................................................................................................ 109

Configuration Guide for Display Drivers (ACPI and XML) Contents

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 6

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

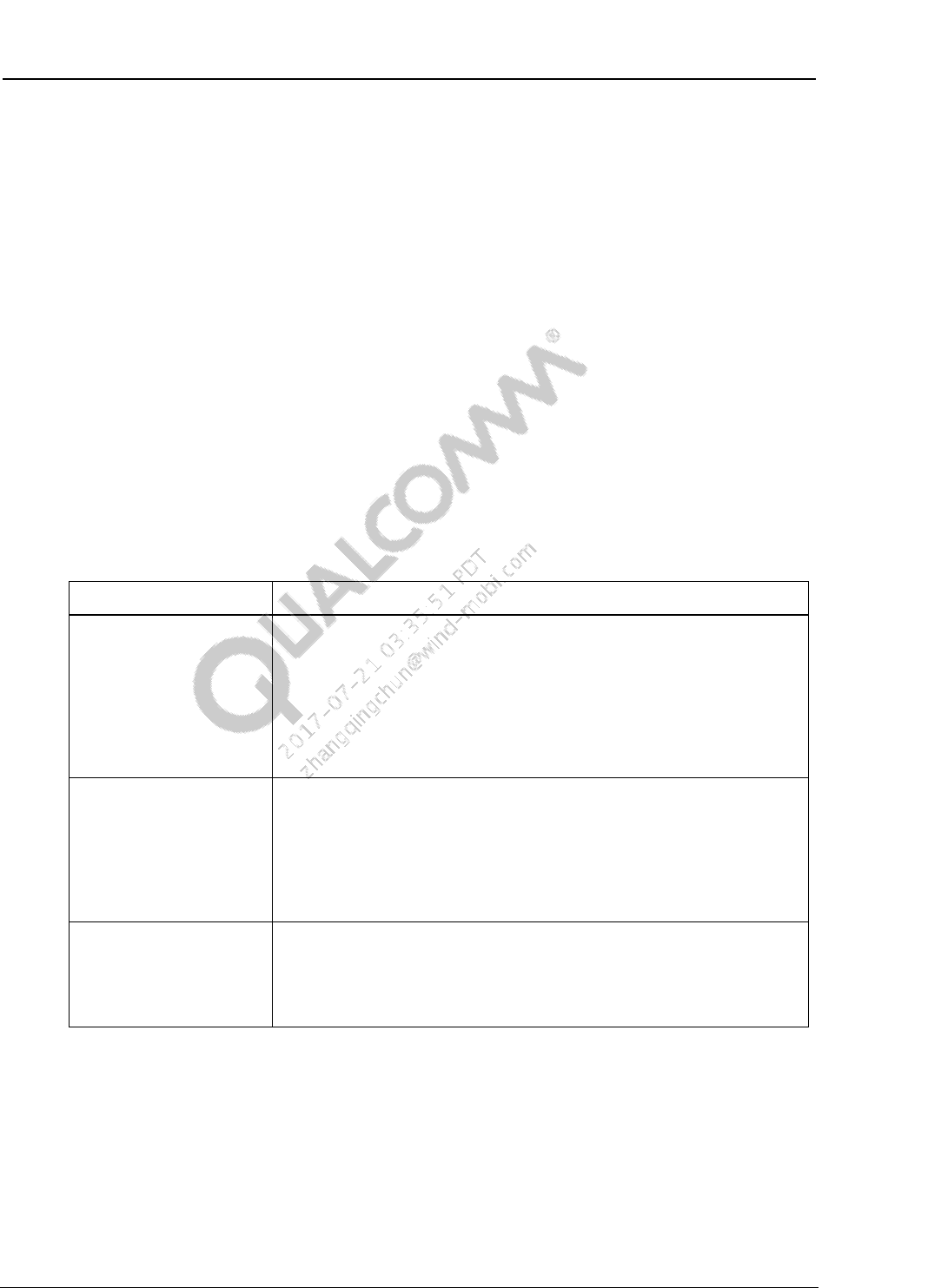

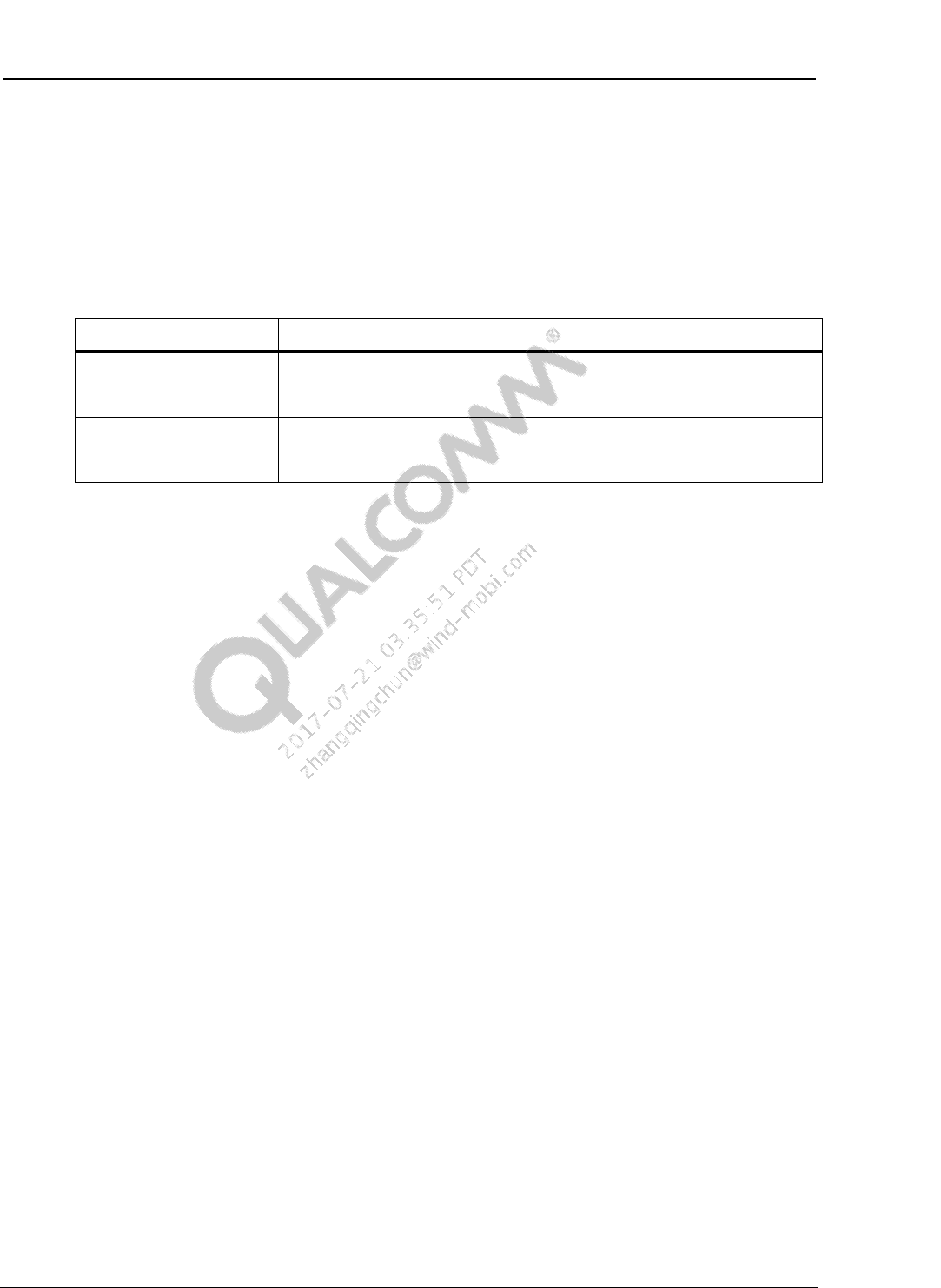

Figures

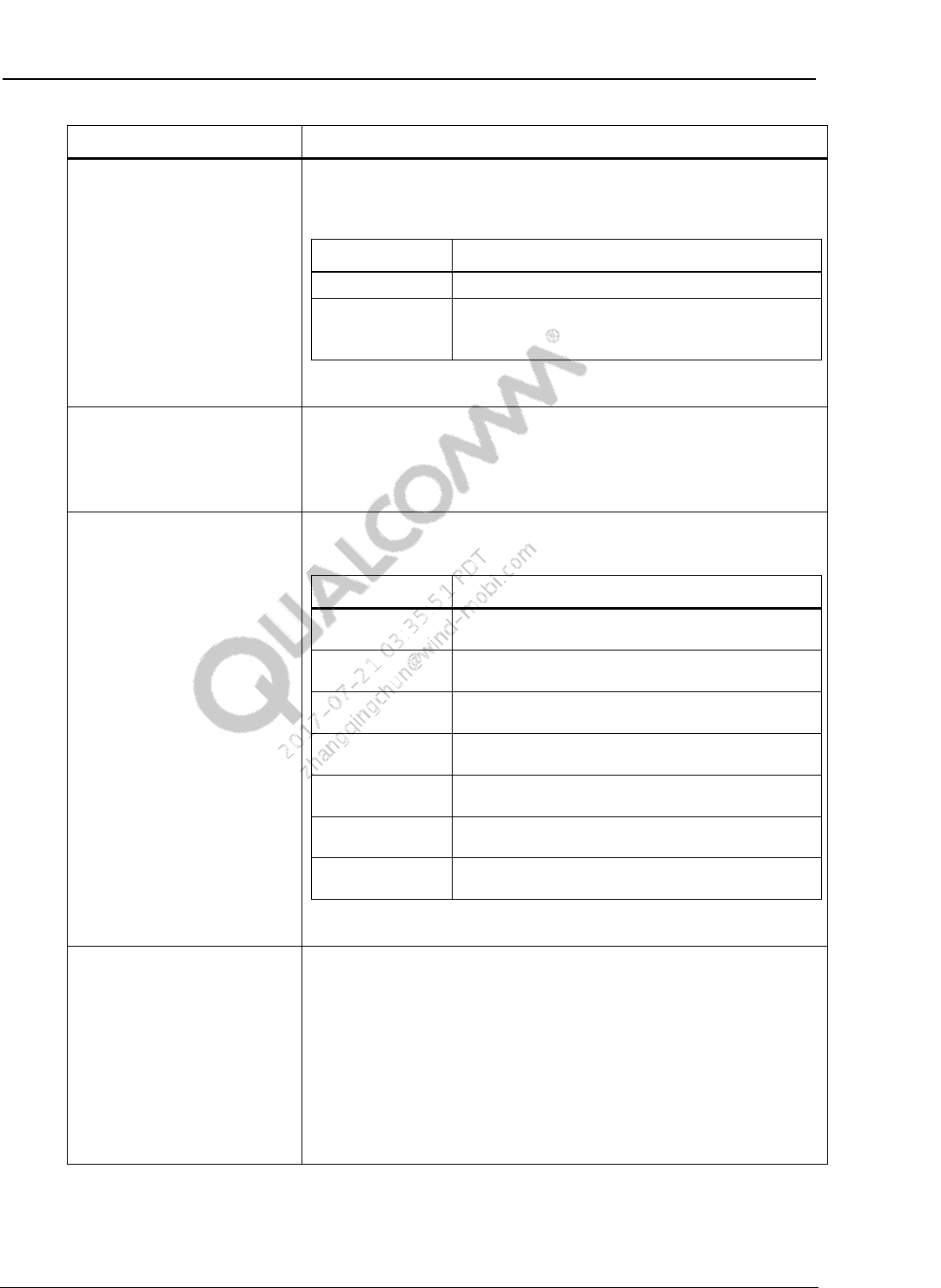

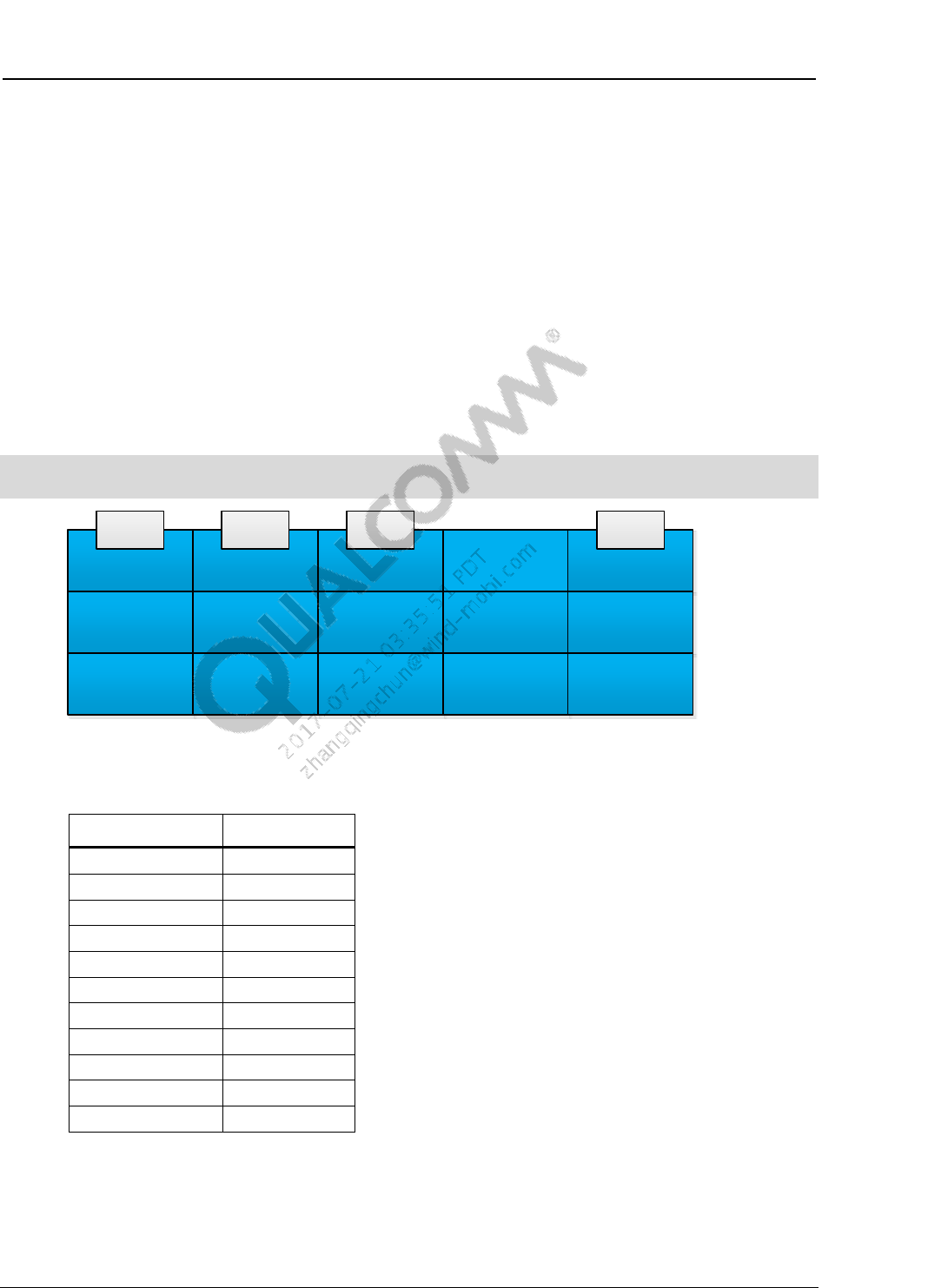

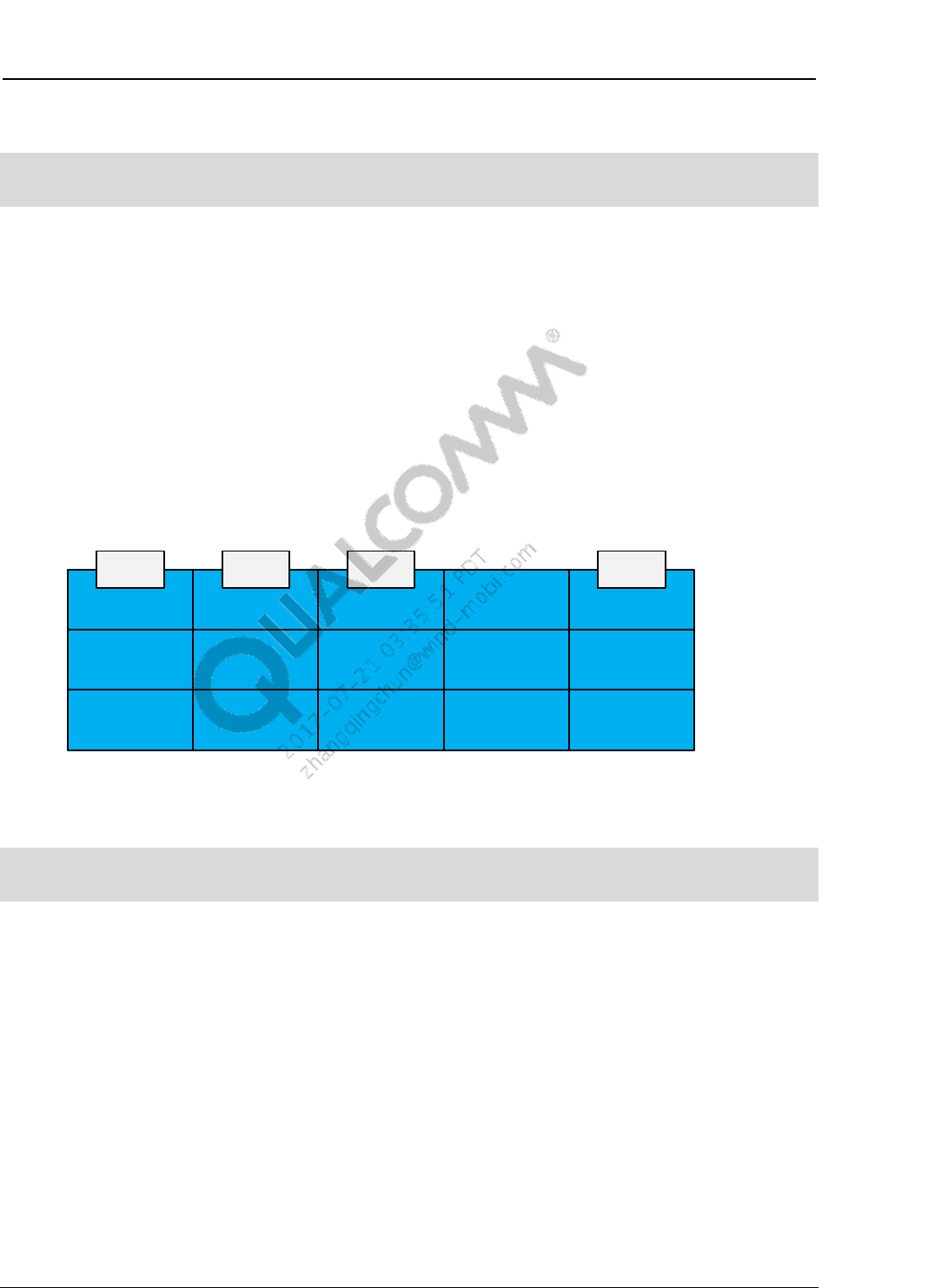

Figure 2-1 Panel configuration role in the boot sequence ............................................................................ 9

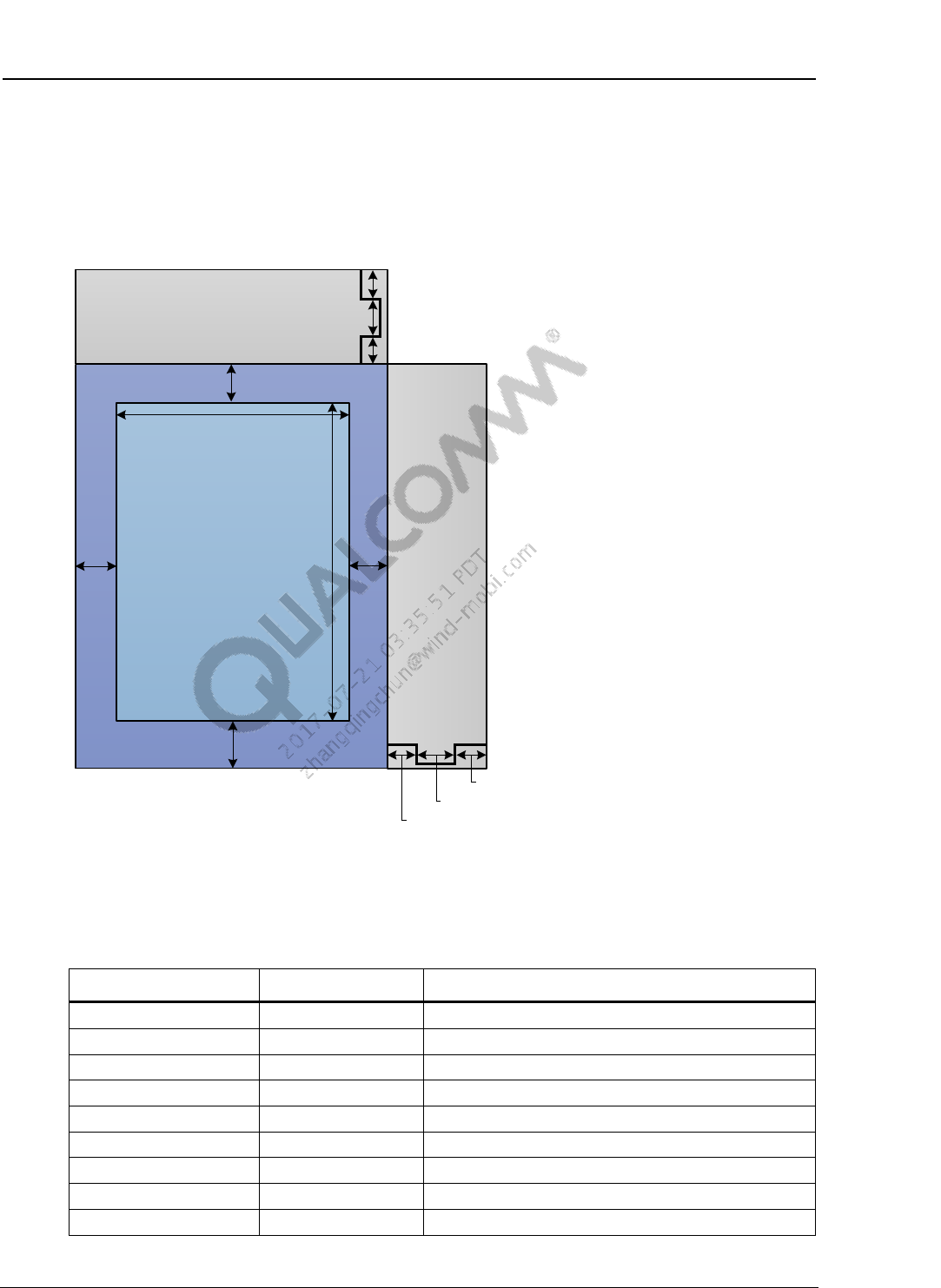

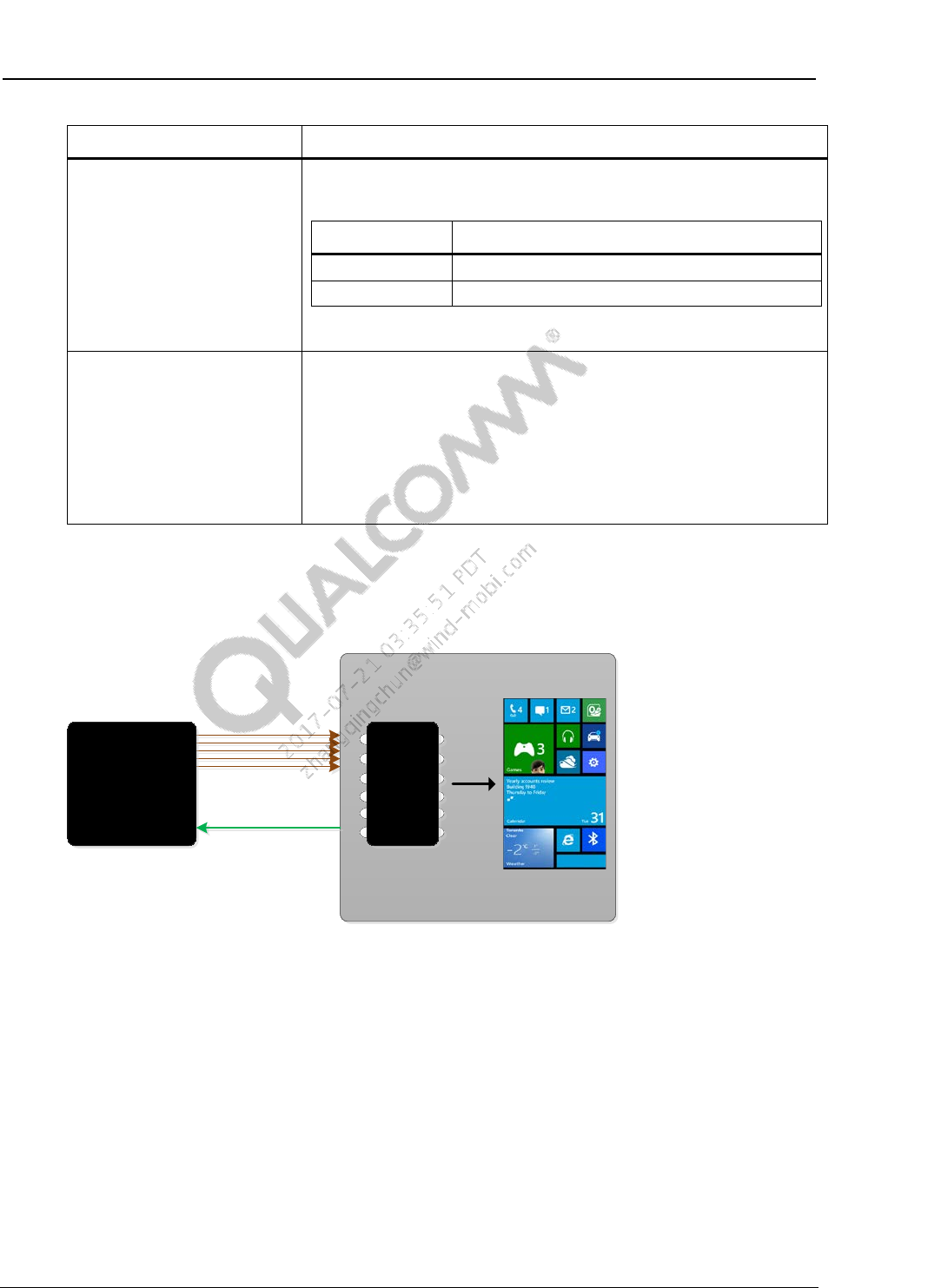

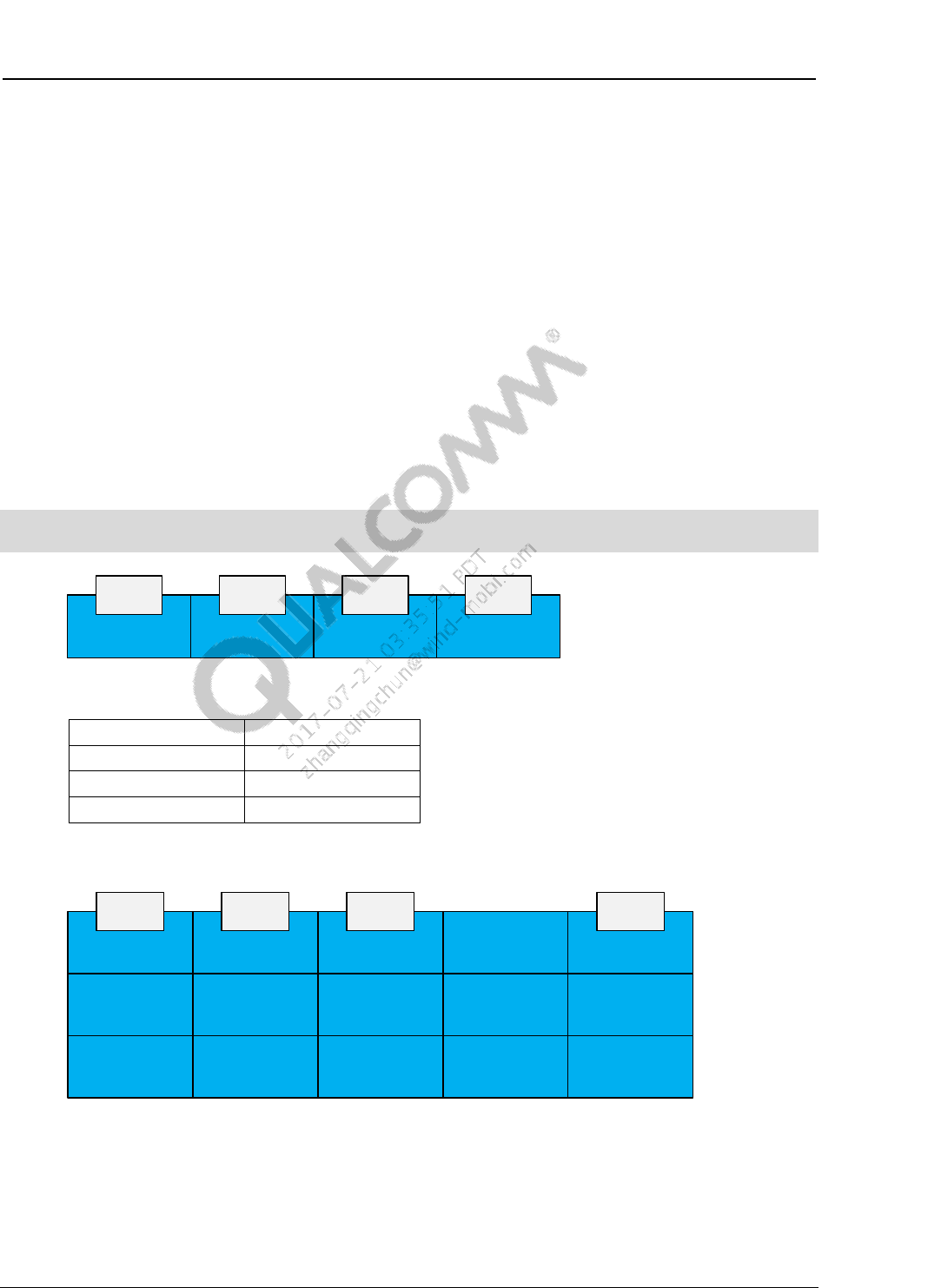

Figure 5-1 Example phone dimensions and EDID population .................................................................. 26

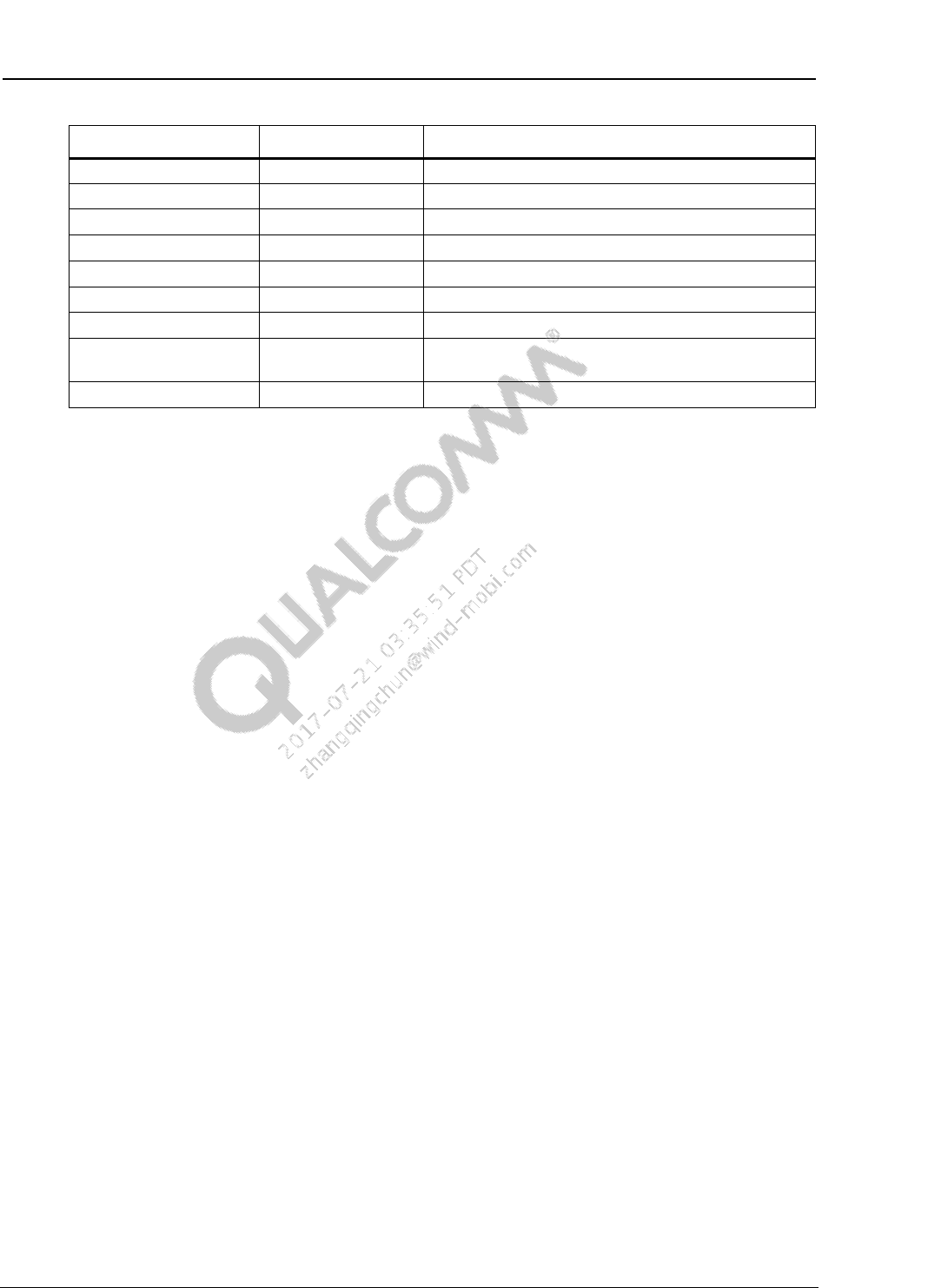

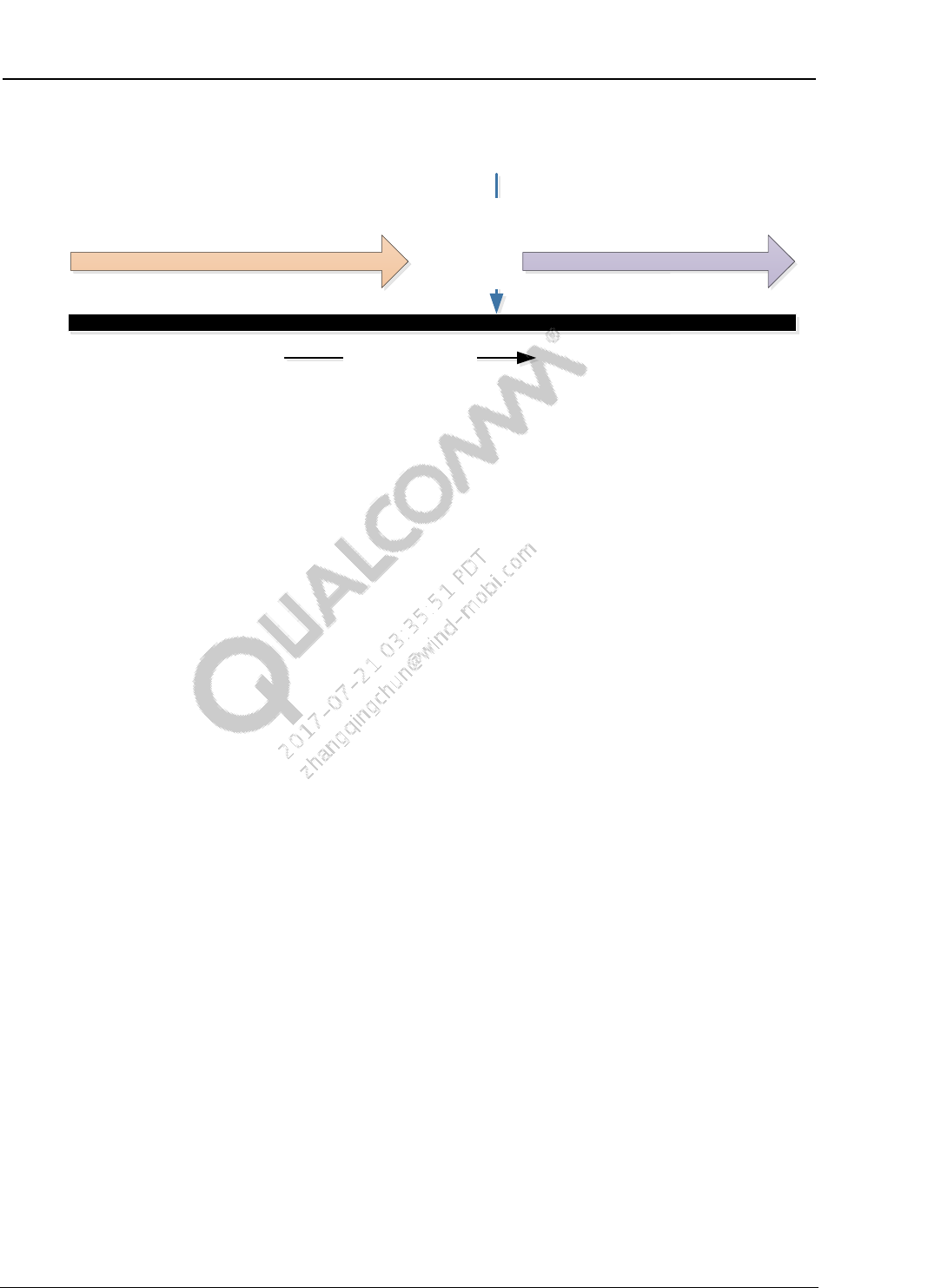

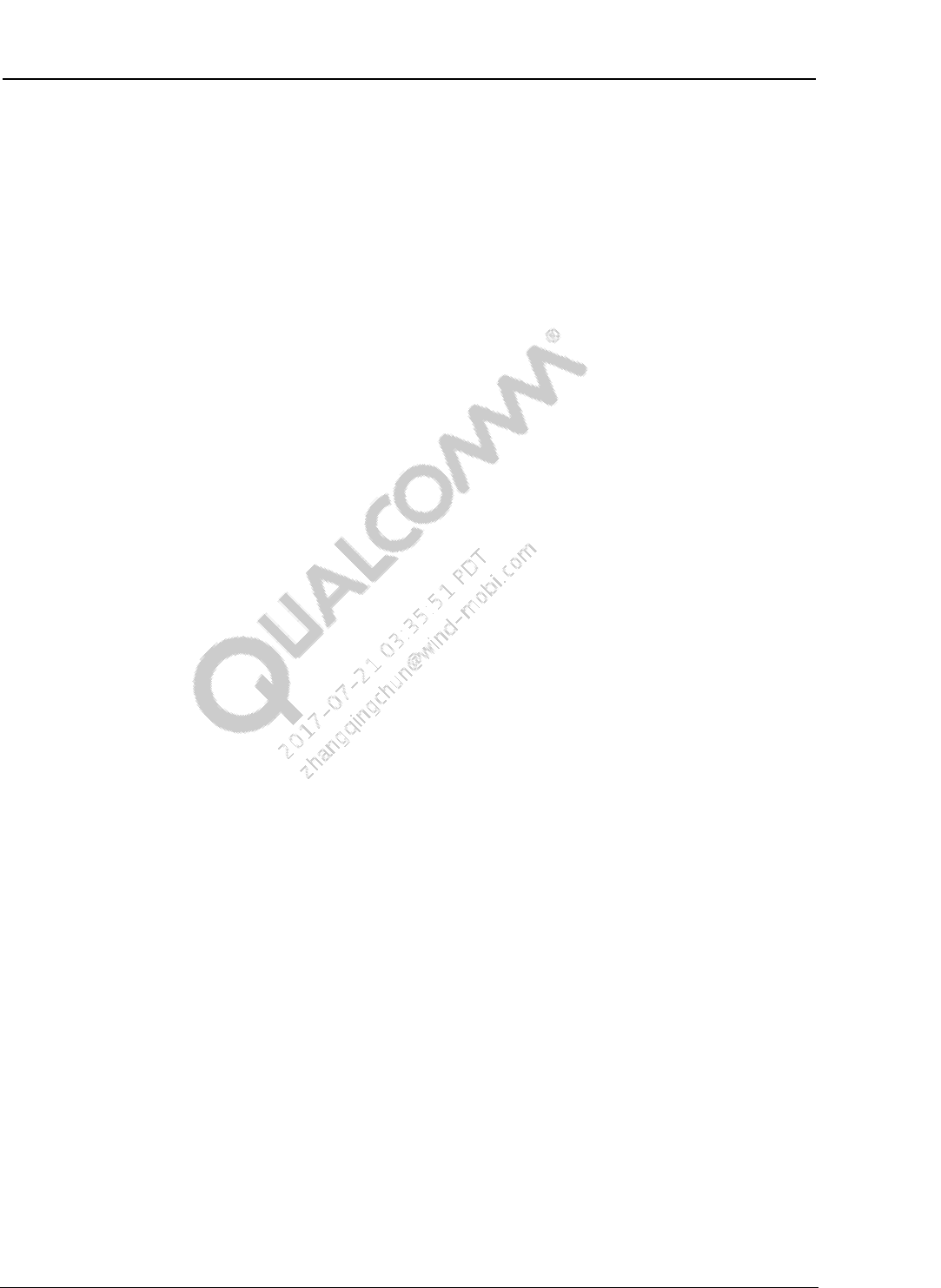

Figure 5-2 Panel timings configuration ..................................................................................................... 28

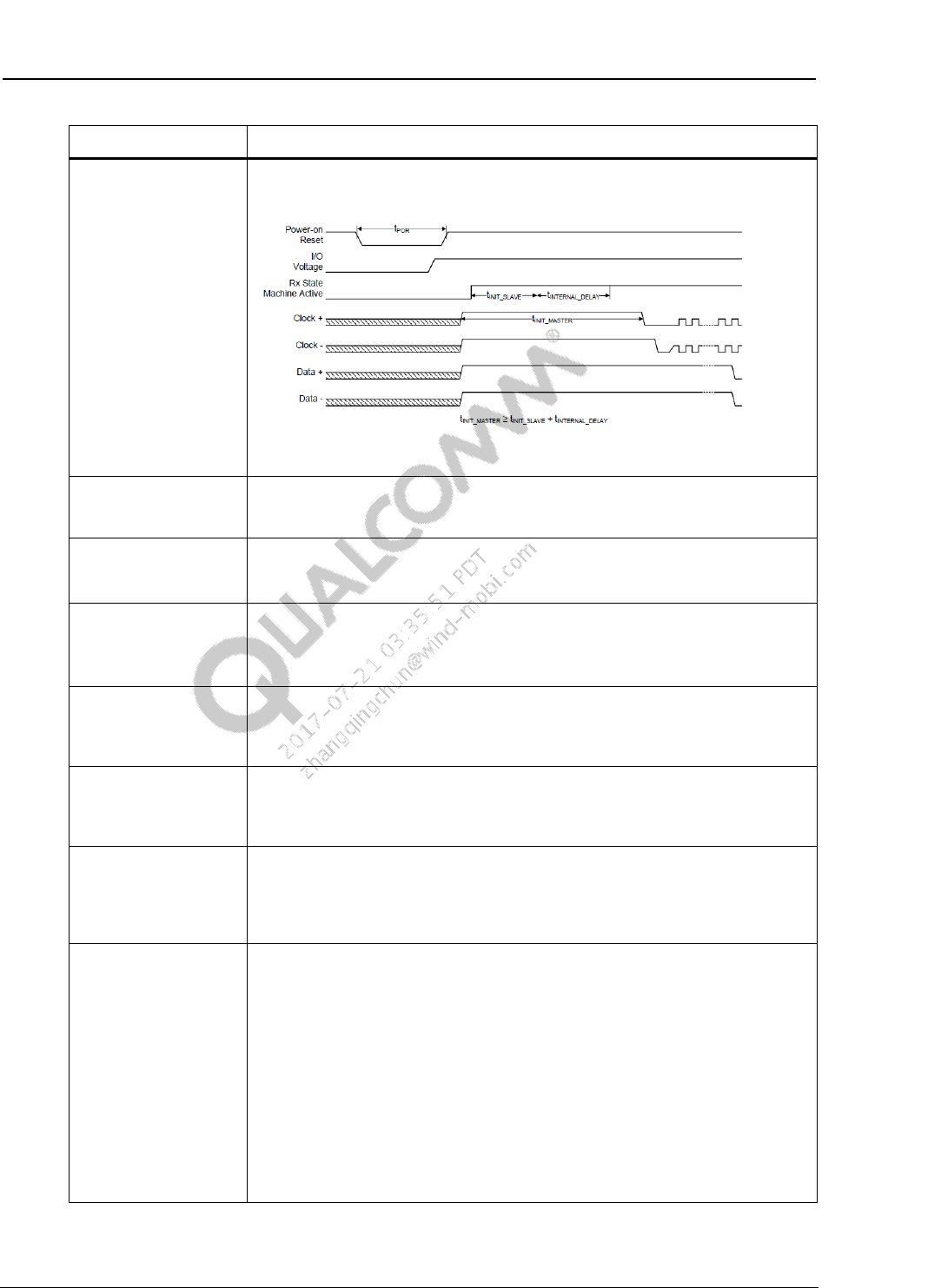

Figure 8-1 Init sequence timing ................................................................................................................. 43

Figure 8-2 DSI DCS command configurations .......................................................................................... 44

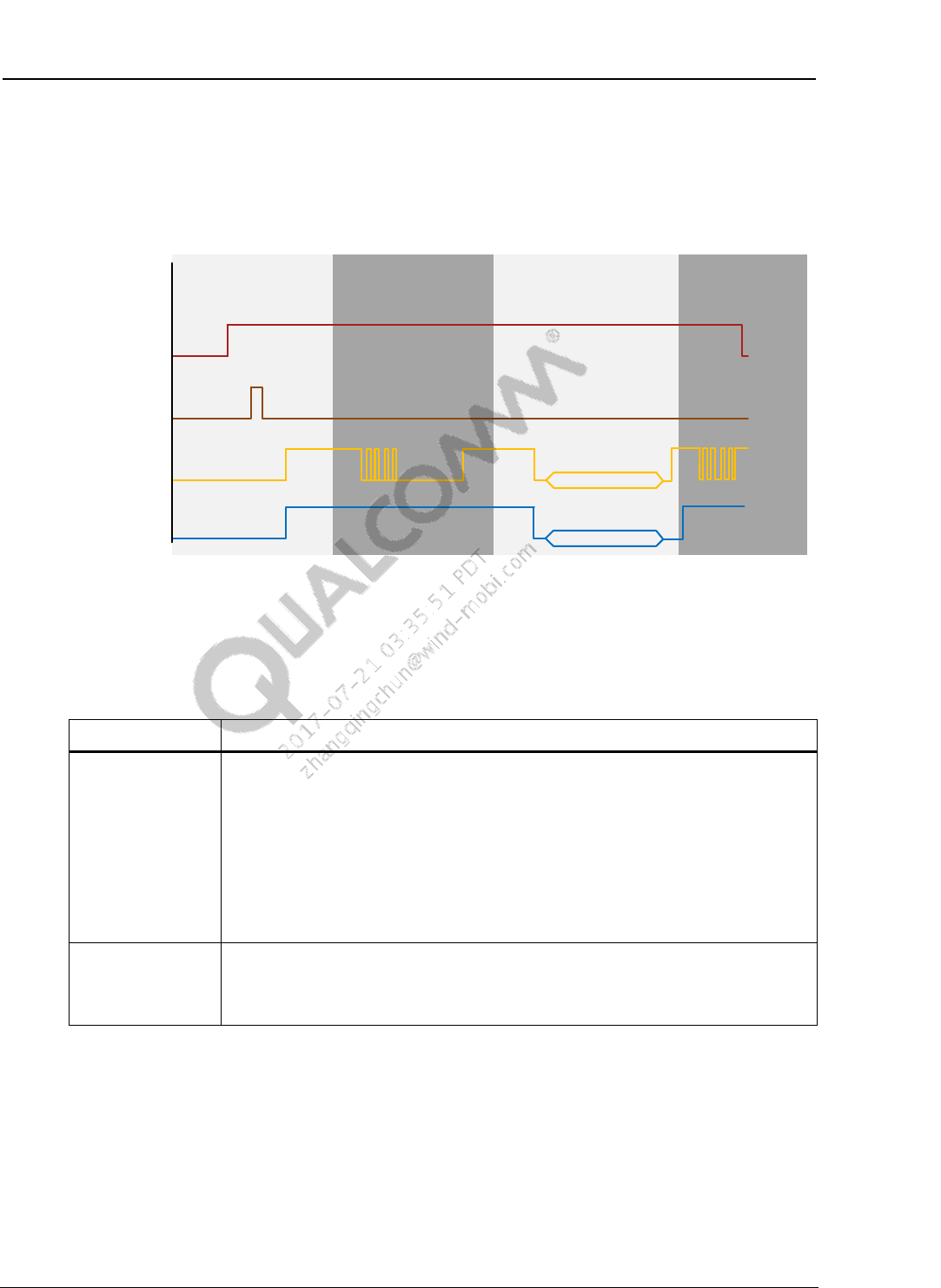

Figure 8-3 DSI Command mode TE synchronization................................................................................ 54

Figure 8-4 DSI data transmission with respect to panel scanline .............................................................. 55

Figure 9-1 Backlight control under WDDM model ................................................................................... 62

Figure 12-1 Panel power-on reset .............................................................................................................. 71

Figure 17-1 PMIC IBB and LAB modules .............................................................................................. 100

Tables

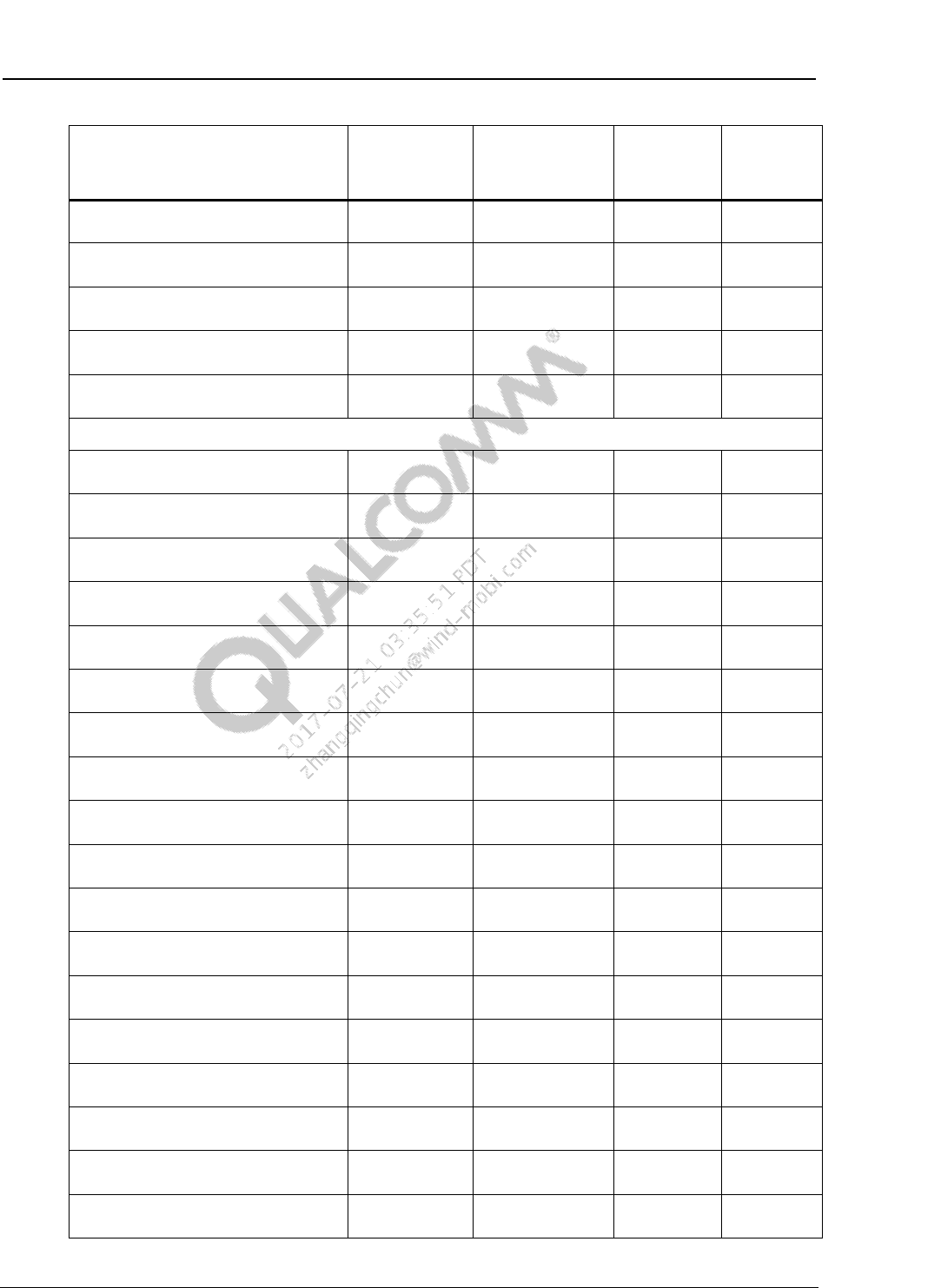

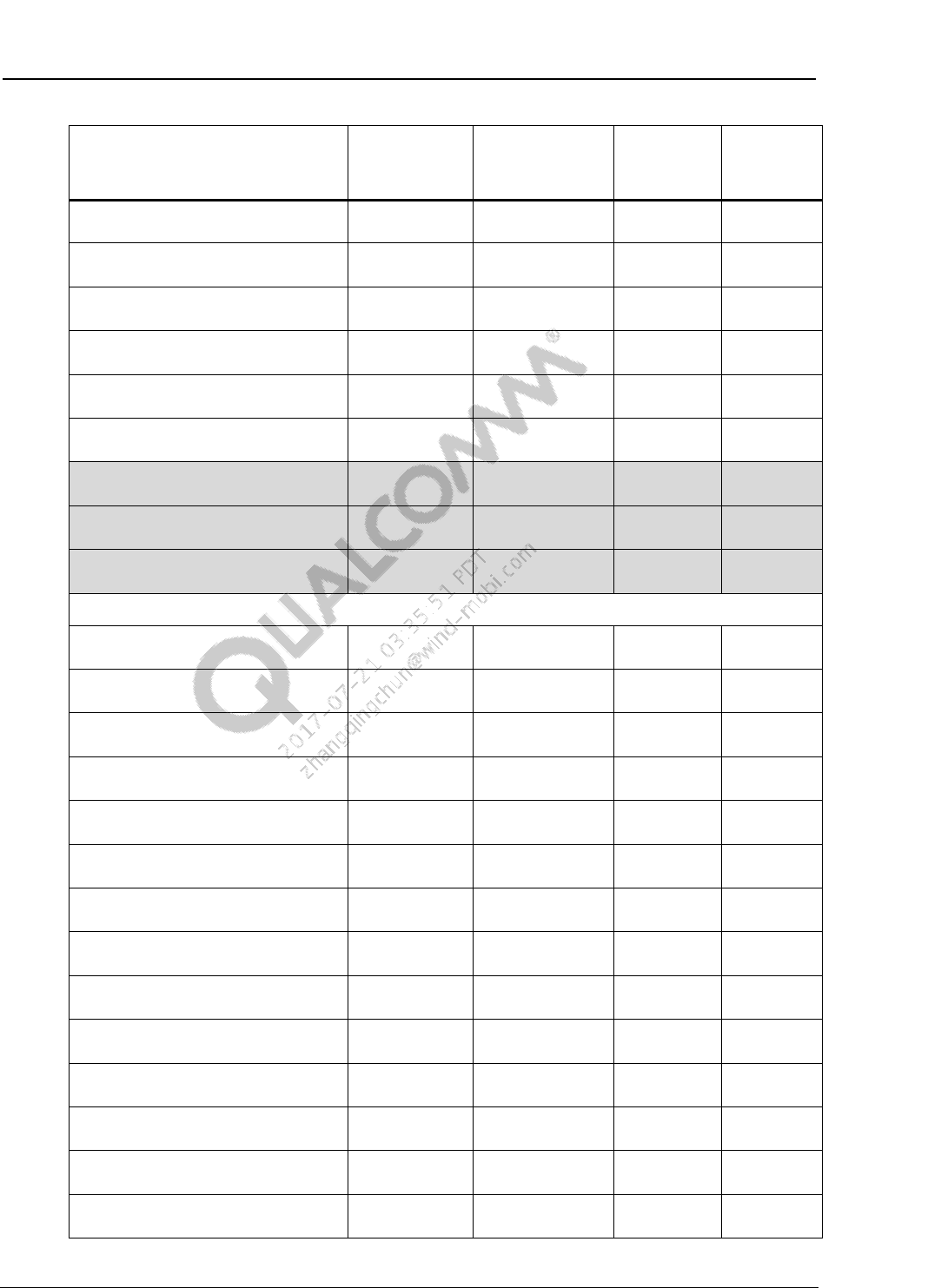

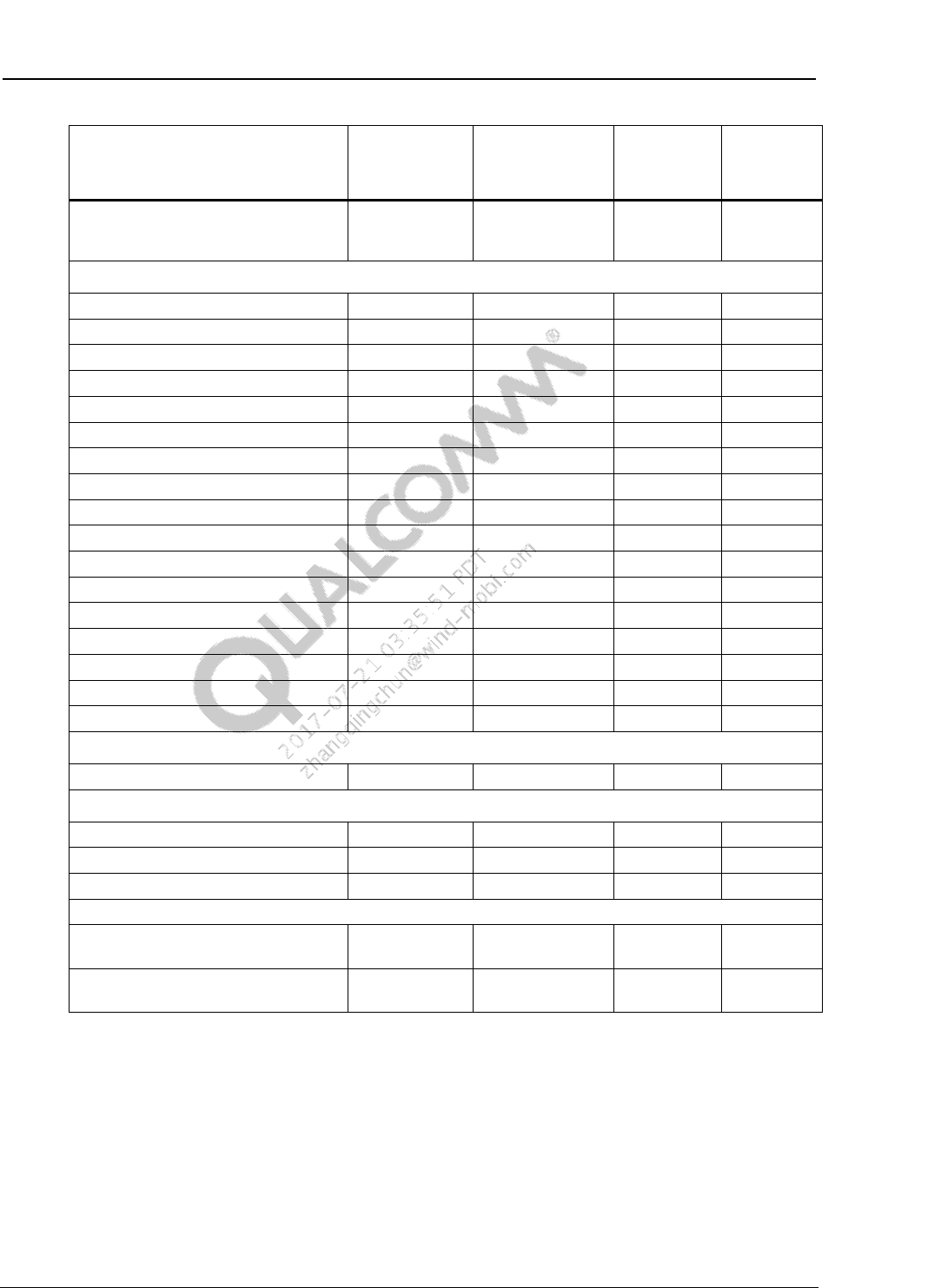

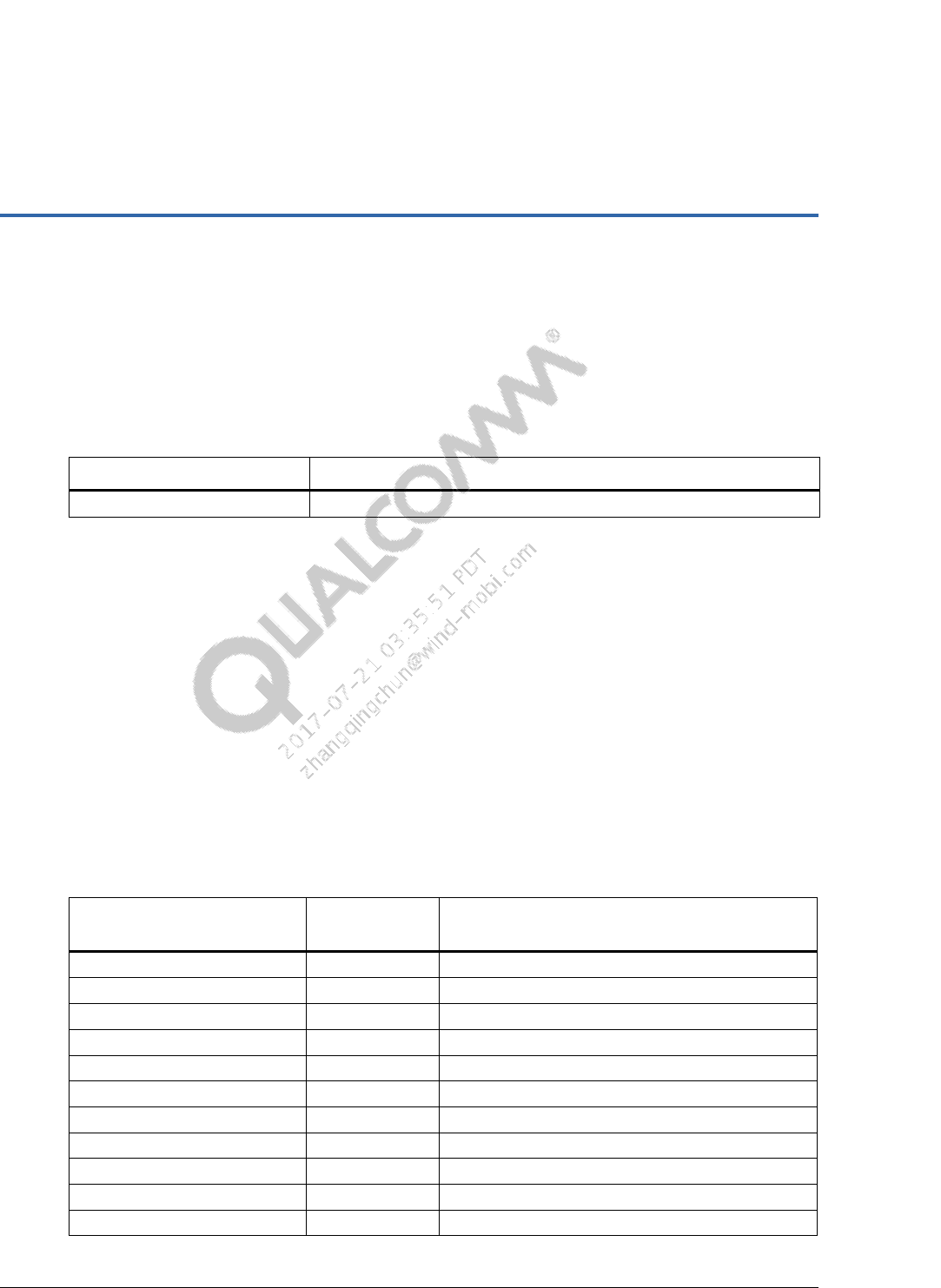

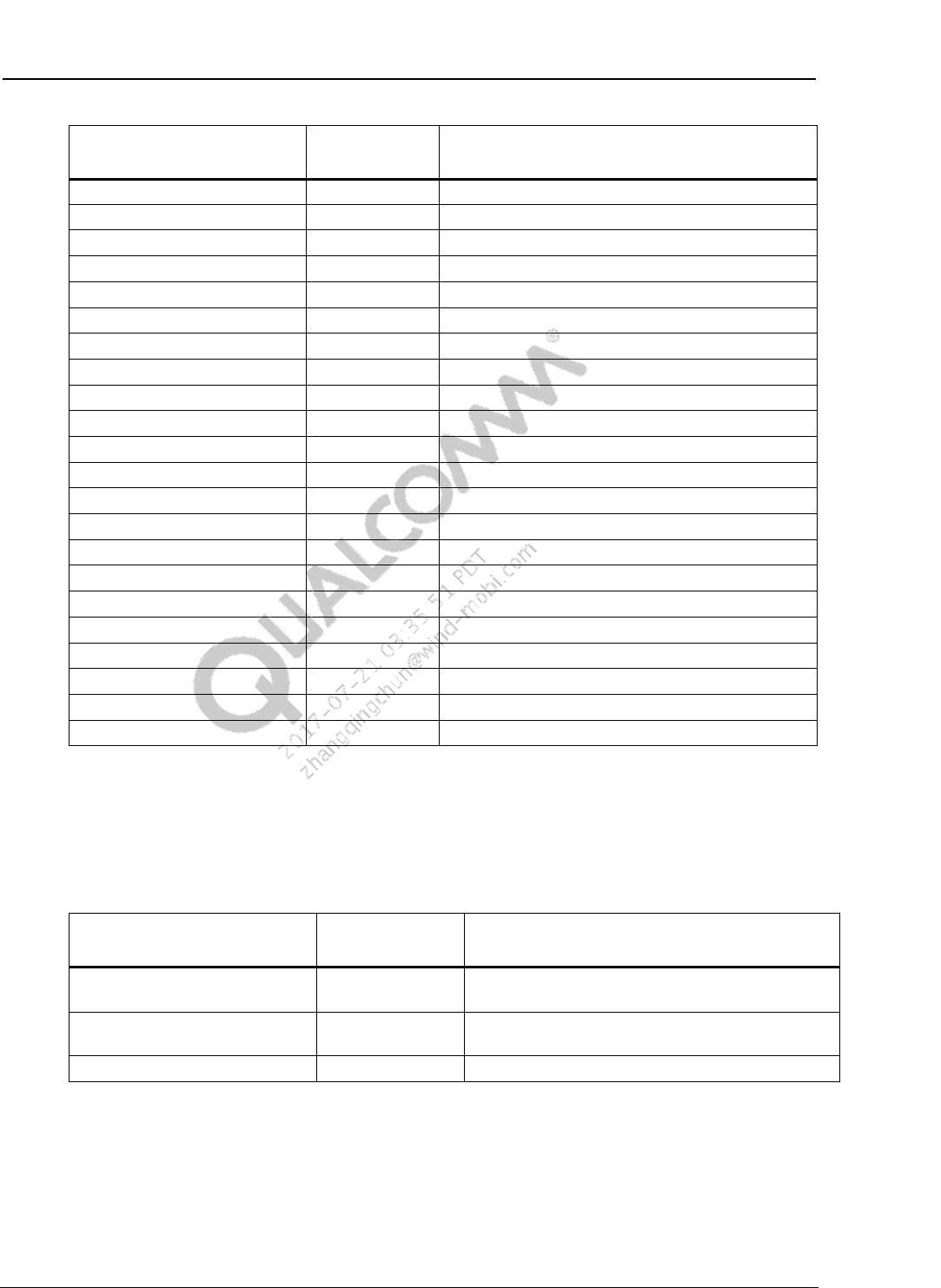

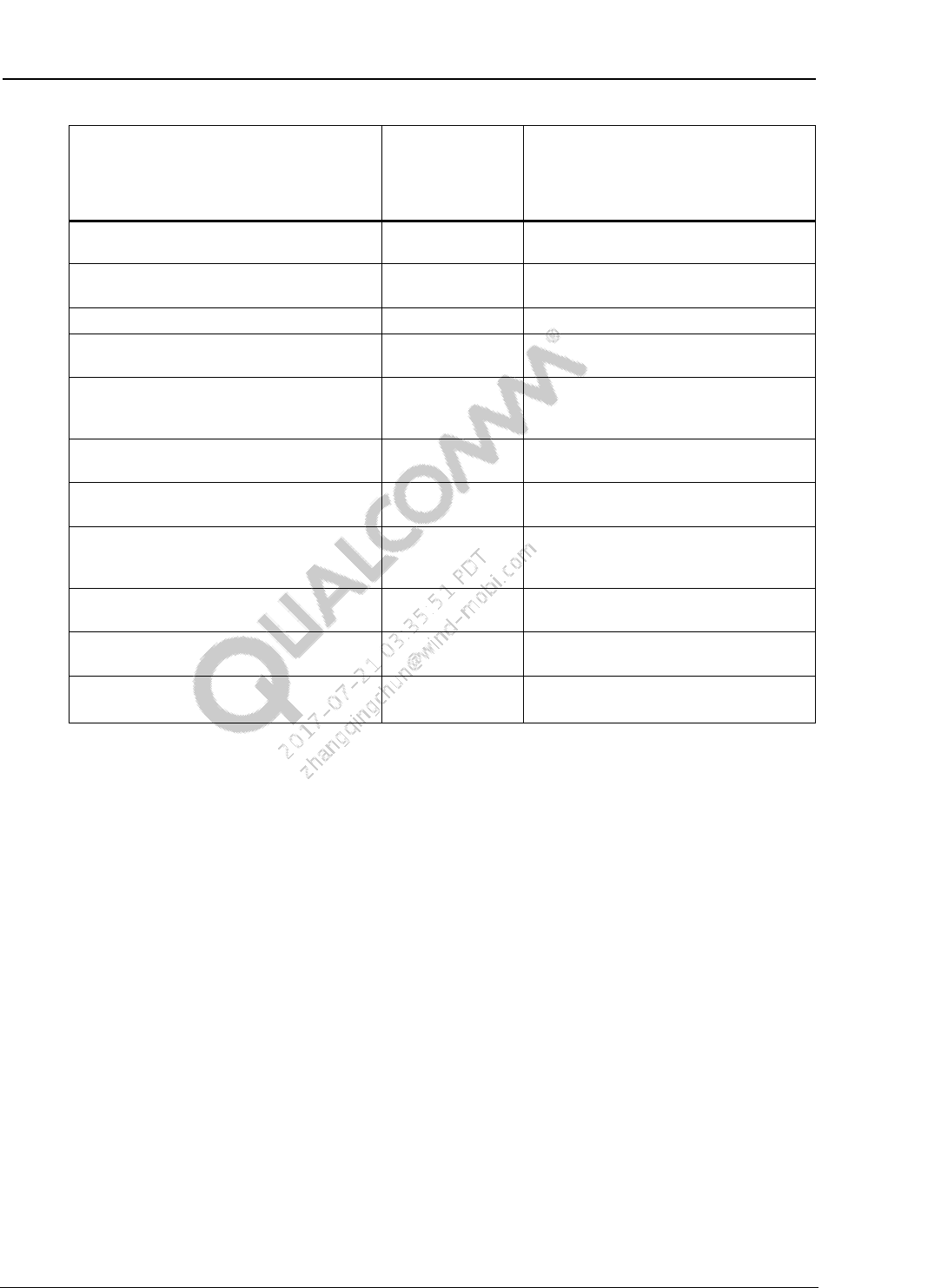

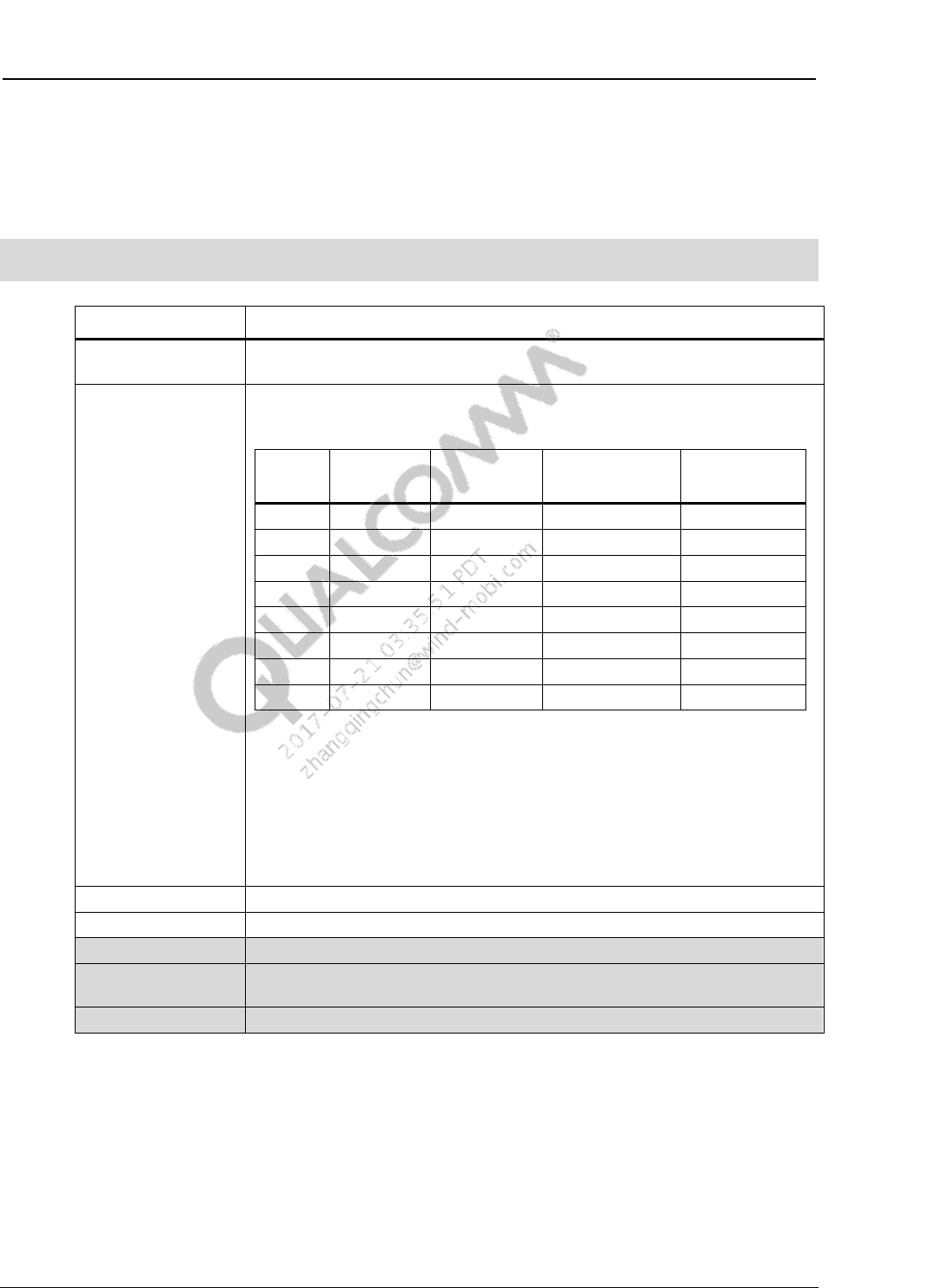

Table 4-1 Supported tag list ....................................................................................................................... 13

Table 5-1 Informational fields ................................................................................................................... 24

Table 5-2 Static EDID fields ...................................................................................................................... 24

Table 5-3 Detailed timing fields ................................................................................................................ 25

Table 5-4 Dynamic EDID fields ................................................................................................................ 26

Table 5-5 Panel timing fields ..................................................................................................................... 28

Table 6-1 Common hardware configuration parameters ........................................................................... 30

Table 7-1 Feature flags that can be enabled or disabled ............................................................................ 33

Table 8-1 Common DSI configurations ..................................................................................................... 35

Table 8-2 Parameters to configure the DSC module for DSI .................................................................... 42

Table 8-3 DSI DCS command configuration tags ..................................................................................... 44

Table 8-4 Supported DCS commands ........................................................................................................ 45

Table 8-5 Special DCS commands ............................................................................................................ 45

Table 8-6 DSI interface timing overrides .................................................................................................. 46

Table 8-7 DSI Video mode configuration .................................................................................................. 47

Table 8-8 DSI Command mode configuration ........................................................................................... 52

Table 8-9 eDP configuration ...................................................................................................................... 58

Table 8-10 HDMI configuration ................................................................................................................ 60

Table 9-1 Common backlight configuration parameters ........................................................................... 63

Table 9-2 PWM (PMIC)-based backlight control ...................................................................................... 64

Table 9-3 CABL configuration .................................................................................................................. 67

Table 9-4 Backlight configuration ............................................................................................................. 68

Table 10-1 ESD Detection and Recovery tags ........................................................................................... 69

Table 10-2 Display recovery threshold ...................................................................................................... 69

Table 11-1 AD core tags ............................................................................................................................ 70

Table 12-1 Panel resources ........................................................................................................................ 72

Configuration Guide for Display Drivers (ACPI and XML) Contents

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 7

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Table 12-2 GPIO configuration tags .......................................................................................................... 74

Table 13-1 Power saving configuration ..................................................................................................... 76

Table 13-2 Power saving levels supported by the driver ........................................................................... 77

Table 14-1 Sharpening parameters ............................................................................................................ 78

Table 17-1 IBB/LAB management configuration.................................................................................... 101

Table A-1 XML tags and descriptions ..................................................................................................... 102

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 8

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

1 Introduction

1.1 Purpose

This document is intended for display developers who are looking to customize the display-

specific Advanced Configuration and Power Interface (ACPI) entries for a particular display

device. Knowledge of display interfaces, Windows display driver model (WDDM) architecture,

and ACPI programming are prerequisites for this document. The XML syntax is common

between UEFI and ACPI, therefore this document applies to both configuration methods.

This document supports the MSM8974, MSM8x26, MSM8x62, MSM8084, MSM8x94,

MSM8996, and MSM8998 chipsets. Configurations mentioned in this document are specific to

these chipset families.

1.2 Conventions

Function declarations, function names, type declarations, and code samples appear in a different

font, e.g., #include.

Code variables appear in angle brackets, e.g., <number>.

Commands to be entered appear in a different font, e.g., copy a:*.* b:.

Button and key names appear in bold font, e.g., click Save or press Enter.

Shading indicates content that has been added or changed in this revision of the document.

1.3 Technical assistance

For assistance or clarification on information in this document, submit a case to Qualcomm

Technologies, Inc. (QTI) at https://createpoint.qti.qualcomm.com/.

If you do not have access to the CDMATech Support Service website, register for access or send

email to support.cdmatech@qti.qualcomm.com.

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 9

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

2 ACPI configuration for display drivers

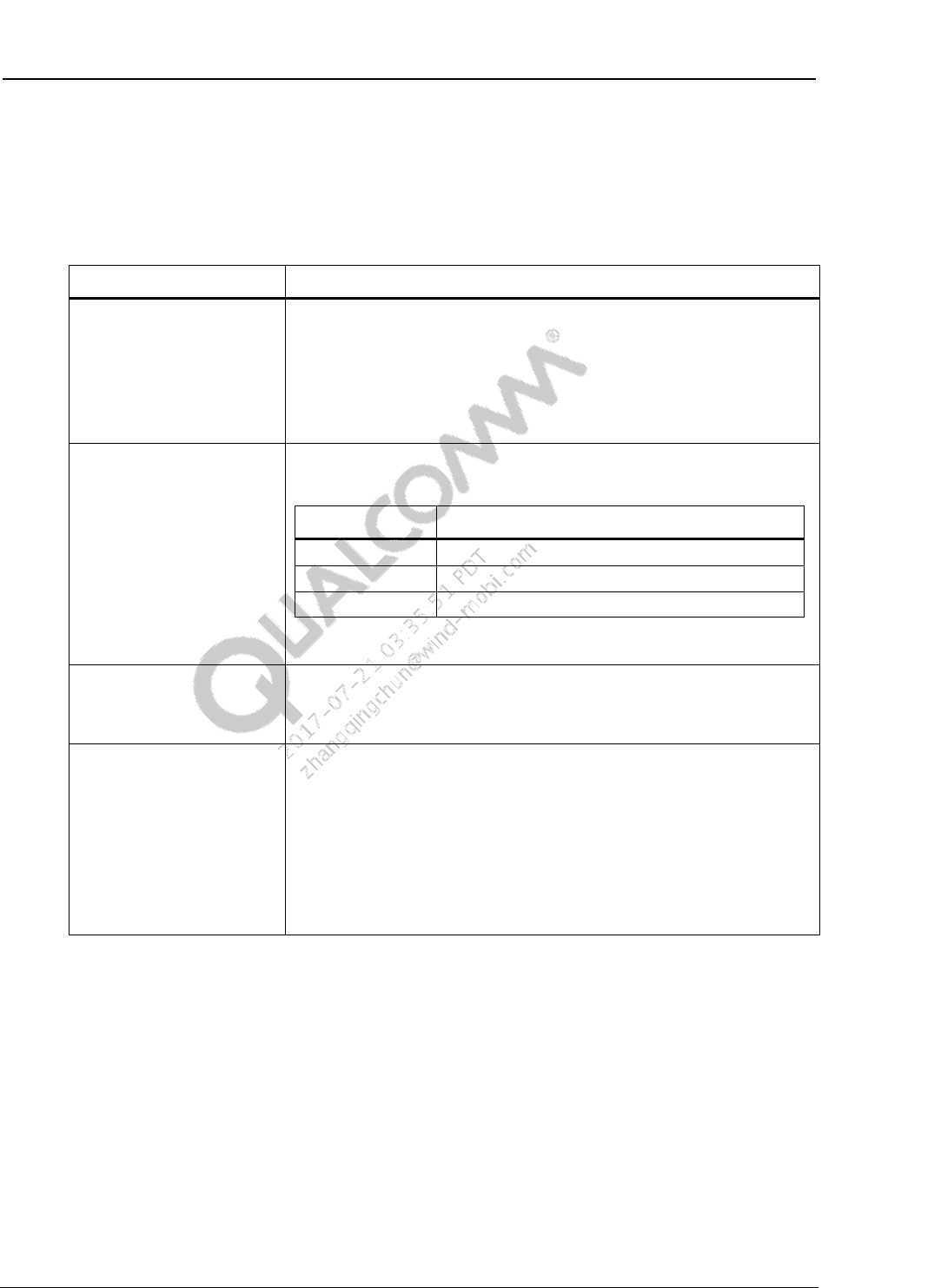

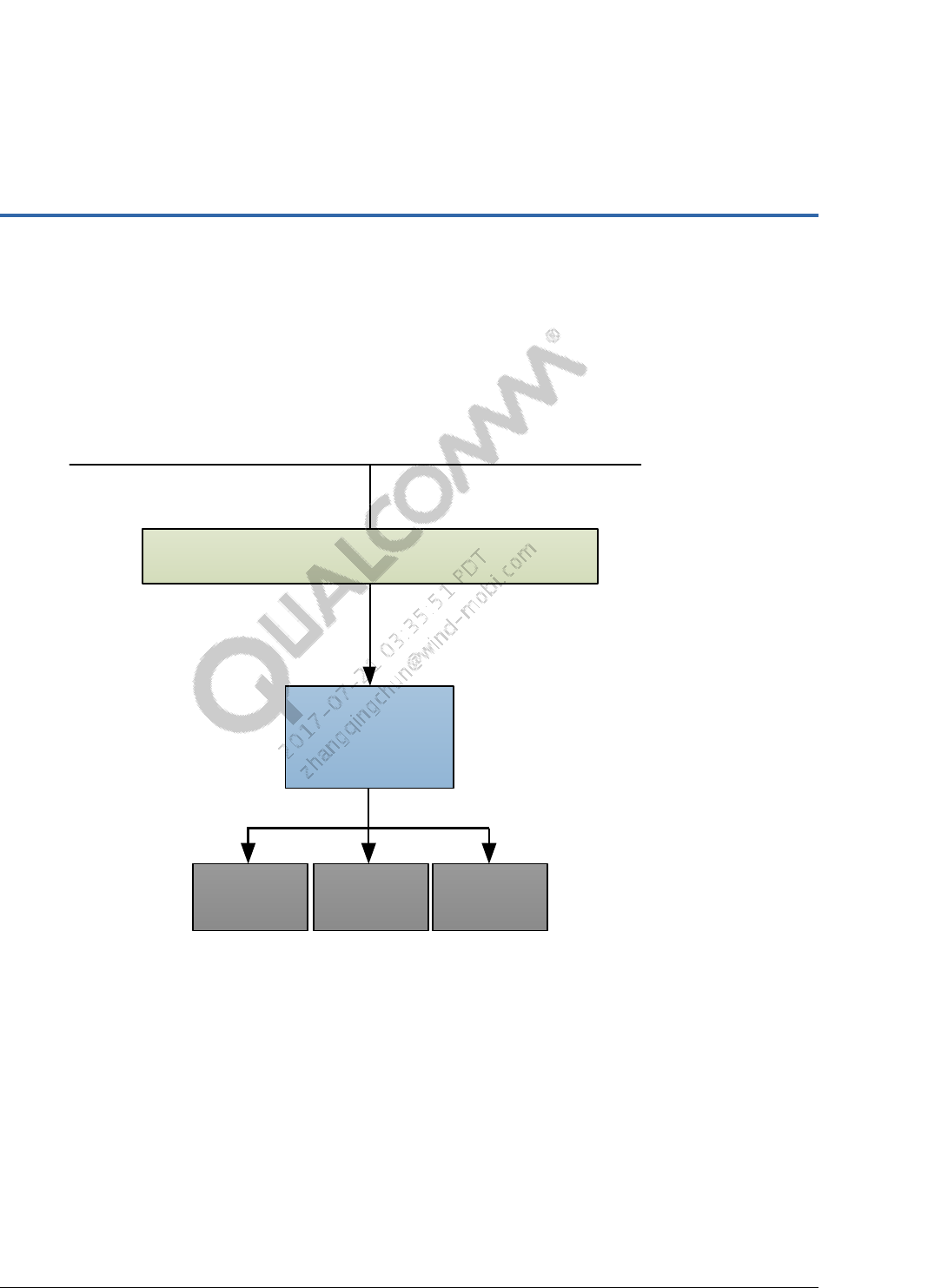

2.1 Panel configuration in the boot sequence

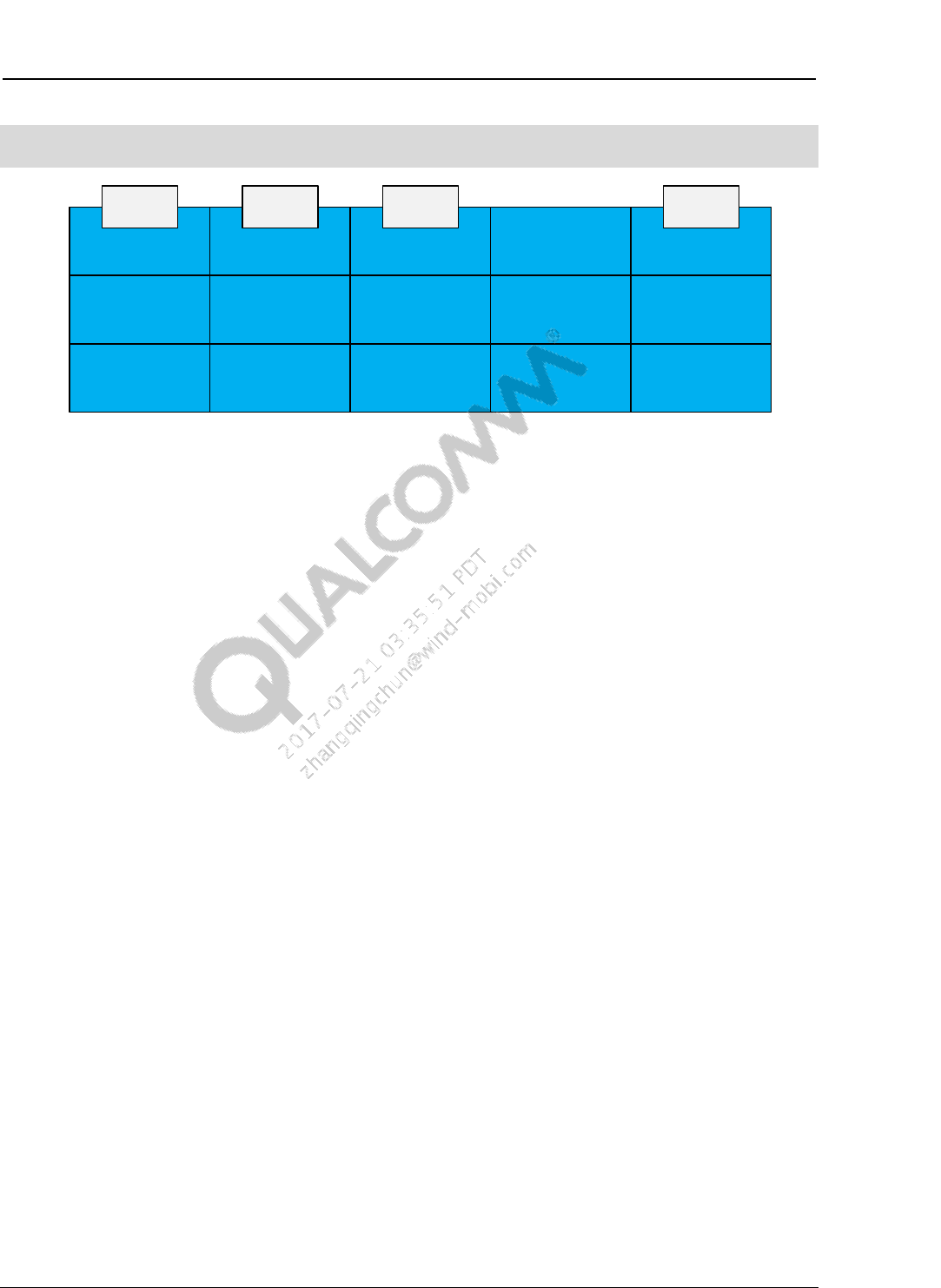

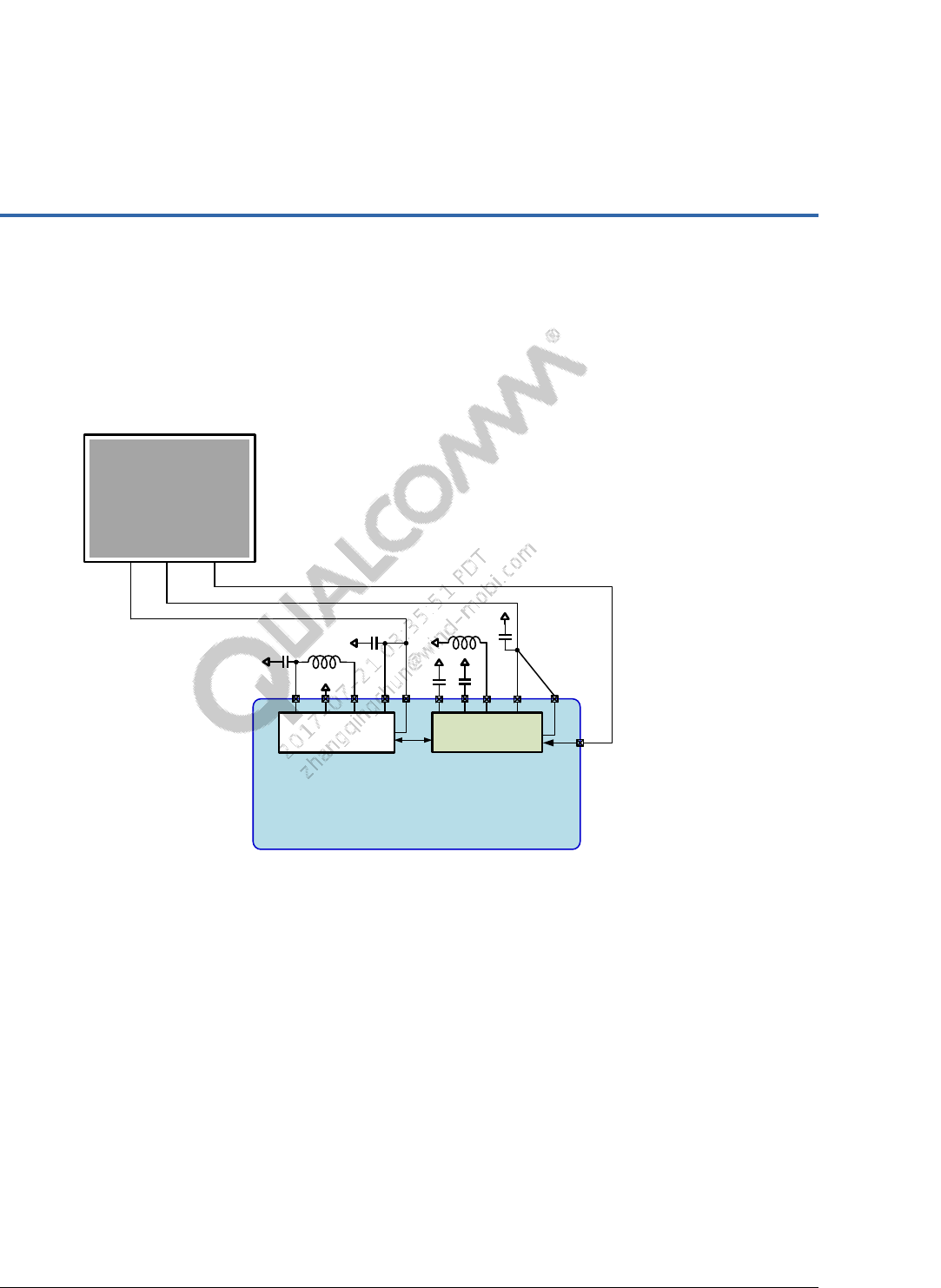

The role of the panel configuration in the boot sequence is shown in Figure 2-1.

Firmware (UEFI)

(xml binary configuration) HLOS Loader Kernel Mode Driver

Figure 2-1 Panel configuration role in the boot sequence

The following two-stage sequence is specific to HLOSes that use UEFI and ACPI:

Firmware (UEFI) boot – During UEFI boot, the panel configuration is loaded directly from a

panel configuration in the UEFI binary. This configuration is parsed and applied to the

display controller.

OS boot (graphics miniport) – During OS boot, the KMD parses the display configuration

from the ACPI (_ROM) method.

Both boot stages use similar XML configurations. However, the data is physically located in two

locations even though the data has many configurations that are identical. The reason for this is

that the UEFI does not directly process data from the ACPI tables, and therefore the data cannot

be shared between both boot sequences. The Figure 2-1 shows the role of panel configuration in

the boot sequence.

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 10

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

3 Panel configuration format

The panel configuration format is XML-like, only certain data fields are parsed and only certain

tags are recognized.

3.1 Tag syntax

The tag syntax is similar to XML using braces for various tags.

<?xml version="1.0" encoding="utf-8"?>

<TagName comments=”any comments”>Tag Data</TagName>

<MultiLineTag>

Tag Data

More Data

</MultiLineTag>

All tags must be unique except for certain keyword tags that are ignored

All tags must end with a </TagName>

Tags are case-insensitive

Tags cannot be made from spaces or special characters

3.2 Special keyword tags

The <?xml xxxxxxxx ?> tag is ignored.

Tags that use the keyword Group are ignored. However, tags within the context of a group

branch are parsed, for example, Group xyz is ignored, but MyTagA is parsed.

<Group xyz>

<MyTagA> data </MyTagA>

</Group>

Comments are added as <!-- Comment -->. However, comments should be avoided because

they add extra parsing time and size to the configuration.

Data appears after the tag name is ignored, but can be used for comments or informational

purposes.

<MyTag this_data is ignored = “””> tag data </MyTag>

Configuration Guide for Display Drivers (ACPI and XML) Panel configuration format

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 11

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

3.3 Supported data types

Parsing of data supports several data types.

Integer – Integer data can be in the form of decimal digits or hex digits. Depending on the

integer size, the range can vary; e.g., if the size is 1 byte, the range is 0x00-0xFF (0 to 255

decimal). Hex digits must be prefixed with “0x”, e.g., these are all valid integer values:

<MyIntegerTag>123456</MyIntegerTag>

<MyHexTag>0xFFEE23</MyHexTag>

Integer list – Integer lists are an ordered list of integers separated by spaces. Each entry is

interpreted as hex values regardless if it is prepended with 0x.

<MyIntergerList>0x1234 0x456 0xAA 0xBB</MyIntegerList>

String – String data can be any alphanumeric sequence including spaces, e.g.:

<MyStringTag>Same String Data 1234</MyStringTag>

Boolean – Boolean data consists of either the true or false keyword tag. The case does not

matter.

<MyBooleanTag>True</MyBooleanTag>

<MyBooleanTag>false</MyBooleanTag>

GUID – The GUID tag accepts a standard Windows GUID, e.g.:

<MyGUIDTag>{0xf9938f2d, 0x3756, 0x4760, 0xa0, 0x44, 0xcb, 0x29, 0xaf, 0xba,

0x5a, 0x69}</MyGUIDTag>

Binary – The binary field is a special field that is used to describe raw information, i.e.,

packet data. Each hex pair byte is separated by spaces and the “0x” prefix is not allowed.

Multiple packets can be formed by adding a new byte sequence on each line.

NOTE: This is an important differentiator. Multiple bytes in the same line represent a single sequence,

while multiple bytes on multiple lines represent multiple packet sequences.

<MyDataSequence>

23 b0 04 29 b3 00 87 29 b6 30 83

</MyDataSequence>

<MultiPacketSequence>

23 b0 04 29 b3 00

87 29 b6 30 83

</MultiPacketSequence >

Configuration Guide for Display Drivers (ACPI and XML) Panel configuration format

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 12

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

3.4 Limitations

ASCII only – Only ASCII characters must be used. Unicode and double byte characters are

not supported.

Limited XML support – The format of the panel configuration is XML-like, and not all XML

tags are supported. Avoid using syntax that is not described in this document.

Configuration size – The panel configuration size is bounded by the amount of memory

allocated to store the configuration. Size limitations include all characters, including white

spaces, tags, and control characters (line feeds and carriage returns).

Firmware – Static structure, no limitations other than compile limitations

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 13

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

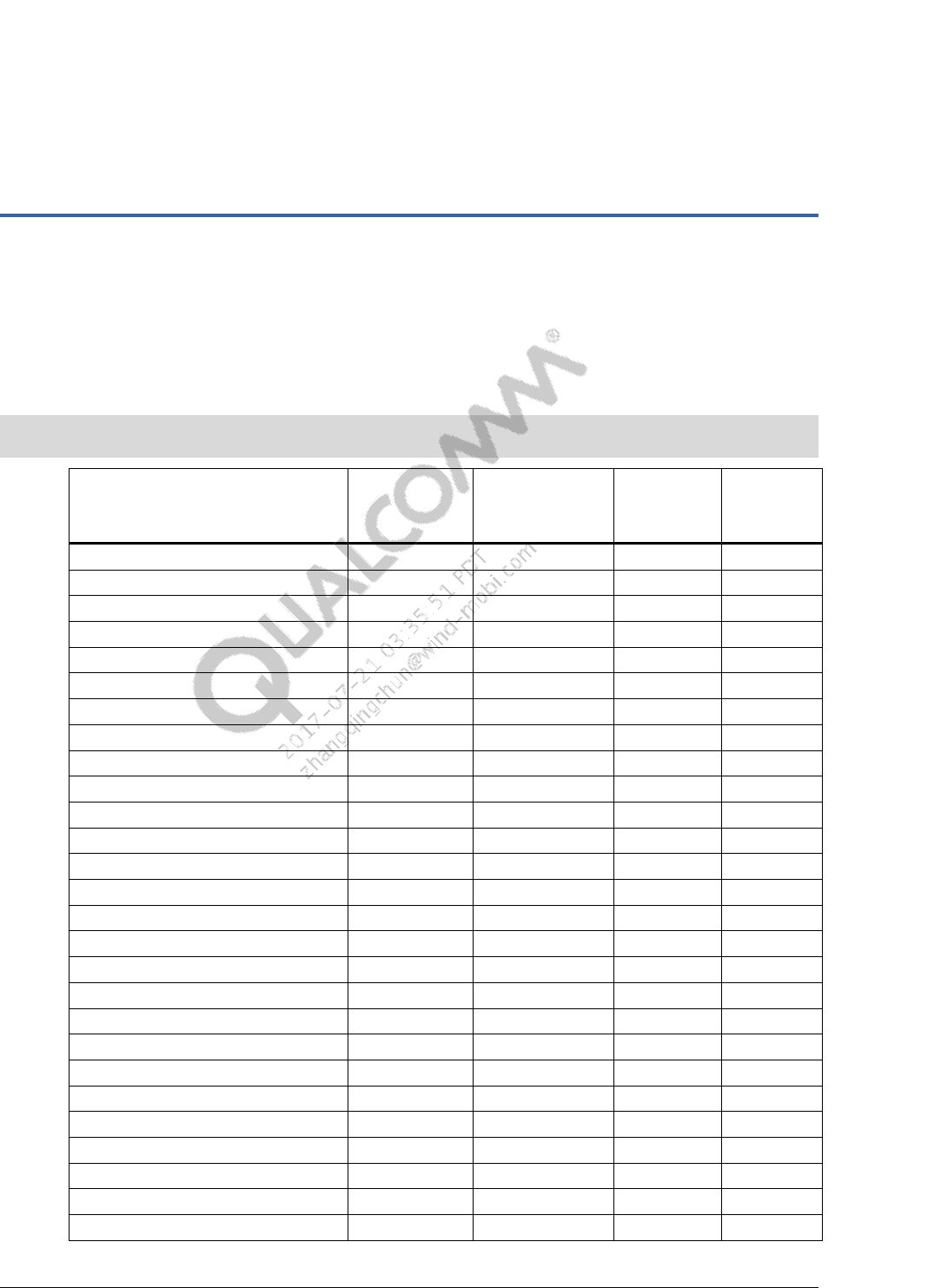

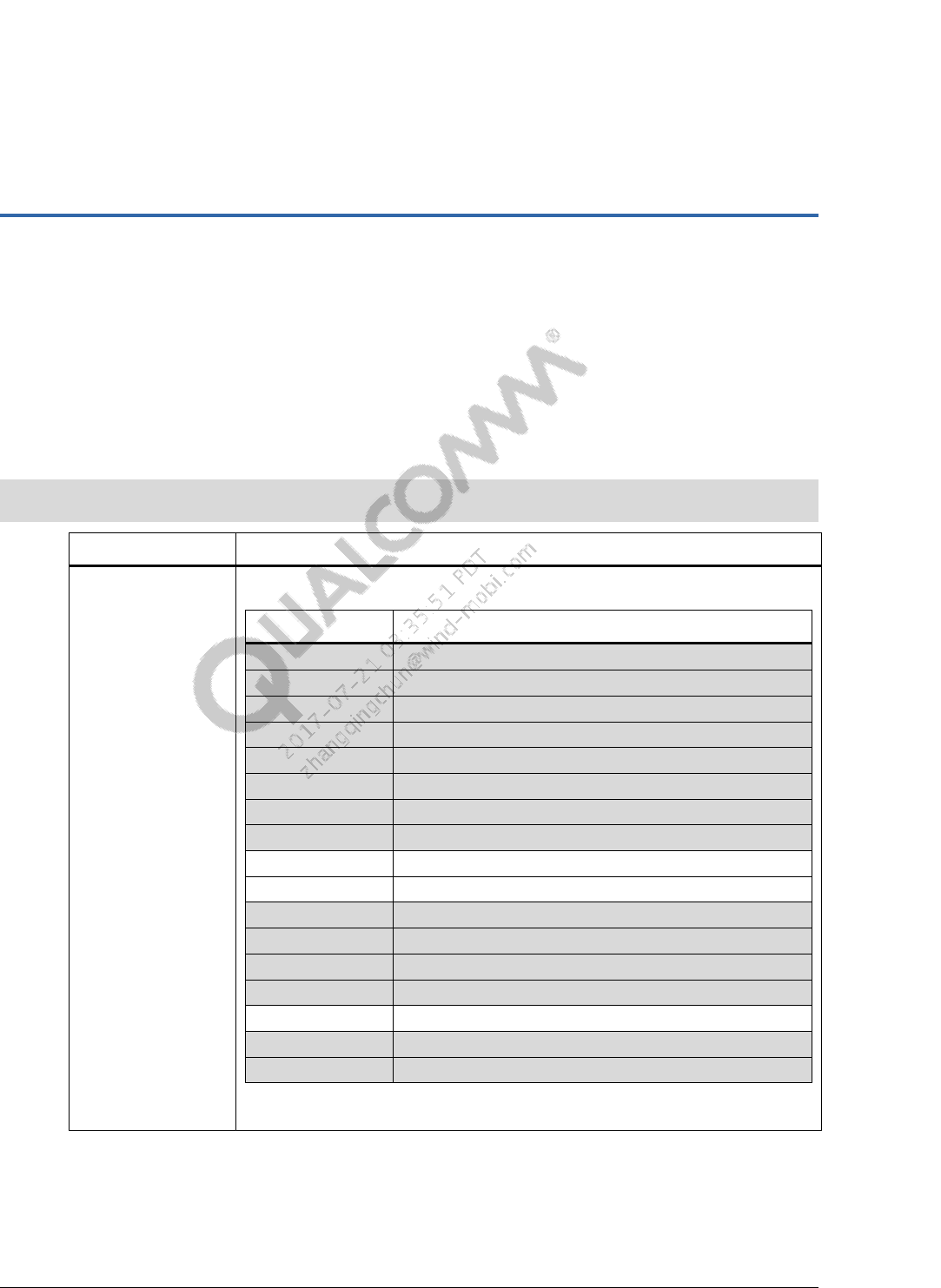

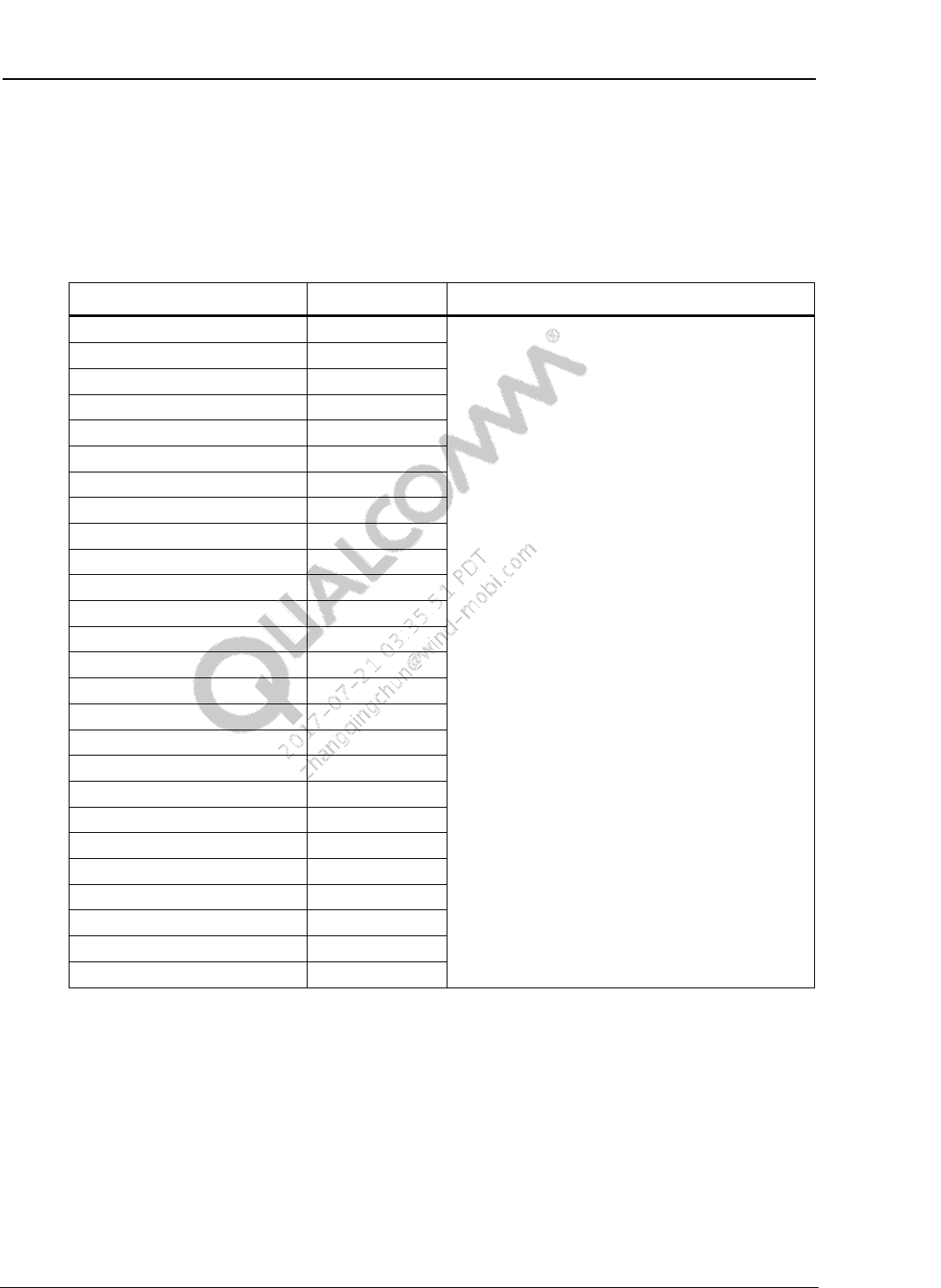

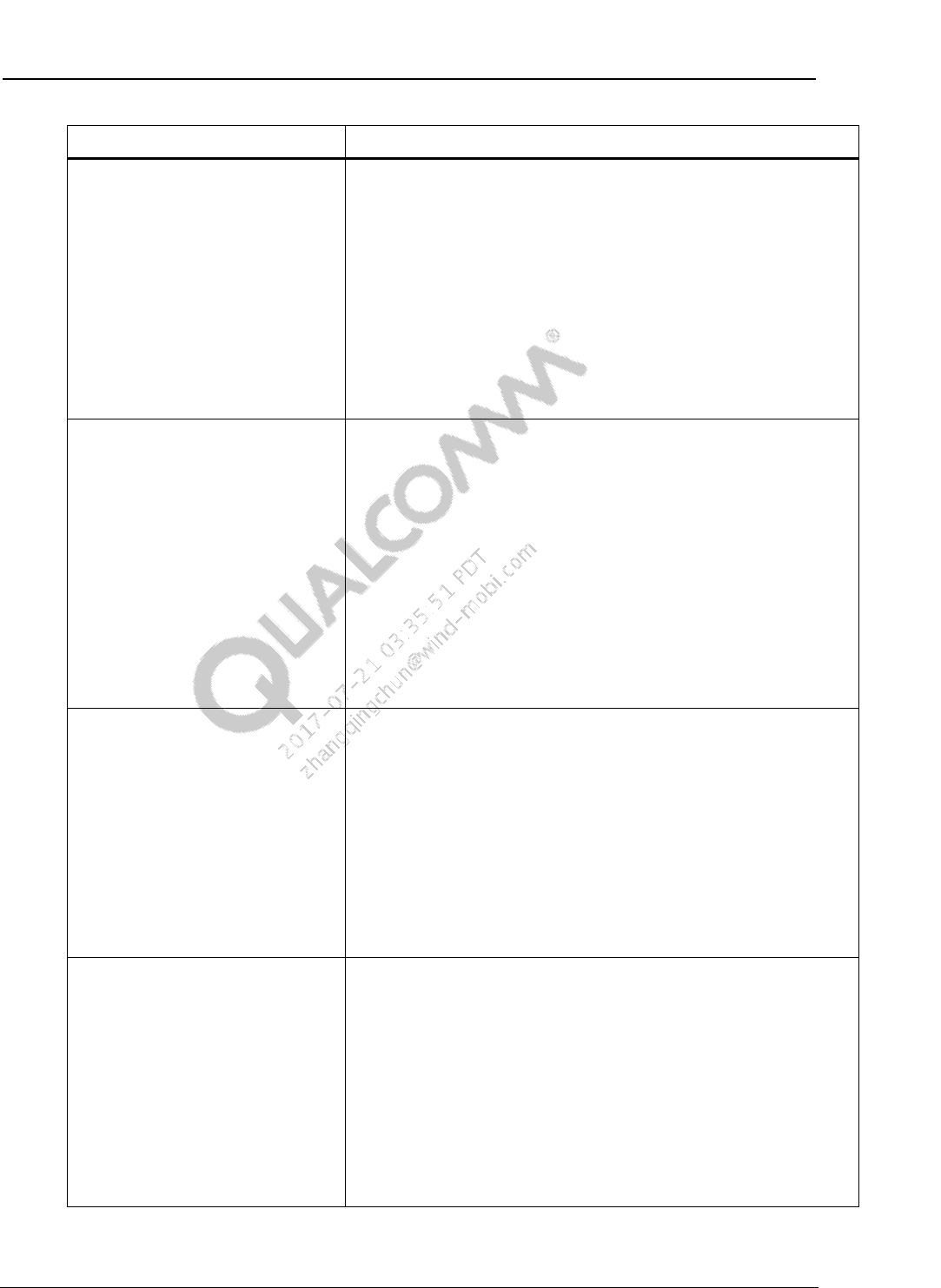

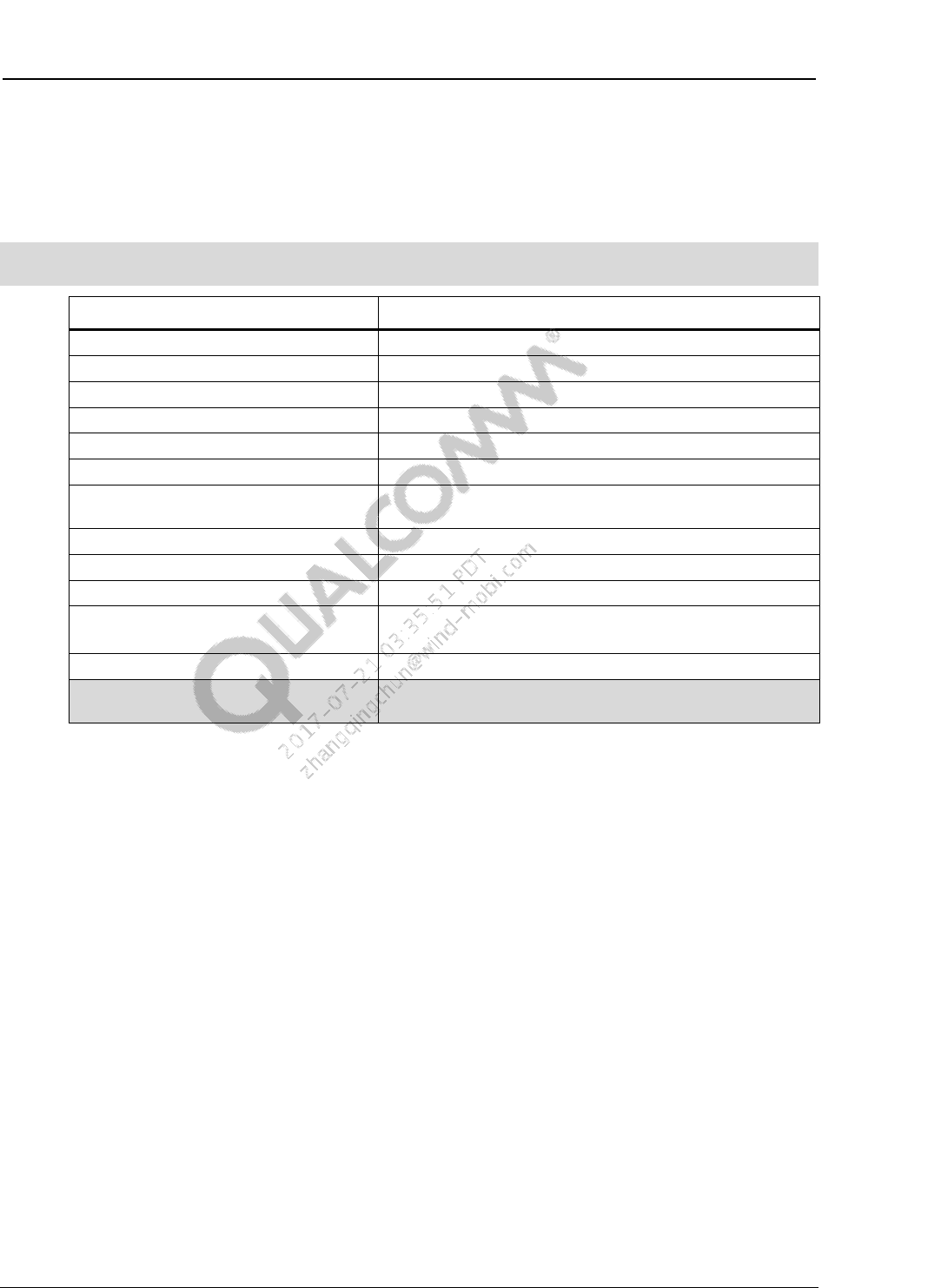

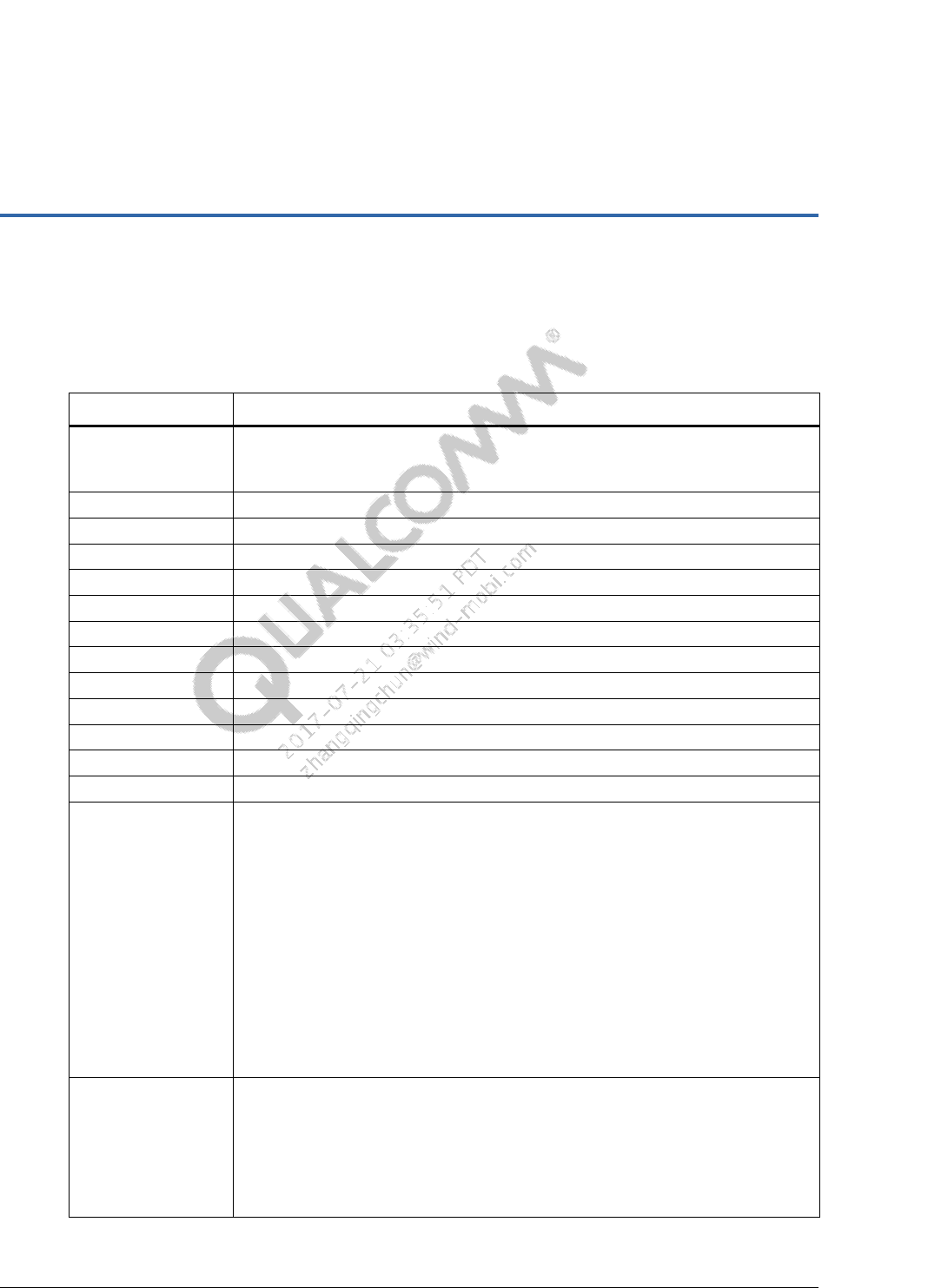

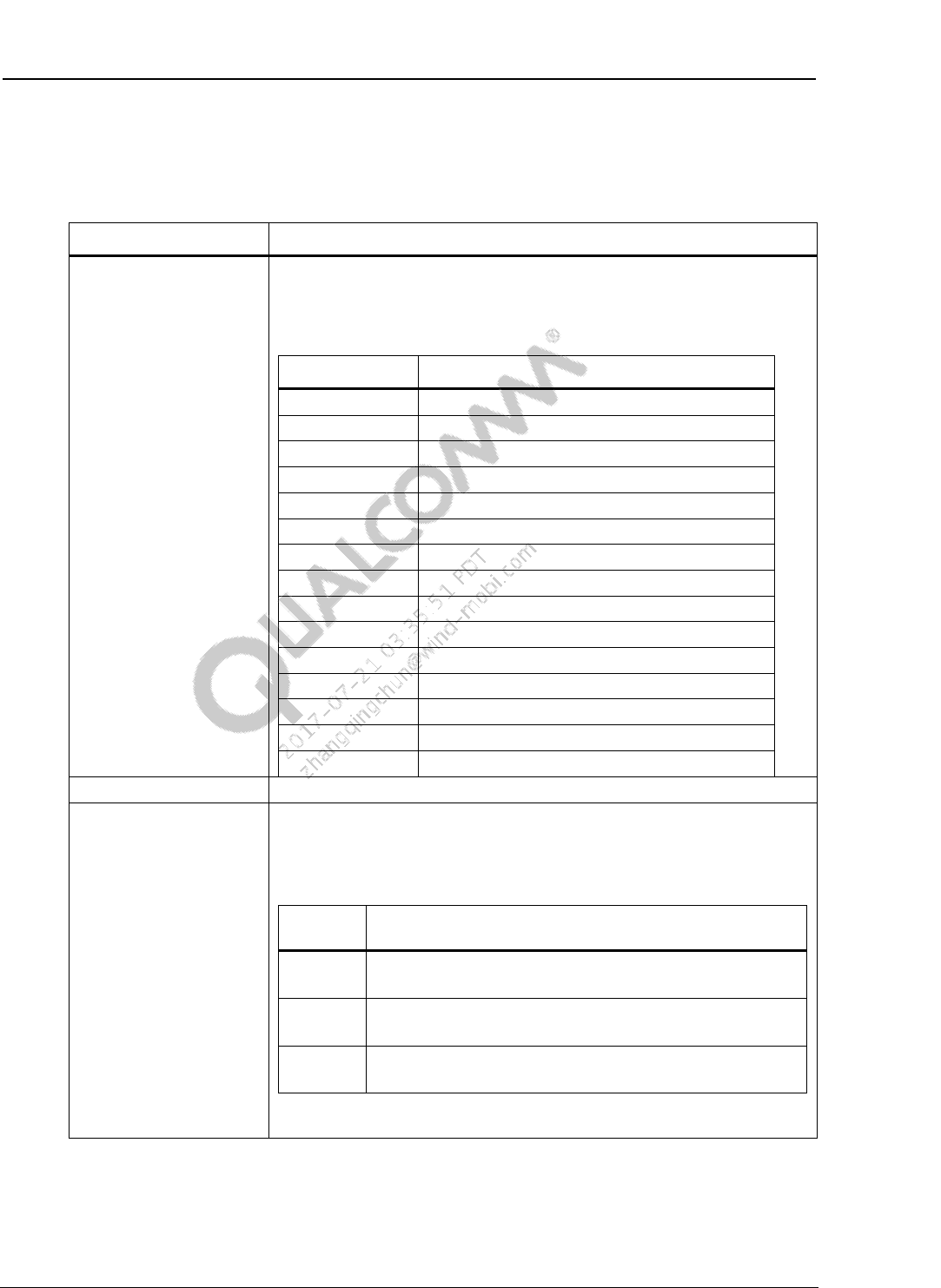

4 Supported tag list

Table 4-1 provides a list of all of the currently supported panel configuration tags. This list is

subject to change.

Table 4-1 Supported tag list

NOTE: The following table has been updated.

Panel name Type

(size in bytes) Purpose Firmware

(UEFI)

supported

Graphics

KMD

supported

PanelName String(13) EDID reporting No Yes

PanelDescription String (128) EDID reporting No Yes

ManufactureID Integer(2) EDID reporting No Yes

ProductCode Integer(2) EDID reporting No Yes

SerialNumber Integer(4) EDID reporting No Yes

WeekofManufacture Integer(1) EDID reporting No Yes

YearofManufacture Integer(1) EDID reporting No Yes

EDIDVersion Integer(1) EDID reporting No Yes

EDIDRevision Integer(1) EDID reporting No Yes

VideoInputDefinition Integer(1) EDID reporting No Yes

HorizontalScreenSize Integer(1) EDID reporting No Yes

VerticalScreenSize Integer(1) EDID reporting No Yes

DisplayTransferCharacteristics Integer(1) EDID reporting No Yes

FeatureSupport Integer(1) EDID reporting No Yes

Red.GreenBits Integer(1) EDID reporting No Yes

Blue.WhiteBits Integer(1) EDID reporting No Yes

RedX Integer(1) EDID reporting No Yes

RedY Integer(1) EDID reporting No Yes

GreenX Integer(1) EDID reporting No Yes

GreenY Integer(1) EDID reporting No Yes

BlueX Integer(1) EDID reporting No Yes

BlueY Integer(1) EDID reporting No Yes

WhiteX Integer(1) EDID reporting No Yes

WhiteY Integer(1) EDID reporting No Yes

EstablishedTimingsI Integer(1) EDID reporting No Yes

EstablishedTimingsII Integer(1) EDID reporting No Yes

ManufacturesTiming Integer(1) EDID reporting No Yes

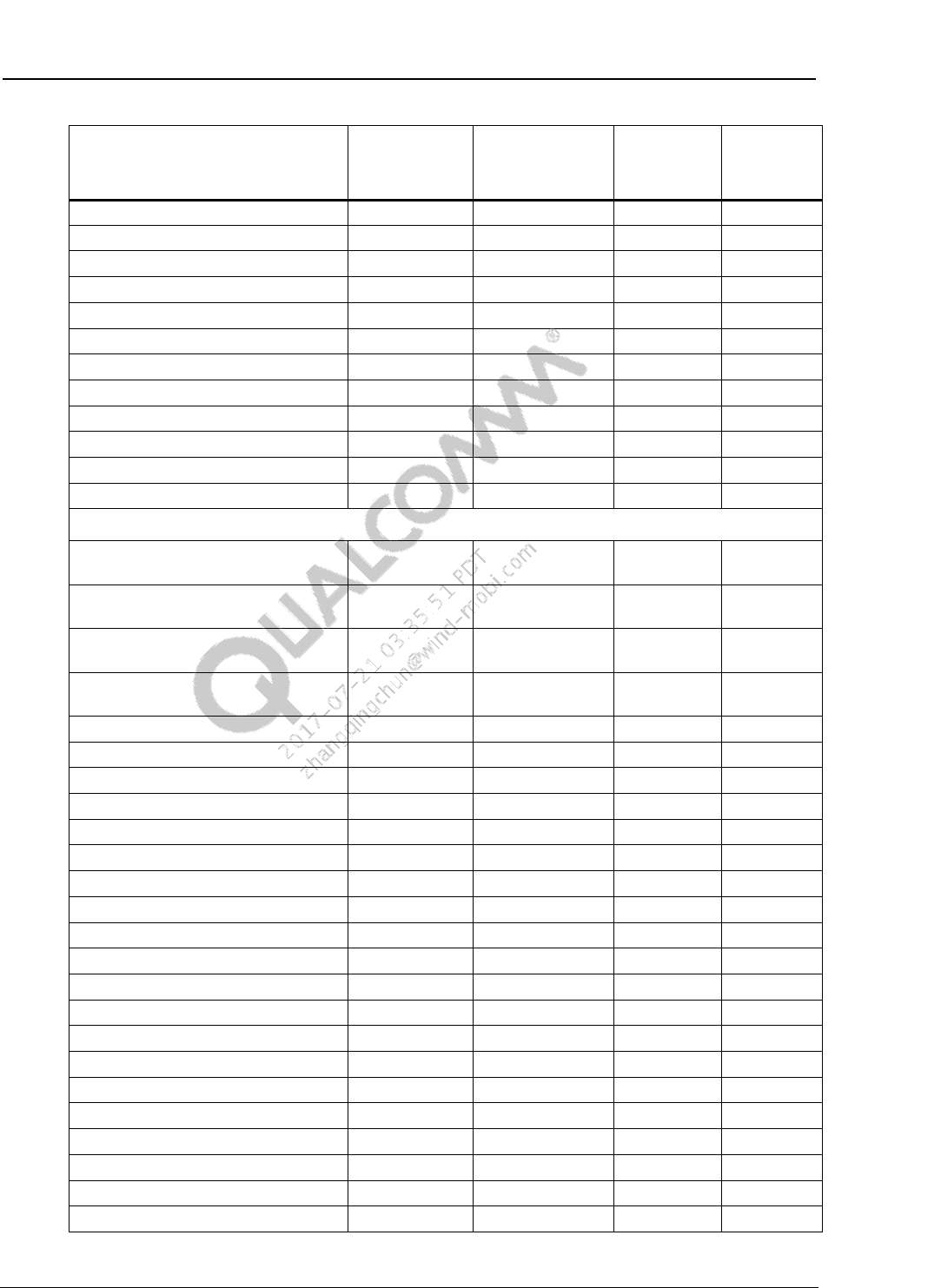

Configuration Guide for Display Drivers (ACPI and XML) Supported tag list

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 14

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

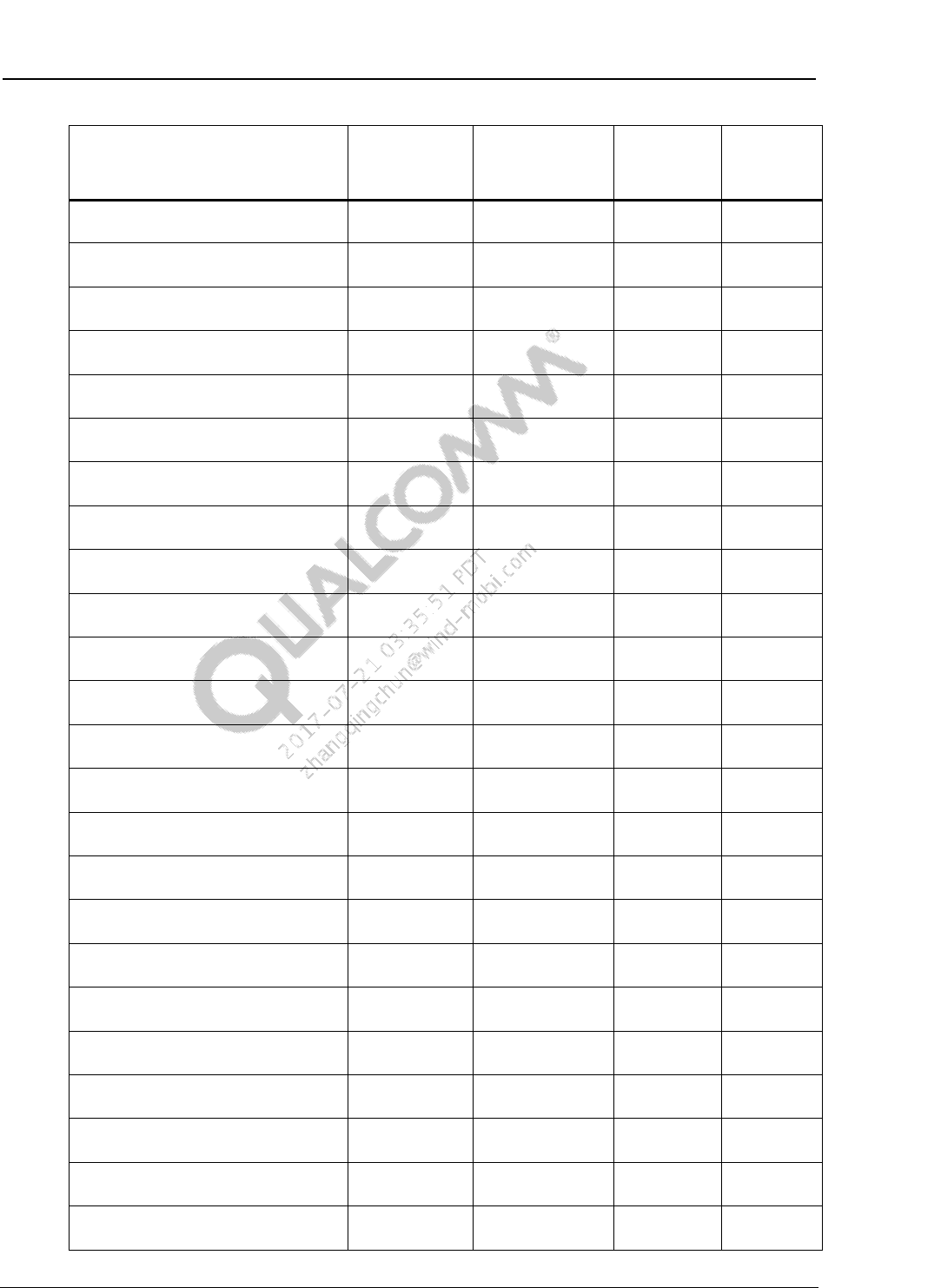

Panel name Type

(size in bytes) Purpose Firmware

(UEFI)

supported

Graphics

KMD

supported

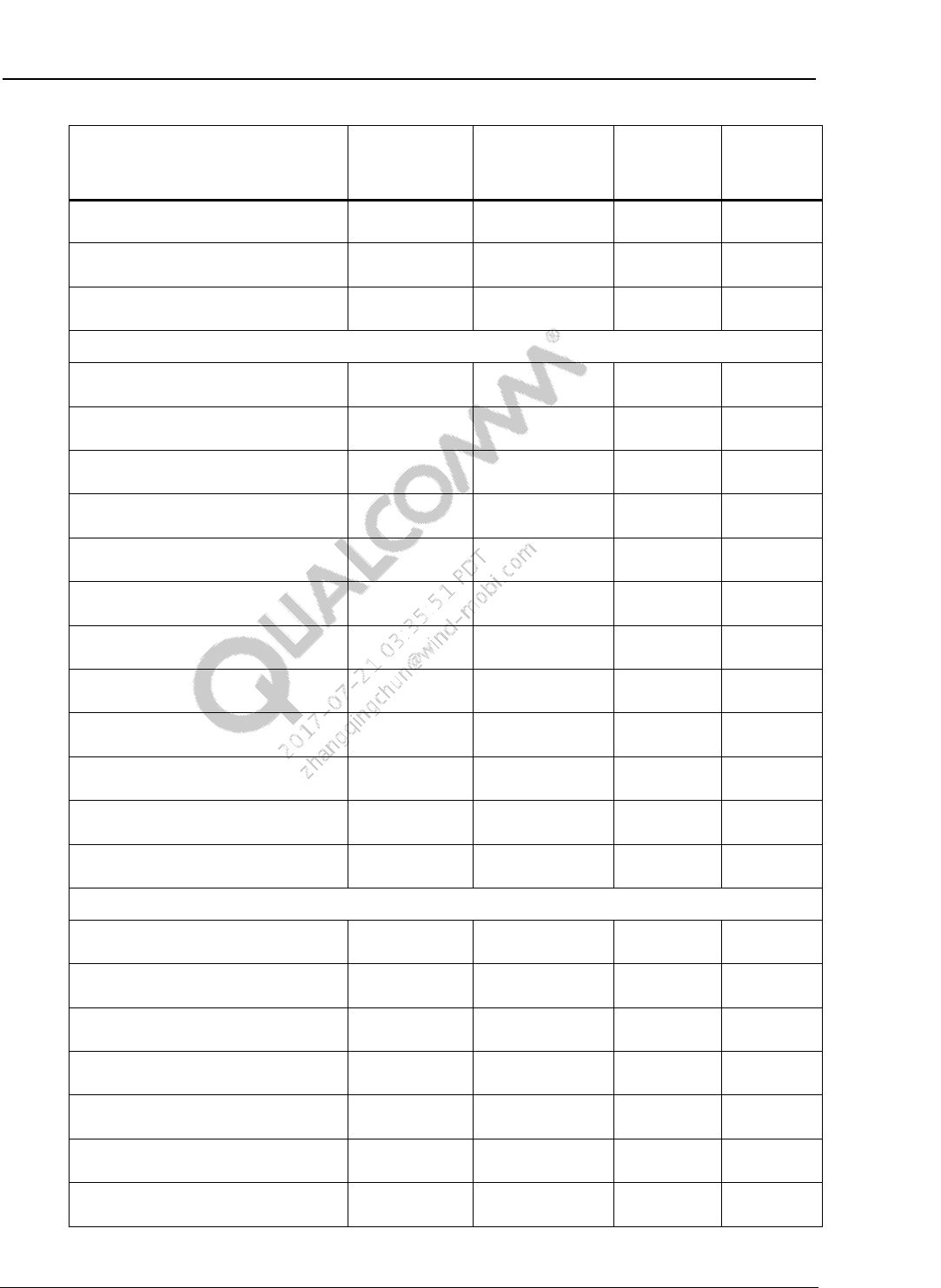

StandardTimings1 Integer(2) EDID reporting No Yes

StandardTimings2 Integer(2) EDID reporting No Yes

StandardTimings3 Integer(2) EDID reporting No Yes

StandardTimings4 Integer(2) EDID reporting No Yes

StandardTimings5 Integer(2) EDID reporting No Yes

StandardTimings6 Integer(2) EDID reporting No Yes

StandardTimings7 Integer(2) EDID reporting No Yes

StandardTimings8 Integer(2) EDID reporting No Yes

SignalTimingInterface Integer(1) EDID reporting No Yes

HorizontalScreenSizeMM Integer(1) EDID reporting No Yes

VerticalScreenSizeMM Integer(1) EDID reporting No Yes

HorizontalVerticalScreenSizeMM Integer(1) EDID reporting No Yes

Display Hardware Configuration

InterfaceType Integer(4) Display hardware

configuration Yes Yes

PanelOrientation Integer(4) Display hardware

configuration No No

InterfaceColorFormat Integer(4) Display hardware

configuration Yes Yes

ComponentOrdering Integer(4) Display hardware

configuration Yes Yes

PixelPacking Integer(4) Display hardware Yes Yes

PixelAlignment Integer(4) Configuration Yes Yes

HorizontalActive Integer(4) Configuration Yes Yes

HorizontalFrontPorch Integer(4) Display hardware Yes Yes

HorizontalBackPorch Integer(4) Configuration Yes Yes

HorizontalSyncPulse Integer(4) Display hardware Yes Yes

HorizontalSyncSkew Integer(4) Configuration Yes Yes

HorizontalLeftBorder Integer(4) Display hardware Yes Yes

HorizontalRightBorder Integer(4) Configuration Yes Yes

VerticalActive Integer(4) Display hardware Yes Yes

VerticalFrontPorch Integer(4) Configuration Yes Yes

VerticalBackPorch Integer(4) Display hardware Yes Yes

VerticalSyncPulse Integer(4) Configuration Yes Yes

VerticalTopBorder Integer(4) Display hardware Yes Yes

VerticalBottomBorder Integer(4) Configuration Yes Yes

InvertDataPolarity Boolean Display hardware Yes Yes

InvertVsyncPolairty Boolean Configuration Yes Yes

InvertHsyncPolarity Boolean Display hardware Yes Yes

BorderColor Integer(4) Configuration Yes Yes

UnderflowColor Integer(4) Configuration No Yes

Configuration Guide for Display Drivers (ACPI and XML) Supported tag list

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 15

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

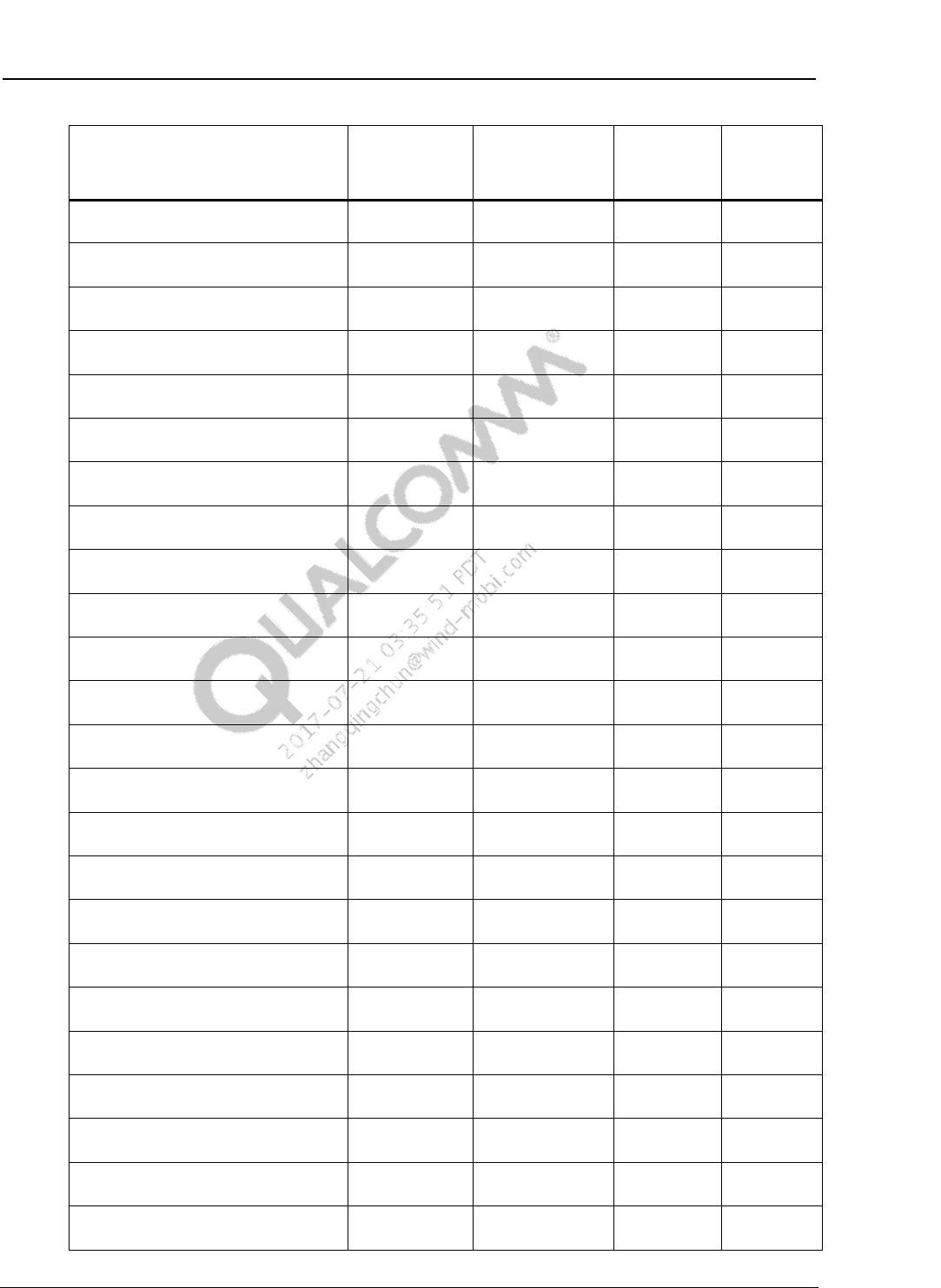

Panel name Type

(size in bytes) Purpose Firmware

(UEFI)

supported

Graphics

KMD

supported

DisplayPrimaryFlags Integer(4) Display

configuration No Yes

DisplayExternalFlags Integer(4) Display

configuration No Yes

ESDDetectionTime Integer(4) ESD detection

and recovery No Yes

ESDDetectionFailureRetry Integer(4) ESD detection

and recovery No Yes

DisplayRecoveryThreshold Integer(4) ESD detection

and recovery No Yes

DSI Hardware Configuration

DSIRefreshRate Integer(4) DSI hardware

configuration Yes Yes

DSIDynamicRefreshRates Integer list(16) DSI hardware

configuration No Yes

DSIBitClockFrequency Integer(4) DSI hardware

configuration Yes Yes

DSIDynamicBlankingRefreshRateList Integer list(16) DSI hardware

configuration No Yes

DSIDynamicVFrontPorchList Integer list(16) DSI hardware

configuration No Yes

DSIDynamicVBackPorchList Integer list(16) DSI hardware

configuration No Yes

DSIDynamicVSyncPulseList Integer list(16) DSI hardware

configuration No Yes

DSIDynamicHFrontPorchList Integer list(16) DSI hardware

configuration No Yes

DSIDynamicHBackPorchList Integer list(16) DSI hardware

configuration No Yes

DSIDynamicHSyncPulseList Integer list(16) DSI hardware

configuration No Yes

DSILanes Integer(4) DSI hardware

configuration Yes Yes

DSIChannelId Integer(4) DSI hardware

configuration Yes Yes

DSIVirtualId Integer(4) DSI hardware

configuration Yes Yes

DSIColorFormat Integer(4) DSI hardware

configuration Yes Yes

DSIPacketTransferHS Boolean DSI hardware

configuration Yes Yes

DSIClockHSForceRequest Integer(4) DSI hardware

configuration Yes Yes

DSIPixelXferTiming Integer(4) DSI hardware

configuration Yes Yes

DSIHostLaneMapping Integer(4) DSI hardware

configuration Yes Yes

Configuration Guide for Display Drivers (ACPI and XML) Supported tag list

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 16

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

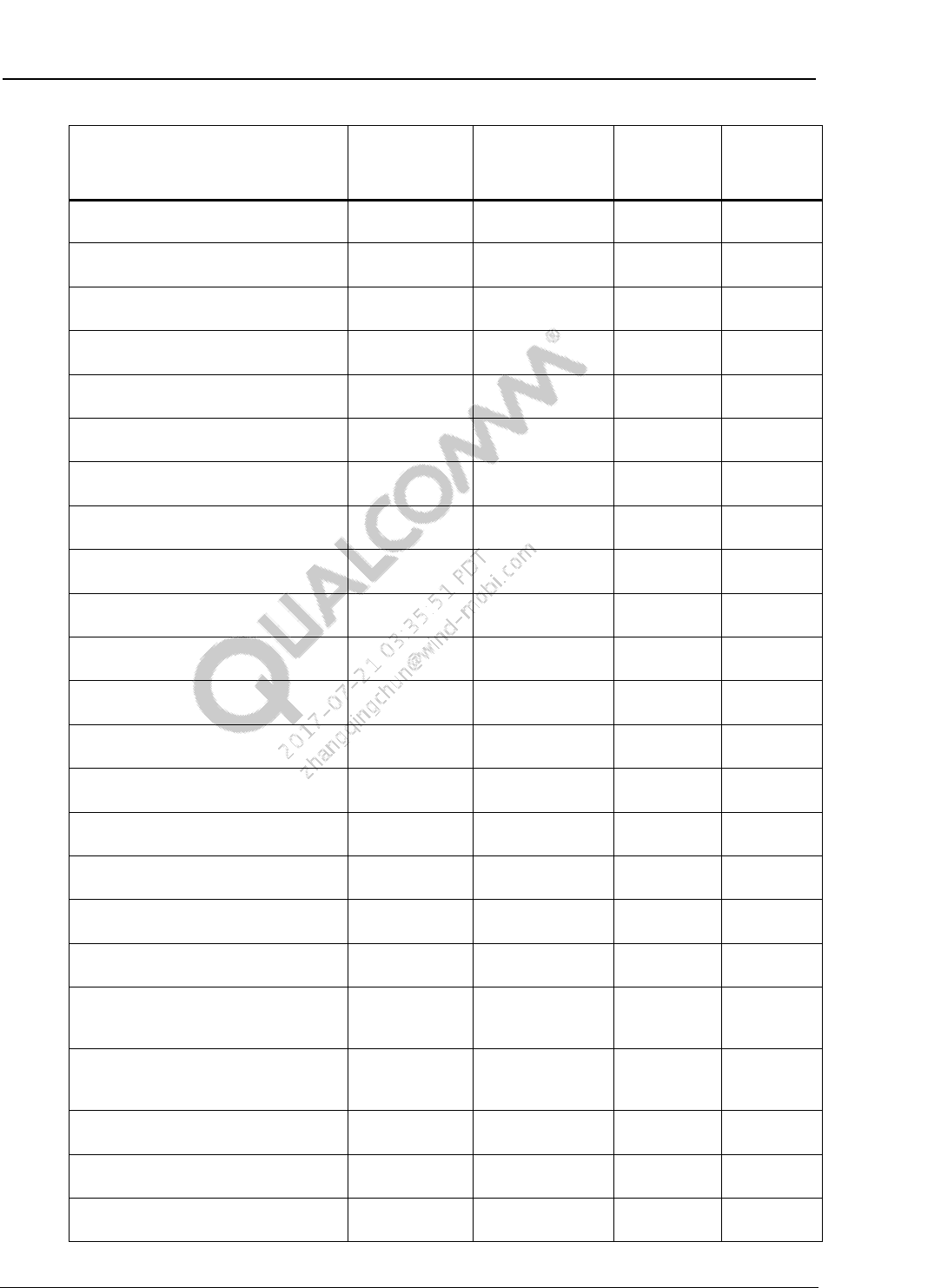

Panel name Type

(size in bytes) Purpose Firmware

(UEFI)

supported

Graphics

KMD

supported

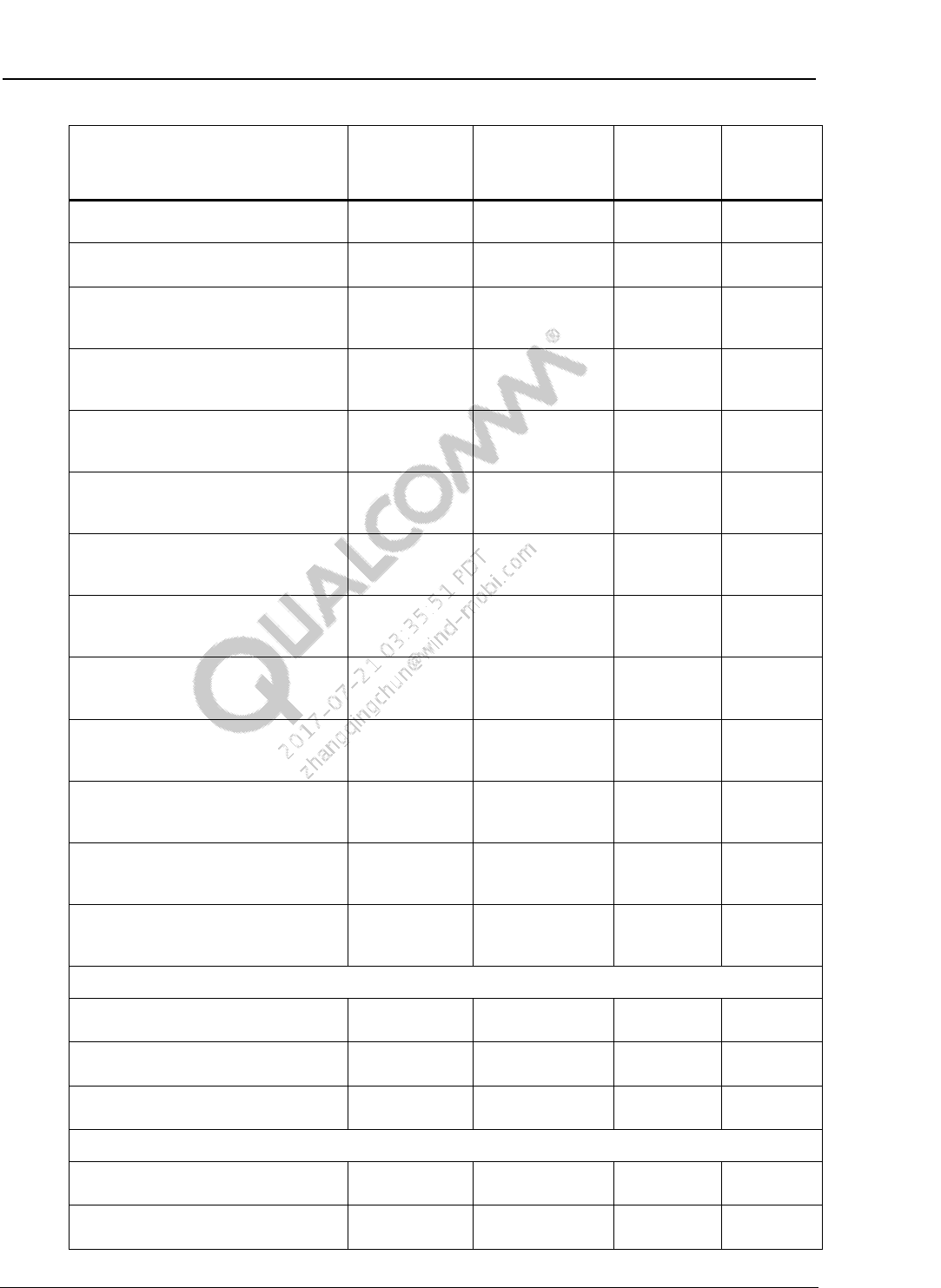

DSILP11AtInit Integer(4) DSI hardware

configuration Yes Yes

DSIPhyDCDCMode Boolean DSI hardware

configuration Yes Yes

DSIEnterULPSPowerDown Boolean DSI hardware

configuration Yes Yes

DSIBitClkScalePercent Integer(4) DSI hardware

configuration No Yes

DSIBitClkScalePercent Integer(4) DSI hardware

configuration No Yes

DSIEscapeClockDivisor Integer(4) DSI hardware

configuration Yes Yes

DSIEscapeClockFrequency Integer(4) DSI hardware

configuration Yes Yes

DSITimingHSZeroOverride Boolean DSI hardware

configuration Yes Yes

DSITimingHSZeroValue Integer(4) DSI hardware

configuration Yes Yes

DSITimingHSExitOverride Boolean DSI hardware

configuration Yes Yes

DSITimingHSExitValue Integer(4) DSI hardware

configuration Yes Yes

DSITimingHSPrepareOverride Boolean DSI hardware

configuration Yes Yes

DSITimingHSPrepareValue Integer(4) DSI hardware

configuration Yes Yes

DSITimingHSTrailOverride Boolean DSI hardware

configuration Yes Yes

DSITimingHSTrailValue Integer(4) DSI hardware

configuration Yes Yes

DSITimingHSRequestOverride Boolean DSI hardware

configuration Yes Yes

DSITimingHSRequestValue Integer(4) DSI hardware

configuration Yes Yes

DSITimingCLKZeroOverride Boolean DSI hardware

configuration Yes Yes

DSITimingCLKZeroValue Integer(4) DSI hardware

configuration Yes Yes

DSITimingCLKTrailOverride Boolean DSI hardware

configuration Yes Yes

DSITimingCLKTrailValue Integer(4) DSI hardware

configuration Yes Yes

DSITimingCLKPrepareOverride Boolean DSI hardware

configuration Yes Yes

DSITimingCLKPrepareValue Integer(4) DSI hardware

configuration Yes Yes

DSITimingCLKPreOverride Boolean DSI hardware

configuration Yes Yes

Configuration Guide for Display Drivers (ACPI and XML) Supported tag list

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 17

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Panel name Type

(size in bytes) Purpose Firmware

(UEFI)

supported

Graphics

KMD

supported

DSITimingCLKPreValue Integer(4) DSI hardware

configuration Yes Yes

DSITimingCLKPostOverride Boolean DSI hardware

configuration Yes Yes

DSITimingCLKPostValue Integer(4) DSI hardware

configuration Yes Yes

DSITimingTASureOverride Boolean DSI hardware

configuration Yes Yes

DSITimingTASureValue Integer(4) DSI hardware

configuration Yes Yes

DSITimingTAGoOverride Boolean DSI hardware

configuration Yes Yes

DSITimingTAGoValue Integer(4) DSI hardware

configuration Yes Yes

DSITimingTAGetOverride Boolean DSI hardware

configuration Yes Yes

DSITimingTAGetValue Integer(4) DSI hardware

configuration Yes Yes

DSITrafficMode Integer(4) DSI hardware

configuration Yes Yes

DSIHsaHseAfterVsVe Boolean DSI hardware

configuration Yes Yes

DSILowPowerModeInHFP Boolean DSI hardware

configuration Yes Yes

DSILowPowerModeInHBP Boolean DSI hardware

configuration Yes Yes

DSILowPowerModeInHSA Boolean DSI hardware

configuration Yes Yes

DSILowPowerModeInBLLPEOF Boolean DSI hardware

configuration Yes Yes

DSIForceCmdInVideoHS Boolean DSI hardware

configuration Yes Yes

DSILowPowerModeInBLLP Boolean DSI hardware

configuration Yes Yes

DSICMDSwapInterface Boolean DSI hardware

configuration Yes Yes

DSICMDUsingTrigger Boolean DSI hardware

configuration Yes Yes

DSITECheckEnable Boolean DSI hardware

configuration Yes Yes

DSITEUsingDedicatedTEPin Boolean DSI hardware

configuration Yes Yes

DSITEvSyncStartPos Integer(4) DSI hardware

configuration Yes Yes

DSITEvSyncContinueLines Integer(4) DSI hardware

configuration Yes Yes

DSITEvSyncStartLineDivisor Integer(4) DSI hardware

configuration Yes Yes

Configuration Guide for Display Drivers (ACPI and XML) Supported tag list

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 18

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Panel name Type

(size in bytes) Purpose Firmware

(UEFI)

supported

Graphics

KMD

supported

DSITEvSyncPosSafetyMargin Integer(4) DSI hardware

configuration Yes Yes

DSITEvSyncBelowSafetyMargin Integer(4) DSI hardware

configuration Yes Yes

DSITEPercentVariance Integer(4) DSI hardware

configuration Yes Yes

DSITEvSyncRdPtrIrqLine Integer(4) DSI hardware

configuration Yes Yes

DSIDataStrengthLP Integer(4) DSI hardware

configuration Yes Yes

DSIDataStrengthHS Integer(4) DSI hardware

configuration Yes Yes

DSIClockStrengthHS Integer(4) DSI hardware

configuration Yes Yes

DSIEnableAutoRefresh Boolean DSI hardware

configuration Yes No

DSIAutoRefreshFrameNumDiv Integer(4) DSI hardware

configuration Yes No

DSIPhyDCDCMode Boolean DSI hardware

configuration Yes Yes

DSIInitSequence Binary DSI panel

configuration Yes Yes

DSITermSequence Binary DSI panel

configuration No Yes

DSIStatusSequence Binary DSI panel status

check No Yes

DSIDisableEoTAfterHSXfer Boolean DSI hardware

configuration Yes Yes

DSIInitMasterTime Integer(4) DSI hardware

configuration Yes Yes

DSIDmaDelayAfterVsync Integer(4) DSI DMA

scheduling No Yes

DSITEvSyncSelect Integer(4) DSI hardware

configuration Yes Yes

DSICmdModeIdleTime Integer(4) DSI hardware

configuration Yes Yes

DSIFBCEnable Boolean Display/DSI

hardware

configuration

Yes Yes

DSIFBCProfileID Integer(4) Display/DSI

hardware

configuration

Yes Yes

DSIControllerMapping Integer List(16) DSI hardware

configuration Yes Yes

DSISlaveControllerSkewLines Integer(4) DSI hardware

configuration Yes Yes

DSITransferRetryCntr Integer(4) DSI hardware

configuration Yes Yes

Configuration Guide for Display Drivers (ACPI and XML) Supported tag list

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 19

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Panel name Type

(size in bytes) Purpose Firmware

(UEFI)

supported

Graphics

KMD

supported

DSINullpacketInsertionBytes Integer(4) DSI hardware

configuration Yes Yes

DSIFlags Integer(4) DSI hardware

configuration Yes Yes

DSIDSCEnable Boolean DSI hardware

configuration Yes Yes

DSIDSCProfileId Integer(4) DSI hardware

configuration Yes Yes

DSIDSCSliceHeight Integer(4) DSI hardware

configuration Yes Yes

DSIDSCSliceWidth Integer(4) DSI hardware

configuration Yes Yes

DSIDSCMajorVersion Integer(4) DSI hardware

configuration Yes Yes

DSIDSCMinorVersion Integer(4) DSI hardware

configuration Yes Yes

DSIDSCScrVersion Integer(4) DSI hardware

configuration Yes Yes

eDP Configuration

EDPRefreshRate Integer(4) eDP hardware

configuration Yes Yes

EDPTraining Integer(4) eDP hardware

configuration Yes Yes

EDPPixelClockFrequency Integer(4) eDP hardware

configuration Yes Yes

EDPDPCDRead Boolean eDP hardware

configuration Yes Yes

EDPEDIDRead Boolean eDP hardware

configuration Yes Yes

EDPNumberOfLanes Integer(4) eDP hardware

configuration Yes Yes

EDPLinkRate Integer(4) eDP hardware

configuration Yes Yes

EDPASSREnable Boolean eDP hardware

configuration Yes Yes

EDPEnhancedFrameEnable Boolean eDP hardware

configuration Yes Yes

EDPMaxLinkRate Integer(4) eDP hardware

configuration Yes Yes

EDPRGBMap Integer(4) eDP hardware

configuration Yes Yes

EDPLaneMap Integer(4) eDP hardware

configuration Yes Yes

EDPHPDActiveLow Boolean eDP hardware

configuration Yes Yes

EDPDynamicRefreshRates Integer List eDP hardware

configuration No Yes

Configuration Guide for Display Drivers (ACPI and XML) Supported tag list

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 20

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Panel name Type

(size in bytes) Purpose Firmware

(UEFI)

supported

Graphics

KMD

supported

EDPStatusSequence Binary eDP panel status

check No Yes

EDPPowerUpWaitInMs Integer(4) eDP hardware

configuration Yes Yes

EDPMaxAuxRetry Integer(4) eDP hardware

configuration Yes Yes

HDMI Configuration

HDMIAviInfoFramePacketsDisable Boolean HDMI hardware

configuration No Yes

HDMIOutVoltageSwingCtrlEnable Boolean HDMI hardware

configuration No Yes

HDMIOutVoltageSwingCtrl Integer(4) HDMI hardware

configuration No Yes

HDMIMaxNumReAuthentication Integer(4) HDMI hardware

configuration No Yes

HDMIMaxModeWidth Integer(4) HDMI hardware

configuration No Yes

HDMIMaxModeHeight Integer(4) HDMI hardware

configuration No Yes

HDMIMaxModeRefreshRate Integer(4) HDMI hardware

configuration No Yes

HDMIMinModeWidth Integer(4) HDMI hardware

configuration No Yes

HDMIMinModeHeight Integer(4) HDMI hardware

configuration No Yes

HDMIMinModeRefreshRate Integer(4) HDMI hardware

configuration No Yes

HDMIInjectedModeList Integer List HDMI hardware

configuration No Yes

HDMIDDCTimeoutInMs Integer(4) HDMI hardware

configuration No Yes

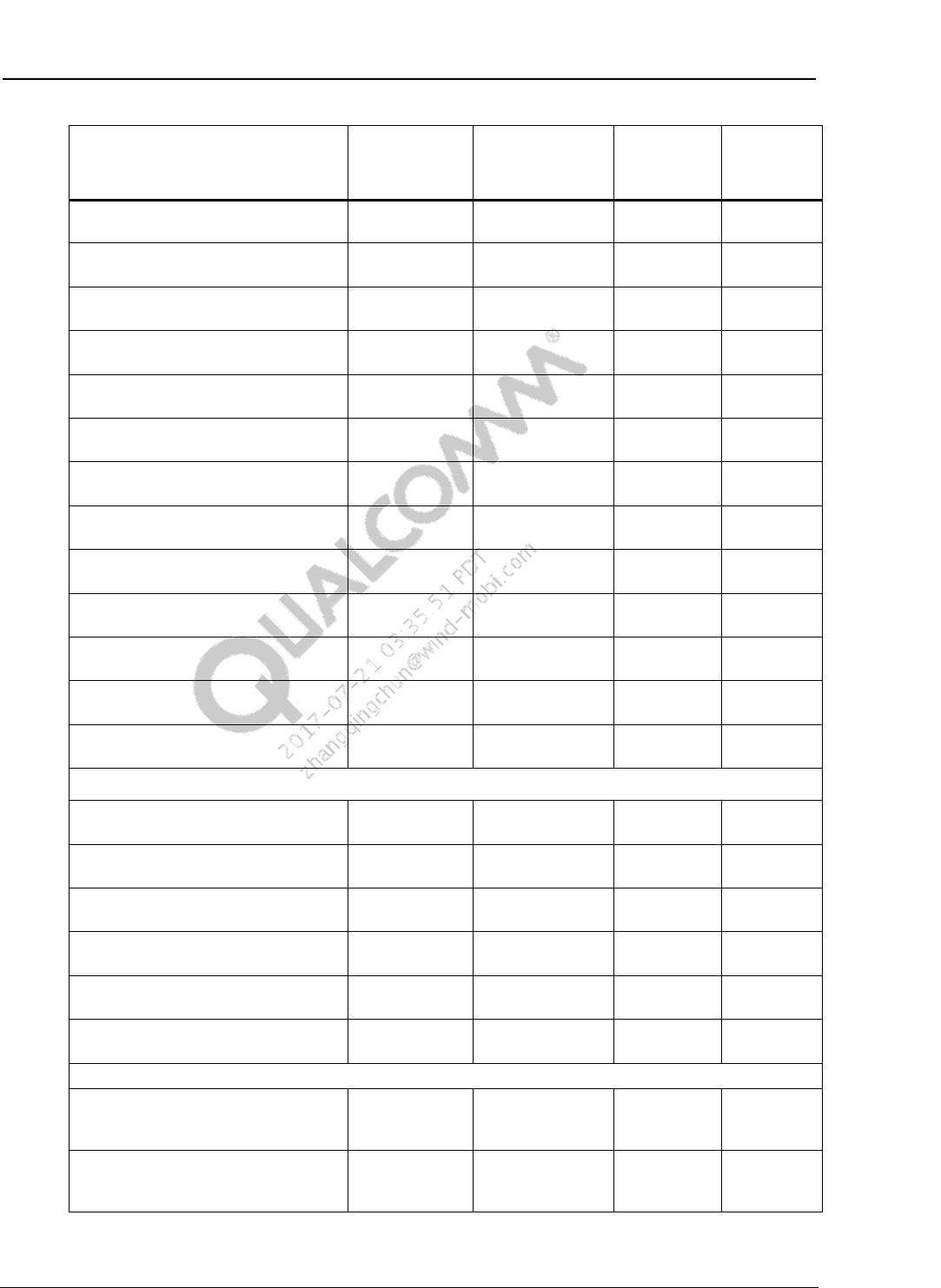

Backlight Configuration

BacklightType Integer(4) Backlight

configuration No Yes

BacklightPmicModel Integer(4) Backlight

configuration No Yes

BacklightPMICNum Integer(4) Backlight

configuration No Yes

BacklightPmicControlType Integer(4) Backlight

configuration No Yes

BacklightPMICBankSelect Integer(4) Backlight

configuration No Yes

BacklightPMICPWMFrequency Integer(4) Backlight

configuration No Yes

BacklightSteps Integer(4) Backlight

configuration No Yes

Configuration Guide for Display Drivers (ACPI and XML) Supported tag list

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 21

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Panel name Type

(size in bytes) Purpose Firmware

(UEFI)

supported

Graphics

KMD

supported

BacklightDefault Integer(4) Backlight

configuration No Yes

BacklightLowPower Integer(4) Backlight

configuration No Yes

BacklightPmicAdvancedConfig Boolean Advance WLED

backlight

configuration

No Yes

BacklightPmicWledInternalModResol

ution Integer(4) Advance WLED

backlight

configuration

No Yes

BacklightPmicWledModulationClkSel Integer(4) Advance WLED

backlight

configuration

No Yes

BacklightPmicWledDimmingMethod Integer(4) Advance WLED

backlight

configuration

No Yes

BacklightPmicWledOvp Integer(4) Advance WLED

backlight

configuration

No Yes

BacklightPmicWledIlim Integer(4) Advance WLED

backlight

configuration

No Yes

BacklightPmicWledFeedbackCtrl Integer(4) Advance WLED

backlight

configuration

No Yes

BacklightPmicWlepLoopCompRes Integer(4) Advance WLED

backlight

configuration

No Yes

BacklightPmicWledVrefControl Integer(4) Advance WLED

backlight

configuration

No Yes

BacklightPmicWledFullScaleCurrent Integer(4) Advance WLED

backlight

configuration

No Yes

BacklightPmicWledModulatorSrcSel Integer(4) Advance WLED

backlight

configuration

No Yes

CABL Configuration

CABLMinUserLevel Integer(4) CABL

configuration No Yes

CABLMinBacklightLevel Integer(4) CABL

configuration No Yes

CABLFilterThreshold Integer(4) CABL

configuration No Yes

Platform Hardware Configuration

Display1Reset1Info String(64) Platform GPIO

configuration No Yes

Display1Power1Info String(64) Platform GPIO

configuration No Yes

Configuration Guide for Display Drivers (ACPI and XML) Supported tag list

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 22

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Panel name Type

(size in bytes) Purpose Firmware

(UEFI)

supported

Graphics

KMD

supported

Display1Power2Info String(64) Platform GPIO

configuration No Yes

Display1Power3Info String(64) Platform GPIO

configuration No Yes

Display1I2C1Info String(64) Platform I2C

configuration No Yes

Display1I2C2Info String(64) Platform I2C

configuration No Yes

Display1Special1Info String(64) Platform GPIO

configuration No Yes

Display4Reset1Info String(64) Platform GPIO

configuration No Yes

Display4Power1Info String(64) Platform GPIO

configuration No Yes

Display4Power2Info String(64) Platform GPIO

configuration No Yes

Display4Power3Info String(64) Platform GPIO

configuration No Yes

Display4Special1Info String(64) Platform GPIO

configuration No Yes

PMIPowerPmicModel Integer(4) PMIC Power

configuration Yes Yes

PMIPowerPmicNum Integer(4) PMIC Power

configuration Yes Yes

PMIPowerConfig Integer(4) PMIC Power

configuration Yes Yes

Dynamic EDID Configuration

DynamicEDIDEnabled Boolean Dynamic EDID

configuration Yes Yes

DynamicEDIDI2CSlaveAddress Integer(4) Dynamic EDID

configuration Yes No

DynamicEDIDI2CFrequency Integer(4) Dynamic EDID

configuration Yes No

DynamicEDIDI2CGSBIPort Integer(4) Dynamic EDID

configuration Yes No

DynamicEDIDPTM Integer(4) Dynamic EDID

configuration Yes Yes

DynamicEDIDStartAddress Integer(4) Dynamic EDID

configuration Yes Yes

Adaptive Brightness

AdaptiveBrightnessFeature Integer(4) Adaptive

brightness

configuration

No Yes

CABLEnable Boolean Adaptive

brightness

configuration

No Yes

Configuration Guide for Display Drivers (ACPI and XML) Supported tag list

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 23

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Panel name Type

(size in bytes) Purpose Firmware

(UEFI)

supported

Graphics

KMD

supported

SVIEnable Boolean Adaptive

brightness

configuration

No Yes

Assertive Display (AD)

ADEnable Boolean AD configuration No Yes

ADMaxIterations Integer(4) AD configuration No Yes

ADStrengthLimit Integer(4) AD configuration No Yes

ADBacklightMin Integer(4) AD configuration No Yes

ADBacklightMax Integer(4) AD configuration No Yes

ADAmbientLightMin Integer(4) AD configuration No Yes

ADCalibrationA Integer(4) AD configuration No Yes

ADCalibrationB Integer(4) AD configuration No Yes

ADCalibrationC Integer(4) AD configuration No Yes

ADCalibrationD Integer(4) AD configuration No Yes

ADFilterA Integer(4) AD configuration No Yes

ADFilterB Integer(4) AD configuration No Yes

ADTFilterControl Integer(4) AD configuration No Yes

ADAssymetry Binary AD configuration No Yes

ADColorCorrection Binary AD configuration No Yes

ADSensorLinearization Binary AD configuration No Yes

ADPrivateData Binary AD configuration No Yes

Power saving configuration

DisplayPowerSavingOverride Integer(4) Power saving No Yes

Sharpening Configuration

SharpeningEdgeThreshold Integer(4) Sharpening No Yes

SharpeningSmoothThreshold Integer(4) Sharpening No Yes

SharpeningNoiseThreshold Integer(4) Sharpening No Yes

GPIO Configuration

TLMMGPIODefaultLow Integer list(8) GPIO

configuration Yes No

TLMMGPIODefaultHigh Integer list(8) GPIO

configuration Yes No

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 24

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

5 Panel configuration tag descriptions

5.1 Informational fields

The fields listed in Table 5-1 are used for informational purposes only. They are optional fields

that may or may not be parsed or used.

Table 5-1 Informational fields

Tag Description

PanelDescription Used for debugging purposes

5.2 EDID fields

The graphics KMD needs to report accurate EDID information about all monitors, internal and

external. For details, see VESA Enhanced Extended Display Identification Data – Implementation

Guide (Version 1.0 (June 2001)).

Only the first 128-byte block of the EDID is reported to the operating system. No extension

blocks are supported.

5.2.1 Static EDID fields

The following fields are statically defined in the panel configuration and reported as is to the

operating system as shown in Table 5-2. The OEM is responsible for populating these fields to

meet the panel definition.

Table 5-2 Static EDID fields

Tag EDID field

offset EDID field description

PanelName 58h Detailed timing #3 or display descriptor

ProductCode 0Ah ID product code

SerialNumber 0Ch ID serial number

WeekofManufacture 10h Week of manufacture

YearofManufacture 11h Year of manufacture

EDIDVersion 12h Version number

EDIDRevision 13h Revision number

VideoInputDefinition 14h Video input definition

HorizontalScreenSize 15h Horizontal screen size in cm of aspect ratio

VerticalScreenSize 16h Vertical screen size in cm of aspect ratio

DisplayTransferCharacteristics 17h Display transfer characteristics (gamma)

Configuration Guide for Display Drivers (ACPI and XML) Panel configuration tag descriptions

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 25

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Tag EDID field

offset EDID field description

FeatureSupport 18h Feature support

Red.GreenBits 19h Red/green low order bits

Blue.WhiteBits 1Ah Blue/white low order bits

RedX 1Bh Red-x high order bits

RedY 1Ch Red-y high order bits

GreenX 1Dh Green-x high order bits

GreenY 1Eh Green-y high order bits

BlueX 1Fh Blue-x high order bits

BlueY 20h Blue-y high order bits

WhiteX 21h White-x high order bits

WhiteY 22h White-y high order bits

EstablishedTimingsI 23h Established timings I

EstablishedTimingsII 24h Established timings I

ManufacturesTiming 25h Established timings I

StandardTimings1 26h Standard timing 1

StandardTimings2 28h Standard timing 2

StandardTimings3 2Ah Standard timing 3

StandardTimings4 2Ch Standard timing 4

StandardTimings5 2Eh Standard timing 5

StandardTimings6 30h Standard timing 6

StandardTimings7 32h Standard timing 7

StandardTimings8 34h Standard timing 8

5.2.2 Detailed timing fields

A single mode is populated in the detailed timing fields based on the EDID configuration given in

Table 5-3, which describes how fields can be overwritten from the detailed timing descriptors.

Table 5-3 Detailed timing fields

Tag Detailed timing

offset Detailed timing description

HorizontalScreenSizeMM 0Ch Horizontal addressable video image size in mm

(lower 8 bits)

VerticalScreenSizeMM 0Dh Vertical addressable video image size in mm

(lower 8 bits)

HorizontalVerticalScreenSizeMM 0Eh Vertical and horizontal upper 4 bits

Configuration Guide for Display Drivers (ACPI and XML) Panel configuration tag descriptions

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 26

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

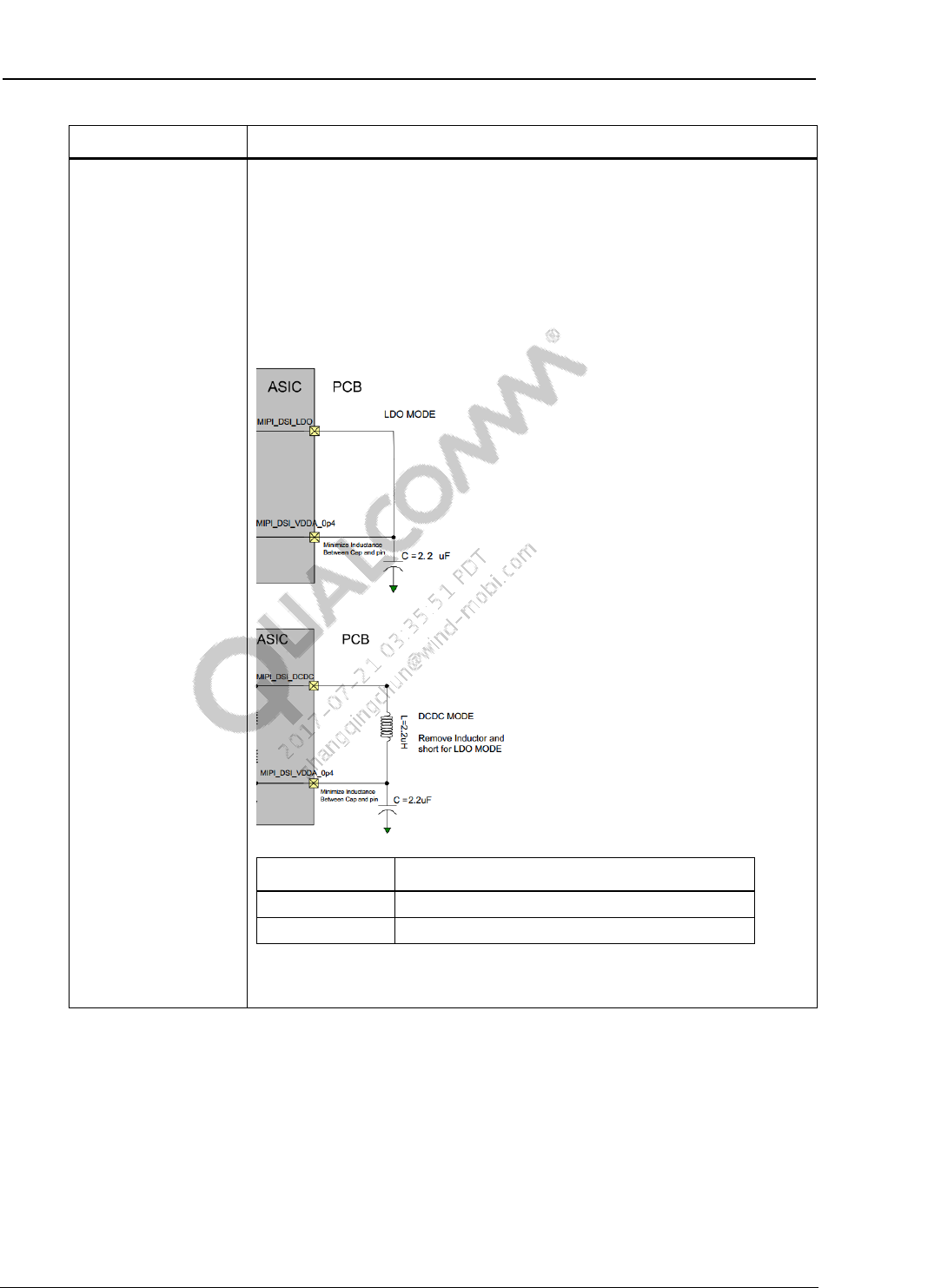

5.2.3 EDID information

Correct EDID information is important to the overall user experience. Inaccurate or invalid EDID

information could result in an overall unpleasant user experience. Specifically, screen dimensions

are important to the overall look and feel of the user interface.

The screen size in both cm and mm must be reported, e.g., if the phone dimensions are 5.8 cm

and 10.3 cm, as shown in Figure 5-1, the EDID would be populated as shown below.

<Group id='EDID Configuration'>

<HorizontalScreenSize>5</HorizontalScreenSize>

<VerticalScreenSize>10</VerticalScreenSize>

</Group>

<Group id='Detailed Timing'>

<HorizontalScreenSizeMM>58</HorizontalScreenSizeMM>

<VerticalScreenSizeMM>103</VerticalScreenSizeMM>

</Group

5.8cm

10.3cm

Figure 5-1 Example phone dimensions and EDID population

5.2.4 Dynamic EDID fields

Only the Preferred Timing mode (see Section 3.10.2 in VESA Enhanced Extended Display

Identification Data Standard ((Defines EDID Structure Version 1, Revision 4) Release A,

Revision 2 (September 2006)) is populated by the driver dynamically based on the panel

configuration. Table 5-4 describes how each field in the detailed timing definition is populated.

Table 5-4 Dynamic EDID fields

Detailed timing field name

Detailed timing

specification

field offset

(size in bytes)

Derived from

(panel configuration field)

Pixel clock/10000 0 (2) DSIRefreshRate/LVDSRefreshRate

Horizontal addressable video (low 8 bits) 2 (1) HorizontalActive

Horizontal blanking (low 8 bits) 3 (1) HorizontalFrontPorch+Horizontal

BackPorch+HorizontalSyncPulse

Horizontal addressable video (high 4 bits)/

Horizontal blanking (high 4 bits) 4 (1) Horizontal Active/Horizontal

FrontPorch+HorizontalBackPorch+

HorizontalSyncPulse

Vertical addressable video (lower 8 bits) 5 (1) VerticalActive

Vertical blanking (low 8 bits) 6 (1) VerticalFrontPorch+

VerticalBackPorch+ VerticalSyncPulse

Configuration Guide for Display Drivers (ACPI and XML) Panel configuration tag descriptions

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 27

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Detailed timing field name

Detailed timing

specification

field offset

(size in bytes)

Derived from

(panel configuration field)

Vertical addressable video (high 4 bits)/

Vertical blanking (high 4 bits) 7 (1) VerticalActive/VerticalFrontPorch+

VerticalBackPorch+ VerticalSyncPulse

Horizontal Front Porch (HFP) (lower

8 bits) 8 (1) VerticalFrontPorch

Horizontal sync pulse width (lower 8 bits) 9 (1) VerticalSyncPulse

Vertical front porch (high 4 bits)/vertical

sync pulse width (high 4 bits) 10 (1) VerticalFrontPorch/VerticalFrontPorch

HFP/ sync pulse/vertical front

porch/vertical sync pulse width (upper

2 bits)

11 (1) HorizontalFrontPorch/HorizontalSync

Pulse/VerticalFrontPorch/VerticalSync

Pulse

Horizontal addressable video image size

(lower 8 bits) 12 (1) HorizontalScreenSize

Vertical addressable video image size

(lower 8 bits) 13 (1) VerticalScreenSize

Horizontal addressable video size (upper

4 bits)/vertical addressable video size

(upper 4 bits)

14 (1) HorizontalActive/VerticalActive

Right/left horizontal border 15 (1) Used to determine the total active

window width

Top/bottom vertical border 16 (1) Used to determine the total active

window height

Signal interface type 17 (1) InvertHsyncPolarity

InvertVsyncPolairty

Configuration Guide for Display Drivers (ACPI and XML) Panel configuration tag descriptions

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 28

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

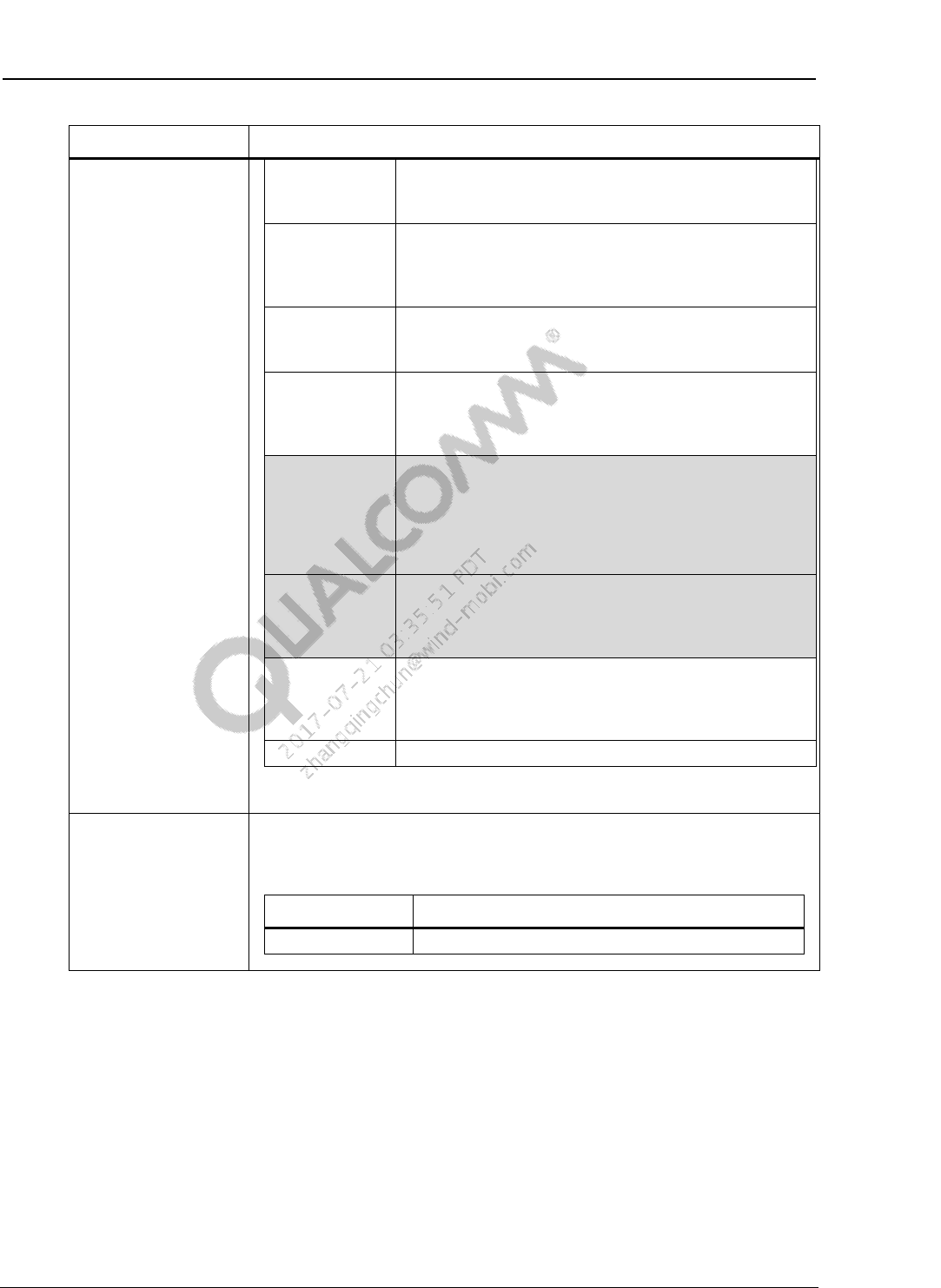

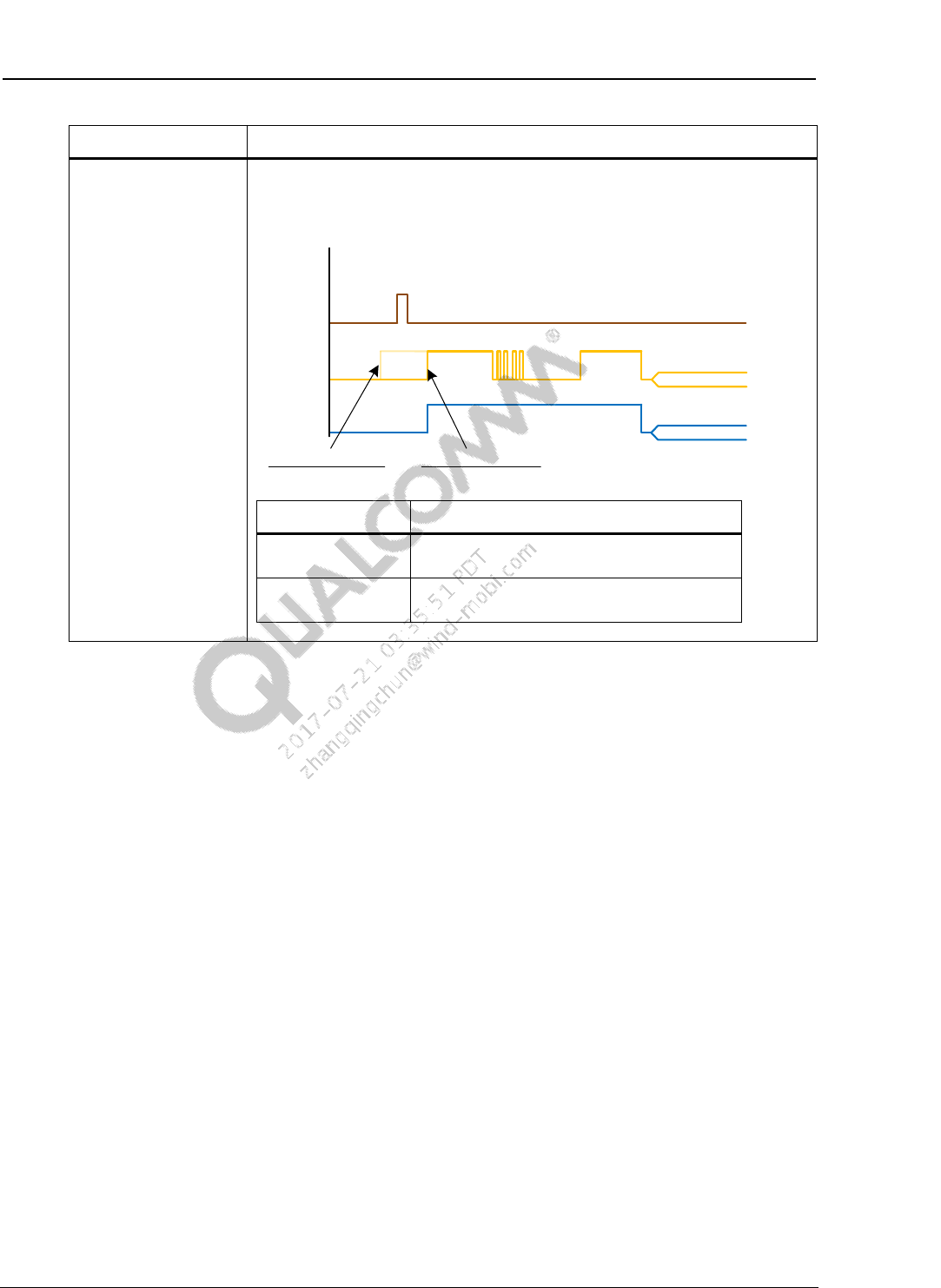

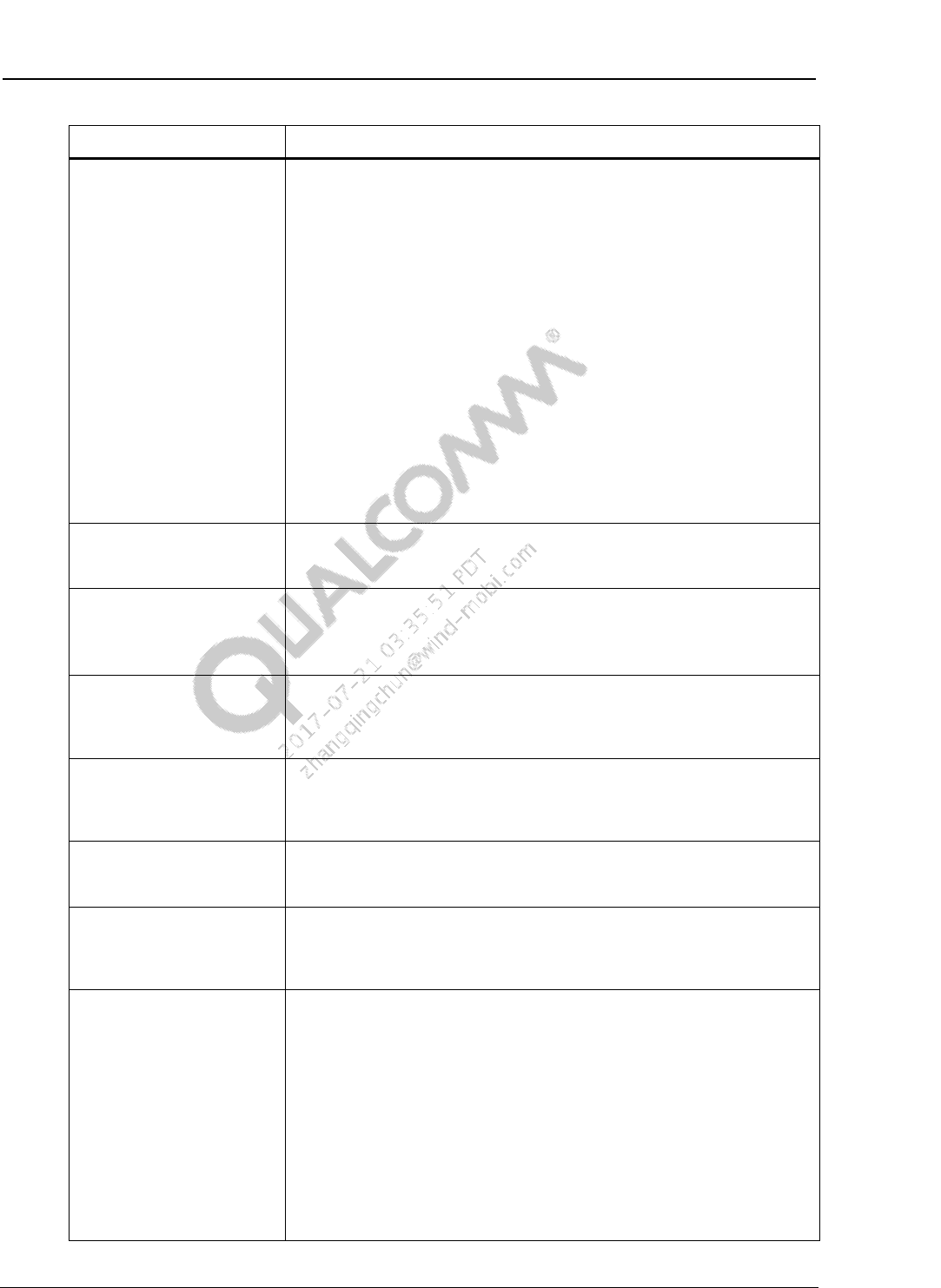

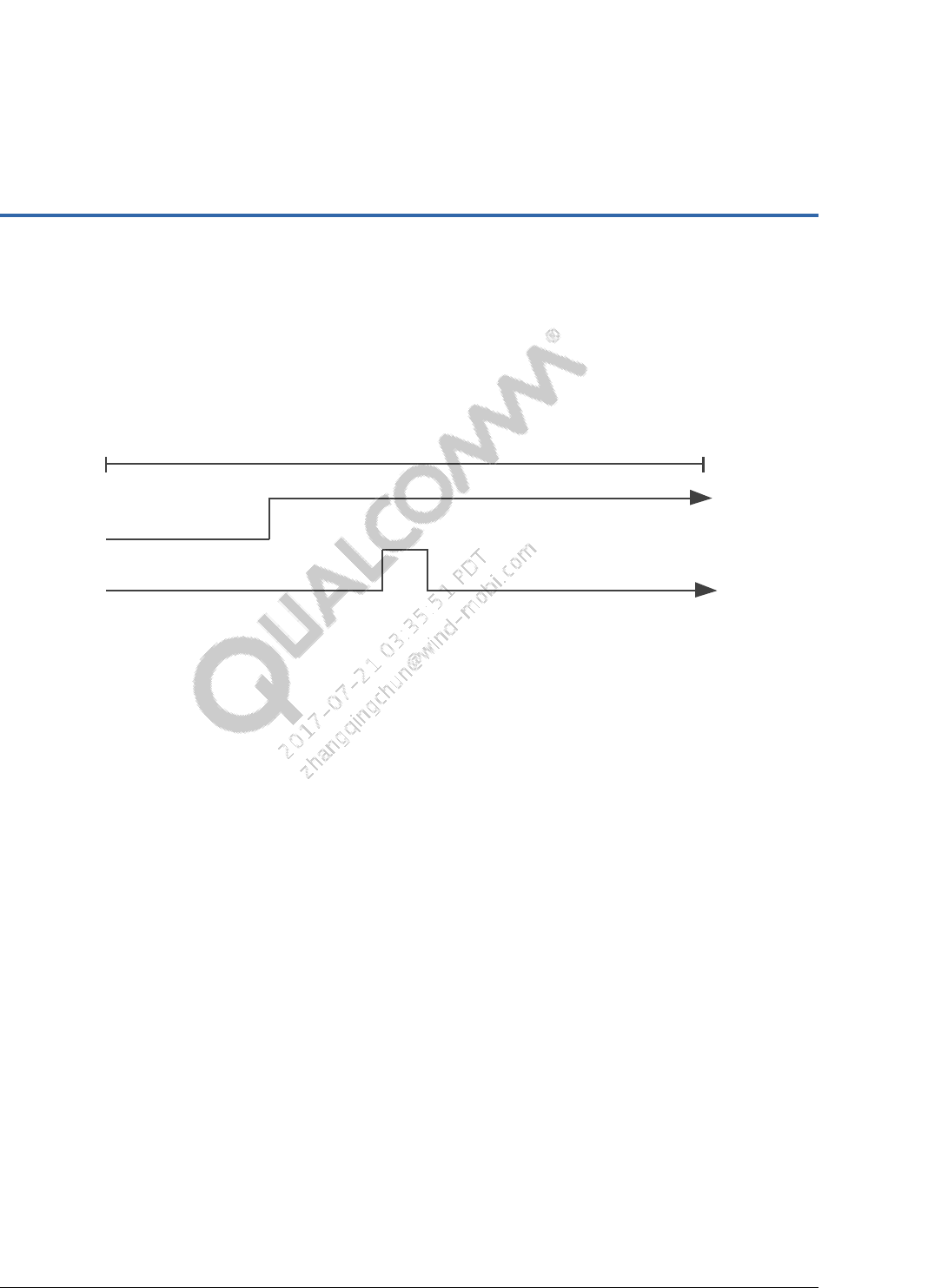

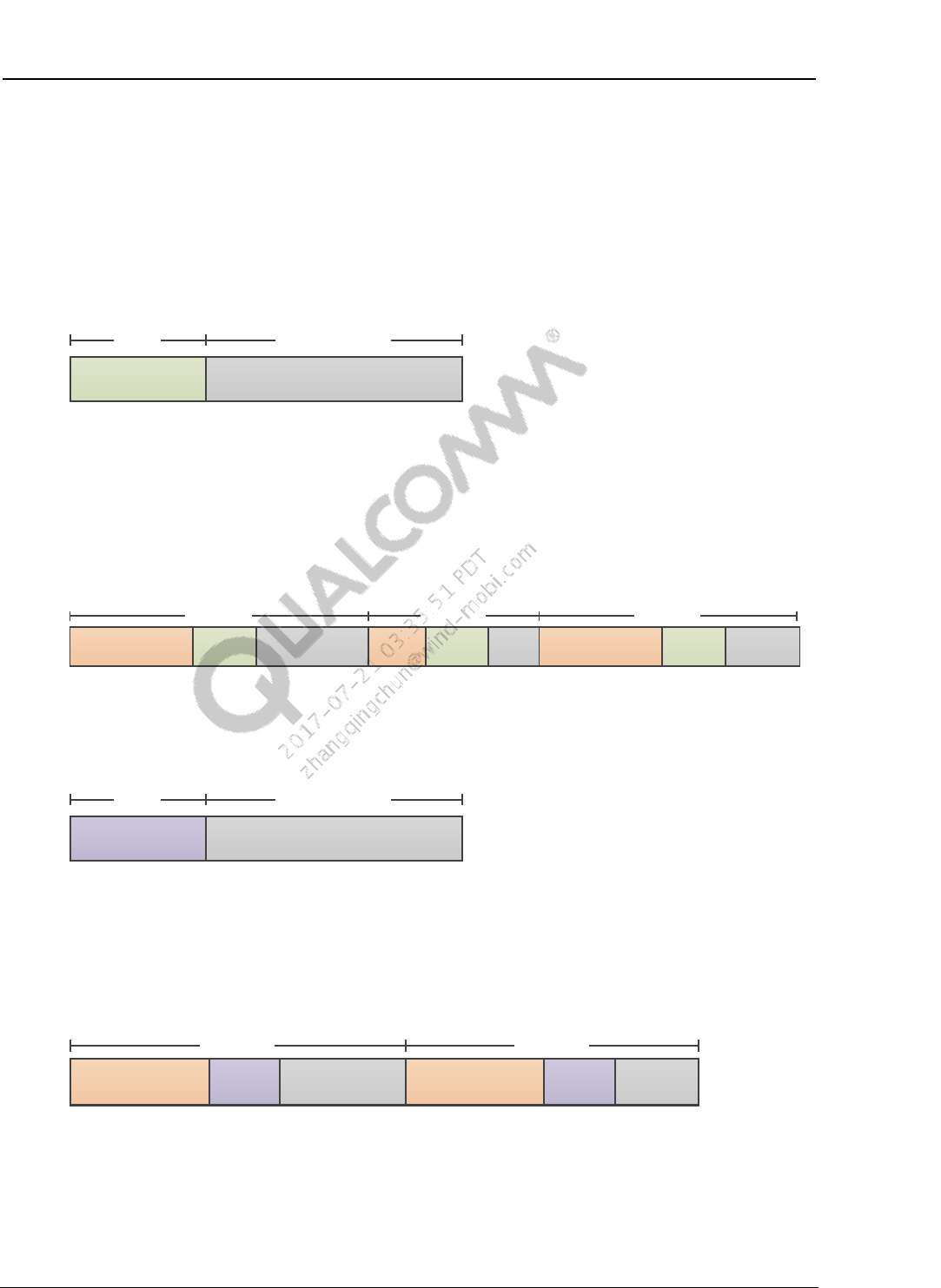

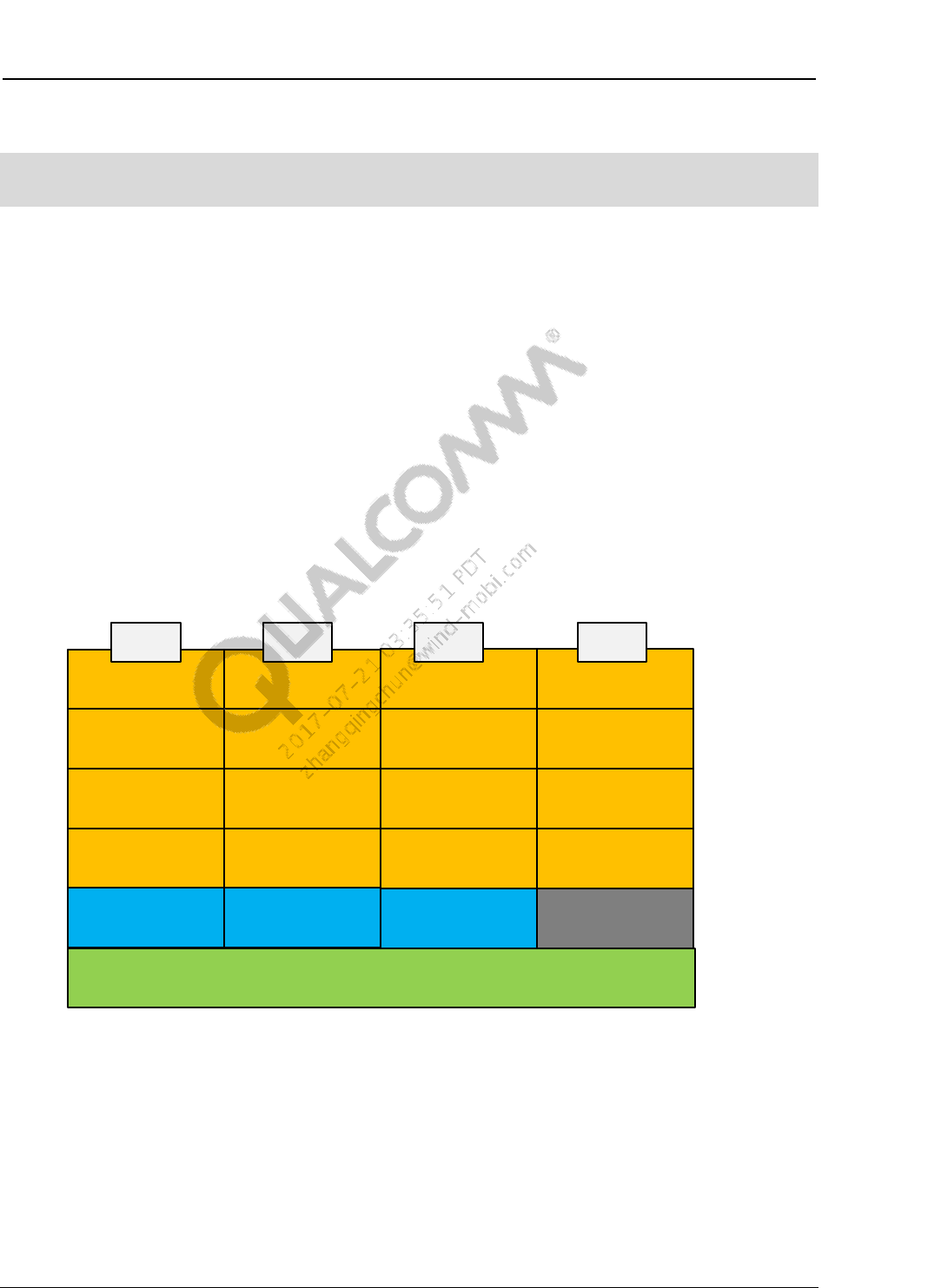

5.3 Panel timings configuration

All panel timings are derived from the following fields in the panel configuration as shown in

Figure 5-2. It is critical that the licensees populate these fields correctly to match their platform

configuration.

Border

Active Region

VerticalActive

VerticalTopBorder

VerticalBottomBorder

HorizontalLeftBorder

HorizontalRightBorder

Horizontal Blanking

Vertical Blanking

VerticalFrontPorch

VerticalSyncPulse

VerticalBackPorch

HorizontalActive

HorizontalFrontPorch

HorizontalSyncPulse

HorizontalBackPorch

Figure 5-2 Panel timings configuration

Table 5-5 lists the panel timing fields.

Table 5-5 Panel timing fields

Tag Units Notes

HorizontalActive Pixels –

HorizontalFrontPorch Pixels –

HorizontalBackPorch Pixels –

HorizontalSyncPulse Pixels –

HorizontalSyncSkew Pixels Not used

HorizontalLeftBorder Pixels Optional, if supported by hardware

HorizontalRightBorder Pixels Optional, if supported by hardware

VerticalActive Lines –

VerticalFrontPorch Lines –

Configuration Guide for Display Drivers (ACPI and XML) Panel configuration tag descriptions

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 29

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Tag Units Notes

VerticalBackPorch Lines –

VerticalSyncPulse Lines –

VerticalTopBorder Lines Optional, if supported by hardware

VerticalBottomBorder Lines Optional, if supported by hardware

InvertDataPolarity Boolean Inverts the data sync pulse polarity

InvertVsyncPolairty Boolean Inverts the vertical sync pulse polarity

InvertHsyncPolarity Boolean Inverts the horizontal sync pulse polarity

BorderColor ARGB8888 Defines the default border color when borders are

enabled

UnderflowColor ARGB8888 Defines the default color when underflow occurs

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 30

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

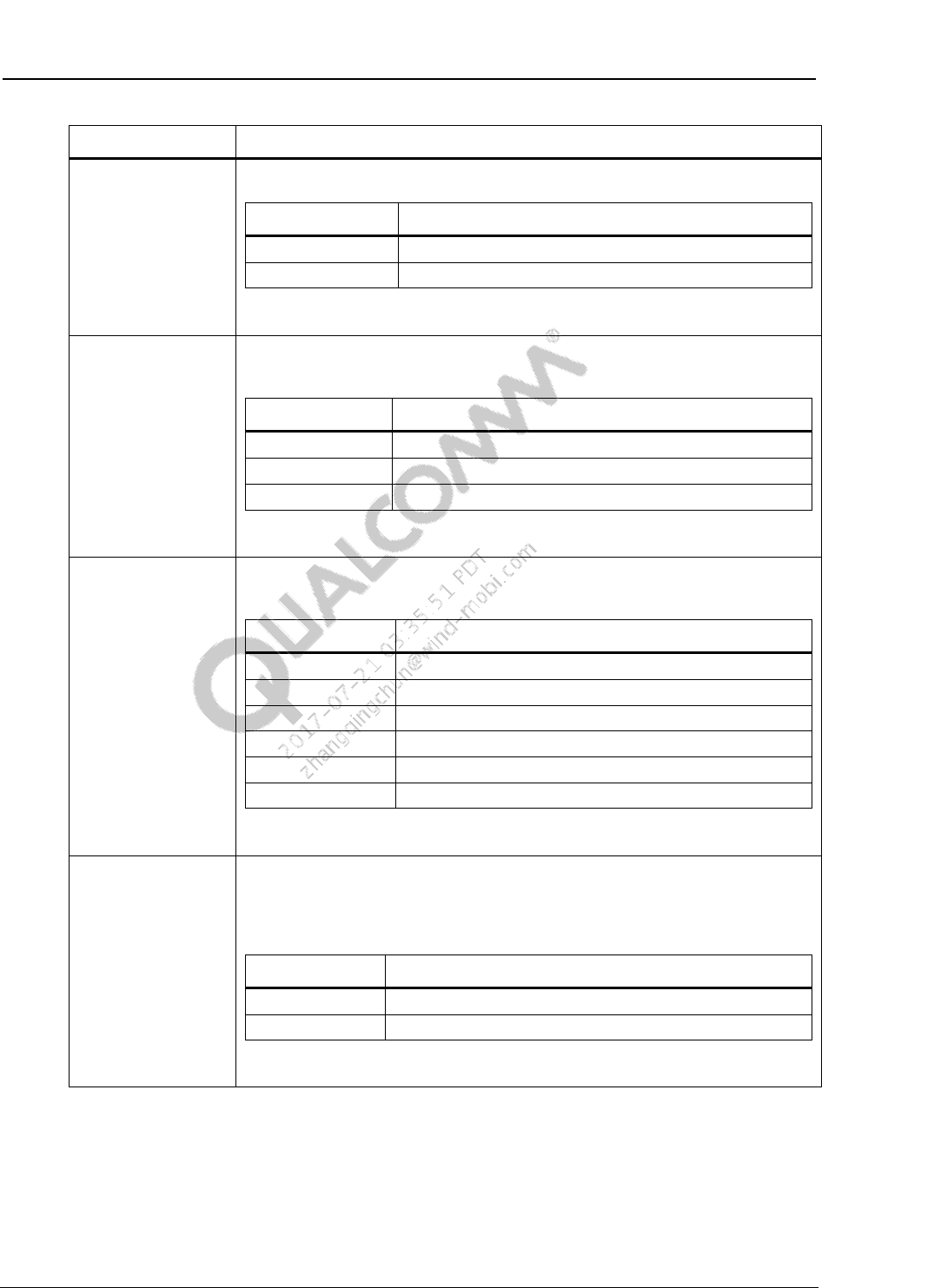

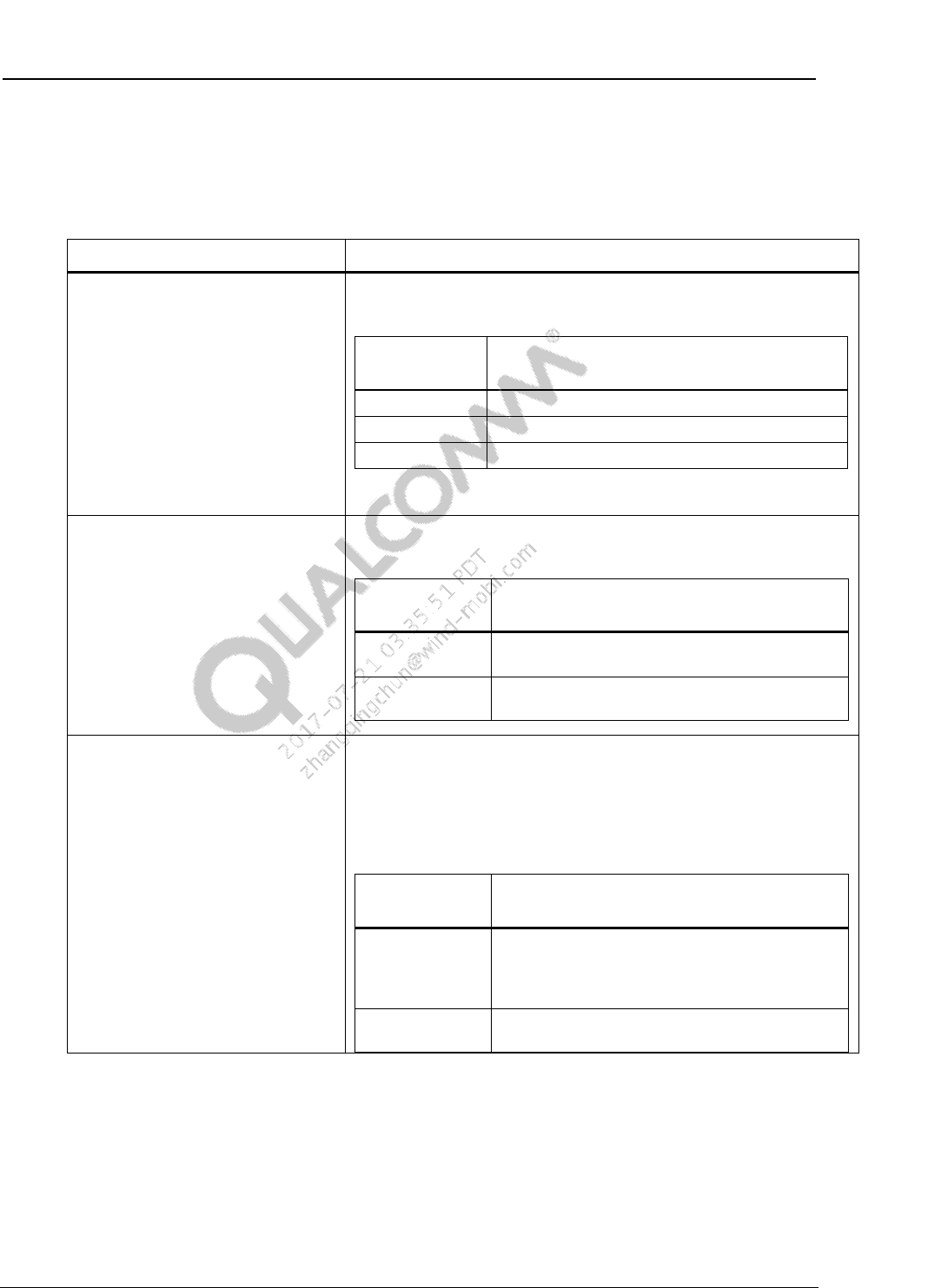

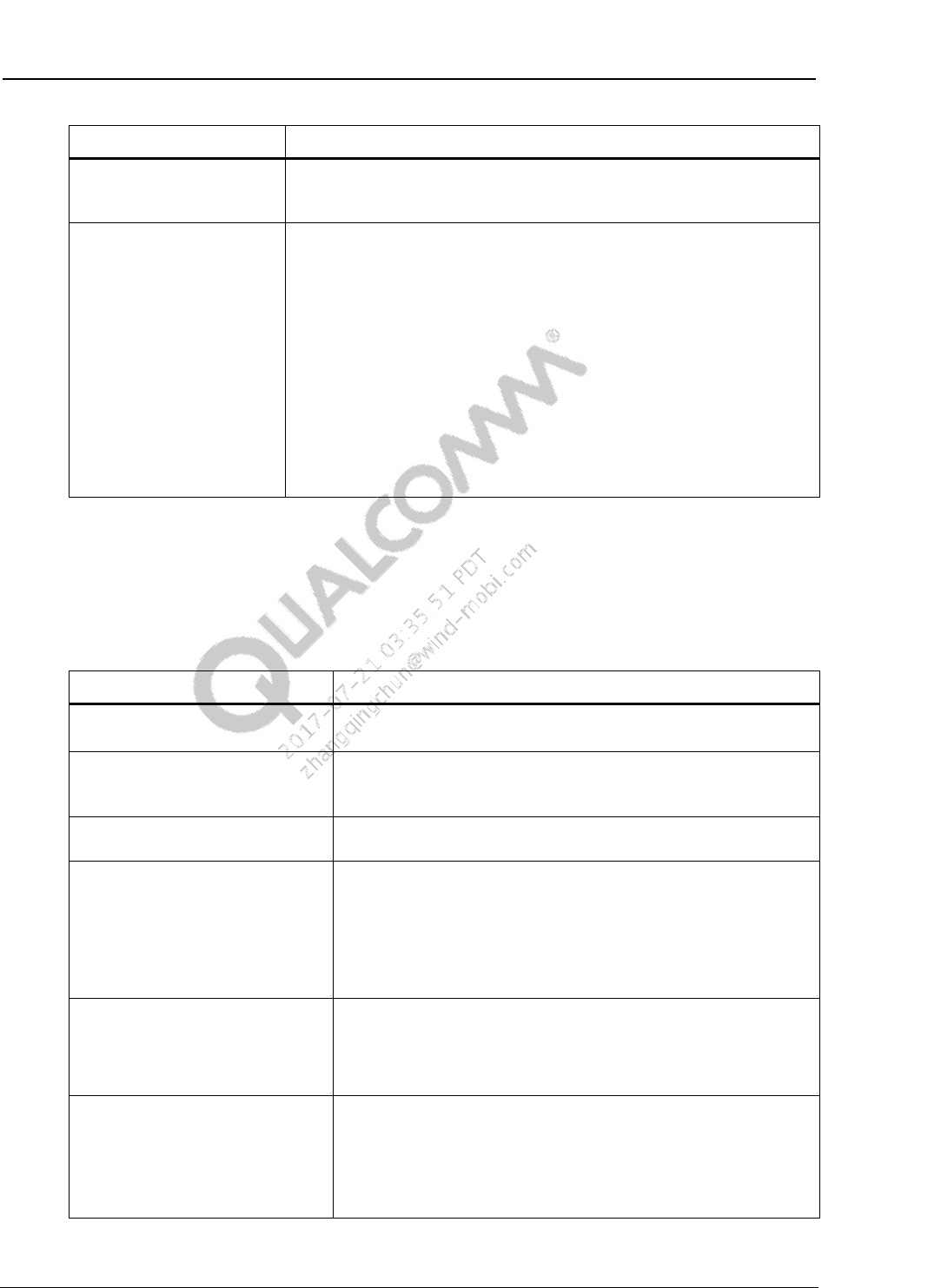

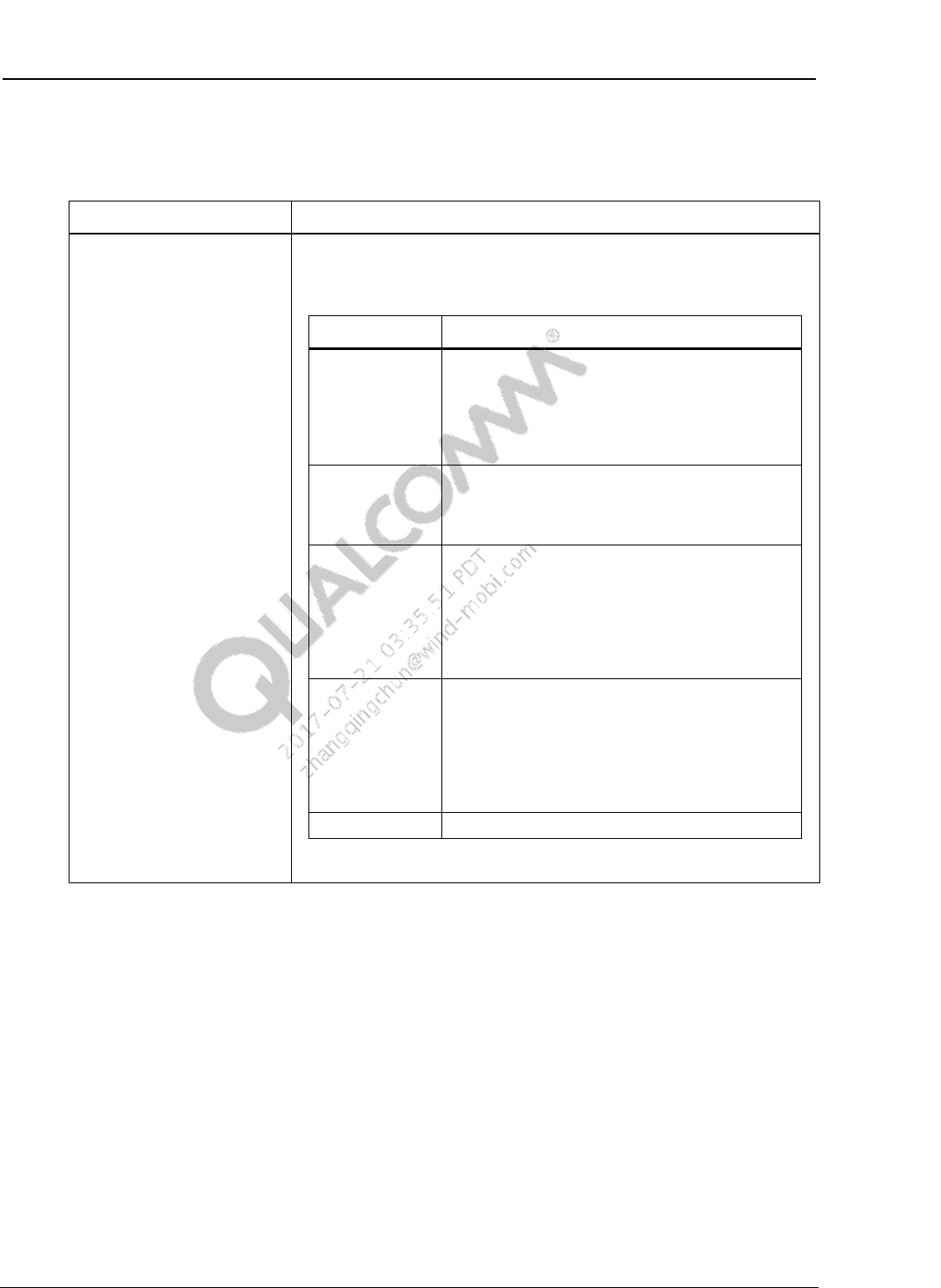

6 Display hardware tag descriptions

6.1 Common hardware configuration parameters

Table 6-1 lists configuration tags that define the interface information for the display. These

settings are critical since they determine the basic interface and mode of communication with the

display.

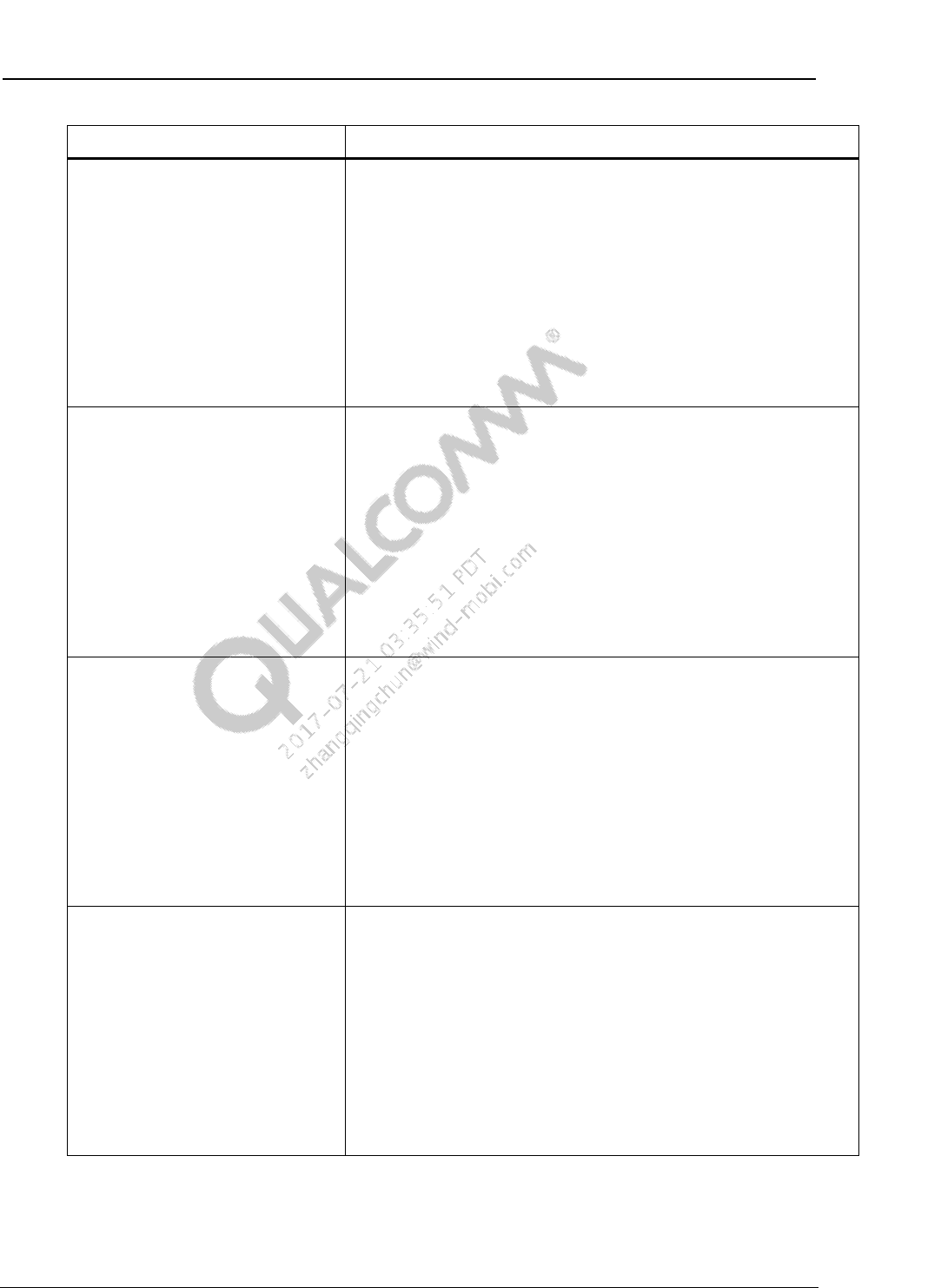

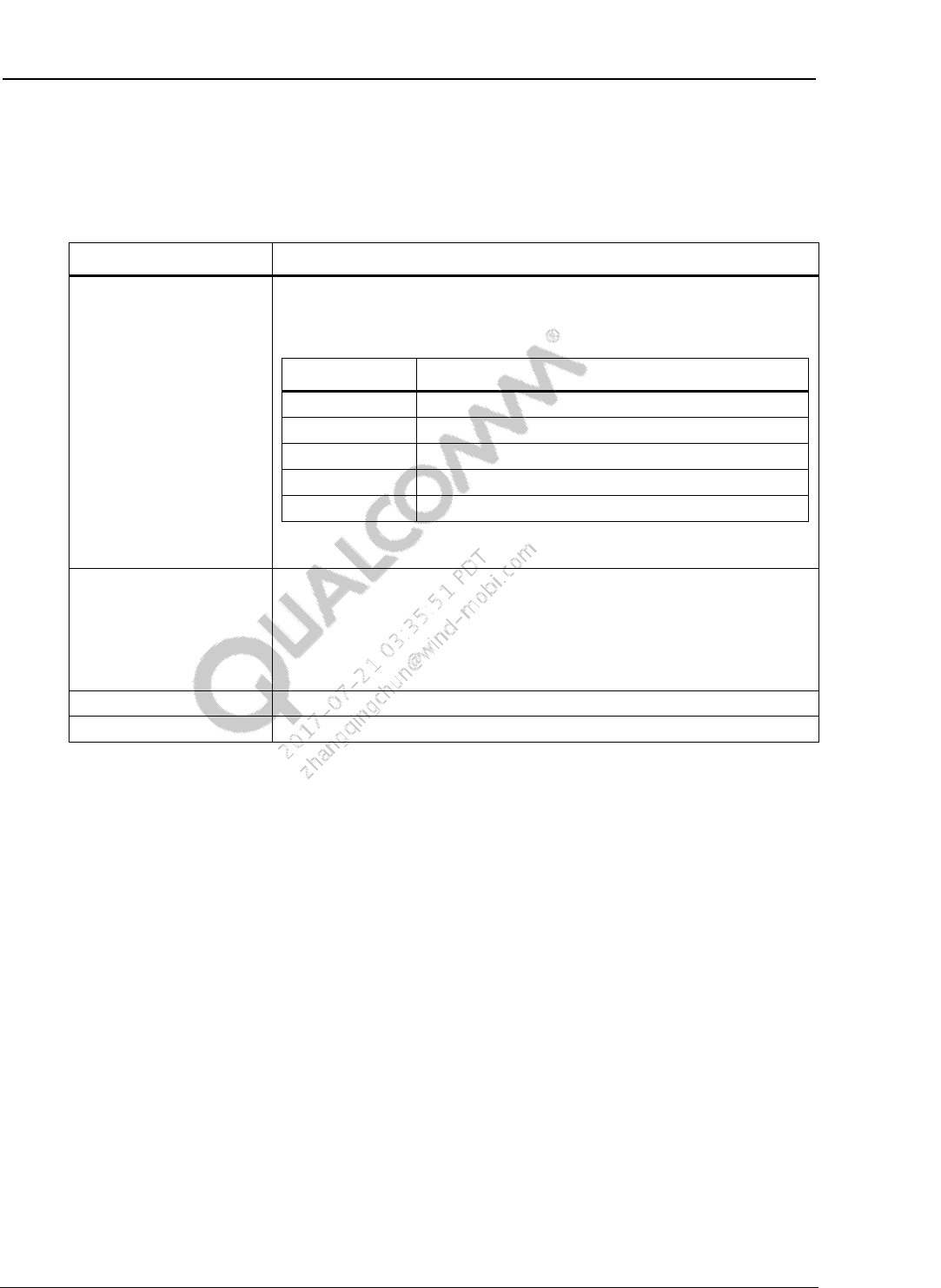

Table 6-1 Common hardware configuration parameters

NOTE: The following table has been updated.

Tag Description

InterfaceType Integer defining the interface between the MSM™ and the panel, based on the

enumerated type QDI_DisplayConnectType

Value (decimal) Definition

0 None, reserved.

1 EBI2, reserved.

2 LCDC, reserved

3 MDDI, reserved

4 MDDI, reserved

5 TV, Analog TV, reserved

6 MDDI, reserved

7 DTV, HDMI, reserved.

8 QDI_DISPLAY_CONNECT_PRIMARY_DSI_VIDEO

9 QDI_DISPLAY_CONNECT_PRIMARY_DSI_CMD

10 DSI, reserved

11 DSI, reserved

12 LVDS, reserved

13 Frame buffer, reserved

14 QDI_DISPLAY_CONNECT_DP

15 DBI, reserved

16 MHL, reserved

All other values are invalid or not supported.

Configuration Guide for Display Drivers (ACPI and XML) Display hardware tag descriptions

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 31

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Tag Description

PanelOrientation Integer defining the physical panel orientation

Value (decimal) Definition

0 QDI_ROTATE_NONE

2 QDI_ROTATE_180

Currently only 0° rotation (none) is supported.

InterfaceColorFormat Integer defining the pixel format (pixel depth) between the MSM and the panel,

based on the enumerated type QDI_PixelFormatType

Value (decimal) Definition

1 QDI_PIXEL_FORMAT_RGB_565_16BPP

2 QDI_PIXEL_FORMAT_RGB_666_18BPP

3 QDI_PIXEL_FORMAT_RGB_888_24BPP

All other values are invalid or not supported.

ComponentOrdering Integer defining the pixel component ordering between the MSM and the panel,

based on the enumerated type QDI_ColorOrderingType

Value (decimal) Definition

0 QDI_COLOR_ORDERING_RGB

1 QDI_COLOR_ORDERING_RBG

2 QDI_COLOR_ORDERING_GRB

3 QDI_COLOR_ORDERING_GBR

4 QDI_COLOR_ORDERING_BRG

5 QDI_COLOR_ORDERING_BGR

All other values are invalid or not supported.

PixelPacking Integer defining the pixel packing format between the MSM and the panel; this is

based on the enumerated type QDI_ColorComponentsPackingType. Packing is

only valid for pixel depths that are not aligned on an 8-bit boundary, such as

18 bpp.

Value (decimal) Definition

0 QDI_COLOR_COMPONENTS_PACKING_TIGHT

1 QDI_COLOR_COMPONENTS_PACKING_LOOSE

All other values are invalid or not supported.

Configuration Guide for Display Drivers (ACPI and XML) Display hardware tag descriptions

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 32

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Tag Description

PixelAlignment Integer defining the pixel alignment between the MSM and the panel, based on

the enumerated type QDI_ColorComponentAlignmentType; alignment is only

valid for loose pixel packet format types

Value (decimal) Definition

0 QDI_COLOR_COMPONENT_ALIGNMENT_LSB

1 QDI_COLOR_COMPONENT_ALIGNMENT_MSB

All other values are invalid or not supported.

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 33

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

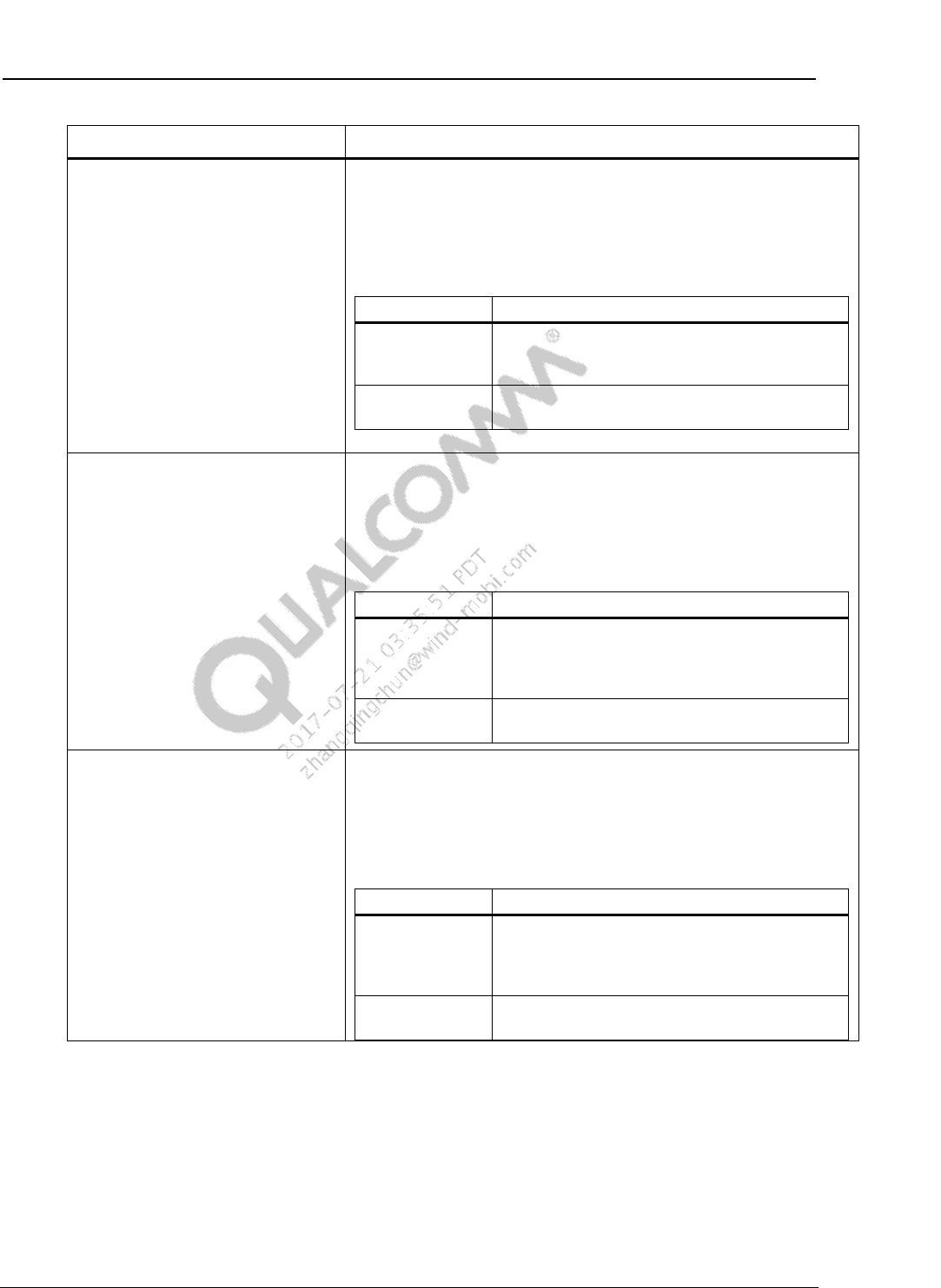

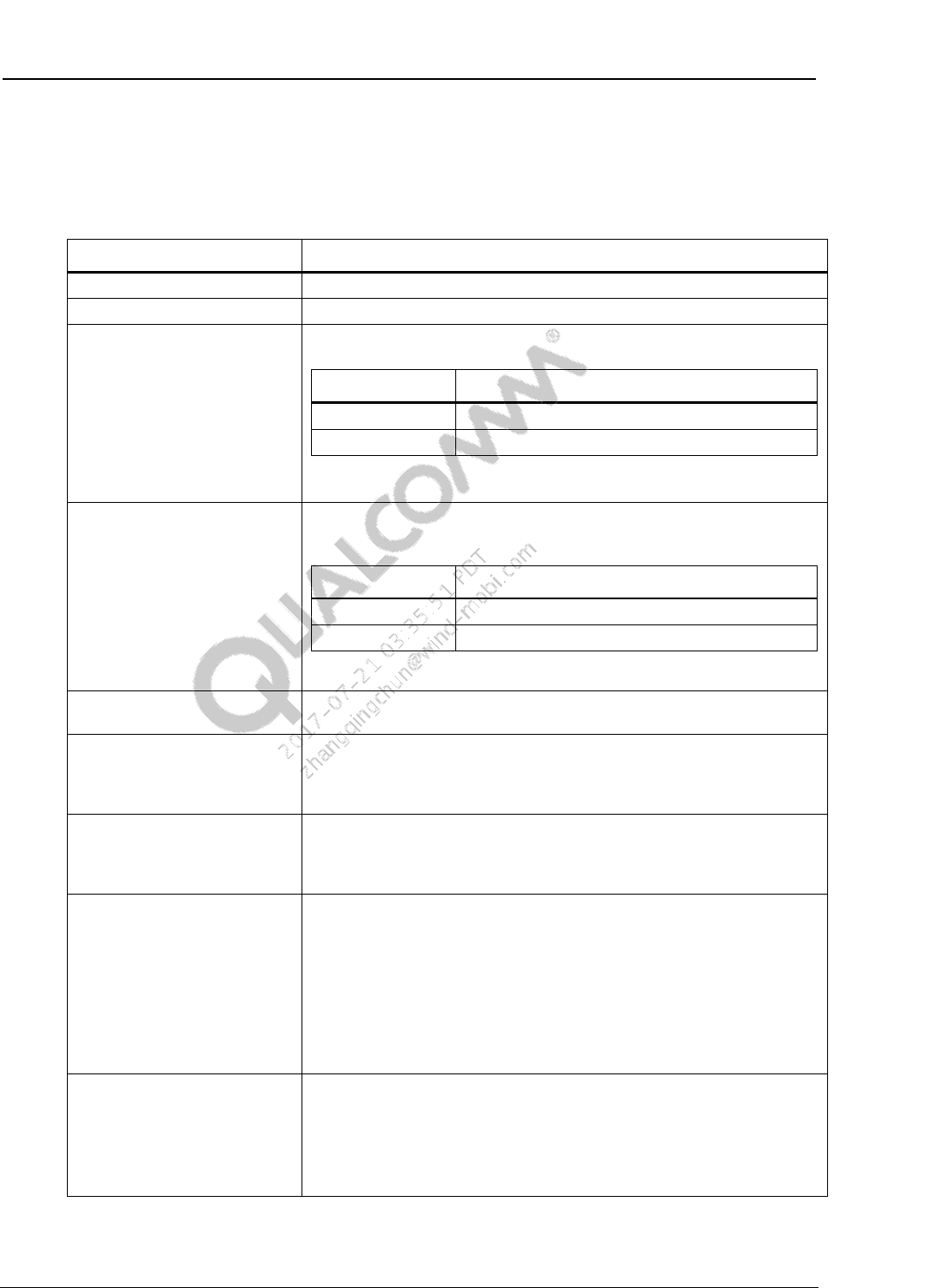

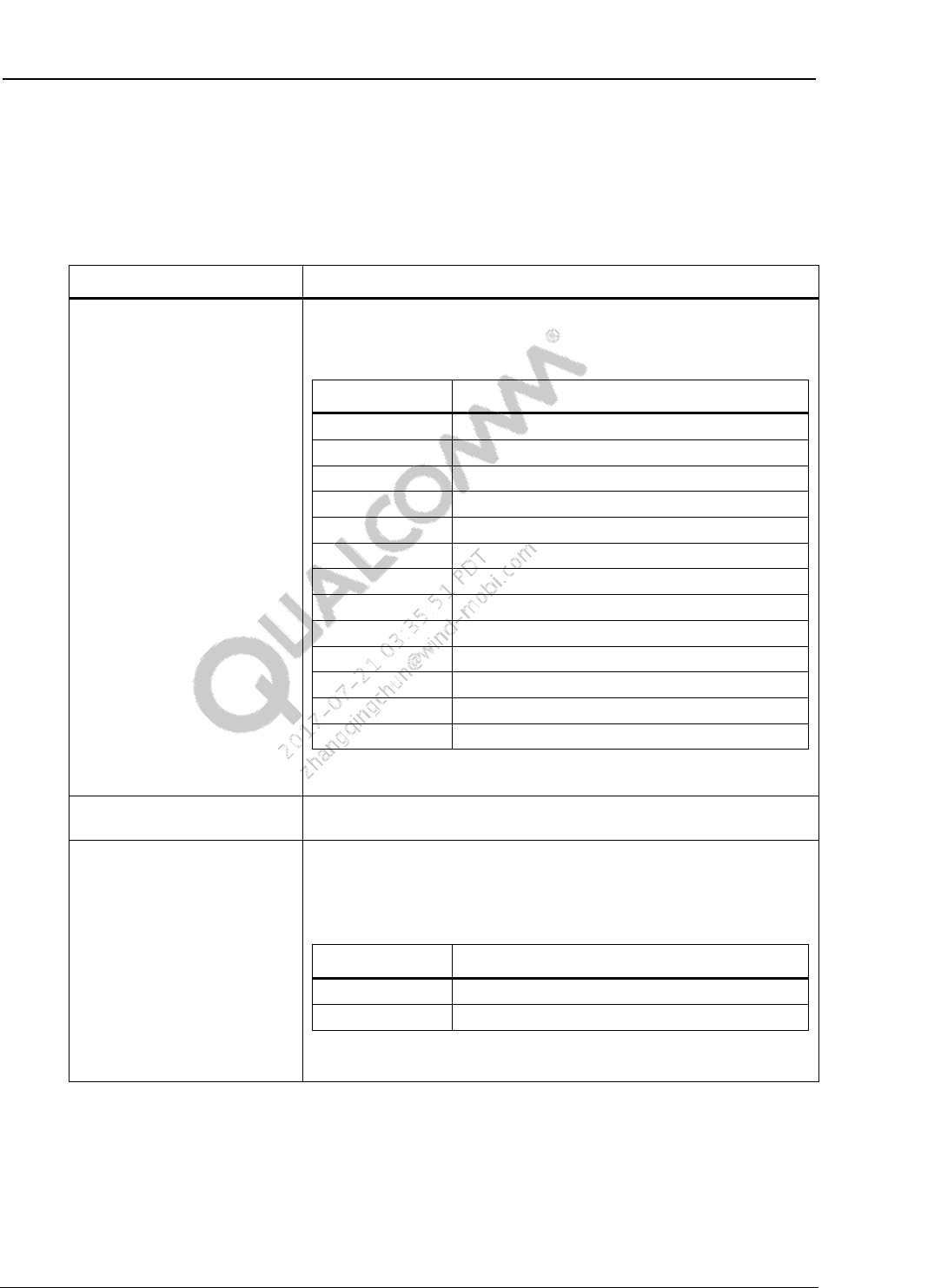

7 Display features

7.1 Display feature flags

Individual display features can be configured based on the feature flags given in Table 7-1. These

are the feature flags that can be enabled or disabled.

Table 7-1 Feature flags that can be enabled or disabled

NOTE: The following table has been updated.

Tag Description

DisplayPrimaryFlags Integer defining with each bit representing a feature that can be enabled or

disabled on the primary panel. Multiple flags can be combined to enable/disable

multiple features.

Value

(decimal) Definition

0x0001 QDI_PANEL_FLAG_FORCE_DISPLAY_REINIT

This flag forces the display to be reinitialized during the

transition from the firmware (UEFI) to the KMD. The

default behavior is to skip initialization when the display is

detected as active after the firmware has completed

execution.

0x0002 QDI_PANEL_FLAG_DISABLE_SBC

This flag disables smooth brightness control. If the

licensee chooses not to support this feature, this can be

disabled with this flag.

0x0004 QDI_PANEL_FLAG_DISABLE_CABL

This flag disables content adaptive backlight leveling.

0x0008 QDI_PANEL_FLAG_DISABLE_HW_CURSOR

This flag disables hardware cursors and fallback to OS

rendered cursors (software cursors).

0x0010 QDI_PANEL_FLAG_DUAL_MODE_SUPPORT

This flag enables the cap to allow the driver to transition

between MIPI DSI command and video mode operation

when the display mode is being reinitialized.

0x0100 QDI_PANEL_FLAG_DSI_DCS_POLLING_TRANSFER

This flag disables the interrupted based notification of

MIPI DSI DCS packets and reverts to a polling-based

mechanism.

0x0200 QDI_PANEL_FLAG_DSI_DCS_DMA_ONLY

This flag is deprecated; do not use. See DSIFlags for

details on DCS configuration.

Configuration Guide for Display Drivers (ACPI and XML) Display features

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 34

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Tag Description

0x0400 QDI_PANEL_FLAG_DSI_DCS_FIFO_ONLY

This flag is deprecated; do not use. See DSIFlags for

details on DCS configuration.

0x0800 QDI_PANEL_FLAG_ENABLE_DFS_IDLESCREEN

This flag enables lowering of the refresh rate during idle

screen (Vsync off) for video mode panels. This is

applicable to configurations that enable dynamic refresh.

0x1000 QDI_PANEL_FLAG_MIRROR_DUAL_PIPE_CONFIG

This is an internal flag used to swap pixel data between

DSI 0 and DSI 1.

0x00002000 QDI_PANEL_FLAG_DISABLE_POST_PROCESSING

This flag disables the postprocessing pipeline within the

display controller. Pixels will not be modified post-

blending.

0x00004000 QDI_PANEL_FLAG_INJECT_DEFAULT_AUDIO_MODE

This flag is used to force the driver to inject a default

audio mode (LPCM, 44.1 kHz) when an external display

EDID is being parsed. This flag can be used to force

overrides for displays that report incorrect or missing

audio EDID information.

0x00008000 QDI_PANEL_FLAG_STEREO_MODE_SUPPORT

This flag is used to force the driver into a VR/AR

composition mode that breaks composition into a left and

right side frame by hardware layer mixer.

0x01000000 QDI_PANEL_FLAG_DISABLE_SEAMLESS_SPLASH

This flag disables the display after UEFI is complete. If

enabled, this flag disables the display from scanning out

after the HLOS image starts.

All other values Reserved

All other values are invalid or not supported.

DisplayExternalFlags Integer defining with each bit representing a feature that can be enabled or

disabled on external panel (HDMI). Multiple flags can be combined to

enable/disable multiple features.

Value (decimal) Definition

All values Reserved

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 35

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

8 Display interface-specific configurations

8.1 DSI interface configurations

8.1.1 Common DSI configurations

These configuration parameters are common for both DSI Command mode and DSI Video mode

given in Table 8-1.

Table 8-1 Common DSI configurations

NOTE: The following table has been updated.

Tag Description

DSIRefreshRate The requested refresh rate in Q16.16 format. This parameter allows the

licensee to configure the rate at which the panel is updated.

The driver will be responsible for calculating the necessary DSI timings and

clock settings to achieve the requested refresh rate, for example:

60 Hz = 0x003C0000

50.5 Hz = 0x00328000

DSIBitClockFrequency This is an optional parameter that allows the licensee to configure an exact bit

clock frequency in Hz which represents the UIinst timing.

DSI Video mode

This setting overrides any value configured for DSIRefreshRate. The

actual DSI refresh rate is recalculated based on the formula:

Refresh rate = (#DSILanes x DSIBitClockFrequency)/ (HorizontalToal

x VerticalTotal x DSIBitsPerPixel)

DSI Command mode

This setting allows the bit clock to be independently configured from the

actual refresh rate, i.e., the transfer rate can be faster/slower than the

reported panel refresh rate.

If the DSIRefreshRate is specified, the driver reports this value to the OS

as the actual panel refresh rate and uses DSIBitClockFrequency to

determine the pixel transfer rate to the panel.

If the DSIRefreshRate is 0, the refresh rate will be calculated based on

DSIBitClockFrequency using the same equation as in

Section 8.1.8.

DSILanes This integer defines the number of DSI lanes. Valid values are 1 through 4.

However, some platforms and MSMs may limit the lanes to 1 to 2 lanes.

Configuration Guide for Display Drivers (ACPI and XML) Display interface-specific configurations

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 36

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Tag Description

DSIChannelId Integer defining the DSI interface used to communicate with the panel; this

must match the desired panel configuration. This setting is based on the

QDI_DSIChannelIDType enumeration.

The licensee must select the appropriate engine, either Video or Command

mode, depending on the type of DSI interface configured.

Value (decimal) Definition

1 QDI_DSIChannelID_Video0

2 QDI_DSIChannelID_CMD0

All other values are invalid or not supported.

DSIVirtualId Integer defining the virtual channel ID used when sending command and pixel

data; some devices may not support virtual channels. This setting is based on

the QDI_DSIDisplayVCType enumeration.

Value (decimal) Definition

0 QDI_DSIDisplayVC_0

1 QDI_DSIDisplayVC_1

All other values are invalid or not supported.

DSIColorFormat Integer defining the color format used to transfer data to the panel; this setting

is based on the QDI_DSIColorFormatType enumeration.

Value (decimal) Definition

18 QDI_DSICOLOR_RGB_565_16BPP

24 QDI_DSICOLOR_RGB_666_18BPP

30 QDI_DSICOLOR_RGB_666_24BPP

36 QDI_DSICOLOR_RGB_888_24BPP

All other values are invalid or not supported.

DSIPacketTransferHS This Boolean determines how the DMA command packets are sent to the

panel. When transferring command data to the panel, the packets can be sent

in either High Speed (HS) or Low Power (LP) mode. This setting determines

how packets are sent.

The exception to this rule occurs during initialization and termination sequences

sent to the panel. In these scenarios, the packets are always in LP mode.

Note: It is recommended that data always be sent in HS mode if the panel

supports it.

Value (Boolean) Definition

FALSE Sends DCS commands in LP mode

TRUE Sends DCS commands in HS mode

Configuration Guide for Display Drivers (ACPI and XML) Display interface-specific configurations

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 37

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Tag Description

DSIClockHSForceReq

uest This integer determines the state of the DSI clock lane. Some panels require

that the clock lane is always active in order to provide a continual clock signal

to the panel.

By default, this should not be used unless the panel requires an always active

clock lane.

Value (decimal) Definition

0 QDI_DSI_ClockLane_Default

DSI clock lane is in inactive (LP11) state

when transfers are not occurring.

1 QDI_DSI_ClockLane_ForceHS

DSI clock lane is always active regardless of

transfers occurring.

2 QDI_DSI_ClockLane_ForceHS_PostInit

DSI Clock lane is forced to HS after the init

sequence has been sent.

DSIHostLaneMapping This integer defines how the data lanes are mapped to the panel. Depending

on the platform, it may be required to map the individual DSI lanes. This

configuration is based on the QDI_DSILaneMapType enumeration.

The default mapping should be used unless the platform requires a special lane

mapping.

Value (decimal) Definition

0 QDI_PANEL_LANE0123MAP

1 QDI_PANEL_LANE3012MAP

2 QDI_PANEL_LANE2301MAP

3 QDI_PANEL_LANE1230MAP

4 QDI_PANEL_LANE0321MAP

5 QDI_PANEL_LANE1032MAP

6 QDI_PANEL_LANE2103MAP

7 QDI_PANEL_LANE3210MAP

All other values are invalid or not supported.

Configuration Guide for Display Drivers (ACPI and XML) Display interface-specific configurations

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 38

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Tag Description

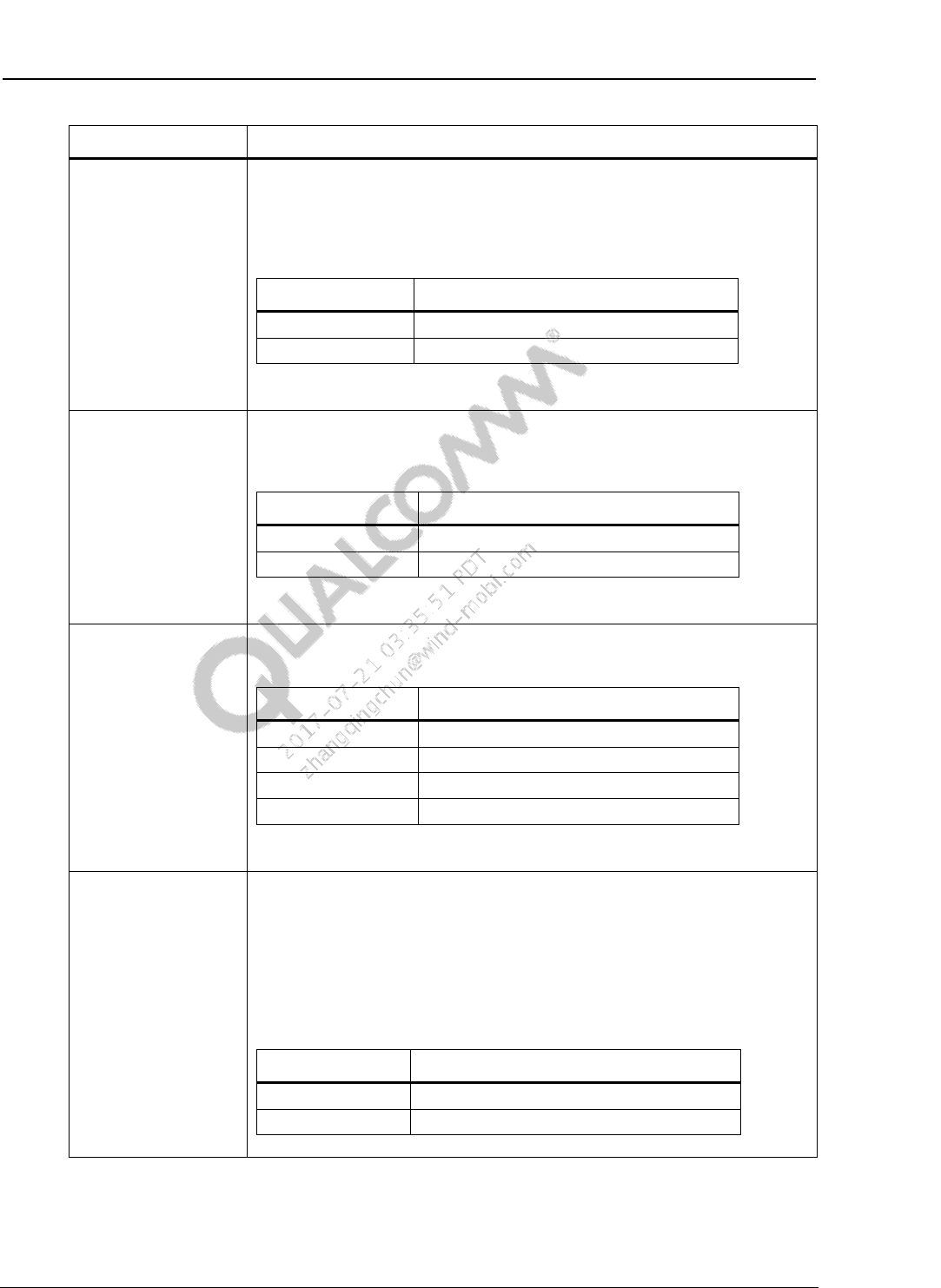

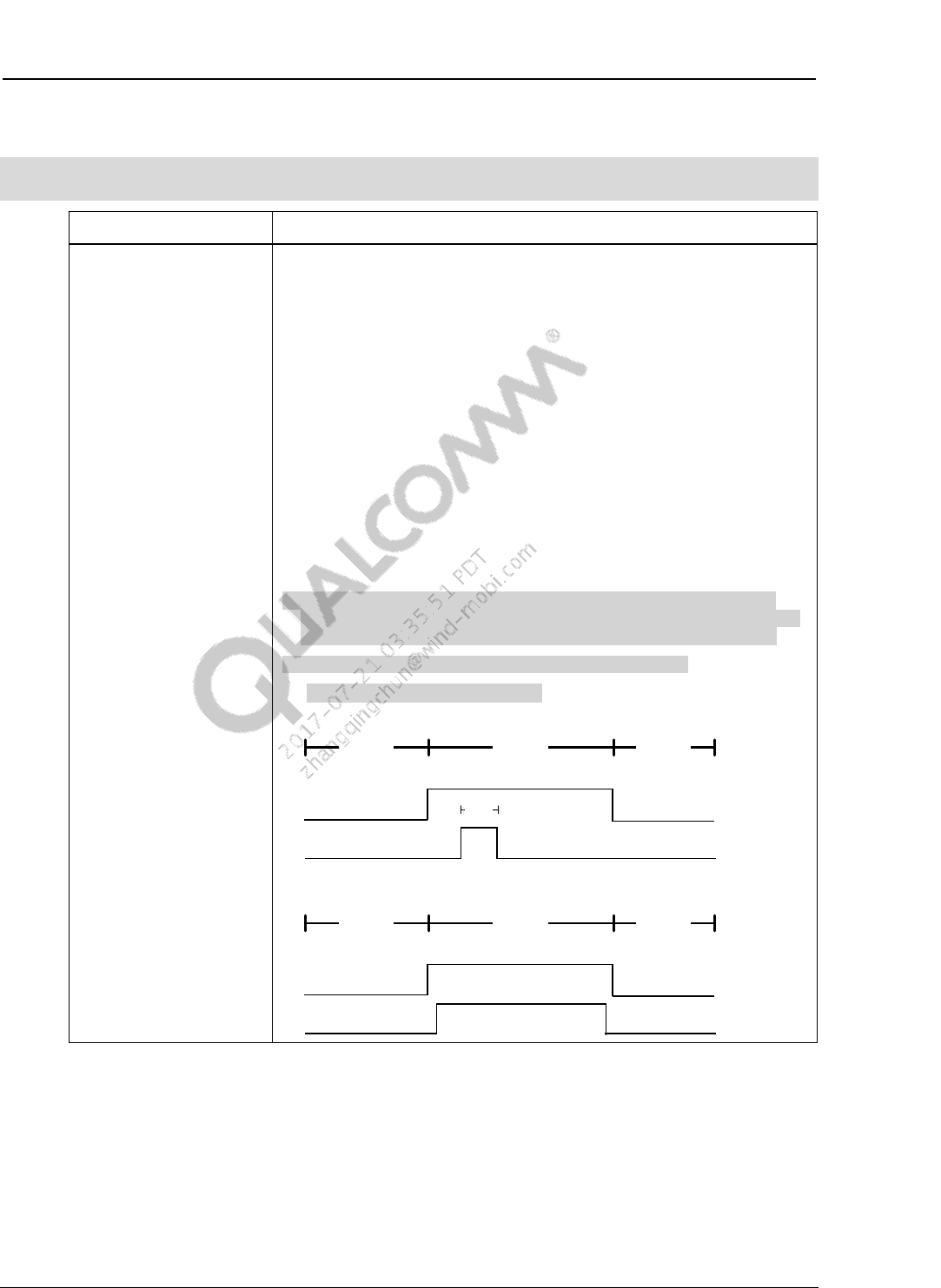

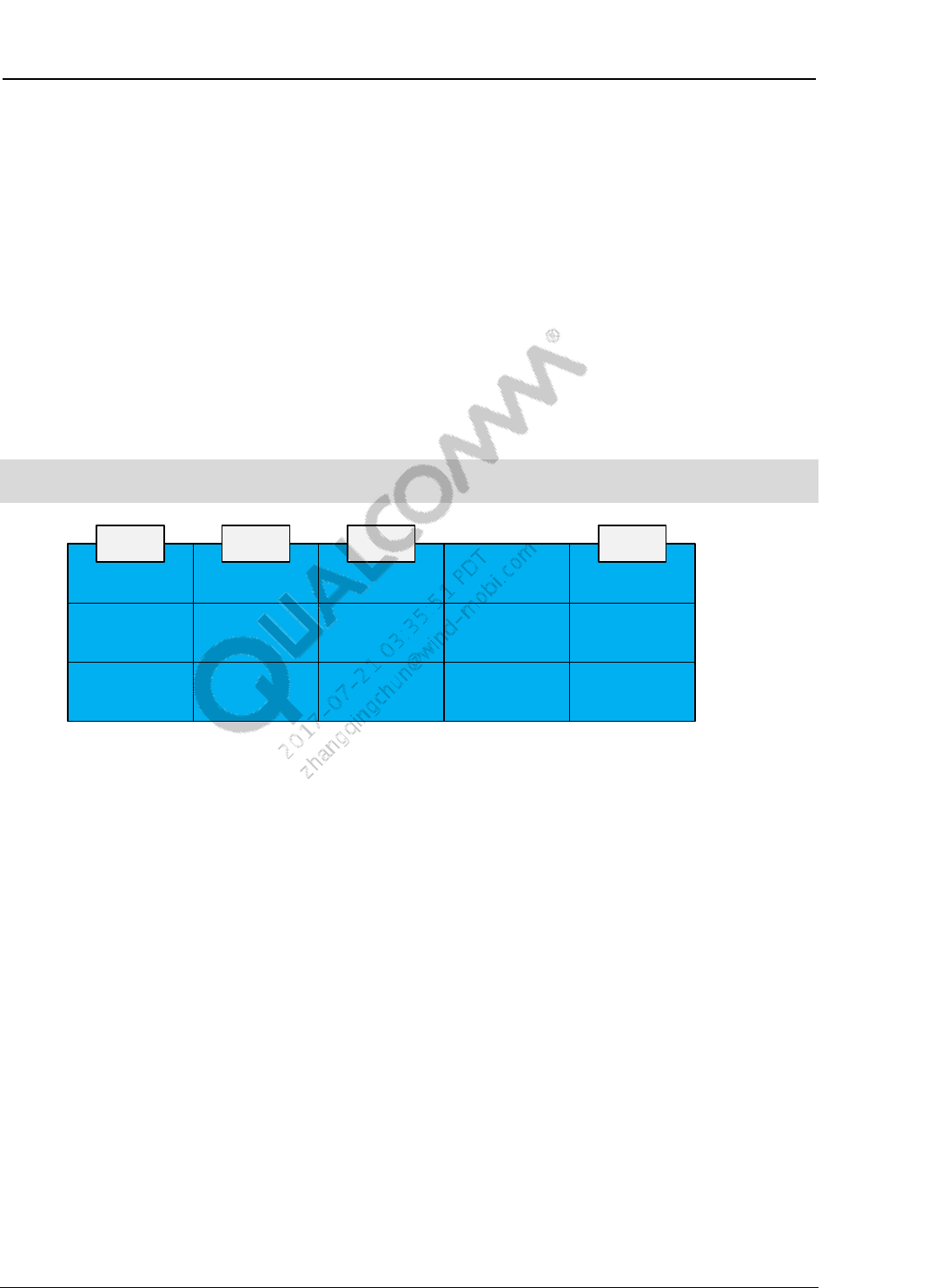

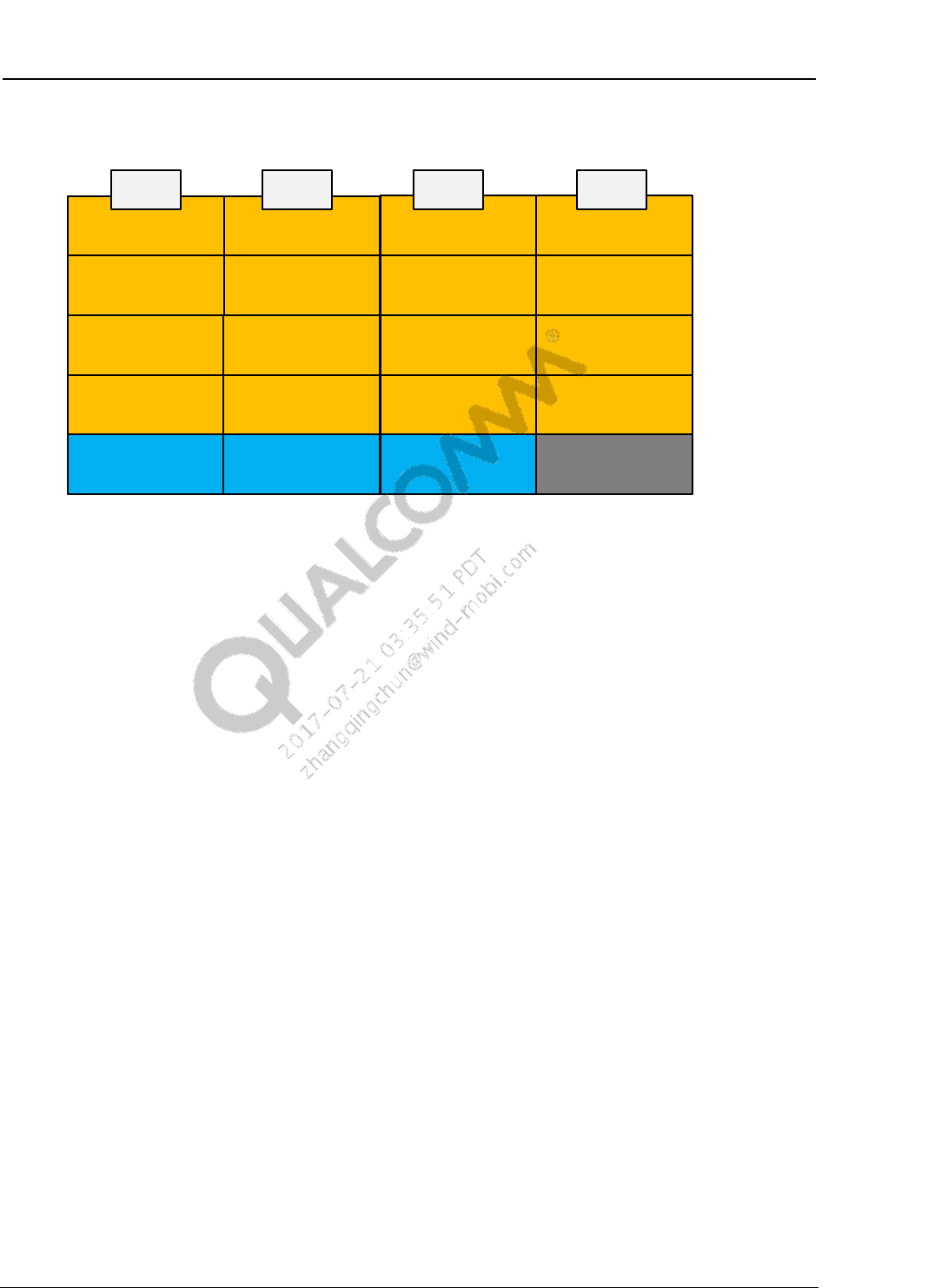

DSILP11AtInit This Boolean determines the status of the DSI clock and data lanes after

hardware initialization. Some panels may require that the DSI clock and lane

must enter LP11 prior to powering up and issuing the hardware reset line.

Panel Reset

Pin

Data Lanes HS Data

HS Clock

LP11 LP11

DSILP11AtInit=TRUE DSILP11AtInit=FALSE

Clock Lane

Value (Boolean) Definition

FALSE DSI data/clock lanes are in LP00 during the

power-on reset sequence

TRUE DSI data/clock lanes are in LP11 during the

power-on reset sequence

Configuration Guide for Display Drivers (ACPI and XML) Display interface-specific configurations

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 39

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Tag Description

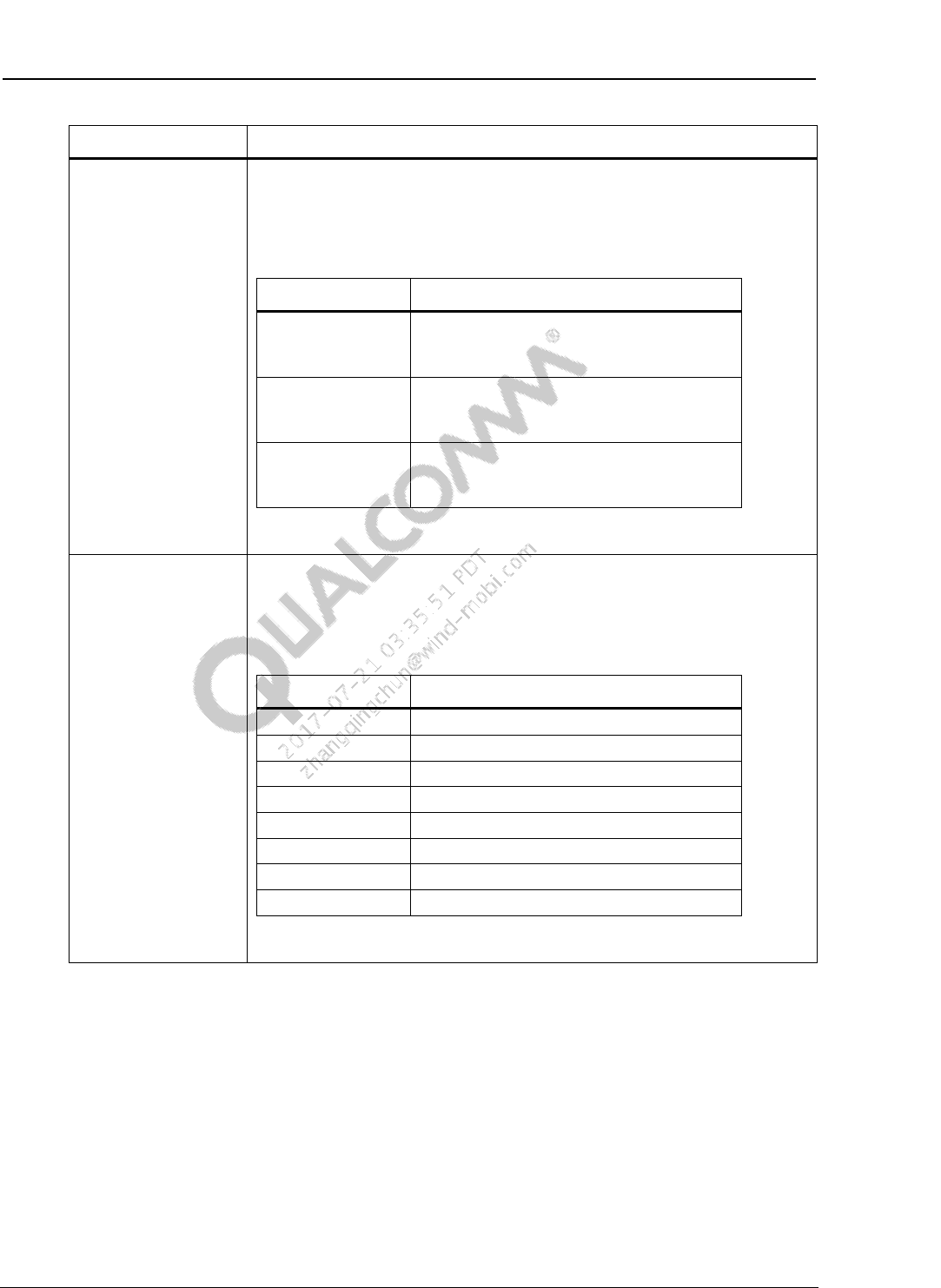

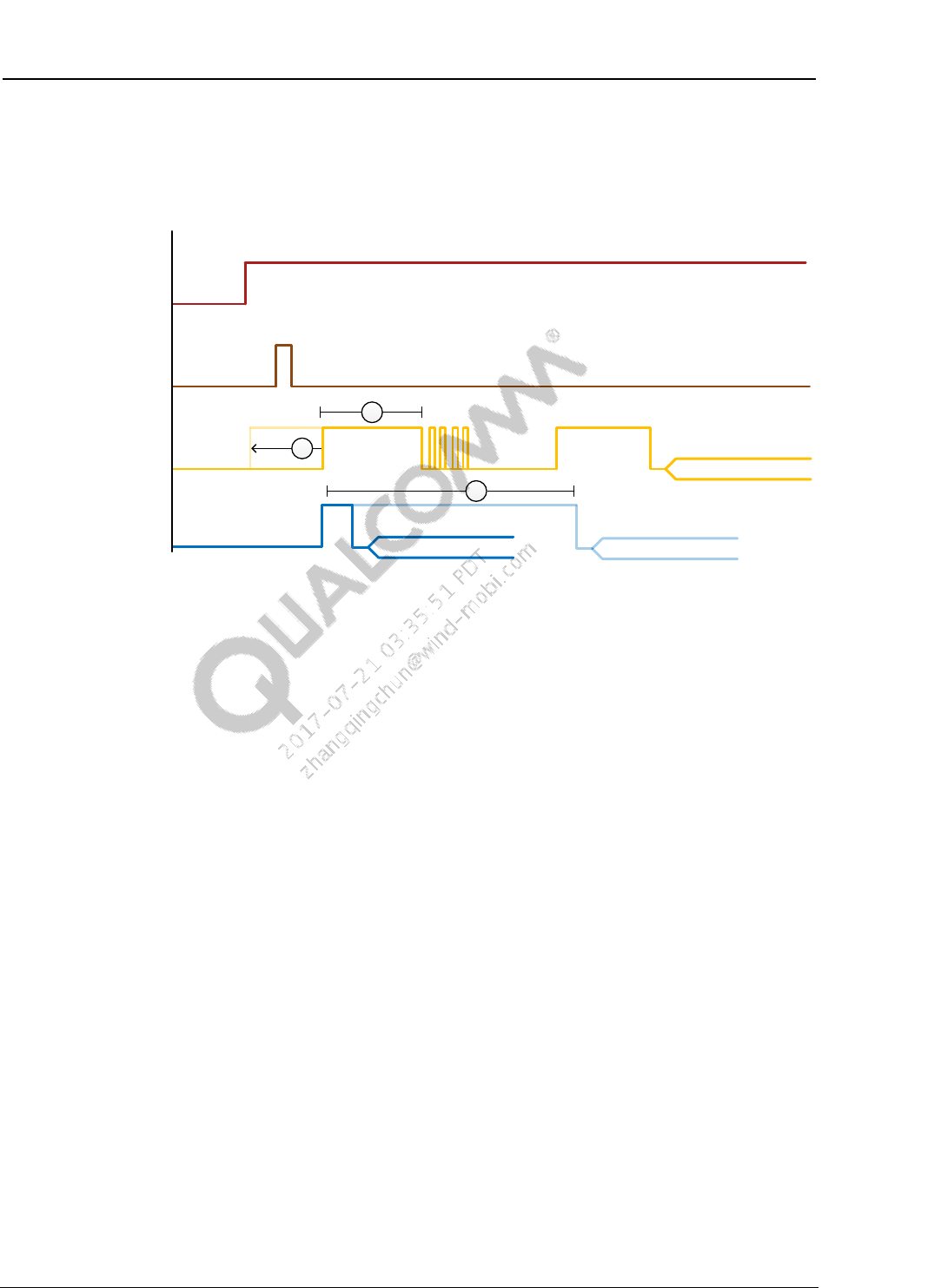

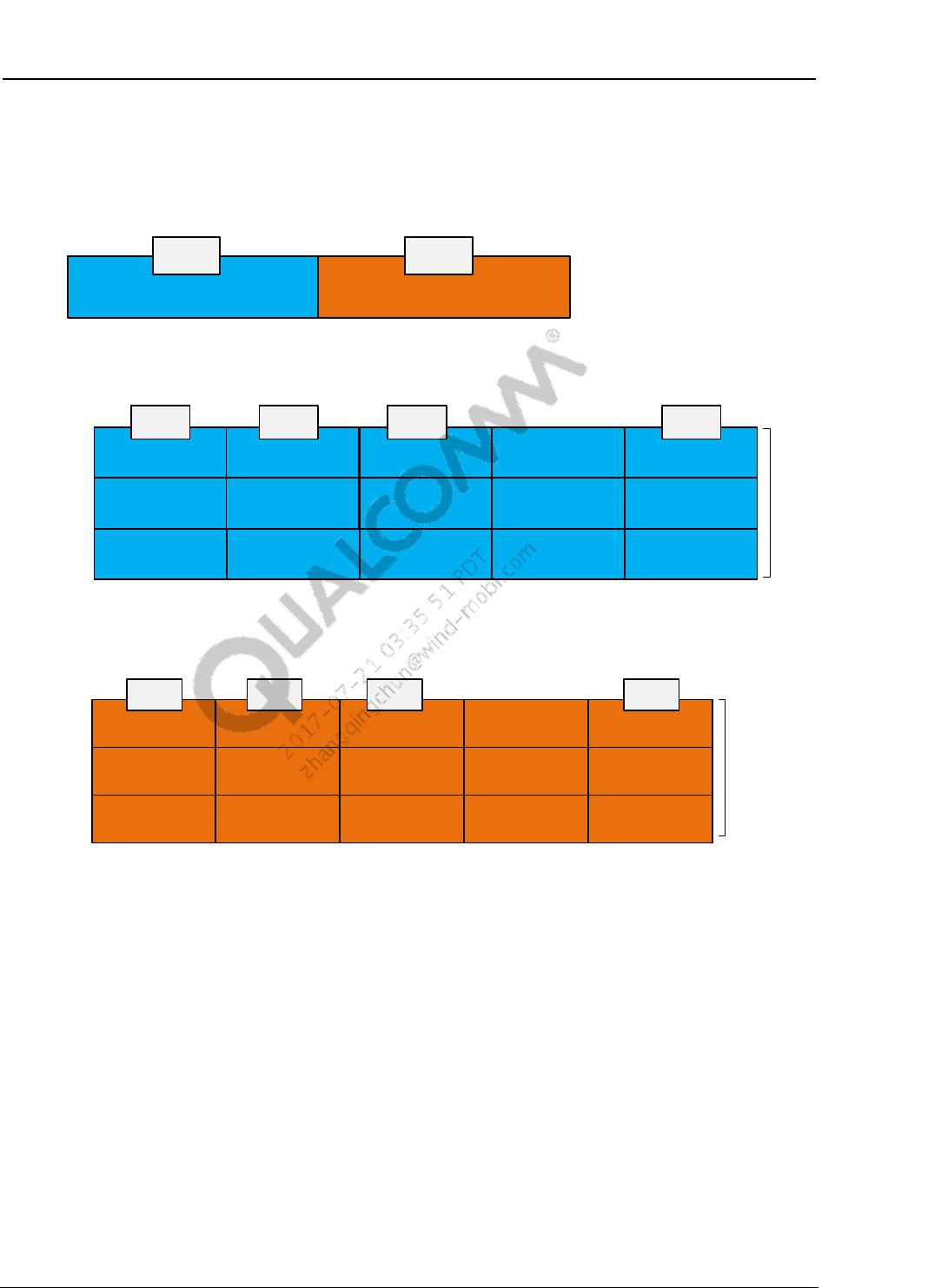

DSIPhyDCDCMode Note: This section is deprecated and no longer supported in the PHY.

DSI PHY supports two modes for generating required voltage for the HSTx

transmitters. One mode uses LDO Regulator and the other uses DCDC

Regulator.

See the diagrams below for details about the LDO vs. DCDC platform

configuration.

The default value is FALSE (LDO mode).

LDO mode

DCDC mode

Value (Boolean) Definition

FALSE DSI PHY regulator is in LDO mode

TRUE DSI PHY regulator is in DCDC mode

Configuration Guide for Display Drivers (ACPI and XML) Display interface-specific configurations

80-NB116-2 G Confidential and Proprietary – Qualcomm Technologies, Inc. 40

MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION

Tag Description