ECL_SSI_Symbols ECL SSI Symbols

User Manual: Pdf ECL_SSI_Symbols

Open the PDF directly: View PDF ![]() .

.

Page Count: 11

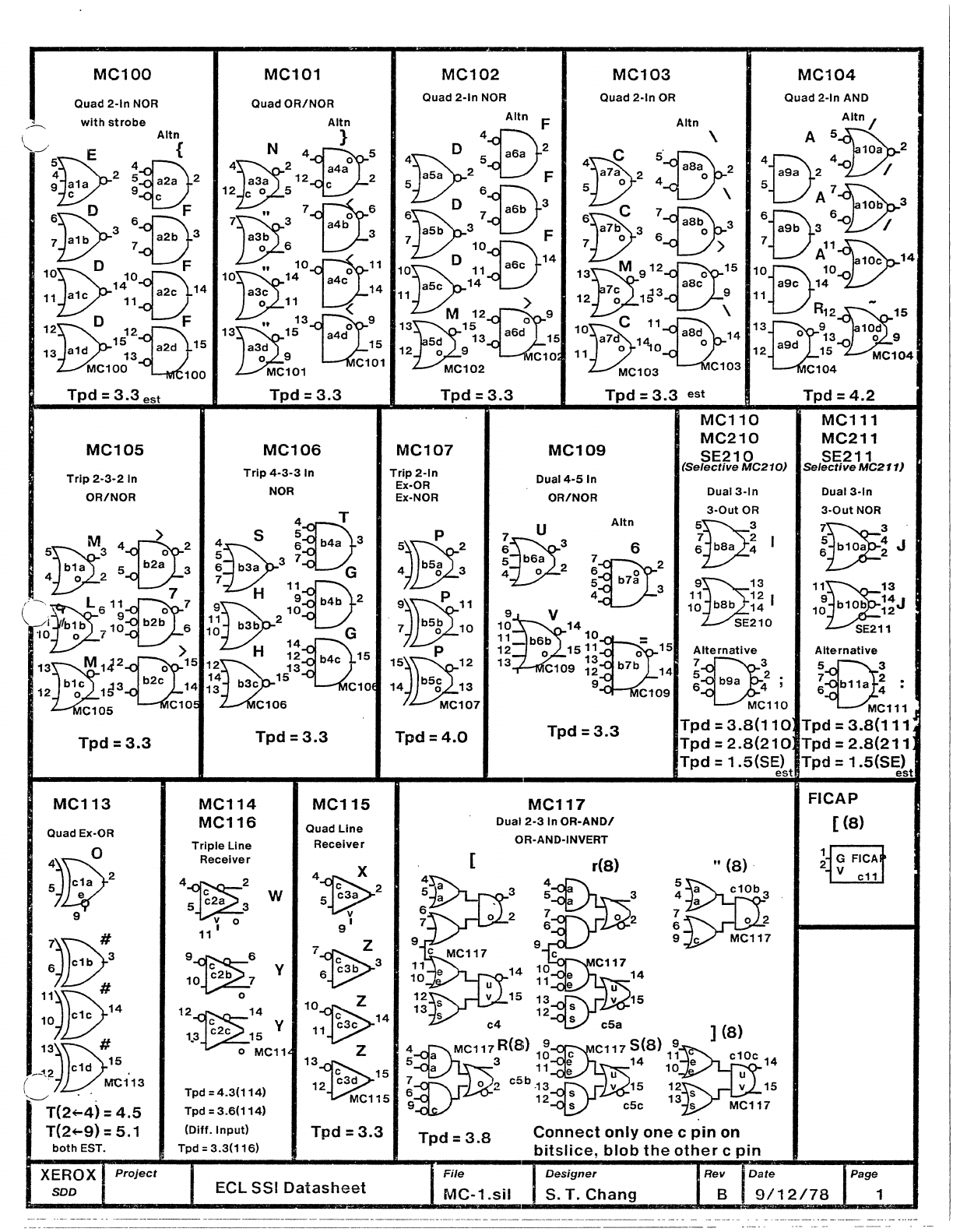

MC100

Quad

2·ln

NOR

with

strobe

Altn

5 E 4 {

i~2

5~2

~9~

6~

6 F

7

V'

70'

10~

10

F

"~'~,a'4

12d,D

12

F

13

a1d

15

13

Q15

MC100

~OO

Tpd

=

3.3

est

MC10S

MC101

Quad

OR/NOR

Altn

}

4B!N

2

404a

O 5

a3a

12

c 2

12

c 0 5

7B2"

3

7S

4bo 6

a3b

3

o 6

10Bl"

1~OS4CO

11

a3c

14

o 11

~

13

m

"

1~31:l4dO

9

a3d

15

o 9 C101

MC101

Tpd

=3.3

MC106

MC102

Quad

2·ln

NOR

4B

AItn F

o 2

4a

5

a6a

5

a5a

26BF

o 3

6~

7

a6b

7

a5b

3

10BF

o

14

10[211

a6c

a5c

14

11

M

12a>

9

13

15

0

[g

d

13

a6d

15

12

0 9

C10

MC102

Tpd

=3.3

MC103

Quad2·ln

OR

Altn \

a7a

2

4B

C

5 0

5't)sa

2

4 0 \

6B

c 75

a7b

aSb

3

o 3 6 0

7 >

13~M912B15

7c

aSc

12

0

1S

3 9

C

11fi\

10

aSd

14

a7

14

0

11

0

10

~'0'

C10.

Tpd

=

3.3

est

MC104

Quad

2·ln

AND

A

5»Altn/

10a

2

4

4-0

{:;:\2

/

5

U

7a

a9b

3

-0

/

6e

A 6

10b

3

7

11

A V

OC

14

10B

10-0

a9c

14

11

R12a-

15

13

0 9

10d

a9d

13-0

0 9

12~15

MC104

Q,04

Tpd

=4.2

MC107

MC109

MC110

MC210

SE210

MC111

MC211

SE211

Trip

2·3·2

In

Trip

4·3·3

In

Trip2·ln

Dual

4·5

In

(Selective

MC2tO)

Selective

MC2ttJ

NOR

Ex·OR

OR/NOR Ex·NOR

S

:B

E!'48

2 P

:&

~

b4a

,

~B!:

b1a

5

b2a

3

4 0 2

H 9

b4b

2

,'----. 11 7 9

10

OR/NOR

!Br'

Altn

6

5

b6a

7B2

4

02

6 0

5

b7a

4 3

Dual3·ln

3·0utOR

~:I

~~~~!I

Dual3·ln

3·0utNOR

~:J

19

b10b

~:J

~

b'a

'11B

. L e

9jb!"

~

i~'

,g

b2:

,

1;&,2

. 7

b5~

10

.~

10

14

10

0 7

10

14e

11_b6b

10

=

U.210

11~13

SE211

13~"2ff5

H

12

b4c

15

15jBf

12

0

15

11 0

15

13 13

12

13

C109

1~~14

b1c

S3

b2c

14

14

15 14

b58

13

12

0 1

,;~

C10.

C109

C105

C10~

C106

MC107

Alternative

Alternative

:9;

!O::

MC110

UC111,J

Tpd

=3.3

MC113

Quad Ex·OR

T(2~4)=4.S

Te2~9)

=

S.1

both

EST.

XEROX

Project

SDD

Tpd=3.3

MC114

MC116

Triple Line

Receiver

4~2

5~3

v 0

11 '

:~

o

w

V

c V

12~14

1.3

c2c

15

o

MC11

Tpd =

4.3(114)

Tpd =

3.6(114)

(Diff. Input)

Tpd =

3.3(116)

MC11S

Quad

Line

Receiver

4 X

~2

9'

7 Z

~3

10~Z

~3C

14

11

Z

13~

~3d

15

12

MC115

Tpd

=3.3

ECl

SSI

Datasheet

Tpd=4.0

Tpd

=3.3

Tpd

=

3.8(11

0

Tpd

=

3.8(111

Tpd

=

2.8(210

Tpd

=

2.8(211

Tpd

=

1.SeSE)

Tpd

=

1.SeSE)

est est

4 a

5 a

6

7

9 c

11 e

10

12

13

s

s

[

MC117

Dual

2·3

In

OR·AND/

OR·AND·INVERT

3

o 2

9

r(8)

::ih~3

~~~2

MC117 c

14 10

11

C117

14

u u

v

15

13~V

15

12

c4

s

c5a

"

(8)

.

5 a

c10b

3

4 a

7 o 2

6

9 MC117

]

(8)

5 a 3

10

c

14

11

e

c10c

14

4$C117

R

(S)

95117S(8)

9

a 11 u

10

u

6

12

s

13

s

7

vn

0 2

C5b.

13y

v

15 12

v 15

9 s

e5c

s MC117

Tpd=3.8

Connect

only

one

C

pin

on

bits

lice,

blob

the

other

C

pin

FICAP

[

(8)

~

G

FIC~t

V c11

File

Designer

Rev

Date

Page

MC-1.sil

S.T.Chang

B

9/12/78

1

I

,....,

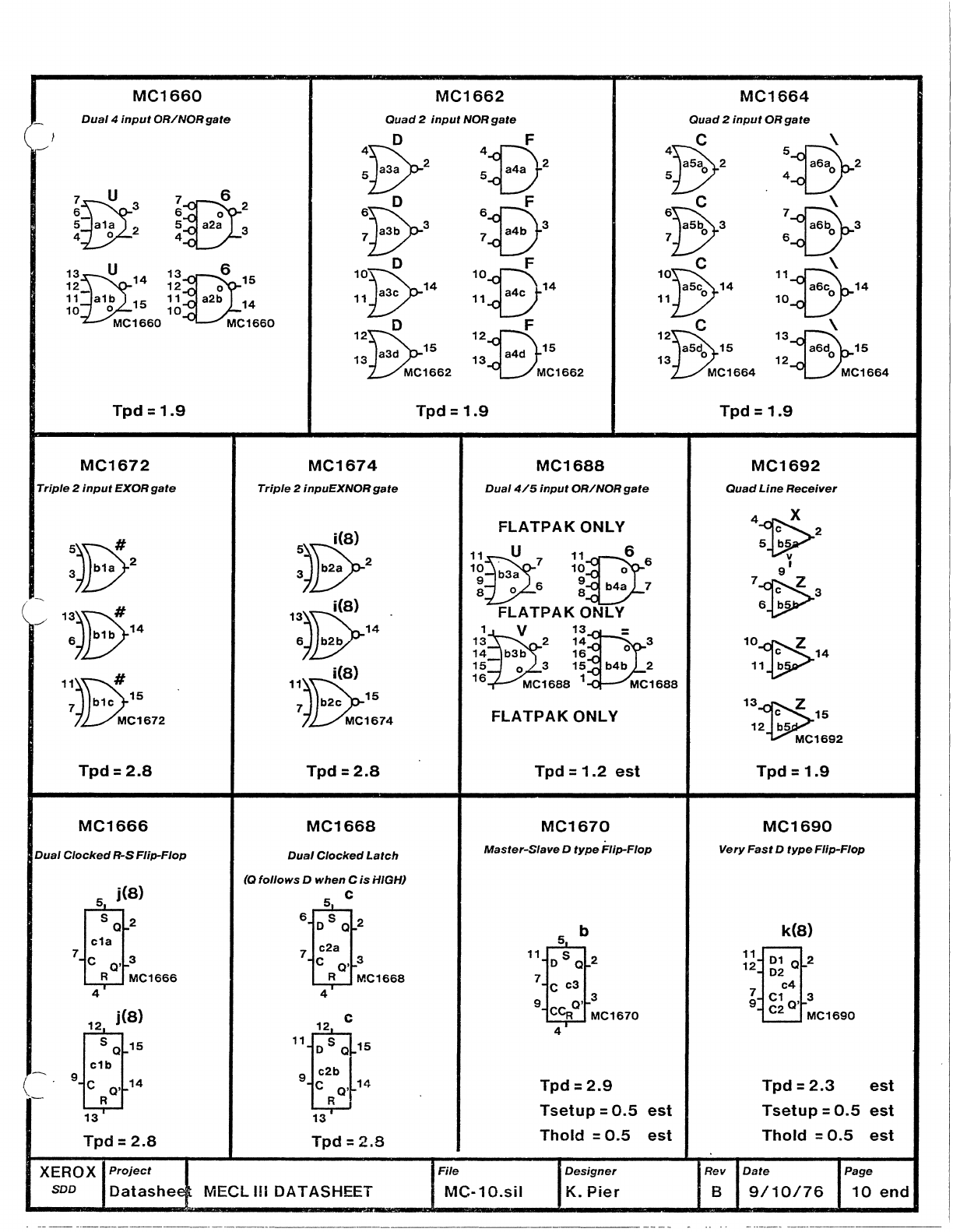

MC1660

Dual

4

input

OR/NOR

gate

~B!U

3

5

a1a

2

4 0

~~~U

14

~~B6

15

11-

a1b

15

11

a2b

14

10

0

10

MC1660

MC1660

Tpd

=

1.9

MC1672

MC1662

Ouad

2

input

NOR

gate

D F

:E>-'

:B'

D F

:&-3

:B3

10E>-D

1°B

F

a3c

14

a4c

14

11 11

12&D

12B.

F

a3d

15

a4d

15

13

13

MC1662

MC1662

Tpd=

1.9

MC1674

MC1688

Triple

2

input

EXOR

gate

Triple

2

inpuEXNOR

gate

Dual

4/5

input

OR/NOR

gate

~E>'

':)3S'4

5d~j(8)

b2a

2

3

13\~14

6j~

FLATPAK ONLY

"~7

11

6

1~

b3a

'0£1"

~

b4a

7

8 0 6

FLATPAK ONLY

14

b3b

16

0

15-

0 3

15

b4b

2

MC1664

Ouad

2

input

OR

gate

C \

{3>'

:&'

C \

03

:&3

10~C

11&\

a5c

o

14

a6c

o

14

11

10

12~C

13a\

a5d

o

15

a6d

o

15

13

12

MC1664

MC1664

Tpd

=

1.9

MC1692

Ouad

Line

Receiver

4~

c 2

5 b

v

9'

7~

c 3

6 b

c

14

11

b

11~~

i(8)

11~~

'~~'

~!~3

16

MC1688

1

MC1688

10~

b1

15

7 c

MC1672

Tpd

=

2.8

MC1666

Dual

Clocked

R-S

Flip-Flop

5

j(8)

s o 2

c1a

7 C 0. 3

R

MC1666

4

~(8)

So

15

c1b

~

9 C

O·

14

-R

13

Tpd=

2.8

XEROX

Project

b2

15

7 c

MC1674

Tpd

=2.8

MC1668

Dual

Clocked

Latch

(a

follows

D

when

C

is

HIGH)

5 C

6.

0

So

2

7

c2a

.• C

0._

3

R

MC1668

4

12

C

110501-15

9

c2b

C

0.

14

R

13

Tpd

=

2.8

SDD

Datashee

MECL III DATASHEET

-

---

----------------------

File

FLATPAK

ONLY

Tpd

=

1.2

est

MC1670

Master-5lave

D

type

Flip-Flop

5 b

11.

S 2

- 0 Of-'

7 C

c3

9

0.

3

CCR

MC1670

4

Tpd=2.9

Tsetup

=

0.5

est

Thold

=

0.5

est

MC-10.sil

Designer

K.

Pier

13~

c

15

12

b5

MC1692

Tpd

=

1.9

MC1690

Very

Fast

D

type

Flip-Flop

k(8)

11

,..--

12-

01

0 2

02

7

c4

9

C1

0• 3

'-

C2

MC1690

-

Tpd

=

2.3

est

Tsetup

=

0.5

est

Thold

=

0.5

est

Rev

Date

Page

B

9/10/76

10

end

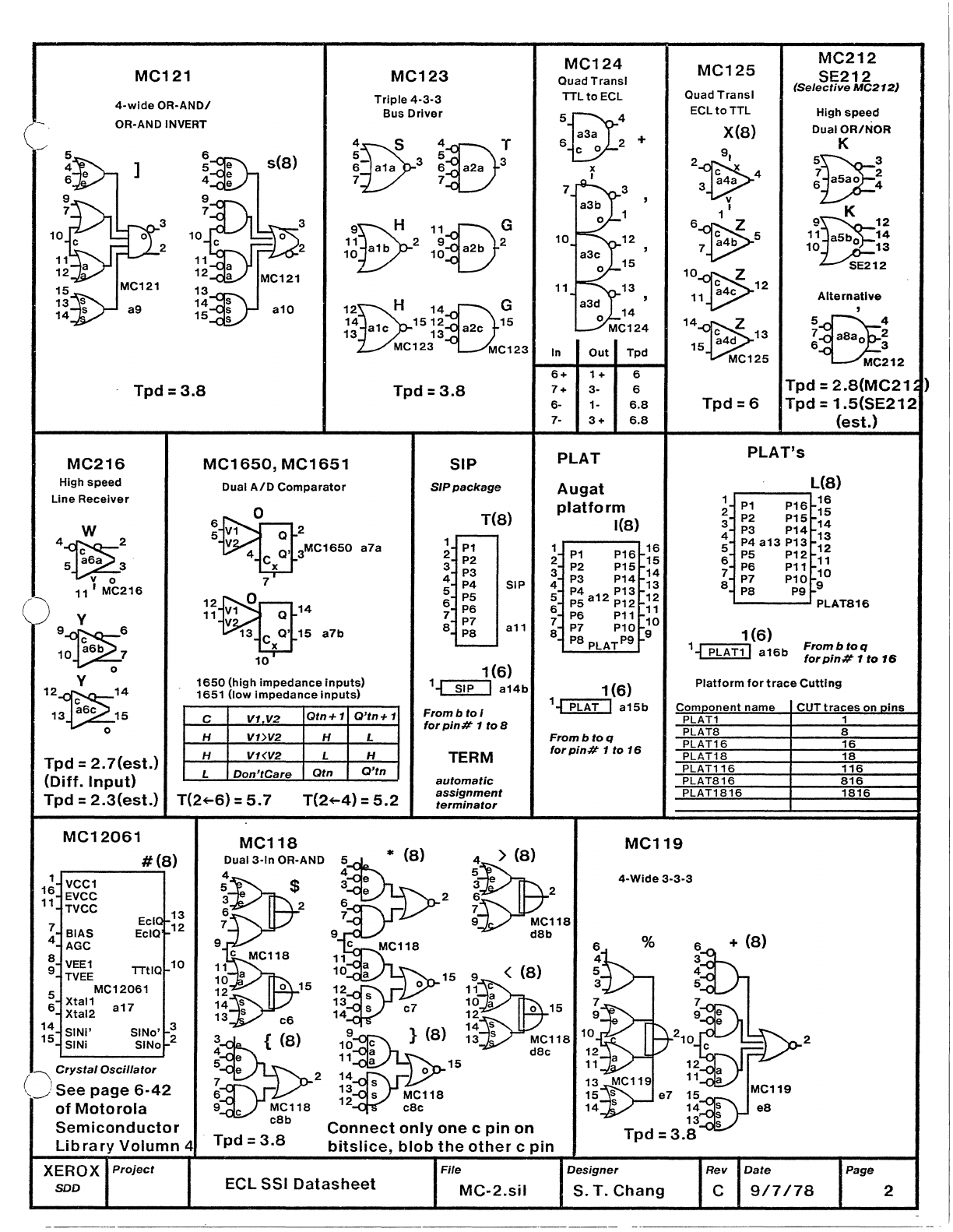

MC12l

MC123

4-wlde

OR-AND/

Triple

4-3-3

Bus

Driver

OR-AND INVERT

./

4 S 4 T

6

Sea)

~E>'

~B'

5

4

3 3

:t:>

"BG

2 11

a1b

2 9

2b

2

10 10

a

a10

12Ei

14B

G

14

a1c

1512

a2c

15

13

13

MC123

MC123

Tpd

=3.a

Tpd

=3.a

MC2l6

High

speed

Line

Receiver

W

4~2

5~3·

v 0

11'

MC216

V

9~6

10~7

o

V

12~14

13~15

o

Tpd

=

2.7(est.)

(Diff.

Input)

Tpd

=

2.3(est.}

MC1650,

MC165l

Dual

A/D

Comparator

~~O

02

V 4

0'

3MC1650

a7a

Cx

12

V1

0

11 V

7

a7b

1650

(high

Impedance

Inputs)

1651

(low

Impedance

inputs)

C V1

V2

Otn+1

O'tn+

1

H V1>V2 H L

H

V1<V2

L H

L

Don',Care

Otn

O'tn

T(2+-6} =

5.7

T(2+-4) =

5.2

SIP

SIP

package

T(a)

1

P1

2 P2

3 P3

4 P4 SIP

5 P5

6 P6

7 P7

8

P8

a11

Frombtol

for

pin#

1

to

8

TERM

automatic

assignment

terminator

MC124

Quad

Transl

TTLtoECL

5B'

a3a

+

6

co2

x

I

7 3

10

12

15

11

13

14

In

Out

Tpd

6+

1+

6

7+

3-

6

6-

1-

6.8

7-

3+

6.8

PLAT

Augat

platform

I(a}

1

2

3

4

5

6

7

8

P1

P16

r

16

15

14

13

12

11

10

g

.-

P2

P15

P3

P14

P4

a12

P13

P5

P12

P6 P11

P7

P10

. P8

PLAT

P9

i.

.

1(6)

1-1~""'P-LA-T""":'1

a15b

Frombtoq

forpin#

1

to

16

MC2l2

MC125

SE2l2

Quad

Transl

(Selective

MC212)

ECLtoTTL

High

speed

X(a)

Dual

OR/NOR

9,

K

2~4

S'

7 2

6

a5ao

4

1 I 9

tl

'2

6~

7

~4b

5 11

a5b

o

14

10

13

10~

SE212

~4C

12

Alternative

11 ,

14~

5a

4

c

13

7

a8a

o 2

15

a4d

6 3

MC125

MC212

Tpd

=

2.a(MC2l

Tpd=6

Tpd

=

1.5(SE212

(est.)

PLAT's

Ua)

P1

P16

P2

P15

P3

P14

16

15

14

1

2

3

4

5

6

7

8

P4

a13

P13

13

12

. P5

P12

-

P6 P11

P7

P10

P8 P9

11

10

9

PLAT816

1(6}

1-1~-P-LA-T-1":'1

a16b

Frombtoq

forpln#

1

to

16

Platform

for

trace

Cutting

Com

onent

name

CUT

traces

on

Ins

PLAT1

PLAT8

8

PLAT16

16

PLAT18

18

PLAT116

116

PLAT816

816

PLAT1816

1816

MC1206l

#(8)

MCl18

Dual3·ln

OR-AND

:~>(8)

MCl19

1

16

VCC1

11 EVCC

TVCC

~.

BIAS

AGC

Ec10_

13

EclQ

12

8

VEE1

10

9.

TVEE

TTtlQ

5

MC12061

6

Xtal1

a17

•

Xtal2

14

SIN)'

15

SINi

SINo'

~

SINo

Crystal

Oscillator

C)

See

page

6·42

of

Motorola

Semiconductor

Lib

ra

ry

Volumn

XEROX

Project

SOD

9

c6

3~(8}

4 e

5 e

7 2

:~C118

c8b

Tpd=3.8

3 2

!

MC118

d8b

c

11

a

ii~,;

151~~<

(:)

15

~

14

s

1~~aC

~

},

(ga),

13

s

MC118

10

~~

d8c

~;~C:18

15

12~

~8C

Connect

only

one

c

pin

on

bitslice,

blob

the

other

c

pin

4-Wlde

3·3·3

%

File

Designer

ECl

SSI

Datasheet

MC·2.sil

S.T.Chang

+

(a)

2

Rev

Date

Page

C

9/7/7a

2

---

------------------

)

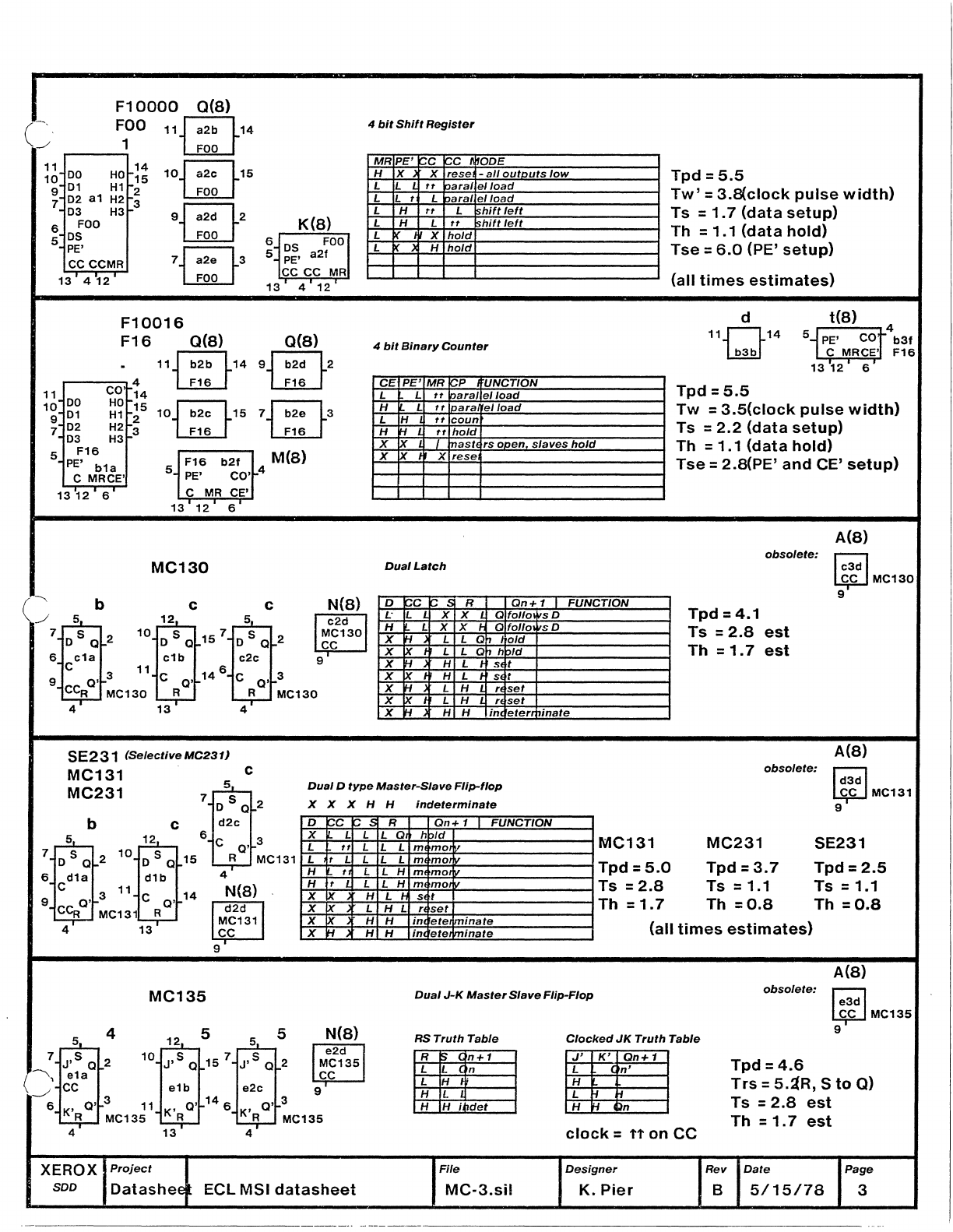

F10000

O(S)

C~~

FOO

11~14

4

bit

Shift

Register

1

FOO

11

14

MR

PE'

G C

ODE

10

DO

HO

15

10~15

H X X

rese

-

all

outputs

low

Tpd

=

5.5

9

D1

Hi

2

FOO

L L

tt

baral

elload

Tw'

=

3.8(clock

pulse

width)

7

D2

a1

H2

3 L L t L

aral

elload

D3

H3

9{:]2

L H

tt

L Ir;hift

left

Ts

=

1.7

(data

setup)

6

FOO

K(S)

L H L

tt

Ir;hift

left

Th

=

1.1

(data

hold)

5

DS

FOO

6

FOO

L

~

X

hold

PE'

DS

L H

hold

Tse

=

6.0

(PE'

setup)

7[;}3

5

PE'

a2f

CC

CCMR

CC

CC

MR

FOO

(all

times

estimates)

13

412

13'

4

12

F10016

d

t(S)

4

F16

O(S) O(S)

11Q14

5

PE'

co

b3t

4

bit

Binary

Counter

b3b

C

MRCE'

F16

.

11~14

9{;D2

13 12

6

4

F16

F16

CE

PE'

MR

P

UNCTION

CO

Tpd

=

5.5

11

14

L L

tt

oaral

elload

10

DO

HO

15

H L

tt

ara

elload

Tw

=

3.5(clock

pulse

width)

9

D1

Hi

2

10~15

7f:}3

L H

tt

H2

coun

Ts

=

2.2

(data

setup)

7

D2

3

F16 F16

H H

tt

hold

D3

H3

X

ast

rs

aDen

slaves

hold

Th

=

1.1

(data

hold)

5

F16

M(8)

X

)(

PE'

F16

b2t

X

rase

Tse

=

2.S(PE'

and

CE'

setup)

b1a

5

1-4

C

MRCE'

PE'

CO'

13 12

6 C

MR

CE'

13 12

6

A(S)

obsolete:

MC130

Dual

Latch

r;J

CC

MC130

9

(~

b c c N(S) D C S R

On+1

I

FUNCTION

5

12

~

I

c2d

L"

L L X X a

folio

sD

Tpd

=

4.1

7 DS a

10

MC130

H L X X h a

folio

sO

Ts

=

2.S

est

2

Dsa

15

7 D S a 2 X L L a

old

CC

Th

=

1.7

est

6

cia

c1b

c2c

X L L a h

Id

9 X H L s t

C

11

14

6

9

CCRa'

3 C a' C

a'

.3 X H L s t

MC130

R R

MC130

X

'H

L H r

set

X L H r

set

4

13

4 X

Ii

H H

in

eter

inate

SE231

(Selective

MC231)

A(S)

MC131

C

obsolete:

5 I d

,

3d

I

MC231

Dual

D

type

Master-Slave

Flip-flop

CC

MC131

7

Dsa

2 X X X H H

indeterminate

9

b C

d2c

D

....

C

....

.li R

an

+ 1 I

FUNCTION

7+

~

6 C Q,3 X L L L a h

Id

MC131 MC231

SE231

L t t L L L m

mo

p/

2

10

S

15

R

MC131

L t L L L L m

moiv

D a D a

Tpd

=

5.0

Tpd

=

3.7

6

d1a

d1b

4 H t L L H m

mo

Tpd=

2.5

C

11

N(S) H t L L H m

mo

Iv.

Ts

=

2.S

Ts

=

1.1

Ts

=

1.1

3 C

14

X X H L h s t

9.

CC

a'

a'

d2d

I X X L H L r

set

Th

=

1.7

Th

=O.S

Th

=O.S

R

MC131

R

MC131

X H H

in

ete

iminate

(all

times

estimates)

4

13

CC

X H H

in

ete

minate

9

A(S)

MC135

Dual

J-K

Master

Slave

Flip-Flop

obsolete:

~

CC

MC135

4 5 5

N(S)

9

5

~ ~

RS

Truth

Table

Clocked

JK

Truth

Table

I

e2d

I

7 J'S a 2

10

J'S a

15

7 J'S a 2

~g135

R

n+1

J'

K'

On+1

Tpd

=

4.6

(

-:;'

L L n L

n'

e1a

L H I H

Trs

=

5.aR,

5

to

Q)

CC

e1b

e2c

9 H

1.

L

6

K'

a'

3

11

K'

Q'

14

6

K'

a'

3 H H i

det

H H

Ts

=

2.S

est

n

R

MC135

R R

MC135

Th

=

1.7

est

4 7 4

clock

=

tt

on

CC

XEROX

Project

File

Designer

Rev

Date

Page

SOD

Datashee

ECl

MSI

data

sheet

MC·3.sil

K.

Pier

B

5/15/78

3

-

--'

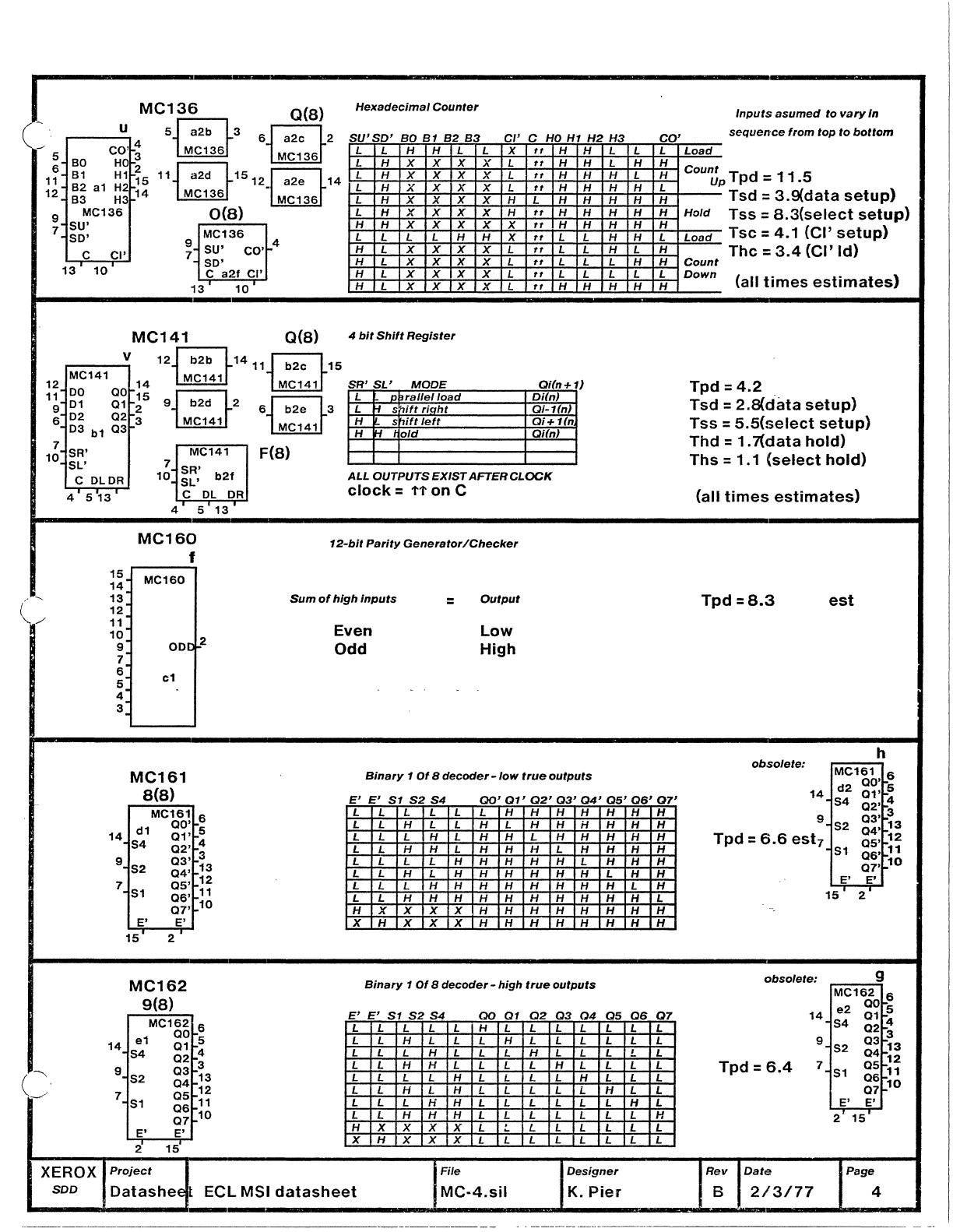

MC136

O(S)

Hexadecimal

Counter

U

-~

5{;;J3

6~2

SU'SD'

BO

B1

B2

B3

CI'

C

HO

H1

H2

H3

CO

MC136

L L H H L L X

tt

H H

5

BO

HO

3

MC136

L H X X X X L " H H

6 2

11

B1

H1

15

11~1512_~14

L H X X X X L

tt

H H

12

B2

a1

H2

14

MC136 MC136

L H X X X X L " H H

B3

H3

L H X X X X H L H H

9

MC136

0(8)

L H x X X X H " H H

7

5U'

H H X X X X X " H H

so'

MC136

L L L L H H X

tt

L L

9

5U'

CO' 4 H L X X X X L L L

C

CI'

7 "

SO'

H L X X X X L " L L

13

10

C

a21

CI'

H L X X X X L

tt

L L

13 10

H L X X X X L " H H

MC141

O(S) 4

bit

Shift

Register

...-

__

--.v

12~1411~15

~~

~'4'

~~:

.~

Mb::"~2

~MC141

rSL:-:R_'rS:=,L_'

D,....:r:~I1~~::r-~i=~-ad~----r-:D~~~/~~j..:.+-i1}

9

02

02

2 6

b2e

3

""L;:;-r.-,,::sI;:n-¥;iif,:-t

7:ri~ajh~t:..-

___

-t~0~i;;.;-1~(nf7.}::t

6

03

031-

3

MC141

MC

141

t-'H~£7-~St:~7;if:.tI:.::e""ft'--

____

-H0:;;ii:+:T'.:.:(n~

b1

t-'H~rH~ro~/d~

_____

~~O=i~m~}~

~-

SR'

MC141 F(S)

10

SL'

7

SR'

C

OL

DR

10

SL'

b21

4'

5

13

C

OL

DR

15_

14

13

12

11

10

~

~-

6

5

4

3

4

MC160

f

MC160

5

13

000

2

cl

MC161

ALL

OUTPUTS

EXIST

AFTER

CLOCK

clock

=

tt

on

C

12-bit

Parity

Generator/Checker

Sum

of

high

Inputs

Even

Odd

=

Output

low

High

Binary

1

Of

B

decoder-low

true

outputs

L

L

H

H

H

H

H

H

H

L

L

H

CO'

L L

H H

L H

H L

H H

H H

H H

H L

L H

H H

L L

H H

8(8)

E'

E'

S1

S2

S4

00'

01'

02'

03'

04'

05'

06'

07'

MC161

6 L L L L L L H H H H H

dl

00'

5 L L H L L H L H H H H

14

01'

L L L H L H H L H H H

54

02'

4 L L H H L H H H L H H

3

9

03'

1-

13

L L L L H H H H H L H

S2

04'

L L H L H H H H H H L

7

Sl

05'

12

L L L H H H H H H H H

11

06'

L L H H H H H H H H H

07'

10

H X X X X H H H H H H

E' E' X H X X X H H H H H H

15

2

MC162

Binary

1

Of

B

decoder

-

high

true

outputs

9(S)

MC162

E'

E'

S1

S2

S4

00

01

02

03

Q4

05

6 L L L

el

00

5 L L H

14

S4

01

I-~

L L L

02

L L H

9

03

3

(~.

52

04

13

L L L

7.

51

05

12

L L H

06

11

L L L

07

10

L L H

H X X

E' E' X H X

2

15

XEROX

Project

SDD

Datashee

t

ECl

MSI

datasheet

L L H L

L L L H

H L L L

H L L L

L H L L

L H L L

H H L L

H H L L

X X L .

~

X X L L

File

MC-4.sil

L L

L L

H L

L H

L L

L L

L L

L L

L L

L L

L L

L L

L L

L L

H L

L H

L L

L L

L L

L L

Designer

K.

Pier

H H

H H

H H

H H

H H

H H

L H

H L

H H

H H

06

07

L L

L L

L L

L L

L L

L L

H L

L H

L L

L L

Inputs

asumed

to

vary

In

sequence

from

top

to

bottom

Load

cou~p

Tpd

= 11

.5

Tsd

=

3.9(data

setup)

Hold

Tss

=

S.3{select

setup)

Load

Tsc

=

4.1

(CI'

setup)

Count

Thc

=

3.4

(CI'

Id)

Down

(all

times

estimates)

Tpd

=

4.2

Tsd

=

2.8(data

setup)

Tss

=

5.5(select

setup)

Thd

= 1

.7(data

hold)

Ths

= 1 .1

(select

hold)

(all

times

estimates)

Tpd

=S.3

est

h

obsolete:

14

9

Tpd

=

6.6

est

7

obsolete:

14

9

Tpd

=

6.4

7

Rev

Date

B

2/3/77

MC161

00'

6

d2

01'

5

S4

02'

4

03'

3

52

04'

13

_~2

05'

-

S1

06'

11

10

07'

E' E'

15

2'

g

MC162

QO

e2

S4

01

02

03

S2

04

05

Sl

06

07

E'

E'

2

15

Page

4

6

5

4

3

1-!3

12

11

1-

10

-.

-------------

---------------

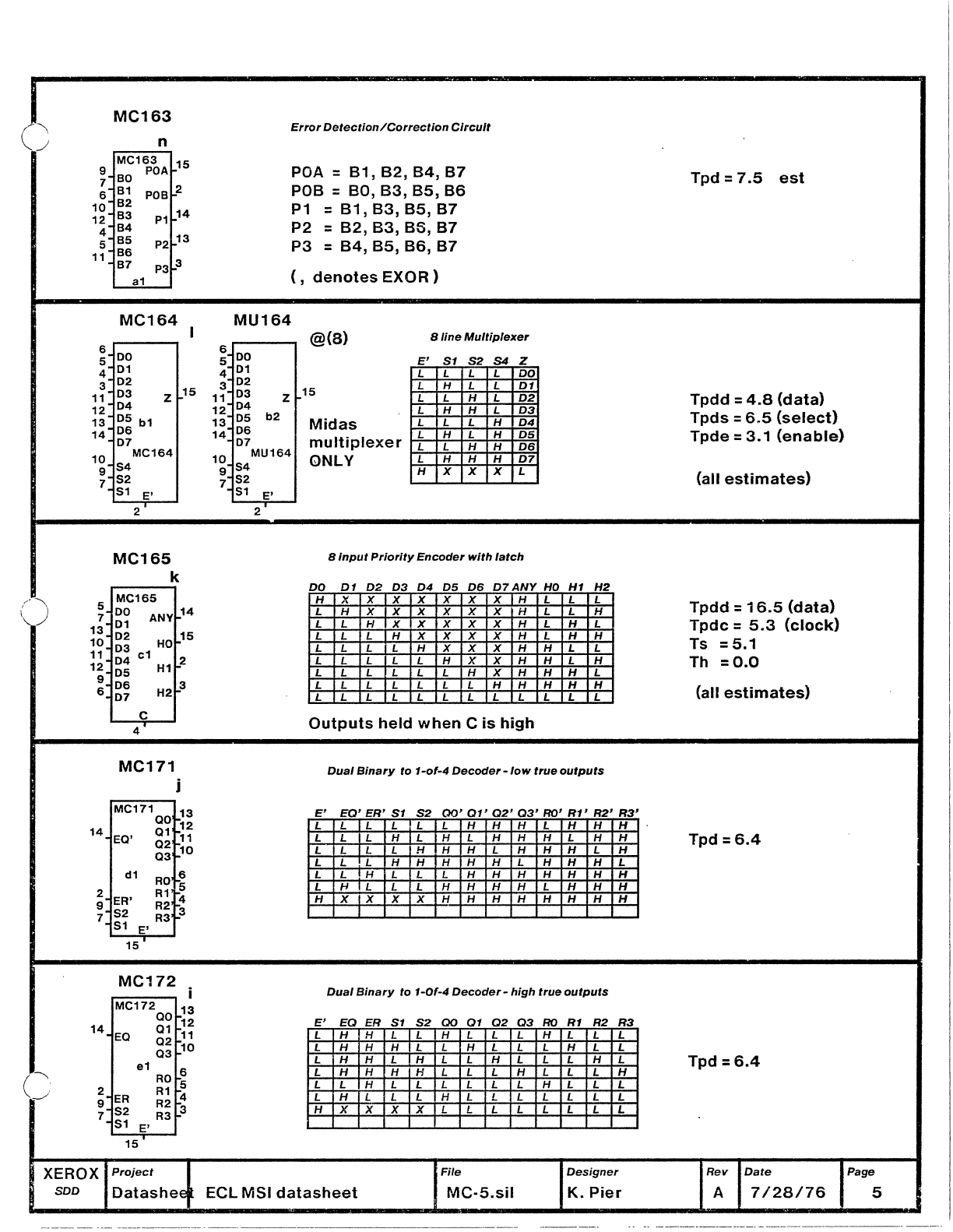

MC163

()

Error

Detection/Correction

Circuit

n

MC163

15

9

BO

POA

POA =

81,82,84,87

Tpd

=

7.5

est

~.

B1

POBr

2

P08

= BO,

83, 85,

86

6

B2

10

B3

14

P1

=

81,83,85,87

12

B4

P1

P2

=

82,

83,

8S,

87

~.

B5 P2 r13

P3

=

84,

85, 86,

87

5 B6

11

B7 P3 3

al

(,

denotes

EXOR)

MC164

MU164

I @(s) 8

line

Multiplexer

~,

6

~,

00

~,

00

E'

S1

S2

S4

Z

01

01 L L L L DO

4

02

4

02

3 3 L H L L

D1

11

03

Z

15

11

03

Z

15

L L H L

D2

Tpdd

=

4.S

(data)

12

04

12

04

L H H L

D3

13,

05

bl

1~,

05

b2

Midas

L L L H

D4

Tpds

=

6.5

(select)

14,

06

14,

06

L H L H

D5

Tpde

=

3.1

(enable)

07

07

multiplexer

L L H H

D6

10

MC164

10

MU164

ONLY

L H H H

D7

9

54

9

54

H X X X L

(all

estimates)

7,

52

7

52

51 E' 51 E'

2 2 •

MC165

8

input

Priority

Encode,

with

latch

k DO

D1

D2

D3 D4

D5

D6

D7ANY

HO

H1

H2

/") 5 MC165 H X X X X X X X H L L L

Tpdd

=

16.5

(data)

00

14

L H X X X X X X H L L H

7 01

ANY

L L H X X X X X H L H L

Tpdc

=

5.3

(clock)

13

02

r

15

L L L H X X X X H L H H

10

03

HO

L L L L H X X X H H L L

Ts

=5.1

11

04

c1 2 L L L L L H X X H H L H Th

=0.0

12

05

H1

L L L L L L H X H H H L

9

06

H2

3 L L L L L L L H H H H H

6

07

L L L L L L L L L L L L (all

estimates)

C

Outputs

held

when

C

is

high

4

MC171

Dual

Binary

to

1-ot-4

Decoder

-low

true

outputs

j

MC171

13

E'

EO'

ER'

S1

S2

QO'01'02'03'RO'R1'R2'R3'

QO

12

L L L L L L H H H L H H H

14

EQ'

Q1

11 L L L H L H L H H H L H H

Tpd=6.4

Q2

.10

L L L L H H H L H H H L H

Q3 L L L H H H H H L H H H L

d1

RO

6 L L H L L L H H H H H H H

2

R1

5 L H L L L H H H H L H H H

9 ER'

R2

4 H X X X X H H H H H H H H

7.

52

R3·

3

Sl

E'

15 •

MC172

i

Dual

Binary

to

1-0f-4

Decoder

-

high

true

outputs

MC172

r~3

QO

E'

EO ER S1

S2

QO

01

02 03

RO

R1

R2

R3

14

Q1

12

EQ

Q2 11 L H H L L H L L L H L L L

Q3

10

L H H H L L H L L L H L L

L H H L H L L H L L L H L

Tpd

=6.4

e1

RO

6 L H H H H L L L H L L L H

()

~,

Rl

5 L L H L L L L L L H L L L

ER

R2

r!

L H L L L H L L L L L L L

9

S2

R3

3 H X X X X L L L L L L L L

7

Sl

E'

15

XEROX

Project

File

Designer

Rev

Date

Page

SDD

Datashee

ECl

MSI

datasheet

MC,5.siI

K.

Pier

A

7/28/76

5

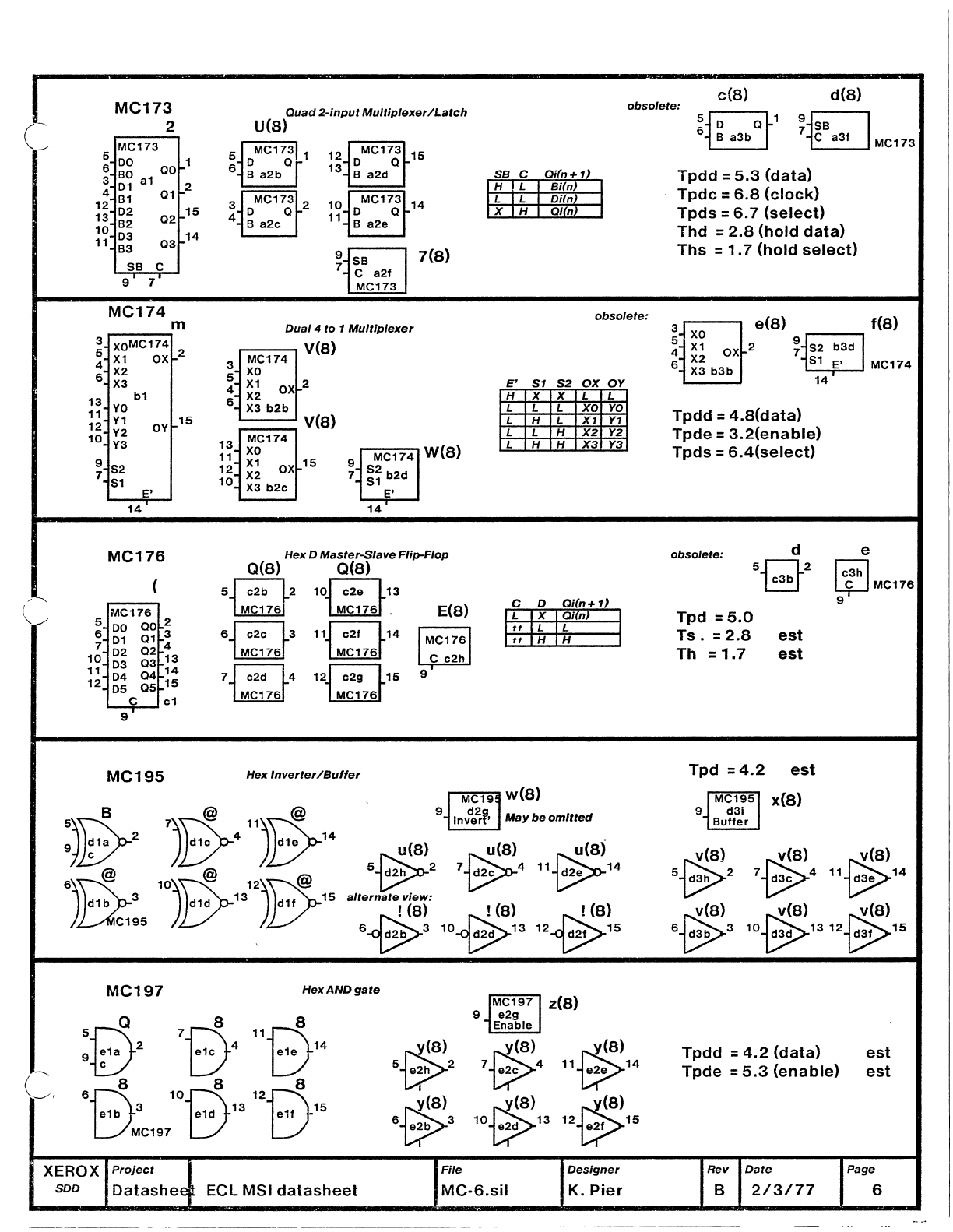

MC173

2

Quad

2-input

Multiplexer/Latch

obsolete:

C{S)

5~1

6~

deS)

9.rs;----,

---',

MC173

5

6·

DO

00t-1

3

BO

a1

2

4

D1

01

12

B1

13

D2

10

B2

11

D3

02t-15

B3

14

03

SB

C

9

7'

MC174

m

.......

--..,

3

XOMC174

5

X1

OX

2

4

X2

6.

X3

13

b1

11

YO

12

Y1

OY

15

10

Y2

Y3

9

82

7

81

E'

14

MC176

(

MC176

5

DO

00

2

6

D1

Q1

3

7

D2

Q2

4

10

D3

Q3

13

1~.

D4

Q4

14

12.

D5

Q5

t-

15

C

c1

9

MC195

U(S)

MC173

1

1~.

MC173

15

5 D Q

D Q 13

6 B a2b B a2d

MC173

MC173

3 2

1~.

14

D 0

11

o Q

4 B a2c B a2e

7(S)

~-

SB

7_

C a2f

MC173

Dual

4

to

1

Multiplexer

V(S}

3

MC174

5

XO

4

X1

OXt-

2

6

X2

X3

b2b

V(S)

MC174

W(S}

13

XO

9

MC174

1

~.

X1

15

1~.

X2

OX

7-

S2 b2d

10

X3

b2c

S1

E'

14

Hex D

Master-S/ave

Flip-Flop

O(S) O(S)

5~2

10[";;"113

~~-

6~3

11~14

~

~

7~4

12~15

~

~

Hex

Inverter/Buffer

E(S)

I

MC1761

C C2hJ

9'

SB

C

Qi(n+

t!

I H ! L i

Bi(n}

J

L L Di('1l J

IX

H Qi(nL J

obsolete:

E'

S1

S2

OX

OY

H X X L L

L L L

XO

YO

L H L

X1

Y1

L L H X2

Y2

L H H X3

Y3

C D

Qi(n+

11

Qt(n} I

I

tt

iL

L I

Itt

iH

H .J

MC11

w(S)

9

Invde~r,

May

be

omitted

B

)~")~

~V2

d1c 4 d1e 14

U(S)

~

U(S)

10)~

12)~

58>2

7 d2c 4

11~14

6)rt.,

d1d

13

d1f

15

alternate

view:

!CS) !

(S)

!

(S)

C195

613>3

10~13

12~15

,

MC197

MC197

Z(S}

9 e29

Enable

~

~

~

5 e2h 2 7 e2c 4

11

e2e

14

~ ~

~

6 e2b 3 10

e2d

13

12 e2f 15

DO

78

s

118

s

:V

2 e1c 4 e1e

14

68

S

1°8S

128S

e1b 3

e1d

13

e1f 15

MC197

Hex

AND

gate

XEROX

Project

File

Designer

SDD

Data8hee~

ECl

MSI

datasheet

MC·6.sil

K.

Pier

----

-

7~MC173

Tpdd

=

5.3

(data)

Tpdc

=

6.S

(clock)

Tpds

=

6.7

(select)

Thd

=

2.S

(hold

data)

Ths

= 1

.7

(hold

select)

e(S}

...------,

~-

xo

~t

!

~~

OXI-2

~

~~

b3d

6

X3

b3b

E'

14

Tpdd

=

4.S(data}

Tpde

=

3.2(enable}

Tpds

=

6.4(select)

obsolete:

e

rc;;]

f(S}

MC174

~MC176

9

Tpd

=5.0

Ts.

=

2.S

est

Th

=

1.7

est

Tpd

=4.2

est

MC195J

xes)

9

d31

Buffer

v(S)

5~2

v(S)

v(s)

7~4

11~14

v(S}

6B>3

v(S)

v(S}

10~1312~15

Tpdd

=

4.2

(data)

est

Tpde

=

5.3

(enable)

est

Rev

Date

Page

B

2/3/77

6

-

0-

---

---

,

~

./

--...

MC140

MCM140

MC142

MCM142

64

Bit

Random

Access

Memory

MC14S

MCM14S

0(S)

13

~5

13~15

Tace

=

14(E'

access)

01

DOf-'

~

(setup

times)

2

AO

~.

A1 2

AO

yeS)

~

A2

a1

~

A1

MC140

Taad

=

11(Ai

access,

MCM142)

Taad

=

17(Ai

access,

MCM140,

148)

Tw'

= 11

(write

pulse

width)

Tsd

=0

Tse=3.5

Tsa=5.5

10

A3

7

A2

A4

A3

9.

A5

1~.

A4

a2c

MCM142

9

A5

W'

E' E' W' E' E'

12

5 4

12

5 4

F145A

F10145A

Te'

=

15

(enable

pulse

width)

(MCM

140

drives

90

ohm

loads)

16

x 4

Register

File

F10145:

Thd

=

3.5

(hold

times)

The

=0

Tha

=3.5

(all

times

estimates)

obsolete:

MC145

MCM145

O(S)

.-

__

..,r

5~2

Tace

=

6.6E'

access)

Taad

=

9.~Ai

access)

a(S) B b(S)

10

AO

5 0 Q 2

b3b

9

MCM145

7 A1

b3t

6

A2

Thd

=

-1.0

A3

.

1~.

AO

~

9 A1

~

A2

b1

4~1

~~0145A

~

5

00

00

2

~

4.

01

01

~~

11

b2d

15

11,.

02

02

15

F145A

12

03

03

14

CE'

WE'

12~14

3'13'

~

MC147

O(S)

MCM147

s

11~15

11

MCM147

15

MC147

01

DO

O(S)

4

3

AO

4 AO

2 A1 3 A1

MC147

A2

c1 2

5

A3

~.

A2

6

A4 A3

c2c

7

A5

~.

A4

10

7

A5

A6

1'0

W'

E' E'

A6

W'

E'

E'

12

14

13

12'

14'

13'

MC149

MCM149

MC150

MCM150

•

4

MCM149

2

AO

00

15

3 A1

9

A2

01

14

:.

A3

1~.

A4

d1

12

6

A5

02r'

5

7

A6

03

11

A7

_CE'

13

F415A

F10415A

O(S)

Hs

2

F415A

3

AO

A1

~.

A2

5

A3

15_

01

2

AO

3 A1

4

A2

5

A3

6

A4

7

A5

15~1

~

6

A4

e2c

7

A5

9

Tsd

=5.0

Z(S)

Tw'

=

4.4(write

pulse

width)

Tse

=

5.0

Te'

=

4.4

(enable

pulse

width)

Tsa

=

3.9

Twr.

=

6.6

(ce,we

output

recover)

CE'

WE'

The

=

0.5

3

13'

Tha

=

1.0

10

F145A

9

AO

A1

MCM145:

Tsd,

Tse

relative

toend-o#-WE'

~-

A2

b2f

A3

Tace

=

10(E'

access)

Tsd

= 0

Thd

=

5.0

CE' WE'

3

13'

Taad

=

15(Ai

access)

Tse

=

5.0

The

=

5.0

Tw'

= 11

(write

pulse

width)

Tsa

=

5.0

Tha

=

5.0

Te'

=

11

(enable

pulse

width)

Twr

=

11.0

128

x 1

bit

Random

Access

Memory

Tace

= 8.SE'

access)

Taad

=

14(Ai

access)

Tw'

=

8.8(write

pulse

width)

Te'

=

11

(enable

pulse

width)

Tsd

=

1.0

(setup

times)

Tse

=

1.0

Tsa

=4.0

Thd

= 1

.0

(hold

times)

The

=

1.0

all

est

All

UNUSED

INPUTS

MUST

BE

TIED

TO

VEE

Tha

=

3.0

(all

times

estimates)

256

x 4

bit

Programmable

ROM

MCM149

MCM150

Tace

=

13

Tace=

10.5

Taad=32

Taad=30

(all

times

estimates)

3

1024

x 1

bit

Random

Access

Memory

e1

Tace

=

10(E'

access)

Tsd

=5

(setup

times)

Taad

=

35(Ai

access)

•

Tse

=5

DC

1

Tw'

=

25

(write

pulse

width)

Tsa

=8

L-

10

A6

A7

11,_

AS

12_

A9

9

10

11,

•

A6

Te'

=

35

(enable

pulse

width)

A7

• a

25ns

Taad,

20

ns.

Tw'

par'

is

available

Thd

=5

(hold

times)

CE'

WE'

14

13

XEROX

Project

12

AS

A9

F415A

CE'

WE'

14

13

SOD

Datashee

ECl

MSI

datasheet

(all

times

estimates)

File

MC-7.sil

Designer

K.

Pier

---------

---------------

--

--

The

=5

Tha

=2

Rev

Date

B

2/14/77

----------------

Page

7

I~

11

5

13

9

12

7

10

4

14'

'.

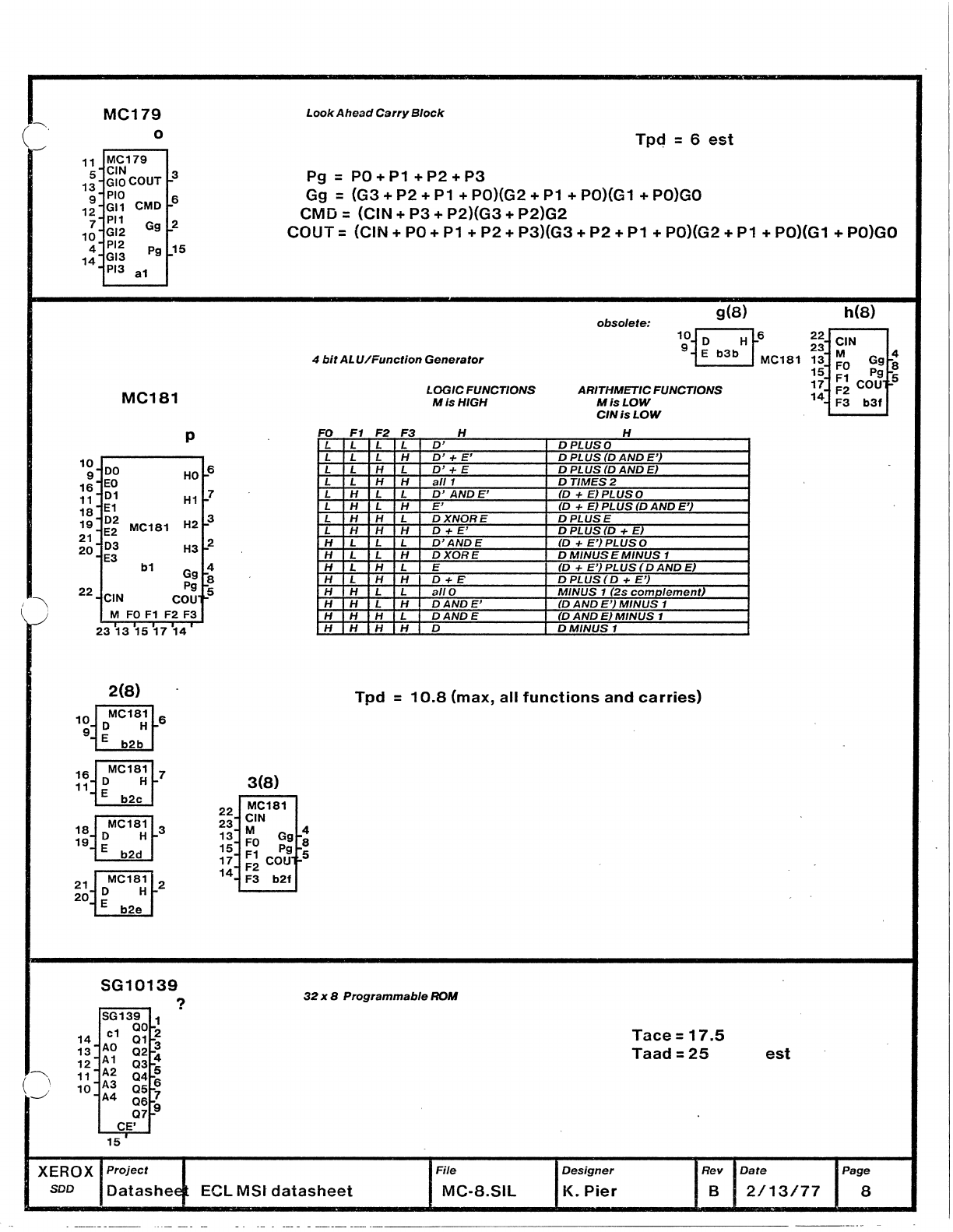

MC179

o

MC179

CIN

GIOCOUT

PIO

GI1

CMD

PI1

Gg

GI2

PI2 Pg

GI3

PI3 a1

3

6

2

.15

MC181

10

DO

9

16

EO

01

11,.

E1

p

HO

6

H1

7

18.

02

19.

E2

21"

03

20

E3

MC181

H2

3

H3

2

b1

22.

CIN

Gg

4

Pg

8

COU 5

M

FO

F1

F2

F3

2313151714

2(8)

10

MC181

6

9 0 H

'.

E

b2b

16

MC181

7

11

0 H

E

b2c

18

MC181

3

19

0 H

E

b2d

21

MC181

2

20

0 H

E

b2e

SG10139

SG139

1

c1

00~2

14

AO

01

3

13

A1

02

4

12

A2

03

5

11

A3

04

6

10

A4

05

7

06

9

Q7

CE'

15

?

XEROX

Project

Look

Ahead

Carry

Block

Tp~

= 6

est

Pg =

PO

+ P1 +

P2

+

P3

Gg =

(G3

+

P2

+

P1

+ PO)(G2 +

P1

+ PO)(G1 + PO)GO

CMD

=

(CIN

+

P3

+

P2)(G3

+

P2)G2

COUT

=

<CIN

+

PO

+

P1

+

P2

+

P3)(G3

+

P2

+ P1 + PO)(G2 + P1 + PO)(G1 + PO)GO

obsolete:

g(8)

4

bit

ALU/Function

Generator

10M-6

9 E

b3b

MC181

LOGIC

FUNCTIONS

ARITHMETIC

FUNCTIONS

Mis

HIGH

Mis

LOW

elN/sLOW

FO

F1

F2 F3

H H

L L L L

0'

o

PLUS

0

L L L H

D'+E'

o

PLUS

(0

AND

E')

L L H L

D'+E

o

PLUS

(0

AND

E)

L L H H

all

1 o

TIMES

2

L H L L

0'

ANDE'

(0

+

E}PLUSO

L H L H

E'

(0

+

E)

PLUS

(0

AND

E'r

L H H L

DXNORE

DPLUSE

L H H H

D+E'

o

PLUS

(0

+

E)

H L L L

D'ANDE

(0

+

E')PLUSO

H L L H

DXORE

o

MINUS

E

MINUS

1

H L H L E

(0

+

E')

PLUS

(0

AND

E)

H L H H

D+E

o

PLUS

(0

+

E'}

H H L L

all

0

MINUS

1

(2s

complement)

H H L H

DANDE'

(0

AND

E')

MINUS

1

H H H L

DANDE

(0

AND

E)

MINUS

1

H H H H 0 o

MINUS

1

Tpd

=

10.8

(max,

all

functions

and

carries)

3(8)

22

MC181

23'

CIN

13

M

Gg

4

15

~~

pg:

1~.

F2

COU

14.

F3

b2t

32

x 8

Programmable

ROM

File

Tace=

17.5

Taad

=25

est

Rev

Date

h(8)

22

CIN

23

M

~!

13

FO

Gg

15

Pg 8

5

17

F1 COU

14

F2

F3

b3t

Page

SOD

Datashee

Eel

MSt

datasheet

MC·8.SIL

Designer

K.

Pier

B

2/13/77

8

-----------------------

--------

--

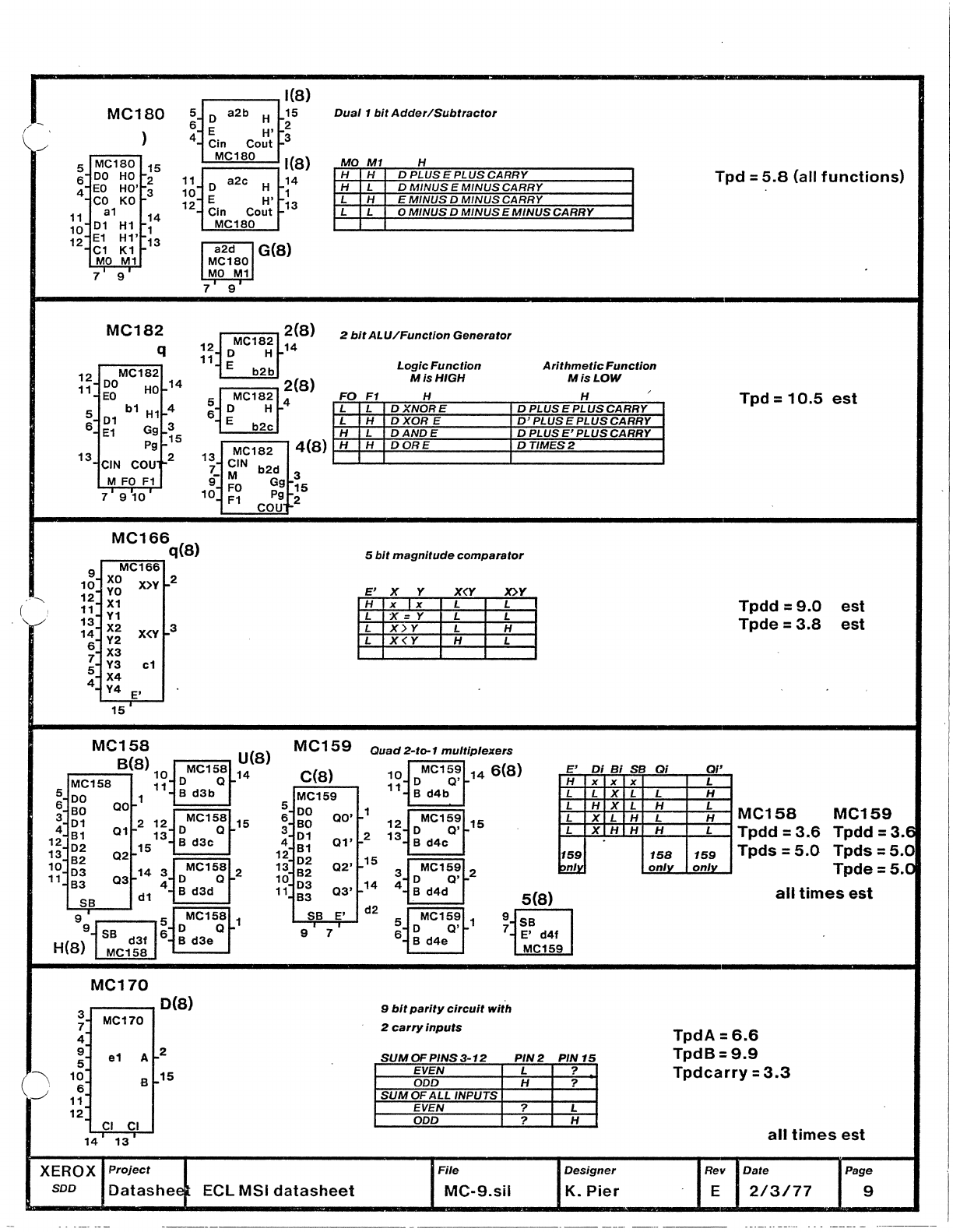

1(8)

MC180

5 o

a2b

H

15

Dual

1

bit

Adder/Subtractor

,,--

6 E 2

) 4

H'

3

../

Cin

Cout

MC180

MC180

1(8)

MO

M1

H

5

15

6

DO

HO

2 11 o

a2c

14

H H o PLUS E

PL

US

CARRY

Tpd

=

5.8

(all

functions)

4

EO

HO' 3

10

H 1 H L o

MINUS

E

MINUS

CARRY

CO

KO

12.

E

H'

..13 L H E

MINUS

0

MINUS

CARRY

11

a1

14

Cln

Cout

L L o

MINUS

0

MINUS

E

MINUS

CARRY

10

01

H1

1

MC180

12

E1

H1'

13

C1

K1

a2d

;1

G(8)

MO

M1

MC180

7

9'

MO

M1

7'

9

MC182

2(8)

2

bit

AlU/Functlon

Generator

MC182

q

12

0 H

14

11

MC182

E

b2b

Logic

Function

Arithmetic

Function

1~.

DO

14

2(S)

Mis

HIGH

Mis

LOW

11

EO

HO

MC182

FO

F1

H H /

Tpd

=

10.5

est

b1

H1

4 5 0 H 4 L L

DXNORE

o PLUS E

PLUS

CARRY

5 6 E L H

OXORE

0'

PLUS E

PLUS

CARRY

6 01 3

b2c

E1

Gg H L

OANOE

o PLUS

E'

PLUS

CARRY

Pg

15

4(S) H H

OORE

o

TIMES

2

MC182

13.

CIN COU ..2

1~.

CIN

b2d

7 3

M

FO

F1

9-

M

FO

Gg

15

7

910

10

Pg

~2

F1

COU

MC166

q(8) 5

bit

magnitude

comparator

9

MC166

10

XO

X)Y

2

1~_

YO

E'

X Y

X(Y

x>y

--,

X1

H x x L l

Tpdd

=9.0

est

( !

1~_

Y1

L

x=y

L L

"-

13

Tpde

=

3.8

est

X2

3 L

X)Y

L H

14

Y2

X<Y

L

X<Y

H L

6

X3

7 Y3 c1

~.

X4

4.

Y4

E'

15

MC15S

U(S)

MC159

Quad

2-t0-1

multiplexers

B(8)

MC158

C(8)

MC159

14

6(8)

E'

Di

Si

SS

Qi

QI'

10

0 Q

14

10

0

0'

H L

MC158

11

11

x x x

5

DO

1 B

d3b

MC159

B

d4b

L L X l L H

6

QO

5 L H X L H l

BO

DO

1

MC15S

MC159

3

01

2

12

MC158

f0015

6

BO

00'

12

MC159

~15

L X L H L H

4

01

o Q 3 o

Q'

L X H H H l

Tpdd

=3.6

Tpdd

=3.6

12

B1

13

B

d3c

4

01

Q1'

2

13

B

d4c

13

02

02

15

12

B1

159

158

159

Tpds

=5.0

Tpds=5.0

B2

02

..

15

10

03

14

3

MC158

f002

1~.

B2

02'

~-

MC159

2

e!!!l!

onlv

onbL

Tpde=5.0

11

B3

03

4.

o Q

1~.

03

14

o

Q'

B

d3d

03'

4 B

d4d

all

times

est

d1

11

B3

5(8)

SB

MC158

SB

E'

d2

MC159

~.

SB

9 5

f001

~-

1

9 SB 6_ o 0 9 7 o

0'

7

E'

d4f

d3f

B

d3e

6 B

d4e

H(8)

MC158

MC159

MC170

D(S) 9

bit

parity

circuit

with

3

7

MC110

2

carry

inputs

4

TpdA

=6.6

9 a1 A 2

SUM

OF

PINS

3-12

PIN

2

PIN

15

TpdB=9.9

5 EVEN L ?

Tpdcarry

=

3.3

\

10

a

f0015

000

H ?

6

SUM

OF

ALL

INPUTS

11 EVEN ? L

12

CI

CI

000

? H

all

times

est

14 13

XEROX

Project

File

Designer

Rev

Date

Page

SOD

Datashee

ECl

MS.

datasheet

MC-9.sil

K.

Pier

E

2/3/77

9

----------

---

----

----

MC175

(

(8)

--,

10

MC175

14

( , 12·

DO

00

15

\.J

13

01

01

2

9

02

02

3

03

03

5.

04

04r

4

a01

CCCCMR

6

711

F470

$

(8)

Quint

Latch

Q

(8)

10

MC175

14

a01b

12

MC175

15

a01c

13

MC175

2

a01d

9

MC175

3

a01e

5

MC175

4

a01f

I

MC175

I )

(8)

Icc

cc

MRI

a019

6 7 11

4K

x 1

random

access

memory

Q

(8)

2

F470

3

AO

17~1

Taad

Taee

Tw'

Tsd

Thd

Tsa

Tha

=

35

=

15

=

25

A

access

CEaccess

write

pulse

setup

data

hold

data

setupaddr

hold

addr

setupCE

holdCE

4 A1

l.ruwJ

= 5

5

5

A2

6

A3

A4

~-

A5

S

10

A6

b01c

11

A7

12

AS

A9

13

A10

14. A 11

CE'

WE'

16 15

MB071

%

(8)

7

AO

S A1

9

10·

A2

c01f

11

A3

12

A4

13

A5

14

A6

A7MB071

6 BSO'

5

BS1'

4

BS2'

3

BS3'WE'

2

XEROX

Project

=

=

Tsee

=

Thee

=

Twd

=

10

5

5

5

=

15

=

20

=

15

Twr

Teer

write

disable

write

recover

CE

recover

256

x 4

random

access

memory

O/Tpackage

+

platform

Q

(8)

19

MB071

23

c01b

18

MB071

22

c01c

17

MB071

21

c01d

16

MB071

20

c01e

Taad

Tabs

=

=

10.0

4,5

8.0

2.0

2.0

2.0

2.0

2.0

2.0

5.0

9.0

4.5

Tw'

Tsd

Thd

Tsa

Tha

=

=

=

=

=

Tsbs

=

Thbs

=

Twd

=

=

Twr

Tbsr

=

A

access

BSaccess

write

pulse

setup

data

hold

data

setup

addr

hold

addr

setup

BS

hold

BS

write

disable

write

recover

BS

recover

File

D

CC

CC

MR

Q(n+1

L L L L L

H L L L H

X H X L

O(n)

X X H L

O(n

X H X H L

X X H H L

3.6

4.4

4.2

Tpdd

=

Tpde

=

Tpdr

=

Ts

=

3.7

=

2.2

Th

F414

256

x 1

random

access

memory

-

(8)

1

AO

2 A1

3

A2

4

A3

9

F414

10

A4

A5

1!.

A6

12

A7

b02c

5 CSO'

6

CS1'

7

CS2'

WE'

14

Q

(8)

13~15

~

Taad

=

Taee

=

Tw'

Tsd

Thd

Tsa

Tha

=

=

=

=

=

Tsee

Thee

=

Twd

=

=

10

6

7

1

2

1

2

1

2

8

Twr

Teer

=

10

6

=

(data)

(clock)

(reset)

(setup)

(hold)

A

access

CEaccess

write

pulse

setup

data

hold

data

setup

addr

hold

addr

setup

CE

holdCE

write

disable

write

recover

CE

recover

F181K

100K

series

4

bit

ALU

0.4

wide

DIP

package

2 (8)

&

(8)

22

F181K

5

15

0 H

E

c02b

11

F181K

19'

CIN'

21'

OE'

G'

10

23

F181

K 4

20

FO

P' 9

14

0 H

17

F1

CO'

8 E

c02c

F2

16

F3

c02f

24

F181K

3

13'

0

HI-'

I,

E

c02d

1

F181K

2

12

0

HI-'

~-

E

c02e

Tdh

Teh

Tfh

Teinh

Teio

Tdpg

Tepg

Tfpg

Tdeo

=

6.5

=

6.5

=

6.5

=

4.7

=

3.6

=

4.1

=

4.1

=

4.1

=

5.4

Teeo

=

5.4

Tfeo

=

5.4

Toeh

=

2.1

Rev

Date

OtoH

Eto

H

Fto

H

CINtoH

CIN

to

CO

Oto

P,G

Eto

P,G

Fto

P,G

OtoCO

EtoCO

FtoCO

OEto

H

SDD

ECl

SSI

Oatasheet

MC11.sil

Designer

K.

Pier

A

9/7/78

Page

11

-----------

-

-----------