Core Instructions

core_instructions

core_instructions

core_instructions

core_instructions

core_instructions

User Manual: Pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 250 [warning: Documents this large are best viewed by clicking the View PDF Link!]

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 377 of 785

addx addx

Add (x’7C00 0214’)

add rD,rA,rB (OE = 0 Rc = 0)

add. rD,rA,rB (OE = 0 Rc = 1)

addo rD,rA,rB (OE = 1 Rc = 0)

addo. rD,rA,rB (OE = 1 Rc = 1)

[POWER mnemonics: cax, cax., caxo, caxo.]

rD ← (rA) + (rB)

The sum (rA) + (rB) is placed into rD.

The add instruction is preferred for addition because it sets few status bits.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO (if Rc = 1)

Note: CR0 field may not reflect the infinitely precise result if overflow occurs (see XER below).

• XER:

Affected: SO, OV (if OE = 1)

Note: The setting of the affected bits in the XER is mode-dependent, and reflects overflow of the 64-bit

result in 64-bit mode and overflow of the low-order 32-bit result in 32-bit mode. For further information

about 64-bit mode and 32-bit mode in 64-bit implementations, see 4.1.2 , “Computation Modes.”

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XO

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 378 of 785

pem8.fm.2.0

June 10, 2003

addcxaddcx

Add Carrying (x’7C00 0014’)

addc rD,rA,rB (OE = 0 Rc = 0)

addc. rD,rA,rB (OE = 0 Rc = 1)

addco rD,rA,rB (OE = 1 Rc = 0)

addco. rD,rA,rB (OE = 1 Rc = 1)

[POWER mnemonics: a, a., ao, ao.]

rD ← (rA) + (rB)

The sum (rA) + (rB) is placed into rD.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

Note: CR0 field may not reflect the infinitely precise result if overflow occurs (see XER below).

• XER:

Affected: CA

Affected: SO, OV(if OE = 1)

Note: The setting of the affected bits in the XER is mode-dependent, and reflects overflow of the 64-bit

result in 64-bit mode and overflow of the low-order 32-bit result in 32-bit mode. For further information

about 64-bit mode and 32-bit mode in 64-bit implementations, see 4.1.2 , “Computation Modes.”

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XO

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 379 of 785

addex addex

Add Extended (x’7C00 0114’)

adde rD,rA,rB (OE = 0 Rc = 0)

adde. rD,rA,rB (OE = 0 Rc = 1)

addeo rD,rA,rB (OE = 1 Rc = 0)

addeo. rD,rA,rB (OE = 1 Rc = 1)

[POWER mnemonics: ae, ae., aeo, aeo.]

rD ← (rA) + (rB) + XER[CA]

The sum (rA) + (rB) + XER[CA] is placed into rD.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO (if Rc = 1)

Note: CR0 field may not reflect the infinitely precise result if overflow occurs (see XER below).

• XER:

Affected: CA

Affected: SO, OV (if OE = 1)

Note: The setting of the affected bits in the XER is mode-dependent, and reflects overflow of the 64-bit

result in 64-bit mode and overflow of the low-order 32-bit result in 32-bit mode. For further information

about 64-bit mode and 32-bit mode in 64-bit implementations, see 4.1.2 , “Computation Modes.”

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XO

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 380 of 785

pem8.fm.2.0

June 10, 2003

addi addi

Add Immediate (x’3800 0000’)

addi rD,rA,SIMM

[POWER mnemonic: cal]

if rA = 0 then rD ← EXTS(SIMM)

else rD ← rA + EXTS(SIMM)

The sum (rA|0) + SIMM is placed into rD.

The addi instruction is preferred for addition because it sets few status bits. Note that addi uses the value 0,

not the contents of GPR0, if rA = 0.

Other registers altered:

•None

Simplified mnemonics:

li rD,value equivalent to addi rD,0,value

la rD,disp(rA) equivalent to addi rD,rA,disp

subi rD,rA,value equivalent to addi rD,rA,–value

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA D

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 381 of 785

addic addic

Add Immediate Carrying (x’3000 0000’)

addic rD,rA,SIMM

[POWER mnemonic: ai]

rD ← (rA) + EXTS(SIMM)

The sum (rA) + SIMM is placed into rD.

Other registers altered:

• XER:

Affected: CA

Note: The setting of the affected bits in the XER is mode-dependent, and reflects overflow of the 64-bit

result in 64-bit mode and overflow of the low-order 32-bit result in 32-bit mode. For further information

about 64-bit mode and 32-bit mode in 64-bit implementations, see 4.1.2 , “Computation Modes.”

Simplified mnemonics:

subic rD,rA,valueequivalent toaddicrD,rA,–value

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA D

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 382 of 785

pem8.fm.2.0

June 10, 2003

addic. addic.

Add Immediate Carrying and Record (x’3400 0000’)

addic. rD,rA,SIMM

[POWER mnemonic: ai.]

rD ← (rA) + EXTS(SIMM)

The sum (rA) + SIMM is placed into rD.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO

Note: CR0 field may not reflect the infinitely precise result if overflow occurs (see XER below).

• XER:

Affected: CA

Note: The setting of the affected bits in the XER is mode-dependent, and reflects overflow of the 64-bit

result in 64-bit mode and overflow of the low-order 32-bit result in 32-bit mode. For further information

about 64-bit mode and 32-bit mode in 64-bit implementations, see 4.1.2 , “Computation Modes.”

Simplified mnemonics:

subic.rD,rA,valueequivalent toaddic.rD,rA,–value

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA D

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 383 of 785

addis addis

Add Immediate Shifted (x’3C00 0000’)

addis rD,rA,SIMM

[POWER mnemonic: cau]

if rA = 0 then rD ← EXTS(SIMM || (16)0)

else rD ← (rA) + EXTS(SIMM || (16)0)

The sum (rA|0) + (SIMM || 0x0000) is placed into rD.

The addis instruction is preferred for addition because it sets few status bits. Note that addis uses the value

0, not the contents of GPR0, if rA = 0.

Other registers altered:

•None

Simplified mnemonics:

lisrD,valueequivalent toaddisrD,0,value

subisrD,rA,valueequivalent toaddisrD,rA,–value

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA D

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 384 of 785

pem8.fm.2.0

June 10, 2003

addmexaddmex

Add to Minus One Extended (x’7C00 01D4’)

addme rD,rA (OE = 0 Rc = 0)

addme. rD,rA (OE = 0 Rc = 1)

addmeo rD,rA (OE = 1 Rc = 0)

addmeo. rD,rA (OE = 1 Rc = 1)

[POWER mnemonics: ame, ame., ameo, ameo.]

rD ← (rA) + XER[CA] – 1

The sum (rA) + XER[CA] + 0xFFFF_FFFF_FFFF_FFFF is placed into rD.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

Note: CR0 field may not reflect the infinitely precise result if overflow occurs (see XER below).

• XER:

Affected: CA

Affected: SO, OV(if OE = 1)

Note: The setting of the affected bits in the XER is mode-dependent, and reflects overflow of the 64-bit

result in 64-bit mode and overflow of the low-order 32-bit result in 32-bit mode. For further information

about 64-bit mode and 32-bit mode in 64-bit implementations, see 4.1.2 , “Computation Modes.”

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XO

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 385 of 785

addzexaddzex

Add to Zero Extended (x’7C00 0194’)

addze rD,rA (OE = 0 Rc = 0)

addze. rD,rA(OE = 0 Rc = 1)

addzeo rD,rA(OE = 1 Rc = 0)

addzeo. rD,rA(OE = 1 Rc = 1)

[POWER mnemonics: aze, aze., azeo, azeo.]

rD ← (rA) + XER[CA]

The sum (rA) + XER[CA] is placed into rD.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

Note: CR0 field may not reflect the infinitely precise result if overflow occurs (see XER below).

• XER:

Affected: CA

Affected: SO, OV(if OE = 1)

Note: The setting of the affected bits in the XER is mode-dependent, and reflects overflow of the 64-bit

result in 64-bit mode and overflow of the low-order 32-bit result in 32-bit mode. For further information

about 64-bit mode and 32-bit mode in 64-bit implementations, see 4.1.2 , “Computation Modes.”

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XO

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 386 of 785

pem8.fm.2.0

June 10, 2003

andxandx

AND (x’7C00 0038’)

and rA,rS,rB(Rc = 0)

and. rA,rS,rB(Rc = 1)

rA ← (rS) & (rB)

The contents of rS are ANDed with the contents of rB and the result is placed into rA.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 387 of 785

andcxandcx

AND with Complement (x’7C00 0078’)

andc rA,rS,rB(Rc = 0)

andc. rA,rS,rB(Rc = 1)

rA ← (rS) + ¬ (rB)

The contents of rS are ANDed with the one’s complement of the contents of rB and the result is placed into

rA.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 388 of 785

pem8.fm.2.0

June 10, 2003

andi. andi.

AND Immediate (x’7000 0000’)

andi. rA,rS,UIMM

[POWER mnemonic: andil.]

rA ← (rS) & ((4816)0 || UIMM)

The contents of rS are ANDed with 0x0000_0000_0000 || UIMM and the result is placed into rA.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA D

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 389 of 785

andis. andis.

AND Immediate Shifted (x’7400 0000’)

andis. rA,rS,UIMM

[POWER mnemonic: andiu.]

rA ← (rS) + ((32)0 || UIMM || (16)0)

The contents of rS are ANDed with 0x0000_0000 || UIMM || 0x0000 and the result is placed into rA.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA D

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 390 of 785

pem8.fm.2.0

June 10, 2003

bxbx

Branch (x’4800 0000’)

btarget_addr (AA = 0 LK = 0)

ba target_addr (AA = 1 LK = 0)

bl target_addr (AA = 0 LK = 1)

bla target_addr (AA = 1 LK = 1)

if AA then NIA ←iea EXTS(LI || 0b00)

else NIA ←iea CIA + EXTS(LI || 0b00)

if LK then LR ←iea CIA + 4

target_addr specifies the branch target address.

If AA = 0, then the branch target address is the sum of LI || 0b00 sign-extended and the address of this

instruction, with the high-order 32 bits of the branch target address cleared in 32-bit mode of 64-bit implemen-

tations.

If AA = 1, then the branch target address is the value LI || 0b00 sign-extended, with the high-order 32 bits of

the branch target address cleared in 32-bit mode of 64-bit implementations.

If LK = 1, then the effective address of the instruction following the branch instruction is placed into the link

register.

Other registers altered:

Affected: Link Register (LR)(if LK = 1)

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA I

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 391 of 785

bcxbcx

Branch Conditional (x’4000 0000’)

bc BO,BI,target_addr (AA = 0 LK = 0)

bca BO,BI,target_addr (AA = 1 LK = 0)

bcl BO,BI,target_addr (AA = 0 LK = 1)

bcla BO,BI,target_addr (AA = 1 LK = 1)

if (64-bit implementation) & (64-bit mode)

then m ← 0

else m ← 32

if ¬ BO[2] then CTR ← CTR – 1

ctr_ok ← BO[2] | ((CTR[m–63] ¦ 0) ⊕ BO[3])

cond_ok ← BO[0] | (CR[BI] ≡ BO[1])

if ctr_ok & cond_ok then

if AA then NIA ←iea EXTS(BD || 0b00)

else NIA ←iea CIA + EXTS(BD || 0b00)

if LK then LR ←iea CIA + 4

The BI field specifies the bit in the condition register (CR) to be used as the condition of the branch. The BO

field is encoded as described in . Additional information about BO field encoding is provided in Section 4.2.4.2

Conditional Branch Control.

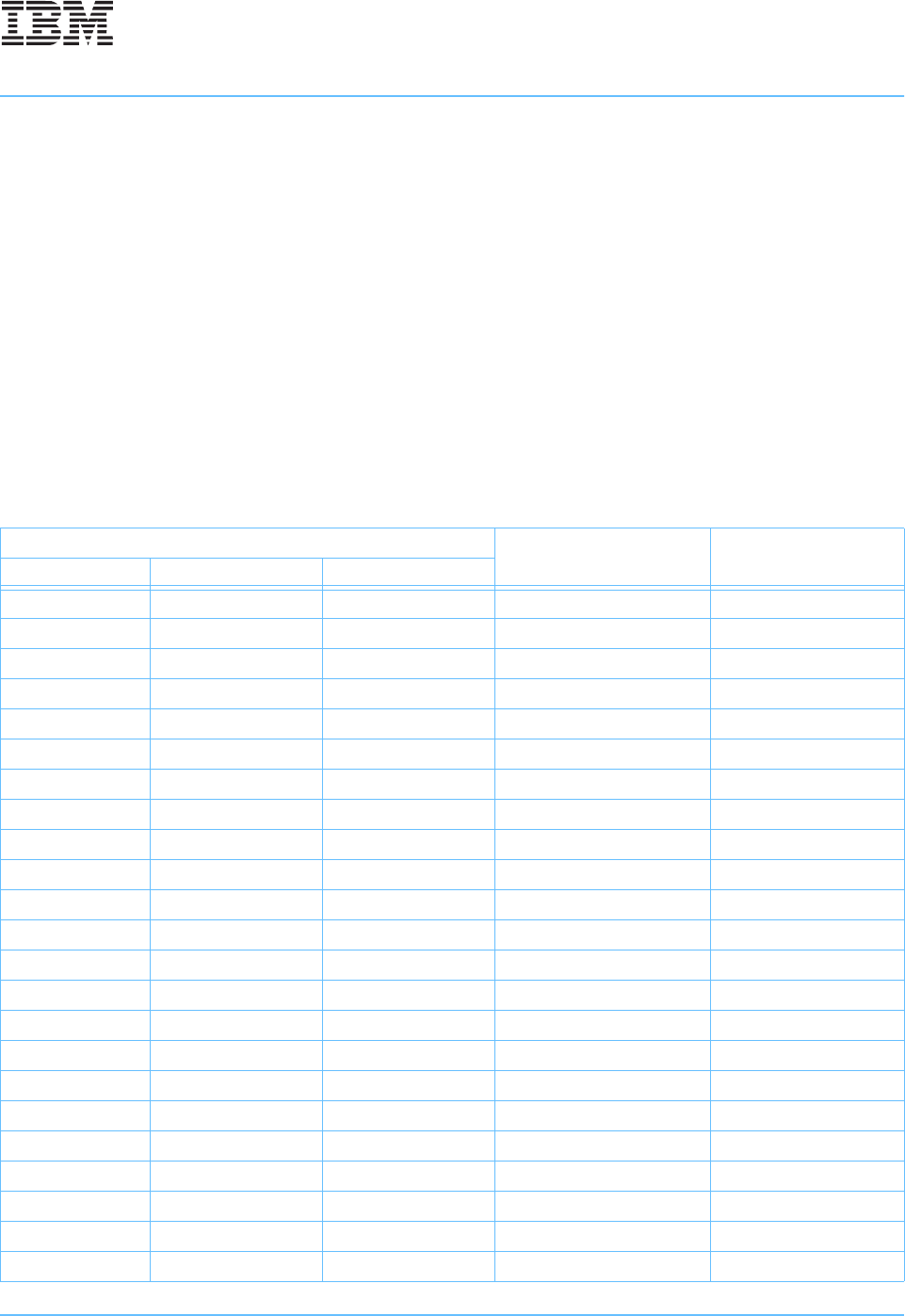

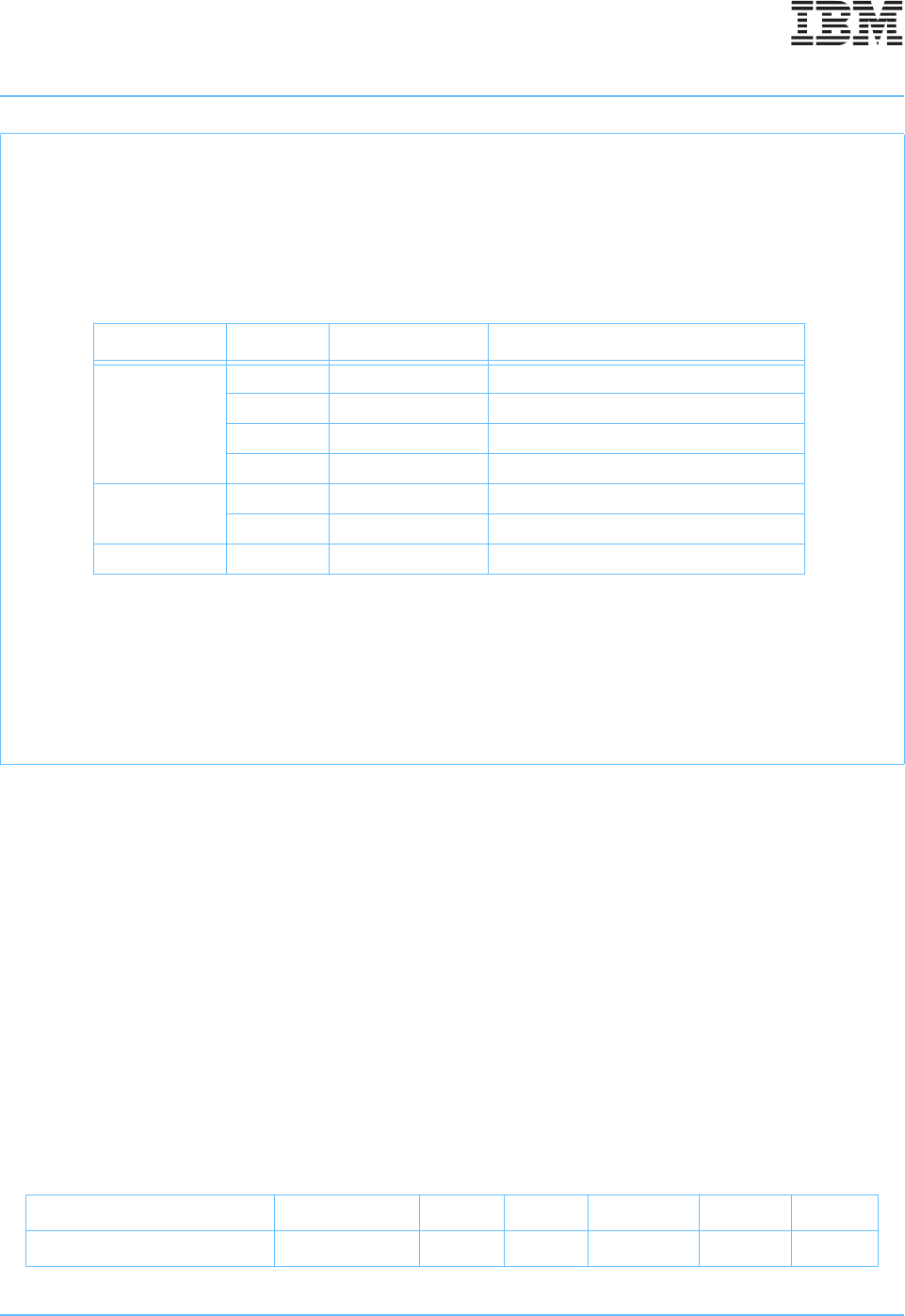

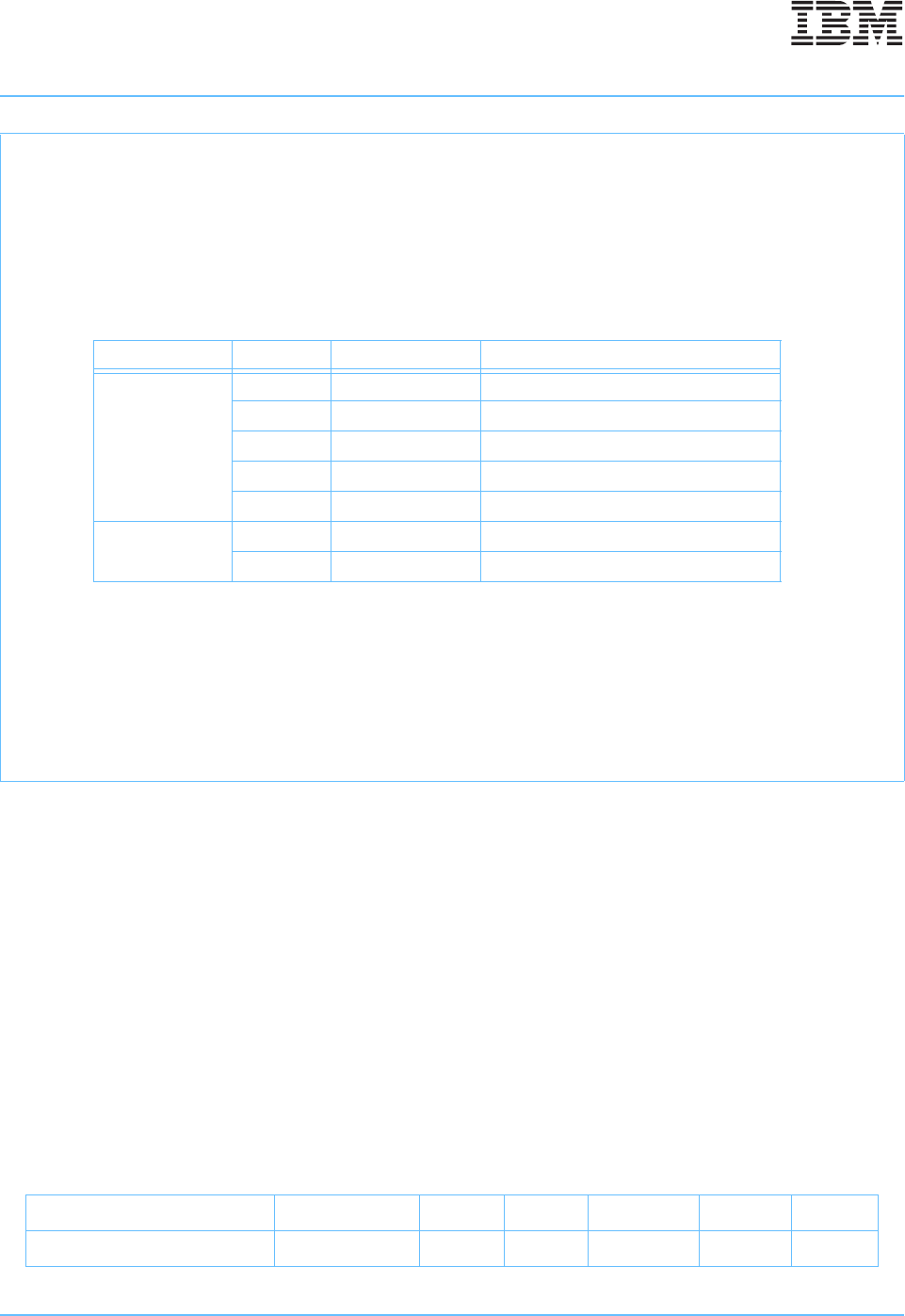

Table 8-6. BO Operand Encodings

BO Description

0000yDecrement the CTR, then branch if the decremented CTR[M–63] ¦ 0 and the condition is FALSE.

0001yDecrement the CTR, then branch if the decremented CTR[M–63] = 0 and the condition is FALSE.

001zy Branch if the condition is FALSE.

0100yDecrement the CTR, then branch if the decremented CTR[M–63] ¦ 0 and the condition is TRUE.

0101yDecrement the CTR, then branch if the decremented CTR[M–63] = 0 and the condition is TRUE.

011zy Branch if the condition is TRUE.

1z00yDecrement the CTR, then branch if the decremented CTR[M–63] ¦ 0.

1z01yDecrement the CTR, then branch if the decremented CTR[M–63] = 0.

1z1zz Branch always.

M = 32 in 32-bit mode, and M = 0 in the default 64-bit mode. If the BO field specifies that the CTR is to be decremented, the entire 64-

bit CTR is decremented regardless of the 32-bit mode or the default 64-bit mode.

In this table, z indicates a bit that is ignored.

Note that the z bits should be cleared, as they may be assigned a meaning in some future version of the PowerPC architecture.

The y bit provides a hint about whether a conditional branch is likely to be taken, and may be used by some PowerPC implementations

to improve performance.

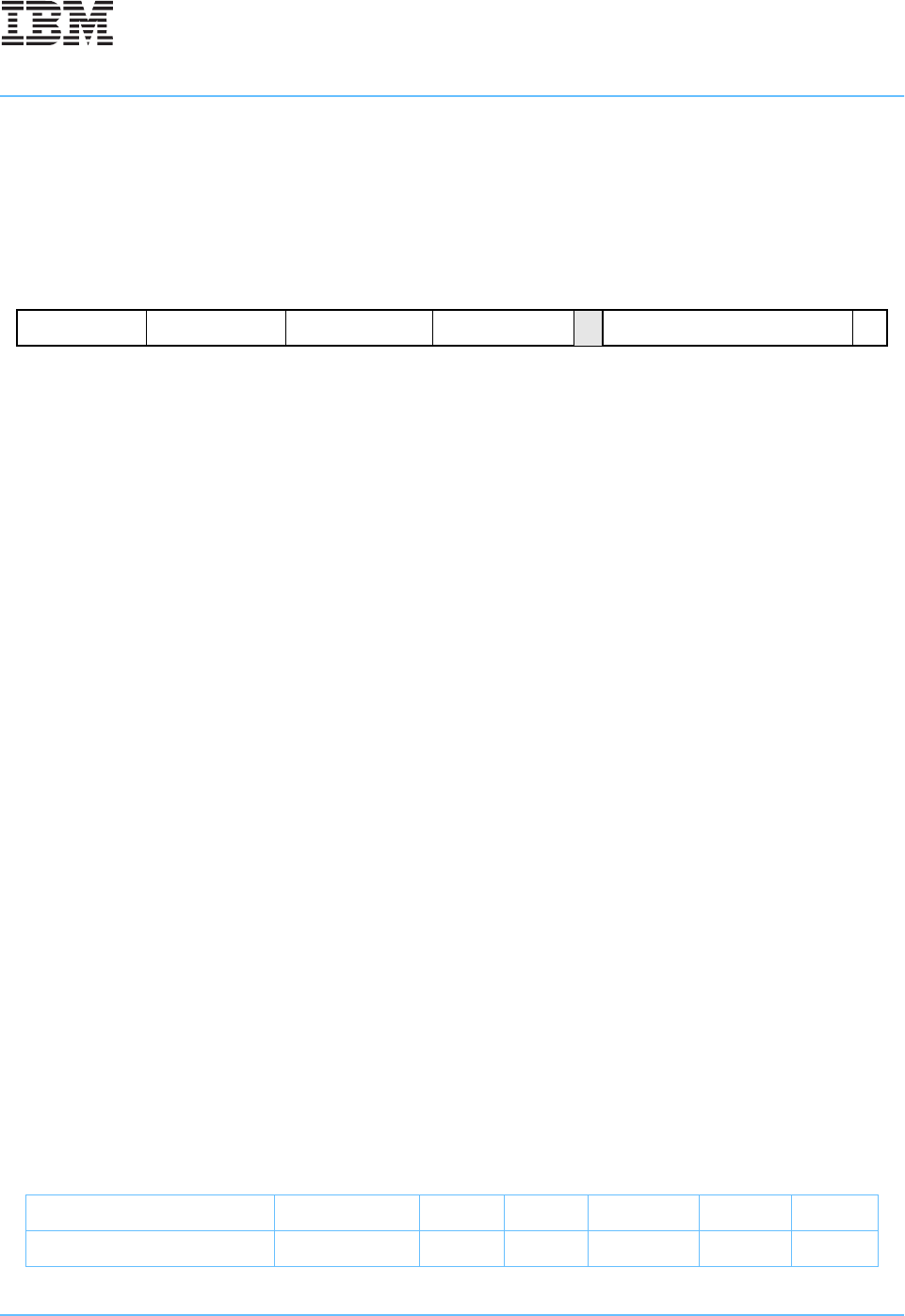

05610111516 293031

16 BO BI BD AA LK

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 392 of 785

pem8.fm.2.0

June 10, 2003

target_addr specifies the branch target address.

If AA = 0, the branch target address is the sum of BD || 0b00 sign-extended and the address of this instruc-

tion, with the high-order 32 bits of the branch target address cleared in 32-bit mode of 64-bit implementations.

If AA = 1, the branch target address is the value BD || 0b00 sign-extended, with the high-order 32 bits of the

branch target address cleared in 32-bit mode of 64-bit implementations.

If LK = 1, the effective address of the instruction following the branch instruction is placed into the link

register.

Other registers altered:

Affected: Count Register (CTR)(if BO[2] = 0)

Affected: Link Register (LR)(if LK = 1)

Simplified mnemonics:

blt target equivalent to

bc 12,0,target

bne cr2,target equivalent to bc 4,10,target

bdnz target equivalent to bc 16,0,target

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA B

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 393 of 785

bcctrxbcctrx

Branch Conditional to Count Register (x’4C00 0420’)

bcctr BO,BI (LK = 0)

bcctrl BO,BI (LK = 1)

[POWER mnemonics: bcc, bccl]

cond_ok ← BO[0] | (CR[BI] ≡ BO[1])

if cond_ok then

NIA ←iea CTR[0–61] || 0b00

if LK then LR ←iea CIA + 4

The BI field specifies the bit in the condition register to be used as the condition of the branch. The BO field is

encoded as described in . Additional information about BO field encoding is provided in Section 4.2.4.2 ,

“Conditional Branch Control.”

.

The branch target address is CTR[0–61] || 0b00, with the high-order 32 bits of the branch target address

cleared in 32-bit mode of 64-bit implementations.

If LK = 1, the effective address of the instruction following the branch instruction is placed into the link

register.

If the “decrement and test CTR” option is specified (BO[2] = 0), the instruction form is invalid.

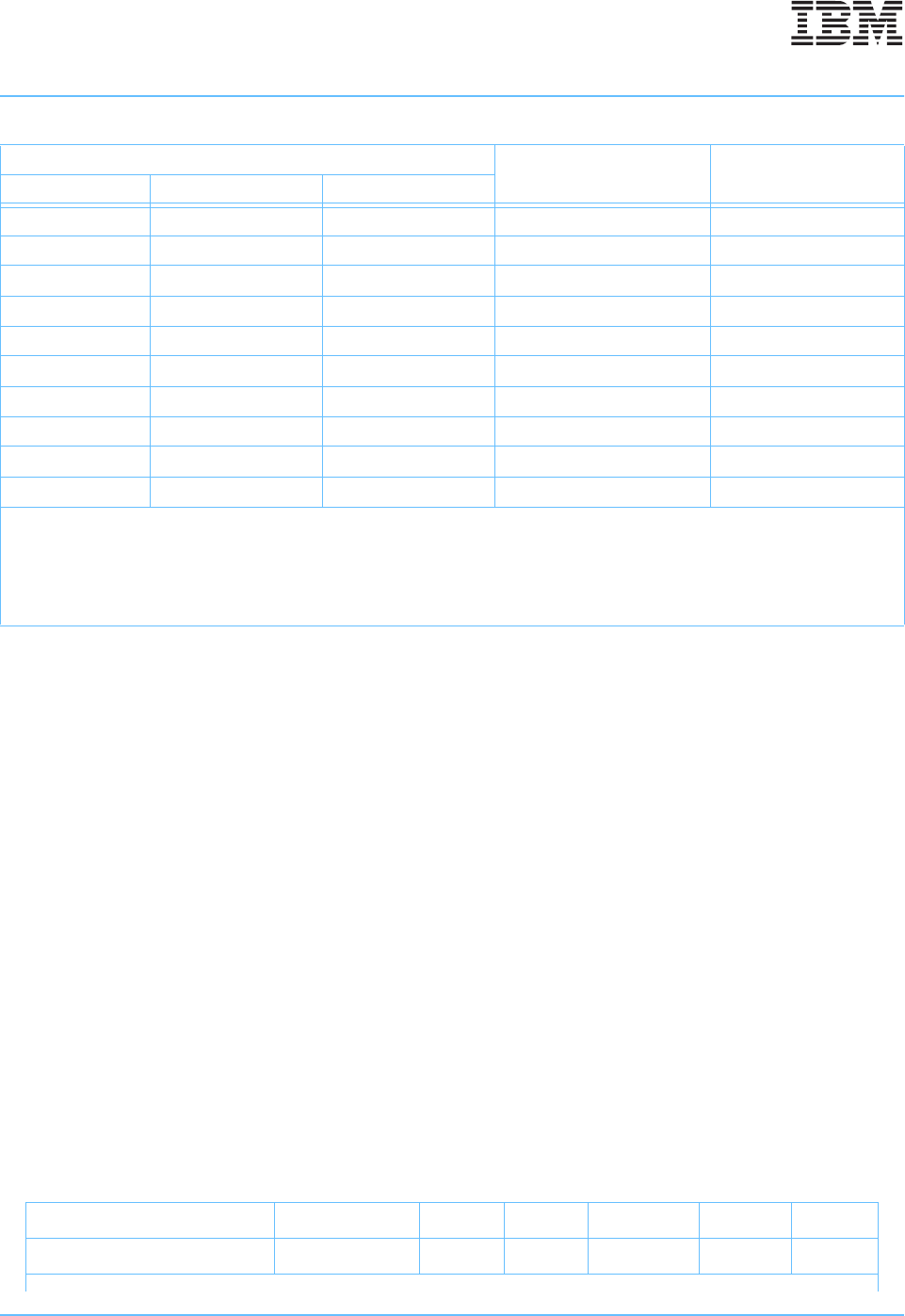

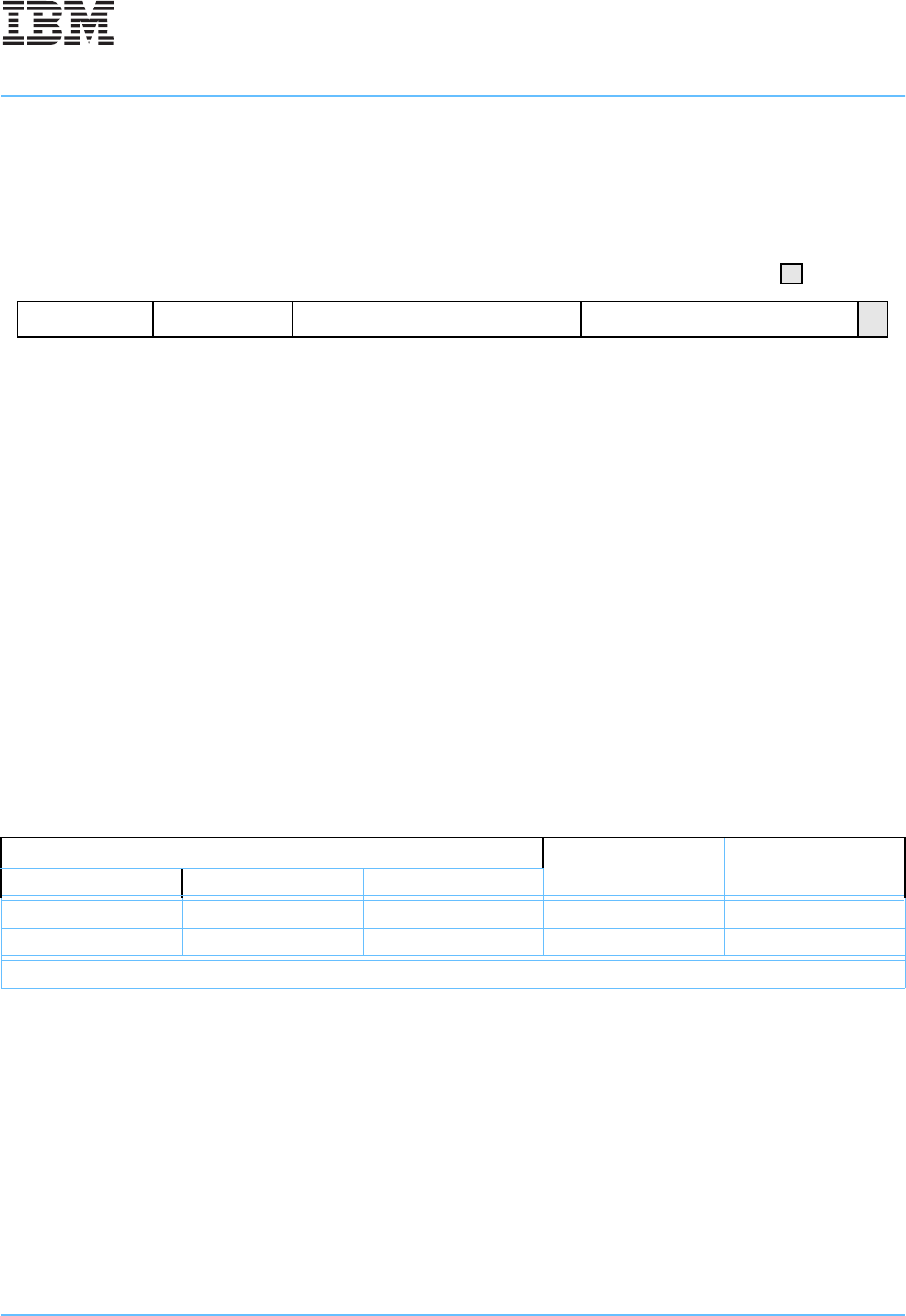

Table 8-7. BO Operand Encodings

BO Description

0000yDecrement the CTR, then branch if the decremented CTR[M–63] ¦ 0 and the condition is FALSE.

0001yDecrement the CTR, then branch if the decremented CTR[M–63] = 0 and the condition is FALSE.

001zy Branch if the condition is FALSE.

0100yDecrement the CTR, then branch if the decremented CTR[M–63] ¦ 0 and the condition is TRUE.

0101yDecrement the CTR, then branch if the decremented CTR[M–63] = 0 and the condition is TRUE.

011zy Branch if the condition is TRUE.

1z00yDecrement the CTR, then branch if the decremented CTR[M–63] ¦ 0.

1z01yDecrement the CTR, then branch if the decremented CTR[M–63] = 0.

1z1zz Branch always.

M = 32 in 32-bit mode, and M = 0 in the default 64-bit mode. If the BO field specifies that the CTR is to be decremented, the entire 64-

bit CTR is decremented regardless of the 32-bit mode or the default 64-bit mode.

In this table, z indicates a bit that is ignored.

Note that the z bits should be cleared, as they may be assigned a meaning in some future version of the PowerPC architecture.

The y bit provides a hint about whether a conditional branch is likely to be taken, and may be used by some PowerPC implementa-

tions to improve performance.

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 394 of 785

pem8.fm.2.0

June 10, 2003

Other registers altered:

Affected: Link Register (LR)(if LK = 1)

Simplified mnemonics:

bltctr equivalent to bcctr 12,0

bnectr cr2 equivalent to bcctr 4,10

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XL

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 395 of 785

bclrxbclrx

Branch Conditional to Link Register (x’4C00 0020’)

bclr BO,BI (LK = 0)

bclrl BO,BI (LK = 1)

[POWER mnemonics: bcr, bcrl]

if (64-bit implementation) & (64-bit mode)

then m ← 0

else m ← 32

if ¬ BO[2] then CTR ← CTR – 1

ctr_ok ← BO[2] | ((CTR[m–63] ¦ 0) ⊕ BO[3])

cond_ok ← BO[0] | (CR[BI] ≡ BO[1])

if ctr_ok & cond_ok then

NIA ←iea LR[0–61] || 0b00

if LK then LR ←iea CIA + 4

The BI field specifies the bit in the condition register to be used as the condition of the branch. The BO field is

encoded as described in Table 8-8. Additional information about BO field encoding is provided in

Section 4.2.4.2 Conditional Branch Control.

The branch target address is LR[0–61] || 0b00, with the high-order 32 bits of the branch target address

cleared in 32-bit mode of 64-bit implementations.

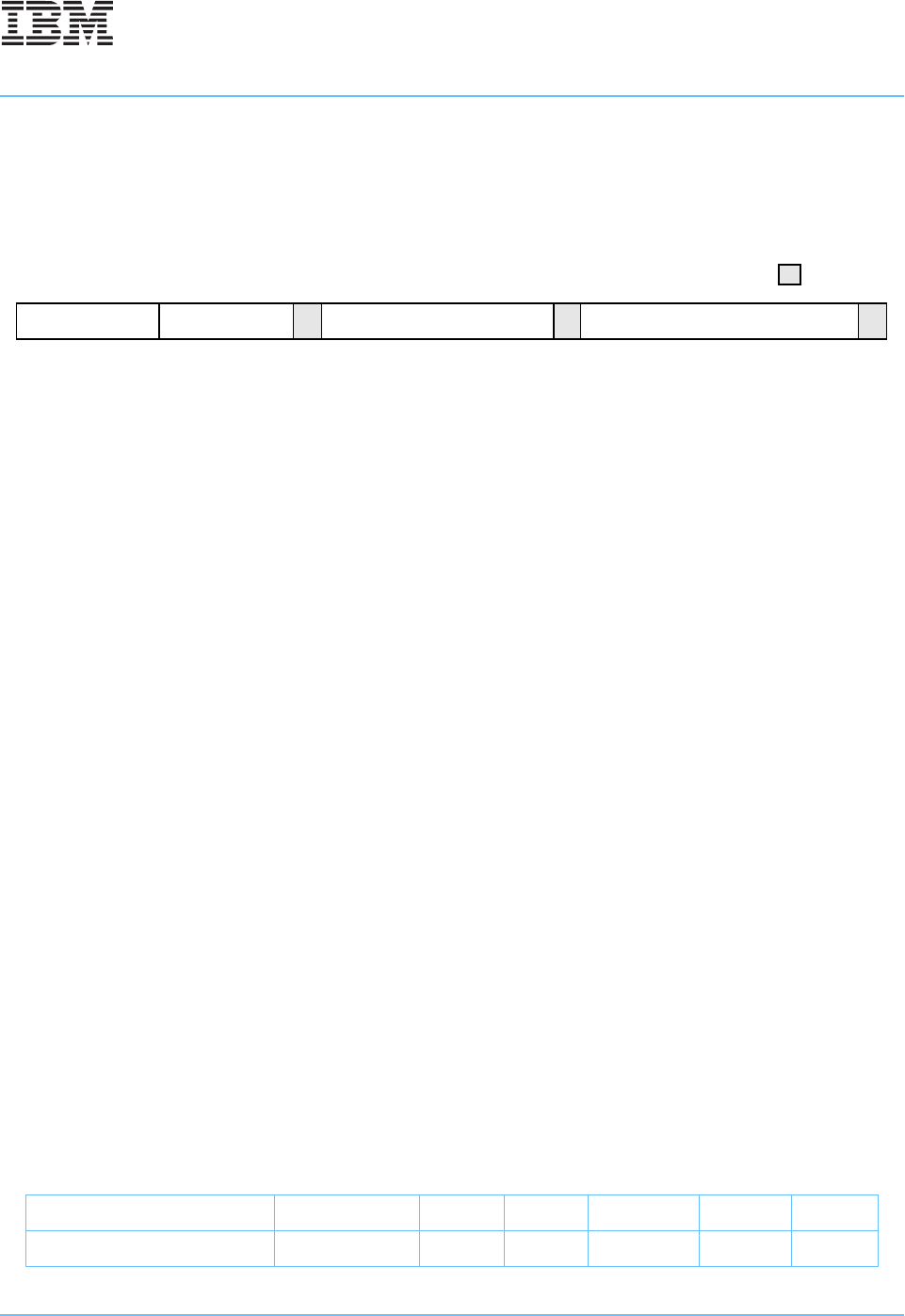

Table 8-8. BO Operand Encodings

BO Description

0000yDecrement the CTR, then branch if the decremented CTR[M–63] ¦ 0 and the condition is FALSE.

0001yDecrement the CTR, then branch if the decremented CTR[M–63] = 0 and the condition is FALSE.

001zy Branch if the condition is FALSE.

0100yDecrement the CTR, then branch if the decremented CTR[M–63] ¦ 0 and the condition is TRUE.

0101yDecrement the CTR, then branch if the decremented CTR[M–63] = 0 and the condition is TRUE.

011zy Branch if the condition is TRUE.

1z00yDecrement the CTR, then branch if the decremented CTR[M–63] ¦ 0.

1z01yDecrement the CTR, then branch if the decremented CTR[M–63] = 0.

1z1zz Branch always.

M = 32 in 32-bit mode, and M = 0 in the default 64-bit mode. If the BO field specifies that the CTR is to be decremented, the entire 64-

bit CTR is decremented regardless of the 32-bit mode or the default 64-bit mode.

In this table, z indicates a bit that is ignored.

Note that the z bits should be cleared, as they may be assigned a meaning in some future version of the PowerPC architecture.

The y bit provides a hint about whether a conditional branch is likely to be taken, and may be used by some PowerPC implementations

to improve performance.

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 396 of 785

pem8.fm.2.0

June 10, 2003

If LK = 1, then the effective address of the instruction following the branch instruction is placed into the link

register.

Other registers altered:

Affected: Count Register (CTR) (if BO[2] = 0)

Affected: Link Register (LR) (if LK = 1)

Simplified mnemonics:

bltlr equivalent to bclr 12,0

bnelr cr2 equivalent to bclr 4,10

bdnzlr equivalent to bclr 16,0

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XL

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 397 of 785

cmp cmp

Compare (x’7C00 0000’)

cmp crfD,L,rA,rB

if L = 0 then a ← EXTS(rA[32–63])

b ← EXTS(rB[32–63])

else a ← (rA)

b ← (rB)

if a < b then c ← 0b100

else if a > b then c ← 0b010

else c ← 0b001

CR[4 ∗ crfD–4 ∗ crfD + 3] ← c || XER[SO]

The contents of rA (or the low-order 32 bits of rA if L = 0) are compared with the contents of rB (or the low-

order 32 bits of rB if L = 0), treating the operands as signed integers. The result of the comparison is placed

into CR field crfD.

In 32-bit implementations, if L = 1 the instruction form is invalid.

Other registers altered:

• Condition Register (CR field specified by operand crfD):

Affected: LT, GT, EQ, SO

Simplified mnemonics:

cmpd rA,rB equivalent to cmp 0,1,rA,rB

cmpw cr3,rA,rB equivalent to cmp 3,0,rA,rB

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 398 of 785

pem8.fm.2.0

June 10, 2003

cmpi cmpi

Compare Immediate (x’2C00 0000’)

cmpi crfD,L,rA,SIMM

if L = 0 then a ← EXTS(rA[32–63])

elsea ← (rA)

if a < EXTS(SIMM) then c ← 0b100

else if a > EXTS(SIMM) then c ← 0b010

else c ← 0b001

CR[4 ∗ crfD–4 ∗ crfD + 3] ← c || XER[SO]

The contents of rA (or the low-order 32 bits of rA sign-extended to 64 bits if L = 0) are compared with the sign-

extended value of the SIMM field, treating the operands as signed integers. The result of the comparison is

placed into CR field crfD.

In 32-bit implementations, if L = 1 the instruction form is invalid.

Other registers altered:

• Condition Register (CR field specified by operand crfD):

Affected: LT, GT, EQ, SO

Simplified mnemonics:

cmpdi rA,value equivalent to cmpi 0,1,rA,value

cmpwi cr3,rA,value equivalent to cmpi 3,0,rA,value

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA D

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 399 of 785

cmpl cmpl

Compare Logical (x’7C00 0040’)

cmpl crfD,L,rA,rB

if L = 0 then a ← (32)0 || rA[32–63]

b ← (32)0 || rB[32–63]

elsea ← (rA)

b ← (rB)

if a <U b then c ← 0b100

else if a >U b then c ← 0b010

else c ← 0b001

CR[4 ∗ crfD–4 ∗ crfD + 3] ← c || XER[SO]

The contents of rA (or the low-order 32 bits of rA if L = 0) are compared with the contents of rB (or the low-

order 32 bits of rB if L = 0), treating the operands as unsigned integers. The result of the comparison is placed

into CR field crfD.

In 32-bit implementations, if L = 1 the instruction form is invalid.

Other registers altered:

• Condition Register (CR field specified by operand crfD):

Affected: LT, GT, EQ, SO

Simplified mnemonics:

cmpld rA,rB equivalent to cmpl 0,1,rA,rB

cmplw cr3,rA,rB equivalent to cmpl 3,0,rA,rB

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 400 of 785

pem8.fm.2.0

June 10, 2003

cmpli cmpli

Compare Logical Immediate (x’2800 0000’)

cmpli crfD,L,rA,UIMM

if L = 0 then a ← (32)0 || rA[32–63]

else a ← (rA)

if a <U ((4816)0 || UIMM) then c ← 0b100

else if a >U ((4816)0 || UIMM) then c ← 0b010

else c ← 0b001

CR[4 ∗ crfD–4 ∗ crfD + 3] ← c || XER[SO]

The contents of rA (or the low-order 32 bits of rA zero-extended to 64-bits if L = 0) are compared with

0x0000_0000_0000 || UIMM, treating the operands as unsigned integers. The result of the comparison is

placed into CR field crfD.

In 32-bit implementations, if L = 1 the instruction form is invalid.

Other registers altered:

• Condition Register (CR field specified by operand crfD):

Affected: LT, GT, EQ, SO

Simplified mnemonics:

cmpldi r A,value equivalent to cmpli 0,1,rA,value

cmplwi cr3,rA,value equivalent to cmpli 3,0,rA,value

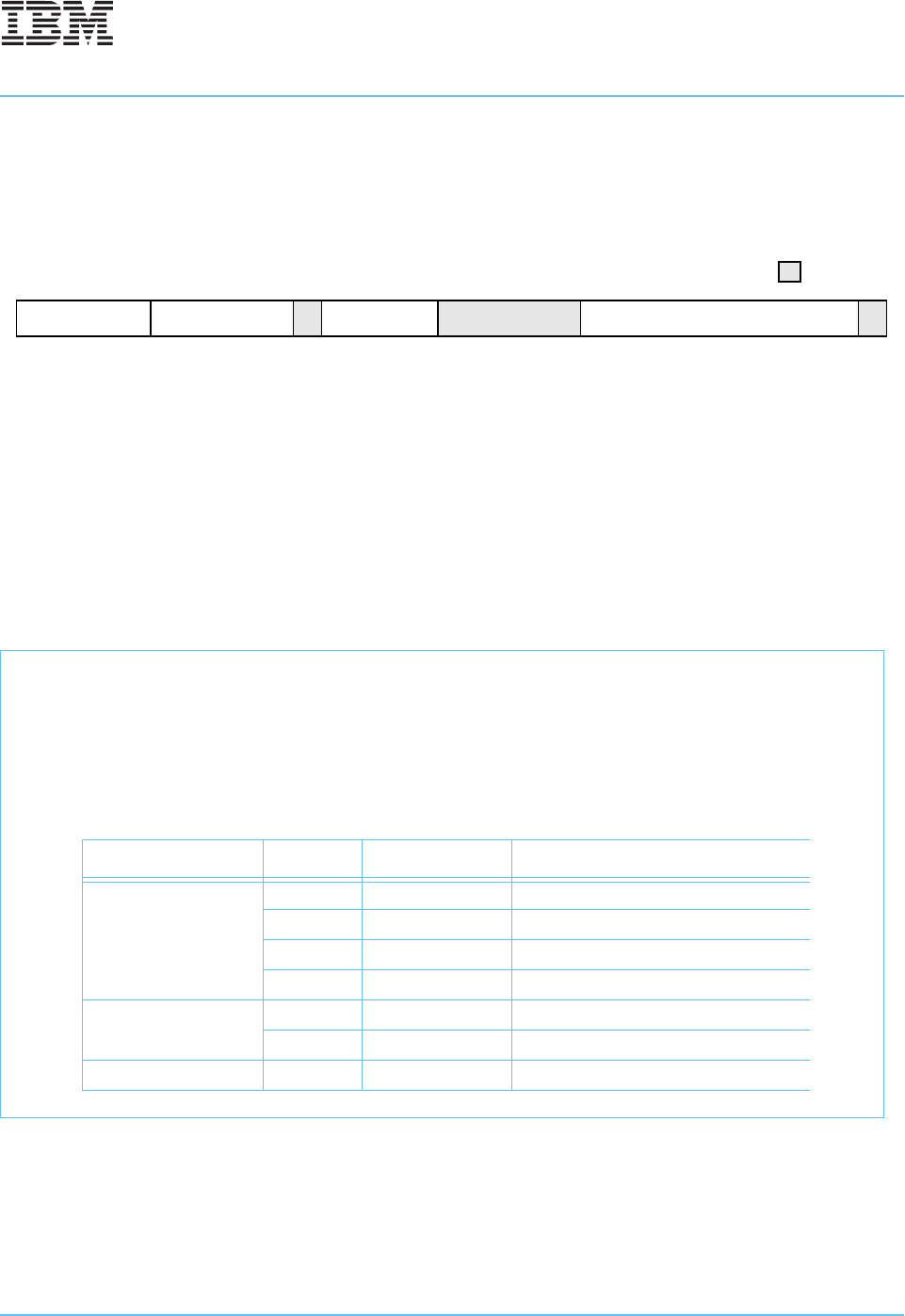

10 crfD 0 L A

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA D

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 401 of 785

cntlzdx64-Bit Implementations Only cntlzdx

Count Leading Zeros Double Word (x’7C00 0074’)

cntlzd rA,rS(Rc = 0)

cntlzd. rA,rS(Rc = 1)

n ← 0

do while n < 64

if rS[n] = 1 then leave

n ← n + 1

rA ← n

A count of the number of consecutive zero bits starting at bit 0 of register rS is placed into rA. This number

ranges from 0 to 64, inclusive.

This instruction is defined only for 64-bit implementations. Using it on a 32-bit implementation will cause the

system illegal instruction error handler to be invoked.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(Rc = 1)

Note: If Rc = 1, then LT is cleared in the CR0 field.

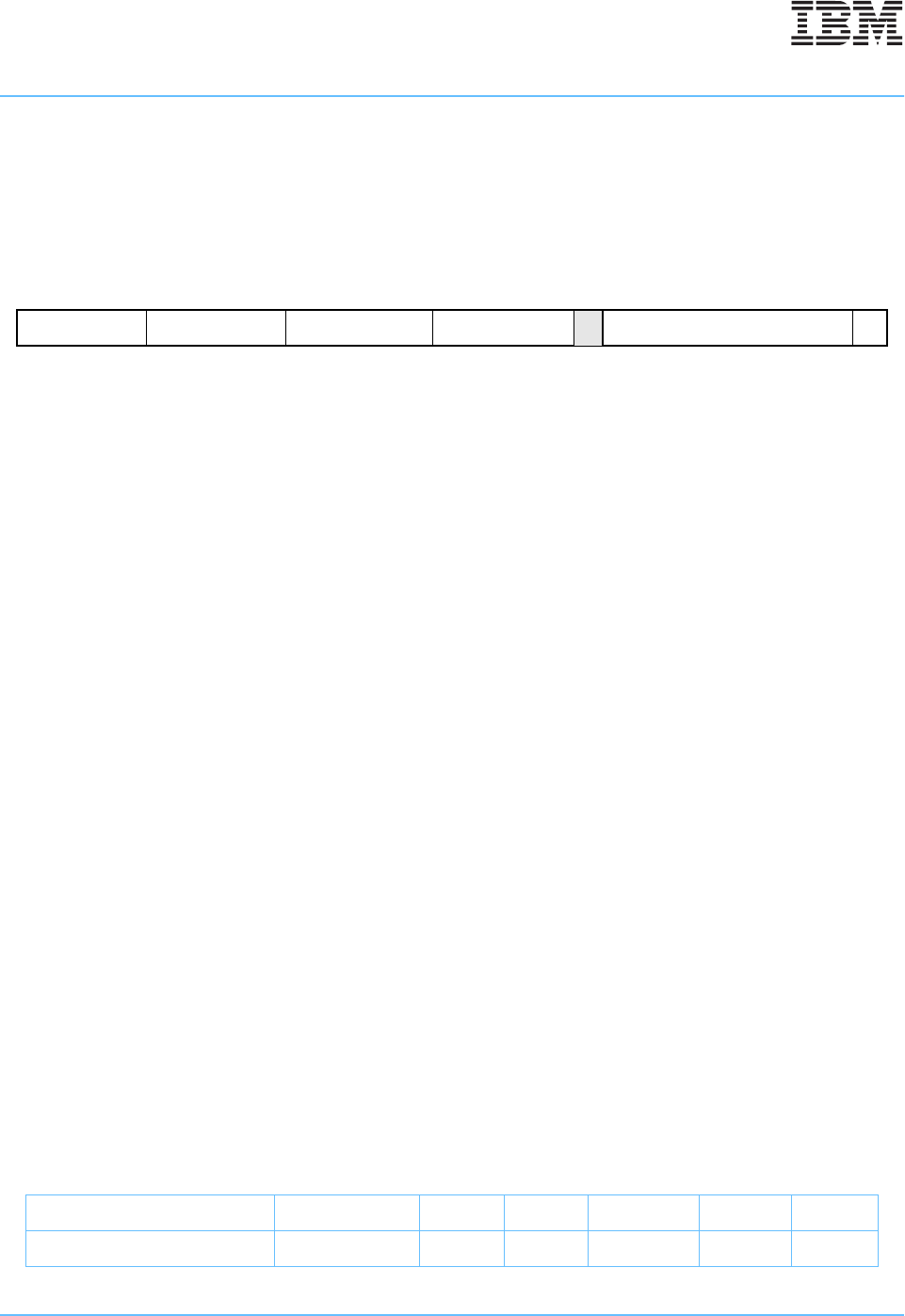

056101115162021 3031

Reserved

31 S A 0 0 0 0 0 58 Rc

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA Ð X

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 402 of 785

pem8.fm.2.0

June 10, 2003

cntlzwxcntlzwx

Count Leading Zeros Word (x’7C00 0034’)

cntlzw rA,rS (Rc = 0)

cntlzw. rA,rS (Rc = 1)

[POWER mnemonics: cntlz, cntlz.]

n ← 320

do while n < 6432

if rS[n] = 1 then leave

n ← n + 1

rA ← n – 32

A count of the number of consecutive zero bits starting at bit 320 of rS (bit 0 in 32-bit implementations) is

placed into rA. This number ranges from 0 to 32, inclusive.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

Note: If Rc = 1, then LT is cleared in the CR0 field.

056101115162021 3031

Reserved

31 S A 0 0 0 0 0 26 Rc

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 403 of 785

crand crand

Condition Register AND (x’4C00 0202’)

crand crbD,crbA,crbB

CR[crbD] ← CR[crbA] & CR[crbB]

The bit in the condition register specified by crbA is ANDed with the bit in the condition register specified by

crbB. The result is placed into the condition register bit specified by crbD.

Other registers altered:

• Condition Register:

Affected: Bit specified by operand crbD

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XL

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 404 of 785

pem8.fm.2.0

June 10, 2003

crandc crandc

Condition Register AND with Complement (x’4C00 0102’)

crandc crbD,crbA,crbB

CR[crbD] ← CR[crbA] & ¬ CR[crbB]

The bit in the condition register specified by crbA is ANDed with the complement of the bit in the condition

register specified by crbB and the result is placed into the condition register bit specified by crbD.

Other registers altered:

• Condition Register:

Affected: Bit specified by operand crbD

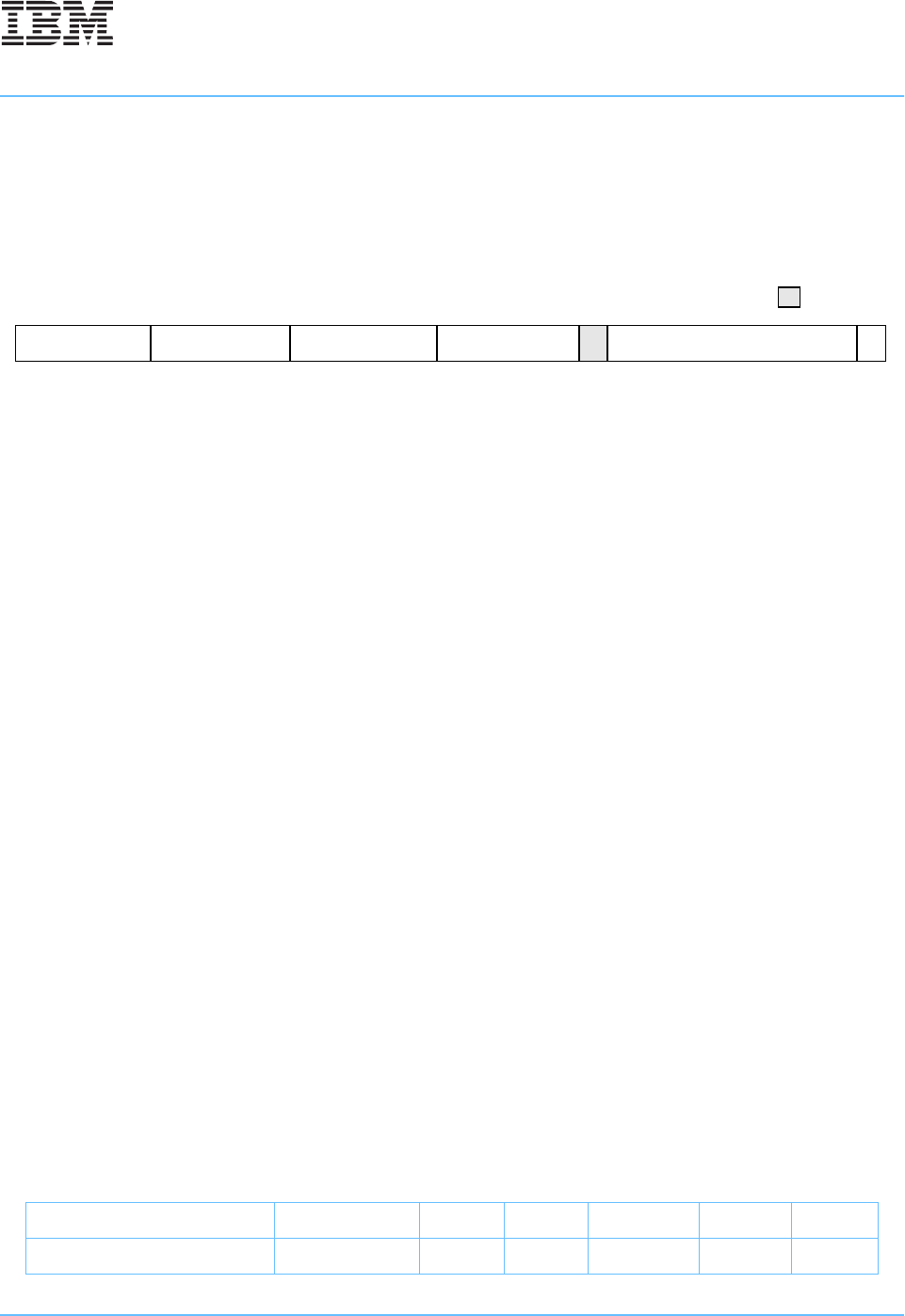

056101115162021 3031

Reserved

19 crbD crbA crbB 129 0

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XL

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 405 of 785

creqv creqv

Condition Register Equivalent (x’4C00 0242’)

creqv crbD,crbA,crbB

CR[crbD] ← CR[crbA] ≡ CR[crbB]

The bit in the condition register specified by crbA is XORed with the bit in the condition register specified by

crbB and the complemented result is placed into the condition register bit specified by crbD.

Other registers altered:

• Condition Register:

Affected: Bit specified by operand crbD

Simplified mnemonics:

crset crbD equivalent to creqv crbD,crbD,crbD

056101115162021 3031

Reserved

19 crbD crbA crbB 289 0

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XL

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 406 of 785

pem8.fm.2.0

June 10, 2003

crnand crnand

Condition Register NAND (x’4C00 01C2’)

crnand crbD,crbA,crbB

CR[crbD] ← ¬ (CR[crbA] & CR[crbB])

The bit in the condition register specified by crbA is ANDed with the bit in the condition register specified by

crbB and the complemented result is placed into the condition register bit specified by crbD.

Other registers altered:

• Condition Register:

Affected: Bit specified by operand crbD

056101115162021 3031

Reserved

19 crbD crbA crbB 225 0

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XL

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 407 of 785

crnor crnor

Condition Register NOR (x’4C00 0042’)

crnor crbD,crbA,crbB

CR[crbD] ← ¬ (CR[crbA] | CR[crbB])

The bit in the condition register specified by crbA is ORed with the bit in the condition register specified by

crbB and the complemented result is placed into the condition register bit specified by crbD.

Other registers altered:

• Condition Register:

Affected: Bit specified by operand crbD

Simplified mnemonics:

crnot crbD,crbA equivalent to crnor crbD,crbA,crbA

056101115162021 3031

Reserved

19 crbD crbA crbB 33 0

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XL

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 408 of 785

pem8.fm.2.0

June 10, 2003

cror cror

Condition Register OR (x’4C00 0382’)

cror crbD,crbA,crbB

CR[crbD] ← CR[crbA] | CR[crbB]

The bit in the condition register specified by crbA is ORed with the bit in the condition register specified by

crbB. The result is placed into the condition register bit specified by crbD.

Other registers altered:

• Condition Register:

Affected: Bit specified by operand crbD

Simplified mnemonics:

crmove crbD,crbA equivalent to cror crbD,crbA,crbA

056101115162021 3031

Reserved

19 crbD crbA crbB 449 0

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XL

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 409 of 785

crorc crorc

Condition Register OR with Complement (x’4C00 0342’)

crorc crbD,crbA,crbB

CR[crbD] ← CR[crbA] | ¬ CR[crbB]

The bit in the condition register specified by crbA is ORed with the complement of the condition register bit

specified by crbB and the result is placed into the condition register bit specified by crbD.

Other registers altered:

• Condition Register:

Affected: Bit specified by operand crbD

056101115162021 3031

Reserved

19 crbD crbA crbB 417 0

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XL

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 410 of 785

pem8.fm.2.0

June 10, 2003

crxor crxor

Condition Register XOR (x’4C00 0182’)

crxor crbD,crbA,crbB

CR[crbD] ← CR[crbA] ⊕ CR[crbB]

The bit in the condition register specified by crbA is XORed with the bit in the condition register specified by

crbB and the result is placed into the condition register specified by crbD.

Other registers altered:

• Condition Register:

Affected: Bit specified by crbD

Simplified mnemonics:

crclr crbD equivalent to crxor crbD,crbD,crbD

056101115162021 3031

Reserved

19 crbD crbA crbB 193 0

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XL

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 411 of 785

dcba dcba

Data Cache Block Allocate (x’7C00 05EC’)

dcba rA,rB

EA is the sum (rA|0) + (rB).

The dcba instruction allocates the block in the data cache addressed by EA, by marking it valid without

reading the contents of the block from memory; the data in the cache block is considered to be undefined

after this instruction completes. This instruction is a hint that the program will probably soon store into a

portion of the block, but the contents of the rest of the block are not meaningful to the program (eliminating

the need to read the entire block from main memory), and can provide for improved performance in these

code sequences.

The dcba instruction executes as follows:

• If the cache block containing the byte addressed by EA is in the data cache, the contents of all bytes are

made undefined but the cache block is still considered valid. Note that programming errors can occur if

the data in this cache block is subsequently read or used inadvertently.

• If the cache block containing the byte addressed by EA is not in the data cache and the corresponding

memory page or block is caching-allowed, the cache block is allocated (and made valid) in the data

cache without fetching the block from main memory, and the value of all bytes is undefined.

• If the addressed byte corresponds to a caching-inhibited page or block (i.e. if the I bit is set), this instruc-

tion is treated as a no-op.

• If the cache block containing the byte addressed by EA is in coherency-required mode, and the cache

block exists in the data cache(s) of any other processor(s), it is kept coherent in those caches (i.e. the

processor performs the appropriate bus transactions to enforce this).

This instruction is treated as a store to the addressed byte with respect to address translation, memory

protection, referenced and changed recording and the ordering enforced by eieio or by the combination of

caching-inhibited and guarded attributes for a page (or block). However, the DSI exception is not invoked for

a translation or protection violation, and the referenced and changed bits need not be updated when the page

or block is cache-inhibited (causing the instruction to be treated as a no-op).

This instruction is optional in the PowerPC architecture.

Other registers altered:

•None

In the PowerPC OEA, the dcba instruction is additionally defined to clear all bytes of a newly established

block to zero in the case that the block did not already exist in the cache.

056101115162021 3031

Reserved

B 758 031 0 0 0 0 0 A

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 412 of 785

pem8.fm.2.0

June 10, 2003

Additionally, as the dcba instruction may establish a block in the data cache without verifying that the associ-

ated physical address is valid, a delayed machine check exception is possible. See 6. , “Exceptions,” for a

discussion about this type of machine check exception.

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

VEA ÐX

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 413 of 785

dcbf dcbf

Data Cache Block Flush (x’7C00 00AC’)

dcbf rA,rB

EA is the sum (rA|0) + (rB).

The dcbf instruction invalidates the block in the data cache addressed by EA, copying the block to memory

first, if there is any dirty data in it. If the processor is a multiprocessor implementation (for example, the 601,

604,and 604e and 620) and the block is marked coherency-required, the processor will, if necessary, send an

address-only broadcast to other processors. The broadcast of the dcbf instruction causes another processor

to copy the block to memory, if it has dirty data, and then invalidate the block from the cache.

The action taken depends on the memory mode associated with the block containing the byte addressed by

EA and on the state of that block. The list below describes the action taken for the various states of the

memory coherency attribute (M bit).

• Coherency required

– Unmodified block—Invalidates copies of the block in the data caches of all processors.

– Modified block—Copies the block to memory. Invalidates copies of the block in the data caches of all

processors.

– Absent block—If modified copies of the block are in the data caches of other processors, causes

them to be copied to memory and invalidated in those data caches. If unmodified copies are in the

data caches of other processors, causes those copies to be invalidated in those data caches.

• Coherency not required

– Unmodified block—Invalidates the block in the processor’s data cache.

– Modified block—Copies the block to memory. Invalidates the block in the processor’s data cache.

– Absent block (target block not in cache)—No action is taken.

The function of this instruction is independent of the write-through, write-back and caching-inhibited/allowed

modes of the block containing the byte addressed by EA.

This instruction is treated as a load from the addressed byte with respect to address translation and memory

protection. It is also treated as a load for referenced and changed bit recording except that referenced and

changed bit recording may not occur.

Other registers altered:

• None

056101115162021 3031

Reserved

B860

31 0 0 0 0 0 A

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

VEA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 414 of 785

pem8.fm.2.0

June 10, 2003

dcbi dcbi

Data Cache Block Invalidate (x’7C00 03AC’)

dcbi rA,rB

EA is the sum (rA|0) + (rB).

The action taken is dependent on the memory mode associated with the block containing the byte addressed

by EA and on the state of that block. The list below describes the action taken if the block containing the byte

addressed by EA is or is not in the cache.

• Coherency required

– Unmodified block—Invalidates copies of the block in the data caches of all processors.

– Modified block—Invalidates copies of the block in the data caches of all processors. (Discards the

modified contents.)

– Absent block—If copies of the block are in the data caches of any other processor, causes the copies

to be invalidated in those data caches. (Discards any modified contents.)

• Coherency not required

– Unmodified block—Invalidates the block in the processor’s data cache.

– Modified block—Invalidates the block in the processor’s data cache. (Discards the modified con-

tents.)

– Absent block (target block not in cache)—No action is taken.

When data address translation is enabled, MSR[DR] = 1, and the virtual address has no translation, a DSI

exception occurs.

The function of this instruction is independent of the write-through and caching-inhibited/allowed modes of the

block containing the byte addressed by EA. This instruction operates as a store to the addressed byte with

respect to address translation and protection. The referenced and changed bits are modified appropriately.

This is a supervisor-level instruction.

Other registers altered:

•None

056101115162021 3031

Reserved

B 470 031 0 0 0 0 0 A

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

OEA Ð X

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 415 of 785

dcbst dcbst

Data Cache Block Store (x’7C00 006C’)

dcbst rA,rB

EA is the sum (rA|0) + (rB).

The dcbst instruction executes as follows:

• If the block containing the byte addressed by EA is in coherency-required mode, and a block containing

the byte addressed by EA is in the data cache of any processor and has been modified, the writing of it to

main memory is initiated.

• If the block containing the byte addressed by EA is in coherency-not-required mode, and a block contain-

ing the byte addressed by EA is in the data cache of this processor and has been modified, the writing of

it to main memory is initiated.

The function of this instruction is independent of the write-through and caching-inhibited/allowed modes of the

block containing the byte addressed by EA.

The processor treats this instruction as a load from the addressed byte with respect to address translation

and memory protection. It is also treated as a load for referenced and changed bit recording except that refer-

enced and changed bit recording may not occur.

Other registers altered:

•None

056101115162021 3031

Reserved

B54031 0 0 0 0 0 A

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

VEA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 416 of 785

pem8.fm.2.0

June 10, 2003

dcbt dcbt

Data Cache Block Touch (x’7C00 022C’)

dcbt rA,rB

EA is the sum (rA|0) + (rB).

This instruction is a hint that performance will possibly be improved if the block containing the byte addressed

by EA is fetched into the data cache, because the program will probably soon load from the addressed byte.

If the block is caching-inhibited, the hint is ignored and the instruction is treated as a no-op. Executing dcbt

does not cause the system alignment error handler to be invoked.

This instruction is treated as a load from the addressed byte with respect to address translation, memory

protection, and reference and change recording except that referenced and changed bit recording may not

occur. Additionally, no exception occurs in the case of a translation fault or protection violation.

The program uses the dcbt instruction to request a cache block fetch before it is actually needed by the

program. The program can later execute load instructions to put data into registers. However, the processor

is not obliged to load the addressed block into the data cache. Note that this instruction is defined architectur-

ally to perform the same functions as the dcbtst instruction. Both are defined in order to allow implementa-

tions to differentiate the bus actions when fetching into the cache for the case of a load and for a store.

Other registers altered:

•None

056101115162021 3031

Reserved

B 278 031 0 0 0 0 0 A

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

VEA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 417 of 785

dcbtst dcbtst

Data Cache Block Touch for Store (x’7C00 01EC’)

dcbtst rA,rB

EA is the sum (rA|0) + (rB).

This instruction is a hint that performance will possibly be improved if the block containing the byte addressed

by EA is fetched into the data cache, because the program will probably soon store from the addressed byte.

If the block is caching-inhibited, the hint is ignored and the instruction is treated as a no-op. Executing dcbtst

does not cause the system alignment error handler to be invoked.

This instruction is treated as a load from the addressed byte with respect to address translation, memory

protection, and reference and change recording except that referenced and changed bit recording may not

occur. Additionally, no exception occurs in the case of a translation fault or protection violation.

The program uses dcbtst to request a cache block fetch to potentially improve performance for a subsequent

store to that EA, as that store would then be to a cached location. However, the processor is not obliged to

load the addressed block into the data cache. Note that this instruction is defined architecturally to perform

the same functions as the dcbt instruction. Both are defined in order to allow implementations to differentiate

the bus actions when fetching into the cache for the case of a load and for a store.

Other registers altered:

•None

056101115162021 3031

Reserved

B 246 031 0 0 0 0 0 A

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

VEA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 418 of 785

pem8.fm.2.0

June 10, 2003

dcbz dcbz

Data Cache Block Clear to Zero (x’7C00 07EC’)

dcbz rA,rB

[POWER mnemonic: dclz]

EA is the sum (rA|0) + (rB).

The dcbz instruction executes as follows:

• If the cache block containing the byte addressed by EA is in the data cache, all bytes are cleared.

• If the cache block containing the byte addressed by EA is not in the data cache and the corresponding

memory page or block is caching-allowed, the cache block is allocated (and made valid) in the data

cache without fetching the block from main memory, and all bytes are cleared.

• If the page containing the byte addressed by EA is in caching-inhibited or write-through mode, either all

bytes of main memory that correspond to the addressed cache block are cleared or the alignment excep-

tion handler is invoked. The exception handler can then clear all bytes in main memory that correspond to

the addressed cache block.

• If the cache block containing the byte addressed by EA is in coherency-required mode, and the cache

block exists in the data cache(s) of any other processor(s), it is kept coherent in those caches (i.e. the

processor performs the appropriate bus transactions to enforce this).

This instruction is treated as a store to the addressed byte with respect to address translation, memory

protection, referenced and changed recording. It is also treated as a store with respect to the ordering

enforced by eieio and the ordering enforced by the combination of caching-inhibited and guarded attributes

for a page (or block).

Other registers altered:

•None

The PowerPC OEA describes how the dcbz instruction may establish a block in the data cache without veri-

fying that the associated physical address is valid. This scenario can cause a delayed machine check excep-

tion; see 6. , “Exceptions,” for a discussion about this type of machine check exception.

056101115162021 3031

Reserved

B 1014 031 0 0 0 0 0 A

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

VEA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 419 of 785

divdx64-Bit Implementations Only divdx

Divide Double Word (x’7C00 03D2’)

divd rD,rA,rB(OE = 0 Rc = 0)

divd. rD,rA,rB(OE = 0 Rc = 1)

divdo rD,rA,rB(OE = 1 Rc = 0)

divdo. rD,rA,rB(OE = 1 Rc = 1)

dividend[0–63] ← (rA)

divisor[0–63] ← (rB)

rD ← dividend + divisor

The 64-bit dividend is the contents of rA. The 64-bit divisor is the contents of rB. The 64-bit quotient is placed

into rD. The remainder is not supplied as a result.

Both the operands and the quotient are interpreted as signed integers. The quotient is the unique signed

integer that satisfies the equation—dividend = (quotient ∗ divisor) + r—where 0 ð r < |divisor| if the dividend is

non-negative, and –|divisor| < r ð 0 if the dividend is negative.

If an attempt is made to perform the divisions—0x8000_0000_0000_0000 ÷ –1 or <anything> ÷ 0—the

contents of rD are undefined, as are the contents of the LT, GT, and EQ bits of the CR0 field (if Rc = 1). In this

case, if OE = 1 then OV is set.

This instruction is defined only for 64-bit implementations. Using it on a 32-bit implementation will cause the

system illegal instruction error handler to be invoked.

The 64-bit signed remainder of dividing (rA) by (rB) can be computed as follows, except in the case that (rA)

= –263 and (rB) = –1:

divd rD,rA,rB# rD = quotient

mulld rD,rD,rB# rD = quotient * divisor

subf rD,rD,rA# rD = remainder

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

• XER:

Affected: SO, OV (if OE = 1)

Note: The setting of the affected bits in the XER is mode-independent, and reflects overflow of the 64-bit

result.

05610111516202122 3031

31 D A B OE 489 Rc

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA Ð XO

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 420 of 785

pem8.fm.2.0

June 10, 2003

divdux64-Bit Implementations Only divdux

Divide Double Word Unsigned (x’7C00 0392’)

divdu rD,rA,rB (OE = 0 Rc = 0)

divdu. rD,rA,rB (OE = 0 Rc = 1)

divduo rD,rA,rB (OE = 1 Rc = 0)

divduo. rD,rA,rB (OE = 1 Rc = 1)

dividend[0–63] ← (rA)

divisor[0–63] ← (rB)

rD ← dividend + divisor

The 64-bit dividend is the contents of rA. The 64-bit divisor is the contents of rB. The 64-bit quotient of the

dividend and divisor is placed into rD. The remainder is not supplied as a result.

Both the operands and the quotient are interpreted as unsigned integers, except that if Rc is set to 1 the first

three bits of CR0 field are set by signed comparison of the result to zero. The quotient is the unique unsigned

integer that satisfies the equation—dividend = (quotient ∗ divisor) + r—where 0 ð r < divisor.

If an attempt is made to perform the division—<anything> ÷ 0—the contents of rD are undefined as are the

contents of the LT, GT, and EQ bits of the CR0 field (if Rc = 1). In this case, if OE = 1 then OV is set.

This instruction is defined only for 64-bit implementations. Using it on a 32-bit implementation will cause the

system illegal instruction error handler to be invoked.

The 64-bit unsigned remainder of dividing (rA) by (rB) can be computed as follows:

divdu rD,rA,rB# rD = quotient

mulld rD,rD,rB#

rD = quotient * divisor

subf rD,rD,rA# rD = remainder

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

• XER:

Affected: SO, OV(if OE = 1)

Note: The setting of the affected bits in the XER is mode-independent, and reflects overflow of the 64-bit

result.

05610111516202122 3031

31 D A B OE 457 Rc

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA Ð XO

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 421 of 785

divwxdivwx

Divide Word (x’7C00 03D6’)

divw rD,rA,rB(OE = 0 Rc = 0)

divw. rD,rA,rB (OE = 0 Rc = 1)

divwo rD,rA,rB (OE = 1 Rc = 0)

divwo. rD,rA,rB(OE = 1 Rc = 1)

dividend[0–63] ← EXTS(rA[32–63])

divisor[0–63] ← EXTS(rB[32–63])

rD[32–63] ← dividend ÷ divisor

rD[0–31] ← undefined

The 64-bit dividend is the sign-extended value of the contents of the low-order 32 bits of rA. The 64-bit divisor

is the sign-extended value of the contents of the low-order 32 bits of rB. The 6432-bit quotient is formed and

placed in rD. The low-order 32 bits of the 64-bit quotient are placed into the low-order 32 bits of rD. The

contents of the high-order 32 bits of rD are undefined. The remainder is not supplied as a result.

Both the operands and the quotient are interpreted as signed integers. The quotient is the unique signed

integer that satisfies the equation—dividend = (quotient * divisor) + r where 0 ð r < |divisor| (if the dividend is

non-negative), and –|divisor| < r ð 0 (if the dividend is negative).

If an attempt is made to perform either of the divisions—0x8000_0000 ÷ –1 or

<anything> ÷ 0, then the contents of rD are undefined, as are the contents of the LT, GT, and EQ bits of the

CR0 field (if Rc = 1). In this case, if OE = 1 then OV is set.

The 32-bit signed remainder of dividing the contents of the low-order 32 bits of rA by the contents of the low-

order 32 bits of rB can be computed as follows, except in the case that the contents of the low-order 32 bits of

rA = –231 and the contents of the low-order 32 bits of rB = –1.

divw rD,rA,rB#

rD = quotient

mullw rD,rD,rB#

rD = quotient ∗ divisor

subf rD,rD,rA# rD = remainder

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

LT, GT, EQ undefined(if Rc =1 and 64-bit mode)

• XER:

Affected: SO, OV(if OE = 1)

Note: The setting of the affected bits in the XER is mode-independent, and reflects overflow of the low-

order 32-bit result.

05610111516202122 3031

31 D A B OE 491 Rc

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XO

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 422 of 785

pem8.fm.2.0

June 10, 2003

divwuxdivwux

Divide Word Unsigned (x’7C00 0396’)

divwu rD,rA,rB (OE = 0 Rc = 0)

divwu. rD,rA,rB (OE = 0 Rc = 1)

divwuo rD,rA,rB (OE = 1 Rc = 0)

divwuo. rD,rA,rB (OE = 1 Rc = 1)

dividend[0–63] ← (32)0 || (rA)[32–63]

divisor[0–63] ← (32)0 || (rB)[32–63]

rD[32–63] ← dividend ÷ divisor

rD[0–31] ← undefined

The 64-bit dividend is the zero-extended value of the contents of the low-order 32 bits of rA. The 64-bit divisor

is the zero-extended value the contents of the low-order 32 bits of rB. A 6432-bit quotient is formed. The low-

order 32 bits of the 6432-bit quotient areis placed into the low-order 32 bits of rD. The contents of the high-

order 32 bits of rD are undefined. The remainder is not supplied as a result.

Both operands and the quotient are interpreted as unsigned integers, except that if Rc = 1 the first three bits

of CR0 field are set by signed comparison of the result to zero. The quotient is the unique unsigned integer

that satisfies the equation—dividend = (quotient ∗ divisor) + r (where 0 ð r < divisor). If an attempt is made to

perform the division—<anything> ÷ 0—then the contents of rD are undefined as are the contents of the LT,

GT, and EQ bits of the CR0 field (if Rc = 1). In this case, if OE = 1 then OV is set.

The 32-bit unsigned remainder of dividing the contents of the low-order 32 bits of rA by the contents of the

low-order 32 bits of rB can be computed as follows:

divwurD,rA,rB# rD = quotient

mullw rD,rD,rB# rD = quotient ∗ divisor

subf rD,rD,rA # rD = remainder

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

LT, GT, EQ undefined(if Rc =1 and 64-bit mode)

• XER:

Affected: SO, OV(if OE = 1)

Note: The setting of the affected bits in the XER is mode-independent, and reflects overflow of the low-

order 32-bit result.

05610111516202122 3031

31 D A B OE 459 Rc

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA XO

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 423 of 785

eciwx eciwx

External Control In Word Indexed (x’7C00 026C’)

eciwx rD,rA,rB

The eciwx instruction and the EAR register can be very efficient when mapping special devices such as

graphics devices that use addresses as pointers.

if rA = 0 then b ← 0

else b← (rA)

EA ← b + (rB)

paddr ← address translation of EA

send load word request for paddr to device identified by EAR[RID]

rD ← (32)0 || word from device

EA is the sum (rA|0) + (rB).

A load word request for the physical address (referred to as real address in the architecture specification)

corresponding to EA is sent to the device identified by EAR[RID], bypassing the cache. The word returned by

the device is placed in the low-order 32 bits of rD. The contents of the high-order 32 bits of rD are cleared.

EAR[E] must be 1. If it is not, a DSI exception is generated.

EA must be a multiple of four. If it is not, one of the following occurs:

• A system alignment exception is generated.

• A DSI exception is generated (possible only if EAR[E] = 0).

• The results are boundedly undefined.

The eciwx instruction is supported for EAs that reference memory segments in which SR[T] = 1 (or STE[T] =

1) and for EAs mapped by the DBAT registers. If the EA references a direct-store segment (SR[T] = 1 or

STE[T] = 1), either a DSI exception occurs or the results are boundedly undefined. However, note that the

direct-store facility is being phased out of the architecture and will not likely be supported in future devices.

Thus, software should not depend on its effects.

If this instruction is executed when MSR[DR] = 0 (real addressing mode), the results are boundedly unde-

fined. This instruction is treated as a load from the addressed byte with respect to address translation,

memory protection, referenced and changed bit recording, and the ordering performed by eieio. This instruc-

tion is optional in the PowerPC architecture.

Other registers altered:

• None

056101115162021 3031

Reserved

31 D A

B 310 0

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

VEA ÐX

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 424 of 785

pem8.fm.2.0

June 10, 2003

ecowx ecowx

External Control Out Word Indexed (x’7C00 036C’)

ecowx rS,rA,rB

The ecowx instruction and the EAR register can be very efficient when mapping special devices such as

graphics devices that use addresses as pointers.

if rA = 0 then b ← 0

else b ← (rA)

EA ← b + (rB)

paddr ← address translation of EA

send store word request for paddr to device identified by EAR[RID]

send rS[32–63] to device

EA is the sum (rA|0) + (rB).

A store word request for the physical address corresponding to EA and the contents of the low-order 32 bits

of rS are sent to the device identified by EAR[RID], bypassing the cache.

EAR[E] must be 1, if it is not, a DSI exception is generated. EA must be a multiple of four. If it is not, one of

the following occurs:

• A system alignment exception is generated.

• A DSI exception is generated (possible only if EAR[E] = 0).

• The results are boundedly undefined.

The ecowx instruction is supported for effective addresses that reference memory segments in which SR[T]

= 0 (or STE[T] = 0), and for EAs mapped by the DBAT registers. If the EA references a direct-store segment

(SR[T] = 1 or STE[T] = 1), either a DSI exception occurs or the results are boundedly undefined. However,

note that the direct-store facility is being phased out of the architecture and will not likely be supported in

future devices. Thus, software should not depend on its effects.

If this instruction is executed when MSR[DR] = 0 (real addressing mode), the results are boundedly unde-

fined. This instruction is treated as a store from the addressed byte with respect to address translation,

memory protection, and referenced and changed bit recording, and the ordering performed by eieio. Note

that software synchronization is required in order to ensure that the data access is performed in program

order with respect to data accesses caused by other store or ecowx instructions, even though the addressed

byte is assumed to be caching-inhibited and guarded. This instruction is optional in the PowerPC architec-

ture.

Other registers altered:

•None

056101115162021 3031

Reserved

31 S A B 438 0

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

VEA ÐX

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 425 of 785

eieio eieio

Enforce In-Order Execution of I/O (x’7C00 06AC’)

The eieio instruction provides an ordering function for the effects of load and store instructions executed by a

processor. These loads and stores are divided into two sets, which are ordered separately. The memory

accesses caused by a dcbz or a dcba instruction are ordered like a store. The two sets follow:

1. Loads and stores to memory that is both caching-inhibited and guarded, and stores to memory that is

write-through required.

The eieio instruction controls the order in which the accesses are performed in main memory. It ensures

that all applicable memory accesses caused by instructions preceding the eieio instruction have com-

pleted with respect to main memory before any applicable memory accesses caused by instructions fol-

lowing the eieio instruction access main memory. It acts like a barrier that flows through the memory

queues and to main memory, preventing the reordering of memory accesses across the barrier. No

ordering is performed for dcbz if the instruction causes the system alignment error handler to be invoked.

All accesses in this set are ordered as a single set—that is, there is not one order for loads and stores to

caching-inhibited and guarded memory and another order for stores to write-through required memory.

• Stores to memory that have all of the following attributes—caching-allowed, write-through not required,

and memory-coherency required.

The eieio instruction controls the order in which the accesses are performed with respect to coherent

memory. It ensures that all applicable stores caused by instructions preceding the eieio instruction have

completed with respect to coherent memory before any applicable stores caused by instructions following

the eieio instruction complete with respect to coherent memory.

With the exception of dcbz and dcba, eieio does not affect the order of cache operations (whether caused

explicitly by execution of a cache management instruction, or implicitly by the cache coherency mechanism).

For more information, refer to 5. , “Cache Model and Memory Coherency.” The eieio instruction does not

affect the order of accesses in one set with respect to accesses in the other set.

The eieio instruction may complete before memory accesses caused by instructions preceding the eieio

instruction have been performed with respect to main memory or coherent memory as appropriate.

The eieio instruction is intended for use in managing shared data structures, in accessing memory-mapped

I/O, and in preventing load/store combining operations in main memory. For the first use, the shared data

structure and the lock that protects it must be altered only by stores that are in the same set (1 or 2; see

previous discussion). For the second use, eieio can be thought of as placing a barrier into the stream of

memory accesses issued by a processor, such that any given memory access appears to be on the same

side of the barrier to both the processor and the I/O device.

Because the processor performs store operations in order to memory that is designated as both caching-

inhibited and guarded (refer to Section 5.1.1 , “Memory Access Ordering”), the eieio instruction is needed for

such memory only when loads must be ordered with respect to stores or with respect to other loads.

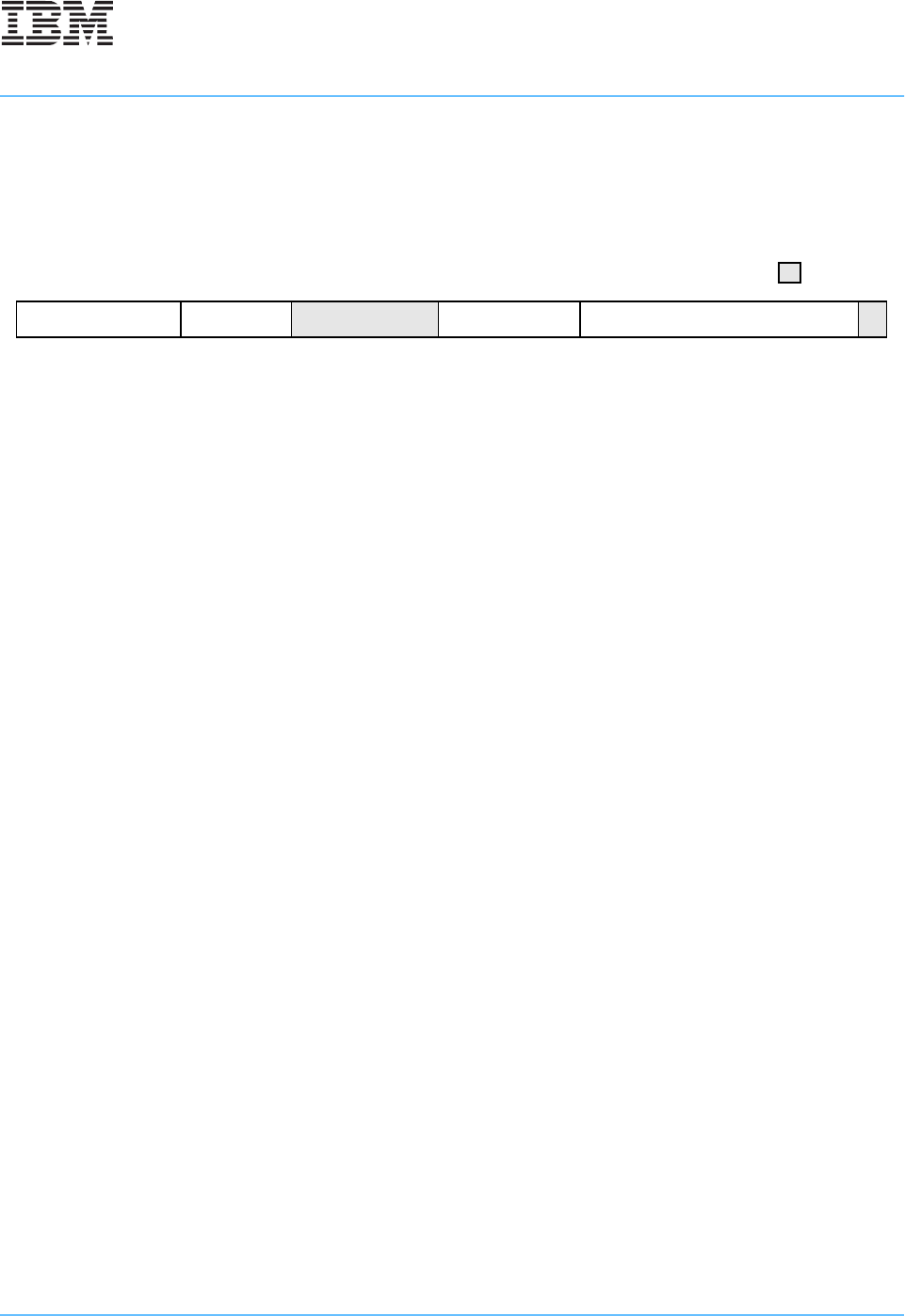

056101115162021 3031

Reserved

31 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 854 0

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 426 of 785

pem8.fm.2.0

June 10, 2003

Note that the eieio instruction does not connect hardware considerations to it such as multiprocessor imple-

mentations that send an eieio address-only broadcast (useful in some designs). For example, if a design has

an external buffer that re-orders loads and stores for better bus efficiency, the eieio broadcast signals to that

buffer that previous loads/stores (marked caching-inhibited, guarded, or write-through required) must

complete before any following loads/stores (marked caching-inhibited, guarded, or write-through required).

Other registers altered:

•None

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

VEA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 427 of 785

eqvxeqvx

Equivalent (x’7C00 0238’)

eqv rA,rS,rB(Rc = 0)

eqv. rA,rS,rB(Rc = 1)

rA ← (rS) ≡ (rB)

The contents of rS are XORed with the contents of rB and the complemented result is placed into rA.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

05610111516 2122 3031

31 S A

B284Rc

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 428 of 785

pem8.fm.2.0

June 10, 2003

extsbxextsbx

Extend Sign Byte (x’7C00 0774’)

extsb rA,rS(Rc = 0)

extsb. rA,rS(Rc = 1)

S ← rS[5624]

rA[56–6324-31] ← rS[56–6324-31]

rA[0–5523] ← (5624)S

The contents of the low-order eight bits of rS[24-31] are placed into the low-order eight bits of rA[24-31]. Bit

5624 of rS is placed into the remaining bits of rA[0-23].

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

056101115162021 3031

Reserved

31 S A

0 0 0 0 0 954 Rc

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 429 of 785

extshxextshx

Extend Sign Half Word (x’7C00 0734’)

extsh rA,rS(Rc = 0)

extsh. rA,rS(Rc = 1)

[POWER mnemonics: exts, exts.]

S ← rS[4816]

rA[48–6316-31] ← rS[48–6316-31]

rA[0–470-15] ← (4816)S

The contents of the low-order 16 bits of rS[16-31] are placed into the low-order 16 bits of rA[16-31]. Bit 4816

of rS is placed into the remaining bits of rA[0–15].

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

056101115162021 3031

Reserved

31 S A 0 0 0 0 0 922 Rc

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 430 of 785

pem8.fm.2.0

June 10, 2003

extswx64-Bit Implementations Only extswx

Extend Sign Word (x’7C00 07B4’)

extsw rA,rS(Rc = 0)

extsw. rA,rS(Rc = 1)

S ← rS[32]

rA[32–63] ← rS[32–63]

rA[0–31] ← (32)S

The contents of the low-order 32 bits of rS are placed into the low-order 32 bits of rA. Bit 32 of rS is placed

into the high-order 32 bits of rA.

This instruction is defined only for 64-bit implementations. Using it on a 32-bit implementation will cause the

system illegal instruction error handler to be invoked.

Other registers altered:

• Condition Register (CR0 field):

Affected: LT, GT, EQ, SO(if Rc = 1)

056101115162021 3031

Reserved

31 S A 0 0 0 0 0 986 Rc

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA Ð X

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 431 of 785

fabsxfabsx

Floating Absolute Value (x’FC00 0210’)

fabs frD,frB (Rc = 0)

fabs. frD,frB (Rc = 1)

The contents of frB with bit 0 cleared are placed into frD.

Note that the fabs instruction treats NaNs just like any other kind of value. That is, the sign bit of a NaN may

be altered by fabs. This instruction does not alter the FPSCR.

Other registers altered:

• Condition Register (CR1 field):

Affected: FX, FEX, VX, OX(if Rc = 1)

B 264 Rc

056101115162021 3031

Reserved

63 D 0 0 0 0 0

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA X

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 432 of 785

pem8.fm.2.0

June 10, 2003

faddxfaddx

Floating Add (Double-Precision) (x’FC00 002A’)

fadd frD,frA,frB(Rc = 0)

fadd. frD,frA,frB (Rc = 1)

[POWER mnemonics: fa, fa.]

The floating-point operand in frA is added to the floating-point operand in frB. If the most- significant bit of the

resultant significand is not a one, the result is normalized. The result is rounded to double-precision under

control of the floating-point rounding control field RN of the FPSCR and placed into frD.

Floating-point addition is based on exponent comparison and addition of the two significands. The exponents

of the two operands are compared, and the significand accompanying the smaller exponent is shifted right,

with its exponent increased by one for each bit shifted, until the two exponents are equal. The two signifi-

cands are then added or subtracted as appropriate, depending on the signs of the operands. All 53 bits in the

significand as well as all three guard bits (G, R, and X) enter into the computation.

If a carry occurs, the sum's significand is shifted right one bit position and the exponent is increased by one.

FPSCR[FPRF] is set to the class and sign of the result, except for invalid operation exceptions when

FPSCR[VE] = 1.

Other registers altered:

• Condition Register (CR1 field):

Affected: FX, FEX, VX, OX (if Rc = 1)

• Floating-Point Status and Control Register:

Affected: FPRF, FR, FI, FX, OX, UX, XX,VXSNAN, VXISI

B 0 0 0 0 0 21 Rc

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA A

Programming Environments Manual

PowerPC RISC Microprocessor Family

pem8.fm.2.0

June 10, 2003

Instruction Set

Page 433 of 785

faddsxfaddsx

Floating Add Single (x’EC00 002A’)

fadds frD,frA,frB (Rc = 0)

fadds. frD,frA,frB(Rc = 1)

The floating-point operand in frA is added to the floating-point operand in frB. If the most-significant bit of the

resultant significand is not a one, the result is normalized. The result is rounded to the single-precision under

control of the floating-point rounding control field RN of the FPSCR and placed into frD.

Floating-point addition is based on exponent comparison and addition of the two significands. The exponents

of the two operands are compared, and the significand accompanying the smaller exponent is shifted right,

with its exponent increased by one for each bit shifted, until the two exponents are equal. The two signifi-

cands are then added or subtracted as appropriate, depending on the signs of the operands. All 53 bits in the

significand as well as all three guard bits (G, R, and X) enter into the computation.

If a carry occurs, the sum's significand is shifted right one bit position and the exponent is increased by one.

FPSCR[FPRF] is set to the class and sign of the result, except for invalid operation exceptions when

FPSCR[VE] = 1.

Other registers altered:

• Condition Register (CR1 field):

Affected: FX, FEX, VX, OX (if Rc = 1)

• Floating-Point Status and Control Register:

Affected: FPRF, FR, FI, FX, OX, UX, XX,VXSNAN, VXISI

05610111516202125263031

Reserved

59 D A

B0 0 0 0 021Rc

PowerPC Architecture Level Supervisor Level 32-Bit 64-Bit 64-Bit Bridge Optional Form

UISA A

Programming Environments Manual

PowerPC RISC Microprocessor Family

Instruction Set

Page 434 of 785

pem8.fm.2.0

June 10, 2003

fcfidx64-Bit Implementations Only fcfidx

Floating Convert from Integer Double Word (x’FC00 069C’)

fcfid frD,frB(Rc = 0)

fcfid. frD,frB(Rc = 1)

The 64-bit signed fixed-point operand in register frB is converted to an infinitely precise floating-point integer.

The result of the conversion is rounded to double-precision using the rounding mode specified by

FPSCR[RN] and placed into register frD.