MCS 4 Msc4 Manual

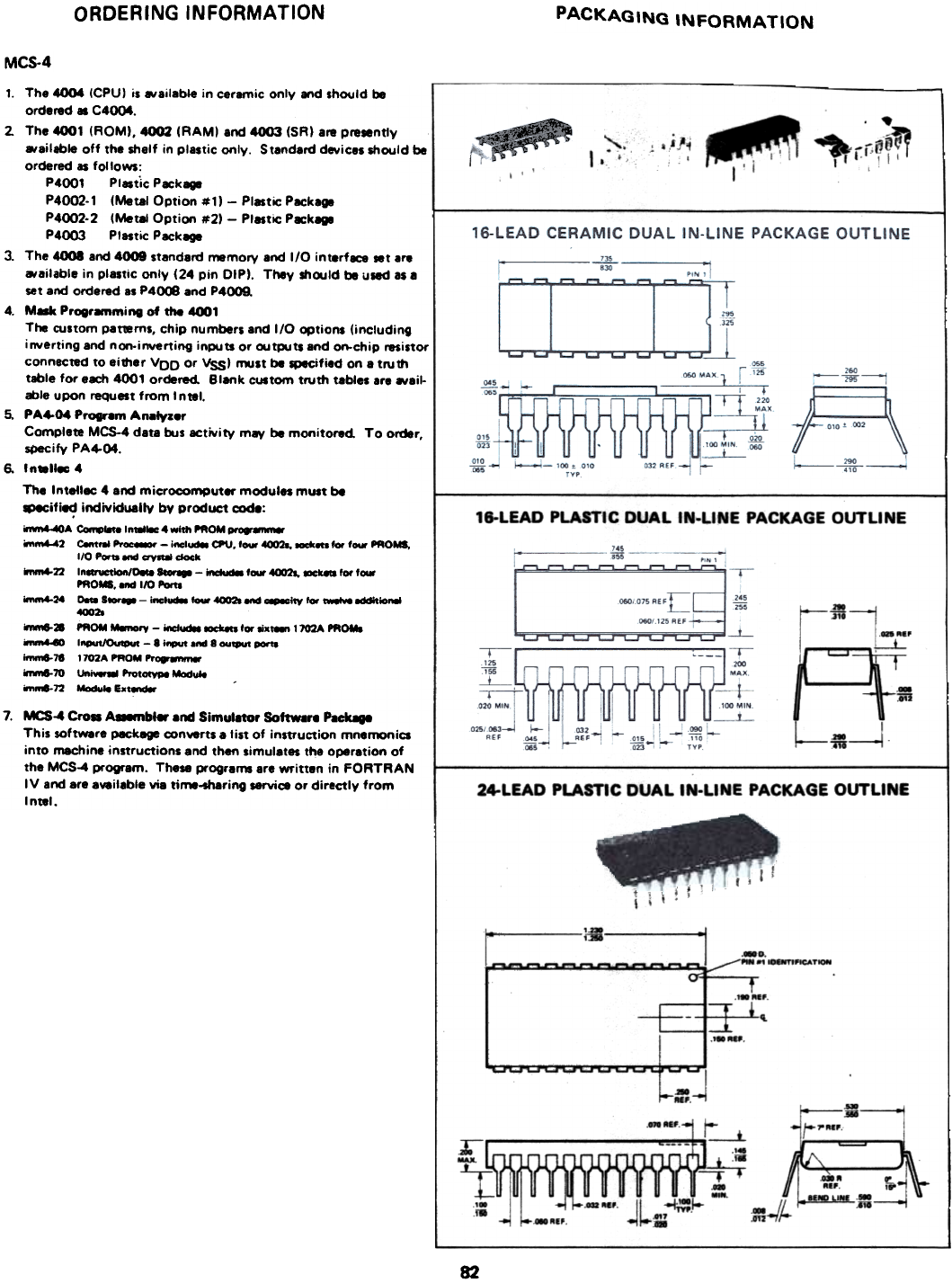

User Manual: Pdf

Open the PDF directly: View PDF ![]() .

.

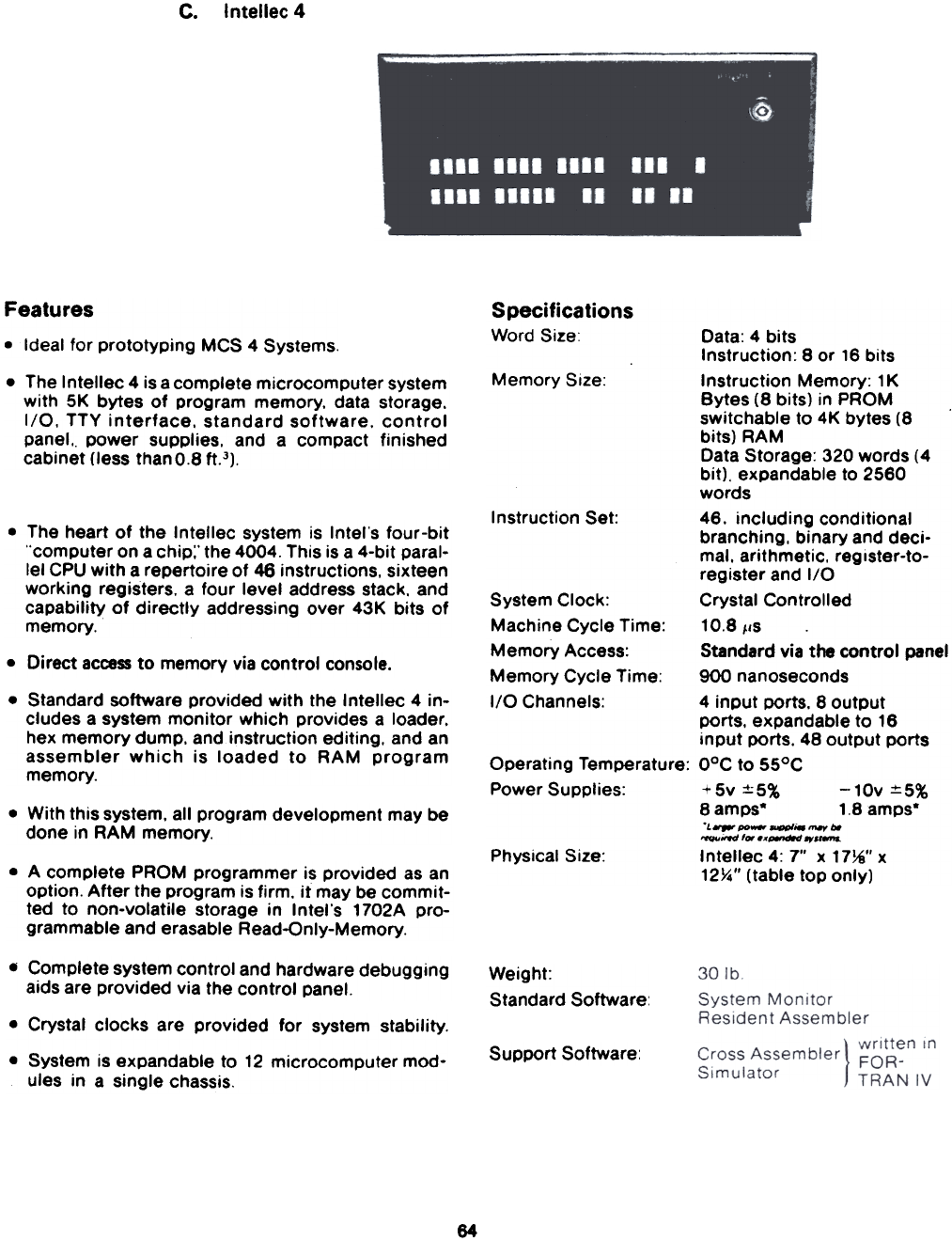

Page Count: 88

"1

Features

. Directly Compatible With

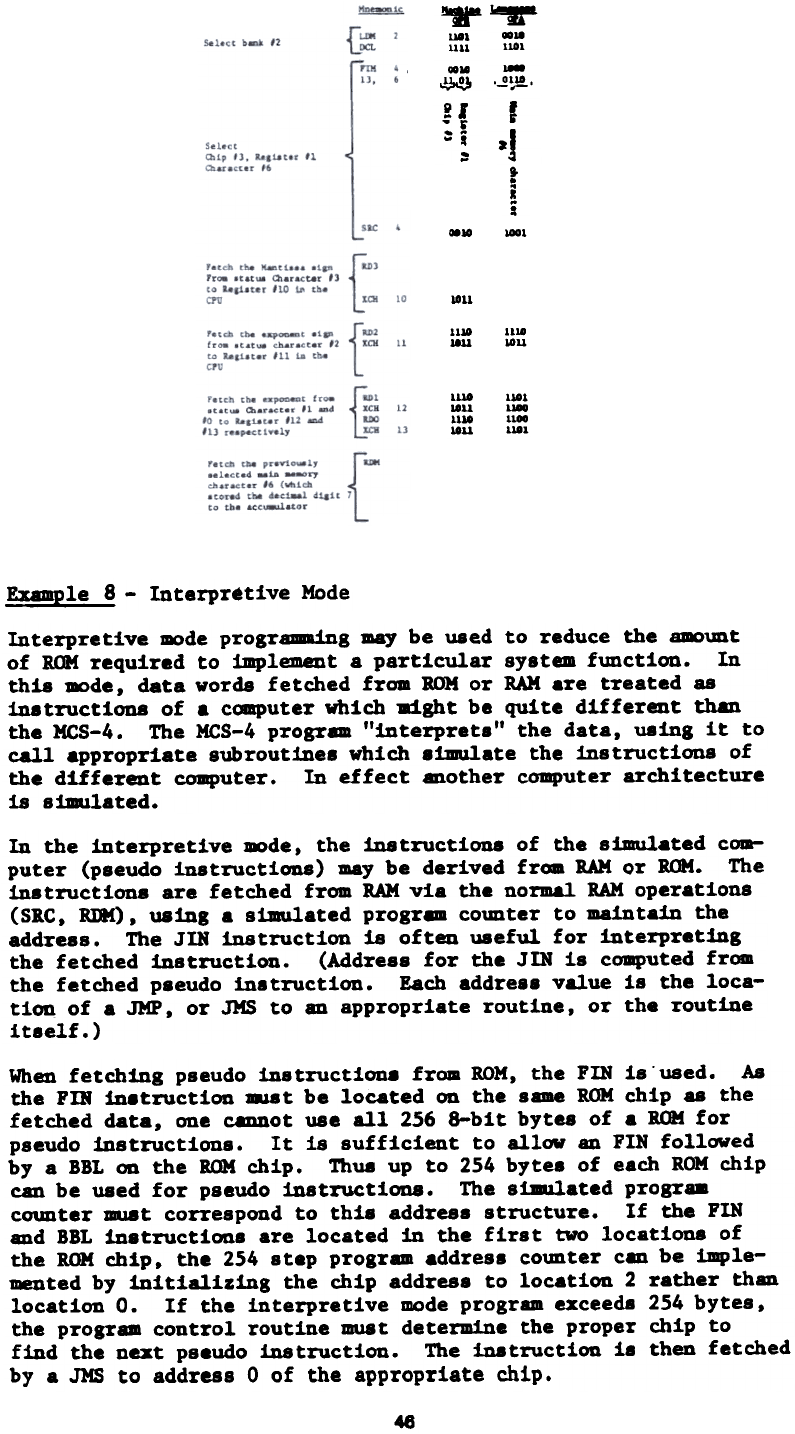

4004 CPU

. Interface 1702A PROMs Directly

to 4004 CPU -- Completely

Eliminates TTL Interface

. Permits Program Storage in

Alterable Memory

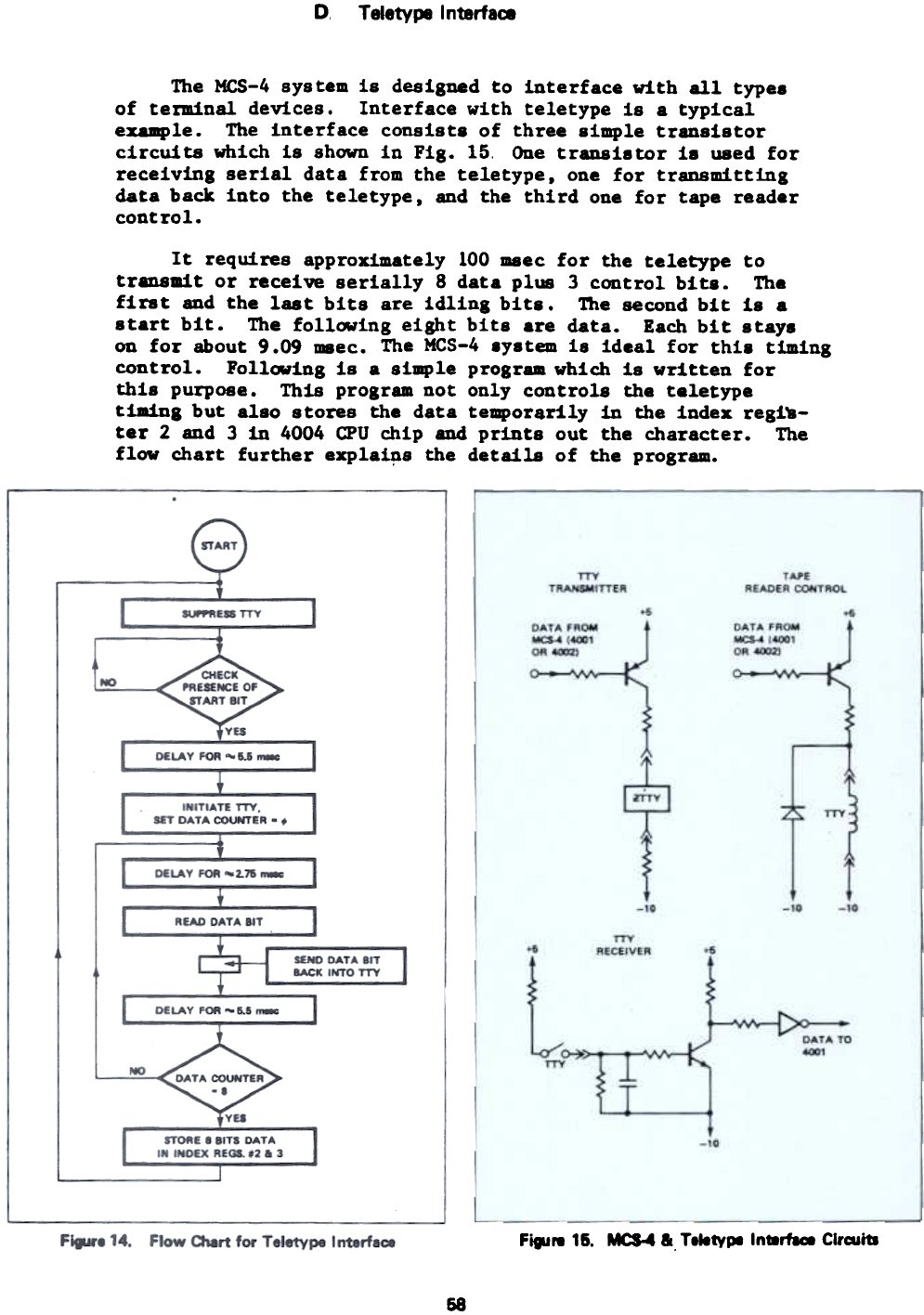

. Execute MCS-4 Programs from

any Mix of Standard Intel PROMs,

ROMs and RAMs

. Expanded 1/0 Port Capability

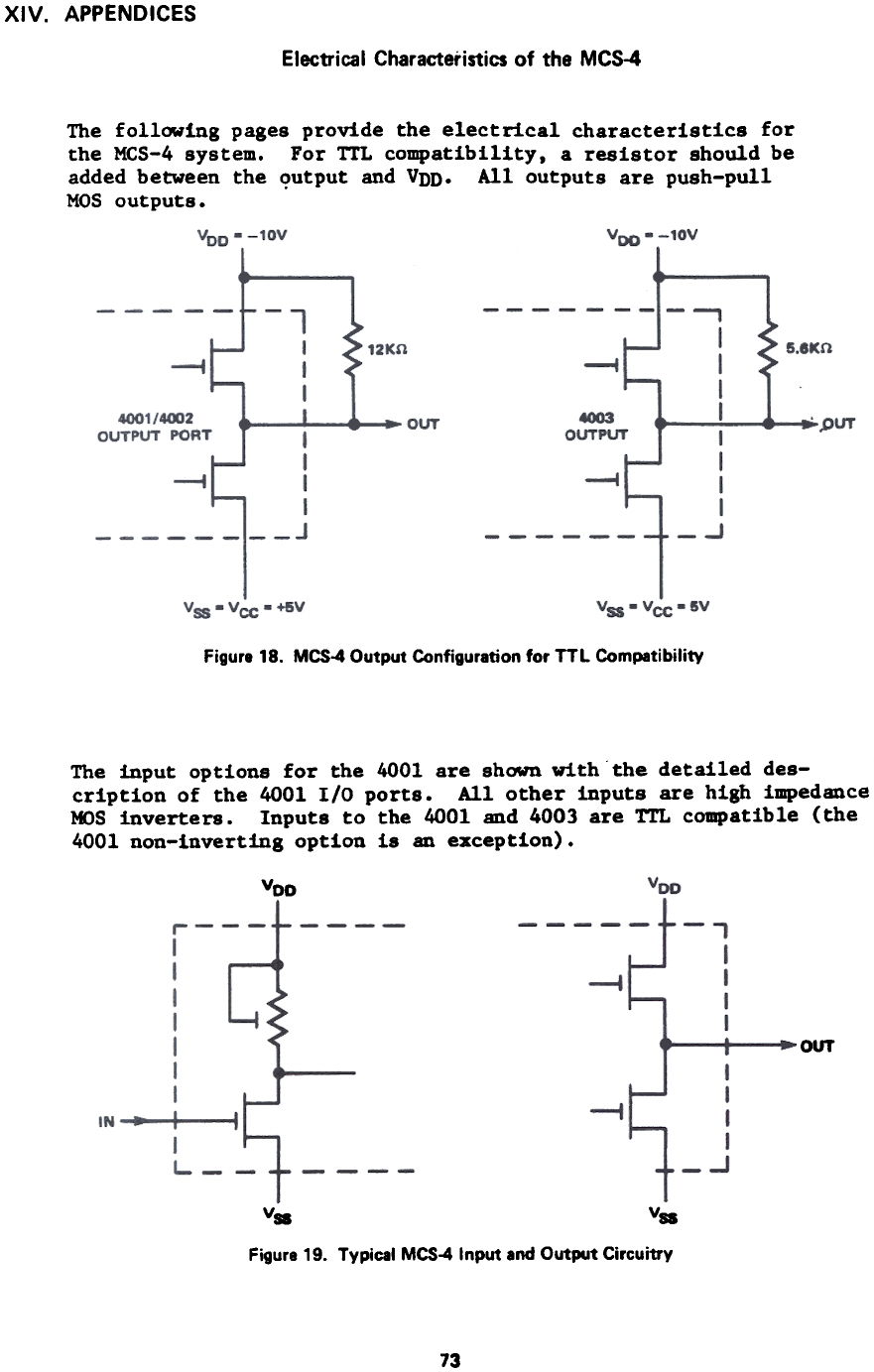

. Each Port May be Both Input and

Output -- Up to 16 4-bit Input

Ports and 16 4-bit Output Ports

. I/O Ports and Control Lines

are TTL Compatible

. Number of I/O Ports is

Independent of the Size of

the Program Memory

. New Instruction WPM (Write

Program Memory) is Used for

Loading Alterable Program

Storage (RAM)

. Microprogrammable

General Purpose Computer

Set

. 4-Bit Parallel CPU With 46

Instructions

. Instruction Set Includes

Conditional Branching,

Jump to Subroutine and

Indirect Fetching

. Binary and Decimal

Arithmetic Modes

. Addition of Two 8-Digit

Numbers in 850

Microseconds

.

. 2-Phase Dynamic Operation

. 10.8 Microsecond

Instruction Cycle

. CPU Directly Compatible

With MCS-4 ROMs and

RAMs

. Easy Expansion - One CPU

can Directly Drive up to

32,768 Bits of ROM and up

to 5120 Bits of RAM

. Unlimited Number of

Output Lines

. Packaged in 16-Pin Dual

In-Line Configuration

.

~

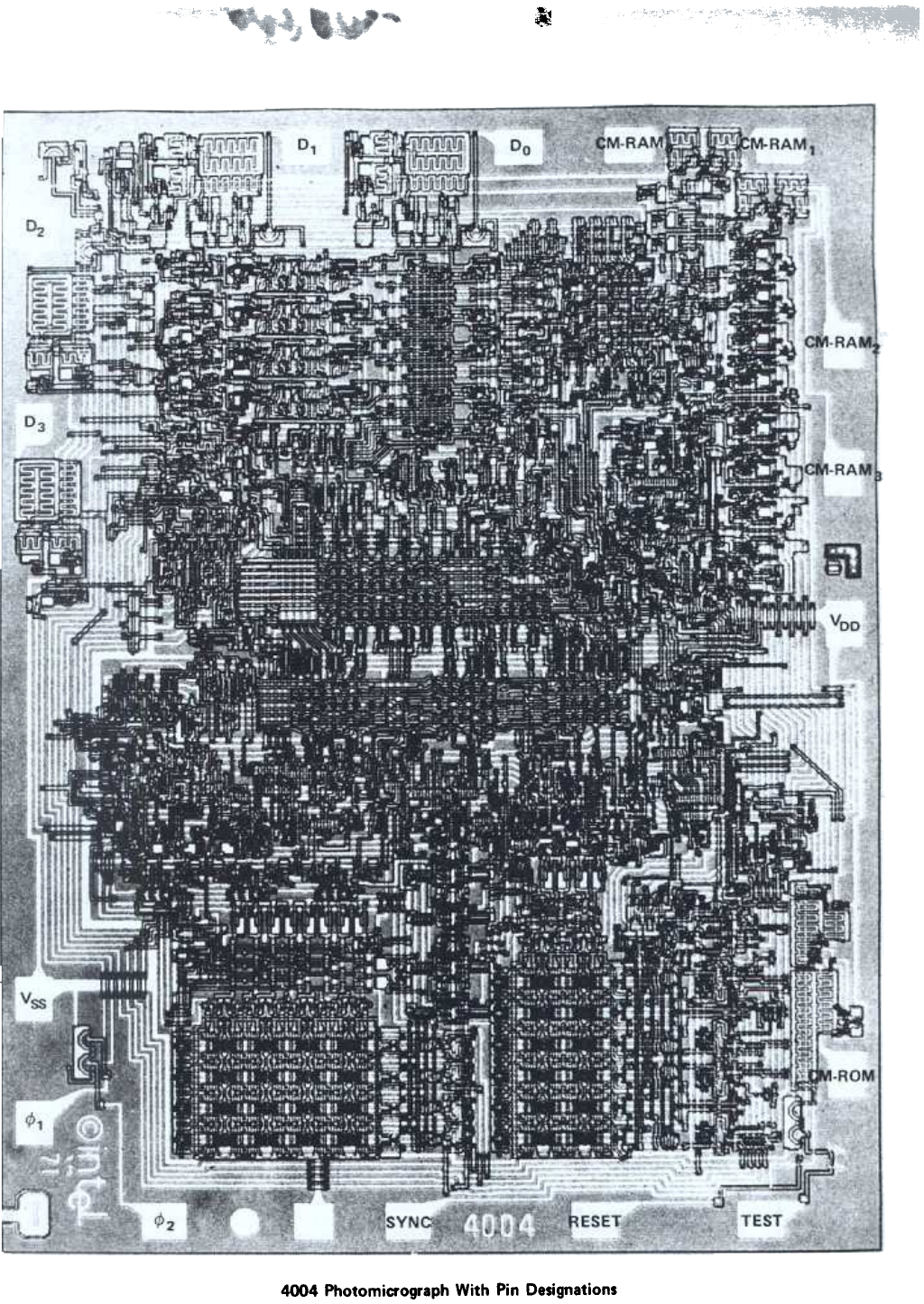

4004 Photomicrograph With Pin Designations

INTRODUCTION - THE ALTERNATIVE TO RANDOM lOGIC SYSTEMS

A. General Discussion

Since its inception, digital computer applications have evolved from

calculation through data processing and into control. The develop-

ment of the minicomputer has vastly increased the scope of computer

usage. In particular, the use of minicomputers in dedicated appli-

cations has had a profound effect on systems design.

Many engineers have found having a minicomputer at the heart of a

system offers significant advantages. Minicomputer systems are

more flexible, can be easily personalized for a particular customer's

requirements, and can be more easily changed or updated than fixed-

logic design systems. For most designers, the programming of a mini-

computer is a much easier and more straightforward procedure than

designing a controller with random logic.

Unfortunately, the size and cost of even the smallest minicomputer has

limited its use to relatively large and costly systems. This has

resulted in many smaller systems being implemented with complicated

random logic. INTEL NOW OFFERS ANOTHER ALTERNATIVE. . . THE MCS-4

MICRO COMPUTER SET.

This new concept in LSI technology makes the power of a general pur-

pose computer available to alDK>st every logic designer and represents

a strong attack on the dependency of systems manufacturers on compli-

cated random logic systems. This component computer from Intel can

provide the same arithmetic, control and computing functions of a

minicomputer in as few as two 16 pin DIP's and costs nearly 2 orders

of magnitude less.

The set is not designed to compete with the minicomputer, but rather

to extend the power of the concept into new ranges of applications.

For example, many systems now built of 55I and MSI TTL can now be.

implemented with a totally self-contained system built around this

set of devices.

Heart of each system is a single chip central processor unit (CPU)

which performs all control and data processing functions. Auxiliary

to the CPU are ROM's which store microprograms and data tables; RAM's

which store data and instructions. and Shift Registers which can

expand the I/O capacity of the system. The MCS-4 system communicates

with circuits and devices outside the family through "ports" provided

on each RAM and ROM.

A system using this set of devices will usually consist of one CPU,

from one to 16 ROM's, up to 16 RAM's and an arbitrary number of SR's.

A minimum system could be designed with just one CPU and one ROM.

With these components, you can build distributed computers, dedicated

computers, or personalized computers and utilize the almost infinite

combinations of microprogramming. The designer buys standard devices,

and with microprogramming of the ROM fulfills his own unique circuit

requirements.

1

~

The three major advantages of Intel microcomputers:

Qreat system flexibility, with easy program changes, ability

to expand or shrink the system, and small size and low power.

Expediency of design, because ROM programming is easier than

random circuit design, system checkout is easier using electri-

cally programmable and erasable ROM's, and ability to insert

new microprograms helps prevent system obsolescence.

Manufacturing economies come from simple DIP package design,

automatic insertion, lower labor costs, lower inventory of

parts and boards.

When designing with random logic (logic gates, flip flops, etc.),

the designer will usually start with a description of the desired

function and attempt to wire counters, gates, etc. to achieve this

function. Switches, displays, etc. are also connected to the logic

To correct errors or make changes in a design usually requires sig-

nificant changes in wiring, often requiring that circuit boards be

scrapped and replaced by new ones.

To do the same design with the HCS-4 Micro Computer Set, the designer

again starts with the functional description. However, he implements

these functions by encoding suitable sequences of instructions in ROM.

The MCS-4 instruction set is quite complete and allows a wide variety

of functions to be performed: decimal or binary arithmetic, counting,

decisions, table-lookup, etc. Switches, displays, etc. are connected

to the system via the input and output ports.

As a result of this organization. almost the entire logic. the entire

I'-personality" of the machine is determined by the instructions in ROM.

Very significant modifications of machine characteristics can be made

by changing or adding ROM's without making any changes in wiring or

circuit boards.

Thus the set offers tremendous flexibility of design and allows the

user to have many of the desirable features of a custom MaS LSI design--

small package count. a set of components which is uniquely his own

(for each user's program routines are his proprietary property)--

and yet have none of the disadvantages of long development cycle. high

development costs. etc. The short design cycle and flexibility asso-

ciated with ROM programming allows much more rapid response to market

demands than is possible with custom LSI and thus provides insurance

against obsolescence.

B. Applications for the MCS-4 Micro Computer Set

Heart of the MCS-4 micro computer set is the 4004 CPU. This device

has a powerful and versatile instruction set which allows the system

to perform a wide variety of arithmetic, control and decision functions

The microprograms stored in the ROM devices give the designer the

power of designing custom computers with standard components. You can

2

use the MCS-4 almost anywhere. Here are a few examples:

Control Functions - Because of low initial cost and flexibility

of programming, the MCS-4 can be used in place of random logic

in systems such as those in process control, numeric controls,

elevator controls, highway and rail traffic controls. By chang-

ing ROM microprograms the whole system can easily be modified

and updated.

Computer Peripherals - The system can be conveniently used in

peripheral equipment to control displays, keyboards, printers,

readers, plotters and to give intelligence to terminals.

Computing Systems - The MCS-4 system is ideally suited for such

devices as billing machines, cash registers, point of sale ter-

minals and accounting machines. For example, the adding of two

8-digit numbers can be done in 850 microseconds. In addition,

the MCS-4 can be efficiently used to decentralize central com-

,puter functions.

Other Applications - The elements of the MCS-4 have many applica-

tions within transportation, automotive, medical electronics and

test systems. where inexpensive dedicated computers can improve

system performance.

c. Features of the MCS-4

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

4-bit parallel CPU with 45 instructions

Decimal and binary arithmetic modes

10.8 ~ instruction cycle

Addition of TWo 8-digit numbers in 850 psec.

Sixteen 4-bit general purpose registers

Nesting of sUbroutines up to 3 levels

Instruction Set includes conditional branching, jump to subroutine,

and indirect fetching

2-phase dynamic operation

Synchronous operation wi th memories

Direct compatibility with 4001,4002 and 4003

No interface circuitry to memory and I/O required

Directly drives up to: 4K by 8 ROM (16 4001's)

1280 by 4 RAM (16 4002's)

128 I/O lines (without 4003)

Unlimited I/O (with 4003's)

Memory capacity expandable through bank switching

16-pin DIP package

P-channe1 Silicon Gate MaS

Minimum system: CPU and one ROM

3

II, MCS-4 SYSTEM DESCRIPTION

General Description

A.

Each MCS-4 circuit constitues a basic standard building block which

allows the design of many different types of systems which can be

fabricated using the same parts. The only custom part is the ROM

chip which will store a microprogram defined by the user and requires

a metal mask option for each new program.

The MCS-4 micro computer set consists of the following 4 chips, each

packaged in a 16 pin DIP package:

(1)

(2)

(3)

(4)

A Central Processor Unit Chip -CPU - 4004

A Read Only Memory Chip - ROM - 4001

A Random Access Memory Chip - RAM - 4002

A Shift Register Chip - SR - 4003

The CPU contains the control unit and the arithmetic unit of a general

purpose microprogrammable computer. The ROM stores microprograms and

data tables, the RAM stores data and instructions, and the Shift Regis-

ter is used in conjunction with I/O devices to effectively increase

the number of I/O lines.

The MCS-4 set has been designed for optimum interfaceability; the

CPU communicates with the RAM's and ROM's by means of a 4-line data

bus (DO' Dl' D , D). This single data bus is used for all infor-

mation flow be~ee~ the chips except for control signals Which are

sent to RAM and ROM over 5 additional lines. One.CPU controls up

to 16 ROM's (4K x 8 words), 16 RAM's (1280 x 4 words), and 128 I/O

lines without requiring any interface circuit. With the addit,ion

of few gates up to 48 ROMS & RAMS combined and 192 I/O lines can be

controlled by one CPU.

The I/O function, although different from the ROM and RAM functions,

is physically located in the ROM and RAM chips. Each 4001 and 4002

has 4 I/O lines for communication with I/O devices.

4001-ROM - The 4001 is a 2048 Bit metal mask programmable ROM providing

custom microprogramming capability for the MCS-4 micro

computer set. Each chip is organized as 256 x 8 bit words

which can be used for storing programs or data tables. Each

chip also has a 4 bit input-output (I/O) port which is used

to route information to and from the data bus lines in and

out of the system.

4002-RAM - The 4002 performs two functions. As a RAM it stores 320

bits arranged as 4 registers of twenty 4-bit characters each.

As a vehicle of communication with peripheral devices,it

is provided with 4 output lines and associated contro110gic

to perform output operations.

4003-SR - The 4003 is a 10 bit Seria1-in/paralle1-out, serial-out

shift register. Its function is to increase the number of

output lines to interface with I/O devices such as keyboards,

displays, printers, te1etypewriters~ switches, readers, A-D

converters, etc.

4

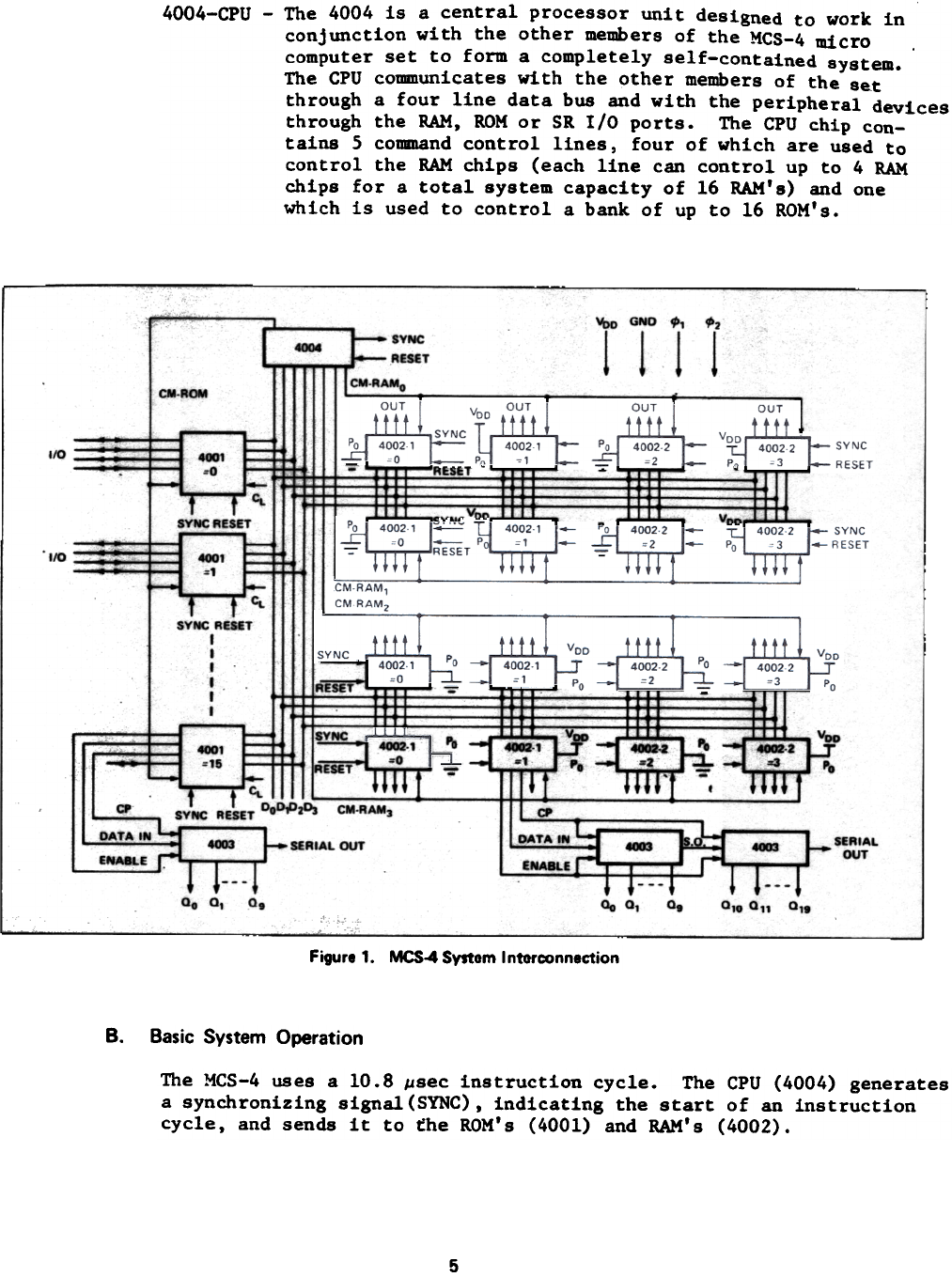

4004-CPU - The 4004 is a central processor unit designed to work in

conjunction with the other members of the MCS-4 micro

computer set to form a completely self-contained system.

The CPU communicates with the other members of the set

through a four line data bus and with the peripheral devices

through the RAM, ROM or SR I/O ports. The CPU chip con-

tains 5 command control lines, four of which are used to

control the RAM chips (each line can control up to 4 RAM

chips for a total system capacity of 16 RAM's) and one

which is used to control a bank of up to 16 ROM's.

~D GNO .,

1 1 1

,.

1.

4004

CM.ROM

1/0 4001 I

=0 I

.r-r ~

SYNC RESET

I

,-

I/O 4001

=1

-1~ CL

SYNC RESET

Figure 1. MCS-4 System Interconnection

B. Basic System Operation

The MCS-4 uses a 10.8 ~sec instruction cycle. The CPU (4004) generates

a synchronizing signal (SYNC), indicating the start of an instruction

cycle, and sends it to the ROM's (4001) and RAM's (4002).

5

I SYNC

I

L - RESET

I

':M-RAMo

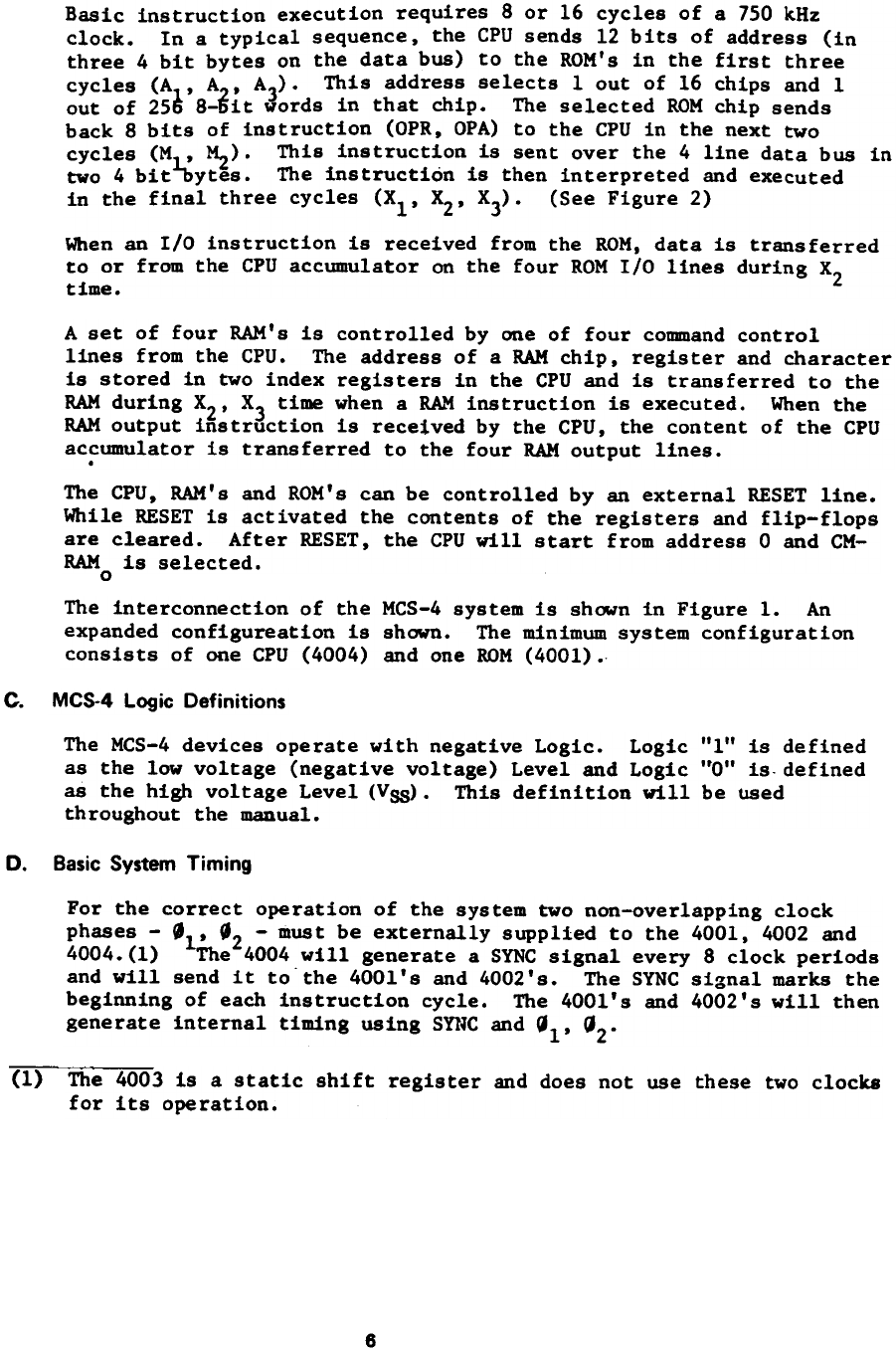

Basic instruction execution requires 8 or 16 cycles of a 750 kHz

clock. In a typical sequence, the CPU sends 12 bits of address (in

three 4 bit bytes on the data bus) to the ROM's in the first three

cycles (A , A ,A3). This address selects lout of 16 chips and 1

out of 256 8-~it words in that chip. The selected ROM chip sends

back 8 bits of instruction (OPR, OPA) to the CPU in the next two

cycles (ML' ~). This instruction is sent over the 4 line data bus in

two 4 bit~ytes. The instruction is then interpreted and executed

in the final three cycles (Xl' ~,X3). (See Figure 2)

When an r/o instruction is received from the ROM, data is transferred

to or from the CPU accumulator on the four ROM r/o lines during X2

time.

A set of four RAM's is controlled by one of four command control

lines from the CPU. The address of a RAM chip, register and character

is stored in two index registers in the CPU and is transferred to the

RAM during X2' X3 time when a RAM instruction is executed. When the

RAM output instruction is received by the CPU, the content of the CPU

accumulator is transferred to the four RAM output lines.

.

The CPU. RAM's and ROM's can be controlled by an external RESET line.

While RESET is activated the contents of the registers and flip-flops

are cleared. After RESET, the CPU will start from address 0 and CM-

RAM is selected.

0

The interconnection of the MCS-4 system is shown in Figure 1. An

expanded configureation is shown. The minimum system configuration

consists of one CPU (4004) and one ROM (4001).

c. MCS-4 Logic Definitions

The MCS-4 devices operate with negative Logic. Logic "1" is defined

as the low voltage (negative voltage) Level and Logic ItO" is- defined

as the high voltage Level (Vss>. This definition will be used

throughout the manual.

D. Basic System Timing

For the correct operation of the system two non-overlapping clock

phases - '1' ~2 - must be externally supplied to the 4001,4002 and

4004.(1) The 4004 will generate a SYNC signal every 8 clock periods

and will send it to'the 400l's and 4002's. The SYNC signal marks the

beginning of each instruction cycle. The 400l's and 4002's will then

generate internal timing using sn~c and ~1' Q2.

(I) The 4003 is a static shift register and does not use these two clocks

for its operation.

6

~~,...

c~

Figure 2. MCS-4 &.ic Instruction Cycle

Figure 2 shows how a basic instruction cycle is subdivided and what

the activity is on the data bus during each clock period. Each data

bus output buffer has three possible states: "1", "0" and floating.

At a given time, only 1 output buffer is allowed to drive a data

line, therefore all the other buffers must be in a floating condition

However, more than 1 input buffer per data line can receive data at

the same time.

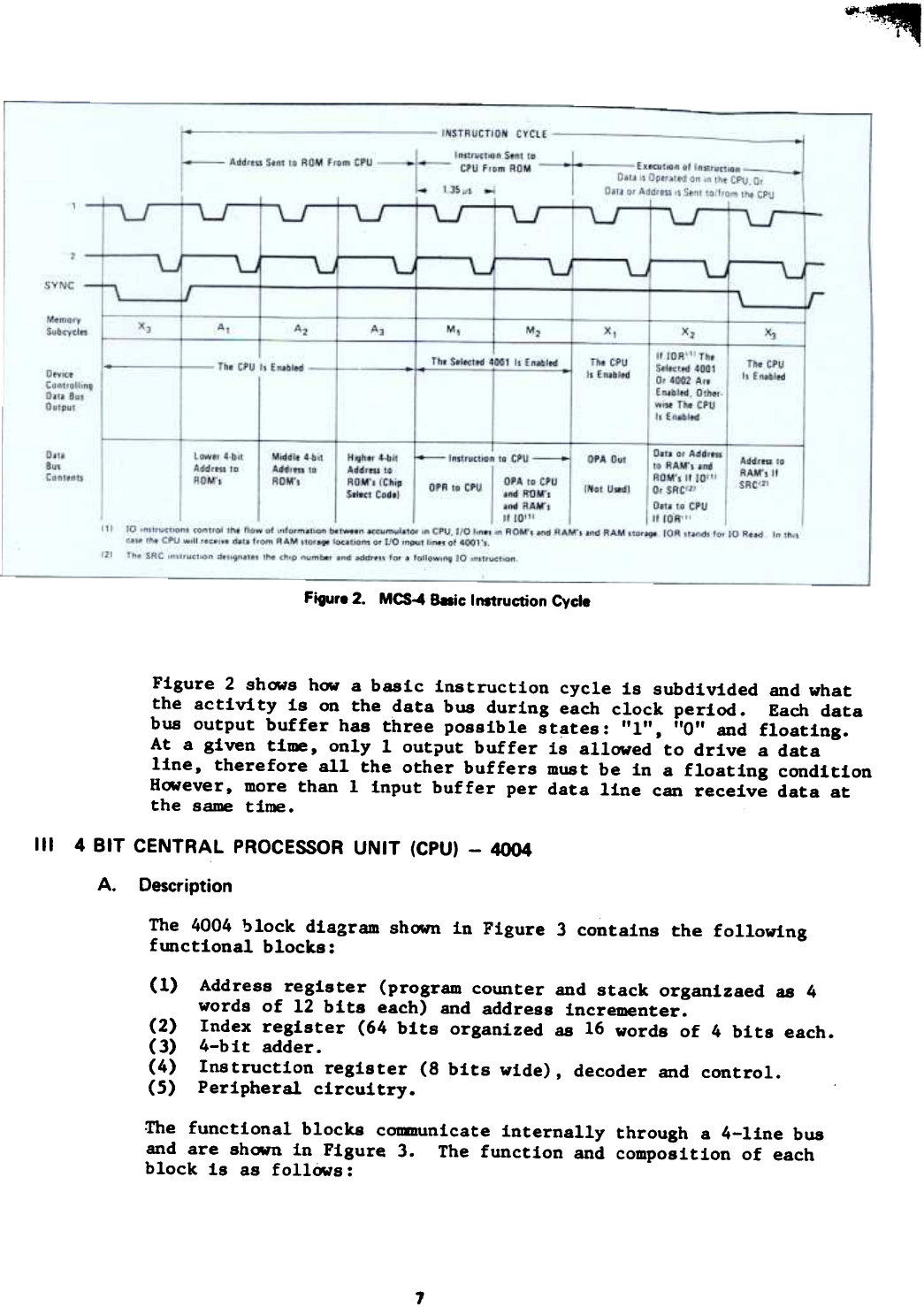

III 4 BIT CENTRAL PROCESSOR UNIT (CPU) - 4004

A. Description

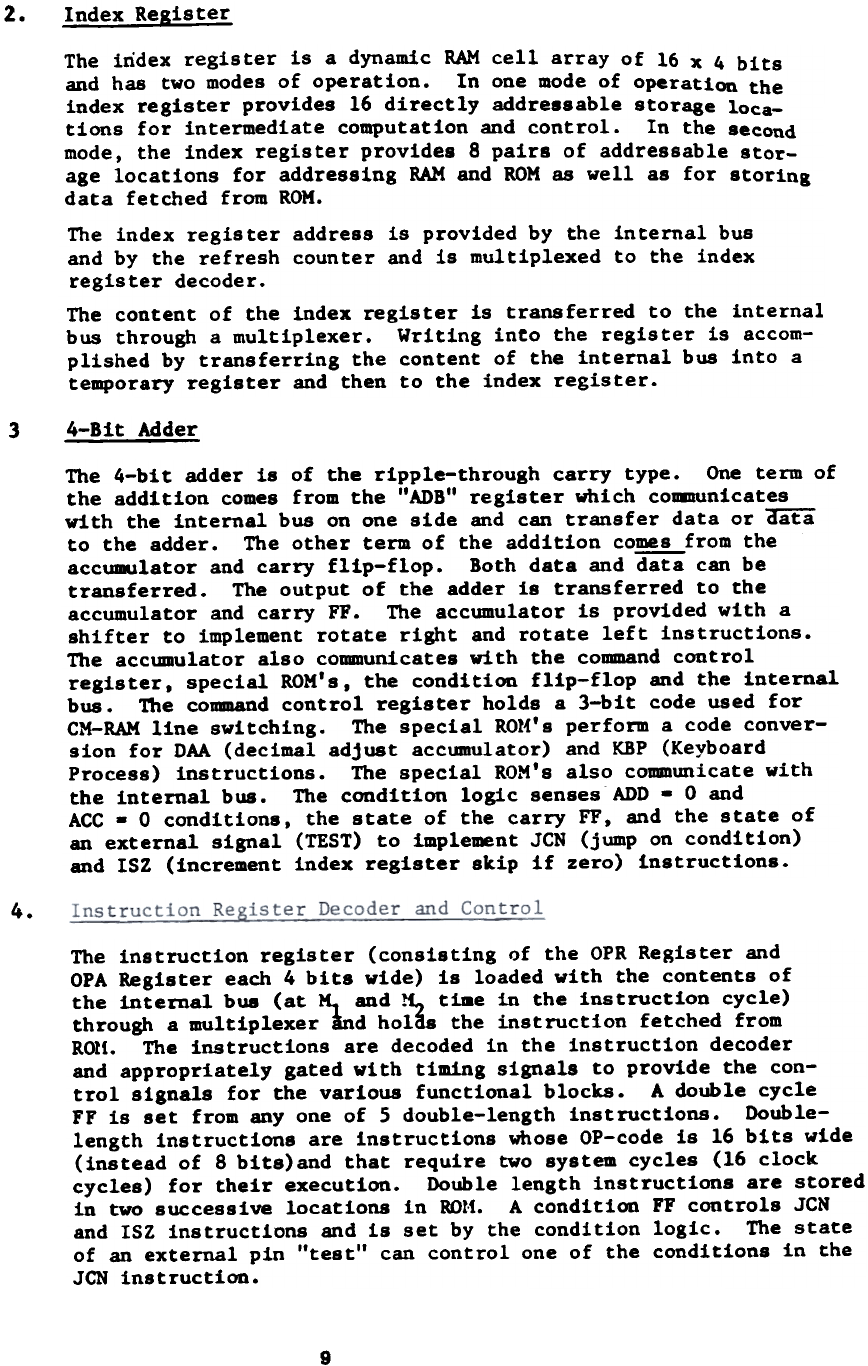

The 4004 block diagram shown in Figure 3 contains the following

functional blocks:

(1)

(2)

(3)

(4)

(5)

Address register (program counter and stack organizaed as 4

words of 12 bits each) and address incrementer.

Index register (64 bits organized as 16 words of 4 bits each.

4-bit adder.

Instruction register (8 bits wide), decoder and control.

Peripheral circuitry.

Ihe functional blocks communicate internally through a 4-line bus

and are shown in Figure 3. The function and composition of each

block is as follOws:

7

.1. Address R ram counter & Stack & Address Incrementer

The address register is a dynamic RAM cell array of 4 x 12 bits.

It contains one level used to store the instruction address

(program counter) and 3 levels used as a stack for subroutine

calls. The stack address is provided by the effective address

counter and by the refresh counter, and it is multiplexed to the

decoder.

The address when read is stored in an address buffer and is

demultiplexed to the internal bus during A , A2' and AJ in three 4-

bit slices (see Figure 2 for basic instruc!ion cycle). The address

is incremented by a 4-bit carry look-ahead circuit (address incre-

menter) after each 4-bit slice is sent out on the data bus. The

incremented address is transferred back to the address buffer and

finally written back into the address register.

SYNC TOT RESET

CM CM CM CM

RAMo RAM, RAM, RAMJ

v. v.

r I

.. SYNC

OOTPVT

eufflR

..

INTERNAl

RElET

'IF

---T-

CM-RAM

OUTPUT BUFFERS TIMING

ADORE.

INCREMENTER

~~~

CC*TROL

REGISTER

~

h~ ~ CYCLE LOG~

'IP . 'IF

~

AW\.I.. MULTIPLEXER a-

ICX*TROL

FOR

THE

~RE8

MOISTER .

IMJeX

REGISTER

:;rtiR

lrC<*TROl

ADORE.

REGISTER

(PROGRAM

~ER

. STACK'

4 . 12 BIT

DYNAMIC

RAM

.-CIAL

~

~ER

~IVER

.

MUX

~

~IN-OUT

8UFFE~

.,

ACC~AT~

~ CMRY FIF ~A

DECOOER

~

DlmDER

ADGER

.

~

OONTROt.

~

MUX

. "IFTER

#2

j MJFFER .

r8"t REGISTER r-

---I REFRE84

.~R

I~UCTION ~R

~.3 ~ER ~EFFECTIVE A(X)RE8

~R

I I*TR~

orA

REGIsnR

~I

IEGI~R

~

,REGISTER

~

AW\.I.

.MUX

ADa

BUffER REG.

..

--L-

REFRE"

ICOUNTIR

DECOOER

DRIVER

.

MUX

INDEX

REGISTER

',.4 lIT

DYNAMIC RAM

~

INTERNAl. DATA IW

Figure 3. 4004 CPU Block Diagram

8

CM

~=

BUFFER

2. Index Register

The index register is a dynamic RAM cell array of 16 x 4 bits

and has two modes of operation. In one mode of operation the

index register provides 16 directly addressable storage loca-

tions for intermediate computation and control. In the second

mode, the index register provides 8 pairs of addressable stor-

age locations for addressing RAM and ROM as well as for storing

data fetched from ROM.

The index register address is provided by the internal bus

and by the refresh counter and is multiplexed to the index

register decoder.

The content of the index register is transferred to the internal

bus through a multiplexer. Writing into the register is accom-

plished by transferring the content of the internal bus into a

temporary register and then to the index register.

34-Bit Adder

The 4-bit adder is of the ripple-through carry type. One term of

the addition comes from the "ADB" register which coanunicates

with the internal bus on one side and can transfer data or QiEi

to the adder. The other term of the addition comes from the

accumulator and carry flip-flop. Both data and data can be

transferred. The output of the adder is transferred to the

accumulator and carry FF. The accumulator is provided with a

shifter to implement rotate right and rotate left instructions.

The accumulator also communicates with the command control

register, special ROM's, the condition flip-flop and the internal

bus. The command control register holds a 3-bit code used for

CM-RAM line switching. The special ROI~'s perform a code conver-

sion for DAA (decimal adjust accumulator) and KBP (Keyboard

Process) instructions. The special ROM's also communicate with

the internal bus. The condition logic senses ADD - 0 and

ACC - 0 conditions, the state of the carry FF, and the state of

an external signal (TEST) to implement JCN (jump on condition)

and ISZ (increment index register skip if zero) instructions.

4.

The instruction register (consisting of the OPR Register and

OPA Register each 4 bits wide) is loaded with the contents of

the internal bus (at ~ and ~ t~e in the instruction cycle)

through a multiplexer And hol&s the instruction fetched from

ROll. The instructions are decoded in the instruction decoder

and appropriately gated with timing signals to provide the con-

trol signals for the various functional blocks. A doUble cycle

FF is set from anyone of 5 double-length instructions. Double-

length instructions are instructions whose OP-code is 16 bits wide

(instead of 8 bits)and that require two system cycles (16 clock

cycles) for their execution. Double length instructions are stored

in two successive locations in ROl.I. A condition FF controls JCN

and ISZ instructions and is set by the condition logic. The state

of an external pin "test" can control one of the conditions in the

JCN instruction.

9

5. Peripheral Circuitry

This includes:

a. The data bus input-output buffers communicating between

data pads and internal bus.

b. Timing and SYNC generator.

c. 1 ROM command control (CM-ROM) and the 4 RAM command control

(C~RAMi) output buffers.

d. Reset flip-flop.

During reset (Reset pin low), all RAM's and static FF's are cleared,

and the data bus is set to "0". After reset, program control will

start from "0" step and CM-RAM is selected. To completely clear

all registers and RAM locationi in the CPU the reset signal must be applied

for at least 8 full instruction cycles (6-4 clock cycles) to allow the

index register refresh counter to scan all locations in memory.

(256 clock cycles for the 4002 RAM).

6.Instruction Repertoire

The instruction repertoire of the 4004 consists of:

a. 16 machine instructions (5 of which are doUble length)

b. 14 accumulator group instructions

c. 15 in~ut/outP.ut and RAM instructions

B.

The instruction set and its format will be briefly described in

the next section. Section VII will then describe each instruction

in detail.

CPU Instruction Set Format, Index Register Organization,

and Operation of 'the Address Register and Command Lines

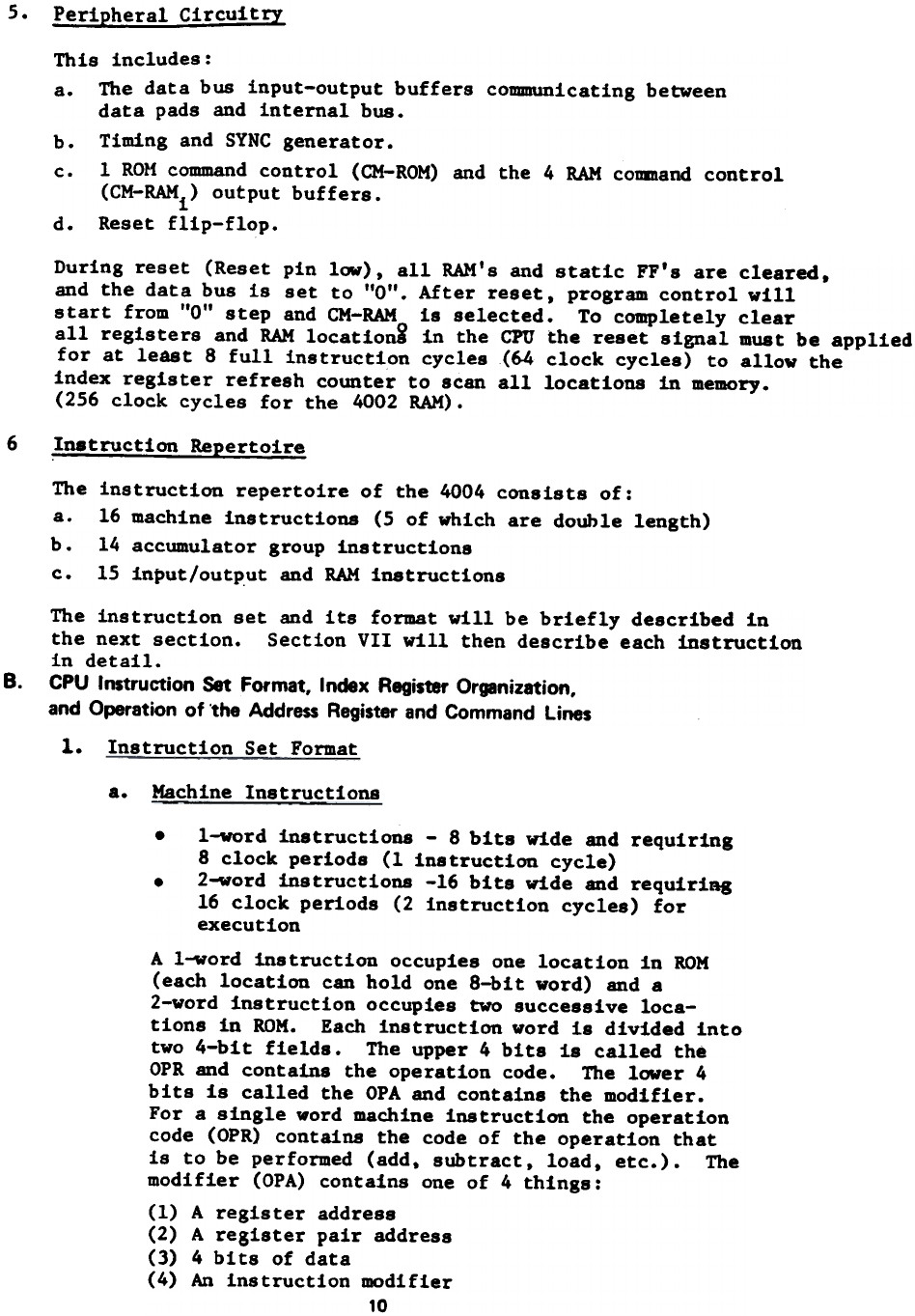

1. Instruction Set Format

Machine Instructions

a.

. l-word instructions - 8 bits wide and requiring

8 clock periods (1 instruction cycle)

. 2-word instructions -16 bits wide and requiriag

16 clock periods (2 instruction cycles) for

execution

A l-word ins truction occupies one location in ROM

(each location can hold one 8-bit word) and s

2-word instruction occupies two successive loca-

tions in ROM. Esch instruction word is divided into

two 4-bit fields. The upper 4 bits is called the

OPR and contains the operation code. The lower 4

bits is called the OPA and contains the modifier.

For a single word machine instruction the operation

code (OPR) contains the code of the operation that

is to be performed (add. subtract. load. etc.). The

modifier (OPA) contains one of 4 things:

(1) A register address

(2) A register pair address

(3) 4 bits of data

(4) An instruction modifier

10

For a 2-word machine instruction the 1st word is similar

to a l-word instruction, however, the modifier (OPA)

contains one of 4 things:

(1) A register address

(2) A register pair address

(3) The upper portion of another ROM address

(4) A condition for jumping

ONE WORD INSTRUCTIONS

0, 0, 0, 0. 0, 0, 0, 0.

Ix/xlxlxJxlx/xlxl

~ DrA

nW> M>RD INSTRUCTIONS

lit INSTRtx:TION CYCLE 2oId INSTRtx:T1ON CYCLE

D, DJ D, De D, DJ D, De D, D, D, De D, DJ D, De

I X I X I X I X I X I X I X I ~l I X I X I X I X I X I X I X I Xl

~ ~A ~ ~A

( OP ~ I MODIFIER .J

I ~COOI I MOOIFIERI

I OP CODE I ~IFIER I

lx I x I x I x I ~NO~~A~E;;ERR INDEX REGISTER X X X X AO~ESS

R R R R

~

I X I X I X I X IIN:Ex.~~~S:S:R P:R INo X REGISTER PAIR

X X X X ADDRESS

R R R X

OR

1 X I X 1 X I X 1 DATA 1

1"1"1"1"100001

I w I w I w I v I ~R ADORE. I

I X I X I X I X I A, AJ AJ AJ I

OR

, v I v I v I v , CONDITION I

,X I X I X I X I c, C. CJ C. I

OR

Ix I x I x I x I ~NDE:'l.~~~;ER R INDEX REGISTER X X X X ADDRESS

R R

MIDOLE ADDRESS LOWER ADORE8

A, A, A, A, A, A, A, A,

OR

l x I x I x I x IIN~XA~~rs\R PA:IINDEX REGISTER PAIR

X X X X ADDRESS

R

I UPPER DATA I LOWER DATA I

I DZ OJ DZ OJ I D, D, D, D, I

T8bIo 1- M8d1ine Instruction F~

The 2nd word contains either the middle portion (in OPR) and

lower portion (in OPA) of another ROM address or 8 bits of

data (the upper 4 bits in OPR and the lower 4 bits in OPA).

The upper 4 bits of instruction (OPR) will always be fetched

before the lower 4 bits of instruction (OPA) during MI and

M2 times respectively. Table I illustrates the contents of

each 4-bit field in the machine instructions.

b. Input/Output & RAM Instructions and Accumulator Group

Instructions

In these instructions (which are all single word) the OPR

contains a 4-bit code which identifies either the I/O

instruction or the accumulator group instruction and the OPA

contains a 4-bit code which identifies the operation to be

performed. Table II illustrates the contents of each 4-bit field.

0, 0, Dt Dt Dt 0, Dt Dt

Lxlxlxlxlx!xlx!xl

~ ~

IWVY.QJTPUT . I . I . I . I a I - I - I - I - I

RAMIN8TR~~ I 1 I 1 I 1 I . I x I x I x I x I

~ULATO" GA~ . 1 I 1 I 1 I 1 I x I x I x I x I

INIT"~'OM ."'I'I'IAIAIAIAI

--AI X . EITHB A ~ A ..,-.

Table II - 1/0 and Accumulltor Group Instruction Formats

11

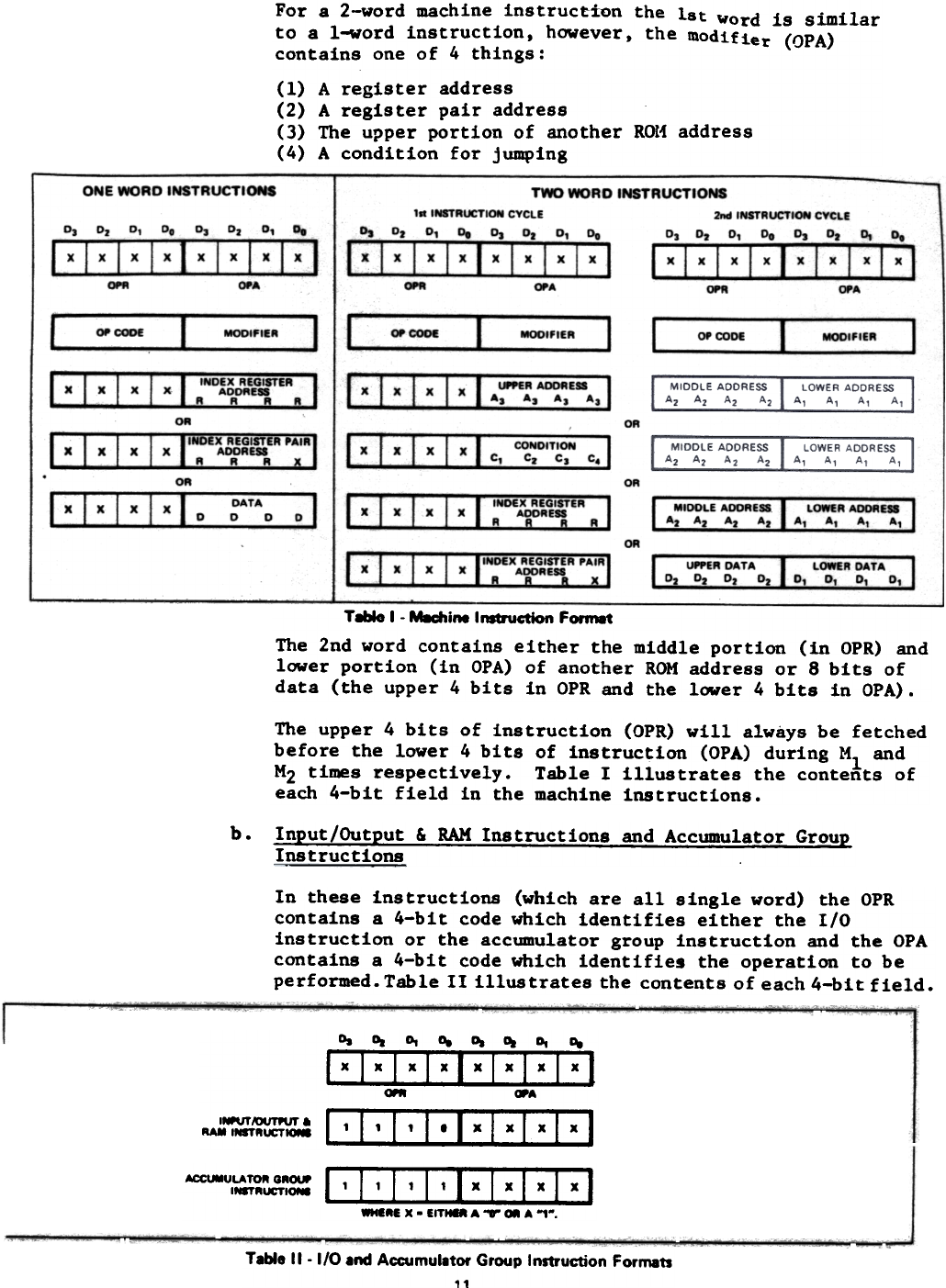

2. Index Register Oraanization

The index register can be addressed in two modes

By specifying lout of 16 possible locations with art OPA

code of the form RRRR(l) (See Table III).

a.

b. By specifying lout of 8 pairs with an OPA code of the

form RRRX{2) (See Table III).

When the index register is used as a pair register, the even

number register (RRRO) is used as the location of the middle

address or the upper data fetched from the ROM, the odd nwmer

register (RRRl) is used as the location of the lower address

or the lower data fetched from the RO~.

SINOLE REGISTER ADORE_NO

REGISTER 'AIR AOORESING

REGISTER

NU_ER

REGISTER

PAIR

N~ER

Teble III . Index Register Organization

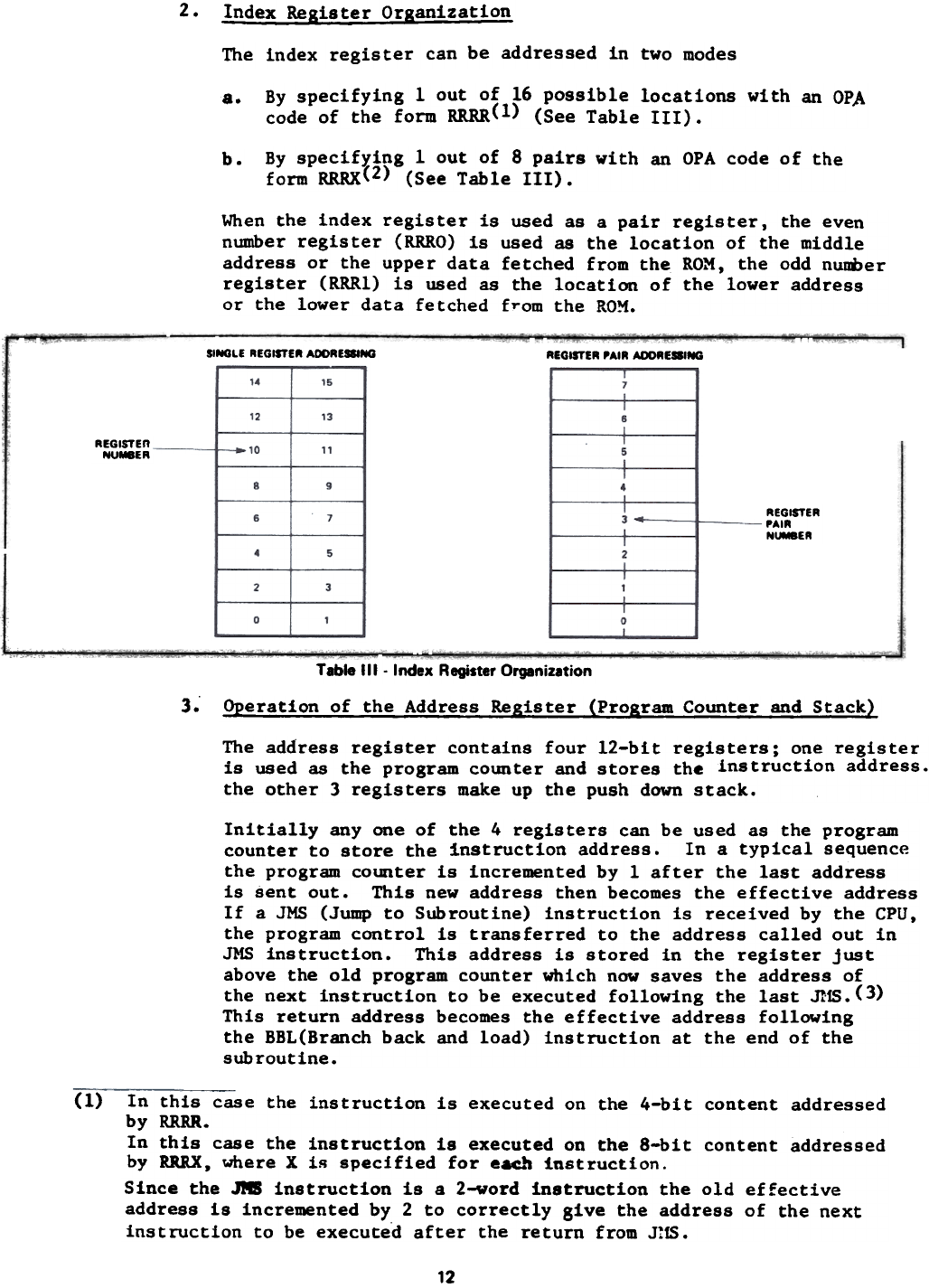

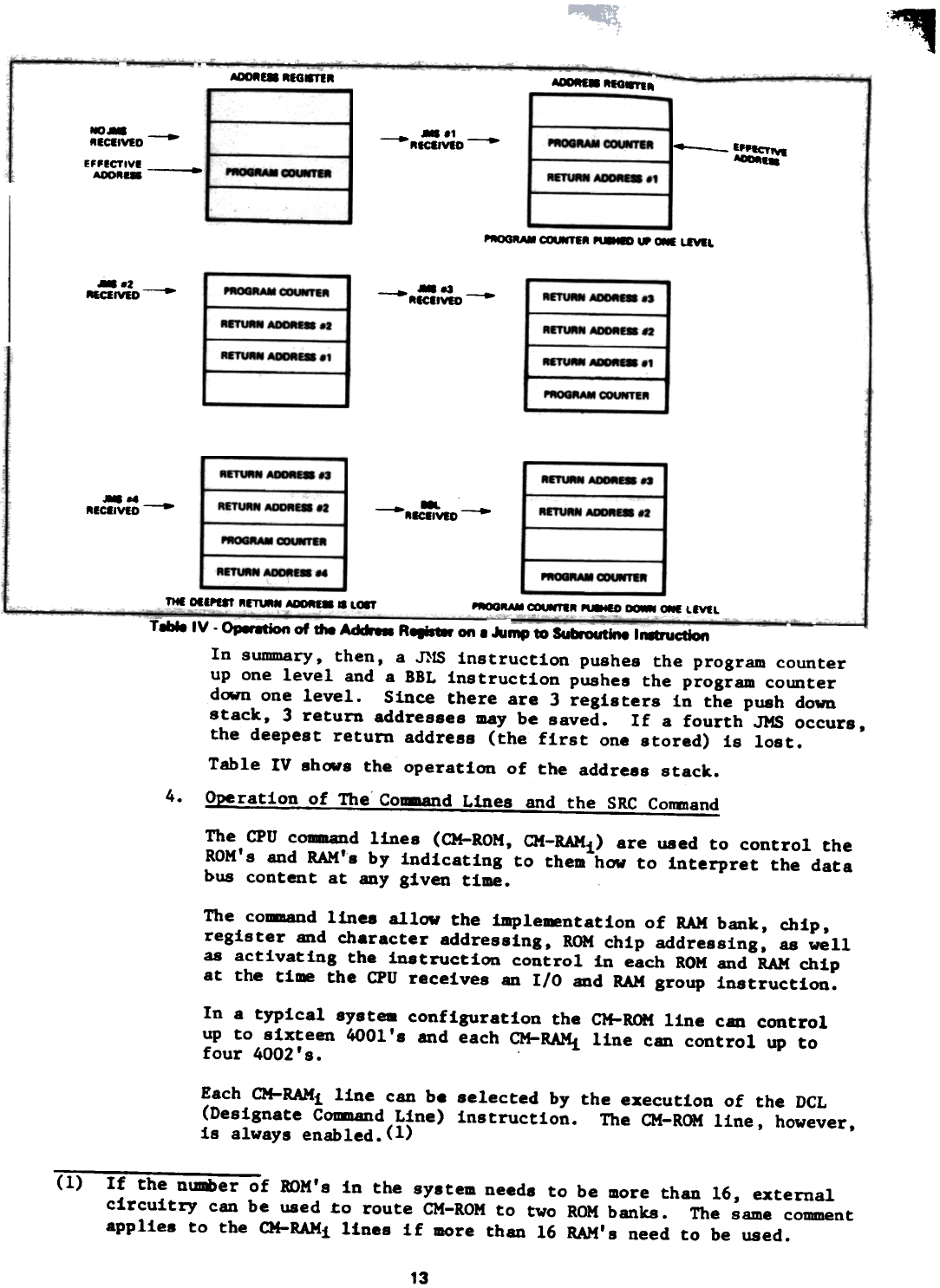

3. Operation of the Address Register (Proaram Counter and Stack)

The address register contains four 12-bit registers; one register

is used as the program counter and stores the instruction address.

the other 3 registers make up the push down stack.

Initially anyone of the 4 registers can be used as the program

counter to store the instruction address. In a typical sequence

the program counter is incremented by 1 after the last address

is sent out. This new address then becomes the effective address

If a JMS (Jump to Subroutine) instruction is received by the CPUt

the program control is transferred to the address called out in

JMS instruction. This address is stored in the register just

above the old program counter which now saves the address of

the next instruction to be executed following the last ~ffi.(3)

This return address becomes the effective address following

the BBL(Branch back and load) instruction at the end of the

subroutine.

(-1) In this case the instruction is executed on the 4-bit content addressed

by RRRR.

In this case the instruction is executed on the a-bit content addressed

by RRRX, where X iR specified for e~~ instruction.

Since the JNS instruction is a 2-word instruction the old effective

address is incremented by 2 to correctly give the address of the next

instruction to be execute"d after the return from J~fS.

12

:~

~- RIG~R

~ RIG~R

- ~.1

~1CafYaO - ~~~R --=:-

~..

RIcaIWD --

EF,eCTlve -

AOOR"

'ROGRAM COt*TIR ~~_.,

PMJORAM ~R ~ W ~ Law..

"-2-

~IVED PROGRAM ~I~ '-83 -

- ~ICIIVID

~ETUM ~ .J

RmMN ADORa8 .~

AIT\MN ~E8 n

R~ ~E8 .1

AlTUM ~.. .,

~~IR

R~~.J

RmMN ~E8 n

MT~ ACORE8 .2

RlcalVEO - --.~ICIIVIO - ~~.2

~~R

R~ -£8 ..

~~R

nIE ~ , RET\MN ~ . L~ ~~ ax*TaR ~ ~ ~ llVll

-

T... IV. ~.afi of the Ad*-. ReIiIt8r on . .hAmp to Subroutine It.-ruction

In sununary, then, a J}fS instruction pushes the program counter

up one level and a BBL instruction pushes the program counter

down one level. Since there are J registers in the push down

stack, J return addresses may be saved. If a fourth JMS occurs,

the deepest return address (the first one stored) is lost.

Table IV shows the operation of the address stack.

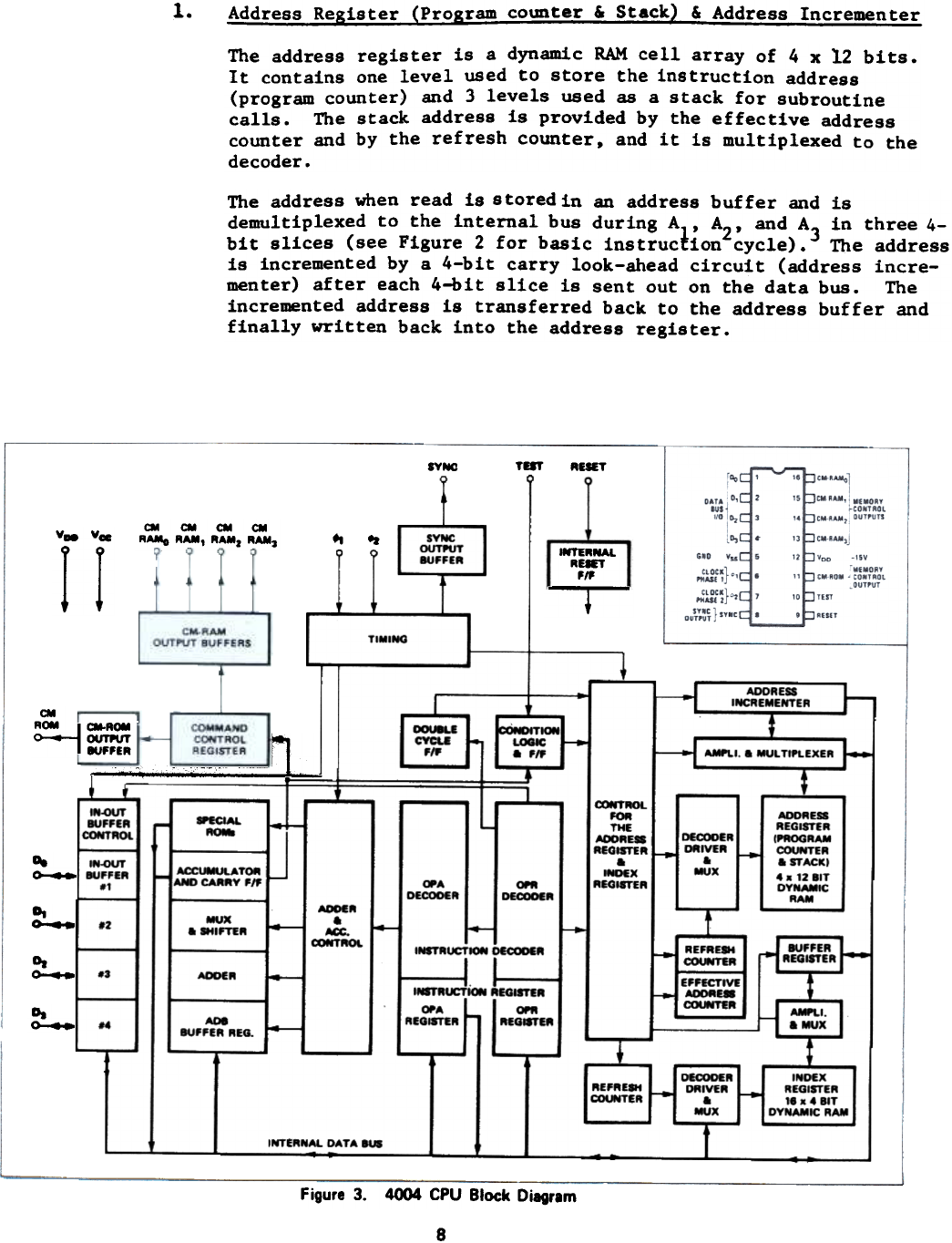

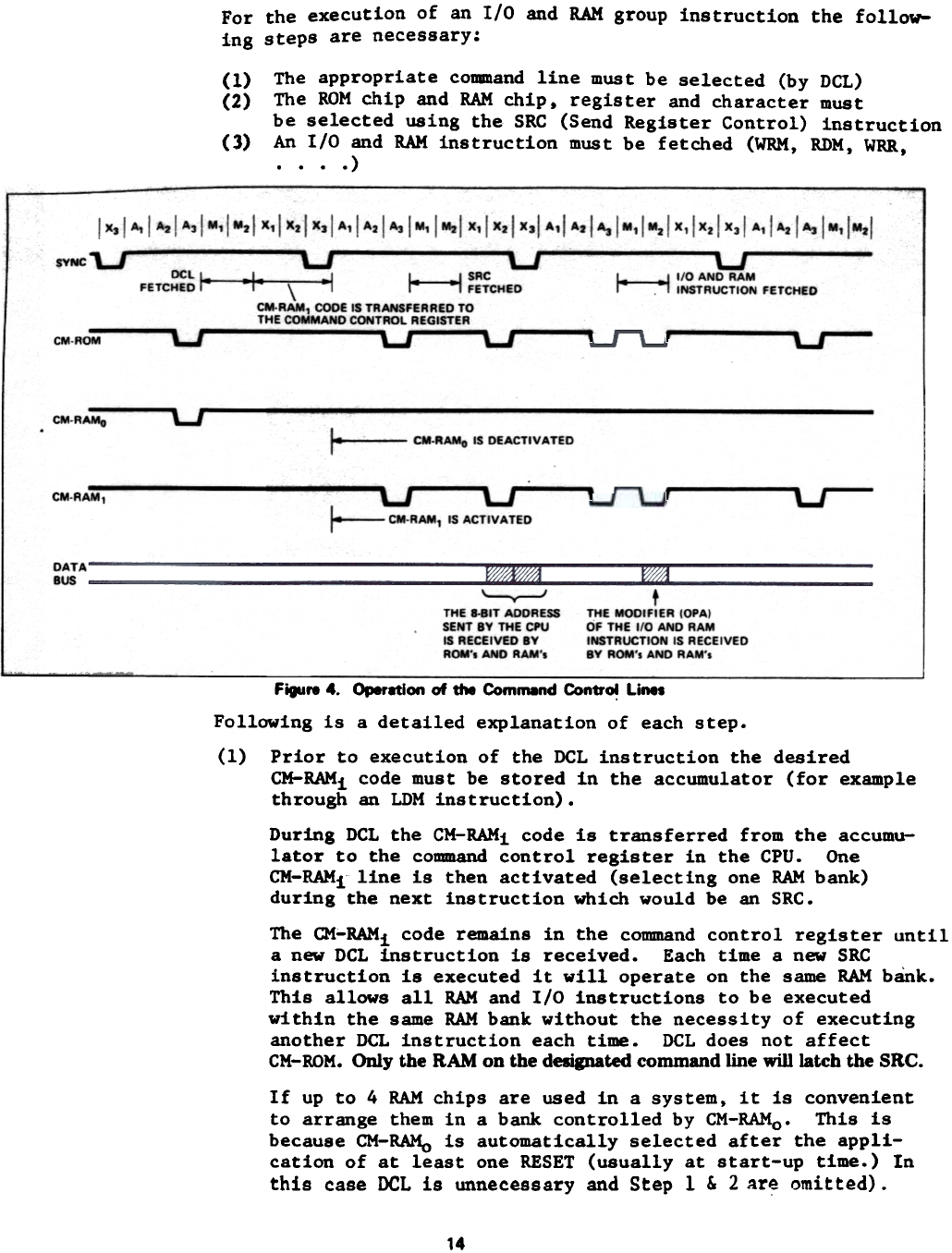

4. ~ration of The Co~d Lines and the SRC Conma!}.!!

The CPU command linea (~ROH. CM-RAMi) are used to control the

ROM's and RAM'. by indicating to them how to interpret the data

bus content at any given time.

The command linea allow the implementation of RAM bank, chip,

register and character addressing, ROM chip addressing, as well

as activating the instruction control in each ROM and RAM chip

at the time the CPU receives an I/O and RAM group instruction.

In a typical systea configuration the ~ROH line can control

up to sixteen 4001' s and each ~RAMi line can control up to

four 4002'8. .

Each CM-RAMi line can b. selected by the execution of the DCL

(Designate Command Line) instruction. The CM-ROM line, however,

is always enabled.(l)

. -. ~

(1) If the number of ROM's in the system needs to be more than 16, external

circuitry can be used to route CM-ROM to two ROM banks. The same comment

applies to the ~RAMi lines if more than 16 RAM's need to be used.

13

For the execution of an I/O and RAM group instruction the follow-

ing steps are necessary:

(1)

(2)

The appropriate command line must be selected (by DCL)

The ROM chip and RAM chiP. register and character must

be selected using the SRC (Send Register Control) instruction

An I/O and RAM instruction must be fetched (WRM. RDM. WRR,

. . . .)

(3)

Xsi ..1 Aa I AJ I-,!.., I X,I Xa1-J I A,I A21 Aa I M, I ~ I X,I X2/ XI! A,I At I A, 1-,1-2! X,I X21 XJ I A,I Aa I AJ I M,I ~:

SYNC 'U ~ U

DCL 1- _1- _I I J ~C

FETCHED r -,- \ -I FETCHED

CM.RAM, CODE IS TRANSFERRED TO

THE COMMAND CONTROL REGISTER

U

~

1- - I 110 AND RAM

1--' INSTRUCTION FETCHED

CM.ROM ,'-' '-'

CM.RAMo

~- CM.RAMO IS DEACTIVATED

u

CM-RAM1 u u

~ CM.AAM, IS ACTIVATED

DATA

BUS

' '

THE I.BIT ADDRESS

SENT BY THE CPU

IS RECEIVED BY

ROM', AND RAM',

t

THE MODIFIER 10PAI

OF THE If 0 AND RAM

INSTRUCTION IS RECEIVED

BY ROM's AND RAM',

F.". 4. Operation of the Comm.nd Control: Lines

Following is a detailed explanation of each step.

(1) Prior to execution of the DCL instruction the desired

~RAMi code must be stored in the accumulator (for example

through an LDM instruction).

During DCL the CM-RAMi code is transferred from the accumu-

lator to the command control register in the CPU. One

CM-RAMi line is then activated (selecting one RAM bank)

during the next instruction which would be an SRC.

The CM~RAMi code remains in the command control register until

a new DCL instruction is received. Each time a new SRC

instruction is executed it will operate on the same RAM bank.

This allows all RAM and 1/0 instructions to be executed

within the same RAM bank without the necessity of executing

another DCL instruction each time. DCL does not affect

CM-ROM. Only the RAM on the designated command line will latch the SRC.

If up to 4 RAM chips are used in a system, it is convenient

to arrange them in a bank controlled by CM-RAMo. This is

because CM-RAMo is automatically selected after the appli-

cation of at least one RESET (usually at start-up time.) In

this case DCL is unnecessary and Step 1 & 2 are omitted).

14

.,

(3)

a)

The SRC instruction specified an index register pair in

the CPU, whose content is an 8-bit address (this 8-bit

address has previously been stored in the register pair)

used to select a RAM chip, register and character and a ROM

chip. This address is sent to the data bus during X2 and

X3 time of the SRC instruction cycle. At X2 time the

CM-ROK line and the selected CM-RAKi line are in a logic

true state to indicate which bank of RAMS and ROMS are to

respond to th~ 8-bit address that is now on the data bus.

The 8-bit address is interpreted in the following way:

The first 4-bits (X2 time) select

one chip out of 16; a flip-flop is

set in the selected chip.

b) The second 4-bits (X3 time) are

ignored.

by the ROM's

a) The first four bits sent out at X2 time

select one out of four chips and one out

of four registers. The two higher order

bits (D), D2) select the chip and the two

lower order bit. (Dl, no) select the

register.

by the RAM'.

b)

(4)

The second 4-bits (XJ time) select one

4-bit character out of 16; The address

is stored in the address register of

the selected chi~.

(See Section ~ for a detailed description

of the RAM chip)

At this time one ROM chip and one RAM chip, register and

character,have been selected. If the CPU fetches an I/O

and RAM in8truction, it will cause the CM-ROH and the

selected CM-RAMi line to be logical true at M2 time. This

all0W8 the previously selected ROM's and RAM's to receive

the modifier of the instruction.' The selected ROM and

RAM will decode the instruction (as well 88 the CPU) and

appropriately execute it during the execution time of the

same instruction cycle.

It should be added that the ~ROM and the selected ~RAMf

lines are always in a logical true state at AJ tiae of any

instruction cycle.

~ROK equals "1" at AJ ti~ indicates to ROM's that the

code at AJ time is the chip number of a ROM within their

bank. This feature allows the user to expand the system.

to more than 16 ROM chips.

Cli-RAMt equals "I" at AJ ti~ has no meanins for the RAM

chips, however, it could be meaningful if ROM's an4 RAM's

were controlled by a c)1-RAHi line.

Figure 4 summarizes the operation of the command lines in

the various instruction cycles.

15

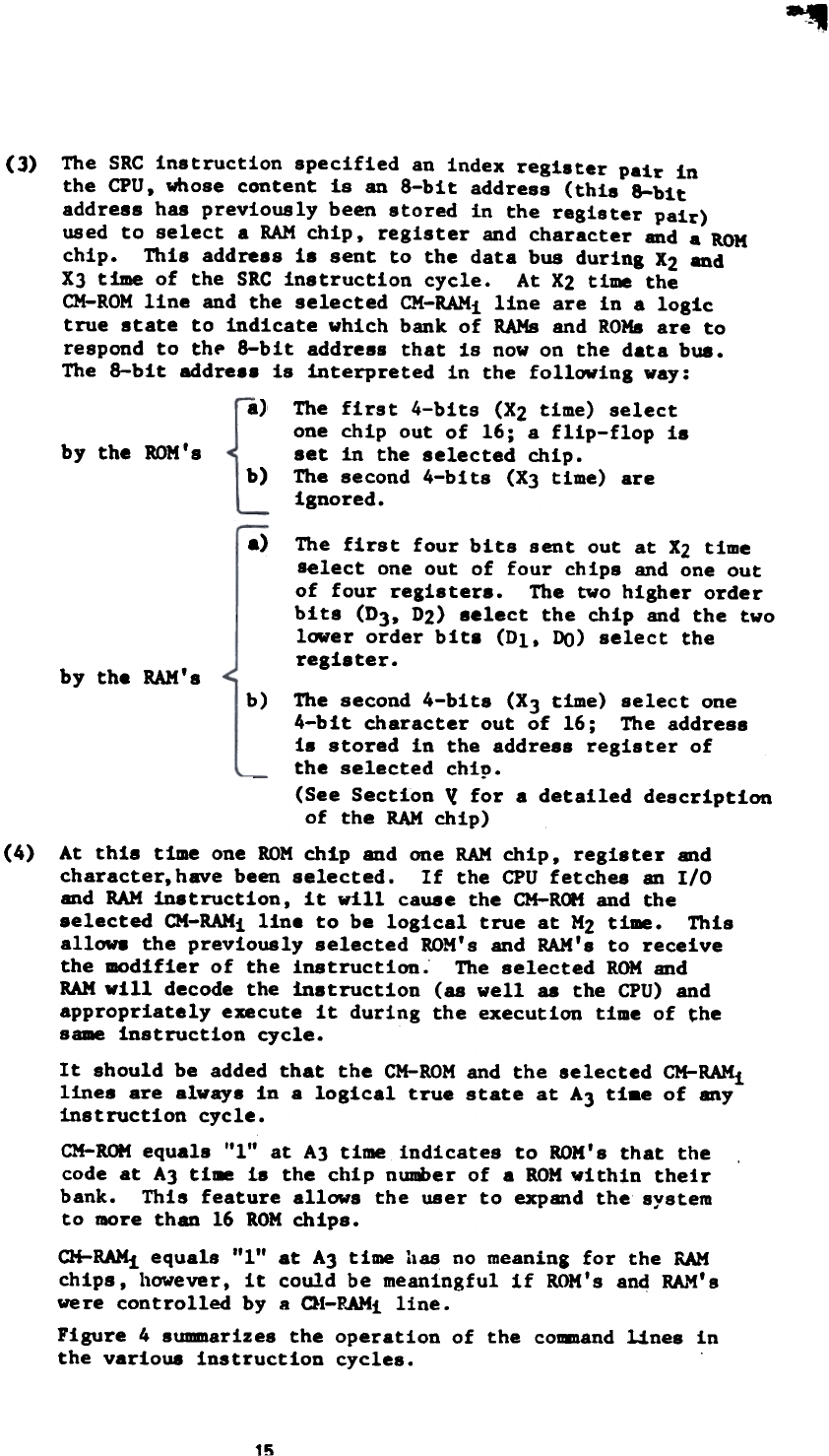

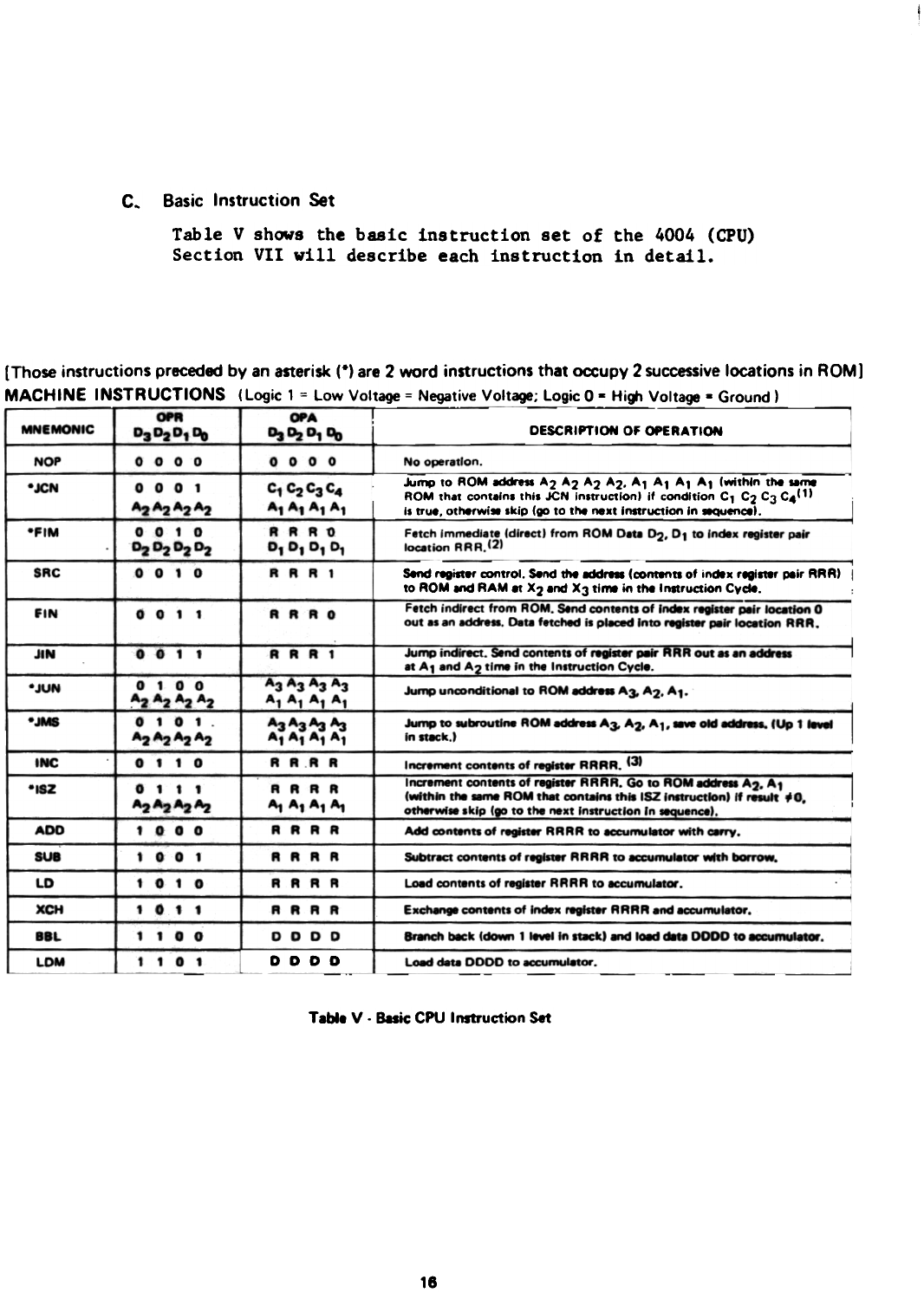

Basic I nstruction Set

c~

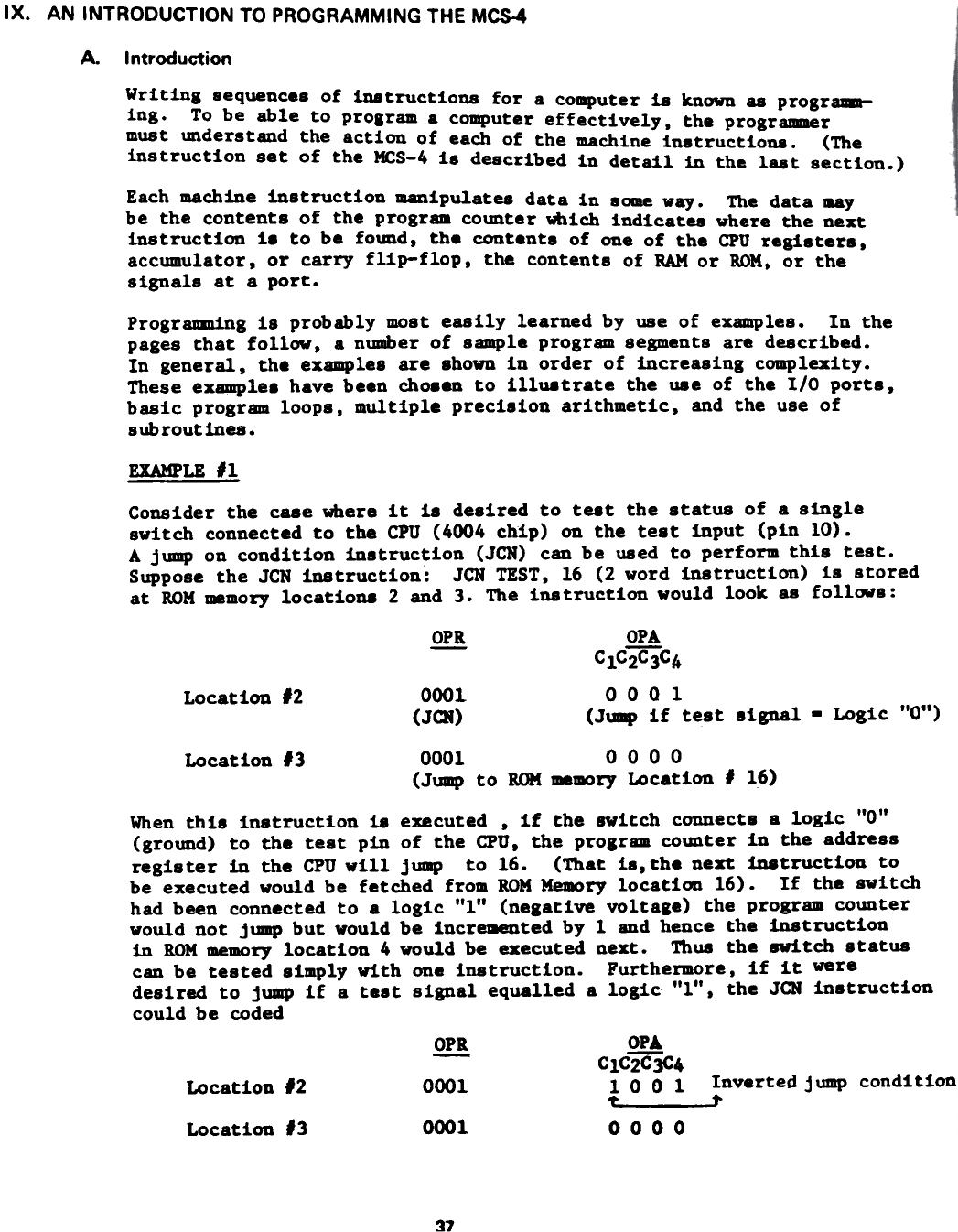

Table V shows the basic instruction set of the 4004 (CPU)

Section VII will describe each instruction in detail.

[Those instructions preceded by an asterisk (.) are 2 word instructions that occupy 2 successive locations in ROM]

MACHINE INSTRUCTIONS (Logic 1 = Low Voltage = Negative Voltage; Logic 0 & Hi~ Voltage. Ground)

MNEMONIC DESCRIPTION DF OPERATION

NOF

-JCN

OPR

~DzD'De

0 0 0 0

.

0 0 0 1

~~A2~

0 0 1 0

Dz~Dz~

0 0 1 0

MA

DJ~o,~

0 0 0 0

C1 ~C3C4

A1 A, A1 A~

~ R R 0

°1 °1 °1 0,

R R A 1

No operadon

- - - - -

Ju~ to ROM 8dfkeSI A2 A2 A2 A2. A1 A1 A1 A1 (within the ROM that contalnl thll JCN Inltructlonl If condition C1 C2 C3 C4111

II true, otherwi. Ikip (go to the next InltrUctlon In ~encel.

"FIM Fetch Immedle.. Idlrect) from ROM 0818 ~. D1 to Index register pelr

l0C8tion RRR.12)

SRC Send register ~trol. Send N .td,-. (contwntl of index r",ater peir RRRI

to ROM Ind RAM 8t X2 and X3 dIM in the Inttruction Cyde.

-- -- - -

r--Ffldlliidr"8ct-fromROM~n..nts of ".. ~j.lr ~n 0-

out.l.n 8ddreA. 0818 fet~ II pIKed IntO regll.., pelr l0C8tlon RRR.

Jump Indirect. re9iater pair RRR out.. en 8d«...

.t A1 end A? tln8 In the Instruction Cycle.

FIN 0 0 , , R R R 0

JIN 0 0 1 1 A A A 1

'JUN

Ju~ unmnditional to ROM -»- A30 A2. A1

-J" Jump to wbroutlne ROM addI'HI AJ. A2. A1. 8V8 old 8dd, (Up 1 level

In_k.1

Iftcr!nwntcontentl of_r8tI8t- RRRR. 131

INC

-ISZ

0 1 0 0

A2 A2 A2 A2

0 1 0 1

A2~~~

0 1 1 0

0 1 1 1

~~~~

1 0 0 0

1 0 0 1

A3A3A3A3

A1 A1 A1 A1

~A3~~

A1 A1 A1 A1

~ R R ~

lna-_t COi1ten.. of r8jst., RRRR. Go ro ROM 8dfk- A2. A,

(within rN .me ROM thet contain. chi. ISZ in.tructlon) If r..ult ~ 0

ot'--. .klp (~to tN next Instruction In 8qU8'-~.

ADD

StM

LD

XCH

IlL

LDM

A " A R

A, A1 A1 A,

R R R R

R R R R

Add mntentl of regilt. RRRR to ~mulator with carry.

SubtrKt contents of r8gi1- R R R R fO 8CCUmul8ror with borrow.

1011) A A A R

A R A A

0 0 0 0

LO8d ~n18nt. of ~r RRRR to 8CCUmulator.

, 0 , ,

, , 0 (

, , 0 ,

Excn.,. contentS of ~x register RRRR and 8CCUmllator.

a-IdI beck I~ 1 IewIln lt8Ck) ~ 1O8d ~. DDDD to ~mul.tor

D D D D I.oed d8t8 DODO to ~mu"tor .

Table V. Basic CPU Instruction Set

18

,.,

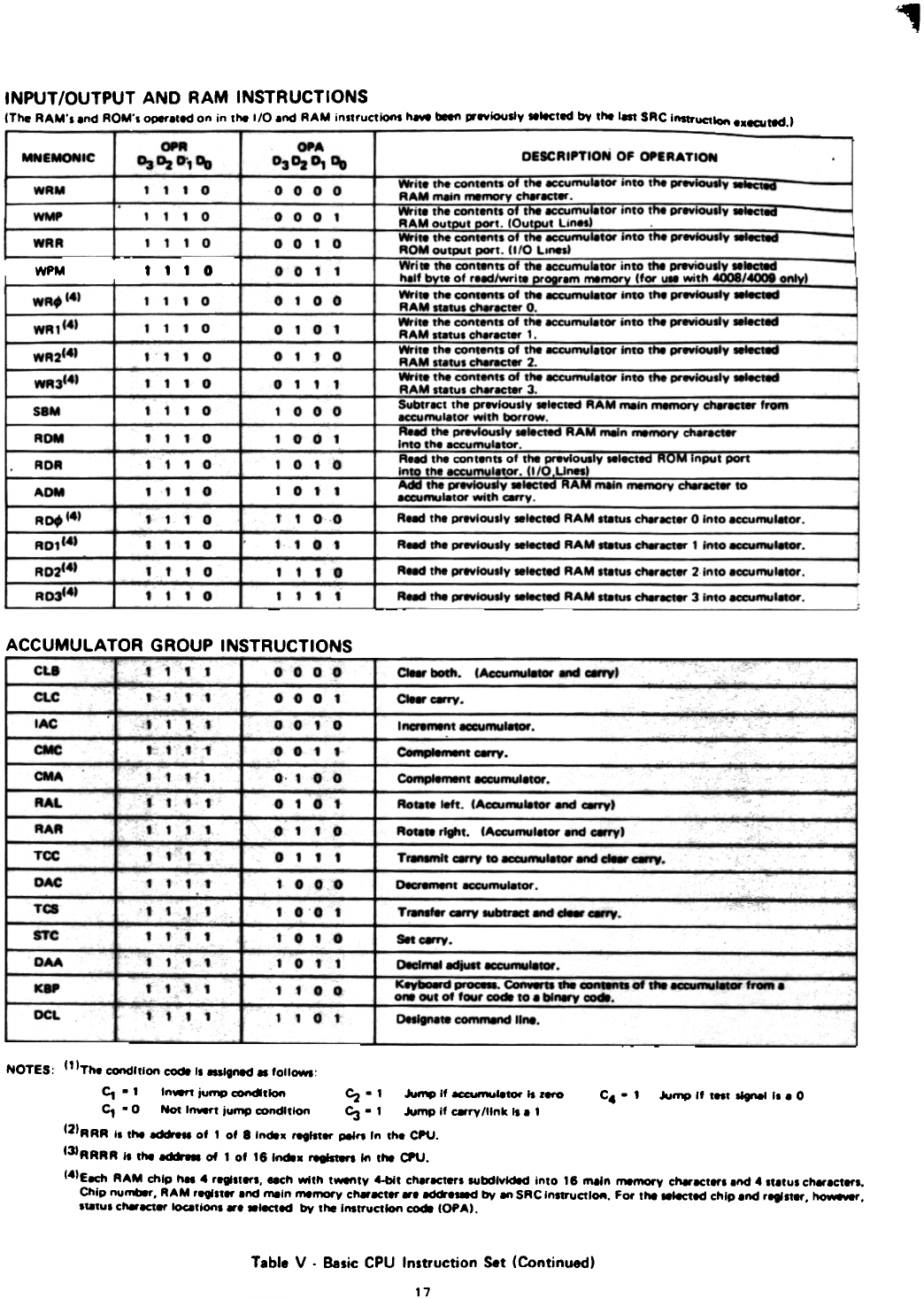

INPUT/OUTPUT AND RAM INSTRUCTIONS

(The RAM'I8nd ROM', ~8t8d on in the 1/0 8nd RAM inltructionl h_!.en ~8VlousiV lelect8d by the 181 SAC instruetlo.. 8x8CUttd.1

I DEKRIPTION OF ~R.T~

Wrile Ihe conlenll of lhe Kcumu18tM Inlo I e D'eY1ou V-

RAM ~n memoty cl\8l'Kter.

Wrlle lhe ~tenll of lhe __1M inlO tM Pl'8ViOuliV --- ~

RAM au t t. IOu t LInes!

Write the contents of the Kcumu tM nto t

ROM outPUI port. 11/0 Llnnl

Wri. the con18fttl of the -_tor intO the PIWioUllv -.. -

\ h8lf byte of rNd'-i. ~..~ me~y IfM '* with -.,-. Of*vl -

Write the contents of the Kcumu18tM Into the prwiOullV 8I8cted

RAM Itatul character O.

Write lhe contents of the KCUn-.18tor Into the pr8¥iOu"v -.ct8d

RAM ltatul char- 1.

Write the cont.nts of the acwmulatM Into the Pl'8ViouslV 8I8cted

RAM Iiatul ch8r8ct... 2.

Write lhe conten.. of the _n-.I8tM IntO the D'eYlouIIy 8I8ct8d

RAM statUI cI\8I'- 3.

SubtrKt the D'eYIouIlV 8lect8d RAM ~in -V cI\8I'- from

aeeurnulalor with bof'row.

R.~ the ptevfously 1818ct8d A meln ff8fr*Y ~

Into the KCUmu4ator. '

~~ -~~u-~i -the ..-vIo\Aly 8I8cted ROM Input POI't .

into lhe accumUIe\or.II/O.Unell_-

~ the ~8VIou"V -lee.- RAM m81n n.mory clw- to

I _rnulatM with ~y.

MNEMONIC

WRM

WMP

WRR

~

OJ ~ D", Do

, , , 0

, , , 0

, , , 0

CWA

o,~Dt~

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1WPM t t t 0

W~141

WR1141

WAr41

WA3141

IBM

ADM

ADA

ADM

A~141

AD114)

ADr4)

AD~4J

0 t 0 4

t 1 , 0

1 1 1 0 0 tOt

0 1 1 0

. 1 t t

t . 0 (

, 1 , 0

, , , 0

, , , 0

, , 1 0

, , , 0

, 1 1 0

, 0 0 ,

, 0 t .

, 0 1 ,

1 1 1 0

. 1 1 0

1 1 0 0

1 1 0 1

R.-j the pnviouliV _lected RAM status c_- 0 Into _n-.18t0l'.

RNd the pr8¥I~"V 8tect8d RAM statUI C'-Kt8l' 1 into 8CCU~I.tor.

1 , 1 0

t , , 0

1 1 1 0

~ 1 1 .

RMd tN prwiously selected RAM status ctwKt8f 2 into -~a.-.

Read the ~lViOUsty .18ct8d RAM statUI c'-Kter 3 Into 8«u".,I8tor.

ACCUMULATOR GROUP INSTRUCTIONS

CL8

CLC

lAC

CMC

CMA

RAL

RAR

T~

DAC

-

TQ

STC

DAA

K8P

DCL

, , , ,

, , , ,

, , , ,

~ , , 1

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0.1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 C

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

t t t t

t f t t

-,

t t t t

, . . 1

, , 1 ,

0- bodt. IAccumul8tOl"'-rv1

0- -rv.

I t -.mII'-'.

.

~ ;;-~t~.

~ t -~.

Aoy.. left. IA~mu nd C8Ty1

~ ,...t. IAccu-'-.. ~I

Tr8ftfmlt C8rry to _mu18tor 8nd ct.- ~.

D8Cr8n8nt -mul8tOl'.

T~1fer ~ Iubtr8Ct 8M --~.

Set -rv.

t . 1 ~

1 1 ., 1

t 1 t t

I D8d"-, 8djust KaI --

KeybO8'd prOC88. Co_" lhe mftUn" of lhe Kaln-.I8tor fr- . --

I 018 ~I of f- ~ 10 . bln.-y ~.

1 i 1 1 0..,.- ~ line

NOTES: (11Th. condItion codellasI9n8d. follows:

~ . t Inwn jump concItlon ~ . 1 ~ If Is r- Cc . 1 Jump If t8l1 Iign8I II . 0

C, .0 Not Inwn jump condition ~ . 1 Jump if c.-rv/llnk II a 1

(2IRRR II the ~.. of 1 of 8 In~. '89111.. ~ In the CPU.

t3lRRRR II the ~ of 1 of 16 lna. r8III1W1ln the CPU.

(CIEech RAM chip h. C '89IIt.,l. each with t-tv 4-bit ch.'Kte'IIU~lvldld Into 18 main ~~ Ch8"Kt.,18nd C Itatul ch.,act.,l.

Chip numt.,. RAM '89IIt., and me.n ~~v ch.8C1.,.. 8dtke.-d by 8ft SAC Instructl_. F~ the .18C18d chip and ""11... ~.

IUtUI cwect., IoC8tionl.. -18C18d by the Instruction code tOPAI.

Table V - Basic CPU Instruction Set (Continued)

17

~

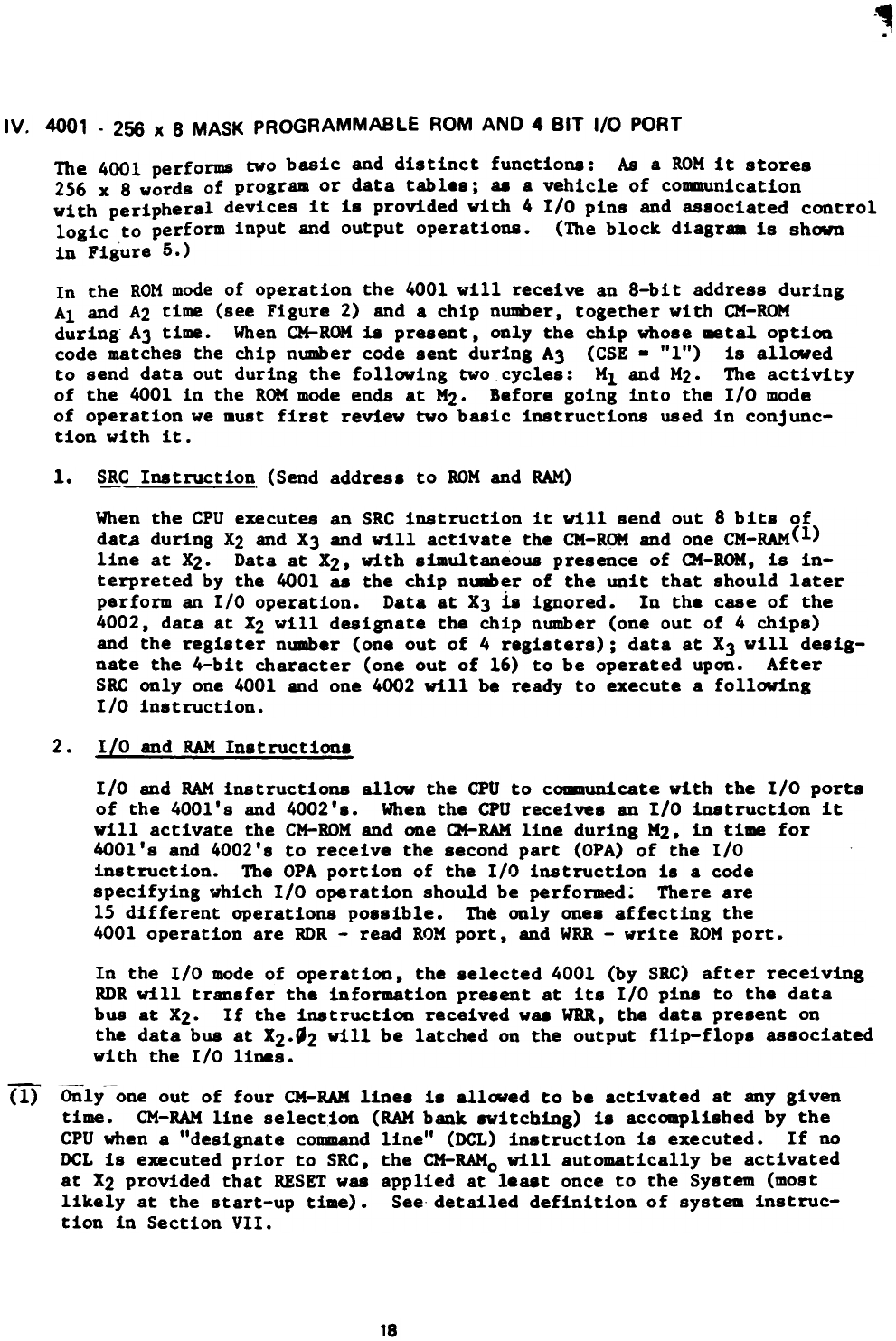

4001 - 256 x 8 MASK PROGRAMMABLE ROM AND 4 BIT I/O PORT

IV.

The 4001 performs tWo basic and distinct functions: As a ROM it stores

256 x 8 words of program or data table.; as a vehicle of communication

with peripheral devices it i. provided with 4 I/O pins and associated control

logic to perform input and output operations. (The block diagraa is shown

in Figure 5.)

In the ROM mode of operation the 4001 will receive an 8-bit address during

Al and A2 time (see Figure 2) and a chip number, together with CK-ROM

during AJ time. When CM-ROM 18 present, only the chip whose ~tal optioo

code matches the chip n\DDber code sent during AJ (CSE - "1") is allCNed

to send data out during the following two cycles: HI and H2. The activity

of the 4001 in the ROM mode ends at M2' Before going into the I/O mode

of operation we must first review two basic instructions used in conjunc-

tion with it.

1. SR~ Instruction. (Send addresa to ROM and RAM)

When the CPU executes an SRC instruction it will send out 8 bits of

data during X2 and X3 and will activate the CM-ROM and one CM-RAM(l)

line at X2. Data at X2, with simultaneous presence of CM-ROK, is in-

terpreted by the 4001 as the chip nU8ber of the unit that should later

perform an I/O operation. Data at X3 ia ignored. In the case of the

4002, data at X2 will designate the chip number (one out of 4 chips)

and the register number (one out of 4 regi8ters); data at X3 will desig-

nate the 4-bit character (one out of 16) to be operated upon. After

SRC only one 4001 and one 4002 will be ready to execute a following

I/O instruction.

2. I/O and RAM Instructions

1/0 and RAM instructions allow the CPU to communicate with the 1/0 port8

of the 4001'8 and 4O02's. When the CPU receives an 1/0 instruction it

will activate the CM-ROM and one CM-RAK line during M2, in time for

4001'8 and 4002'8 to receive the second part (OPA) of the 1/0

instruction. The OPA portion of the 1/0 instruction is a code

8pecifying which 1/0 operation should be performed; There are

15 different operations pos8ible. The only ones affecting the

4001 operation are RDR - read ROM port, and WRR - write ROM port.

In the I/O mode of operation. the selected 4001 (by SIC) after receiving

RDR will transfer the information preaent at its I/O pina to the data

bus at X2- If the instruction received waa WRR. the data pre8ent on

the data bus at X2 -~2 will be latched on the output flip-flop8 associated

with the I/O liMa.

m

--

Only one out of four CM-RAK lines is allowed to be activated at any given

time. CM-RAM line selection (RAM bank 8Witcbing) i8 acccupli8hed by the

CPU when a "designate couaand line" (DCL) instruction is executed. If no

DCL is executed prior to SRC. the ~RAKo will automatically be activated

at X2 provided that RESET was applied at l...t once to the System (most

likely at the start-up time). See detailed definition of system instruc-

tion in Section VII.

18

Figure 5 shows the block organization of the 4001. The ROM array has a

dynamic mode of operation ~nd is divided into two blocks of 16 x 64

cells each. Multiplexing is needed for both address to address register

and data to data bus output buffer operations.

~e HTC flip-~lop controls the outputting of data. It is set at A3'

(see Figure 2). if CM-ROM and CSE (chip select) are "1". CSE is a single

4-input AND gate of the 4 data bus lines, using Di or 151 according to

the chip number that the user wants to assign to the chip. This

is accomplished by metal mask option.

The SRC flip-flop is set by CM-ROM and CSE at X2' (see Figure 2), and

presets the I/O control logic for a following input or output operation.

TIMING generates all internal timing silnals for the ROM and I/O

control using SYNC. ~l and G2. A RESET(l) signal will clear all static

flip-flops and will inhibit data out.

The output flip-flops associated with I/O pins can a180 be cleared

usine an external CL pin.

-(l~T i~ed for the start-u? of the system.

IIWVT

~FEM

~'ARTIAL

~R

~

-

r-

DATA -

!4L-.

ICKmUT MlFFEAI

..,

t-- . 1- r

110 Ct»ITROL

~~

IK

,.

~~

'--

~

Of

0,

o.

Da

~

M~

CLQ8T ~

Fi~r. 5. 4001 ROM Block Di..m

19

f.

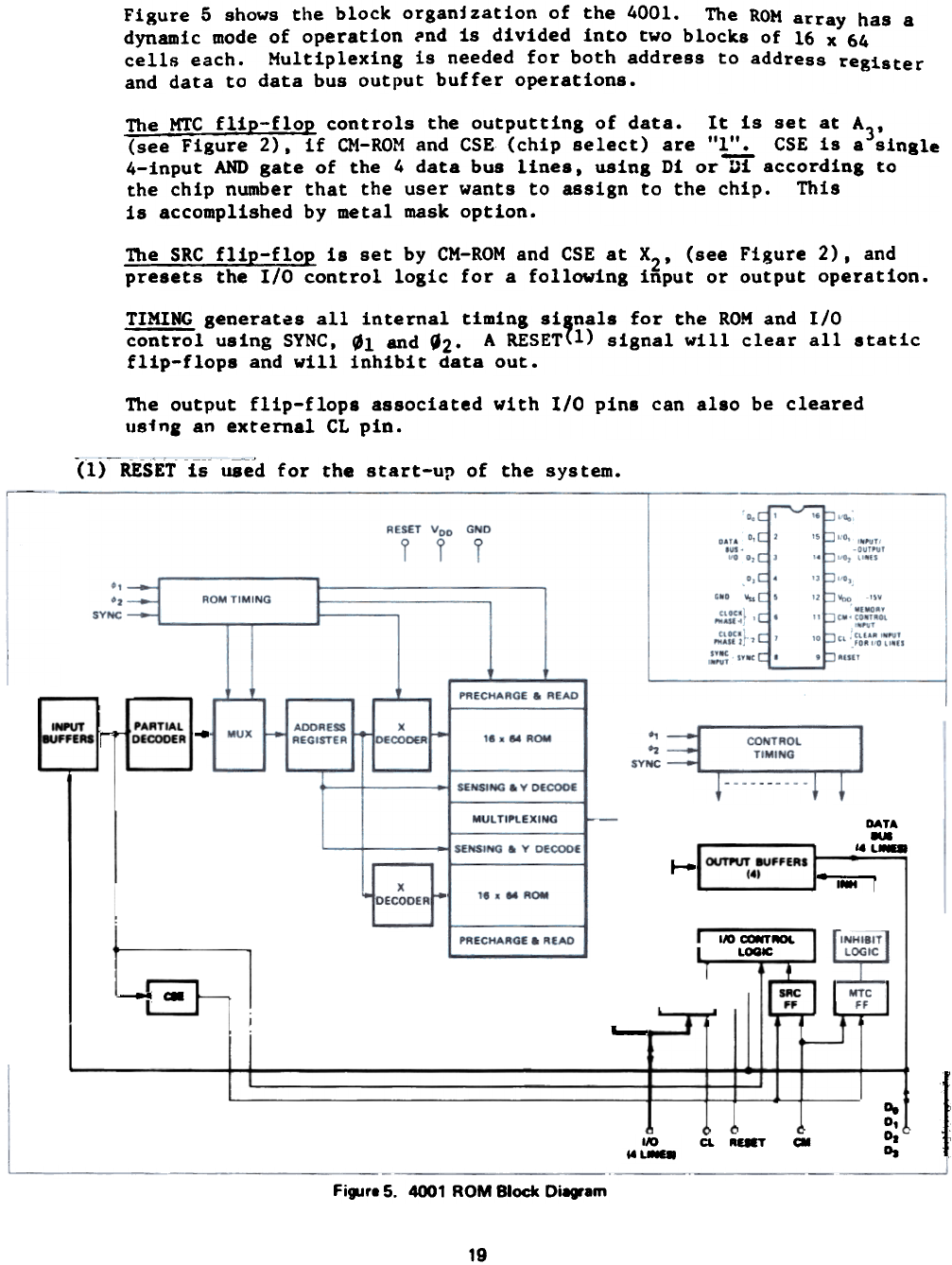

ROM Options and Ordenn! the ROM

Each 1/0 pin on each ROM can be uniquely

chosen to be either an input or output line

by metal option. Also each input or output

can either be inverted or direct. When the

pin is chosen as an input it may have an on.

chip resistor connected to either VDD or VSS.

Figure 6 shows the available options for each

1/0 pin.

When ordering a 4001 the following informa-

tion must be specified:

1. Chip number

2. All the metal options for each 1/0 pin

3. ROM pattern to be stored-'ineach of the

256 locations.

A blank customer truth table is available upon

request from Intel. A copy of this table is

shown in the appendix.

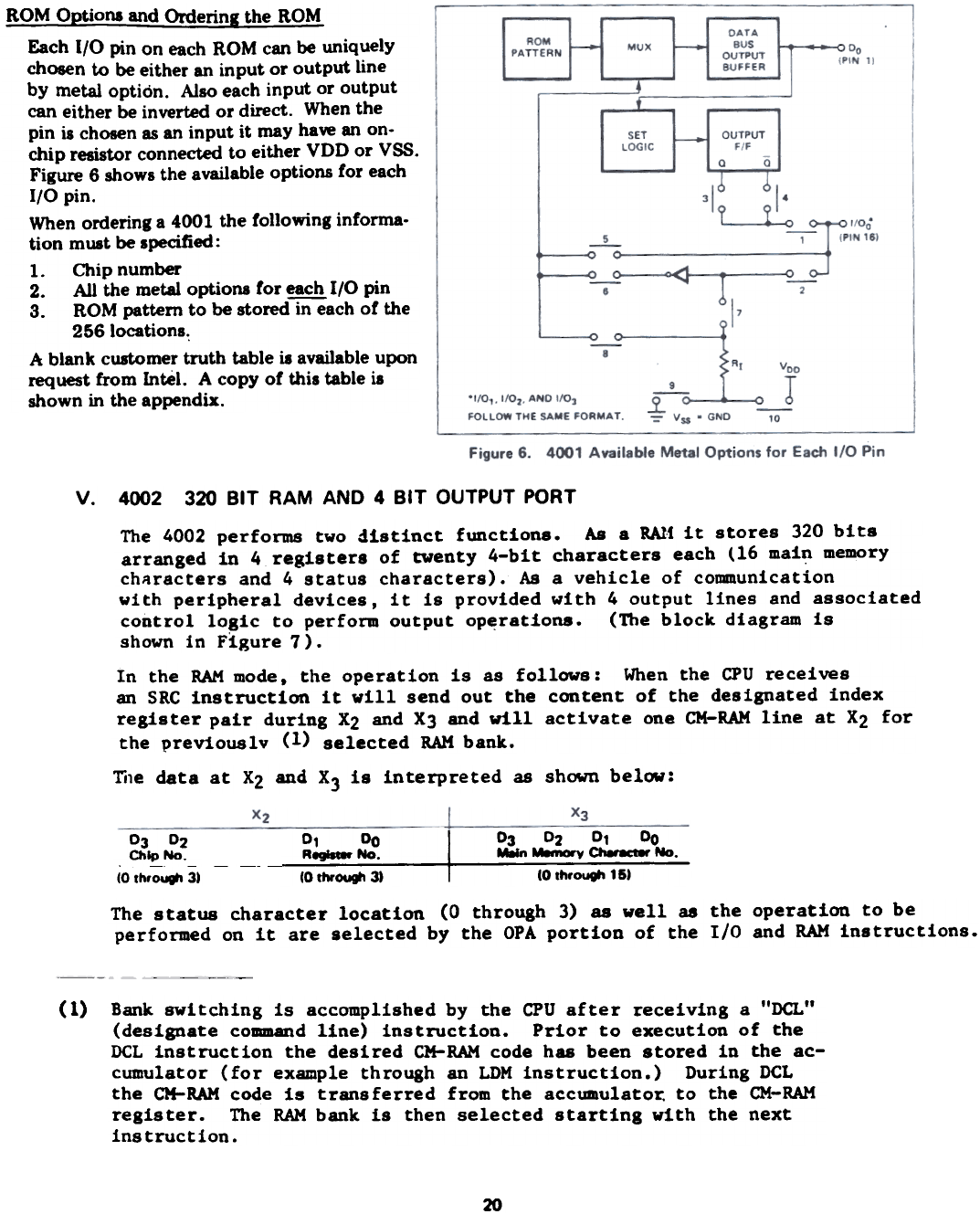

320 BIT RAM AND 4 BIT OUTPUT PORT

v. 4002

The 4002 performs two distinct functions. As a RAIl it stores 320 bits

arranged in 4 registers of twenty 4-bit characters each (16 main memory

chRracters and 4 status characters). As a vehicle of communication

with peripheral devices, it is provided with 4 output lines and associated

control lo~ic to perform output operations. (The block diagram is

shown in Figure 7).

In the RAM mode. the operation is as follows: When the CPU receives

an SRC instruction it will send out the content of the designated index

register pair during X2 and X3 and will activate one CM-RAM line at X2 for

the previously (1) selected RAM bank.

~1e data at X2 and X3 is interpreted as shown below:

- -

I ::='- ~ I ~~~;~~~ ~°No.1 Do 03 02 01 DO

RIgis18I' No. M8In M8mory Ch8f8ct8r No.

10 through 3) CO th,~ 161

°3 °2

Chip No.

.~

10 rhro.q. 31

The status character location (0 through 3) as well 88 the operation to be

performed on it are selected by the OPA portion of the I/O and RAM instructions.

Bank switching is accomplished by the CPU after receiving a "DCL"

(designate command line) instruction. Prior to execution of the

DCL instruction the desired ~RAM code has been stored in the ac-

cumulator (for example through an LDM instruction.) During DCL

the ~RAM code is transferred from the accumulato~ to the CM-RAM

register. The RAM bank is then selected starting with the next

instruction.

(1)

20

.,

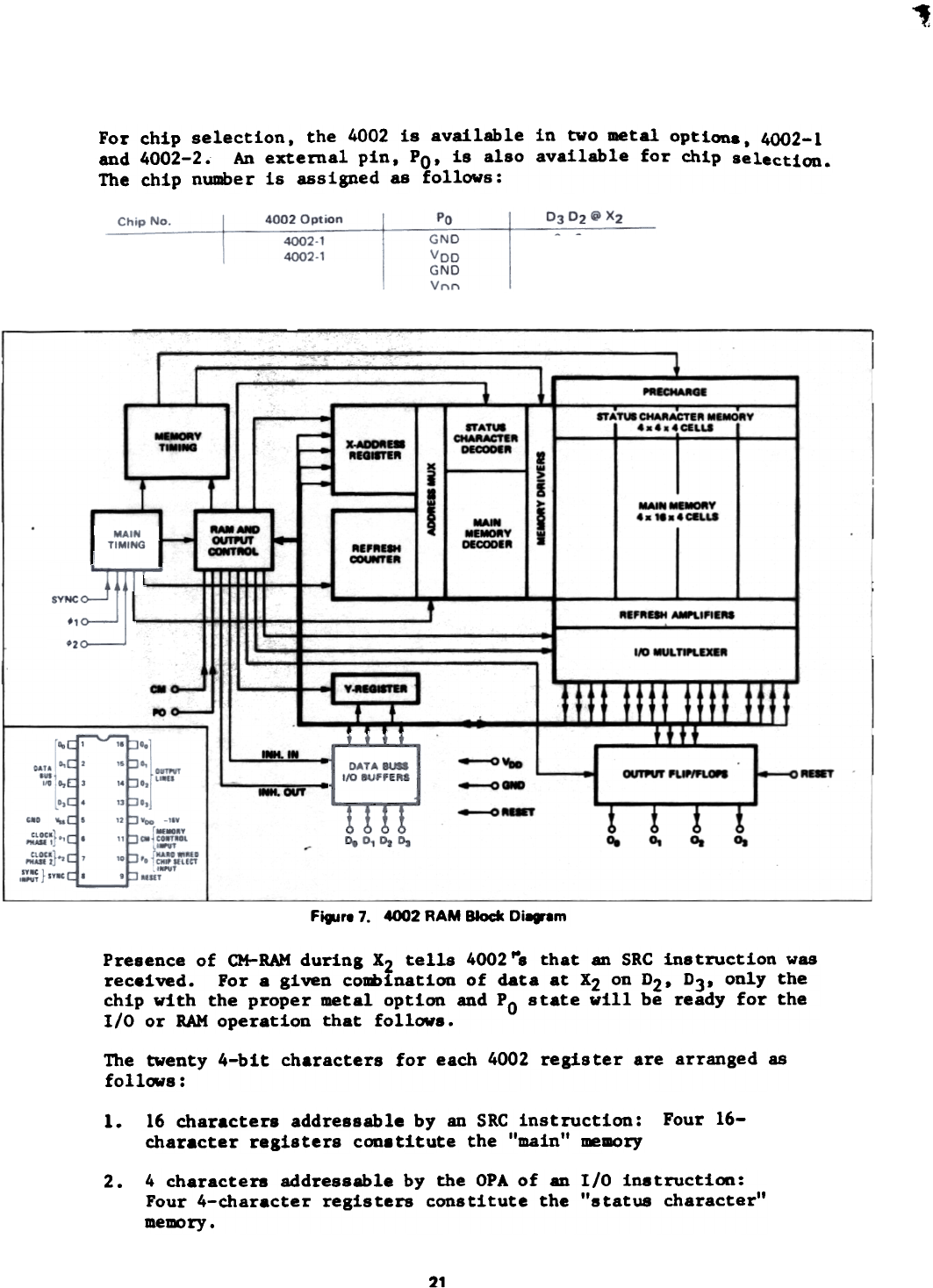

For chip selection. the 4002 is available in two metal optiona, 4002-1

and 4002-2. An external pin. PO. is also available for chip selection.

The chip number is assigned as follows:

~ICHAAGI

. '-J

STAT\8 CHARACTER MIMORY

~ CI~ ~

ITATW

~ACTER

~R

M~Y

TIMING

,..-: X.ADOAE8

~EGI8TIR

MAIN .I~Y

..,...CELLS

MAIN

M~Y

~R

RAMAIC

0UTP\n

CX*T~

REFRE8f

~IR

~EF~IIM ~IFIEM

I~ MUioTIPLExaR

!~ t

~O--

Mo--'"

H Y~IGI8TIR

J .

. ...«If. --0

--0

--0

~ 'UP"L~ o~

"1 1 1 l'

0. 0. 0, 0,

Fi.,re 7. 4002 RAM Block Di...m

Presence of ~RAM during X2 tells 4002 ~8 that an SRC instruction was

received. For a given combination of data at X2 on D2- D3J only the

chip with the proper metal option and Po state will be ready for the

I/O or RAM operation that follows.

The twenty 4-bit characters for each 4002 register are arranged as

follCNs:

Four 16-

1. 16 characters addressable by an SRC instruction:

character registers con8titute the !'main" .mory

4 characters addressable by the OPA of an I/O in8truction:

Four 4-character registers constitute the "status character"

memry.

2.

21

v.

~

RI8T

Two separate X decoders switch between main and status characcer

memories.

When an I/O or RAM instruction is received by the CPU, the CPU

will activate one CH-RAM line during M2 ' in time for the 4002's

to receive the OPA (2nd part of the instruction), which will

specify the I/O or RAM operation to be performed. Shown below

is a list of the 15 possible I/O and RAM operations.

The I/O and RAM operations are divided into Read operations (lOR)

and Write operations (lOW). The state of DJ will determine if

the operation is a read or a write. DJ. 1 for lOR, DJ. 0 for

lOW (see Basic Instruction Set, shown in Section IIIc).

For each I/O instruction the action is 88 shown in the following

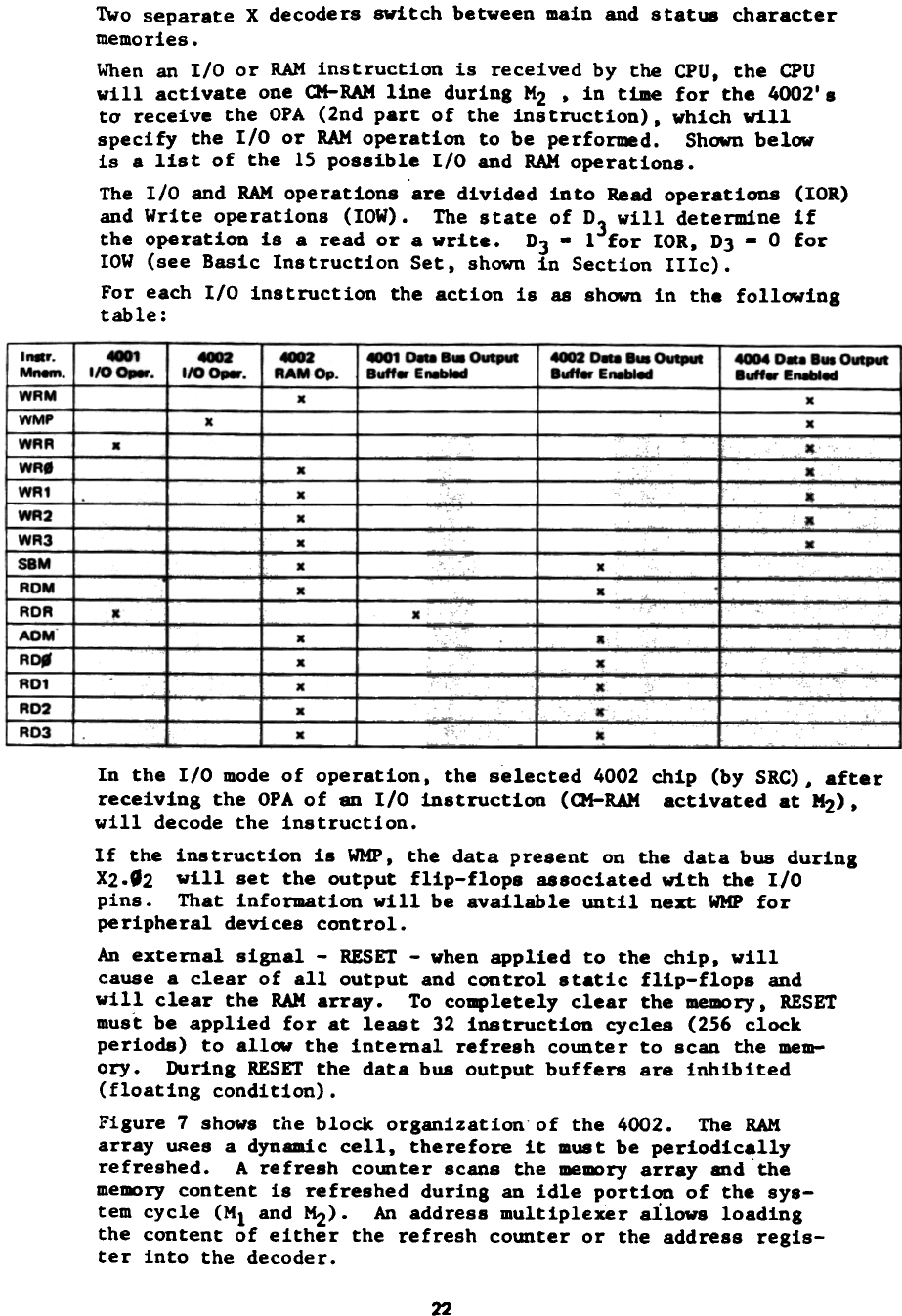

table:

~

RAM Op.

x

4001 0-. 8&8 Output

8uff.EMbled

11.cr. I ~ I 4m2

I ~., 11O0P8W. ~ 1100..

4002 Del. BI8 Dutput

Buff... Enebled

~ 0.. Bus Output

Buff.. En-..

r WRM

~

.

-

.

.

WAf

WA'

WR2

WA3 I

S8M

ADM

ADA

.

.

~

.

.

~

.

In the 1/0 mode of operation. the selected 4002 Chip (by SRC), after

receiving the OPA of an 1/0 instruction (CM-RAM activated at M2).

will decode the instruction.

If the instruction is WMP. the data present on the data bus during

x2.82 will set the outpu~ flip-flops aasociated with the 1/0

pins. That information will be available until next WMP for

peripheral devices control.

An external signal - RESET - when applied to the chiP. will

cause a clear of all output and control static flip-flops and

will clear the RAK array. To completely clear the memory. RESET

must be applied for at leaat 32 instruction cycles (256 clock

periods) to allow the internal refresh counter to scan the me~

ory. During RESET the data bus ou~put buffers are inhibited

(floating condition).

Figure 7 shows the block organization of the 4002. The RAM

array URes a dynamic cell. therefore it must be periodically

refreshed. A refresh counter scans the memory array and'the

memory content is refreshed during an idle portion of the sys-

tem cycle (HI and M2). An address multiplexer ailows loading

the content of either the refresh counter or the address regis-

ter into the decoder.

22

.

VI.

The RAM control is composed of an SRC flip-flop, chip selection

loaic, an instruction register, instruction decoder and I/O con-

trollogic. This block controls the loading of the addres8

register, the status and main memory decoder switching, the gen-

eration of memory timing, the enable of the data bus input-output

buffers, the RAM read/write operations, and the loading of the

output flip-flops.

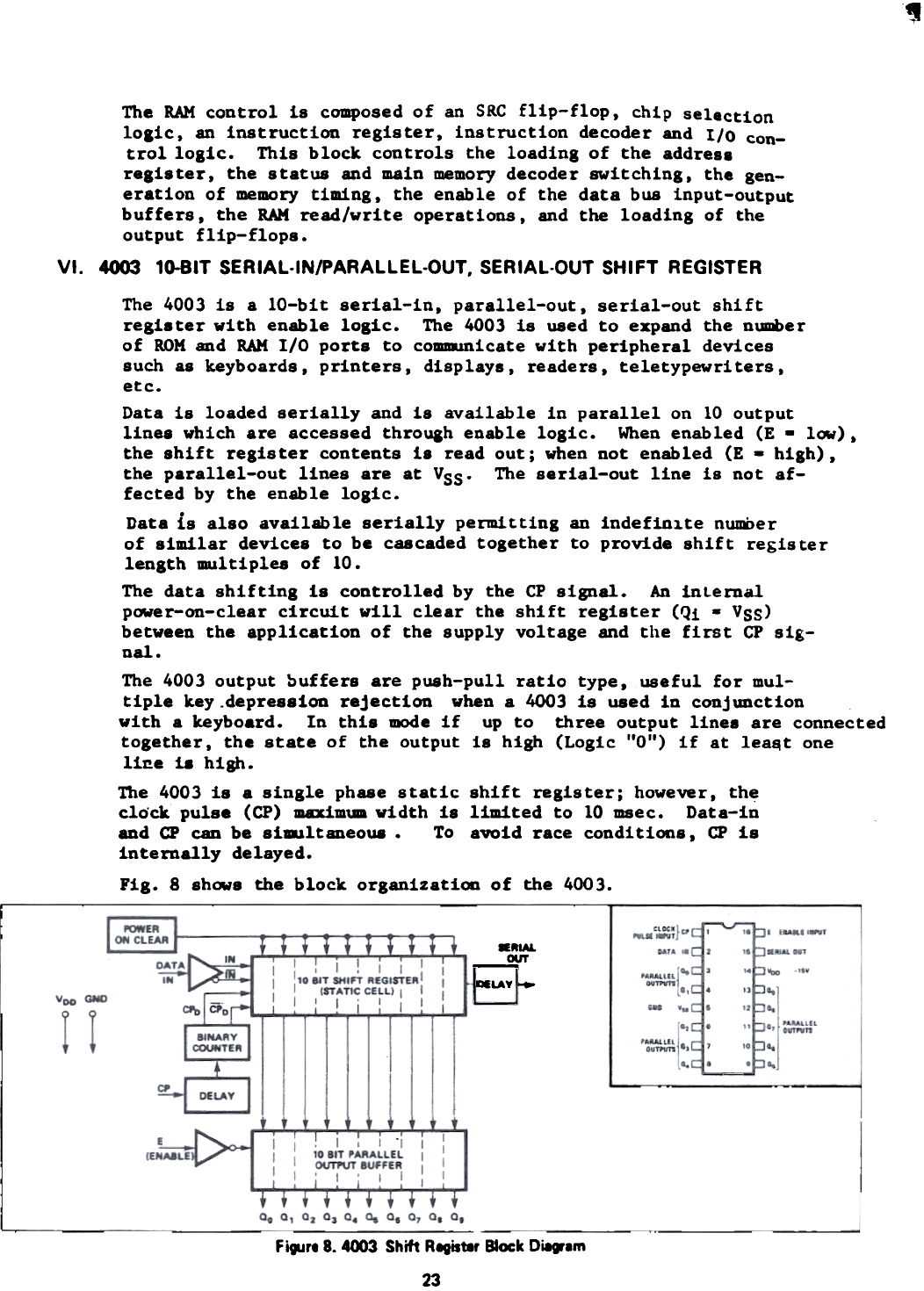

4003 1o-BIT SERIAL.IN/PARALLEL.OUT. SERIAL-OUT SHIFT REGISTER

The 4003 is a 10-bit serial-in, parallel-out, serial-out shift

register with enable logic. The 4003 is used to expand the number

of ROM and RAM I/O ports to communicate with peripheral devices

such as keyboards, printers, displays, readers, teletypewriters,

etc.

Data is loaded serially and is available in parallel on 10 output

line. which are accessed throuah enable logic. When enabled (E - low),

the shift register contents i8 read out; when not enabled (E - high),

the parallel-out lines are at VSS. The serial-out line is not af-

fected by the enable logic.

Data is also available serially permitting an indefin~te number

of similar device8 to be cascaded together to provide shift register

length multiples of 10.

The data shifting is controlled by the CP signal. An internal

power-on-clear circuit will clear the shift register (Qi . VSS)

between the application of the supply voltage and the first CP sig-

nal.

The 4003 output buffer8 are push-pull ratio type, useful for mul-

tiple key .depre88ion rejection when a 4003 is used in conjunction

with a keyboard. In thi8 mode if up to three output lines are connected

together, the state of the output Is high (Logic "0") if at lea~t one

1i!!.e 18 high.

The 4003 is a single phase static shift register; however, the

clock pulse (cp) ID8Xim\D width i8 limited to 10 msec. Data-in

and CP can be simultaneous. To avoid race condition8, CP is

internally delayed.

Fig. 8 show8 the block organization of the 4003.

_RIA&.

our

~

--LAY ~

F~r. 8.4003 Shift Register Block Di8gram

23

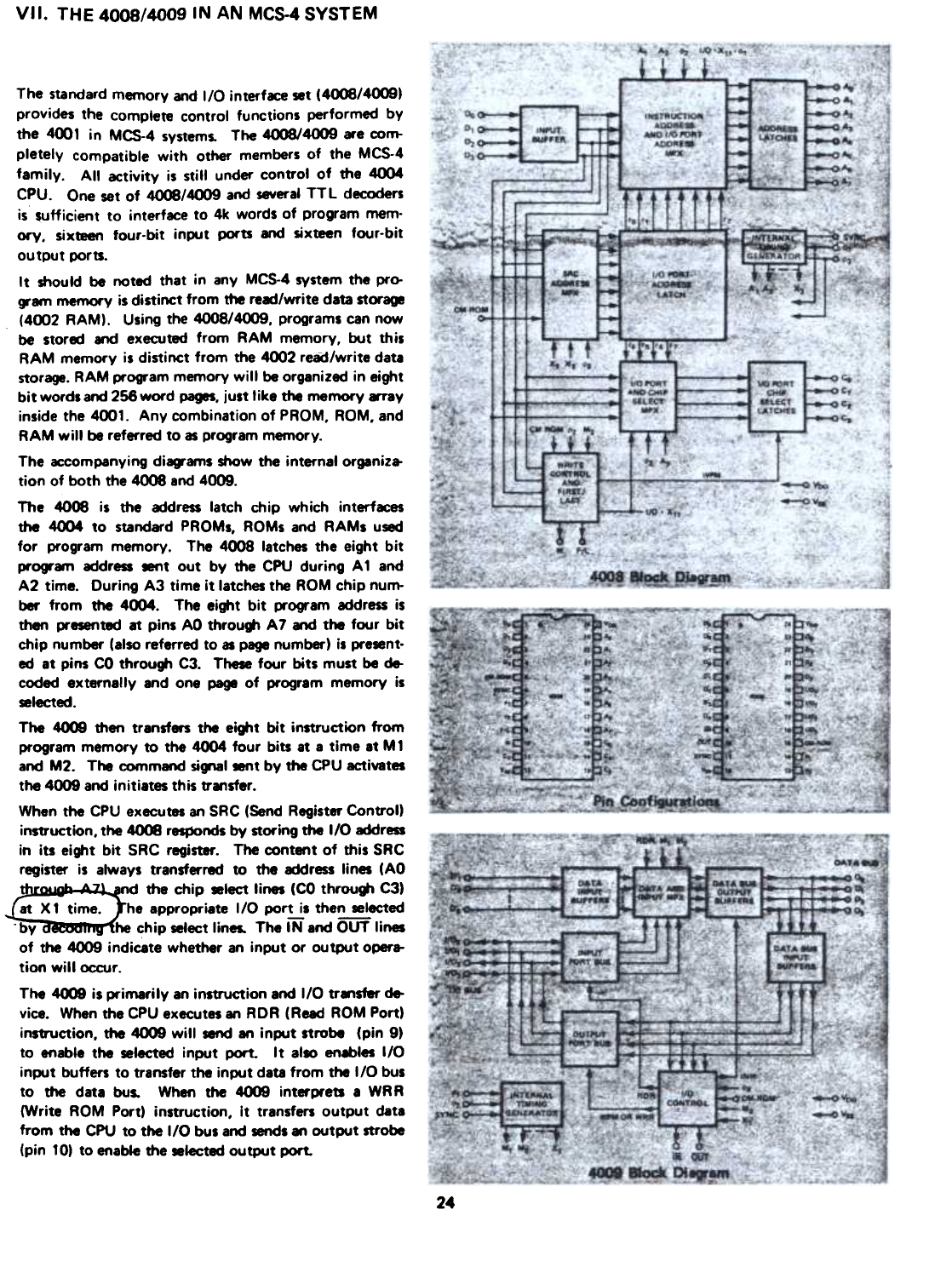

VII. THE 4008/4009 IN AN MCS-4 SYSTEM

The standard memory and I/O interf-=e set (4008/4()(m)

provides the complete control functions performed by

the 4001 in MCS-4 systems. The 4008/4009 are com-

pletely compatible with other members of the MCS-4

family. All activity is still under control of the 4004

CPU. One set of 4008/4009 and seYeral TTL decoders

is $ufficient to interface to 4k words of program mem-

ory, sixteen four-bit input ports and sixteen four-bit

output ports.

It should be noted that in any MCS-4 system the pro-

""am memory is distinct from the re.t/write data st~

(4002 RAM). Using the 4008/4009, programs can now

be stored and executed from RAM memory, but this

RAM memory is distinct from the 4002 read/write data

storage. RAM program memory will be organized in eight

bit words am 256 word pages, just like the memory 8Tay

inside the 4001. Any combination of PROM, ROM, and

RAM will be referred to as program memory.

The ~companying diagrams show the internal organiz.

tion of both the 4008 and 4009.

The 4008 is the address latch chip which interfaces

the 4004 to standard PROMs, ROMs and RAMs used

for program memory. The 4008 latches the eight bit

prO'#'~ address ..,t out by the CPU during A 1 and

A2 time. During A3 time it latches the ROM chip num-

ber from the 4004. The eight bit program address is

then presented at pins AO throu~ A 7 and the four bit

chip number (also referred to as page number) is pre.nt.

ed at pins CO throu~ C3. These four bits must be de-

coded externally and one page of program memory is

.Iected.

The 4CX» then transfers the ei~t bit instruction from

program memory to the 4004 four bits at a time at M 1

and M2. The command sipl ~t by the CPU activates

the 4009 and initiates this tr.,sfer.

When the CPU executes an SRC (Send Register Control)

instruction, the 4O(m responds by storing the 110 address

in its eight bit SRC register. The content of this SRC

register is always transferred to the address lines (AO

-! ~5iJd the chip .Iect lines (CO throu~ C3)

at X 1 time. he ~ppropria~ I/O POr!..!.s the~~ted

"by he chip .Iect lines. The IN and OUT lines

of the 4009 indicate whether an input or output oper.

tion will occur.

The 4CX» is primarily an instruction and I/O tr.,ster de-

vice. When the CPU executes an RDR (Read ROM Port)

instruction, the 4009 will 8nd an input strobe (pin 9)

to enable the .Iected input port. It aim en8bles I/O

input buffers to transfer the input data from the I/O bus

to the data bus. When the 4CX» interprets a WR R

(Write ROM Port) instruction, it transfers output data

from the CPU to the I/O bus and .oos ., output strobe

(pin 10) to enable the .lected output port.

24

..

A formerly undefined instruction is now used in conjunction with the 4008/4009 to write data into the RAM progr~ memory.

This new instruction is ~11ed WPM (Write Program Memory - 111000111. When an inStruCtion is to be stored in RAM

program memory, it is written in two four.bit segments. The F/L signal from the 4008 keeps track of which half is being

written. When the CPU executes a WPM instruction, the chip select lines of the 4~ are jammed with "1111". In the system

design this should be designated as the RAM channel. The W line"on the 4008 is also activated by the WPM instruction.

The previously .lected SRC address on line AO through A7 of the 4~ becomes the address of the RAM word being

written. By appropriately decoding the chip select lines, the W line, and F/l, the write strobes can be generated for the memory,

The F/L line is initially high when power comes on. It then pulses low when every ~nd WPM is executed. A high on the

F/L line means that, the first four bits are being written, and a low means that the last four bits are being written. The 4009

transfers the segment of the instruction to the I/O bus at X2 of the WPM instruction. The SRC address sent to RAM is only

8 bits. When more than one page of RAM (256 bytes) is being written, an output port must be used to supply additional

address lines for higher order addr~.

Definition of Write Propam Memory Instruction

Mnemonic: WPM Description: The chip select lines of the 4008 are forced to "1111"

OPA OPA: 11100011 at X1 time and the content of the -=cumulator is available on the

Symbolic: 4009 110 bus at X2. AAM prQ9'am memory can be loaded four

1111 C3C2C, Co of ~ bits at a time. The previous SAC address is .nt out on lines AO

ACC ""'1/031/~ 1/0,1/00 of 4009 through A7 of 4008.

SAC Address --- Ao - A7 of 4008

System Illustrations Using the 4008 8Id 4009

Four systems are shown where the MCS-4 components are used with standard Intel memory elements as the program memory.

Notice that several different approaches to chip .Iect. port decoding, and the 110 elements are shown.

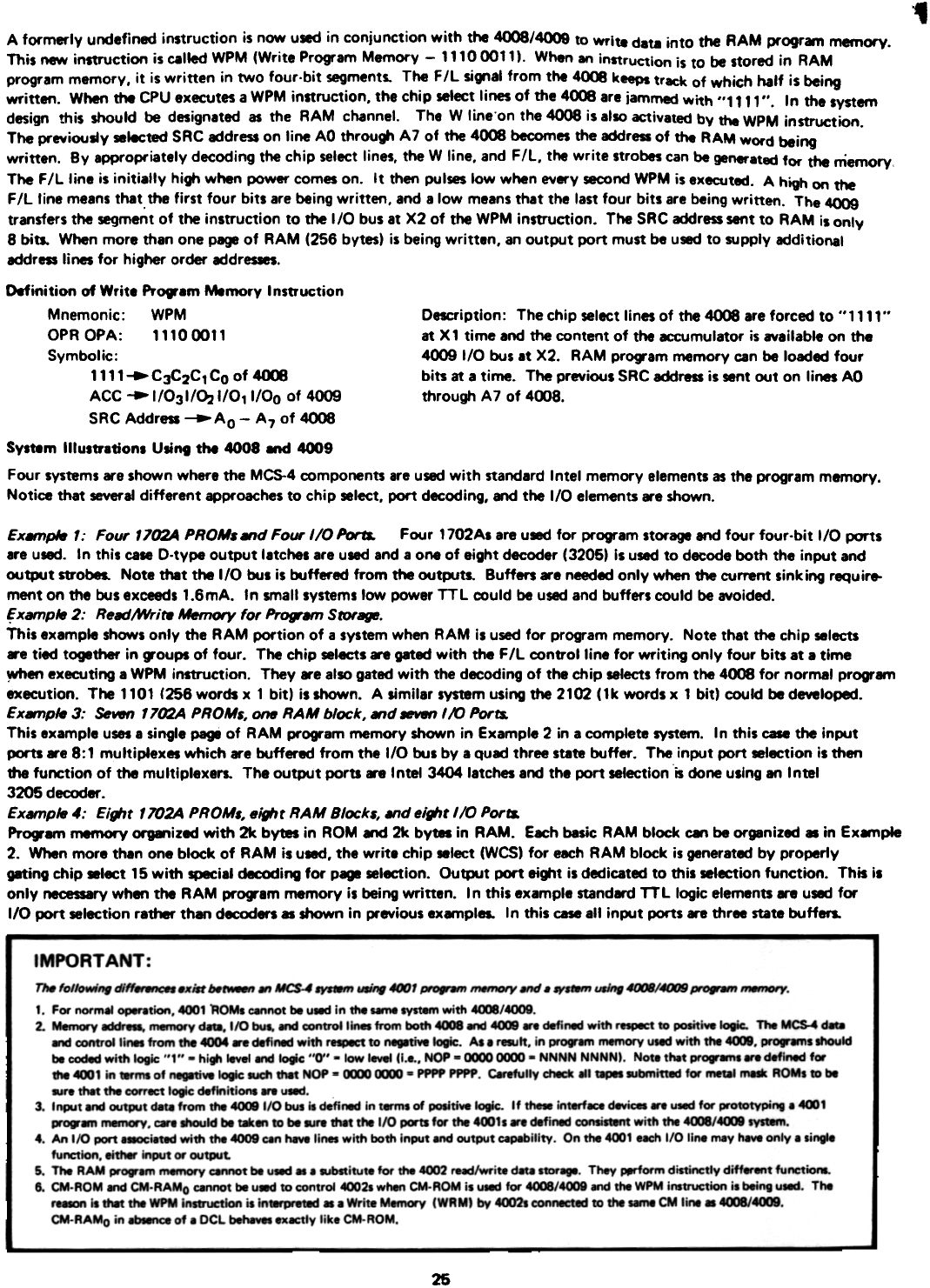

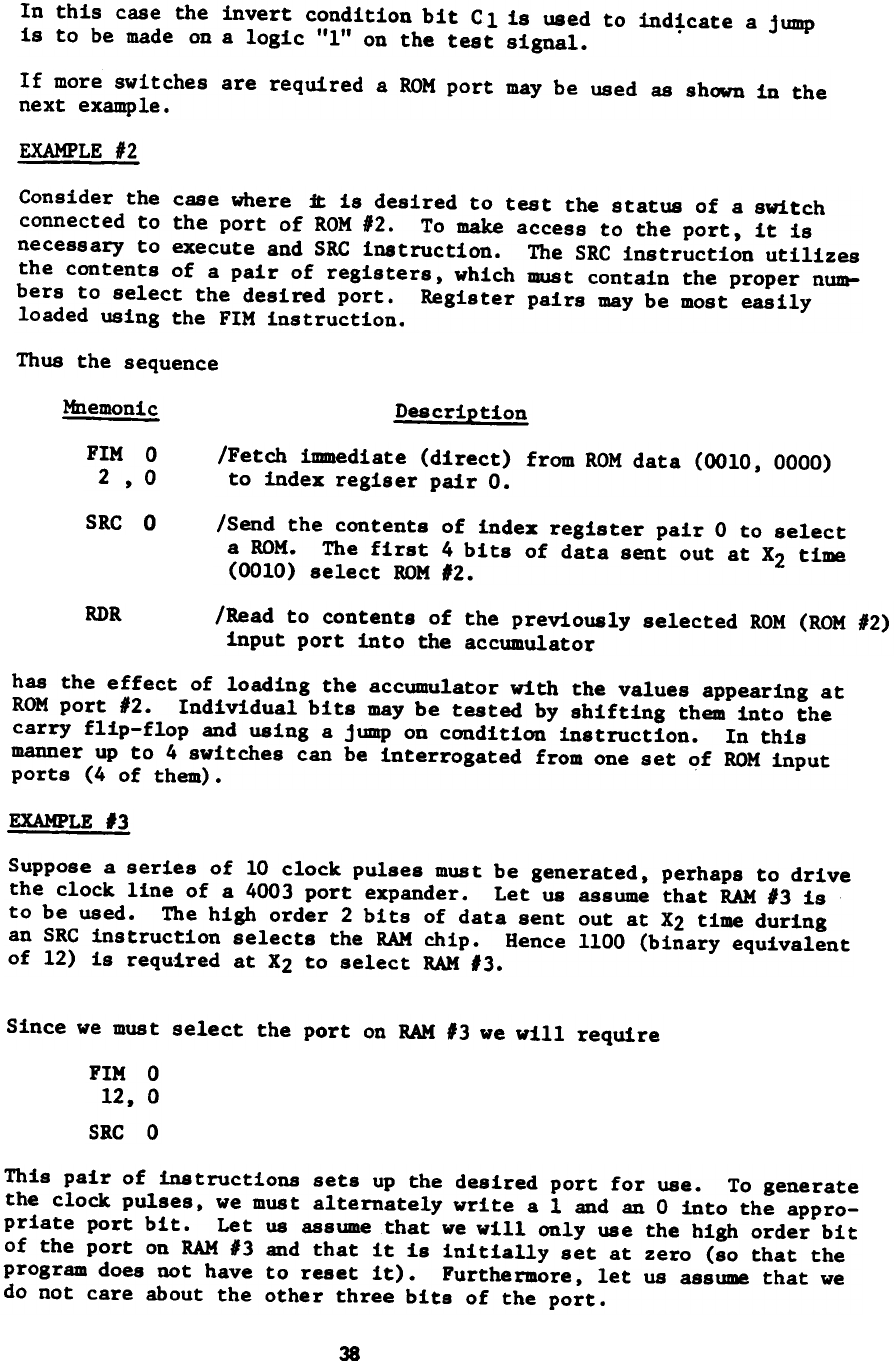

Ex.",p'- 1: Four 17O2A PROM..,d Four 110 PtN'1a. Four 1702AI are u8d for program Itorage and four four.bit I/O ports

are used. In this caR D.type output latches are used and a one of eight decoder (3205) Is u8d to decode both the input and

output strobes. Note that the I/O bul is buffered from the outpJtI. Buffen are needed only when the current sinking requi~

ment on the bus exceeds 1.6mA. In small systems low power TTL could be used and buffers could be avoided.

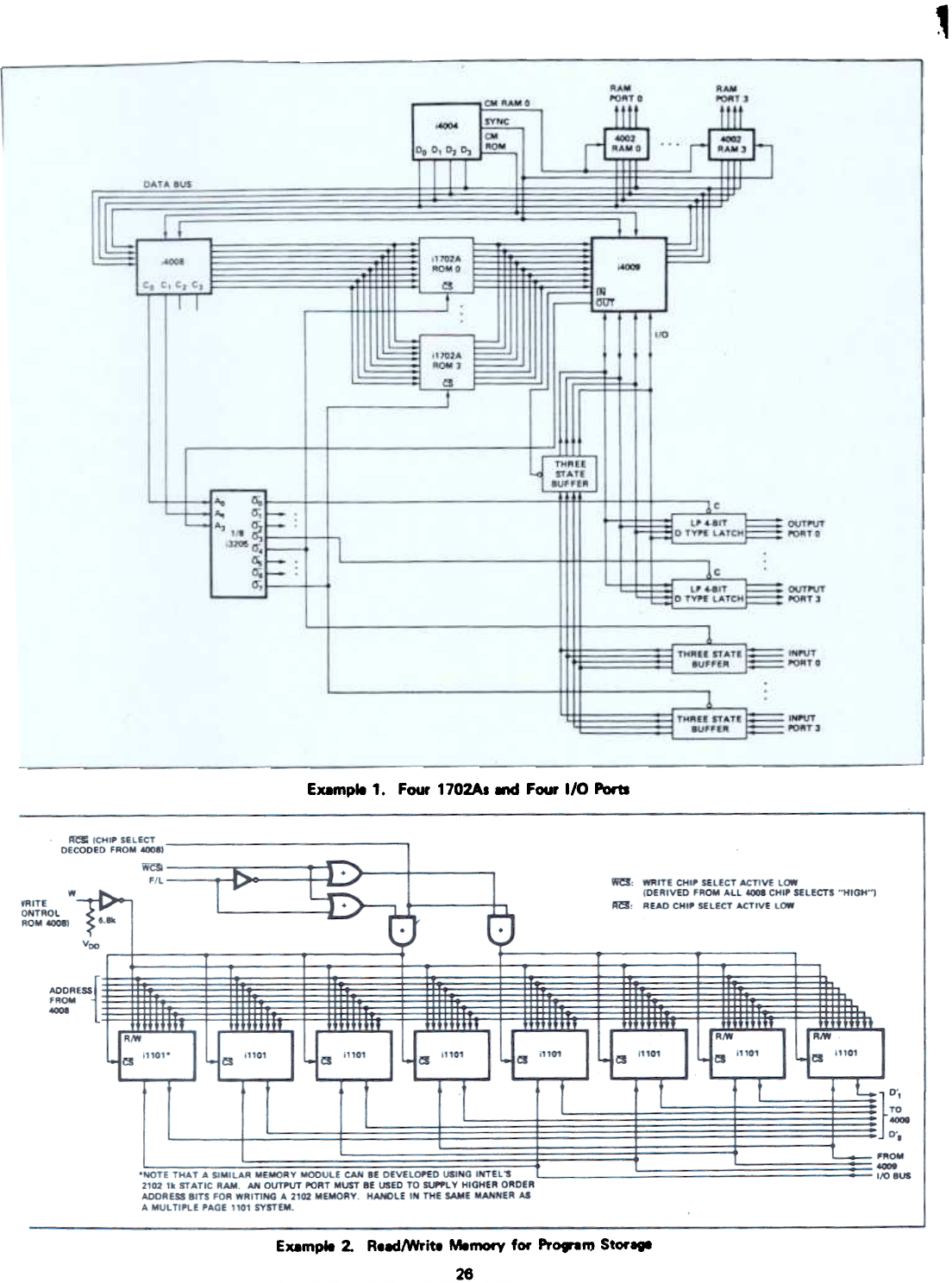

~xample 2: ReadtWrir. Memory for Pro,am Sror..

This example shows only the RAM portion of a system when RAM is used for program memory. Note that the chip selects

are tied t~ther in ,#,oups of four. The chip alects are gated with the F/L control line for writing only four bits at a time

.when executing a WPM instruction. They.e also gated with the decoding of the chip selects from the 4008 for normal program

execution. The 1101 1256 words x 1 bit) is shown. A similar system using the 2102 (1k words x 1 bit) could be dewloped.

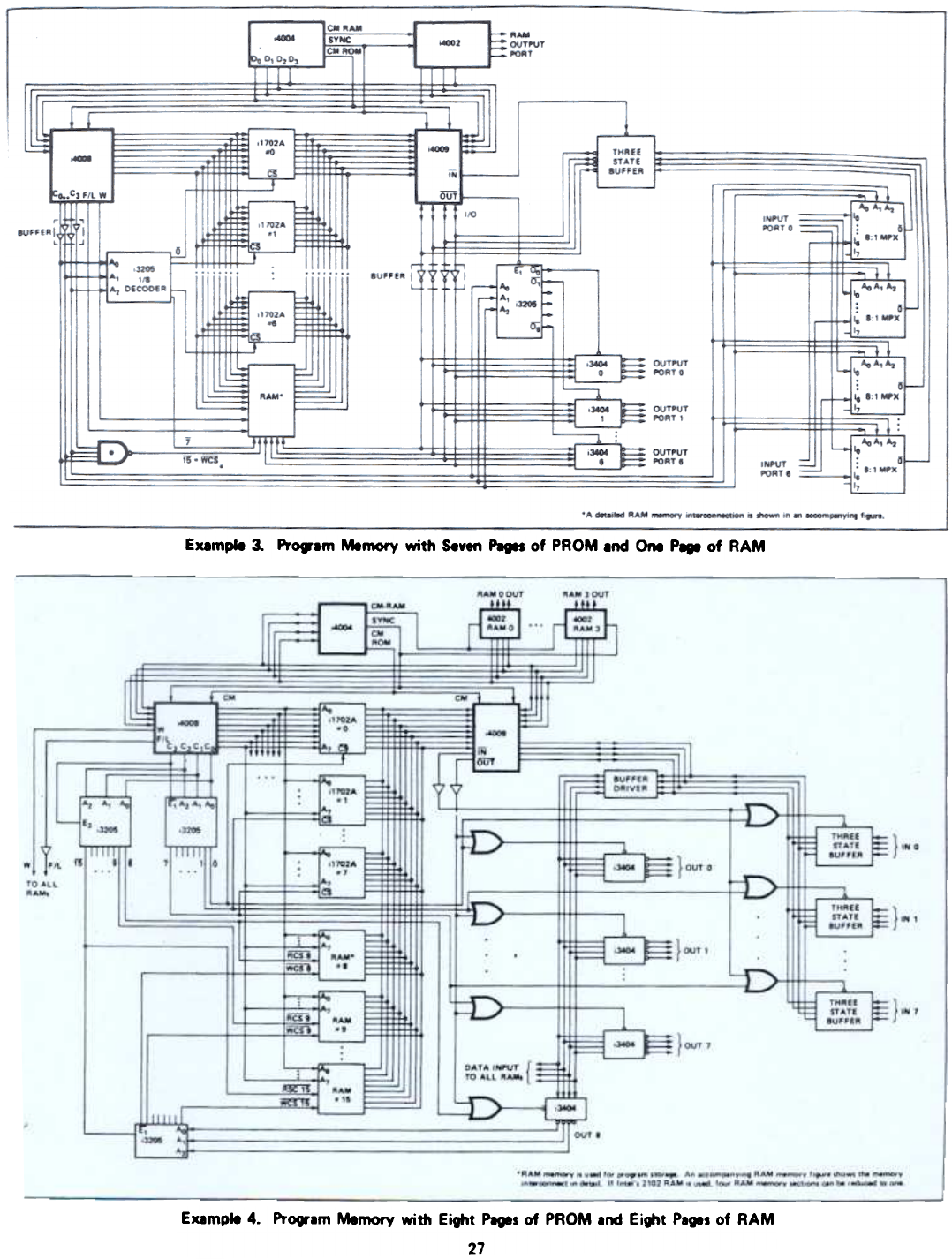

Ex~p" 3: Se.." 17O2A PROMs, one RAM block, .,d..,." I/O Ports.

This example uses a single P9 of RAM program memory shown in Example 2 in a complete system. In this case the input

ports .e 8: 1 muhipiexes which are buffered from the I/O bul by a quad three state buffer. The input port sefection is then

the function of the multiplexers. The outpl.it ports are Intel 3404 latches and the port selection is done using an Intel

3205 decoder.

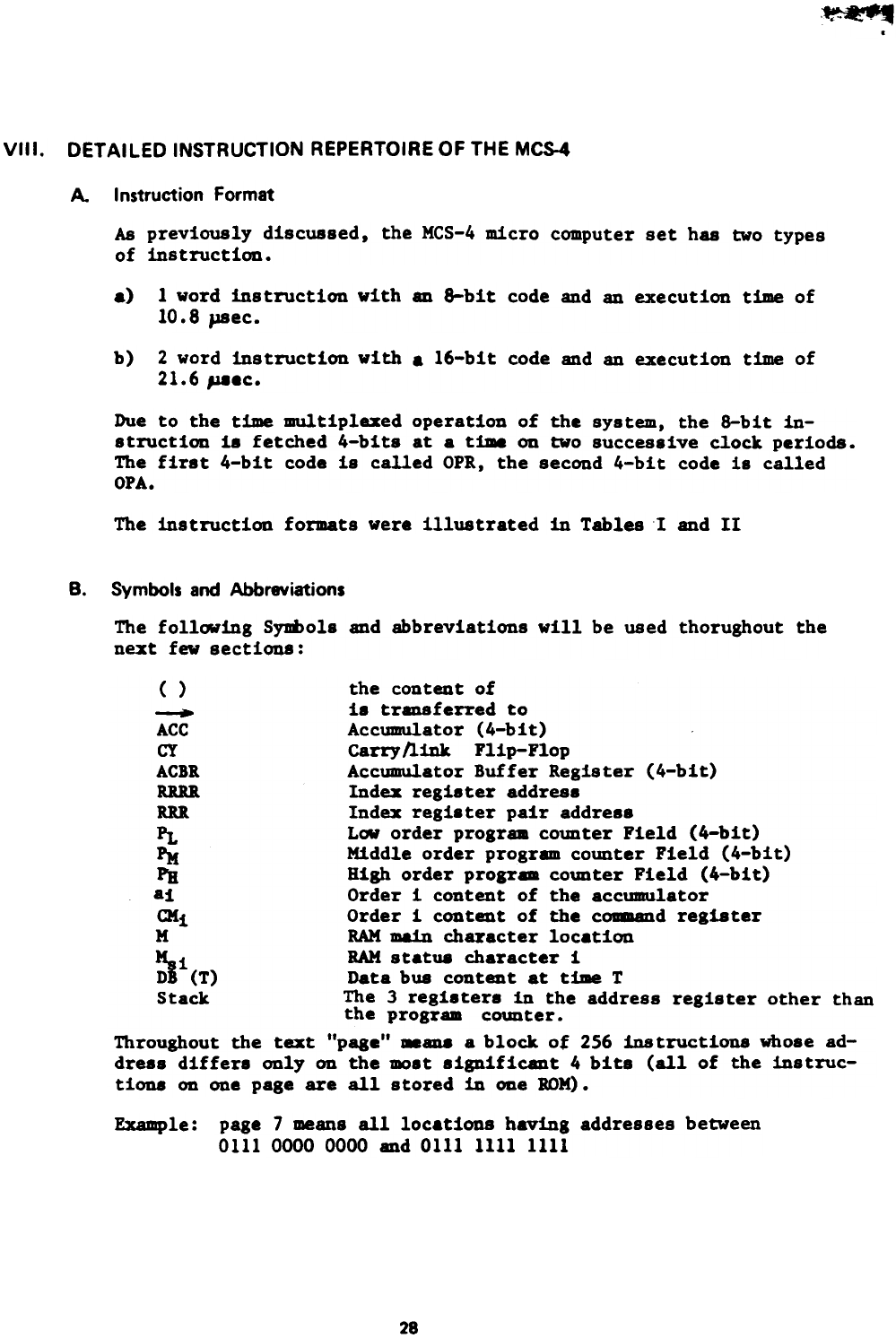

Example 4: EifIJt 1702A PROM" eigflt RAM Slocks, ."d eilht I/O Ports.

Pro".8m memory ~ized with 2k bytes in ROM m 2k bytes in RAM. EKh basic RAM block C8\ be organized - in Ex8nple

2. When more than one block of RAM is u~. the write chip select (WCS) for each RAM block is generated by properly

gating chip .I~t 15 with special decoding for P9 alection. Output port eight is dedicated to this _Iection function. This II

only necessary when the RAM prO9'am memory is being written. In this example standard TTL logic elements... used for

I/O port alection rather than decoders - shown in previous ex.nples. In this case all input portS are three state buffers.

IMPORTANT:

The followi", dlff ,.;. .xilt be~ ., MCS..f IYIMm urillf 4001 ~ nIenIOrY .nd . 'Y""" uI/"f 4«1B/4/D P'o,¥II /rI8mOI'Y.

,. FM normel oper8tbt, 4001 }tOMs --' be ~ In the ..,. ~ with ~/4009.

2. M-V MId~, memory d_, I/O~. Ind mntrollmer from both 4008 ~ 4(D ... defin.t with respect to potitiw logic. The Mcs.4 d..

8wJ comrolll~ from the 4004 ... defi- with ~ to neg8tiw logic. AI. r8JIt, in prQ9'lm memory used with the 4(D. pr~.1tIouIcI

be co-.wlttliogic "1" - hl~ '-I ~.. "0" -low '-I (i..., HOP - CDX)CDX) - NNNN NNNNI. Notethet prc.-8nI_"-1rI.t fa'

the 4001 In t8r1nS of negetiw logic ~ th8t NOP - CDX) CDX) - pppp PPPP. C8r8fully check all tapes .,bmittad fM metal m" ROMI to be

-- th8t the corrKt logic detklltl- - u8t.

3. I"""t"" ~tPlt d8t8 from the 4«» 1/0 ~ is d8fi- in -- of poIitiV8logic. If t'- interf- devi~ - u* fM prototyping . 4001

Pl'C9'8n m8n1a'Y, c.-eltlould be tMIn to be.,.. th.t the I/O ports fM the 40011... defin.t conlistant with the 4008/4(8 syItam.

4. An I/O ~ _i818d with the 4009 can ~ Ii,. with both input ~ OUtput c8P8bitity. On the 4001 88d\ I/O line may ~ only .Ii'"

function, 811'- i"tlUt or ~tIMIf.

5. The RAM prc.-.m memory cannot be u* - . .,bltitut. for the 4002 mdt-it. data ltor.. They ~orm distinctly d~t functioN.

8. CM-ROM ~ CM-RAMO --' be u8t to control GJ2I ~ CM-ROM il ~ fa' 4Ca/4008 ~ the WPM irwtNctlon il b8inI U-S. The

~ Is th8t the WPM Inl1ructlon II interpretad -. Writ. M-V (WRMI by 40021 connectad to the -- CM line - 4CXI8/4008.

CM.RAMo in ~ of. DCL b8f\8V818Xactly like CM-ROM.

25

,

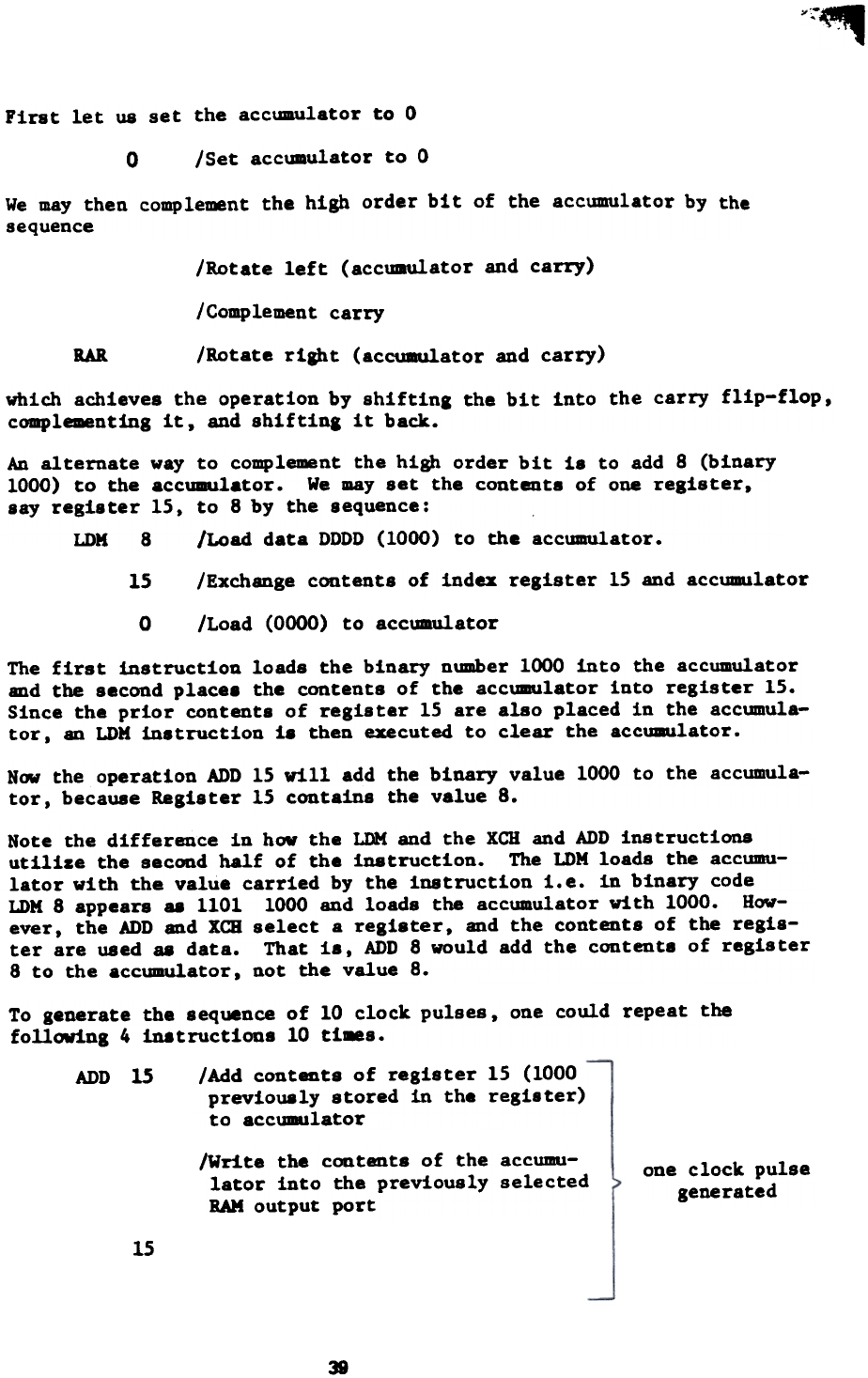

Eumple 1. Four 1102As - Four 1/0 Po.1I

Eump'- 2. Re./Write MemofY for Pro.--"' Stor.

26

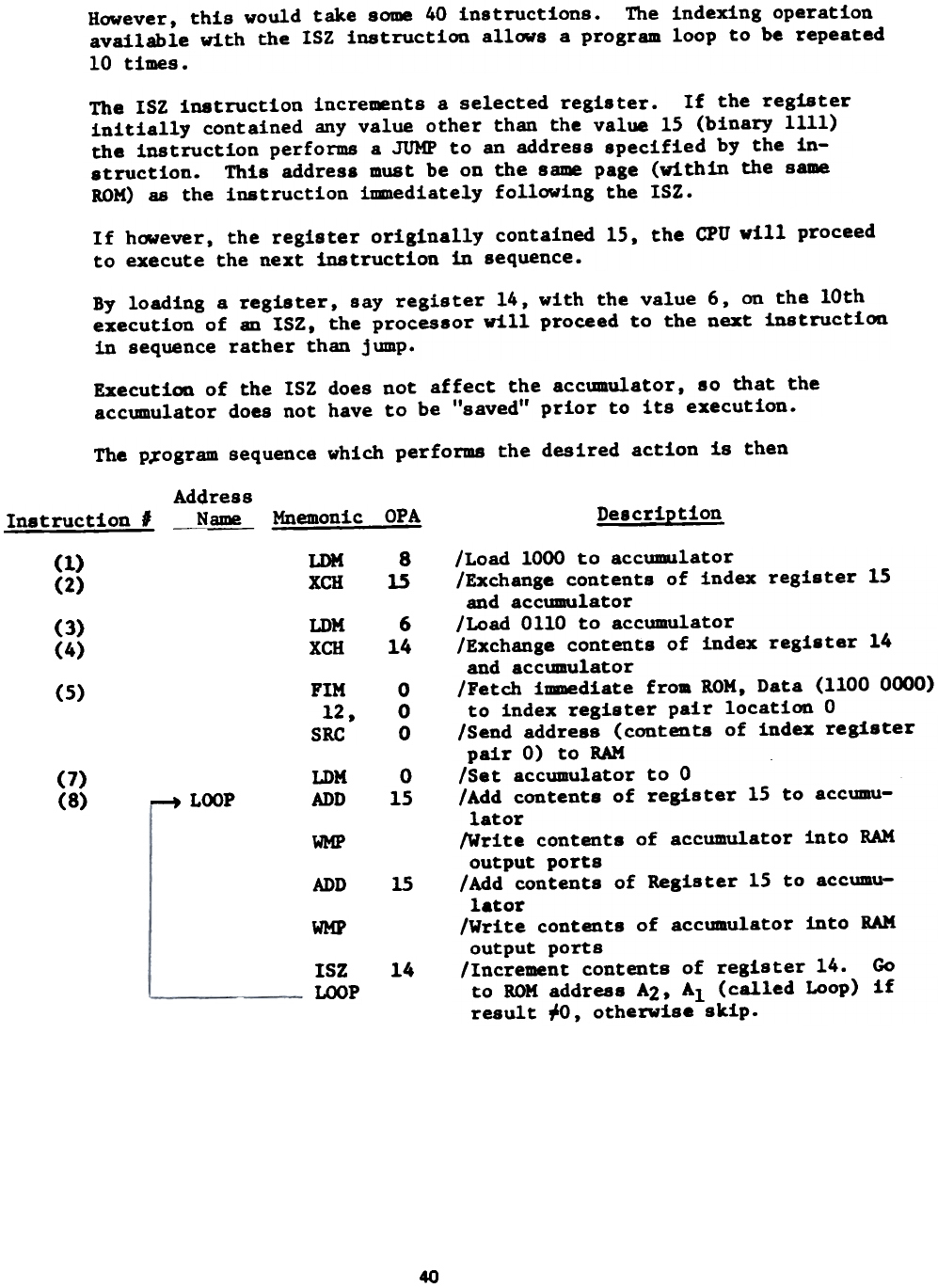

Eumple 3. PrOW8m Memory with Seven P8g8t of PROM 8nd One p. of RAM

Example 4. Pro".m Memory with Ei9ht P8geS of PROM .rId Eight P.~s of RAM

27

.~~ .

DETAILED INSTRUCTION REPERTOIRE OF THE MCS-4

VIII.

A. Instruction Format

As previously discussed, the MCS-4 micro computer set has two types

of instruction.

a) 1 word instruction with an 8-bit code and an execution time of

10.8 psec.

b) 2 word instruction with. 16-bit code and an execution time of

21.6 pa8C.

Due to the time multiplexed operation of the system, the 8-bit in-

struction 18 fetChed 4-bit. at a time on two successive clock periods.

The first 4-bit code i. called CPR, the second 4-bit code is called

CPA.

The instruction formats were illustrated in Tables I and II

B. Symbols and Abbreviations

The following SyDbol8 and abbreviations will be used thorughout the

next few sections:

( ) the content of

i8 transferred to

ACC Accumulator (4-bit)

CY Carry /link Flip-Flop

ACBR Accumulator Buffer Register (4-bit)

RRRR Index regi8ter addres8

RRR Index regia ter pair addres8

~ Low order program counter Field (4-bit)

~ Middle order prosram counter Field (4-bit)

PH High order progr.. counter Field (4-bit)

ai Order i content of the accumulator

CHi Order i content of the command register

M RAM main character location

~i RAM statua character i

DI (T) Data bus content at time T

Stack The 3 register8 in the address register other than

the program counter.

Throughout the text "pase" _ana a block. of 256 instructions whose ad-

dre8s differs only on the most 8ignificant 4 bits (all of the instruc-

tiona on one page are all stored in one ROM).

Example: page 7 means all locations having addresses between

0111 0000 0000 and 0111 1111 1111

28

..:'~

c. Format for Describing Each Instruction

Each iD8truct100 v111 b. de.cr1b.d .. follow.:

(1) ~_ic ."01 _d --in.

(2) OP" _d OPA cod.

(3) S,.olic repr..eotatiOD of the iD8tractiOD

(4) Deacript100 of the iD8truCtiOD (if n.ce..ery)

(5) ~le aDd/or excapt1oD8 (if nec..aery)

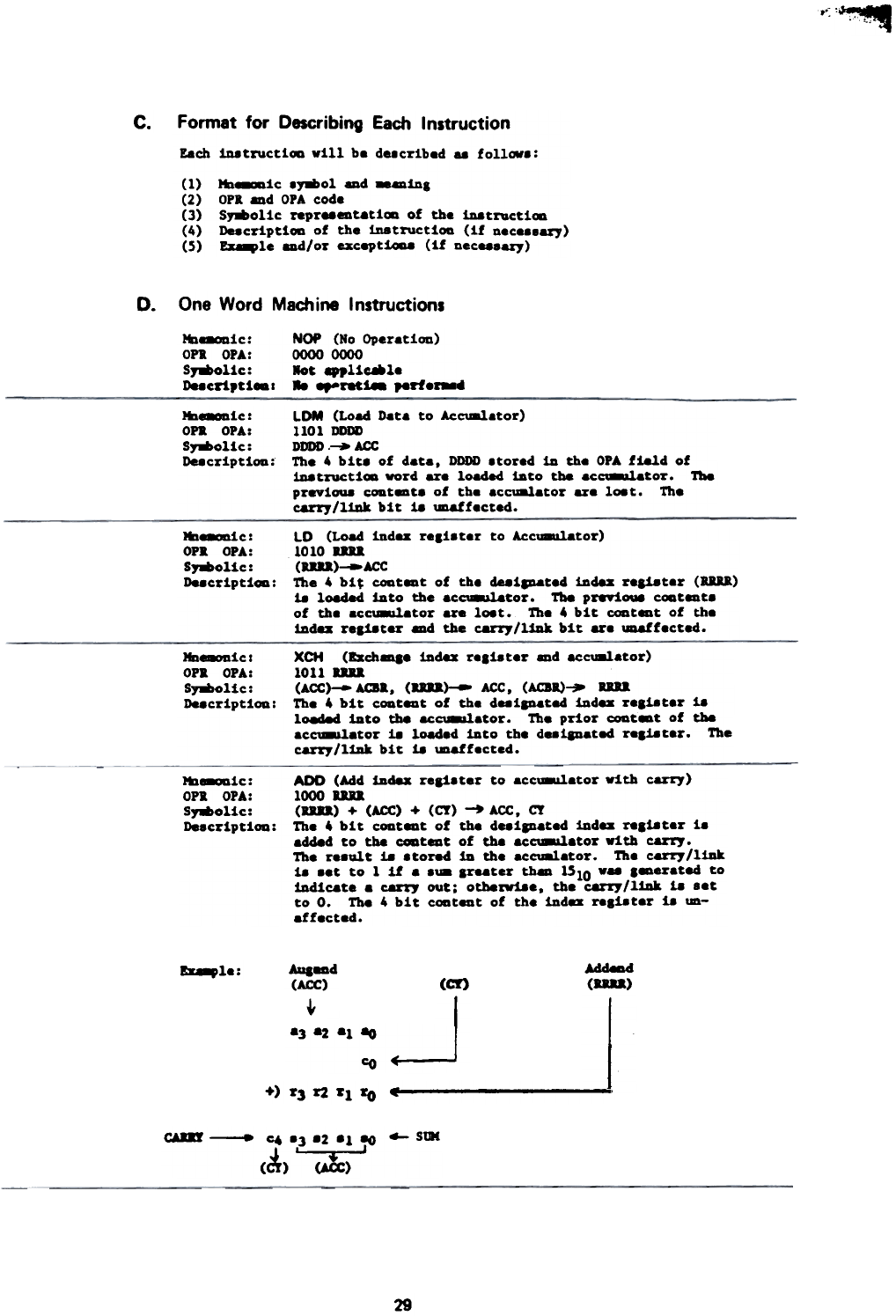

D. One Word Mad1ine Instructions

!t1_ic: NOP (No Operation)

on orA: 0000 0000

S,.oUc: Moc, ..,Uc81.

D88cri,c,I_a .. ...~18 ,.I'f.~.

MD88ODie: L~ (Load Data to AeCU8lator)

on OPAl 1101 DDOO

S,.olie: DODD .-. ACC

Deeeripti_: The 4 bit. of data. DODD atorecl iD the OPA fielcl of

iD8trueti~ vorcl are loaclecl iDto the ae~tor. The

previ0U8 e-teDt. of the aeCU8lator are loat. The

eury/liDk bit 18 unaffeetecl.

HD88ODic: LD (L084 indez re.i8ter to AccU8Ulator)

OPI. OPAl 1010 DB

S,.olic: (DB)--ACC

ne8criptiOD: The 4 bi~ coot8Dt of tbe da8iaaated indaz reliater (l.1l.I.)

18 loedecl into the ac~~or. The prerlo.- CODt8Dt8

of the accU8Ulator are loet. The 4 bit CODt8Dt of the

indaz reliater ad the carry/11IIk bit are IlDaffected.

MD_icl XCH (bch-.e index re.18ter cd acc\8lator)

opa OPAl 1011 IDa

S,-ol1c: (ACC>- ACU. (1Da>-- ACC. (ACBR)~ IDa

Deacriptioa: The 4 bit coat8Dt of the d..ilD&ted ind.. re.18ter 18

lo8d8d into the ac~ator. The prior coat_t of the

ac~ator 18 loaded into the de.ilDated re.18ter. The

carry/liDk bit 18 UDaffected.

*_ic: ADD (Add iDdu rep.ter to acc~ator with carry)

OPI. OPA: 1000 UI.I.

Sy8olic: (DII.) + (ACC) + (Cf) ~ ACC, Cf

ne.criptioo: The 4 bit coot8Dt of the de.ilDated iDdcz rel18ter i.

ad4ed to the ~teat of the 8C~ator with carry.

The re.lIlt 18 .tored iD the ac~ator. The carry/liDk

i. .et to 1 if a .ua ar..ter th8D 1S10 ... leDerated to

iDclicate a carry out; ot.he~e, the carry/liDk ia .et

to O. The 4 bit coateat of the iDdcz reliater 18 UD-

affected.

~

(DU)

I

~l.: Aua~

(ACC)

'"

(cr)

a3 a2 al ao

co +-_J

+) r) r2 rl ro ~

CADI - C4 83 82 81 ~ - StD(

<i,> L~~

29

.

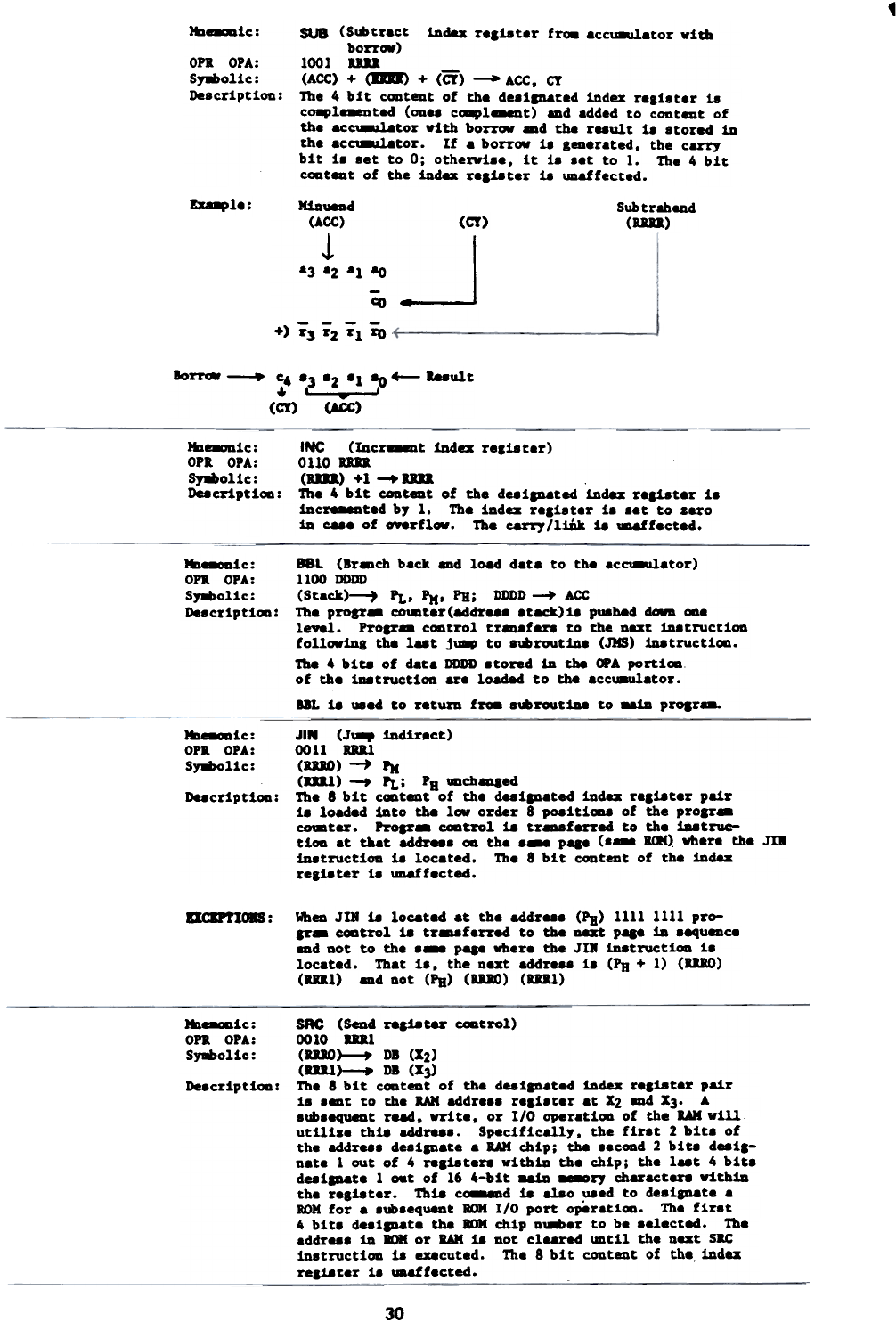

HD88DDic: 5lnI (Subtract iDdex rea18ter fro. acCU8Ulator with

borr~)

on orA: 1001 lID

Sy8o1ic: (ACC) + (IDK) + ('ct") - ACC, CY

DescriptiOD: The 4 bit content of the de8ilnated iDdex relister is

cO8ple8ented (on.. ca8pl888Dt) 8Dd added to CODtCDt of

the ac~tor with bo~ _d the r..u1t 18 stored iD

the ac~tor. If a borr~ 18 geDerated, the carry

bit i8 set to 0; othervi.e, it 18 set to 1. The 4 bit

coatCDt of the 1Dd8z rea18ter 18 unaffected.

~l.: Subtr8bend

(RID.)

HiD_d

(ACC) (cr)

a3f2 al~ ~

+) r3 r2 rl "io

Io~ ~ 83 82 81 eo 4- "'u1t

.. ,- -- '

(Cf) (ACC)

MDe.onic: INN: (InCr888Dt 1D4ex resister)

OPI. OrA: 0110 un

S}8Iolic: (UD) +1 -.DD.

DeacriptiOD: The 4 bit coateDt of the deailD&ted indez reai8ter i.

inCr888Dted by 1. The index rea1eter i. .et to .ero

in c..e of overflow. The cerry/ltDk 18 unaffected.

~c: 88L (Brach back 8Dcl 1084 data to the ac~tor)

on orA: 1100 DODD

S,.bolic: (Stack)---J Pt- ~- PH; DODD ~ ACC

Deacr1pti_: The proar- CO18ter(addr... .tack)18 pU8bed dOIfD _e

level. Proar" c_trol tr8D8fer. to the D8Kt iD.tructiOD

foUov1Dl the lut j~ to .ubroutiD8 (J1tS) iD8tructi_.

The 4 b1t8 of data DODD .tored iD tb8 CWA porti-

of the iDatruct1- are loaded to tha accU8Ulator.

IBL 18 U8ed to retum f~ 81IbrwtiD8 to ~ proar...

~ic: JIN (J~ 1D~ct)

on. OPA: 0011 ID1

Sy8Iolic: (010) -. PM

(.u.l) -. 'L; PH _cb-.ecI

De8criptiaa: Tbe 8 bit caoteot of the d88i8Beteci 1DdcK rea18ter pair

i8 loedad into the low order 8 po.iti0D8 of the proar"

COIater. hoar- ~trol 18 treafea- to the 1D8true-

tiaa at thet addra. ~ the .- p... (.- I(J() where the JIB

1D8truCtiOD 18 loceted. The 8 bit CODteDt of the indcK

rel18ter 18 lmaffectecl.

Wbeo JIB t. located at the addr... (Pa) 1111 1111 pro-

ar- _trol t. tr..ferred to the D8Zt pq8 in nq_ce

_d Dot to the .- p... where the Jm iD8trvctiOD 1.

locat.d. That i., the Dazt addr... 1. (Pa + 1) (KIlO)

(1Dl) _d Dot (PH) (u..Q) (01.1)

1IC8P'rtC8:

__ic: SAC (Send reai8tu ~t.rol)

on OPA: 0010 IDl

Syllbolic: (010)-.- DB (Xv

(1Dl)-. DB (%y

Descript.i_: The 8 bit. ~t.-t. of t.be deei.-t.ed iAdez re&i8t.er pair

is S8Dt. t.o t.be lAM address relist.er at. X2 and X3' A

subseq-t. reacl. vr1t.e. or I/O operat.i- of t.be UK will

ut.1l1.e t.b18 address. Specifically, t.be f1rat. 2 b1t.s of

t.be address dee1lDat.e a aAH chip; t.be secODd 2 bit.a d..il-

nat.e 1 out. of 4 reliet.era wit.biA t.be chip; t.be laat. 4 bit.a

deai.-t.e 1 out. of 16 4-bit. ~ -1'1 ch-act.ar8 rit.biA

t.ba re.18t.er. Th18 c~d 18 8180 used t.o des1.-t.e .

ROM for a sUbseq~t ROM I/O port. op.rat.~_. The firat.

4 bit.a dee1.-t.e f.h8 ROM chip n,.ar t.o be s8lect.ed. The

addr..s iA ~ or UK 18 not. cleared _t.i1 t.be nest. s.c

iD8t.ruCt.iOD 18 uecut.ed. The 8 bit. CODt_t. of the, iAdex

reli8t.er is _affected.

30

~..,

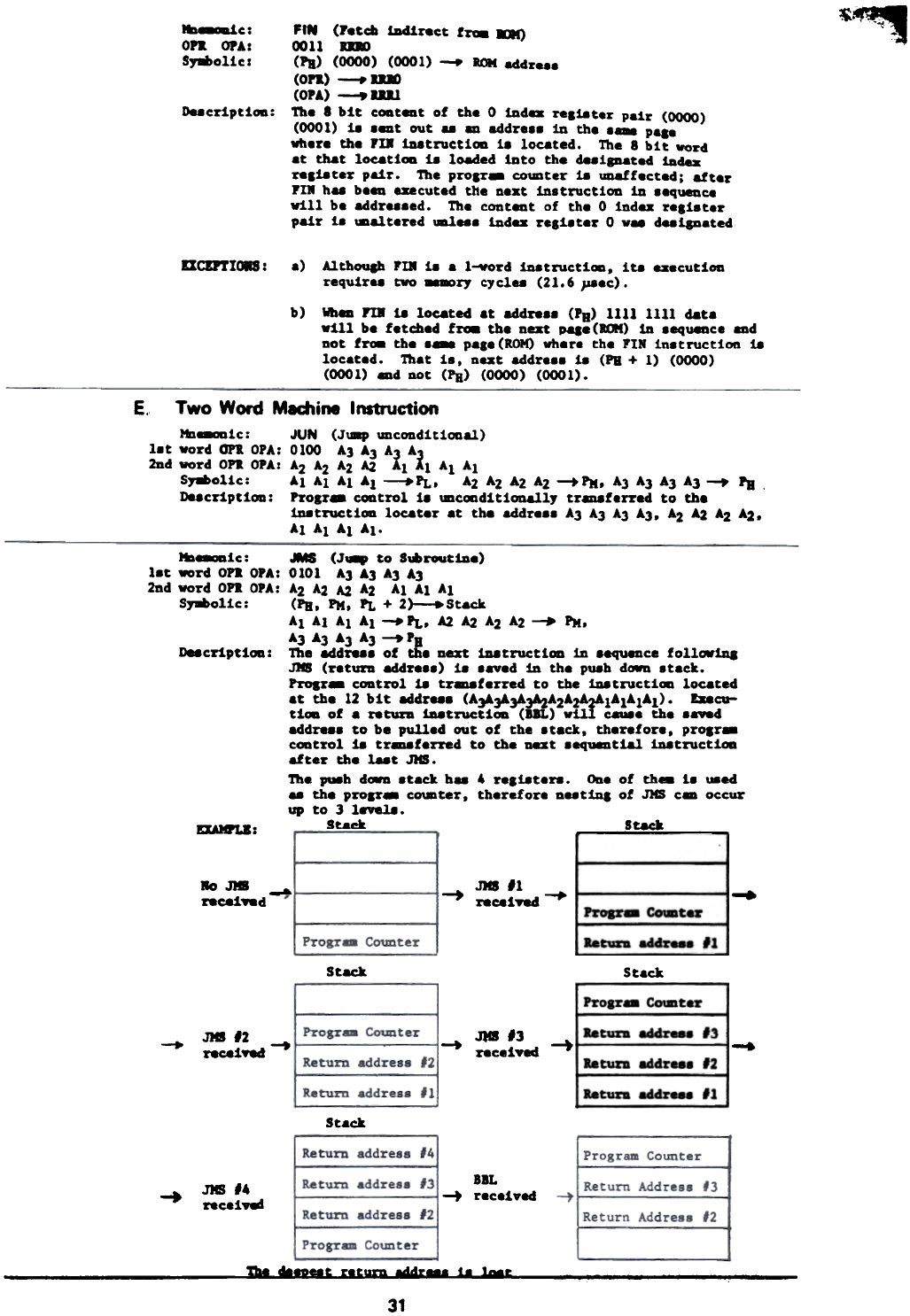

~c: FIN (I'etcb 1D41rect f~ ->

on. orA: 0011 om

SY8bolicl (Pa) (0000) (0001) --. 10M addre..

(On.) - ~

(OlA) --91U1

D88criptioa: The 8 bit coateDt of the 0 index rel18ter pair (0000)

(0001) i. .eDt out .. 8D addre.. in the paae

where the FII 1D8tructioa i. located. The 8 bit word

at that locati~ u loaded into the d88ilDated in~

relute~ pair. The proar" COUDte~ 18 uaaffected; after

FII b.. beeD executed the next in.truction in .equence

vi1l be addr...ed. The conteDt of the 0 indez reli.ter

pair i. UDaltered UDl... indez re.uter 0 v.. d..ignated

UClPrII-. : a) Althouih FII 1a a 1-word ~truct1OD. ita ezecut1oa

requ1r.. two ..-ory cycle. (21.6 paec).

b) Wb8a FIB 18 located at a4dre.. (Pa) 1111 1111 4ata

will be fetched f~ the Dezt pqe (1mI) in .equence and

Dot f~ the pa.. (ao.o wh.re the FIR inetruct1oc 18

loc.ted. That 18. Dezt addre.. 1. (PH + 1) (0000)

(0001) and DOt (Pa) (0000) (0001).

E. Two Word Mdine Instruction

HD88ODic: JUN (JU8p unconditional)

l.t word on OPAl 0100 AJ AJ AJ AJ

2nd word on OPA: A2 A2 A2 A2 Al Al Al Al

S,.ol1c: Al Al Al Al --+Pt. A2 A2 A2 A2 -+PK. AJ AJ AJ AJ""" Pg

Deacription: Prolr.. control i. UDcoaditioaally traD8f.rred to the

1D8truction locater .t the addu.. AJ AJ AJ AJ. A2 A2 A2 A2.

Al Al Al AI-

~88ODic: JMS (JU8p ~o SubroutiDe)

18~ word OpR OPA: 0101 A] A] A] A]

2Dd word OpR OPA: A2 A2 A2 A2 Al Al Al

SY8bolic: (PH. PM. Pt + 2~Stack

Al Al Al Al - PL. A2 A2 A2 A2 -. PM.

A3 A3 A3 A] -+ PI

D88crlp~i_: 'nIe eddrea8 of the next. 1D8truc~i- iD 8equence foll~iDa

JNB (r8turD addr888) i8 88Ved iD the puah do.n st8ck.

P1'OI1'- control 18 traaferred to the 1D8tructi- located

at the 12 bit eddr"8 (AJAJA~JA2A2A~IA1A1AV. EaaCD-

ti- of a nt1lZD 1D8tructl- (IlL) will ~e the 8.-4

addre88 ~o be p~ed out of the 8tack. therefore. prolr..

c_trol 18 tr_ferred to the nest 8~t1al 1D8t1'UctiOD

after the l..t JNB.

'nIe p.-h do.n 8tack h.. 4 rel18ten. One of th- 18 \8ec1

.. the P1'Ol1'- COUD~er. therefore n..tiDa of JHS CaD occur

up to 3 1.-18.

~: Suck ~ Stack

RoJ18

nce1.-d -a. --. JIG 11

recelY8d

~

hoar- Co1mt..r

I.. t.1IZB -.r- , 1

Stack Stack

I Pr°lr- C_ter

1- - -

Ilat.1lZB ~ 13

I Proir- COImtu

I lat:ara ~ #2

-. J1tI 13

received

-+ JIm 12

"cd'" -. ~-.

lletum 8ddr... 12

, "tuzn addr... '1 I latum 8cldr... , 1

Stack

"tun 8ddr... ,.

I latum addr... ..,

.nm ,.

nee1v-'

-. IlL

-+ received

18t:UZD 8ddr... 12

rroar- Co8tu

'rb8 --_to r8toUrft add.-. f. t_..

31

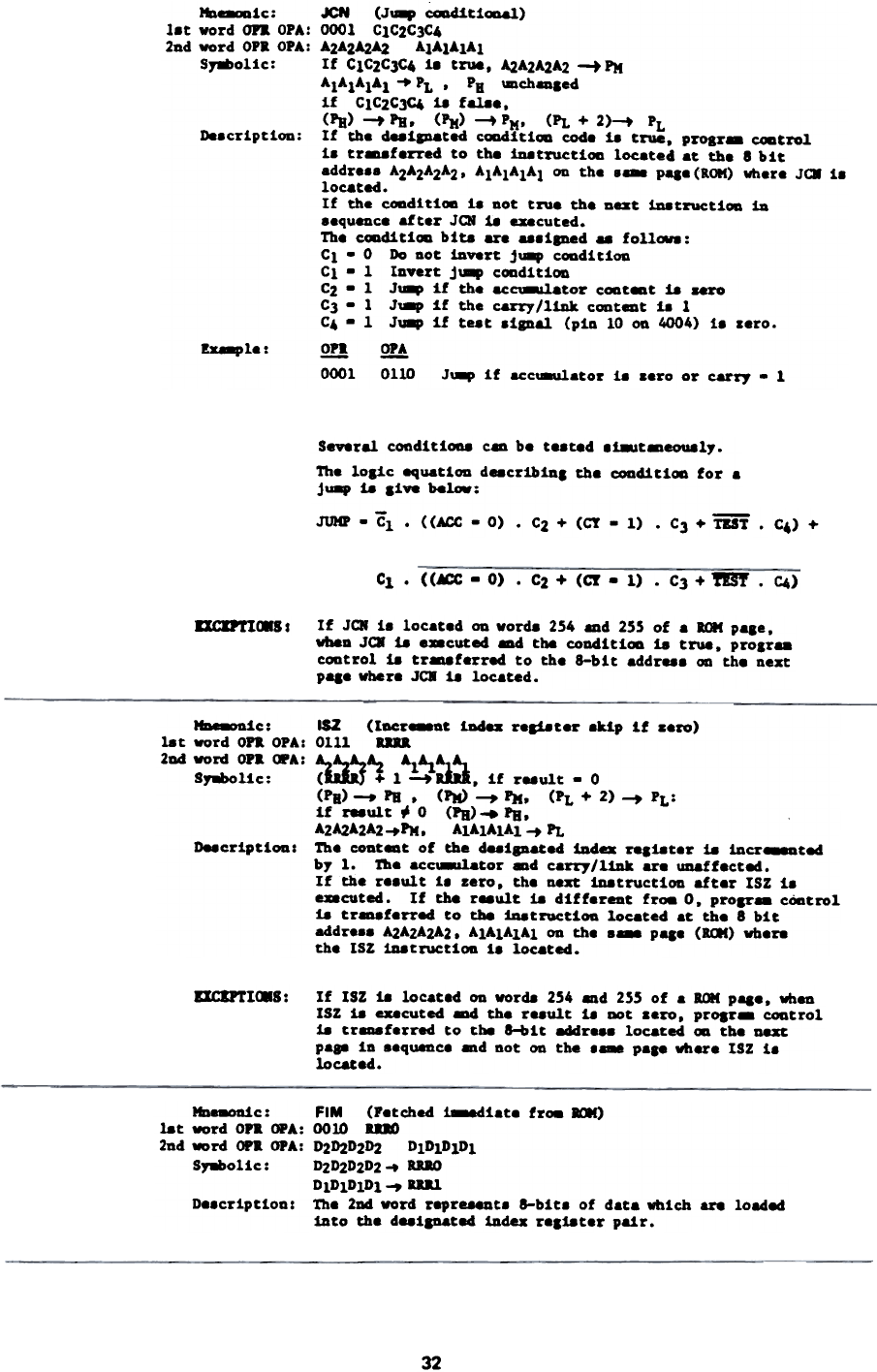

*_1c: .K:N (J~ Caliit1CXi&l)

l.t word ora OPA: 0001 CICZC3C4

2nd word opa OPAl AZAZA2A2 AIAIAIAl

Sy8bolic: If CICZC3C4 1. t~, A2AZA2AZ --. PM

AIAIAIAI -. PL' PH unch8Dled

if CICZC3C4 1. f&18e,

(Pa) -t PH, ('K) -+ PM' (PL + Z)-. PL

De.criptiOD: If the duilDated cODAi1ti~ code 1. true, proar- ~tzo1

1. tr~ferTed to the ia8truct1~ locate' at the 8 bit

addre.. AZAZAZAZ' AIAIAIAl OD the PAle (ROM) where JC8 i.

located.

If the CODd1t1~ 18 Dot true the nest ia8truct1~ in

.eqU8Dce after JCN 18 ezecuted.

The ~d1t1~ b1t8 are ...iped .. fo11-.:

Cl . 0 Do Dot invert jU8p c~dit1OD

Cl . 1 Invert ju.p c~d1tiOD

Cz . 1 Ju.p if the ac~tor c~t_t 1. aero

C3 . 1 JU8p 1f the carry'link CODteDt 1. 1

C4 . 1 Ju.p if te.t .1IDal (pin 10 OD 4004) 1. zero.

~le: ~ 9!.!.

0001 0110 Ju.p 1f accU8Ulator 1. zero or carry . 1

S...r~ cond1t10ft8 CaD be tested e18ut8De0u81y.

The loaJ.c equat1OD ducr1b1a, the coodit1OD for a

jU8p 18 1198 belaw:

J1JHP . C1 . «ACC . 0) . C2 + (Cf . 1) . C3 + "TiiT . C4) +

Cl . «~ - 0) .-Cz+ (cr--;-l) . C3 + m! . C4)

aCIP'rI~ s If JCR i. located OD word. 254 and 255 of a 10M pale.

wben JCR 18 .-cuted and the coDditi- 18 true. prolr-

control 18 traaaferred to the 8-bit addr... on the next

PAle where Ja 18 located.

HD88Inic: ISZ (Iocr_at. indo rep.t.er .kip if .8ro)

lat. word on OPAl 0111 lIaR

2ac1 word on CWA: A.,~~ ~~A,A,

Sy8bol1c: {bIIJ + 1 -'11111. if r..ult. . 0

(PH) -. PH. (PM) --. PH. (~+ 2) -. PL I

if 1'88ul t. ~ 0 (Pa) PH.

A2A2A2A2..,.PM. AlAlAlAl-t PL

Deacript.ioal The coat.eat. of t.he cleai.-r.ed iDcIa re.18t.er 18 iDcr_t.ed

by 1. The accU8Ulat.or 804 carry/liDk are unaffect.ed.

If t.he re.ult. i8 .ero. the next. 1D8t.1'\Ictioa aft.er ISZ i.

--cut If the r..ult. 18 differ_t. fr~ O. pr°81'- cciDt.rol

18 tr8D8fe1'1'ed to the iDat.ructioa locat.ed at. t.he 8 bit.

acldre.. A,zAzA,zA,2. AlAlAlAl oa the .-- Pale (1(»1) where

the ISZ 1D8cructioa i. locat.ed.

Uc&PT1~S : If ISZ 18 locat.d on vorde 254 end 255 of a 10M pea.. wheD

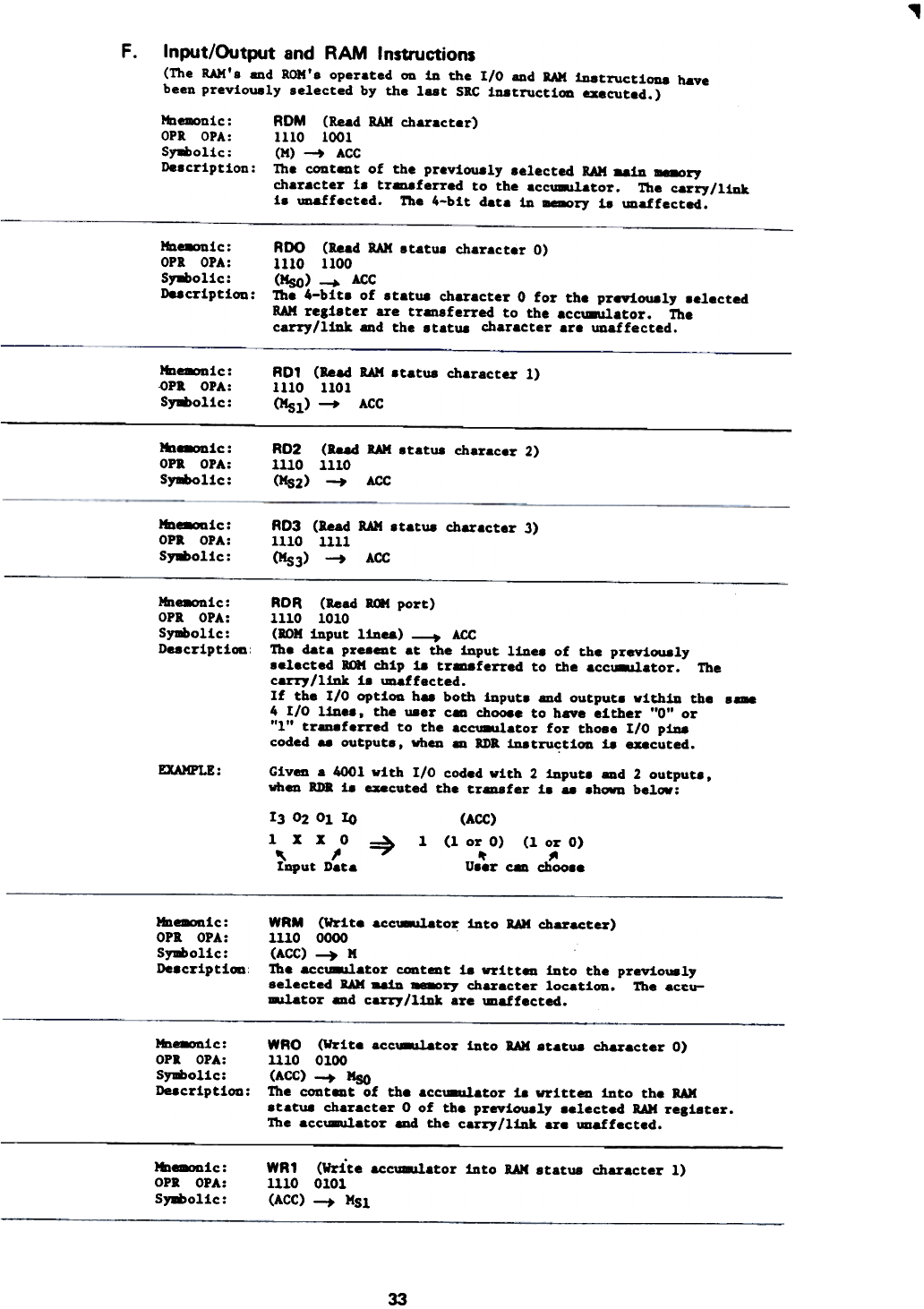

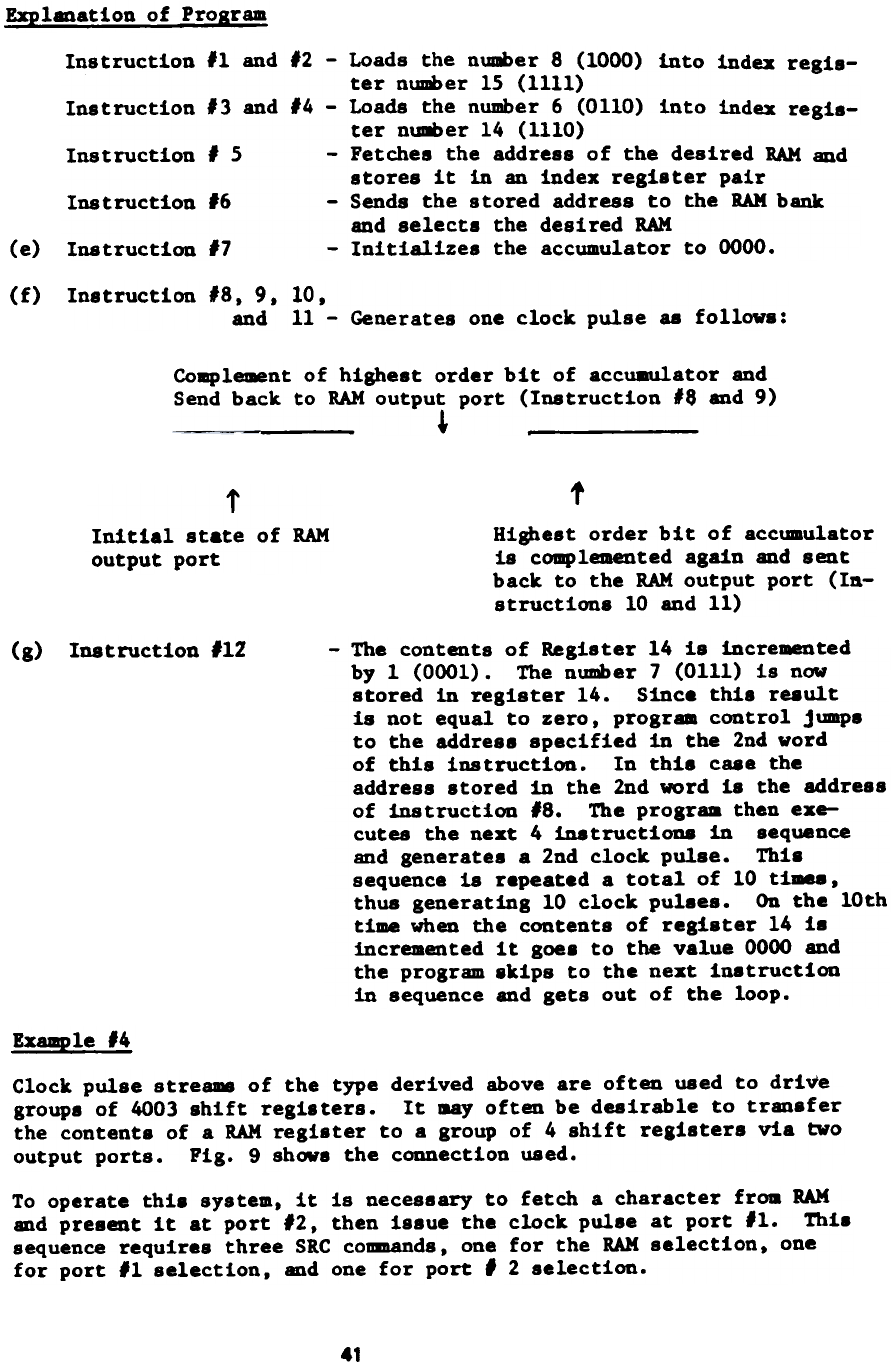

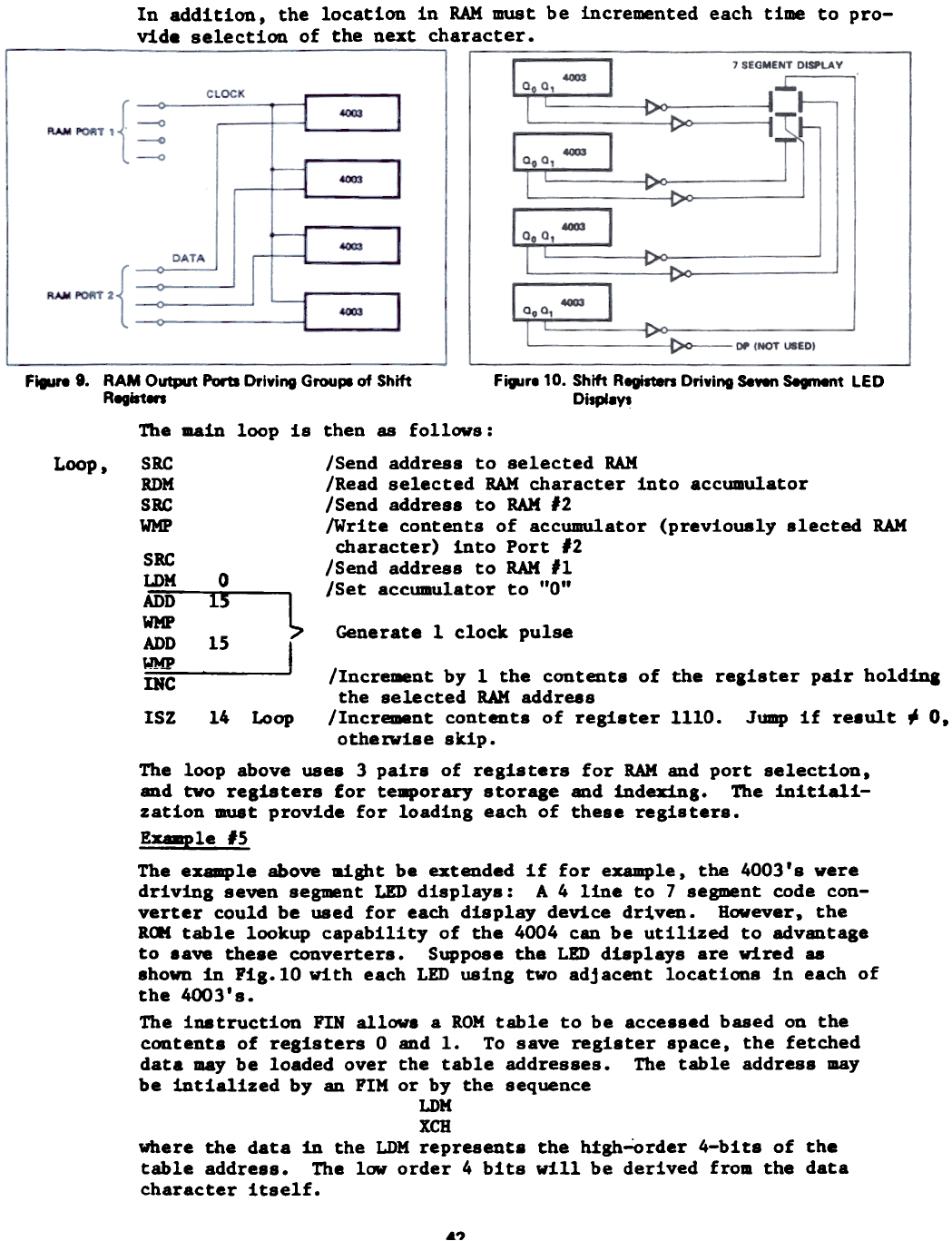

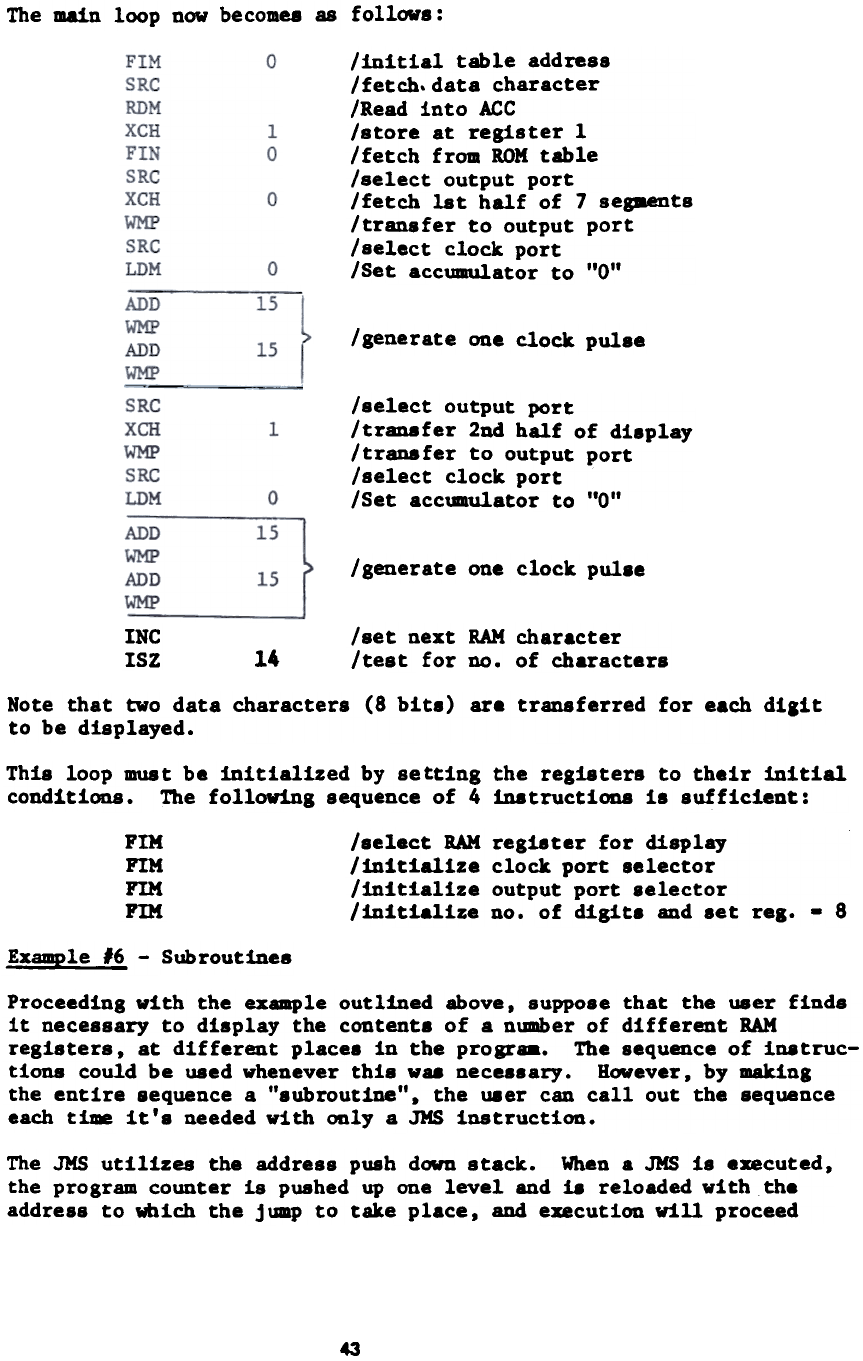

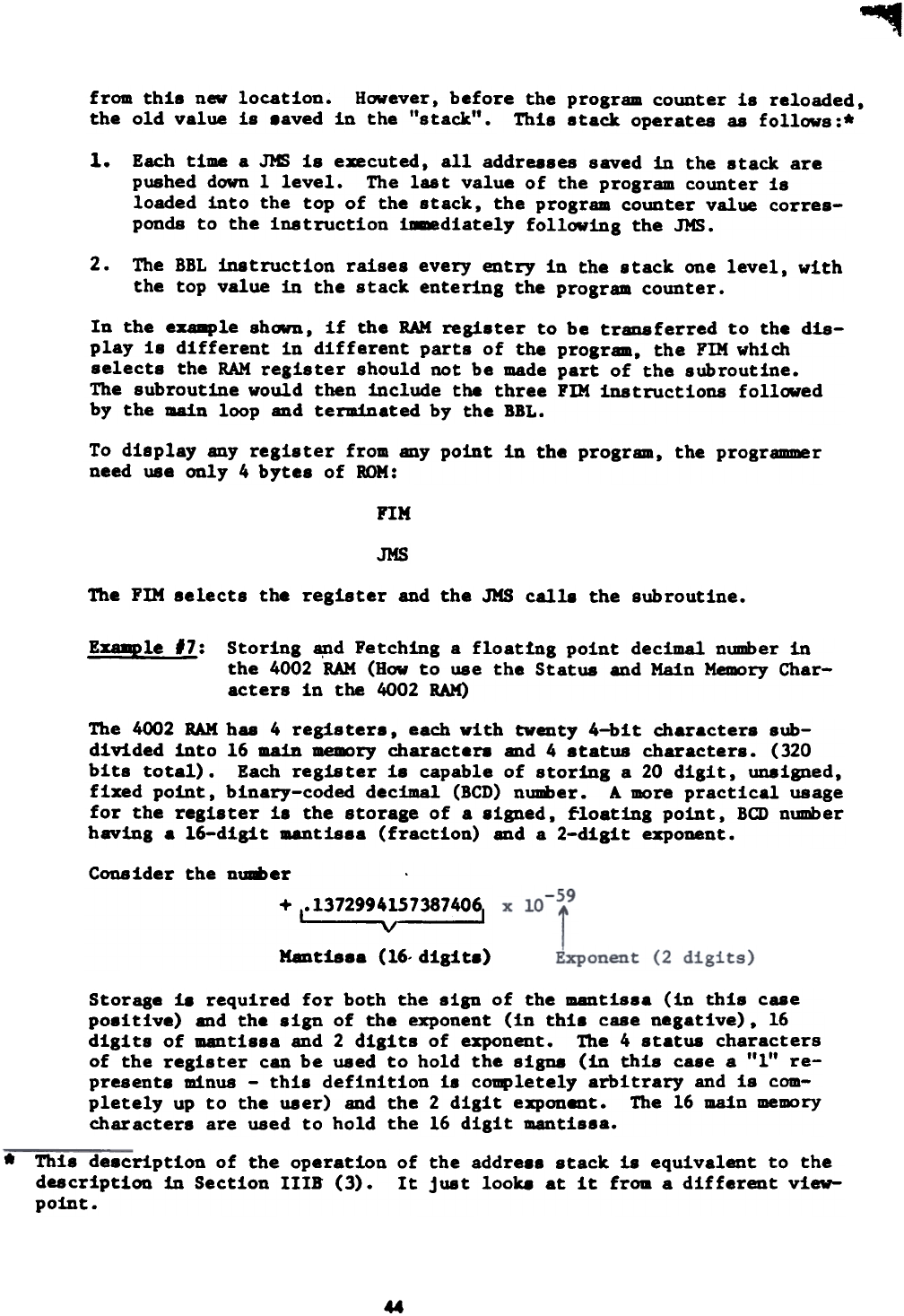

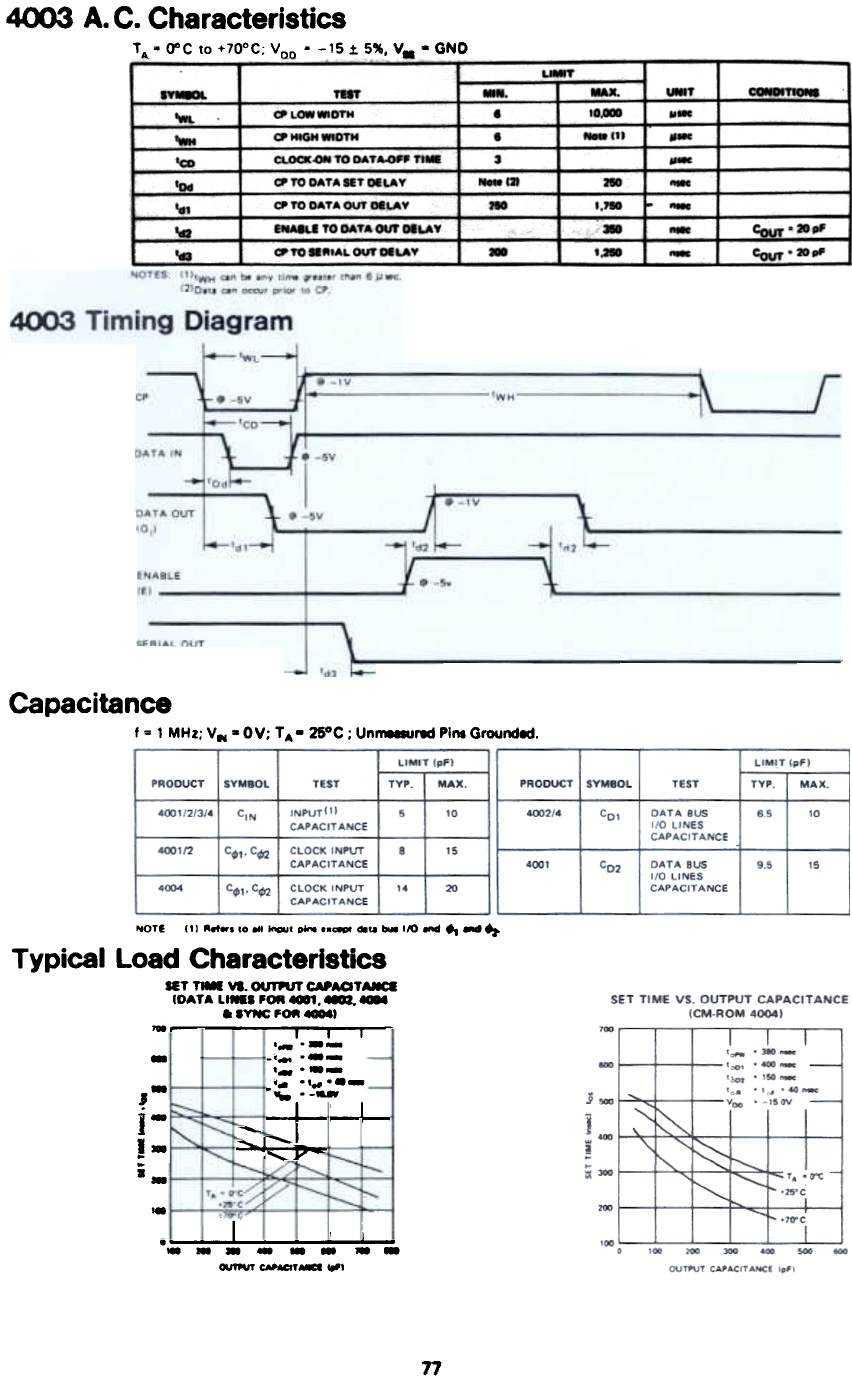

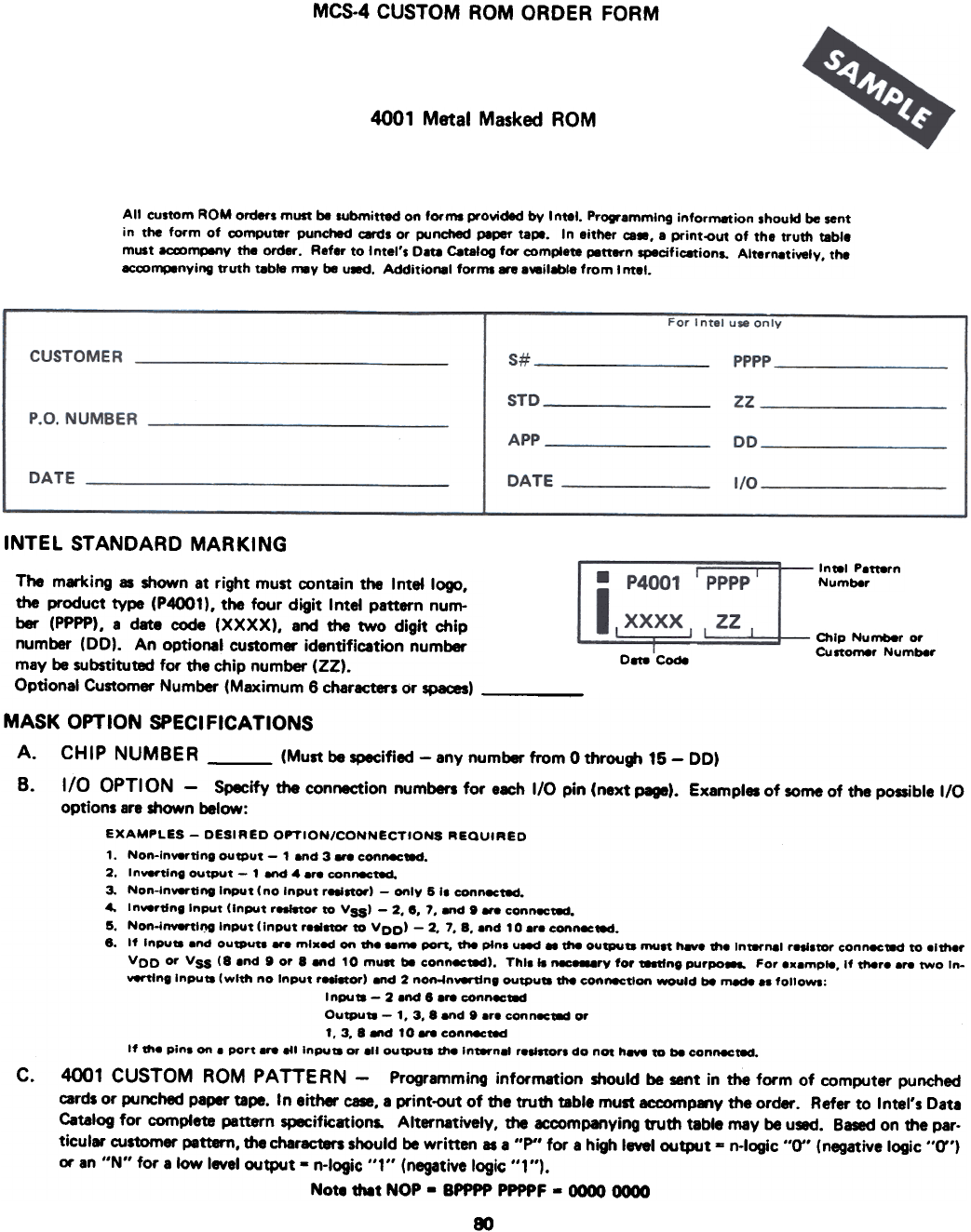

ISZ 18 executed end the r..ulc 18 DOt ..ro. proar.. ooatrol