Sony DVP S500D User Manual CD/DVD SYSTEM Manuals And Guides 98060757

SONY DVD Systems Manual 98060757 SONY DVD Systems Owner's Manual, SONY DVD Systems installation guides

DVP-S505D 98060757

User Manual: Sony DVP-S500D DVP-S500D SONY CD/DVD SYSTEM - Manuals and Guides View the owners manual for your SONY CD/DVD SYSTEM #DVPS500D. Home:Electronics Parts:Sony Parts:Sony CD/DVD SYSTEM Manual

Open the PDF directly: View PDF ![]() .

.

Page Count: 78

DVP-M35/S300/S305/S315/

S500D/S 505D/$715

OPERATION MANUAL

_CD/DVD PLAYER

Contents

1. Outline ....................................................................................................................................6

1-1. Series line-up ...............................................................................................................6

1-2. External appearance diagram ..................................................................................7

1-3,.Internal appearance diagram (top view) ..............................................................8

1-4. Disc drive unit ...........................................................................................................10

1-5. Block diagram ........................................................................................................... 13

2. SIGNAL PROCESSING BLOCK ...................................................................15

2-1. DVD RF FRONT END ..........................................................................................15

2-1-1. Attenuation of OP Output Signals ......................................................................... 16

2-1-2. HPF ........................................................................................................................ 16

2-1-3. RF Front End Processing: IC001 SSI33P3720 ...................................................... 16

2-2. CD RF FRONT END ..............................................................................................19

2-3. RF SIGNAL PROCESSING BLOCK ...............................................................2O

2-4. Decrypt Block ...........................................................................................................21

2-5. AV Decoder Block ...................................................................................................21

2-6. OSD Block .................................................................................................................21

L

2-7,. DNR, Video Encoder Blocks ................................................................................23

2-8. Clock Generation Block ......................................................................................... 24

2-9. AC-3 Decoder Block ...............................................................................................25

2-10. Audio L, R 2ch Signal Block .............................................................................26

2-11. Audio 5. lch Signal Block ....................................................................................27

2-12. DVP-S715 AU-205 Board Block Diagram ....................................................28

2-13. System Control Block ...........................................................................................29

2-14. Interface Control Block ........................................................................................29

3. SERVO BLOCK ...........................................................................................................33

3-1. General Description of Servo Circuits ............................................................... 33

3-1-1. Optical Pickup Control .......................................................................................... 33

3-1-2. Sled Control ........................................................................................................... 33

3-1-3. Spindle Control ...................................................................................................... 33

3-1-4. Tilt Control ............................................................................................................ 33

3-I-5. Disc Loading and Chucking .................................................................................. 33

3-1-6. Disc Judgment ....................................................................................................... 33

3-2. Servo Operation at DVD Play .............................................................................. 34

3-2-1. Optical Pickup Control .......................................................................................... 34

3-2-2. Sled Control ........................................................................................................... 41

3-2-3. Spindle Control ...................................................................................................... 43

3-2-4. Tilt Control ............................................................................................................ 44

3-3. Servo Operation at CD and Video CD Playing ...............................................46

3-3-1. Optical Pickup Control .......................................................................................... 46

3-3-2. Sled Control ........................................................................................................... 50

3-3-3. Spindle Control ...................................................................................................... 50

3-3-4. Tilt Control ......................................................................... :.................................. 50

3-4. Disc Loading and Chucking ..................................................................................50

3-4-1. Motor Driver .......................................................................................................... 51

3-4-2. Tray Position Detection ......................................................................................... 51

3-5. Differentiation of Disk Type ................................................................... 52

3-5-1. CD/DVD Differentiation ........................................................................................ 52

3-5-2. SL/DL Differentiation ............................................................................................ 52

3-5-3. Differentiation ............ i........................................................................................... 52

3-6. Block Diagram (Servo) ...........................................................................................53

4. IC PIN DESCRIPTION ..........................................................................................55

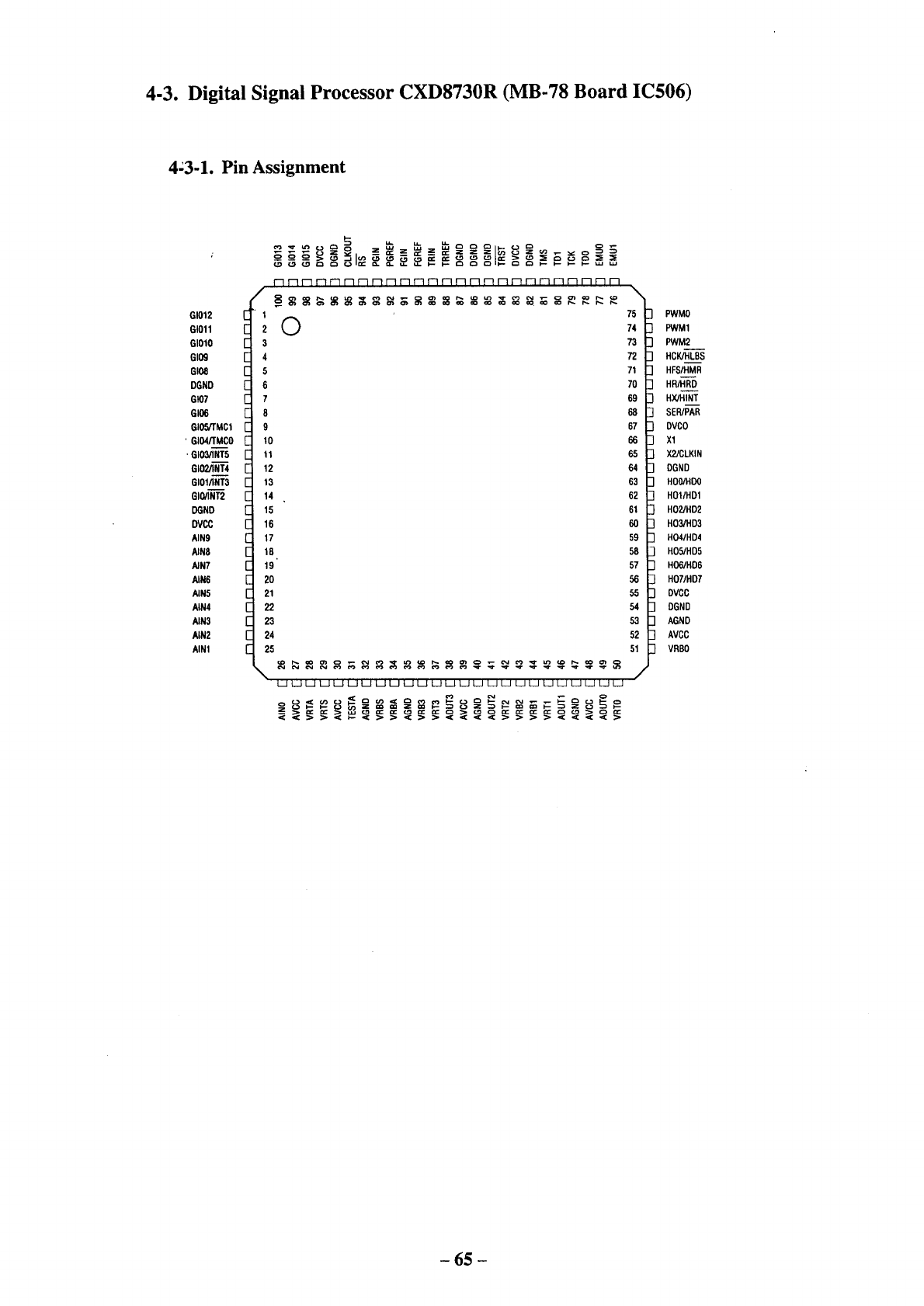

4-1. ARP CXD1865R (IC806 on MB-80 board) .....................................................55

4-1-1. Block Diagram .................................................................................... ................... 55

4-1-2. Pin Functions ....................................................................................... '.................. 57

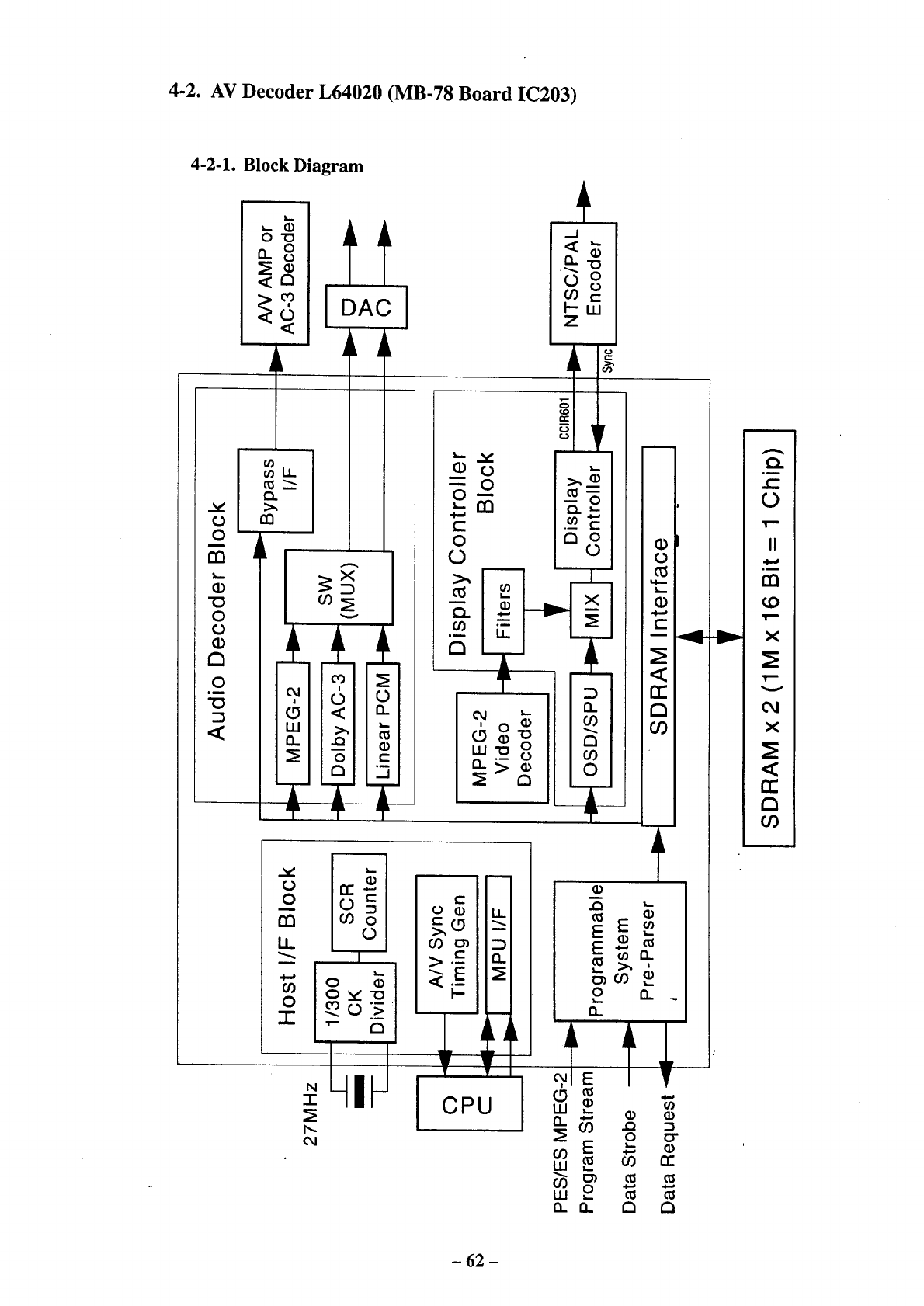

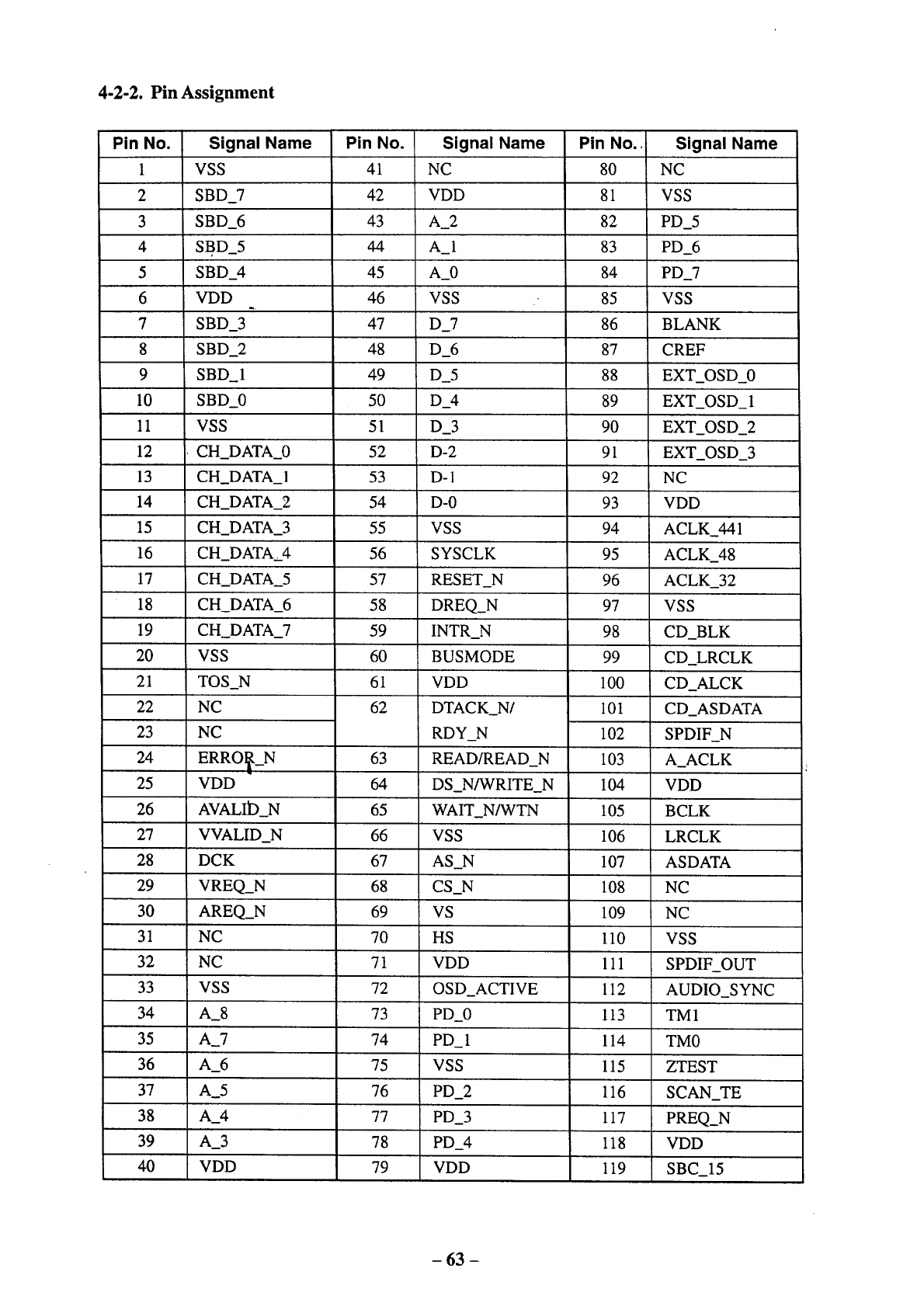

4-2. AV Decoder L64020 (IC203 on MB-78 board) ..............................................62

4-2-1. Block Diagram ....................................................................................................... 62

4-2-2. Pin Assignment ...................................................................................................... 63

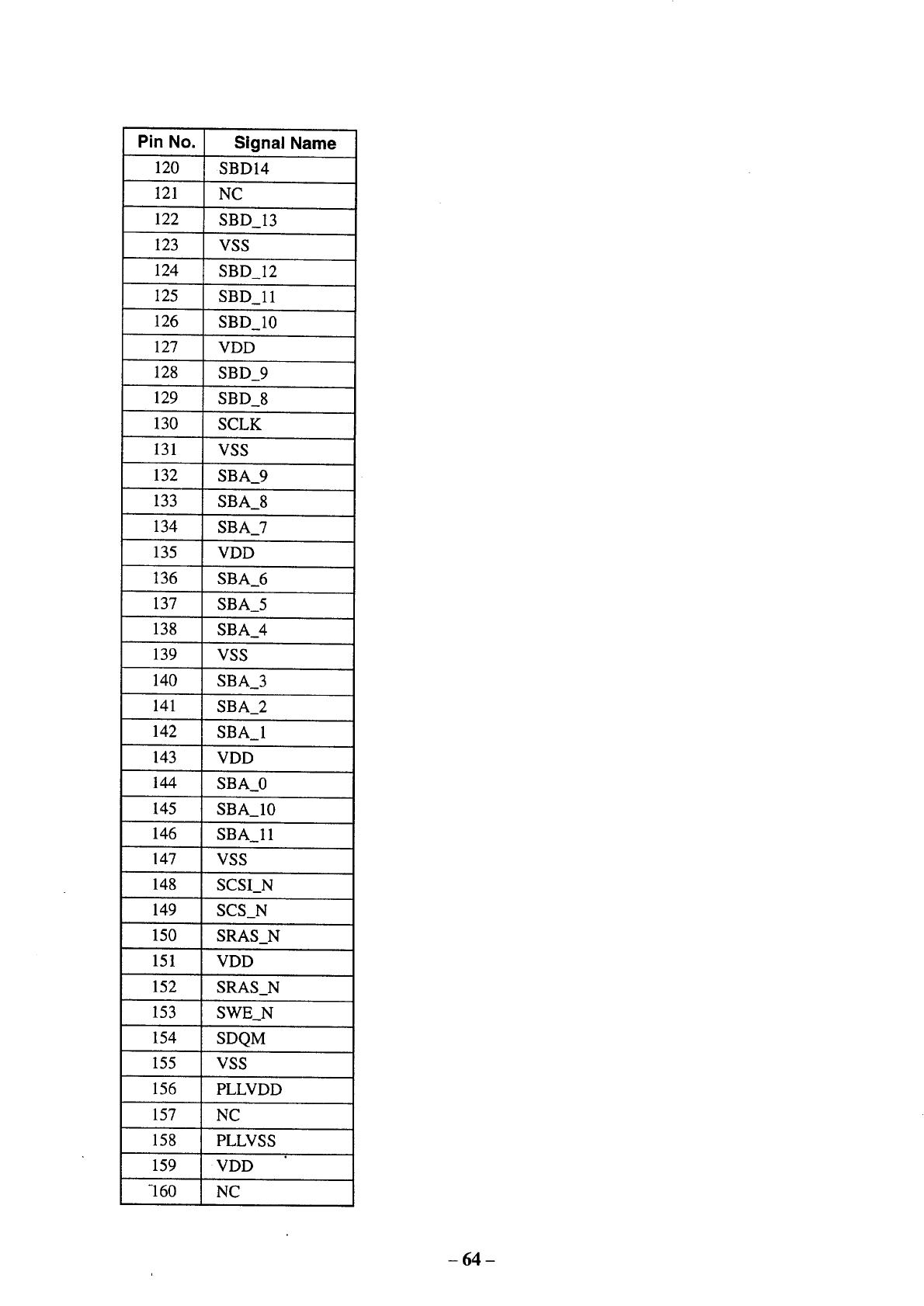

4-3. Digital Signal Processor CXD8730R (1C506 on MB;.78 board) ............... 65

4-3:1. Pin Assignment ...................................................................................................... 65

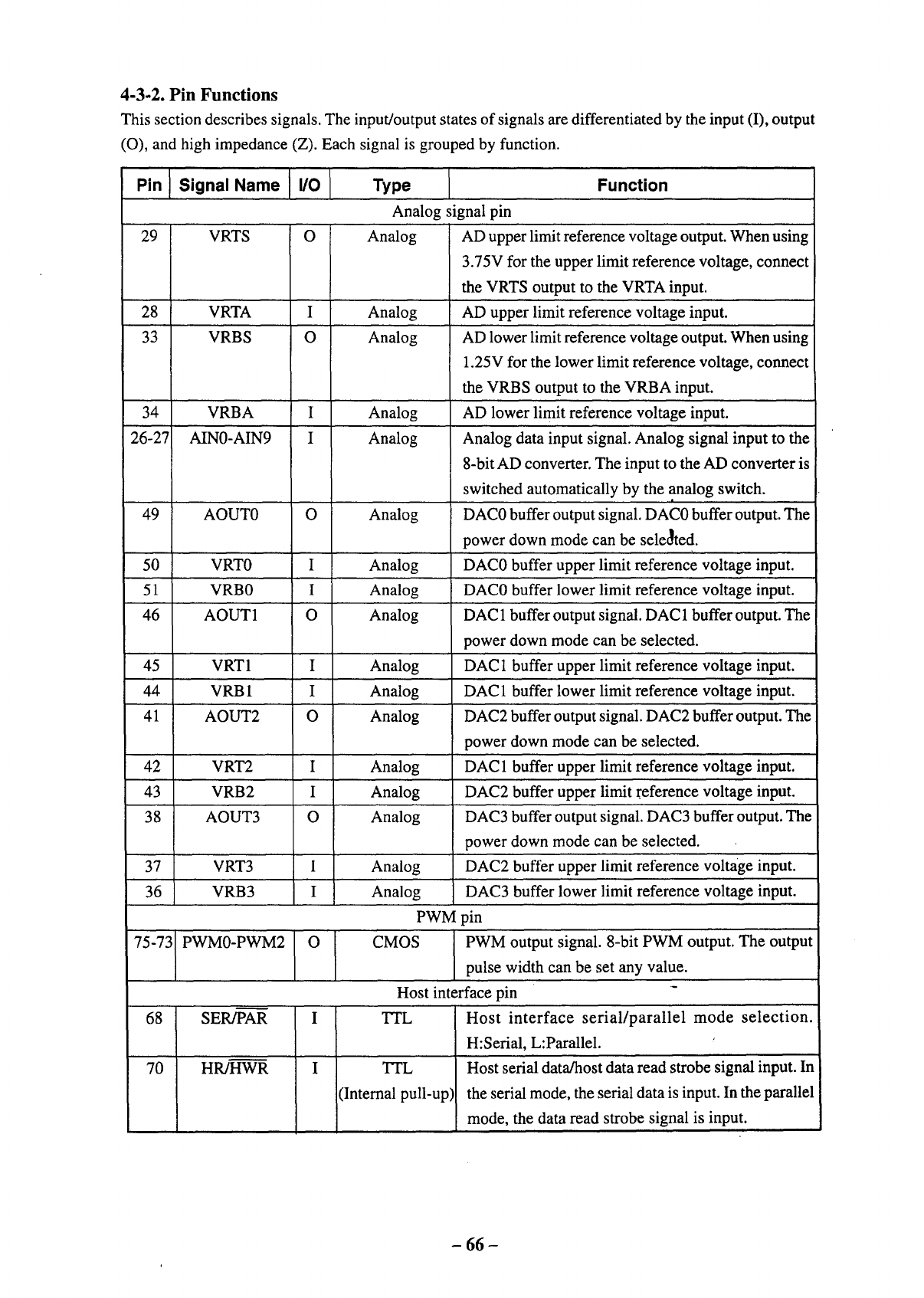

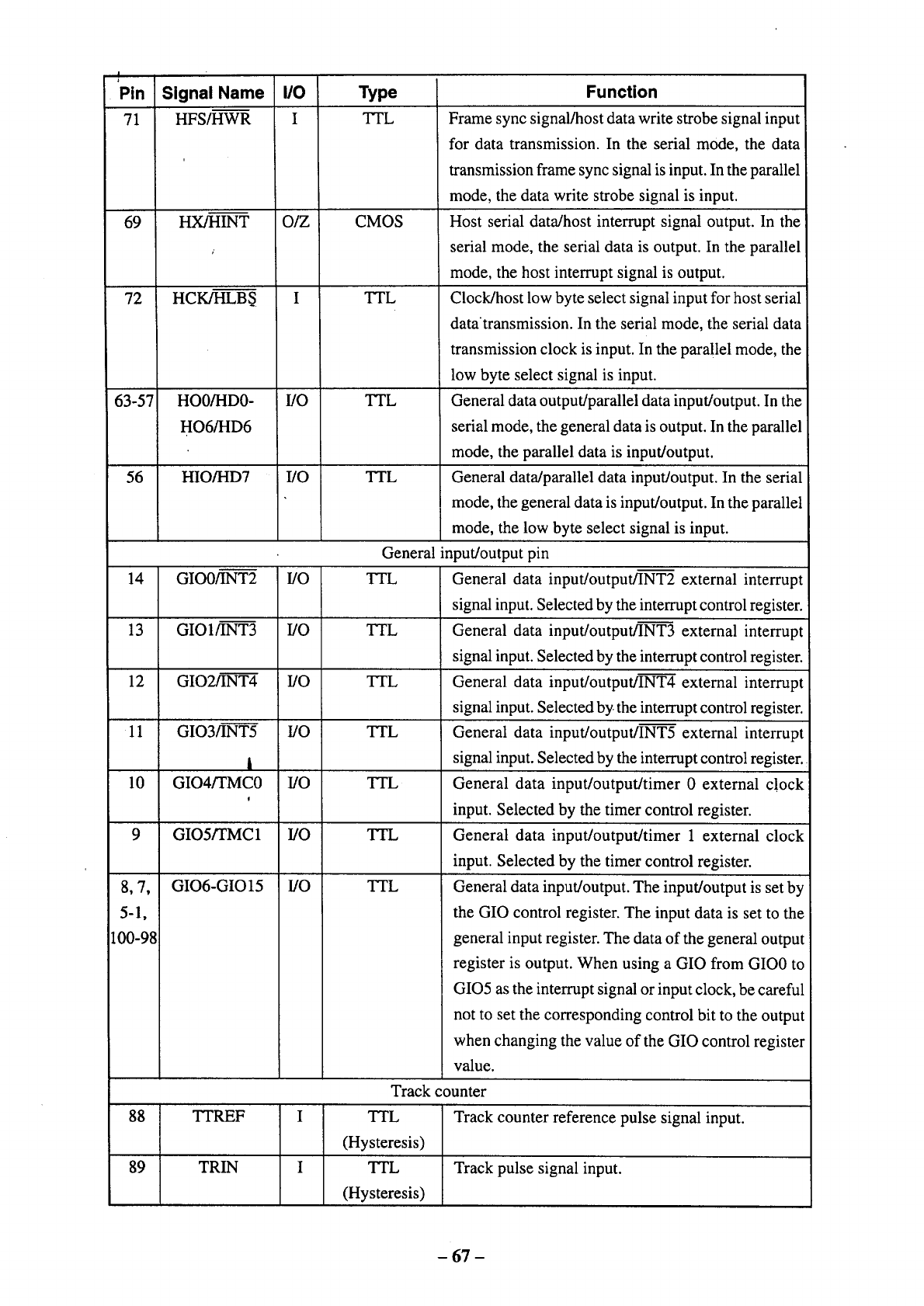

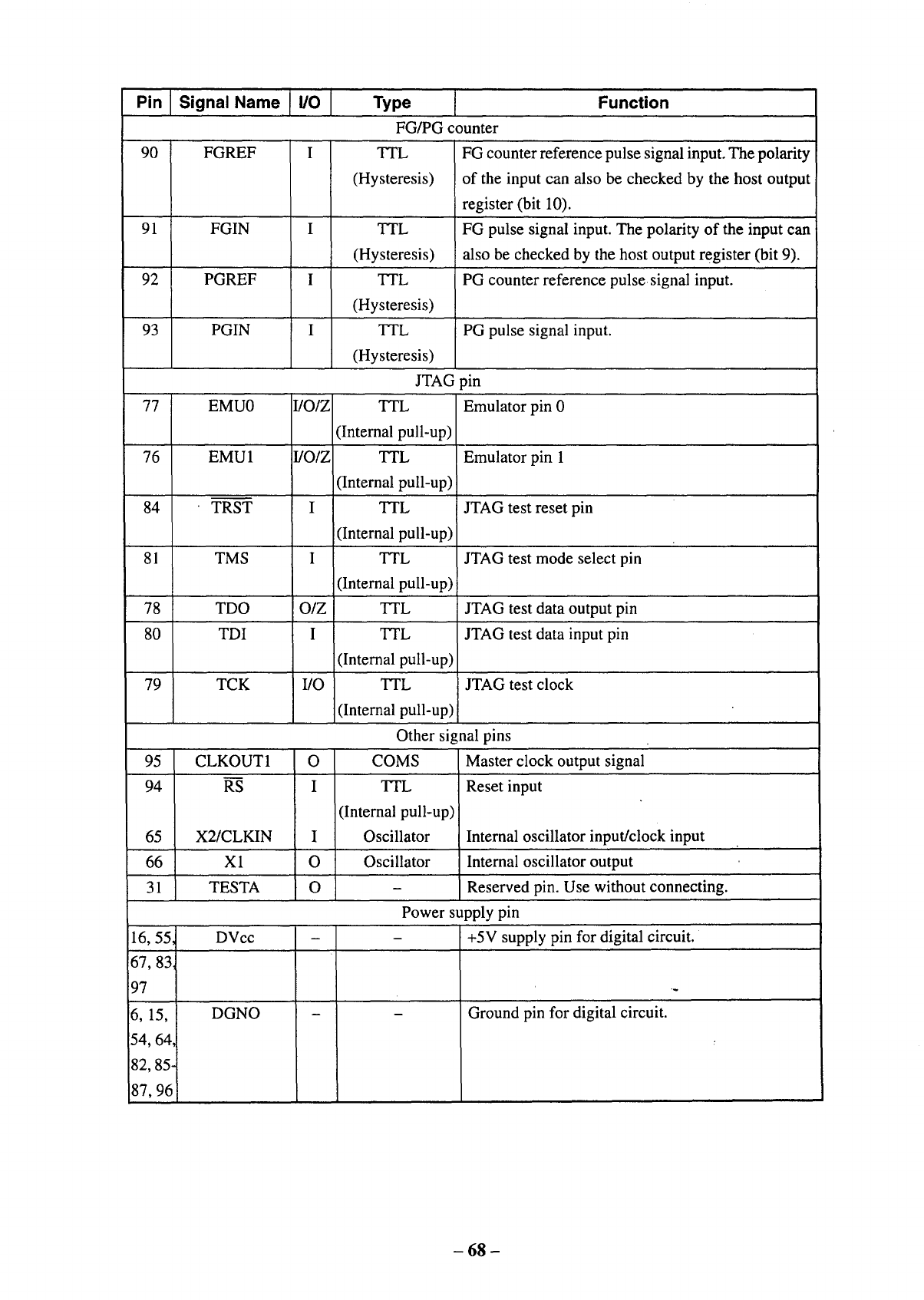

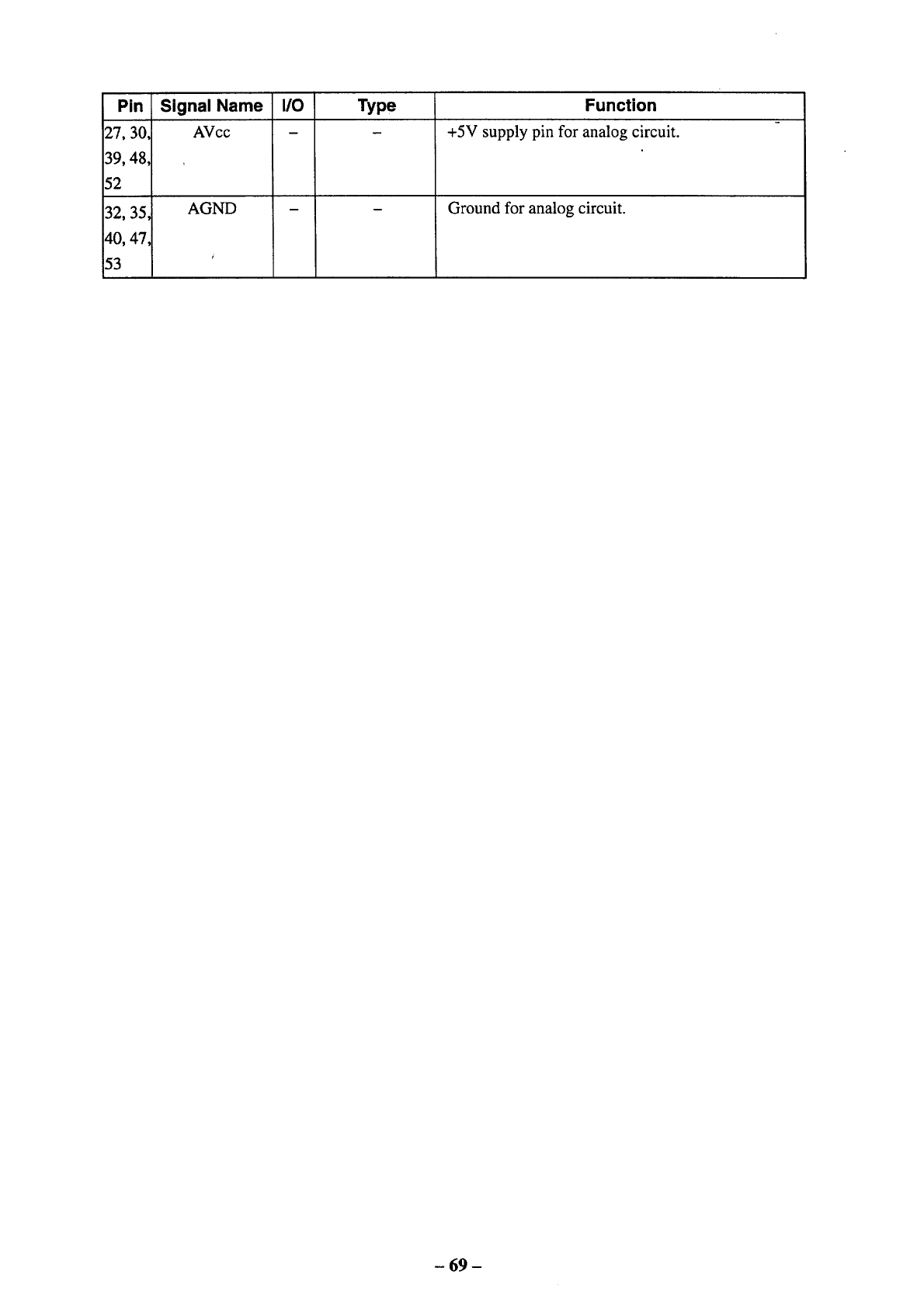

4-3-2. Pin Functions ......................................................................................................... 66

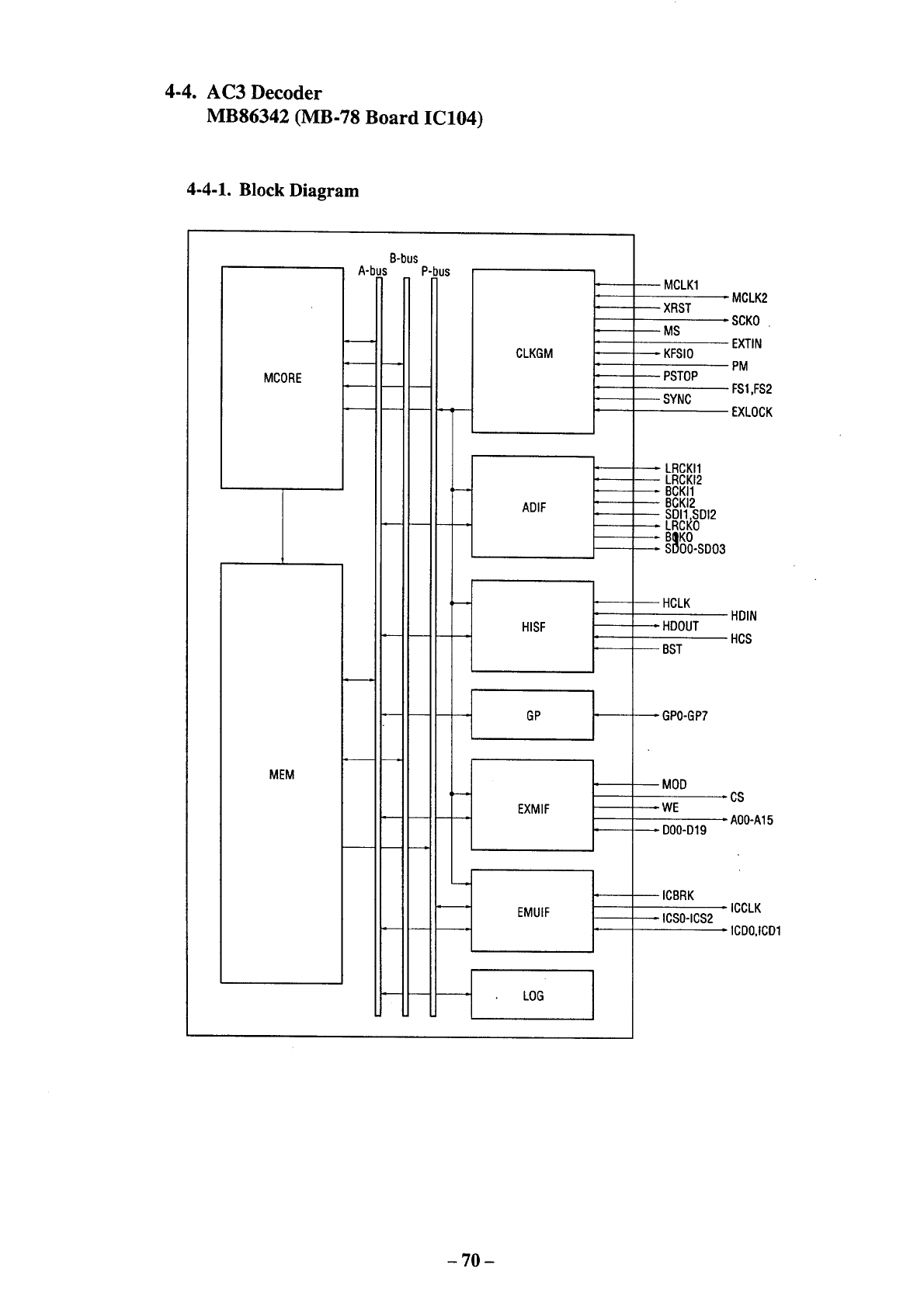

4-4. AC-3 Decoder MB86342 (IC104 on MB-78 board) ......................................70

4-4-1. Block Diagram ....................................................................................................... 70

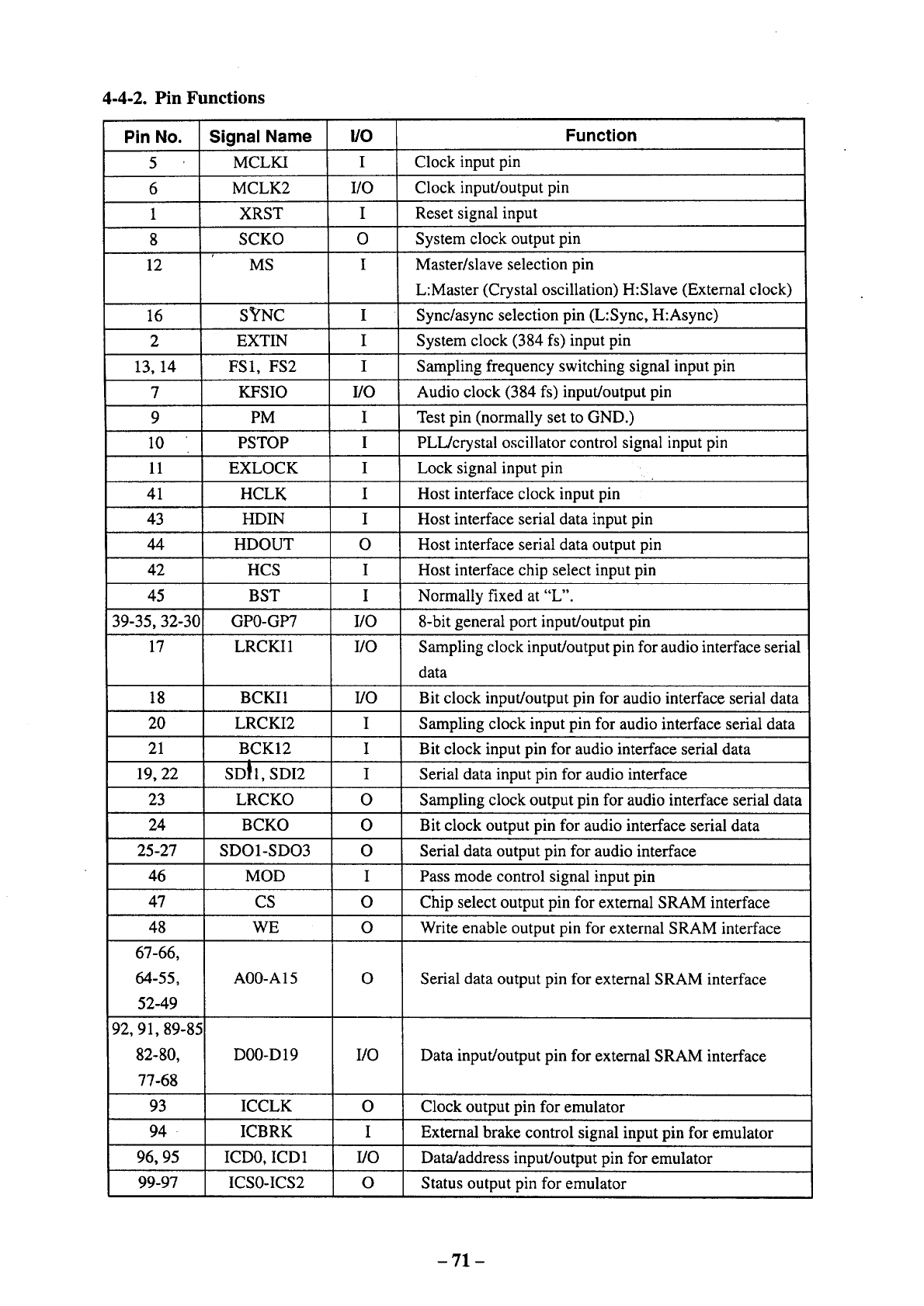

4-4-2. Pin Functions ......................................................................................................... 71

-4-

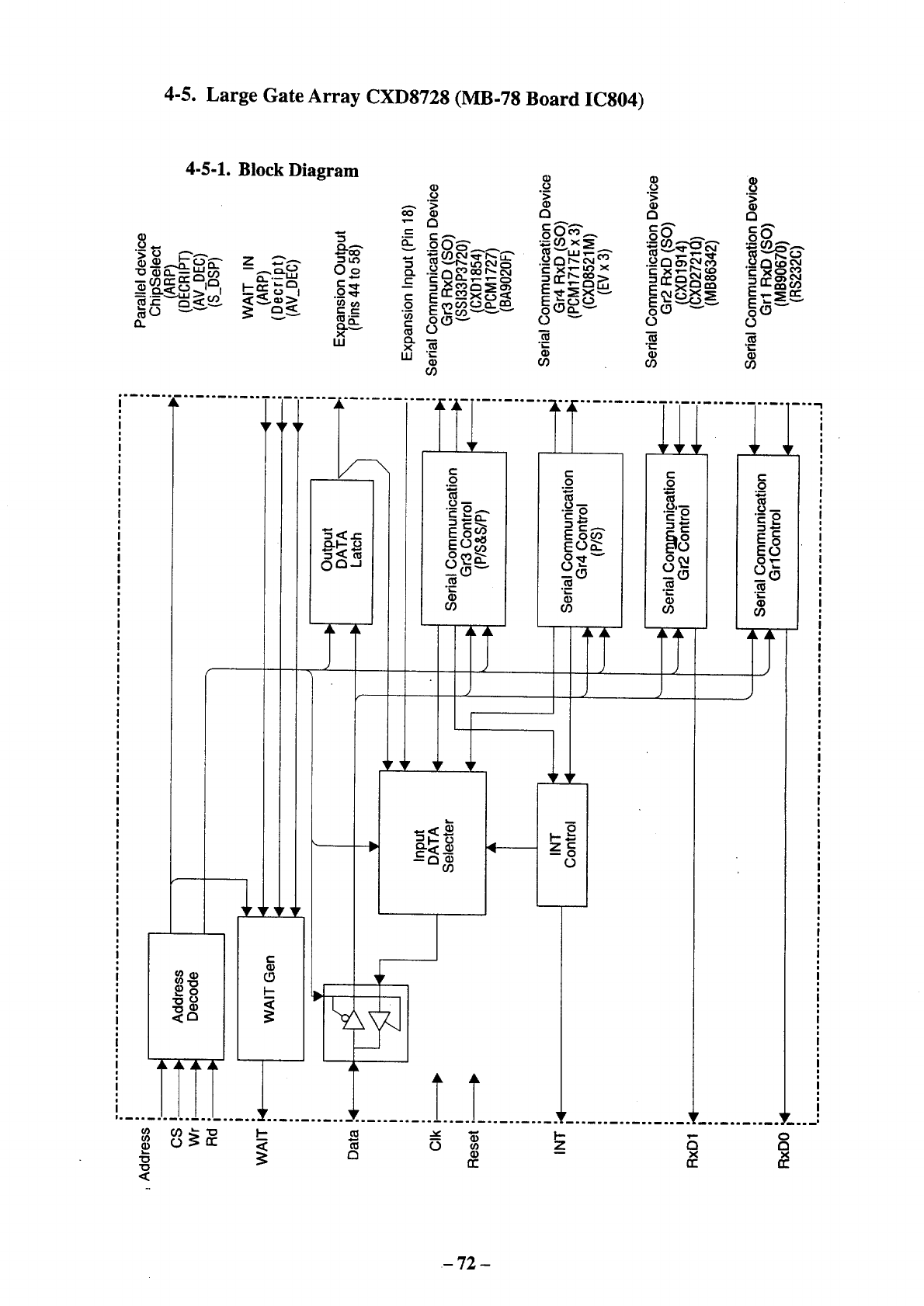

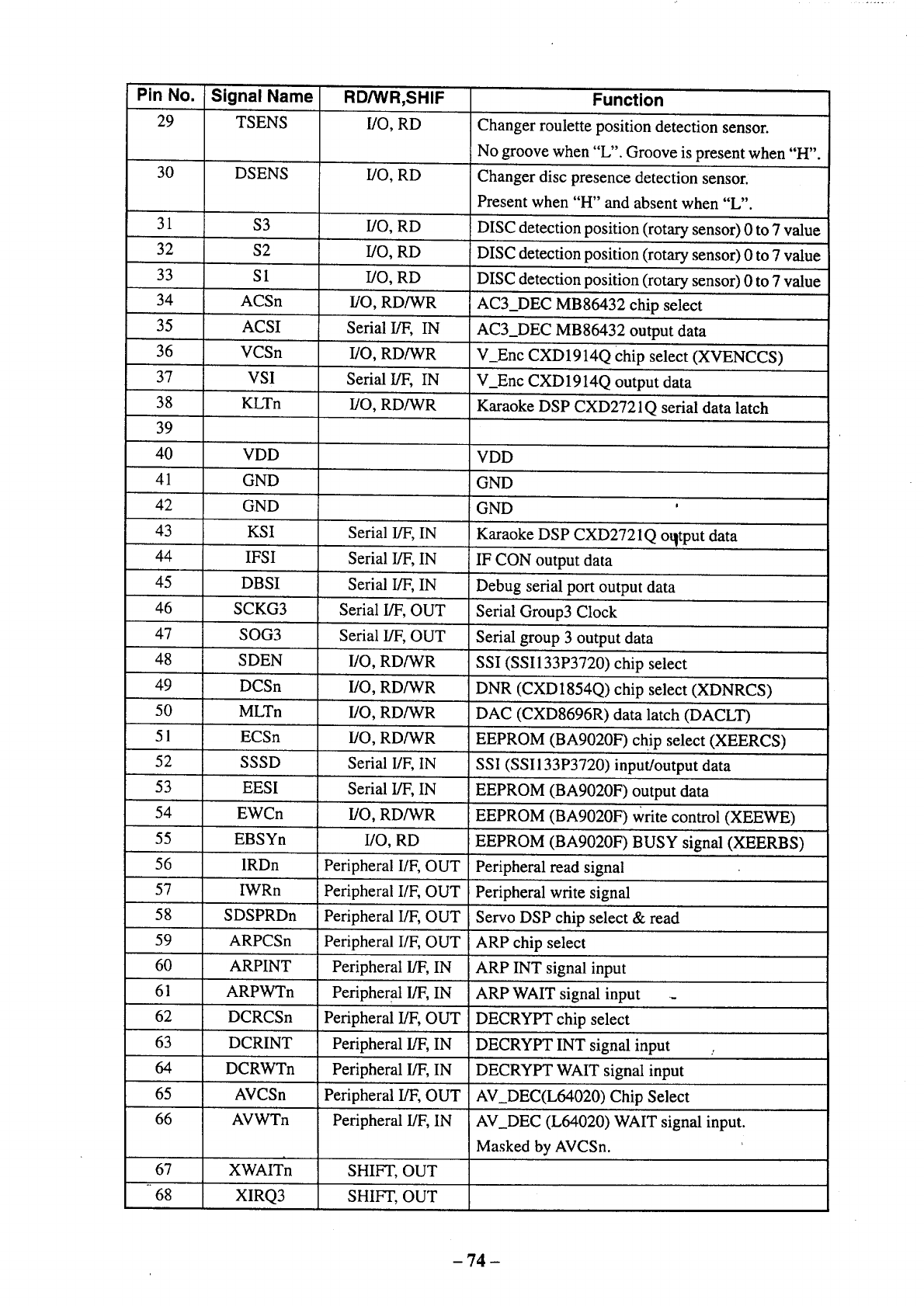

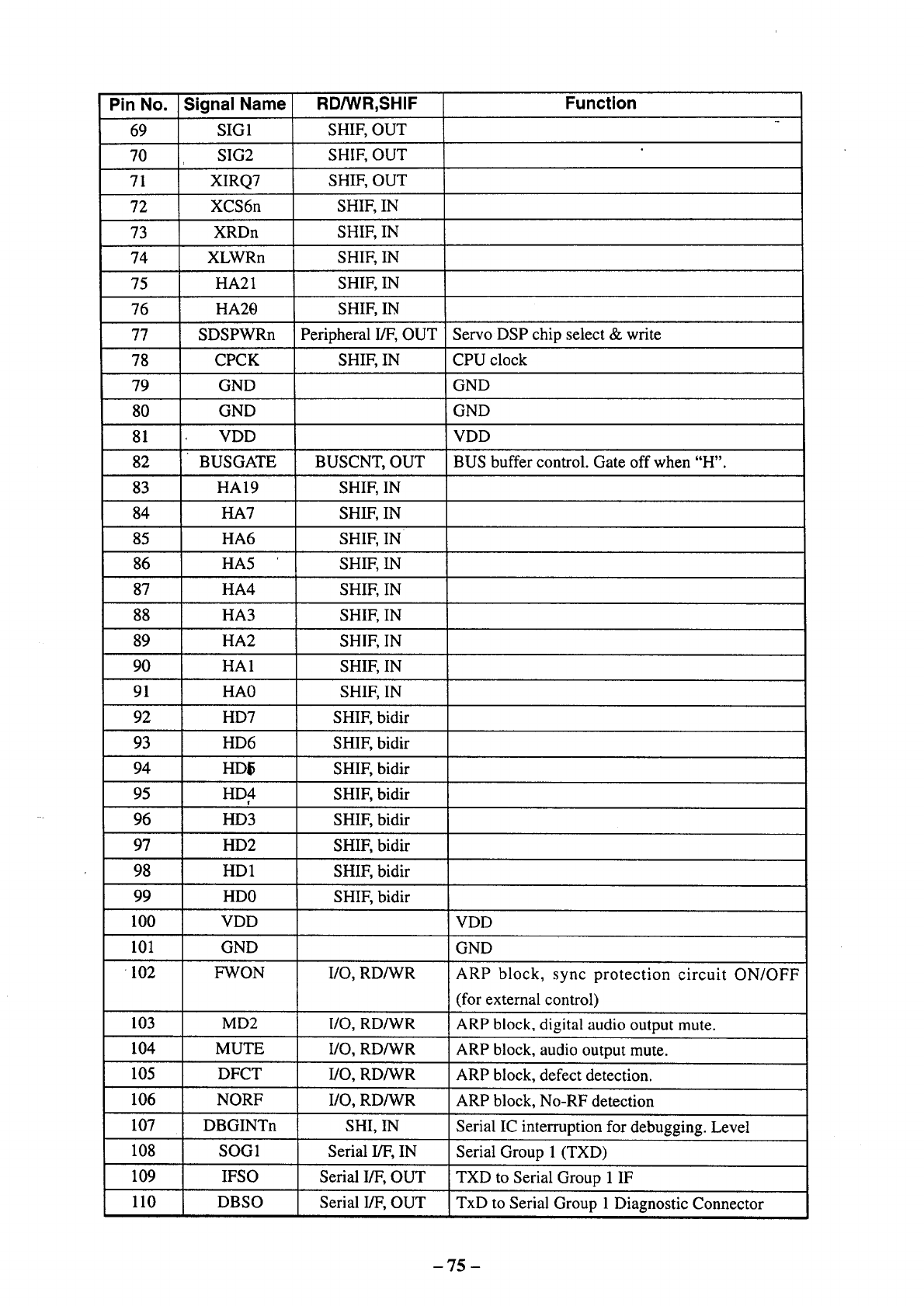

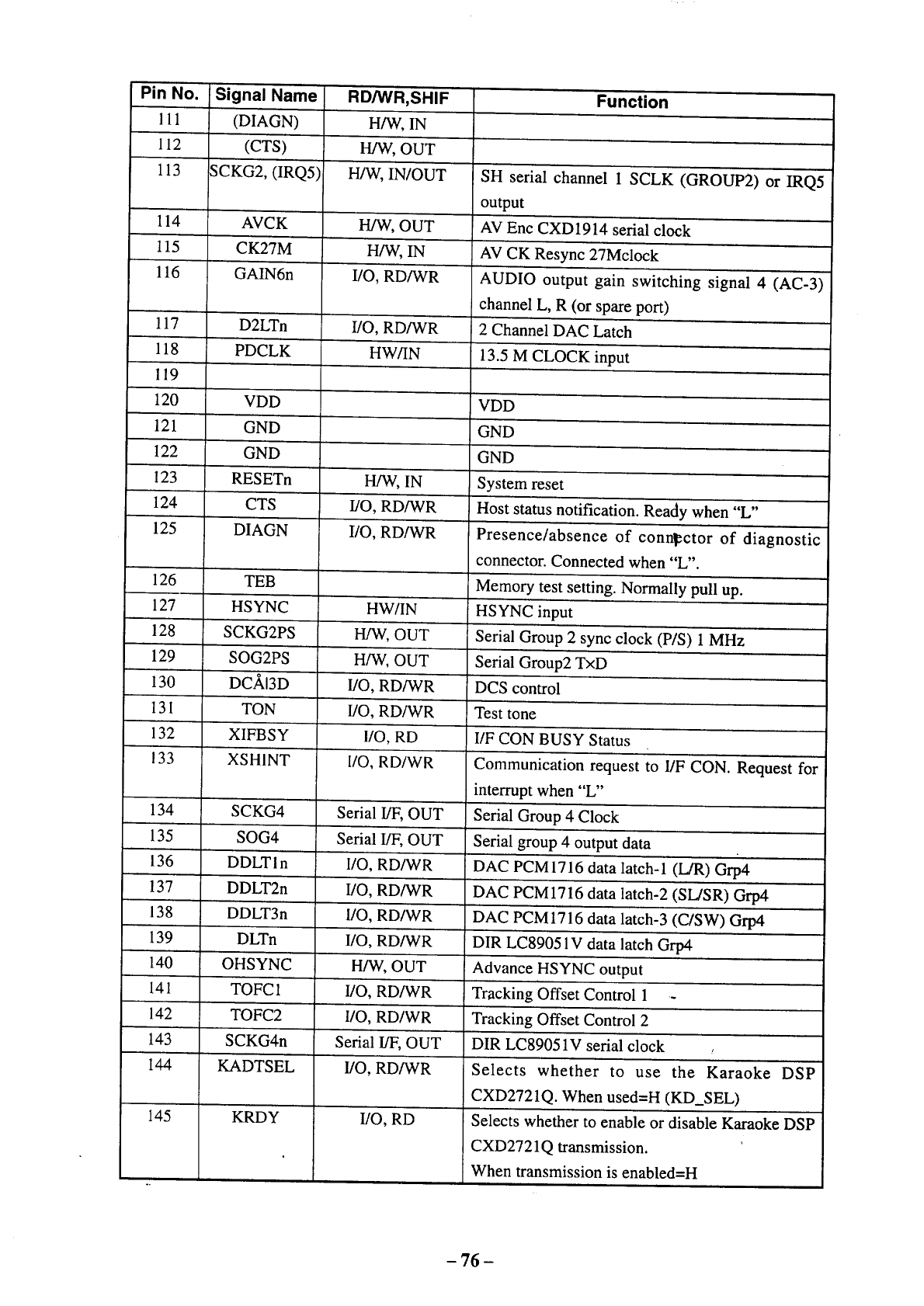

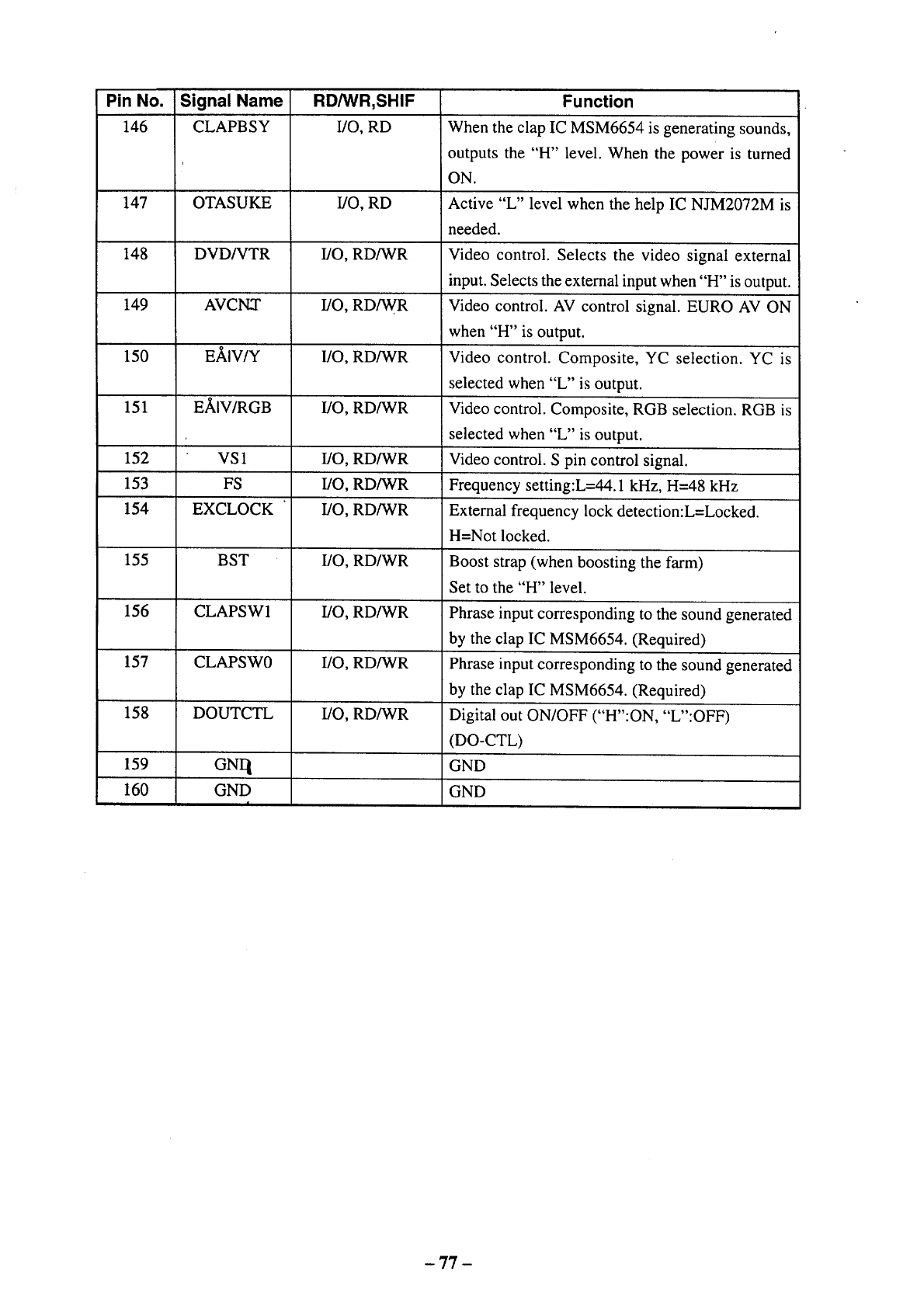

4-5. Large Gate Array CXD8728 (IC804 on MB-78 board) ................................ 72

4-5-1. Block Diagram .................................................................................................... 7..72

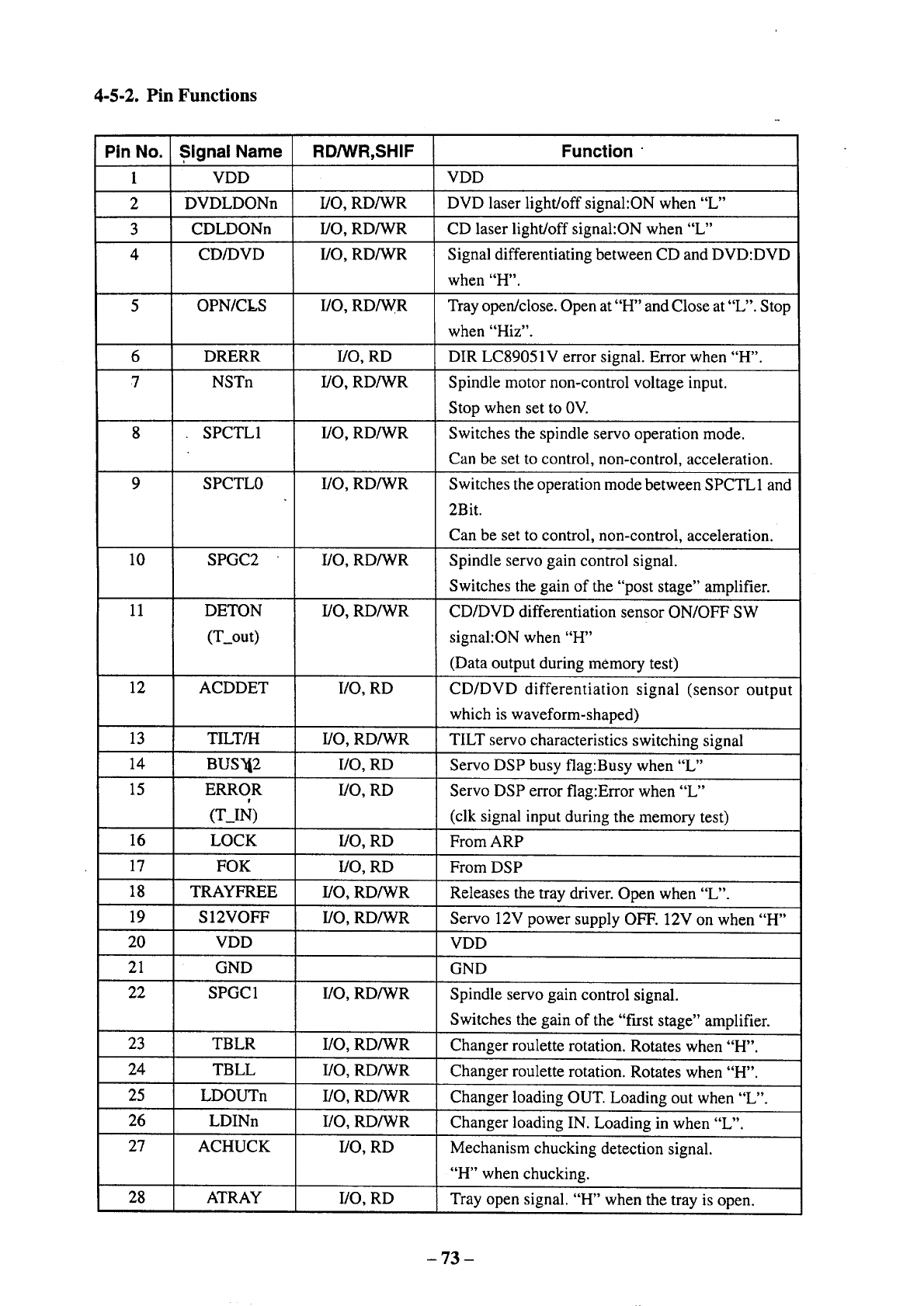

4-5-2. Pin Functions ........................................................................................................ 73

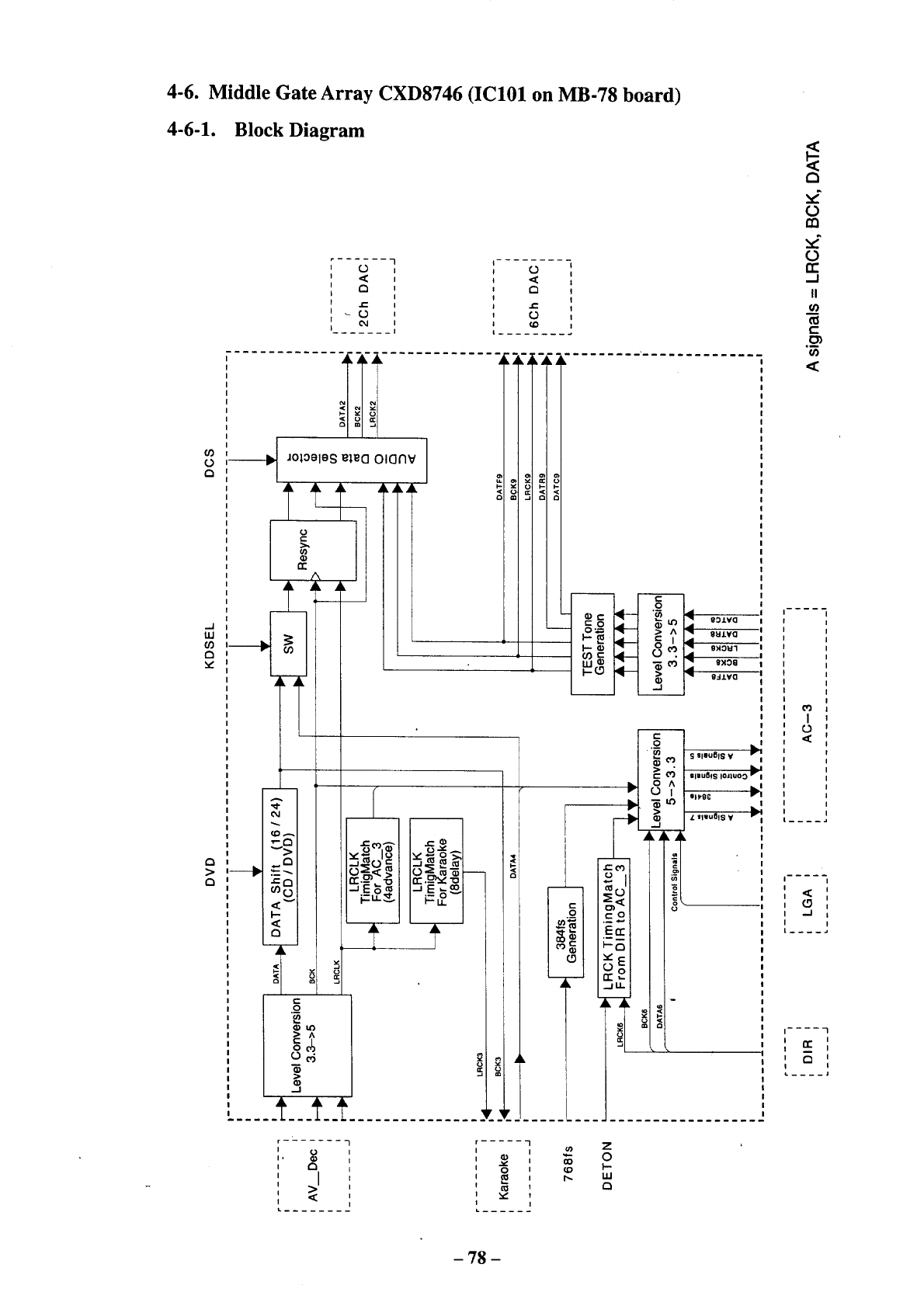

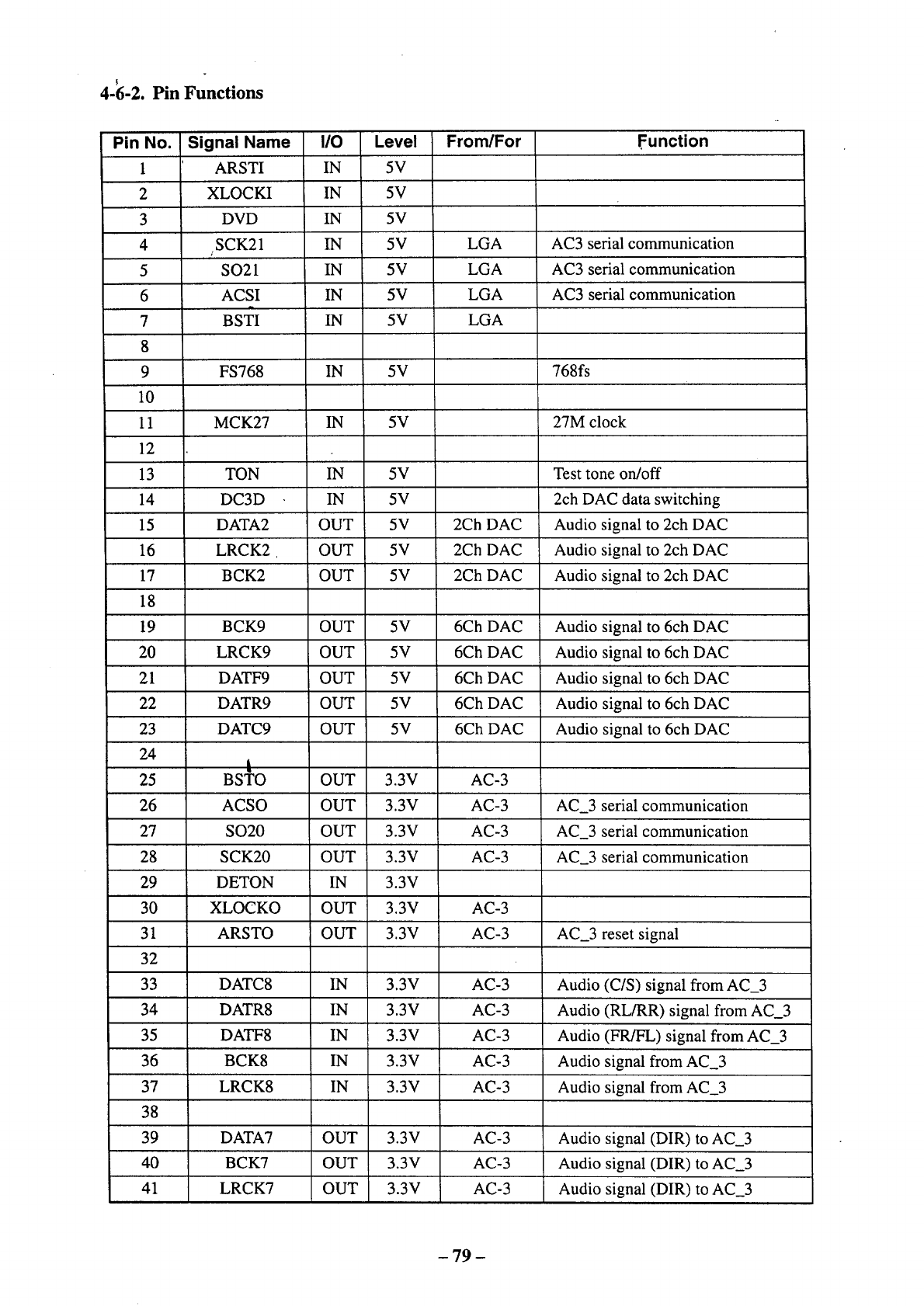

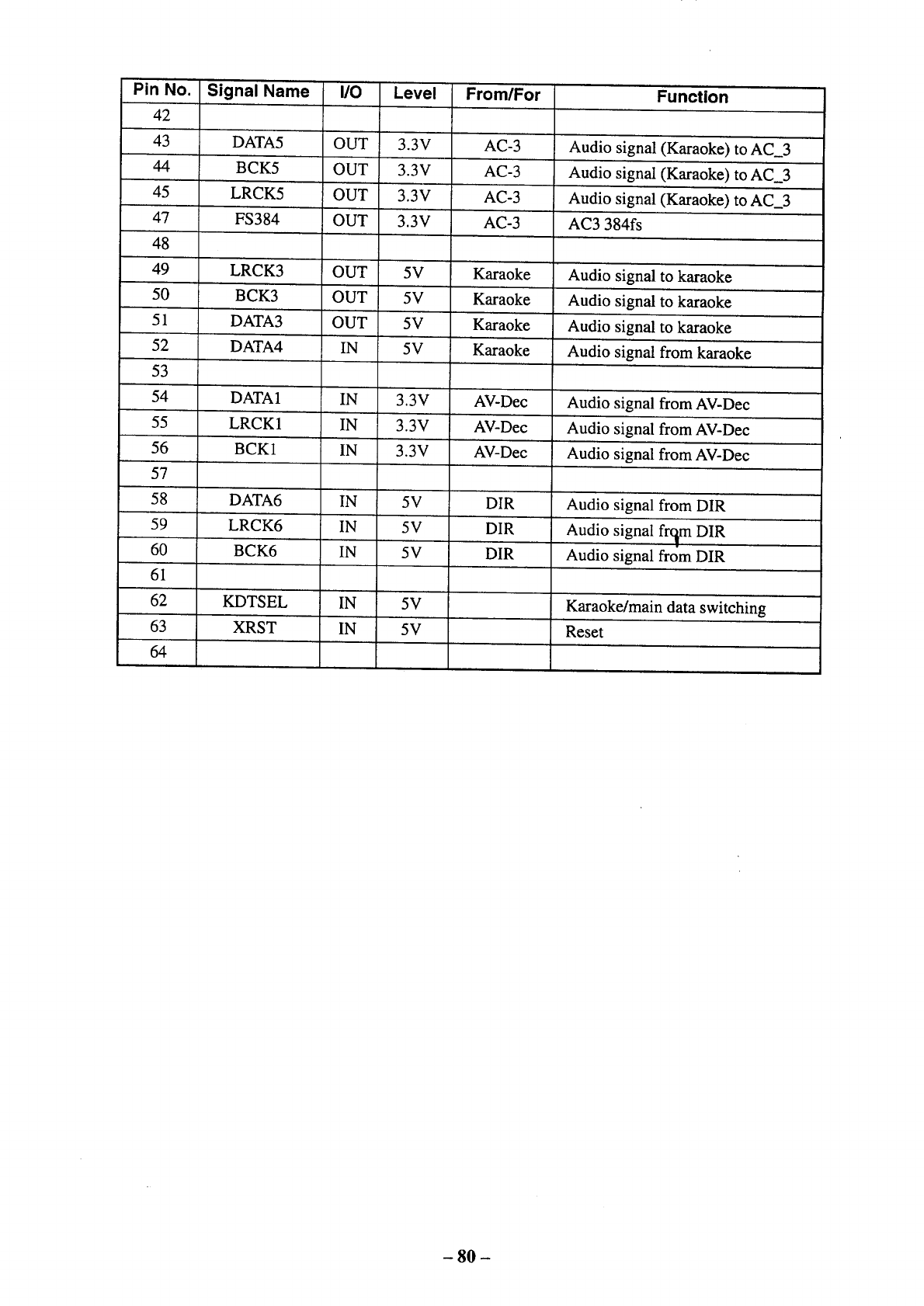

4-6. Middle Gate Array CXD8746 (IC 101 on MB-78 board) ............................. 78

4-6-1. Block Diagram ....................................................................................................... 78

4-6-2. Pin Functions ......................................................................................................... 79

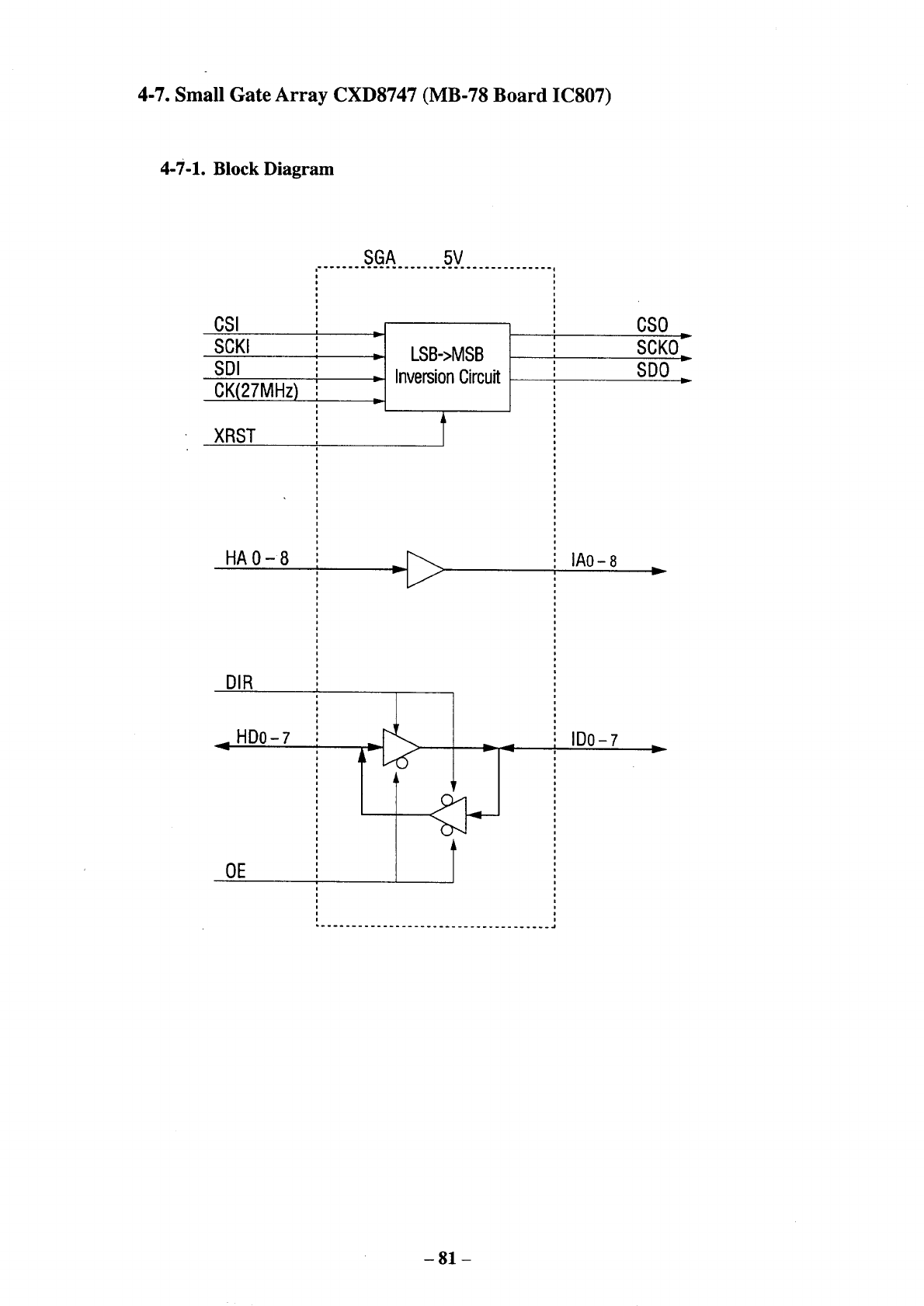

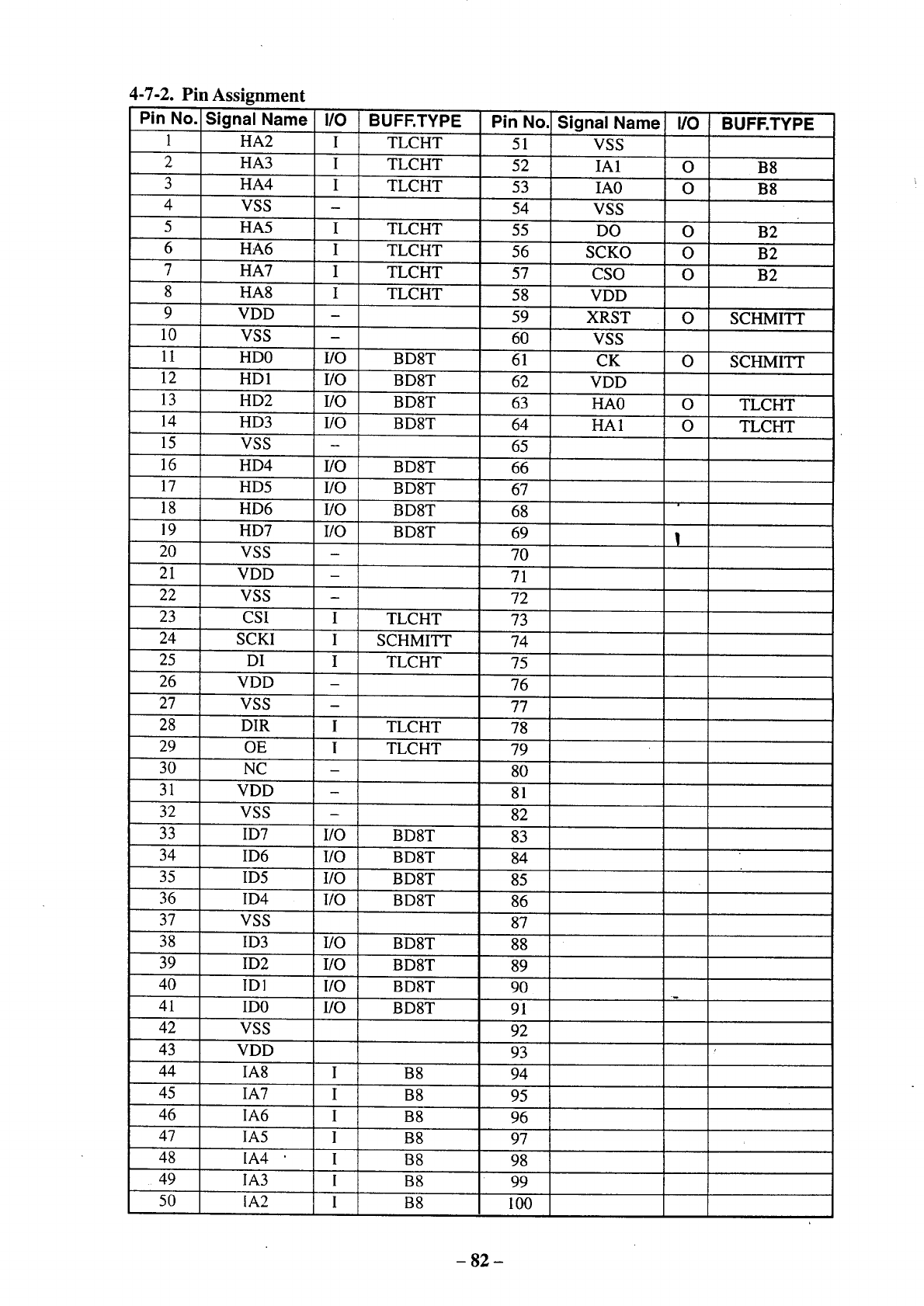

'4-7. Small Gate Array CXD8747 (IC807 on MB-78 board) ............................... 81

4-7-1. Block Diagram ....................................................................................................... 81

4-7-2. Pin Assignment ..................................... ............................ :.................................... 82

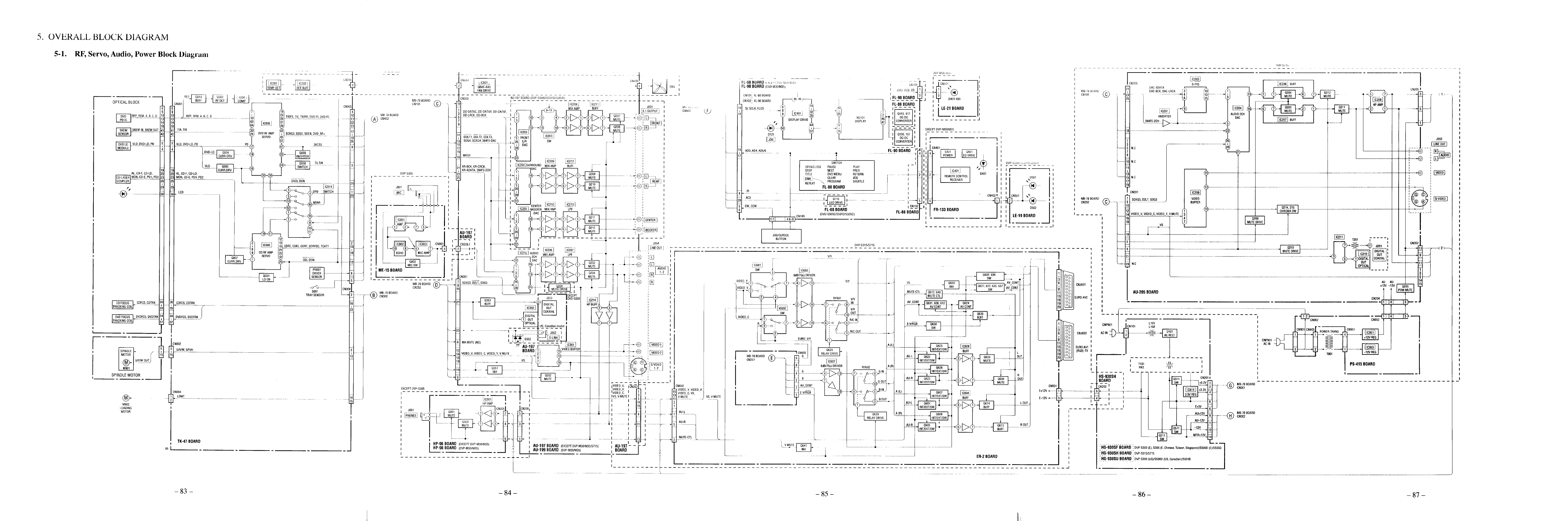

5. OVERALL BLOCK DIAGRAM ......................................................................83

5-1. RF, Servo, Audio, Power Block Diagram ......................................................... 83

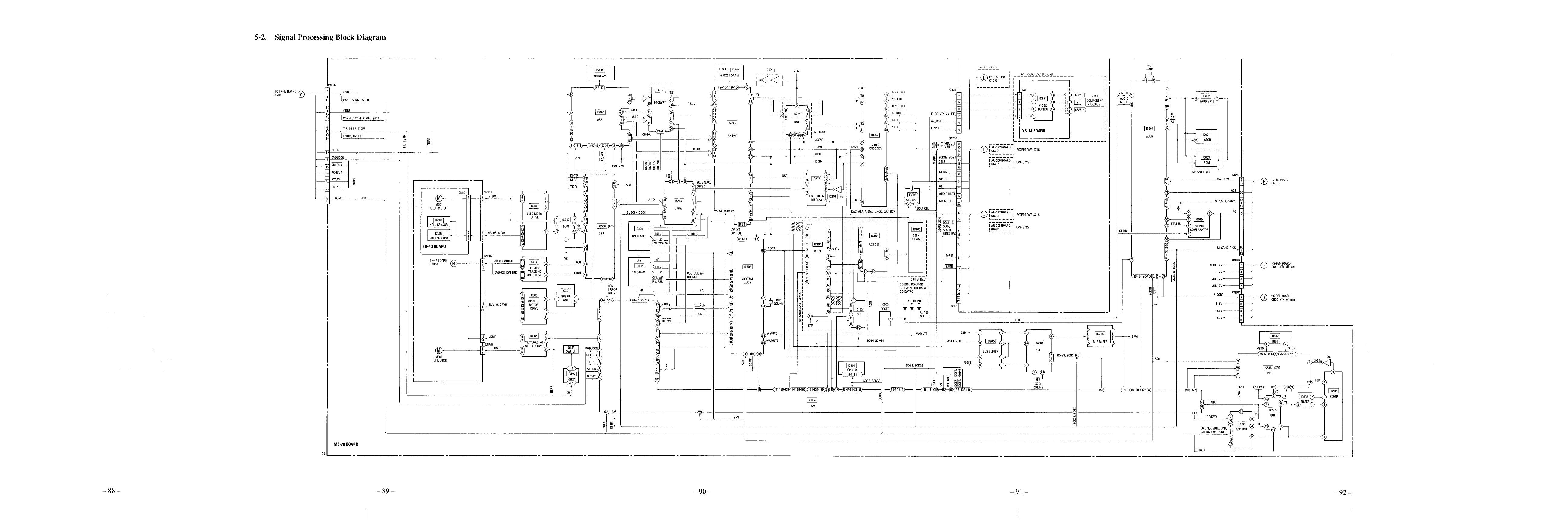

5-2. Signal Processing Block Diagram ....................................................................... 89

5

1. Outline

This guidebook describes the DVD-Video.

It also describes the functions not used in the DVP Series.

For the functions used in the DVP Series, refer to Secions 2 to 5, or Service Manual.

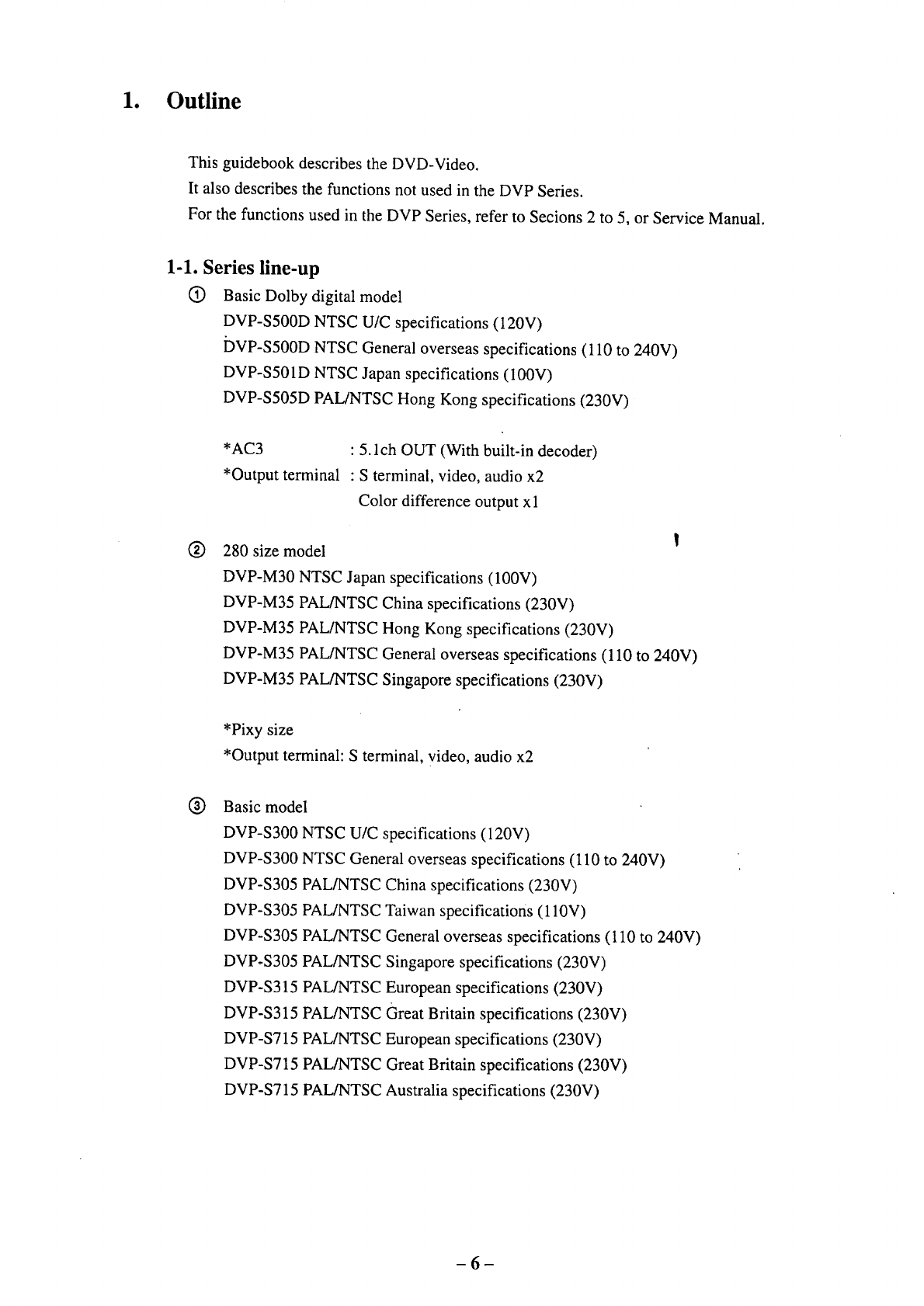

1-1. Series line-up

O Basic Dolby digital model

DVP-S500D NTSC U/C specifications (120V)

DVP-S500D NTSC General overseas specifications (110 to 240V)

DVP-S501D NTSC Japan specifications (100V)

DVP-S505D PAL/NTSC Hong Kong specifications (230V)

®

*AC3

*Output terminal

: 5.1 ch OUT (With built-in decoder)

: S terminal, video, audio x2

Color difference output xl

280 size model

DVP-M30 NTSC Japan specifications (100V)

DVP-M35 PAL/NTSC China specifications (230V)

DVP-M35 PAL/NTSC Hong Kong specifications (230V)

DVP-M35 PAL/NTSC General overseas specifications (110 to 240V)

DVP-M35 PAL/NTSC Singapore specifications (230V)

®

*Pixy size

*Output terminal: S terminal, video, audio x2

Basic model

DVP-S300 NTSC U/C specifications (120V)

DVP-S300 NTSC General overseas specifications (110 to 240V)

DVP-S305 PAL/NTSC China specifications (230V)

DVP-S305 PAL/NTSC Taiwan specifications (ll0V)

DVP-S305 PAL/NTSC General overseas specifications (110 to 240V)

DVP,S305 PAL/NTSC

DVP- $315 PAL/NTSC

DVP-S315 PAL/NTSC

DVP-S715 PAL/NTSC

Singapore specifications (230¥)

European specifications (230V)

Great Britain specifications (230V)

European specifications (230V)

DVP-S715 PAL/NTSC Great Britain specifications (230V)

DVP-S715 PAL/NTSC Australia specifications (230V)

-6-

*Output terminal AC3

21P Euro (DVP-S315, $715)

S terminal, video, audio x l

Note: Video-CDs recorded in the PAL format can be played only by general overseas

specifications models.

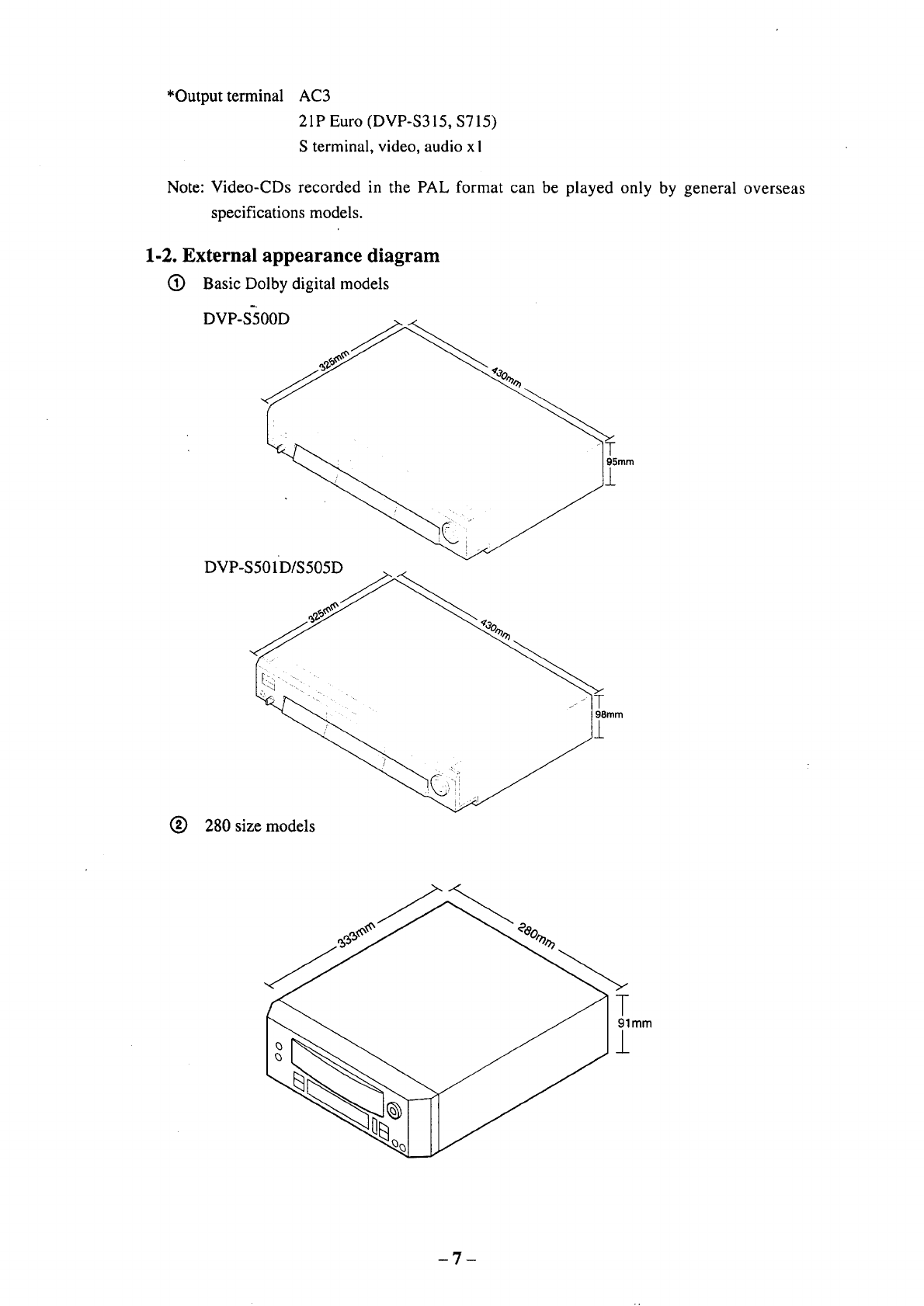

1-2. External appearance diagram

(_) Basic Dolby digital models

DVP-S'500D

DVP-S501D/S505D

98ram

±

(_) 280 size models

T

91mm

1

7

(_ Basic models

DVP-S300/S305/S315

±

DVP-S715

i

!

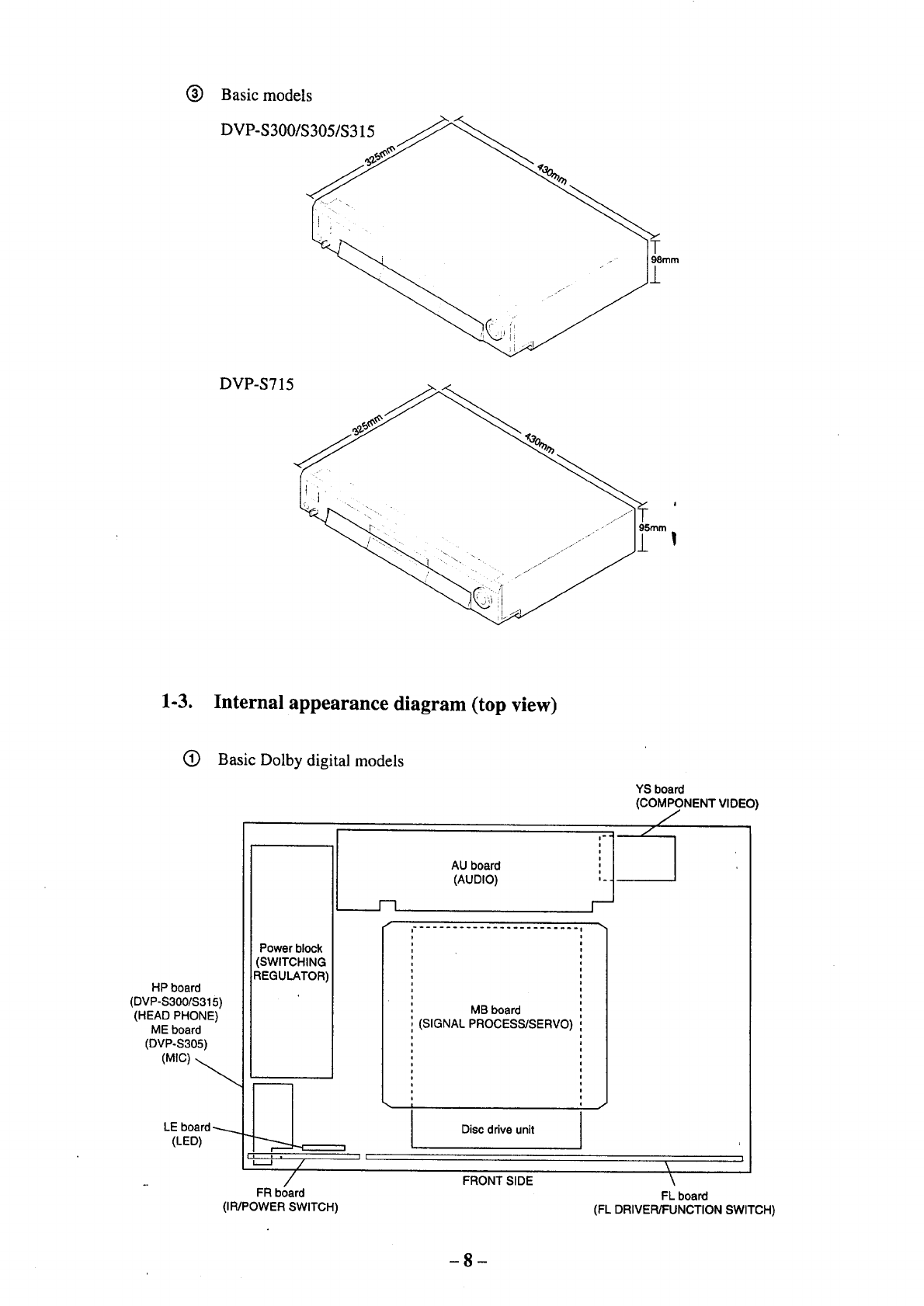

1-3. Internal appearance diagram (top view)

(_) Basic Dolby digital models

HP board

(DVP-S300/S315)

(HEAD PHONE)

ME board

(DVP-S305)

(MIC)

LE board

(LED)

Power block

(SWITCHING

REGULATOR

';---; '/

/

FR board

(IR/POWER SWITCH)

.__.__F3

AU board

(AUDIO)

.........................

I

MB board

(SIGNAL PROCESS/SERVO)

YS board

(COMPONENT VIDEO)

J

iDisc drive unit

FRONT SIDE

i

1

i

\

FL board

(FL DRIVER/FUNCTION SWITCH)

8

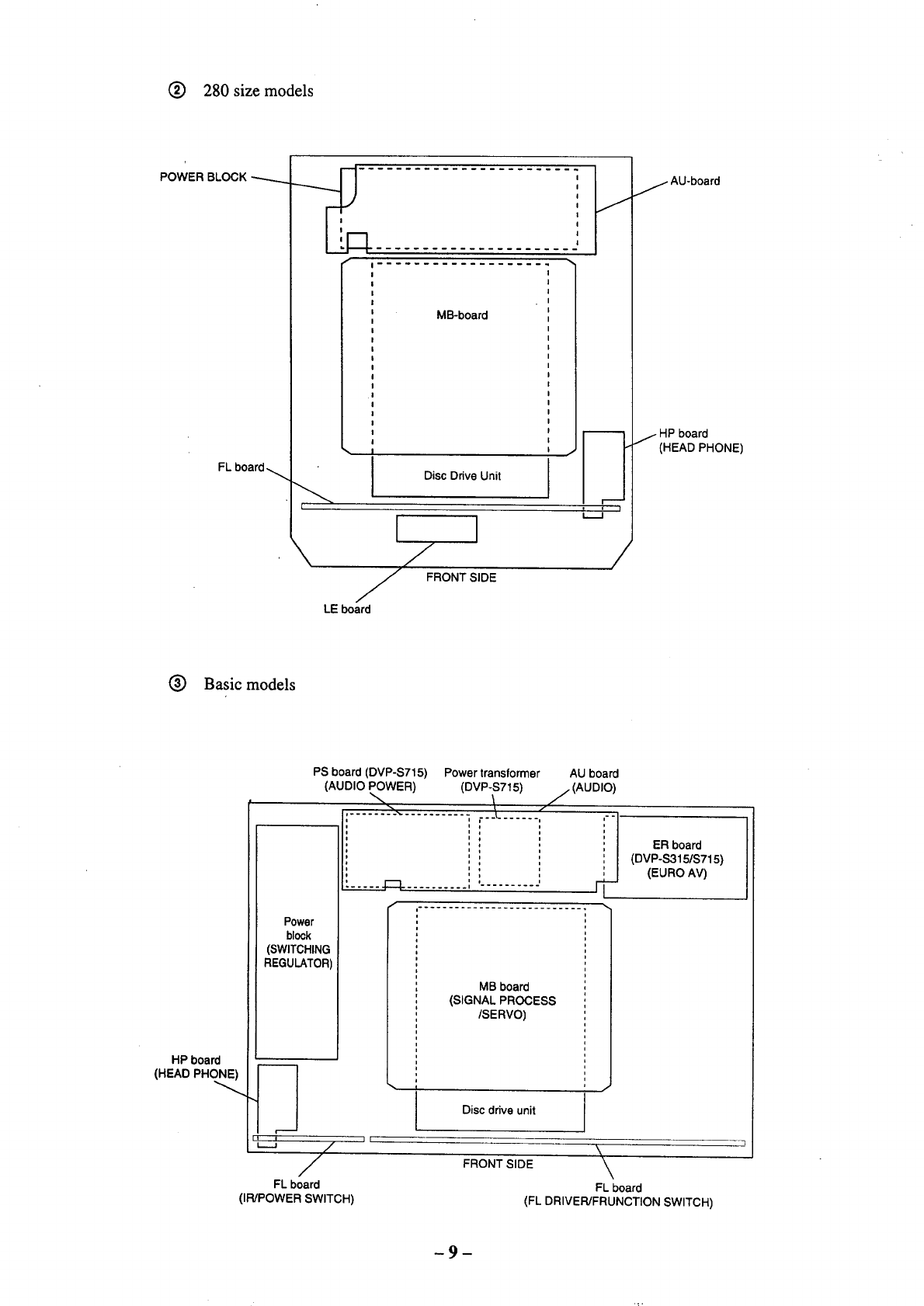

(_) 280 size models

POWER BLOCK _..

FL board

MB-board

--....,

\

Io,sco ,vou , i

I I

/

FRONT SIDE

LE board

, , '1

ii

/

jAU-board

j HP board

(HEAD PHONE)

(_) Basic models

HP board

(HEAD PHO._

PS board (DVP-S715) Power transformer AU board

(AUDIO POWER) (DVP-S715) ,_ (AUDIO)

............. .......... _t III tIIII111 lIlllll_I ........ JI 111 _Iltl""IIll "

Power

block

(SWITCHING

REGULATOR)

ER board

(DVP-S315/S715)

(EURO AV)

iii f--J I

' ' /

/

FL board

MB board

(SIGNAL PROCESS

/SERVO)

(IR/POWER SWITCH)

Disc drive unit

FRONT SIDE

FL board

(FL DRIVEFVFRUNCTION SWITCH)

9

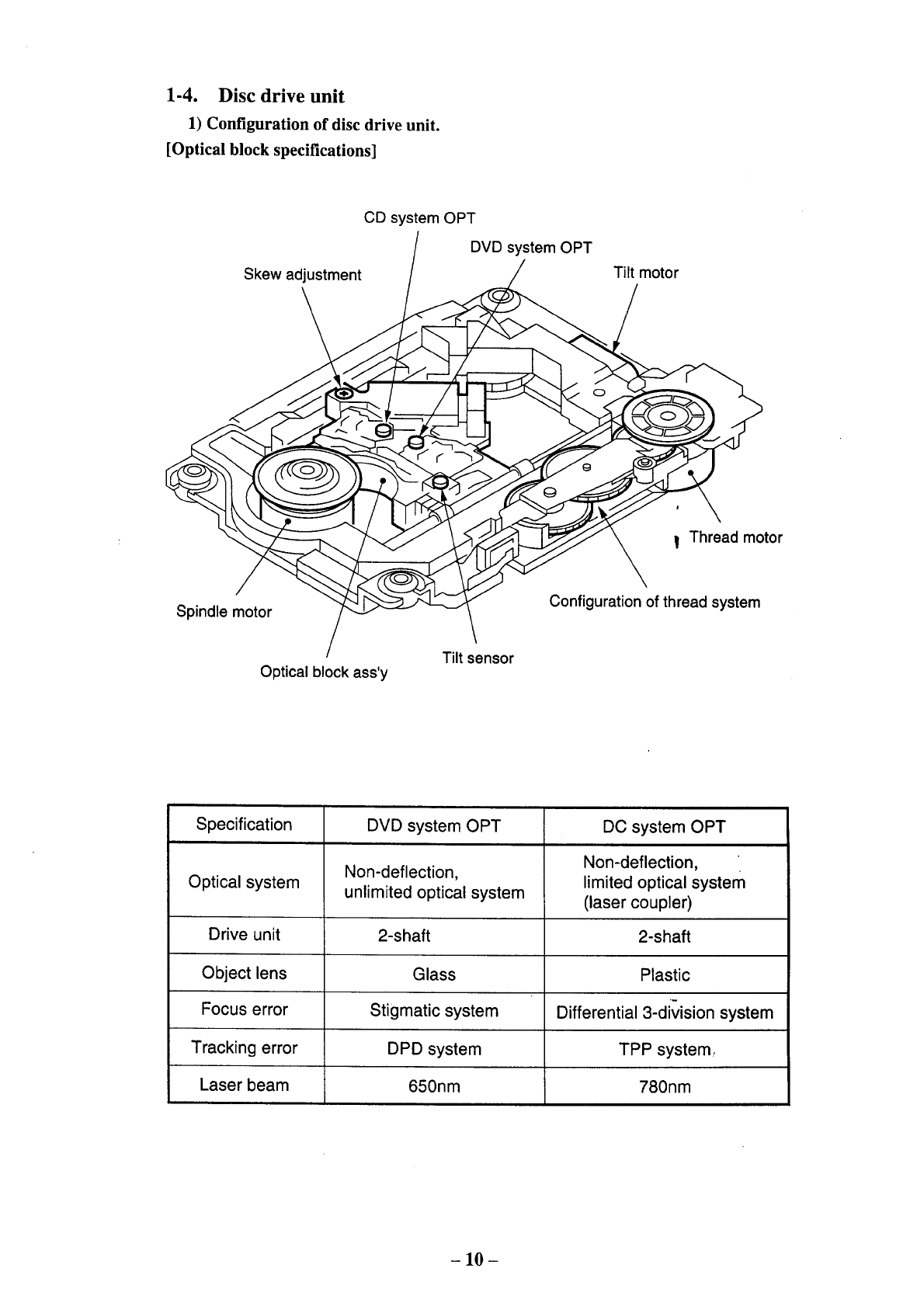

1-4. Disc drive unit

1) Configuration of disc drive unit.

[Optical block specifications]

CD system OPT

Skew adjustment

J

Spindle motor

Optical block ass'y

DVD system OPT

Tilt motor

iThread motor

Configuration of thread system

Tilt sensor

Specification DVD system OPT DC system OPT

Non-deflection,

Non-deflection, limited optical system

Optical system unlimited optical system (laser coupler)

Drive unit 2-shaft 2-shaft

Object lens Glass Plastic

Focus error Stigmatic system Differential 3-division system

Tracking error DPD system TPP system,

Laser beam 650nm 780nm

-10-

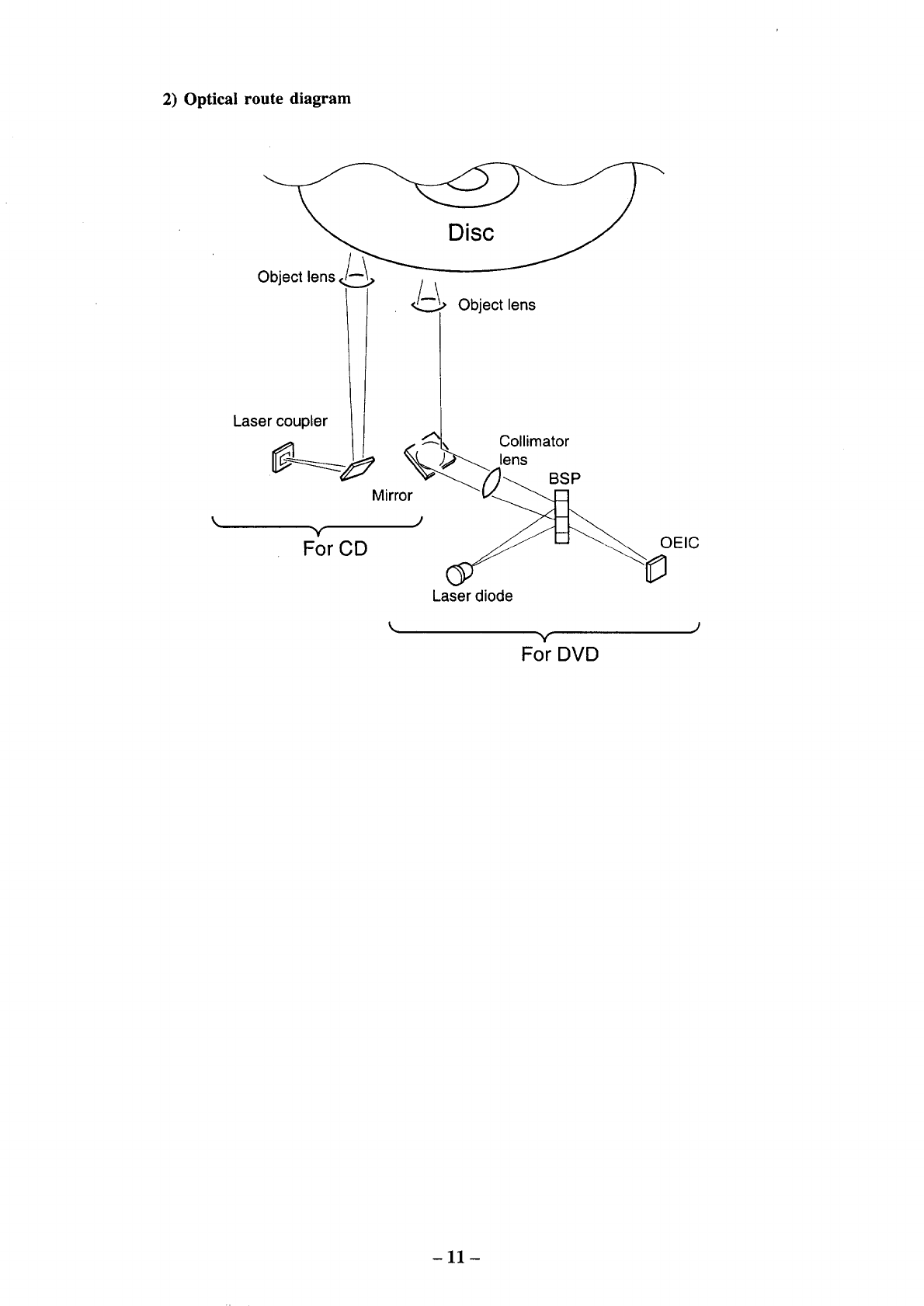

2) Optical route diagram

k

Las Objec ator

_.... lens

Mirror _)_._,._

y J

ForCD (__ ' ' -_"_ OEIC

Laser diode

Y

For DVD

-11-

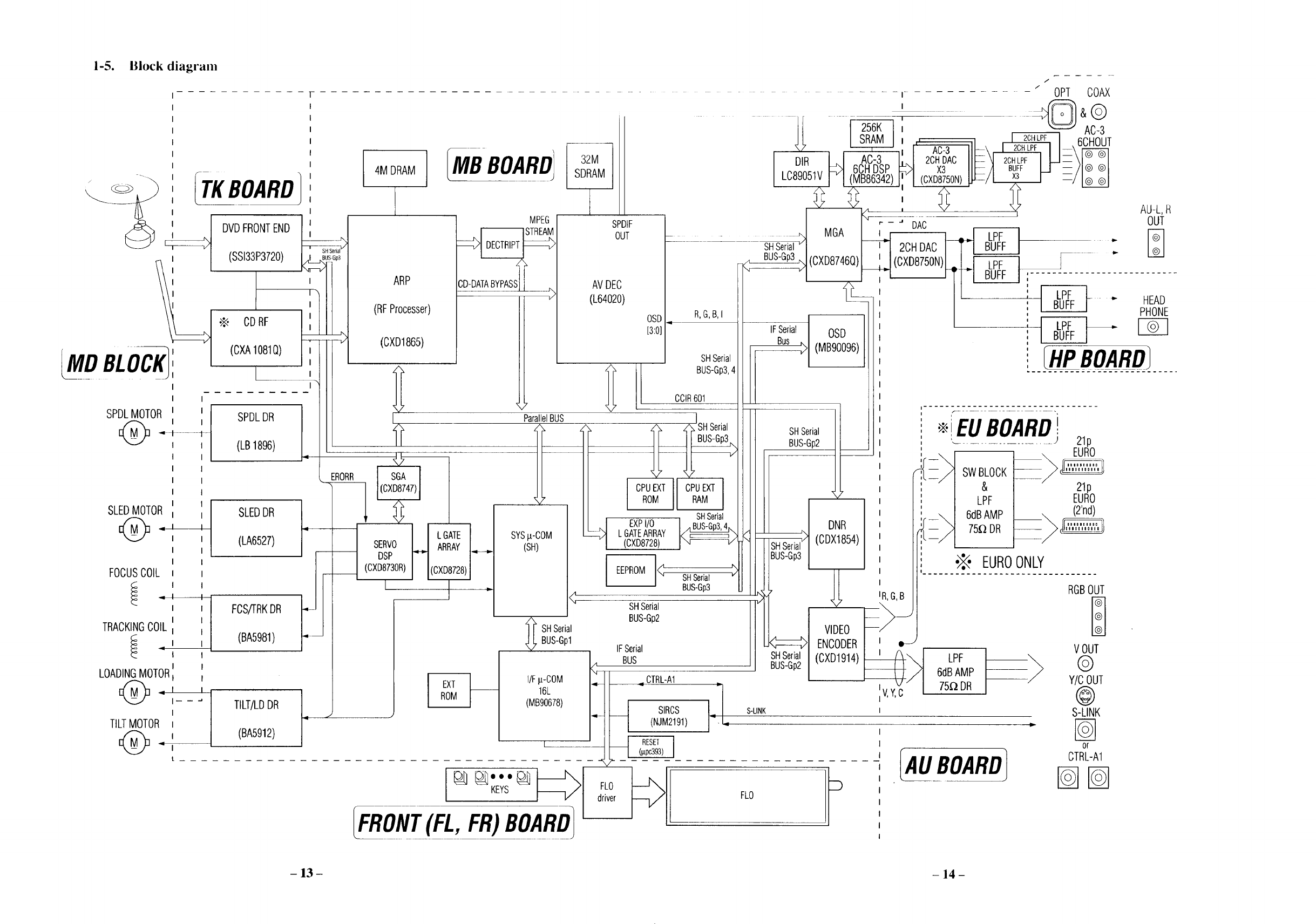

1-5. Block diagram

©

ITKBOARDI

I

_. CDRF

I

SPDLMOTOR I

@ '

SLEDMOTOR

@. ,

I

I

I

FOCUSCOIL I

_ ,i

i

/

/

I............ OPT COAX

TRACKINGCOIL

4M DRAM IMB BOARD132M

SDRAM

.i : &(_)

256K i -_

SRAM I , i 2CHLPF AC-3

ILc8D910R51vH (MBA8C63342)6CHDSP __l]__ _x3 2C_PFB_F___l--;__

...... -_ MGA ____.1 I_ _PF---_ ,..

--- -- SHSerial"l I II 2CHDAC I T-I BUFF I r *

_-- B_(OXD8746Q)[ I_I(oxDa750N)I_I F_

"-_1 _ _ rTCL_ ..........

OSD_ R,G,B,I /ill / ,, --

[3:0] -- IFSerial OSD / , LP.F

SHSerial - Bus_ (MB90096) BUFf /

- s_oo ,4I '11,

CCIR601 ___ II_l[ '- .... .-_------ -------------- -----T ---

__SHSeri_ SHSerial !1 ÷EU BOARD

AI IIBUS-Gp'_BUS-ep2_ ,.................... P21p

4_4_

SPDIF

OUT

LOADINGMOTOR

_I- - ""

I

TILTMOTOR I

®, t

DVDFRONTEND

(SSI33P3720)

'i

I

(CXA1081Q)

[

AVDEC

(L64020)

MPEG

ARP

(RFProcesser)

(CXD1865)

CPRUoEMXTIICPRuAEMxT

.IEXPi-qTd--:_

L GATEARRAY

1_(CXD8728) l_

I E_o_<___ >

_-- SHSera

/1

AU-L,R

OUT

D

HEAD

PHONE

OARDI

I EURO

[ZJ SWBLOCK

& 21p

'v' LPF EURO

IISHSerial (CDX1854) L----J 75aDR

BUS-G"3/_ "_ EUROONLY RGBOUT

IR,G,B

BUS-Gp2 U

VIDEO

IFSerial I1<_ ENCODER I

BUS SHSerial (CXD1914)

BUS-Gp2

S-LINK

FLO

driver

CTRL-A1

FLO

LPF

6dBAMP

75_ DR

V OUT

©

__i) Y/OOUZ

@

S-LINK

-_

or

SPDLDR ParallelBUS

Z

1411

(LB1896)

ERORR SGAI

SLEDDR

(LA6527)

FCS!FRKDR

(BA5981) SHSerialBUS-Gpl

I/Fp-COM

16L

(MB90678)

H lG

SERVO ARI

DSP

(CXD8730R)i I(C×D

I

SIRCS(NJM2191)

RESETI

(ppc393) I

7-

1

TILT/LDDR l" "_

1

(BA5912)

_E

IAY

}728)

SYSp-COM

(SH)

i

F_ONT(FL, FR)BOAR_

CTRL-A1

1,4.

-13- -14 -

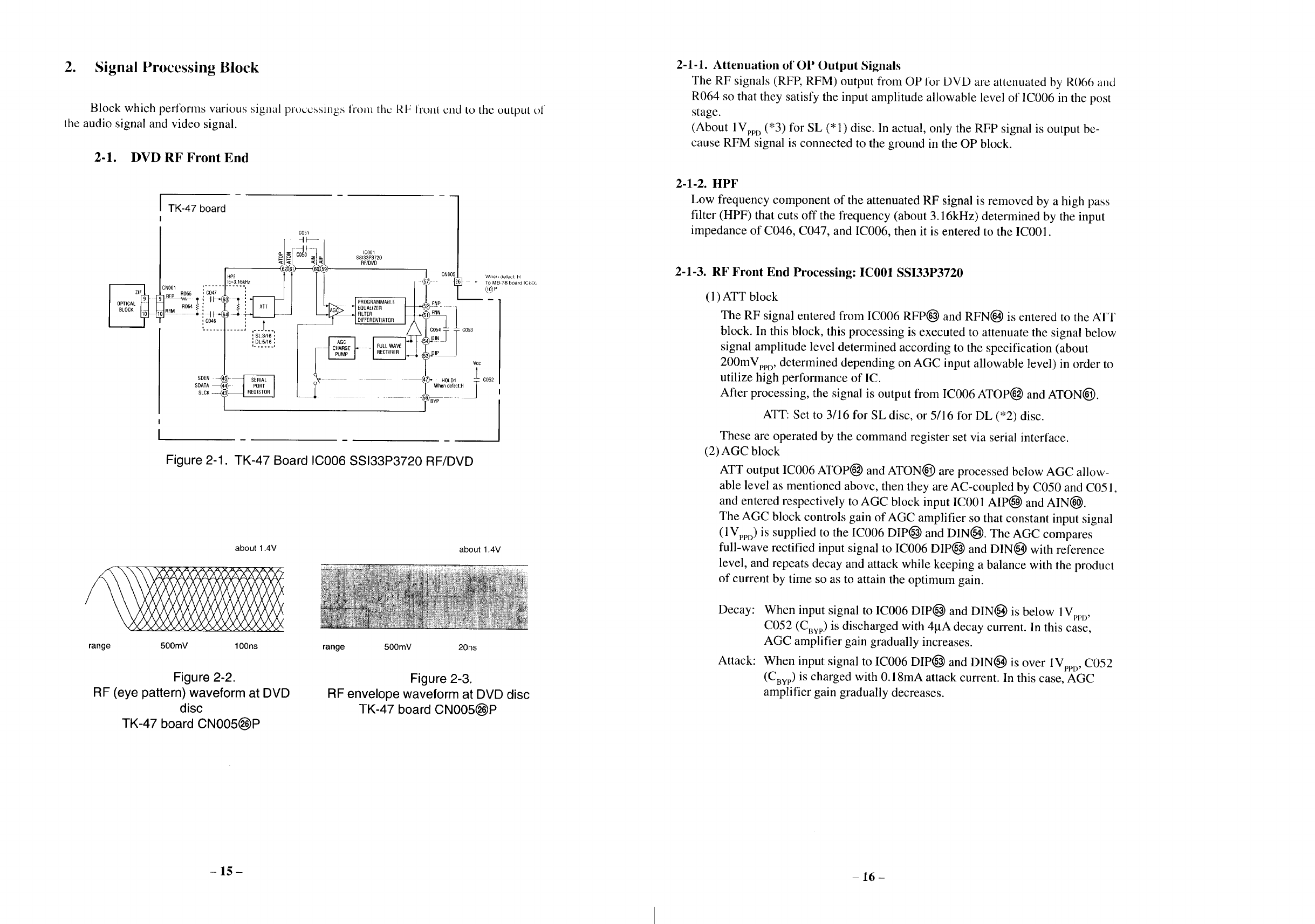

2. Signal Processing Block

Block which perfornls various signal proccssings from the RF frollt cnd to the output of

the audio signal and video signal.

2-1. DVD RF Front End

TK-47 board

0051

oo o ,coo,

8SI33P3720

_ _ _ RFIDVD

IC=3.16kHz

CR001

R066 ,0047

.ru ._ - t F_ 4)

i0046

...L..

' SL:3 6

', DL:5/16 !

SDEN --

SDATA

SLCK

',V_a..,,,,o0_ <"

i 17171ii ,

CNO0_

_When delecl H

TO MB-78 board ICs0b

_ _- c053

_.,.T T

]_D IP_ VCC

Figure 2-1. TK-47 Board IC006 SSI33P3720 RF/DVD

about 1.4V about 1.4V

range 500mV lO0ns range 500mV 20ns

Figure 2-2.

RF (eye pattern) waveform at DVD

disc

TK-47 board CN005_)P

Figure 2-3.

RF envelope waveform at DVD disc

TK-47 board CN005(_P

2-1-1. Attenuation of OP Output Signals

The RF signals (RFP, RFM) output from OP for DVD are attenuated by R066 and

R064 so that they satisfy the input amplitude allowable level of IC006 in the post

stage.

(About IVpp D (*'3) for SL (*1) disc. In actual, only the RFP signal is output be-

cause RFM signal is connected to the ground in the OP block.

2-1-2. ttPF

Low frequency component of the attenuated RF signal is removed by a high pass

filter (HPF) that cuts off the frequency (about 3.16kHz) determined by the input

impedance of C046, C047, and IC006, then it is entered to the IC001.

2-1-3. RF Front End Processing: IC001 SSI33P3720

(1) ATT block

The RF signal entered from IC006 RFP(_) and RFN(_ is entered to the ATT

block. In this block, this processing is executed to attenuate the signal below

signal amplitude level determined according to the specification (about

200mVwD, determined depending on AGC input allowable level) in order to

utilize high performance of IC.

After processing, the signal is output from IC006 ATOP_ and ATONe).

ATT: Set to 3/16 for SL disc, or 5/16 for DL (*2) disc.

These are operated by the command register set via serial interface.

(2) AGC block

ATT output IC006 ATOP(_ and ATONe) are processed below AGC allow-

able level as mentioned above, then they are AC-coupled by C050 and C051,

and entered respectively to AGC block input IC001 AIP_ and AIN(_.

The AGC block controls gain of AGC amplifier so that constant input signal

(1VppD) is supplied to the IC006 DIP@ and DIN_). The AGC compares

full-wave rectified input signal to IC006 DIP(_ and DIN(_) with reference

level, and repeats decay and attack while keeping a balance with the product

of current by time so as to attain the optimum gain.

Decay:

Attack:

When input signal to IC006 DIP(_ and DIN(_) is below I Vppl) ,

C052 (CByp) is discharged with 41aA decay current. In this case,

AGC amplifier gain gradually increases.

When input signal to IC006 DIP_ and DIN(_) is over 1VpeD, C052

(CuvP) is charged with 0.18mA attack current. In this case, AGC

amplifier gain gradually decreases.

-15 - - 16 -

Theinputsignalto IC006DIP_ andDIN_) isa signalprocessedafterEQblock

mentionedlater.

"1:SingleLayerdisc *2:DualLayerdisc *3:Peakto PeakDifferential

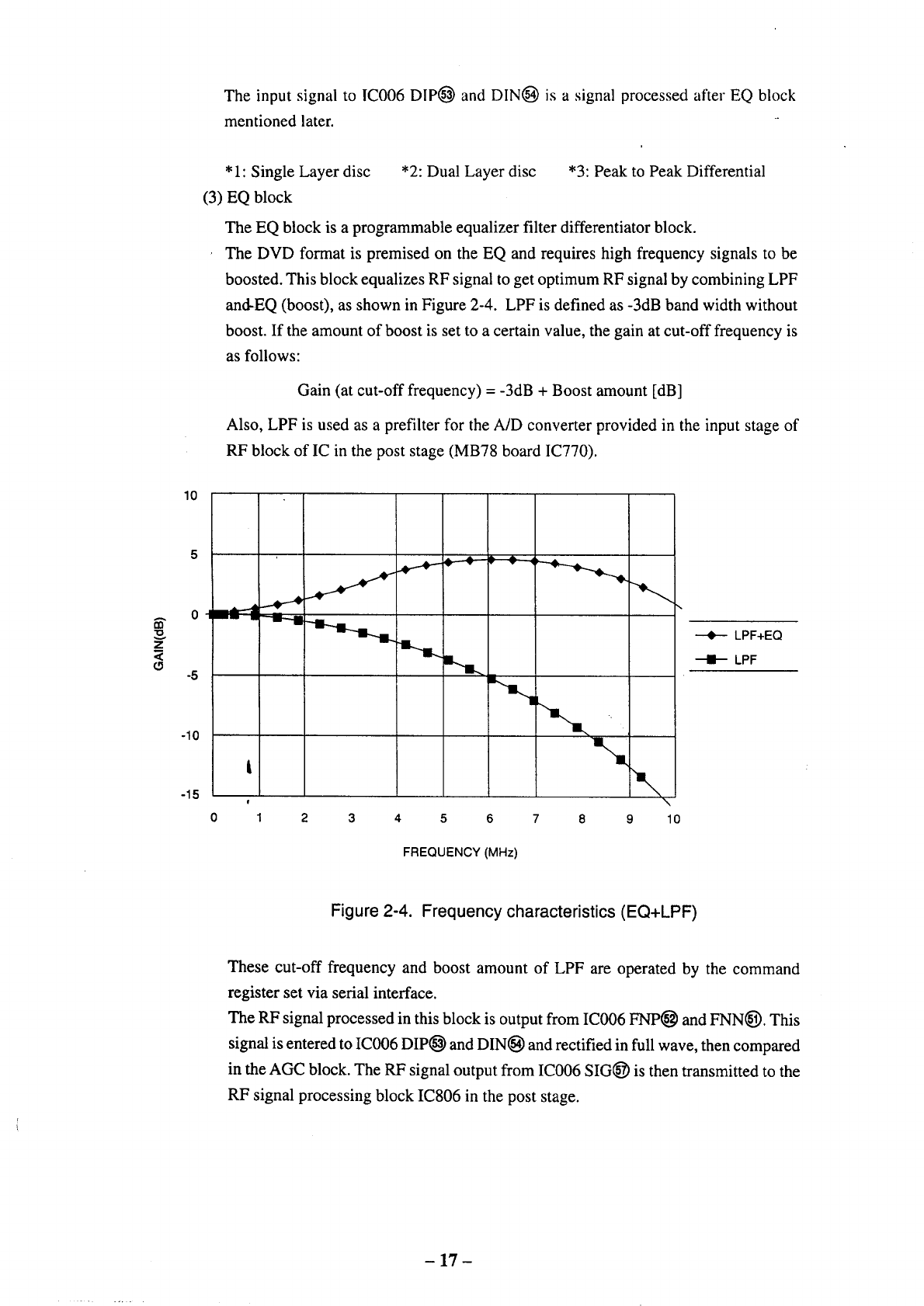

(3)EQblock

TheEQblockisaprogrammableequalizerfilterdifferentiatorblock.

TheDVDformatis premisedontheEQandrequireshighfrequencysignalstobe

boosted.ThisblockequalizesRFsignaltogetoptimumRFsignalbycombiningLPF

and-EQ(boost),asshownin Figure2-4. LPFisdefinedas-3dBbandwidthwithout

boost.If theamountofboostissettoacertainvalue,thegainatcut-offfrequencyis

asfollows:

Gain(atcut-offfrequency)= -3dB+ Boostamount[dB]

Also,LPFisusedasaprefilterfortheA/D converterprovidedintheinputstageof

RFblockof IC inthepoststage(MB78boardIC770).

wl

v

_z

10

-5

-10

-15

0

t

1 2 3456 7 8 9 10

FREQUENCY (MHz)

---e.--- LPF+EQ

--D-- LPF

Figure 2-4. Frequency characteristics (EQ+LPF)

These cut-off frequency and boost amount of LPF are operated by the command

register set via serial interface.

The RF signal processed in this block is output from IC006 FNP_ and FNN(_). This

signal is entered to IC006 DIP_ and DIN(_) and rectified in full wave, then compared

in the AGC block. The RF signal output from IC006 SIG(_ is then transmitted to the

RF signal processing block IC806 in the post stage.

- 17 -

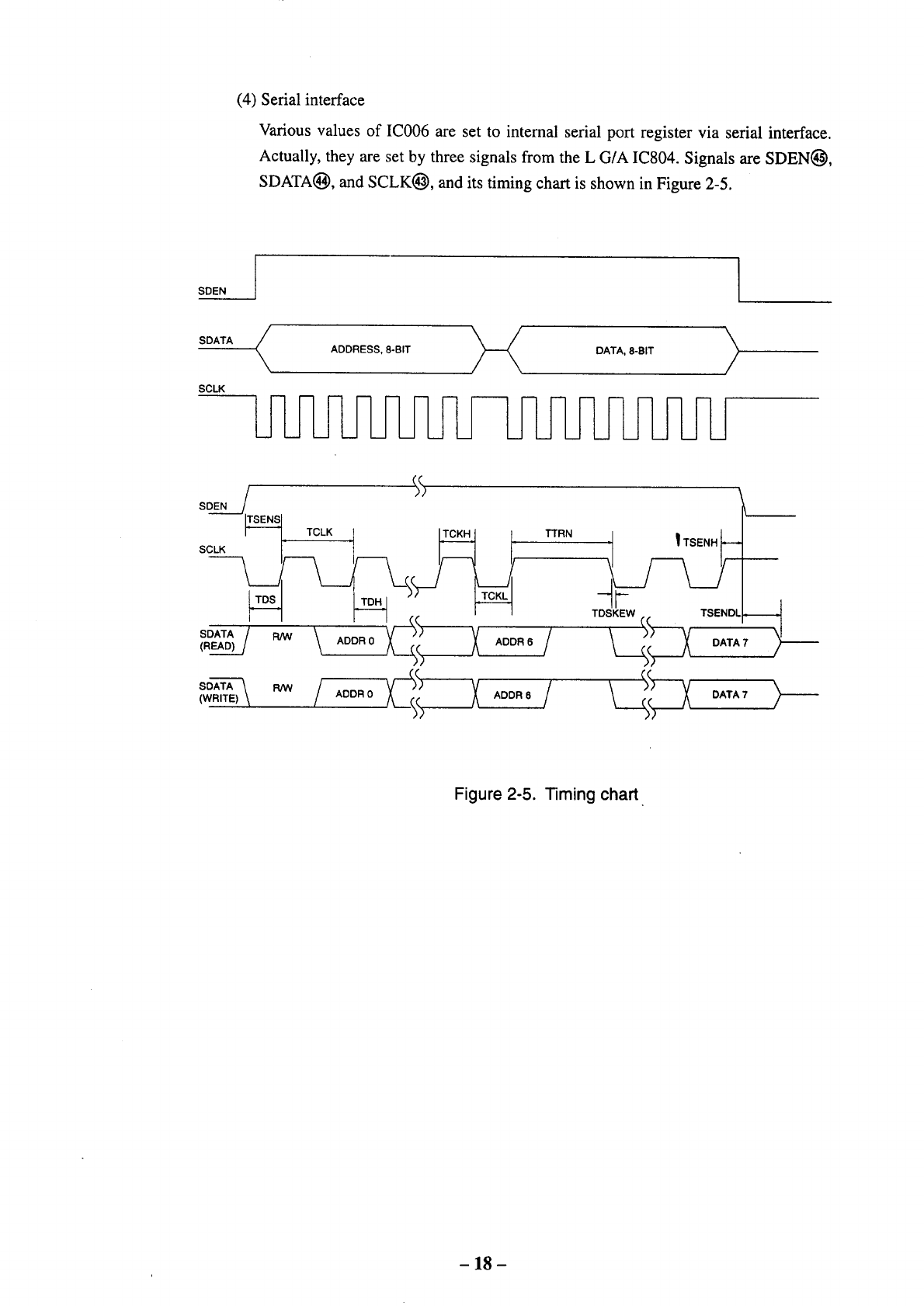

(4) Serial interface

Various values of IC006 are set to internal serial port register via serial interface.

Actually, they are set by three signals from the L G/A IC804. Signals are SDEN_,

SDATA_), and SCLK(_, and its timing chart is shown in Figure 2-5.

SDEN

SDATA (

SCLK LJ

ADDRESS, 8-BIT _DATA, 8-BIT )

SDEN

SCLK

SDATA /

(READ)/

SDATA \

(WRITE)

TCLK TTRN

ADDR0

ADDR0

Figure 2-5. Timing chart

- 18-

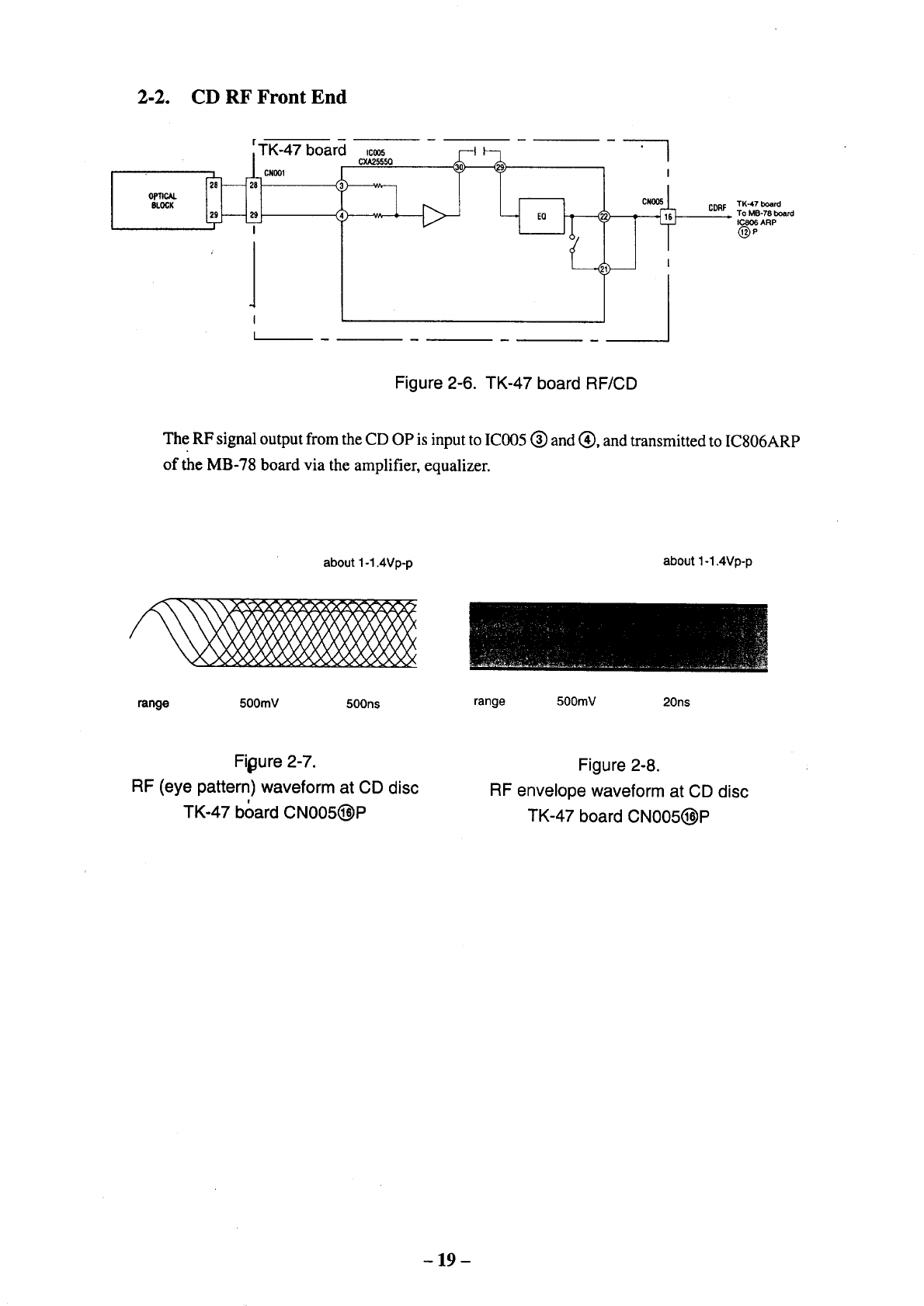

2-2. CD RF Front End

OPTICAL

BLOCK

rTK-47 board

_1 cNO01 -_

<

CXA,?.5550

CDRF TK-47 board

To MB-78 board

IC.806 ARP

Figure 2-6. TK-47 board RF/CD

The RF signal output from the CD OP is input to IC005 (_) and (_), and transmitted to IC806ARP

of the MB-78 board via the amplifier, equalizer.

about 1-1.4Vp-p about 1-1.4Vp-p

range 500mY 500ns range 500mY 20ns

Fi0ure 2-7.

RF (eye pattern) waveform at CD disc

I

TK-47 board CN005(_P

Figure 2-8.

RF envelope waveform at CD disc

TK-47 board CN005(_P

- 19 -

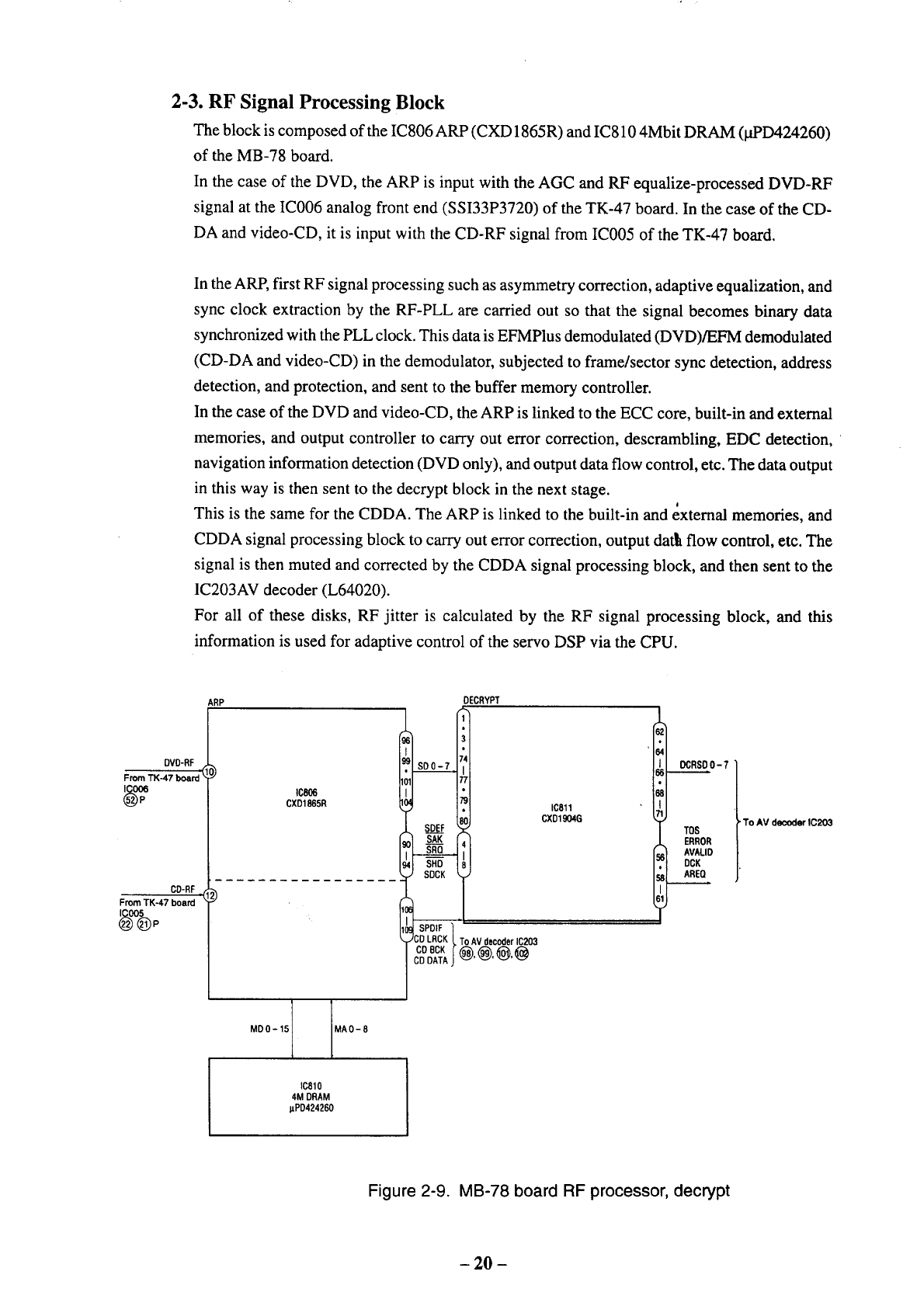

2-3. RF Signal Processing Block

The block is composed of the IC806 ARP (CXD 1865R) and IC810 4Mbit DRAM (I.tPD424260)

of the MB-78 board.

In the case of the DVD, the ARP is input with the AGC and RF equalize-processed DVD-RF

signal at the IC006 analog front end (SSI33P3720) of the TK-47 board. In the case of the CD-

DA and video-CD, it is input with the CD-RF signal from IC005 of the TK-47 board.

In the ARP, first RF signal processing such as asymmetry correction, adaptive equalization, and

sync clock extraction by the RF-PLL are carried out so that the signal becomes binary data

synchronized with the PLL clock. This data is EFMPlus demodulated (DVD)/EFM demodulated

(CD-DA and video-CD) in the demodulator, subjected to frame/sector sync detection, address

detection, and protection, and sent to the buffer memory controller.

In the case of the DVD and video-CD, the ARP is linked to the ECC core, built-in and external

memories, and output controller to carry out error correction, descrambling, EDC detection,

navigation information detection (DVD only), and output data flow control, etc. The data output

in this way is then sent to the decrypt block in the next stage.

J

This is the same for the CDDA. The ARP is linked to the built-in and external memories, and

CDDA signal processing block to carry out error correction, output datll flow control, etc. The

signal is then muted and corrected by the CDDA signal processing block, and then sent to the

IC203AV decoder (L64020).

For all of these disks, RF jitter is calculated by the RF signal processing block, and this

information is used for adaptive control of the servo DSP via the CPU.

ARP DECRYPT

DVD-RF (

From TK-47 boa_

CD-RF.(

From TK-47 boa_

IC806

CXD1865R

_O LRCK(. To AV decoder IC203

CD DATA)_J, _-.-, ,_J, _-._

IC811

CXD1904G

OCRSD0 - 7

TOS

ERROR

AVALID

DCK

AREQ

' To AV decoder IC203

MDO-15 MAO-8

IC810

4M DRAM

pPD424260

Figure 2-9. MB-78 board RF processor, decrypt

- 20 -

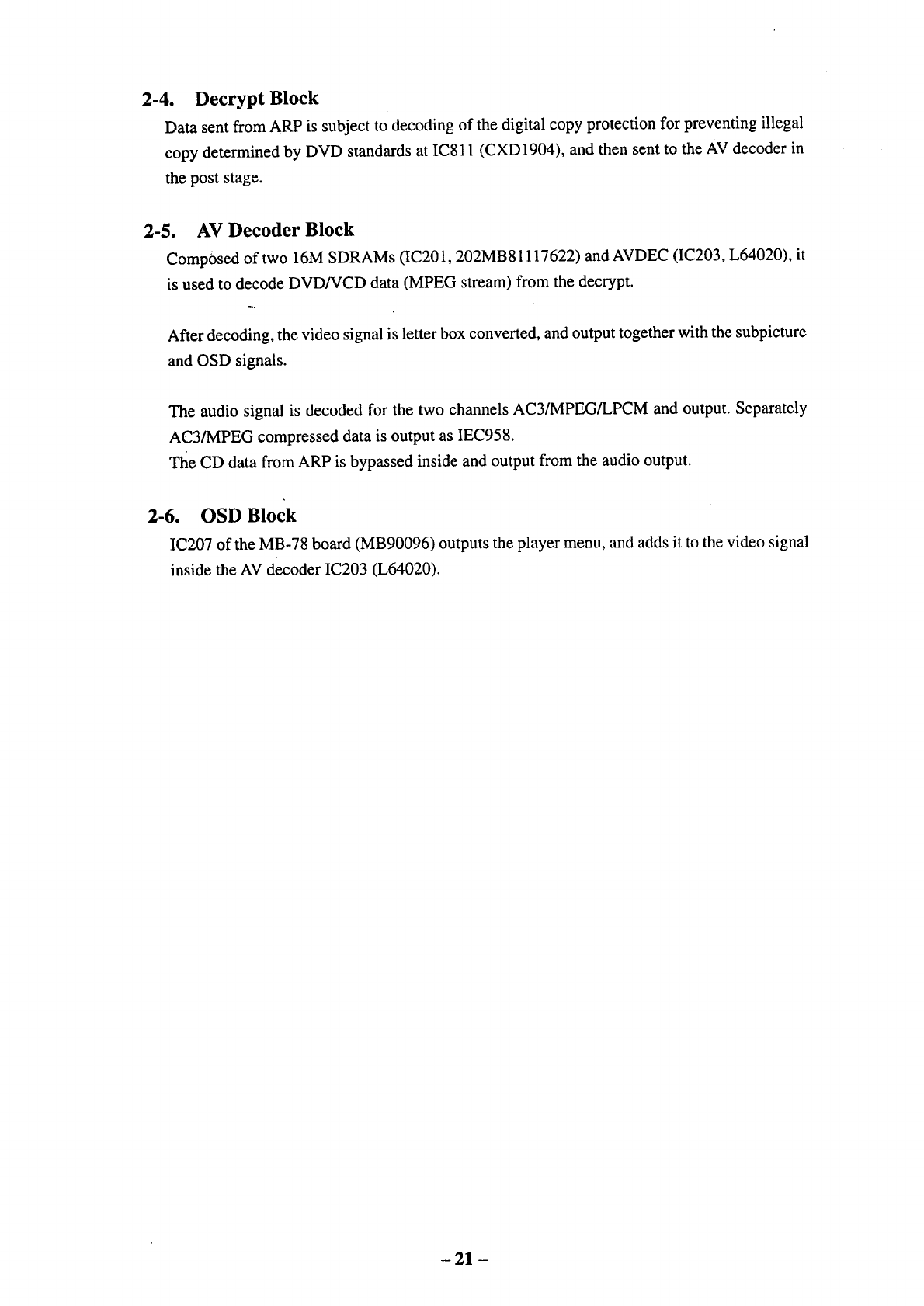

2-4. Decrypt Block

Data sent from ARP is subject to decoding of the digital copy protection for preventing illegal

copy determined by DVD standards at ICS11 (CXD1904), and then sent to the AV decoder in

the post stage.

2-5. AV Decoder Block

Comp0sed of two 16M SDRAMs (IC201,202MB 81117622) and AVDEC (IC203, L64020), it

is used to decode DVD/VCD data (MPEG stream) from the decrypt.

After decoding, the video signal is letter box converted, and output together with the subpicture

and OSD signals.

The audio signal is decoded for the two channels AC3/MPEG/LPCM and output. Separately

AC3/MPEG compressed data is output as IEC958.

The CD data from ARP is bypassed inside and output from the audio output.

2-6. OSD Block

IC207 of the MB-78 board (MB90096) outputs the player menu, and adds it to the video signal

inside the AV decoder IC203 (L64020).

- 21 -

IC203 AV Decoder

(L64020)

FromIC807 ('CG--'_'O

SGA , _SO

CXD08747 ' L SCLKO

IC207

MB90096

OSO

FromIC806ARP --

DCRSD 0-7

TOS

ERROR

AVALID

DCK

AREQ

CDLRCK

CDBCK

CDDATA

SPDIF

YC0-7

-- To IC251 DNR

AU-197

0353

iC351_C°axial °utptzt ] 0joltal

GPIF32T Ioutput

IC102 OIR (To LC8905t)

AVDATA

AV LRCK

AVBCK

tTo IC101 MGA (2cll signal)

IC201

IC202

16M SOP,AM

AVIO0-15

Figure 2-10. AV Decoder, OSD

- 22 -

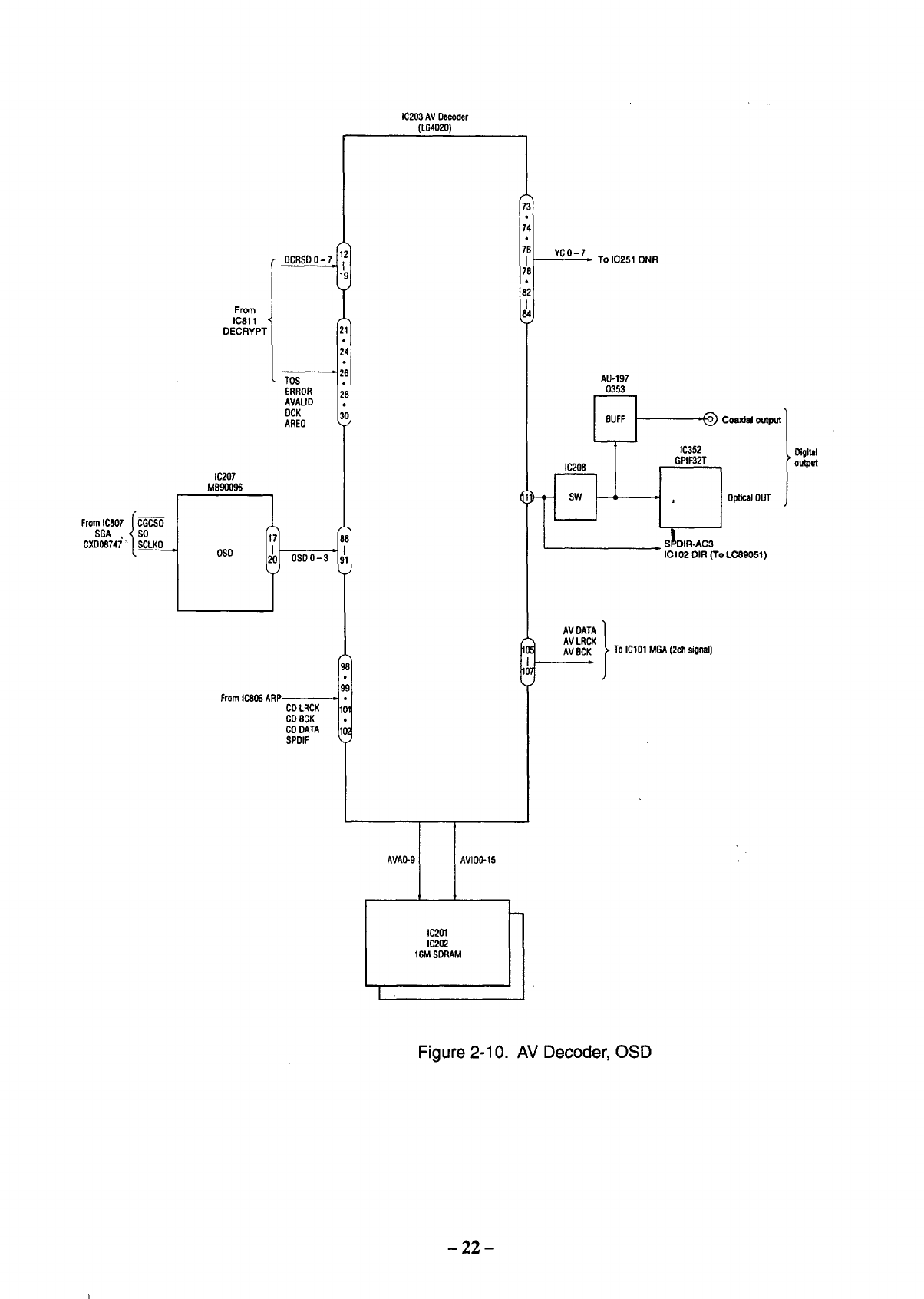

2-7. DNR, Video Encoder Blocks

The video data from the AV decoder is sent to IC251, DNR (CXD1854), subjected to video

noise reduction, and sent to the IC252 video encoder CXD1914 in the post stage. The video

data is converted to NTSC/PAL video signal (Color difference signal/S-Y, S-C/composite) here.

IC252

IC2510NR VIDEO ENCORDER

CXD1854 CXD 1914

From vr

IC203 '"

AV Decoder

C0-7

YO-7

R-Y 1

For color difference output

Y

J

B-Y

VIDEOC

ForS terminal

VIDEOY

VIDEOV Compositevideo

Figure 2-11. DNR video encoder

Signals are output externally after passing through the 75 _ driver.

- 23 -

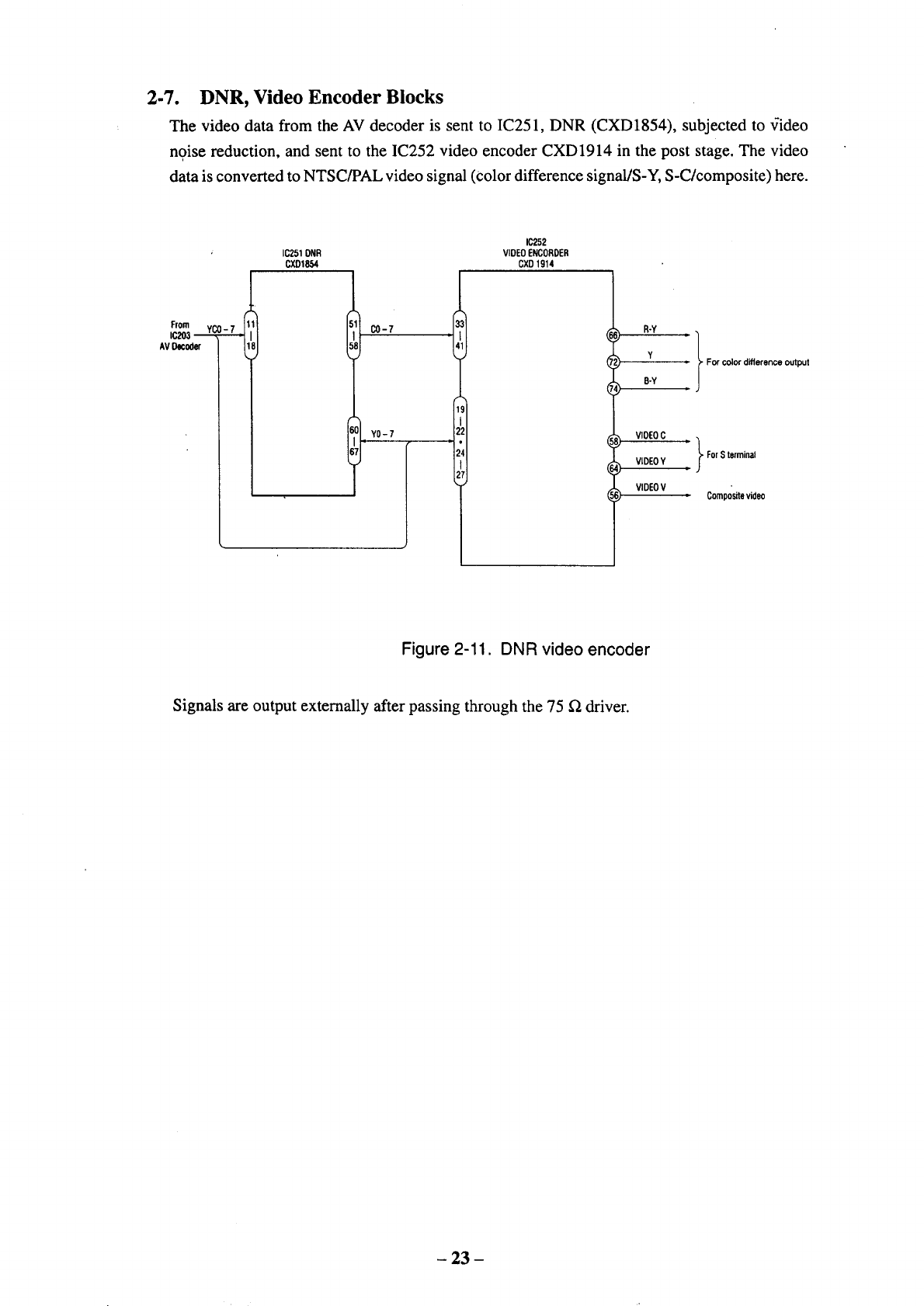

2-8. Clock Generator Block

The IC209 CXD8696PLL IC generates 27 MHz, and using this as the master clock, generates

the system clock for audio decoding.

System Clock 384fs 768fs

CD/VCD 16.9344 MHz 33.8688 MHz

DVD 18.4320 MHz 36.8640 MHz

IC209 IC206 SN74ABT12608

PLL

CXD8696 BUFF

X210

27MHz

)

)

1(;205 SN74ABT12608

BUFF

27.0000MHz

)7_Sfs

384fs

=

33.8688MHz

Figure 2-12. Clock generator

- 24 -

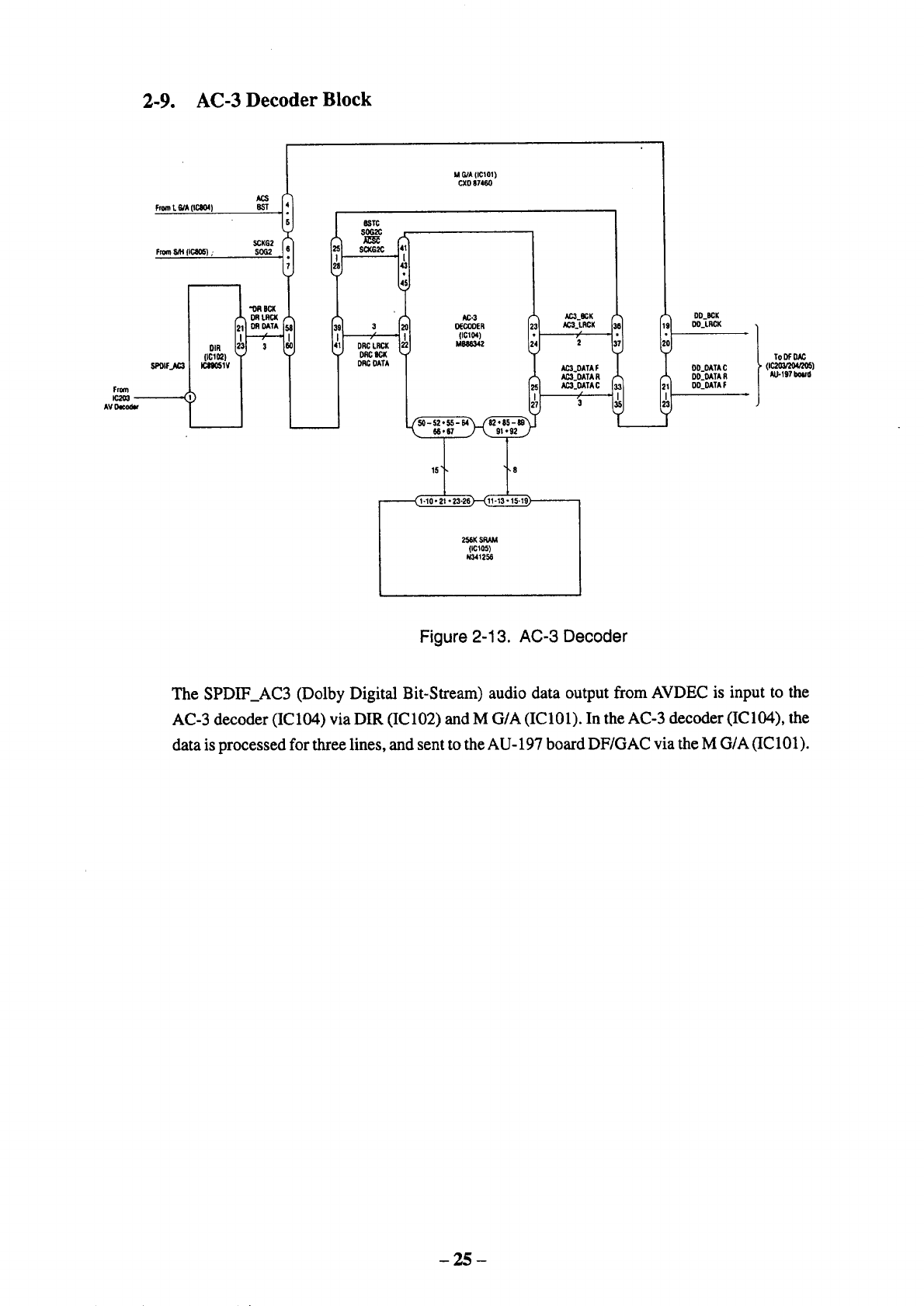

2-9. AC-3 Decoder Block

FromL_A (tC_4) 8s'r

SCKG2

SOG2From_11c8o5);

I

AV_II

OR LRCK (

M G/A (IC101)

CXO 87460

6STC

$062C

AC-3

DECODER

(IC_04)

M886342

AC3__K

AC;_LRCK

/2

AC3_DATA F

AC3_OATAR

AC3.OATA C

/3

DD_BCK l

DO_LRCK

DD_OATA F 1

256KS_

N341256

Figure 2-13. AC-3 Decoder

The SPDIF_AC3 (Dolby Digital Bit-Stream) audio data output from AVDEC is input to the

AC-3 decoder (IC104) via DIR (IC102) and M G/A (IC101). In the AC-3 decoder (IC104), the

data is processed for three lines, and sent to the AU- 197 board DF/GAC via the M G/A (IC 101).

- 25 -

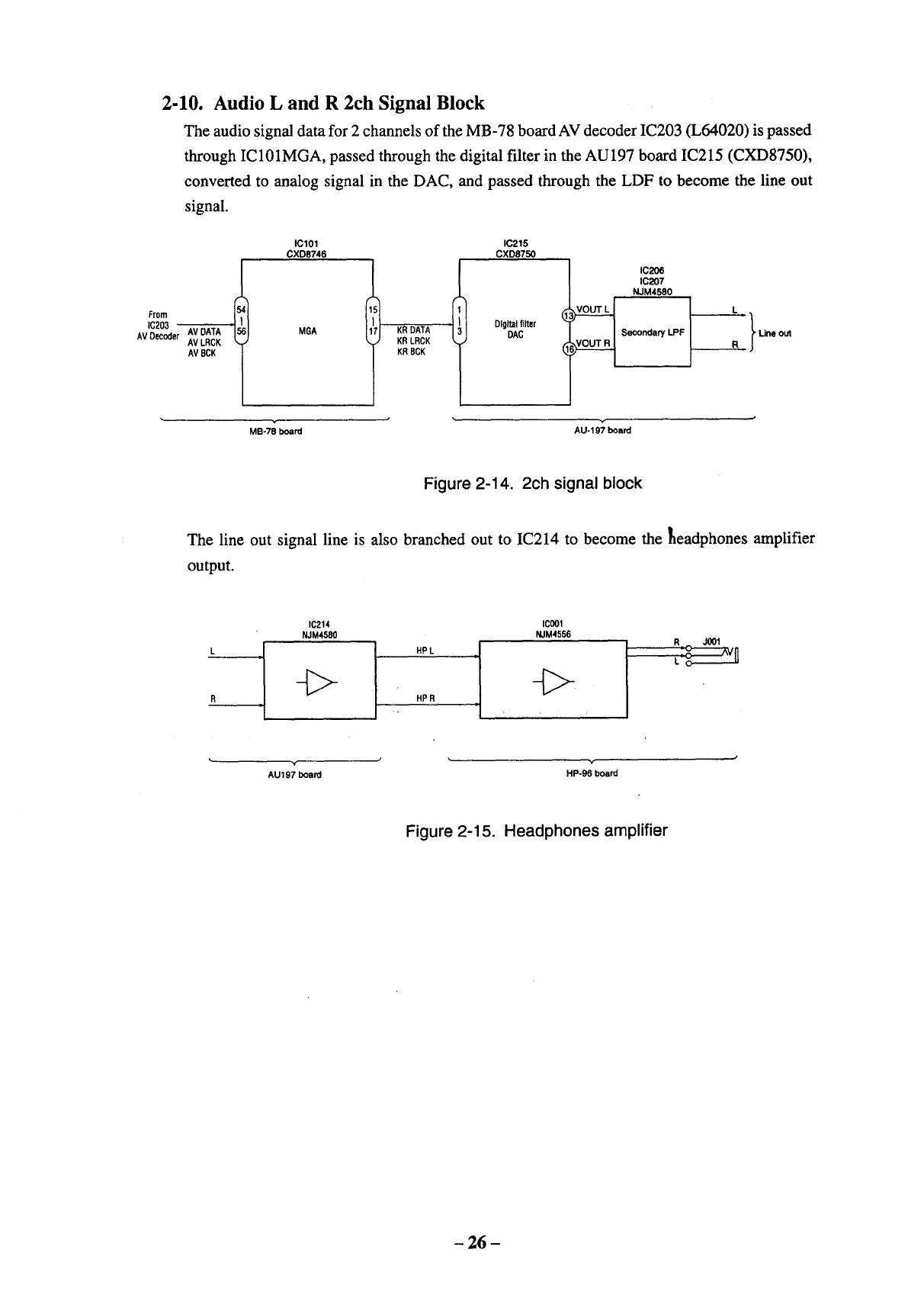

2-10. Audio L and R 2ch Signal Block

The audio signal data for 2channels of the MB-78 board AV decoder IC203 (L64020) is passed

through IC101MGA, passed through the digital filter in the AU197 board IC215 (CXD8750),

converted to analog signal in the DAC, and passed through the LDF to become the line out

signal.

From

IC203

AVDecoder AVDATA

AVLRCK

AVBCK

IC101 IC215

CXD8746 CXD8750

MGA KRDATA

KRLRCK

KR BCK

Digitalfilter

DAC

IC206

IC207

NJM4580

Secondary LPF Line oul

MB-78 board ""AU-197 board

Figure 2-14. 2ch signal block

The line out signal line is also branched out to IC214 to become the _eadphones amplifier

output.

L

R

IC214 IC001

NJM4580 NJM4556

-E> .,. -E>

R JO01

Y

AU197 board

_r

HP-96 board

Figure 2-15. Headphones amplifier

- 26 -

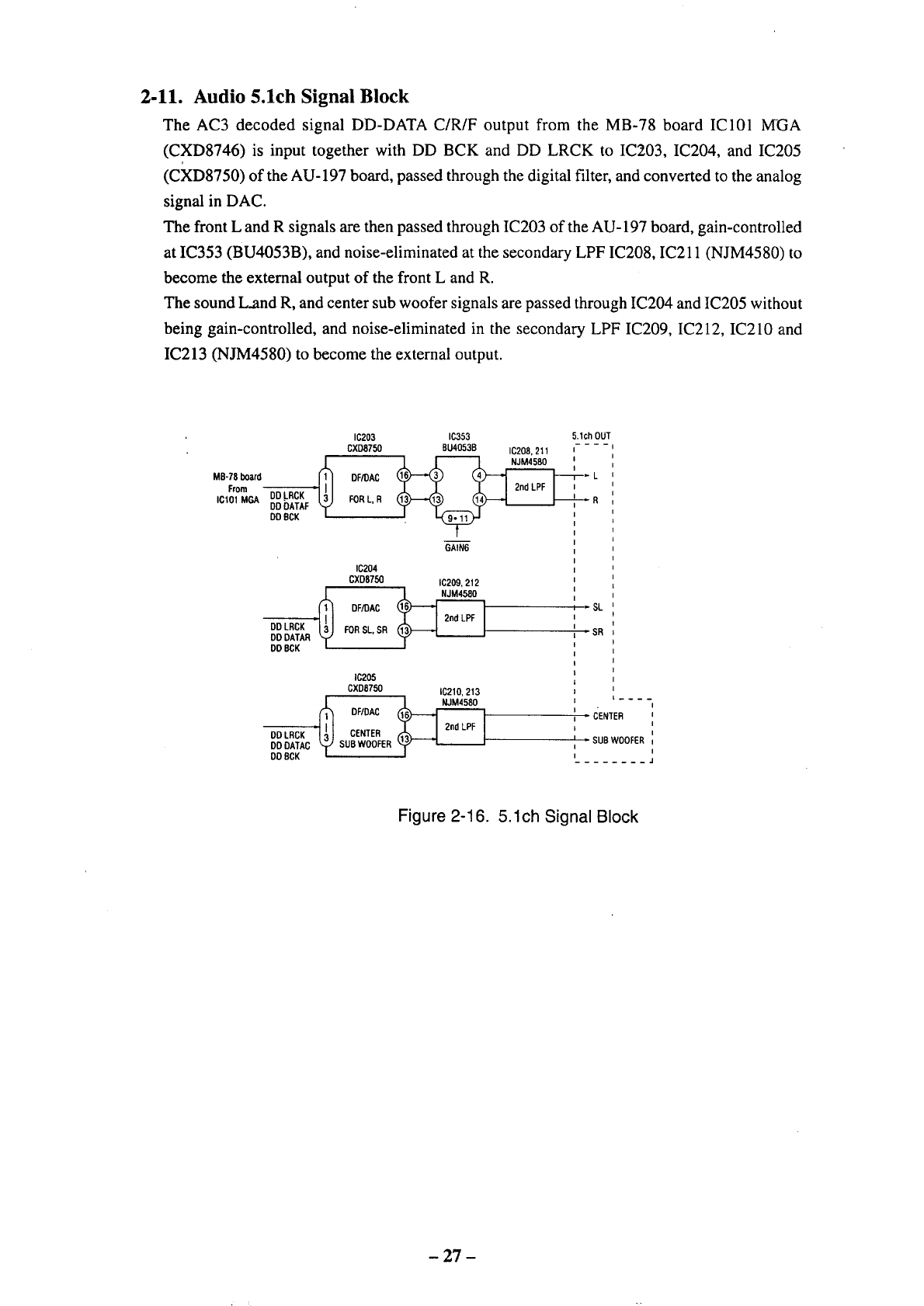

2-11. Audio 5.1ch Signal Block

The AC3 decoded signal DD-DATA C/R/F output from the MB-78 board IC101 MGA

(CXD8746) is input together with DD BCK and DD LRCK to IC203, IC204, and IC205

(CXD8750) of the AU-197 board, passed through the digital filter, and converted to the analog

signal in DAC.

The front L and Rsignals are then passed through IC203 of the AU- 197 board, gain-controlled

at IC353 (BU4053B), and noise-eliminated at the secondary LPF IC208, IC211 (NJM4580) to

become the external output of the front L and R.

The sound Land R, and center sub woofer signals are passed through IC204 and IC205 without

being gain-controlled, and noise-eliminated in the secondary LPF IC209, IC212, IC210 and

IC213 (NJM4580) to become the external output.

IC203 5.1ch OUT

CXD8750

MB-78board _DF/DAC

From DD LRCK =FOR L,R

IC101MGA DDbATAF

DDBCK

IC204

CXD8750

,_DF/DAC

DD LRCK FOR SL, SR

DO DATAR

DO BCK

IC205

CXD8750

___ DF/DAC

DD LRCK CENTER

DD DATAC SUB WOOFER

DO 8CK

IC353

BU4053B IC208, 211

GAIN6

---L

_R

IC209,212

, - SL-SR

IC210,213

_CENTER:

I

I

'SUBWOOFER I

I I

I_J

Figure 2-16. 5.1ch Signal Block

- 27 -

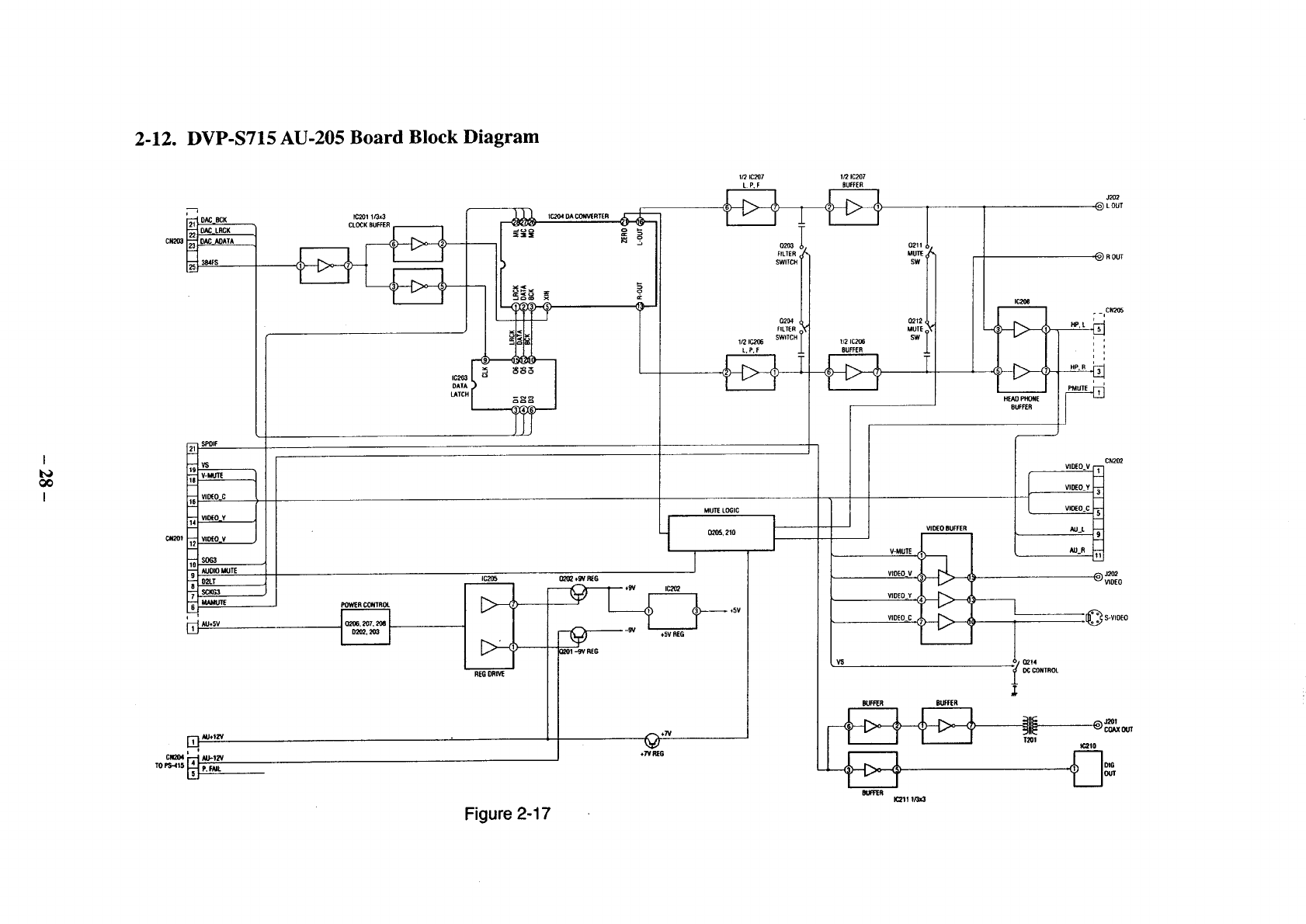

2-12. DVP-S715 AU-205 Board Block Diagram

I

i

7_

OAC BCK

DA,C LRCK

CN203 OAC AOATA

IF

CN201 SOG3

AUDIOMUTE

D2LT

SCKG3

_AU*SV

_E01 1/3x3 IC204 DA CONVERTER _i

CLOCK BUFFER

kATe

1/2 _CL_I7 1/2 IC207

L P, F BUFFER

0203

FILTER

SWITCH

POWERCONTROL

MUTE LOGIC

0205, 210

I

IC_85 Q2_ *W REG

_ ÷5V

---_ --W _EV REG

_1 .-_ REO

REG DRIVE

Q204

FILTER

SWITCH

1/2 1C206

L,P,F

['1--_AU*E2V

i'

CRY04 _ _1_

TO_-415 p. FAIL

Figure 2-17

1

t/2 IC206

BUFFER

0211

MUTE

SW

0212

MUTE

SW

VIDEO BUFFER

V_OEO V,

VIDEO Y

VIDEOIC

vs

J202

(_) L OUT

i (_ R OUT

IC208 HP, L ;" _ ,CN205

PMUTE I,

CR202

VIDEO V

VIOEO_YAuL

J20_

_) VIDEO

[© S-V,D_O

Q214

OCCONTROL

BUFFER BLB:FER

J_F

©c_

_tO

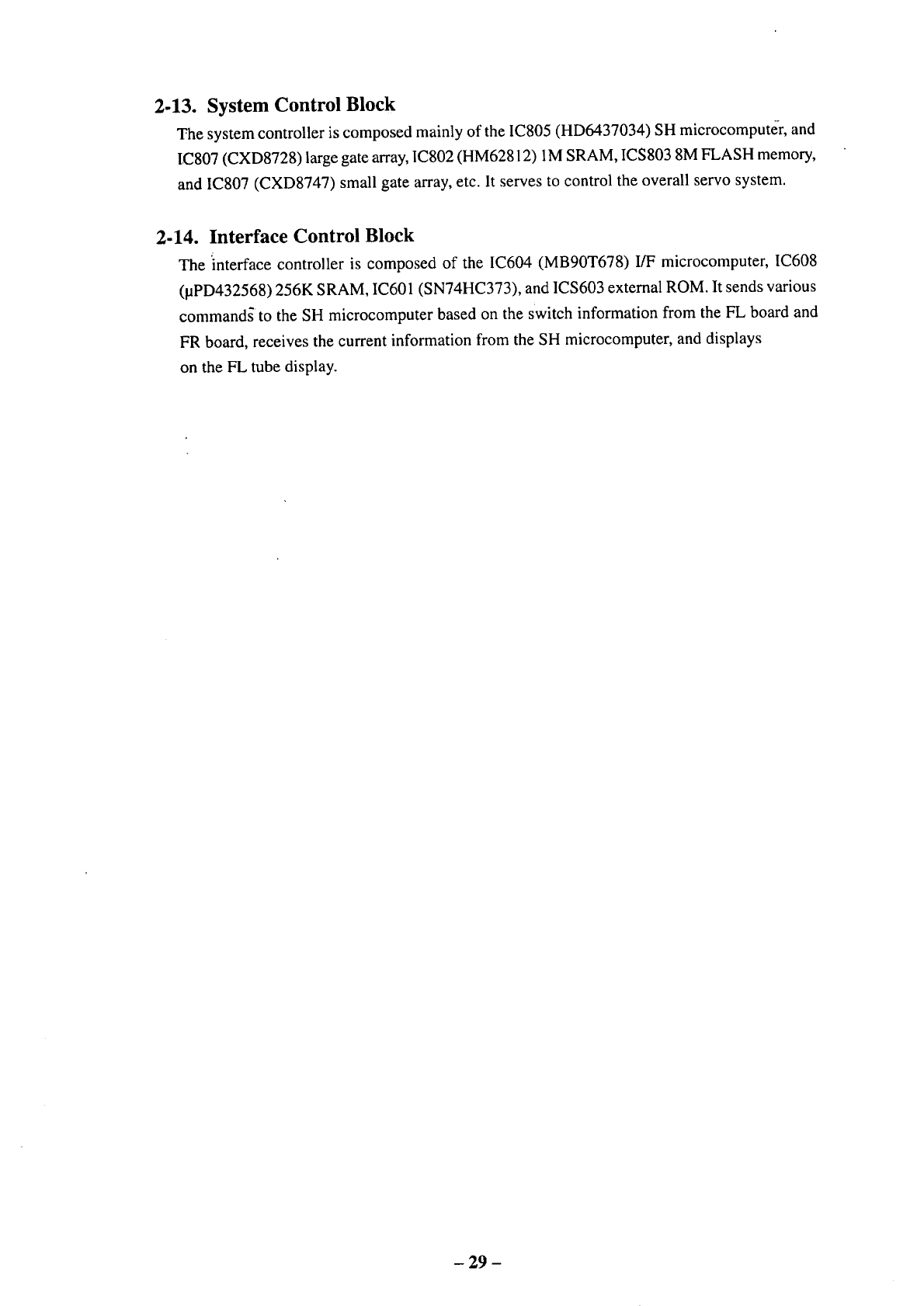

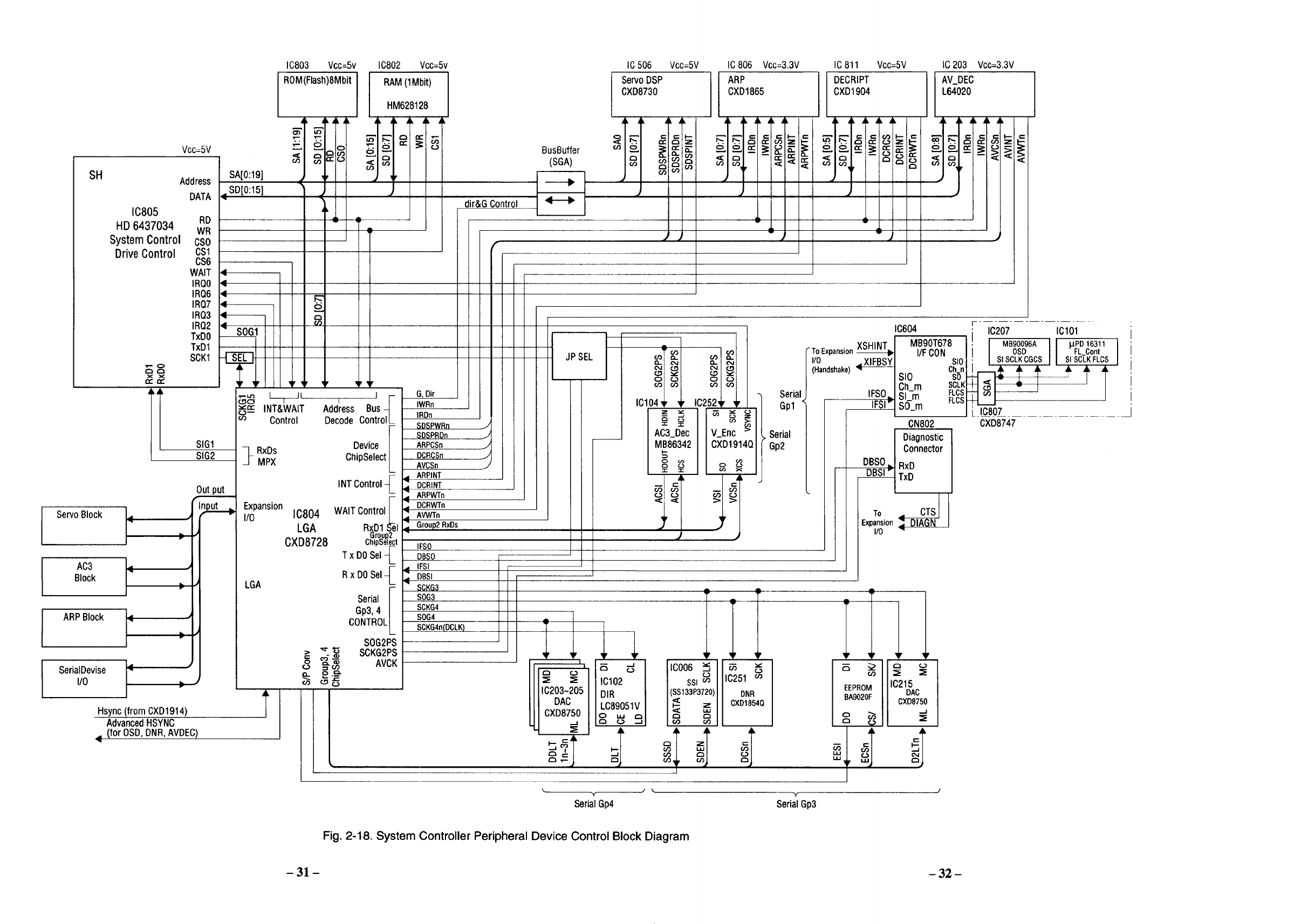

2-13. System Control Block

The system controller is composed mainly of the IC805 (HD6437034) SH microcomputer, and

IC807 (CXD8728) large gate array,1C802 (HM62812) 1M SRAM, ICS803 8M FLASH memory,

and IC807 (CXD8747) small gate array, etc. It serves to control the overall servo system.

2-14. Interface Control Block

The 'interface controller is composed of the IC604 (MBg0T678) I/F microcomputer, IC608

(_PD432568) 256K SRAM, IC601 (SN74HC373), and ICS603 external ROM. It sends various

commands to the SH microcomputer based on the switch information from the FL board and

FR board, receives the current information from the SH microcomputer, and displays

on the FL tube display.

- 29 -

SH

Servo Block

I

AC3 i_

Block

J

ARPBlock i_

J

SerialDevise i_

I/0

SA[0:19]

4SD[0:15]

Vcc=5V

Address

DATA

10805

HD 6437034 RD

WR

System Control CSO

Drive Control CSl

CS6

WAIT

1:3 r'_

XX

r,-- tY-

t

IRQO

IRQ6

IRQ7

IRQ3

IRQ2

TxDO

TxD1

SCK1

SIC1

SIC2

I

SOG1]

Out put

Iv

T

Hsync (from 0XD1914)

AdvancedHSYNC

• (for OSD, DNR,AVDEC)

1(3803 Vcc=5v

ROM(Flash)SMbit

IC802 Vcc=5v

RAM (1Mbit)

HM628128

._k ,LL A

r_ 00 ,,'-

_<_1_

T

•--Lo L JI

{9O T

____ INT&WAIT

co Control

_RxDs

MPX

Expansion

I/O 10804

LGA

CXD8728

T

LGA

=.-

o

fO

Q.

Address Bus

Decode Controll_

Device I

ChipSelectL

INT Control-_

WAlT C:nxt_:ll,

Gro.up.2

Chip_elect

r_

Tx DOSel -_

Rx DOSel

n

Serial [-

Gp3,4 /

CONTROLL

SOG2PS

_" 13 SCKG2PS

_- _ AVCK

=_J3

G,Oir

IWRn

IRDn

SDSPWRn

SDSPRDn

ARPCSn

DCRCSn

AVCSn

4 ARPINT

DCRINT

4ARPWIn

4DCRWrn

AVWTn

4Group2RxOs

4

IFSO

DBSO

IFSI

•DBSI

_CKG3

SOG3

SCKG4

SOG4

SCKG4n(DCLK)

IC 506

Servo DSP

CXD8730

dir&G Control

BusBuffer

(SGA)

J

J

J

J

JPSEL I

101

IC203~205

II DAC

oxo8 2

10102

DIR

LC89051V

o_,

Vcc=5V

,'-" I--

C3 z

_cE

O'3 (:3

00

j

IC806 Vcc=3.3V

ARP

CXD1865

t d, Ai, d

P

I

_._

I

_1_1 _/_1

AC3 Dec VEnc >

MB8-6342I C_D_9_4Q/

;°J

Serial

Gpl "

Serial

Gp2

,coo6_ _

SSl o_ IC251 (n

(SS133P3720) DNR

I_: ,,z, CXD1854Q

(::3 t-'t

IC811 Vcc=5V

DECRIPT

CXD1904

_--I._. _ _ _z_

o,1o "__

;

i

d

IC 203

AV_DEC

L64020

"To Expansion

I/O XI_FBSY

(Handshake)

IFSO=

IFSI_

10604

MB90T678

I/FCON SlO

Ch_n

SlO SO

Ch m SCLK

- FLCS

Sl_m FLCS

SO_m

CN802

Diagnostic

IConnector

DBSO..1 Rxl3

DBSI"t Tx[)

Expansion_ DIAGN I

I/O

II

03

EEPROM

BA9020F

LU

1.1.1

Vcc=3.3V

,,=:

1

IC215

DAC

CXD8750

10207 IC101

MB90096A 11 pPD16311

OSD FL_ConI

SlSCLKCGGS SISCLKFLCS

10807

0XD8747

y.

Serial Gp4

)kY

Serial Gp3

Fig. 2-18. System Controller Peripheral Device Control Block Diagram

- 31 - -32-

3. SERVO BLOCK 3-2. Servo Operation at DVD Play

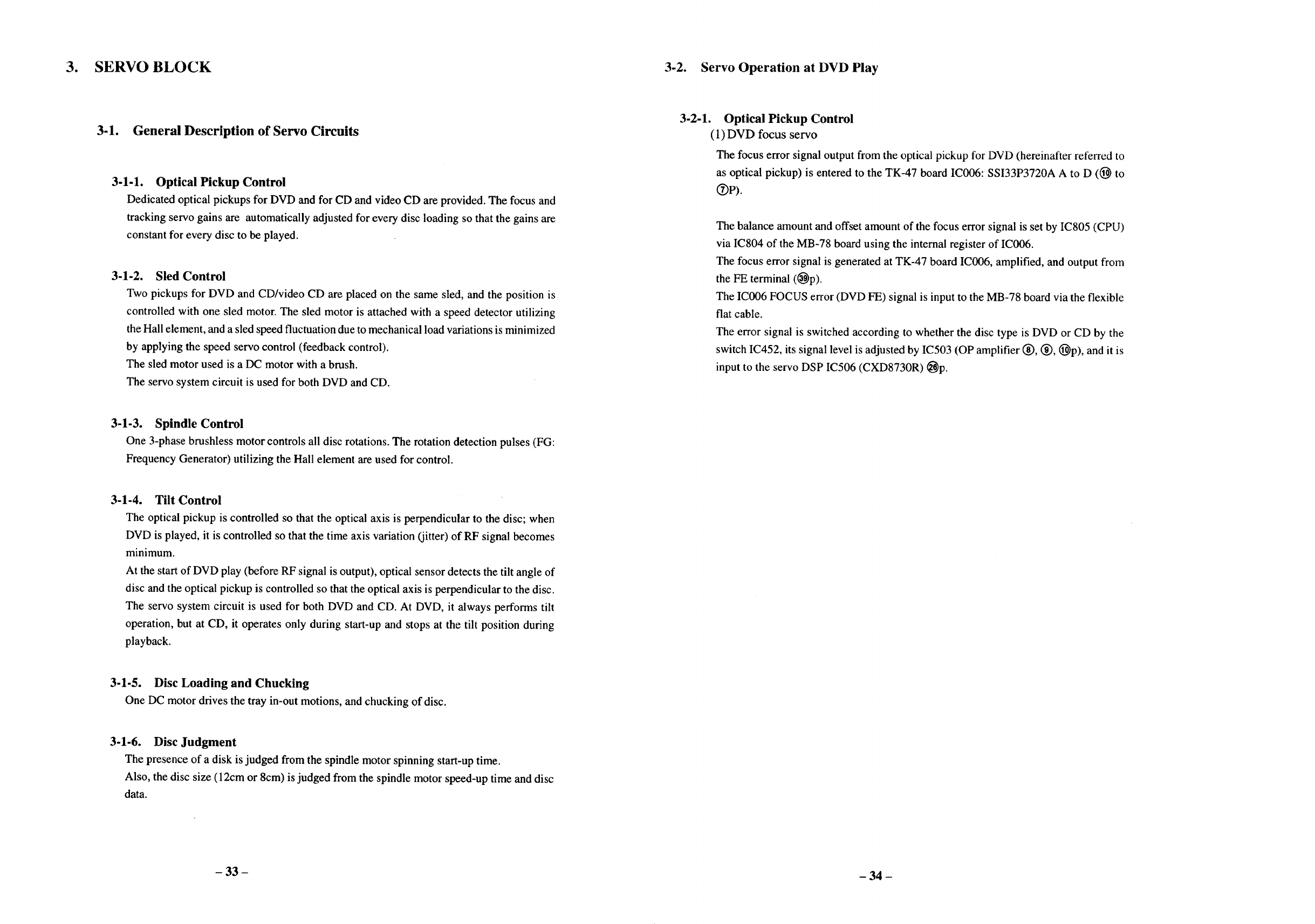

3-1. General Description of Servo Circuits

3-1-1. Optical Pickup Control

Dedicated optical pickups for DVD and for CD and video CD are provided. The focus and

tracking servo gains are automatically adjusted for every disc loading so that the gains are

constant for every disc to be played.

3-1-2. Sled Control

Two pickups for DVD and CD/video CD are placed on the same sled, and the position is

controlled with one sled motor. The sled motor is attached with a speed detector utilizing

the Hall element, and a sled speed fluctuation due to mechanical load variations is minimized

by applying the speed servo control (feedback control).

The sled motor used is a DC motor with a brush.

The servo system circuit is used for both DVD and CD.

3-1-3. Spindle Control

One 3-phase brushless motor controls all disc rotations. The rotation detection pulses (FG:

Frequency Generator) utilizing the Hall element are used for control.

3-1-4. Tilt Control

The optical pickup is controlled so that the optical axis is perpendicular to the disc; when

DVD is played, it is controlled so that the time axis variation (jitter) of RF signal becomes

minimum.

At the start of DVD play (before RF signal is output), optical sensor detects the tilt angle of

disc and the optical pickup is controlled so that the optical axis is perpendicular to the disc.

The servo system circuit is used for both DVD and CD. At DVD, it always performs tilt

operation, but at CD, it operates only during start-up and stops at the tilt position during

playback.

3-1-5. Disc Loading and Chucking

One DC motor drives the tray in-out motions, and chucking of disc.

3-1-6. Disc Judgment

The presence of a disk is judged from the spindle motor spinning start-up time.

Also, the disc size (12cm or 8cm) is judged from the spindle motor speed-up time and disc

data.

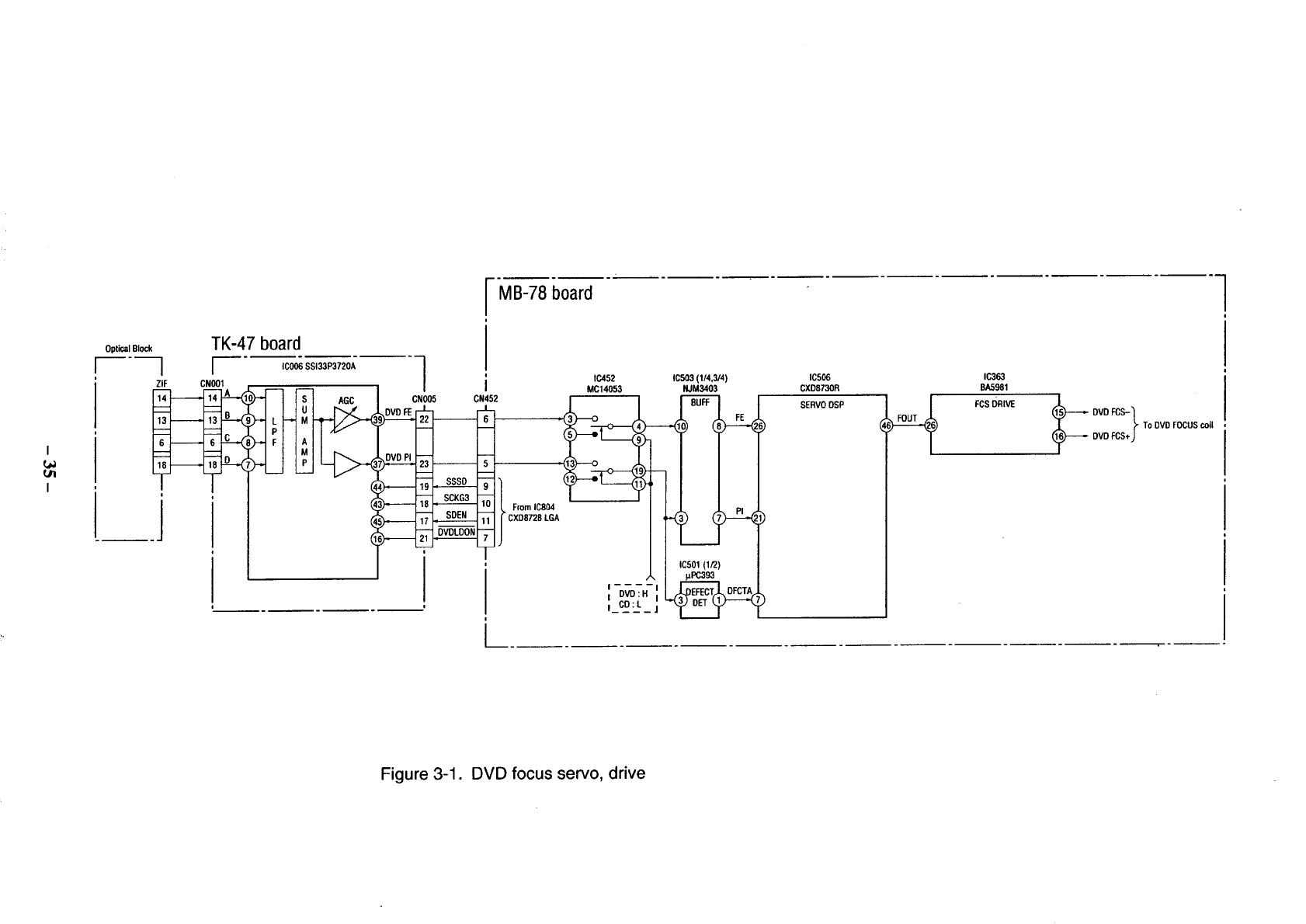

3-2-1. Optical Pickup Control

(1) DVD focus servo

The focus error signal output from the optical pickup for DVD (hereinafter referred to

as optical pickup) is entered to the TK-47 board IC006: SSI33P3720A A to D ((_ to

(_)P).

The balance amount and offset amount of the focus error signal is set by IC805 (CPU)

via IC804 of the MB-78 board using the internal register of IC006.

The focus error signal is generated at TK-47 board IC006, amplified, and output from

the FE terminal (_p).

The IC006 FOCUS error (DVD FE) signal is input to the MB-78 board via the flexible

flat cable.

The error signal is switched according to whether the disc type is DVD or CD by the

switch IC452, its signal level is adjusted by IC503 (OP amplifier (_), (_), (_p), and it is

input to the servo DSP IC506 (CXD8730R) _p.

-33 - - 34 -

I

Ln

I

Optical Block

r

i

i

i

]

ZIF

TK-47 board

IC006 SS133P3720A

CNO01 I

MB-78 board

i

I

' tC452

I MC14053

i

I

CNO05 CN452 r I

_-- _ ,__

_sso7] '._---_--_

s_,,_,<l ,,o,.,cBo,,' ' I

' I__'__ l

|

iC503 (1/4,3/4)

NJM3403

FE

IC501 1/2

IC506

CXD8730R

SERVODSP

IC363

BA5981

FCSDRtVE

DVD FCS--_ To DVD FOCUScoil

DVDFCS+_

Figure 3-1. DVD focus servo, drive

The IC506 Servo DSP: CXD8730 on MB-78 board provides the following control in

the focus servo system.

(a) Focus search

The optical pickup lens is moved toward a disc to turn on the focus servo.

The focus servo loop is turned on when the PI (Pull IN) signal (used for FOK:

Focus OK) exceeds the specification (Vc +0.25V) and the FE signal zero-crossing

is detected.

(b) Focus gain adjustment

The gain of digital filter in the IC506 is automatically adjusted so that the focus

servo loop gain becomes optimum.

Consequently, the optimum gain for each disc to be played can be attained, besides

correction of gain variations in focus actuator (coil) and optical pickup sensor

(photodiode for focusing).

(c) Focus bias adjustment

The focus bias is added to the focus servo filter so as to mi_mize the jitter.

Consequently, a variation of optical pickup and disc can be automatically corrected.

(d) Focus jump

Operation carried out when playing back the DVD dual layer disc to perform

focusing jump between layer 0 (PU side layer) and layer 1 (far end layer).

First the servo loop is turned off, the kick voltage is supplied to the focus actuator,

and the focus is jumped to the targeted layer. As the focus approaches the desired

layer, the FE signal appears. The voltage of this signal is monitored, the deceleration

pulse is generated, and the focus servo is turned ON again after focusing.

These operations from the start to end of jumping are all performed inside the

DSP.

- 36 -

,'topped

CNI_OOmV: : _ i 2ms/div

I_. 10:1 _(2ms_'_v)

:!I' i

:T

...........................ii...................!........;..................................

! :

: !

i

Figure 3-2. Example of S-shape

waveform for the DVD disc

(single layer) MB-78 board

CN303 (_P

;topped

CHI=5_mV: _ + : _$/_v

: : : f i _2QOk875

...... ]....... ]...... ]......... i ........ ??......... ]......... !......... i ........ [........

i: ;i '* i_}i

'!i .... ............il_.............................ii..............

i

......................................................... :......... ! ......... :...................

i :

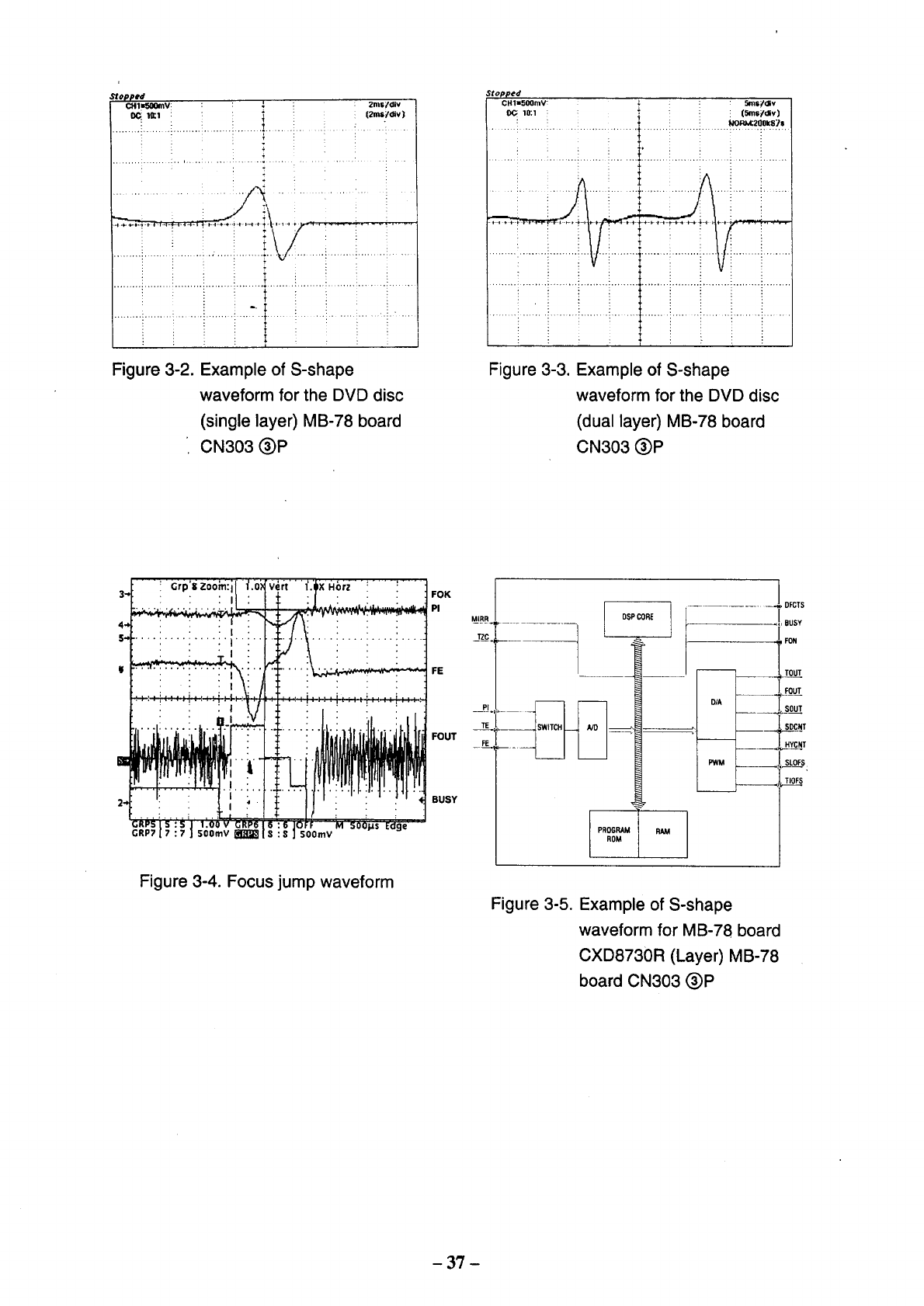

Figure 3-3. Example of S-shape

waveform for the DVD disc

(dual layer) MB-78 board

CN303 (_)P

FOK

PI

FE

FOUT

BUSY

Figure 3-4. Focus jump waveform

M_IRR............

Tzc]

................ .ii, DFCTS

[

OSPCORE IBUSY

I FON

___ _ I,ou,

PWM l _ SLOFS

fTiOFS

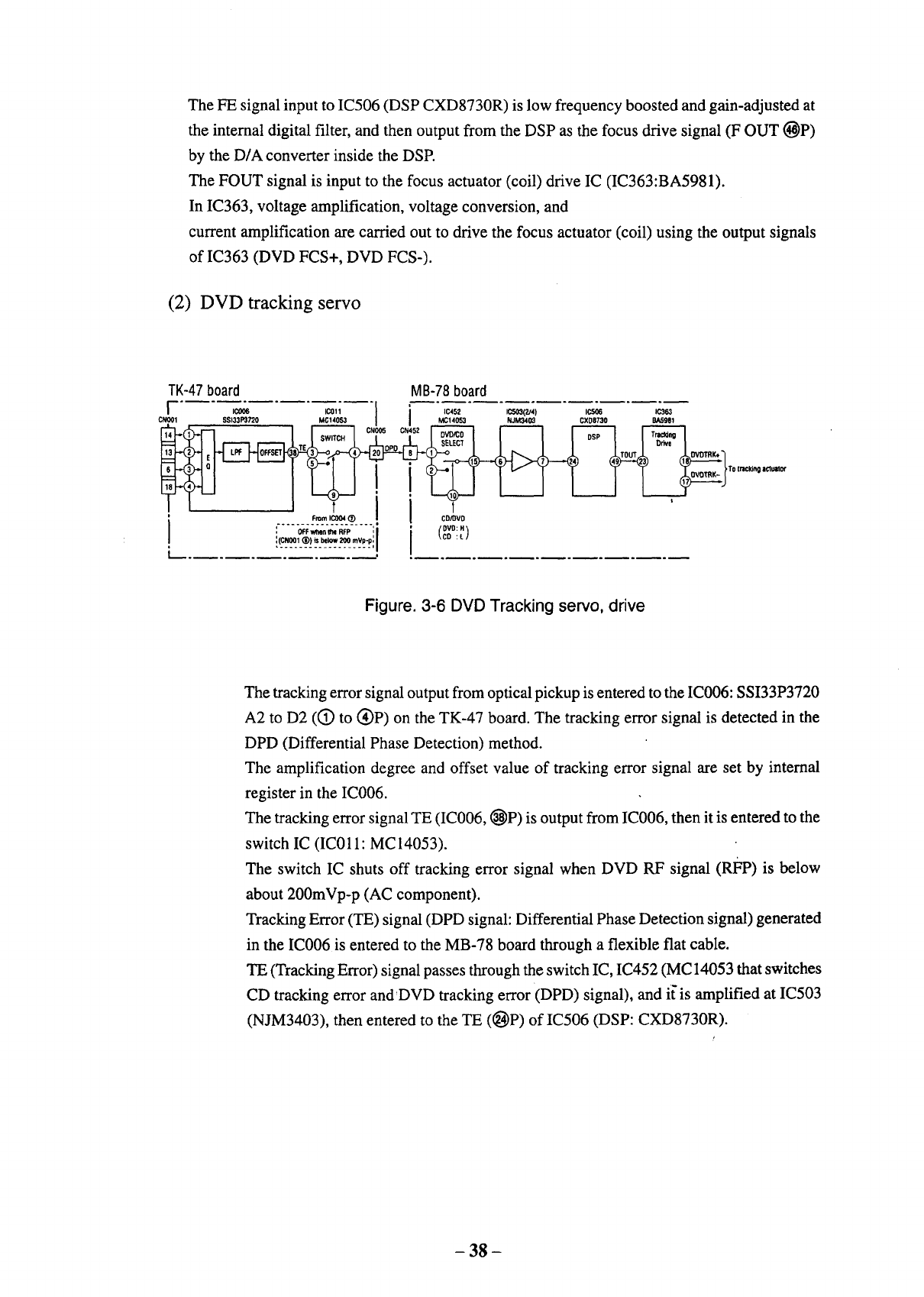

Figure 3-5. Example of S-shape

waveform for MB-78 board

CXD8730R (Layer) MB-78

board CN303 (_)P

-3? -

The FE signal input to IC506 (DSP CXD8730R) is low frequency boosted and gain-adjusted at

the internal digital filter, and then output from the DSP as the focus drive signal (F OUT _)P)

by the D/A converter inside the DSP.

The FOUT signal is input to the focus actuator (coil) drive IC (IC363:BA5981).

In IC363, voltage amplification, voltage conversion, and

current amplification are carried out to drive the focus actuator (coil) using the output signals

of IC363 (DVD FCS+, DVD FCS-).

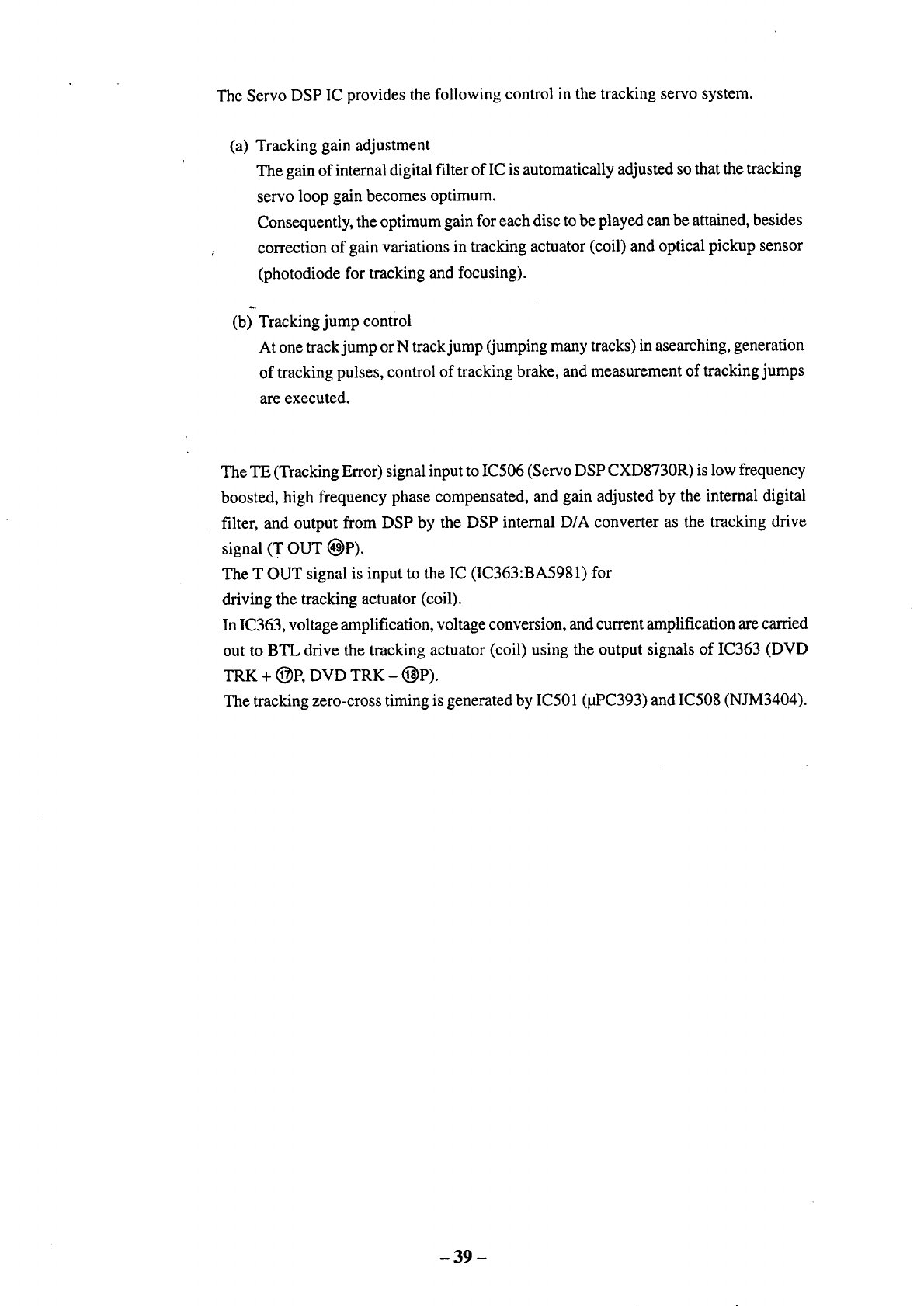

(2) DVD tracking servo

TK-47board MB-78 board

ICG06 IC011 i Ic452 IC503(2/4) IC506 IC363

CNO01 8S133P3720 MC14053 IMC14053 NJM3403 CXD8730 BA5981

DPD TOUT D_I d

'....... F_'*pLc_..__.. _ Ict;iovo

', OFFwf'mnI_ RFP ', _ (OVO: H_

!(.c__ooL._!_ .._,y.vp.-.pl I_co:_/

To tr_kino actuator

Figure. 3-6 DVD Tracking servo, drive

The tracking error signal output from optical pickup is entered to the IC006:SSI33P3720

A2 to D2 (O to (_)P) on the TK-47 board. The tracking error signal is detected in the

DPD (Differential Phase Detection) method.

The amplification degree and offset value of tracking error signal are set by internal

register in the IC006.

The tracking error signal TE (IC006, _P) is output from IC006, then it is entered to the

switch IC (IC011: MC 14053).

The switch IC shuts off tracking error signal when DVD RF signal (RFP) is below

about 200mVp-p (AC component).

Tracking Error (TE) signal (DPD signal: Differential Phase Detection signal) generated

in the IC006 is entered to the MB-78 board through a flexible fiat cable.

TE (Tracking Error) signal passes through the switch IC, IC452 (MC14053 that switches

CD tracking error andDVD tracking error (DPD) signal), and it"is amplified at IC503

(NJM3403), then entered to the TE (_)P) of IC506 (DSP: CXD8730R).

!

- 38 -

The Servo DSP IC provides the following control in the tracking servo system.

(a) Tracking gain adjustment

The gain of intemal digital filter of IC is automatically adjusted so that the tracking

servo loop gain becomes optimum.

Consequently, the optimum gain for each disc to be played can be attained, besides

correction of gain variations in tracking actuator (coil) and optical pickup sensor

(photodiode for tracking and focusing).

(b) Tracking jump control

At one track jump or N track jump (jumping many tracks) in asearching, generation

of tracking pulses, control of tracking brake, and measurement of tracking jumps

are executed.

The TE (Tracking Error) signal input to IC506 (Servo DSP CXD8730R) is low frequency

boosted, high frequency phase compensated, and gain adjusted by the internal digital

filter, and output from DSP by the DSP internal D/A converter as the tracking drive

signal (T OUT _P).

The T OUT signal is input to the IC (IC363:BA5981) for

driving the tracking actuator (coil).

In IC363, voltage amplification, voltage conversion, and current amplification are carded

out to BTL drive the tracking actuator (coil) using the output signals of IC363 (DVD

TRK + _)P, DVD TRK - (_P).

The tracking zero-cross timing is generated by IC501 (1JPC393) and IC508 (NJM3404).

- 39 -

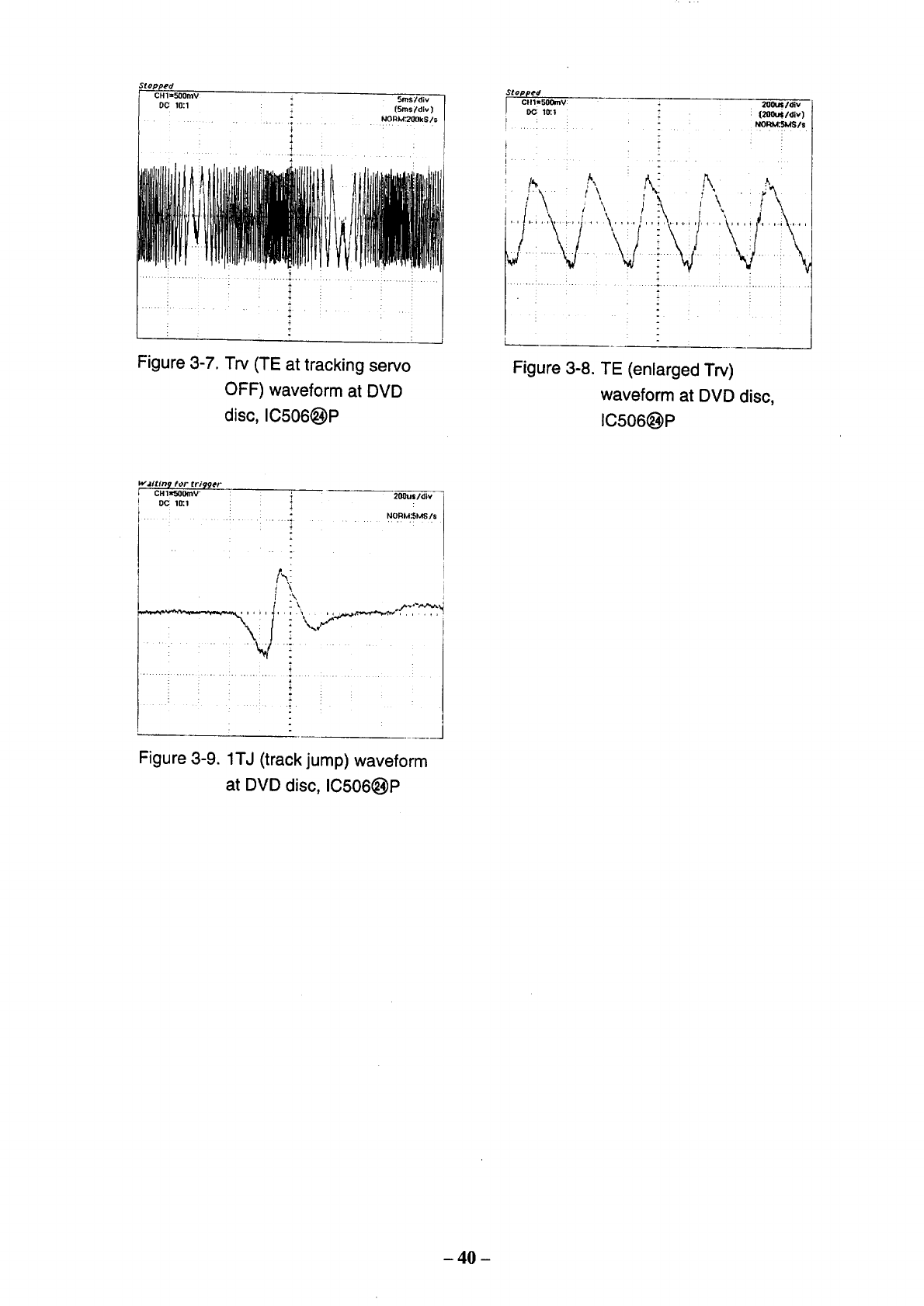

_.t,opped

CHI=500mV

DC 10:1

_" 5m:S_/div r

:: (Sm$t'div)

2NORM:20_kS/S

t

Figure 3-7. Trv (TE at tracking servo

OFF) waveform at DVD

disc, IC506(_)P

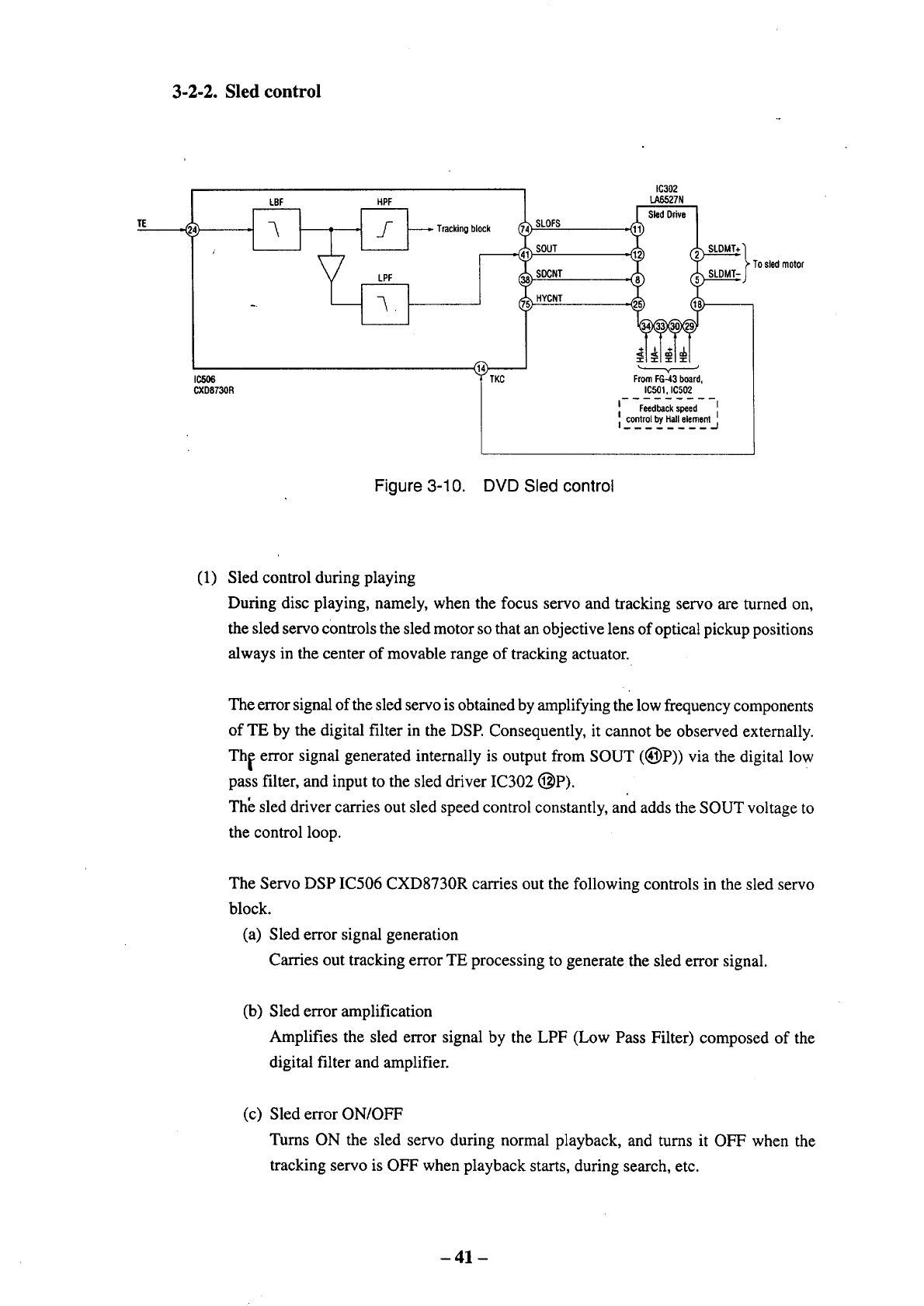

Stopped

CHlt506mV: 200us/dfv

• i (200_/div)

MORM:.SMS/$

Figure 3-8. TE (enlarged Try)

waveform at DVD disc,

IC506(_)P

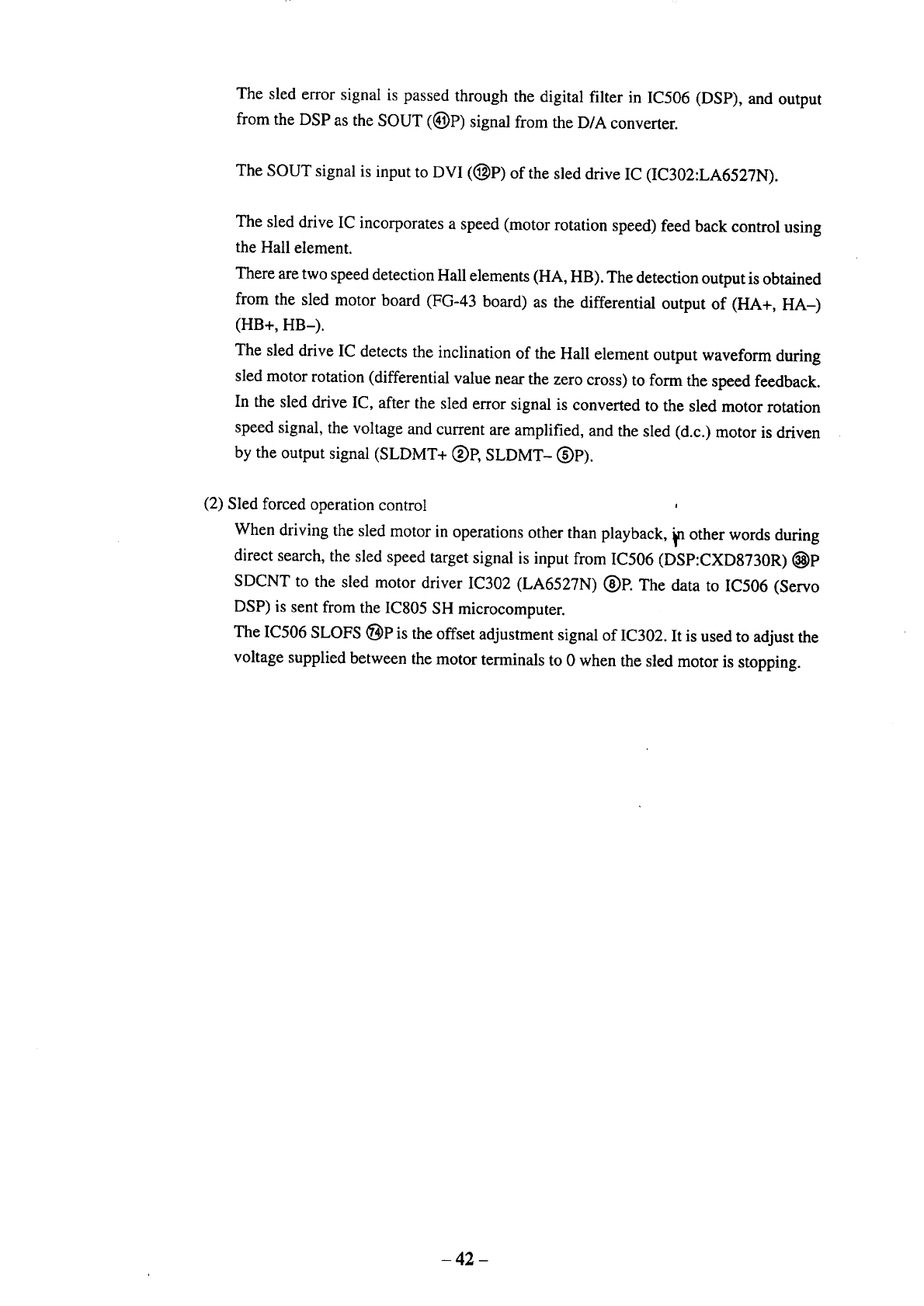

Figure 3-9. 1TJ (track jump) waveform

at DVD disc, IC506_)P

-40 -

3-2-2. Sled control

LBF HPF

=_ Tracking block _,

IC506

CXD8730R

SLOFS

SOUT

SDCNT

HYCNT

IC302

LA6527N

,_ledDrive

,(

,(

,(

.(

FromFG-43 board,

IC501, IC502

I

I Feedback speed I

II control by Hall element j

Figure 3-10. DVD Sled control

' SLDMT _" To sled motor

_J

(1) Sled control during playing

During disc playing, namely, when the focus servo and tracking servo are turned on,

the sled servo controls the sled motor so that an objective lens of optical pickup positions

always in the center of movable range of tracking actuator.

The error signal of the sled servo is obtained by amplifying the low frequency components

of TE by the digital filter in the DSE Consequently, it cannot be observed externally.

Th[ error signal generated internally is output from SOUT ((_)P)) via the digital low

pass filter, and input to the sled driver IC302 (_P).

Thh sled driver carries out sled speed control constantly, and adds the SOUT voltage to

the control loop.

The Servo DSP IC506 CXD8730R carries out the following controls in the sled servo

block.

(a) Sled error signal generation

Carries out tracking error TE processing to generate the sled error signal.

(b) Sled error amplification

Amplifies the sled error signal by the LPF (Low Pass Filter) composed of the

digital filter and amplifier.

(c) Sled error ON/OFF

Tums ON the sled servo during normal playback, and turns it OFF when the

tracking servo is OFF when playback starts, during search, etc.

- 41 -

The sled error signal is passed through the digital filter in IC506 (DSP), and output

from the DSP as the SOUT ((_)P) signal from the D/A converter.

The SOUT signal is input to DVI ((_P) of the sled drive IC (IC302:LA6527N).

The sled drive IC incorporates a speed (motor rotation speed) feed back control using

the Hall element.

There are two speed detection Hall elements (HA, HB). The detection output is obtained

from the sled motor board (FG-43 board) as the differential output of (HA+, HA-)

(HB+, HB-).

The sled drive IC detects the inclination of the Hall element output waveform during

sled motor rotation (differential value near the zero cross) to form the speed feedback.

In the sled drive IC, after the sled error signal is converted to the sled motor rotation

speed signal, the voltage and current are amplified, and the sled (d.c.) motor is driven

by the output signal (SLDMT+ (_)E SLDMT- (_)P).

(2) Sled forced operation control

When driving the sled motor in operations other than playback, _n other words during

direct search, the sled speed target signal is input from IC506 (DSP:CXD8730R) _)P

SDCNT to the sled motor driver IC302 (LA6527N) (_)P. The data to IC506 (Servo

DSP) is sent from the IC805 SH microcomputer.

The IC506 SLOFS (_P is the offset adjustment signal of IC302. It is used to adjust the

voltage supplied between the motor terminals to 0 when the sled motor is stopping.

- 42 -

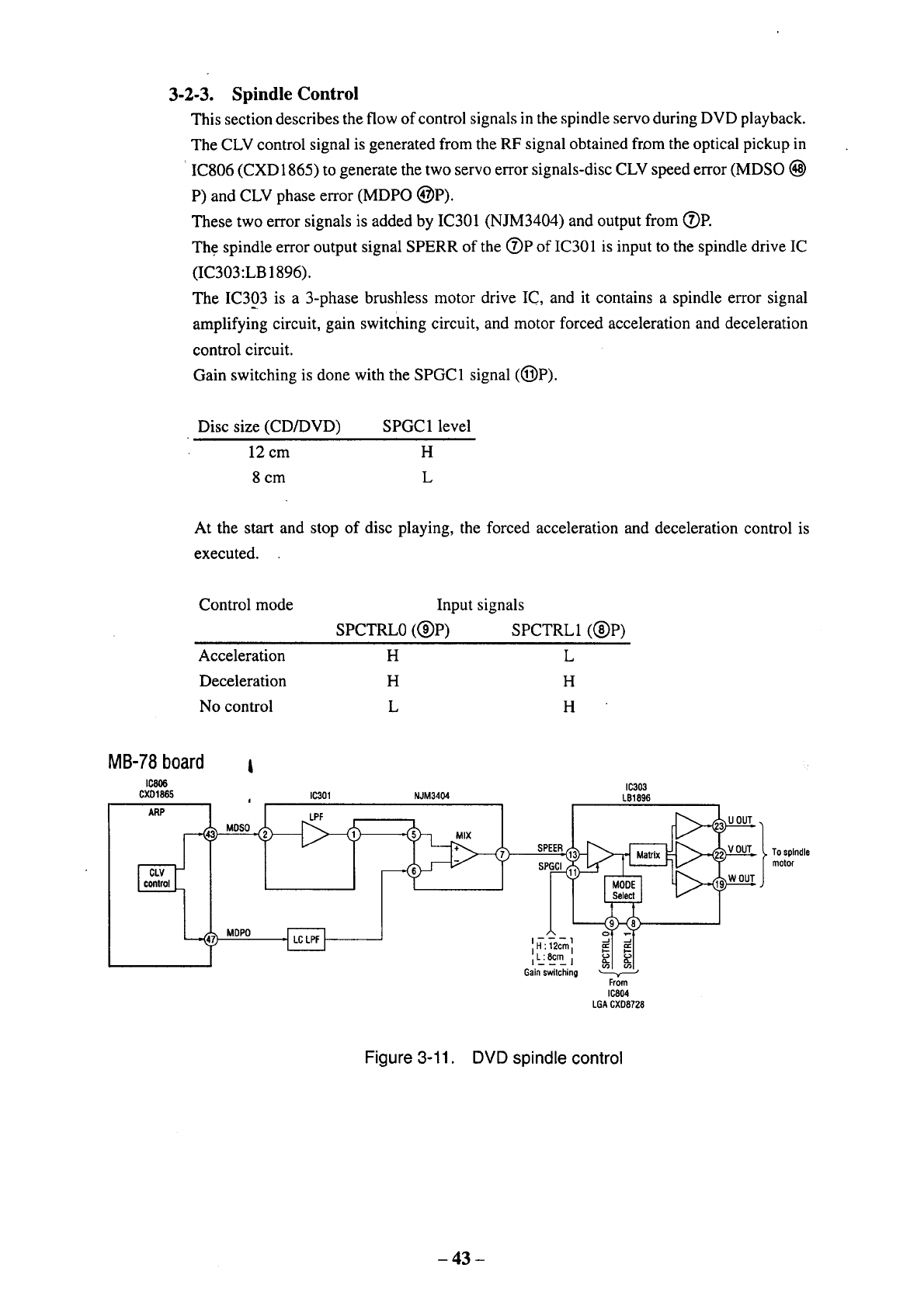

3-2-3. Spindle Control

This section describes the flow of control signals in the spindle servo during DVD playback.

The CLV control signal is generated from the RF signal obtained from the optical pickup in

'IC806 (CXD1865) to generate the two servo error signals-disc CLV speed error (MDSO (_

P) and CLV phase error (MDPO (_)P).

These two error signals is added by IC301 (NJM3404) and output from OP.

The spindle error output signal SPERR of the OP of IC301 is input to the spindle drive IC

(IC303:LB 1896).

The IC303 is a 3-phase brushless motor drive IC, and it contains a spindle error signal

amplifying circuit, gain switching circuit, and motor forced acceleration and deceleration

control circuit.

Gain switching is done with the SPGC1 signal ((_)P).

Disc size (CD/DVD) SPGC1 level

12 cm H

8 cm L

At the start and stop of disc playing, the forced acceleration and deceleration control is

executed.

Control mode Input signals

SPCTRL0 ((_)P) SPCTRL 1 ((_)P)

Acceleration H L

Deceleration H H

No control L H

MB-78 board t

le806

CXD1865

ARP

IC301 NJM3404

MDPO ,I-'_"___

IC303

LB1896

SPEER_

H' 12cm _:l _I

' I I,-

,L:Scm, _1 ;_1

-- -- -- '-ol U_l

Gain switching From

IC804

LGACXD8728

_1 TO spindle

•lmotor

Figure 3-11. DVD spindle control

- 43 -

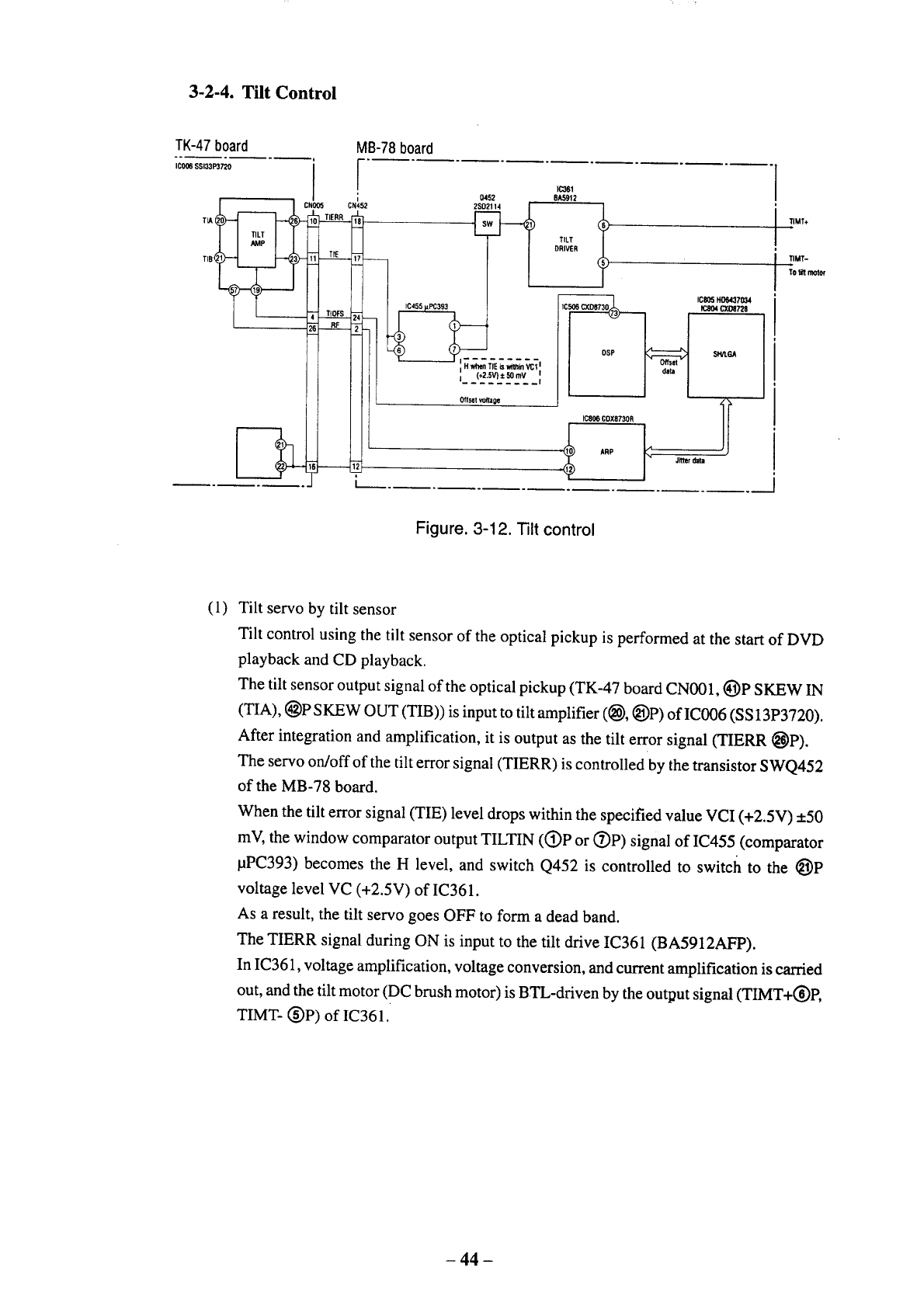

3-2-4. Tilt Control

TK-47board MB-78 board

IC006SSI33P3720

| | CNO06 TIERRcN452

T_

TIB_ TfE

jL..__ TIOFS

0452

2SD2114

Offsetvoffaoe

1(;361

BA5912

TILT t

DRIVER

OSP

tC806 CDXE730R

ARP

IC8051,10_7034

1C804_8

$H/LGA

t,litter

1

1

i

l TIMT÷

I TIMT-

To_ll_m

I

I

I

J

Figure. 3-12. Tilt control

(1) Tilt servo by tilt sensor

Tilt control using the tilt sensor of the optical pickup is performed at the start of DVD

playback and CD playback.

The tilt sensor output signal of the optical pickup (TK-47 board CN001, (_)P SKEW IN

(TIA), _P SKEW OUT (TIB)) is input to tilt amplifier (_), _)P) of IC006 (SS 13P3720).

After integration and amplification, it is output as the tilt error signal (TIERR _)P).

The servo on/off of the tilt error signal (TIERR) is controlled by the transistor SWQ452

of the MB-78 board.

When the tilt error signal (TIE) level drops within the specified value VCI (+2.5V) +50

mV, the window comparator output TILTIN ((_)P or (_)P) signal of IC455 (comparator

pPC393) becomes the H level, and switch Q452 is controlled to switch to the _[])P

voltage level VC (+2.5V) of IC361.

As a result, the tilt servo goes OFF to form a dead band.

The TIERR signal during ON is input to the tilt drive IC361 (BA5912AFP).

In IC361, voltage amplification, voltage conversion, and current amplification is carried

out, and the tilt motor (DC brush motor) is BTL-driven by the output signal (TIMT+(_)P,

TIMT- (_)P) of IC361.

- 44 -

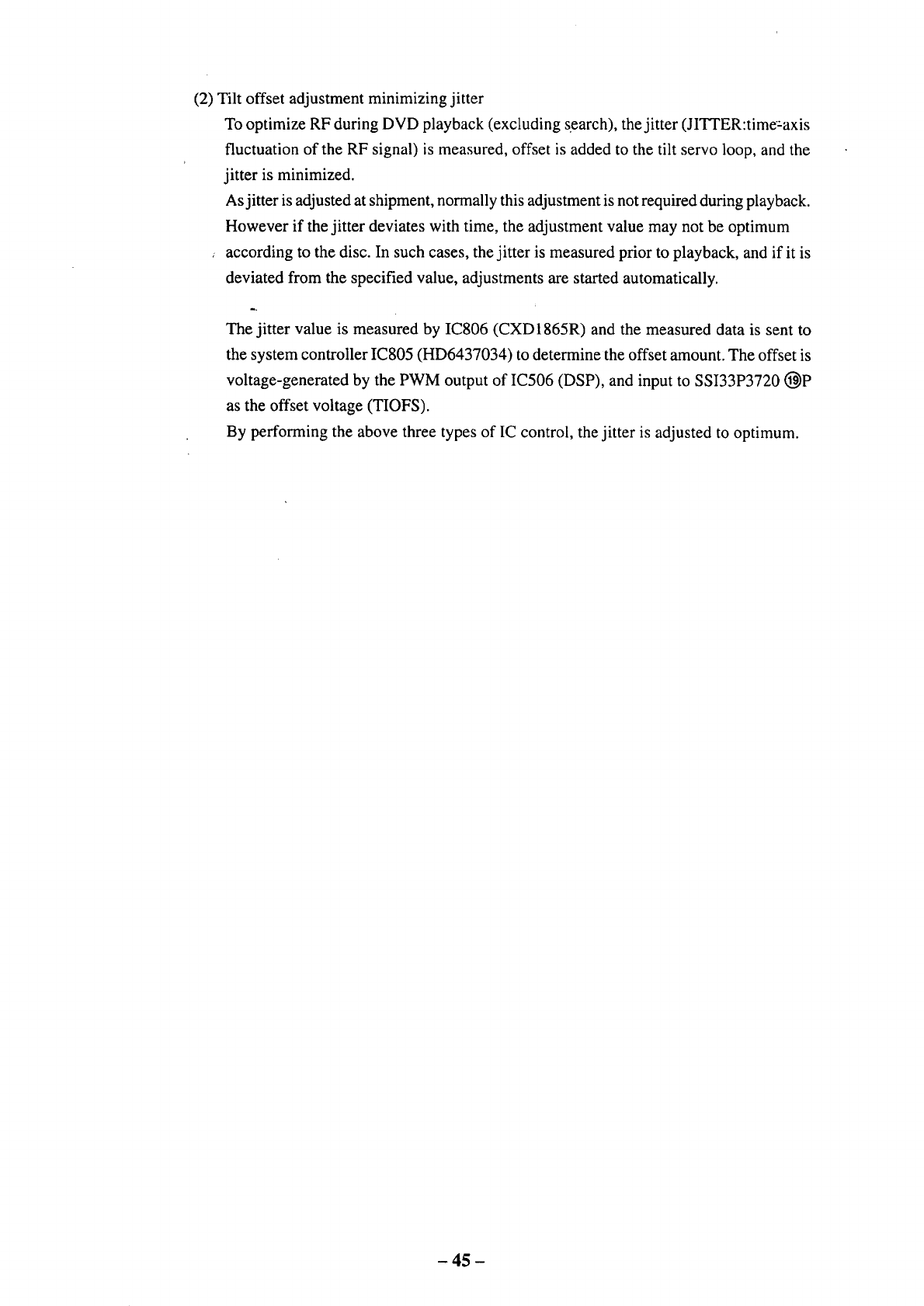

(2) Tilt offset adjustment minimizing jitter

To optimize RF during DVD playback (excluding search), the jitter (JITTER:time:axis

fluctuation of the RF signal) is measured, offset is added to the tilt servo loop, and the

jitter is minimized.

As jitter is adjusted at shipment, normally this adjustment is not required during playback.

However if the jitter deviates with time, the adjustment value may not be optimum

, according to the disc. In such cases, the jitter is measured prior to playback, and if it is

deviated from the specified value, adjustments are started automatically.

i.

The jitter value is measured by IC806 (CXD1865R) and the measured data is sent to

the system controller IC805 (HD6437034) to determine the offset amount. The offset is

voltage-generated by the PWM output of IC506 (DSP), and input to SSI33P3720 (_P

as the offset voltage (TIOFS).

By performing the above three types of IC control, the jitter is adjusted to optimum.

- 45 -

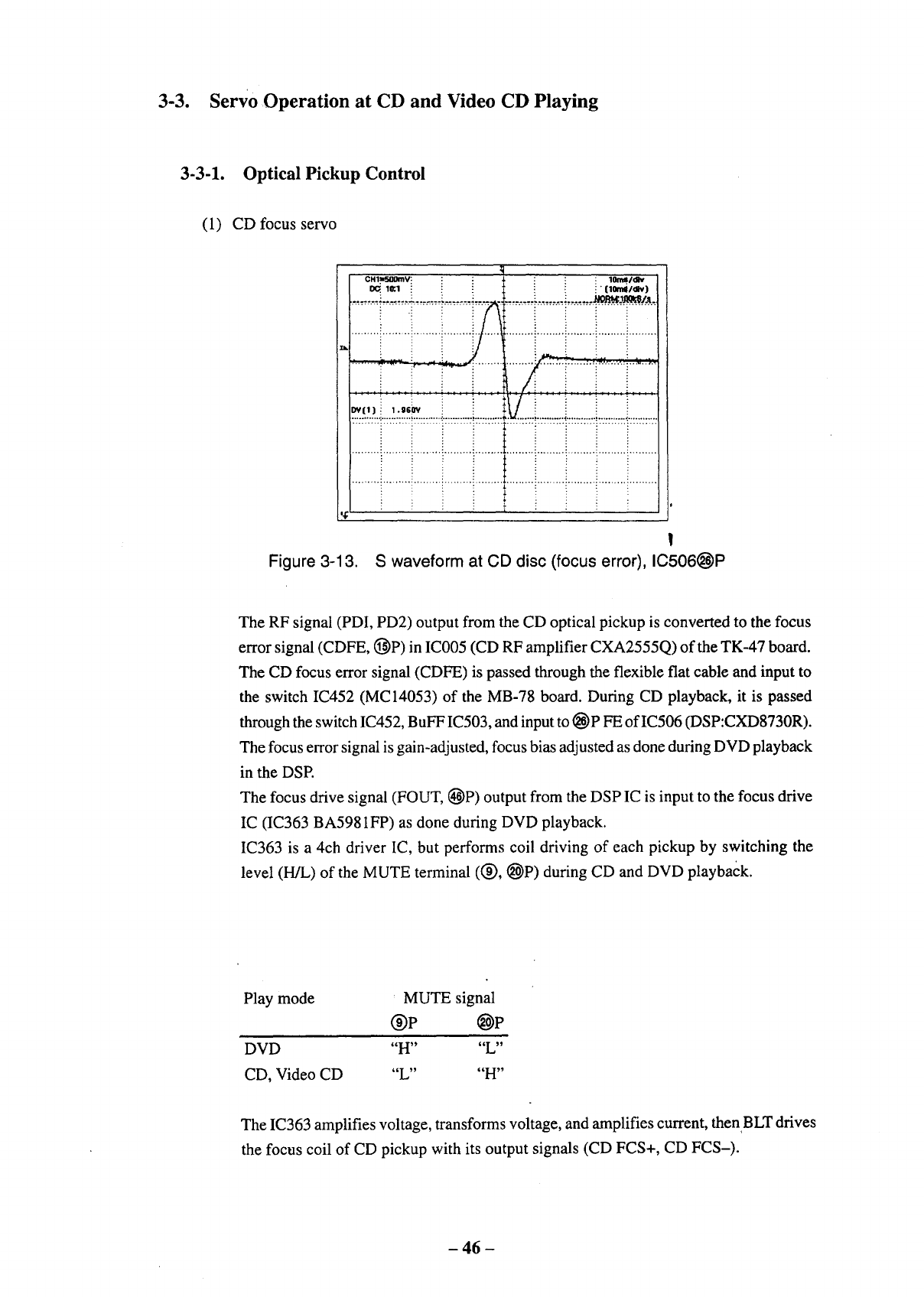

3-3. Servo Operation at CD and Video CD Playing

3-3-1. Optical Pickup Control

(1) CD focus servo

!

CH 1154]OmV: !lOtrnl/dlv

...................i.............................:.............................::.........i........

...................ii.............................t.............................!.........!.........

I

................... {............................. ! ............................. :......... _.........

1

:'i .... T ,, , • . •

!

Figure 3-13. S waveform at CD disc (focus error), IC506_)P

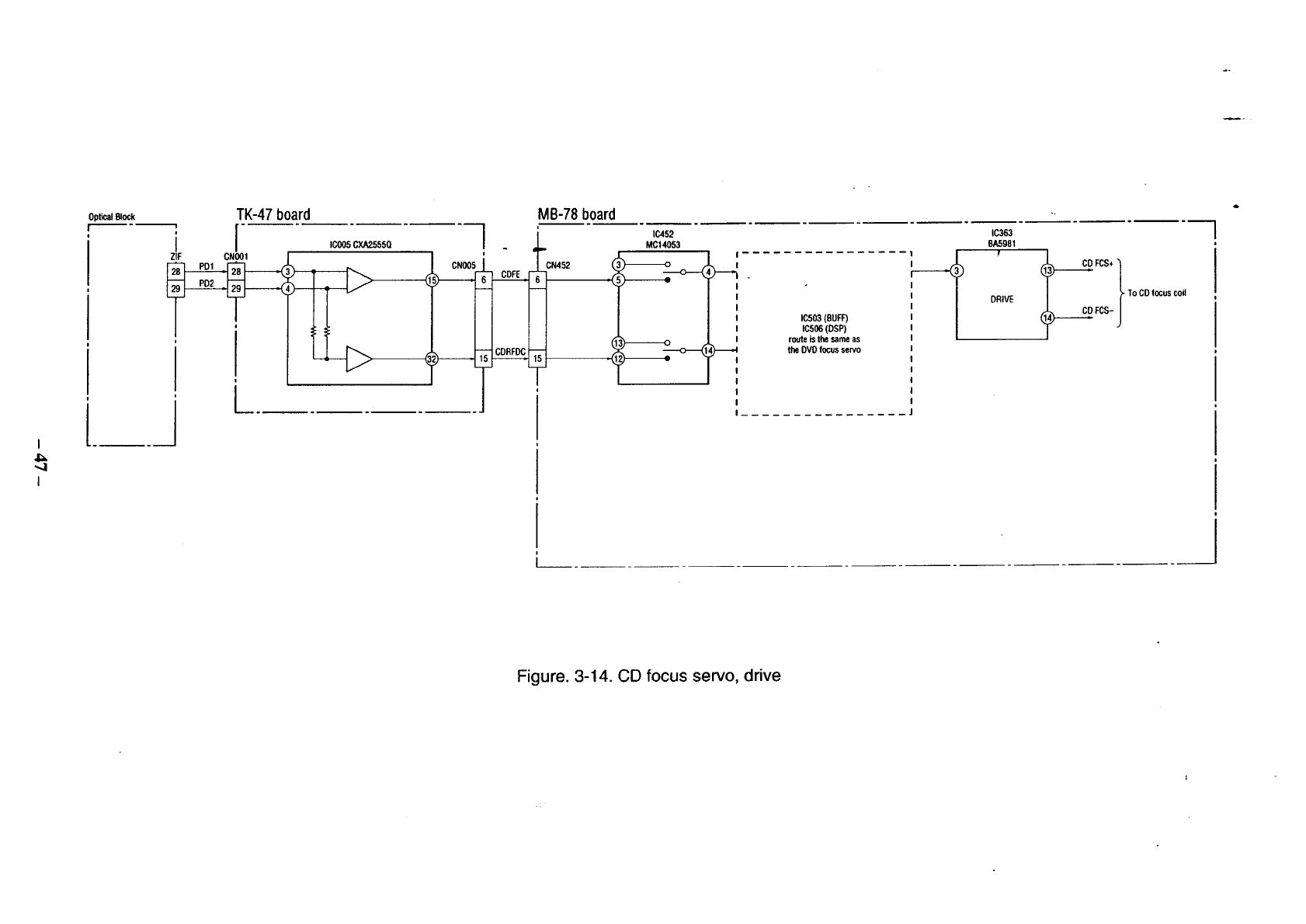

The RF signal (PDI, PD2) output from the CD optical pickup is converted to the focus

error signal (CDFE, (_)P) in IC005 (CD RF amplifier CXA2555Q) of the TK-47 board.

The CD focus error signal (CDFE) is passed through the flexible flat cable and input to

the switch IC452 (MC14053) of the MB-78 board. During CD playback, it is passed

through the switch IC452, BuFF IC503, and input to _)P FE of IC506 (DSP:CXD8730R).

The focus error signal is gain-adjusted, focus bias adjusted as done during DVD playback

in the DSP.

The focus drive signal (FOUT, _P) output from the DSP IC is input to the focus drive

IC (IC363 BA5981FP) as done during DVD playback.

IC363 is a 4ch driver IC, but performs coil driving of each pickup by switching the

level (H/L) of the MUTE terminal ((_), _P) during CD and DVD playback.

Play mode MUTE signal

_)P _P

DVD "H .... L"

CD, Video CD "L .... H"

The IC363 amplifies voltage, transforms voltage, and amplifies current, then BLT drives

the focus coil of CD pickup with its output signals (CD FCS+, CD FCS-).

- 46 -

I

I

OpticalBlock TK-47board

I

ZIF CNO01

IC005 CXA2555Q

CNO05

i

JI

|

L

|

MB-78 board

D

CN452

IC452

MC14053

I

I

I

I

I

I_

IC503(BUFF)

IC506 (DSP)

routeis the sameas

the DVDfocusservo

IC363

BA5981

DRIVE

C_ FCS* 1

To CD focuscoil

_cs-j

1

i

L_.

Figure. 3-14. CD focus servo, drive

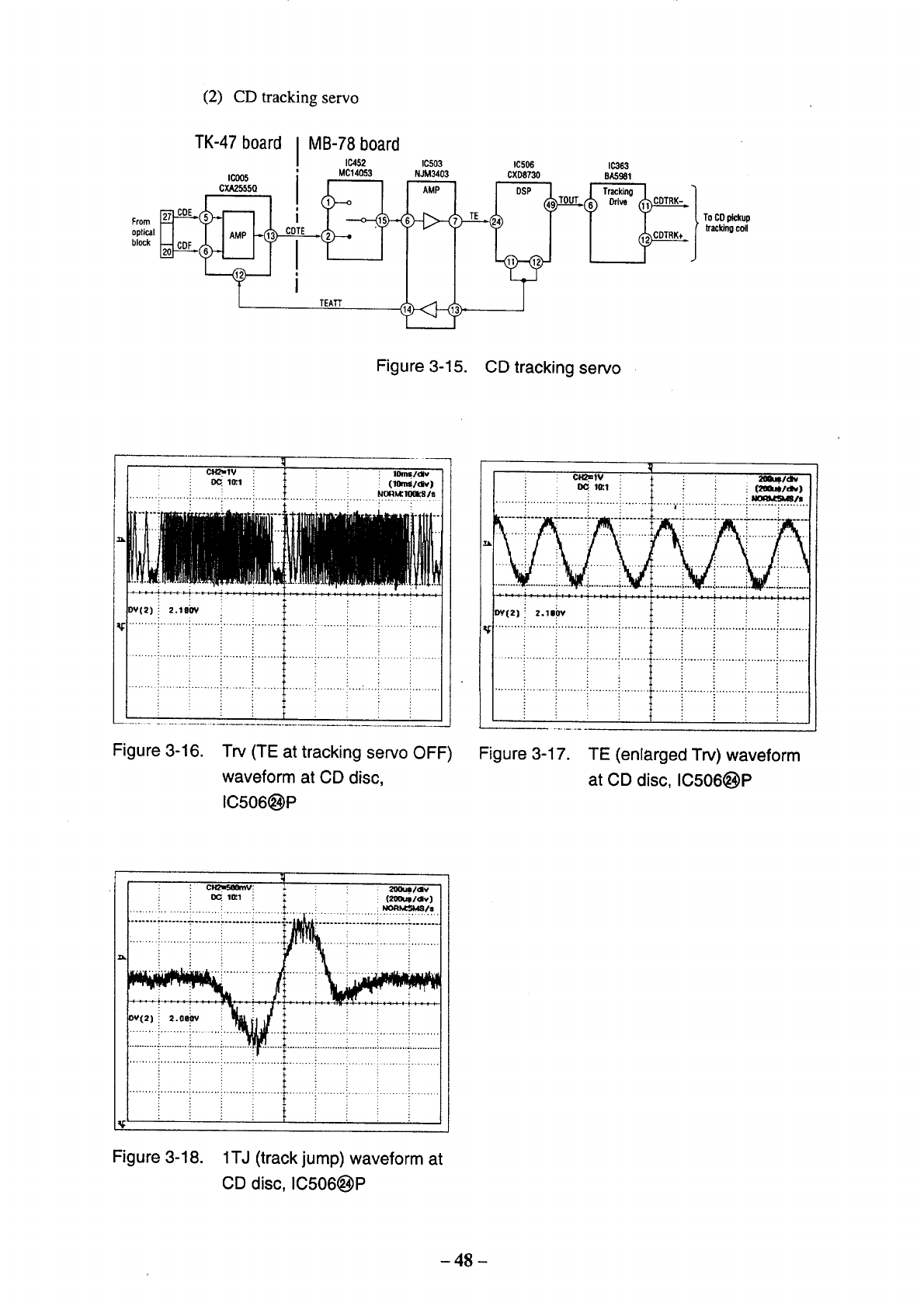

(2) CD tracking servo

From

optical

block

TK-47 board

s

IC005

CXA25550

c[

MB-78 board

IC452 IC503

MC14053 NJM3403 IC506

CXD8730 le_3

BA5981

ToCO_up

trackingcoil

Figure 3-15. CD tracking servo

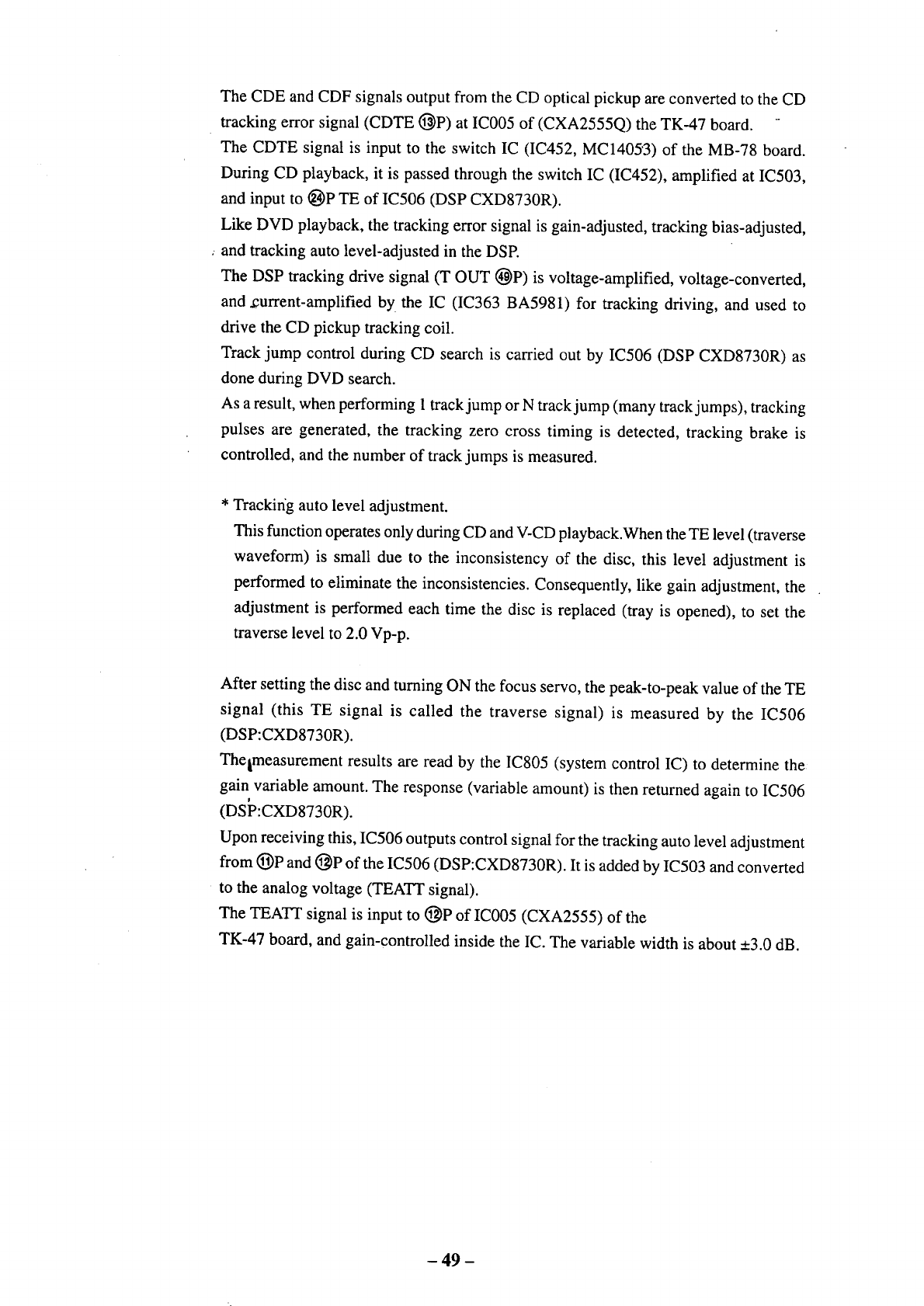

Figure 3-16. Try (TE at tracking servo OFF)

waveform at CD disc,

IC5061_)P

iCH2=lV i i 2muild_

.OC I_I - i (2Wu*/d_]

! :: i i _/,

................... i ......... i................... t ...... _! ......... ! ................... !.........

,.j

i+.

_(zl : z.1#_

'_i.........i.........i.....................................................................i.........

.........:........._..................._.........•.......................................;........

:?

Figure 3-17. TE (enlarged Try) waveform

at CD disc, IC506(_)P

cmn,,_mv: !Zoo_,/a_v

:iNO_M:SM_Is

........ ÷....... ÷....... _........ _....... _," _........ ._....... .;........ F........

o',',i'.o'_ i_,i/_ i i i i

................................................. ÷ ................................................

.............................i........._:........._.................................................

• . : , :: !

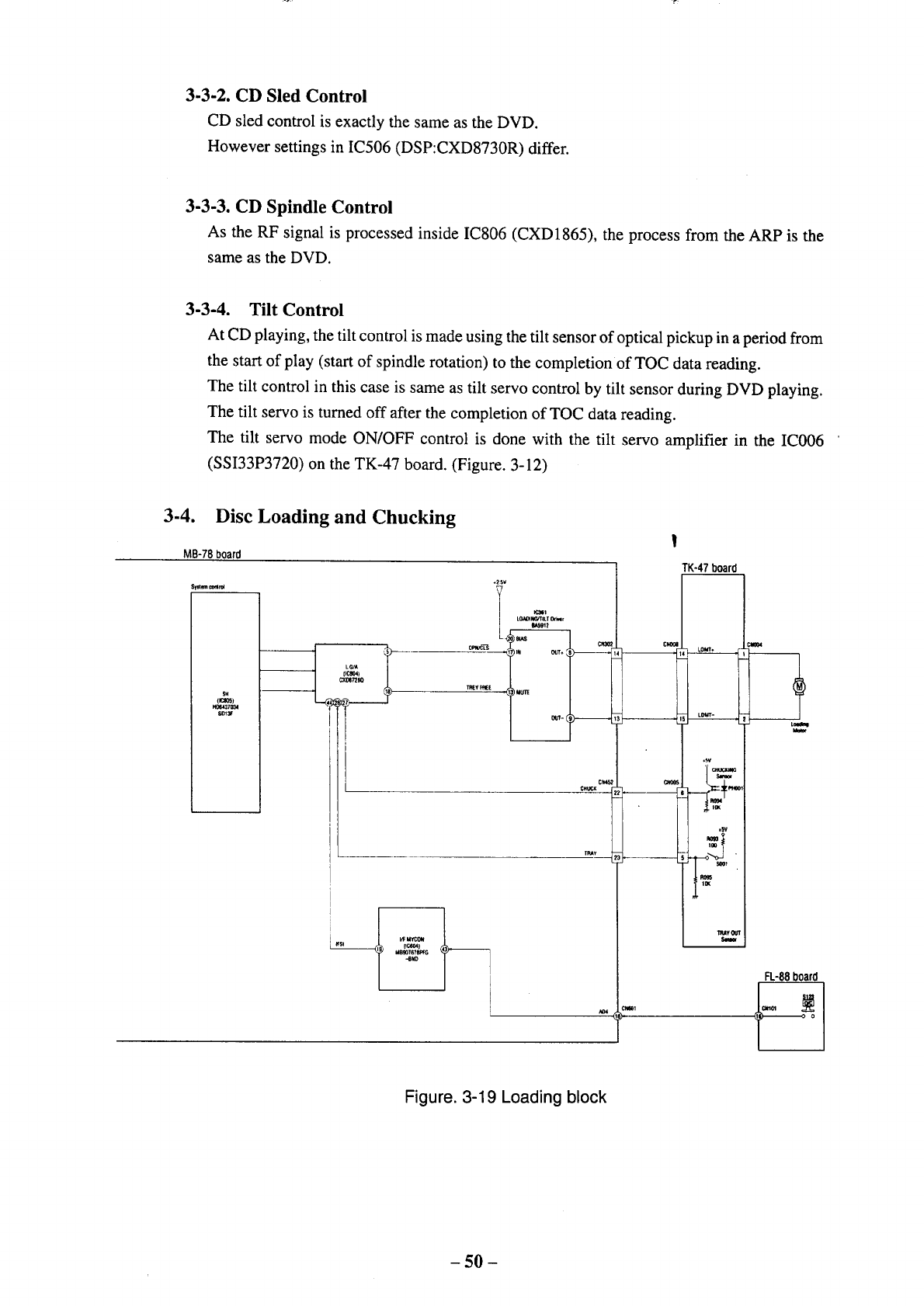

Figure 3-18. 1TJ (track jump) waveform at

CD disc, IC506(_)P

- 48 -

The CDE and CDF signals output from the CD optical pickup are converted to the CD

tracking error signal (CDTE (_)P) at IC005 of (CXA2555Q) the TK-47 board. -

The CDTE signal is input to the switch IC (IC452, MC1405'3) of the MB-78 board.

During CD playback, it is passed through the switch IC (IC452), amplified at IC503,

and input to _)P TE of IC506 (DSP CXD8730R).

Like DVD playback, the tracking error signal is gain-adjusted, tracking bias-adjusted,

and tracking auto level-adjusted in the DSP.

The DSP tracking drive signal (T OUT (_)P) is voltage-amplified, voltage-converted,

and .current-amplified by the IC (IC363 BA5981) for tracking driving, and used to

drive the CD pickup tracking coil.

Track jump control during CD search is carried out by IC506 (DSP CXD8730R) as

done during DVD search.

As a result, when performing 1 track jump or N track jump (many track jumps), tracking

pulses are generated, the tracking zero cross timing is detected, tracking brake is

controlled, and the number of track jumps is measured.

* Tracking auto level adjustment.

This function operates only during CD and V-CD playback.When the TE level (traverse

waveform) is small due to the inconsistency of the disc, this level adjustment is

performed to eliminate the inconsistencies. Consequently, like gain adjustment, the

adjustment is performed each time the disc is replaced (tray is opened), to set the

traverse level to 2.0 Vp-p.

After setting the disc and turning ON the focus servo, the peak-to-peak value of the TE

signal (this TE signal is called the traverse signal) is measured by the IC506

(DSP:CXD8730R).

The|measurement results are read by the IC805 (system control IC) to determine the

gain variable amount. The response (variable amount) is then returned again to IC506

f

(DSP:CXD8730R).

Upon receiving this, IC506 outputs control signal for the tracking auto level adjustment

from (_)P and (_P of the IC506 (DSP:CXD8730R). It is added by IC503 and converted

to the analog voltage (TEATT signal).

The TEATr signal is input to _)P of IC005 (CXA2555) of the

TK-47 board, and gain-controlled inside the IC. The variable width is about _+3.0 dB.

- 49 -

3-3-2. CD Sled Control

CD sled control is exactly the same as the DVD.

However settings in IC506 (DSP:CXD8730R) differ.

3-3-3. CD Spindle Control

As the RF signal is processed inside IC806 (CXD1865), the process from the ARP is the

same as the DVD.

3-3-4. Tilt Control

At CD playing, the tilt control is made using the tilt sensor of optical pickup in a period from

the start of play (start of spindle rotation) to the completion of TOC data reading.

The tilt control in this case is same as tilt servo control by tilt sensor during DVD playing.

The tilt servo is turned off after the completion of TOC data reading.

The tilt servo mode ON/OFF control is done with the tilt servo amplifier in the IC006

(SSI33P3720) on the TK-47 board. (Figure. 3-12)

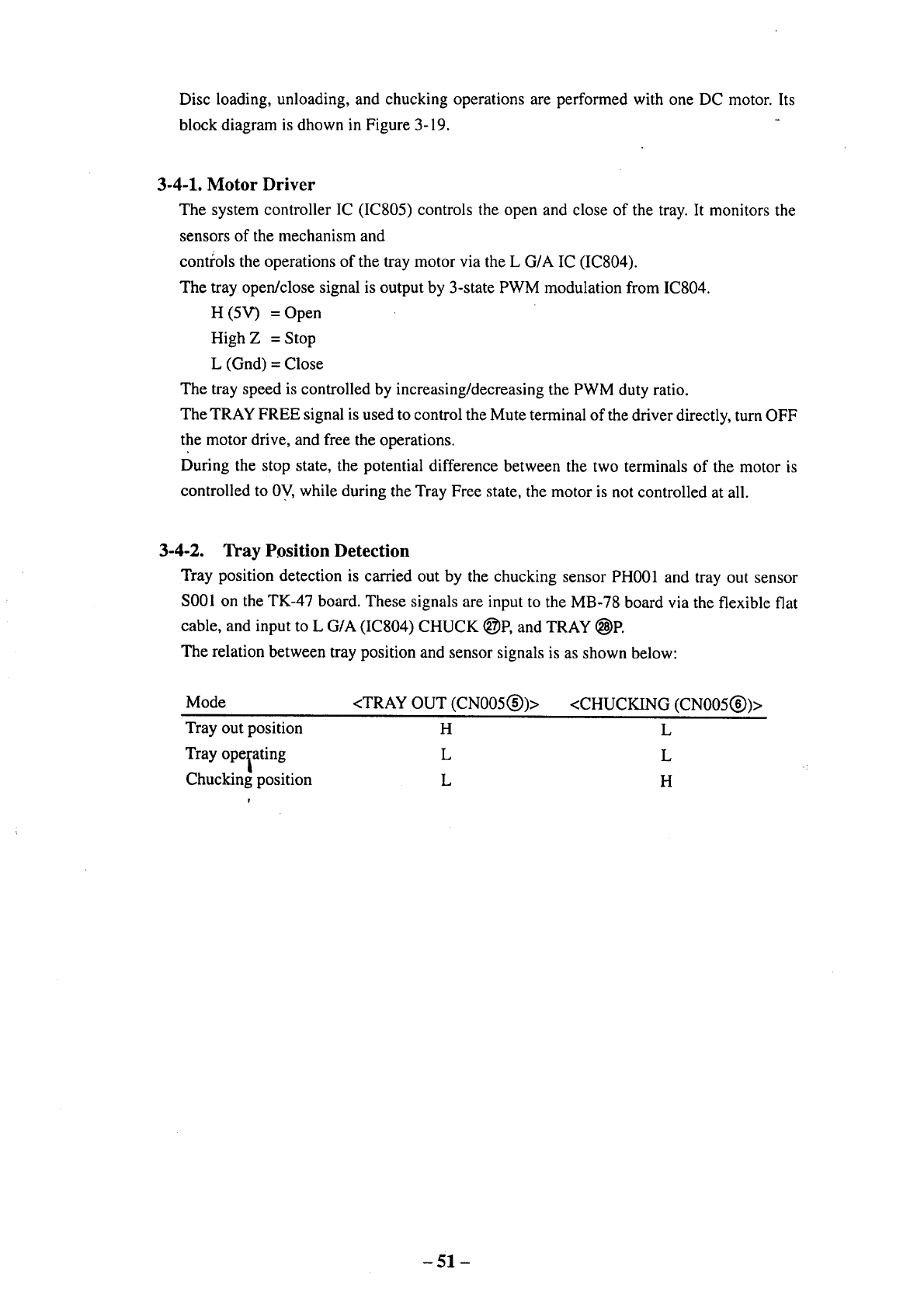

3-4. Disc Loading and Chucking

MB-78board

HO_3r_

S013_

IIC_)

C_t_2eO

LOADff_w_TU.TOfkqz

T_Y _t

C_

CKUCK CN00S

)C_01

!

TK-47board

C_l, !LOM1. •

, LOUT- •

I (_lCXlt_

n

,,w

t_

FL-88board

Figure. 3-19 Loading block

- 50 -

Disc loading, unloading, and chucking operations are performed with one DC motor. Its

block diagram is dhown in Figure 3-19.

3-4-1. Motor Driver

The system controller IC (IC805) controls the open and close of the tray. It monitors the

sensors of the mechanism and

conti:ols the operations of the tray motor via the L G/A IC (IC804).

The tray open/close signal is output by 3-state PWM modulation from IC804.

H (5V) = Open

High Z = Stop

L (Gnd)= Close

The tray speed is controlled by increasing/decreasing the PWM duty ratio.

The TRAY FREE signal is used to control the Mute terminal of the driver directly, turn OFF

the motor drive, and free the operations.

During the stop state, the potential difference between the two terminals of the motor is

controlled to 0V, while during the Tray Free state, the motor is not controlled at all.

3-4-2. Tray Position Detection

Tray position detection is carded out by the chucking sensor PH001 and tray out sensor

S001 on the TK-47 board. These signals are input to the MB-78 board via the flexible flat

cable, and input to L G/A (IC804) CHUCK _)P, and TRAY _P.

The relation between tray position and sensor signals is as shown below:

Mode <TRAY OUT (CN005(_))> <CHUCKING (CN005(_))>

Tray out position H L

Tray opefating L L

Chucking position L H

!

-51 -

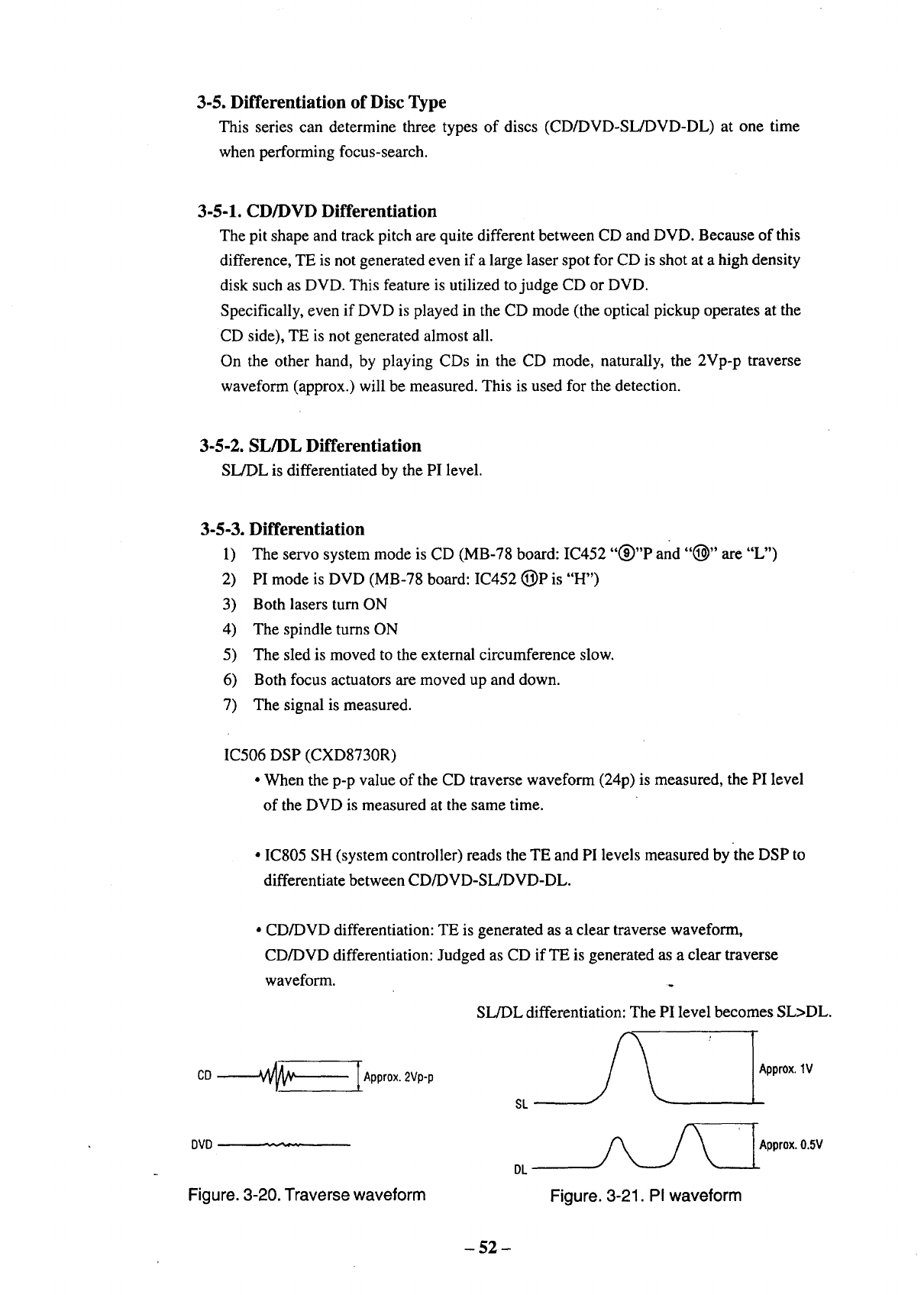

3-5. Differentiation of Disc Type

This series can determine three types of discs (CD/DVD-SL/DVD-DL) at one time

when performing focus-search.

3-5-1. CD/DVD Differentiation

The pit shape and track pitch are quite different between CD and DVD. Because of this

difference, TE is not generated even if a large laser spot for CD is shot at a high density

disk such as DVD. This feature is utilized to judge CD or DVD.

Specifically, even if DVD is played in the CD mode (the optical pickup operates at the

CD side), TE is not generated almost all.

On the other hand, by playing CDs in the CD mode, naturally, the 2Vp-p traverse

waveform (approx.) will be measured. This is used for the detection.

3-5-2. SL/DL Differentiation

SL/DL is differentiated by the PI level.

3-5 -3.

1)

2)

3)

4)

5)

6)

7)

Differentiation

The servo system mode is CD (MB-78 board: IC452 "(_)"P and "(_" are "L")

PI mode is DVD (MB-78 board: IC452 (_)P is "H")

Both lasers turn ON

The spindle turns ON

The sled is moved to the external circumference slow.

Both focus actuators are moved up and down.

The signal is measured.

IC506 DSP (CXD8730R)

•When the p-p value of the CD traverse waveform (24p) is measured, the PI level

of the DVD is measured at the same time.

• IC805 SH (system controller) reads the TE and PI levels measured bythe DSP to

differentiate between CD/DVD-SL/DVD-DL.

• CD/DVD differentiation: TE is generated as a clear traverse waveform,

CD/DVD differentiation: Judged as CD if TE is generated as a clear traverse

waveform.

CD __h_ I Approx. 2Vp-p

SL/DL differentiation: The PI level becomes SL>DL.

•_'IApprox.1V

SL

OVO ----.... -

Figure. 3-20. Traverse waveform

DL

Figure. 3-21. PI waveform

,rox.0.5V

-52 -

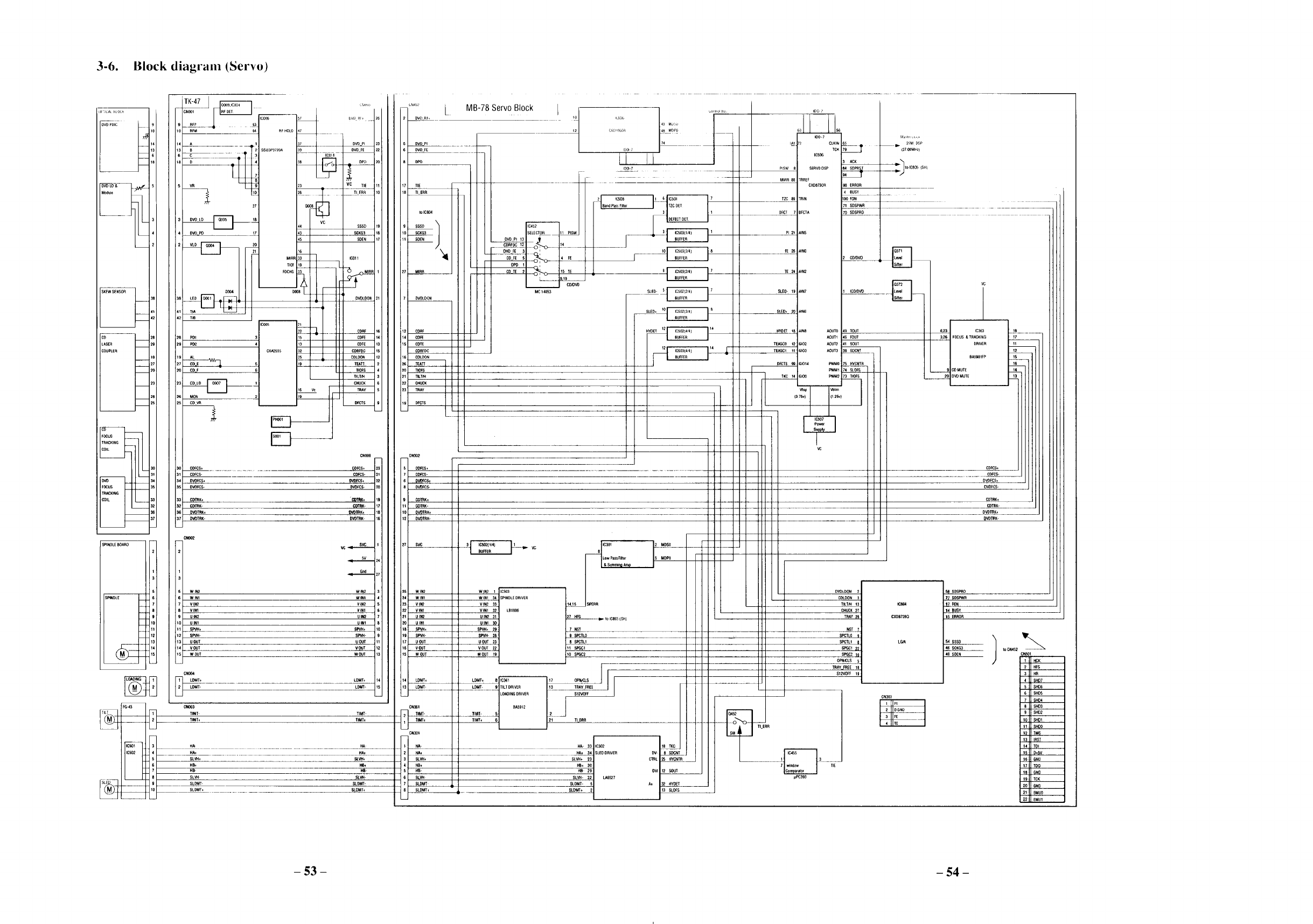

3-6. Block diagram (Servo)

,_ :k;AL _LOCK

DVDPDIC 9

14

18

S

38

4t

42

t9

27

20

23

26

25

FOCUS

TRACKING

COIL

3O

TR._KtNG

COIL i

SPINDLEBOARO

JTK-47 J

9_ icoo6 57

lO RFU 64 _F HOLO4Z

14 A ........ 1 37

13 B 2 ssi33P372oA 39

R C .... 3

_e D 4 38

7

5 VR 23

26

27 _08

3OVULO _VC

41

4 OVDPO lr 43

MIRa

TIOF

FOCHG

29 PD2 4

CX_SS5

19 AL

27 E

2O CD.F F

23 cp LC i

_ cx/_2555 _ I I- ---- 16 VC

121

uv_) Rh

DVDP_

OVDFE

_Pa

VC Tie

•TIERR

ssso

COKG3

i(:Oll

CRRF

COTE

CORFOC

COLCON

tEAl1

t_OFS

CHUCK

TRAY

_CTS

C_(

COFCR+

D_,FCS-

c¢_x,

CDTRK-

C_008

DVDTRK,

OYOTRK-

WIN2

WlNt

VlN2

VINt

CIN2

UIN1

SPVH,

SPVH-

UCOT

VCOT

w OUT

131

151 WIN2

]RL WiN1

17L VIN2

I81 Wm

I 9 I UIN2

]tOL UIN1

J'L s_.

It2L RPVH.

bUL uout

114L vOut

bSL wOUT

CNOO4

LDMT÷

LDMT-

LDMT+

LDMT-

1-43 CN0O3

TIMT.

TIMT,

TIMT-

TIMT*

IC501 HA

IC502 HA_ .............

Ti_7-

HB*

HB-

__ SLVH

SLDMT-

HA

SLVH+

He,

HB-

SLVH-

SLOMT-

SLOMT+

DVO FE

OPD

C_3OZ

I_I OFCS+

_U-

OVDFCS-

COr_K+

COTRK- '

RVDTRK÷

RVDTRK-

S_

w IN2

W I_1

VIN2

ViN1

U IN2

U IR1

S_VH÷

SPVH-

U OUT --

VOUT

WOUT

LDMT*

ON3_I

[_ TIMT_

TIMT_

CNU0_

SL_

_DMT

SLDMT*

L MR-78 Servo Block t

TI_ERR

OVOLDON

CRLDON

TILT/H

NUT

SPCTLI

SPGCl

OPNtCLS

S12VOFF

_1op

(375v)

CXDB728Q

2zM DSP

<27OOMHz)

<s.i

FON

IC363

DRWER

8A5981FP

CR/OVO

MC14053

W,IN2 1 IC303

WIN1 34 SPINDLEDRiVER

VIN2 33

VINI 32 LB1896

UIN2 31

UIN1 _0

U_H._ _NST

SPVH- 28 9 SPCTLO

UOUT 23 sS_CTL1

VOUT 22 seGcl

WOUT 19 SFGC2

LDMT- 9 TILTDRIVER 13 TRAYFREE

LOADINGDRIVER S12VOFF

BASg_2

TIMT- 5 2

TIM% 6 TI=E_R

ITS06

MUt,O

CXDI86!,R MDpo

ID_

HA- 311C302

HA* 34 SLEDORIVER

SLVH+ 23

_30

Ha 29

SLVH- Lk6527

SLDMT- A*

ULDMT+

IA1.

PISW

TZ¢

DFCT

FE

te

$LEO-

SLED*

HYRET

TEACCO

TEAGCI

OETS

CN303

IPI

DGND

CDFCS-

RVO_CS*

OVDFCS-

CDTRK+

CO_K-

DVDmK_

D_TRK-

SSSD 1

SCKG3 toCN4S2 _

SDEN CN501

1 kICK

2 NFS

3HR

4 UHD7

5 SHD6

6 SHD5

7SHD4

SSHD3

g SHD2

F0 SHD!

ll SHDU

t2 TMS

13 IRST

14 TOI

lS D*_V

16 GNU

17 TOO

I_ GNp

19 TCK

2O GND

2_ EMU0

22 _MUl

- 53 - - 54 -

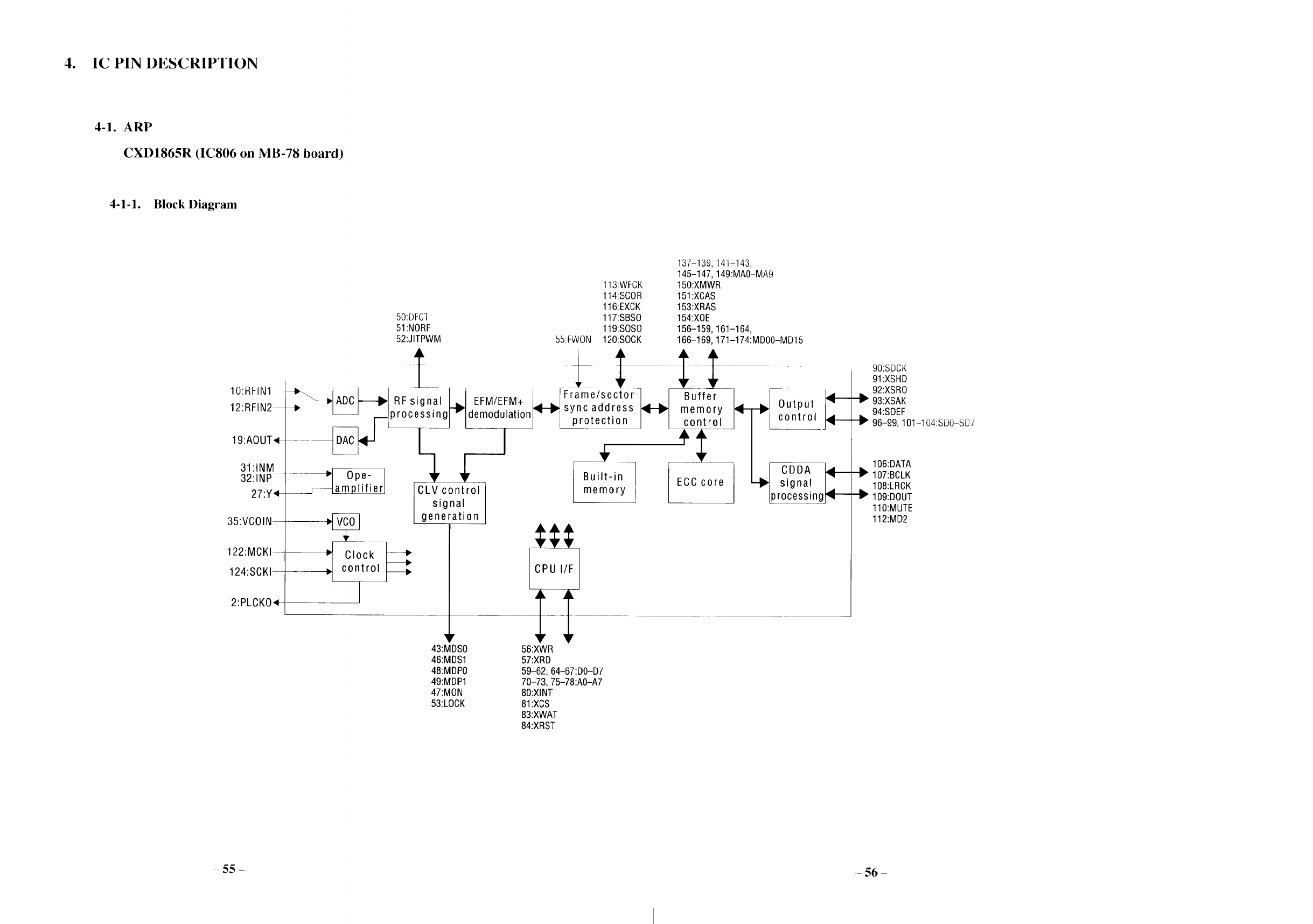

4. IC PIN DESCRIPTION

4-1. ARP

CXD1865R (IC806 oil MB-78 board)

4-1-1. Block Diagram

13T-139, 141-143,

145-147, 149:MAO-MA9

113:WFCK 150:XMWR

114:SC0R 151:XCAS

116:EXCK 153:XRAS

50:DEC1 117:SBSO 154:XOE

51:NORF 119:SOS0 156-159, 161-164,

52:JITPWM 55:FWON 120:SOCK 166-169, 171-174:MDOO-MD15

T Out,,ut"--

.... ,protec,.on.'' ontro'I %

]_ NpM__[ Ope- I __ Built-in _ ECC-core I. _

27.y__a plifierl CLVcontrol memory L-II_.I signal /

" _ _gLesiegrnatI,°n_ _ Iprocessing[_'--"

IO:RI:-IN1

12:RFIN2

lg:AOUT_

124:SCKI

2:PLCKO_

35:VCOIN c,oc

control CPU I/F

43:MDSO 56:XWR

46:MDS1 57:XRD

48:MDPO 59-62, 64-67:DO-D7

49:MDP1 70-73, 75-78:AO-A7

47:MON 80:XlNT

53:LOCK 81:XCS

83:XWAT

84:XRST

90:SDCK

91:XSHD

92:XSRO

93:XSAK

94:SDEF

96-99, 101-104:SDO-SDt

106:DATA

107:BCLK

108:LRCK

109:DOUT

110:MUTE

112:MD2

55 - - 56 -

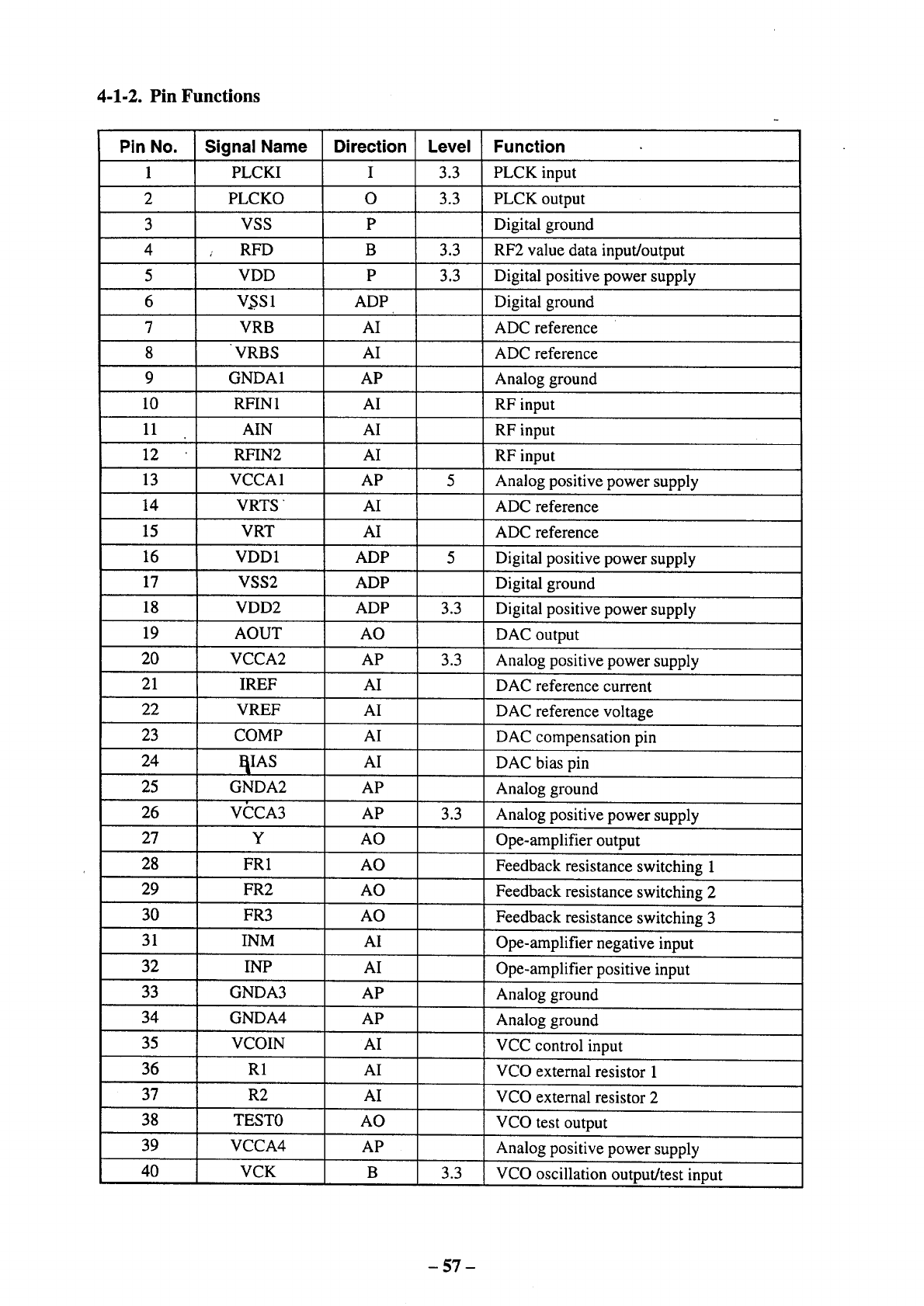

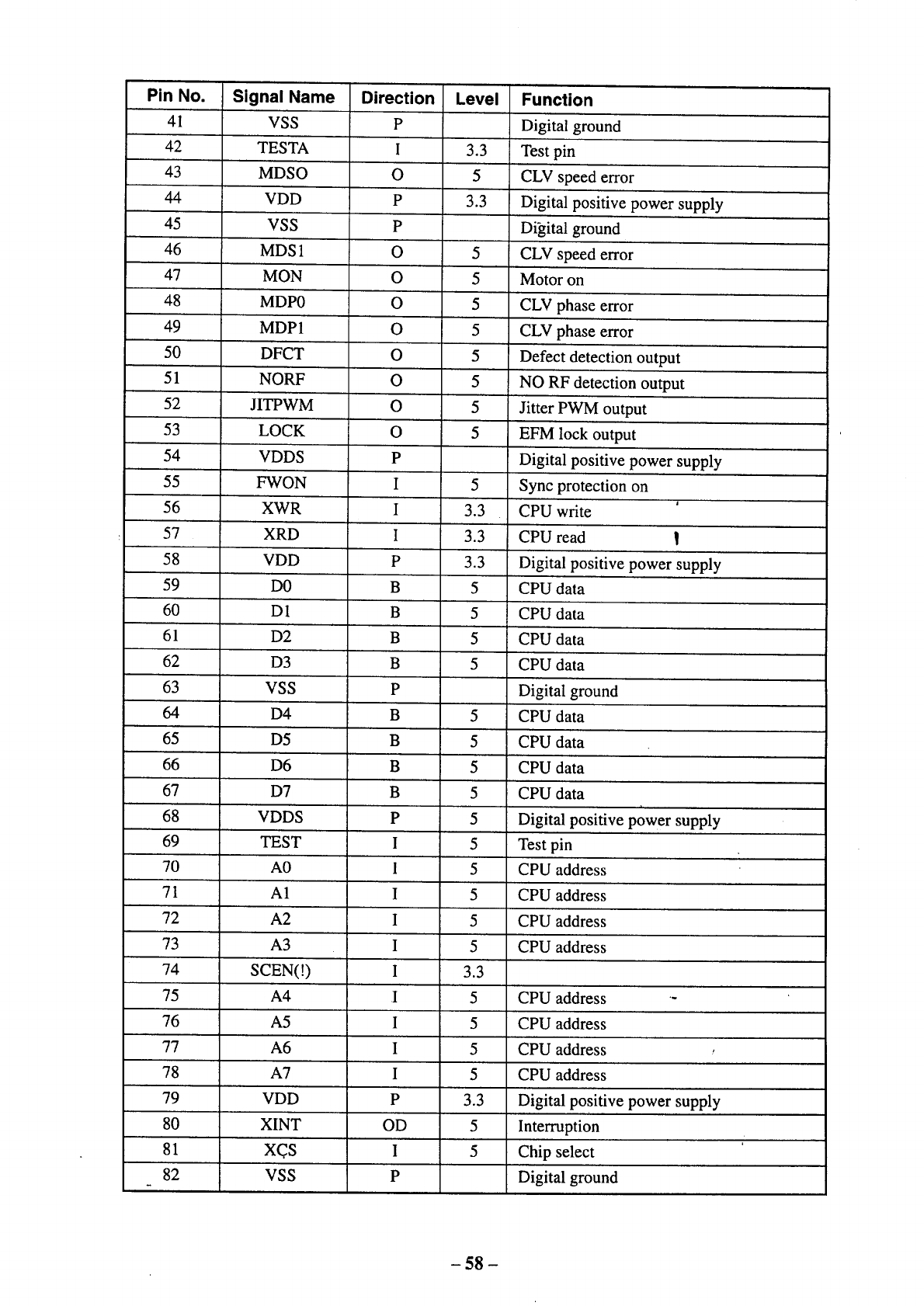

4-1-2. Pin Functions

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

Signal Name

PLCKI

PLCKO

VSS

i RFD

VDD

v_s1

VRB

VRBS

GNDA1

RFIN1

AIN

RFIN2

VCCA1

VRTS"

VRT

VDD1

VSS2

VDD2

AOUT

VCCA2

IREF

VREF

COMP

I_IAS

GNDA2

VCCA3

Y

FR1

FR2

FR3

INM

INP

GNDA3

GNDA4

VCOIN

R1

R2

TEST0

VCCA4

VCK

Direction

I

O

P

B

P

ADP

AI

AI

AP

AI

AI

AI

AP

AI

AI

ADP

ADP

ADP

AO

AP

AI

AI

AI

AI

AP

AP

AO

AO

AO

AO

AI

AI

AP

AP

AI

AI

AI

AO

AP

B

Level

3.3

3.3

3.3

3.3

5

5

3.3

3.3

3.3

3.3

Function

PLCK input

PLCK output

Digital ground

RF2 value data input/output

Digital positive power supply

Digital ground

ADC reference

ADC reference

Analog ground

RF input

RF input

RF input

Analog positive power supply

ADC reference

ADC reference

Digital positive power supply

Digital ground

Digital positive power supply

DAC output

Analog positive power supply

DAC reference current

DAC reference voltage

DAC compensation pin

DAC bias pin

Analog ground

Analog positive power supply

Ope-amplifier output

Feedback resistance switching 1

Feedback resistance switching 2

Feedback resistance switching 3

Ope-amplifier negative input

Ope-amplifier positive input

Analog ground

Analog ground

VCC control input

VCO external resistor 1

VCO external resistor 2

VCO test output

Analog positive power supply

VCO oscillation output/test input

-57 -

Pin No.

41

42

43

44

45

46

47

48

49

50

51

Signal Name

VSS

TESTA

MDSO

VDD

VSS

MDS 1

MON

MDP0

MDP1

DFCT

NORF

Direction

P

I

0

P

P

0

0

0

0

0

0

Level

3.3

5

3.3

5

5

5

5

5

5

Function

Digital ground

Test pin

CLV speed error

Digital positive power supply

Digital ground

CLV speed error

Motor on

CLV phase error

CLV phase error

Defect detection output

NO RF detection output

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

JITPWM

LOCK

VDDS

FWON

XWR

XRD

VDD

DO

D1

D2

D3

VSS

D4

D5

D6

D7

VDDS

TEST

A0

A1

A2

A3

SCEN(!)

A4

A5

A6

A7

VDD

XINT

XCS

VSS

O

O

P

I

I

I

P

B

B

B

B

P

B

B

B

B

P

I

1

I

I

I

I

I

I

I

I

P

OD

I

P

5

5

5

3.3

3.3

3.3

5

5

5

5

5

5

5

5

5

5

5

5

5

5

3,3

5

5

5

5

3.3

5

5

Jitter PWM output

EFM lock output

Digital positive power supply

Sync protection on

CPU write

CPU read l

Digital positive power supply

CPU data

CPU data

CPU data

CPU data

Digital ground

CPU data

CPU data

CPU data

CPU data

Digital positive power supply

Test pin

CPU address

CPU address

CPU address

CPU address

CPU address

CPU address

CPU address

CPU address

Digital positive power supply

Interruption

Chip select

Digital ground

-58-

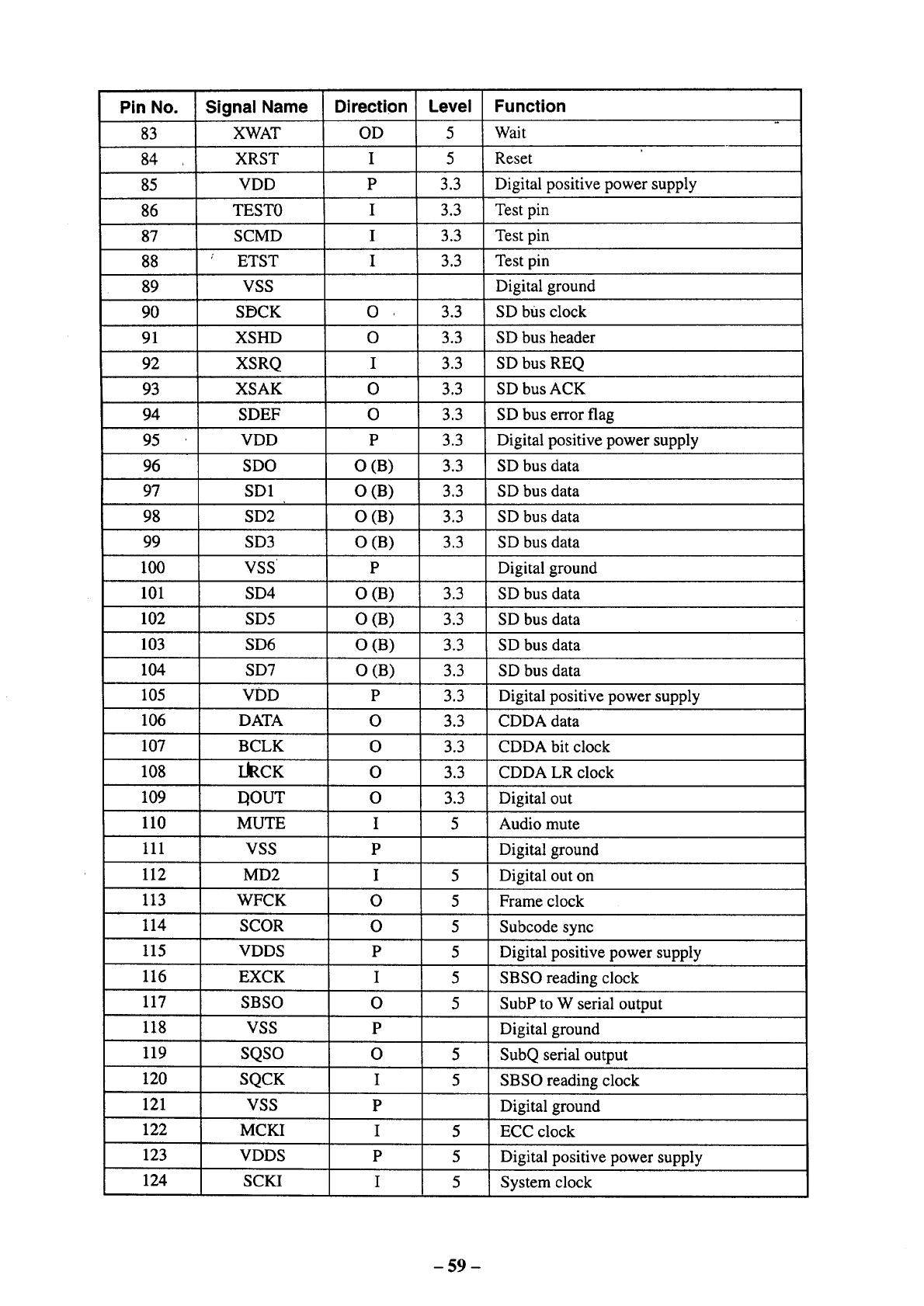

Pin No.

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

Signal Name

XWAT

XRST

VDD

TEST0

SCMD

" ETST

VSS

SDCK

XSHD

XSRQ

XSAK

SDEF

VDD

SDO

SD1

SD2

SD3

VSS

SD4

SD5

SD6

SD7

VDD

DATA

BCLK

URCK

I_OUT

MUTE

VSS

MD2

WFCK

SCOR

VDDS

EXCK

SBSO

VSS

SQSO

SQCK

VSS

MCKI

VDDS

SCKI

Direction

OD

I

P

I

I

I

0

0

I

0

0

P

o (B)

O (B)

O (B)

o (a)

P

o (a)

o (B)

0 (B)

O (B)

P

O

O

O

O

I

P

I

O

O

P

I

O

P

O

I

P

I

P

I

Level

5

5

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

5

5

5

5

5

5

5

5

5

5

5

5

Function

Wait

Reset

Digital positive power supply

Test pin

Test pin

Test pin

Digital ground

SD bus clock

SD bus header

SD bus REQ

SD bus ACK

SD bus error flag

Digital positive power supply

SD bus data

SD bus data

SD bus data

SD bus data

Digital ground

SD bus data

SD bus data

SD bus data

SD bus data

Digital positive power supply

CDDA data

CDDA bit clock

CDDA LR clock

Digital out

Audio mute

Digital ground

Digital out on

Frame clock

Subcode sync

Digital positive power supply

SBSO reading clock

SubP to W serial output

Digital ground

SubQ serial output

SBSO reading clock

Digital ground

ECC clock

Digital positive power supply

System clock

-59 -

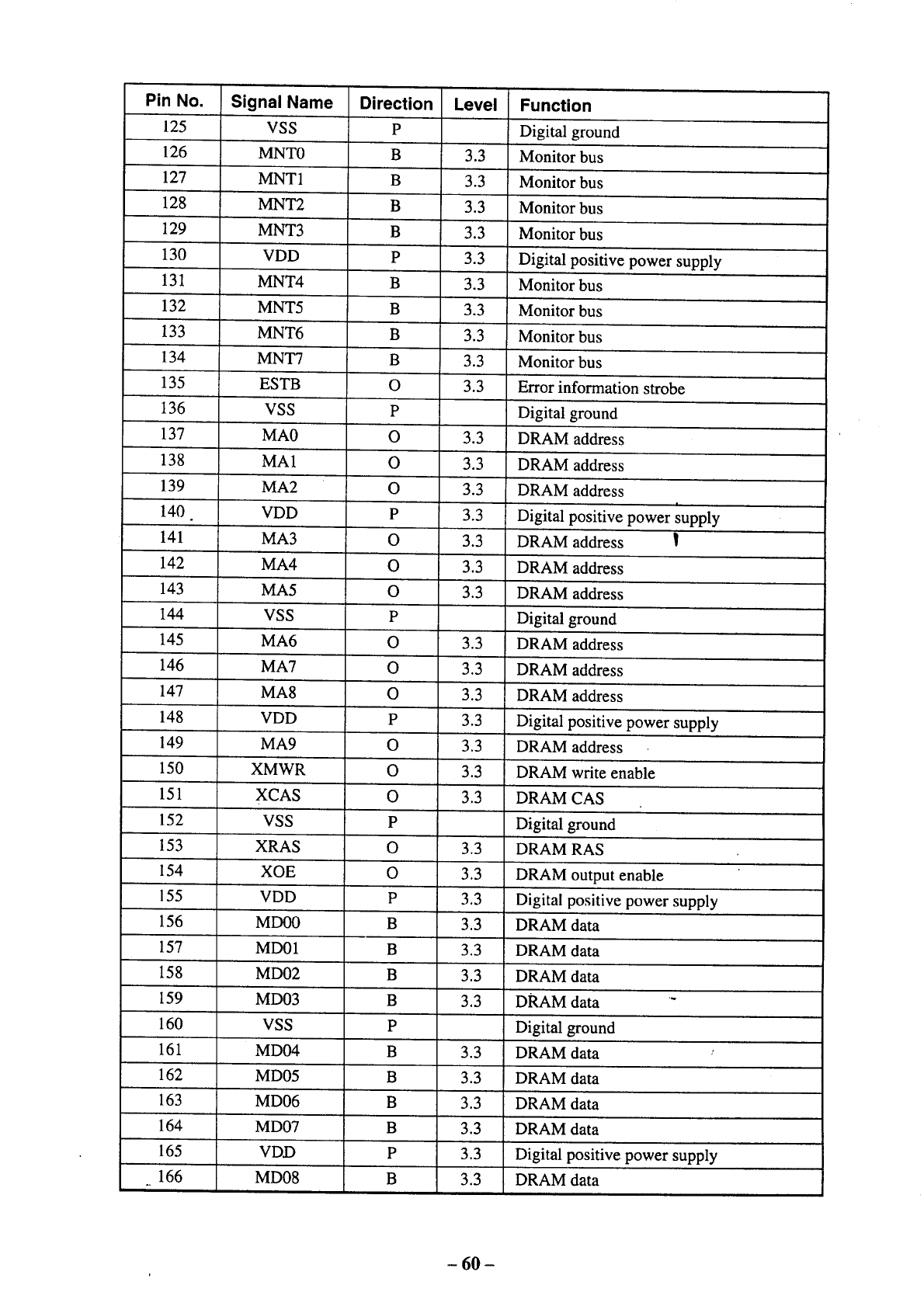

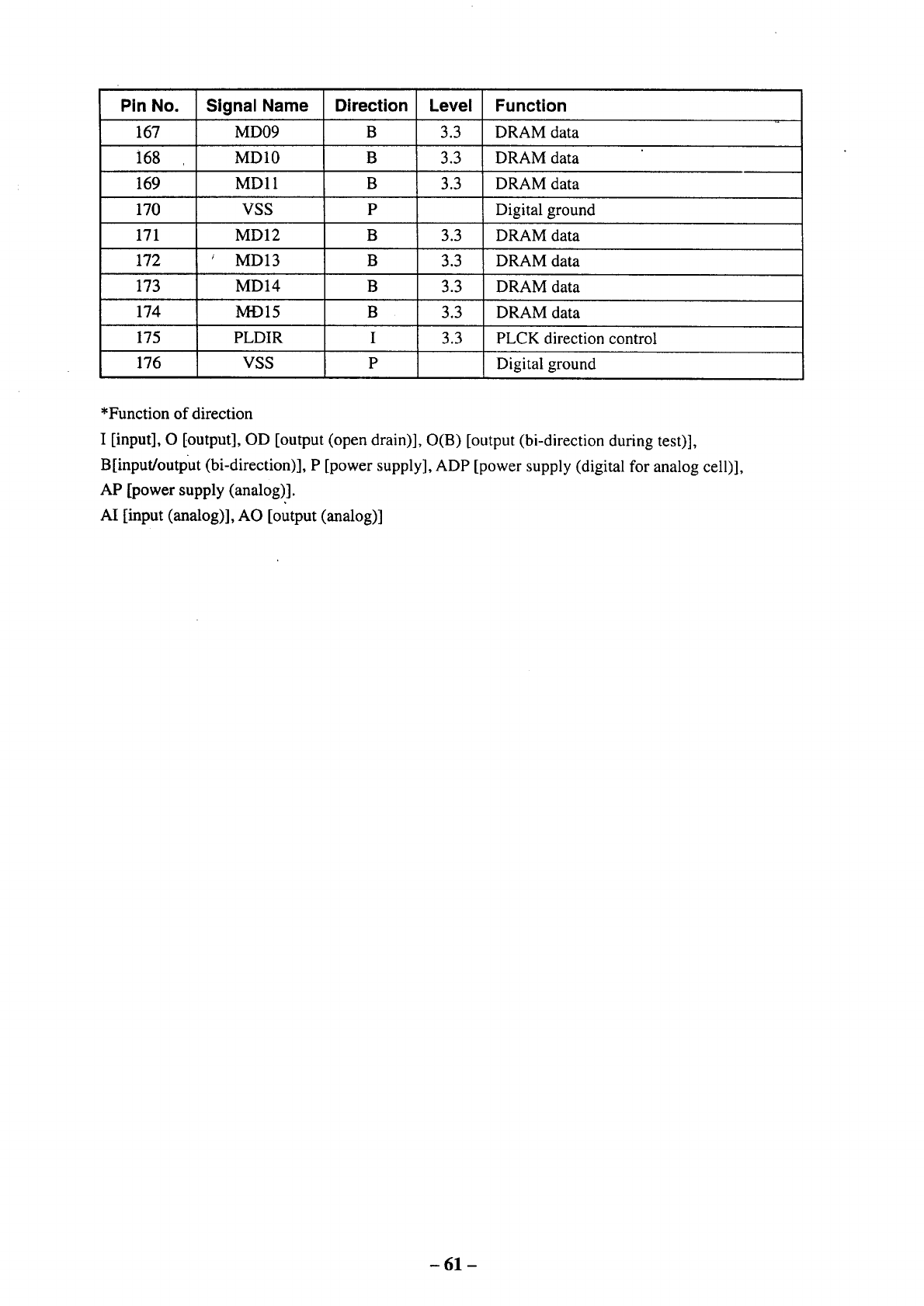

Pin No.

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

Signal Name

VSS

MNT0

MNT1

MNT2

MNT3

VDD

MNT4

MNT5

MNT6

MNT7

ESTB

VSS

MA0

MA1

MA2

VDD

MA3

MA4

MA5

VSS

MA6

MA7

MA8

VDD

MA9

XMWR

XCAS

VSS

XRAS

xoz

VDD

MD00

MD01

MD02

MD03

VSS

MD04

MD05

MD06

MD07

VDD

MD08

Direction

P

B

B

B

B

P

B

B

B

B

O

P

O

O

O

P

O

O

O

P

O

O

O

P

O

O

O

P

O

O

P

B

B

B

B

P

B

B

B

B

P

B

Level

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

Function

Digital ground

Monitor bus

Monitor bus

Monitor bus

Monitor bus

Digital positive power supply

Monitor bus

Monitor bus

Monitor bus

Monitor bus

Error information strobe

Digital ground

DRAM address

DRAM address

DRAM address

!

Digital positive power supply

DRAM address !

DRAM address

DRAM address

Digital ground

DRAM address

DRAM address

DRAM address

Digital positive power supply

DRAM address

DRAM write enable

DRAM CAS

Digital ground

DRAM RAS

DRAM output enable

Digital positive power supply

DRAM data