Tektronix Water Dispenser 494A Users Manual

494A to the manual 67a0ebf2-7266-4669-9a5c-00505daf38a6

2015-02-03

: Tektronix Tektronix-Water-Dispenser-494A-Users-Manual-464251 tektronix-water-dispenser-494a-users-manual-464251 tektronix pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 336 [warning: Documents this large are best viewed by clicking the View PDF Link!]

Service

Manual

494A

& 494AP

Tektronix

o

o

o

o

o

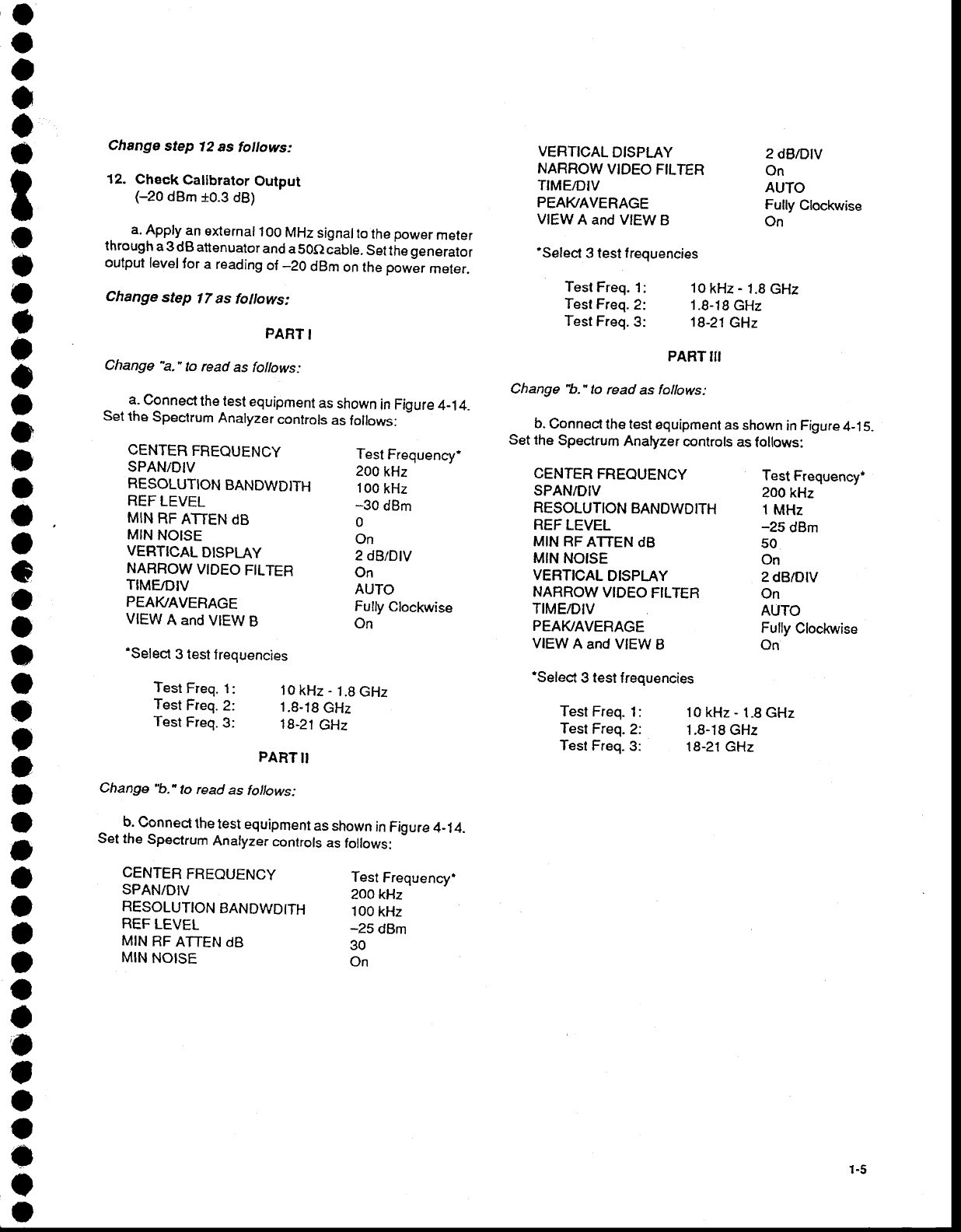

o

o

o

o

o

o

I

o

o

o

o

a

o

o

o

o

o

o

o

o

o

o

o

o

o

o

a

o

o

a

o

o

o

o

o

o

o

o

o

Spectrum

Analyzers

Volume 1

070-ss60-00

Warning

The servicing

instructions

are for use

by qualified

personnel

only. To avoid personal

injury, do not

perform any

servicing unless

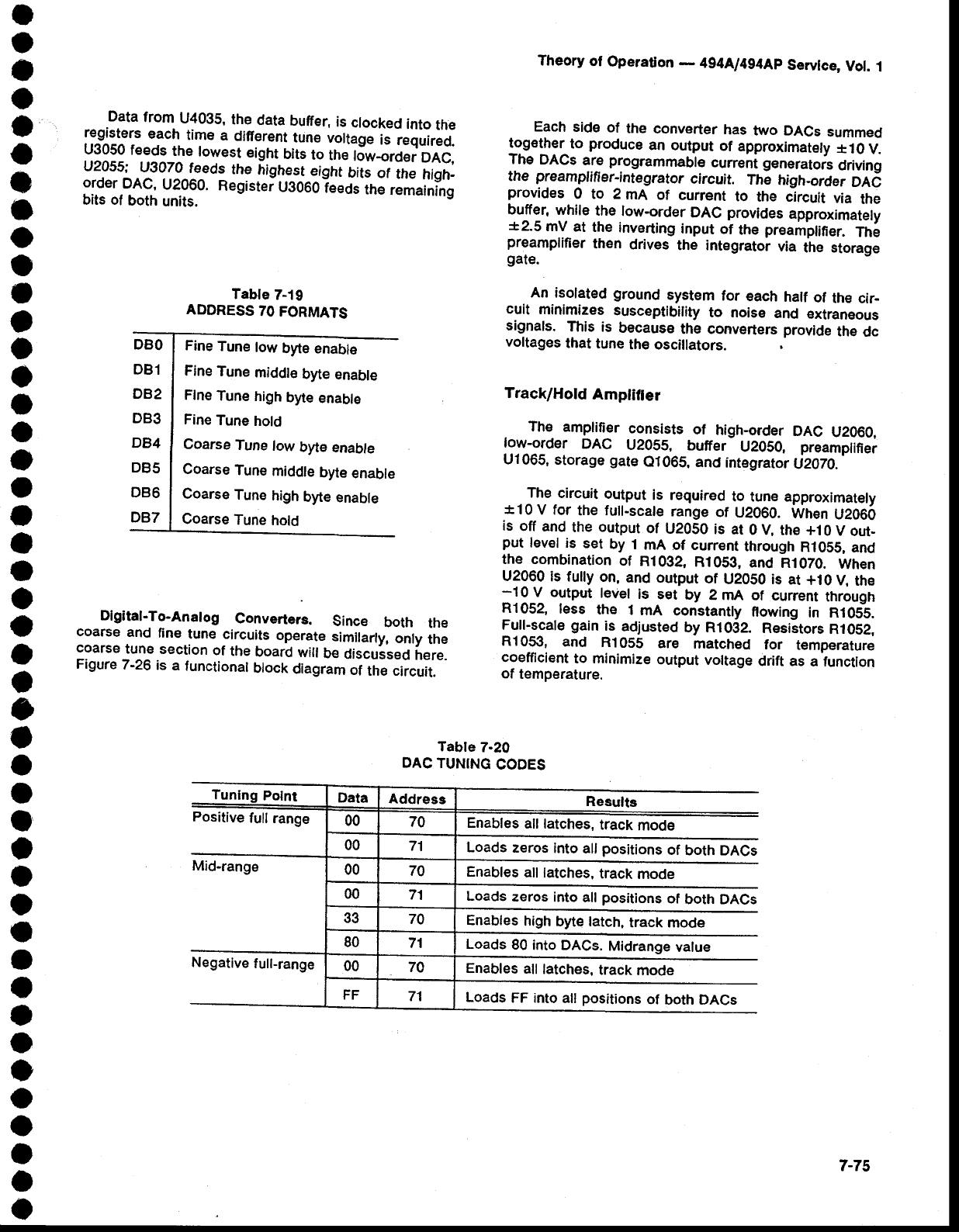

you are

qualified to

do so. Refer to the Safety

Summary

prior to

performing

service.

Please

check for change information at the rear

of this manual.

First

Edition:

January

1

987

Copyright @

Tekrronix, Inc. 1987.

All rights reserved.

Tektronix products

are covered by U.S. and foreign patents,

issued

and pending. Information in this publication supercedes

that in all previously published material. Specifications and price change

privileges reserved.

Printed

in the

U.S.A.

Tektronix,

Inc., P.O. Box 1000,

Wilsonville, OR 97070_1000

TEKTRONIX and TEK are registered

trademarks

of Tektronix. Inc.

I

o

o

o

?

o

a

o

o

t

o

o

O

o

o

o

o

a

o

o

o

o

o

o

o

o

o

o

o

o

o

a

o

o

o

o

a

o

o

o

o

a

o

o

o

o

o

o

o

o

o

o

o

o

a

o

I

o

o

O

o

o

o

o

o

o

o

o

o

o

o

O

I

o

o

o

o

o

o

t

o

o

o

o

I

O

a

o

RELEASE

OF COPYRIGHT

Tektronix

cannot

provide

manuals

for

measurement

products

that are

no

longer

eligible for

long

term

support.

Tektronix

hereby

grants permission

and license

for

others

to reproduce

and distribute copies

of any

Tektronix

measurement

product

manual,

including

user manuals, operato/s

manuals,

service

manuals,

and the

like,

that

(a)

have

a Tektronix

part

Number

and

(b)

are for

a measurement product

that is no longer

supported

by

Tektronix.

A Tektronix

manual may be

revised to reflect

changes

made

to the

product

during

its manufacturing

life. Thus,

different

versions

of a manual may

exist for any

given

produot.

Gare

should

be

taken

to ensure

that

one

obtains the

proper

manual

version for

a specific

product

serial number.

This

permission

and license

does not

apply

to

any

manual

or

other

publication

that

is still available from

Tektronix,

or to

any

manual

or other

publication

for

a video

production

product

or a color

printer

product.

Tektronix

does not

wanant the

accuracy

or

completeness

of the information,

text,

graphics,

schematics,

parts

lists,

or other

material

contained

within

any measurement

product

manual

or other

publication

that is not

supplied by

Tektronix or that is

produced

or distributed

in

accordance

with

the

permission

and

license

set

forth

above.

TEKTRONIX

SHALL

NoT BE LIABLE

FoR

ANY

DAMAGES

WHATSOEVER

(|NCLUD|NG,

WTTHOUT

LtMtTATtON, ANy

CONSEQUENTIAL

OR

INCIDENTAL

DAMAGES,

DAMAGES

FOR

LOSS

OF

PROFITS,

BUSINESS

INTERRUPTION.

OR

FOR

TNFRTNGEMENT

OF TNTELLECTUAL

pROpERTyl

AR|S|NG

OUT

OF

THE

USE

OF ANY

MEASUREMENT

PRODUCT

MANUAL OR OTHER

PUBLICATION

PRODUCED

OR

DISTRIBUTED IN

ACCORDANCE

WITH

THE PERMISSION

AND LICENSE

SET

FORTH

ABOVE

Thomas

F.

Lenihan

Chief

tntellectual

Property

CounselTektronix,

tnc

(503)

627-7266

o

a

o

o

,.'.t

a

o

a

o

a

a

o

o

o

t

a

a

o

I

o

o

o

o

o

o

o

O

a

I

o

a

o

a

o

o

t

a

o

o

a

a

a

a

a

I

o

o

I

o

I

t

I

o

o

I

I

O

o

I

t

o

I

I

o

o

o

o

o

o

o

t

o

I

o

o

o

o

o

I

o

O

t

I

O

o

O

t

o

WARRANTY

Tektronix warrants that this product will be free from defects

in materials and workmanship fbr a period of one (l)

year from the date of shipment. If any such product proves

defective during this warranty feriod, Tektronix, at its

option, either will repair the defective product without charge for parts and labor, or will provide a replacement

in

exchange

for the defective product.

In order to obtain service under this warranty,

Customer

must notify Tektronix of the defect before the expiration

of the warranty period and make suitable arrangements

for the performance of service.

Customer shall be

responsible

for packaging and shipping the defective product to the service center

designated

by Tektronix, with

shipping charges

prepaid-

Tektronix shall pay for the return of the product to Cusromer

if the shipment is to a

location

within the

country

in which the Tektronix

service

center

is located.

customer

shall

be responsible

for

paying all shipping charges,

duties, taxes,

and any other charges

for products

returned

to any other locations.

This warranty shall not apply to any defect, failure or damage

caused

by improper use

or improper or inadequate

maintenance

and care' Tektronix shall not be obligated to furnish service under this warranry a) to repair damage

resulting from attempts

by personnel

other than Tektroriix representatives

to install, repair or service the product;

b) to repair

damage

resulting

from improper

use

or connection

to incompatible

equipment;

or c) to service

a

product that has

been modified or integrated

with other products when the effect of such

modification or

integration increases

the time or difficulty of servicing the product.

TIIIS WARRANTY IS GIVEN BY TEKTRONTX WITH RESPECT TO THIS PRODUCT IN LIEU OF

ANY OTI{ER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS

DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A

PARTICULAR PURPOSE. TEKTRONIX'RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE

PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR

BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY

INDIRECT' SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF

WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF TIM POSSIBILITY OF

SUCH DAMAGES.

O

a

o

I

?

o

a

a

a

a

a

I

t

o

I

a

a

a

O

o

O

o

o

o

t

C

a

I

a

o

O

t

a

o

a

o

a

o

o

a

o

o

I

o

o

o

o

t

o

o

I

I

o

a

O

I

a

o

I

I

o

t

I

o

a

o

O

o

I

o

o

o

I

o

o

I

o

o

o

a

o

I

a

o

o

o

o

o

PREFACE

This manual

contains servic€

information

for the

TEKTRONfX

494A1494Ap.

The information

is tocated

in

two volumes.

Volume

1 contains

the

text and

Volume

2

contains

the diagrams

and parts lists. The Tabte

of

Contents

in each volume lists the contents

of both

volumes.

Manuals

that describe

other

aspects

of the

product

are:

. Operator's

Manual

. Operator's

Handbook

o Programmer's

Manual

o Programmer's

Reference

Guide

Who Should

Use This Manual?

This

rnanual

is intended

for electronic

technicians

with

experience

in servicing

digital,

analog,

and

rf circu-

itw. Circuit

analysis

is mostly

functionil and shoutd

help isolate

most malfunctione

to a board

or block

of

circuitry.

The technician

should

then be abte,

with the

aid of test equipment,

to isolate

the malfunction

to a

specific

component

or components.

This instrument

contains

firmware

that provides

a

thorough instrument

check

during power

up and

during

operation,

and if needed,

guides

the usei

through

ai

abbreviated

front-panel

calibration

procedure.

lf cali_

bration

cannot

be achieved,

a diagnostic

test

detects

and

isolates

most problems

to the

system,

such

as 1st

LO. The

technician

can

then run

troubleshooting

diag-

nostics

to further

isolate

the problem

to the board

or

block of

components.

Refer

to the

Maintenance

section

for

diagnostics

information.

Documentation

Standards

Most

terminology

and graphics

follow

ANSI

stan_

qalds. A glossary

of terms

is provided

as

an

appendix.

Refer

to

the

following

standards:

494A/494AP

Service Vot.

1

. ANSI

Y1.1

- Abbreviations

. ANSI Y32.2

- Graphic

Symbots

o IEEE

91

- Logic

Symbots

Change/History

Inf

ormation

Sometimes

instrument

changes

occur or manual

errors

are found

that make

some of the information

in

the manual

inaccurate.

When

that happens,

Manual

Change

Information

notices

are inserted

at the rear

of

the

manual.

This helps

ensure

that the

manual

contains

the latest

and

most accurate

information

available

when

the

product

is sold.

History information,

with the updated data, is

integrated

into

the text or diagrams:

When

a text

page

is updated,

the revised pages

are identified

by a revi-

sion

date in

the

lower

inside corner

of the

page.

When

a diagram

is updated,

the revision

date is placed

at

the

lower center of the diagram. History information

is

shown

with a gray tint. When a component

value

is

changed,

the

designator on

the drawing

is boxed with

a

grey

outline.

When

a circuit

is deleted

or changed,

the

original

configuration

is shown

in grey,

drawn either

at

its

original

location

or

to the

side

of

the

drawing.

lf you

have a manual

other

than

the

one

that

came

with your

instrument

it may contain revisions

that do not

apply

to your

instrument;

however

all

history

informa-

tion

that

pertains

to the

earlier instruments

is retained.

When a major modification

has been made to an

assembly

or circuit

board, the data for the replaced

assernbly

will follow

the new information

and

will

be

identified

with appropriate

titles

or headings such

as

instrurnent

serial

number range

or the assembly

or

board

part

numbers.

Also, if your

instrument

has an assembly replaced

with a newer version,

documentation

for the newer

assembly

may

be supplied.

Contact

any

Tektronix

Ser-

vice

Center for information.

o

o

o

I

a

o

t

a

a

a

o

a

o

o

I

O

a

a

a

o

o

o

o

o

o

o

t

o

a

a

o

o

I

o

o

o

a

o

o

o

a

o

a

o

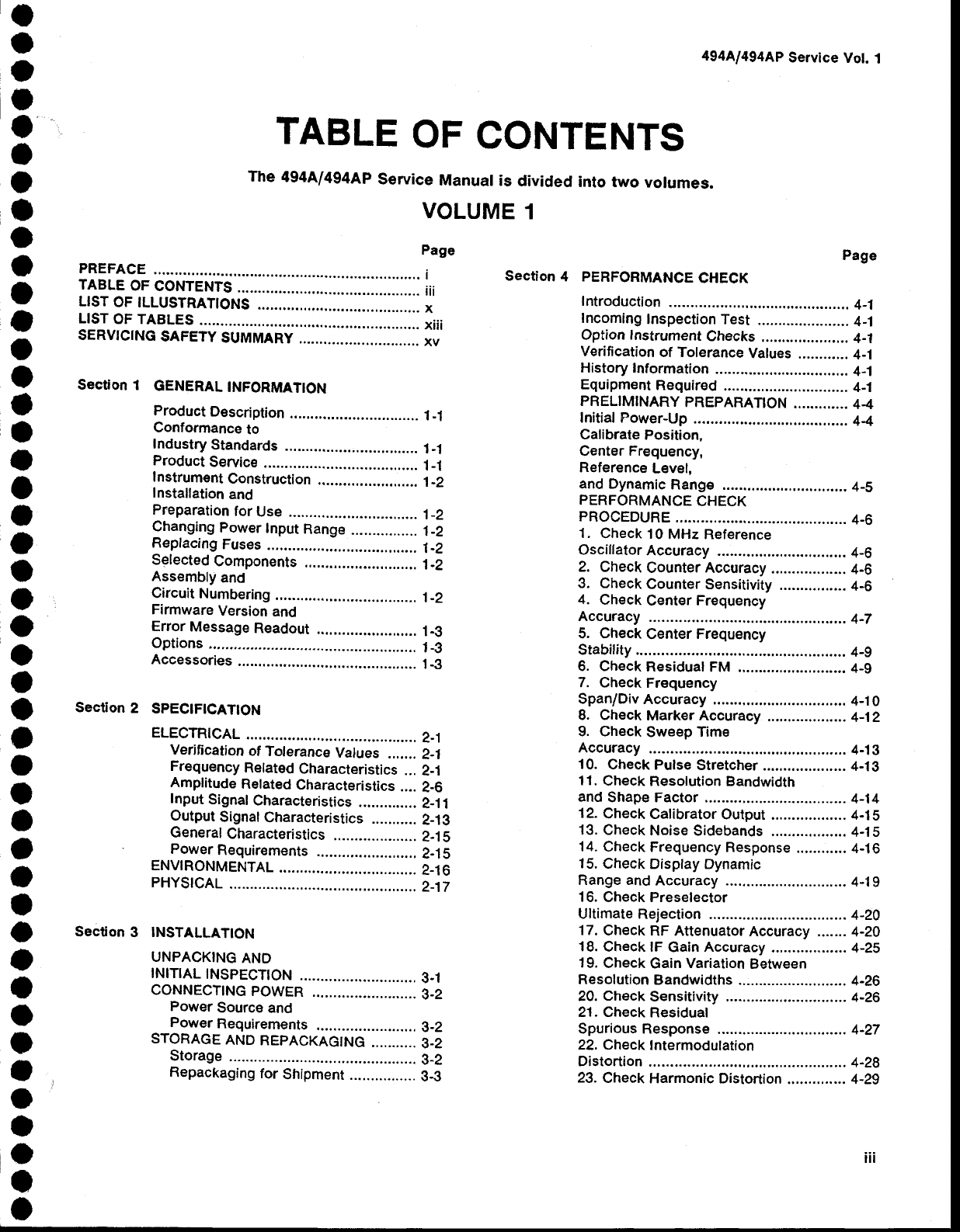

TABLE

OF

CONTENTS

The

494A/494AP

service

Manuat

is divided

into two volumes.

VOLUME

1

Page

PREFACE ........................

i

TABLE

OF

CONTENTS

.............. ..........

iii

LIST

OF ILLUSTRATTONS

........... ........

x

LIST

OF TABLES .............

xiii

SERVICING

SAFETY

SUMMARY .........

xv

Section

1 GENERAL

INFoRMATION

product

Description ...........

1_1

Conformance

to

Industry

Standards ............

1_1

Product

Service .................

1_1

Instrum€nt

Construction ....

1-z

Installation

and

Preparation

for

Use ...........

,l_2

Changing

power

Input

Range

....,.....,.....

1_2

Replacing

Fuses

.........

Selected

Components .......1-2

Assembly

and

Circuit

Numbering ..............

1_2

Firmware

Version

and

Error

Message

Readout ....

1-g

Options ..........

1-g

Accessories ..,....................

1-3

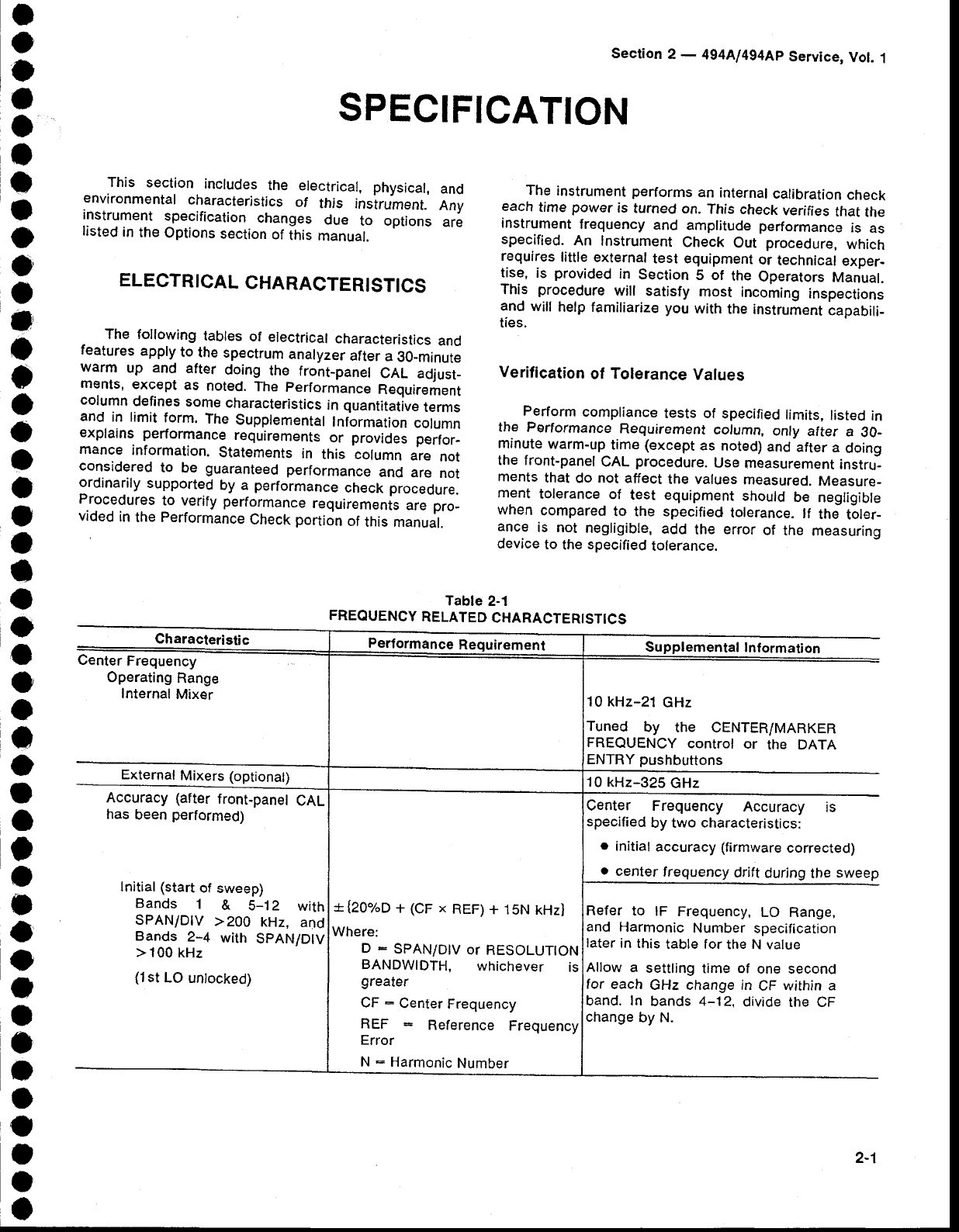

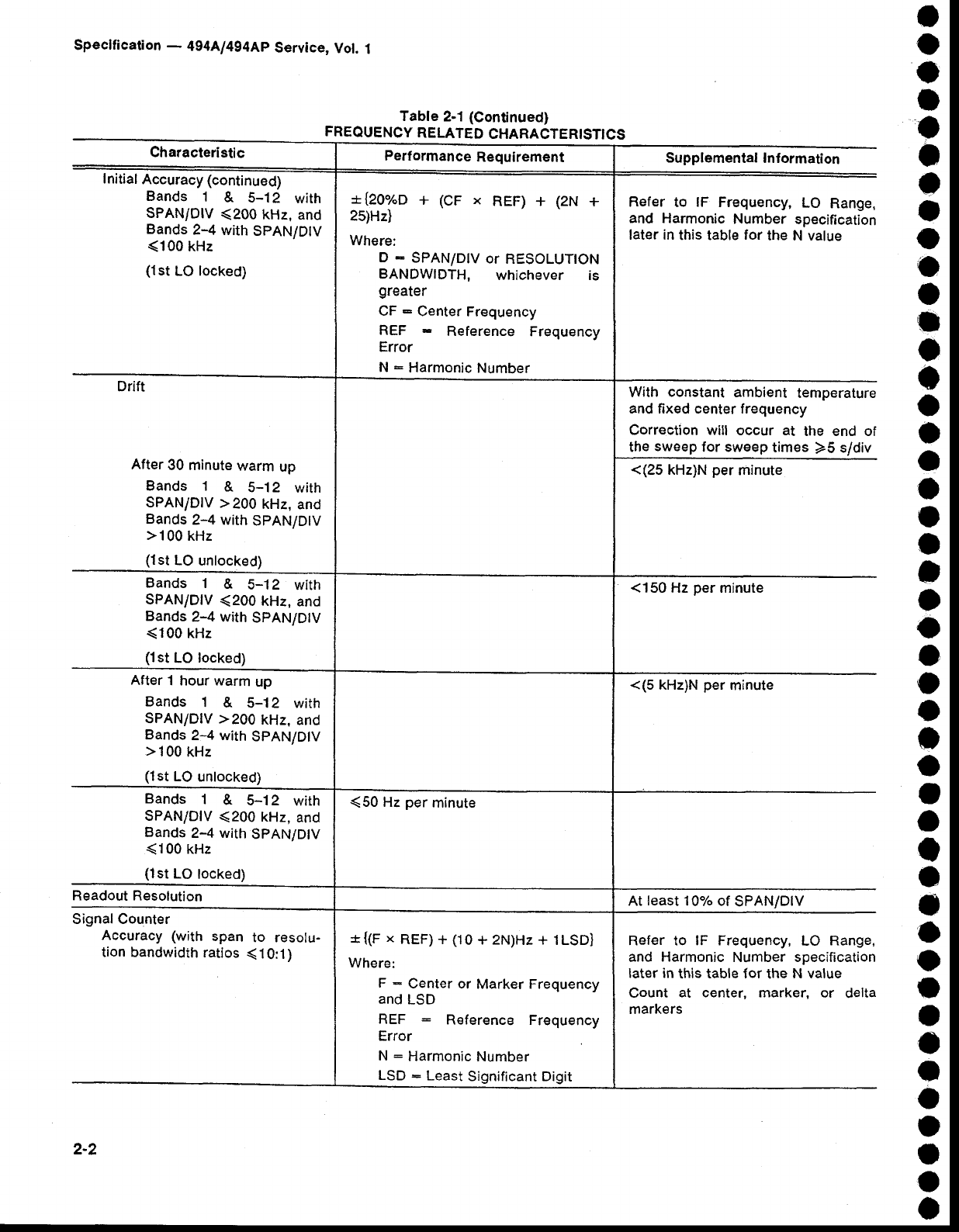

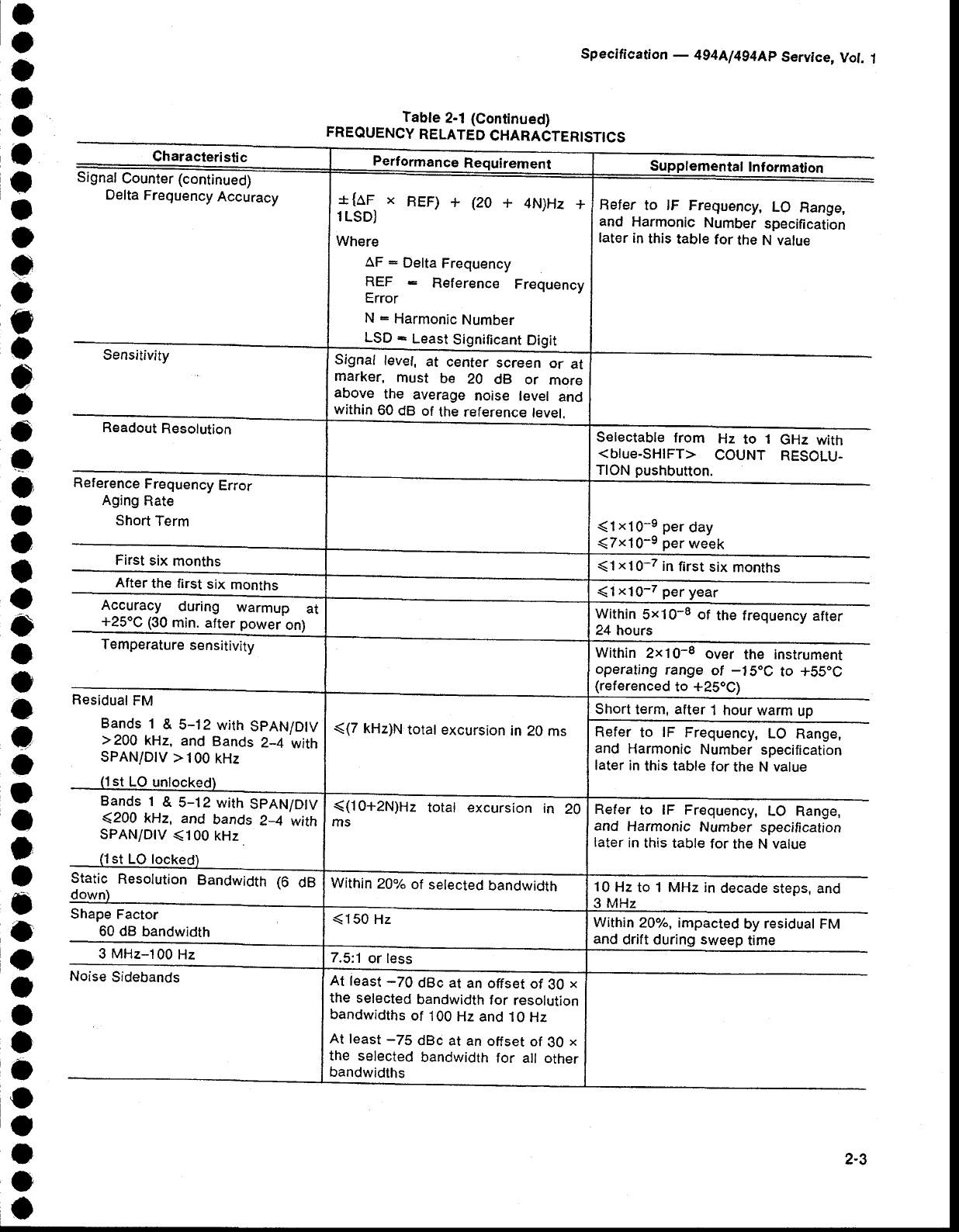

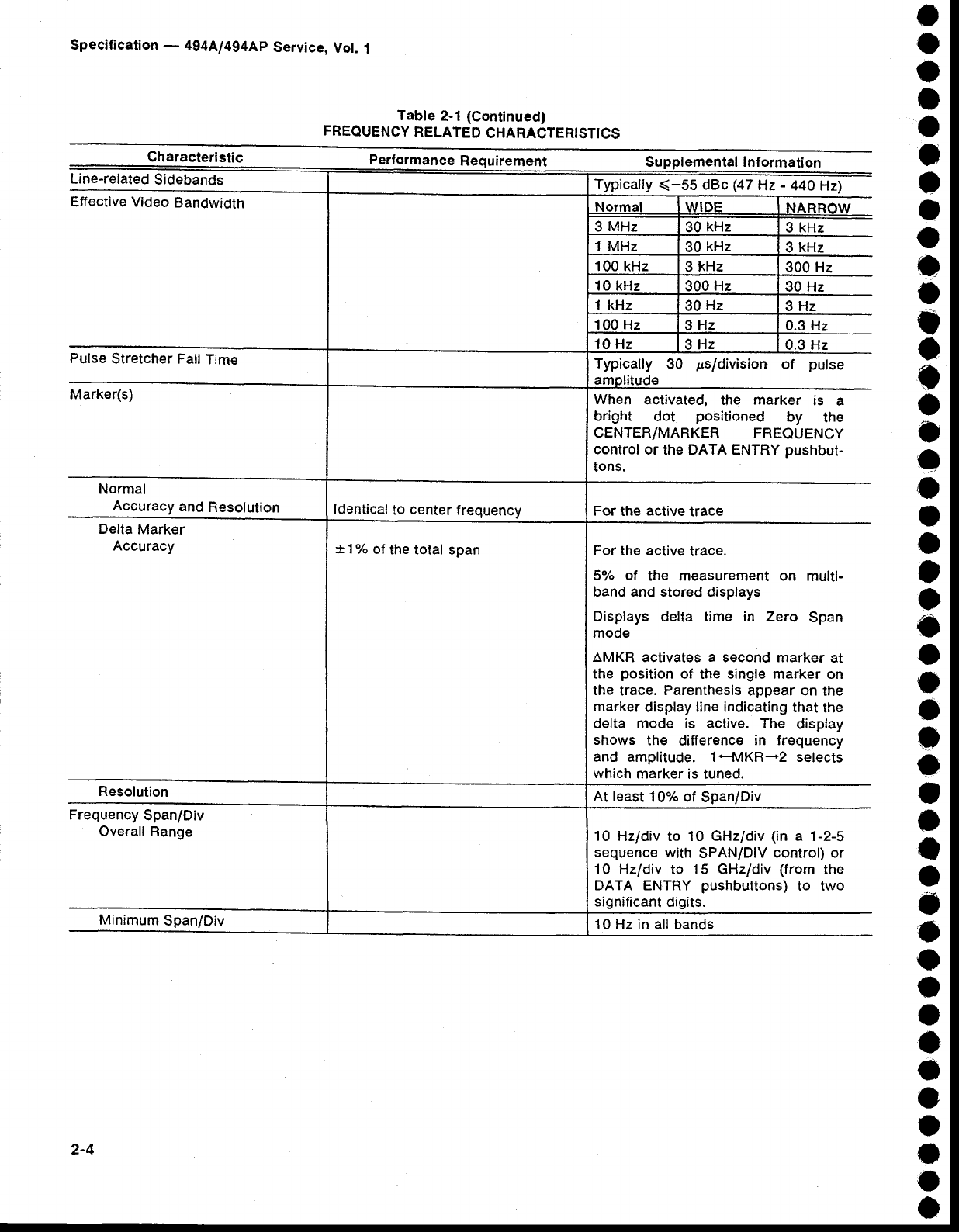

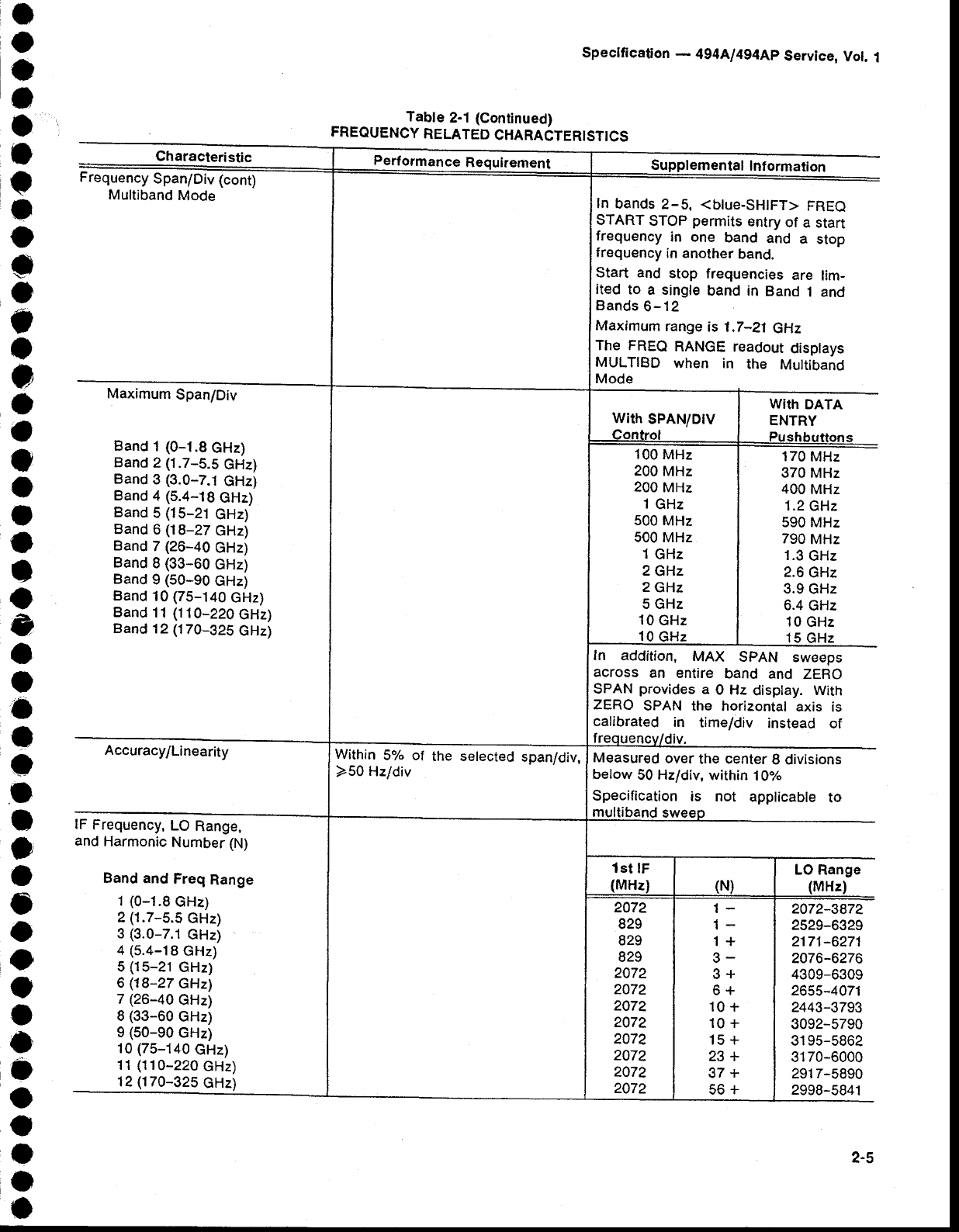

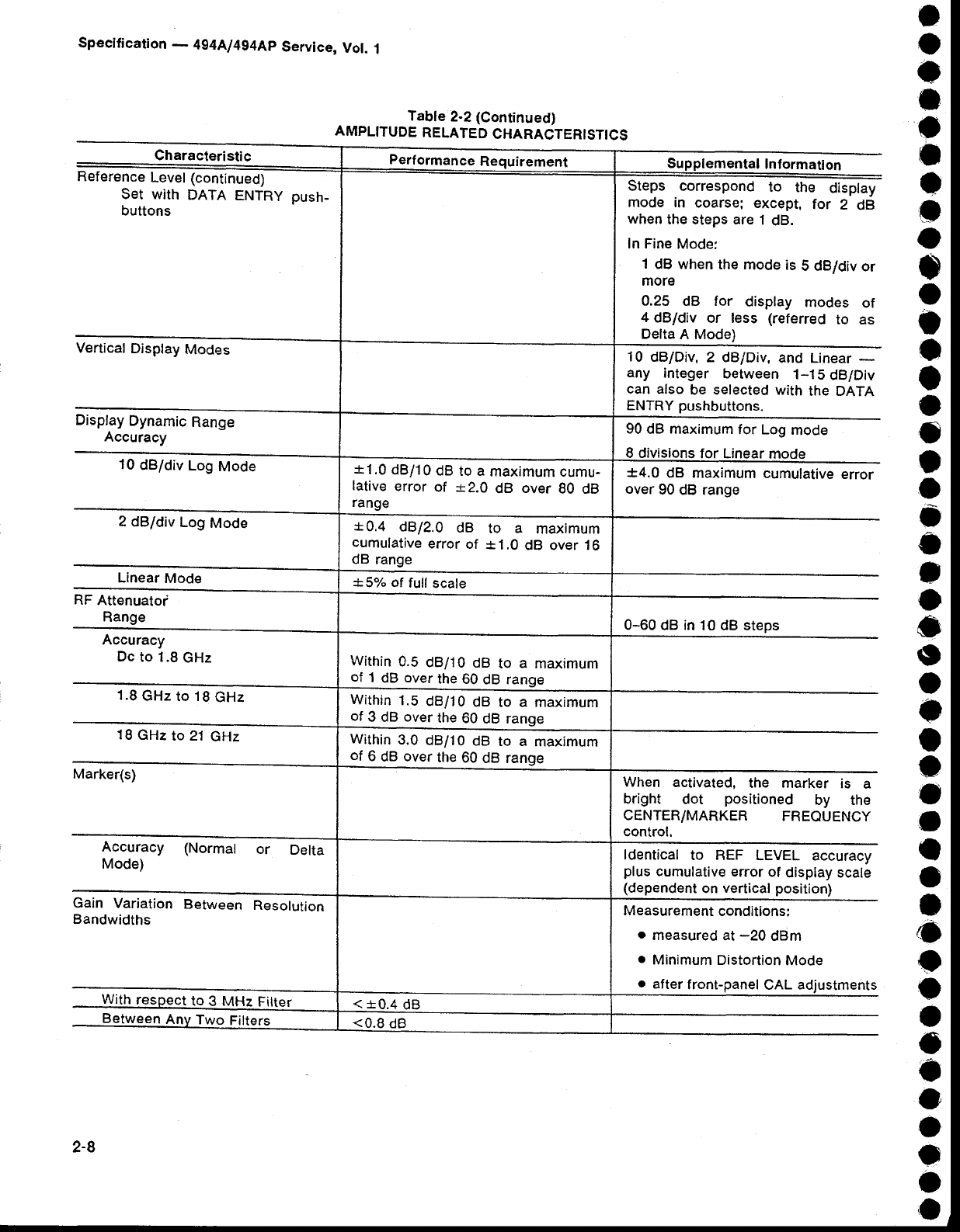

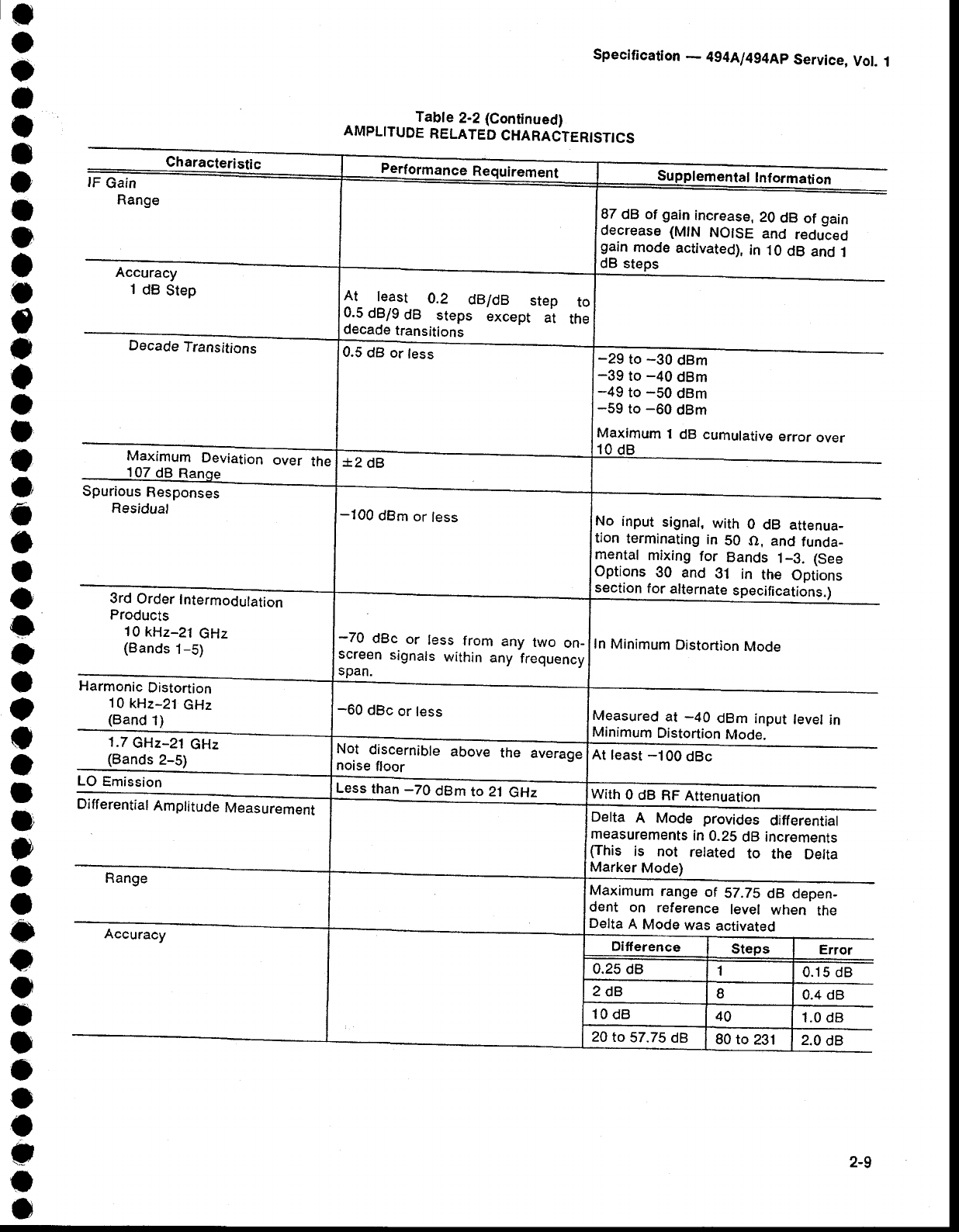

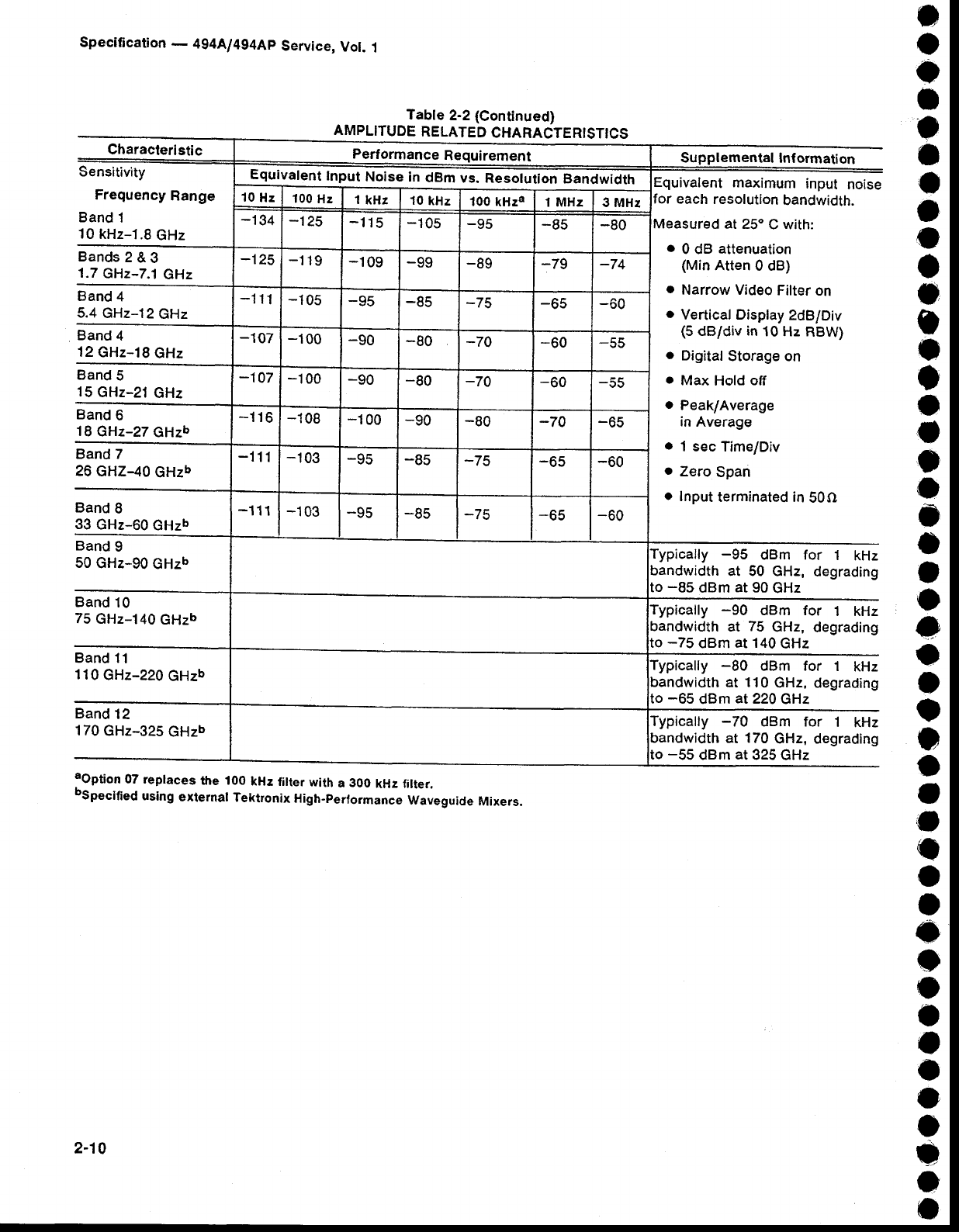

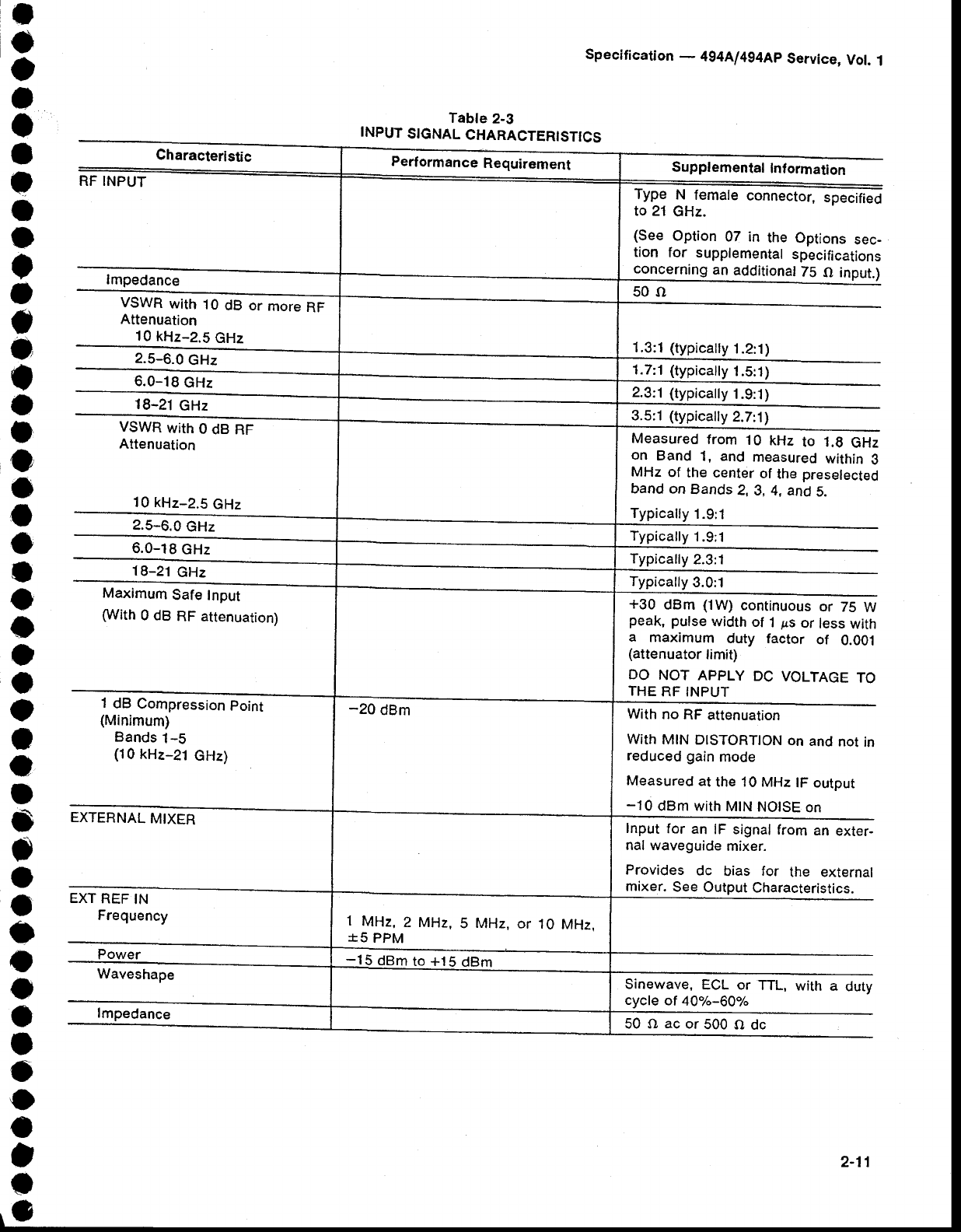

Section2 SPEC|F|CAT|ON

ELECTRICAL

................ .....2-1

Verification

of

Tolerance

Values

.....,.

Z-1

Frequency

Related

Characteristics

...

2-1

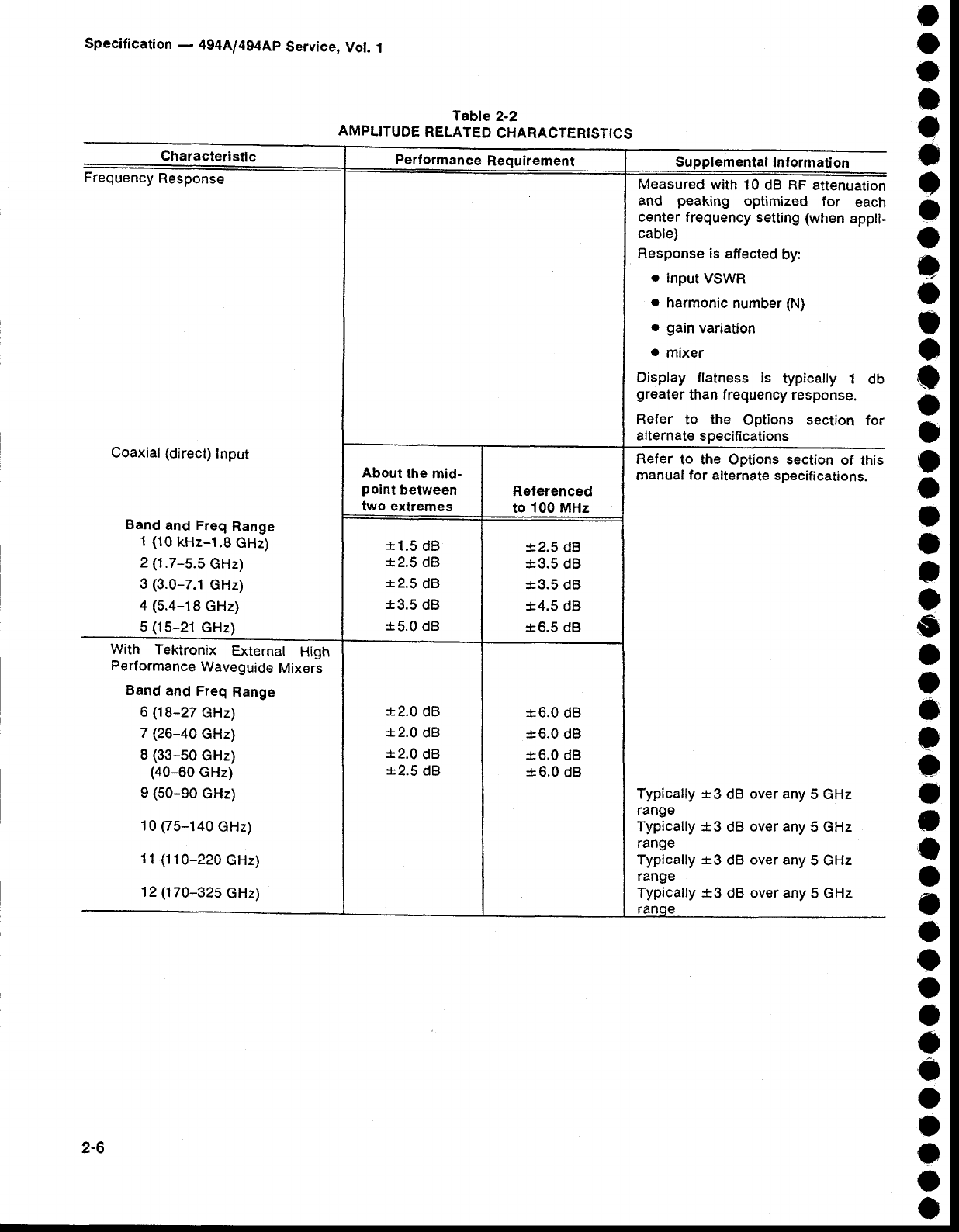

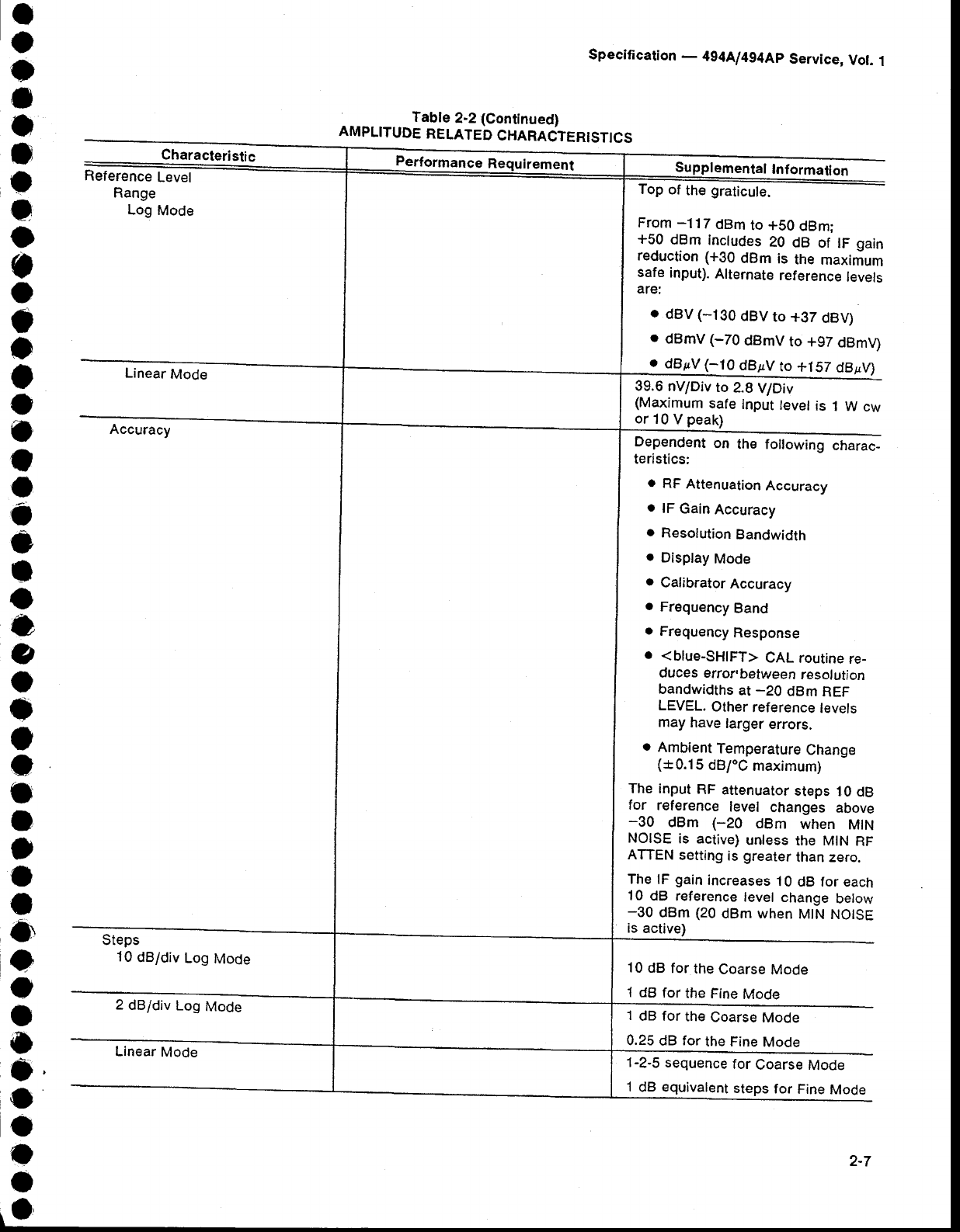

Amplitude

Related

Characteristics

....

2_6

Input

Signat

Characteristics

..............

2-1

1

Output

Signal

Characteristics

...........

2-1g

General

Characteristics

....................

2-1

s

' Power

Requirements

........,.........,.....

2-1 5

ENV|RONMENTAL.......... ...

2_16

PHYSTCAL .....2-.t7

Section

3 INSTALLATION

o

o

o

t

o

o

o

o

o

o

o

a

I

o

I

a

a

o

I

o

o

o

o

o

o

o

o

o

t

o

a

o

I

o

o

t

o

I

a

o

o

a

o

o

UNPACKING

AND

tNtilAL

TNSPECTTON .......,

3-1

coNNECTtNG

POWER .....

3_2

Power

Source

and

Power

Requirements

........................

g_2

STORAGE

AND

REPACKAGING

......,....

3.2

Storage .....

g_2

Repackaging

for

Shipment

................

g-3

494A/494AP

Service

Vot.

1

Page

Section

4 PERFORMANCE

CHECK

Introduction ..,.4-1

Incoming

Inspection

Test

......................

4_1

Option Instrument

Checks

..............,......

4_1

Verification

of Tolerance

Values

............

4_1

History Information ............

4-1

Equipment

Required ..........

4-1

PRELIMINARY

PREPARATTON

.............

4-4

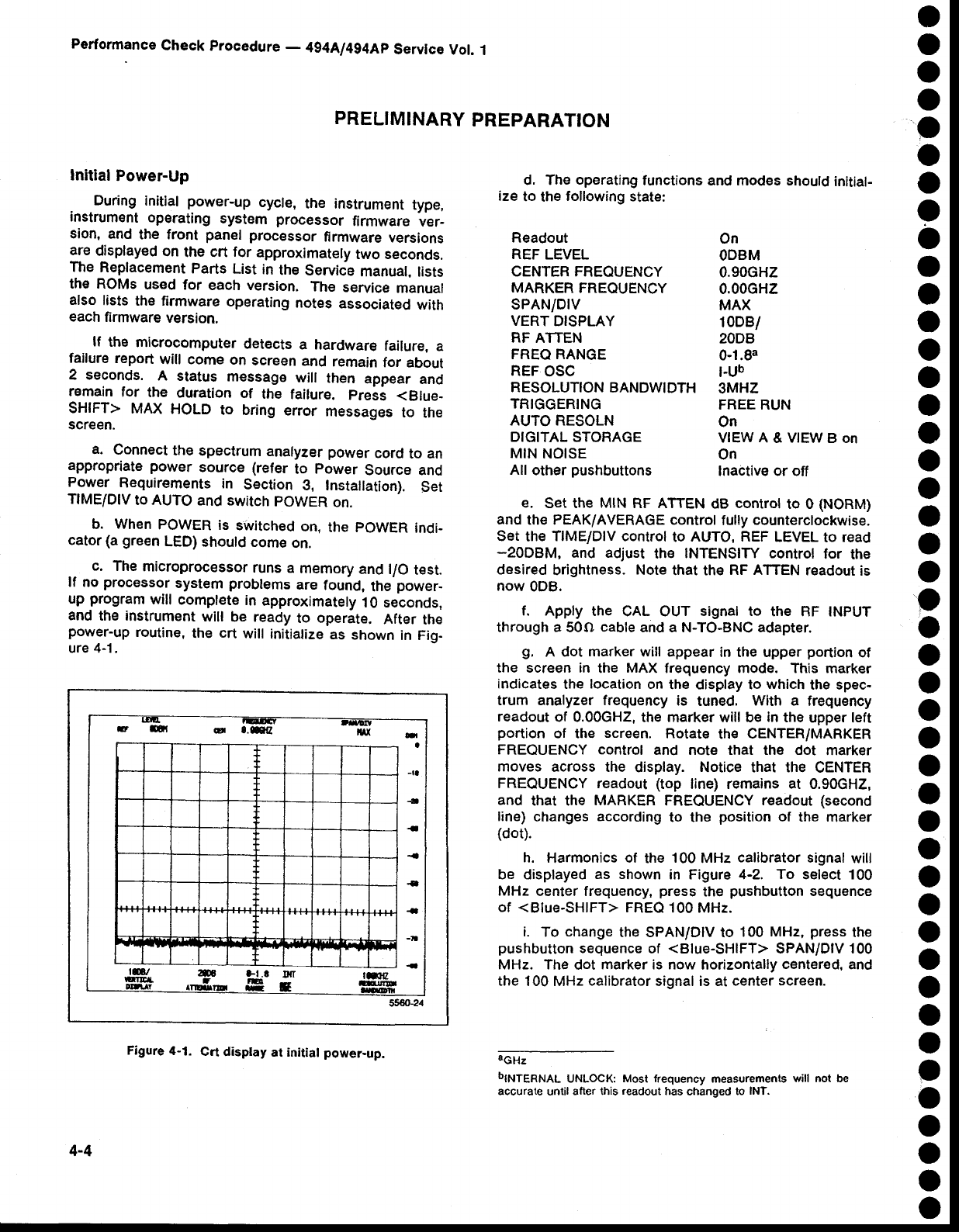

Initial Power-Up

............ .....44

Calibrate

Position,

Center

Frequency,

Reference

Level,

and Dynamic

Range ..........

4-s

PERFORMANCE

CHECK

pRocEDURE

................ .....

4_6

1. Check't0

MHz Reference

Oscillator

Accuracy ...........

4_6

2. Check

Counter Accuracy

..................

4-6

3. Check

Counter Sensitivity

................

4-6

4. Check

CentEr Frequency

Accuracy .,......4-T

5. Check

Center

Frequency

Stability ...........

4-9

6. Check

Residual

FM

..........................

4-9

7. Check

Frequency

Span/Div

Accuracy ............

4-10

8. Check

MarkerAccuracy

...................

4-12

9. Check

Sweep

Time

Accuracy ........4-19

10. Check

Pulse

Stretcher

....................

4-19

11.

Check

Resolution Bandwidth

and

Shape Factor ..........-...4-14

12.

Check

Calibrator

Output

.................. 4-15

13.

Check

Noise

Sidebands

..................

4-15

14.

Check

Frequency Response

............

4-16

15.

Check

Disptay Dynamic

Range and

Accuracy .............................

4-1

g

16.

Check Preselector

Ultimate Rejection .........-...4-20

17.

Check

RF Attenuator

Accuracy

....... 4-20

18.

Check lF

Gain

Accuracy

..................

4-25

'l

9. Gheck

Gain

Variation

Between

Resolution

Bandwidths ......4-26

20.

Check

Sensitivity ......... 4-26

21. Check

Residual

Spurious Response ...........4-27

22. Cheek

lntermodulation

Distortion ........4-2A

23.

Check

Harmonic Distortion

........,..... 4-29

ill

o

o

o

I

.|

r

o

o

a

a

o

I

o

o

t

a

o

O

o

o

o

I

a

o

o

o

t

o

a

a

I

I

I

o

o

o

o

o

I

o

a

a

a

o

tv

49441494AP

Servtce

Vot.

i

Section 4

Section 5

TABLE

OF

CONTENTS

(Gonr.)

page

PERFORMANCE

CHECK

(Conr.)

24.

Check LO

Emission .....4-29

25.

Check 1

dB

Compression

point

.......4-29

26.

Check External

Reference

Input

Power .... 4-31

27.

Check

Triggering

Operation

and

Sensitivity

.............. ..... 4-31

28.

Check

External

Sweep

Operation ...............

4-92

29.

Check

VERT

OUTPUT

Signat

..........

4-34

30.

Check

HORTZ

OUTPUT

Signaf

Level ....4-94

oPTloN

TNSTRUMENTS

.......................

4_34

31.

Check

Option

07

Calibrator

Output ...............

4-94

32.

Check

Option

07

Frequency

Response ......... 4-95

33.

Check

Option

4i Frequency

Span/Div

Accuracy ............

4-gz

34.

Check

Option

42

110

MHz

OUT Level ..........

4-gB

35.

Gheck

Optiopn

42110

MHz

tF

Output

Bandwidth,

Center Frequency,

Bandpass

Ripple,

and

Symmetry

About

110

MHz ..................4-gg

GPIB

VERIFICATTON

PROGRAM

..........

4-39

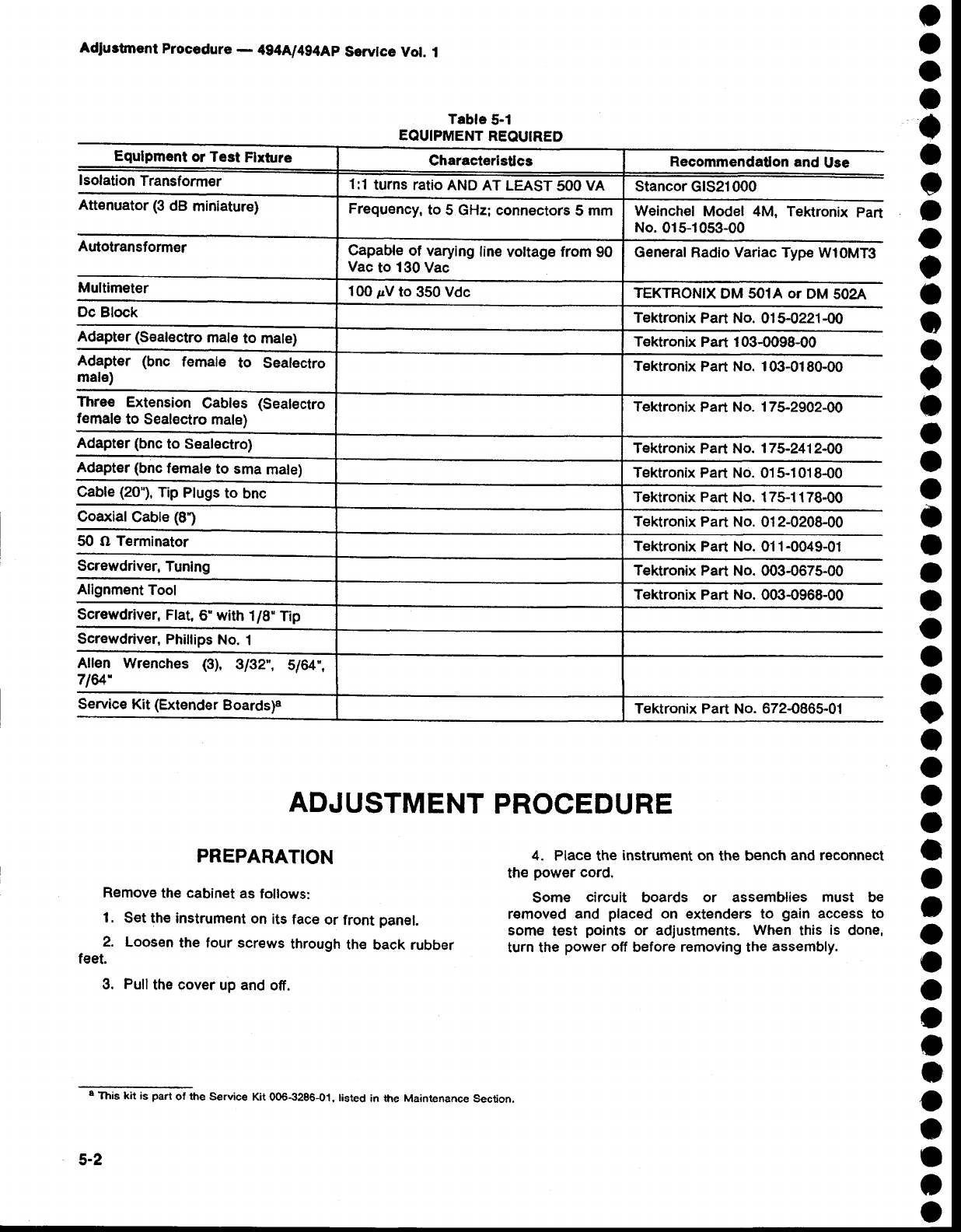

ADJUSTMENT

Introduction ....

5-1

Equipment

Required ..........

5-1

ADJUSTMENT

PROCEDURE

................

5-2

PREPARAT|ON

............. .....5-2

1. Adjust

Low

Voltage

power

Suppty

... 5-3

2. Adjust

Z-Axis

and

High

Voltage

Circuits .........

5-5

3. Adjust

Deflection

Amptifier

Gain

and

Frequency

Response

.............

5-6

4. Adjust

Digital

Storage

Calibration

....

5-g

5. Adjust

Sweep

Timing ....

5-g

6. Adjust

Frequency

Gontrol

System

and

Dot

Marker

Position ....

S-g

7. Adjust

Log

Amplifier

.........................

5-11

8. Adjust

Resolution

Bandwidth

and

Shape Factor ..............

5-14

9. Preset

the Variable

Resolution

Gain

and Band

Leveling

.....,..................

5-19

10. Adjust

Calibrator

Output Levet

........

5-20

11. Adjust

lF

Gain ..............

S-20

12. Adjust

B-SAVE

A

Refergnce

Level

......... .......5-21

13.

Adjust

Preselector

Driver ................

S-21

14.

Adjust

Band

Leveling

for

Coaxial

Bands ...................

5-24

Section 6

Page

15. Adjust

Band

Leveling for

Waveguide

Bands ..............

5-25

16. PhasE

Lock

Calibration ....................

5-2S

OPTION INSTRUMENTS

ONLY .............

5-29

17.

Adjust

Option 07

VR Band Leveling 5-29

18. Adjust

Option 42 Module

.................

5-29

MAINTENANCE

TNTRODUCTTON

...............................

6-1

Removing

the

lnstrument

from its

Cabinet

..........

6-1

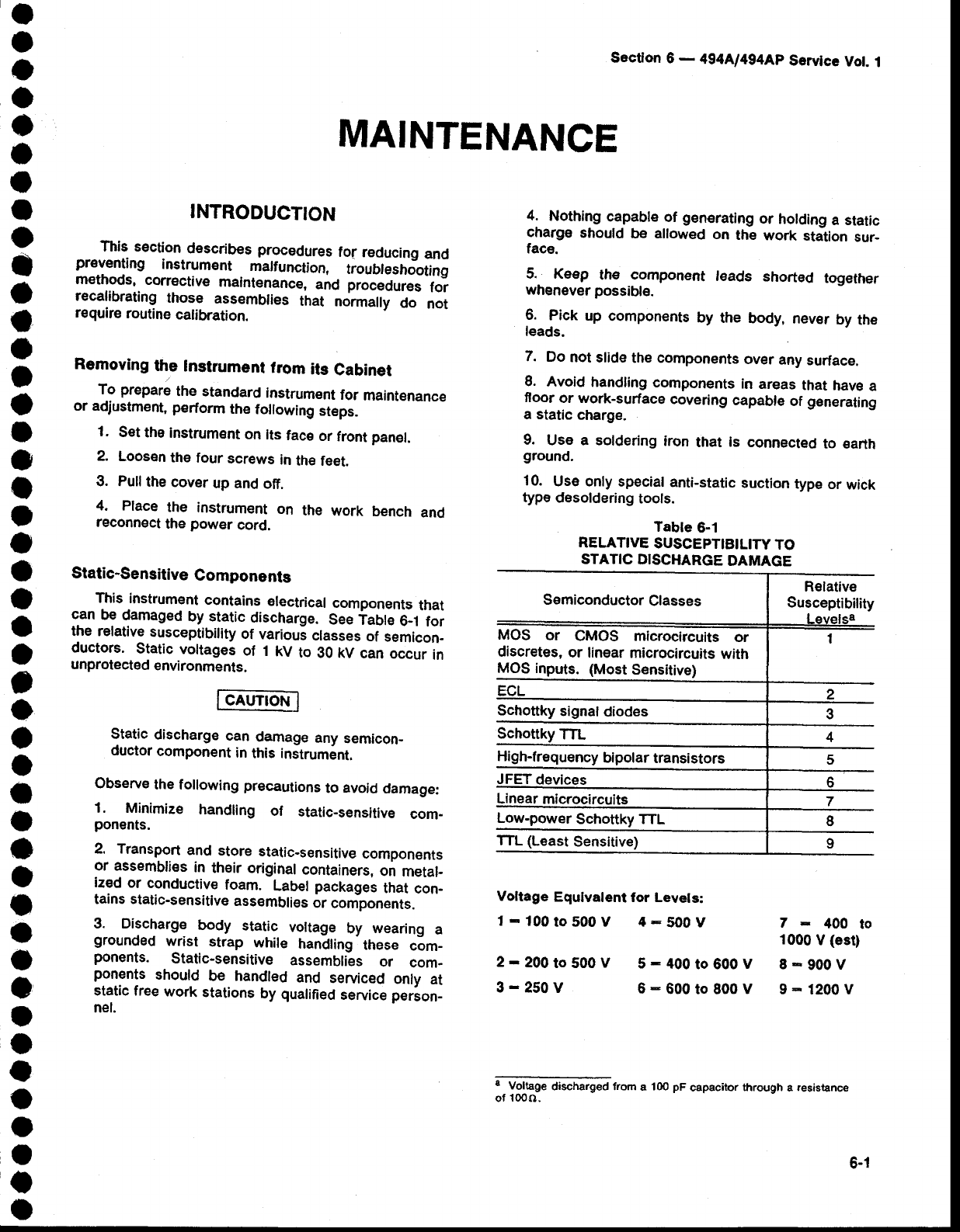

static-sensitive

components .......

6-1

PREVENTIVE

MAINTENANCE

...............

6.2

Elapsed Time

Meter

.....................

6-2

Cleaning ......-............

6-2

Lubrication ...............

6-2

Fixtures and

Tools

for Maintenance

.................,.........

6-2

Visual lnspection

..........................

6-2

Transistor and Integrated

Circuit Checks ..........

6-2

Performance

Checks

and Recalibration

.........................

6-3

Saving Stored Data

in

Battery-Backup

Memory

...............

6-3

TROUBLESHOONNG ........6.3

Troubleshooting

Aids ...................

6-9

Diagrams .............

6-3

Circuit

Board

lllustrations and

Component

Locator Charts .....

6-4

Diagnostics ..........

6-4

General

Troubleshooting

Techniques ...............

6-4

Semiconductor Checks

............

6-4

Diode

Checks

..........................

6-4

Diagnostic Firmware

................,...

6-5

Troubleshooting

Steps

.................

6-5

DTAGNOSTTCS

......................................

6-5

TROUBLESHOOTING

USING

THE

ERROR

MESSAGE DISPLAY

.... 6.5

Introduction ..............6-5

Combination of Error

Messages

...

6-6

Procedure Format .... 6-6

TRACE MODES ............

6-14

Alternate Frequency Display

........

6-14

Auxiliary Synthesizer Control .......

6-14

Correction

Disable/Enable ........-...

6-14

coRRECTtVE MATNTENANCE ..............

6-15

Handling Static

Sensitive

Components .............6-1

5

Obtaining

Replacement Parts .......

6-1

5

Parts

Repair

and Return

Program ...................

6-1

5

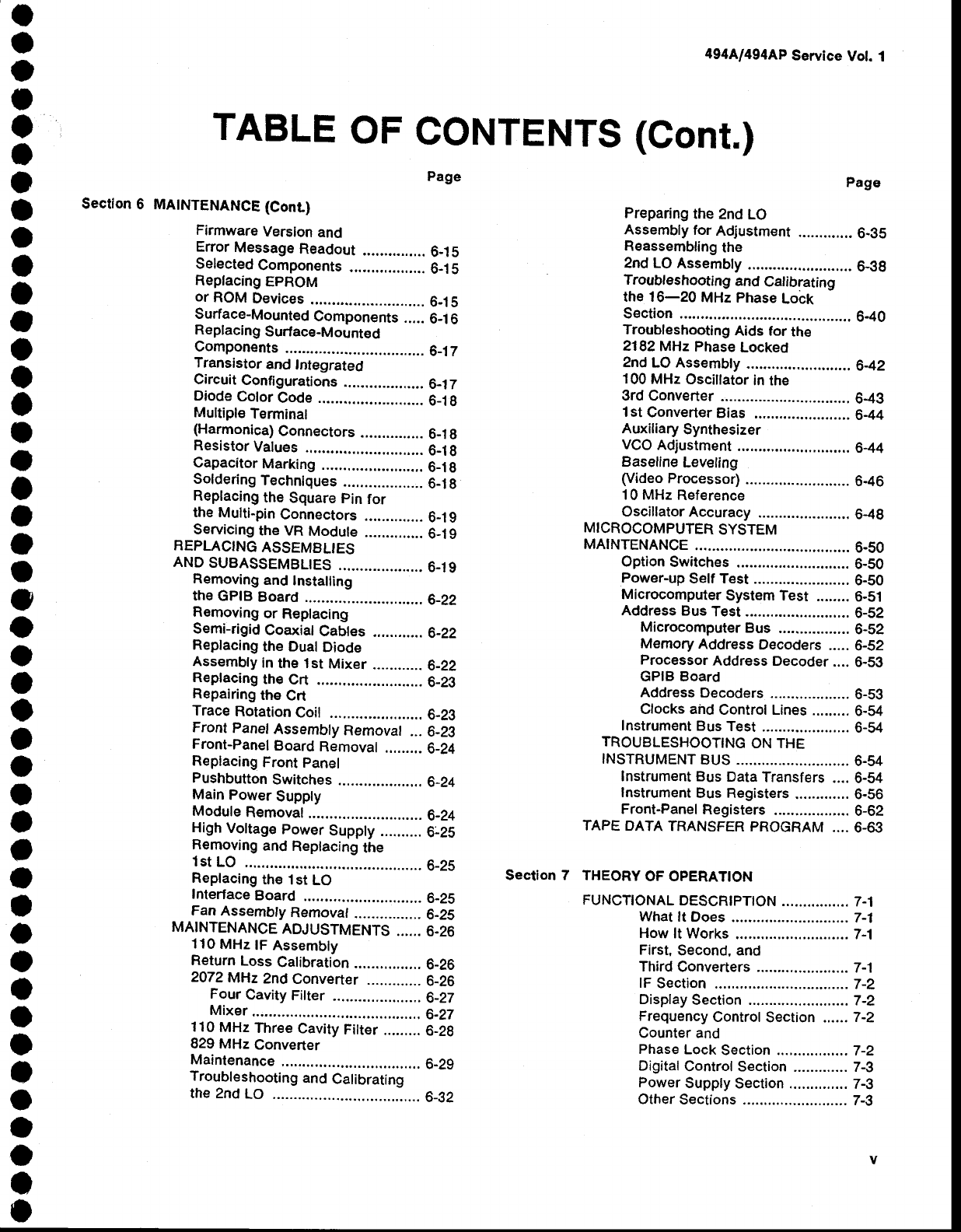

TABLE

OF

CONTENTS

(Conr.)

o

o

o

I

O

I

I

o

o

O

I

a

o

o

a

I

o

I

o

o

t

o

o

o

a

o

o

o

I

o

a

a

t

o

O

o

I

o

o

o

a

o

o

o

494A/494AP

Service

Vot.

1

Section

6

page

MAINTENANCE

(Conr)

Firmware

Version

and

Enor

Message

Readout

...............

6-1

5

Selected

Components

..................

6-1

5

Replacing

EPROM

or

ROM

Devices ........

6-15

Surface-Mounted

Components

.....

6_1

6

Replacing

Surface-Mount€d

Components ..............

6_17

Transistor

and

Integrated

Circuit

Configurations

................,..

6_1

7

Diode

Cotor

Code .........................

6_1

g

Multiple

Terminal

(Harmonica)

Connectors

...............

6_1

g

Resistor

Values .........

6-1g

Capacitor

Marking .....

6_1g

Soldering

Techniques

...................

6-1

g

Replacing

the

Square

pin for

the

Multi-pin

Connectors

..............

6_1g

Servicing

the VR

Module

..............

6-1g

REPLACING

ASSEMELIES

AND

SUBASSEMBLTES

....................

6_19

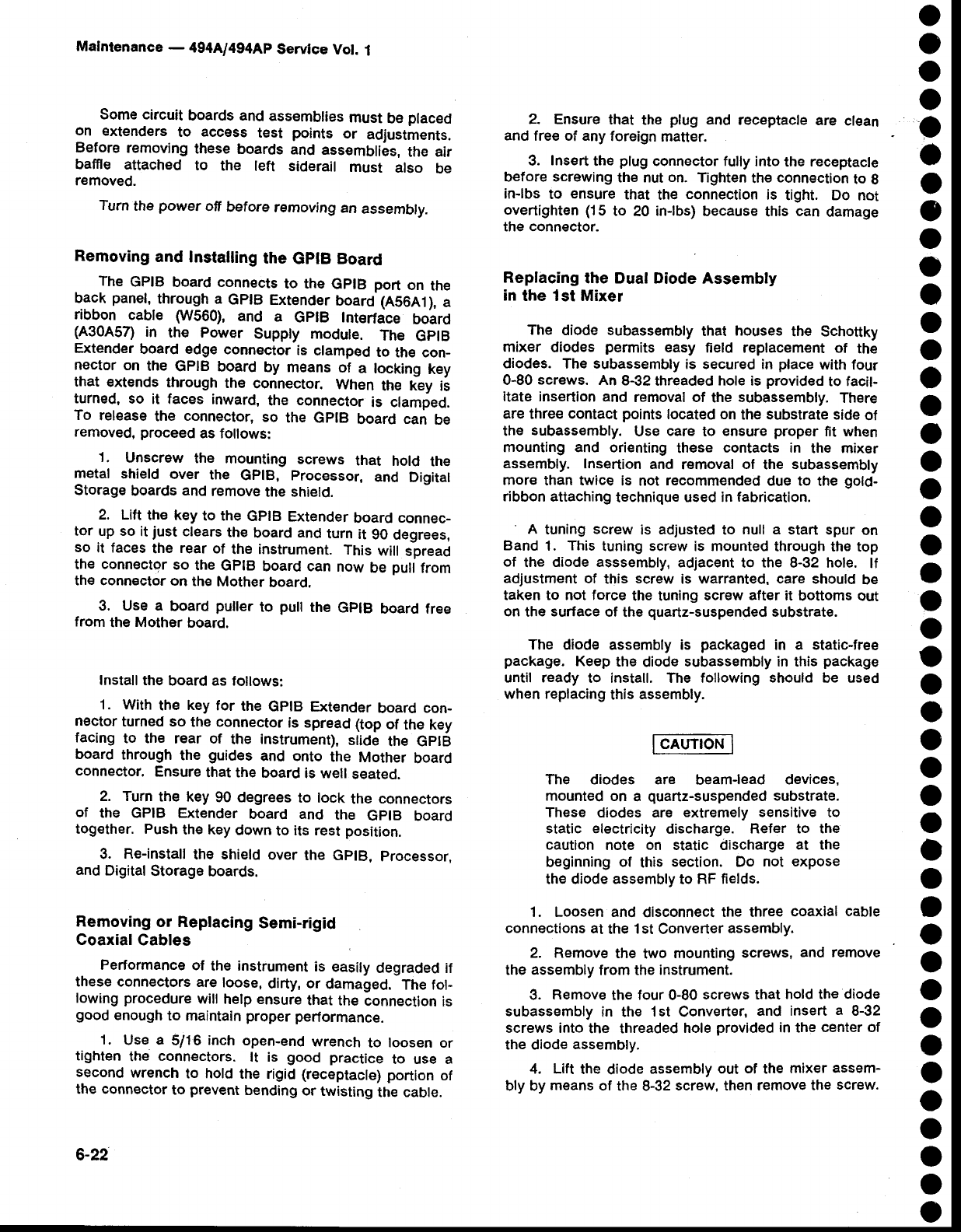

Removing

and

Installing

the

GPIB

Board .........6-22

Removing

or Replacing

Semi-rigid

Coaxial

Cables

............

6_22

Replacing

the Dual

Diode

Assembty

in

the 1st

Mixer

............

6_22

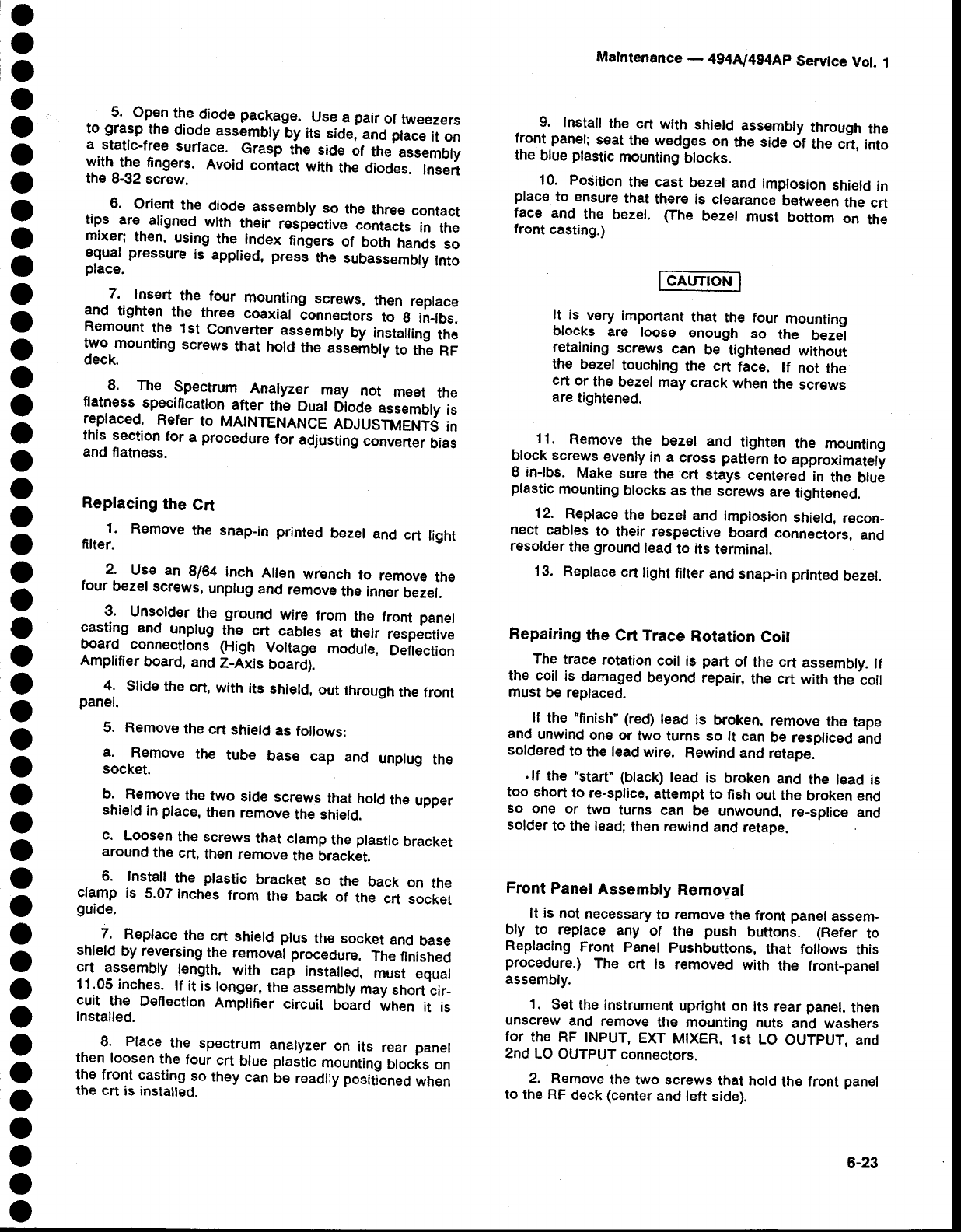

Replaeing

the

Crt ......

6_23

Repairing

the

Crt

Trace

Rotation

Coil ...

6-29

Front

Panel

Assembly

Removal

...6-29

Front-Panel

Board

Removal

.........

6_24

Replacing

Front

panel

Pushbutton

Switches

....................

6_24

Main

Power

Suppty

Module

Removal ........

6_24

High

Vottage

power

Supply

..........

6_25

Removing

and

Replacing

the

lst

LO ..6_25

Replacing

the

l st LO

Interface

Board .........

6_25

Fan

Assembty

Rernovaf

................

6-25

MAINTENANCE

ADJUSTMENTS

......

6.26

110

MHz

tF

Assembty

Return

Loss

Calibration

................

6-26

2072MHz

2nd

Converter

.............

6_26

Four

Cavity

Filter

..........

...........

6_27

Mixer......... ...........,9-27

110

MHz

Three

Cavity

Fitter

.........

6_29

829 MHz

Converter

Maintenance ..............

6_29

Troubleshooting

and

Calibrating

the 2nd

LO ............. ..6-32

Page

Preparing

the

2nd

LO

Assembly

for

Adjustment

.............

6-35

Reassembling

the

2nd LO

Assembty .....

6-9g

Troubleshooting

and

Calibrating

the 16-20 MHz Phase

Lock

Section .....................

6-40

Troubleshooting

Aids

for

the

2182MHz

Phase

Locked

2nd

LO Assembty .....6-42

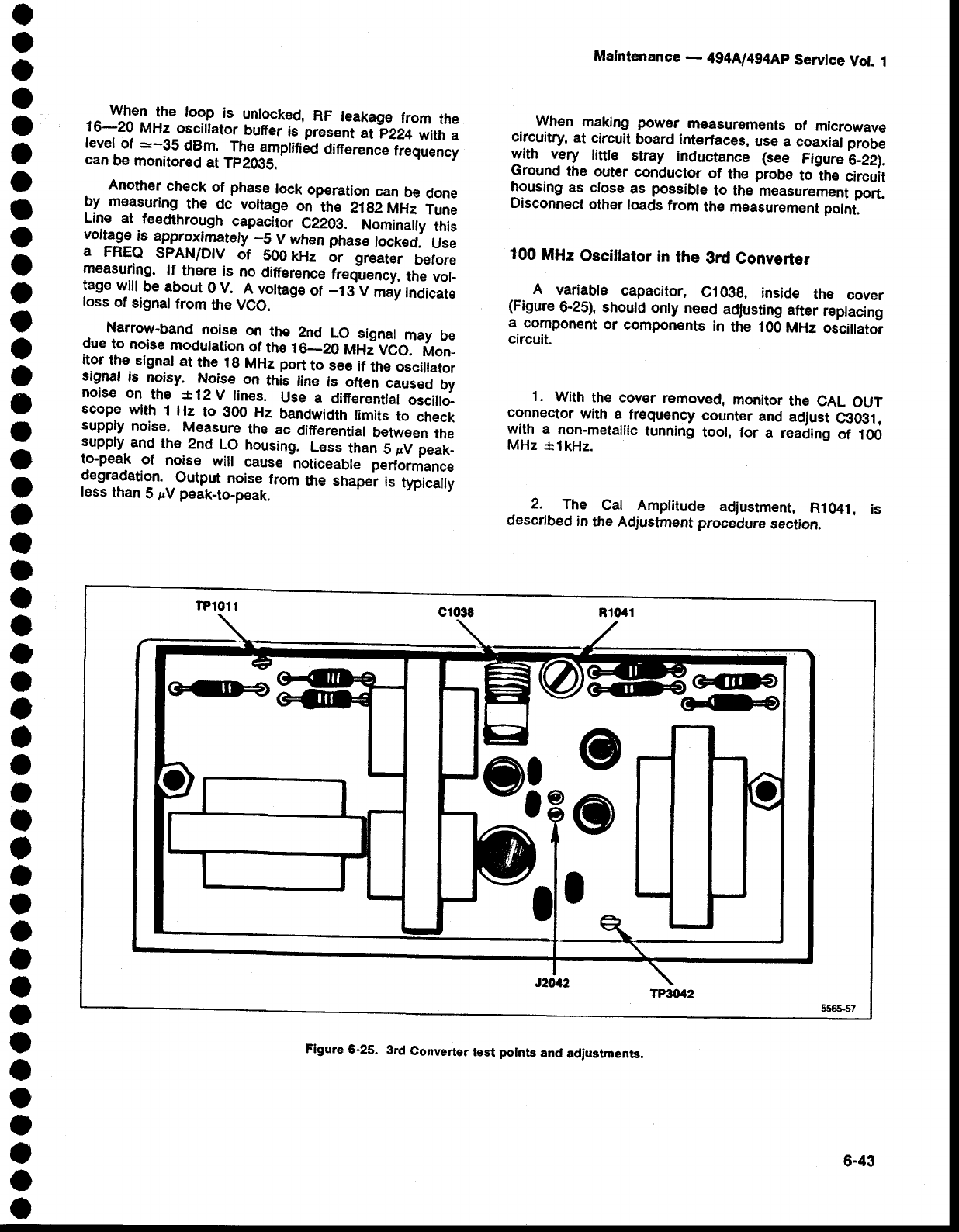

100

MHz

Osciltator

in the

3rd Converter

...............................

649

l st

Converter

Bias .....................,.

6-44

Auxiliary

Synthesizer

VCO

Adjustment

...........................

6-44

Baseline

Leveling

(Video

Processor) .....

6-46

10 MHz

Reference

Oscillator

Accuracy .. 6-49

MICROCOMPUTER

SYSTEM

MATNTENANCE

............. ....

6-50

Option

Switches .......

6-50

Power-up

Self Test ...

6-50

Microcomputer

System Test ........

6-51

Address

Bus

Test .....

6-52

Microcomputer

Bus .................

6-52

Mernory

Address

Decoders

.....

6-52

Processor

Address

Decoder

....

6-59

GPIB Board

Address

Decoders

Clocks ahd

Control Lines

.........

Instrument

Bus

Test

TROUBLESHOOTING

ON THE

INSTRUMENT

BUS

Instrument Bus

Data

Transfers

....

Instrument

Bus Registers,............

Front-Panel

Registers

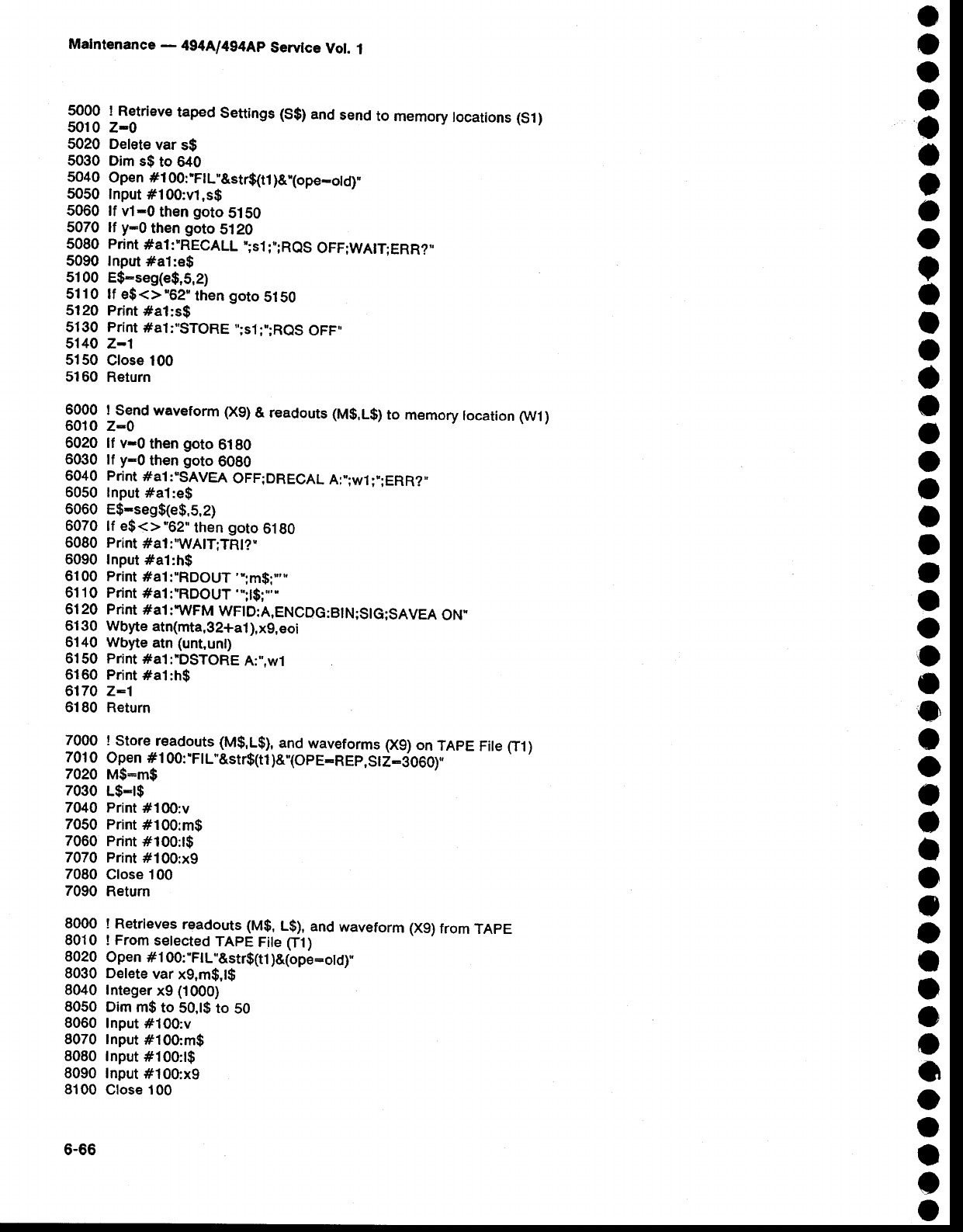

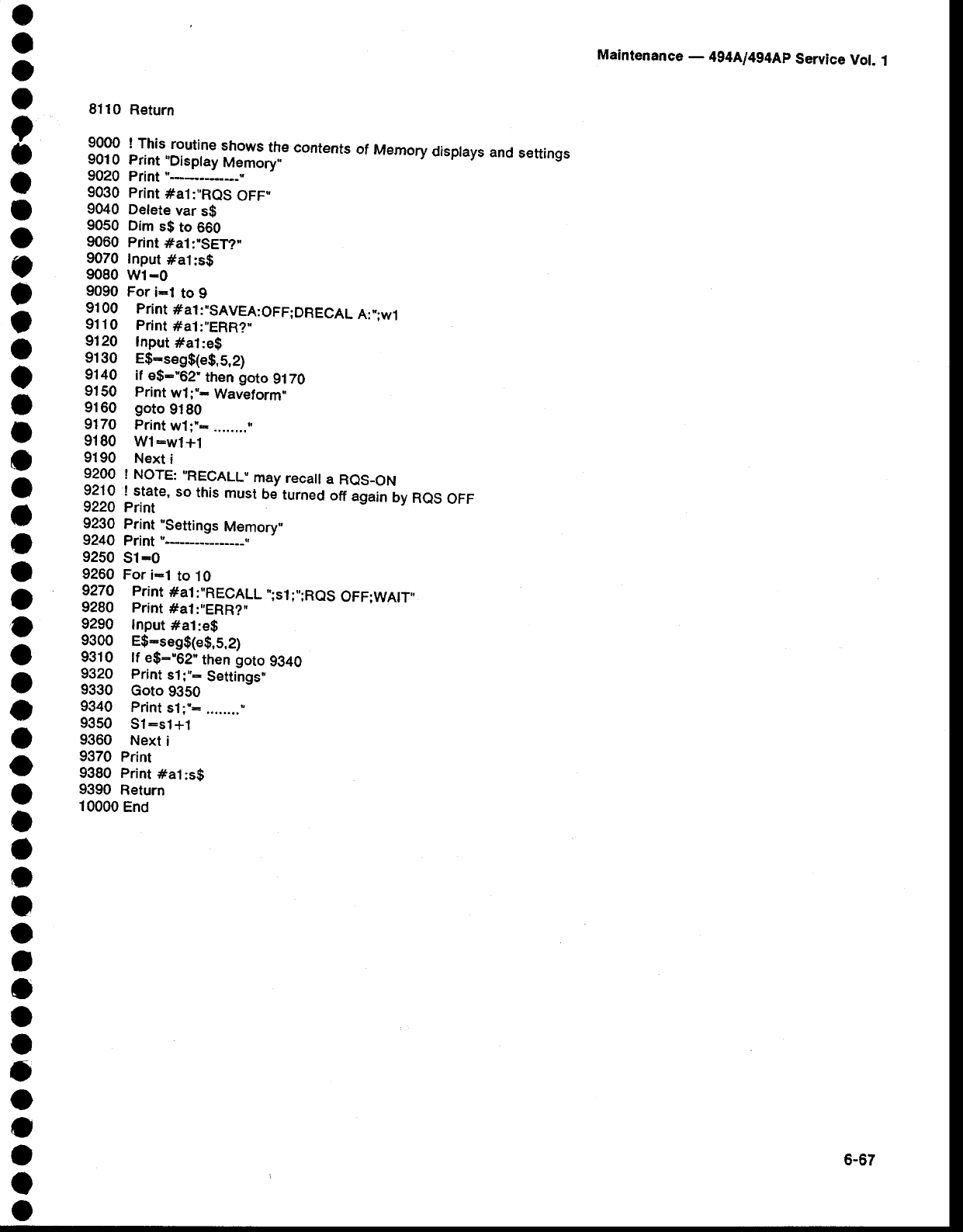

TAPE OATA

TRANSFER

PROGRAM

....

THEORY

OF OPERATION

FUNCTTONAL

DESCR|pTtON

............

.... 7

-1

What

lt Does

................-...........

7-1

How

lt Works .......7-1

First,

Second, and

Third

Gonverters ...........

........... 7

-1

lF

Section ..-.........7-2

Display

Section ....7-2

Frequency

Control

Section .,....

7-2

Counter and

Phase

Lock

Section .............,...

7-2

Digital

Control Section

............. 7-3

Power

Supply

Section ..............

7-3

Other

Sections

...............

.......... 7-3

6-s3

6-54

6-54

6-54

6-54

6-56

6-62

6-63

Section 7

TABLE

OF

CONTENTS

(Cont.)

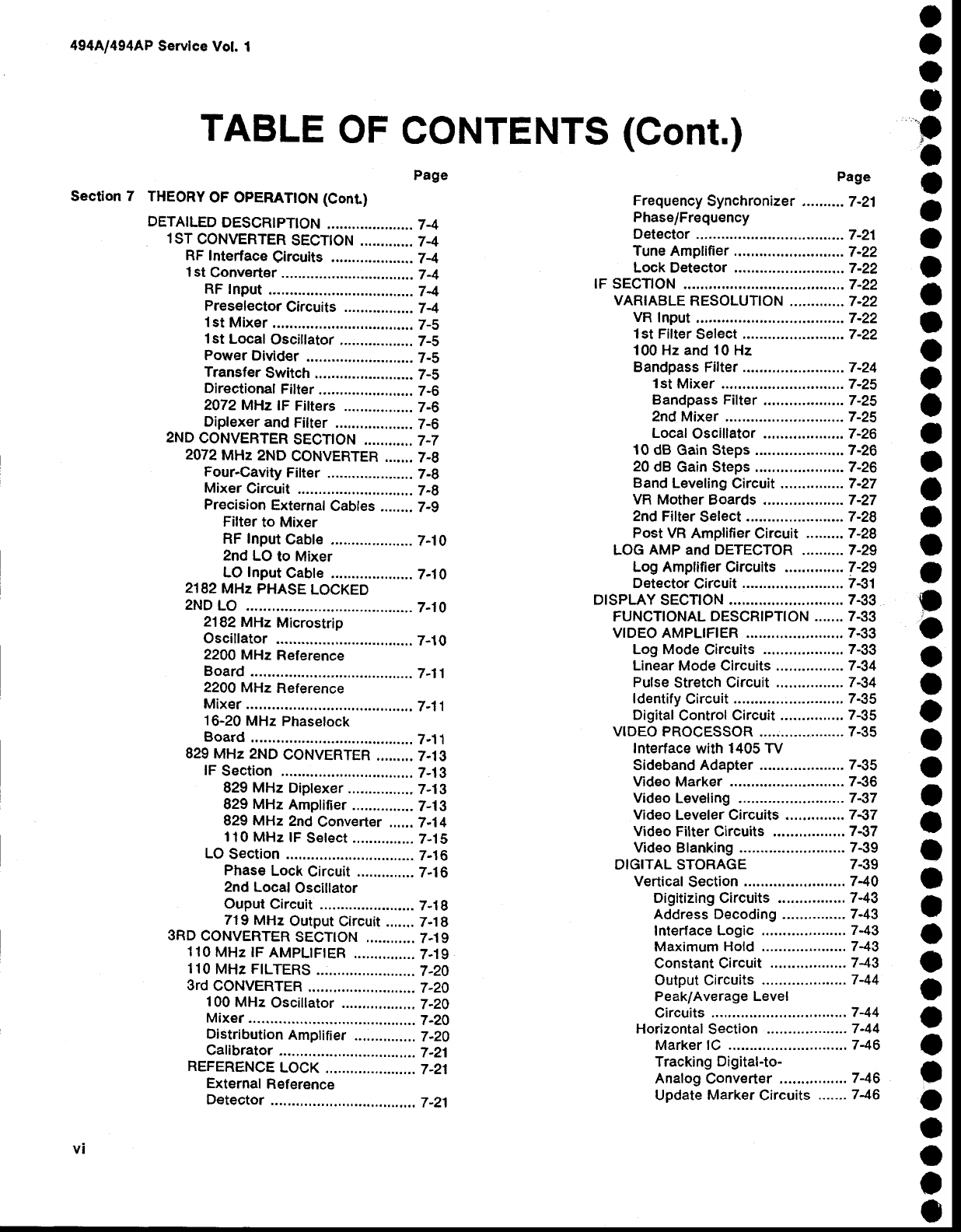

Page

Section 7 THEORY

OF OPERATTON

(Cont)

DETAILED

DESCR|PT|ON

................

.....

7

-4

1ST

CONVERTER

SECTTON

.............

7_4

RF Interface

Qircuits

....................

7-4

'l

st

Converter

.................

..........,,,..

7-4

RF

Input ...............

7-4

Preselector

Circuits ...........,.....

74

lst Mixer ..............

7_5

1st

Local

Oscillator

..................

7_5

power

Divider ......

7-s

Transfer

Switch .... 7-s

Directional

Filter

................,......

Z-6

2O72MHz

tF

Fitters

....,............

7-6

Diplexer

and

Filter

...,...............

Z-6

2ND

CONVERTER

SECTTON

............

7_7

2072

MHz 2ND

CONVERTER

.......

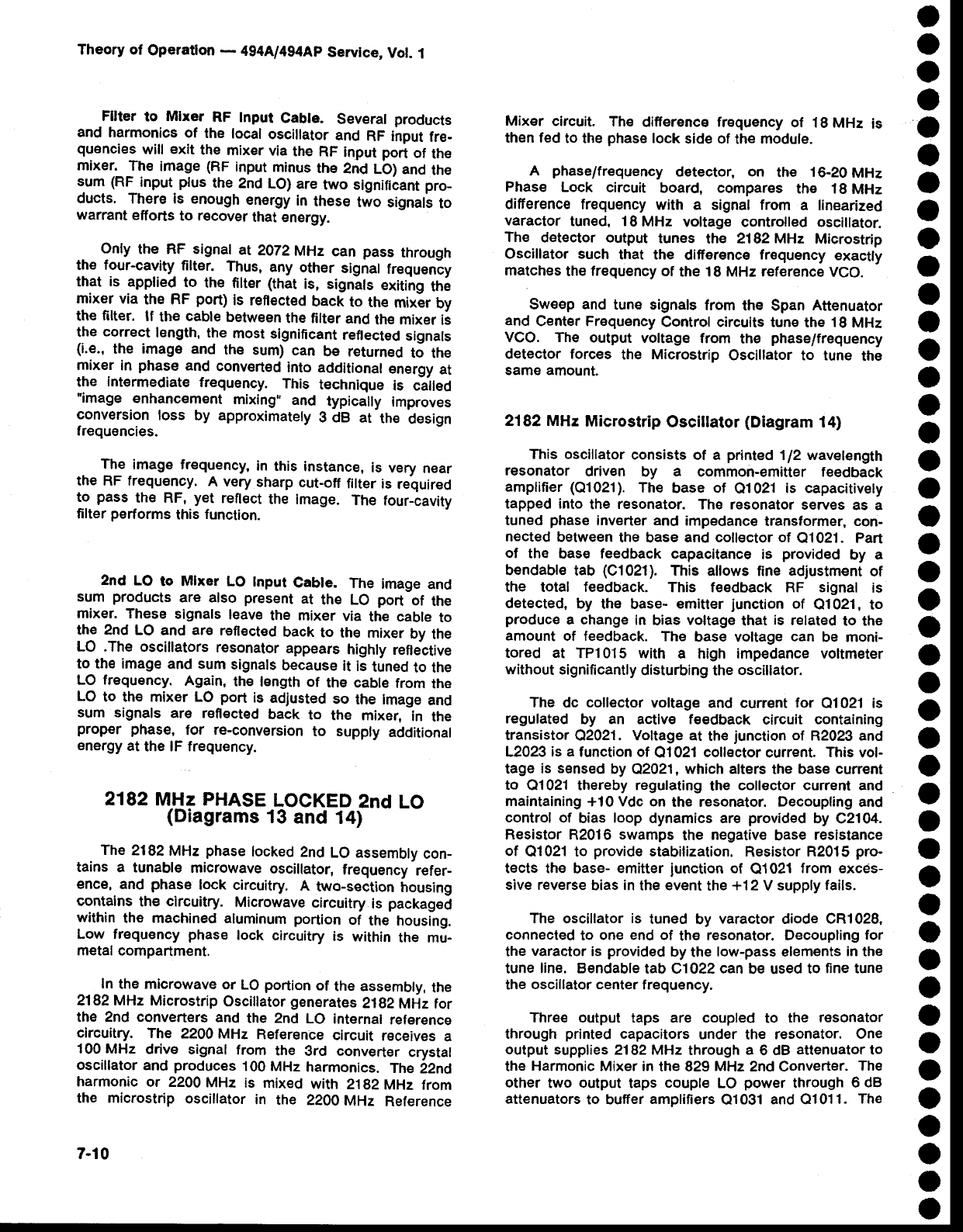

7-8

Four-Cavity

Fi|ter

.......... ...........

Z

-g

Mixer

Circuit

............................

7-g

Precision

External

Cables

........

7-9

Filter

to Mixer

RF

Input

Gable

....................

7-10

2nd LO

to Mixer

LO

Input

Cable

....................

Z-10

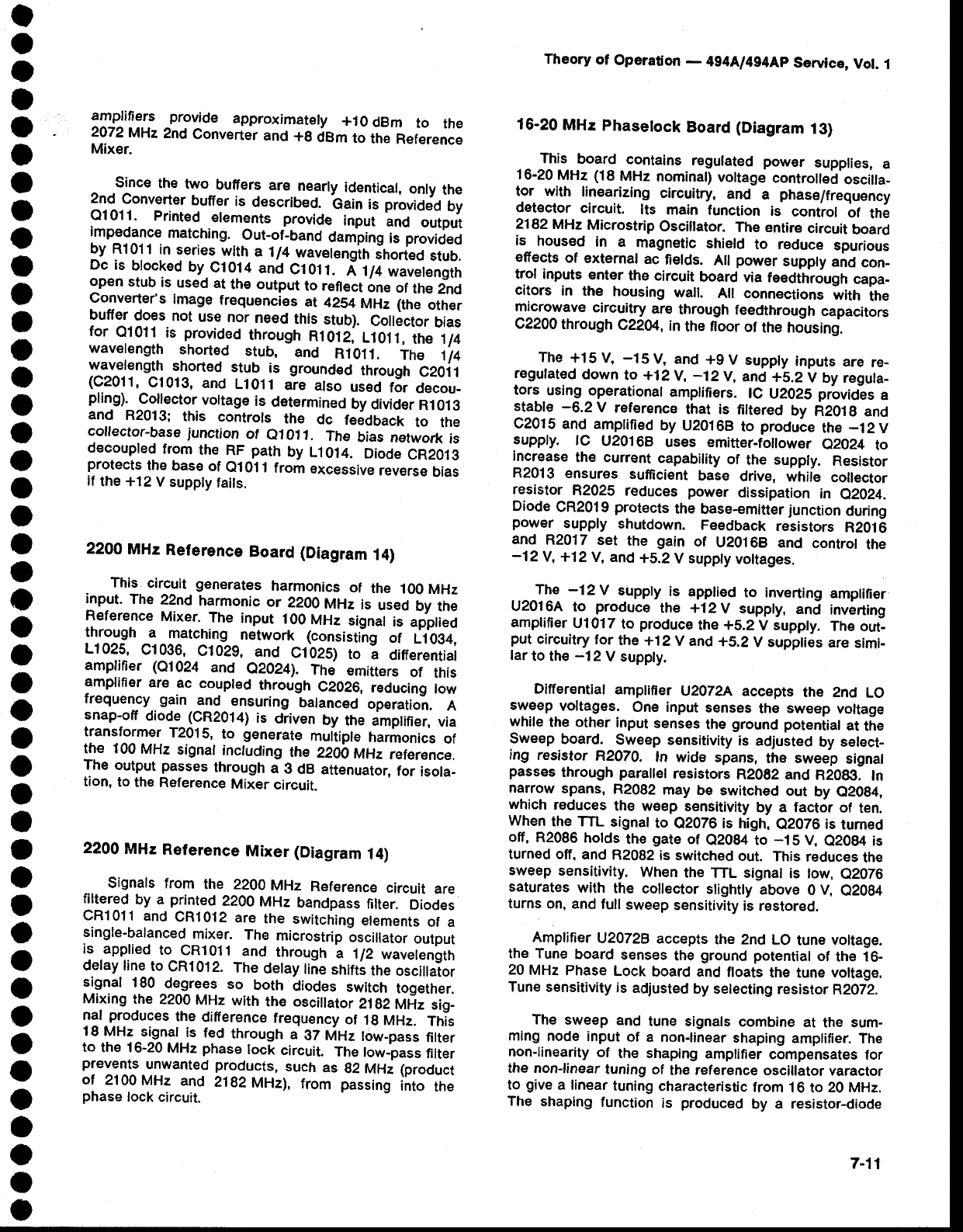

2182MHz

PHASE

LocKED

2ND

LO .....................7-10

2182MHz

Microstrip

Oscillator .............

7-10

2200

MHz Reference

Board ....................7-11

220O

MHz Reference

Mixer ......... ...........7-11

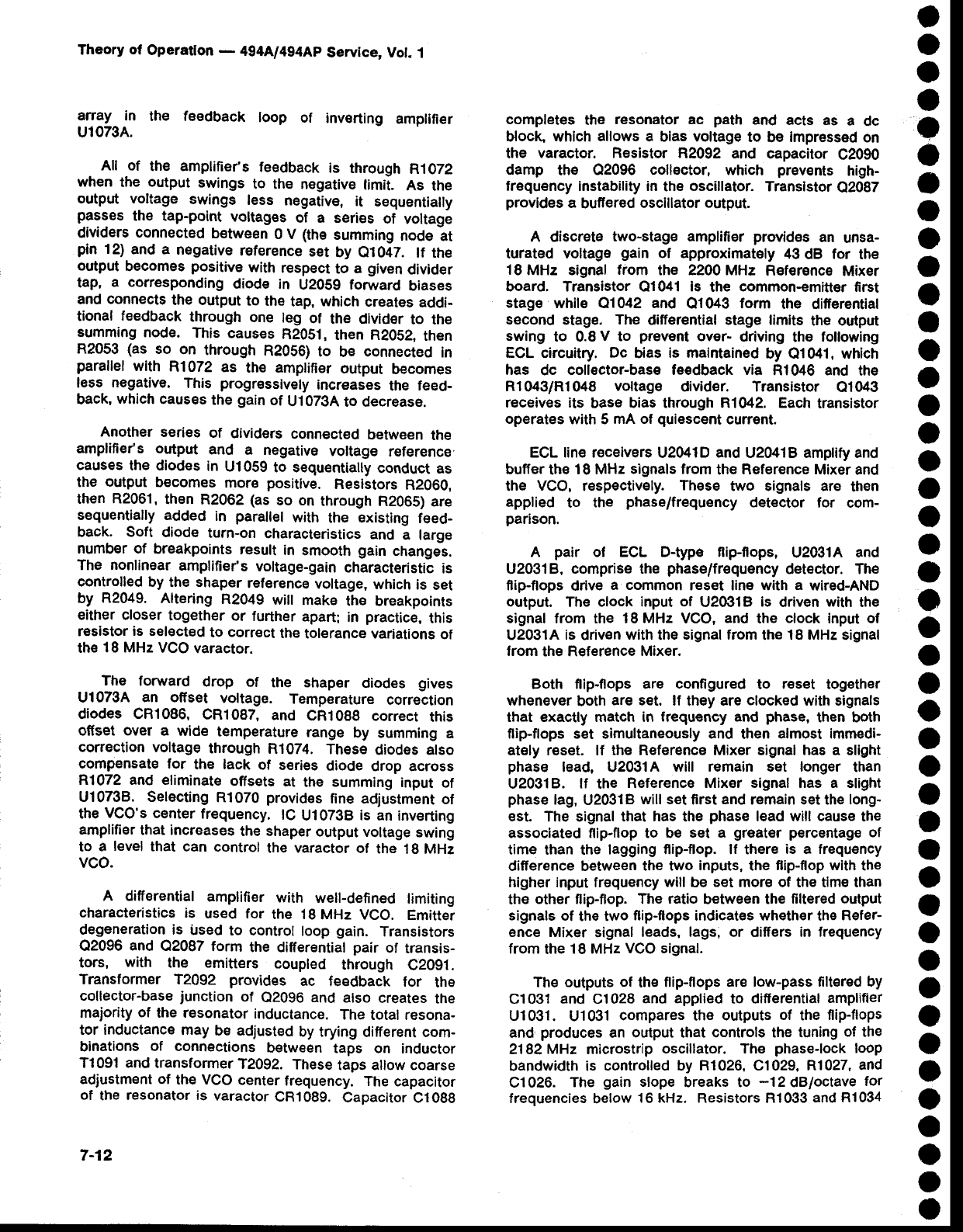

16-20

MHz

phaselock

Board ....................7-11

829

MHz 2ND

CONVERTER

.........7-19

lF

Section ............

7,13

829

MHz

Diplexer

.,..............

7-t

g

829

MHz

Amplifier

...............

t-13

829 MHz

2nd

Converter

...,..7-14

110

MHz lF

Se|ect...............

7-i5

LO

Section ...........

7-16

Phase

Lock

Circuit ..............

7-16

2nd

Local

Oscillator

Ouput Circuit ... 7-19

719

MHz

Output

Circuit

.......

7-18

3RD

CONVERTER

SECTION

......,.....

7-19

110

MHz tF

AMpLtFtER

...............

7-19

110

MHz

FILTERS

3rd

CONVERTER

............ ..............

7

-2A

100

MHz

Oscillator

..................

7_20

Mixer......... ...........

7_20

Distribution

Amplifier

...............

7

-20

Calibrator .............2-21

REFERENCE

LOCK

......,...............

7-21

External

Referance

Det€ctor ...,...,,..,...7-21

Page

Frequency

Synchronizer ..........

7-21

Phase/Frequency

Detector ...,.,..,.....,7-21

Tune Amplifi

er

...............

........... 7-22

Lock Detector ..............

.........

"..

7

-22

rF

sEcTtoN ...................7-22

VAR|ABLE

RESOLUTION

............. 7-22

VR

fnput ...............7-22

1st Filter

Select .....7-22

100 Hz and 10 Hz

Bandpass

Filter

..........

.............. 7

-24

1st Mixer ,..,,.....7-25

Bandpass

Filter

..........

....,.,..

7

-25

2nd Mixer .........7-25

Local

Oscillator .............

......

7-26

10

dB Gain Steps ..........-..........7-26

20

dB Gain Steps .....................7-26

Band

Leveling

Circuit ........,...... 7-27

VR

Mother Boards ................... 7

-27

2nd

Filter

Select ....7-28

Post

VR Amplifier

Circuit

.........7-28

LOG

AMP

and

DETEGTOR

.......... 7-29

Log Amplifier Circuits .............. 7-29

Detector

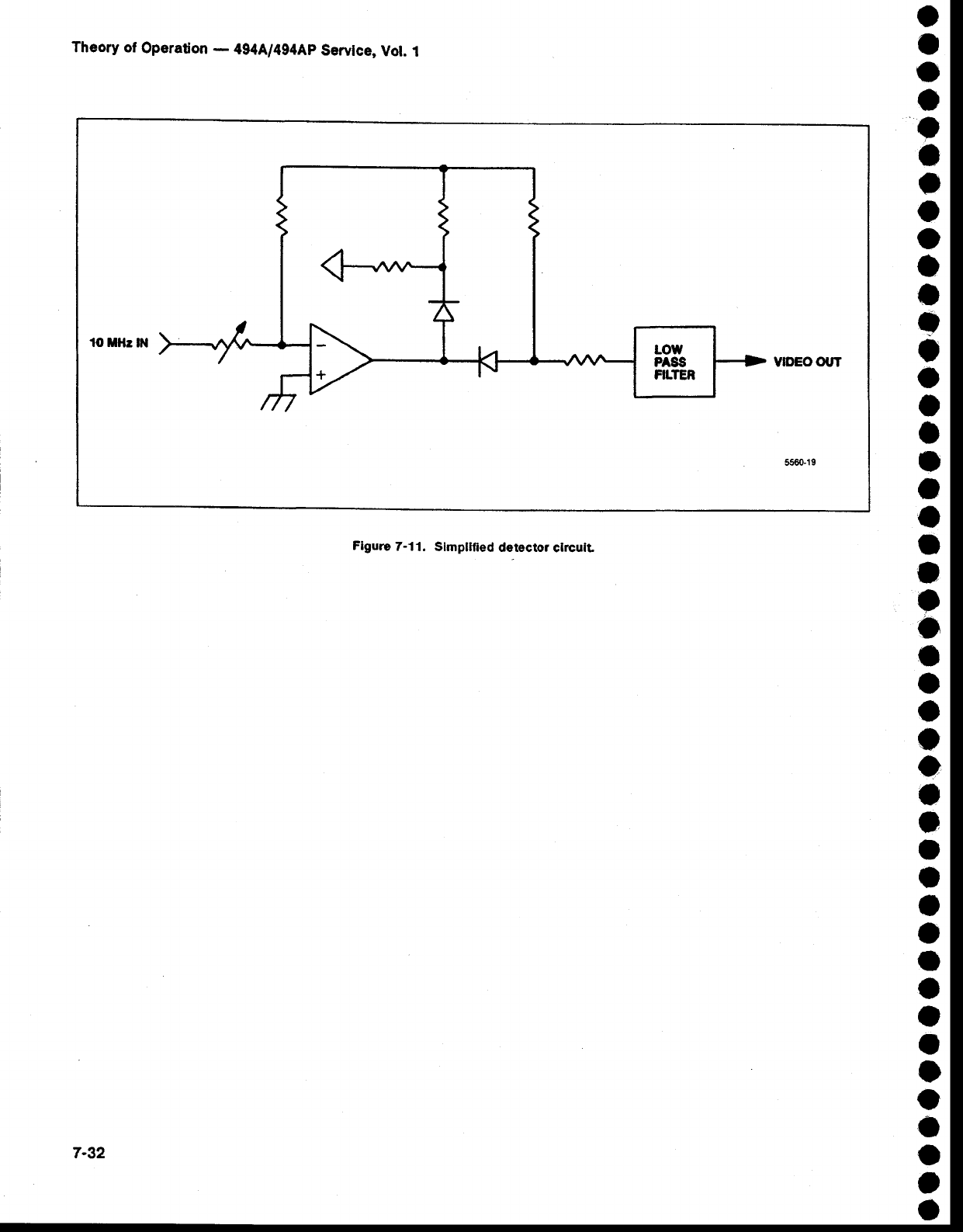

Circuit .-...7-31

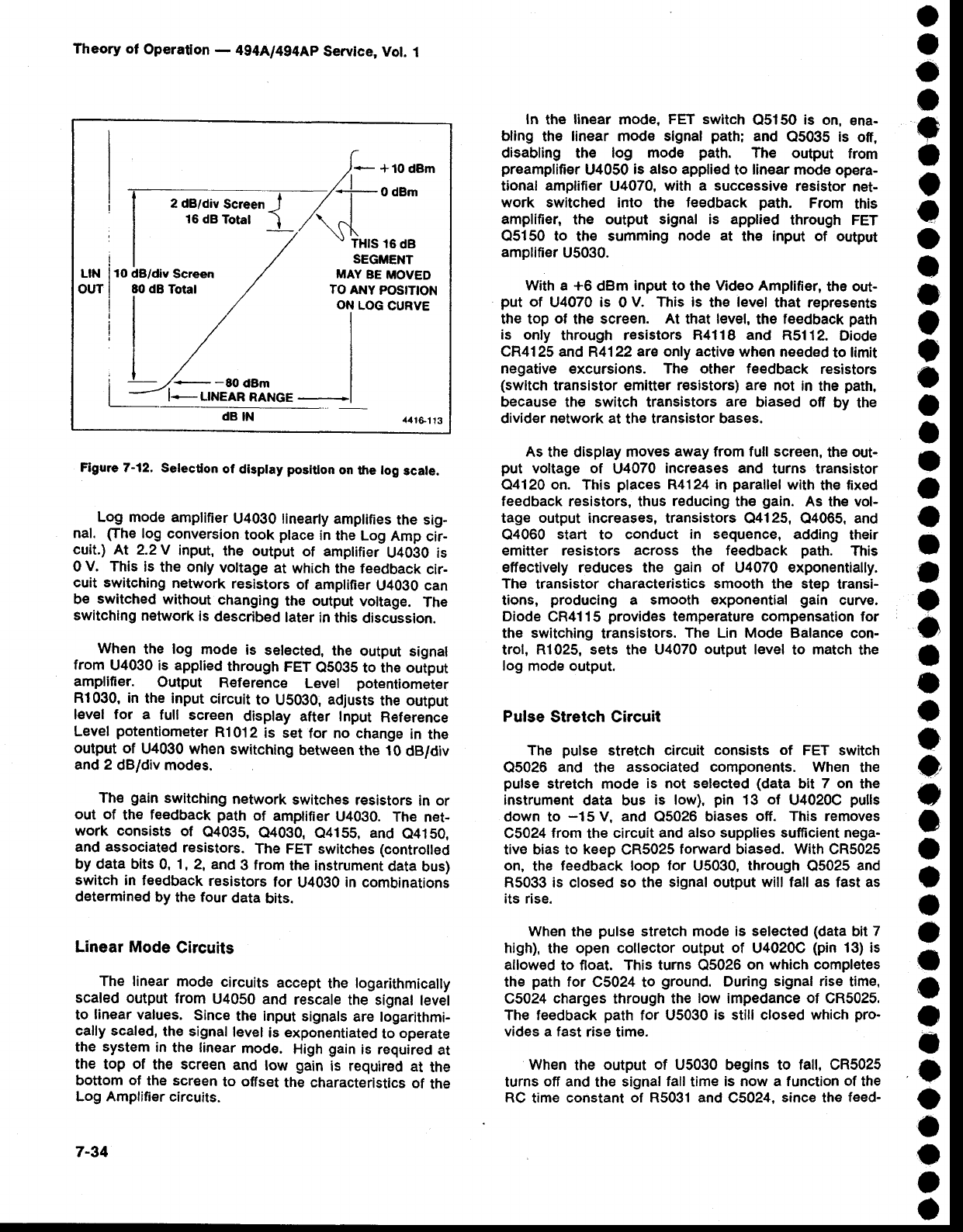

DTSPLAY

SECTTON ........7€3

FUNCTIONAL

DESCRIPTION ....... 7-33

VIDEO

AMPLIFIER .,,.7.33

Log Mode

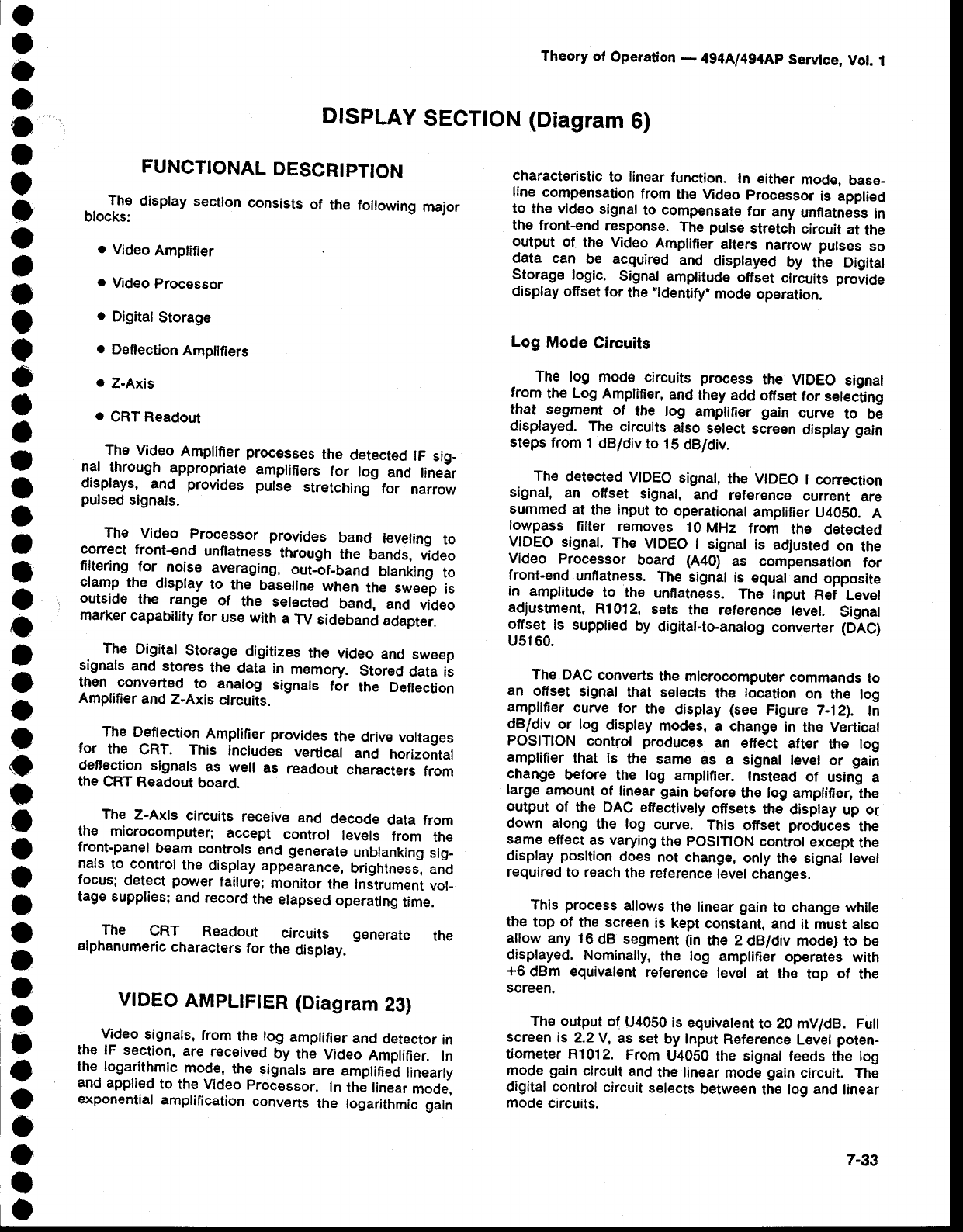

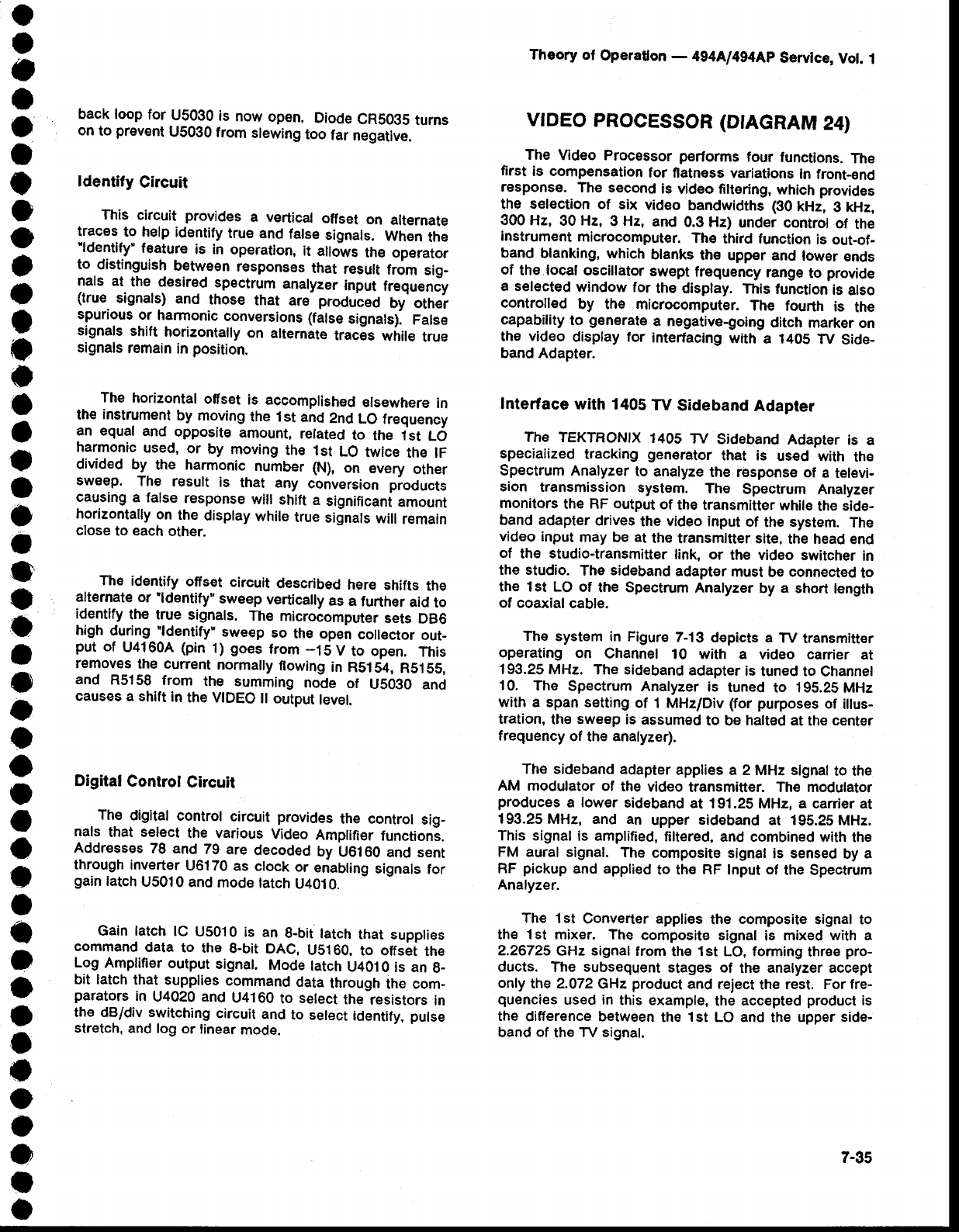

Circuits

................... 7-33

Linear

Mode Circuits ..............-.

7-34

Pulse

Stretch Circuit

................ 7-34

ldentify

Circuit .......

7-35

Digital

Control

Circuit ...............

7-35

vrDEo

pRocESSoR

.................... 7-35

Interface

with

1405 TV

Sideband

Adapter .............-...... 7-35

Mdeo Marker ...........................

7-36

Video

Leveling .......,...... ...........

7

-37

Video

Leveler

Circuits .............. 7€7

Video

Filter Circuits ......,..........

7-37

Video

Blanking

.-..............,........ 7-39

DIGITAL STORAGE 7-39

Verticaf

Section .....740

Digitizing Circuits ................ 743

Address Decoding ............... 7-43

Interface

Logic ......... ..,........

743

Maximum

Hold .................... 743

Constant Circuit

..................

7-43

Output Circuits

....................

7-44

Peak/Average

Level

Circuits .............7-44

Horizontal

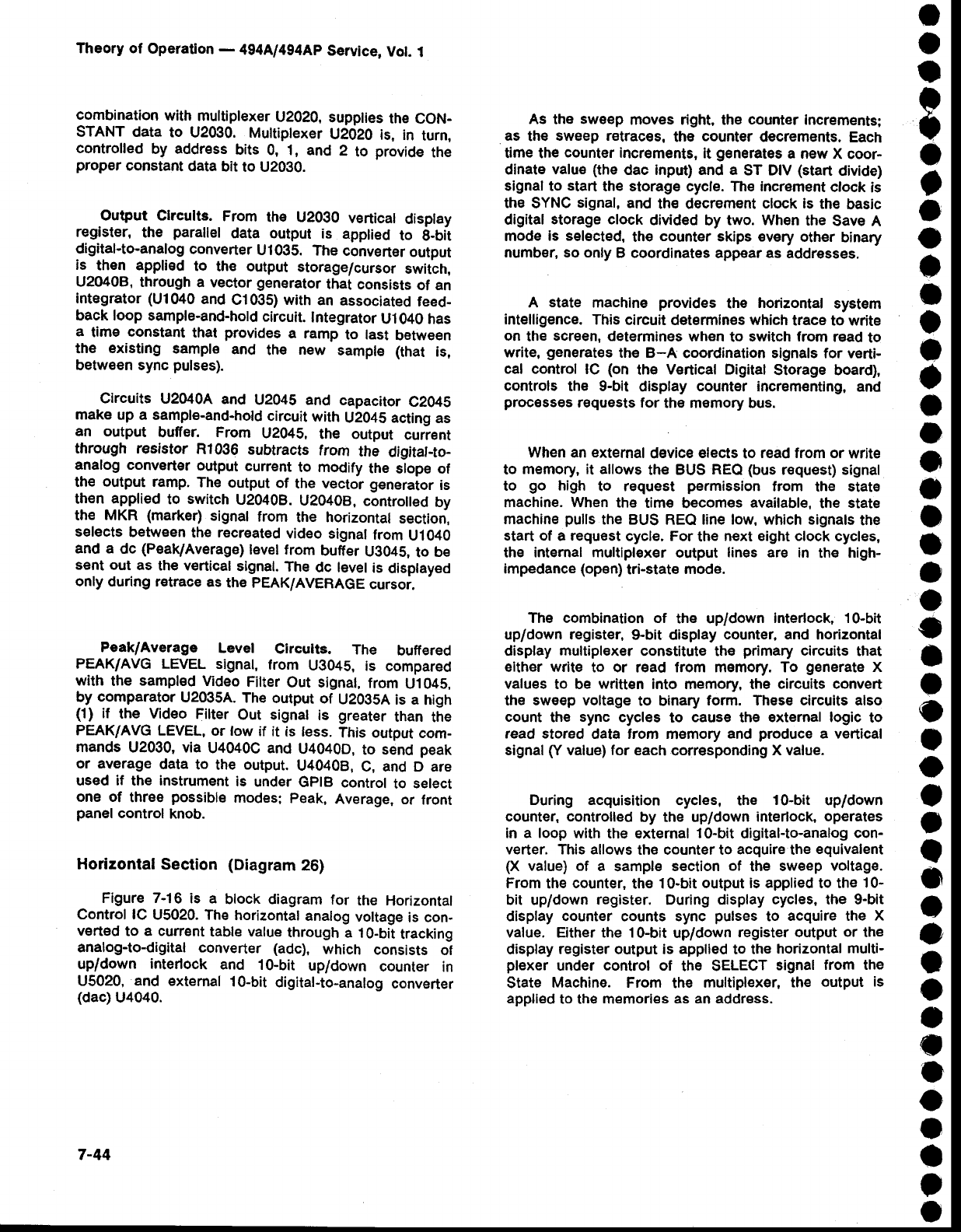

Section

.....-.............

7-44

Marker lC ............................ 7-46

Tracking Digital-to-

Analog

Converter ................

7*46

Update

Marker

Circuits .......746

a

o

o

o

't

o

o

a

a

a

o

o

o

a

o

o

t

o

o

I

o

I

o

o

o

o

o

o

o

o

o

t

o

o

o

o

o

a

o

o

o

o

o

o

494A1494AP

Servlce

Vol. 1

vl

TABLE

OF

CONTENTS

(Conr.)

o

o

o

o

o

o

O

a

o

o

o

a

o

I

t

I

o

I

o

o

I

o

o

a

o

o

o

o

o

t

o

a

I

o

o

t

t

o

a

O

o

o

o

a

494A1494AP

Service

Vot.

I

Page

Section

7 THEORY

OF

OPERATION

(Conr)

Fast

Retrace

Blanking

...,.,...

742

Memories ........7-47

DEFLECTION

AMPLIFIERS

..........

7-47

Horizontal

Section

...............,...

747

Vertical

Section ....249

Z.AXIS

AND

RF

INTERFACE

.......

7-48

RF

Interface

Circuits

................

7_49

Z-Axis

Circuits .....7_49

power-Fail

Detector

.................

7-50

power

Supply

Monitor

.............

7_50

Options

Switch .....

7-50

Timer

......... ..........

7_50

HIGH.VOLTAGE

SUPPLY

.............

7.50

High-Vottage

Osciilator

............

7-50

Voltage

Doubter ... 7_SO

High-Voltag€

Regulator

............

7_S0

Z_Axis

Gtipper ......

7_51

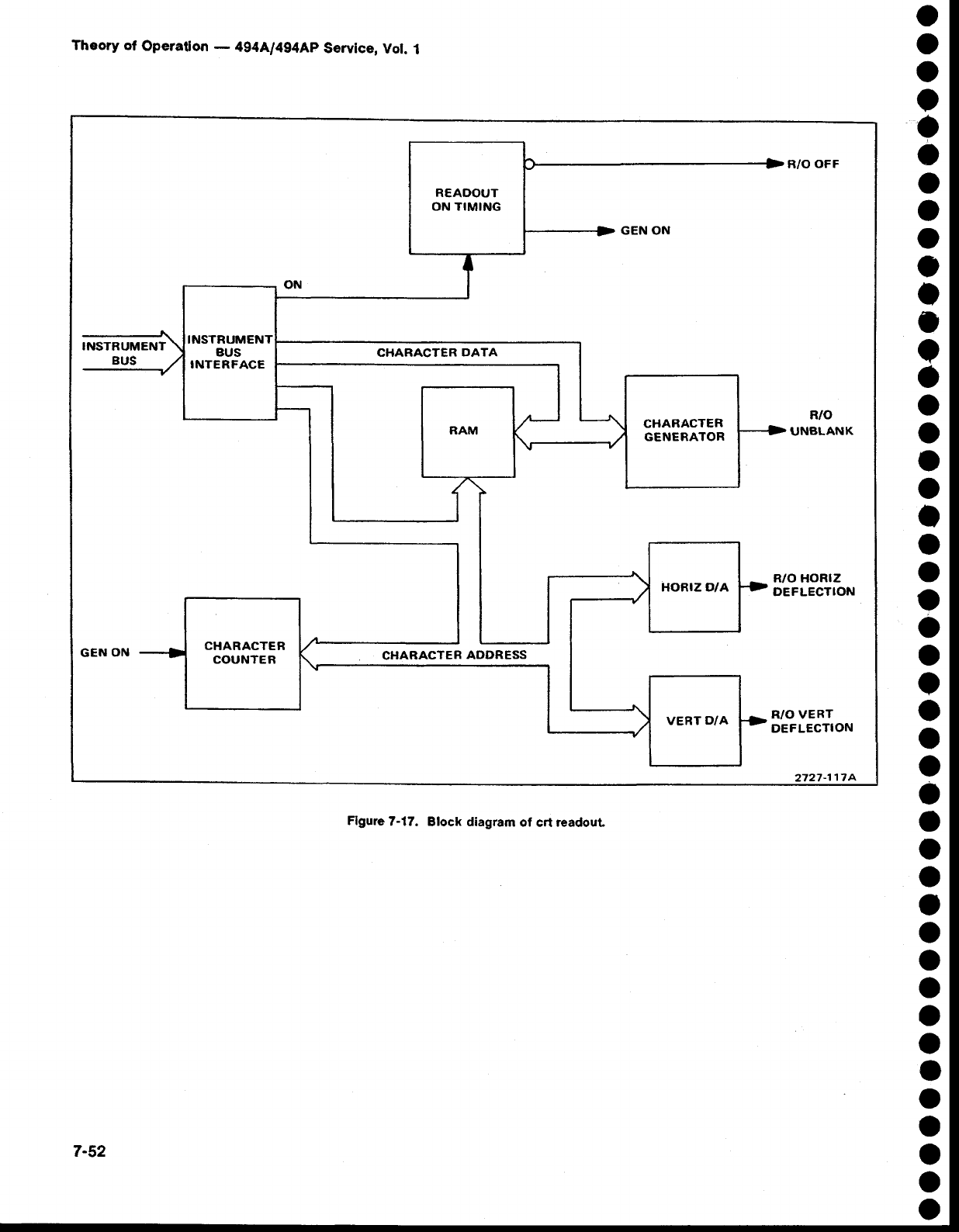

cRT READOUT

............................

7_51

Generating

Readout

.................

Z_51

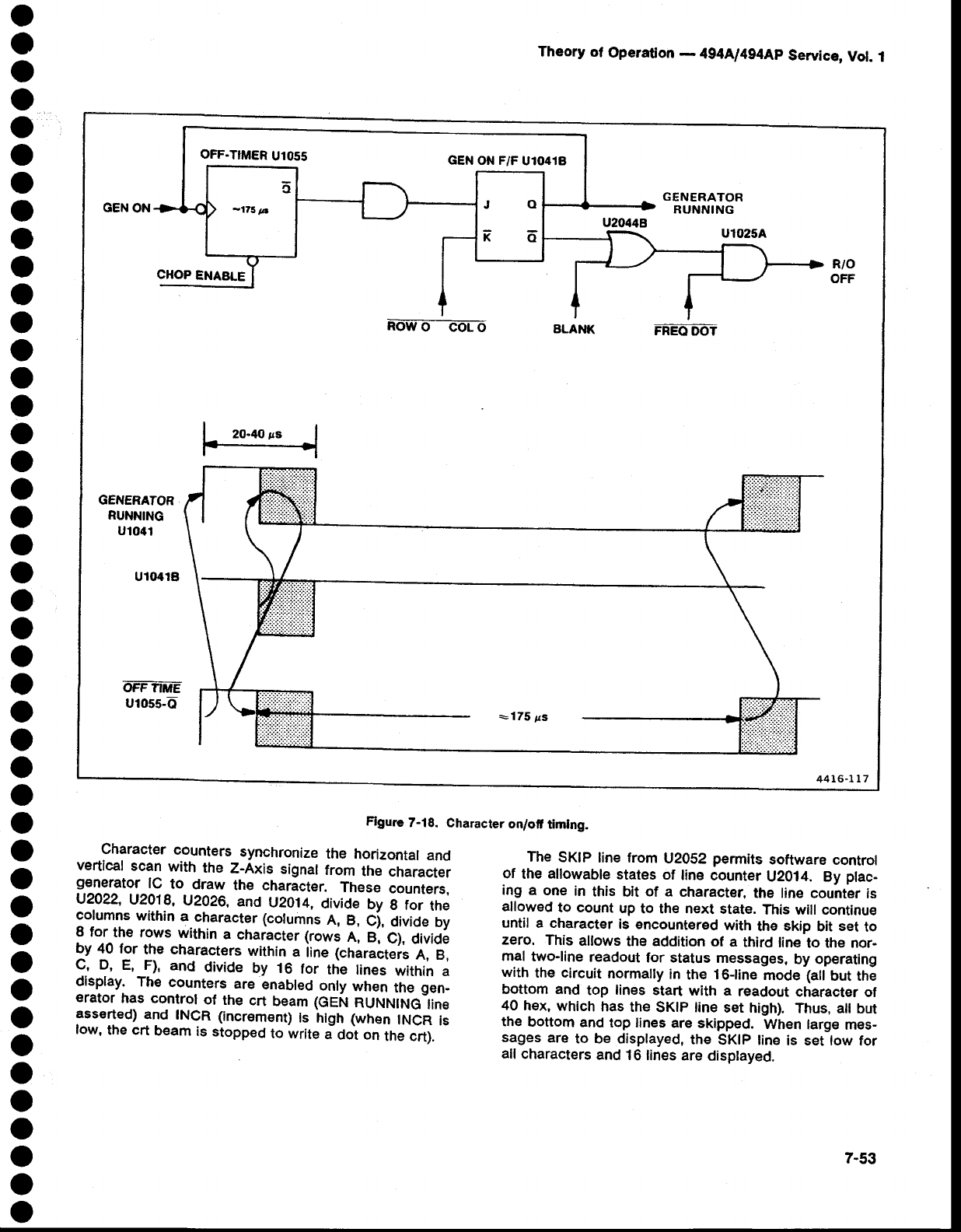

R€adout

OnlOtr Timing

.......

Z-S1

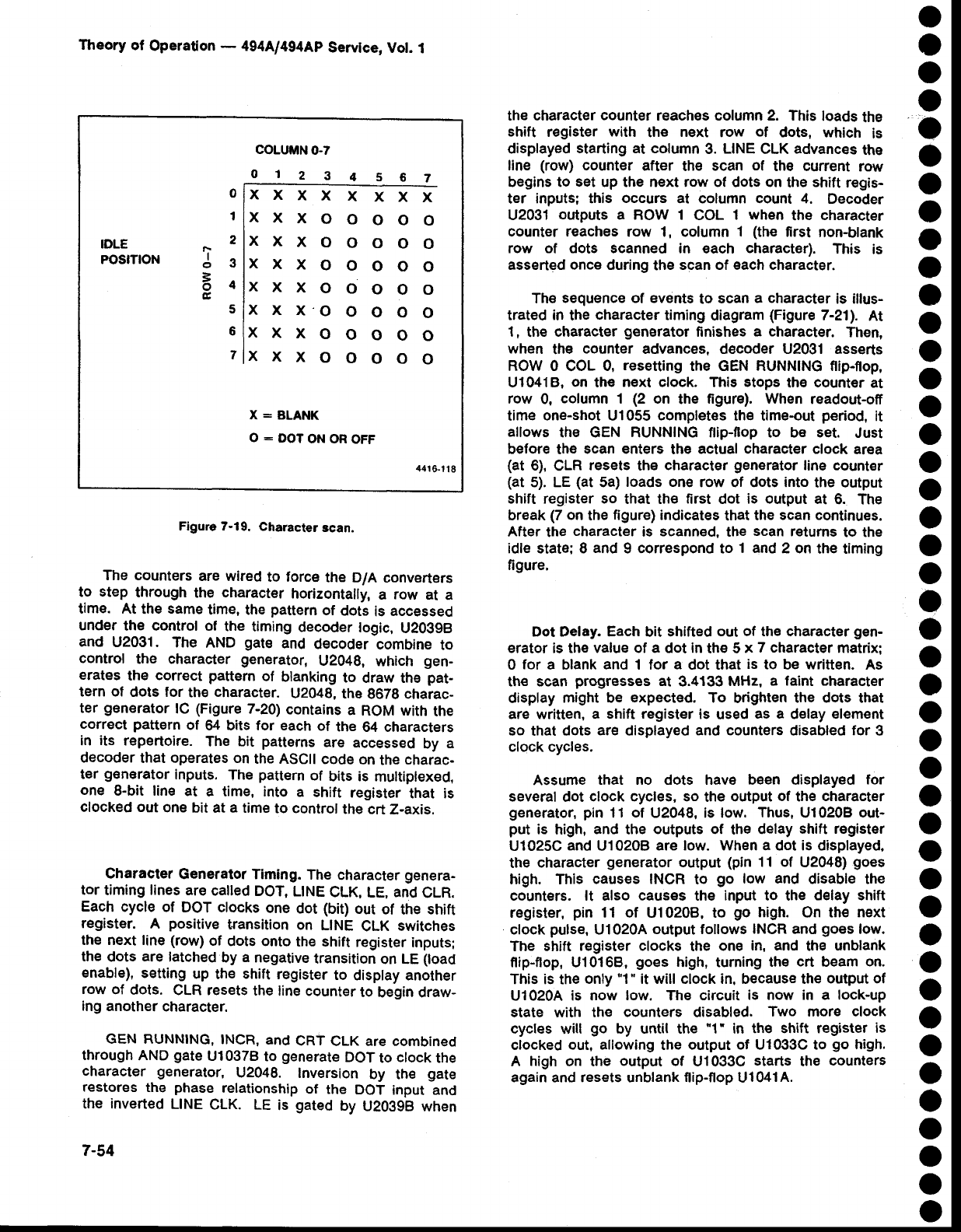

Character

Scan ...................

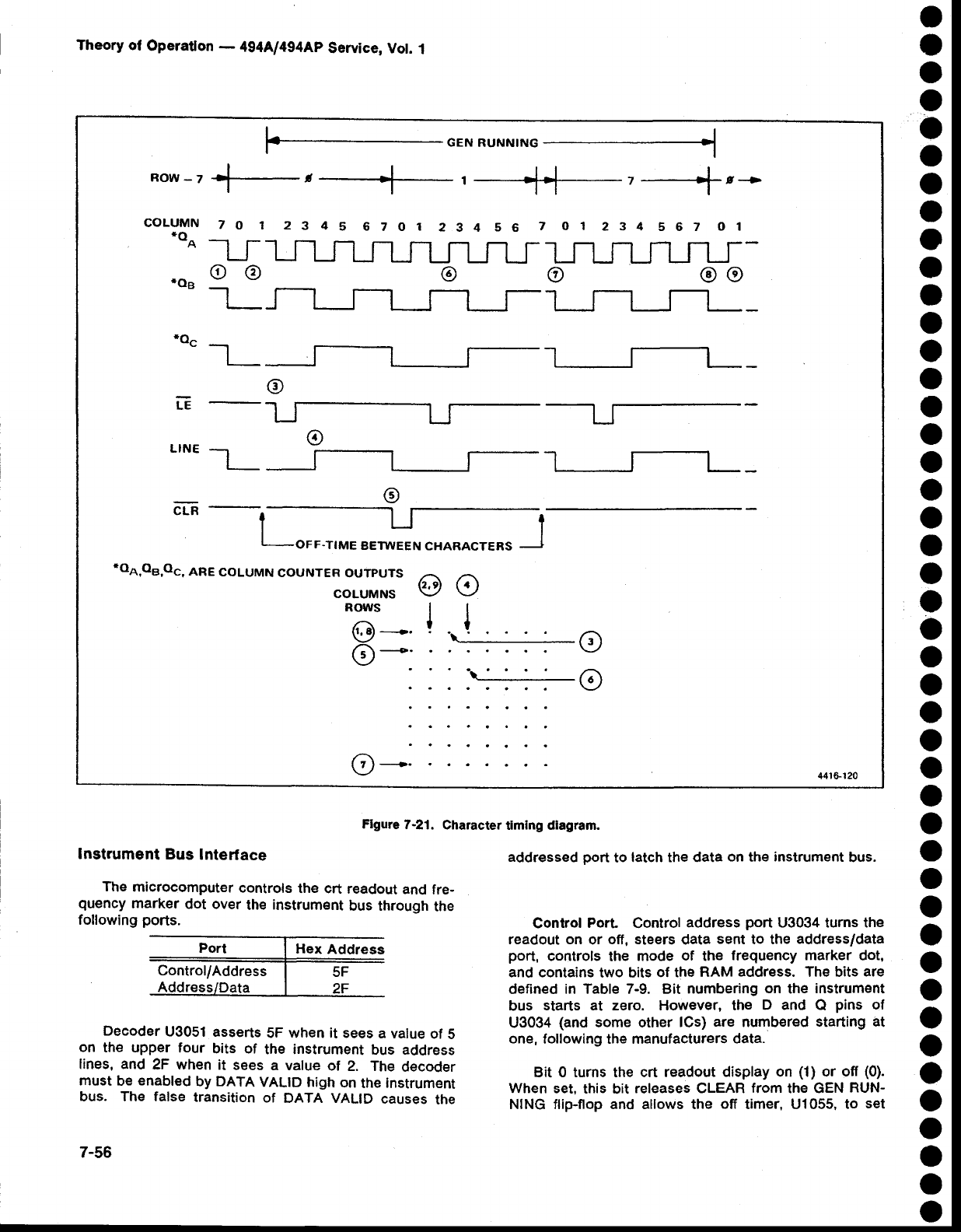

7-Sj

Character

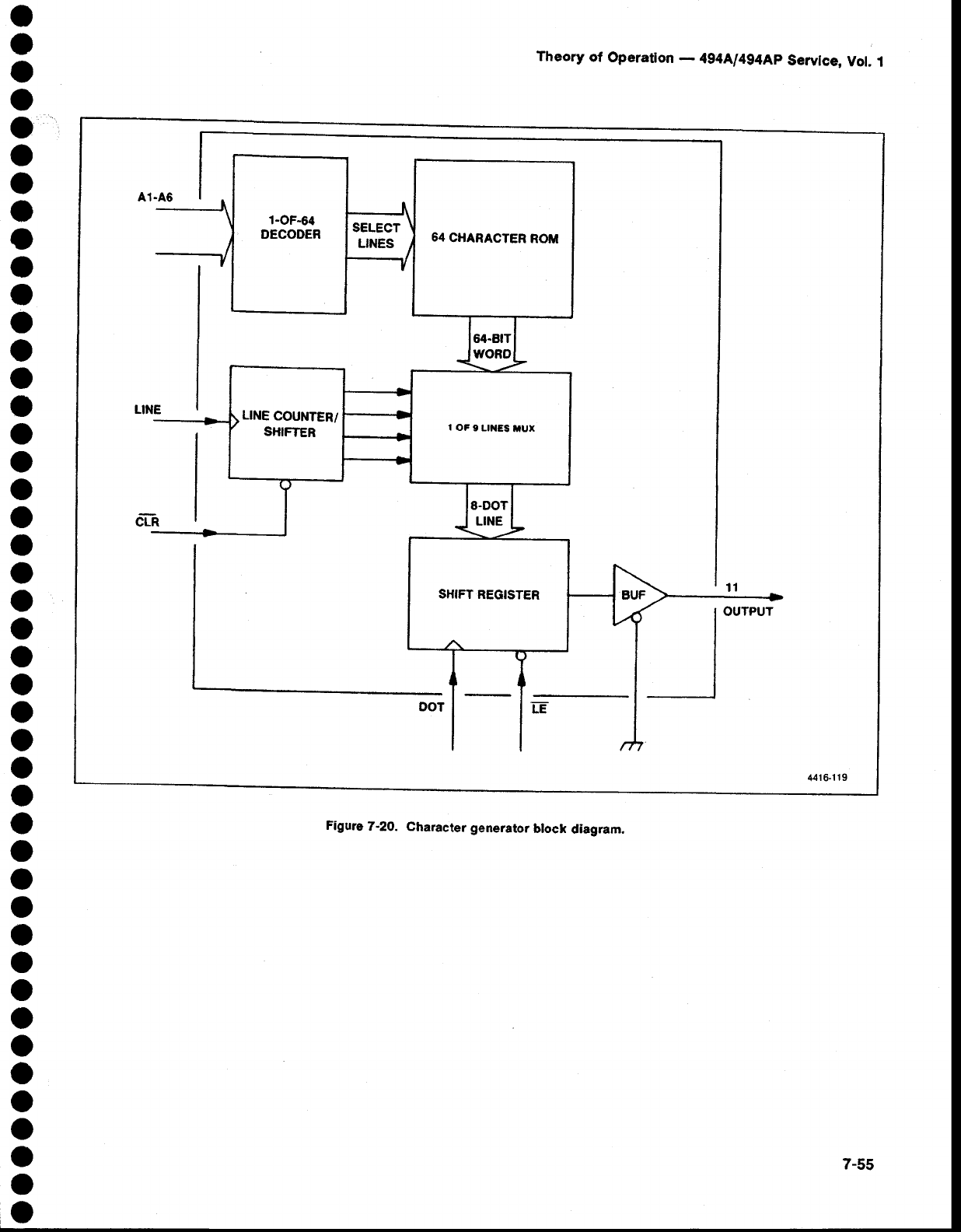

Generator

Timing .............

z-54

Dot

Defay .....-..2-54

lnstrument

Bus

Interface

.........

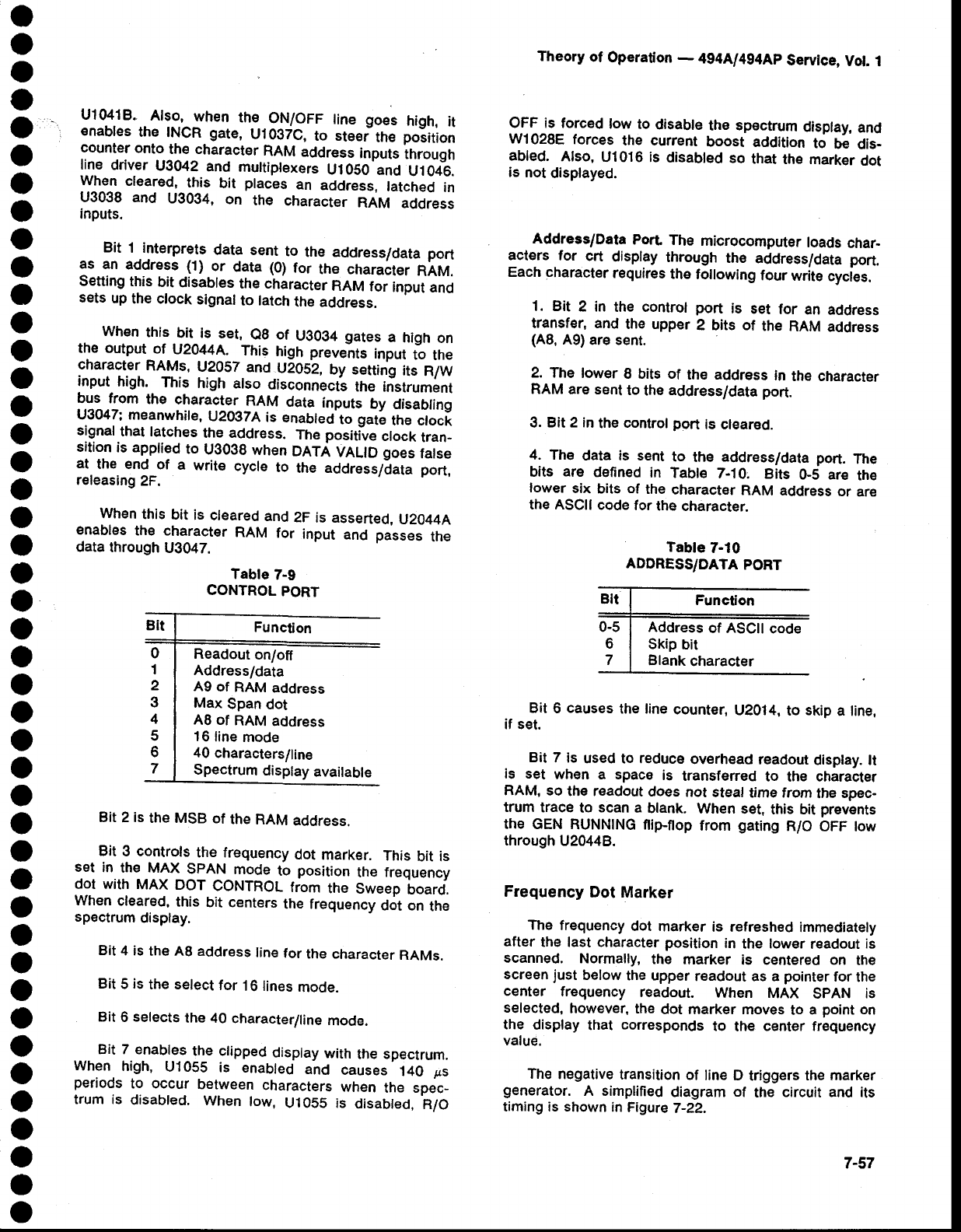

7-56

Control

Port

.........................

7-56

Address/Data

Port

...,...,......

T

-Sz

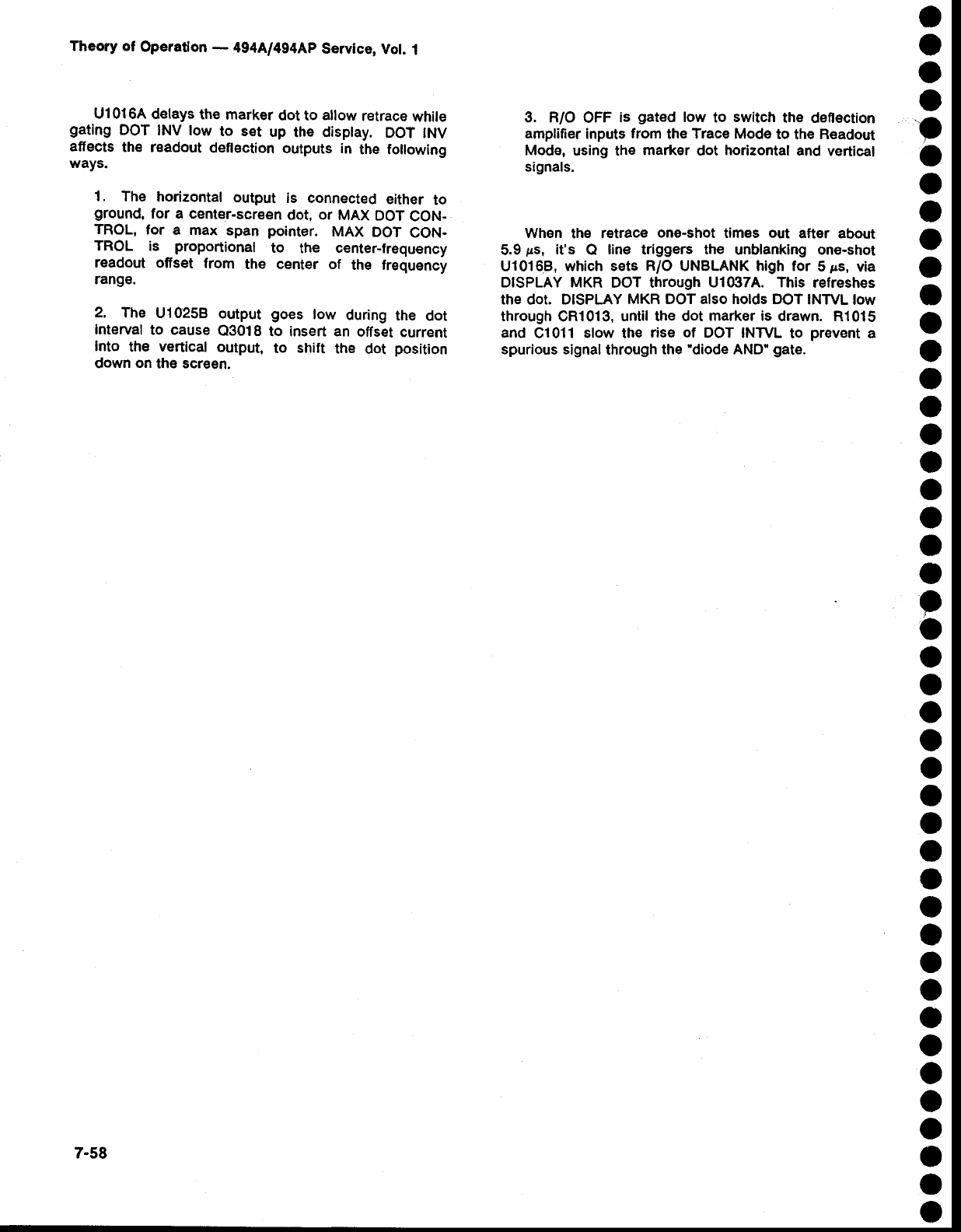

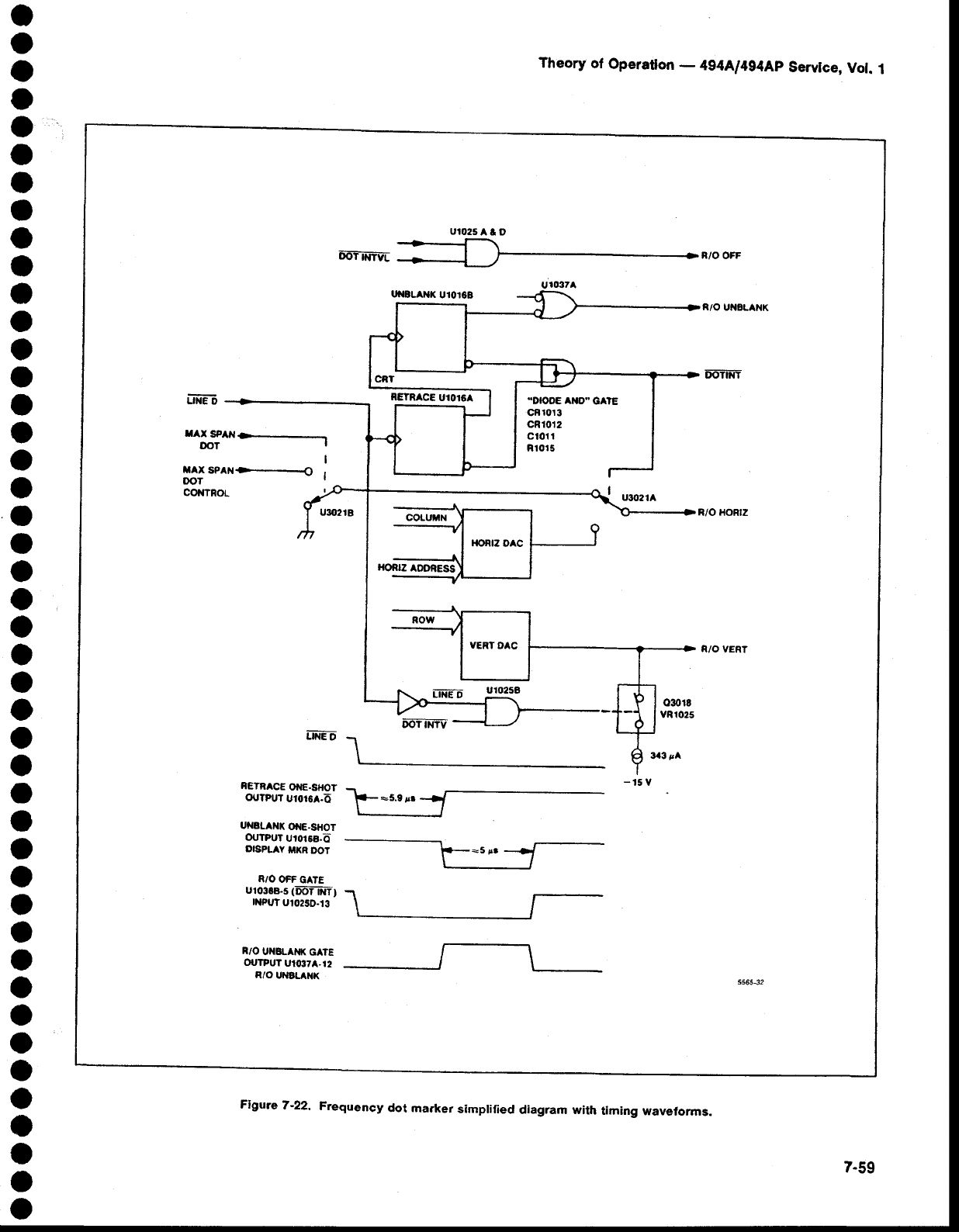

Frequency

Dot

Marker

.,...........

7_57

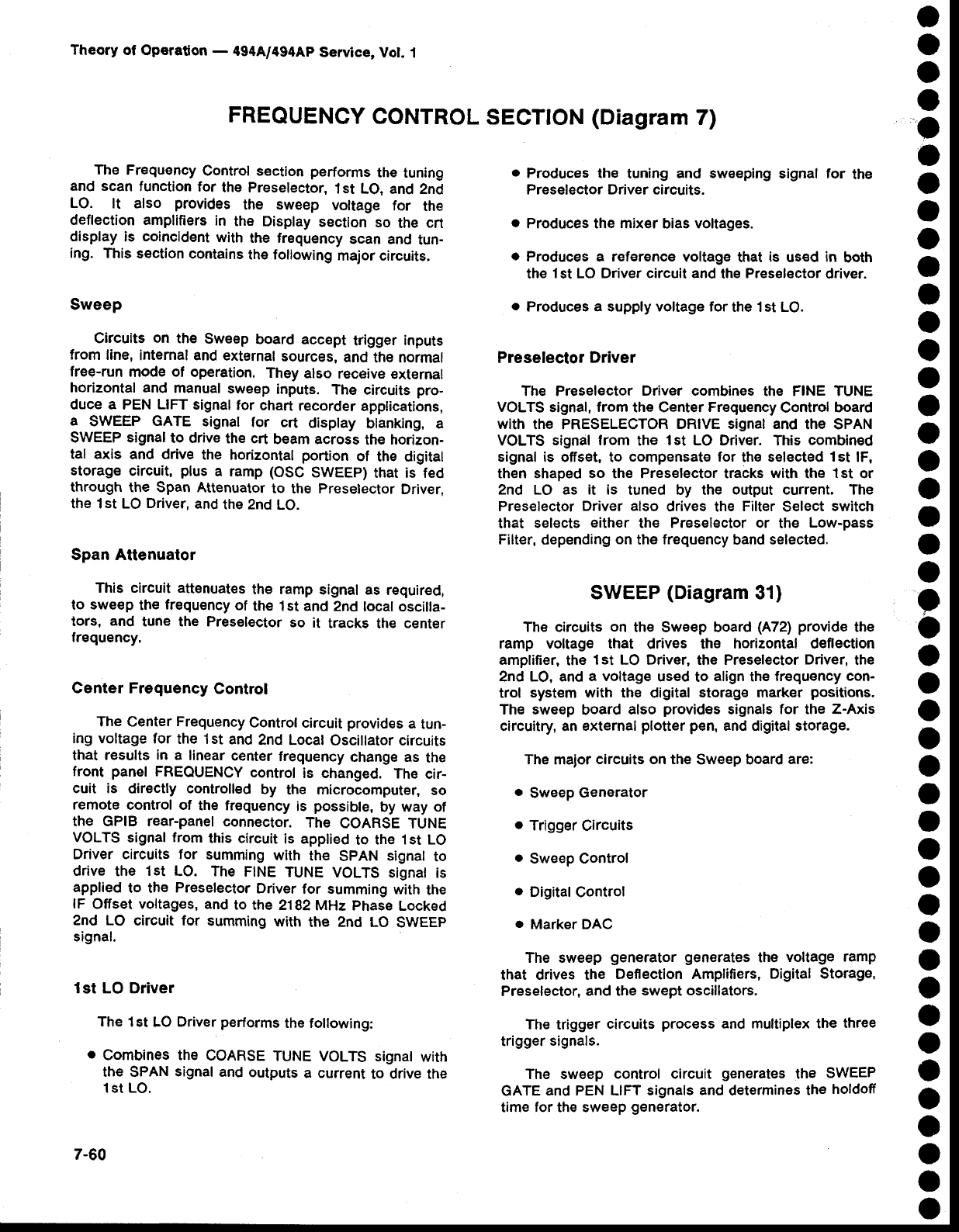

FREQUENCY

CONTROL

sEcTtoN .. 7_60

Sweep ..................

7-60

Span

Attenuator

.......................

Z-60

Center

Frequency

Control ........

7-60

1st

LO

Driver

...........................

7-60

preselector

Driver

....................

Z_60

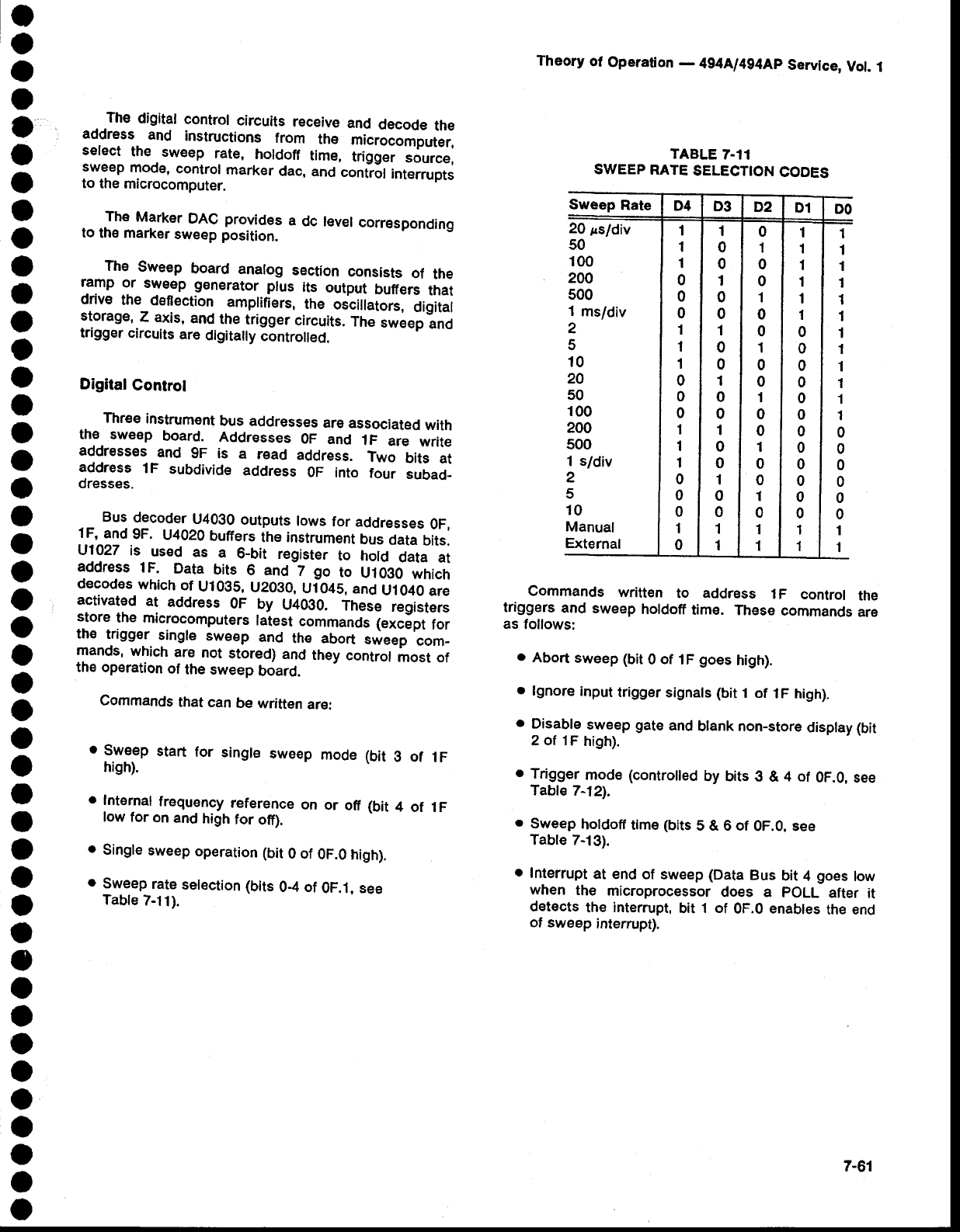

swEEP .....................

7-60

Digital

Controt ......7_61

Sweep

Generator

.....................

7_62

Trigger

Circuits ....7-62

Sweep

Output

Circuits .............

7_62

Marker

DAC

.............................

7-63

Sweep

Control .....

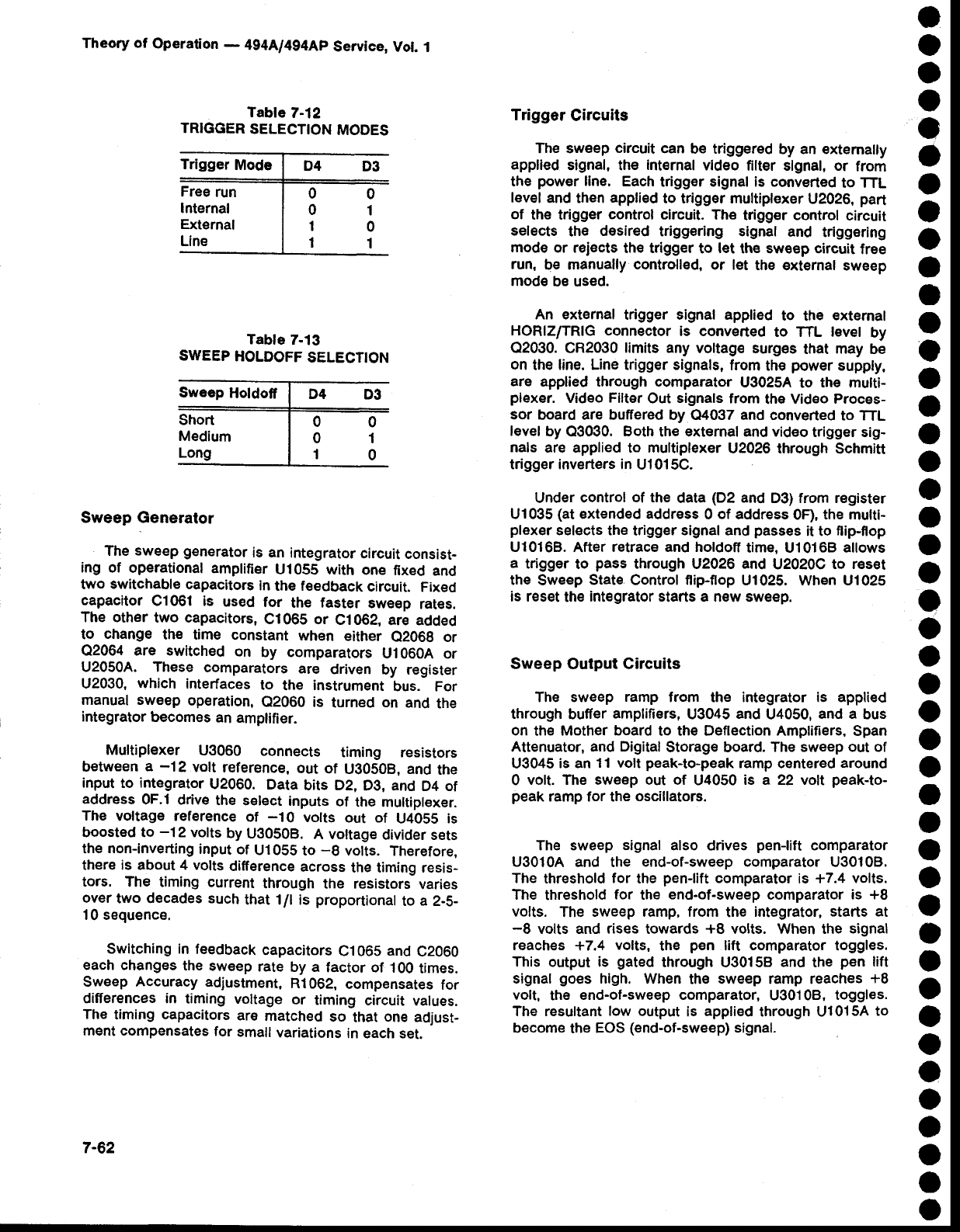

Z_69

Trigger

Control

..................;.....

Z-69

Sweep

Holdoff .....7-64

Interface

Circuits .....................

7_64

spAN ATTENUATOR

...................

7-65

DigitalControl ......

7-65

lnput

Section ........

7_65

Digital-to-Analog

Converter

.....

7_65

Decade

Attenuator

...................

7_66

Page

lst LO DRIVER .........7-67

Digital

Controf ...... 7-6g

Input

Switching

........................

7-69

Oscillator Filter

Switch Driver .......7-69

Summing Amptifier

...................

7-69

Oscillator Driver ... 7-69

Reference

Suppty ....................

Z-69

Mixer Bias

Driver

.....................

7-69

Programmable

Bias

.................

7-69

PRESELECTOR

DRTVER

..............

7-69

Digitaf

Control

Circuits .............

7-70

Oscillator

Voltage

Processor

...

7-lO

lF

Offset ...............7-21

Summing Amplifi

er

...................

7

-71

Tracking

and

Shaper

Circuits ....7-71

Current

Driver ...... Z-72

Preselector

Switch

Driver

.,...... 7-22

CENTER FREQUENCY

CoNTROL -................7-72

Operating

Modes

.....................

7

-72

Digital Control ......7-73

Storage

Registers ..,..,.........

7-74

Digital-to-Analog

Converters .......7-75

Track-and-Hold

Amplifier ......... 7

-7

5

Write-Back

Circuit

........,...........

7-76

-1

0

V Reference

Buffer ......... ..7-76

COUNTER

and

PHASE

LOCK

sEcTroN ...7-77

FUNCTIONAL

DESCRIPTION ....... 7-77

Phase

Lock

Assembly ............. 7-77

Frequency

Gontrol

................... 7

-78

Controlling

the

Oscillator Frequency

......,.,.,

7

-78

Counting

the

lF .................... 7-78

HARMONIC

MIXER ..7.78

AUXILIARY

SYNTHESIZER

.......... 7-79

COUNTER

BOARD .,,7.82

Address Decoder

.....................

7-82

Service

Request

Circuits

......... 7-82

Data Buffers .........7-82

Input Amplifiers

and

Multiplexer ........... 7-83

+2n

Gounter .........

7.83

21

-bit

Counter ..........................

7-83

PHASE LOCK

SYNTHESIZER

...,..7.83

Synthesizer ..........

7-83

Phase Lock

.............................. 7-84

Offset

Mixer ........................ 7-84

Error

Amplifier

.....................

7-85

Controlled

Oscillator

............ 7-86

Strobe Driver

Circuit

............ 7-86

vll

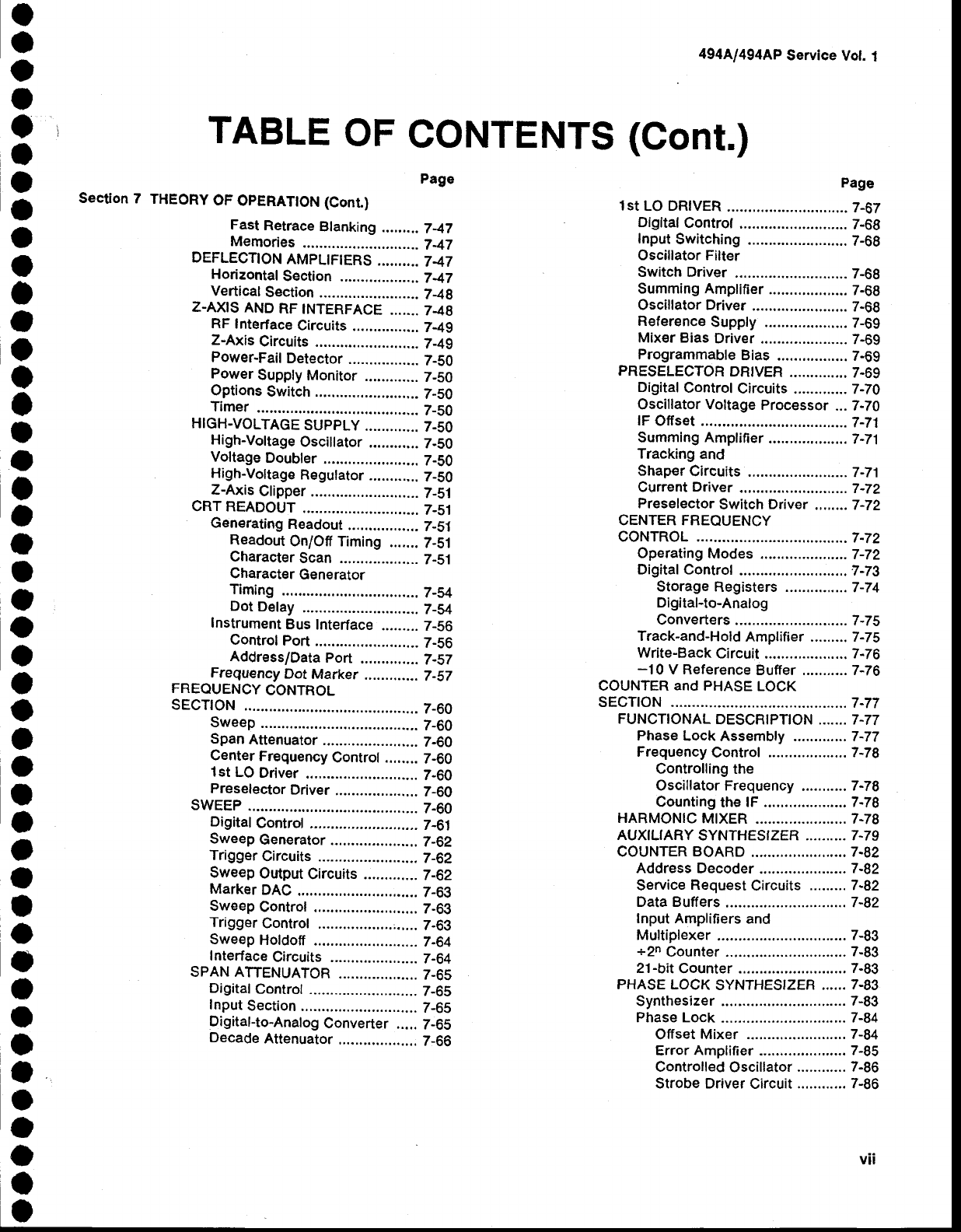

TABLE

OF

CONTENTS

(Cont.)

Page

Section

7 THEORY

OF

OPERATTON

(Conr)

DtctTAL

CONTROL

SECTTON

.......... 7_88

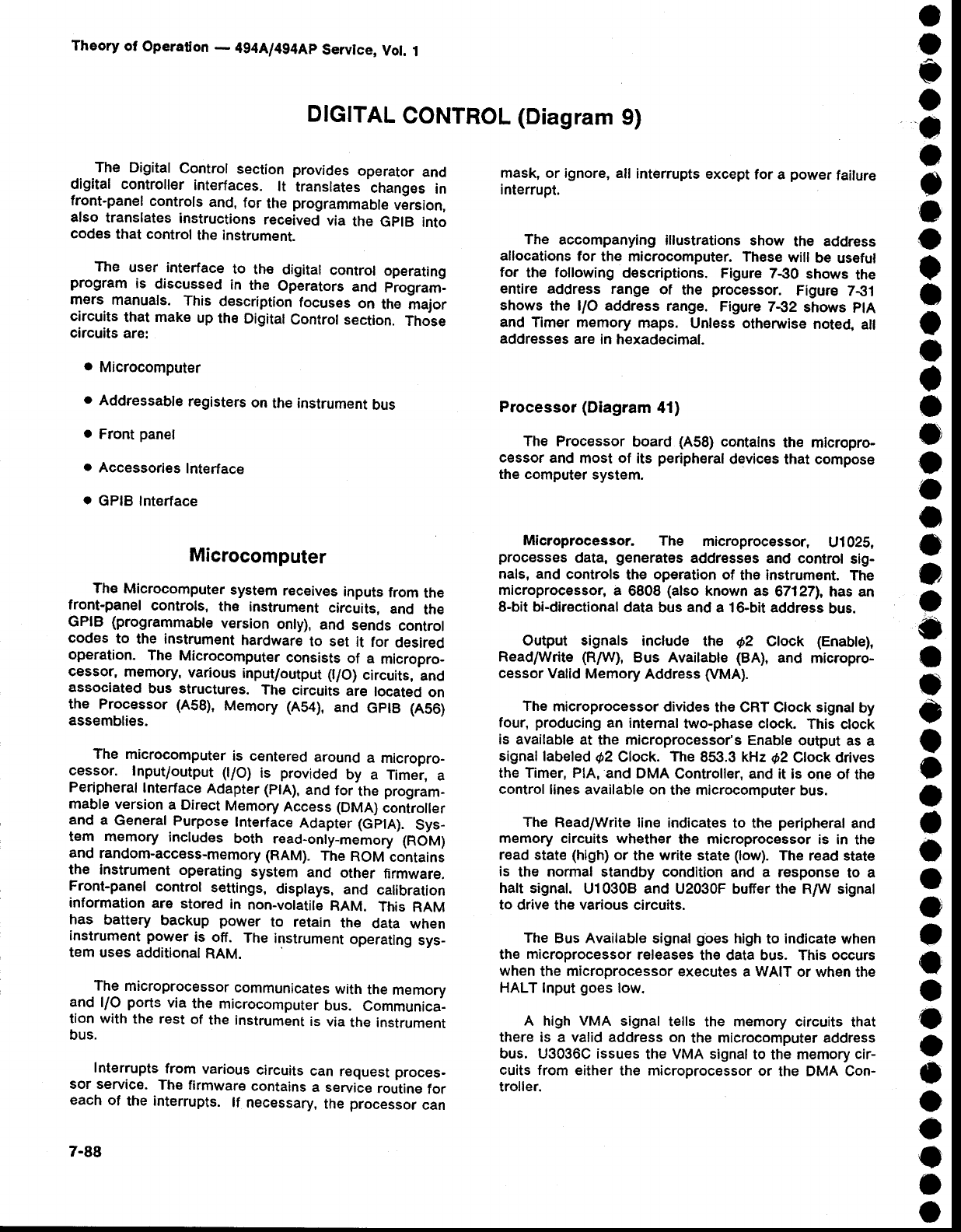

Microcomputer

.............................

7-gg

Processor .............

7-gg

Microprocessor

...................

7-88

Cfock ......... ......7-92

Microcomputer

Bus

........,....

T-92

Address

Decoder

................

Z-92

Timer ......... ......7-gz

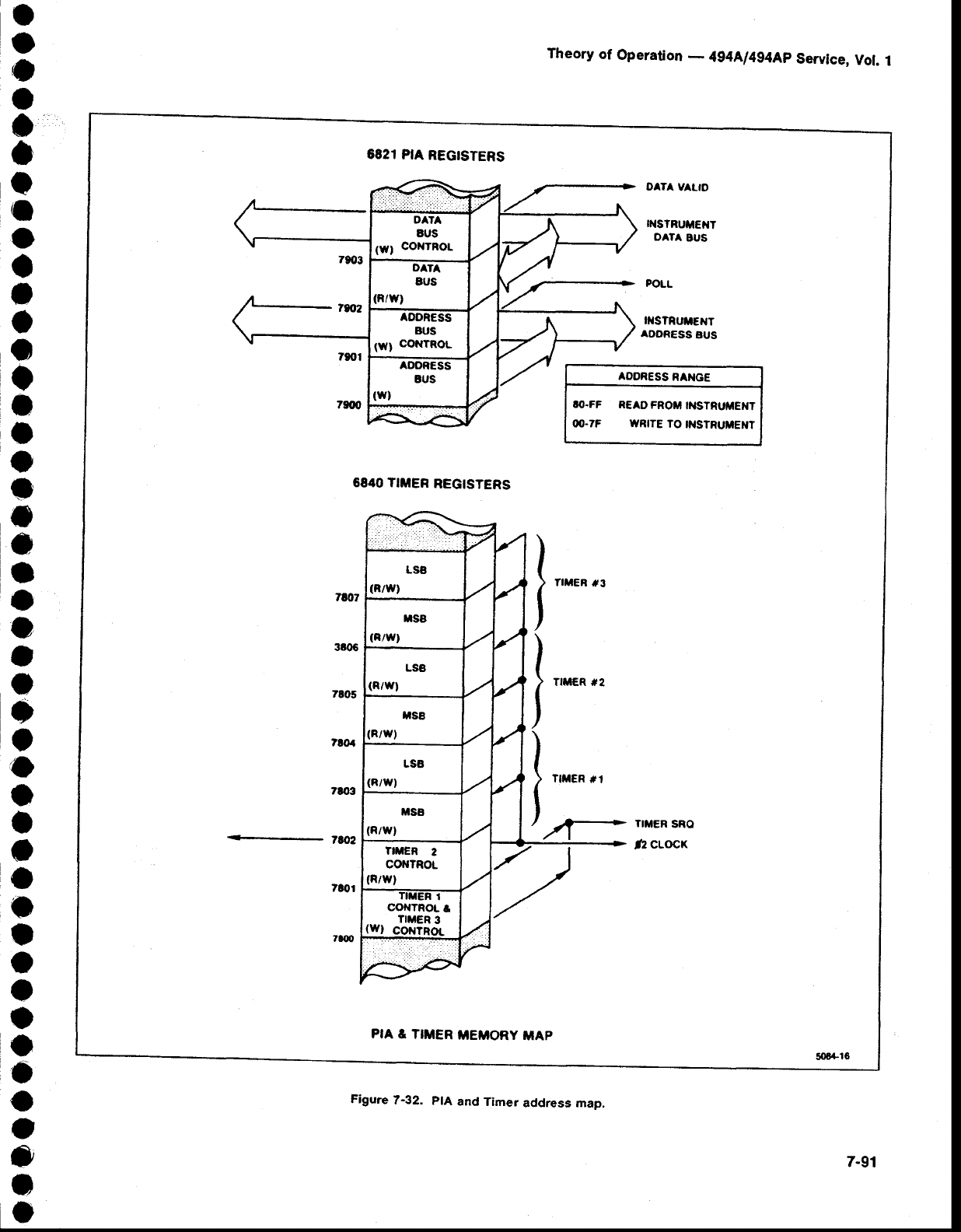

PIA and

lnstrument

Bus ...... 7-92

DMA

Controller

.............

......

7

-gz

Interrupt

Processing

...........:

7-93

Memory .................2-94

Address

Decoders

..............

7-94

RAM

.......... ......7-94

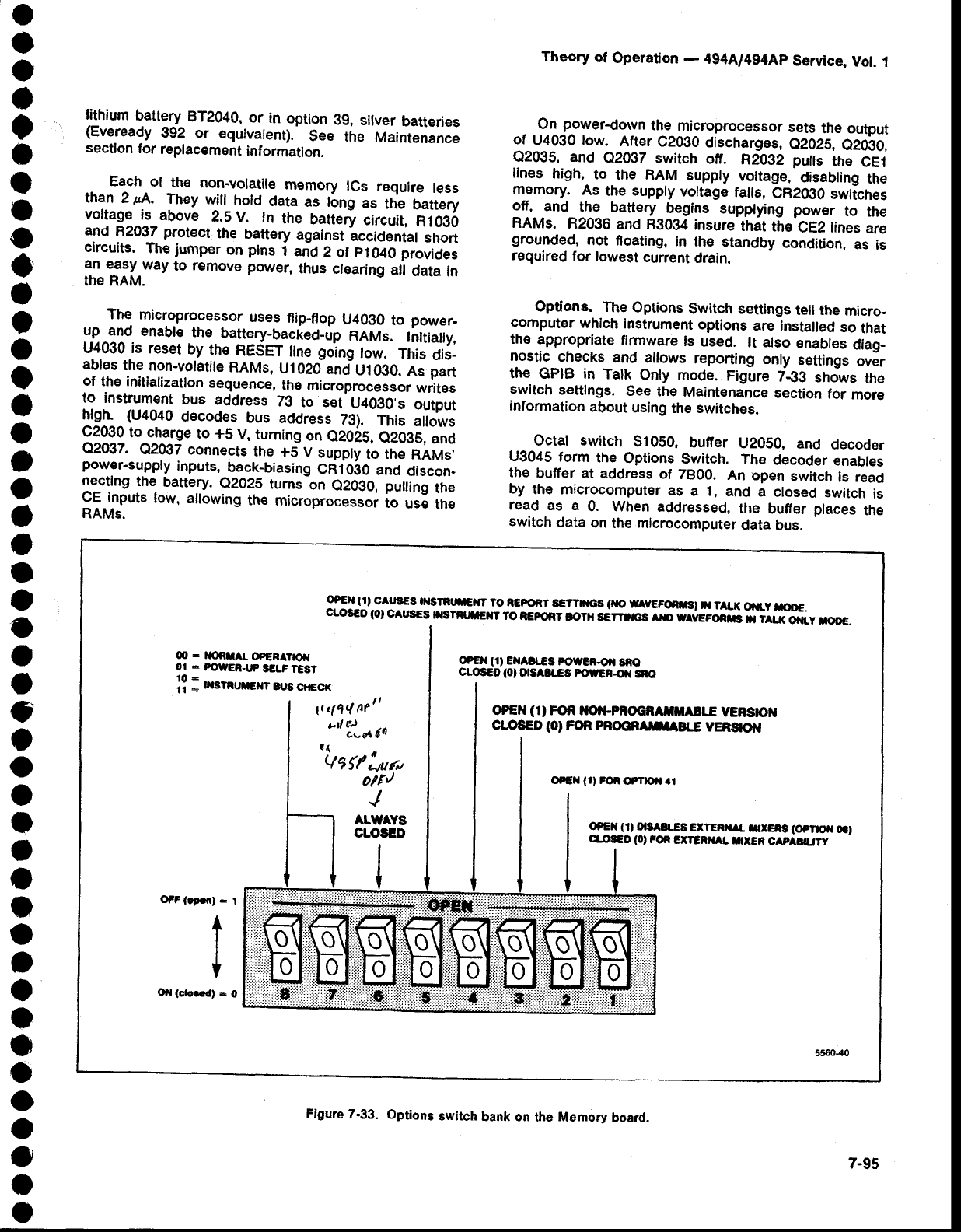

Options .............

7-95

ROM .......... ......7-96

ROM

Banks

and

GptB

.............

7-96

Address

Decoder

................

7-96

Bank

Selector

......................

7-96

Bank

ROMs .....

7-96

GPIB

Switches

...............,....

7-97

GPfA

.......... ......7-97

Accessoriss

Interface

.......,.,....

Z-gT

Front

panel ..........

7_97

Pot€ntiometers

....................

7-98

output Mode

shift

R€gisters

and

LEDs

............ 7-98

Processor ...,.... 7-98

Scanning the Keyboard

....... 7-98

Scanning

the FREQUENCY

ControlCoder .. 7-gg

Outputting

the

Correct

Code .......................

7-99

Software .......... 7-gg

Main

Scan

Routine

..............

7-99

Keyboard

Check

Subroutine .......7-100

Frequency

Coder

Subroutine

Check

................

7-1 00

Output

Subroutine

...............

7-100

Page

POWER

SUPPLY ..........7-103

Primary

Circuits ........

7-103

Line

Input

Circuits ....................

7-1 03

Invert€r Circuit ..... 7-103

Multivibrator ....

7-103

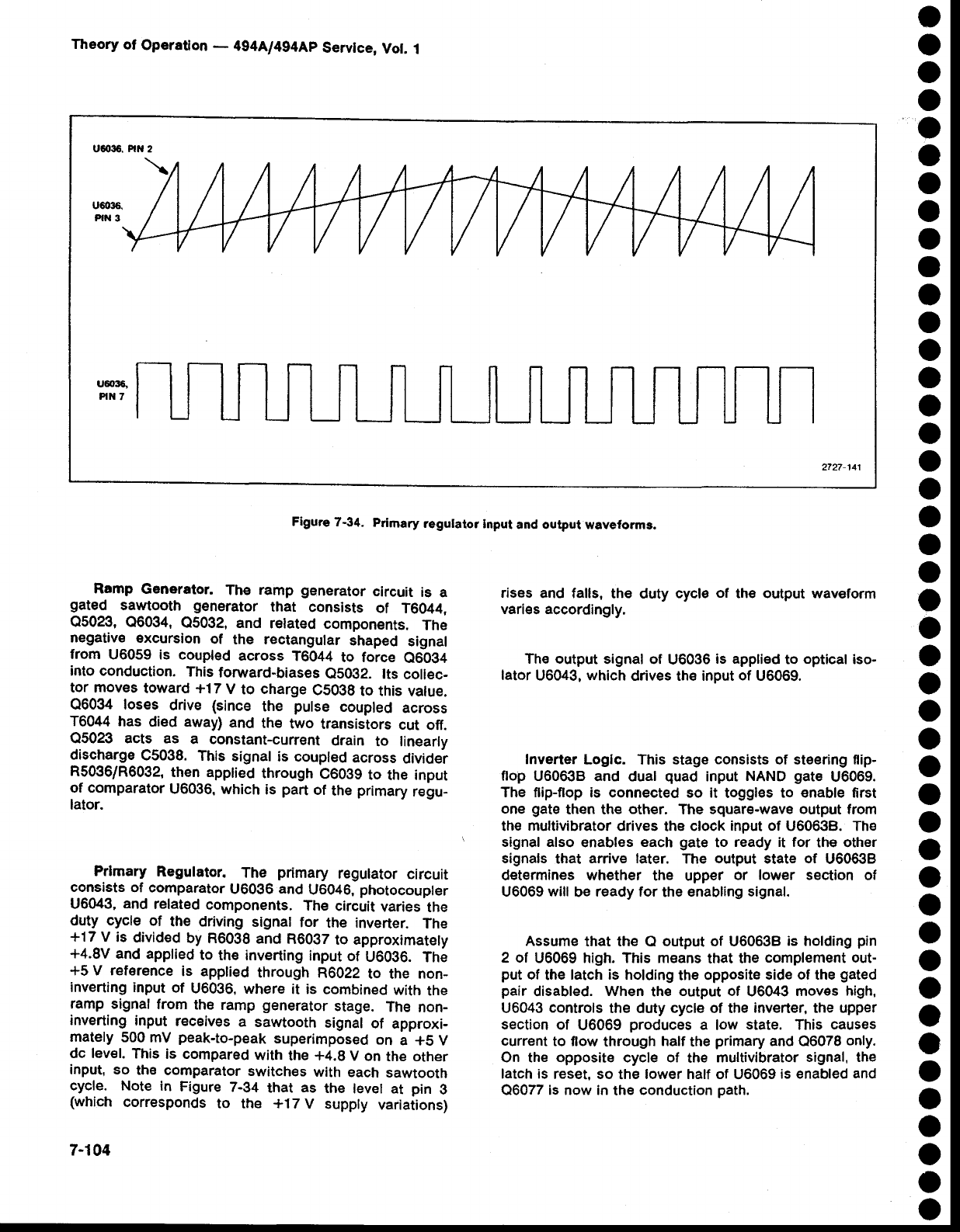

Ramp

Generator ..................

7-l

04

Primary

Regulator

...............

7-1 04

Inverter

Logic ......................

7-1

04

Inverter

Driver

.............,.......

7-1 05

Output Stage .............,.........

7-1 05

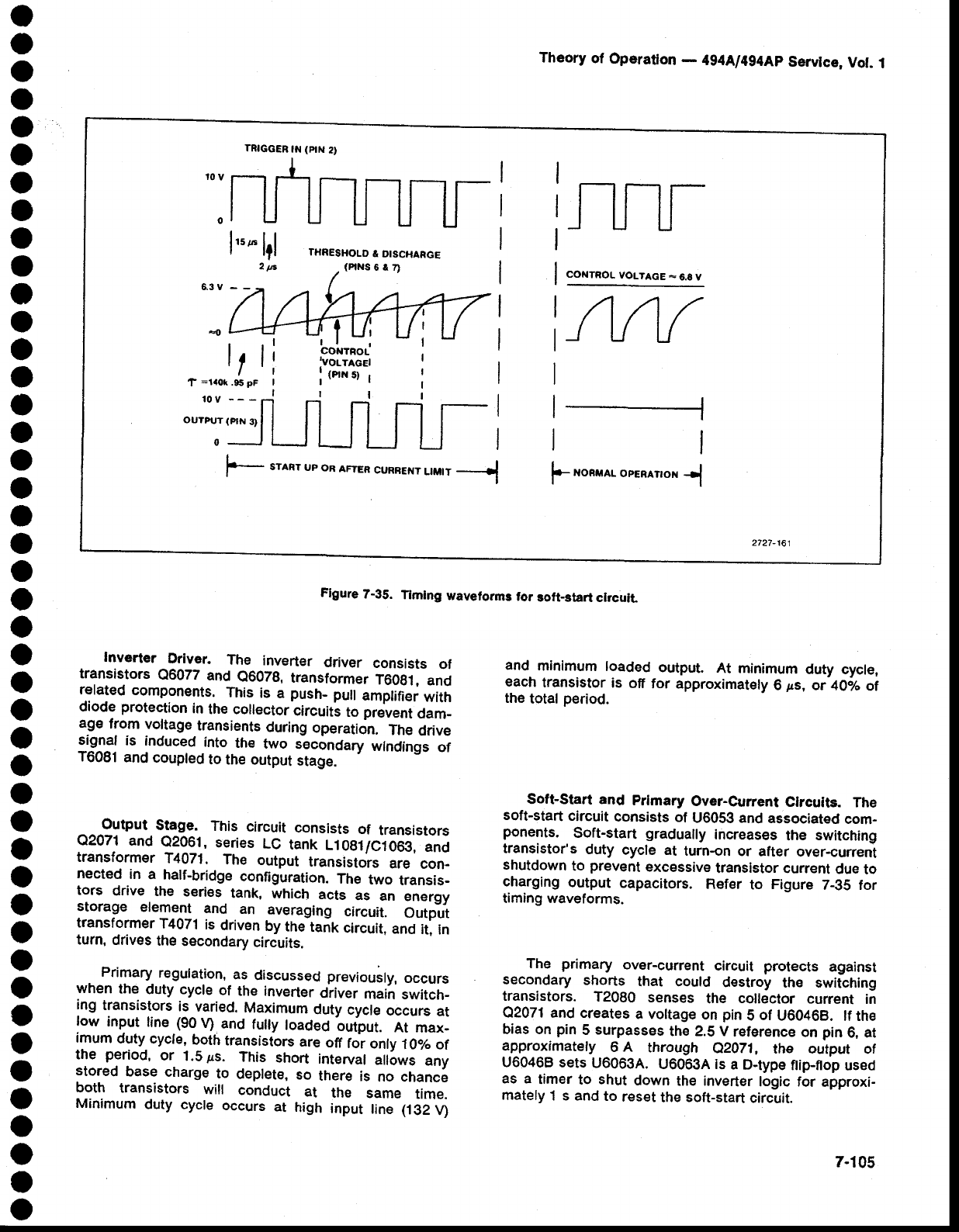

Soft Start

and Primary

Over-Current

Circuits ......"... 7-1 05

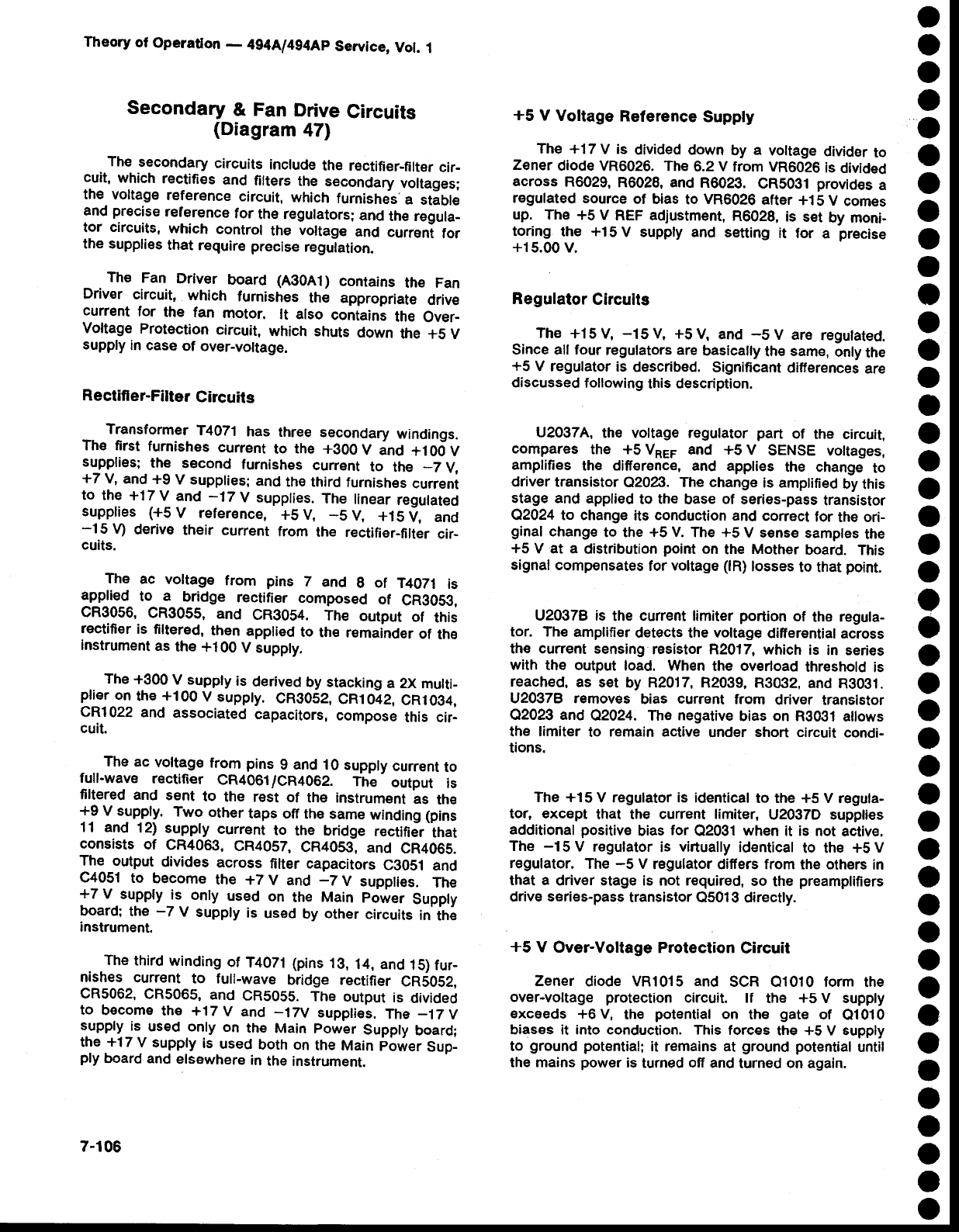

Secondary &

Fan Drive

Circuits ..... 7-106

Rectifi er-Filter Circuits ..................

7-1 06

*5V Voltage

Reference

Supply

Regulator

Circuits ..... 7-106

+5V Over-Voltage

Protection

Circuit ...... 7-106

Fan

Drive

Circuit -......7-107

Sectlon

8 OPTIONS

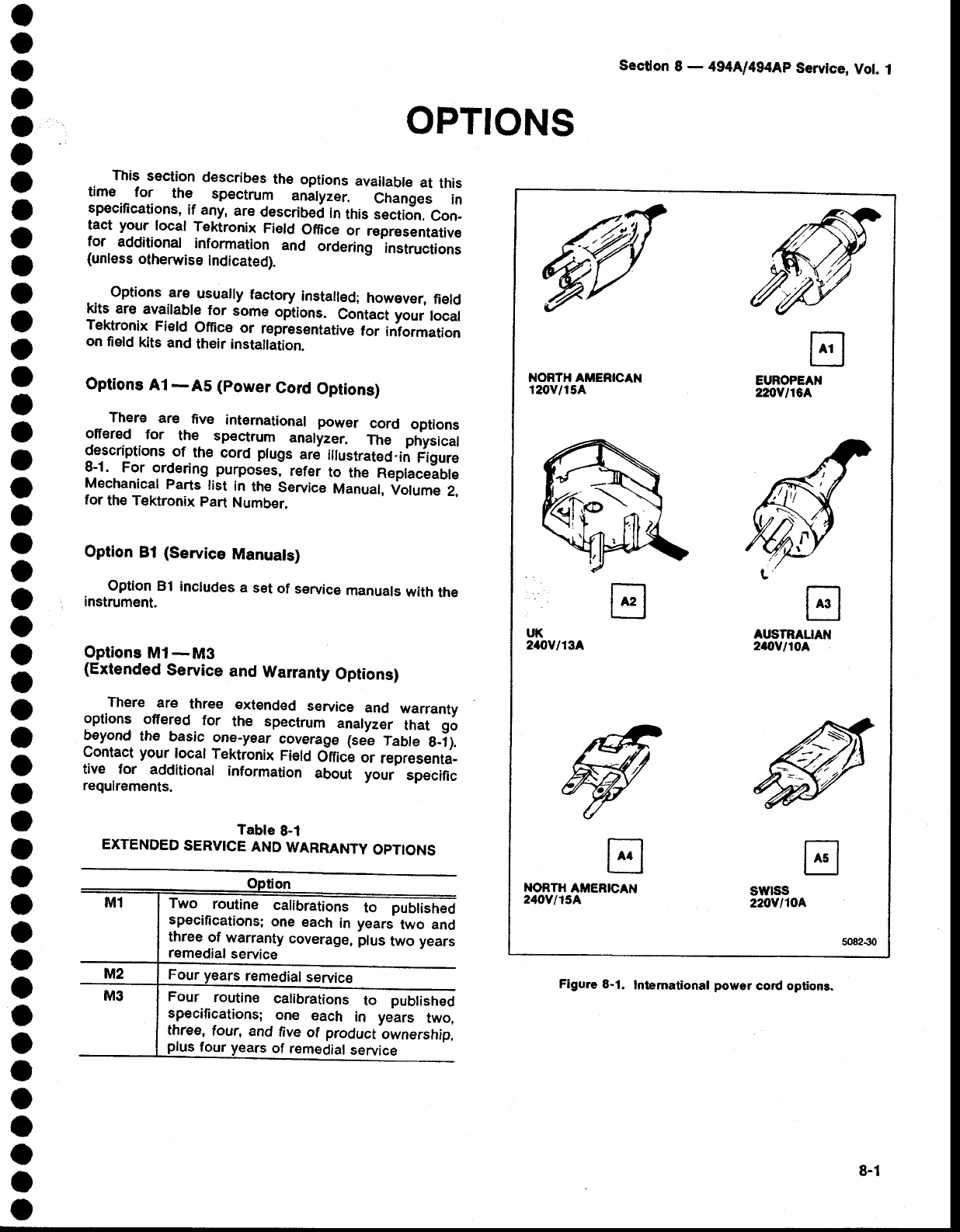

Options

A1-A5 Power

Cord Options ....

8-1

Option Bl Service

Manuals ...................

8-1

Options Ml-MS Extended Service

and Wananty

Options ........

8-1

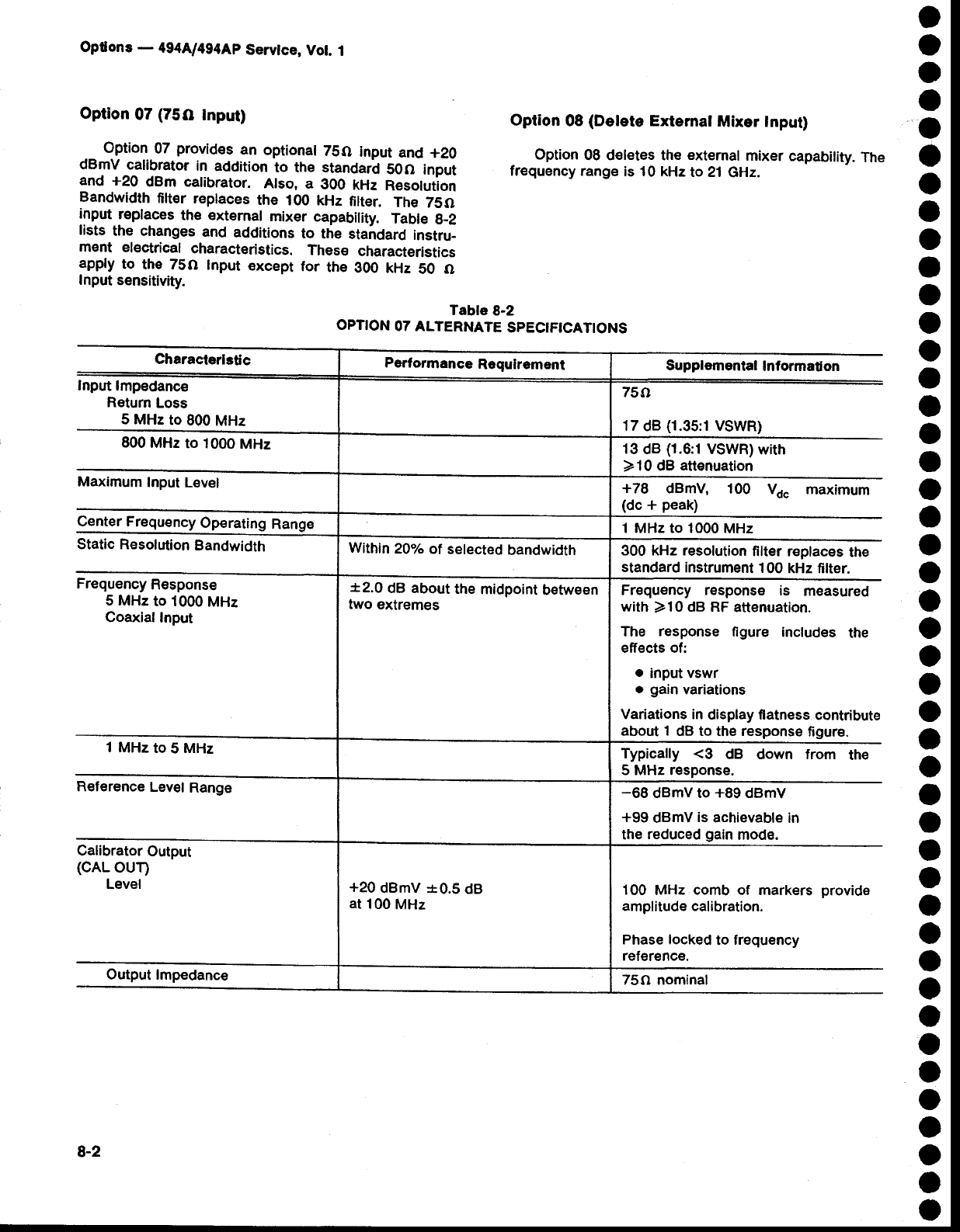

Option

07

75O Input

..............................

8-2

Option 08 Delet€

External

Mixer Input ....8-2

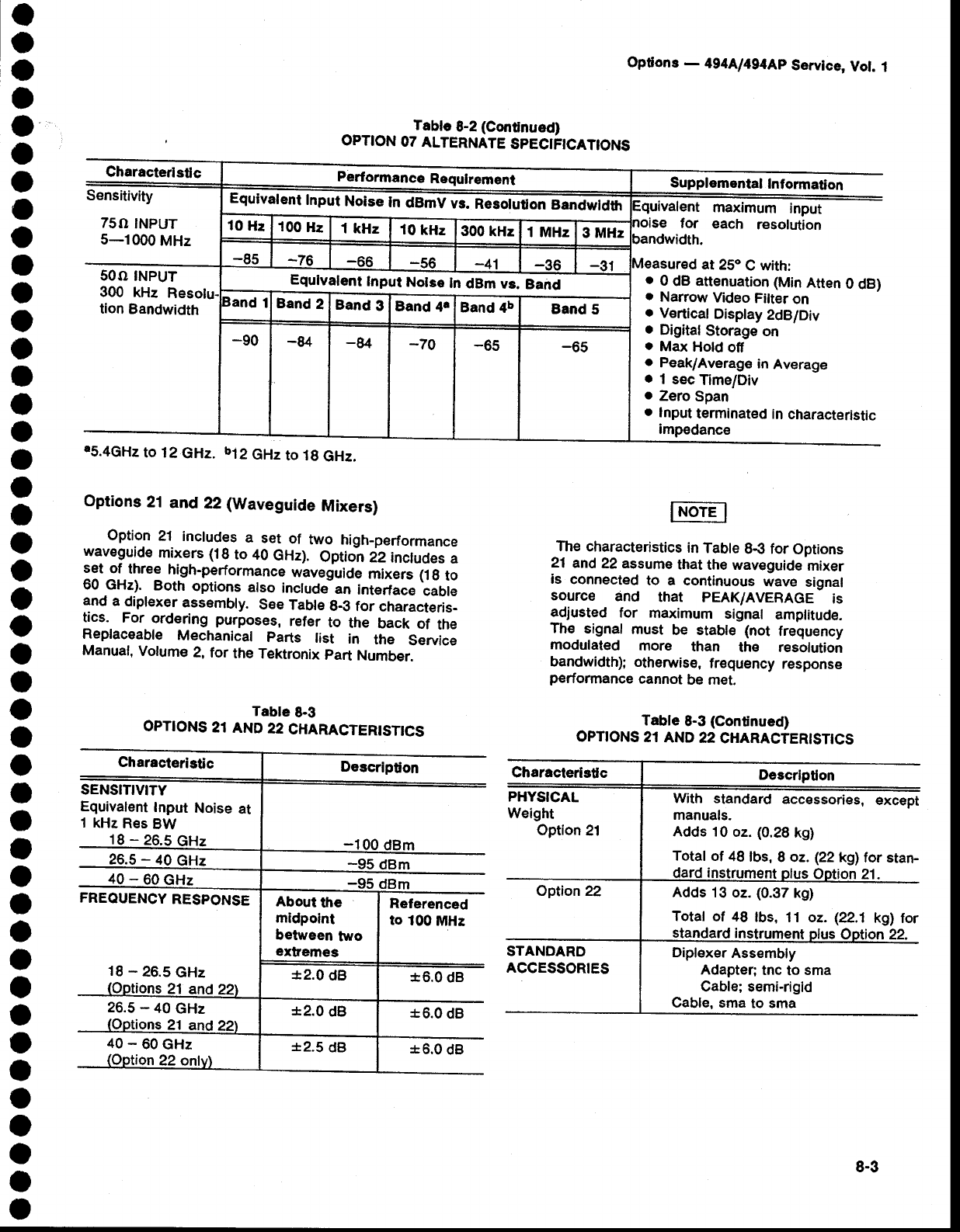

Options 21 and 22

Waveguide Mixers .............

8-g

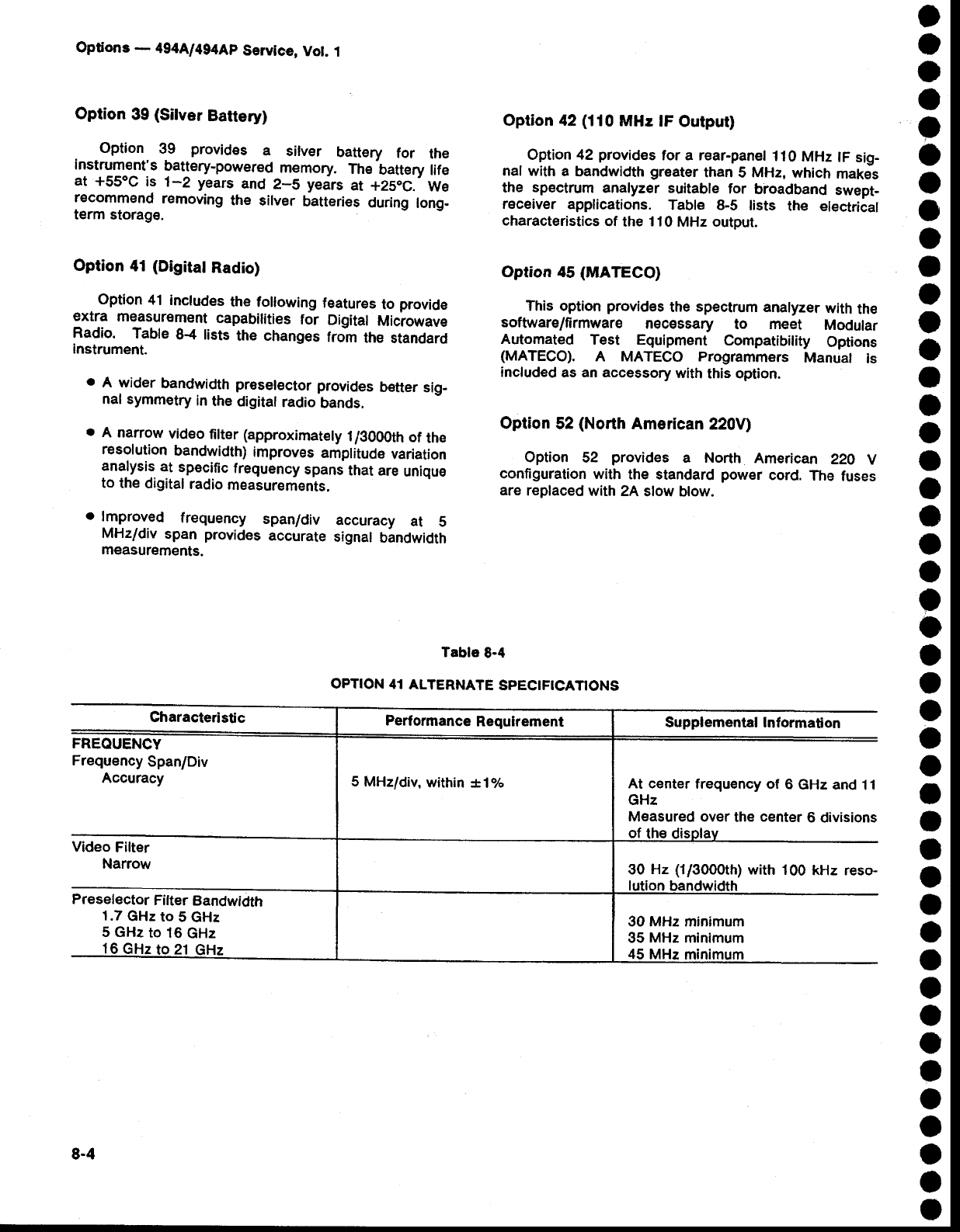

Option 39

Alternate Battery ...................

84

Option

41

Digital Radio .........................

8-4

Option

42110 MHz

lF Output

................

8-4

Option

45 MATECO ...........

8-4

Option

52 North American

220V ............

8-4

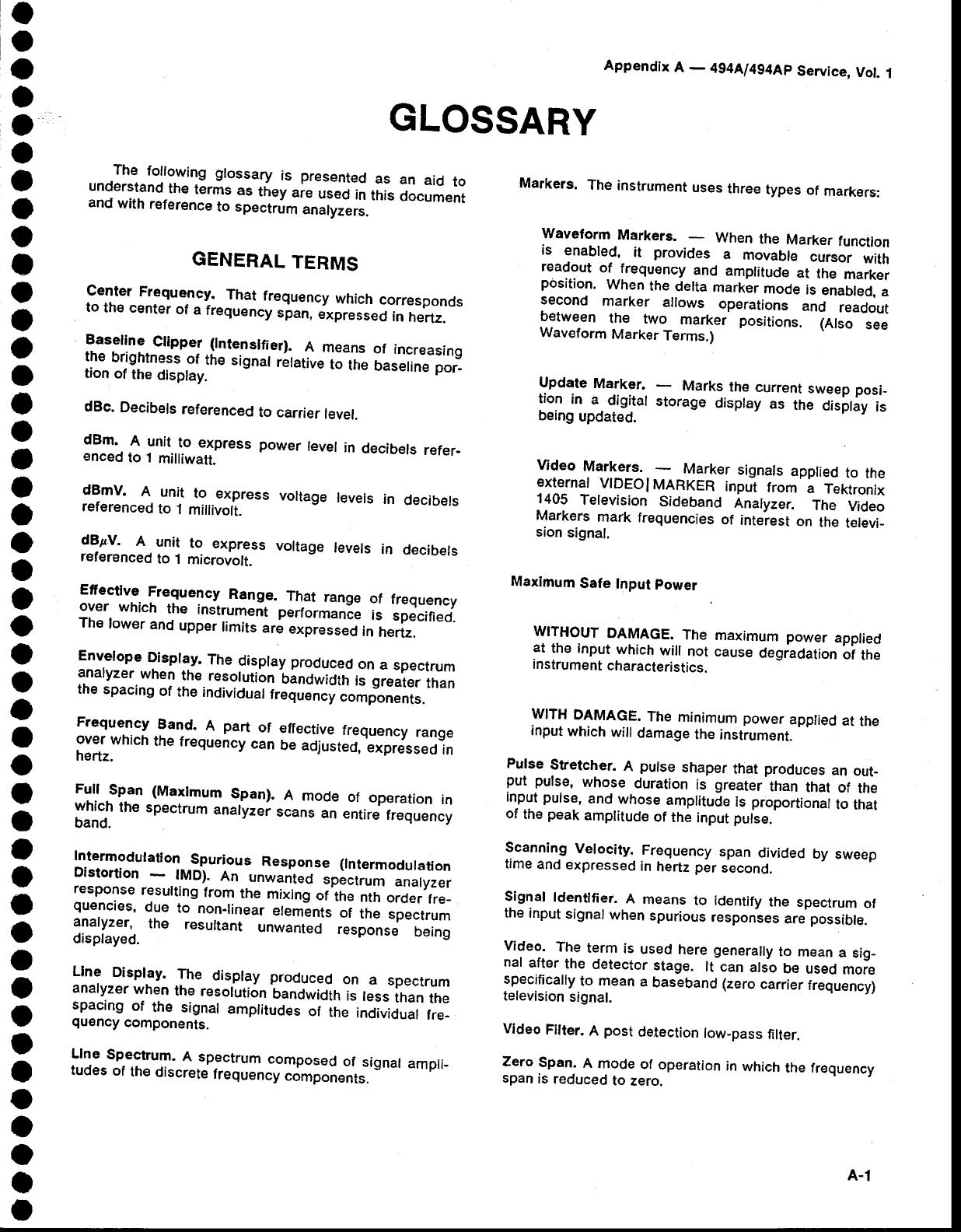

Appendlx A GLOSSARY

GENERAL

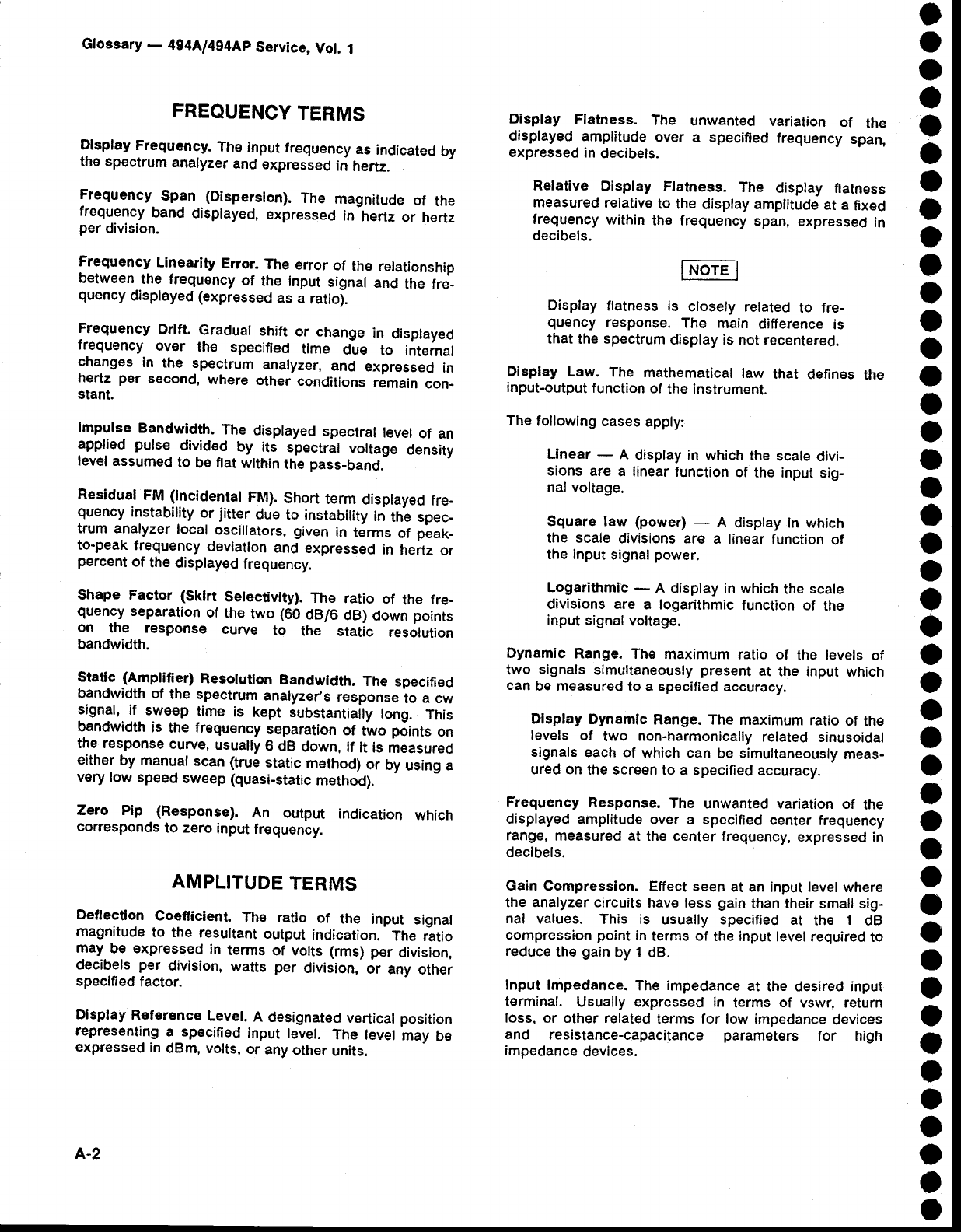

TERMS ........ A.1

FREQUENCY TERMS ... A-2

AMPLITUDE TERMS .....

A-2

DIGITAL

STORAGE

TERMS ..-.......... A-3

WAVEFORM

MARKER

TERMS ........ A-3

o

a

o

I

,a

o

o

a

o

a

I

o

t

o

t

a

o

o

I

a

a

o

o

o

o

a

o

t

a

o

I

o

o

o

I

o

o

I

o

O

o

o

o

4944/494AP

Servlce

Vot. 1

v||l

494A/{94AP

Service Vot.

1

TABLE

OF

CONTENTS

(Cont.)

VOLUME

2

Sec|ion

9 REPLACEABLE

ELECTRICAL

PARTS

Section

10 DTAGRAMS

Section

1.I REPLACEABLE

MECHANICAL

PARTS

494A/494AP

Servlce Vol. 1

Figure page

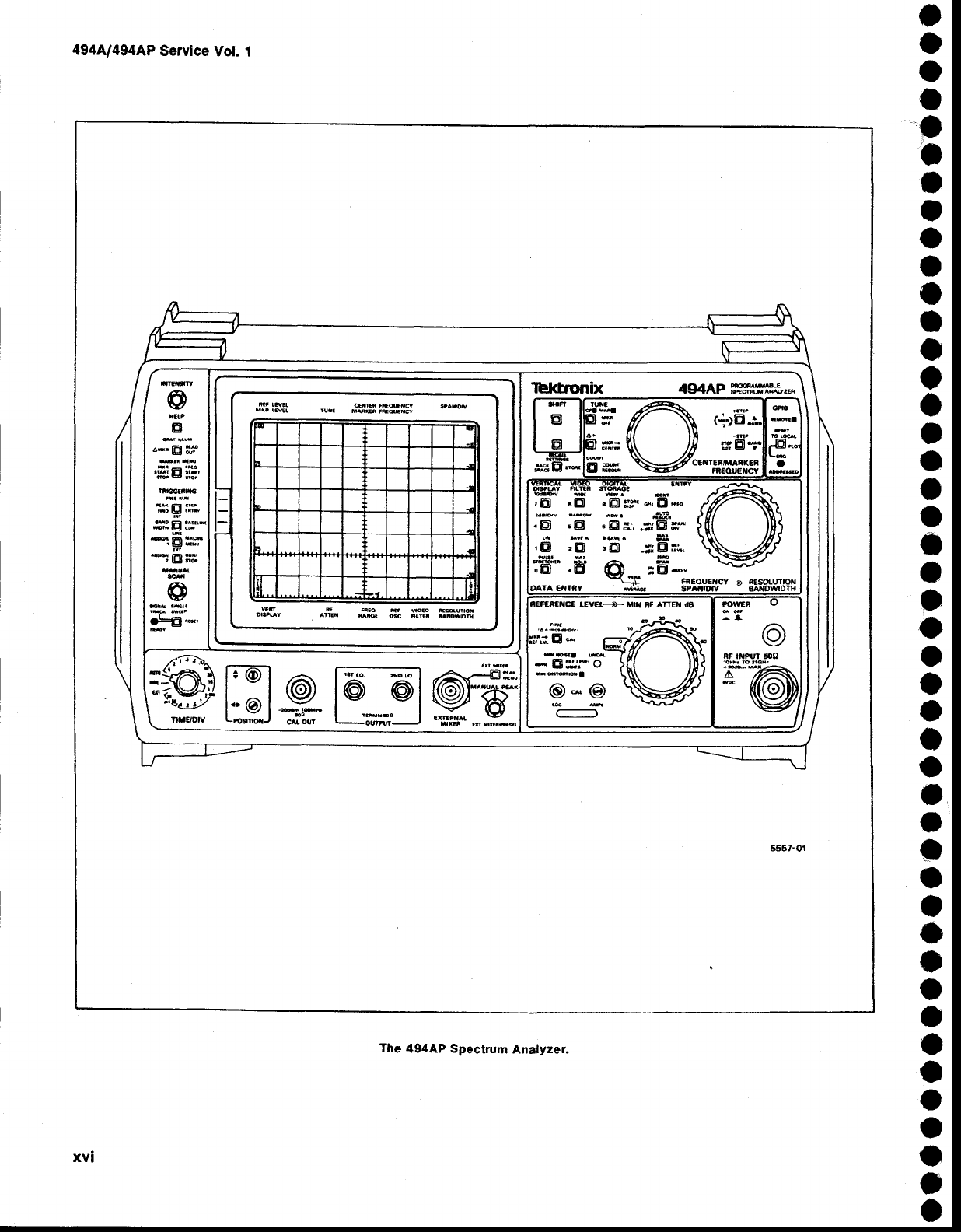

The 494AP

Spectrum

Analyzer.

...................

xvi

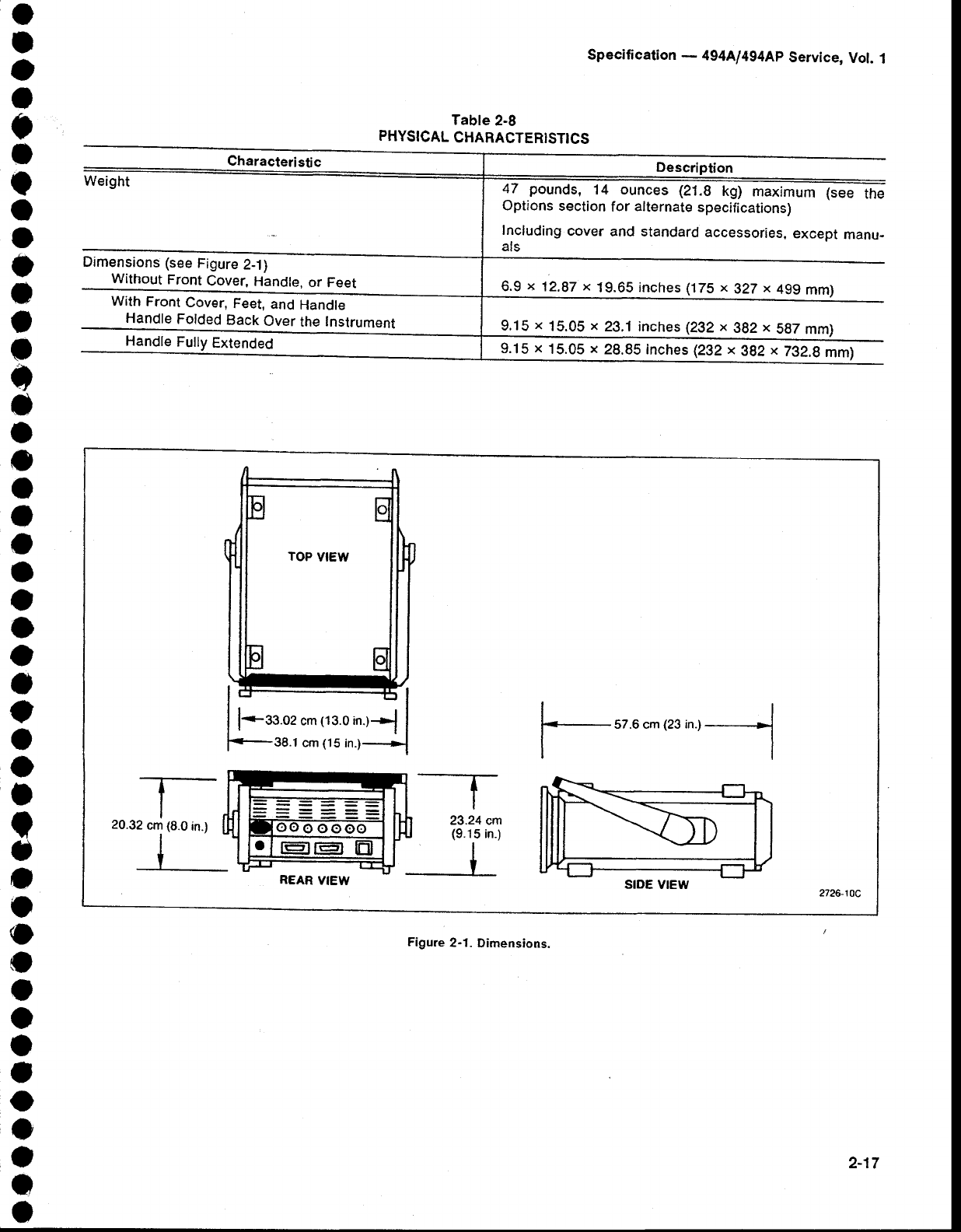

2-1 Dimensions. ....,....,..2-12

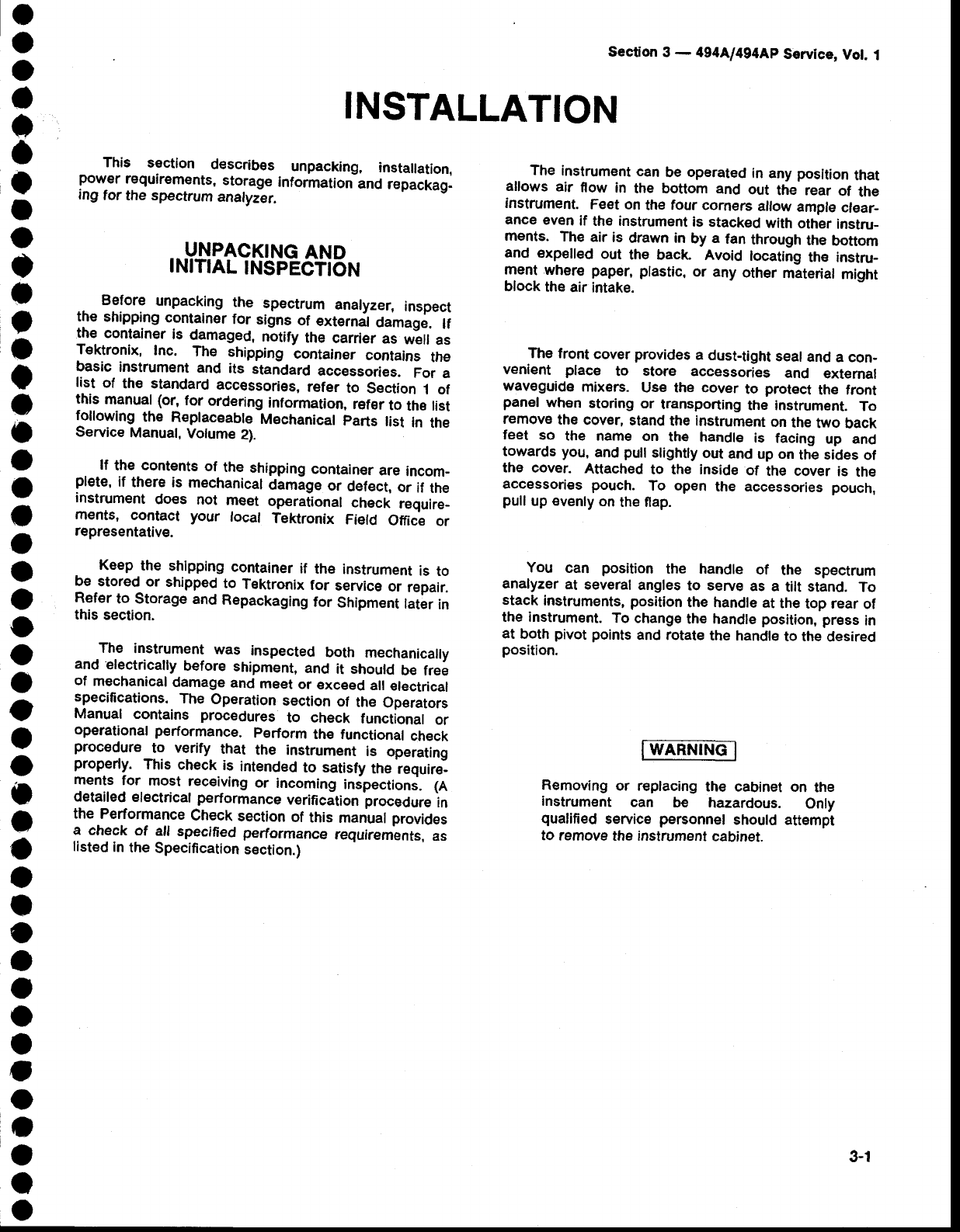

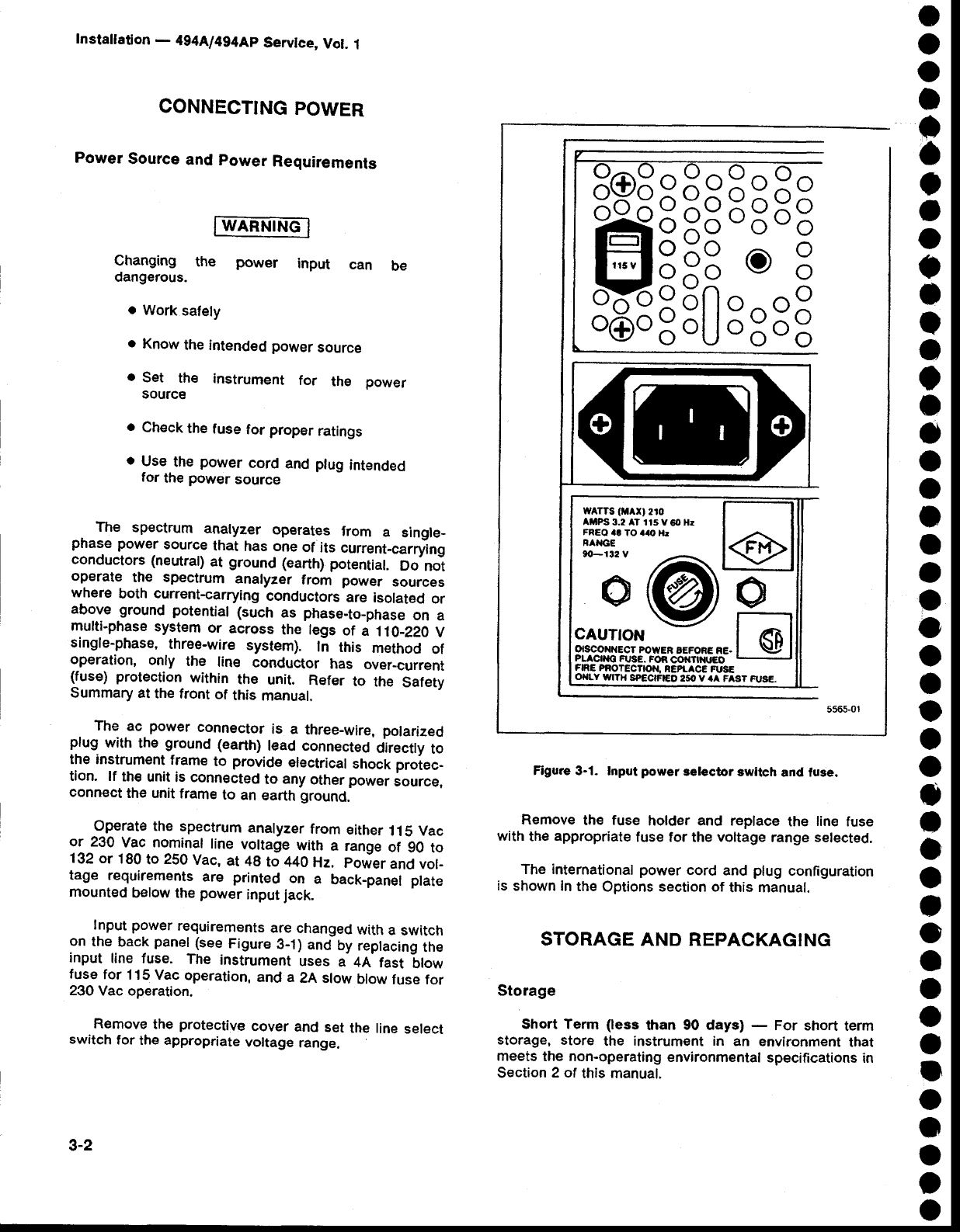

3-1 Location

of input

power

selector

switch

and fine

fuse.

.._....... .....,..,.........9-2

4-1 Crt

display at

initial

power-up.

......................

4-4

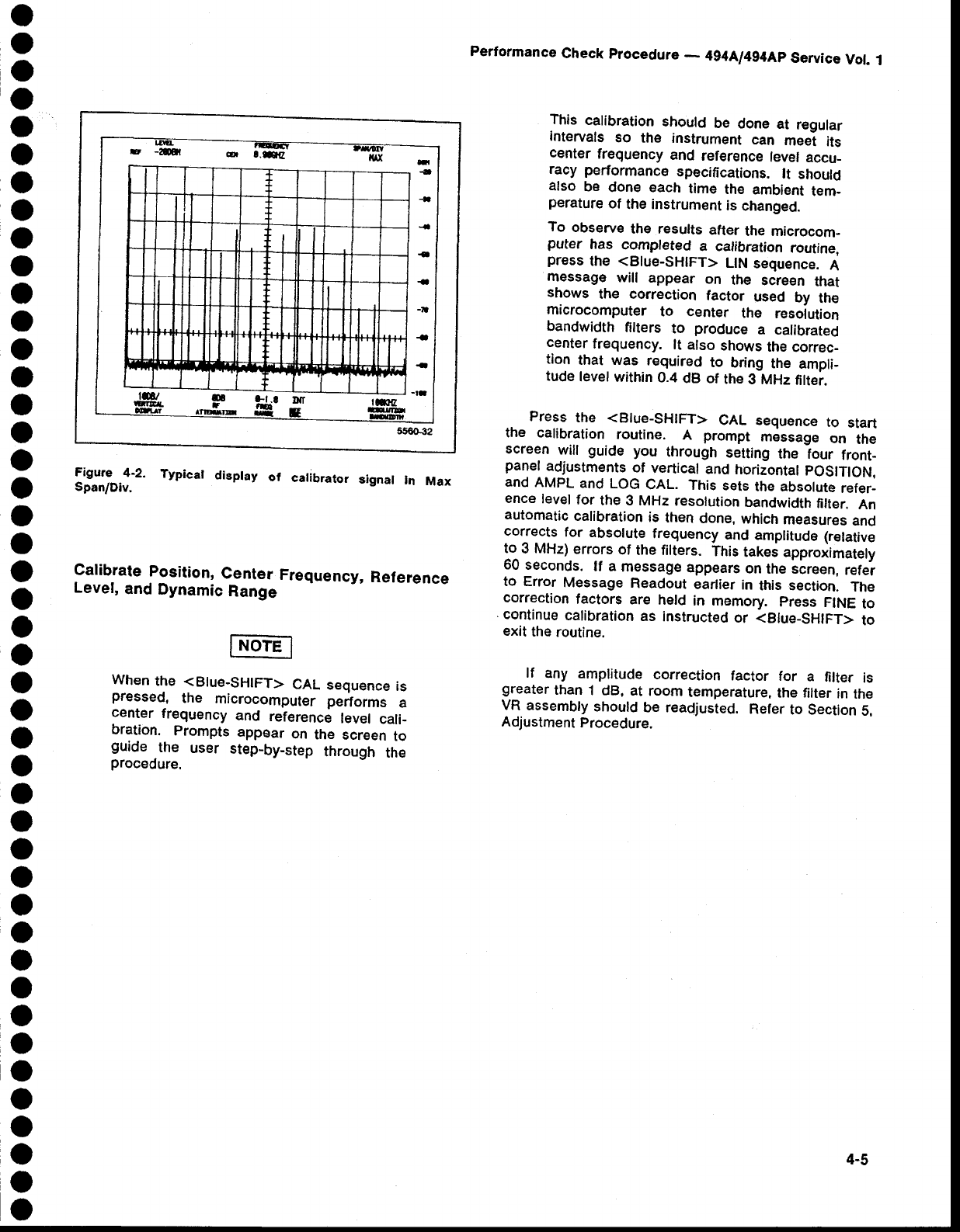

4-2 Typical

display of catibrator

signal

in Max

SpanlDiv.

...............................

4-5

4-3 Test

equipment

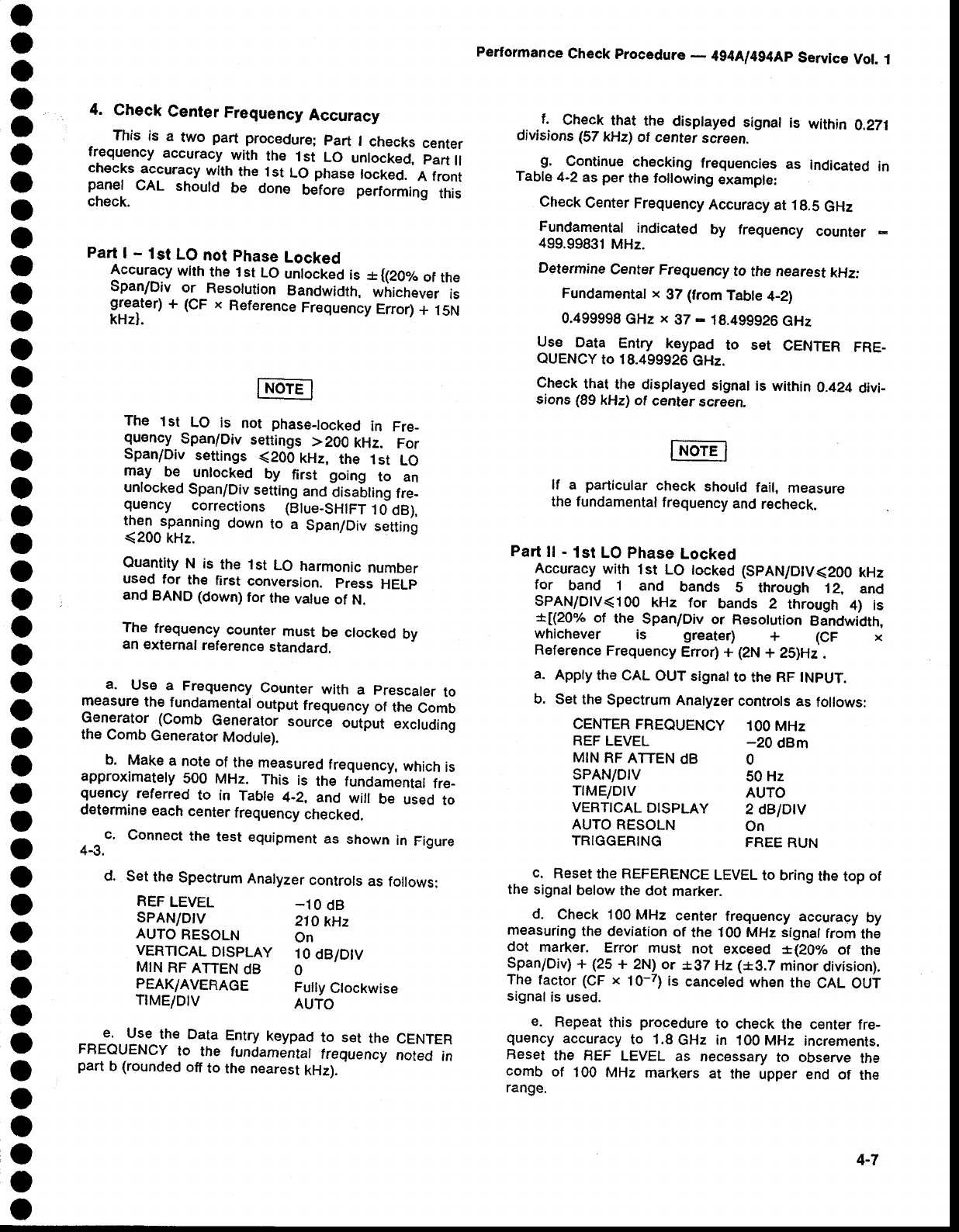

setup

lor checking

center

frequency

accuracy. ....... 4-g

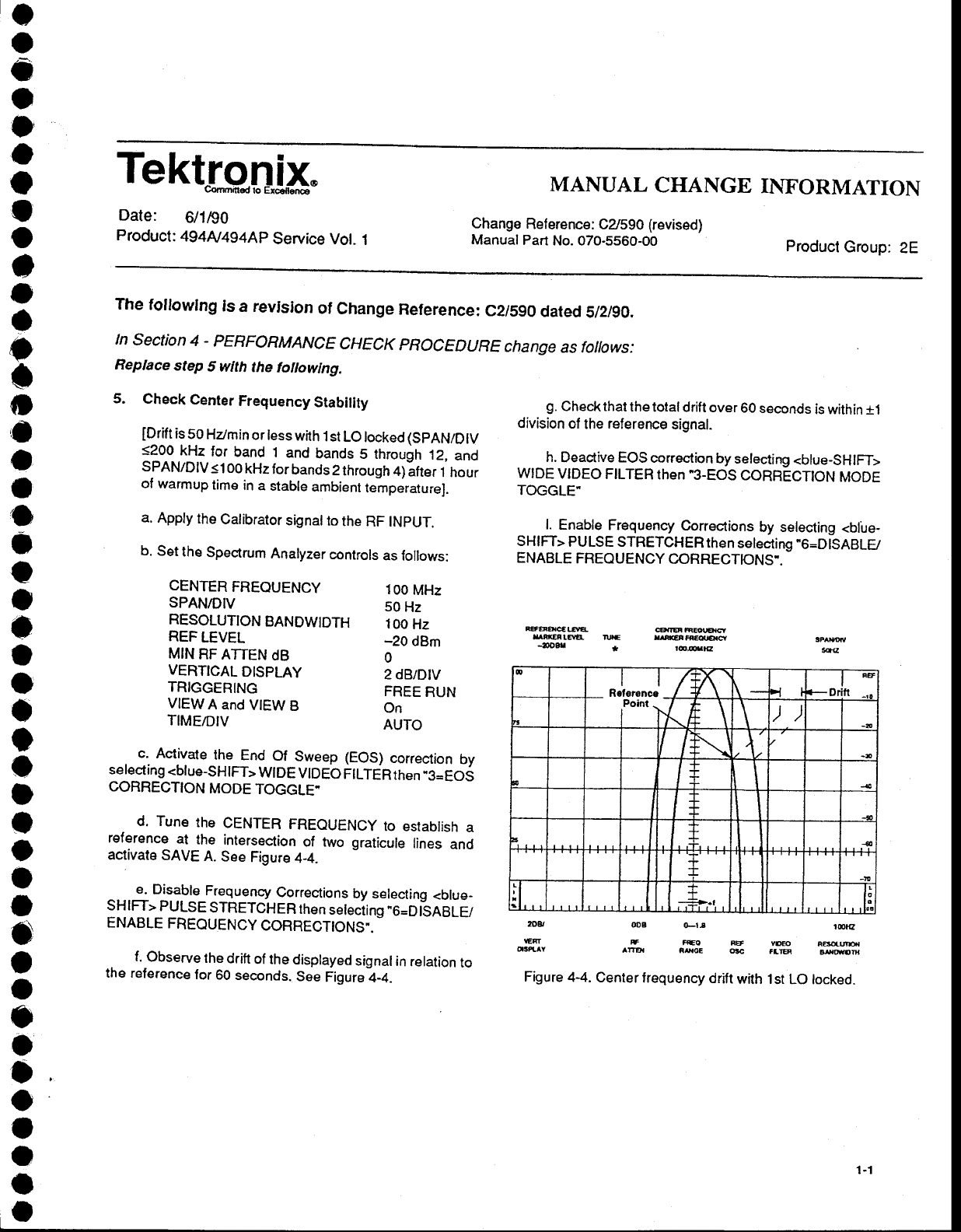

44 Center frequency

drift with

the

1st

LO

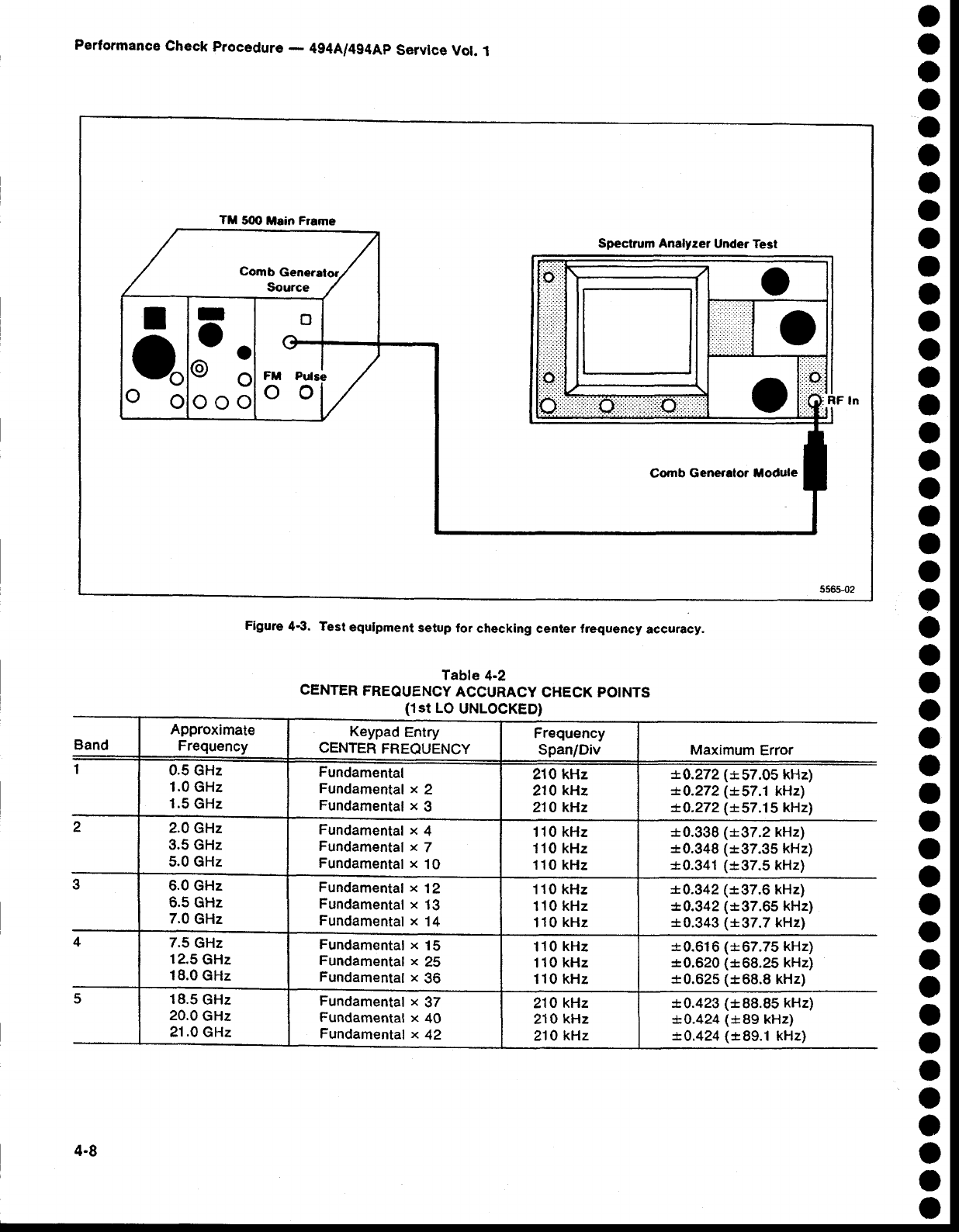

tocked. ....................4-9

4-5 Typical

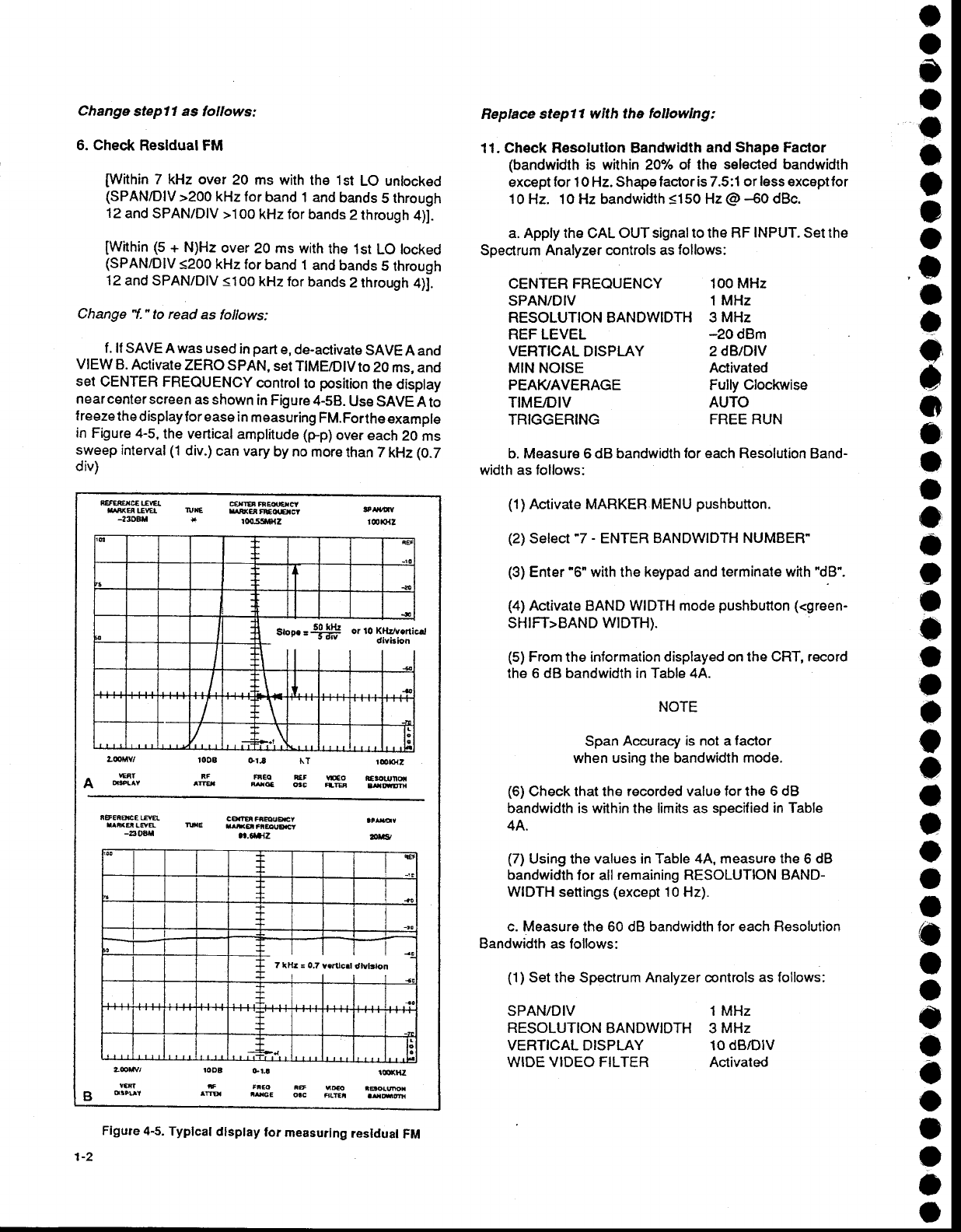

display

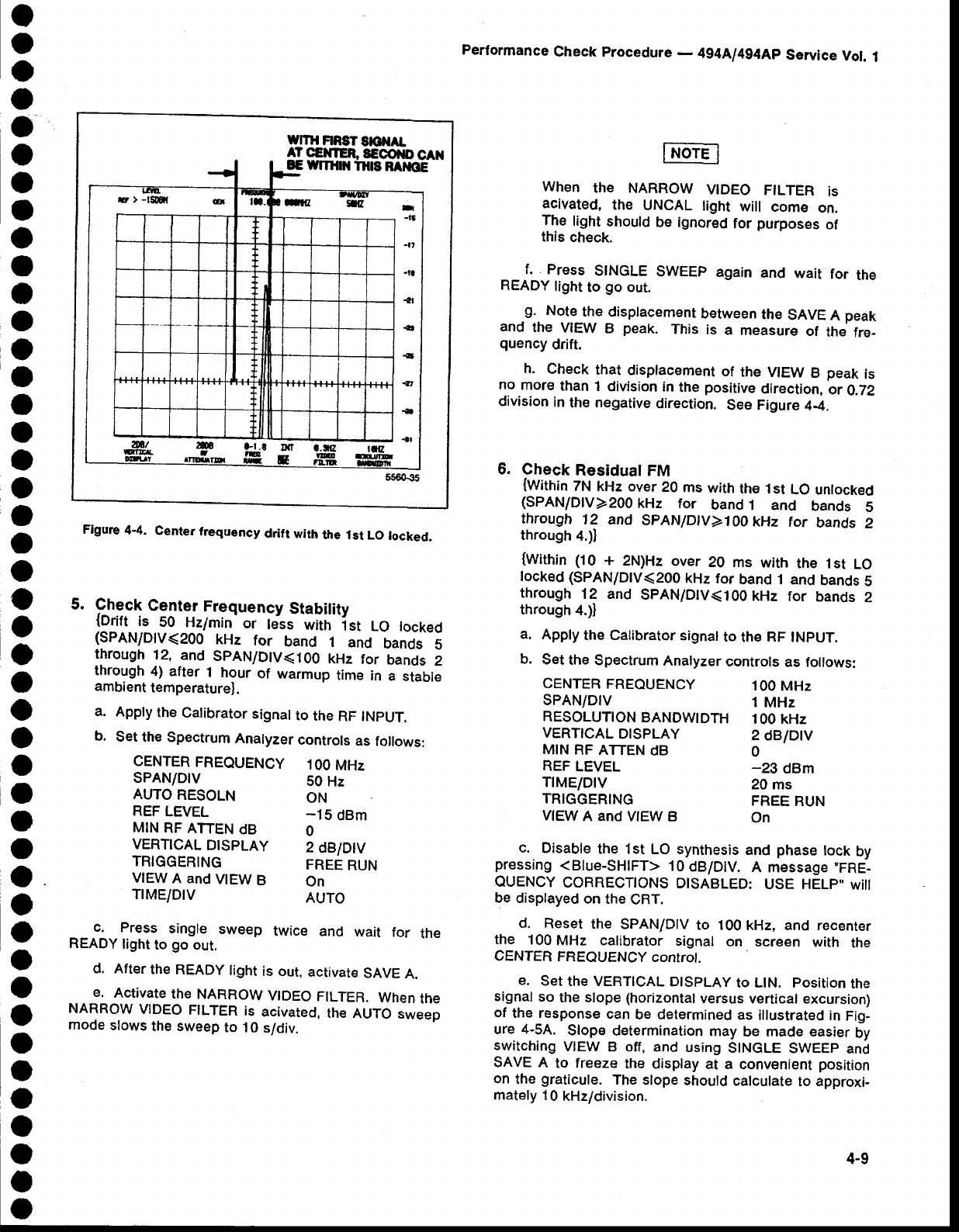

for measuring

residual

FM. ............ ..................4-10

4-6 Typical

marker

display for

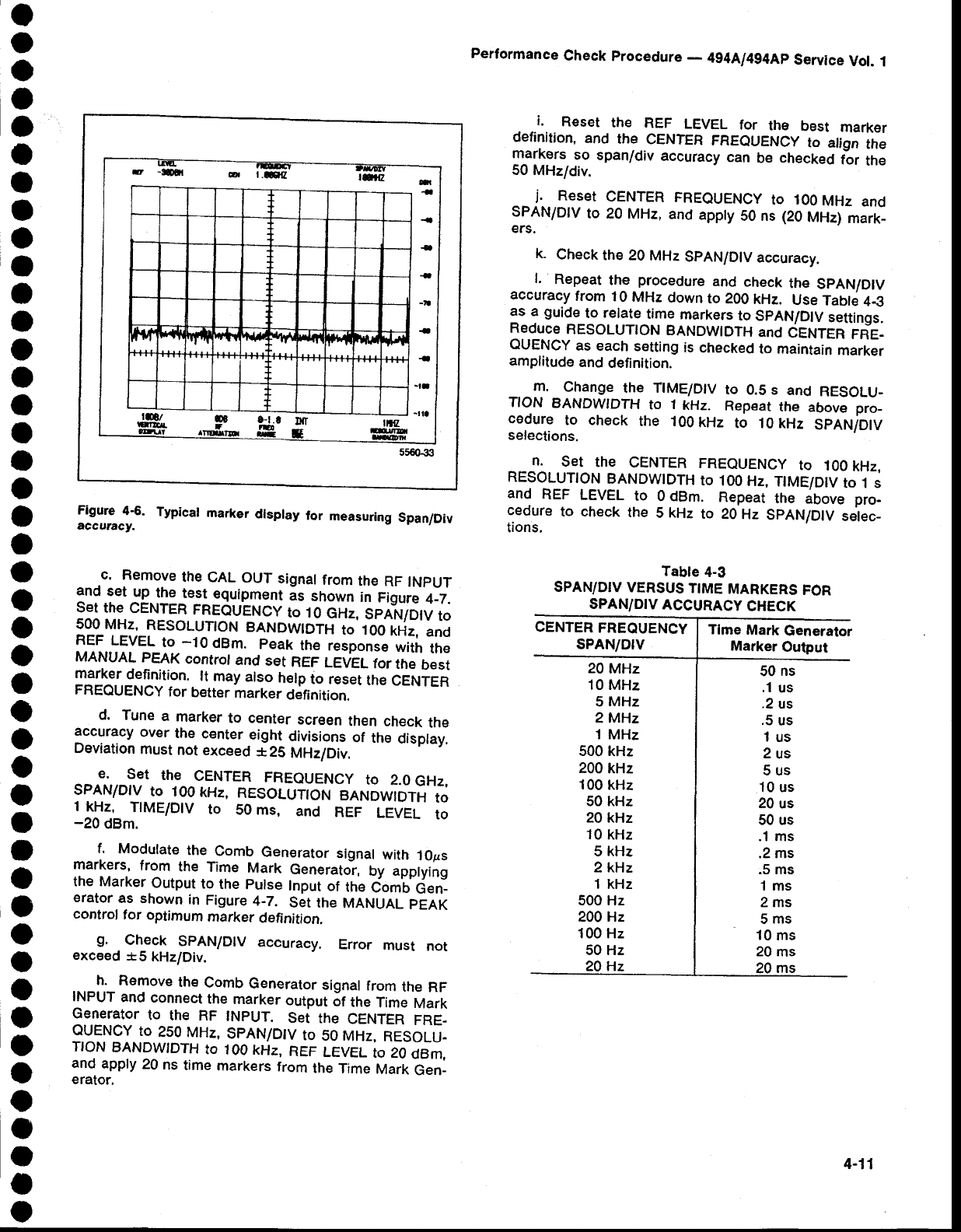

measuring

Span/Div

accuracy.

.....................

4-1 1

4-7 Test

equipment

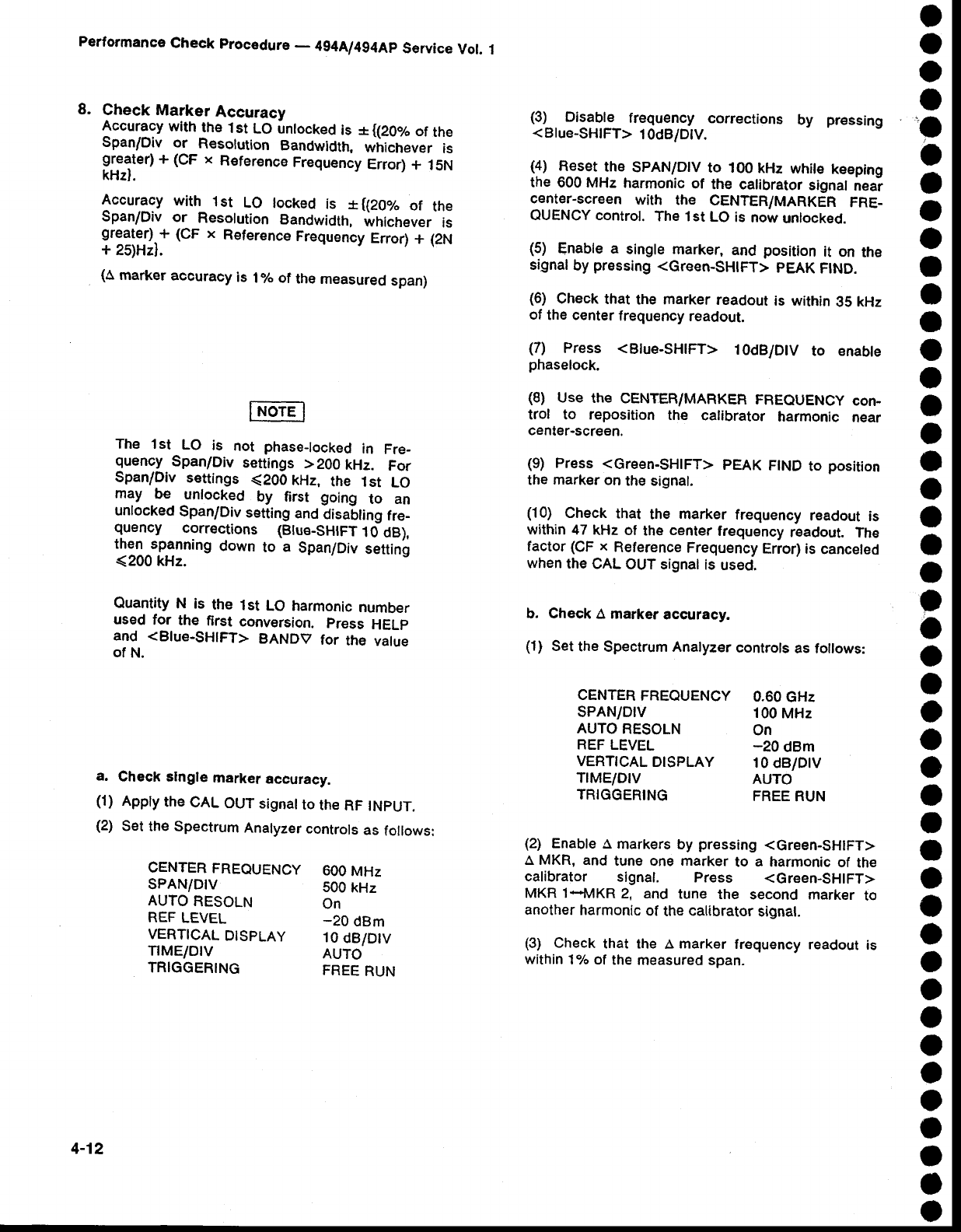

setup for checking

frequency

Span/Div and

sweep

Time/Div

accuracy. ....................

4-13

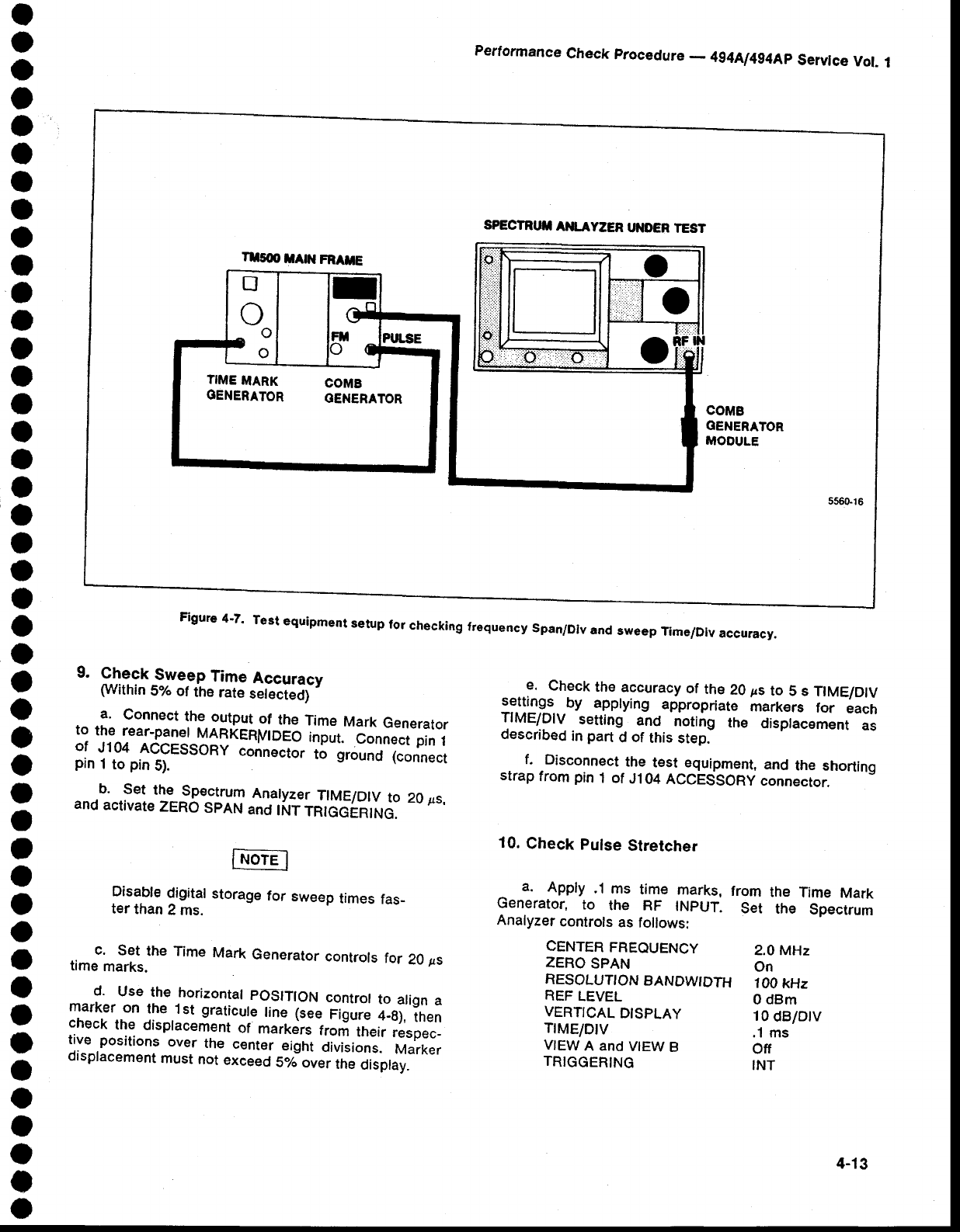

4-8 Typical

display

for measuring

Time/Div

accuracy. ....................

4-14

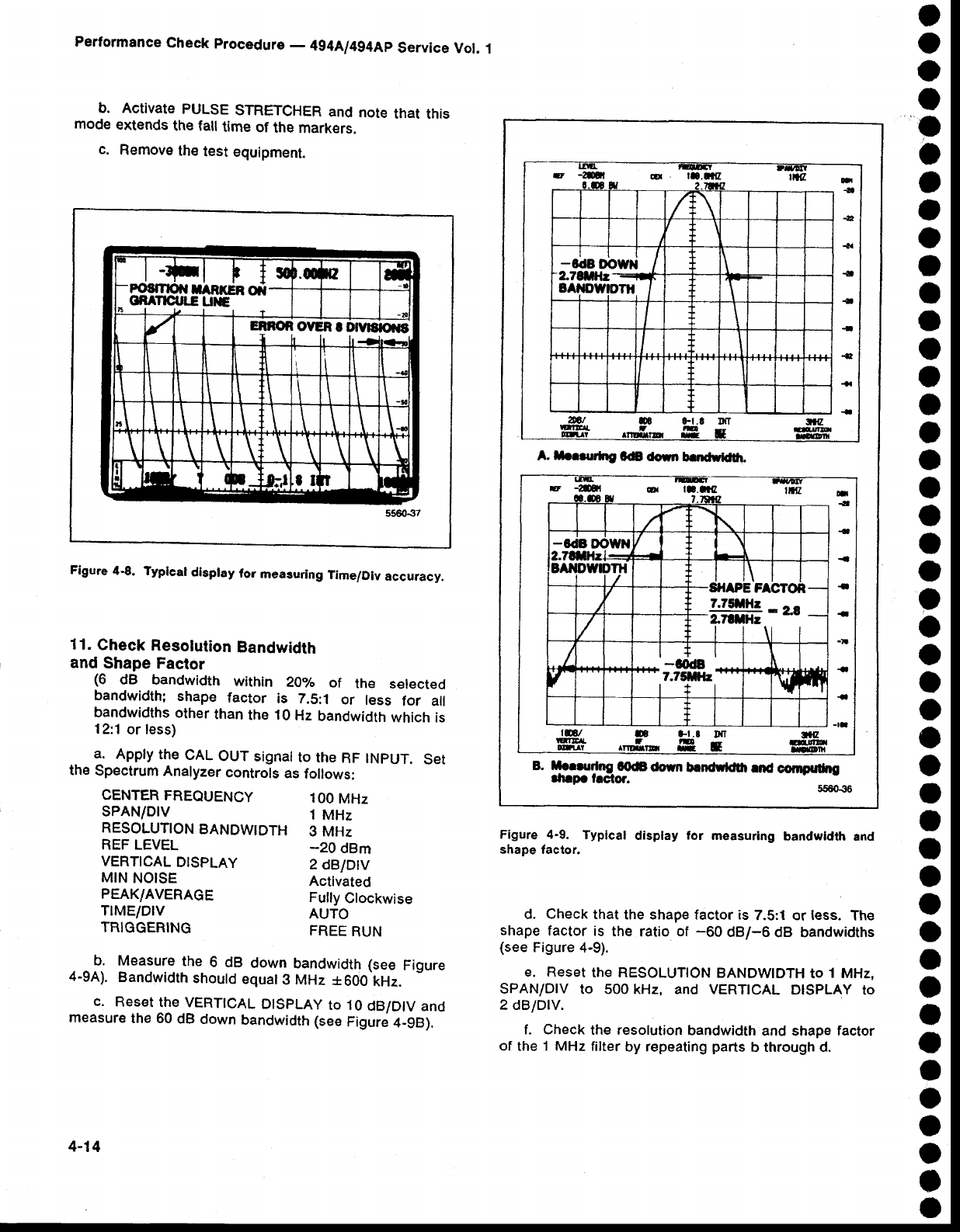

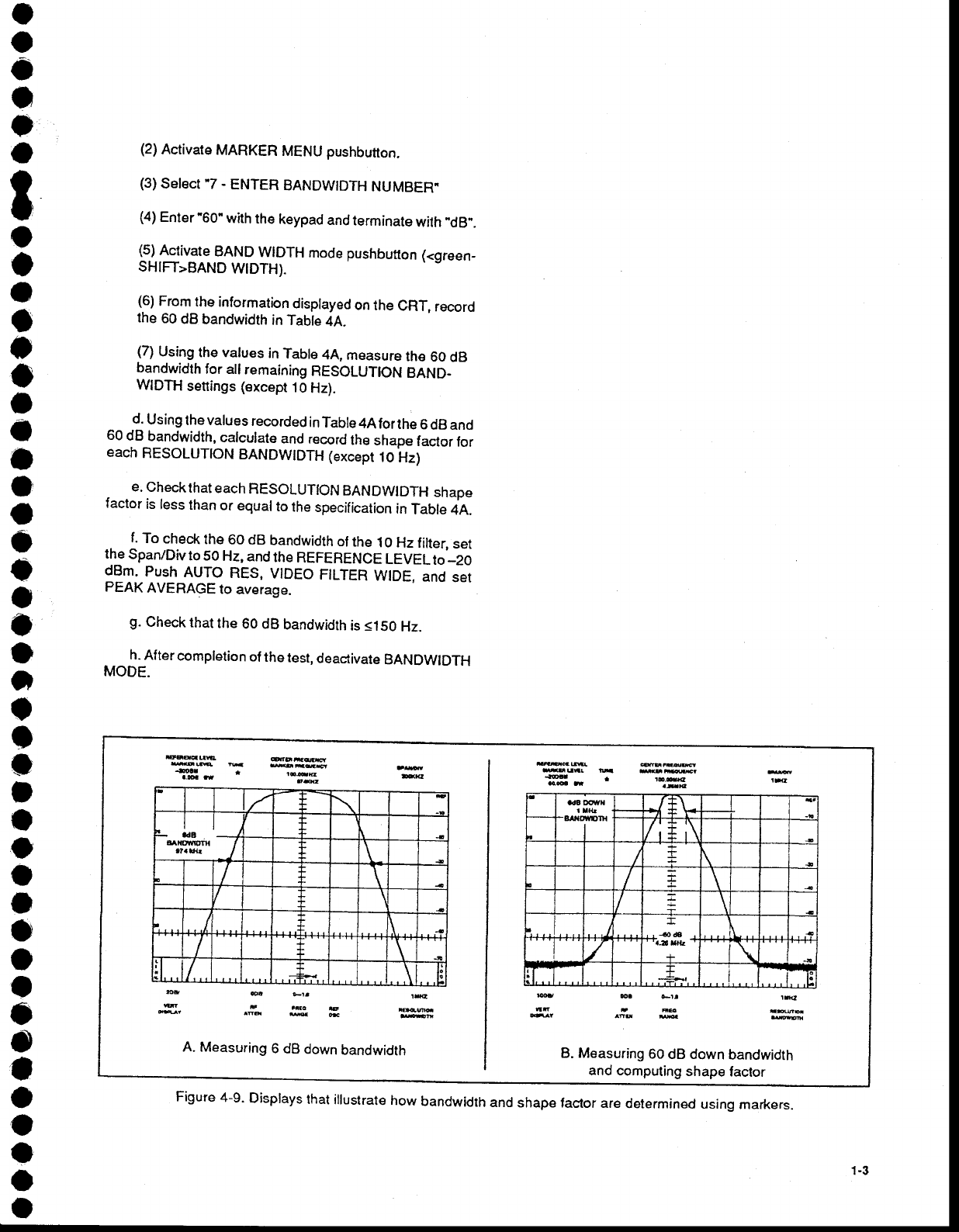

4-9 Typical

display

for measuring

bandwidth and

shape

factor. .....4-14

4-10 Typical

display

for measuring

noise sidebands.

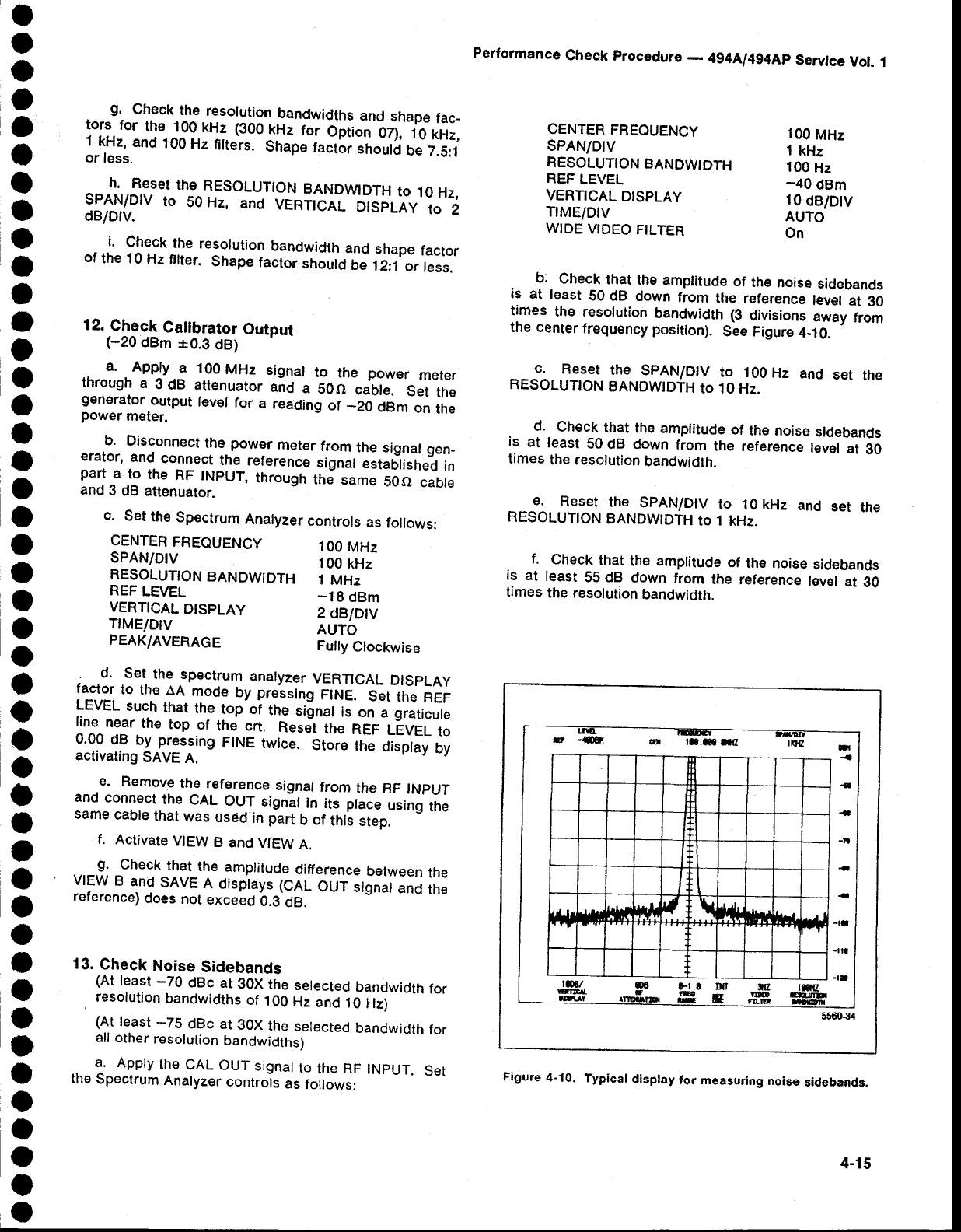

........... ............ 4-15

4-1'l Test

equipment

s€tup tor

measuring

0.01

GHz to 21

GHz

frequency

response. ..................

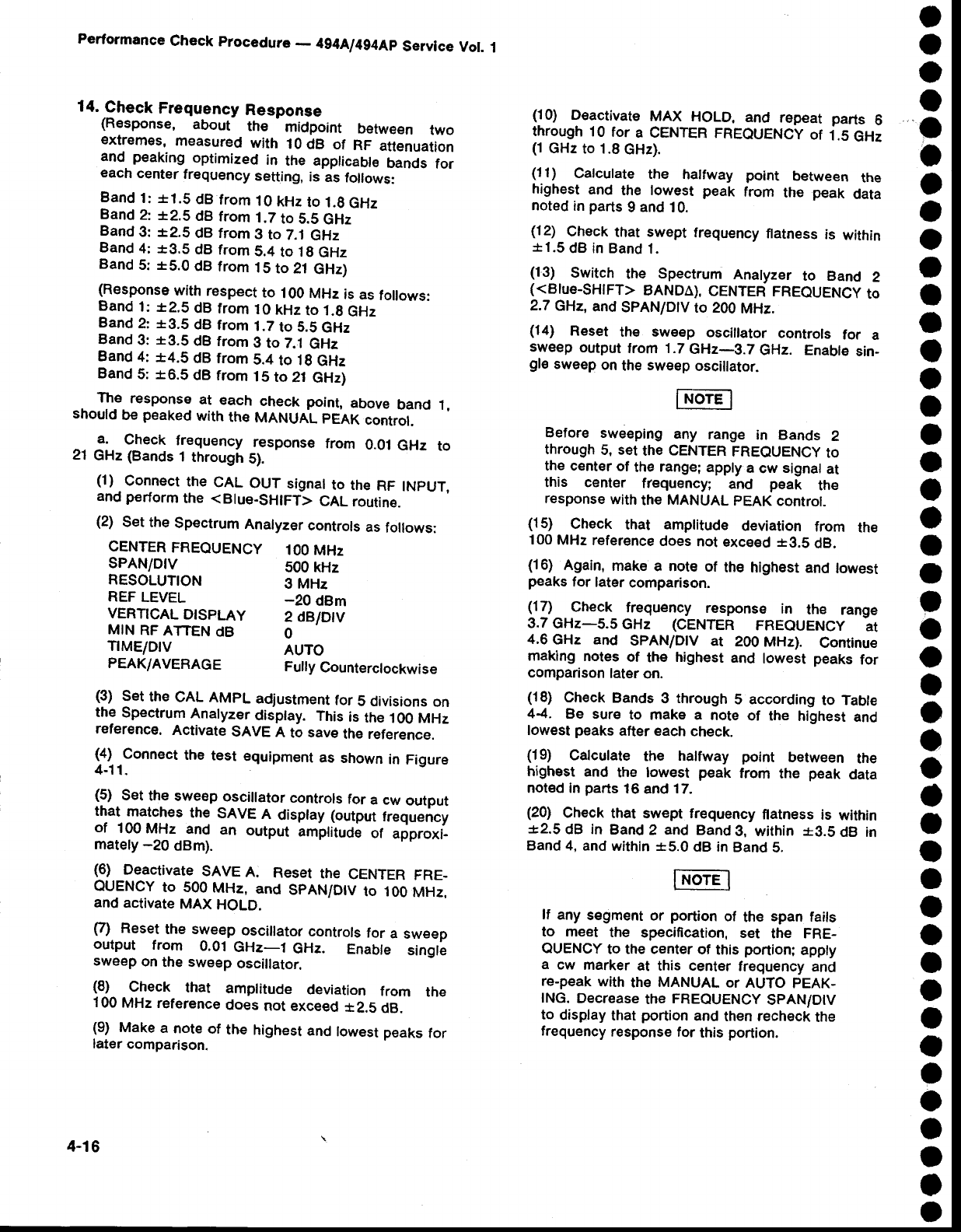

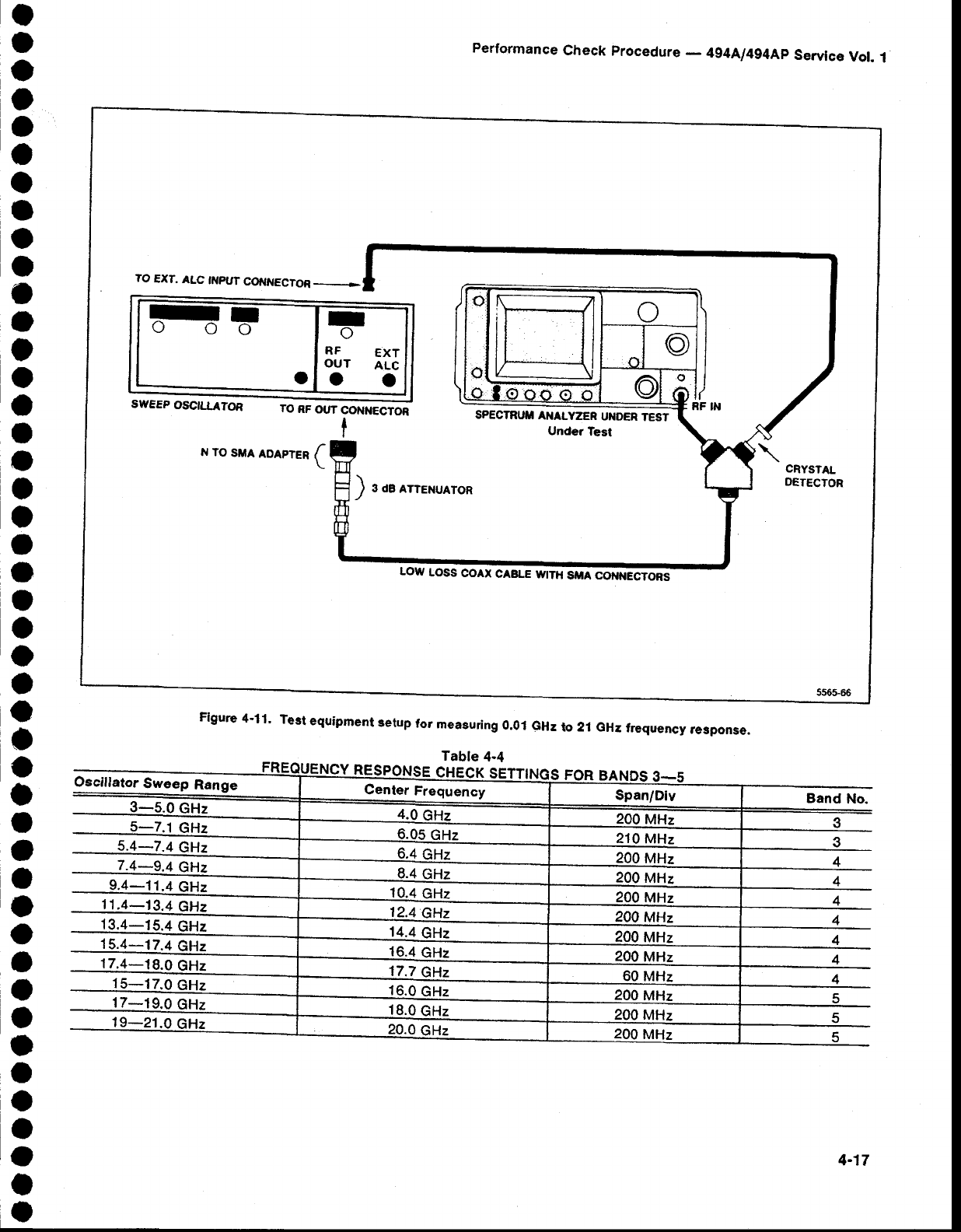

4-17

4-12 Test equipment

setup

for

measuring

10

kHz

to

l0 MHz

frequency

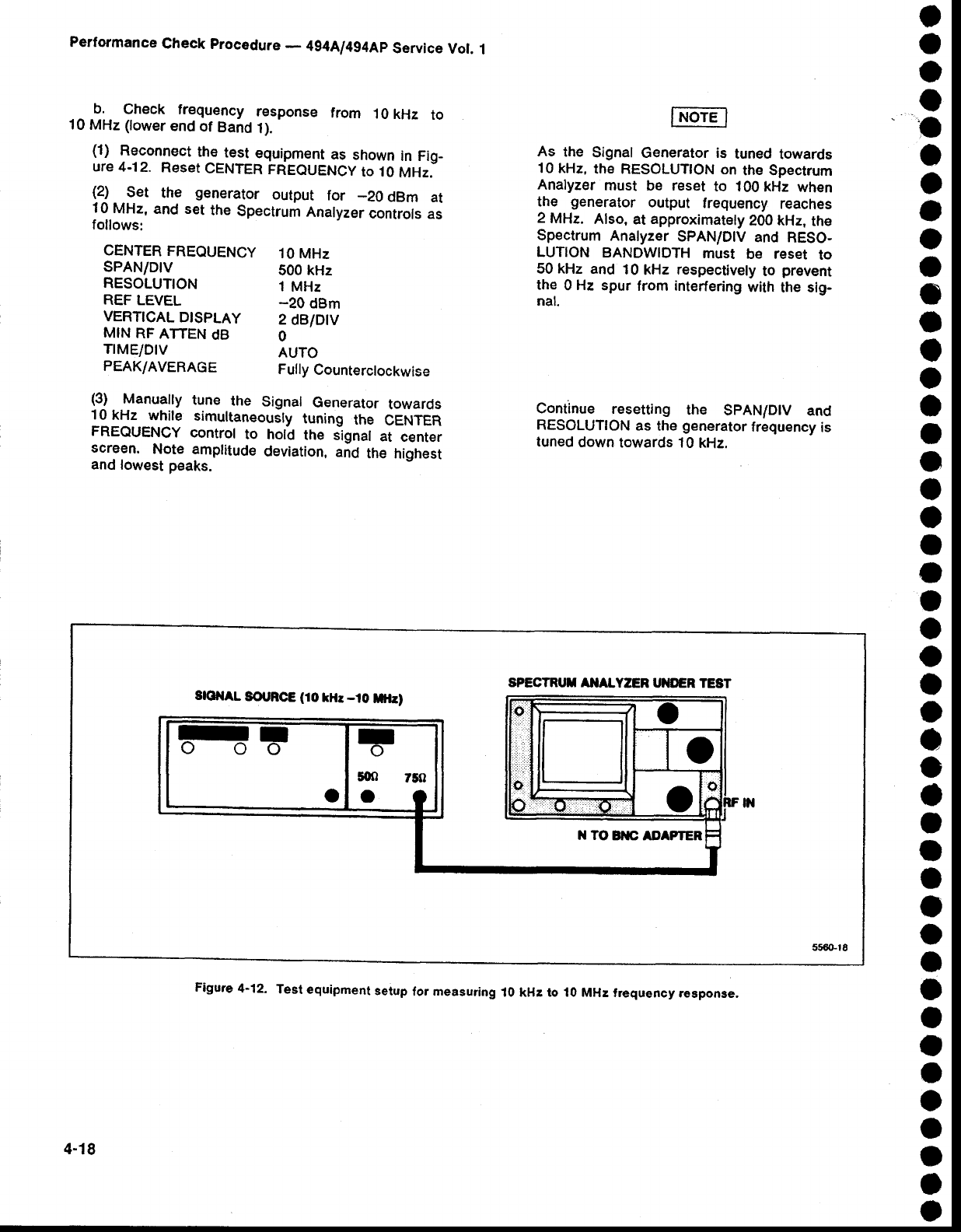

response. ..................

4-19

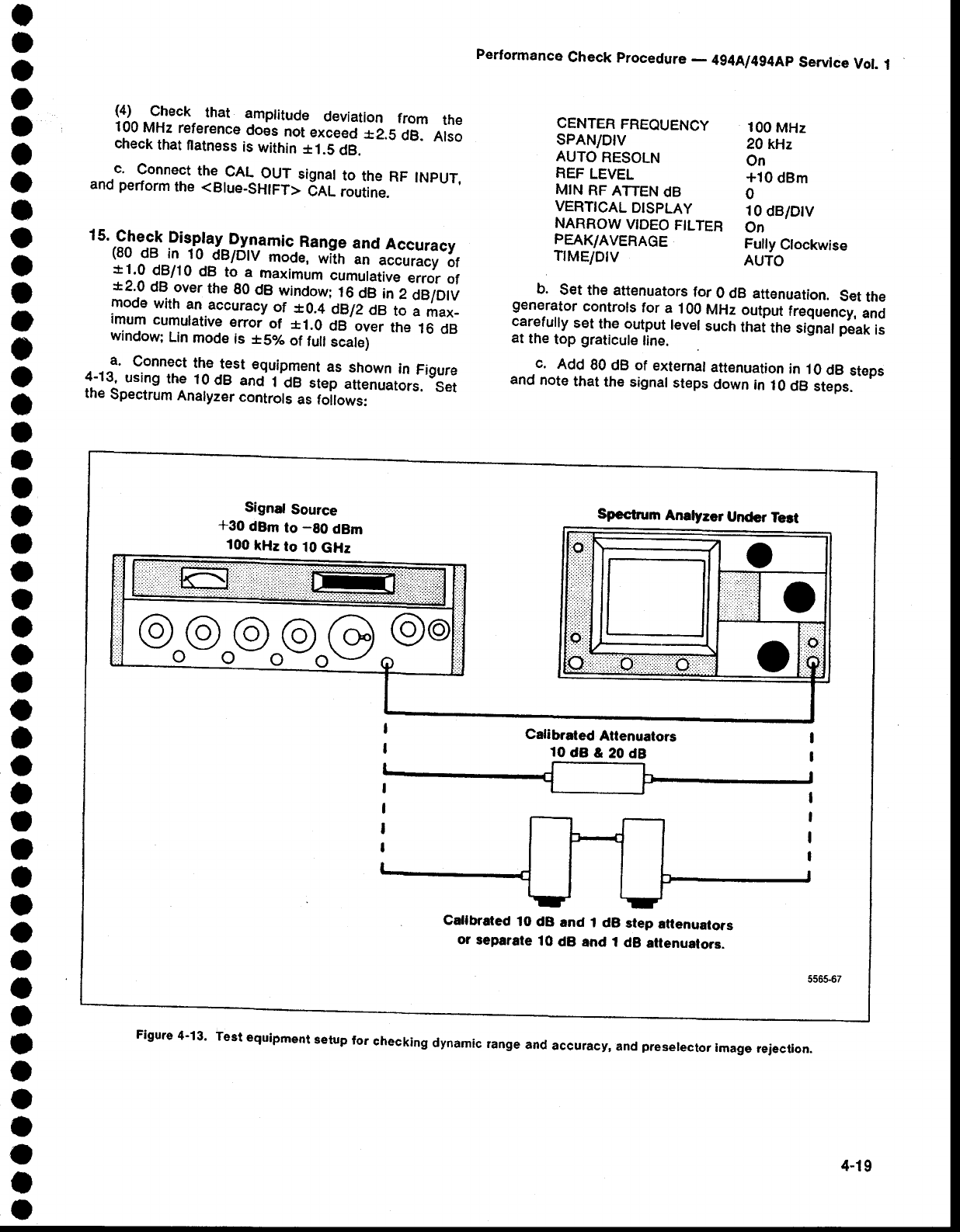

4-13 Test

equipment

setup for

checking

dynamic range

and accuracy,

and

preselector

rejection. ................

4-19

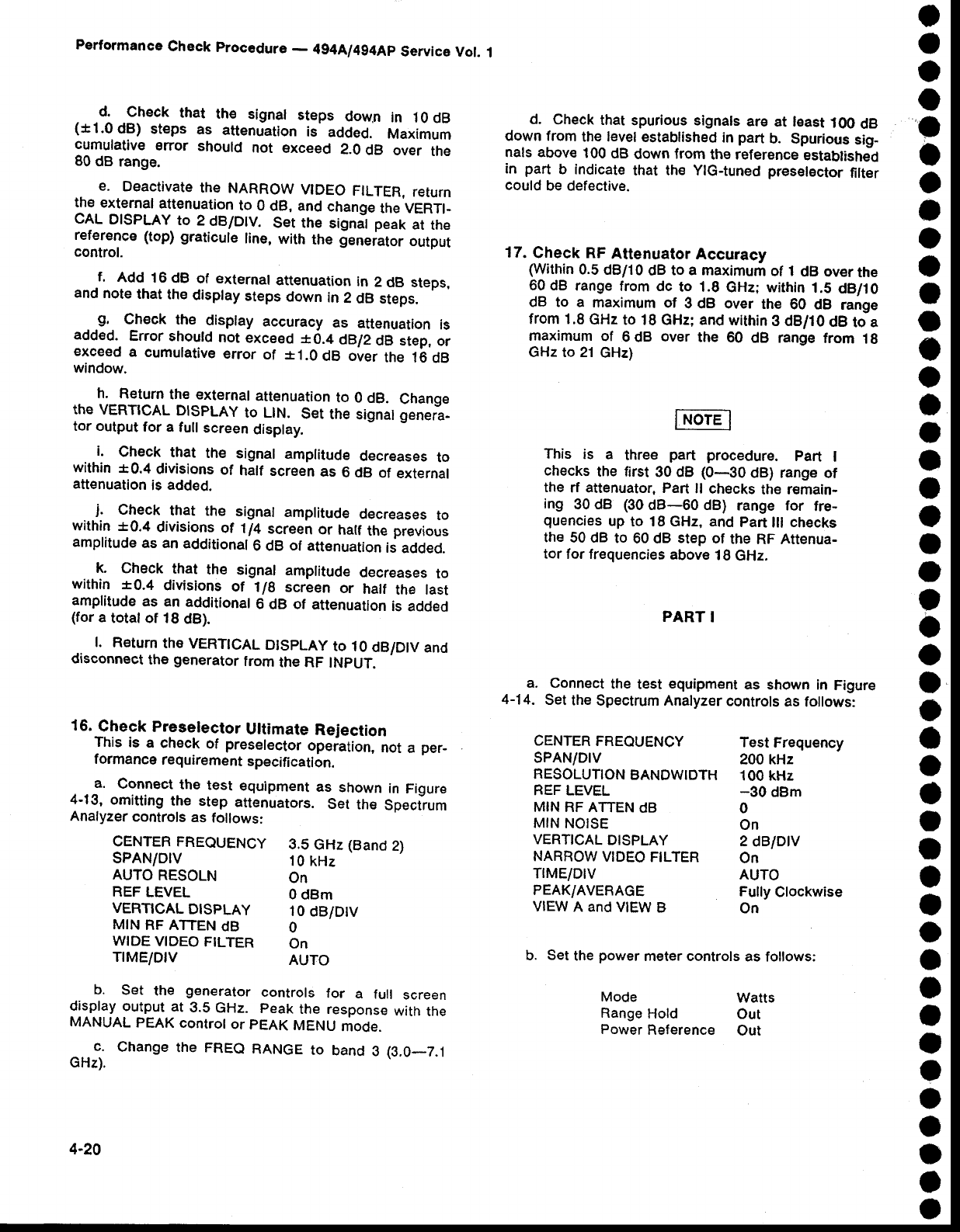

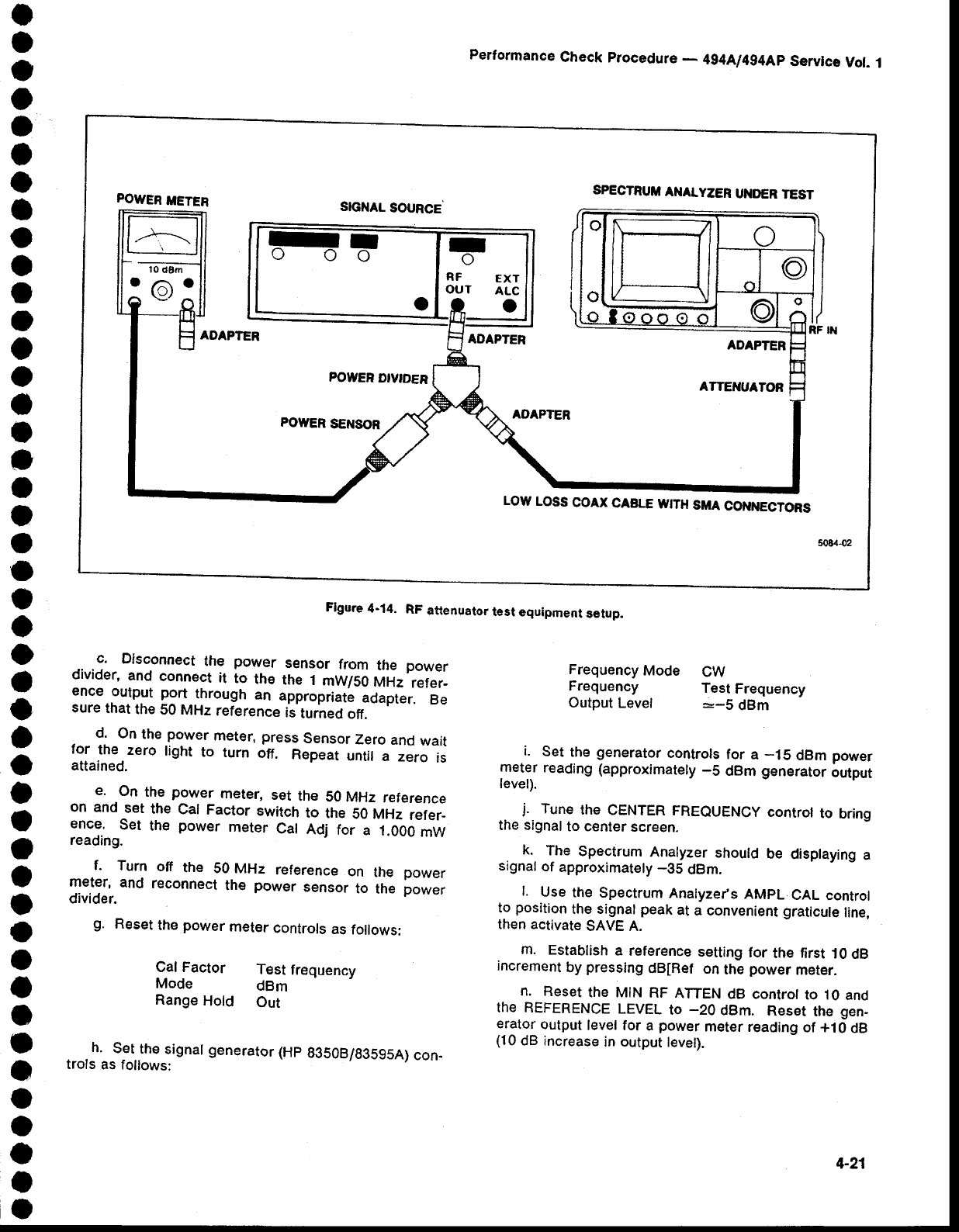

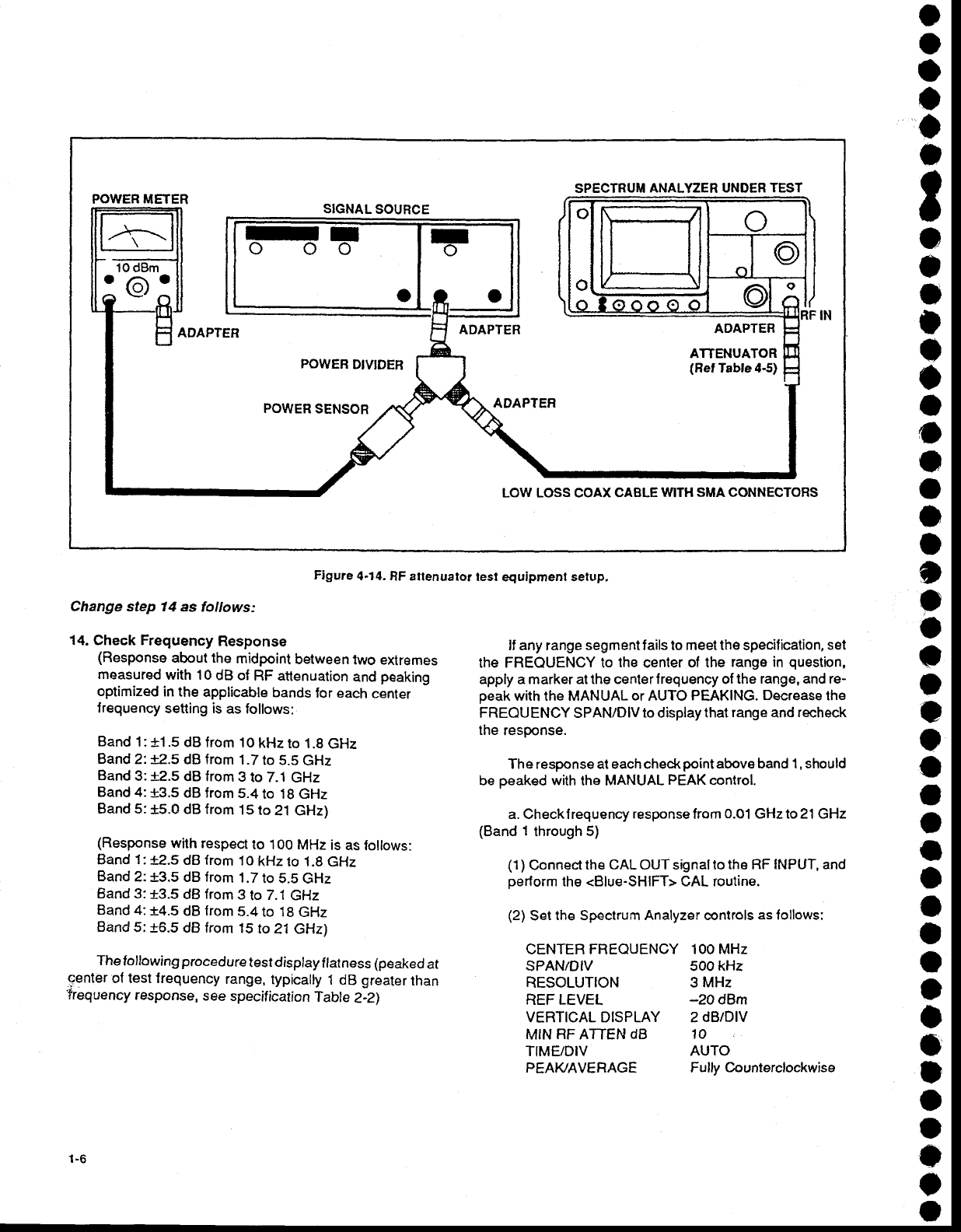

4-14 RF

attenuator

test equipm€nt

setup.

............4-21

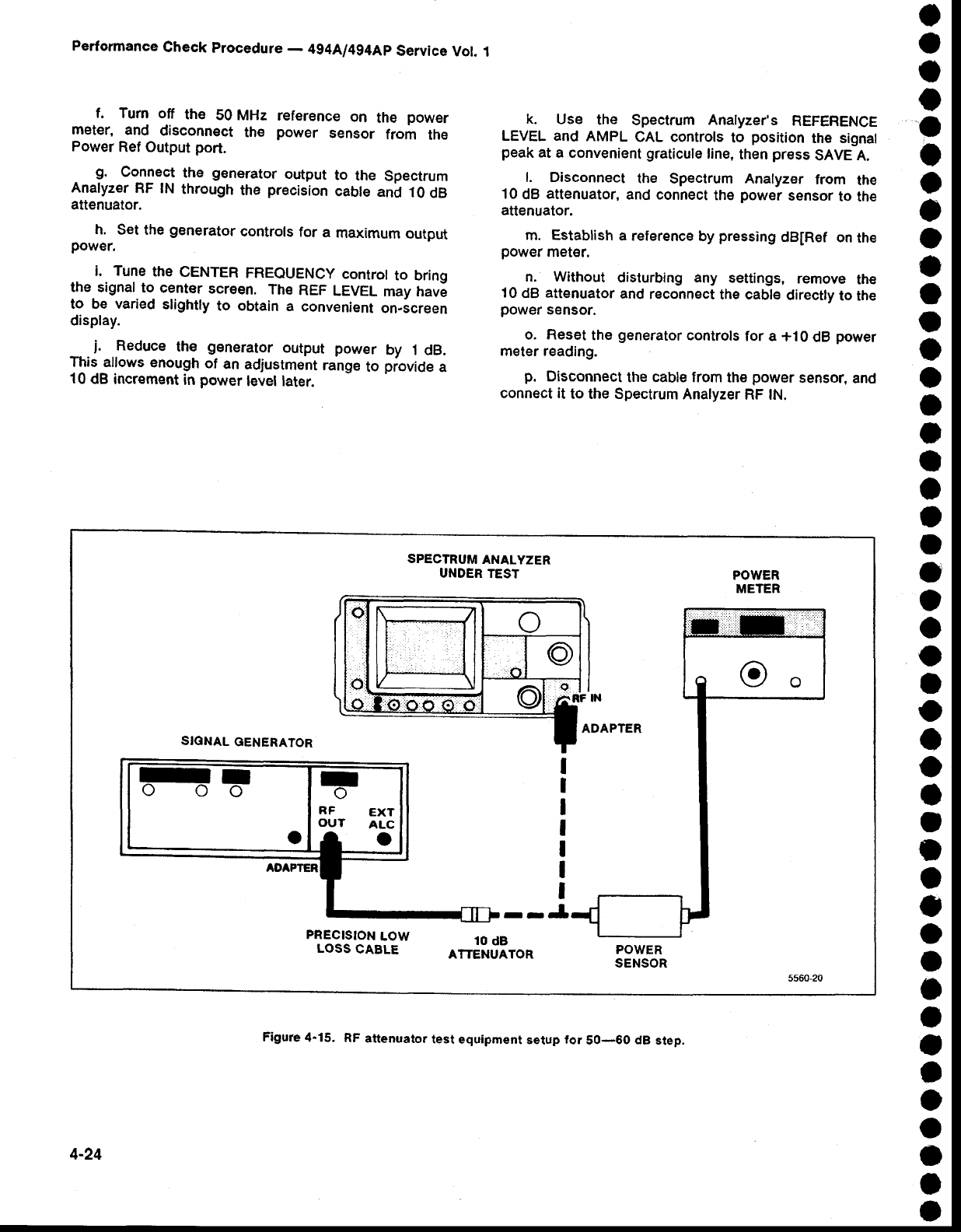

4-1

5 RF attenuator

test

equipment

setup

lor

50-60 dB step. .........,.........4-24

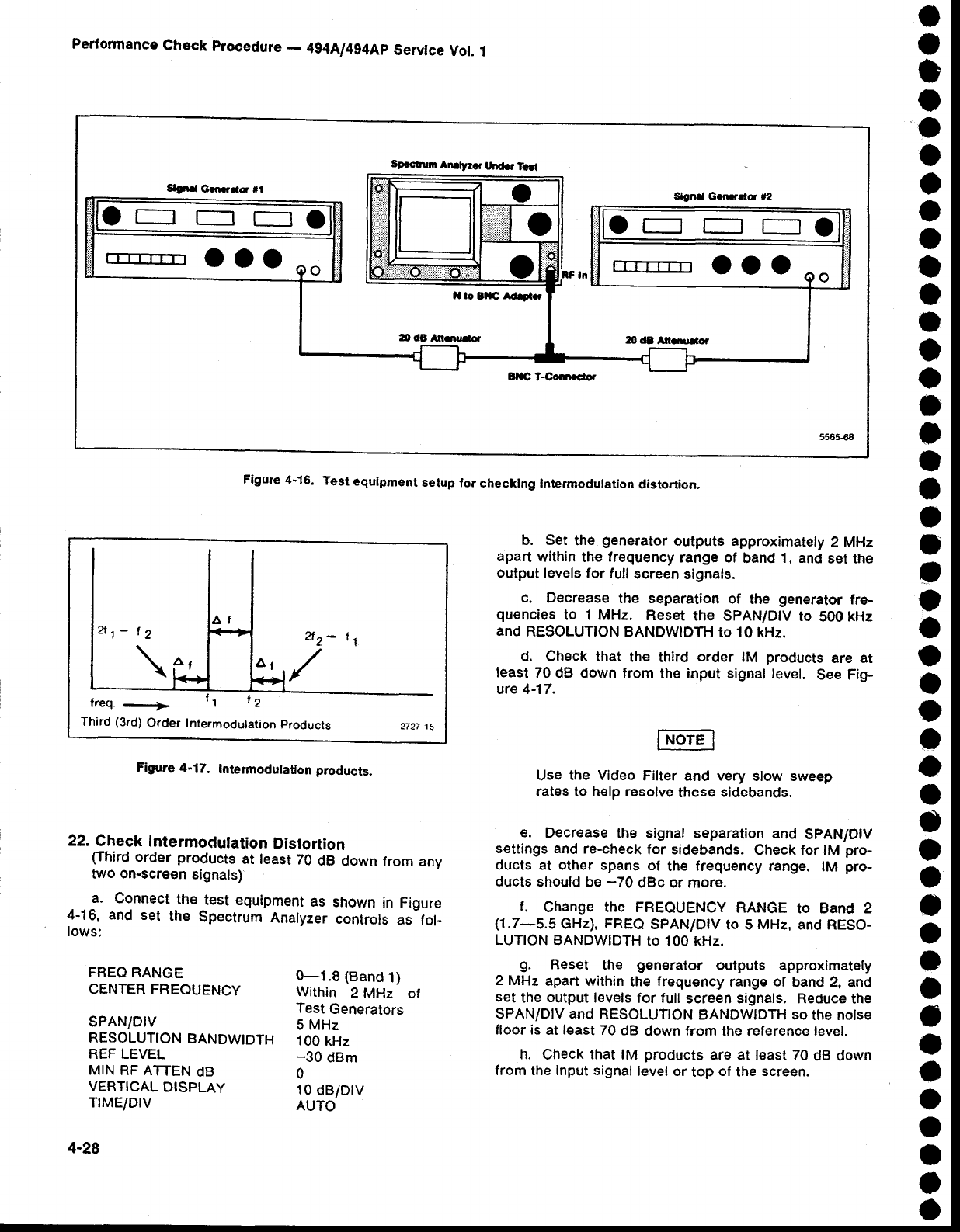

4-1 6 . Test

equipment

setup for checking

intermodulation

distortion ....,,,....4-28

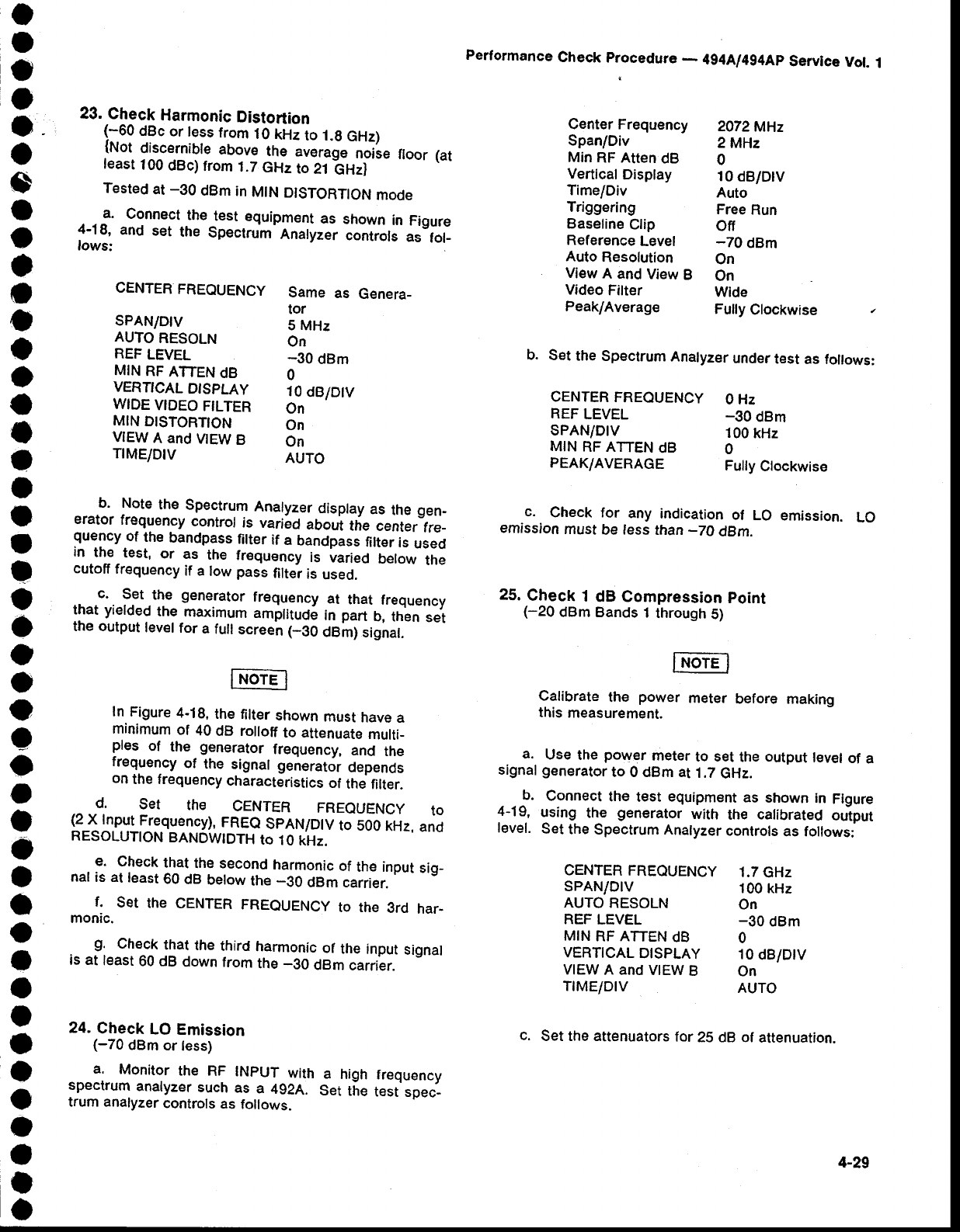

4-17 f

ntermodulation

products ............4-29

4-1

I Test

equipment

setup

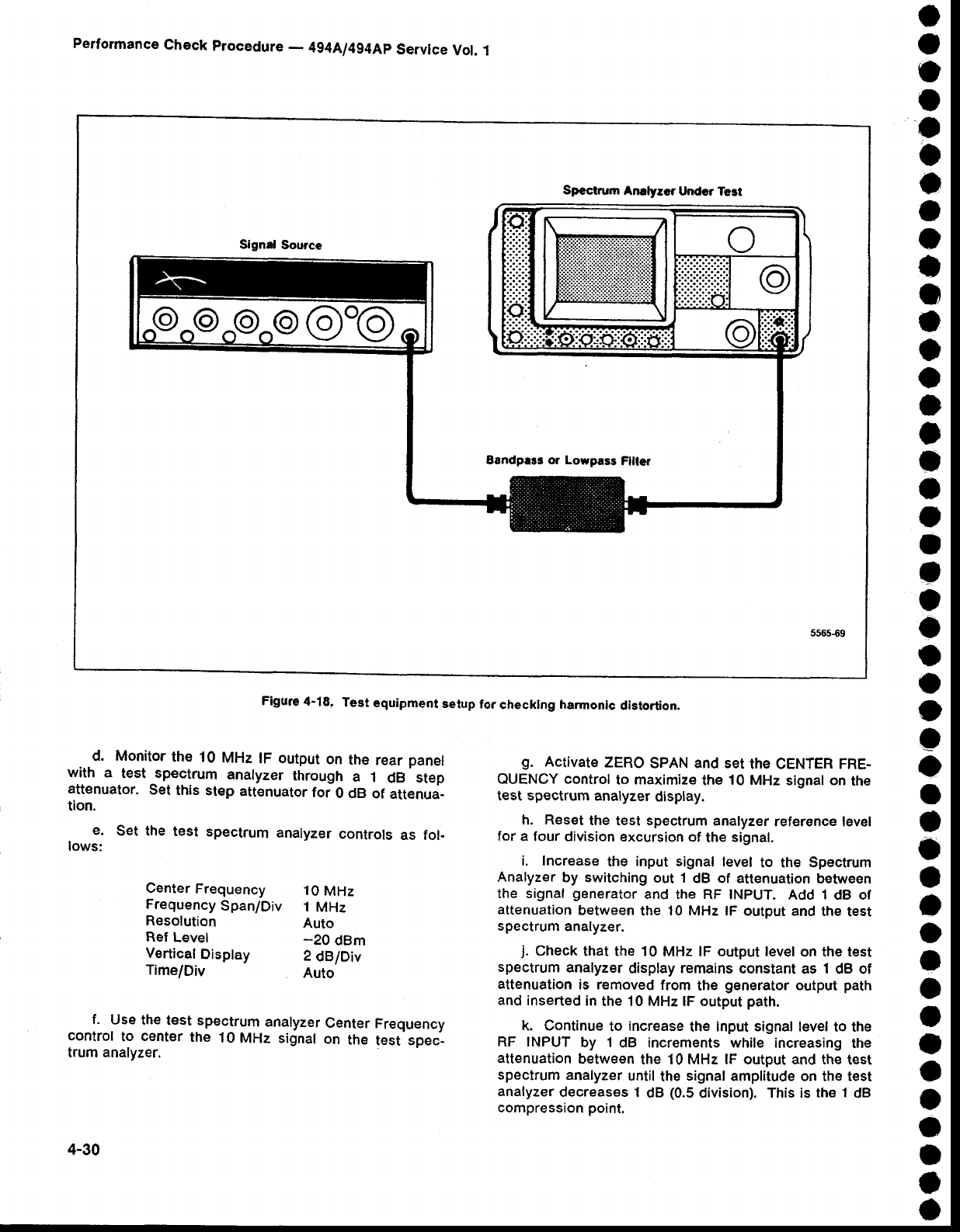

for checking

harmonic

distortion. ..............,...

4-90

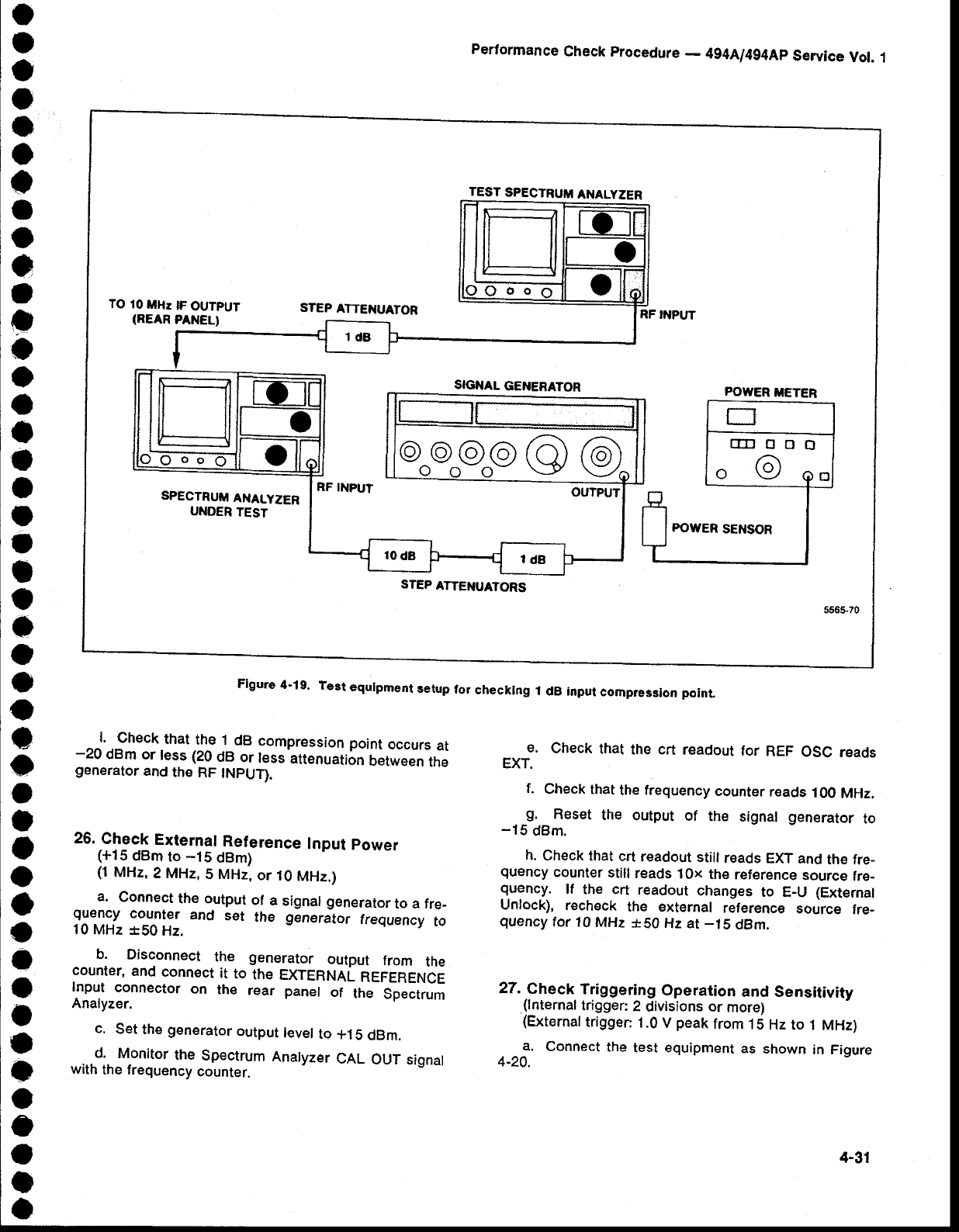

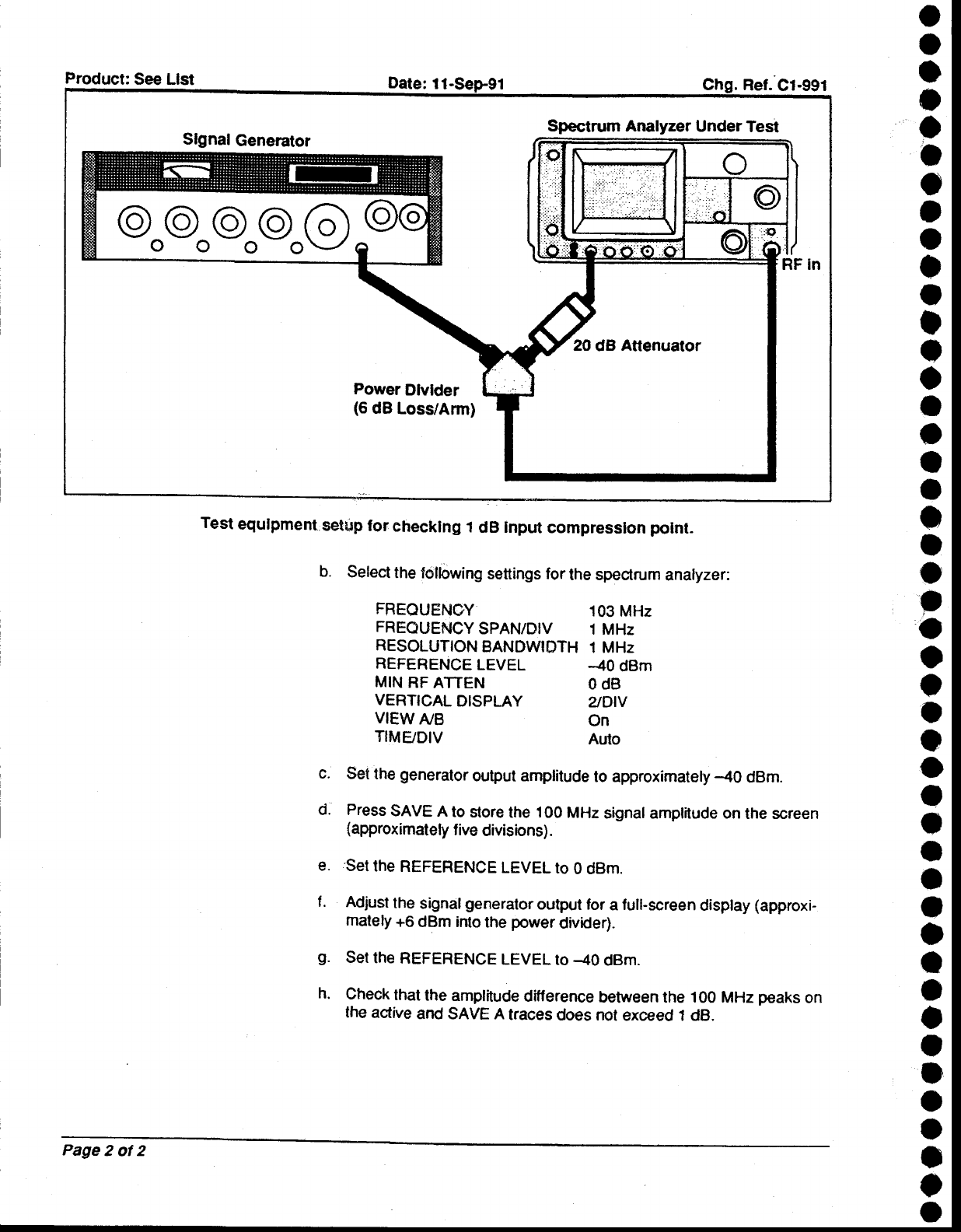

4-19 Test equipment

setup

for

checking

1

dB

input

compression point.

..........................,...

4-31

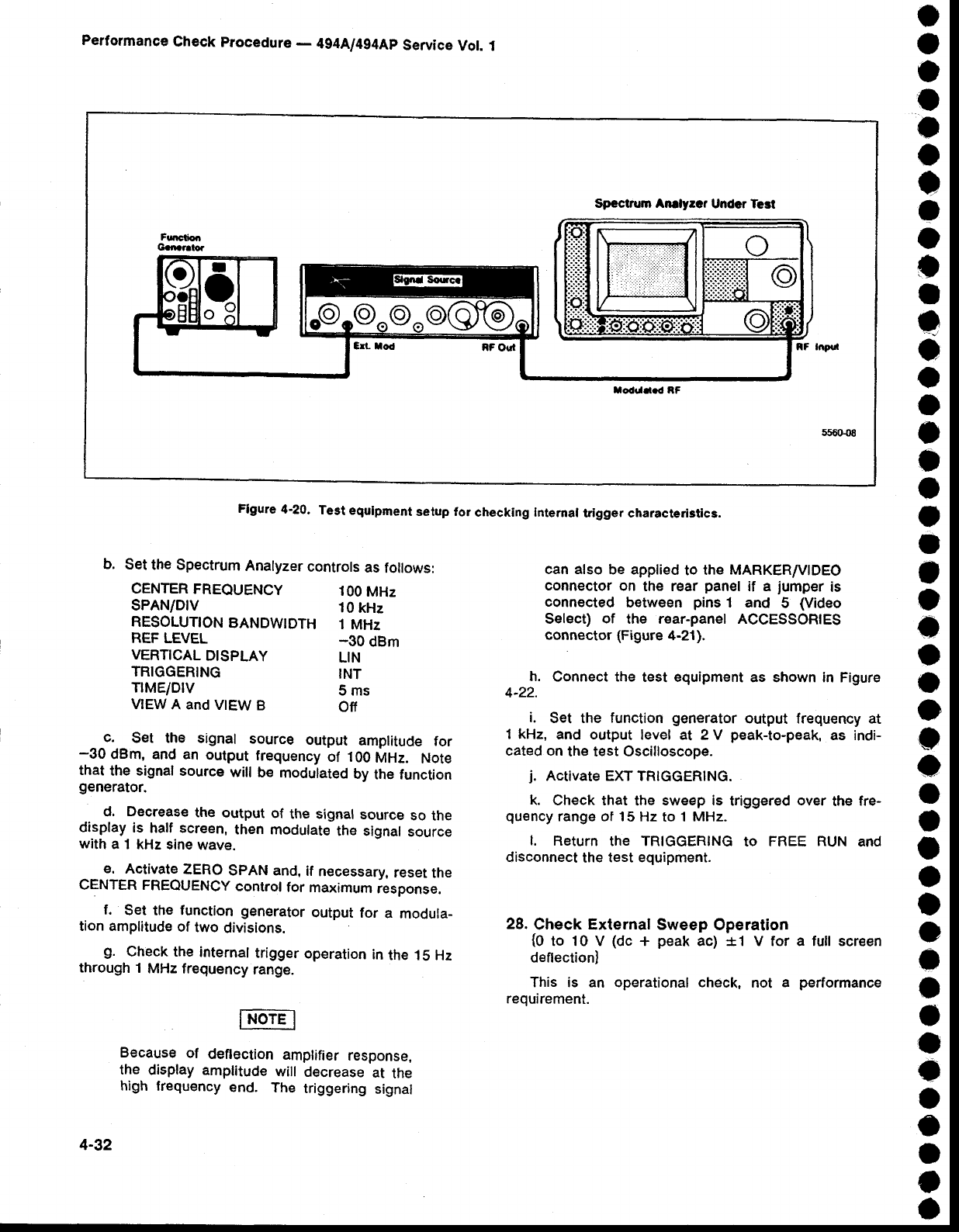

4-20 T€st equipment

setup for checking

internal

trigger characteristics.

..............

......-

4-92

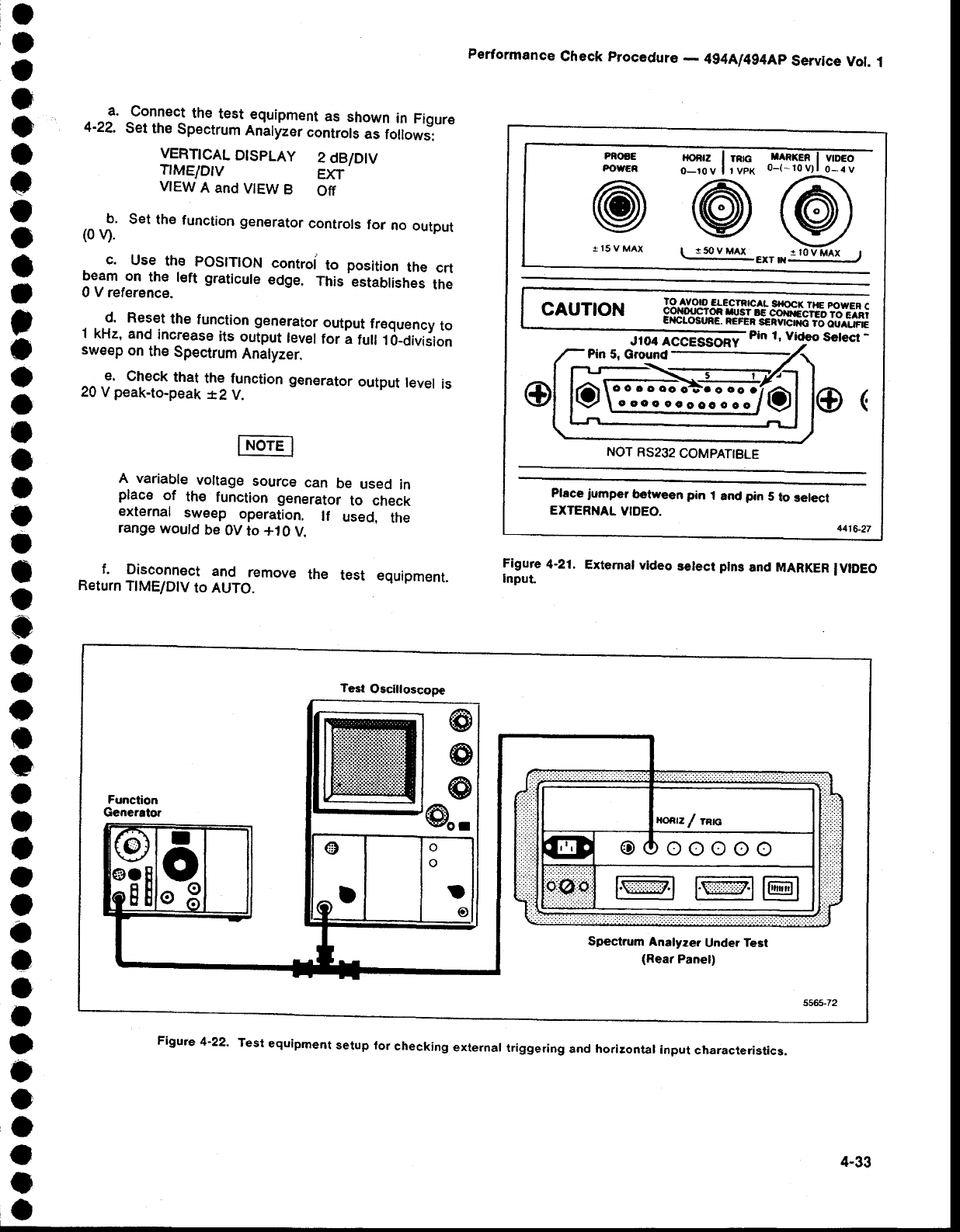

4-21 External

video

select

pins

and

MARKER

IVIDEO

input.

.......... ..

4-30

4-22 Test

equipment

setup for

checking

external

triggering

and horizontal

input

characteristics. .................

4-33

x

Figure Page

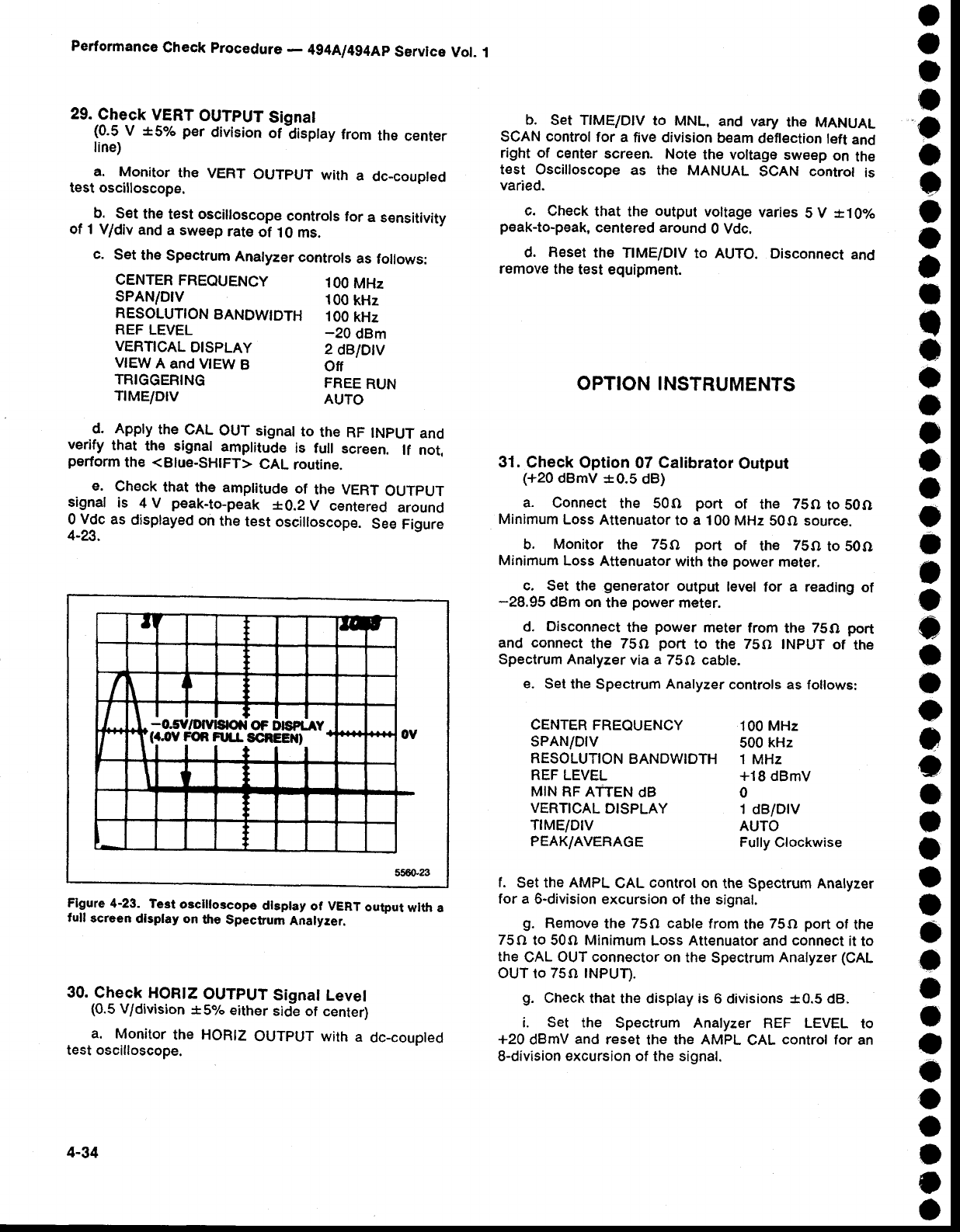

4-23 Test

oscilloscope

display

of

VERT

output

with a full screen display

on

the

Spectrum

Analyzer. .......4-34

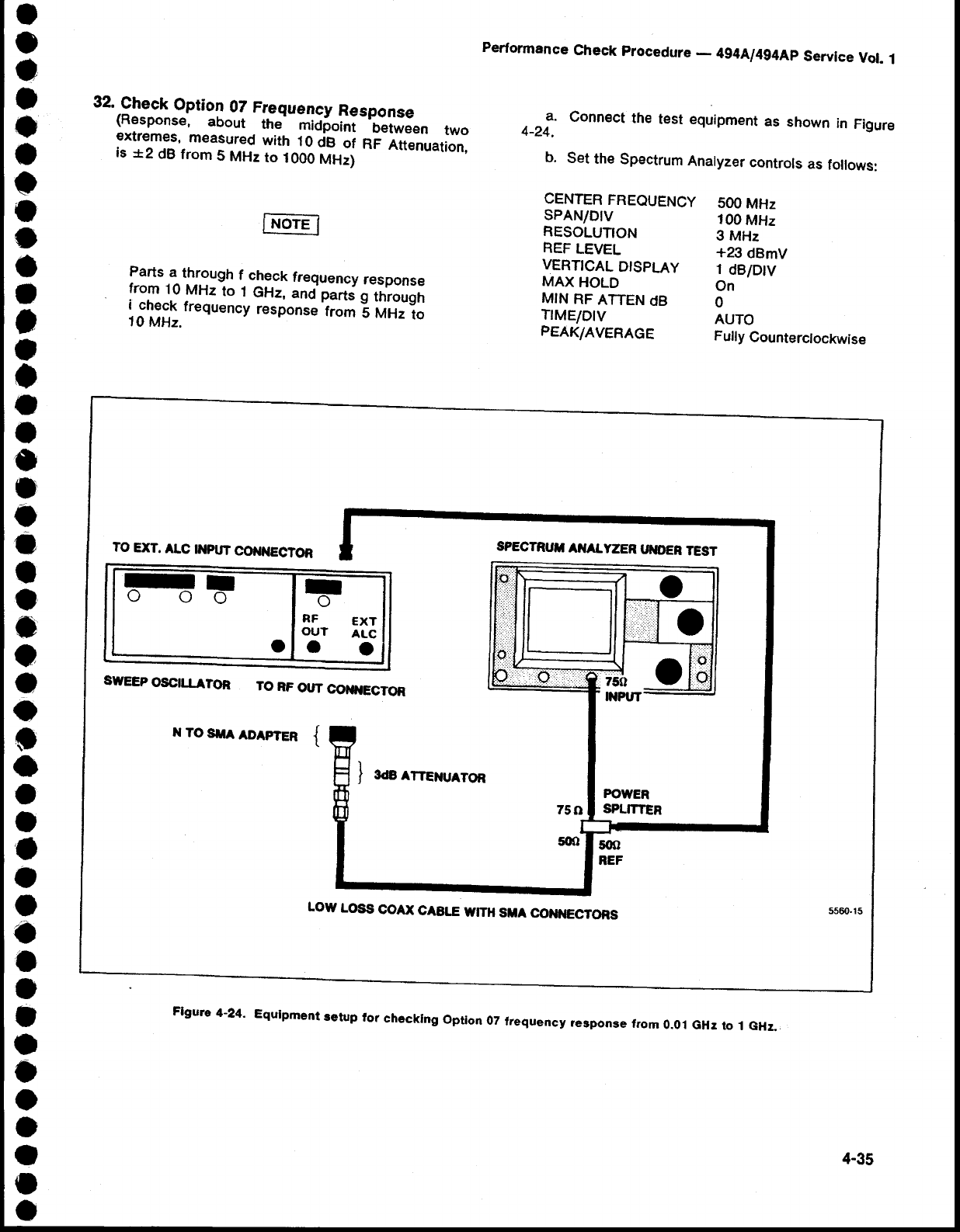

4-24 Equipment

setup

for checking

Option 07

frequency

response

from

0.01 GHz to 1 GHz. .......... 4-35

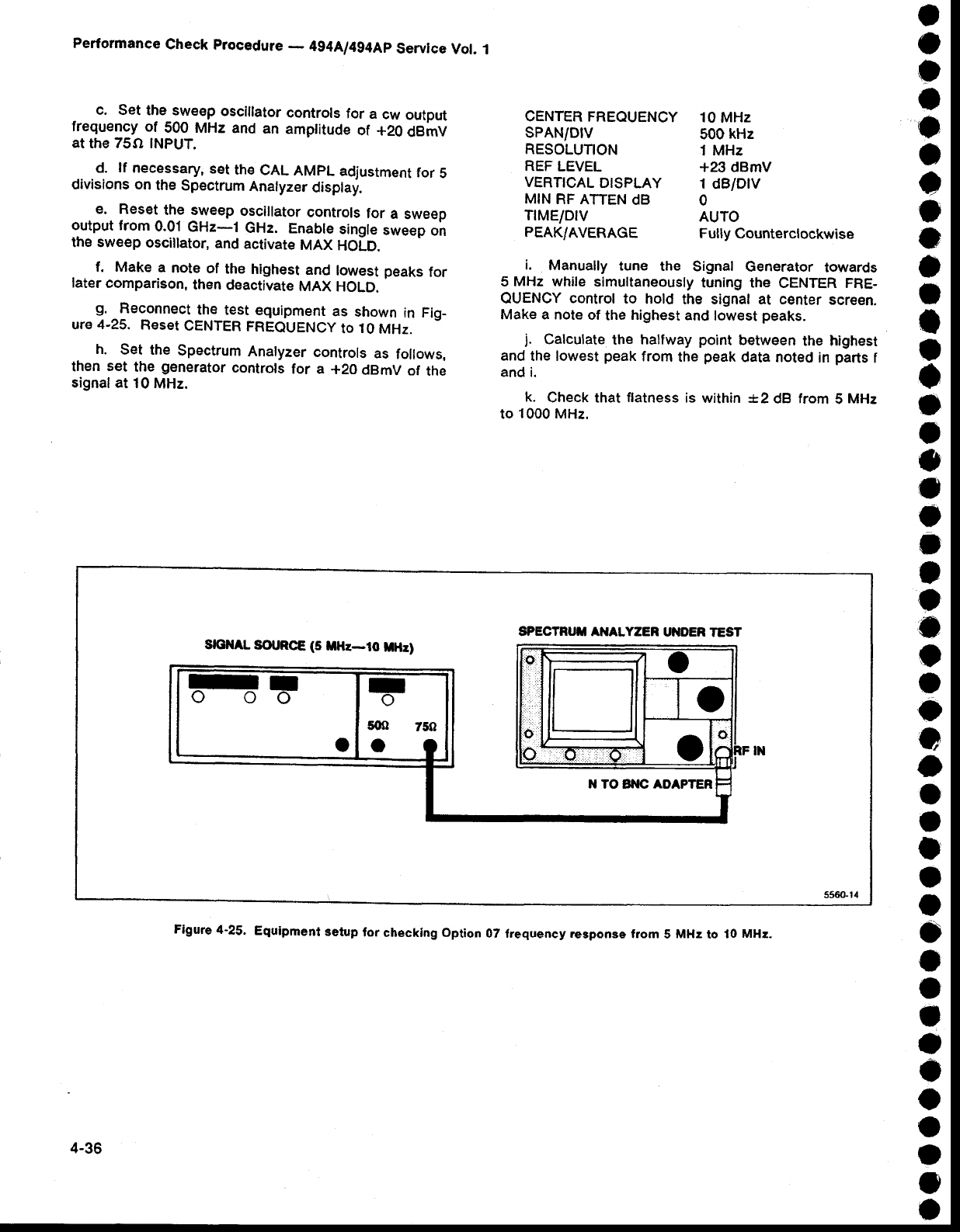

4-25 Equipment

setup for checking

Option

07 frequency response

from

5

MHz

to

10

MHz. ............ 4€6

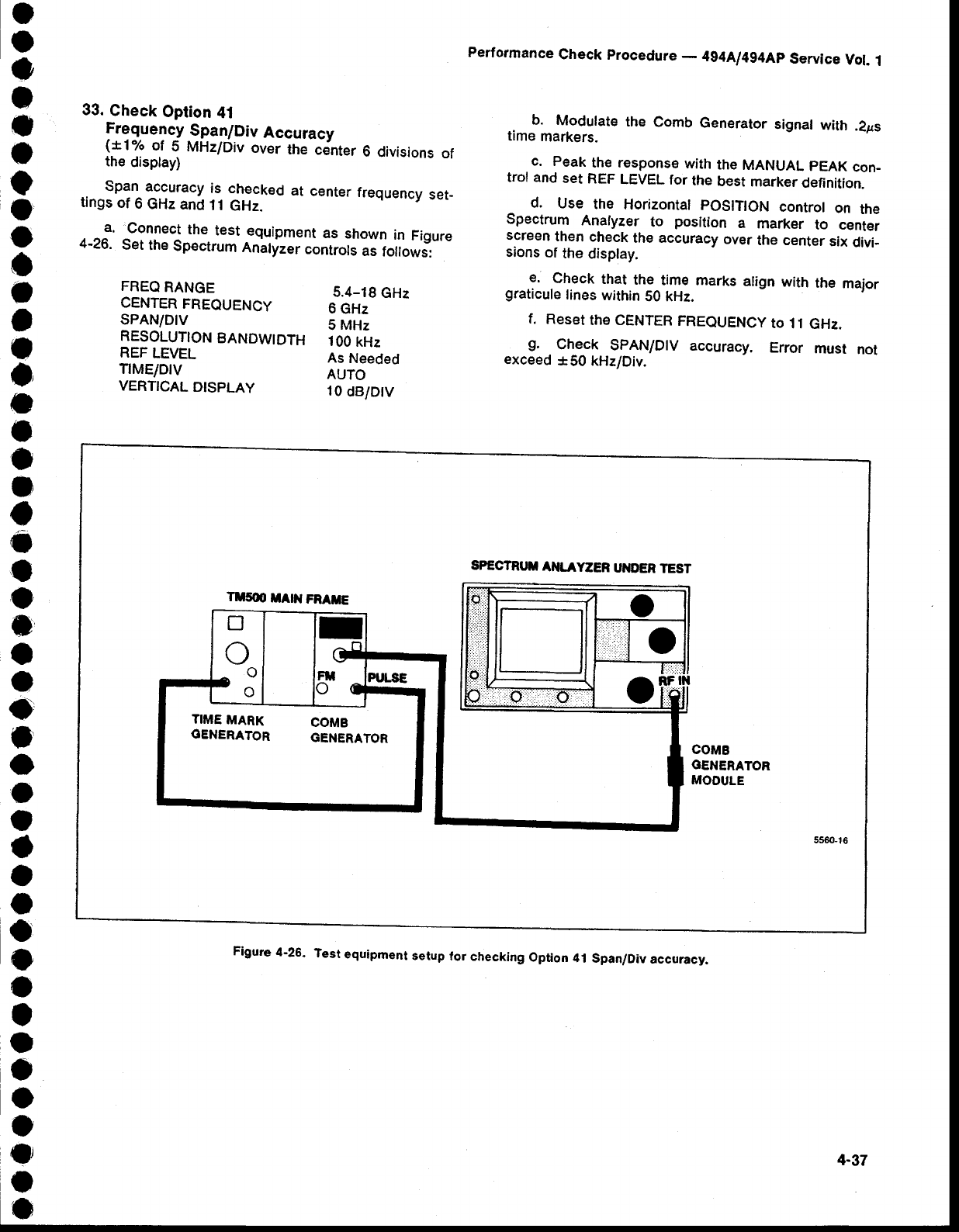

4-26 Test equipment

setup

for checking

Option 41

Span/Div

accuracy. ..

4-37

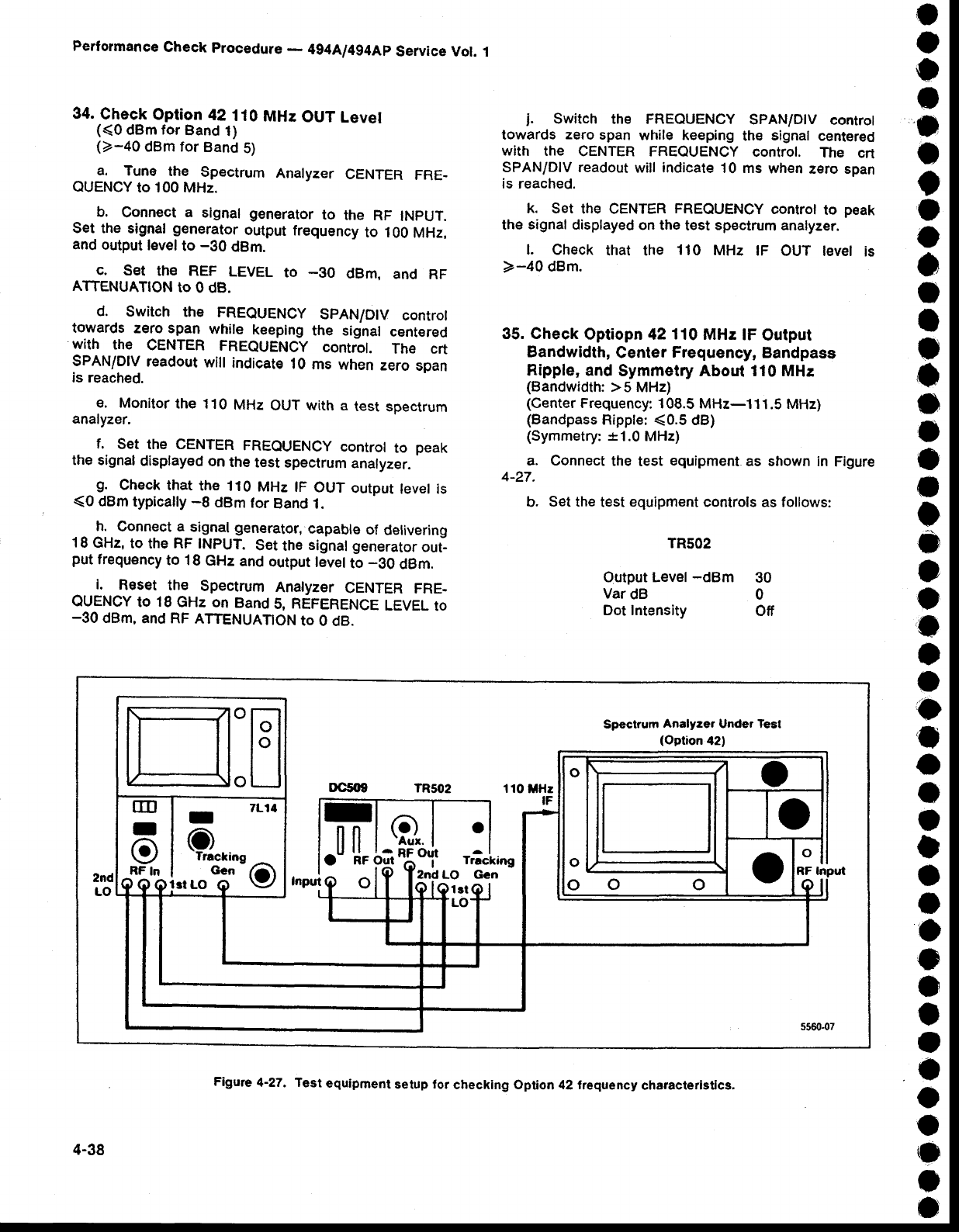

4-27 Test equipment

setup

for checking

Option

42 frequency

characteristics.

............

4-38

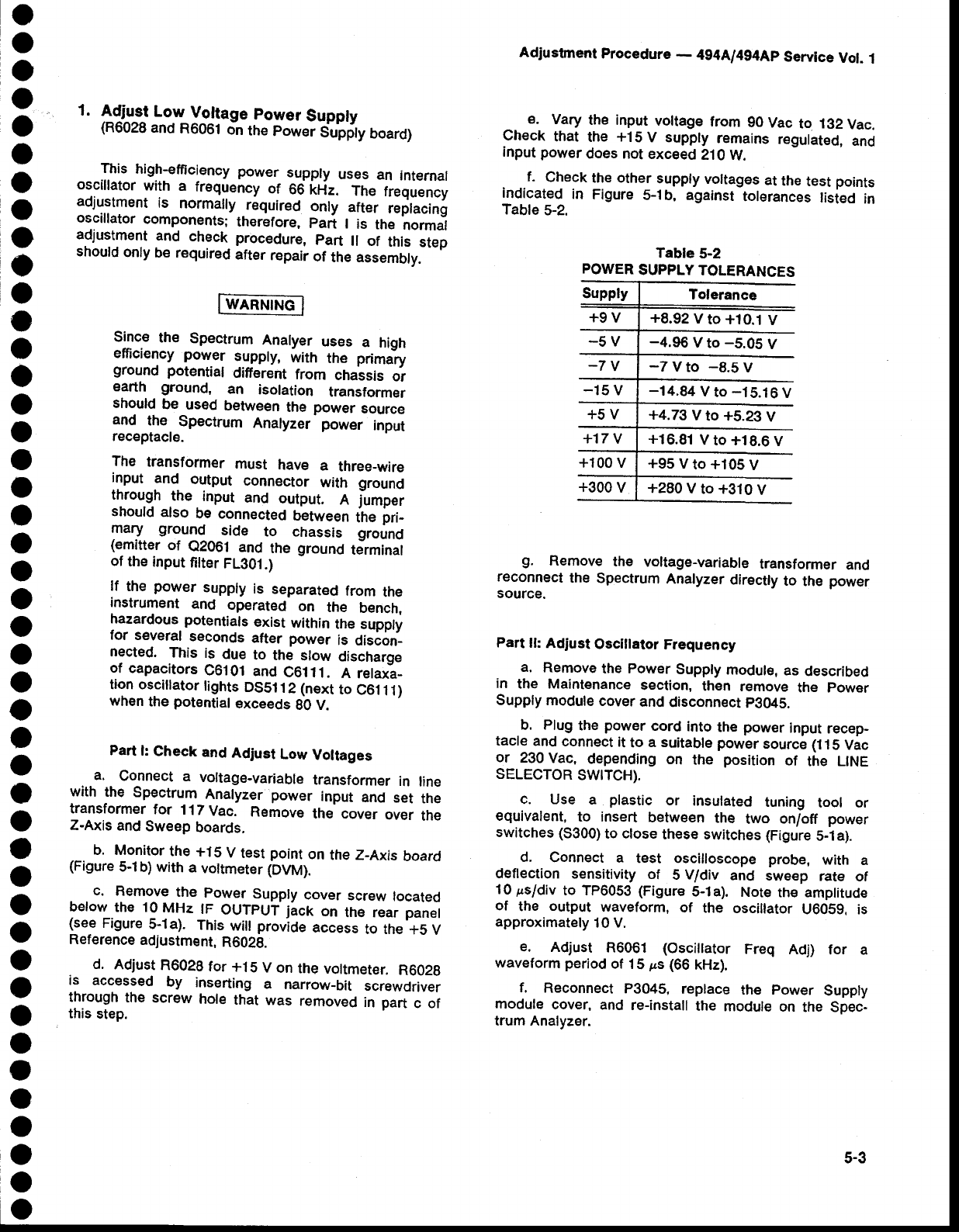

5-1 Low voltage

power

supply adiustmentsi

..................................... 5-4

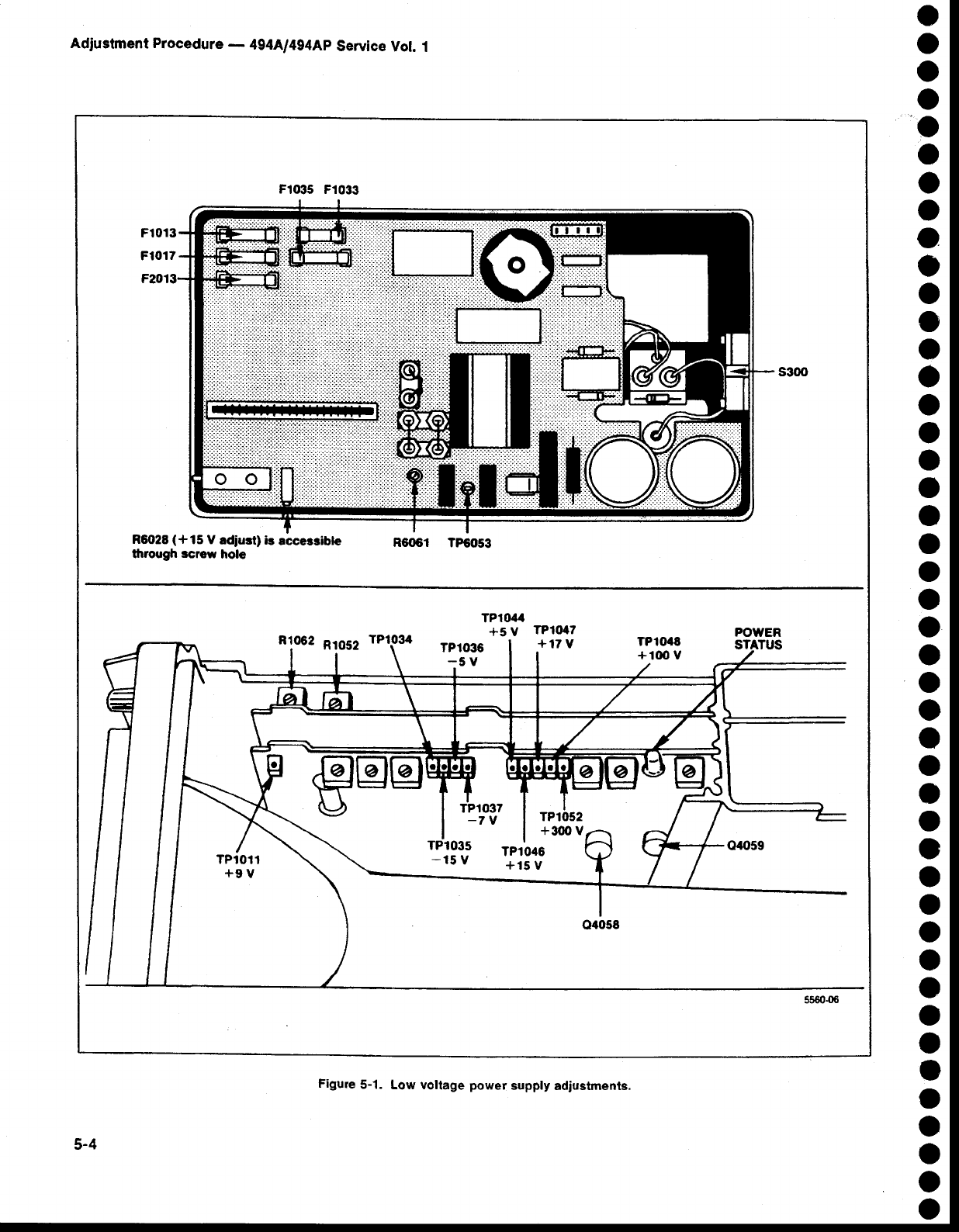

5-2 Crt display

adjustment and

test

point

locations. .................. 5-5

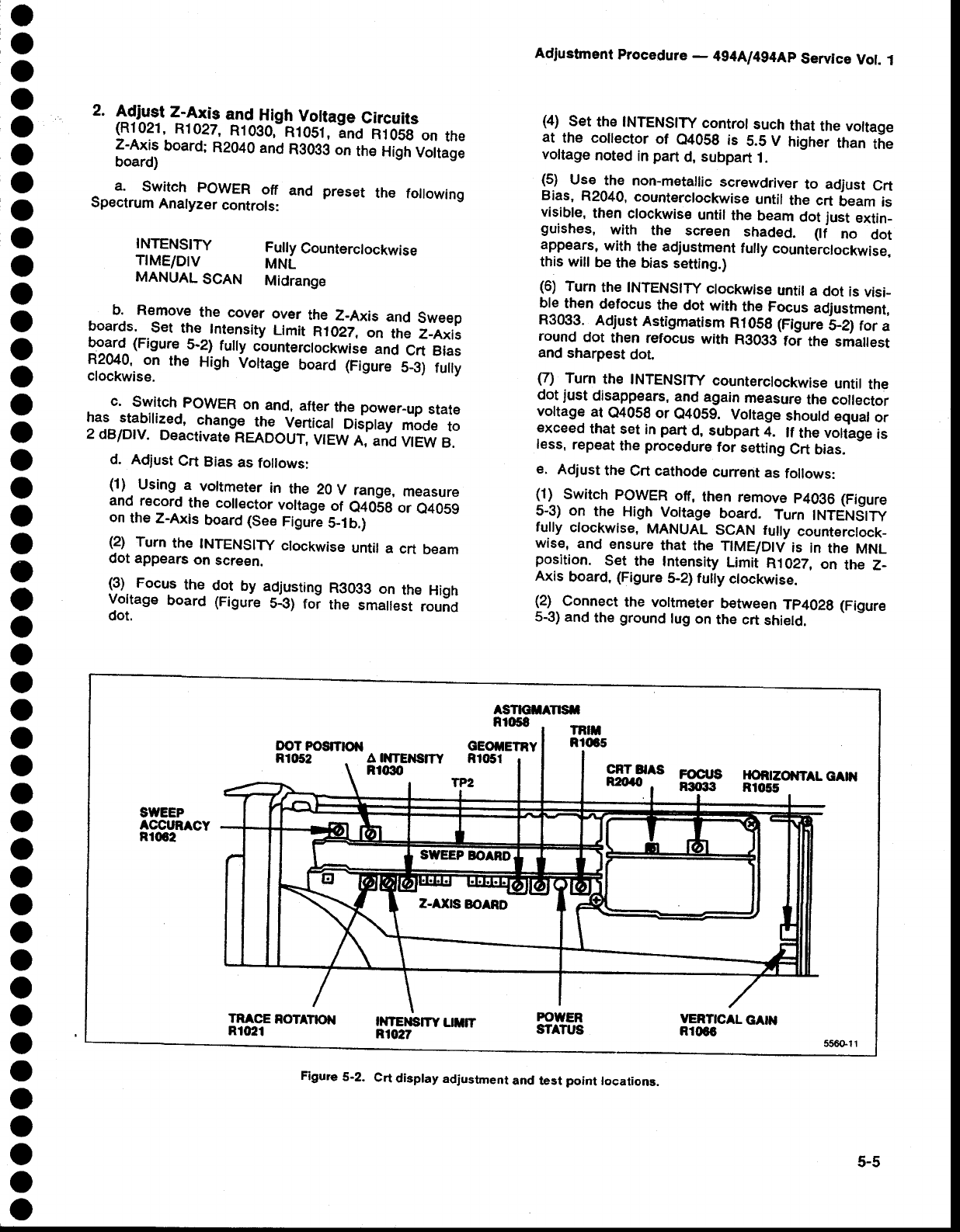

5-3 Adjustment and

test

point

locations

on High Voltage

module.

............... 5-6

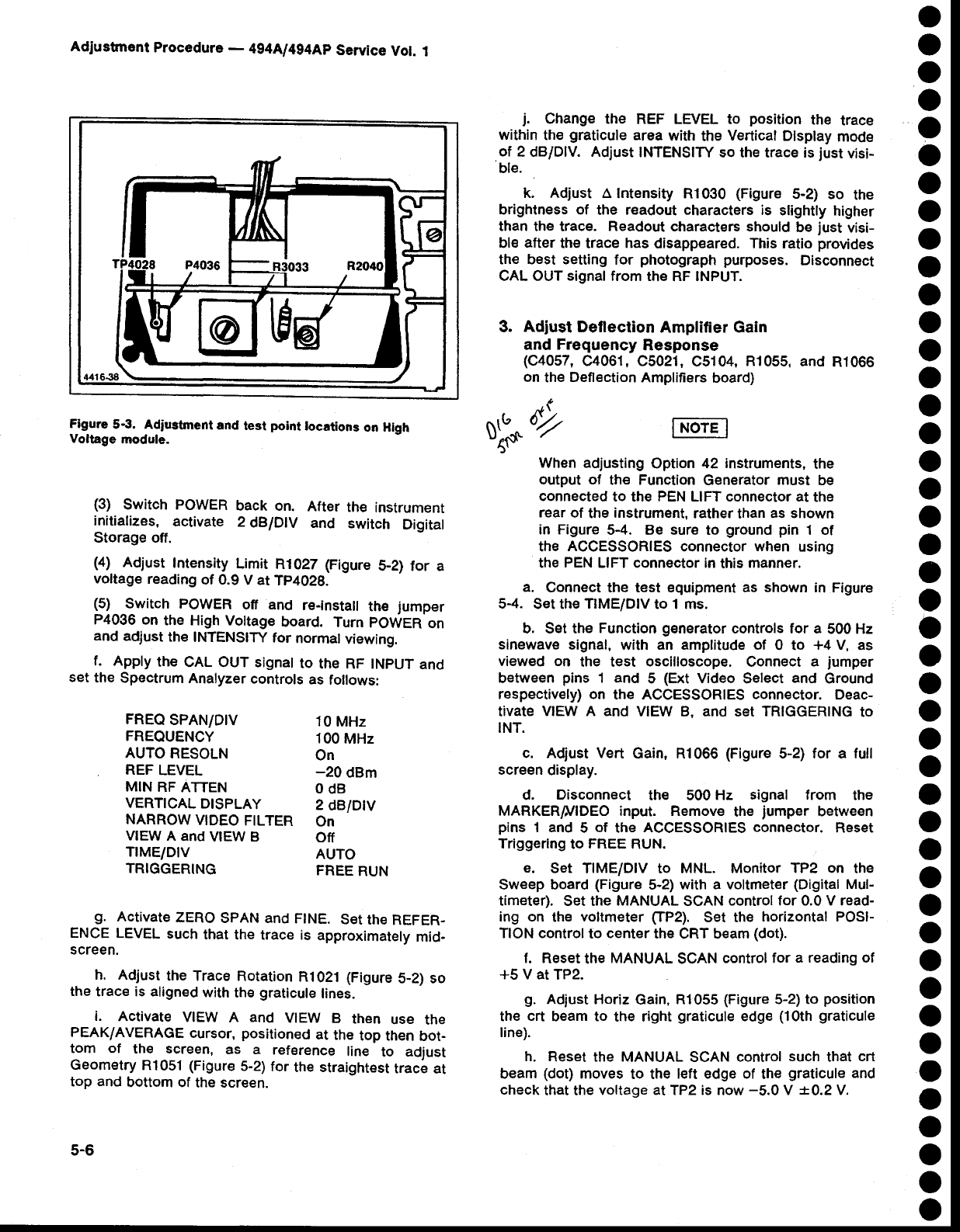

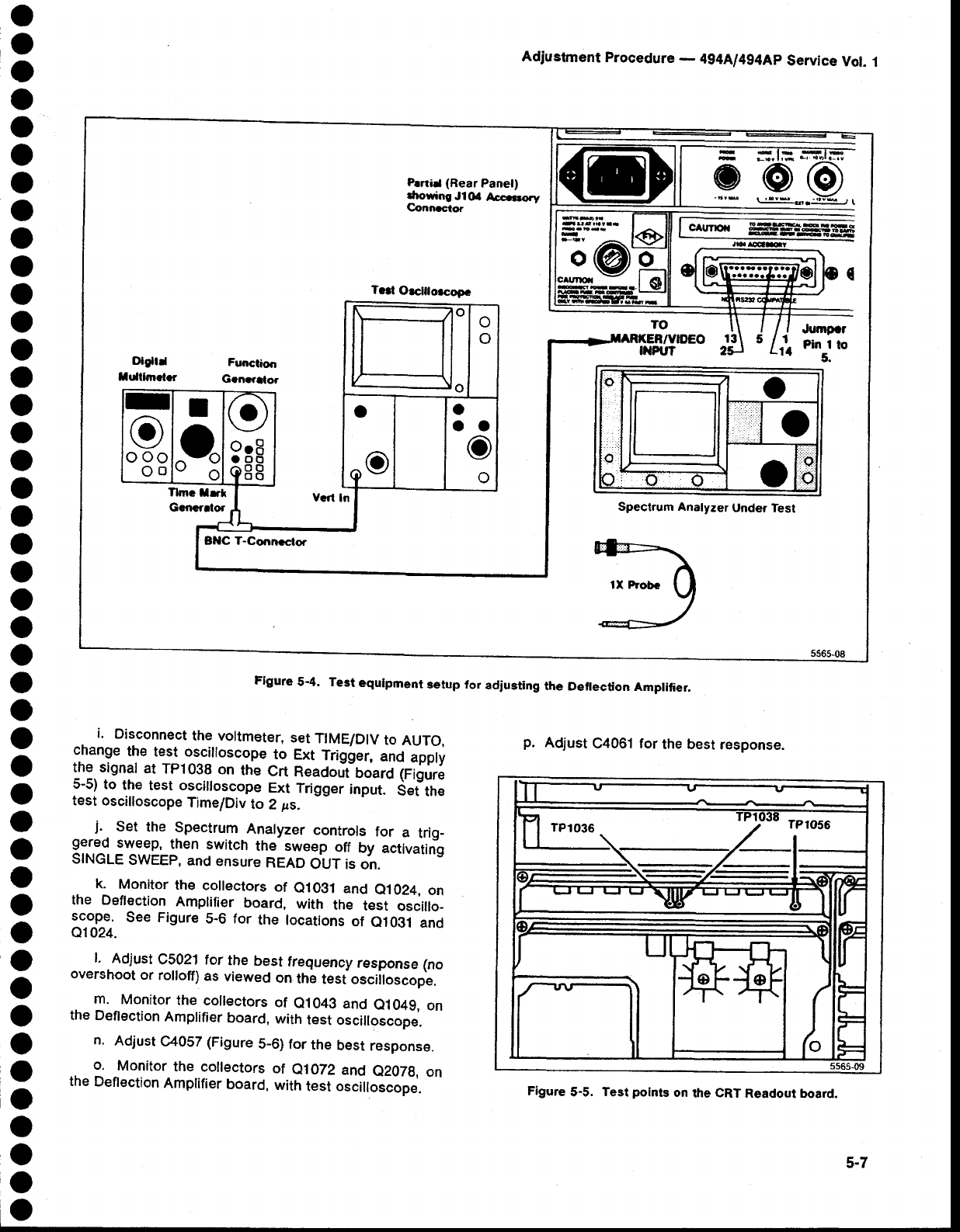

5-4 Test equiprnent setup

for

adjusting

the Deflection

Amplifier.

................ 5-7

5-5 Test

points

on

the CRT

Readout

board. .....5-7

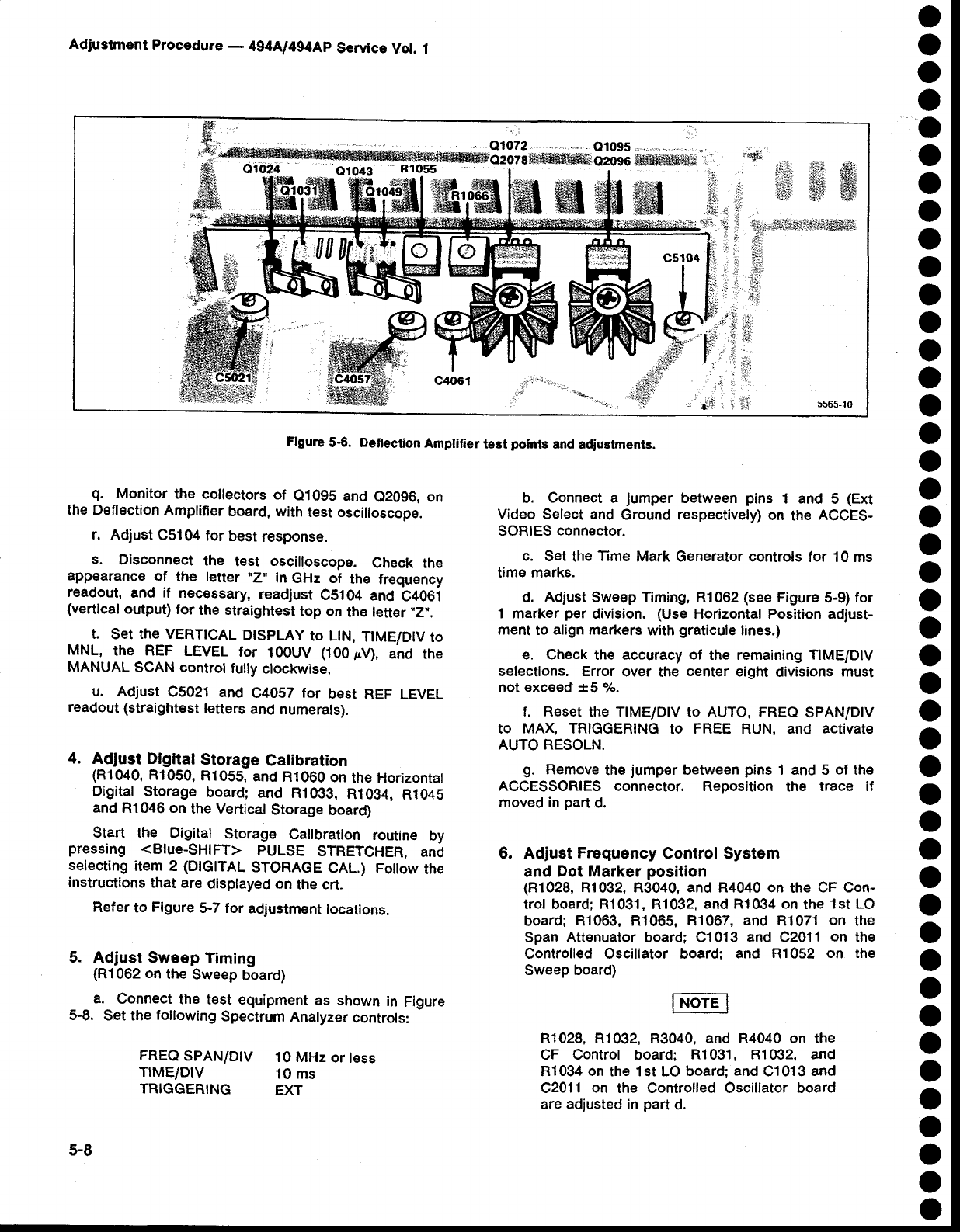

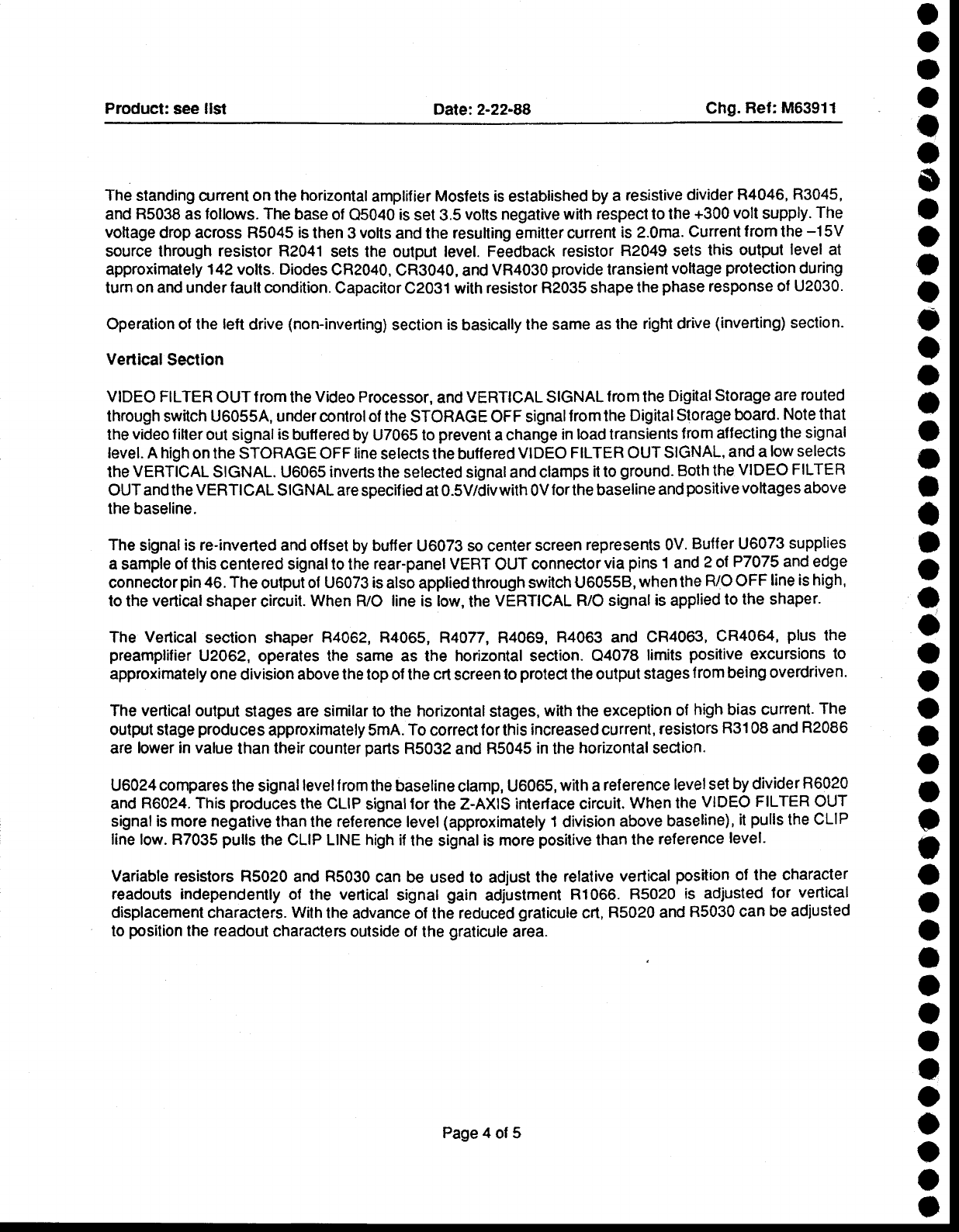

5-6 Deflection Amptifier

test

points

and

adjustments. .......... ............

5-8

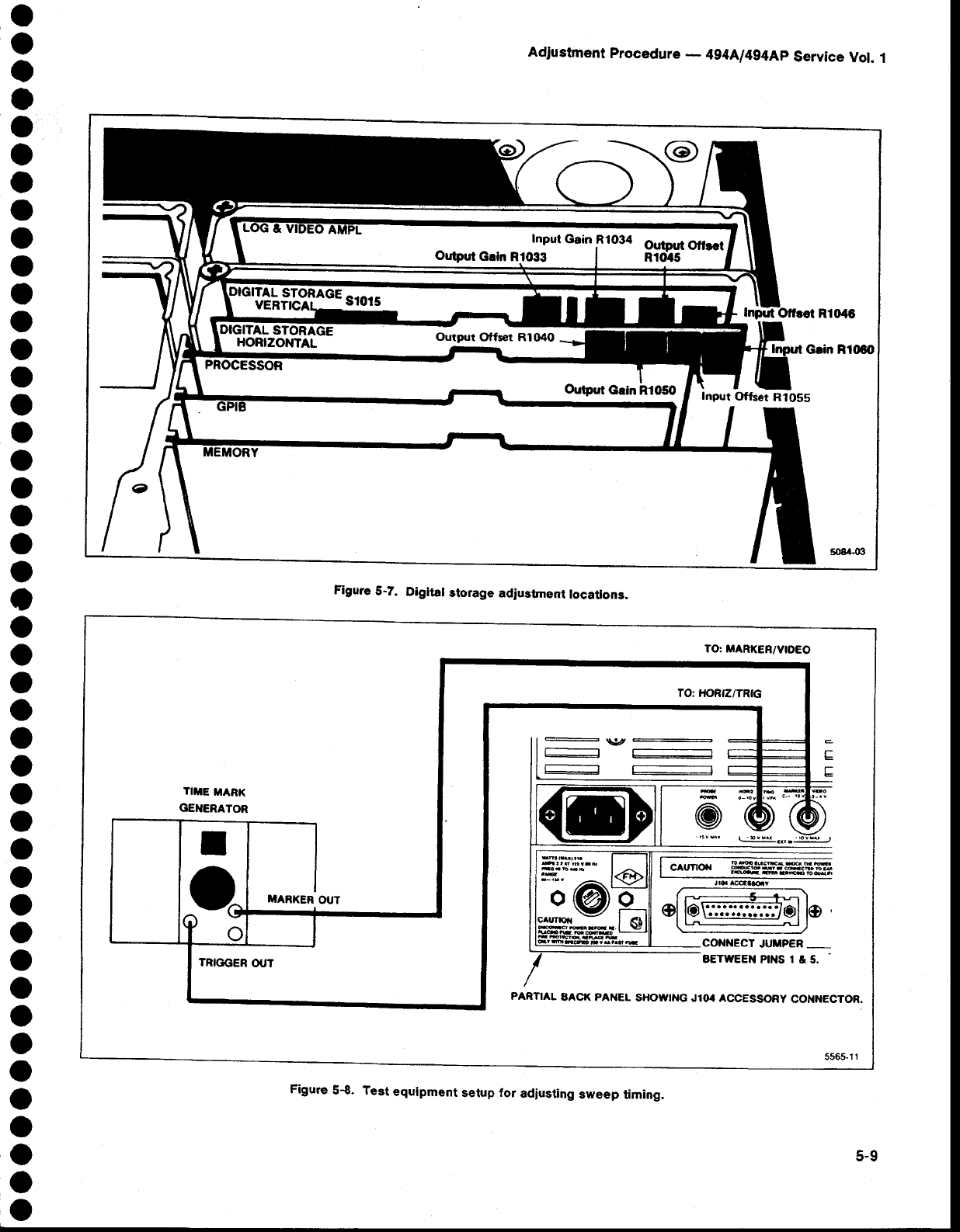

5-7 Digital storage adjustment

locations. .........,.... 5-9

5-8 Test

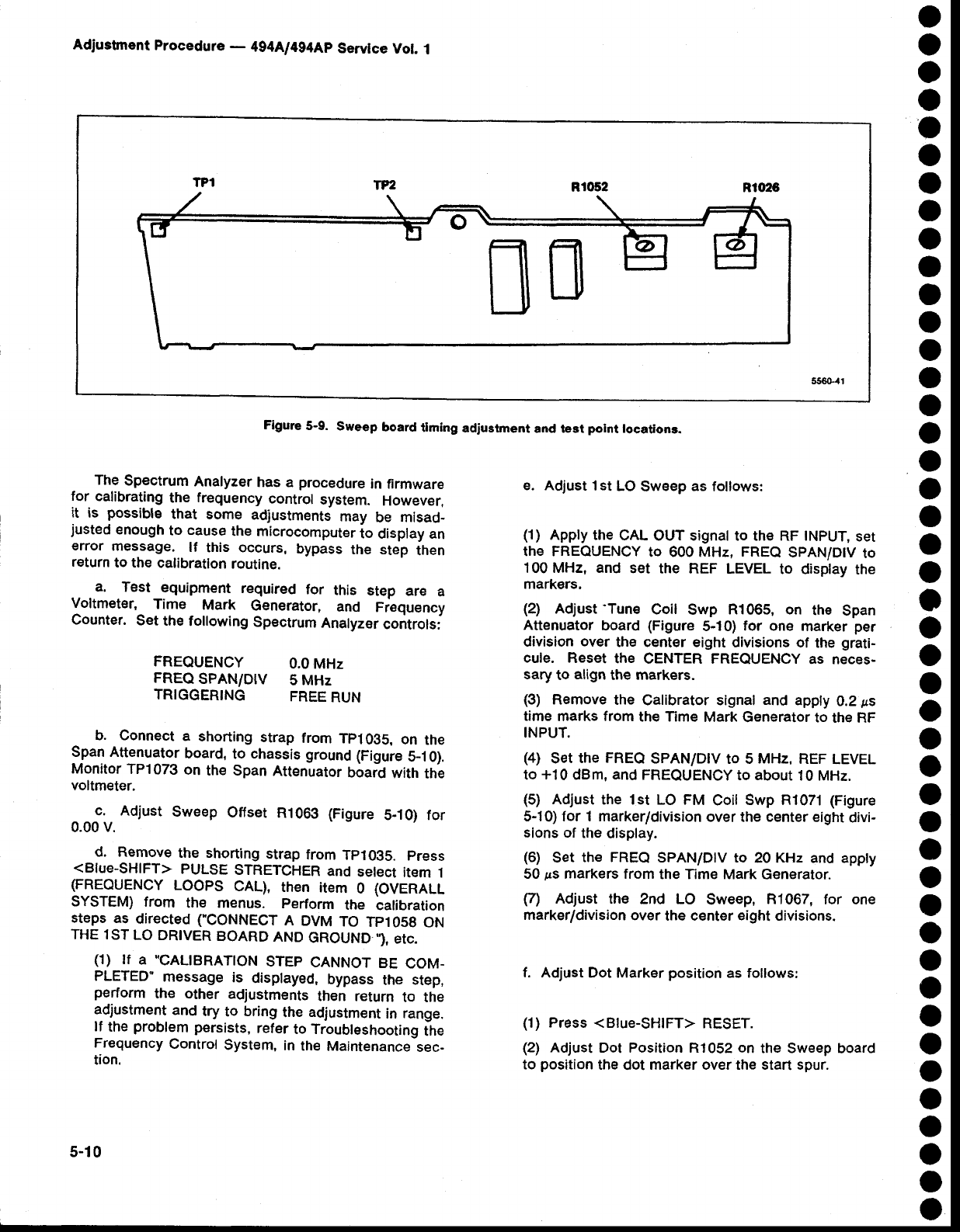

equipment setup

for

adjusting sweep timing. ............ 5-9

5-9 Sweep board timing adjustment

and

test

point

locations.

............................... 5-10

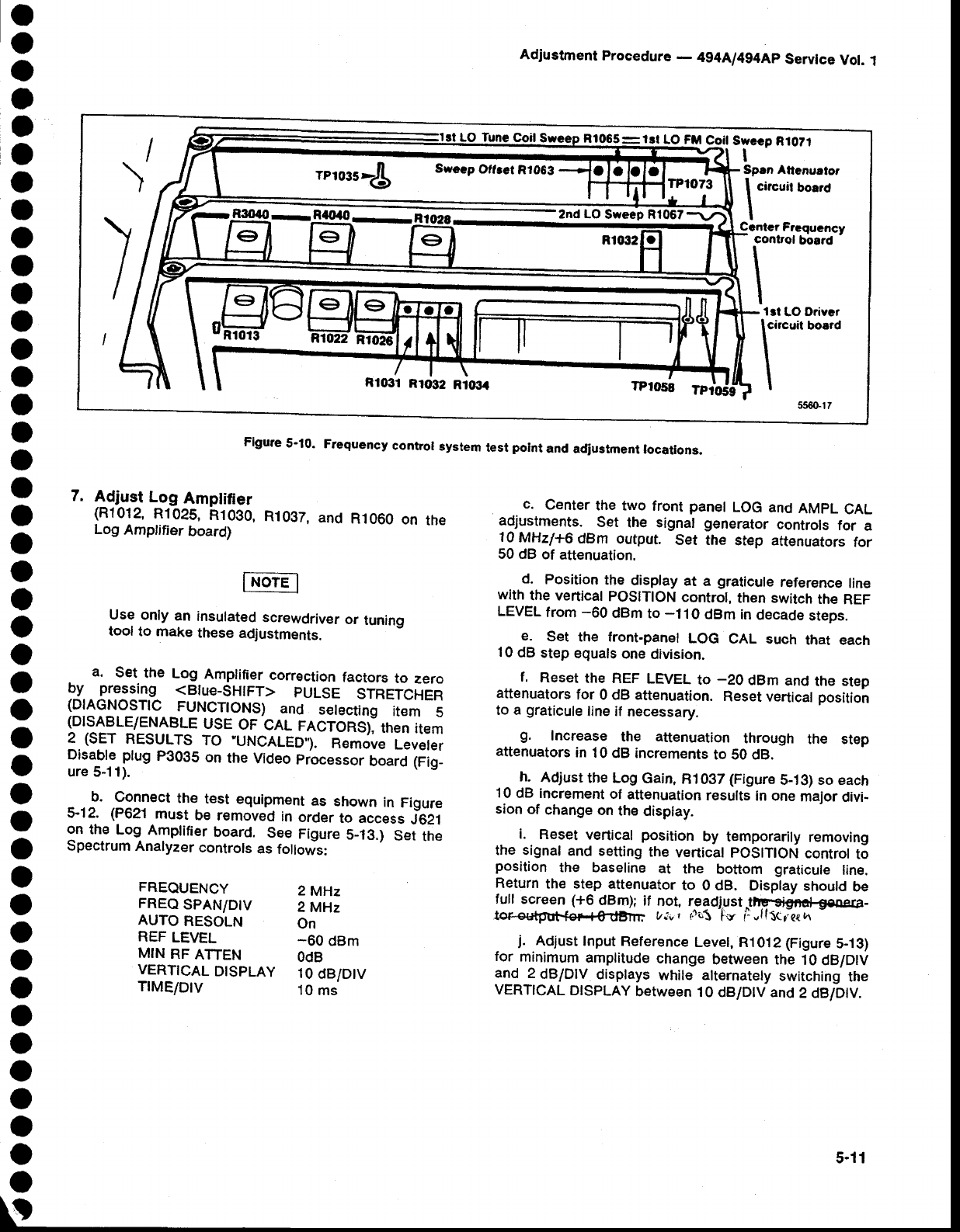

5-10 Frequency

control system test

point

and adjustment

locations.

................... 5-11

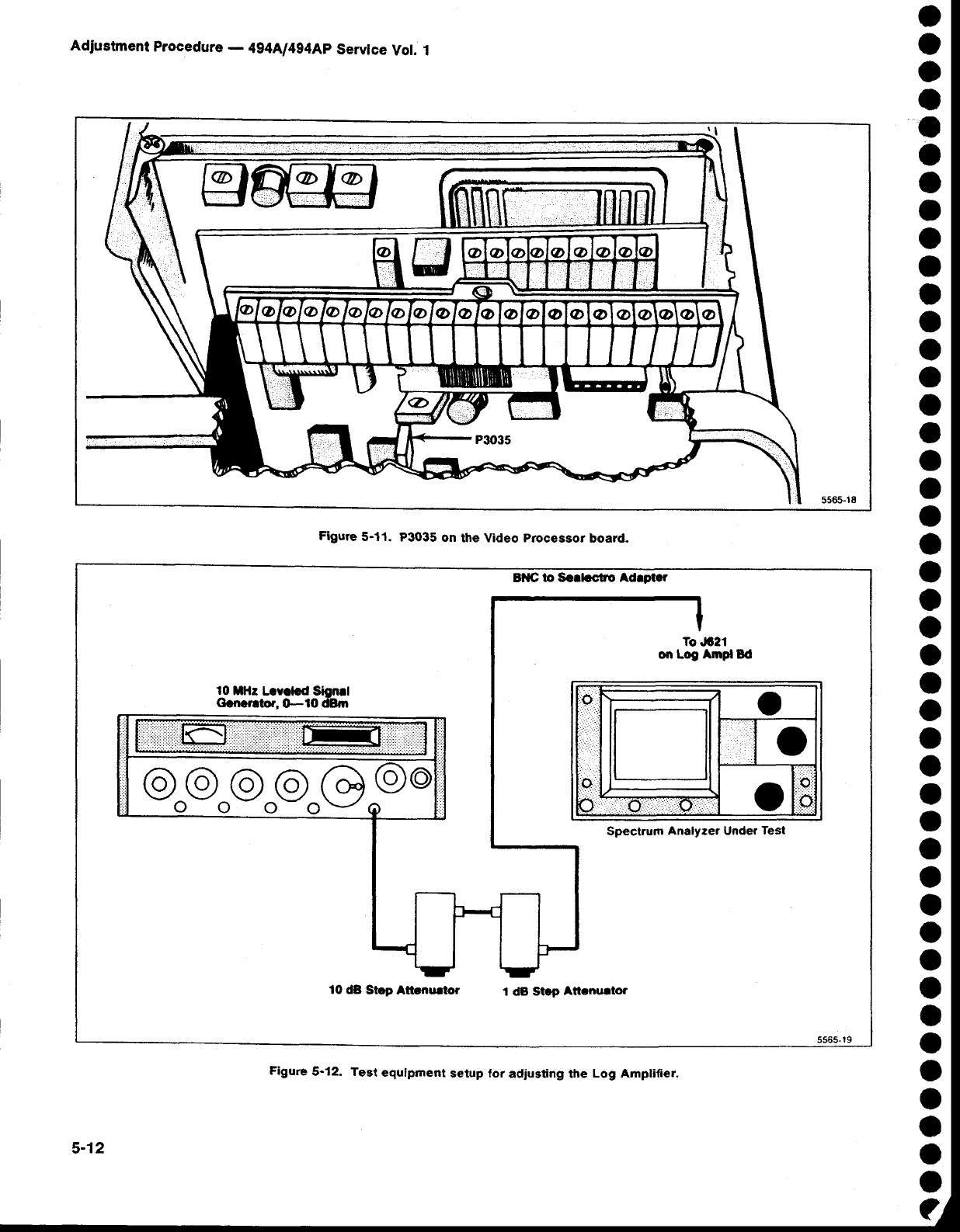

5-11 P3035

on

the Video Processor board.

......... 5-12

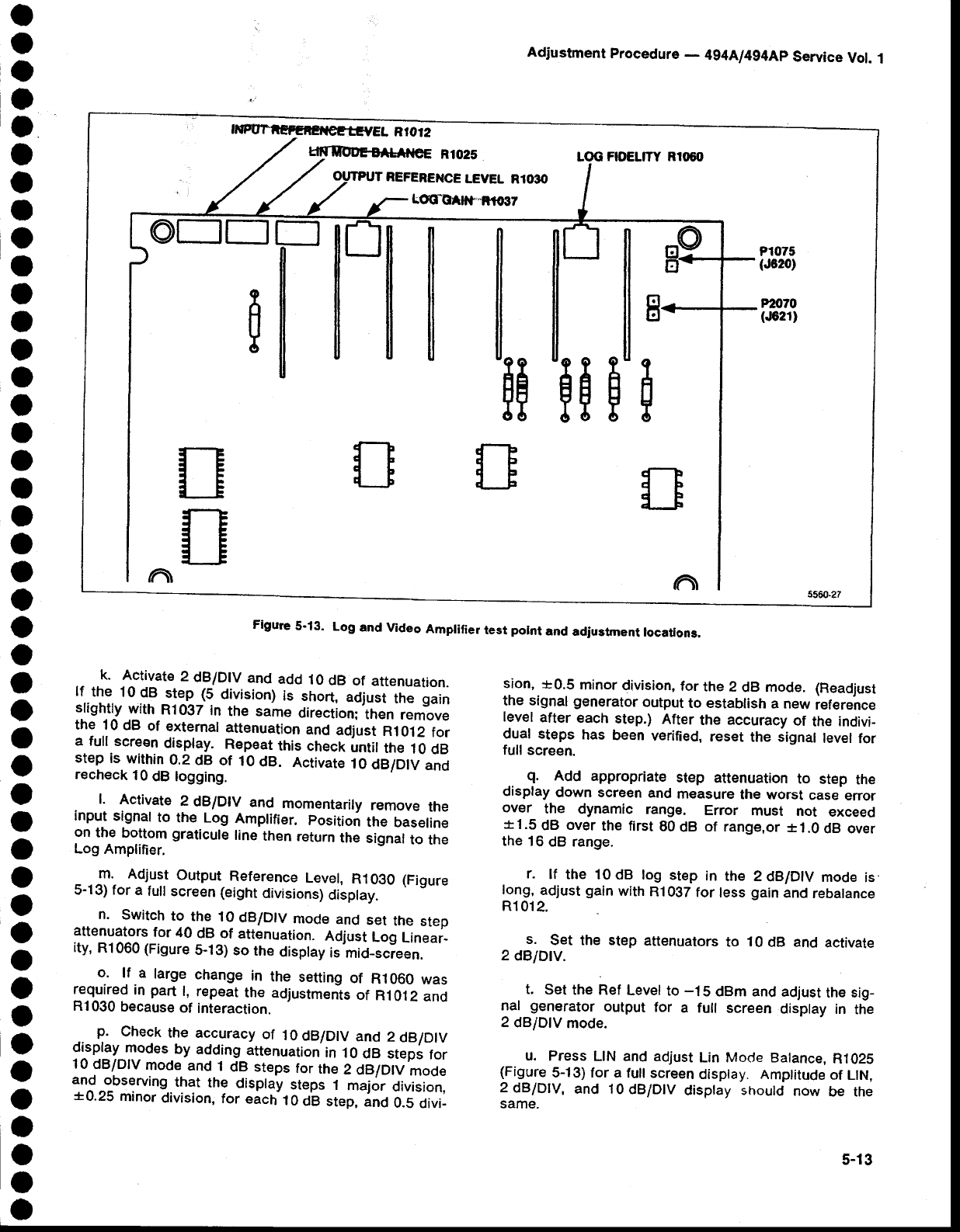

5-12 Test

equipment setup for adjusting

the Log Amplifier. ..................... 5-12

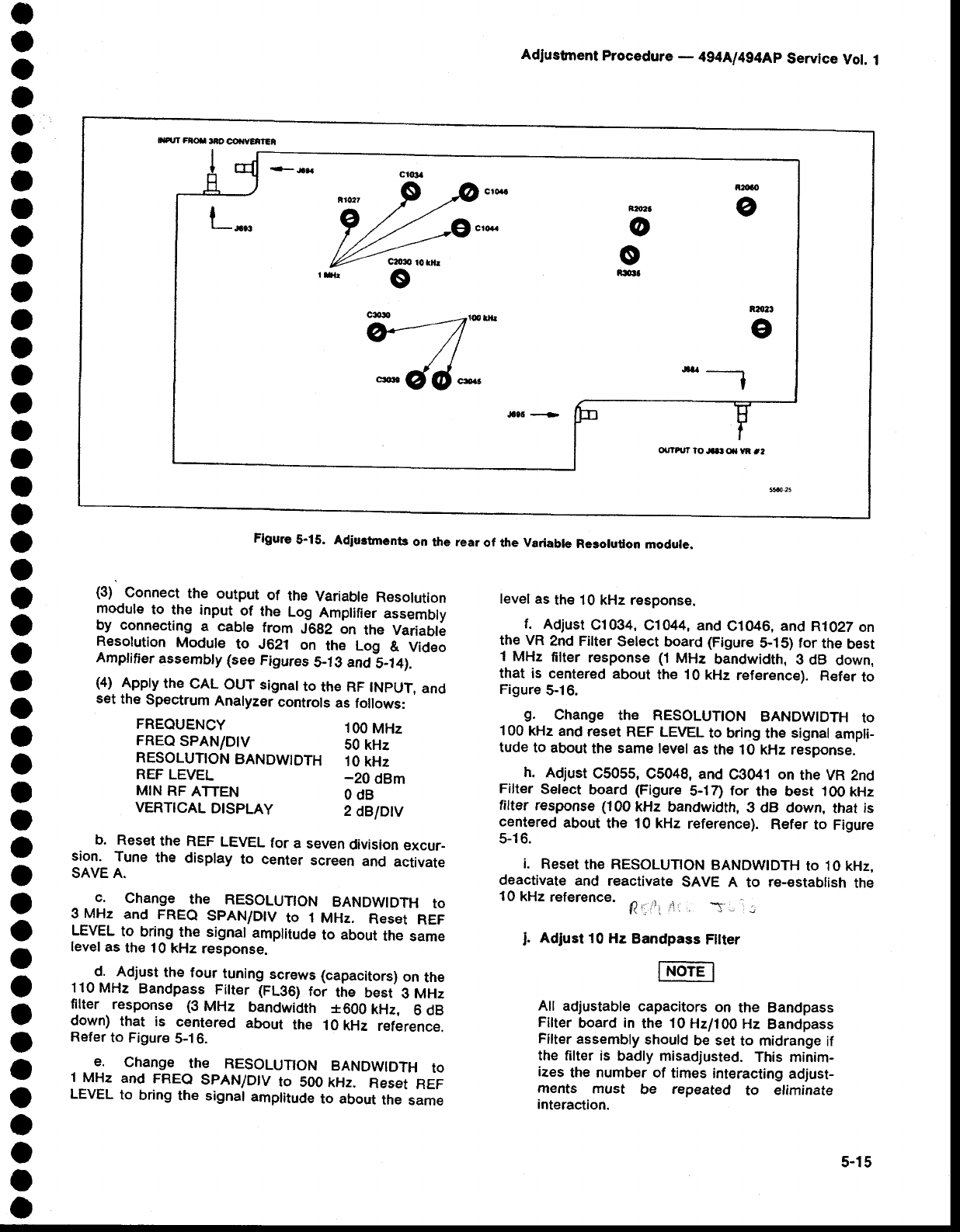

5-13 Log and Video Amplifier test

point

and adjustment locations ........... 5-13

5-14 Test equipment

setup for adjusting

the

Variabl€ Resolution

module. ..........,.......,

5-14

5-1 5 Adjustments

on

the

rear

of the

Variable Resolution

module. ..... 5-15

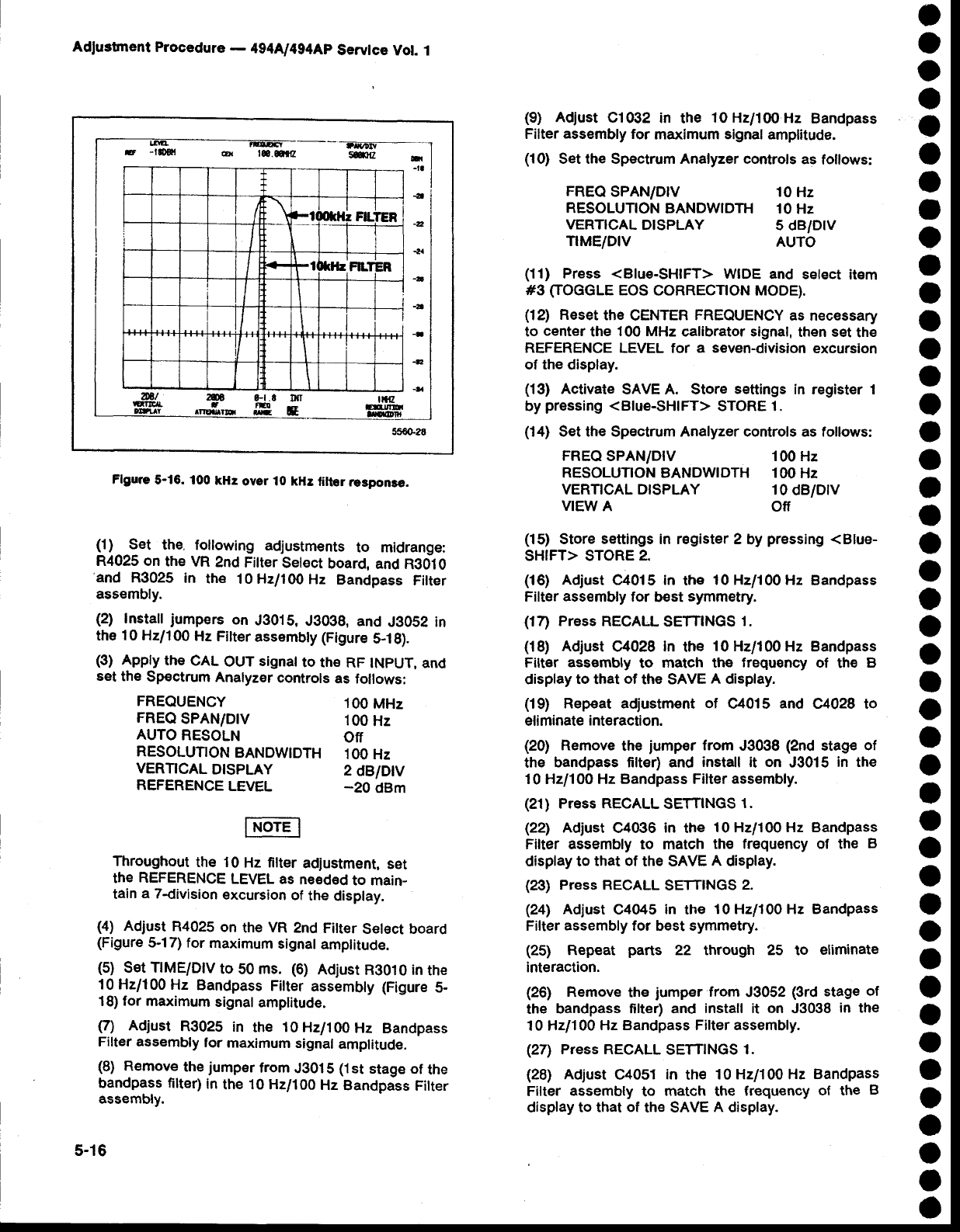

5-16 100 kHz over 10 kHz

filter

response. ........... 5-16

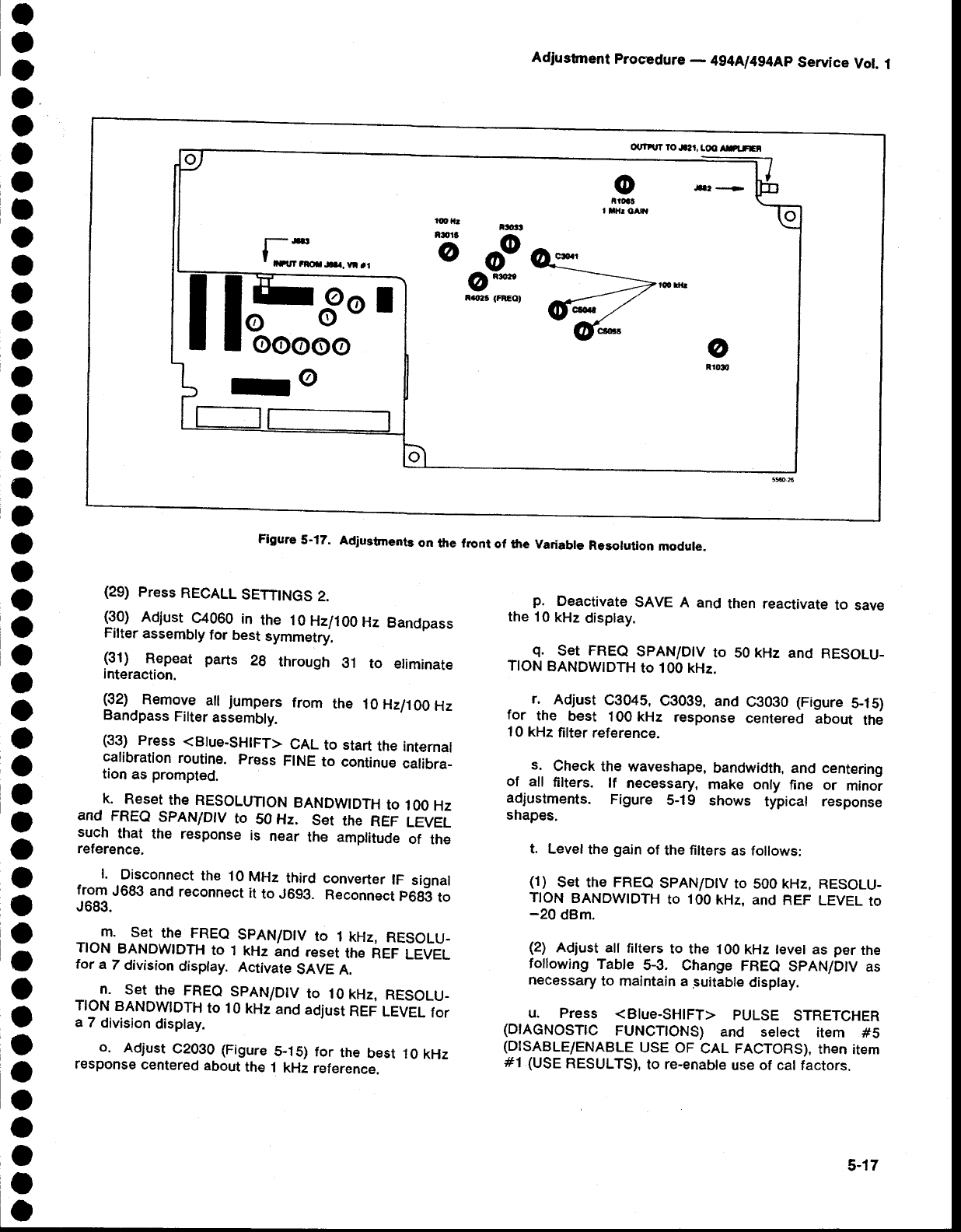

5-17 Adjustments

on

the

tront

of the

Variable

Resolution

module. .....

5-18

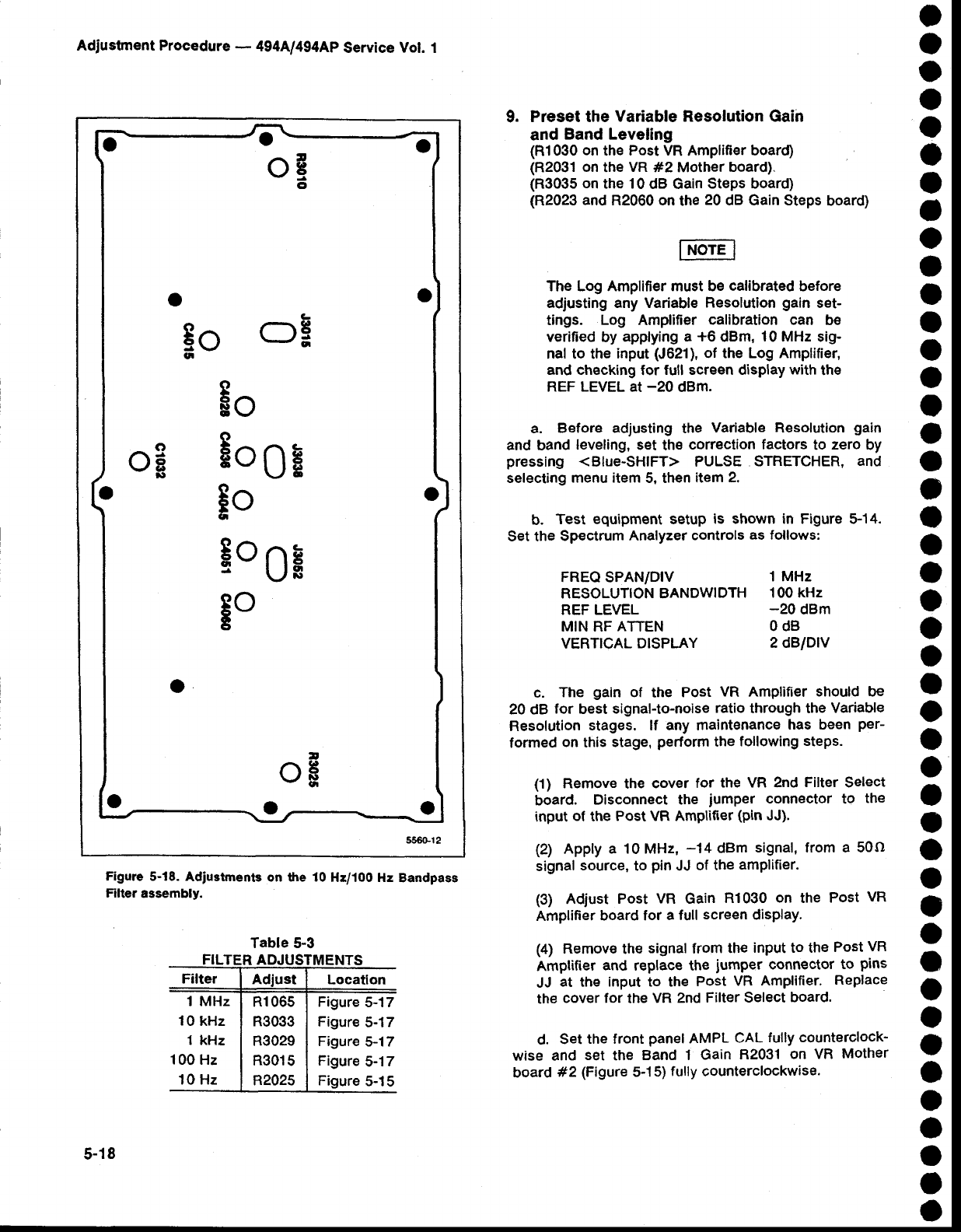

5-18 Adjustments

on

the 10

Hzl'|00 Hz

Bandpass Filter Assembly.

...........................

5-18

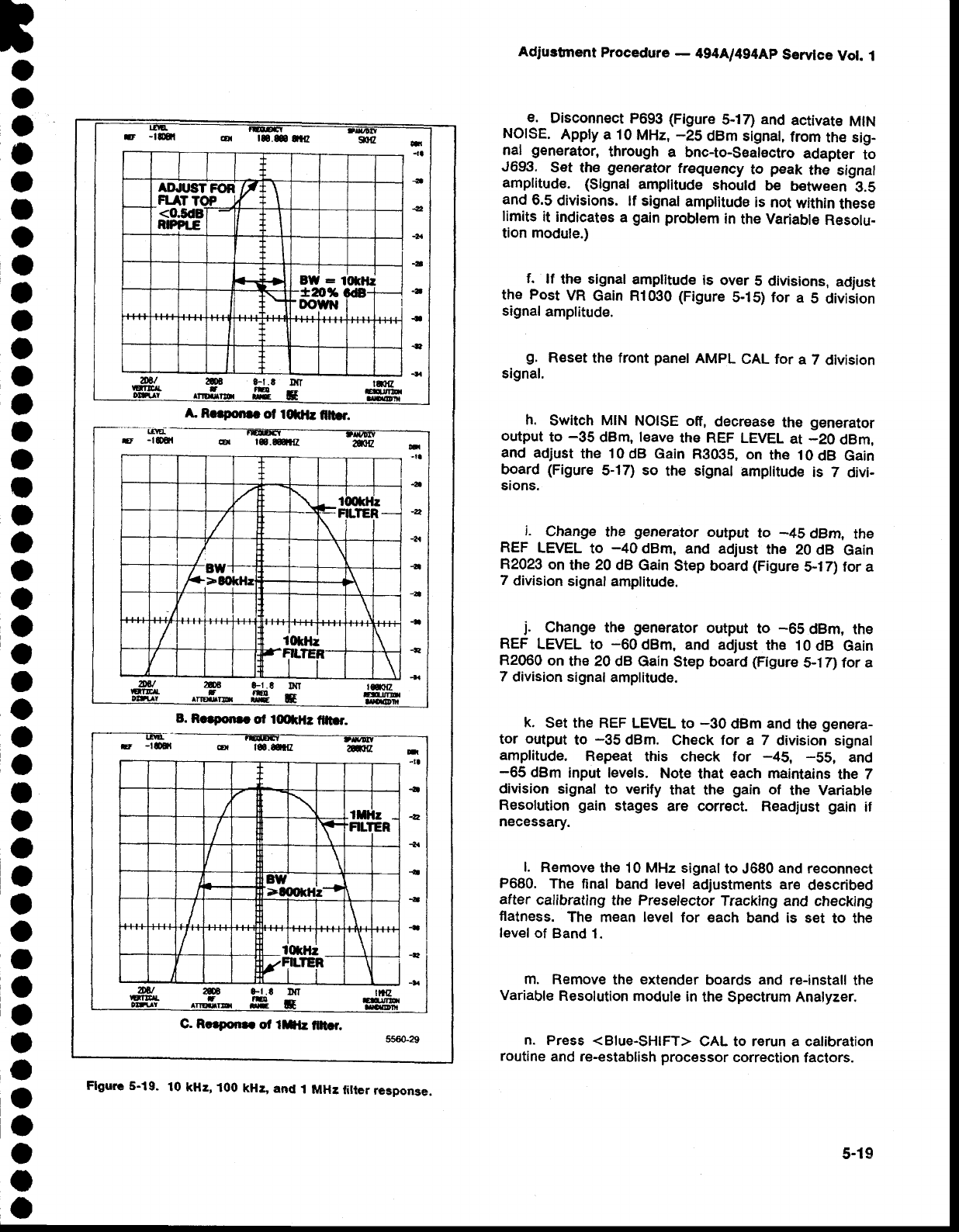

5-19 10

kHz, 100

kHz, and

1 MHz filter

response.

....,.............................

5-1

I

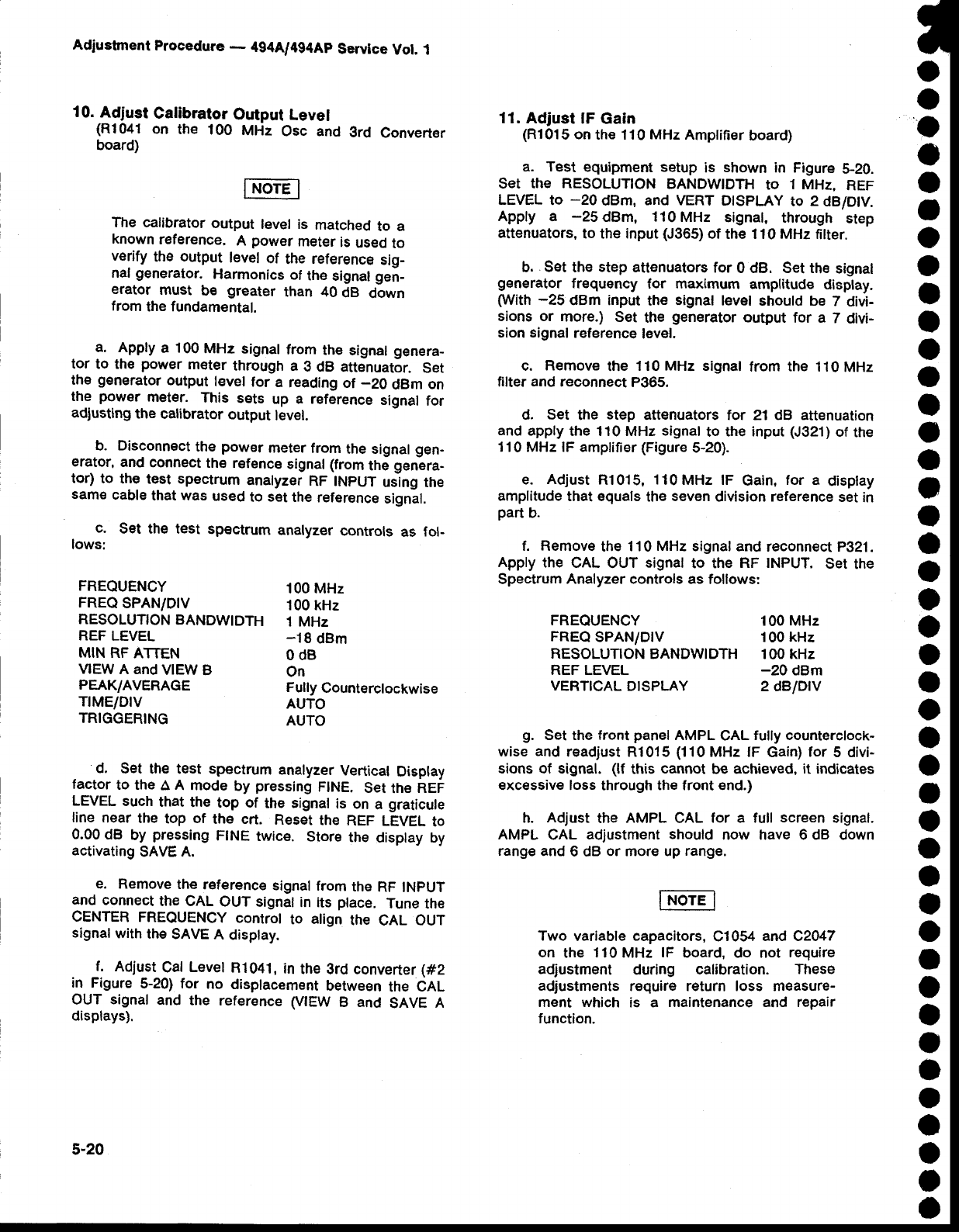

5-20 lF

gain

test

setup, and

adiustment

and connector

locations. ..........

5-21

LIST

OF

ILLUSTRATIONS

I

a

o

o

t

t

a

a

o

o

o

I

o

I

o

t

o

o

o

I

a

a

o

o

o

o

I

o

o

I

I

o

I

O

t

o

a

a

O

o

o

o

o

o

LIST

OF

ILLUSTRATIONS

(Conr.)

Page Flgure

I

o

o

a

o

I

I

o

o

a

I

a

t

o

I

I

o

t

o

o

I

t

o

a

o

o

a

o

I

I

a

o

o

o

I

o

I

o

a

o

o

o

o

I

494A/494AP

Servtce

Vot.

1

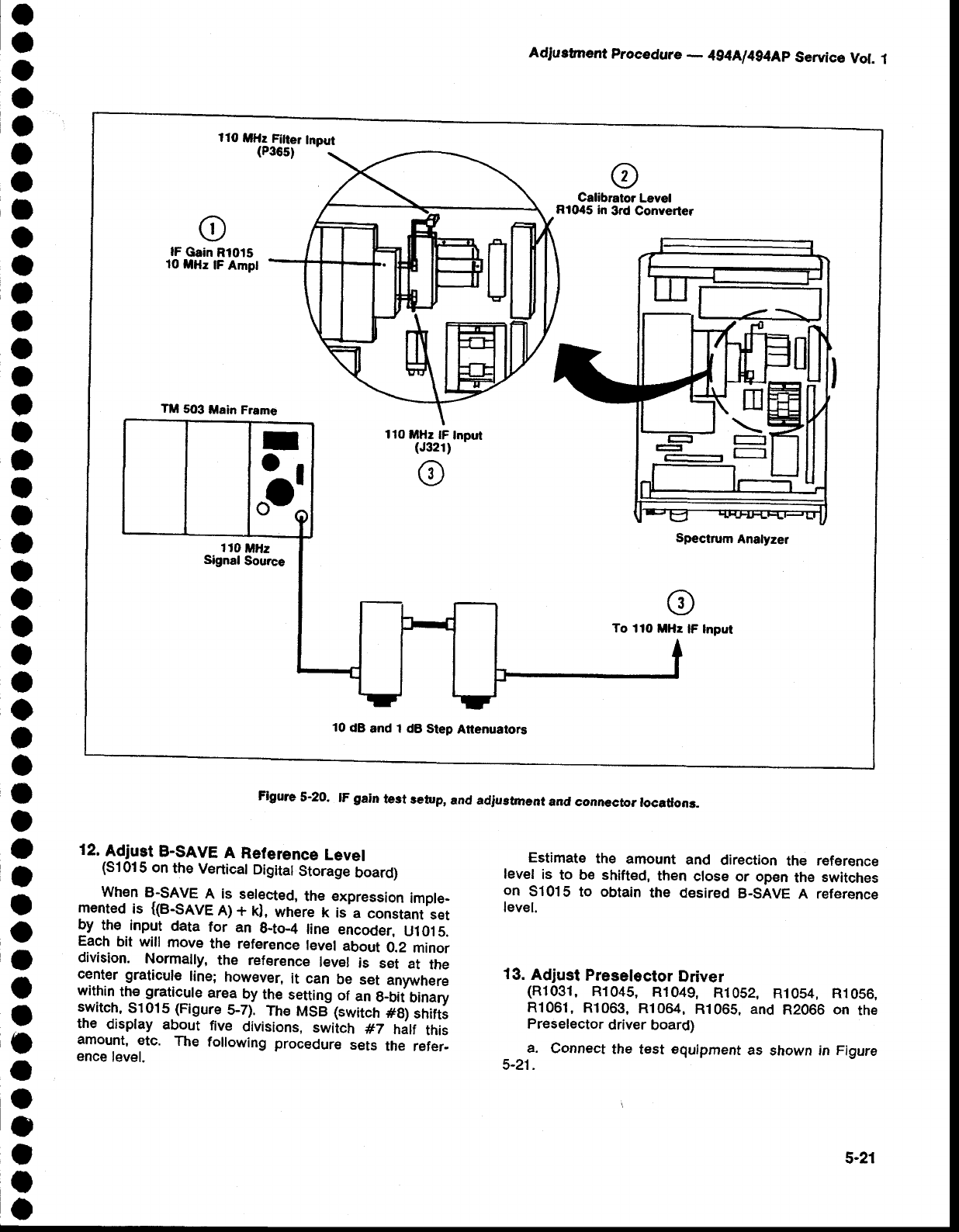

Figure

5-21 PreseleetorDriver

adjustment

setup.

......... ............5_22

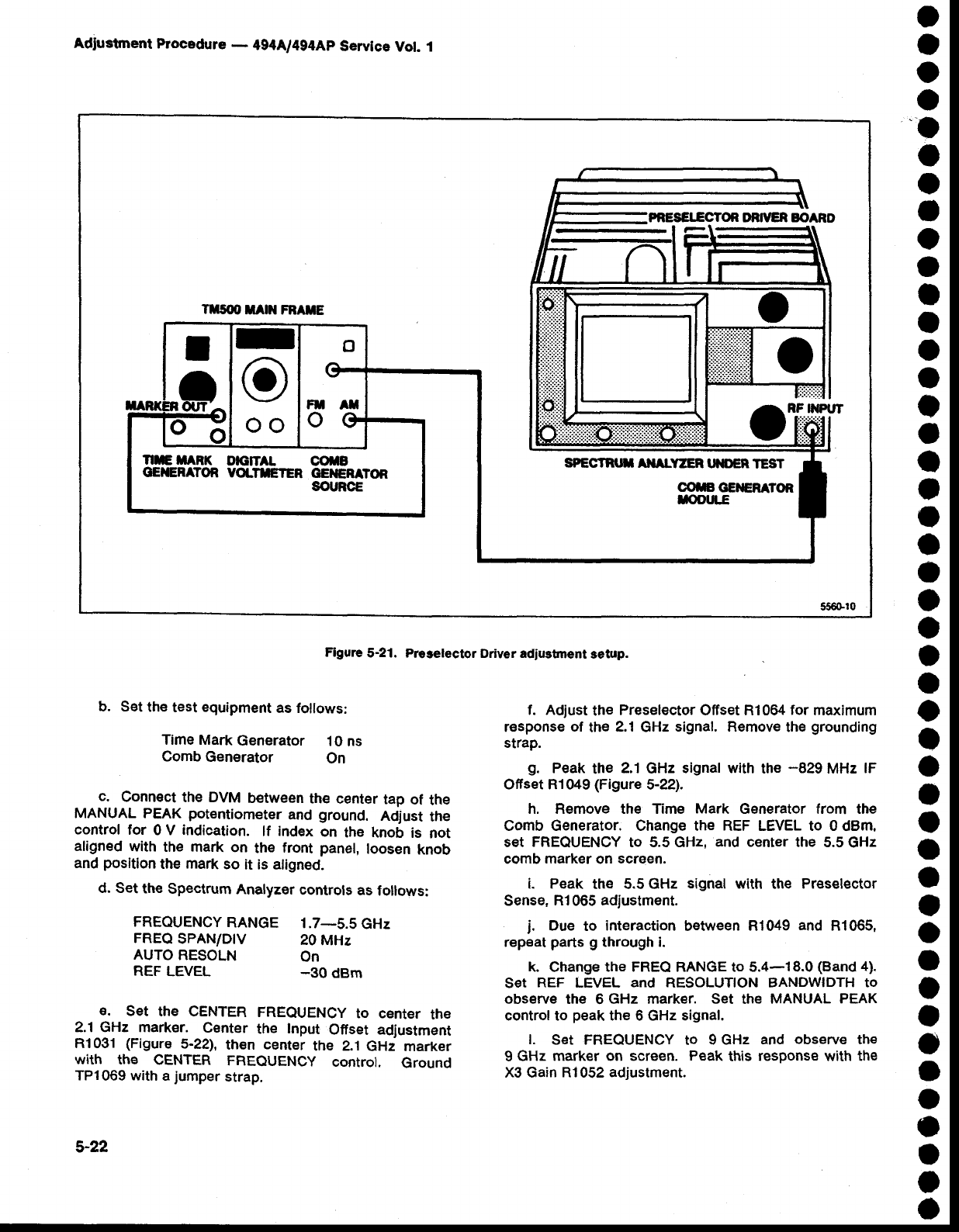

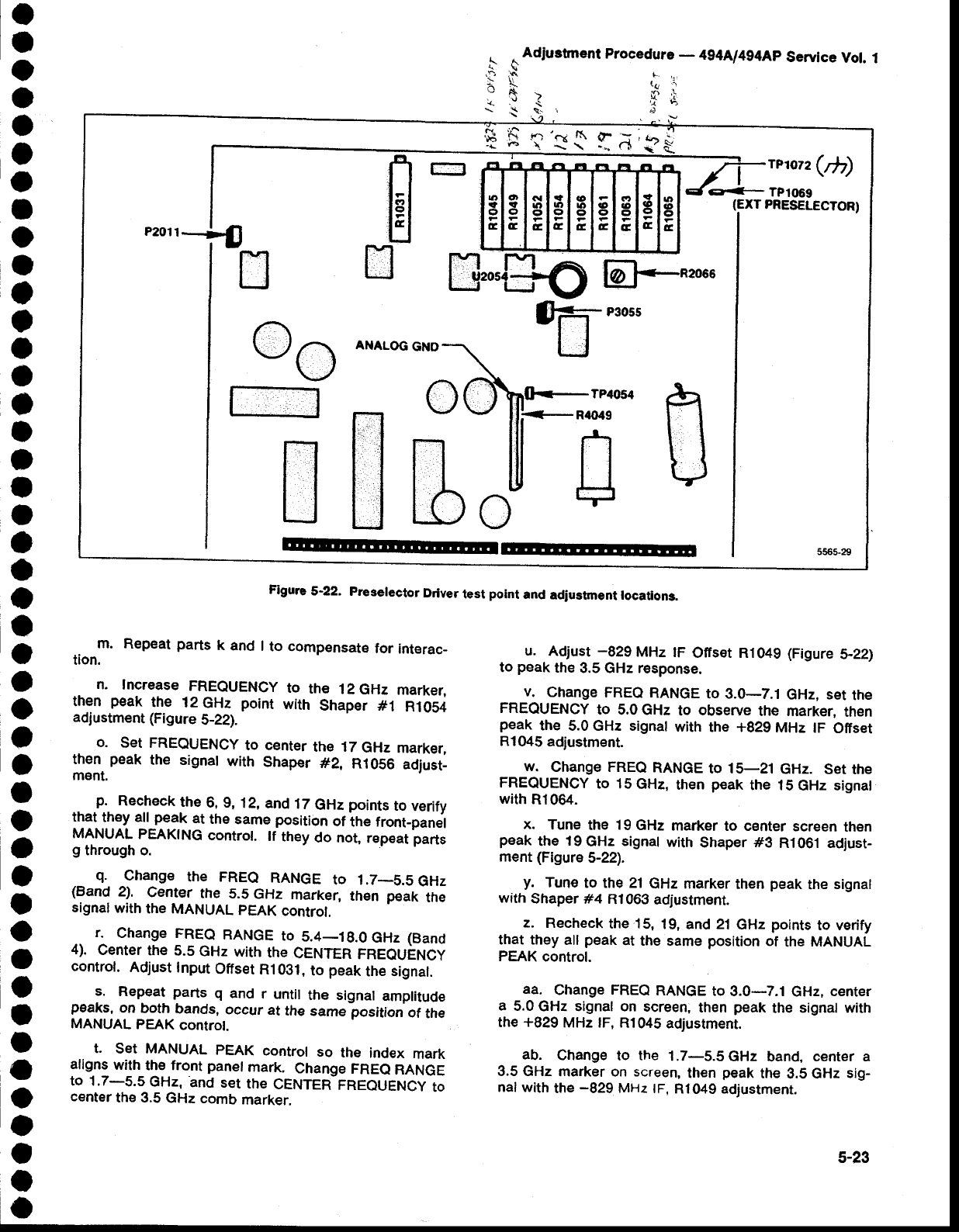

5-22 Preselector

Driver

test

point

and

adjustment

locations ...........

S_Zg

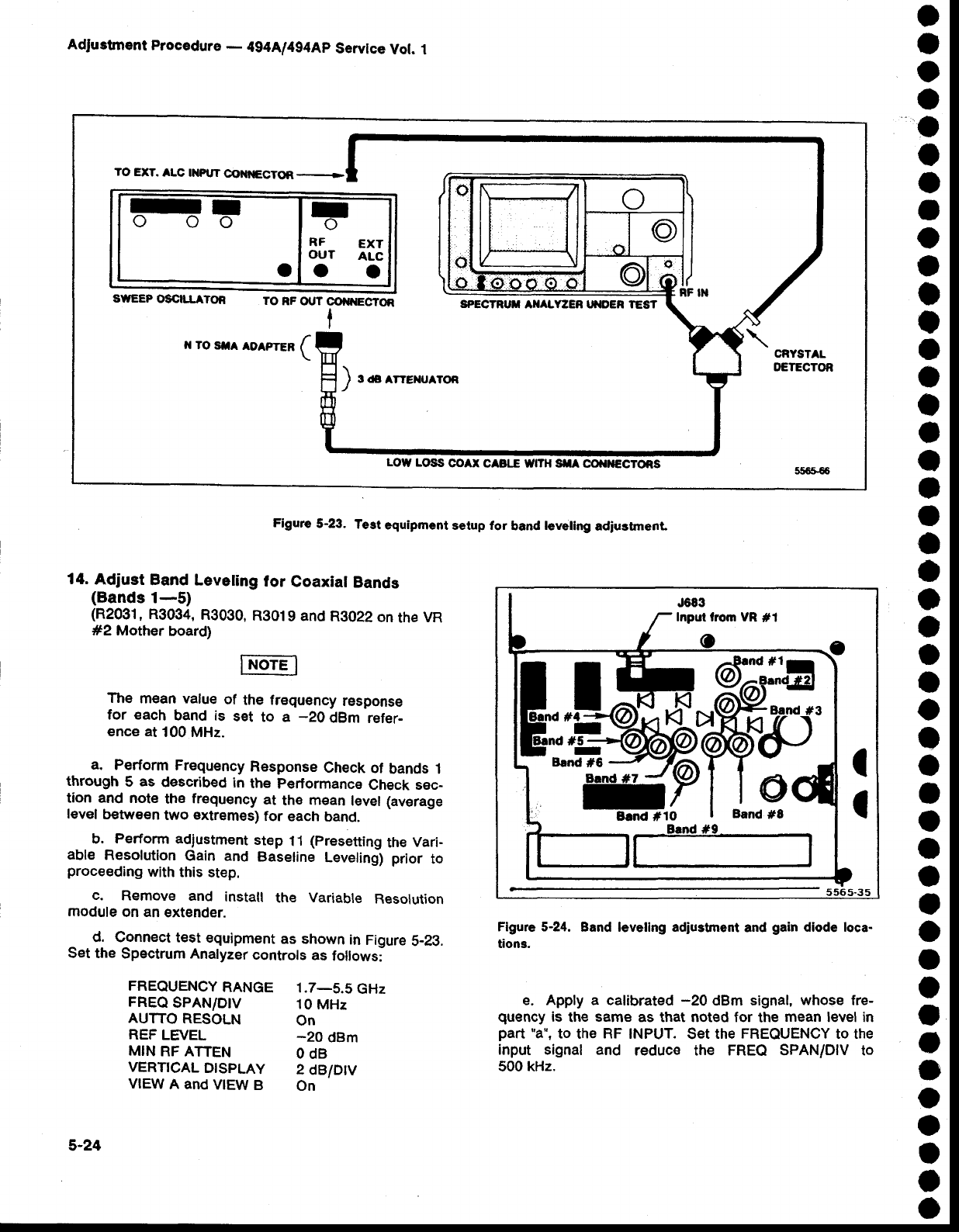

5-23 Test

equipment

setup

for band

leveling

adjustment. ,.................-

S-24

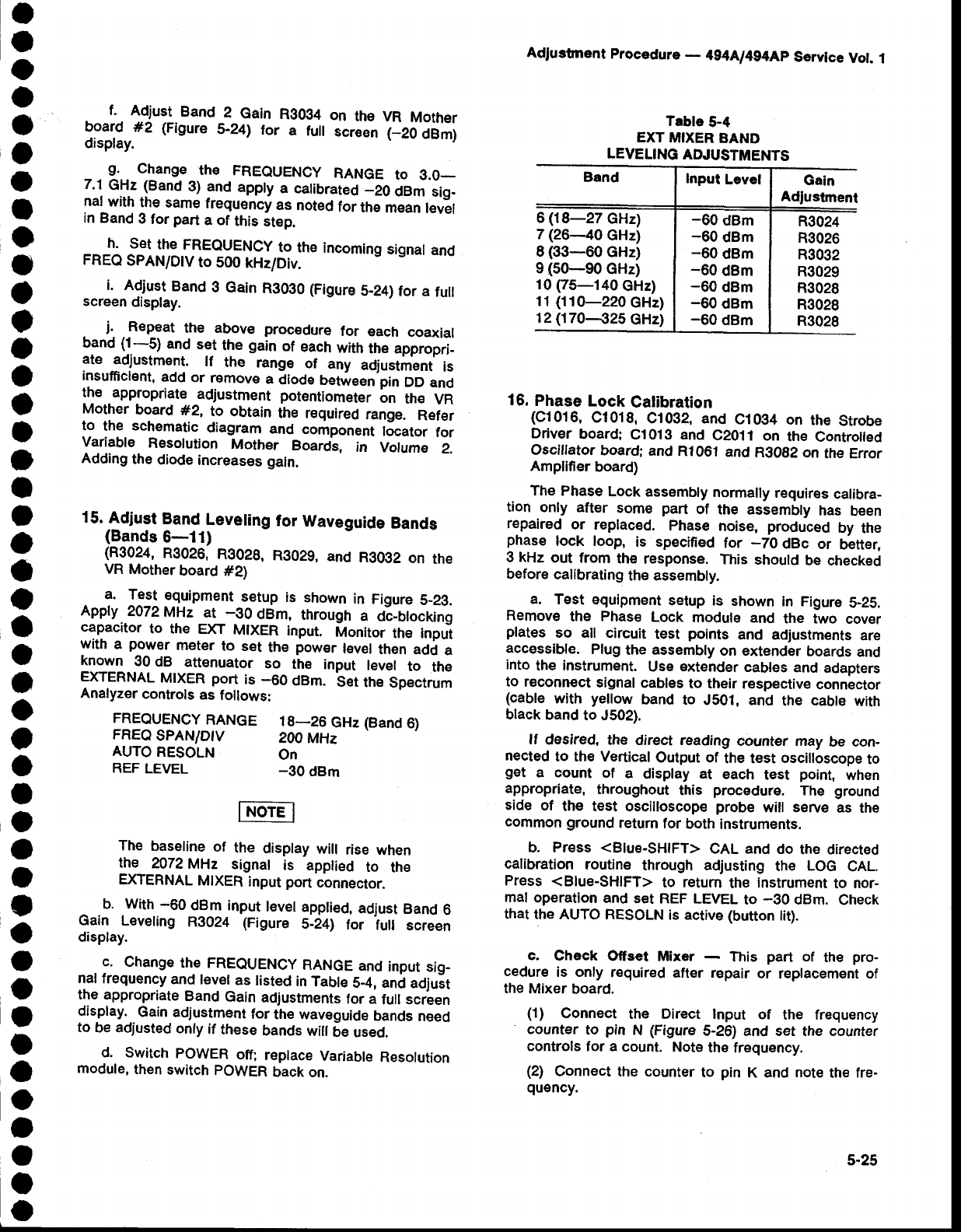

5-24 Band

leveling

adjustment

and

gain

diode locations. ...-.....,,,....5-24

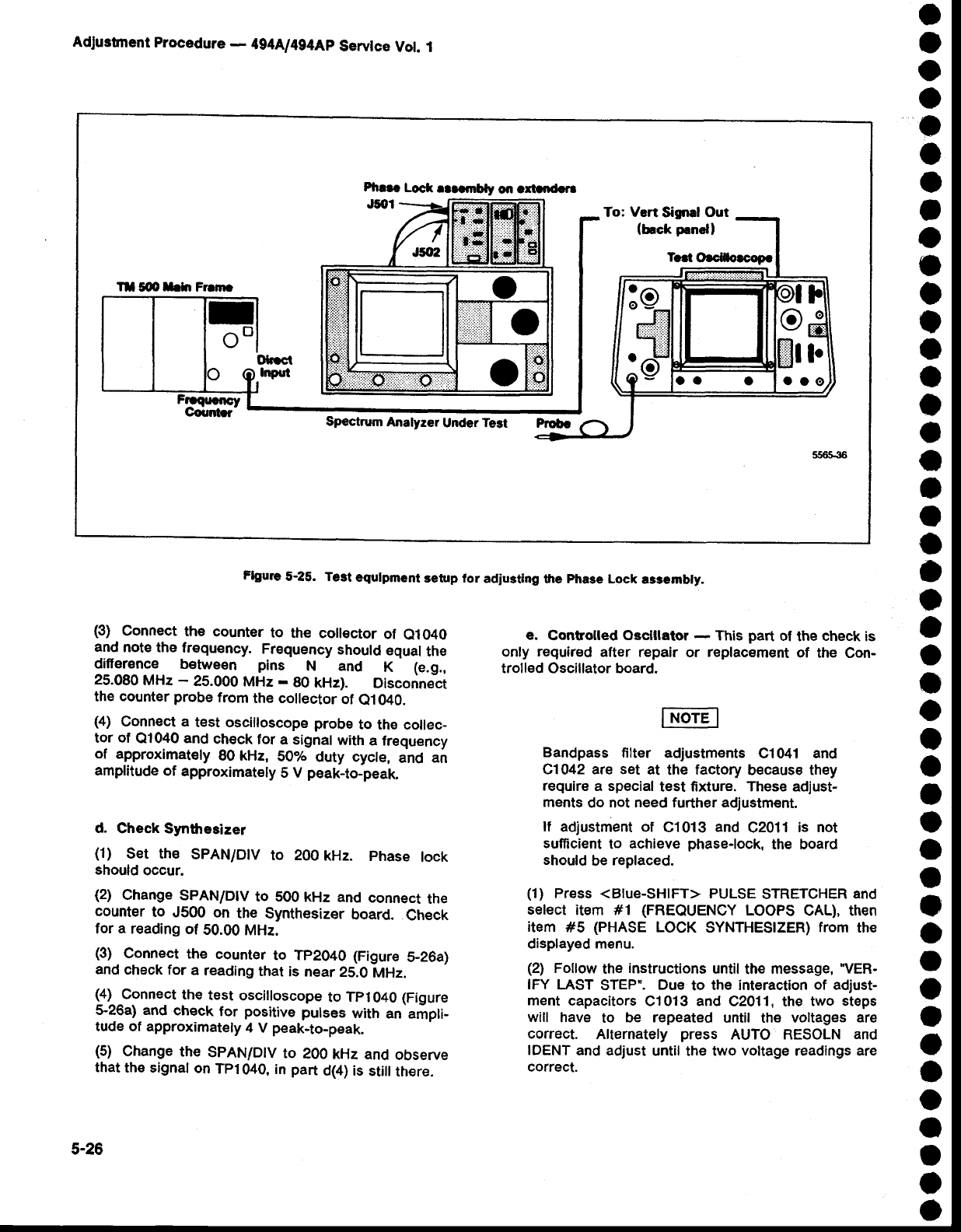

5-25 Test

equipment

s€tup

for adjusting

the

phase

Lock

assembly.

...........................

5_26

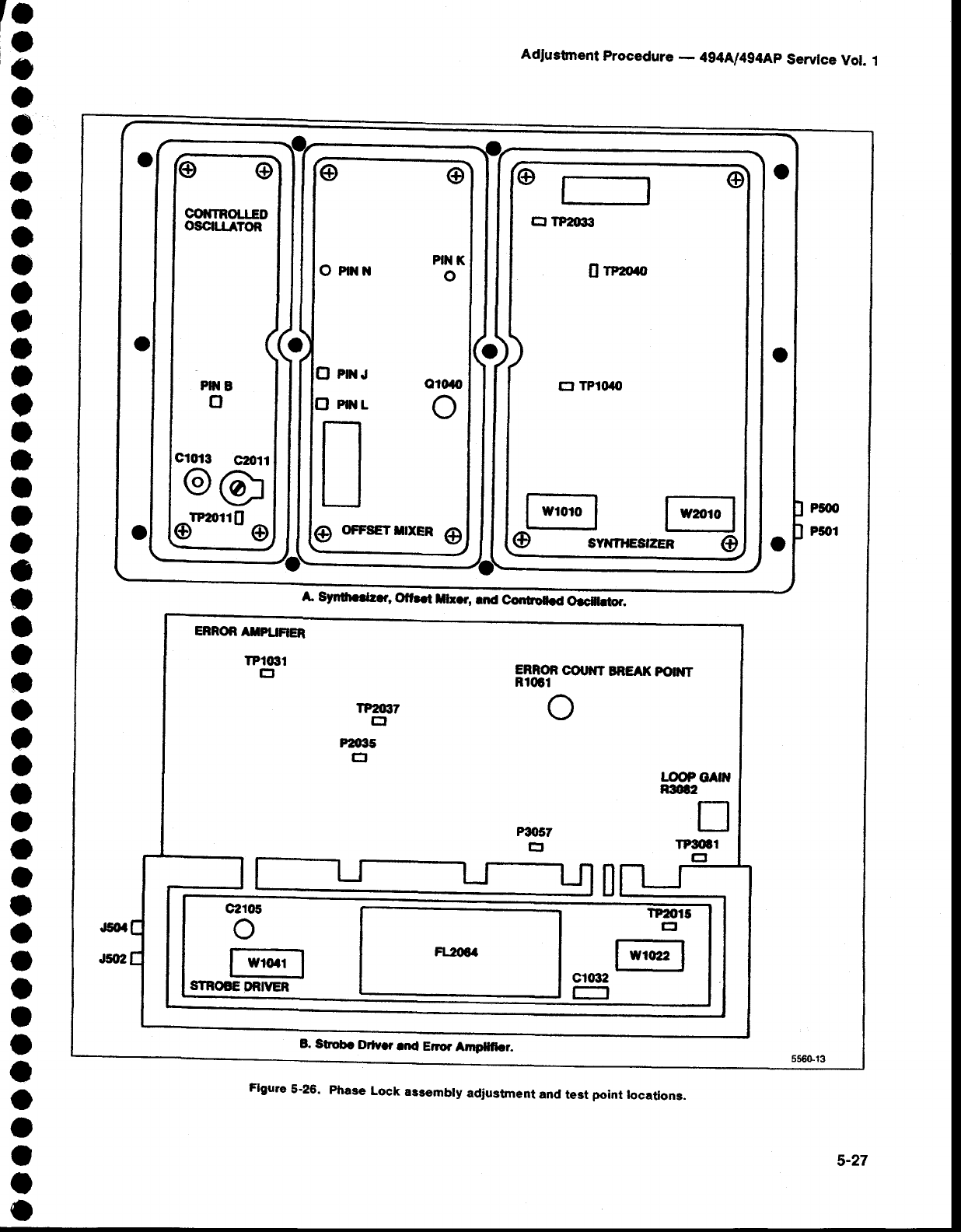

5-26 Phase

Lock

assembly

adjustment

and

test

point

locations.

.............,.................

S_27

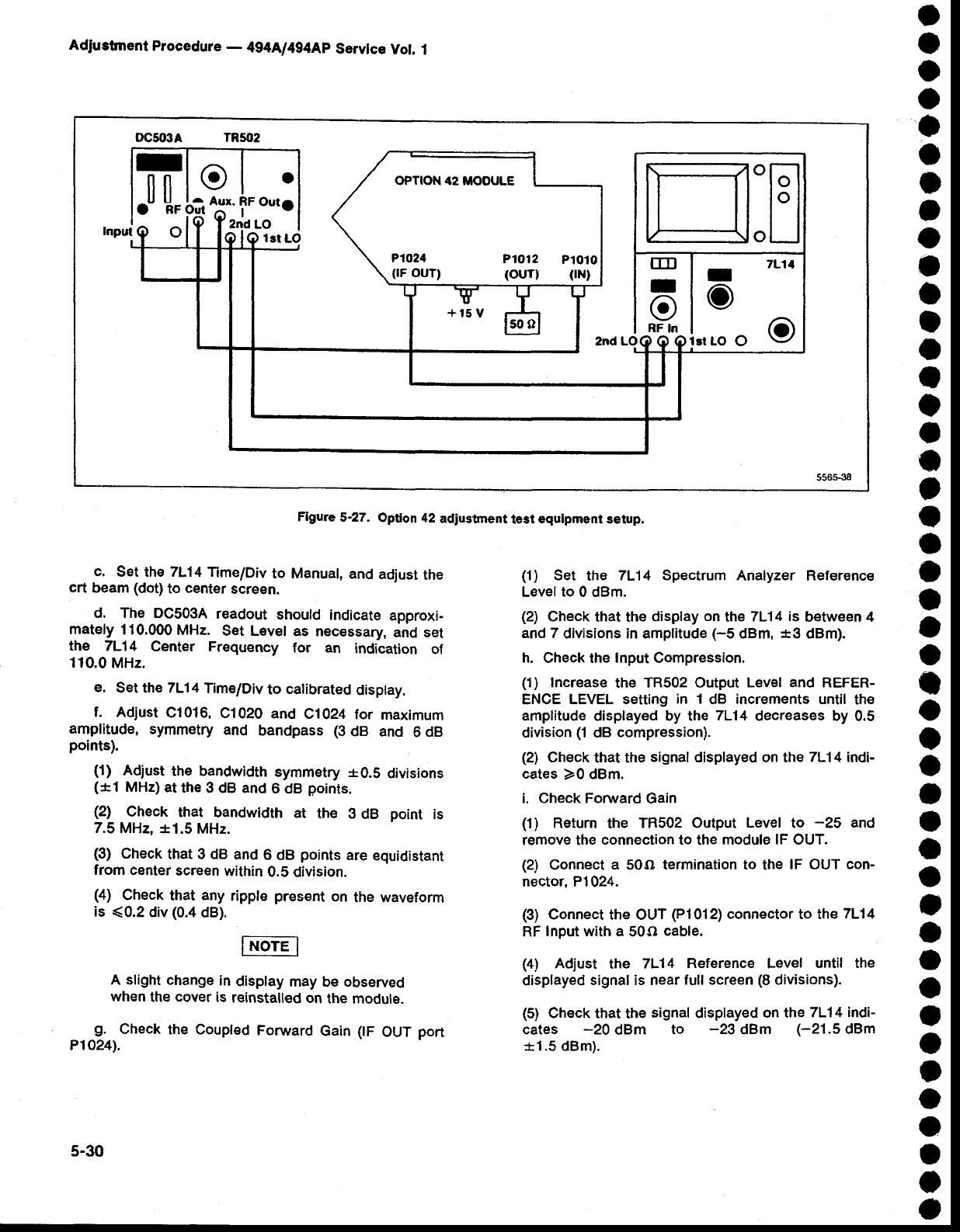

5-27 Option

42

adjustment

test

equipment

setup.

......... .............

S_g0

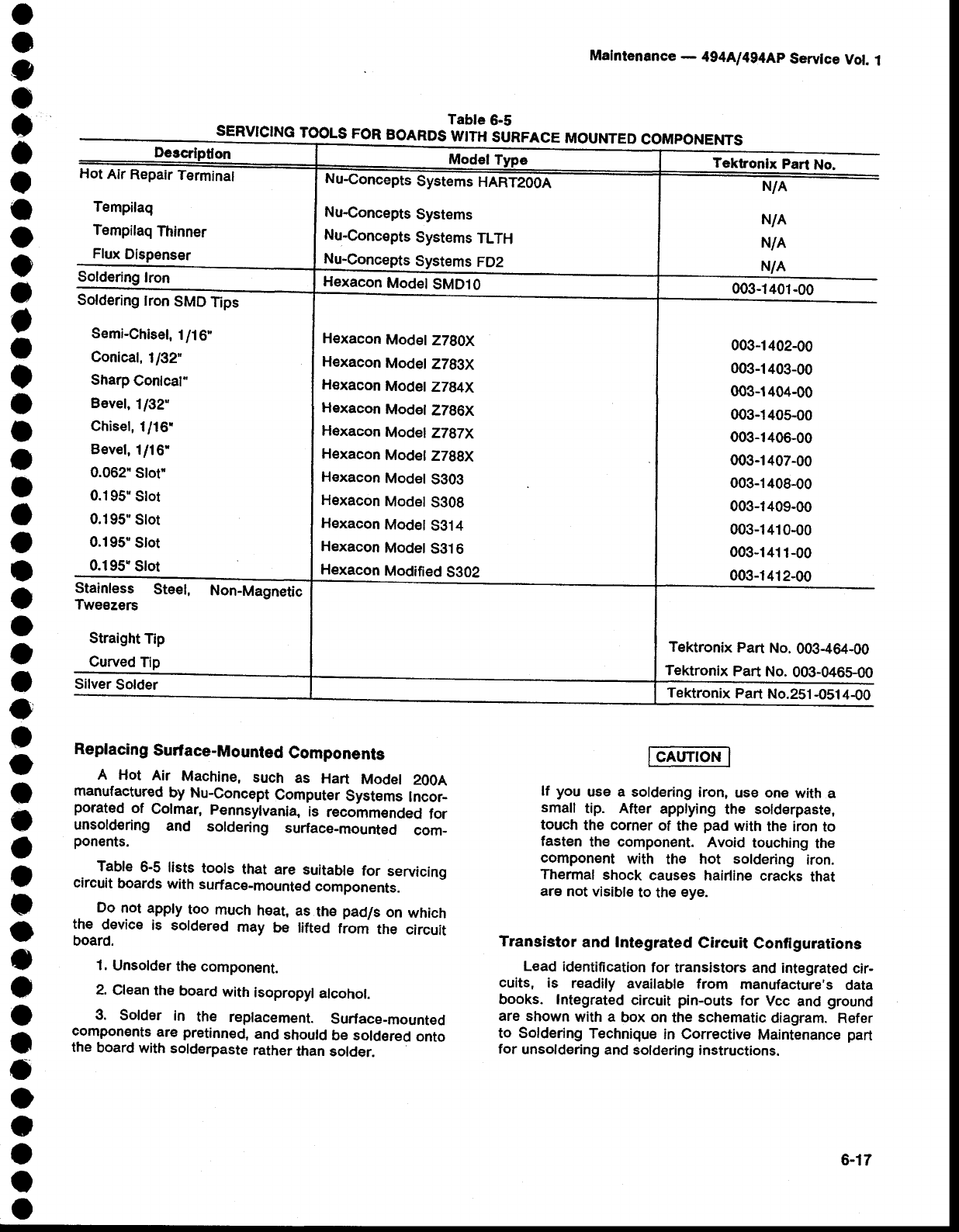

6-1 Surface-mounted

components

lead

configuration. ....................

6_1

6

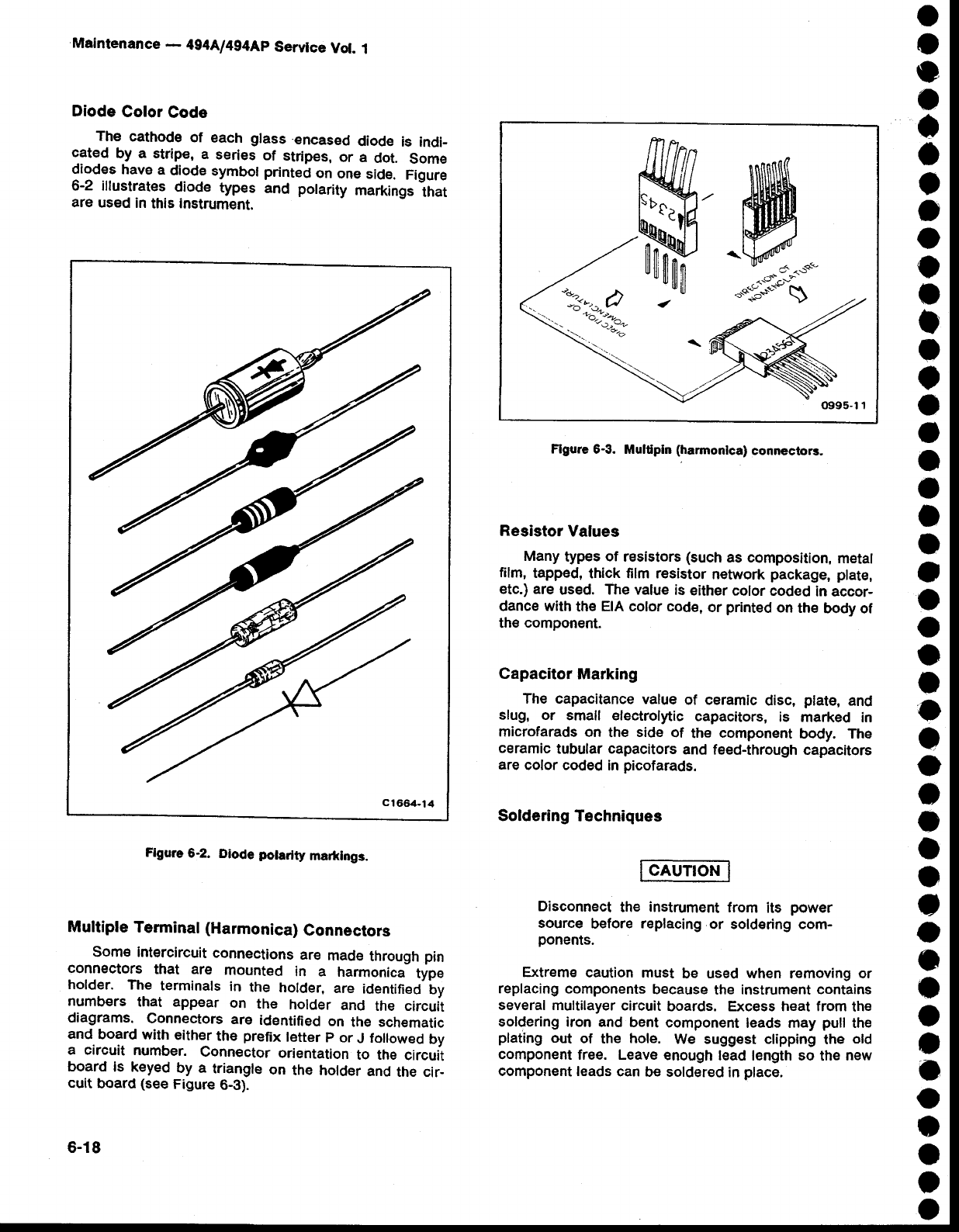

6--? Diode

potarity

markings. ..........

6-18

9-9 Multipin

(harmonica)

connectors.

.................

6_1g

9-1 Servicing

the

vR

assembty. ......

6_19

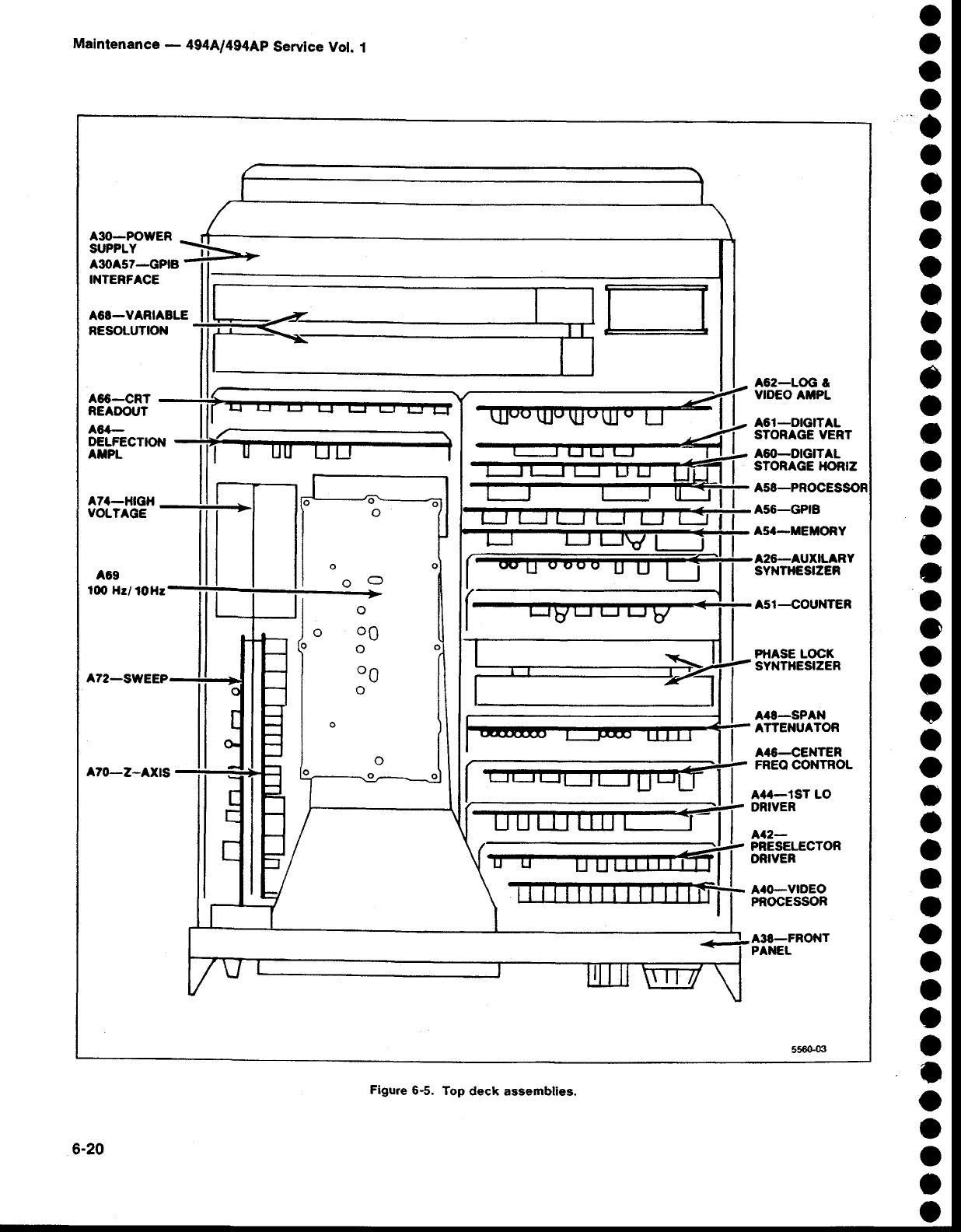

9-9 Topdeckassembties.

.............................,-...6-20

6-6 RF

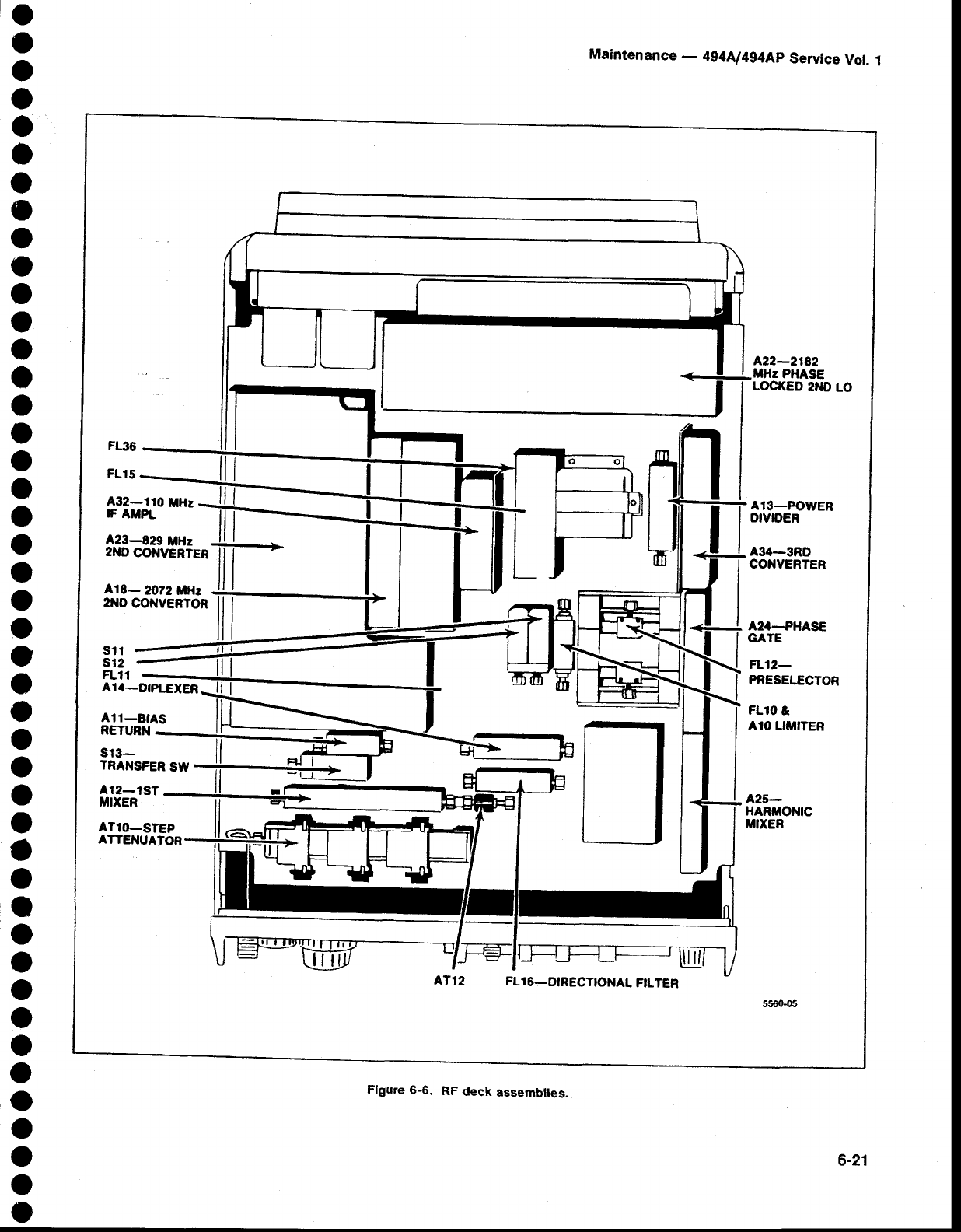

deck assemblies. ................

6_2.1

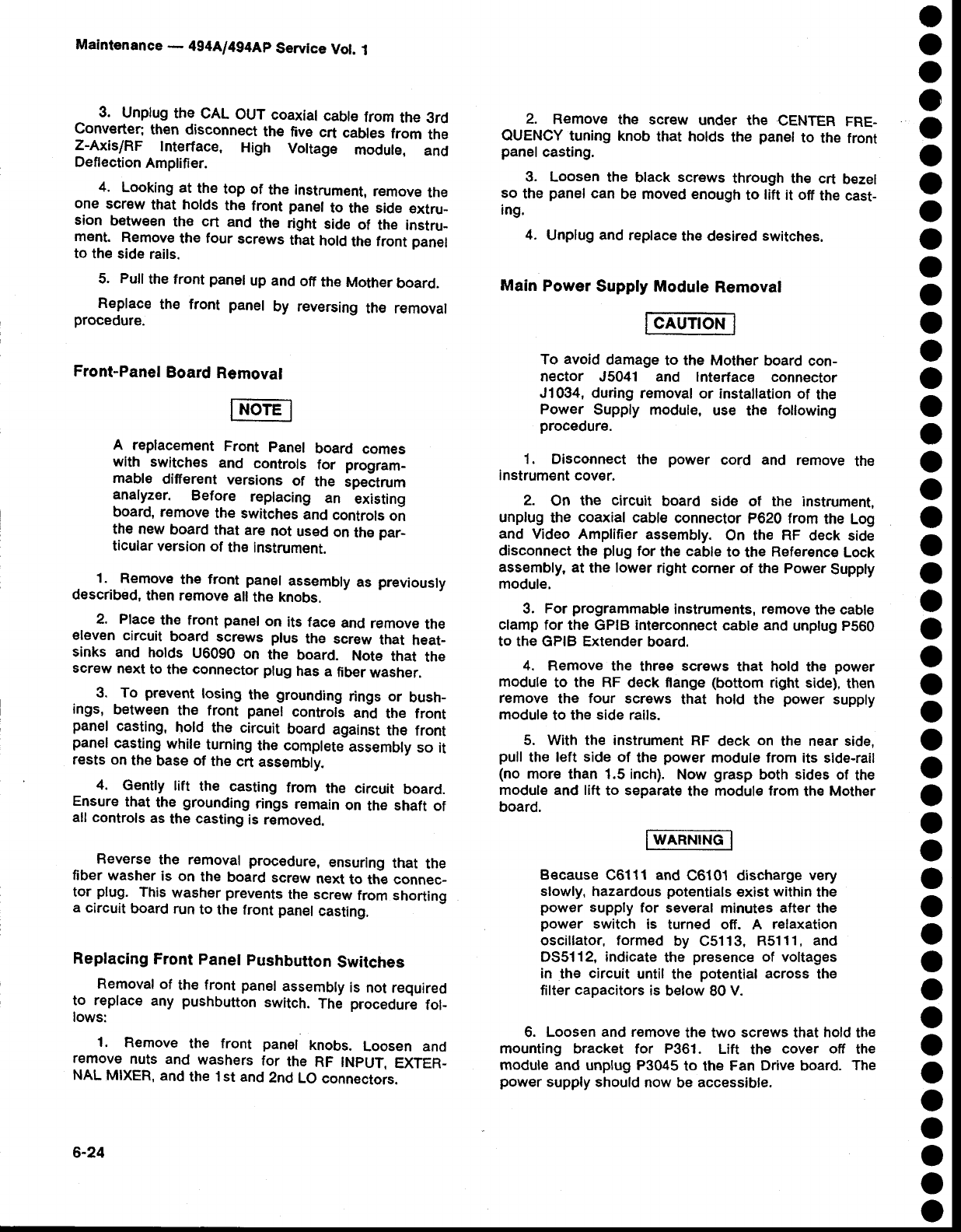

6-7 Removing

the 1st

LO

Interface

board. .....

6-25

9-9 Fan

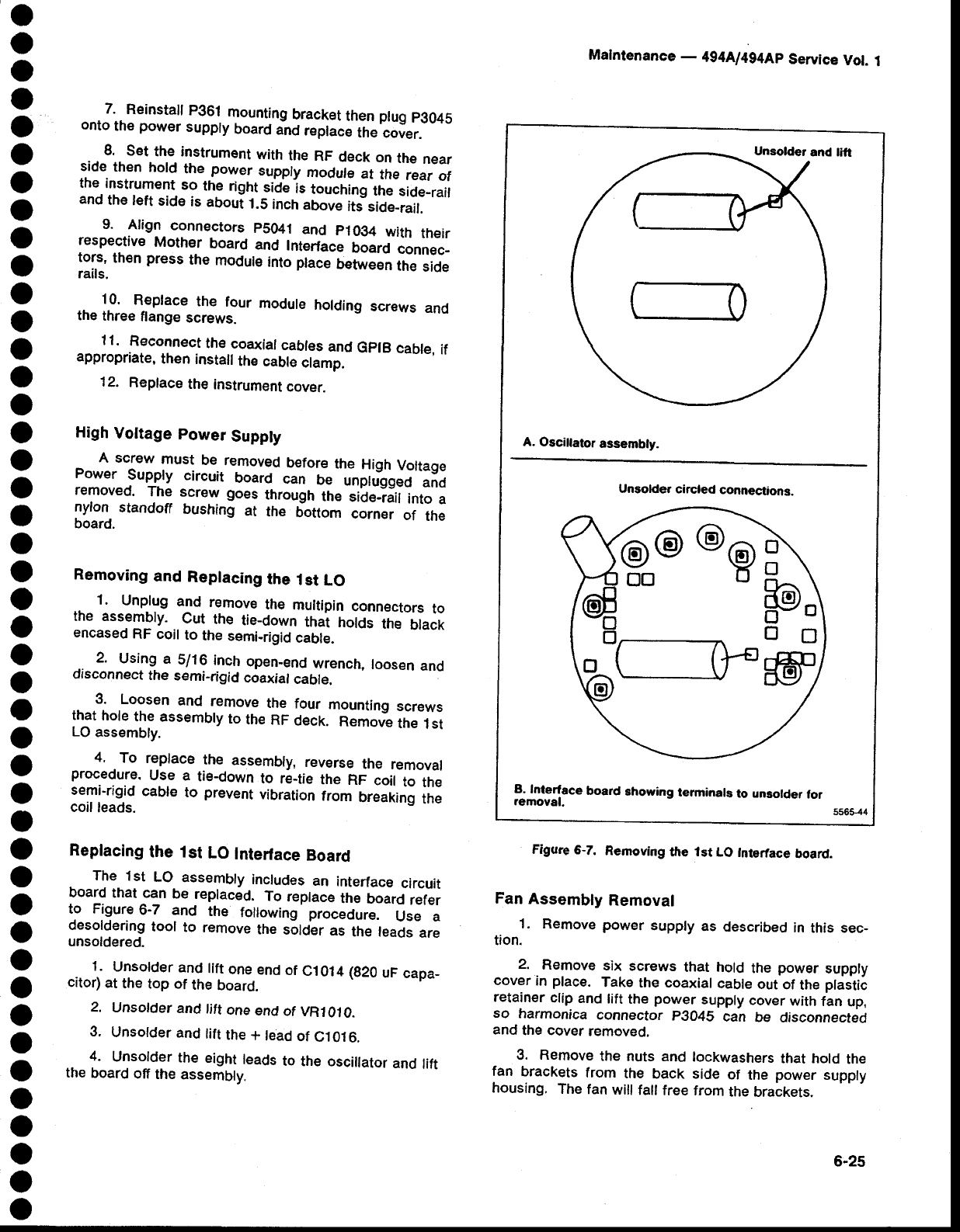

assembty

mounting. ..........

6-26

6-9 110

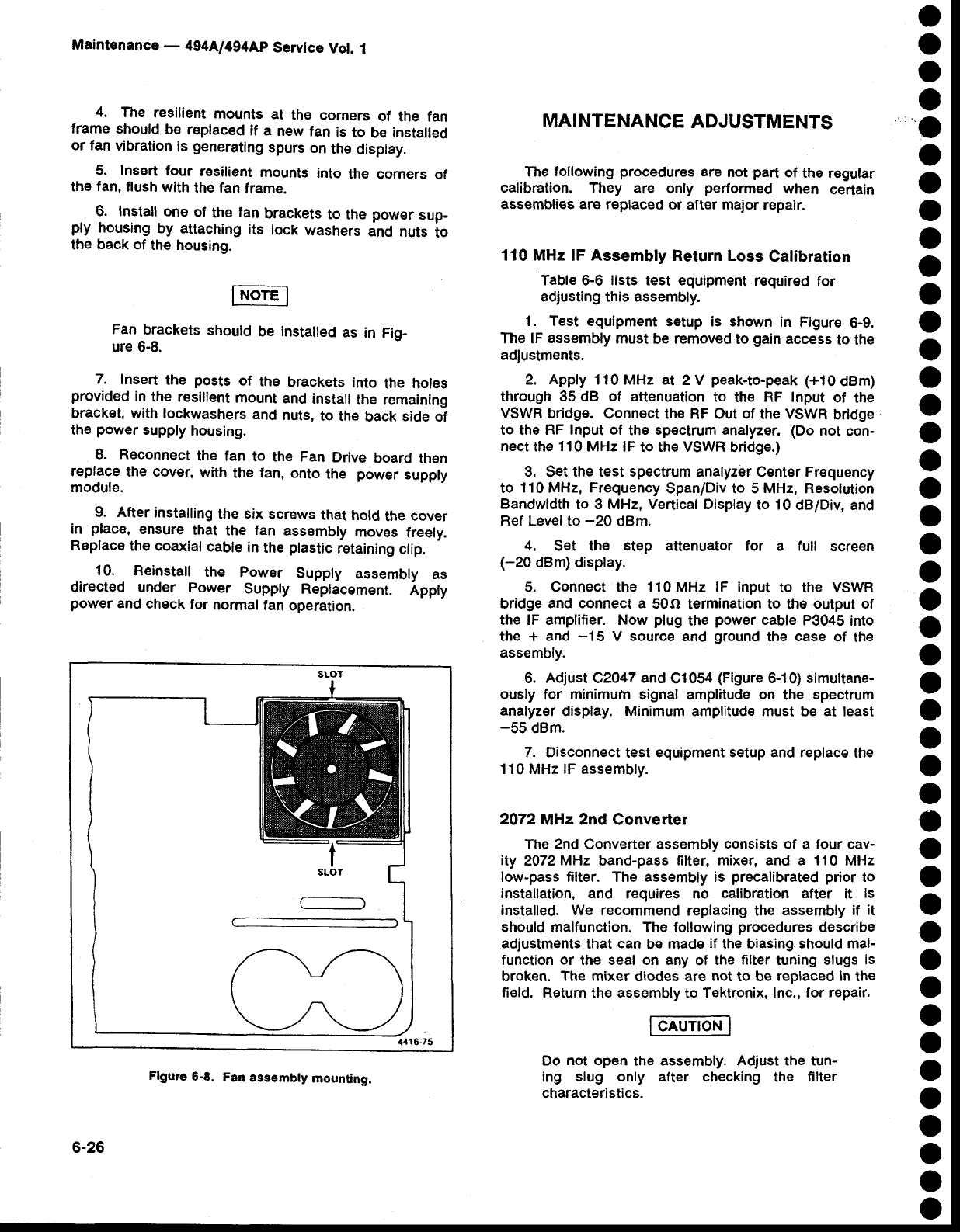

MHz

lF return

loss

adiustment

setup.

......... ............6-2T

6-10 110

MHz

tF

test

points

and

adjustments.

.......... ............

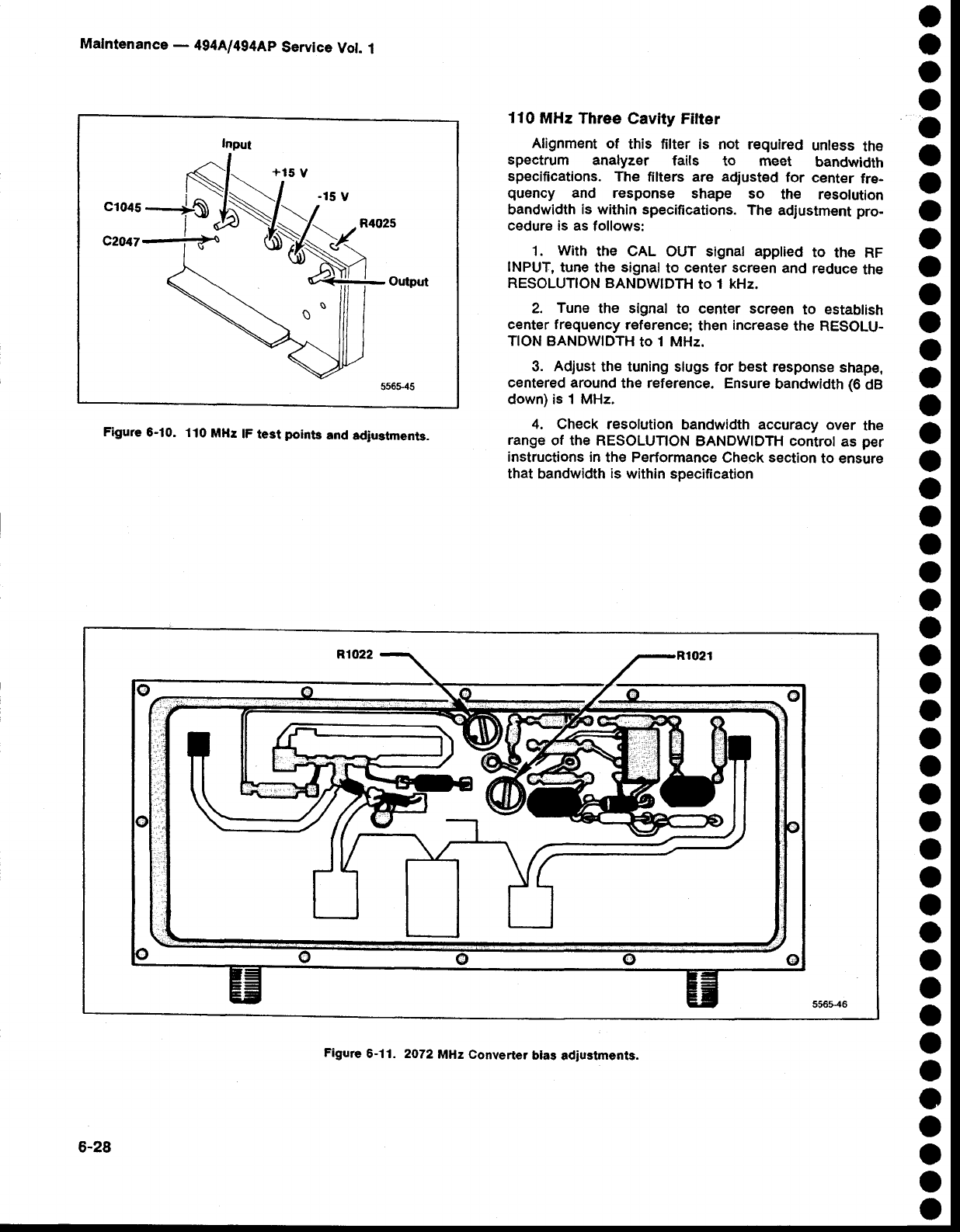

6-2g

6-11 2072MHz

Converter

bias

_ adjustments. ..........

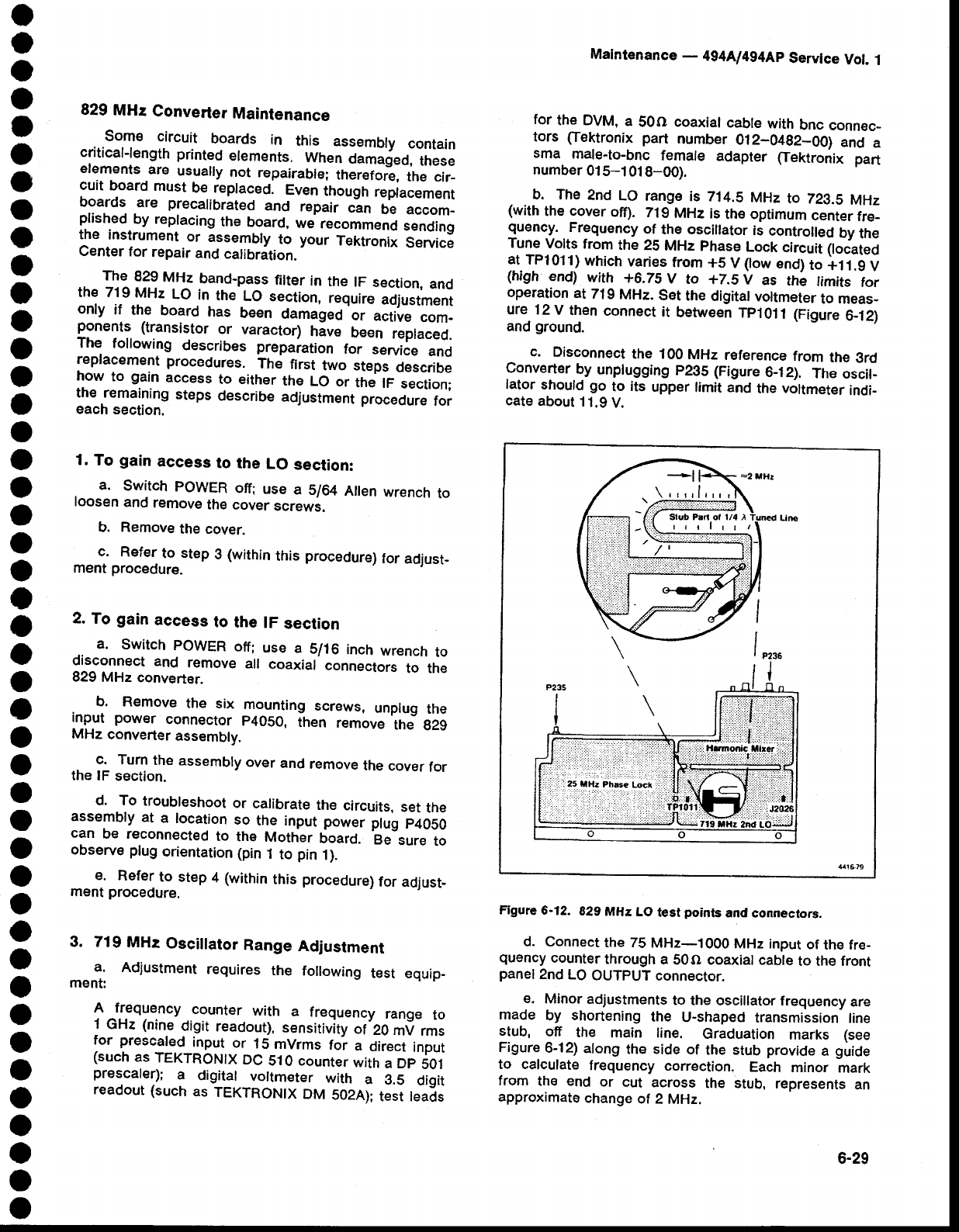

6_2g

6-12 829

MHz

LO

test

points

and

connectors.

........... ............

6-29

6-13 829

MHz

amptifier

test

iack

and

jumper. ....

6_30

6-14 829

MHz

filter

test

equipment

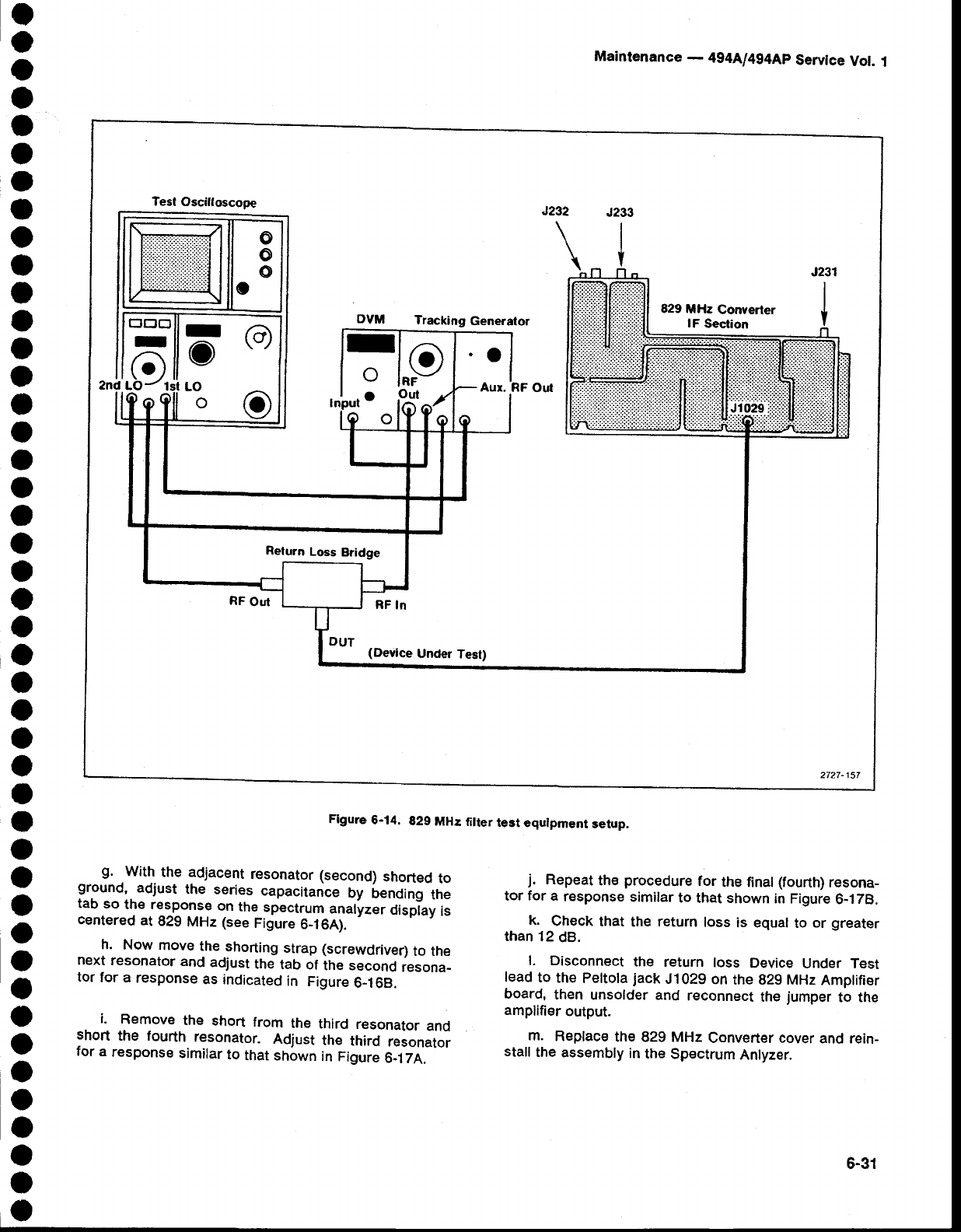

setup.

......... .............

6-gi

6-15 829

MHz

Converter

filter

tune

tabs. .............

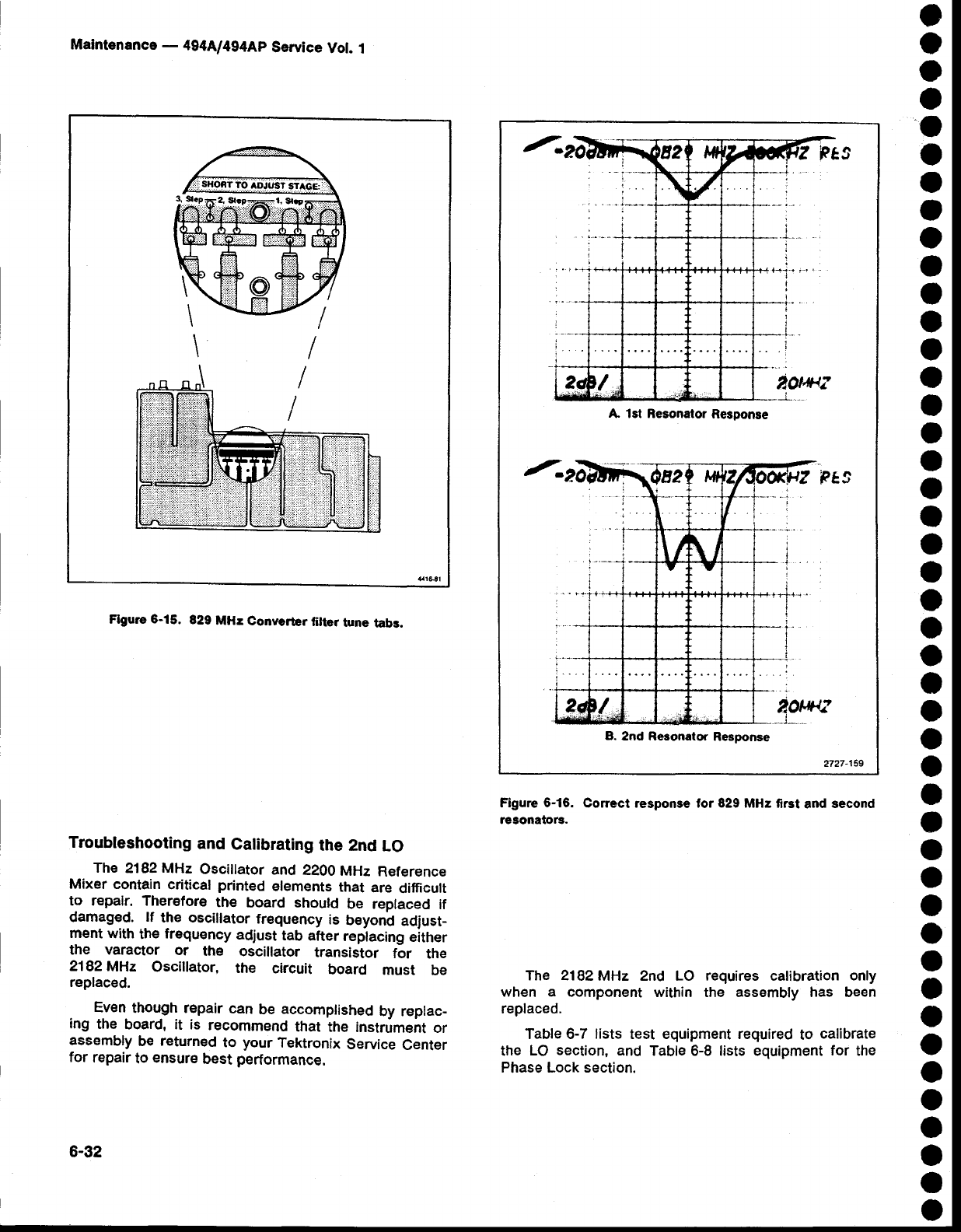

6-32

6-16 Correct

response

for 929

MHz

first

and

second

resonators. ....

6-92

6-17 Correct

response

for 829

MHz

third

and

fourth

resonators.

.........................

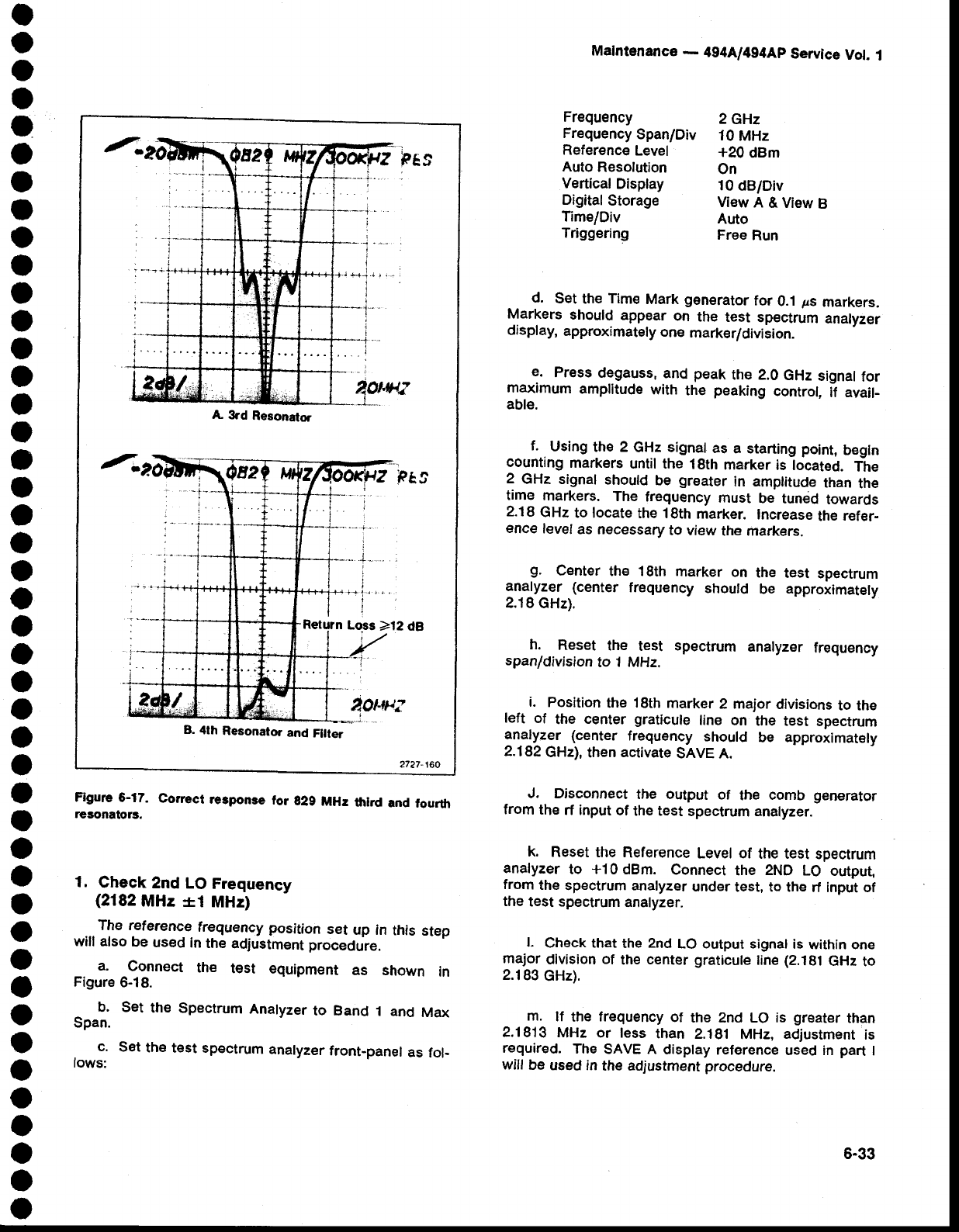

6_9g

6-18 2182MHz

2nd

LO

frequency

- accuracy

test

setup.

........ .........

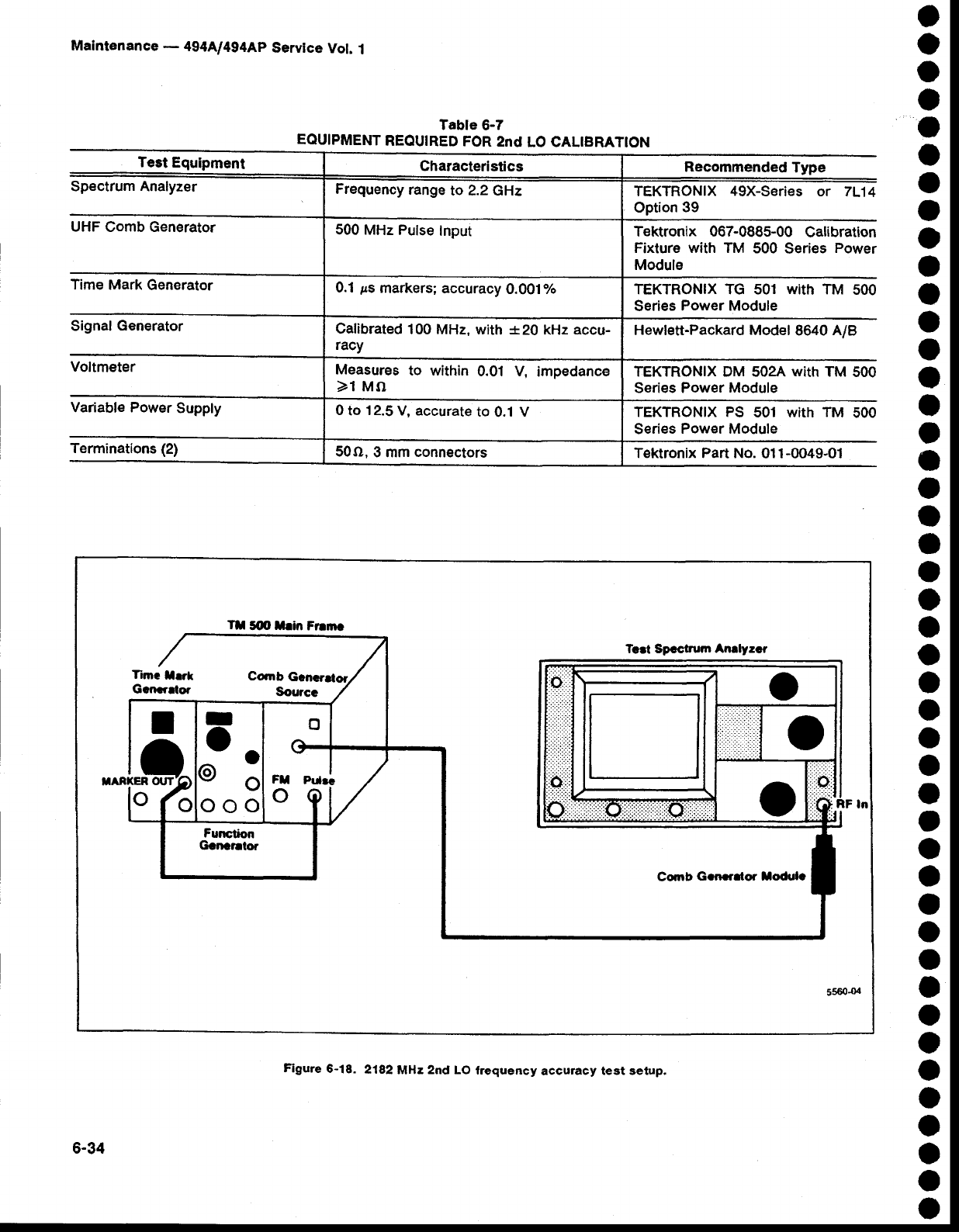

6_94

6-19 2182MHz

phase

Locked

2nd

LO

adjustment

setup.

......... ............

6_96

6-20 16-20 MHz

phase

Lock

circuit

test

point

and

component

locations.

................,..

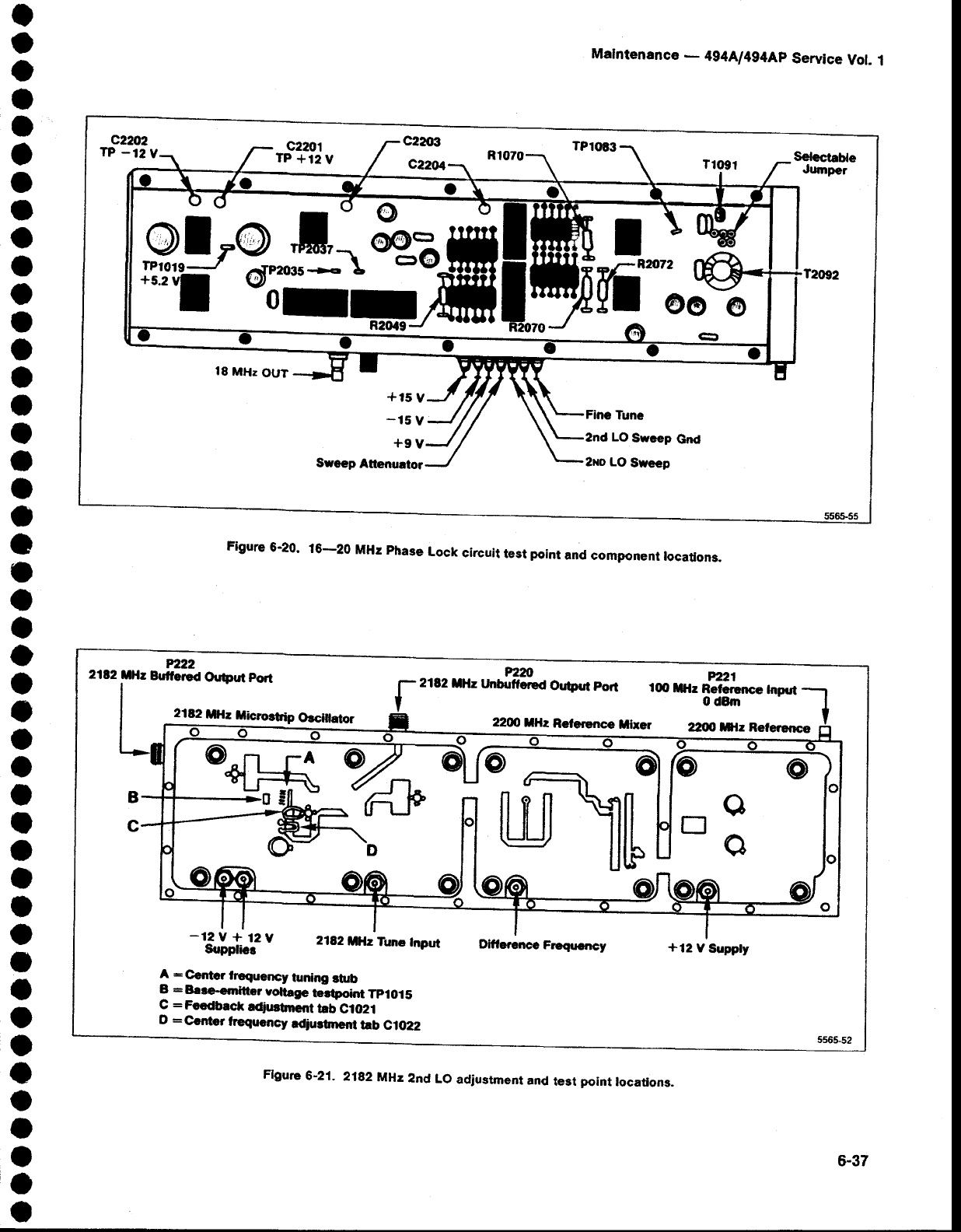

6_32

6-21 2182MHz

2nd

LO

adjustment

6-22 Coaxial

test

probe

Page

construction

details. ..................

6-gg

6-23 2182MHz

2nd LO

Phase

Lock

adjustment

setup.

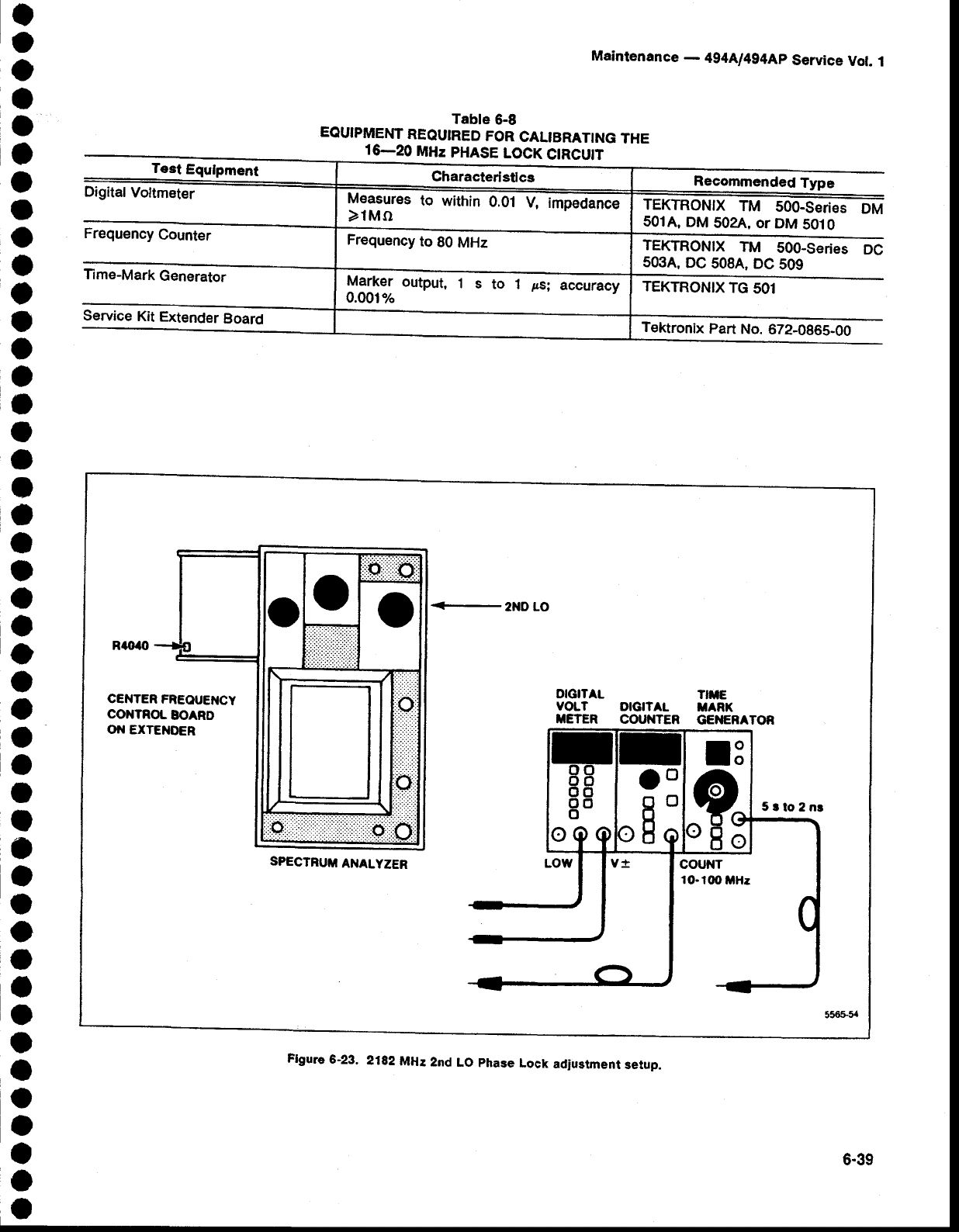

........ ..............

6_39

6-24 Tune

and

Sweep Range

adjustments ............641

6-25 3rd

Converter

test

points

and

adjustments.

.......... ............

6_43

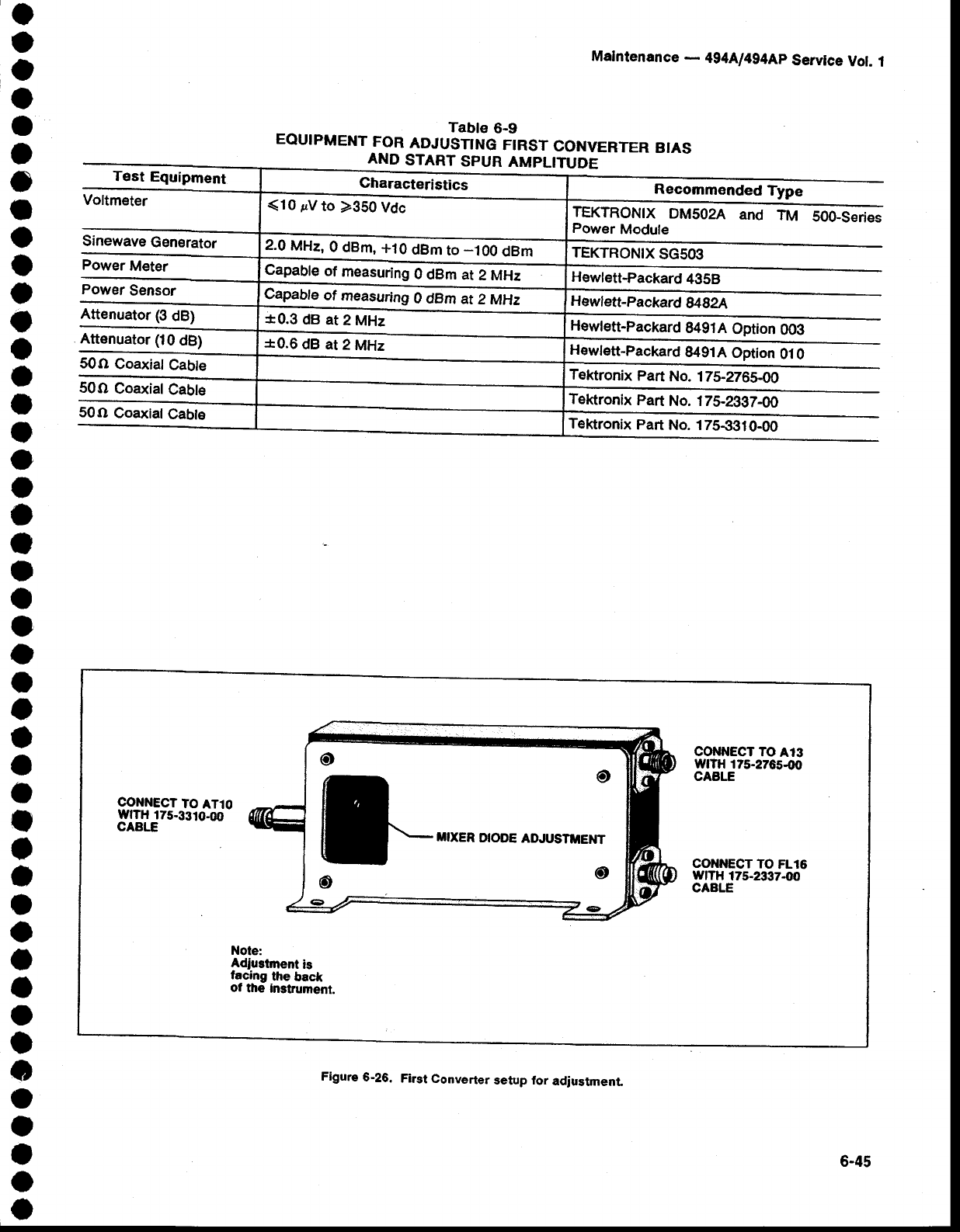

First

Converter setup

for adjustment.

..........

6-45

1st

LO Driver

board adjustment

and

test

point

locations.

...............................

646

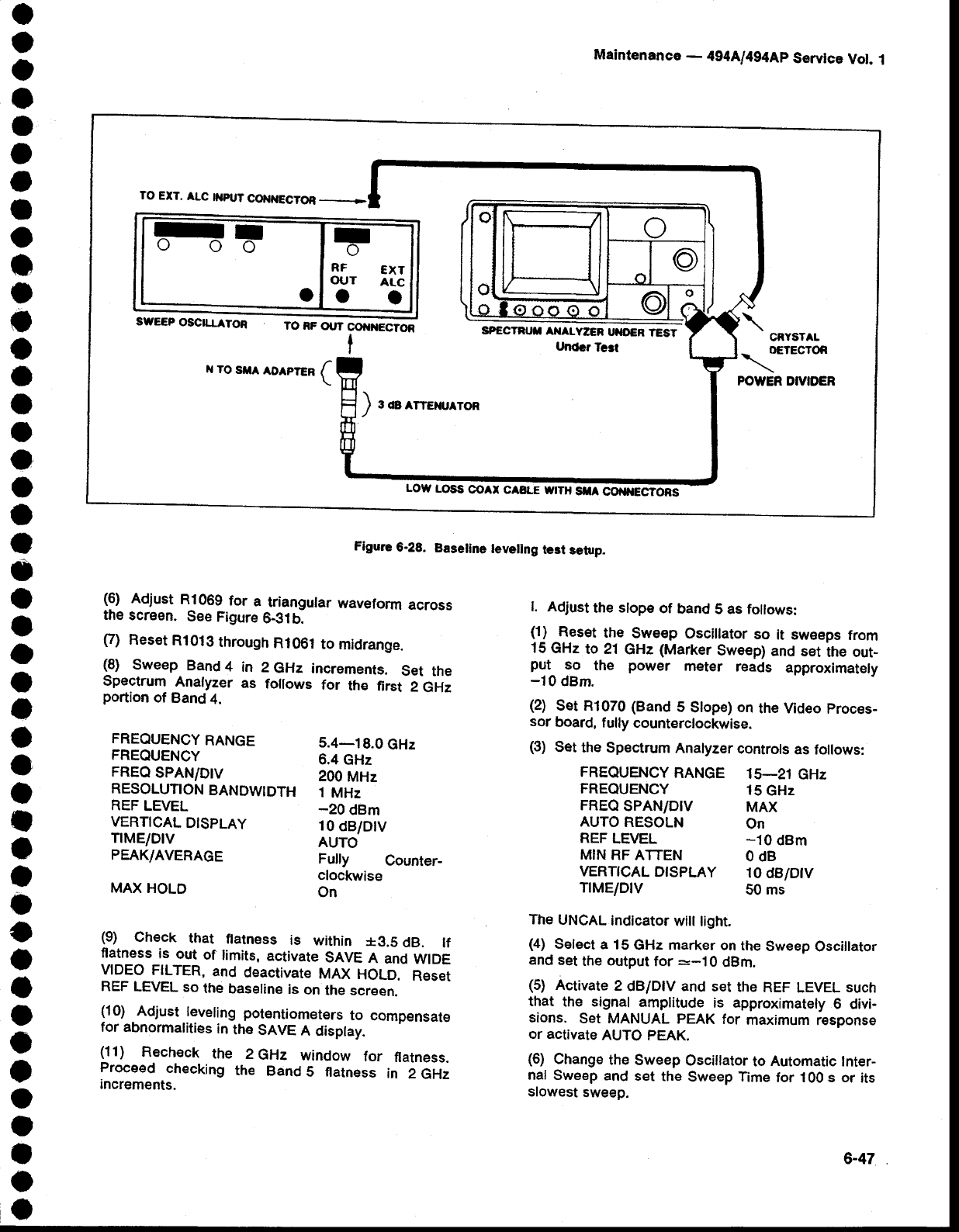

Baseline

leveling

test

setup, .....647

Typical

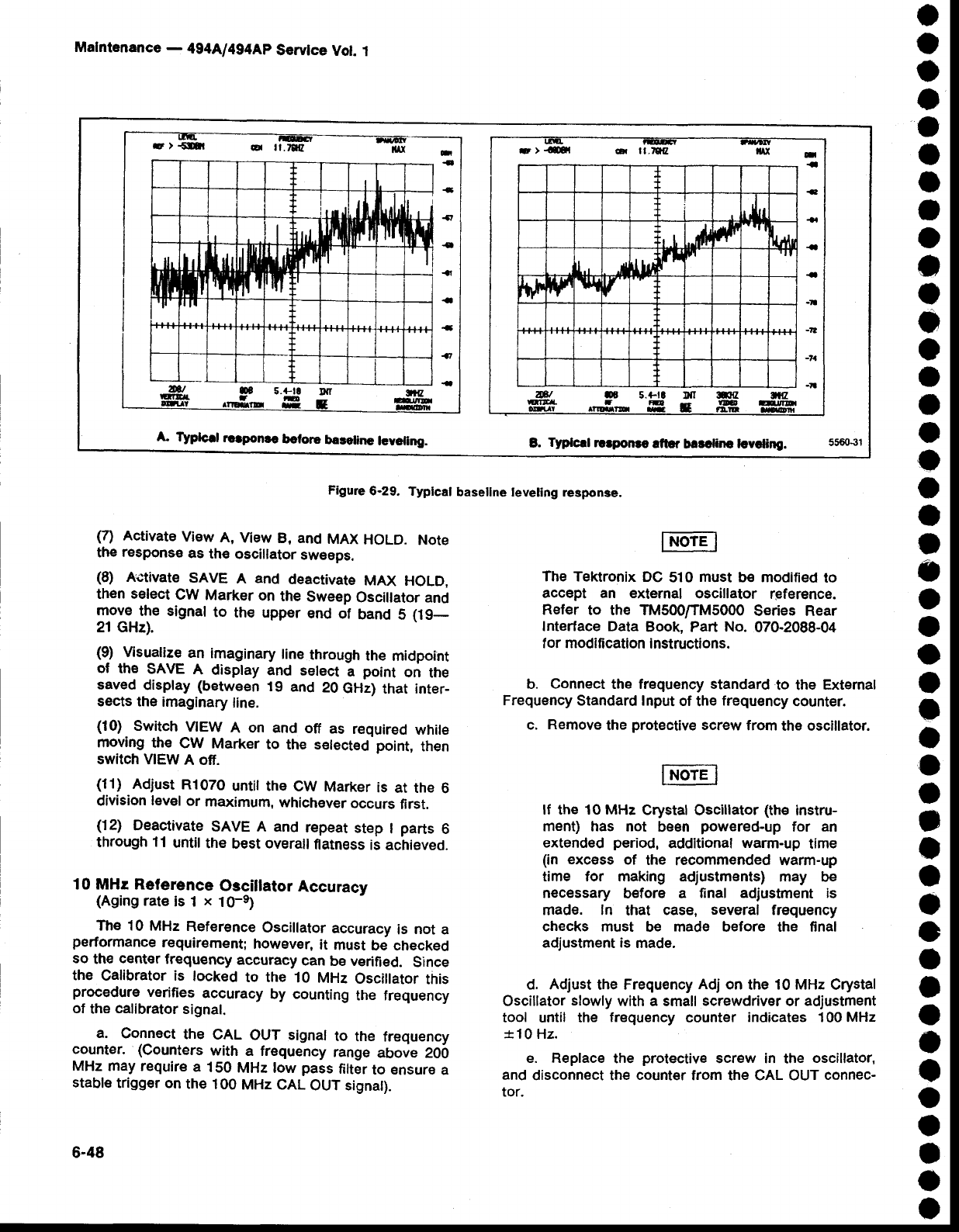

baseline

leveling

response.

.............,

649

Baseline

leveling

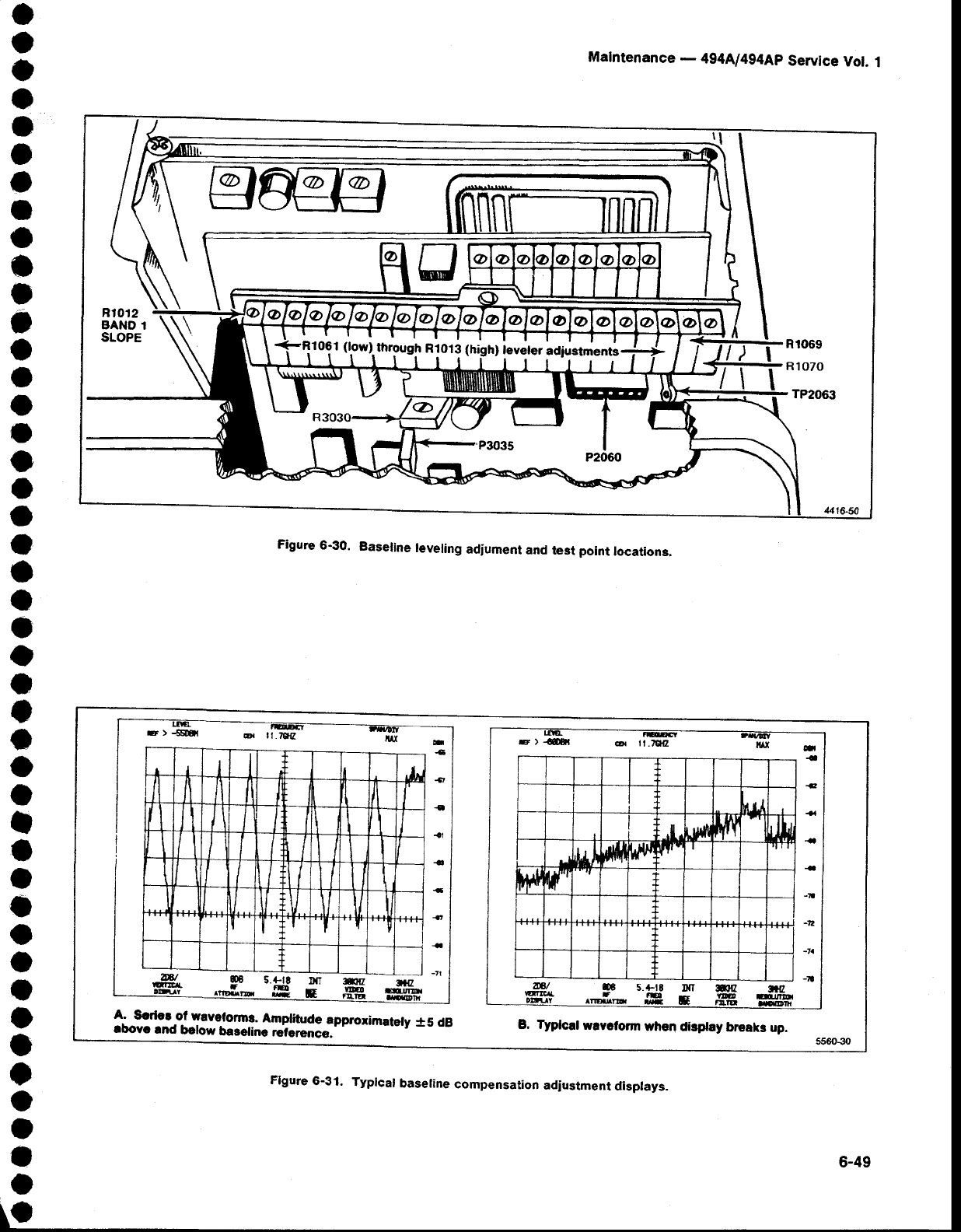

adjument

and

test

point

locations.

...............................

649

Typical

baseline

compensation

response. ...........

6_49

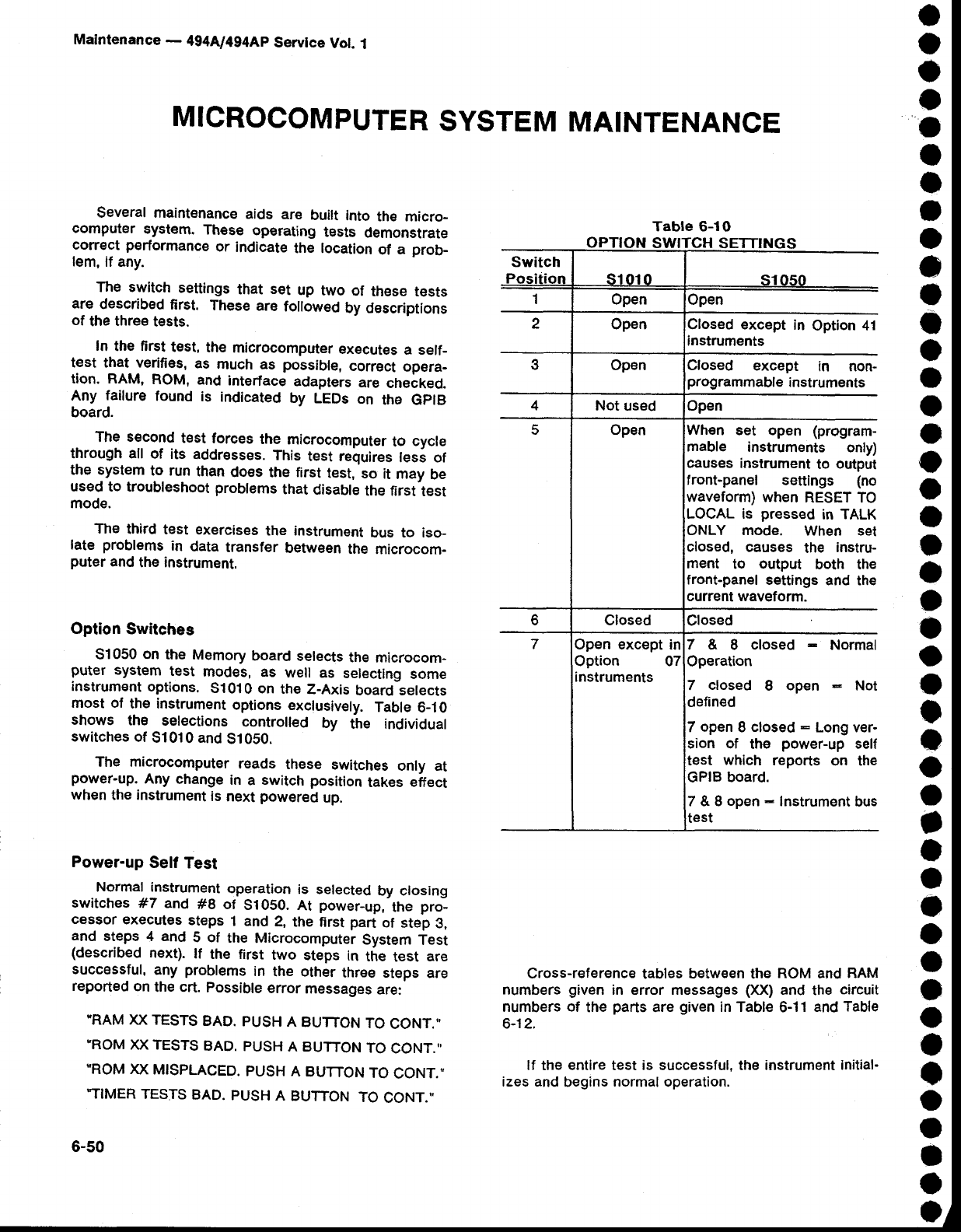

6€2 A15

through A12 in

microcomputer

test mode. .......

6-52

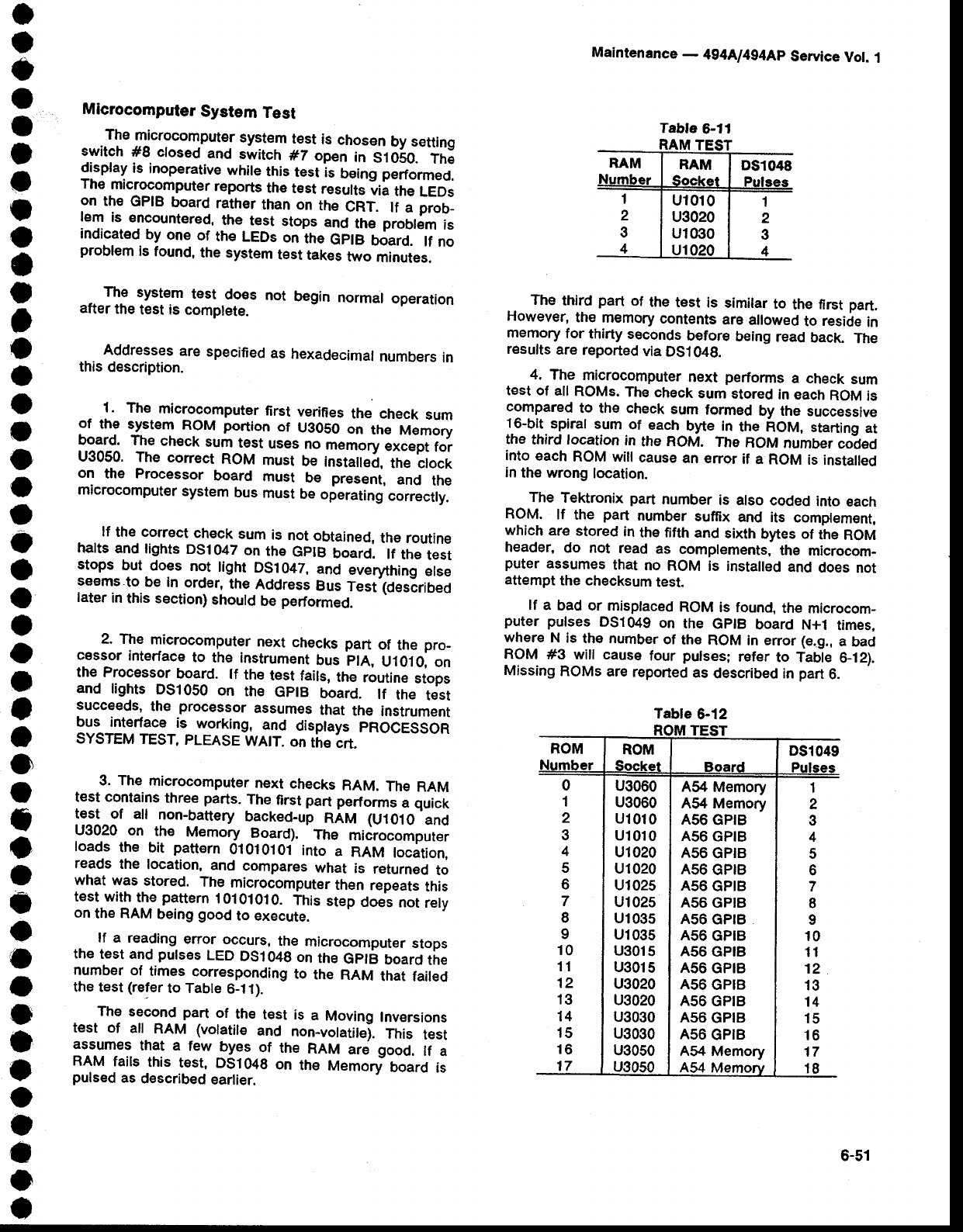

6-33 Four

main

bloack select

outputs

of address

decoder

U2045. ......

6_59

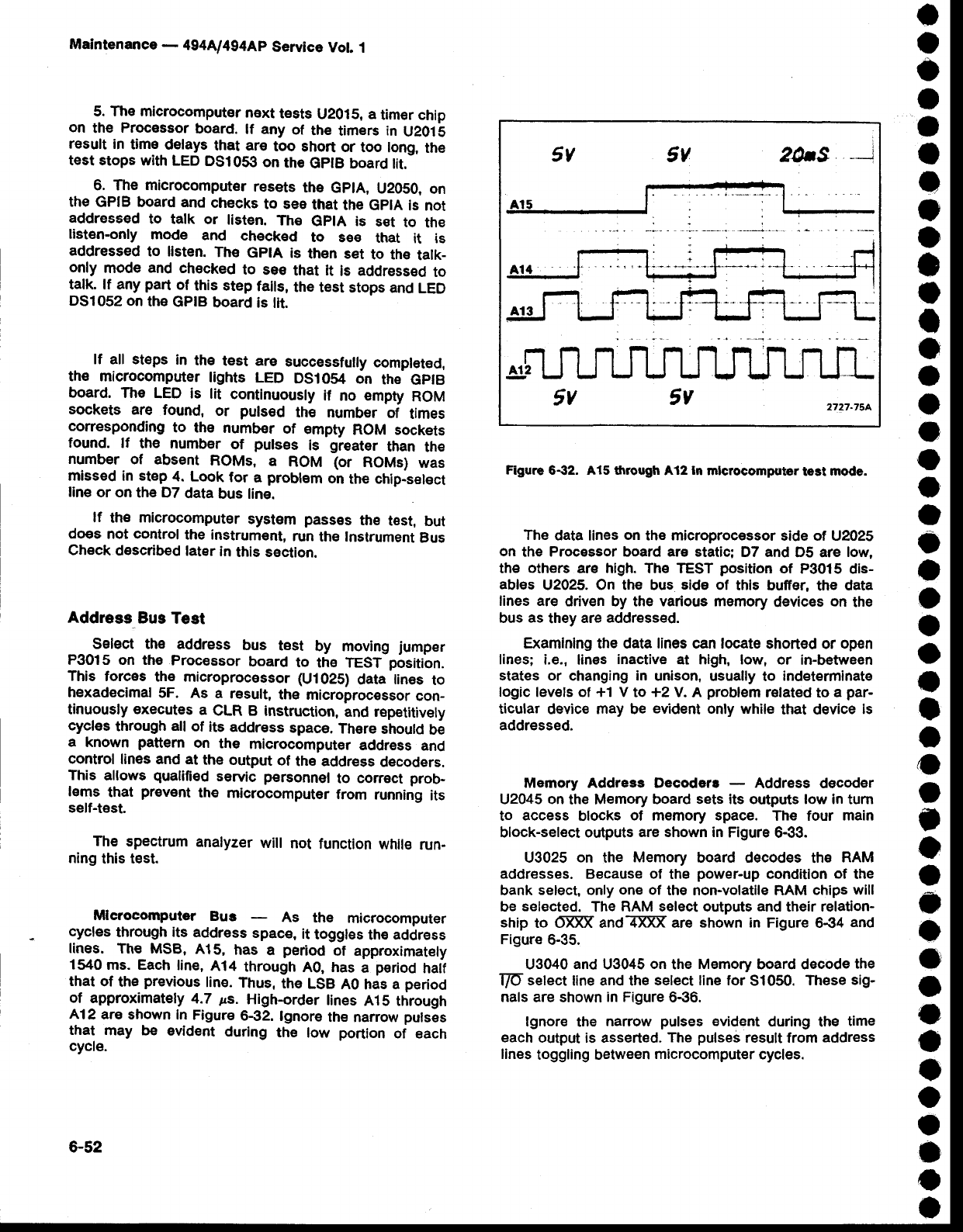

6-34 RAM

select output

in

relation

to O'XXX. ...................

6-53

6-35 RAM setect

output

in

relation

toTffi. ...................6-5g

6-36 -UOand

S1050 setect

tines

in

relation

to

oxxx. ...................

6-53

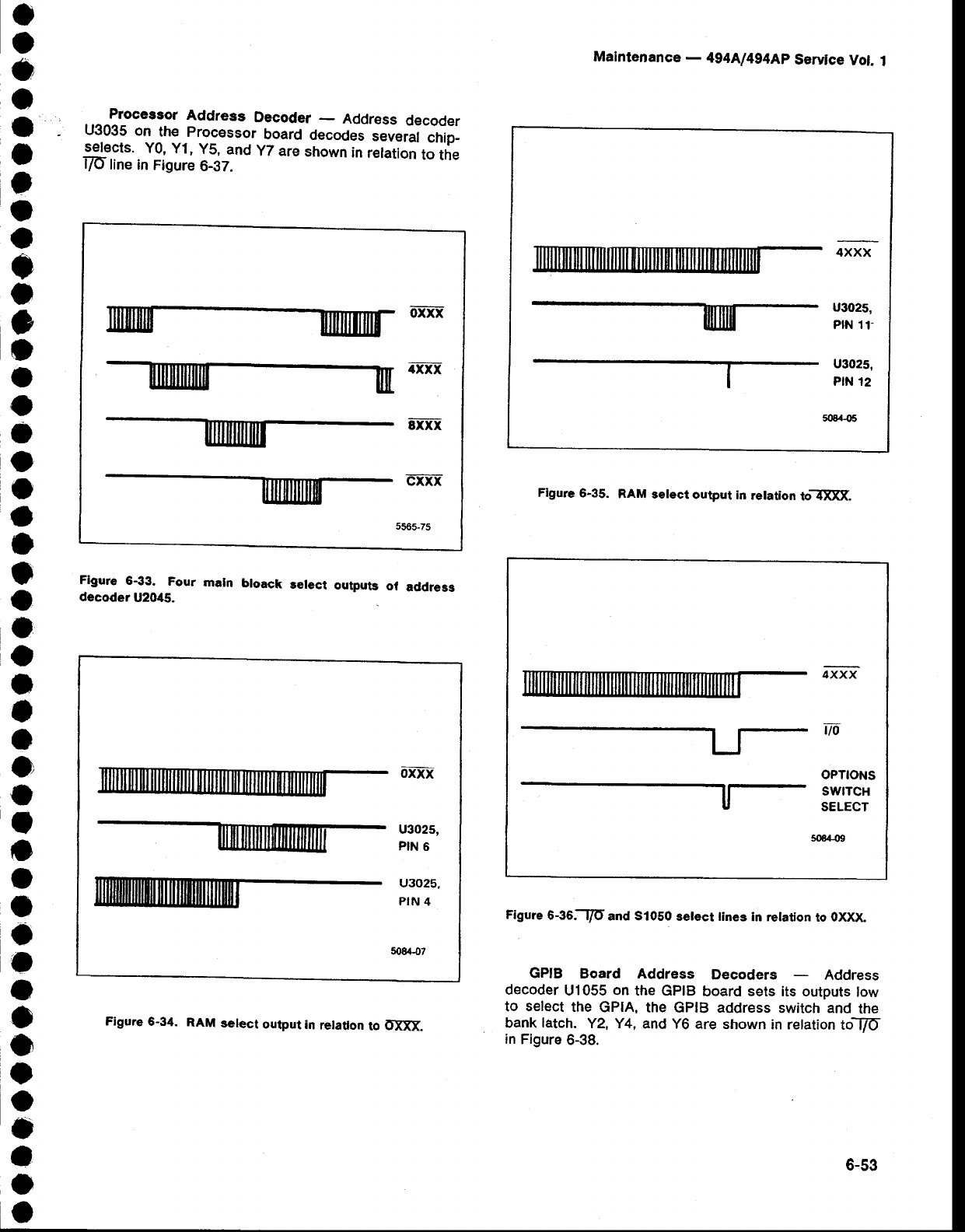

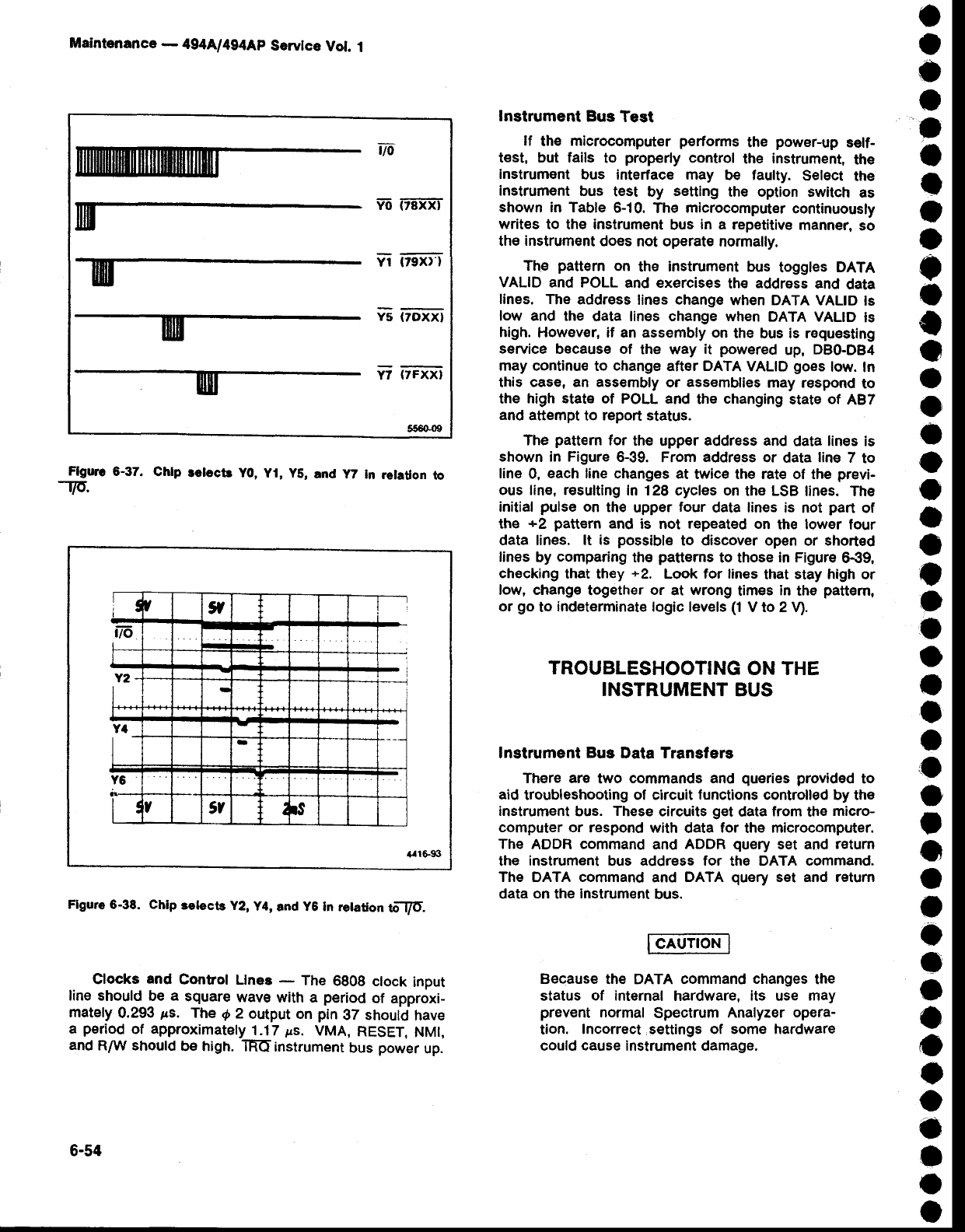

6-37 Chip

selects

Y0, Y1,

yS,

and

Y7 in retation

toT/O-. ...........

6-54

6-38 Chip

selects

Y2, Y4,

and

y6

in retation

td:IIO. .. 6-54

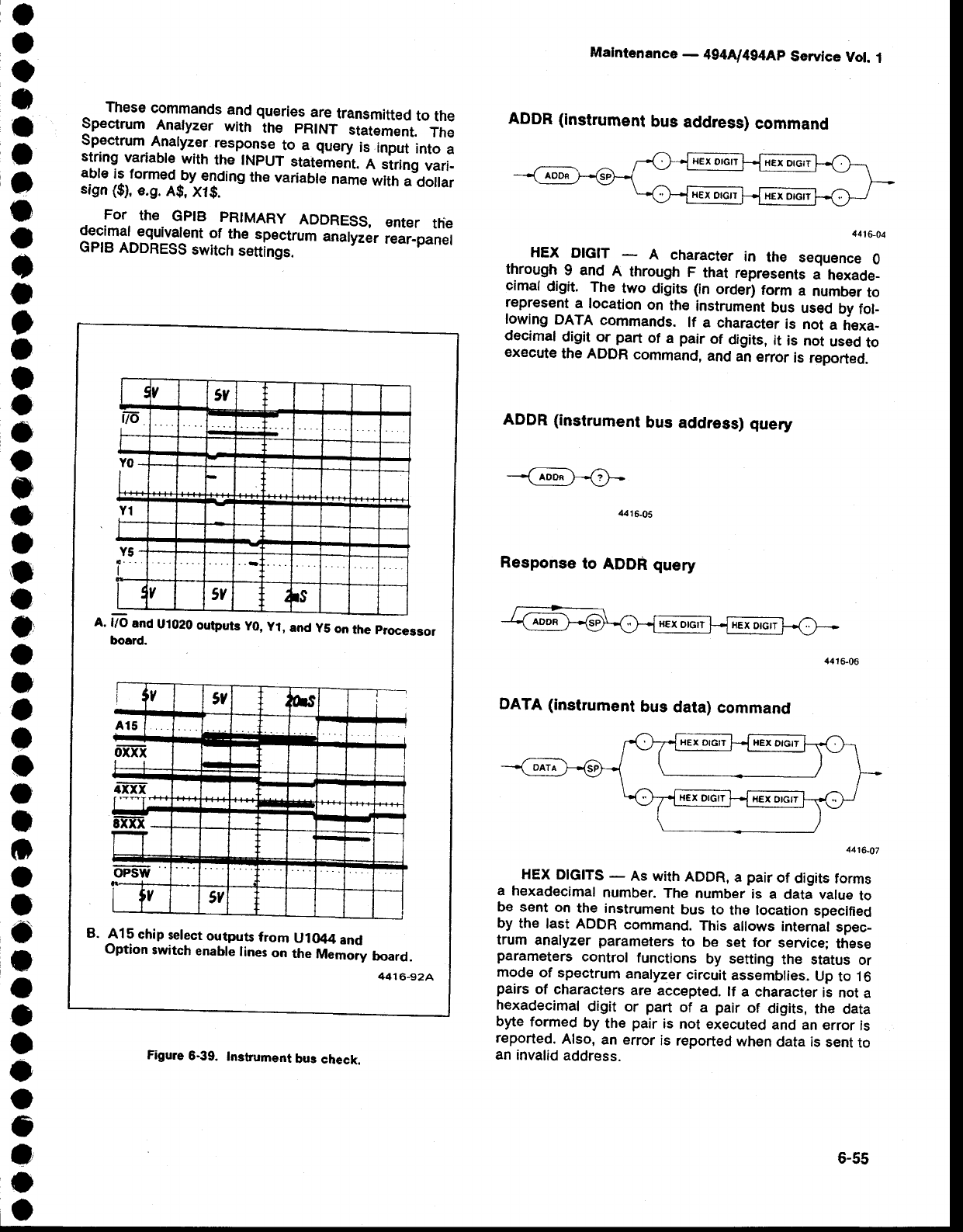

6-39 Instrument

bus check. ..............

6-55

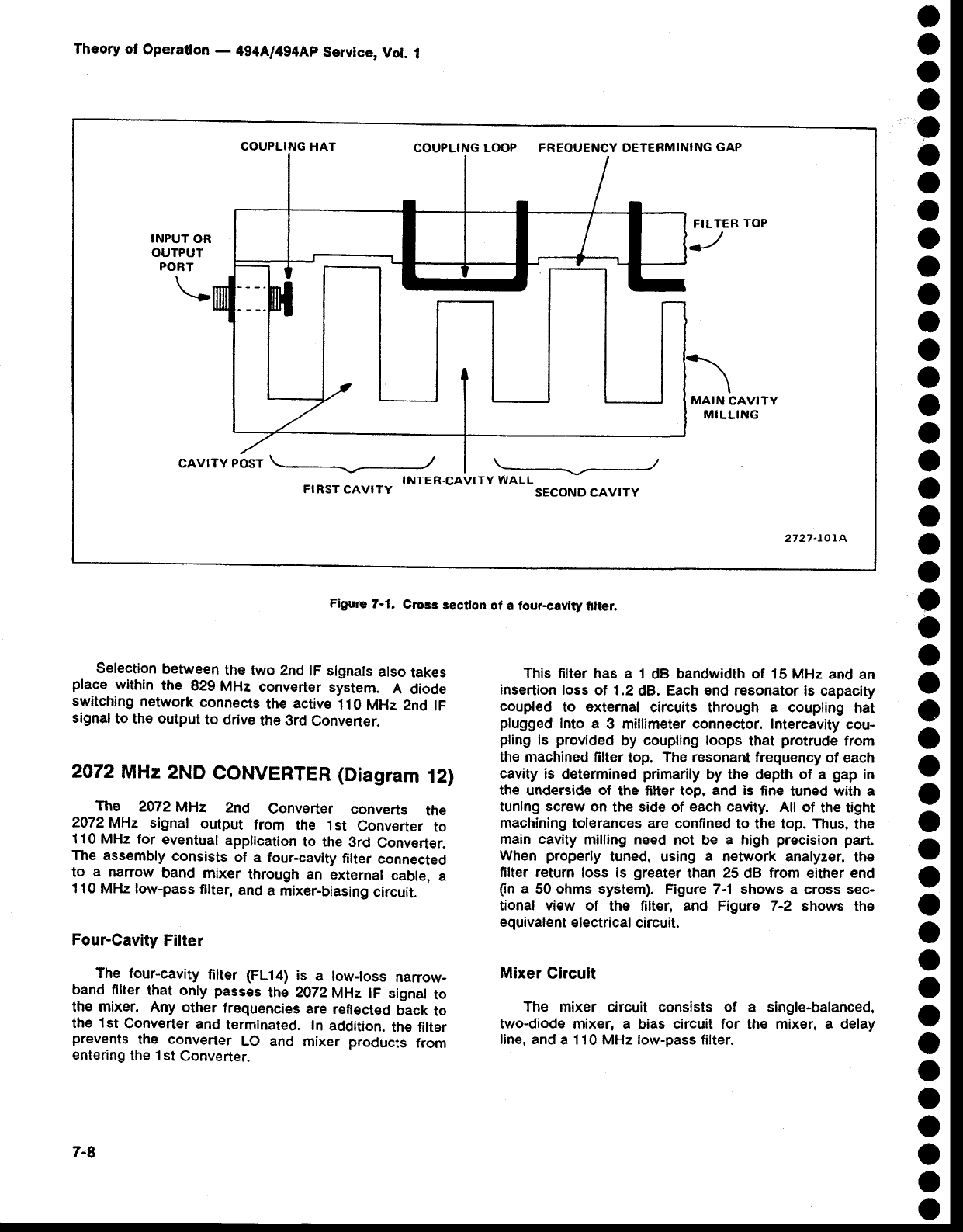

7-1 Cross

section

of

a

four-cavity

filter. .......... ..........

7-g

7-2 Equivalent

circuit of

the

four-cavity

filter. ..................

7-g

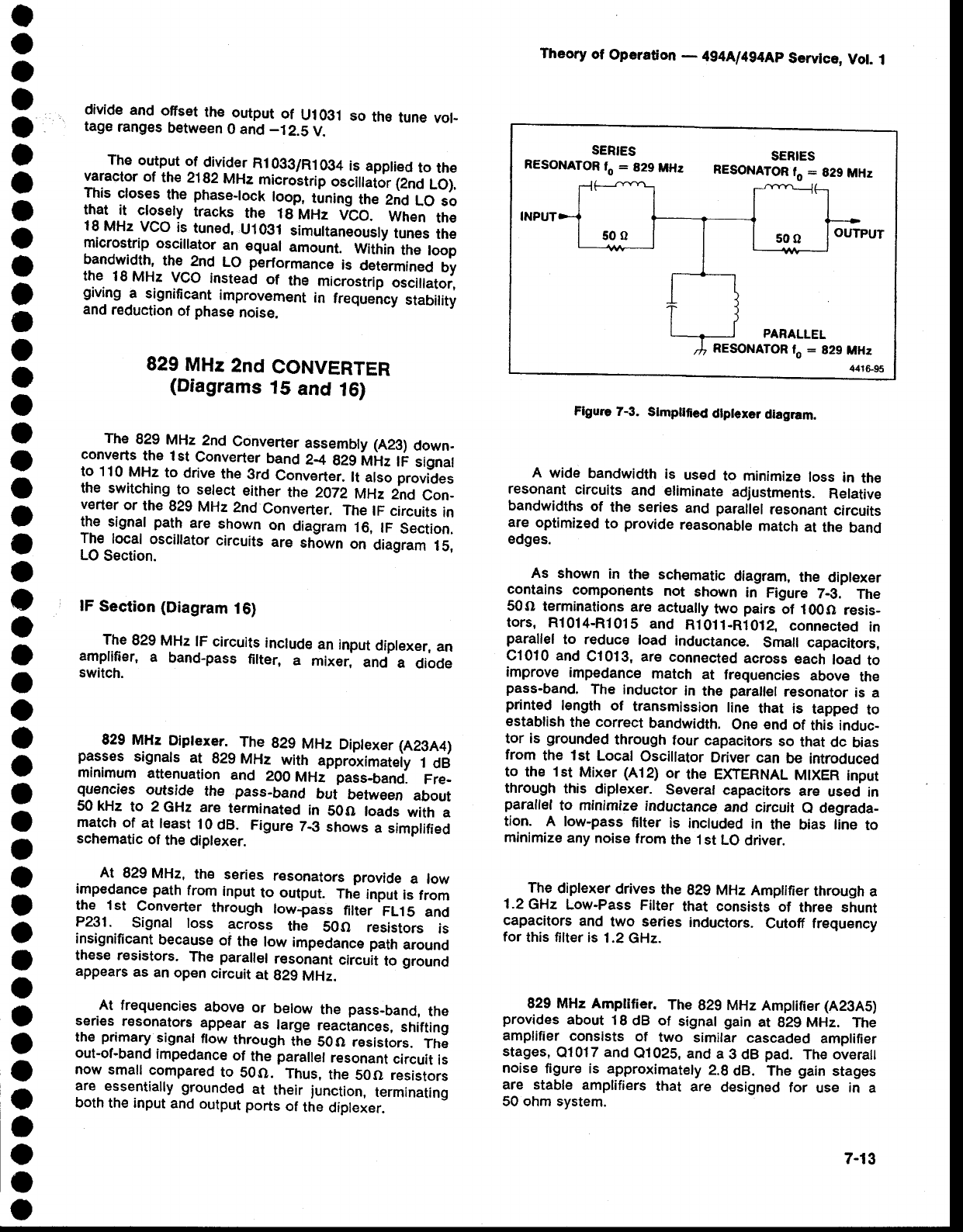

7-3 Simplified

diplexer

diagram. .....

7-19

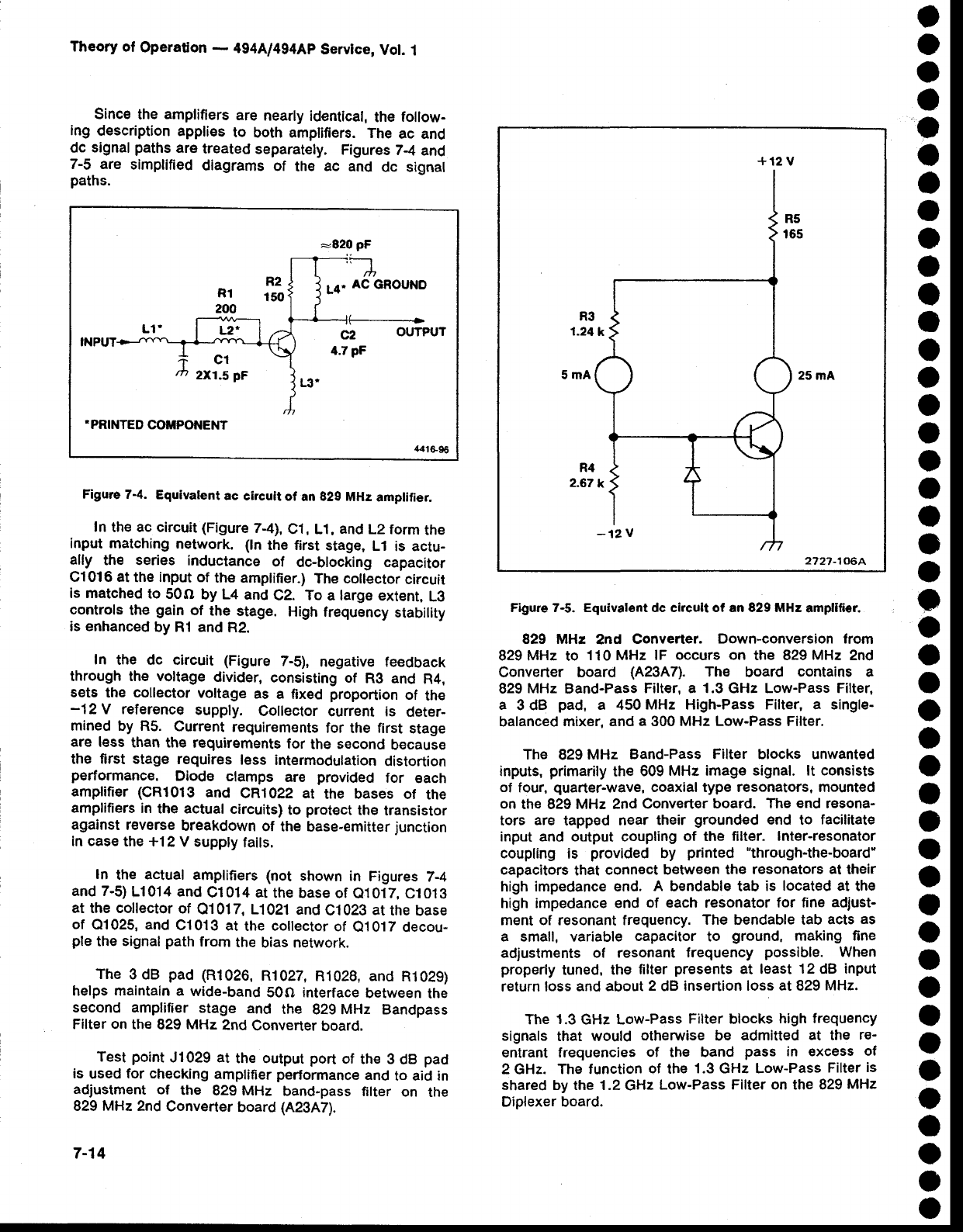

7-4 Equivalent ac

circuit

of

an

829

MHz

amplifier.

..................................

7-1

4

7-S Equivalent

dc circuit

of

an

829 MHz

amplifier.

..........................,.......

7-'t

4

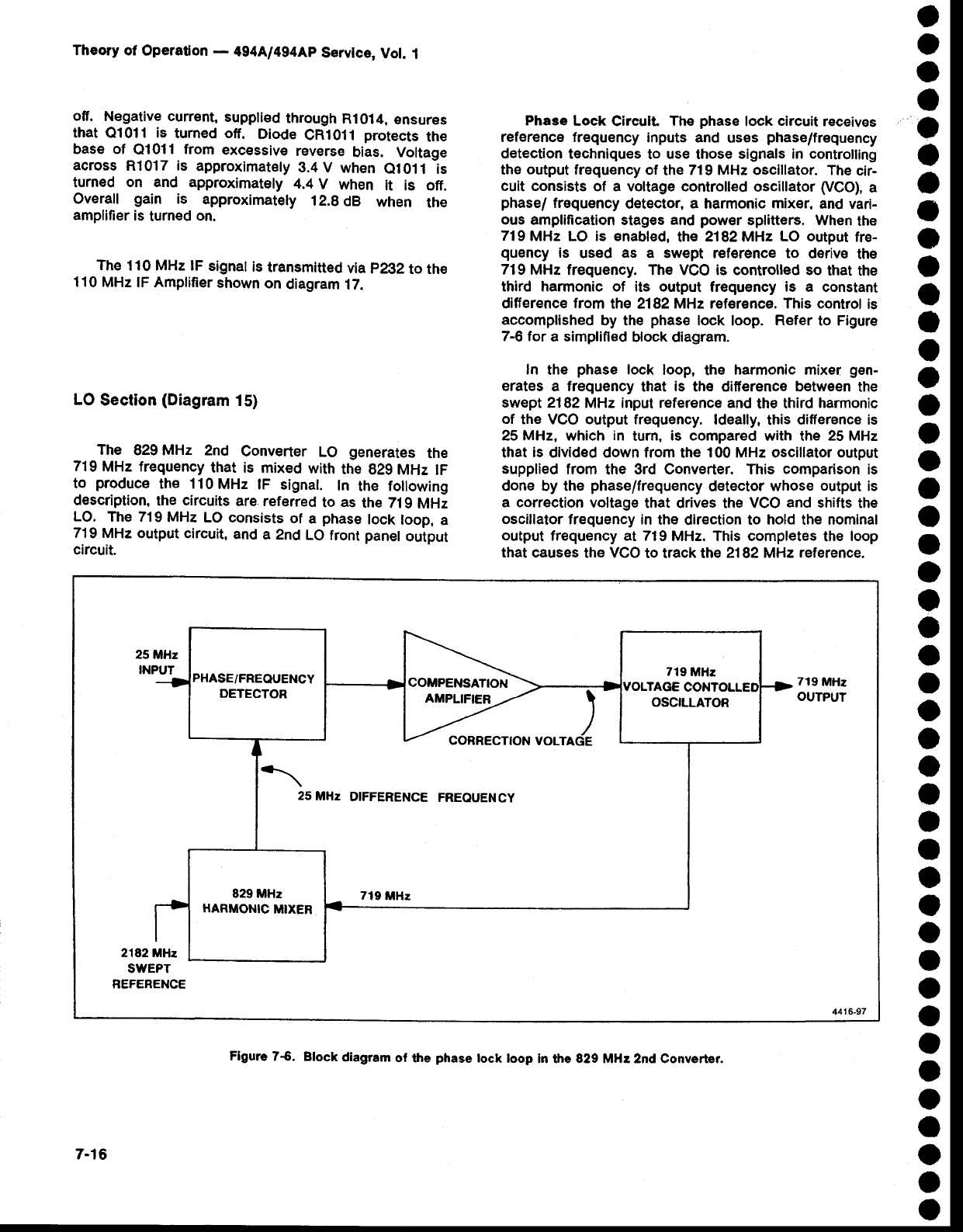

7-6 Block

diagrarn of the

phase

lock loop

in

the

829

MHz

2nd

Converter.

....................7-16

7-7 Bridged'T"attenuator

equivalent

circuit. .....................

7-lg

7-8 Block

diagram

of

a

three

stage

log amplifier. ....................

7-29

7-g Log

amplifier

gain

curve

showing

break

points .................

7-90

7-14 Curve

showing

end-of-range

for a log amplifier. ....................

7-gO

7-11 Simplified

detector

circuit. ........,2-gz

6-26

6-27

6-28

6-29

6-30

6-31

xl

494A/494AP

Servlce

Vot. 1o

I

o

a

I

I

o

a

o

I

I

I

o

o

O

t

o

o

o

I

a

I

o

o

I

o

o

o

o

)

o

o

a

o

o

I

a

o

I

o

o

o

o

t

LIST

OF

ILLUSTRATIONS

(Cont.)

Page Figure

Figure

7-12 Selection of disptay

position

on

the

log

scale. .....7-94

7-13 Functional

diagram

showing

the

sp€ctrum

analyzer

and 1405

TV

Sideband Adapter

system. ........

7€6

7-14 Simplified

diagram

of

video filter. .............

Z-39

7-15 Vertical

control

lC

bfock diagram.

.............. .............241

7-16 Horizontalcontrol

lc

bfock diagram.

.............. .............145

7-17 Block diagram

of

crt

readout. .............7-52

7-18 Character on/off

timing ...............

7-53

7-1

I Character scan.

.,........ ...............

7-54

7-20 Charactergenerator

block diagram.

............... ............ 7-5S

7-21 Character

timing

diagram. ......... 7-56

7-22 Frequency

dot

marker

simplified

diagram

with

timing

waveforms.

...................

7-Sg

Page

7-23 Simplified

digital-to-analog

converter. ....-........

7-66

7-24 Simplified span

decade attanuator.

.............. 7-67

7-25 DAC variance

graph. ................7-73

7-26 Simpfffied

tune

voltage converter.

................ 7-74

7-27 Simplified

schematic

of harmonic

mixer.

...... 7-79

7-28 Block

diagram of a basic synthesizer.

.........

7-80

7-29 Basic

block

diagram

of a -rN

synthesizer

with a variable

modulus

prescaler.

...............

7-80

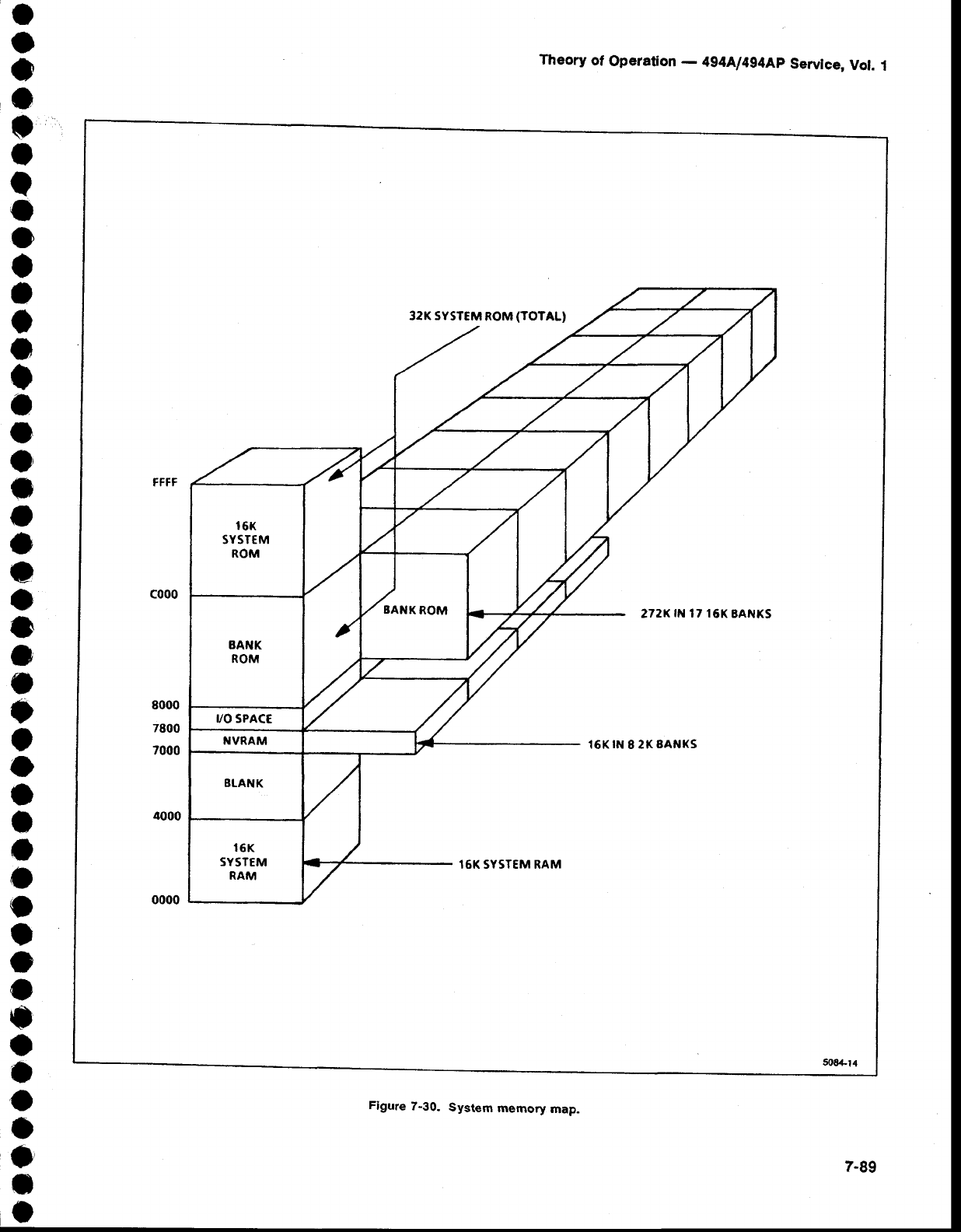

System memory map. .......... .... 7-89

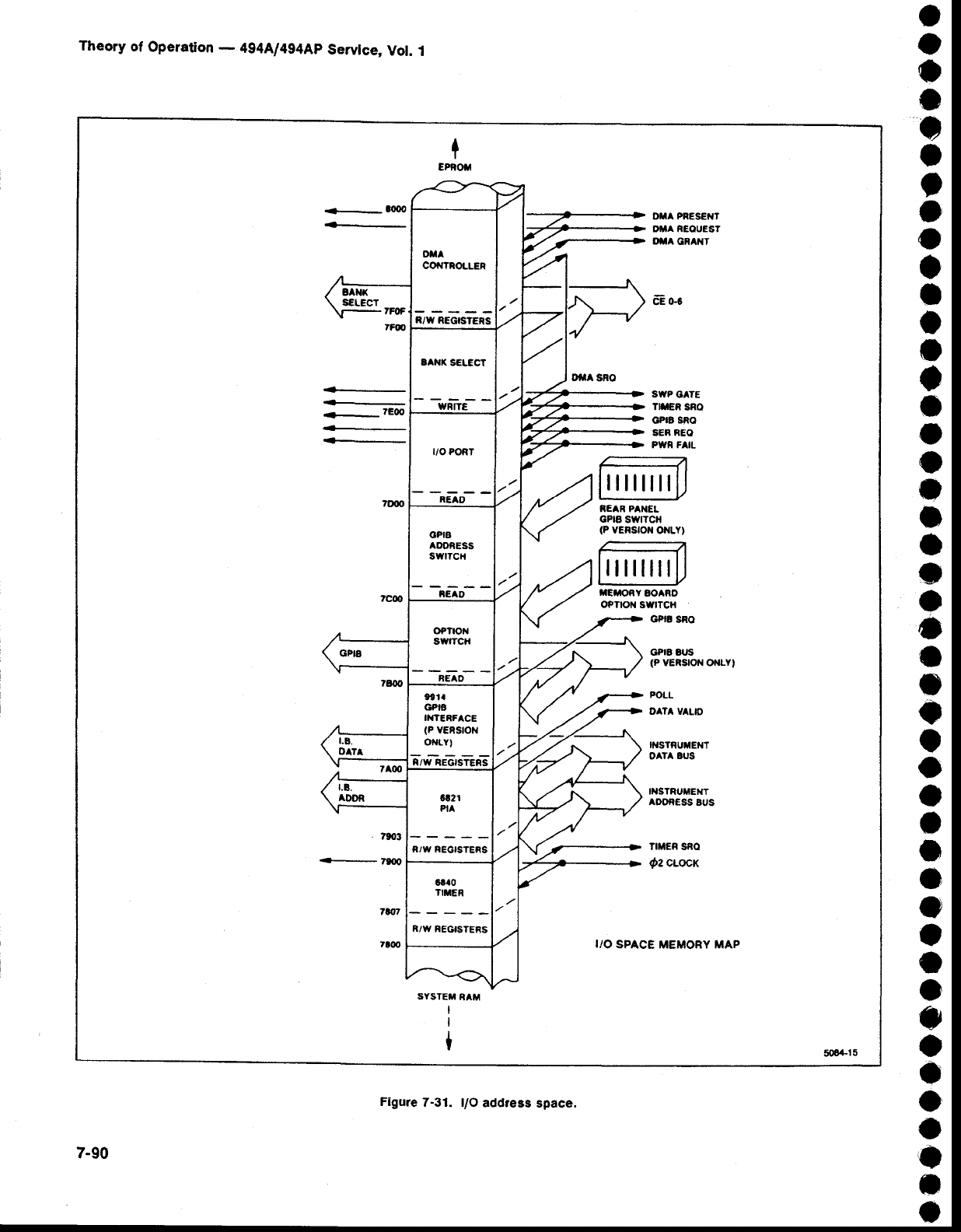

l/O address

spac€. ...................7-90

PIA

and

Timer address map. .... 7,91

Options switch

bank

on

the Memory

board. ..............

7-95

Primary regulator

7€0

7-31

7-32

7€3

7-34 input/output

waveforms. ...........

7-104

7-35 Timing waveforms for soft-start

circuit.

.......

7-105

8-1 Int€rnational

Power

cord options.

................

8-1

xil

o

a

o

a

o

O

I

I

O

o

o

I

o

I

t

I

I

I

I

I

o

I

o

a

I

o

t

o

I

t

a

o

o

o

a

o

I

o

o

o

o

o

o

o

494A1494AP

Service

Vot.

1

Table page

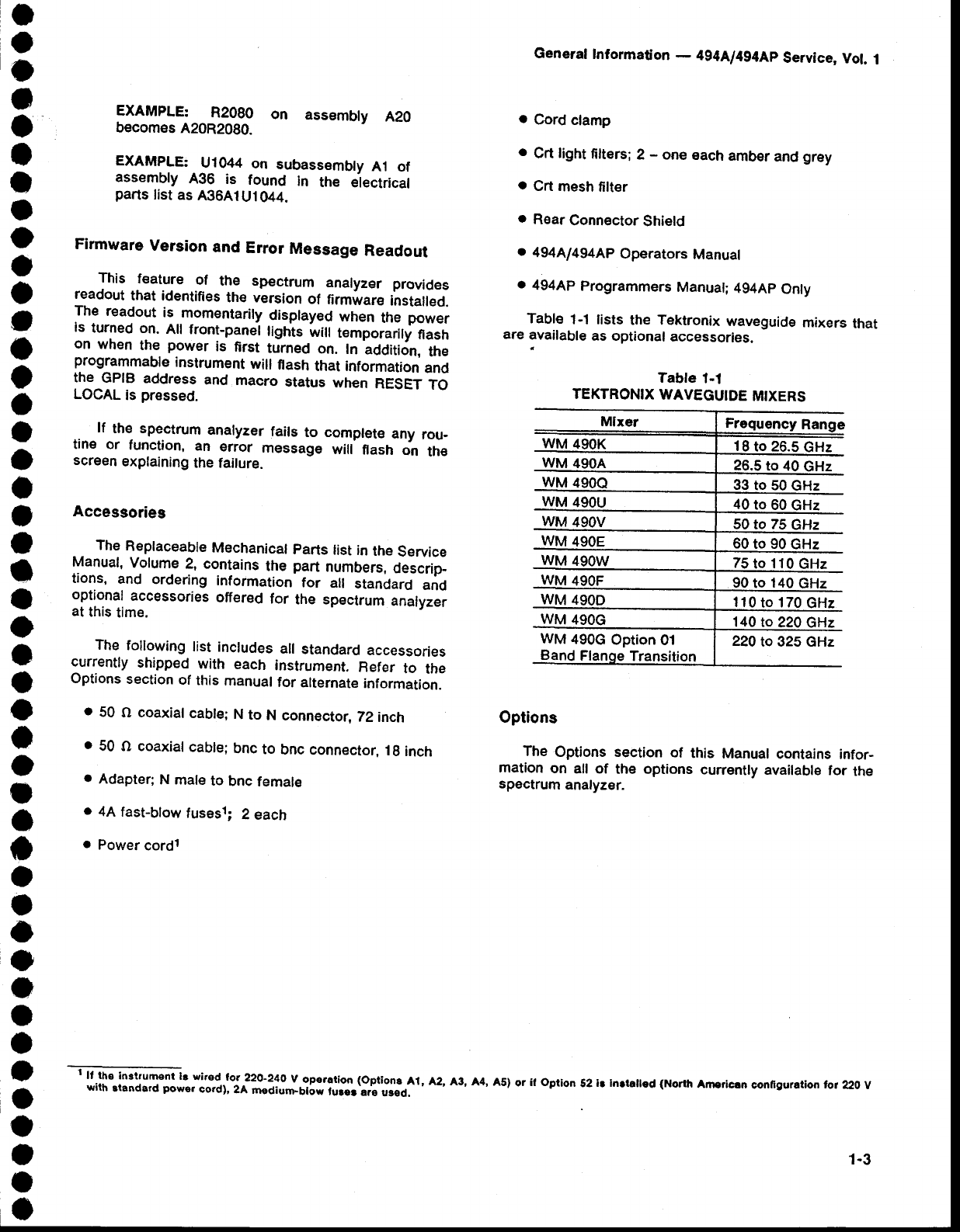

1-1 TEKTRON'X

WAVEGUIDE

MIXERS

..............

1-3

2-1 FREQUENCY

RELATED

CHARACTERTSTTCS ..................

2-1

2-2 AMPLITUDE

RELATED

CHARACTERTSTTCS .................

2_6

2-3 INPUT

SIGNAL

CHARACTERTSTTCS ..................

2_11

24 OUTPUT

SIGNAL

CHARACTERTSTICS ........,.........

2_13

2-5 GENERALCHARACTERTSTTCS

...................

2_15

2-6 POWER

REQUTREMENTS

............................

2_15

2.7 ENVIRONMENTAL

CHARACTERTSTTCS ........,.........

2-16

2-8 pHySIcALCHARACTERIST|CS

..................2-17

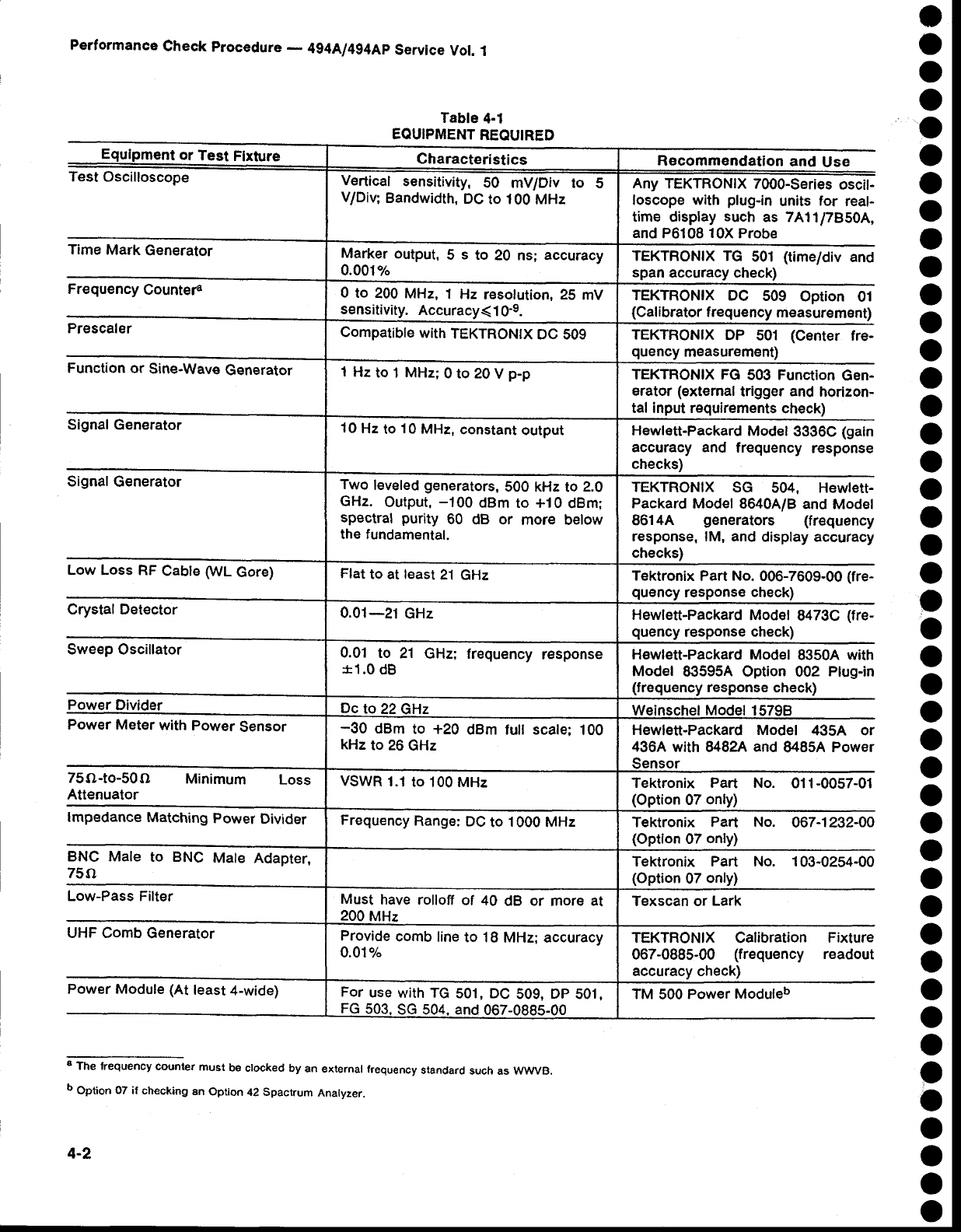

4.1 EQUIPMENT

REQUIRED ..........4-2

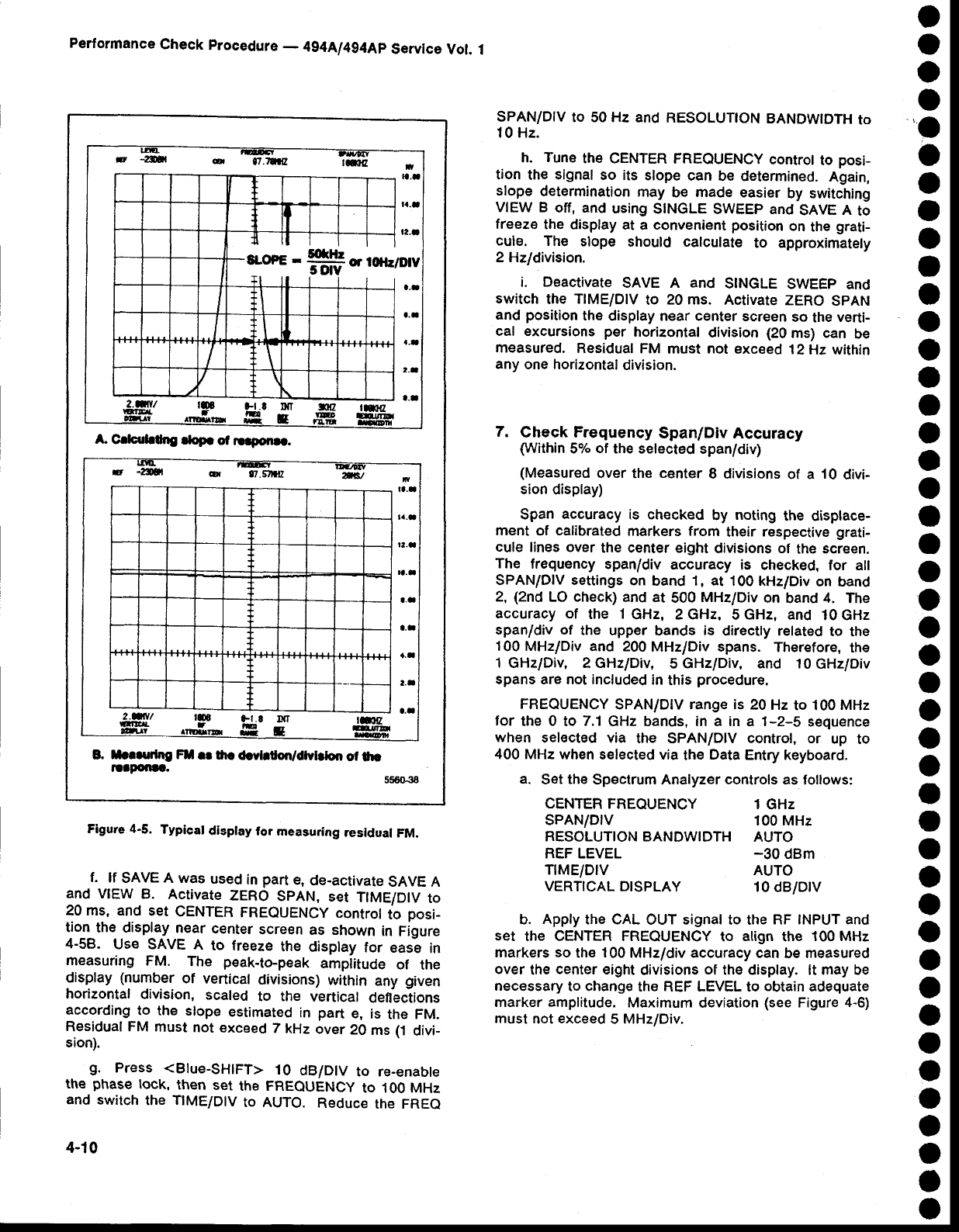

4.2 CENTER FREQUENCY

ACCURACY

CHECK

pOtNTS

(1st

LO

UNLOCKED)

.........

4-a

4-3 SPAN/D|V

VERSUS

TIME

MARKERS

FOR

SPAN/DIV

ACCURACY

CHECK .................4-11

44 FREQUENCY

RESPONSE

CHECK

SETTINGS

FOR

BANDS

3_5 ..........

.,..........

4-17

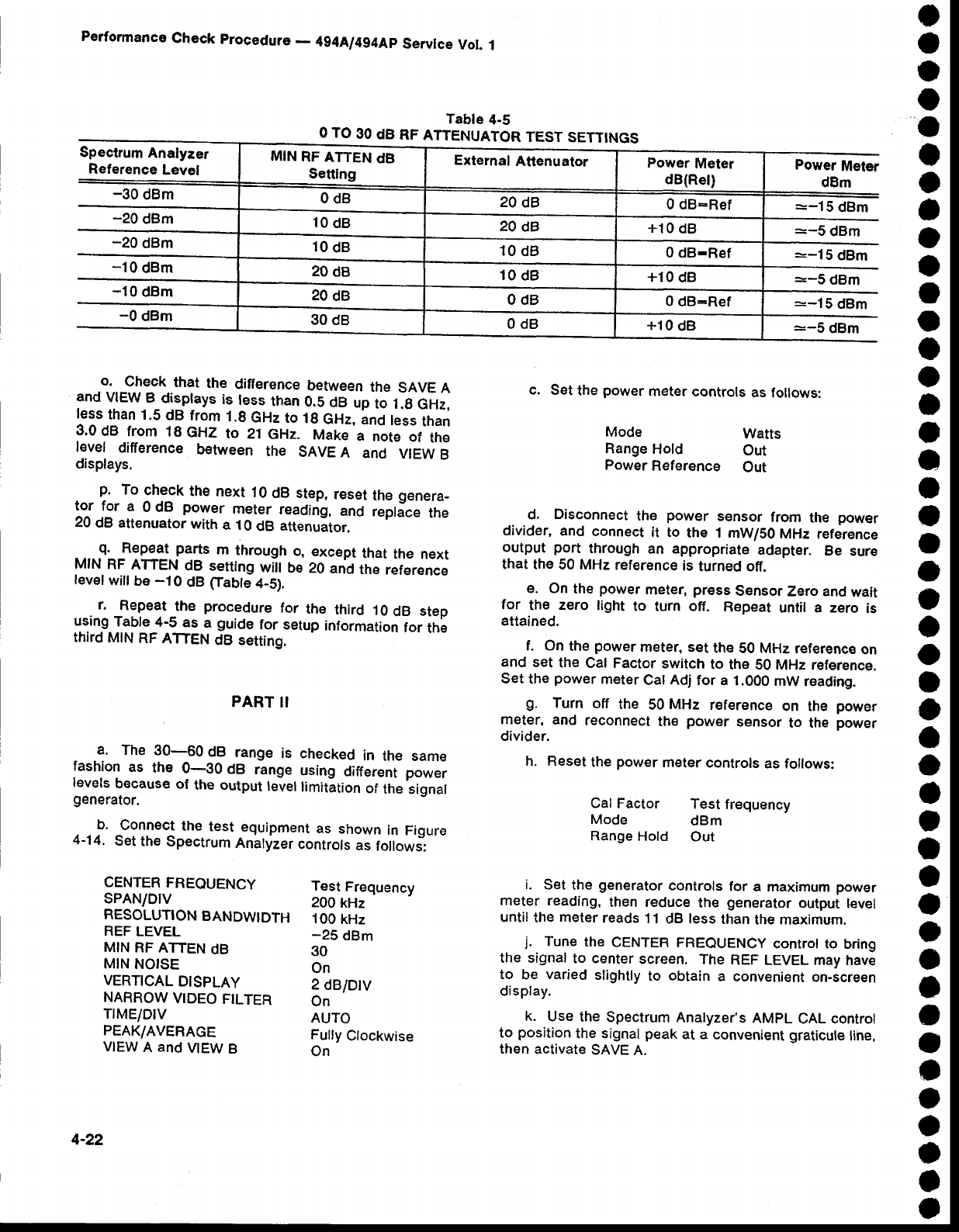

4.5 O

TO

30

dB RF

ATTENUATOR

TEST

SETT|NGS

........... ...........

4-22

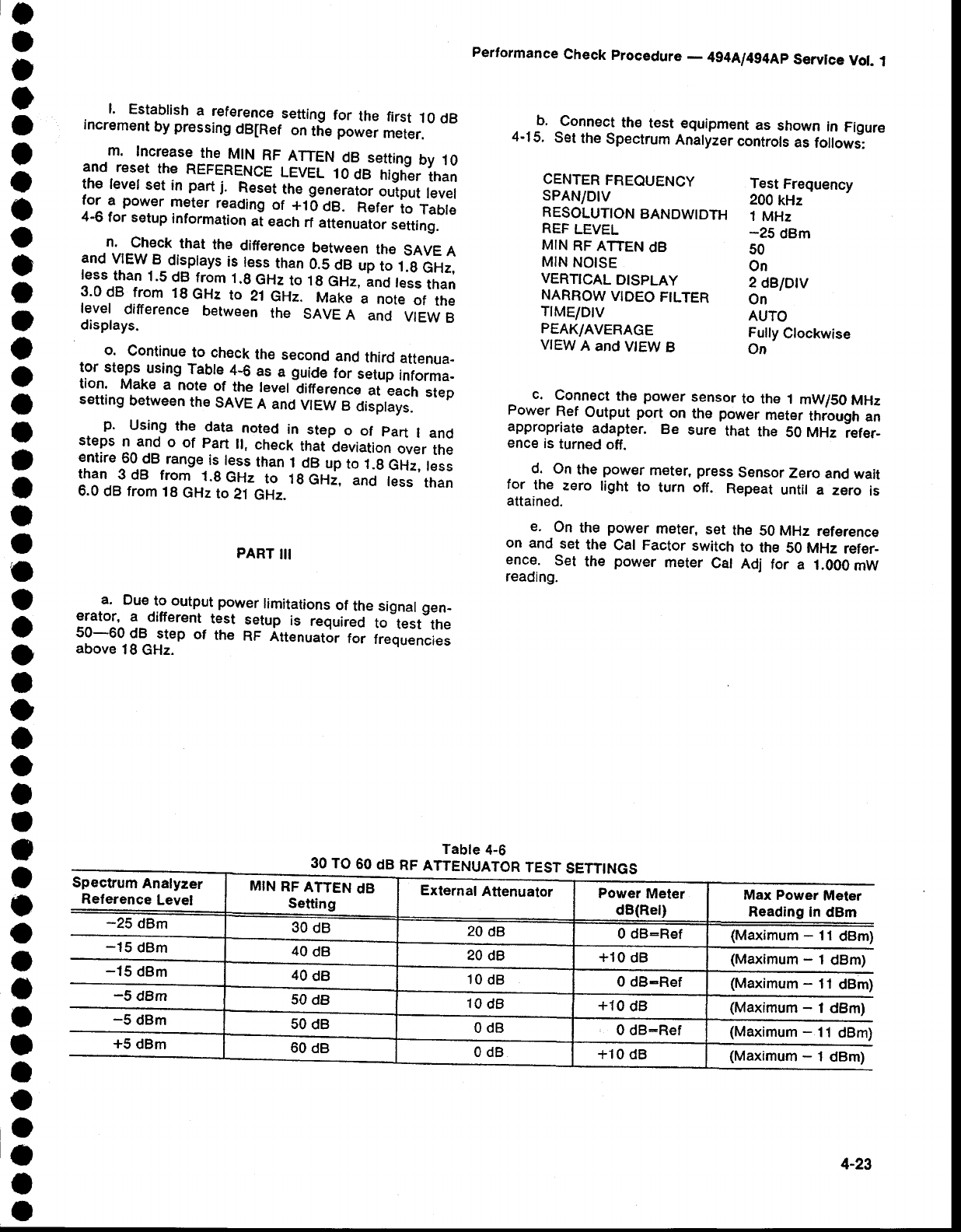

4.6 30 TO

60

dB

RF

ATTENUATOR

TEST

SETTINGS ..4-2g

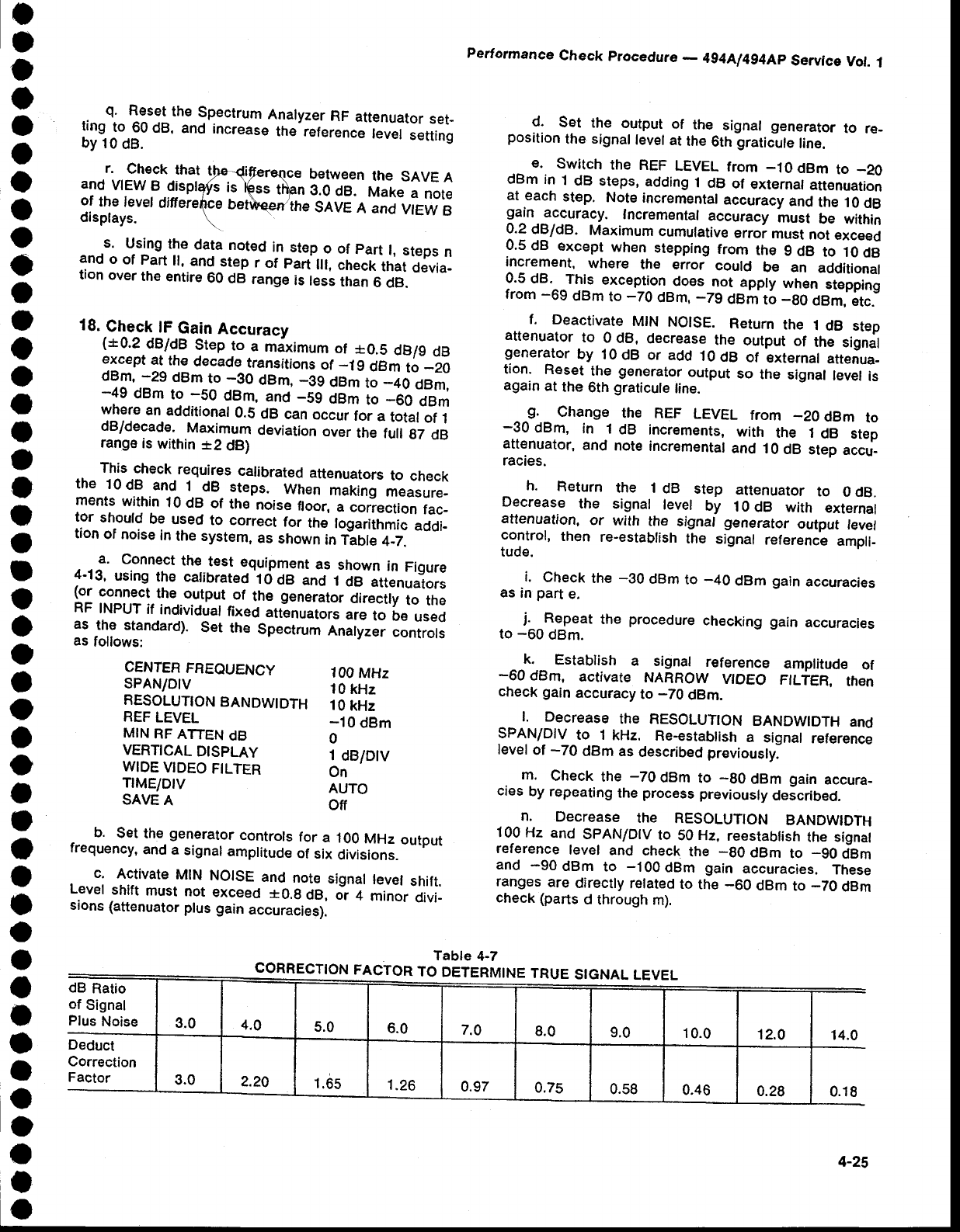

4-7 CORRECTION

FACTOR

TO

DETERMINE

TRUE

SIGNAL

LEVEL

.............

4-25

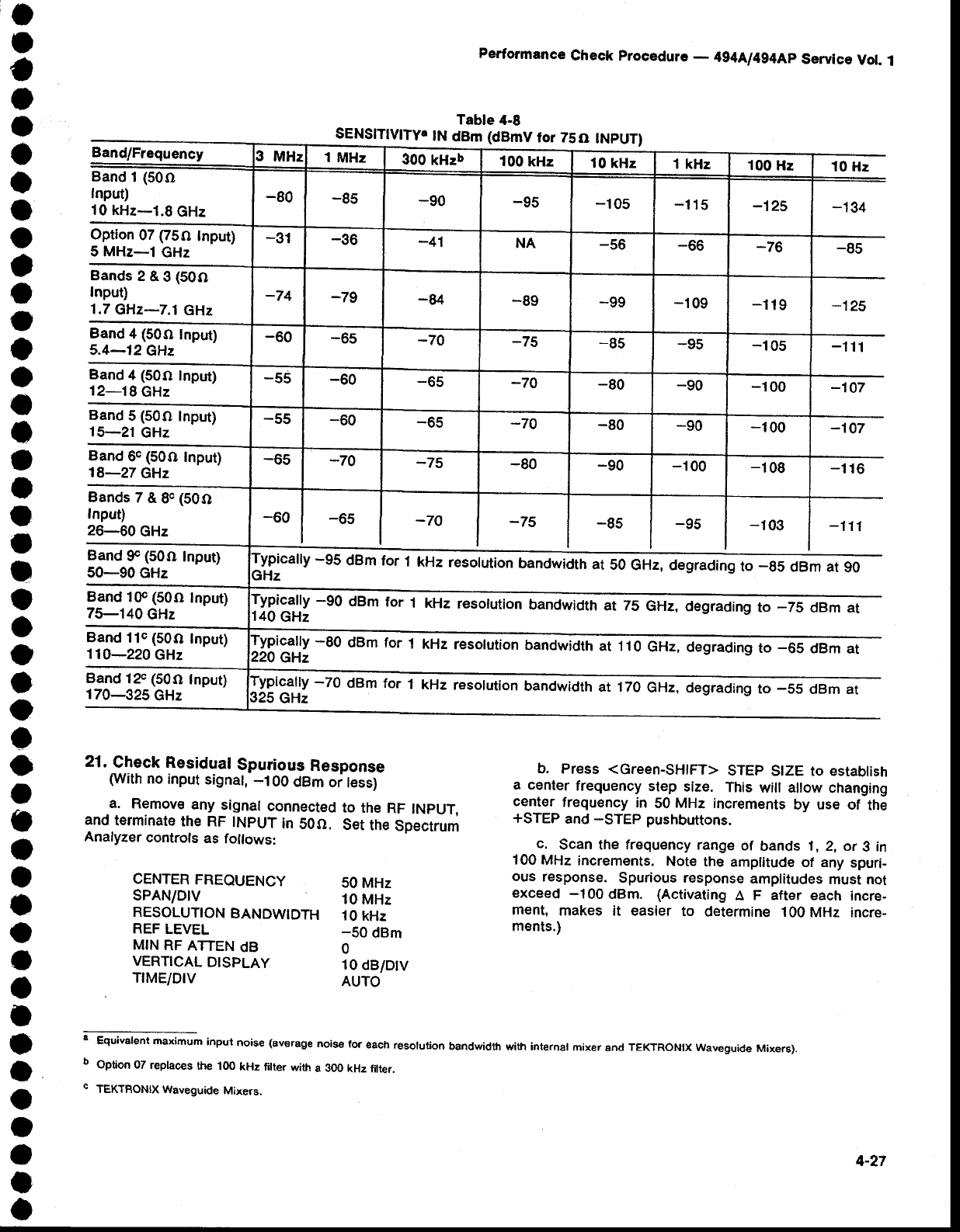

4-8 SENSlTlury .........4_27

EQUIPMENT

REQUIRED ..........

5-2

powER

suppLy ToLERANCES

.................

5_3

FTLTER

ADJUSTMENTS

...............................

5-1 I

EXT MIXER

BAND

LEVELING

ADJUSTMENTS

............. ..........

5-25

RELATIVE

SUSCEPTIBILITY

TO

STATTC DTSCHARGE

DAMAGE

...................

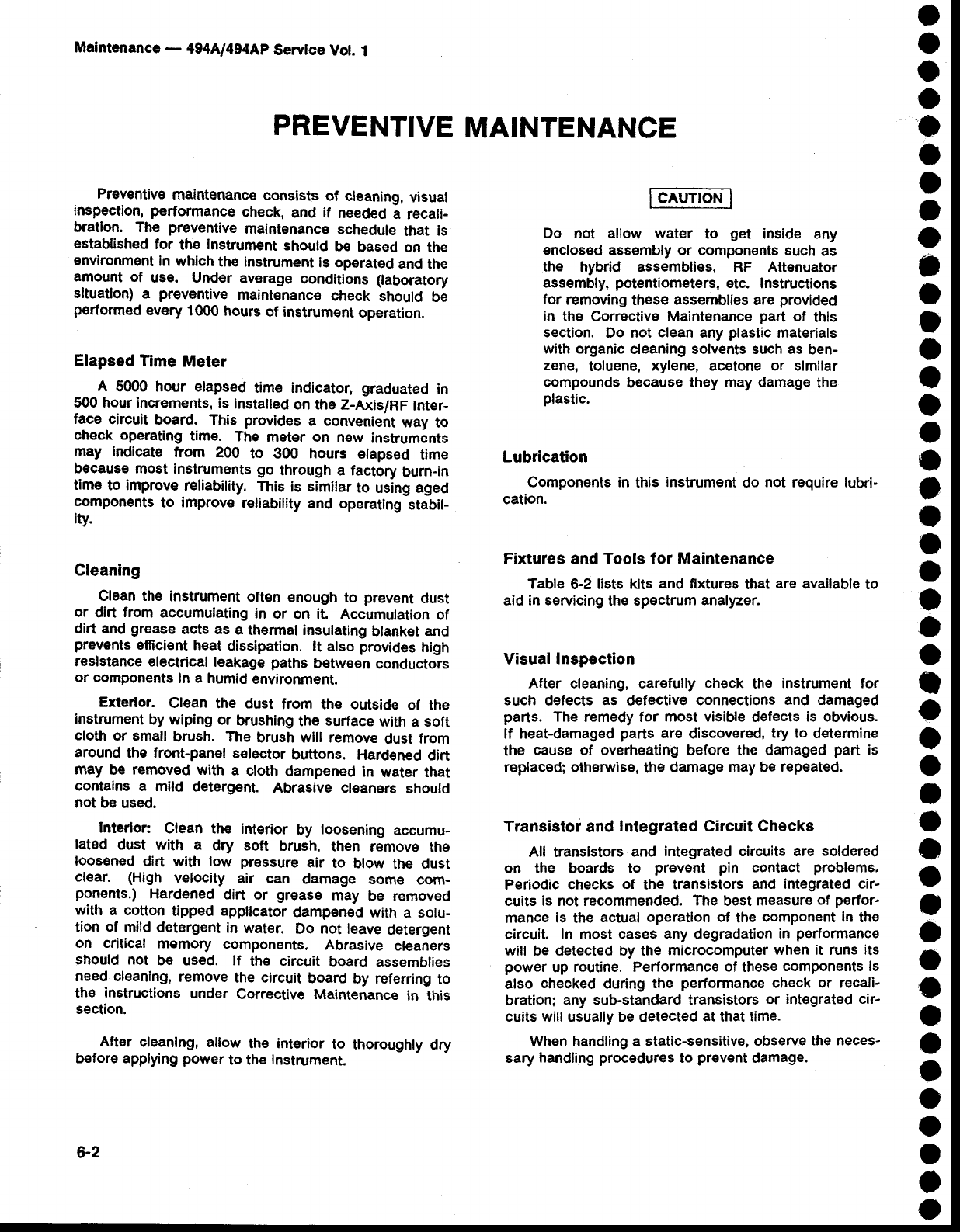

6_1

SERVICE

KITS

AND

TOOLS ....

6-3

POWER

SUPPLY

RANGES ......

6.8

SELECTED

COMPONENTS

..........................

6-1 6

SERVICING

TOOLS

FOR

BOARDS

WITH

SURFACE

MOUNTED

COMPONENTS

............. ...........6_17

page

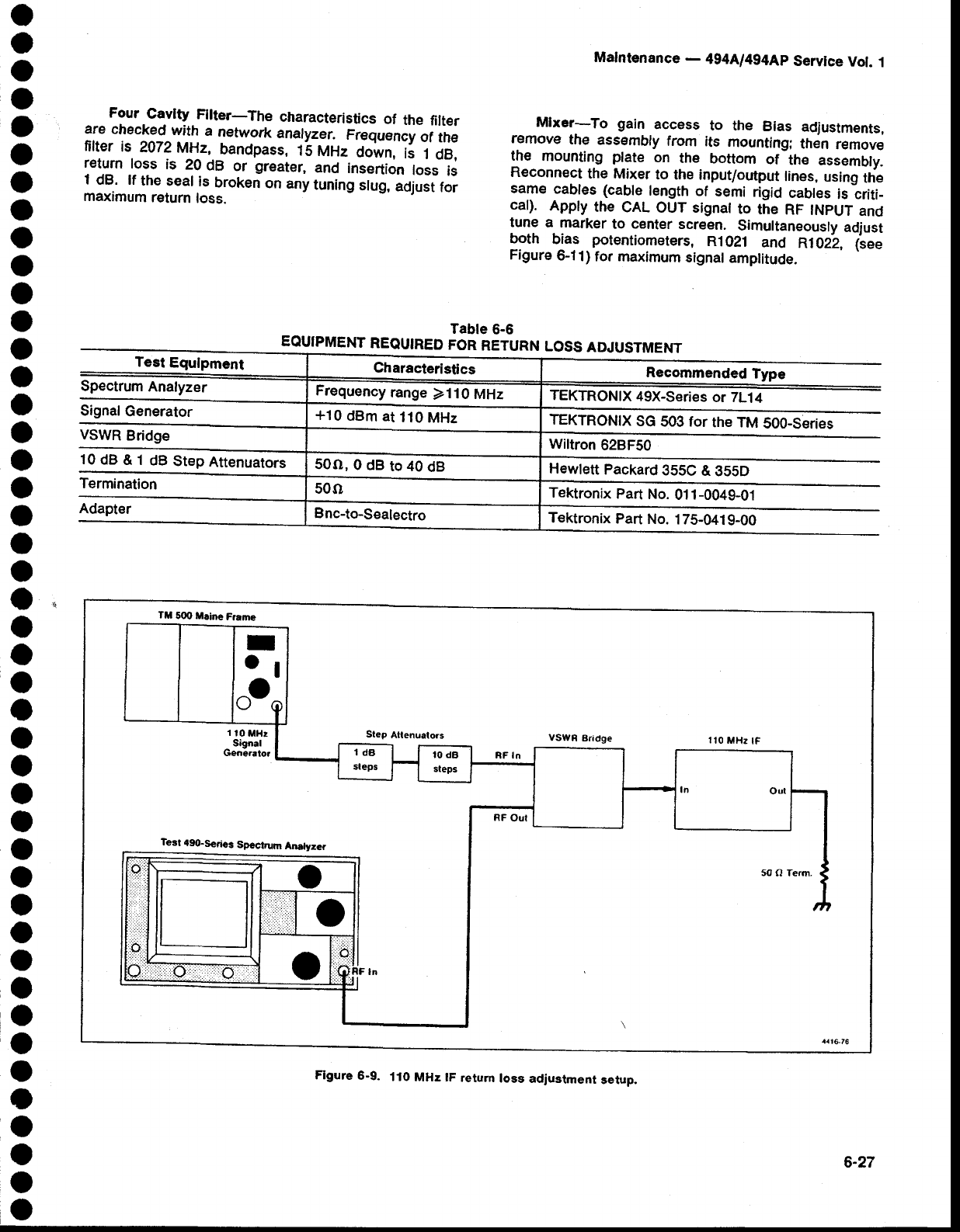

EQUIPMENT

REQUIRED

FOR

RETURN

LOSS ADJUSTMENT ...............6-27

EOUIPMENT

REQUIRED FOR

2nd LO

CALIBRATION

.................................

6-94

EQUIPMENT

REQUIRED FOR

CALIBRATING

THE

16-20 MHz

PHASE

LOCK

CtRCUtr

................................

6-39

6-9 EQUIPMENT

FOR

ADJUSTING

FIRST

CONVERTER

BIAS AND

START

SPUR

AMPLITUDE ......

645

6-10 OPTION

SWTTCH

SETTTNGS ...6-50

6-11 RAM

TEST ...........6-51

6-12 ROM TEST ...........

6-51

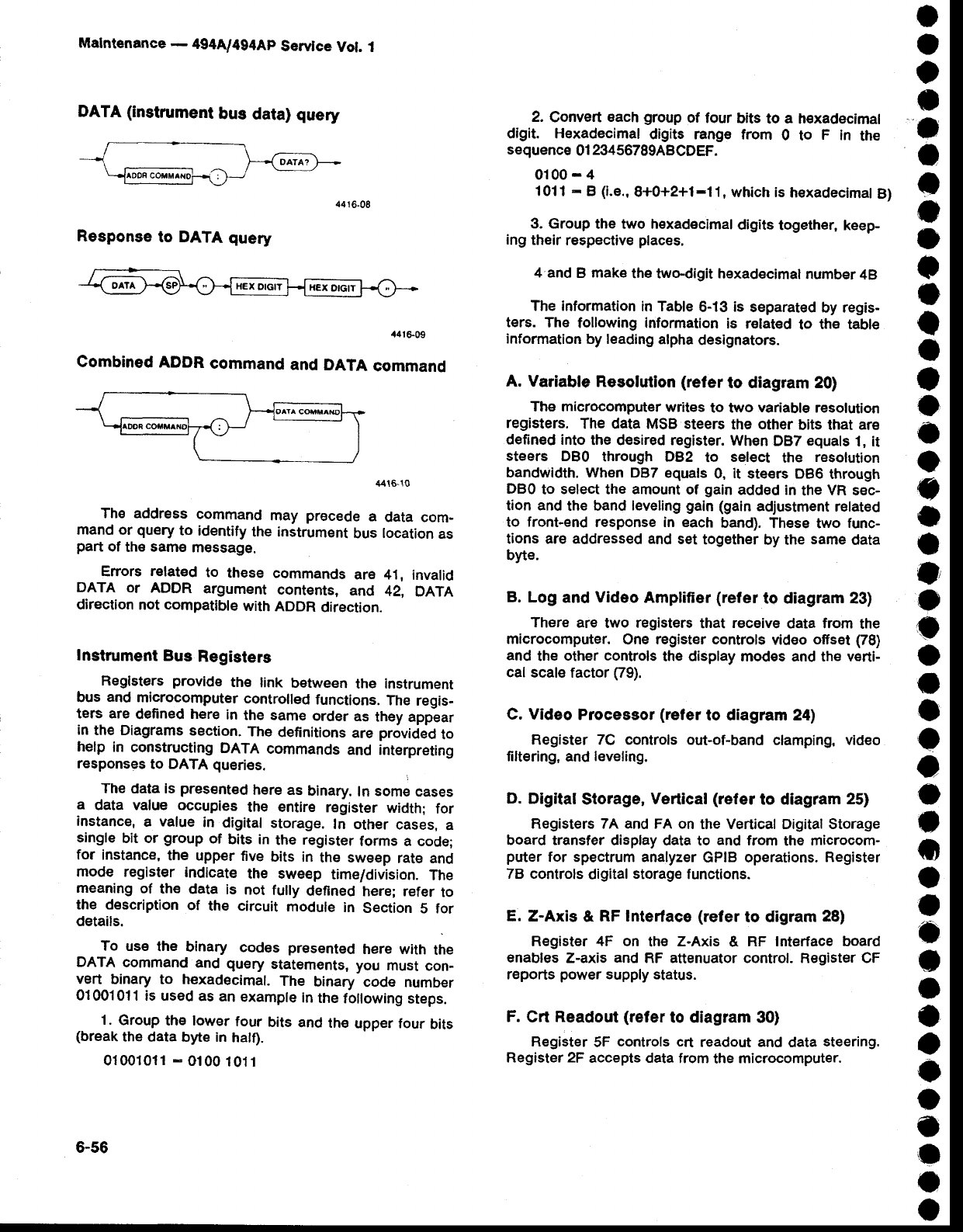

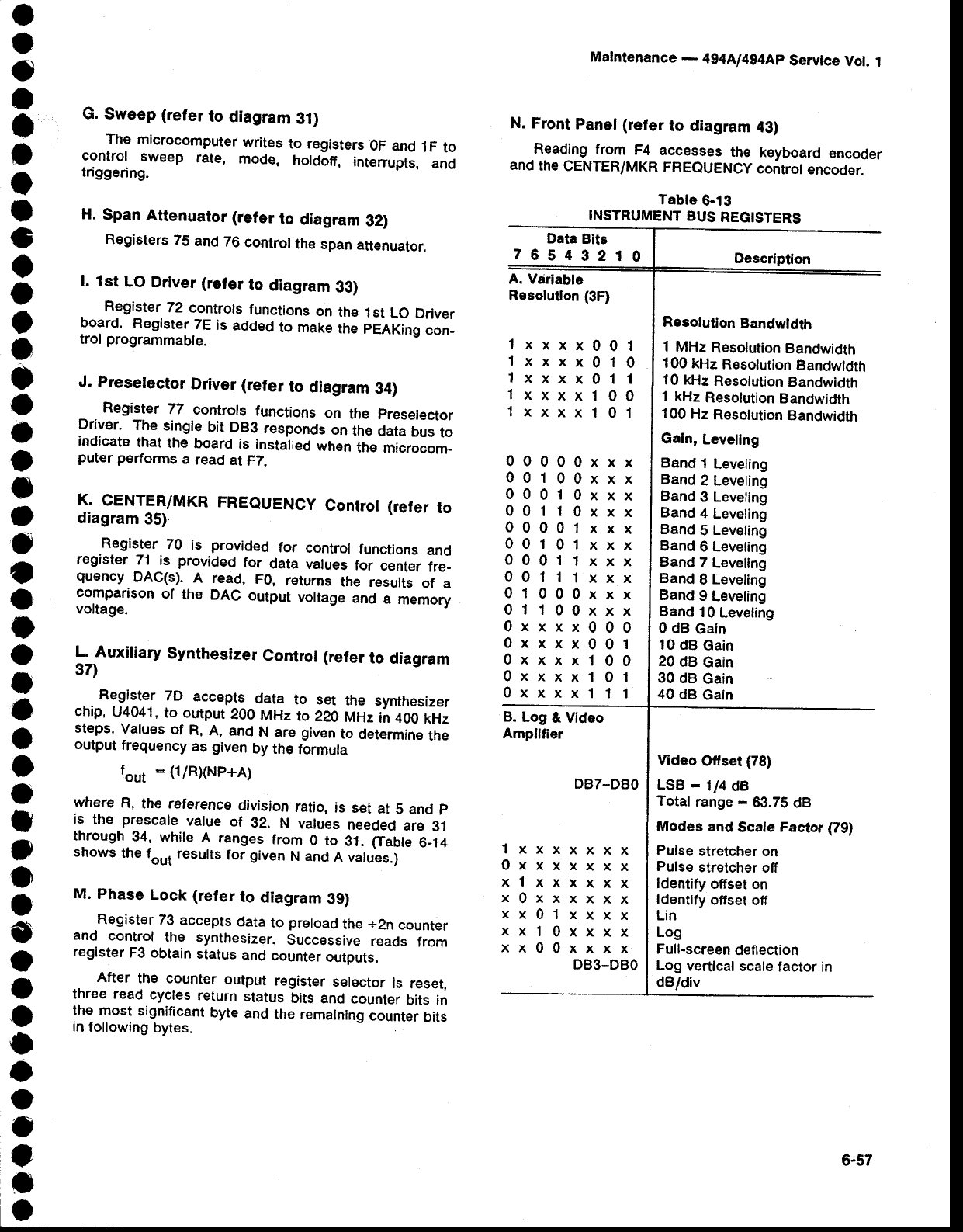

6.13 INSTRUMENT

BUS REGISTERS

..................

6-57

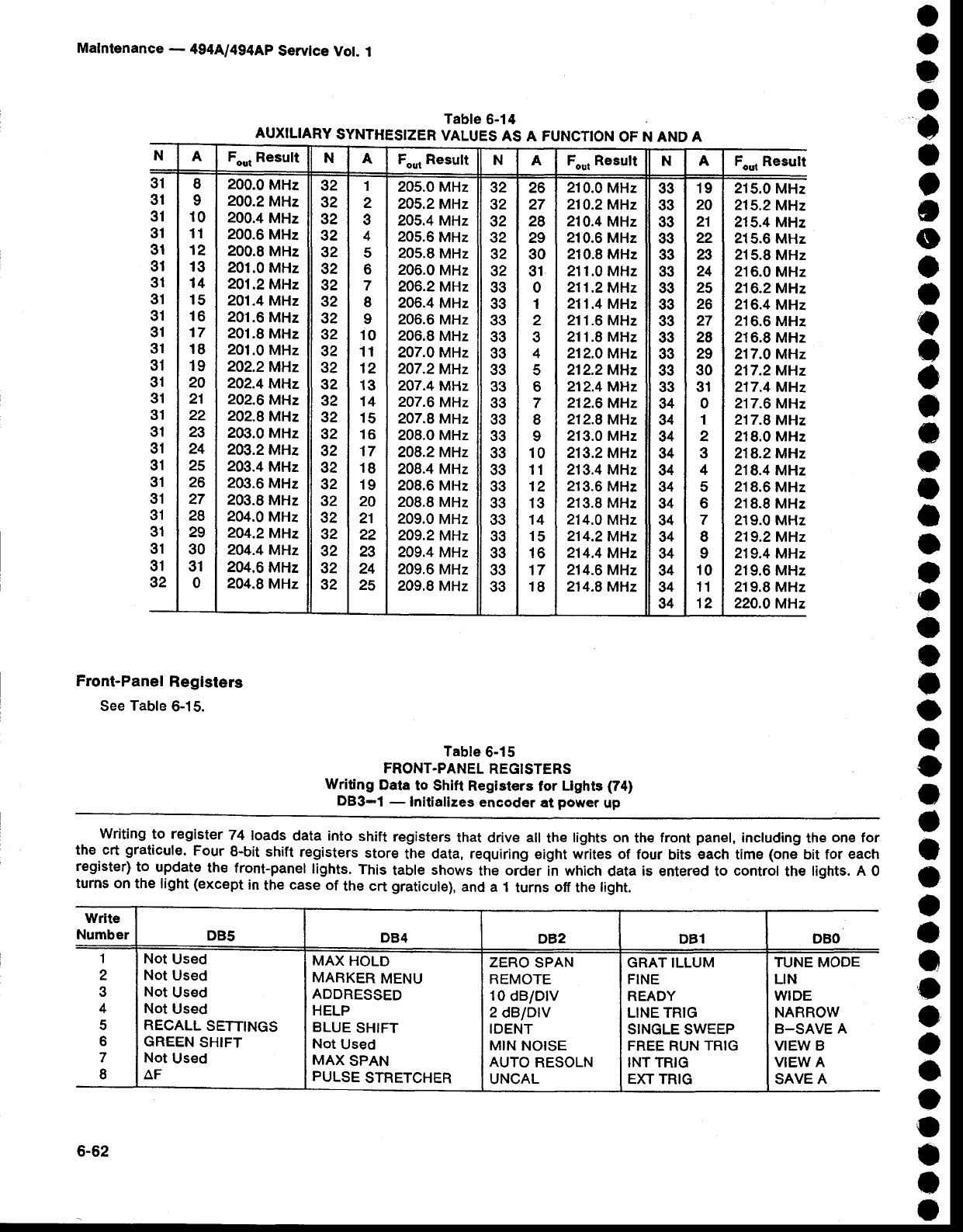

6.14 AUXILIARY

SYNTHESIZER

VALUES

AS

A FUNCTTON

OF N AND

A .....................

6-62

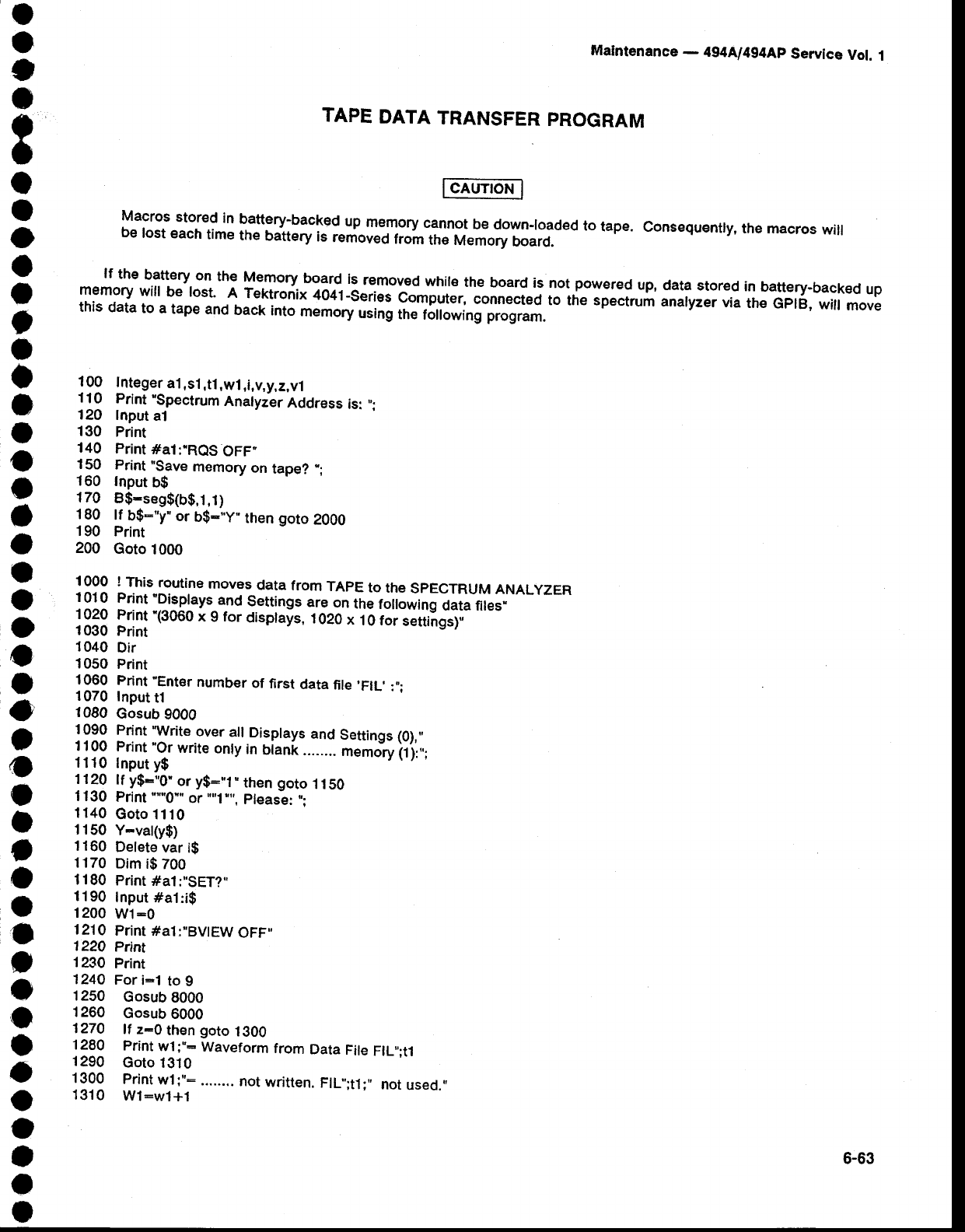

6-15 FRONT-PANEL

REGrSTERS

........................

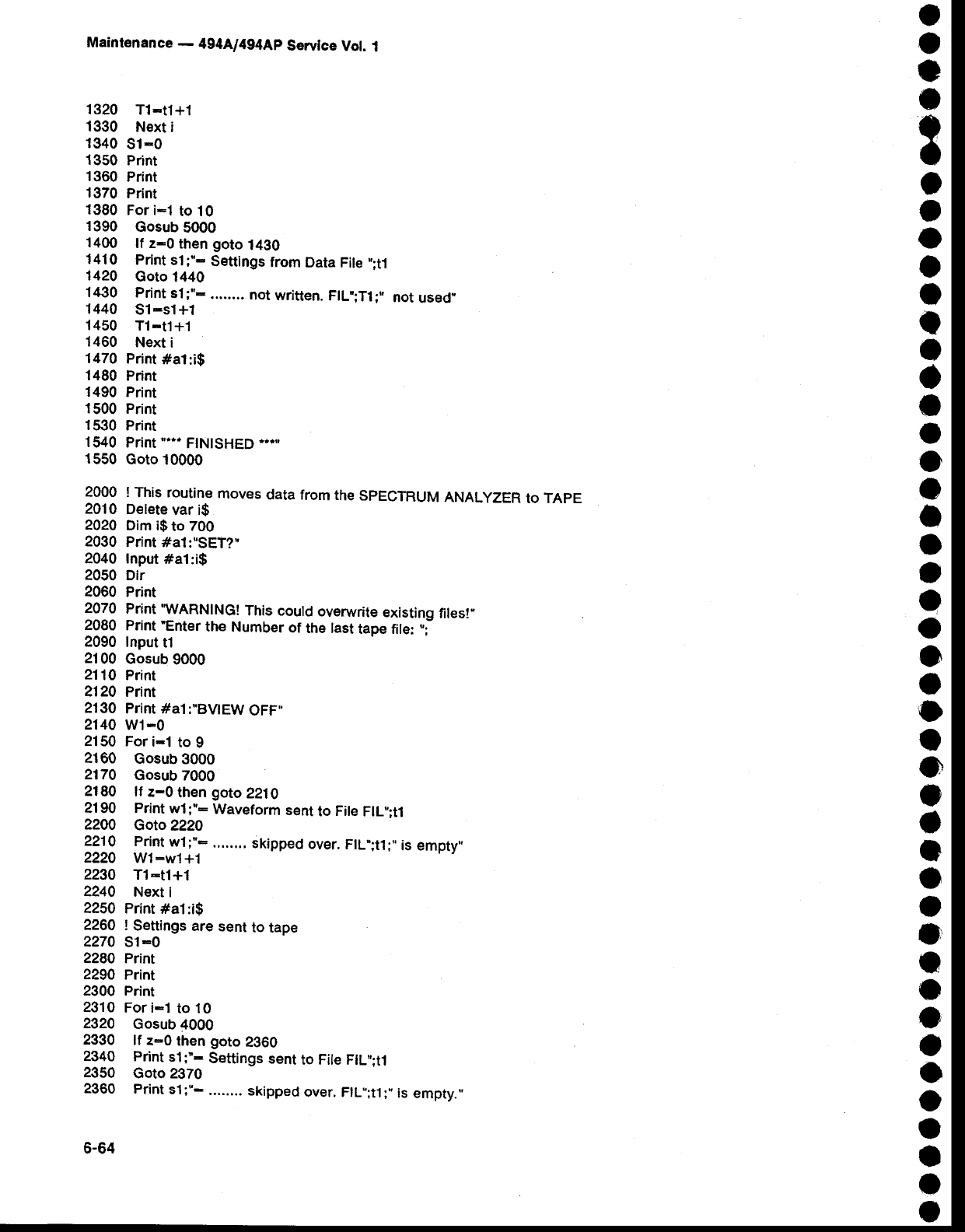

6-62

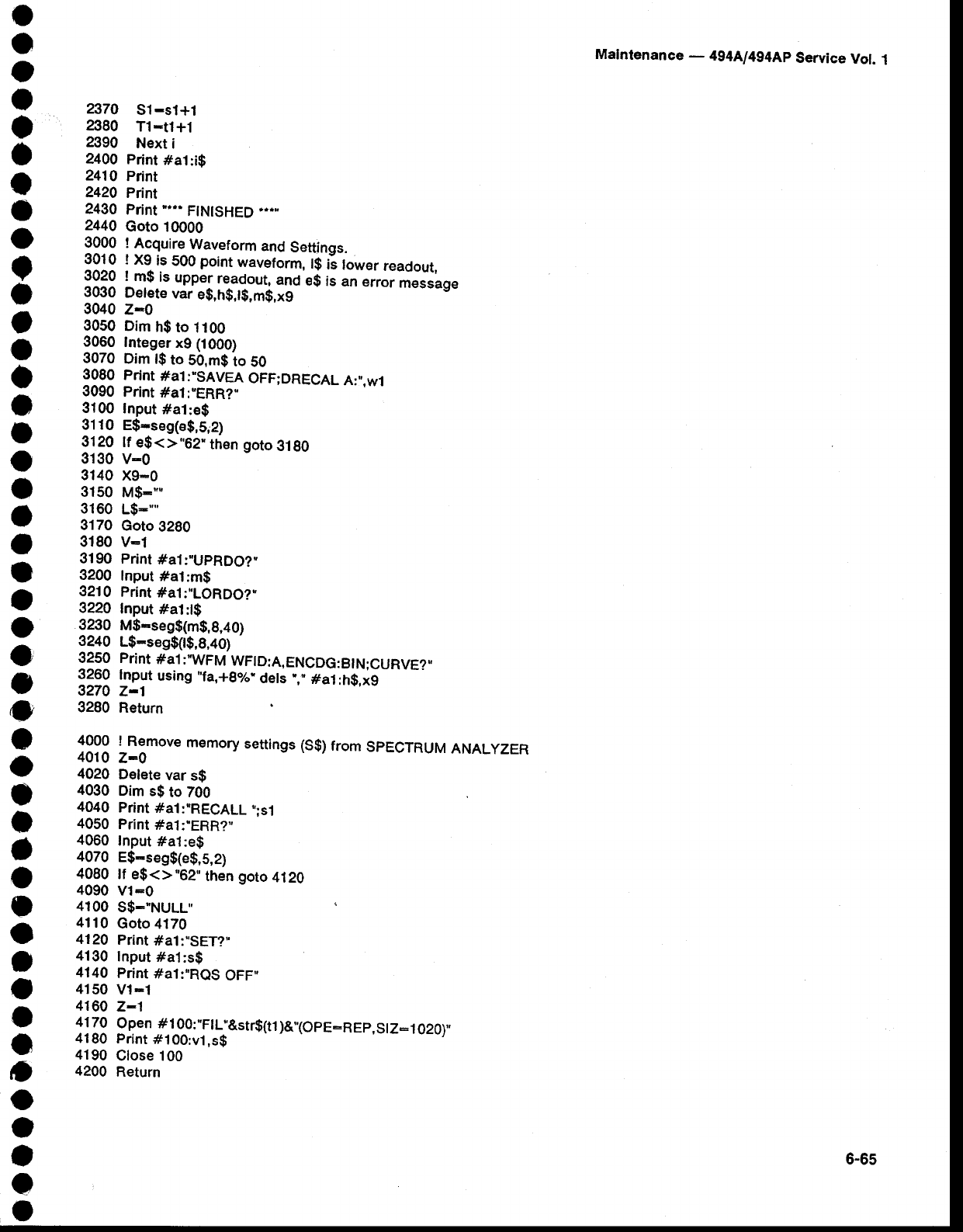

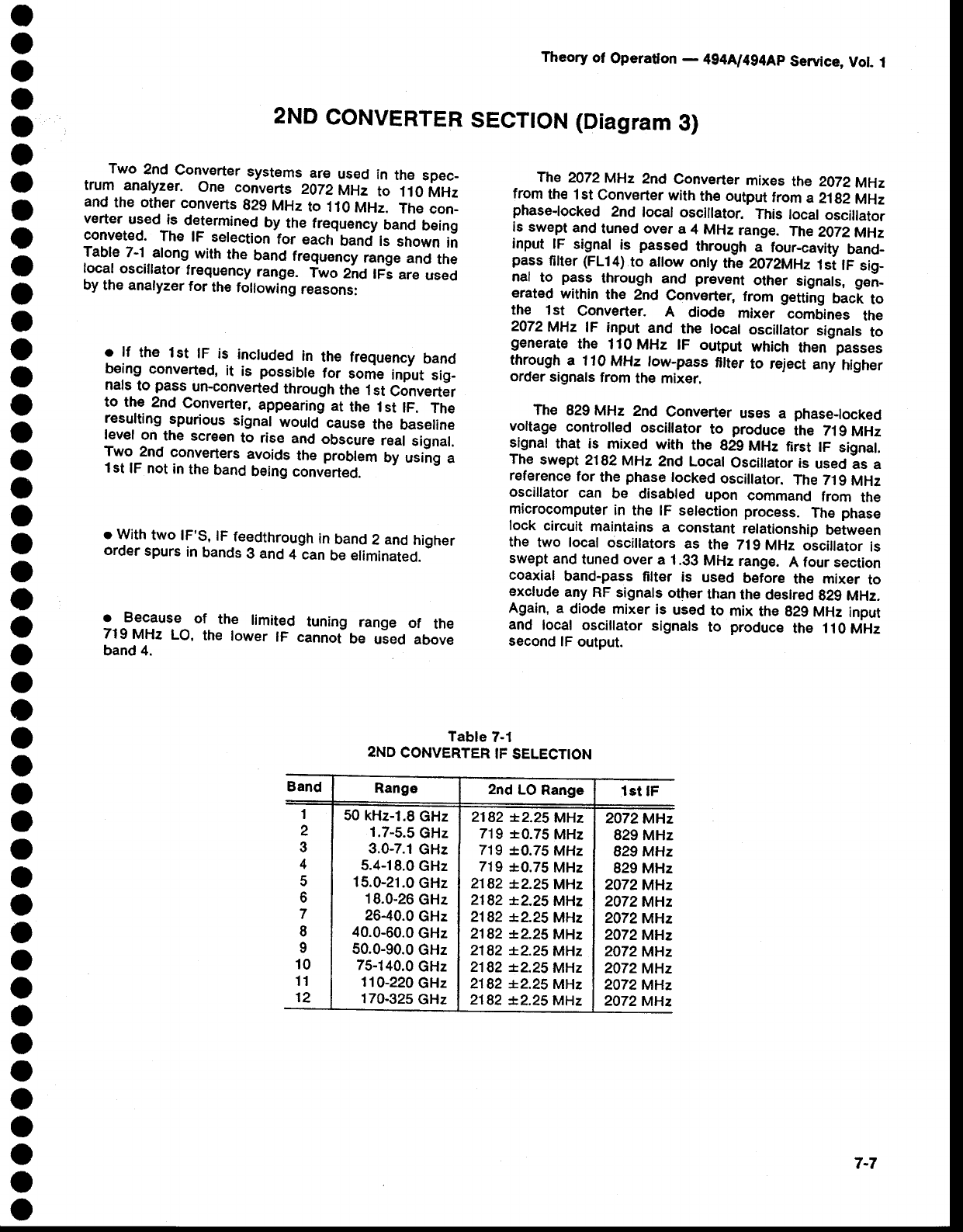

7-1 zND

CONVERTER

tF

SELECTTON

...............7_7

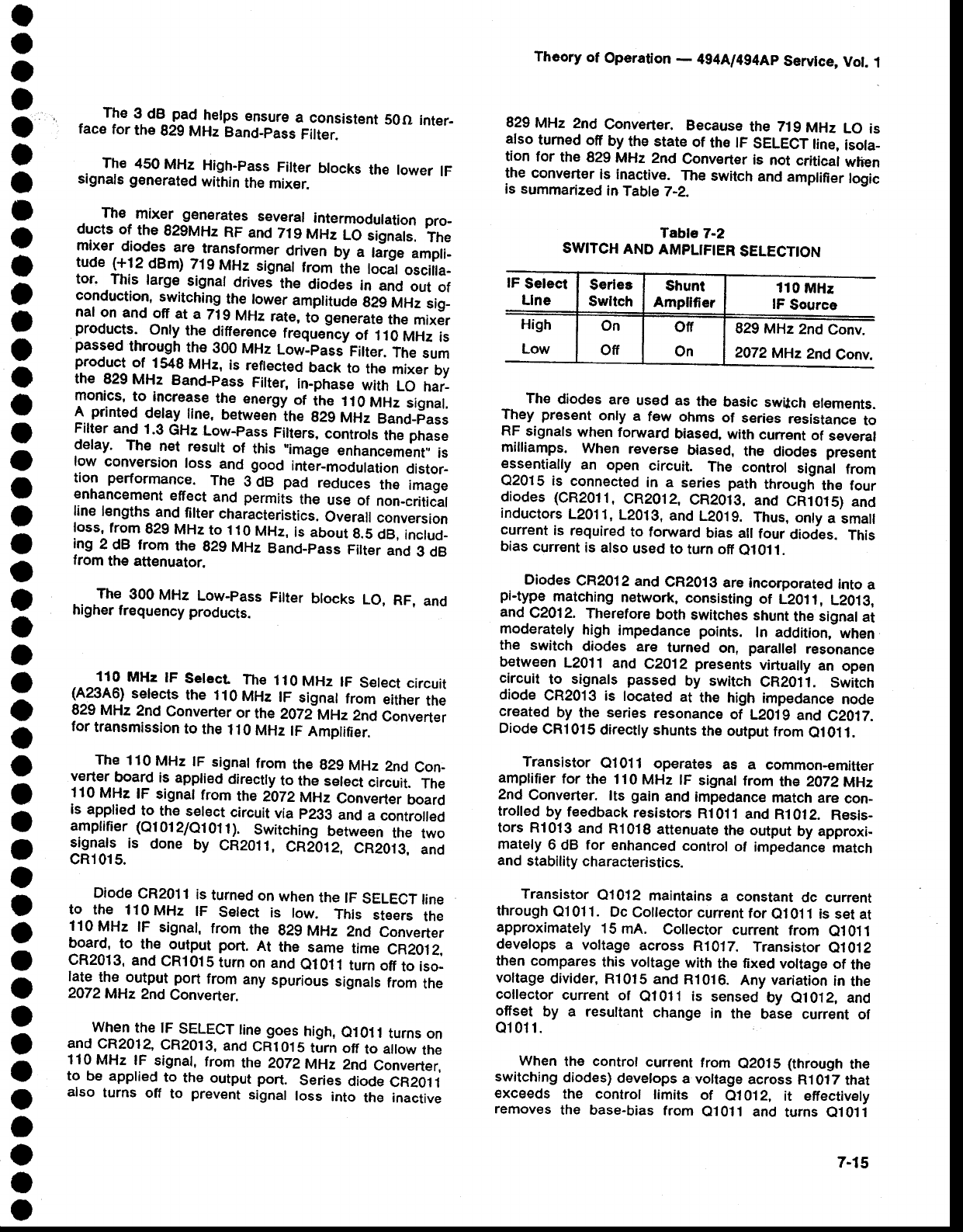

7-2 SWITCH AND

AMPLIFIER

SELECTION ..........7-1s

7.3 BANDWIDTH

SELECTION ........7.23

7-4 GAIN

STEP

COMBTNATTONS.......................7-27

7.5 PROGRESSION

OF

cAlN REDUCTTON

.......... .........7_30

7.6 FILTER

COMPONENT

COMBINATIONS

......7.38

7-7 RF TNTERFACE

LTNES .............7-49

7-8 U2039

TRUTH

TABLE ..............

7-49

7-9 CONTROL PORT ..7-57

7-1O ADDRESS/DATA

PORT ...........7-57

7.1'I SWEEP

RATE

SELECTION

CODES .............7-61

7-12 TRtccER

SELECTTON

MODES

...............,...7-62

7-13 SWEEP HOLDOFF

SELECT|ON

....,..............7-62

7.'14 CALIBRATION

CONTROL

7-15

7-1

6

7-17

7-18

7-19

7-20

7-21

7-22

7-23

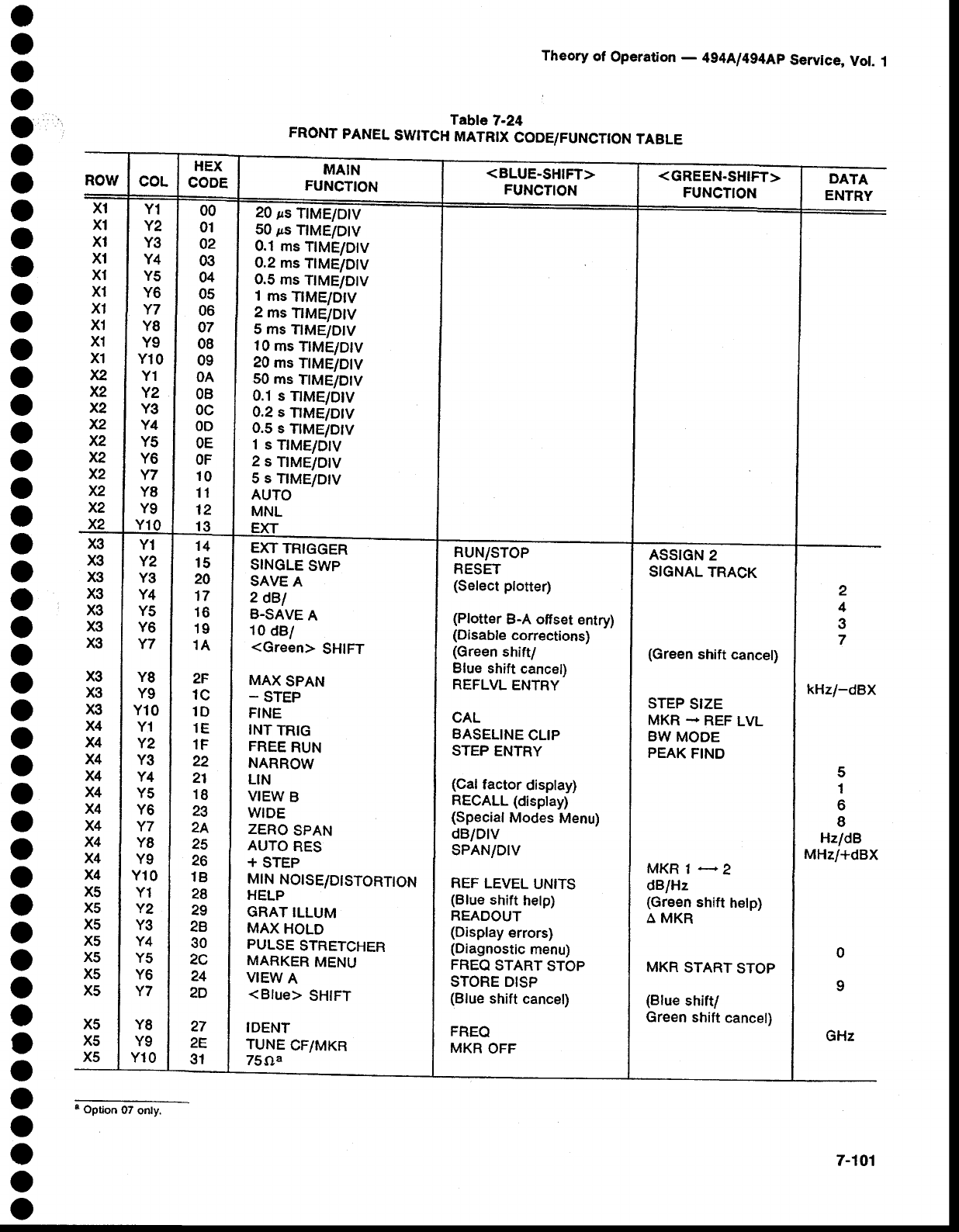

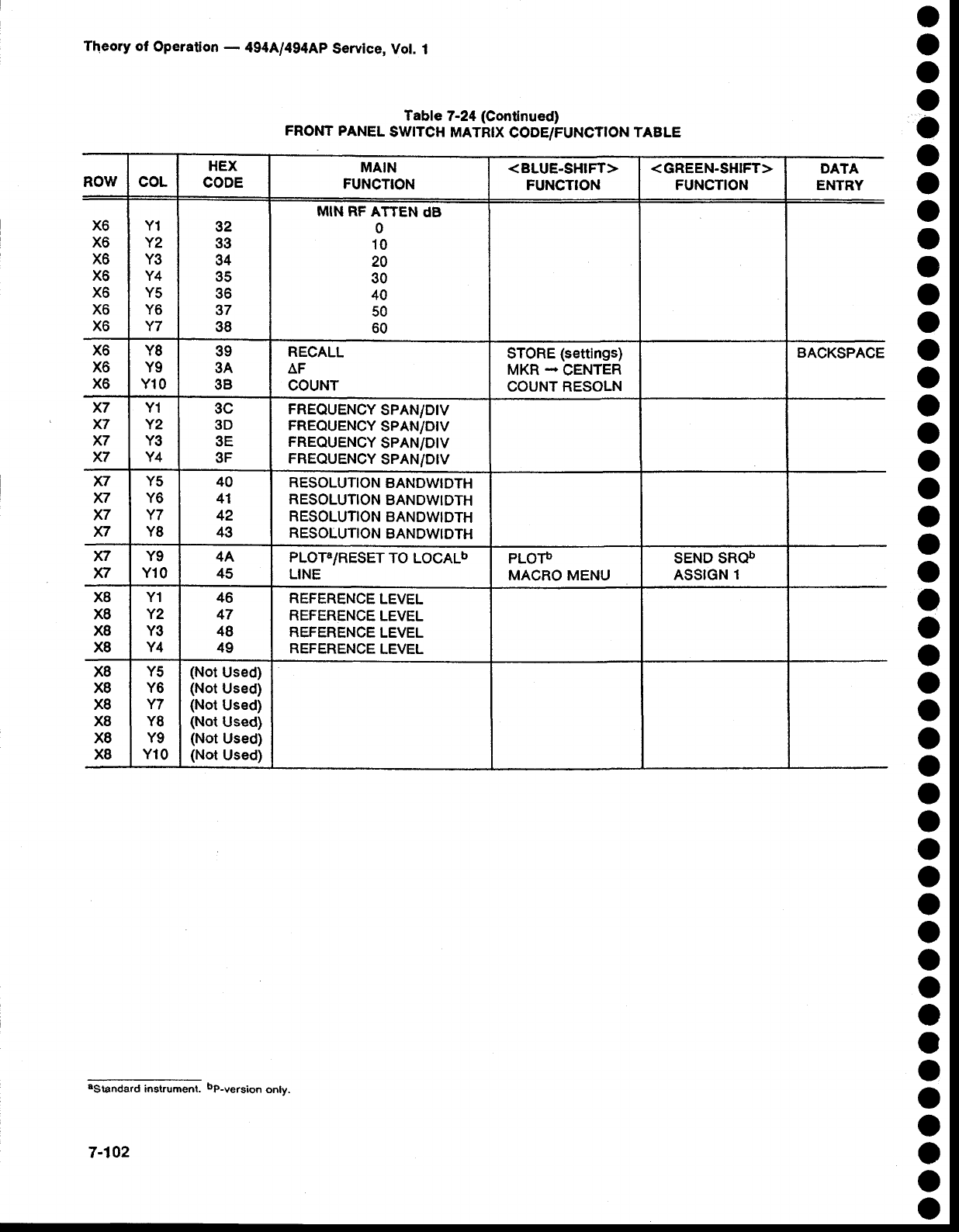

7-24

SELECTTON

CODES .................

7-66

AfiENUATION

SELECTION

CODES

...........

7.67

u4017 oUTPUT

LTNES .............

7-68

u5031

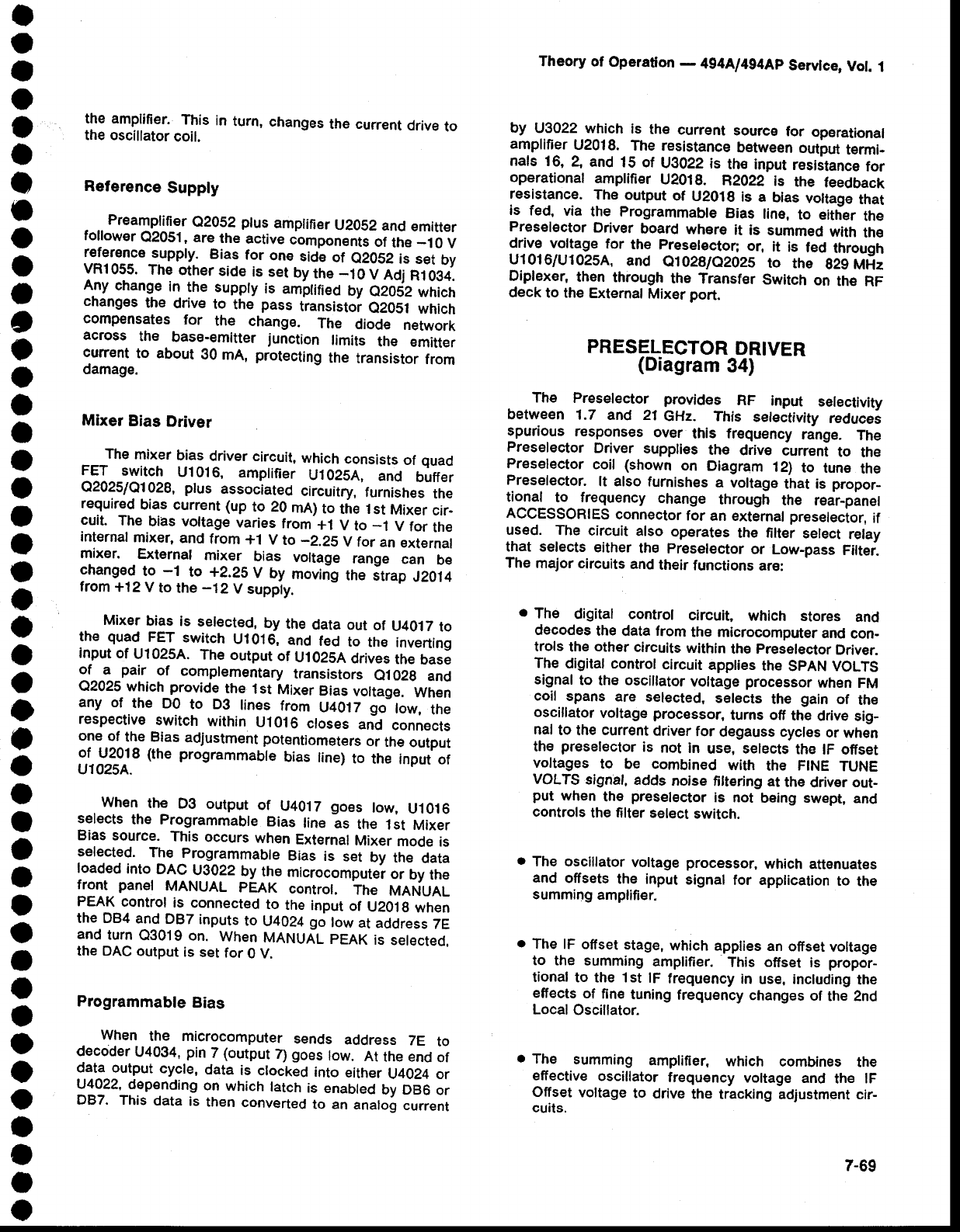

oUTPUT LrNES .............7-70

PRESELECTOR

FREQUENCY

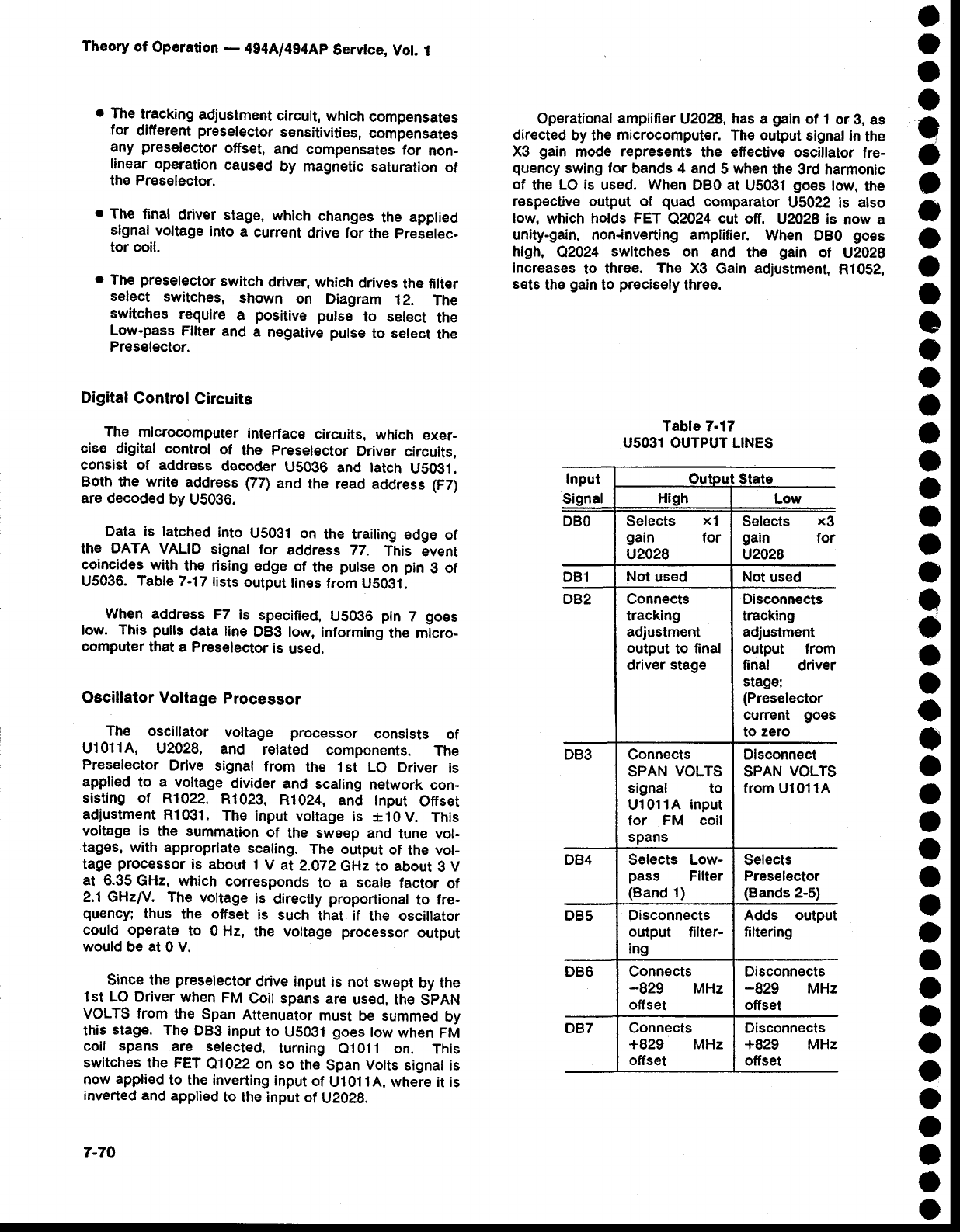

BANDS ..,...,. 7-71

ADDRESS 70

FORMATS ..............................

7-75

DAC TUNING

CODES ..............7-75

u2025 oUTPUT

LTNES ............. 7-8s

POLL

BITS ........... 7-93

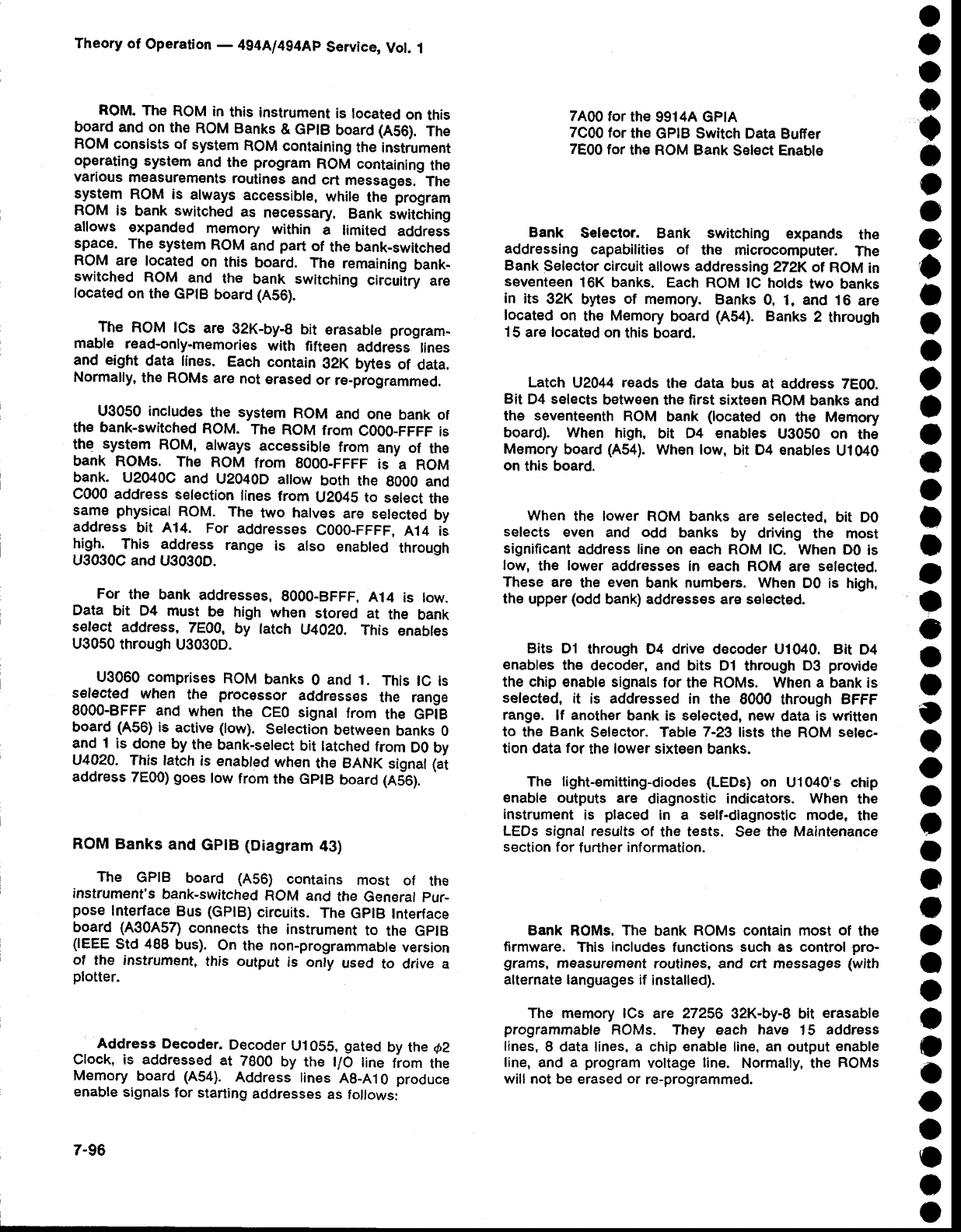

ROM

BANK

SELECTTON

DATA

................... 7-97

FRONT PANEL

SW'TCH

MATRIX

CoDE/FUNCT|ON

TABLE ........

7-101

LIST

OF TABLES

Table

6-6

6-7

6-8

5-1

5-2

5-3

5-4

6-1

6-2

6-3

64

6-5

xltl

{944/494AP

Service

Vot. 1

Table page

8.1 EXTENDED

SERVICE

AND

WARRANW

OPT|ONS .............8_1

8.2 OPNON

07 ALTERNATE

spEctFtcATloNs ...................

8-2

8.3 OPTIONS

21 AND

22

WAVEGUIDE

MtxERS

CHARACTERTSTTCS

......................

8_3

page

OPTION 41 ALTERNATE

SPECTF|CAT|ONS

......... ............8-4

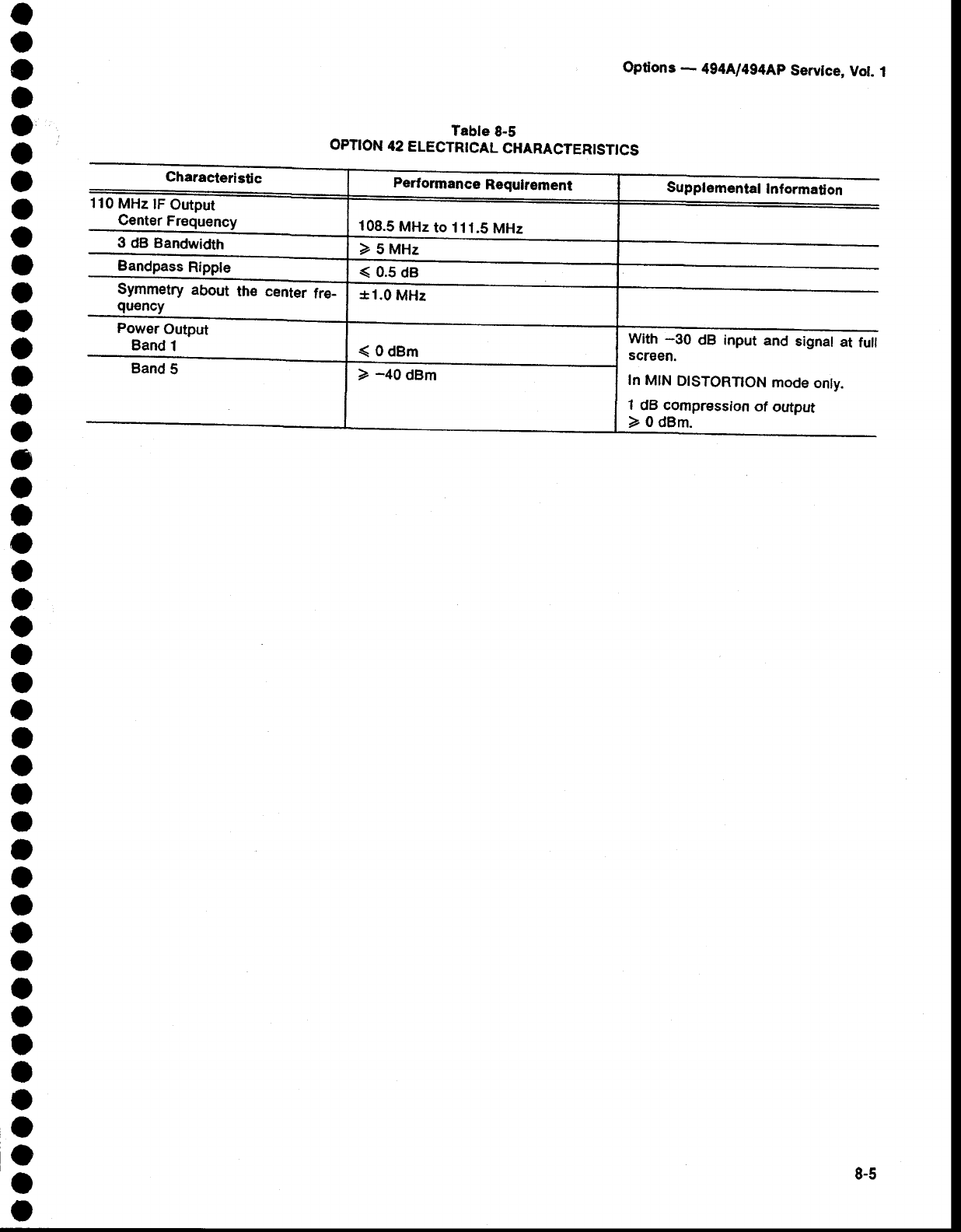

OPTION 42 ELECTRICAL

CHARACTERTSTTCS ..................

8-5

o

o

o

a

I

o

)

I

o

o

o

I

o

t

o

I

o

t

a

I

o

I

o

O

I

O

I

o

t

a

t

I

a

o

I

o

I

a

I

a

a

o

o

o

Table

84

8-5

LIST

OF TABLES

(Cont.)

t

o

o

I

o

I

I

I

o

o

o

a

o

O

t

I

o

I

o

I

I

o

o

o

o

I

o

o

o

o

o

o

I

o

o

t

a

o

o

o

o

o

I

I

SERVICING

SAFETY

SUMMARY

FOR

QUALIFIED

SERVICE

PERSONNEL

ONLY

494A|494AP

Service

Vot.

1

Do

Not

Service

Alone

Do

not

perform

internal

service

or adjustment

of this

product unless anoth€r

person

capable

of rendering

first

aid

and

resuscitation

is

present.

Do Not Wear Jewelry

. Remove

jewelry

prior

to servicing.

Rings,

neck-

laces,

and other

metallic

objects

could

come

into con_

tact

with

dangerous

voltages

and

currents.

Use Gare When Servicing With power On

Dangerous

voltages

exist at several

points

in this

product. To avoid personal injury, do not touch

exposed

connections

and components

while power

is

on.

Djsconnect power before removing protective

panels,

soldering,

or

replacing

components.

Power Source

This product

is intended

to operate

from a power

source that will not apply more than 250 volts rms

between

the supply

conductor

and ground. A protective

ground

connection

by way of the grounding

conductor

in the

power

cord

is

essential

for safe operation.

X-Radiation

X-ray

emission

generated

within

this instrument

has

been sufficiently

shielded.

Do not modify

or otherwis€

alter

the

high

voltage

circuitry

or

the crt enclosure.

TERMS

In

This Manual

CAUTION statements identify conditions or prac_

tices that could result in damage

to the equipment

or

other property.

WARNING statements identify conditions or prac_

tices that could result in personal

injury or loss of liie.

As Marked

on Equipment

CAUTION

indicates

a personal

injury

hazard

not

imm€diately accessible as one reads the marking, or a

hazard to property including

the equipm€nt itself.

DANGER indicates a personal

injury hazard immedi-

atefy accessible as one reads the marking,

SYMBOLS

In

This

Manual

This symbol indacates

where appticable

cau-

tionary

or other

information

as to be

tound.

As Marked

on Equipment

t DANGER

- High

vortage.

Protective ground

(earth)

terminal-

ATTENTION

- Refer

to manual.

Refer

to manual.

Grounding

the Product

This product

is grounded

through

the grounding

conductor

of the

power

cord. To avoid