Telit Communications S p A WE9223GR Bluetooth and WiFi module User Manual v1 low quality

Telit Communications S.p.A. Bluetooth and WiFi module v1 low quality

User guide

xE922-3GR

Hardware User Guide

1VV0301272

Rev.0.8 - 2017-01-05

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 2 of 112

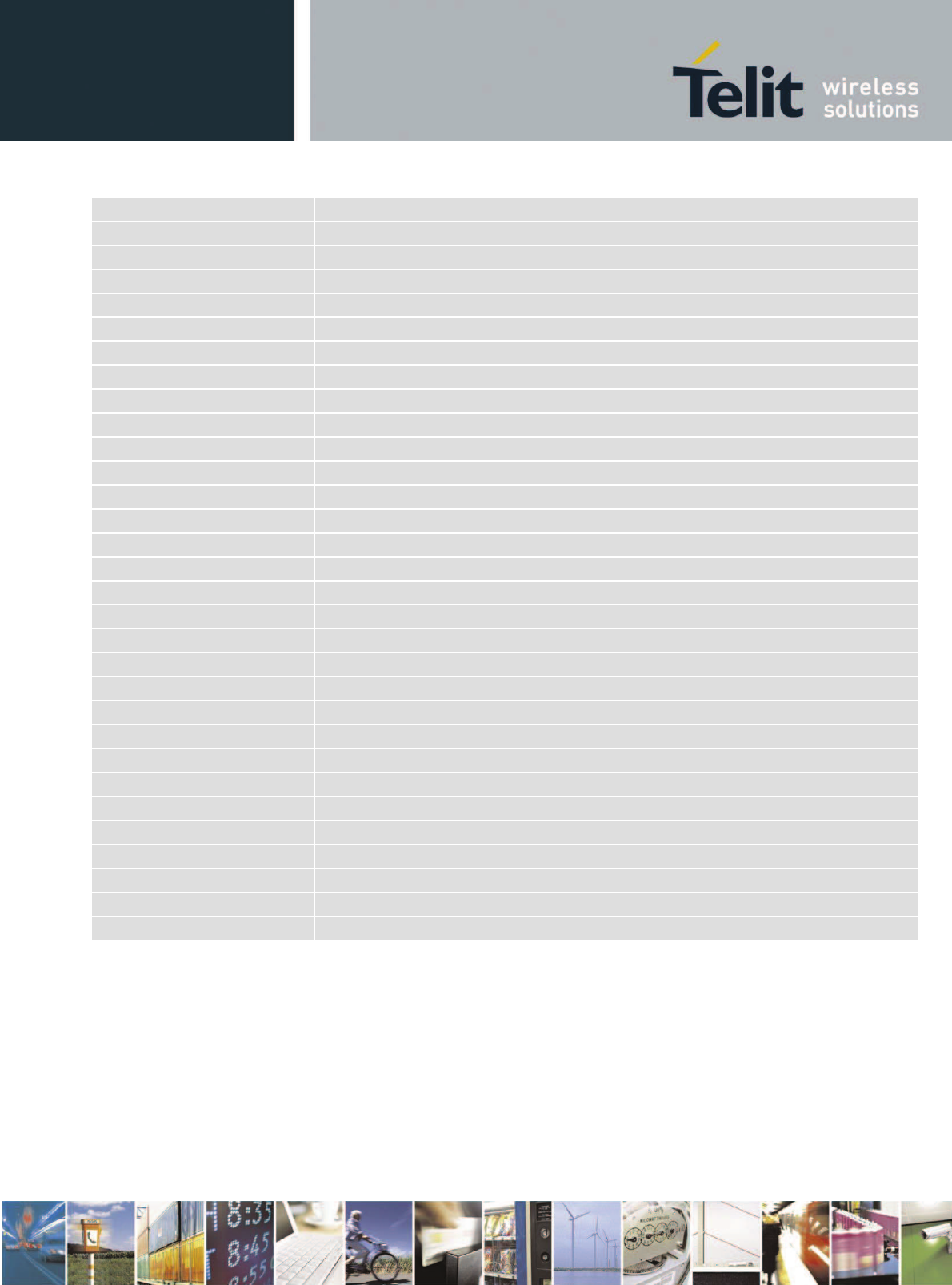

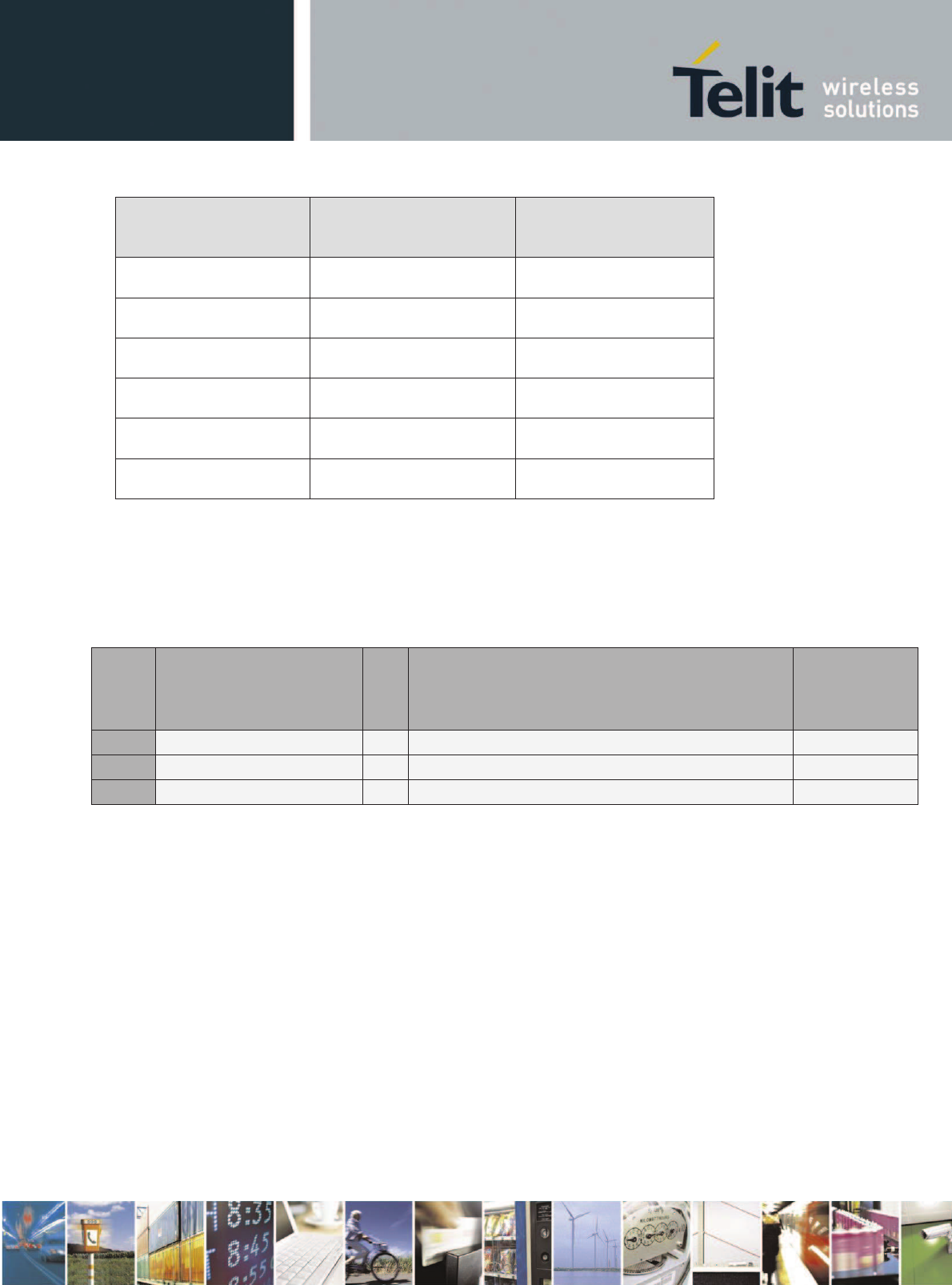

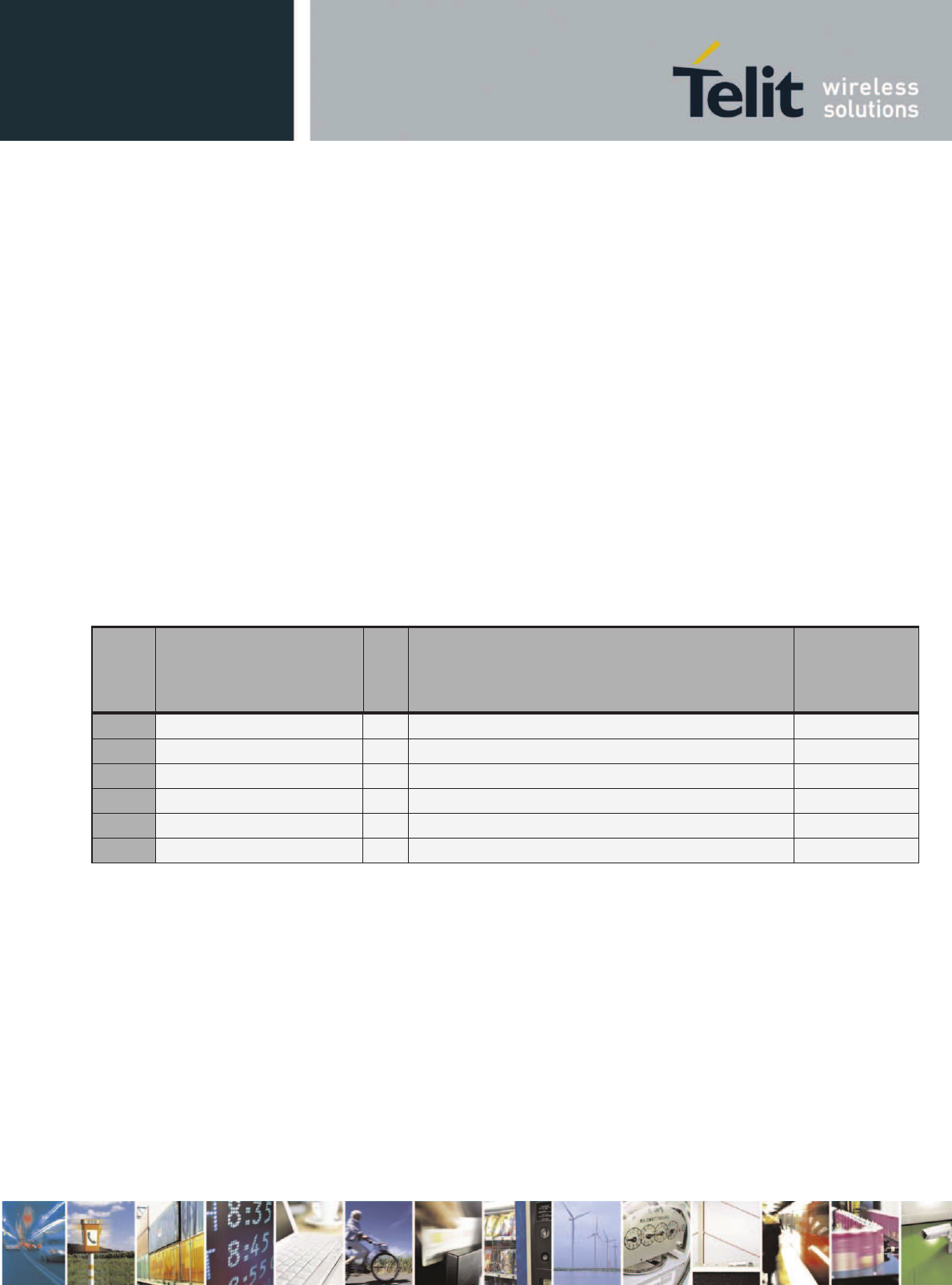

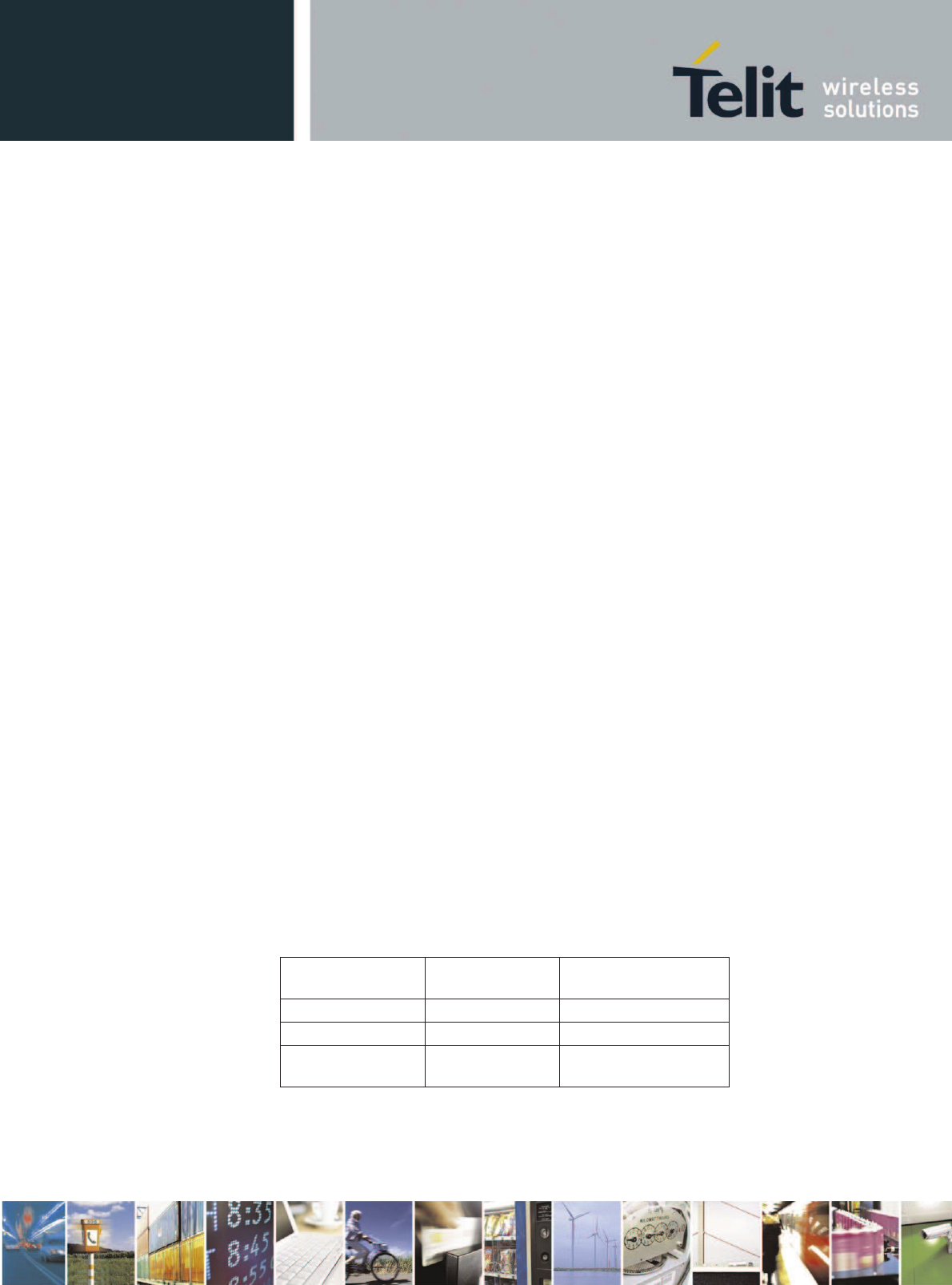

APPLICABILITY TABLE

APPLICABILITY TABLE 1

PRODUCT

HE922-3GR

WE922-3GR

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 3 of 112

SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

Notice

While reasonable efforts have been made to assure the accuracy of this document, Telit assumes

no liability resulting from any inaccuracies or omissions in this document, or from use of the

information obtained herein. The information in this document has been carefully checked and

is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies or

omissions. Telit reserves the right to make changes to any products described herein and

reserves the right to revise this document and to make changes from time to time in content

hereof with no obligation to notify any person of revisions or changes. Telit does not assume

any liability arising out of the application or use of any product, software, or circuit described

herein; neither does it convey license under its patent rights or the rights of others.

It is possible that this publication may contain references to, or information about Telit products

(machines and programs), programming, or services that are not announced in your country.

Such references or information must not be construed to mean that Telit intends to announce

such Telit products, programming, or services in your country.

Copyrights

This instruction manual and the Telit products described in this instruction manual may be,

include or describe copyrighted Telit material, such as computer programs stored in

semiconductor memories or other media. Laws in the Italy and other countries preserve for Telit

and its licensors certain exclusive rights for copyrighted material, including the exclusive right

to copy, reproduce in any form, distribute and make derivative works of the copyrighted

material. Accordingly, any copyrighted material of Telit and its licensors contained herein or

in the Telit products described in this instruction manual may not be copied, reproduced,

distributed, merged or modified in any manner without the express written permission of Telit.

Furthermore, the purchase of Telit products shall not be deemed to grant either directly or by

implication, estoppel, or otherwise, any license under the copyrights, patents or patent

applications of Telit, as arises by operation of law in the sale of a product.

Computer Software Copyrights

The Telit and 3rd Party supplied Software (SW) products described in this instruction manual

may include copyrighted Telit and other 3rd Party supplied computer programs stored in

semiconductor memories or other media. Laws in the Italy and other countries preserve for Telit

and other 3rd Party supplied SW certain exclusive rights for copyrighted computer programs,

including the exclusive right to copy or reproduce in any form the copyrighted computer

program. Accordingly, any copyrighted Telit or other 3rd Party supplied SW computer

programs contained in the Telit products described in this instruction manual may not be copied

(reverse engineered) or reproduced in any manner without the express written permission of

Telit or the 3rd Party SW supplier. Furthermore, the purchase of Telit products shall not be

deemed to grant either directly or by implication, estoppel, or otherwise, any license under the

copyrights, patents or patent applications of Telit or other 3rd Party supplied SW, except for

the normal non-exclusive, royalty free license to use that arises by operation of law in the sale

of a product.

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 4 of 112

Usage and Disclosure Restrictions

License Agreements

The software described in this document is the property of Telit and its licensors. It is furnished

by express license agreement only and may be used only in accordance with the terms of such

an agreement.

Copyrighted Materials

Software and documentation are copyrighted materials. Making unauthorized copies is

prohibited by law. No part of the software or documentation may be reproduced, transmitted,

transcribed, stored in a retrieval system, or translated into any language or computer language,

in any form or by any means, without prior written permission of Telit

High Risk Materials

Components, units, or third-party products used in the product described herein are NOT fault-

tolerant and are NOT designed, manufactured, or intended for use as on-line control equipment

in the following hazardous environments requiring fail-safe controls: the operation of Nuclear

Facilities, Aircraft Navigation or Aircraft Communication Systems, Air Traffic Control, Life

Support, or Weapons Systems (“High Risk Activities"). Telit and its supplier(s) specifically

disclaim any expressed or implied warranty of fitness for such High Risk Activities.

Trademarks

TELIT and the Stylized T Logo are registered in Trademark Office. All other product or service

names are the property of their respective owners.

Copyright © Telit Communications S.p.A. 2016.

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 5 of 112

Contents

1. Introduction ..................................................... 9

1.1. Scope ....................................................... 9

1.2. Audience ..................................................... 9

1.3. Contact Information, Support ....................................... 10

1.4. Text Conventions............................................... 10

1.5. Supporting documents ........................................... 11

1.6. Product Variants ............................................... 11

1.7. Abbreviations ................................................. 11

2. General Product Description ......................................... 13

2.1. Overview .................................................... 13

2.2. General Functionality and Main Features ............................... 15

2.3. Reference table of RF bands characteristics ............................. 19

2.3.1. Cellular network: ................................................. 19

2.3.2. WiFi/Bluetooth .................................................. 20

2.3.3. GNSS ........................................................ 20

2.4. Applications .................................................. 20

2.5. Sensitivity ................................................... 21

2.6. High level block Diagram ......................................... 22

2.7. Environmental requirements ....................................... 23

2.7.1. Temperature range ................................................ 23

2.8. xE922-3GR Mechanical Specifications ................................ 24

2.8.1. Dimensions ..................................................... 24

2.8.2. Weight ........................................................ 24

2.8.3. RoHS compliance ................................................ 24

3. xE922-3GR Module pin out .......................................... 25

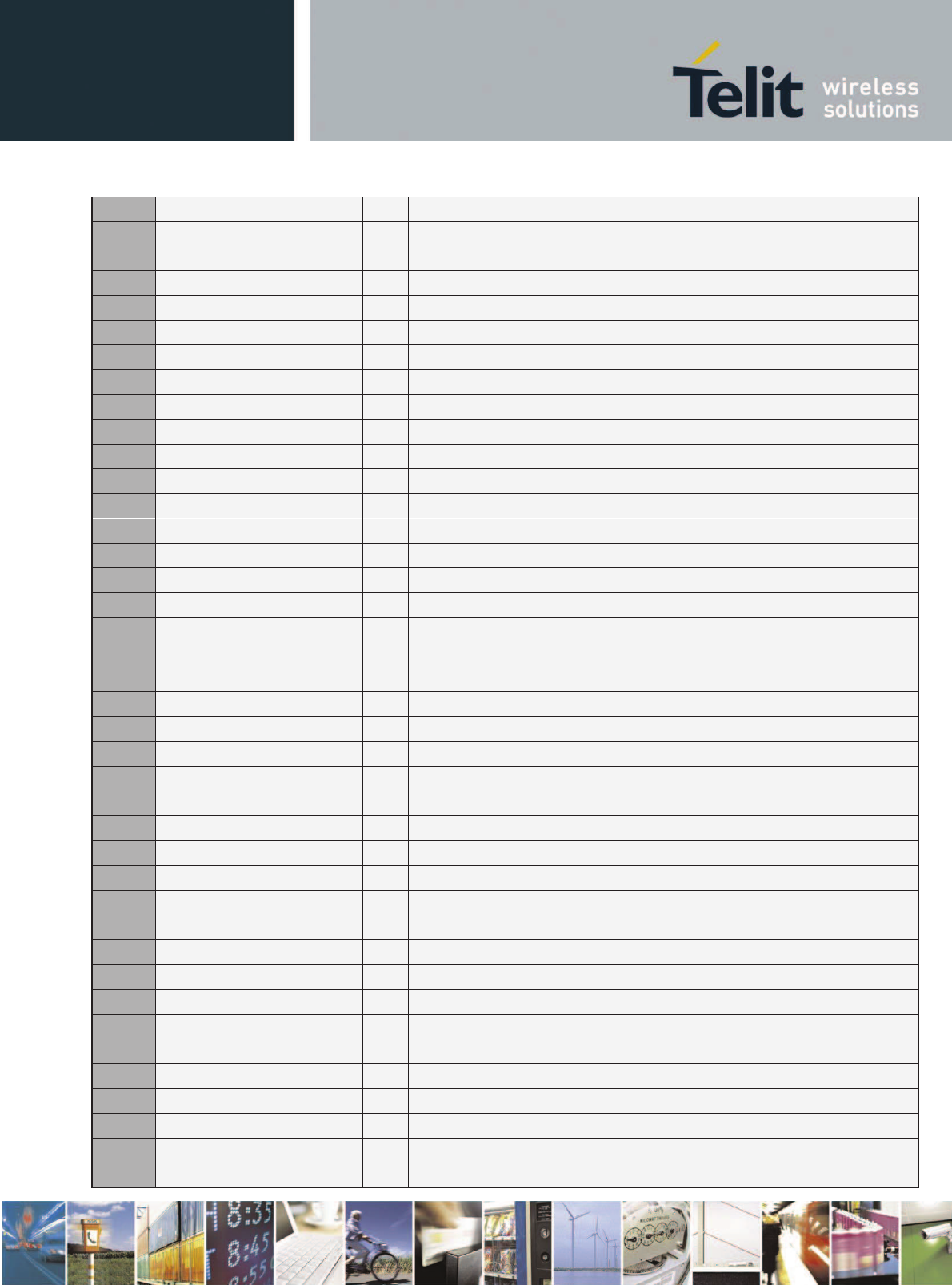

3.1. PIN table .................................................... 25

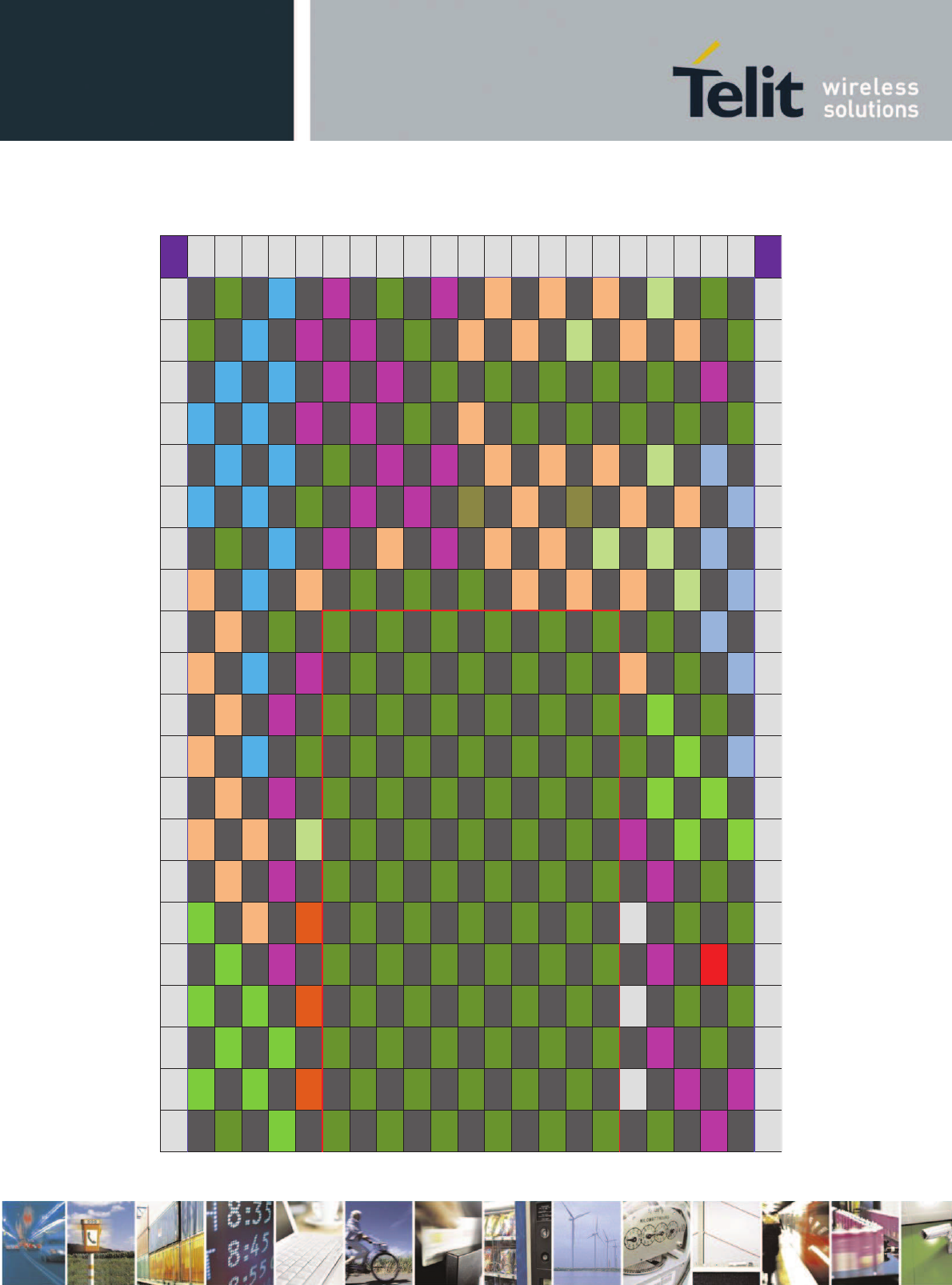

3.2. LGA Pads Layout .............................................. 37

4. Electrical specifications ............................................. 39

4.1. Absolute maximum ratings – not operational ............................. 39

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 6 of 112

4.2. Recommended operating conditions .................................. 39

4.3. Logic Level Specifications ........................................ 39

5. Power supply .................................................... 41

5.1. Input supply .................................................. 41

5.2. Output supply ................................................. 42

5.2.1. Linear voltage regulators .................................. 42

5.2.1.1. VAUX_1P8V ............................................... 42

5.2.1.2. VAUX_2P85V .............................................. 43

5.2.1.3. VAUX_3P0V ............................................... 43

5.2.1.4. VSIM1/2 ................................................. 44

5.2.2. DC/DC stepdown ................................................. 44

5.2.2.1. 1V8_OUT ................................................. 44

5.3. Typical system power consumption ................................... 45

5.4. RTC backup .................................................. 47

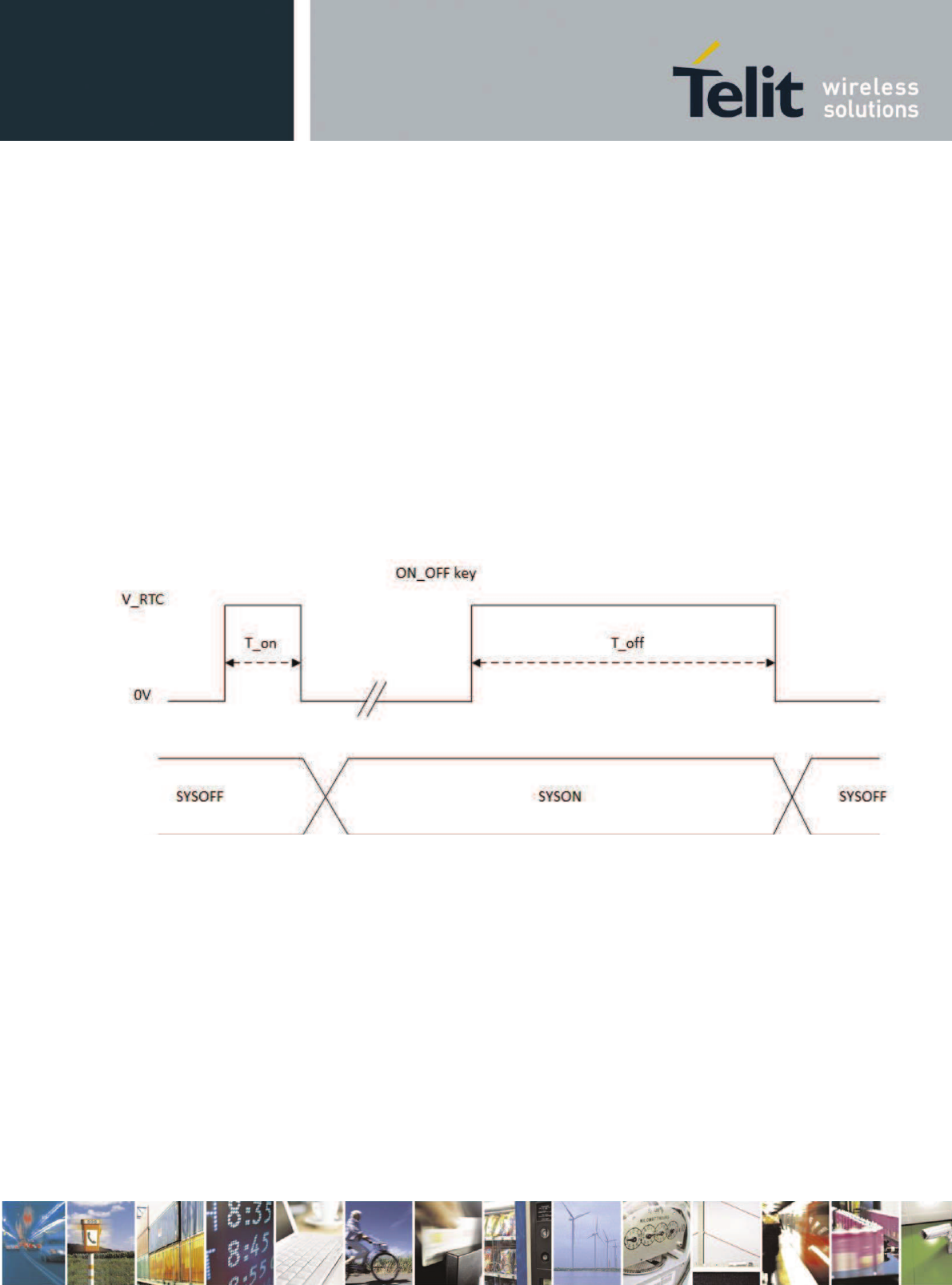

6. Power ON/OFF and reset control ...................................... 49

6.1. Power On .................................................... 49

6.1.1. ON_OFF key action ............................................... 49

6.1.2. Switching ON due to charging ........................................ 50

6.1.3. Switching on due to RTC alarm ....................................... 50

6.2. Power off .................................................... 50

6.2.1. Soft power off ................................................... 50

6.2.2. Emergency power off .............................................. 50

6.3. Reset ....................................................... 50

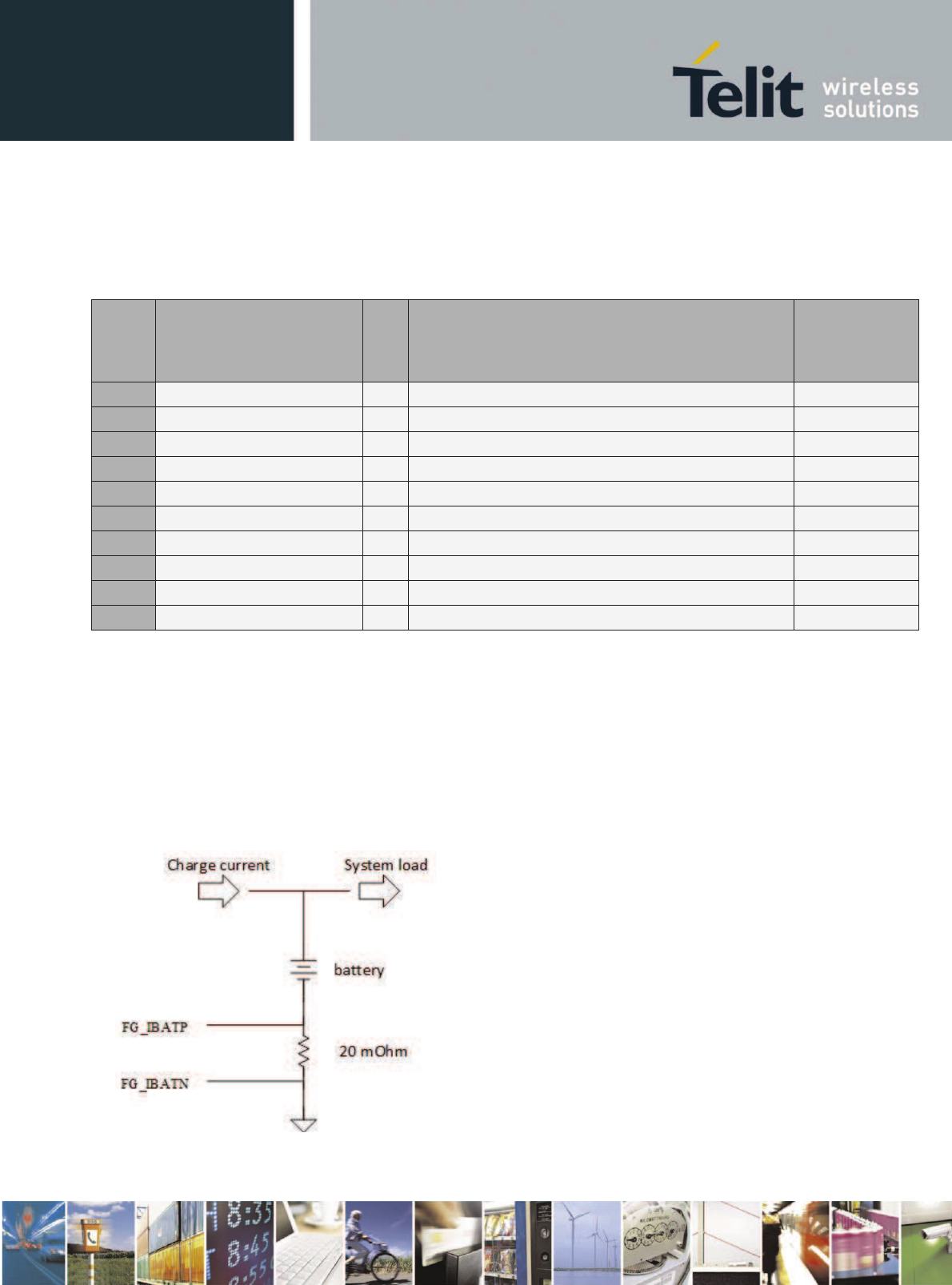

7. Battery management .............................................. 51

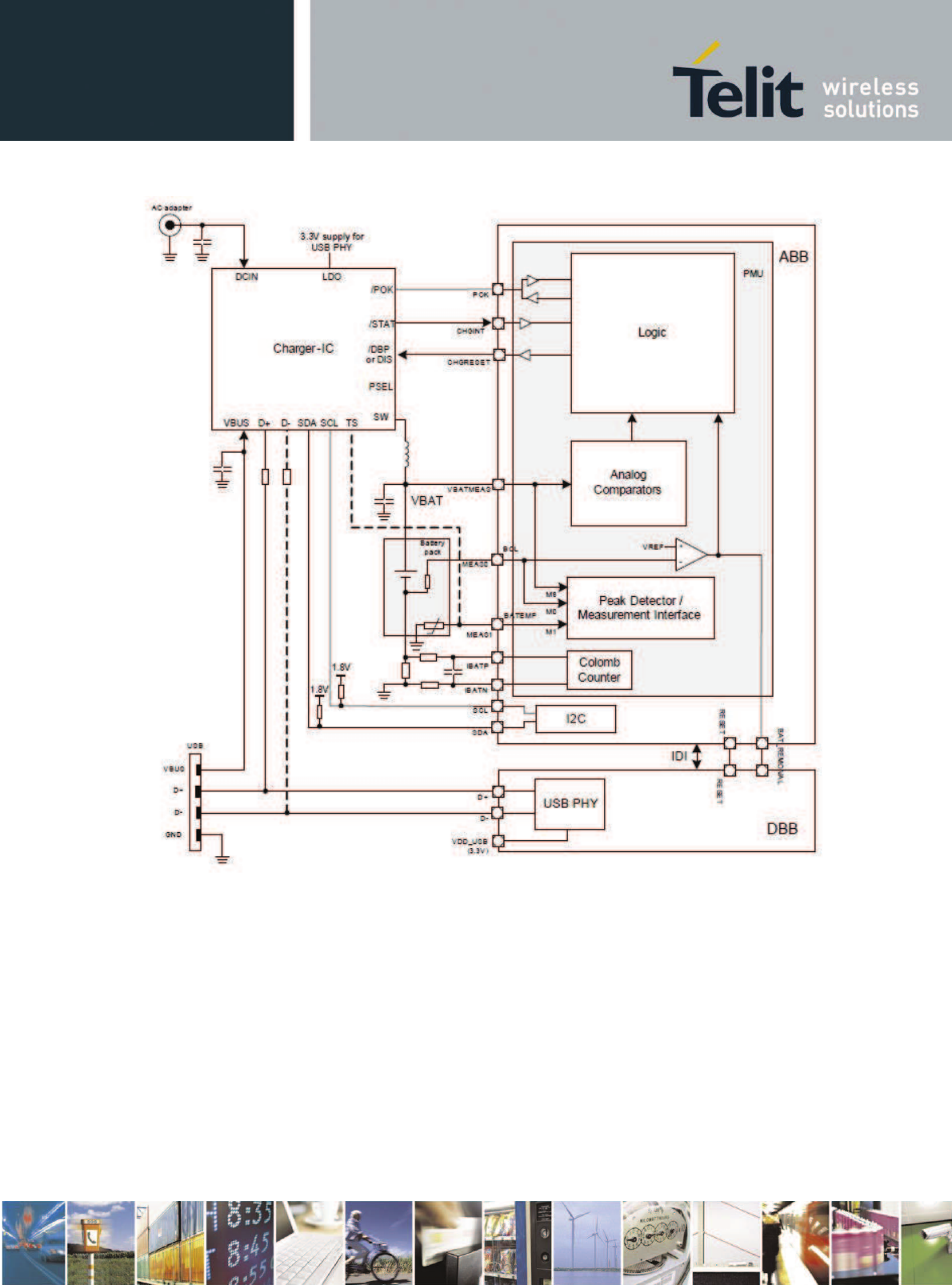

7.1. Coulomb counter ............................................... 51

7.2. Battery charging ............................................... 52

7.2.1. Block diagram ................................................... 52

7.2.2. Battery/charger-less operation ........................................ 54

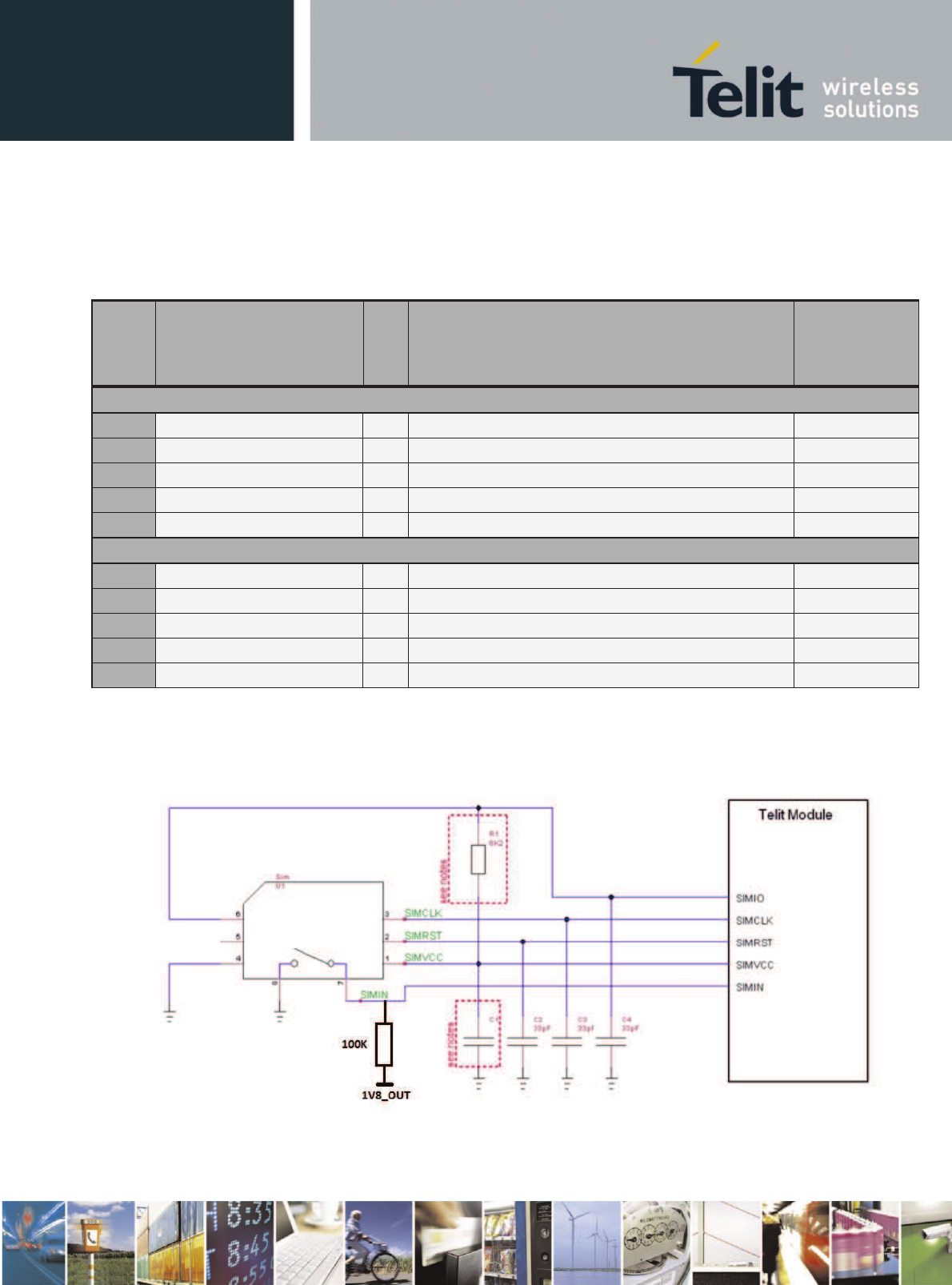

8. USIM interface .................................................. 55

9. USB port ....................................................... 57

10. Display interface ................................................ 60

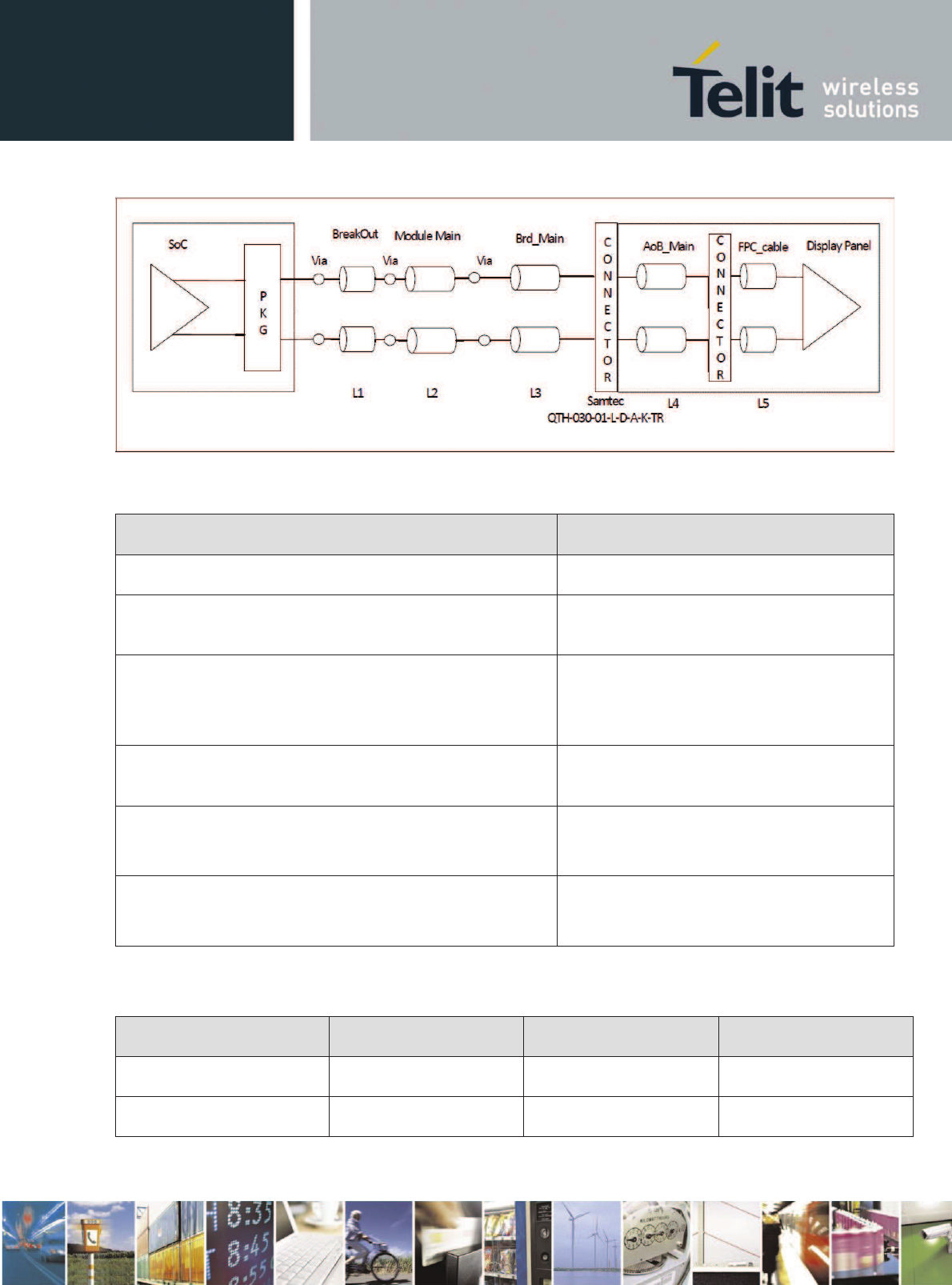

10.1. MIPI-DSI .................................................. 60

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 7 of 112

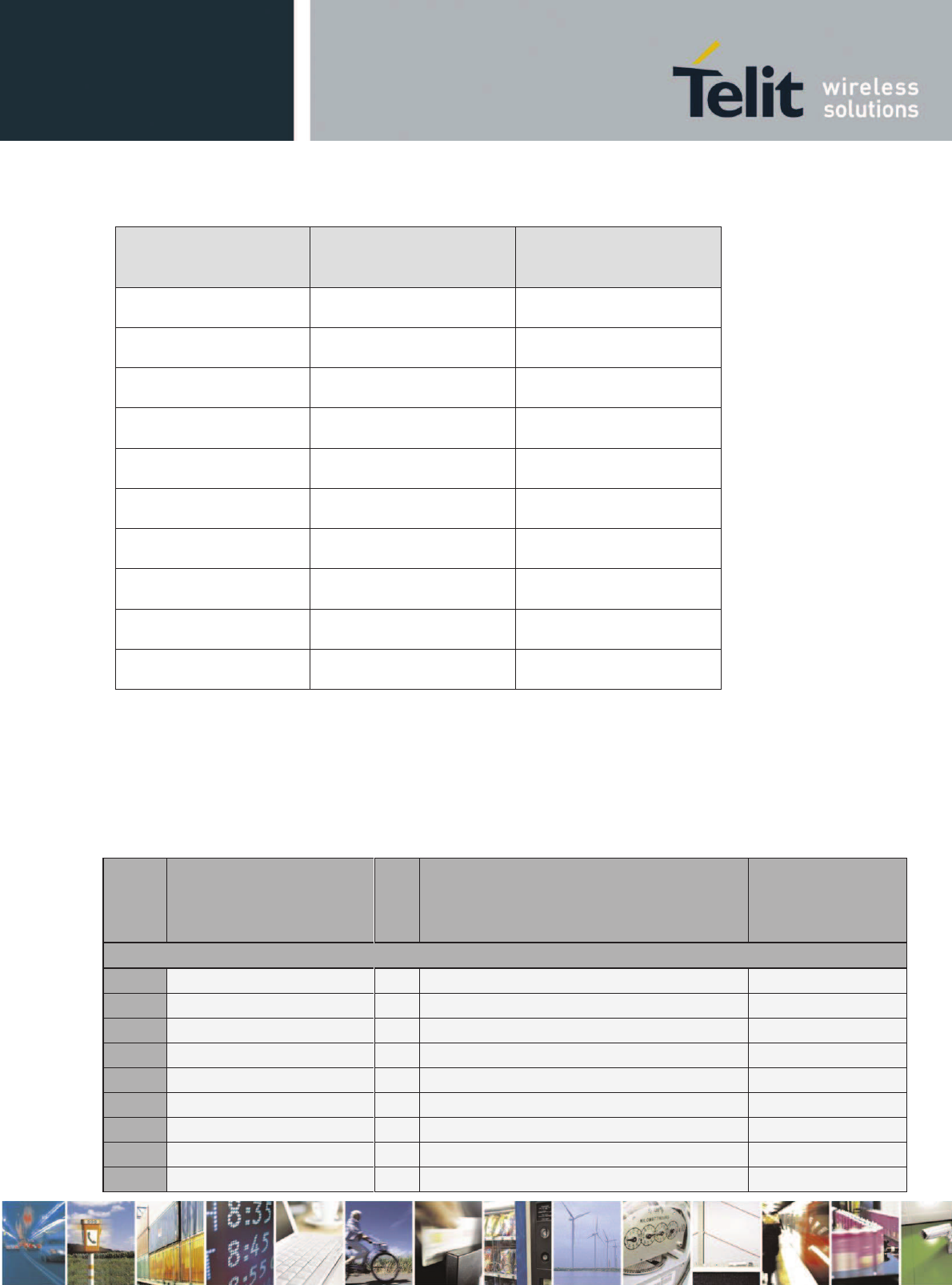

10.2. LVDS ..................................................... 62

10.3. Backlight control ............................................. 64

10.4. LED_CURSINK ............................................. 65

10.5. Touch panel ................................................. 66

11. Camera interface ............................................... 67

12. Peripheral interfaces ............................................. 71

12.1. I2C ...................................................... 71

12.2. USIF ..................................................... 72

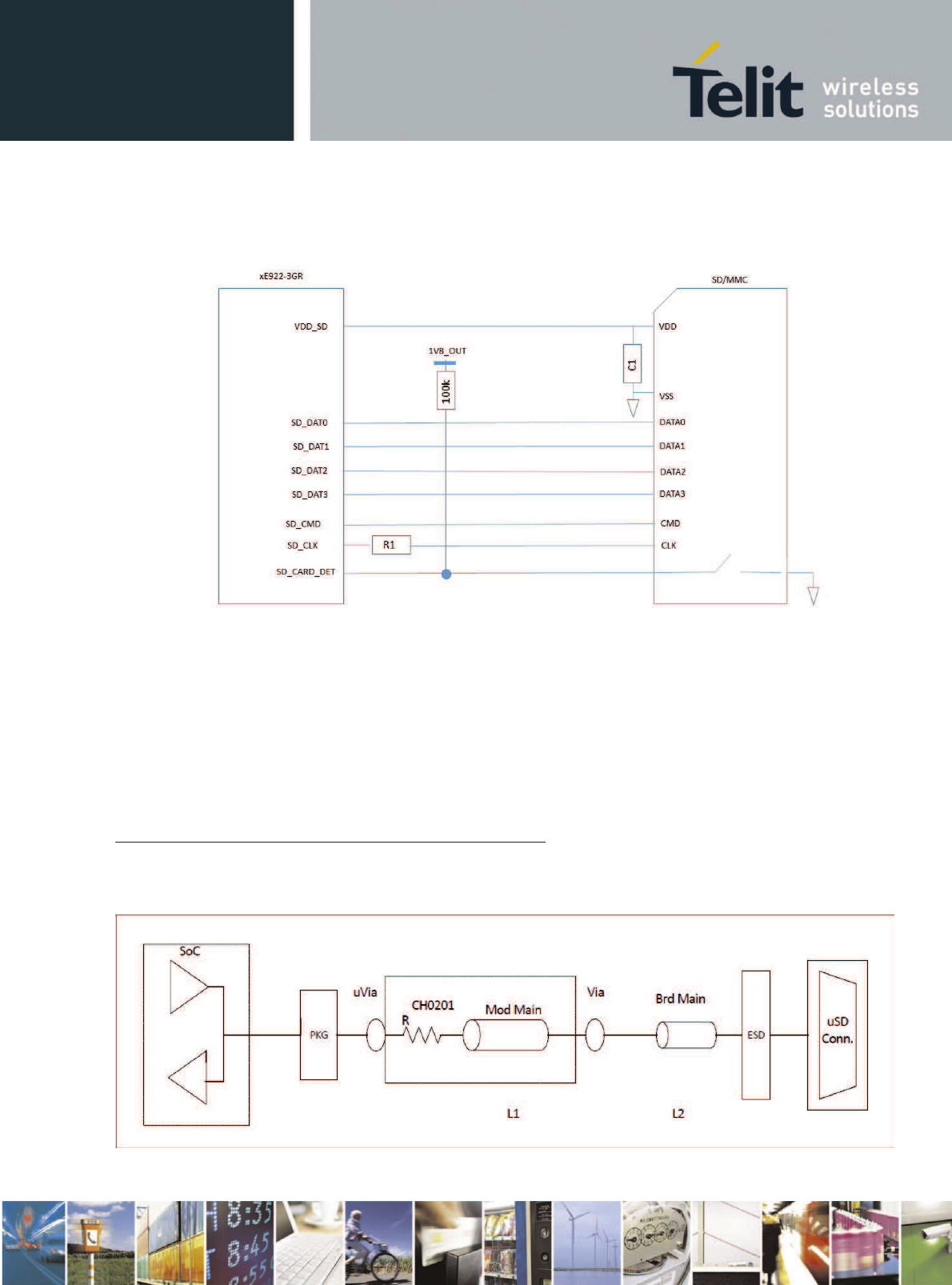

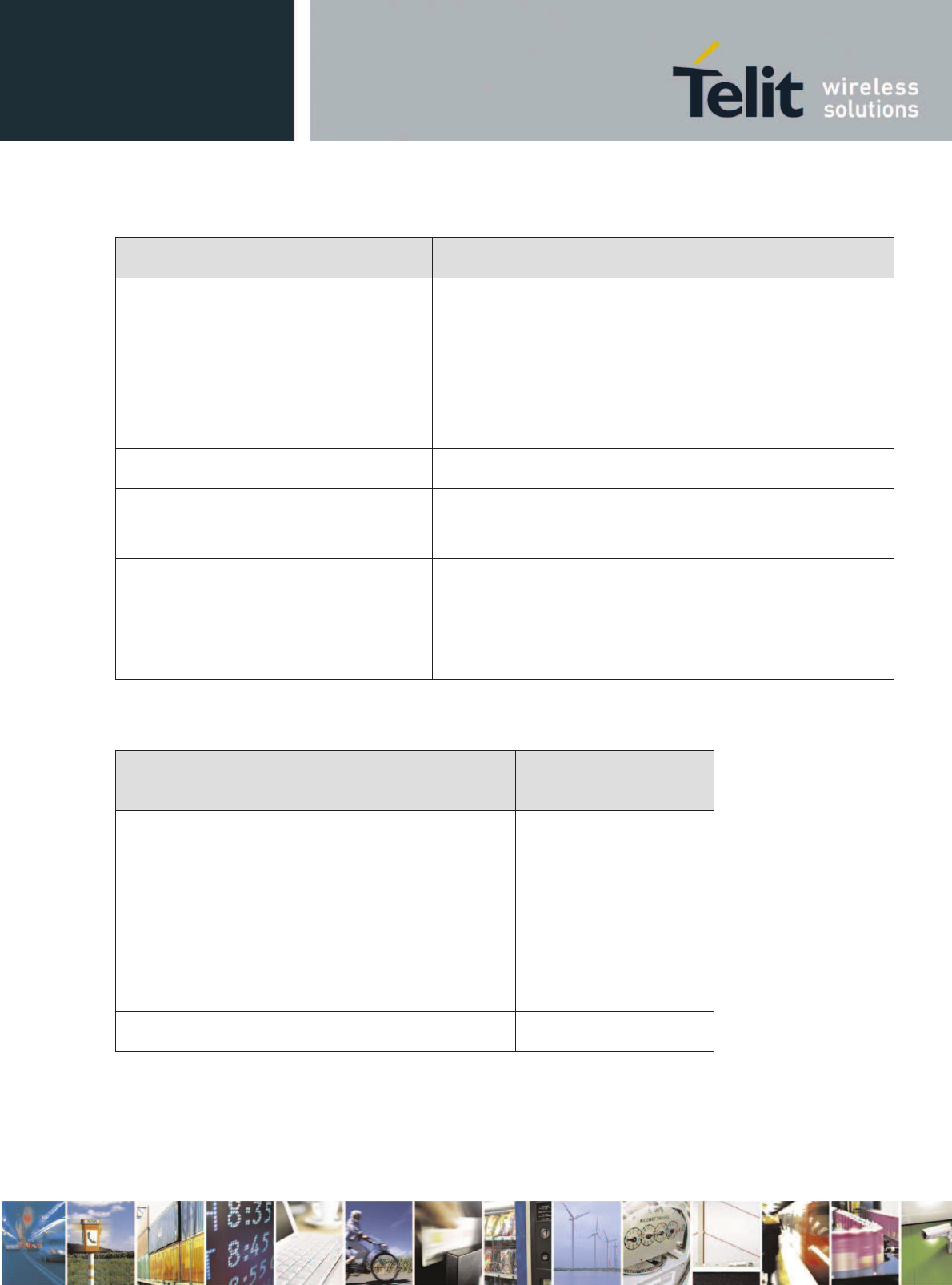

12.3. SDMMC/SDIO .............................................. 74

12.4. ADC ..................................................... 77

13. General purpose I/O ............................................. 78

14. Debug / flash interfaces ........................................... 81

14.1. USB2.0 HS ................................................. 81

14.2. USIF2 .................................................... 81

14.3. JTAG ..................................................... 81

14.4. Test pads ................................................... 81

15. Audio ........................................................ 82

15.1. Analog .................................................... 82

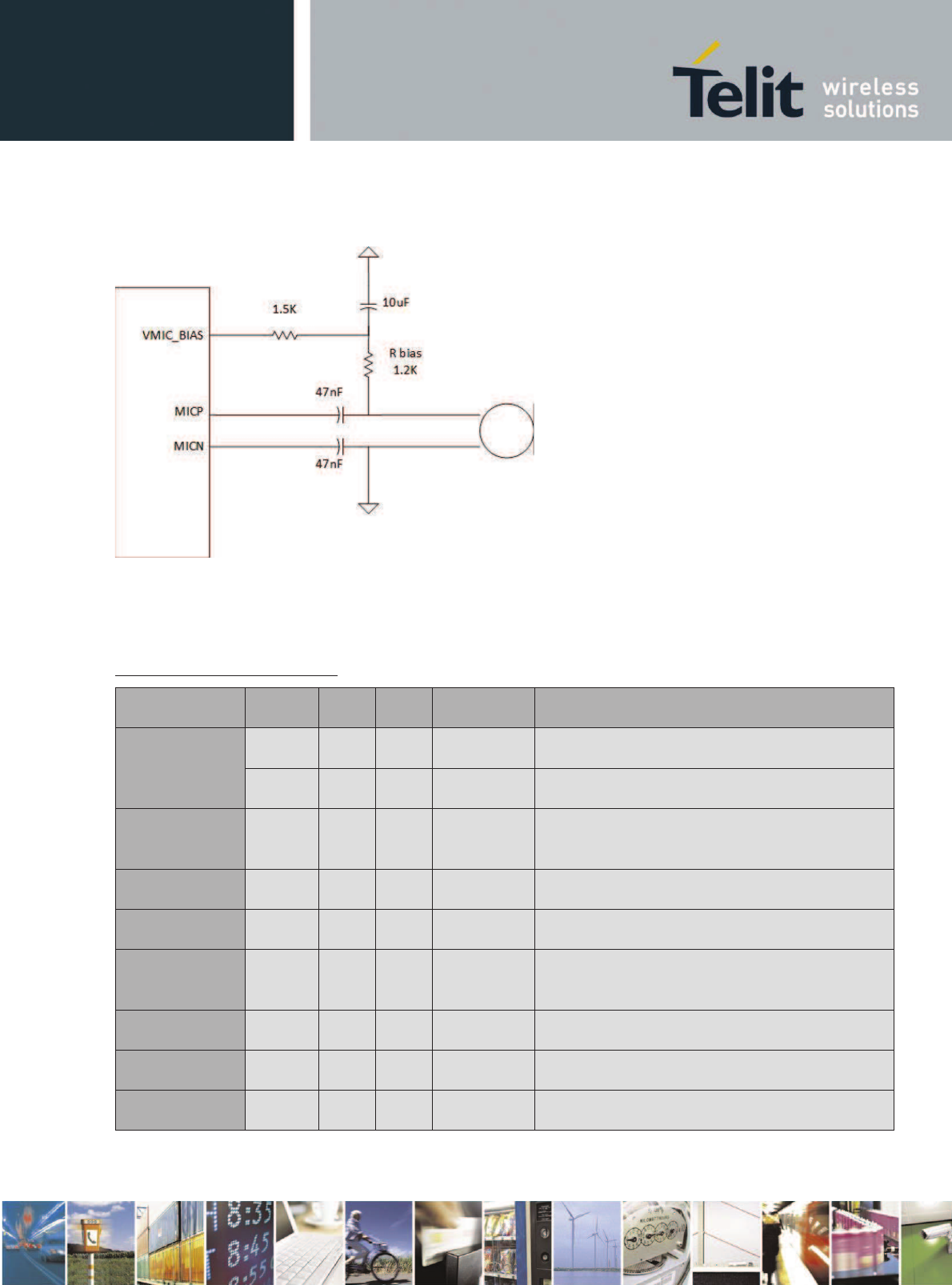

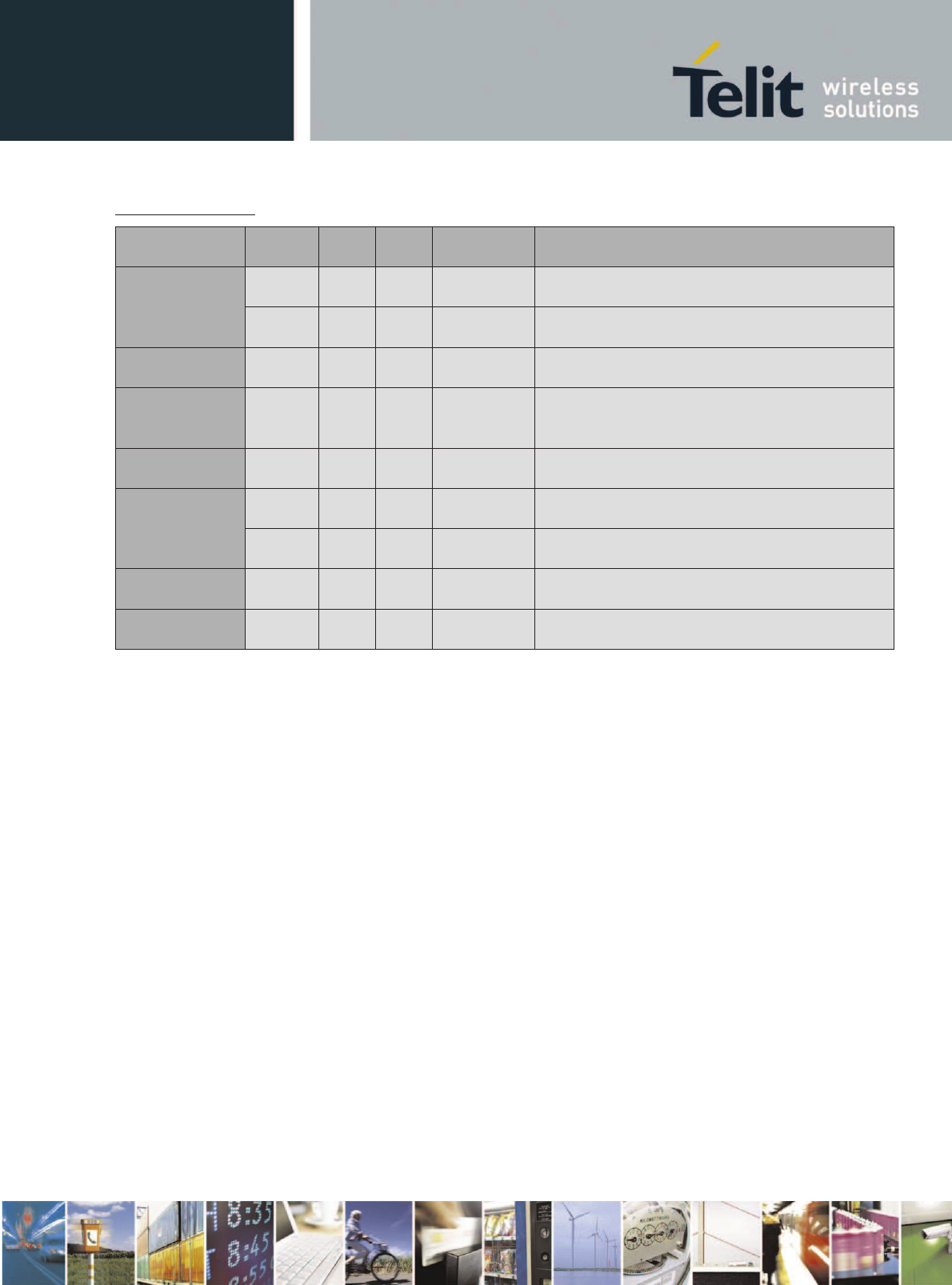

15.1.1. Analog IN...................................................... 83

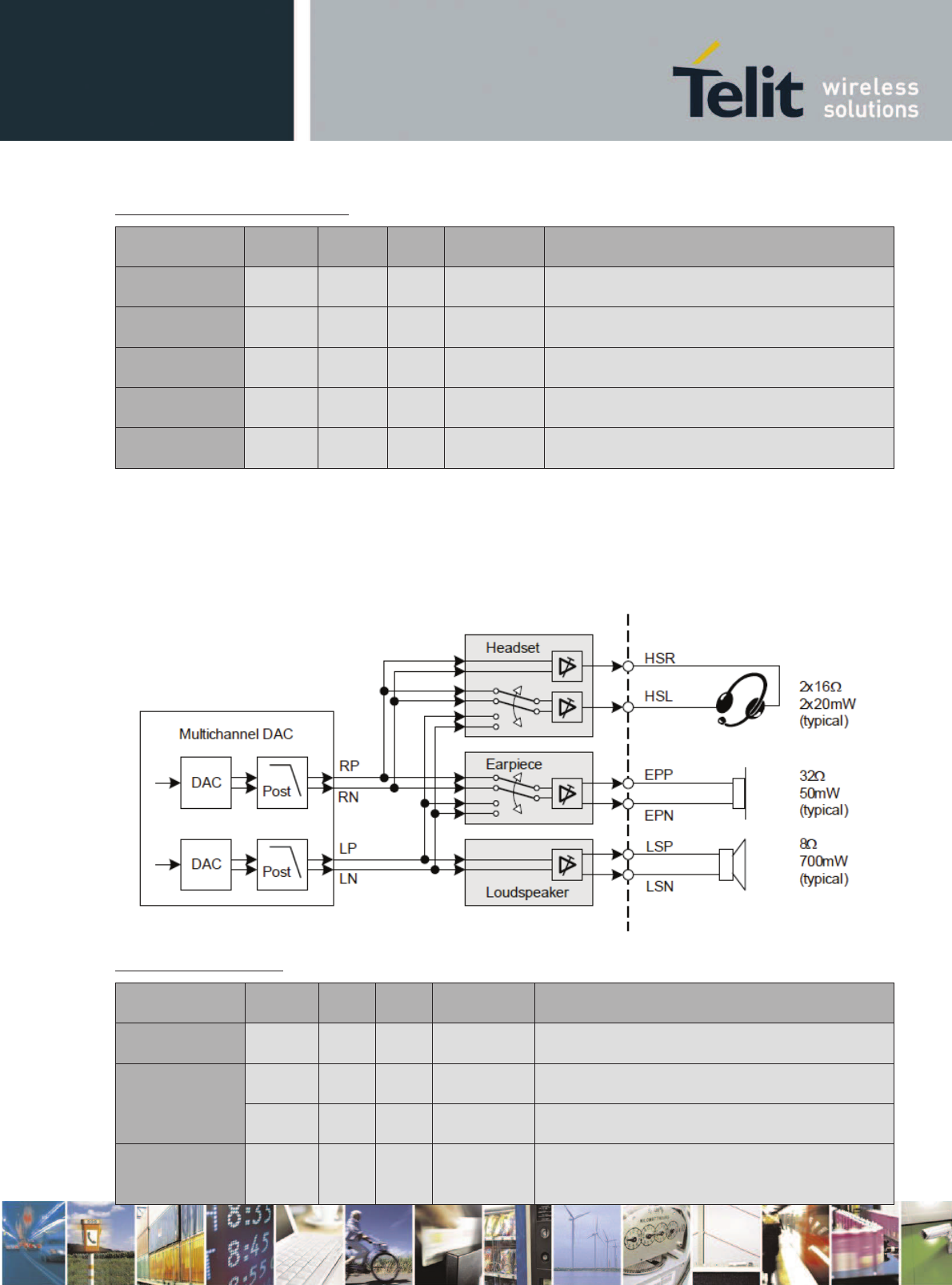

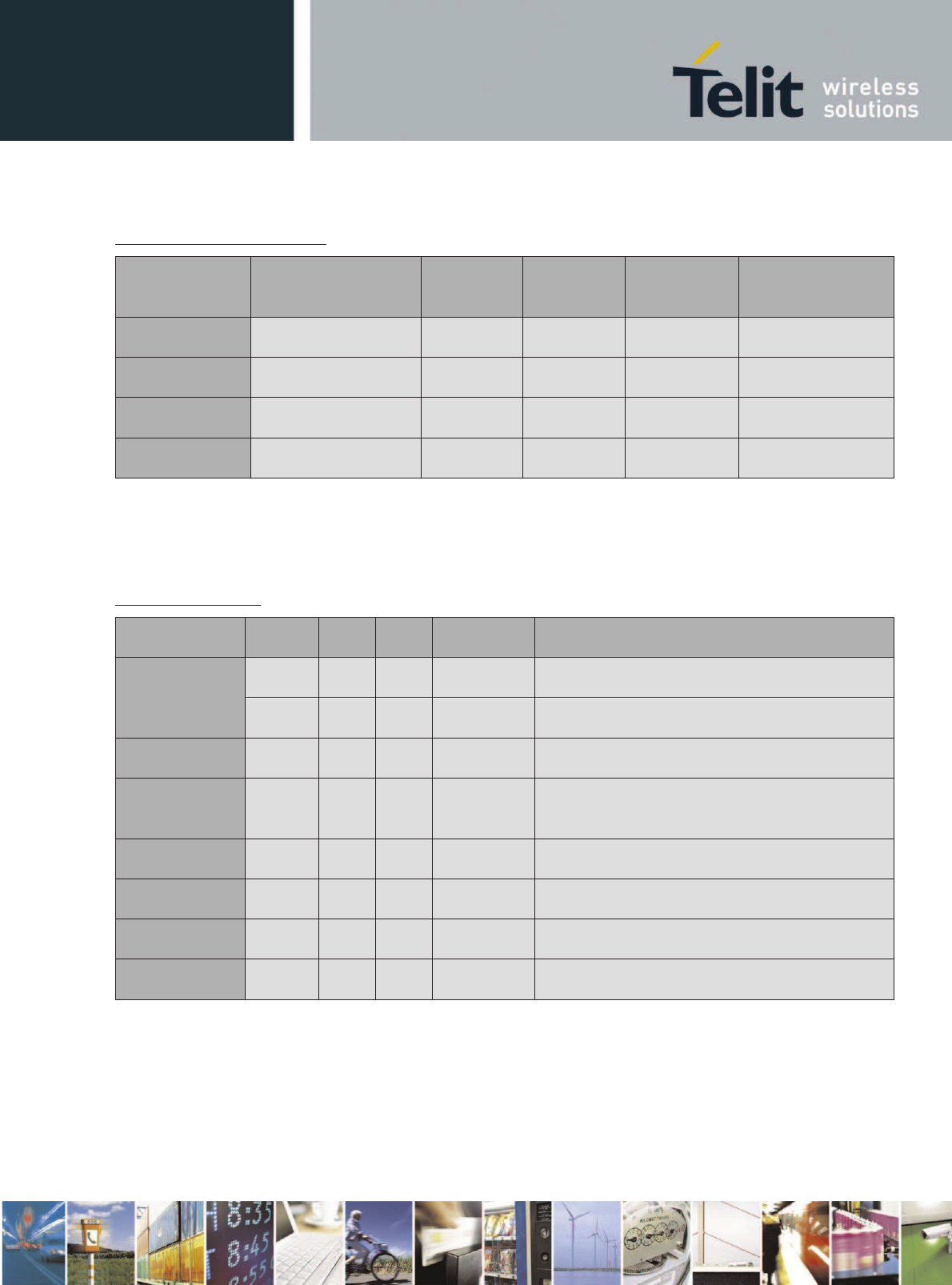

15.1.2. Analog OUT .................................................... 86

15.1.2.1. Earpiece ................................................. 87

15.1.2.2. Headset .................................................. 87

15.1.2.3. Loudspeaker .............................................. 88

15.2. Digital .................................................... 90

15.2.1. I2S .......................................................... 90

15.2.2. Digital microphone ................................................ 90

16. Antenna(s) .................................................... 91

16.1. GSM/WCDMA Antenna Requirements ............................. 91

16.1.1. GSM/WCDMA Antenna – PCB line Guidelines............................. 92

16.1.2. GSM/WCDMA Antenna – Installation Guidelines ........................... 92

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 8 of 112

16.2. WiFi/BT Antenna Requirements ................................... 93

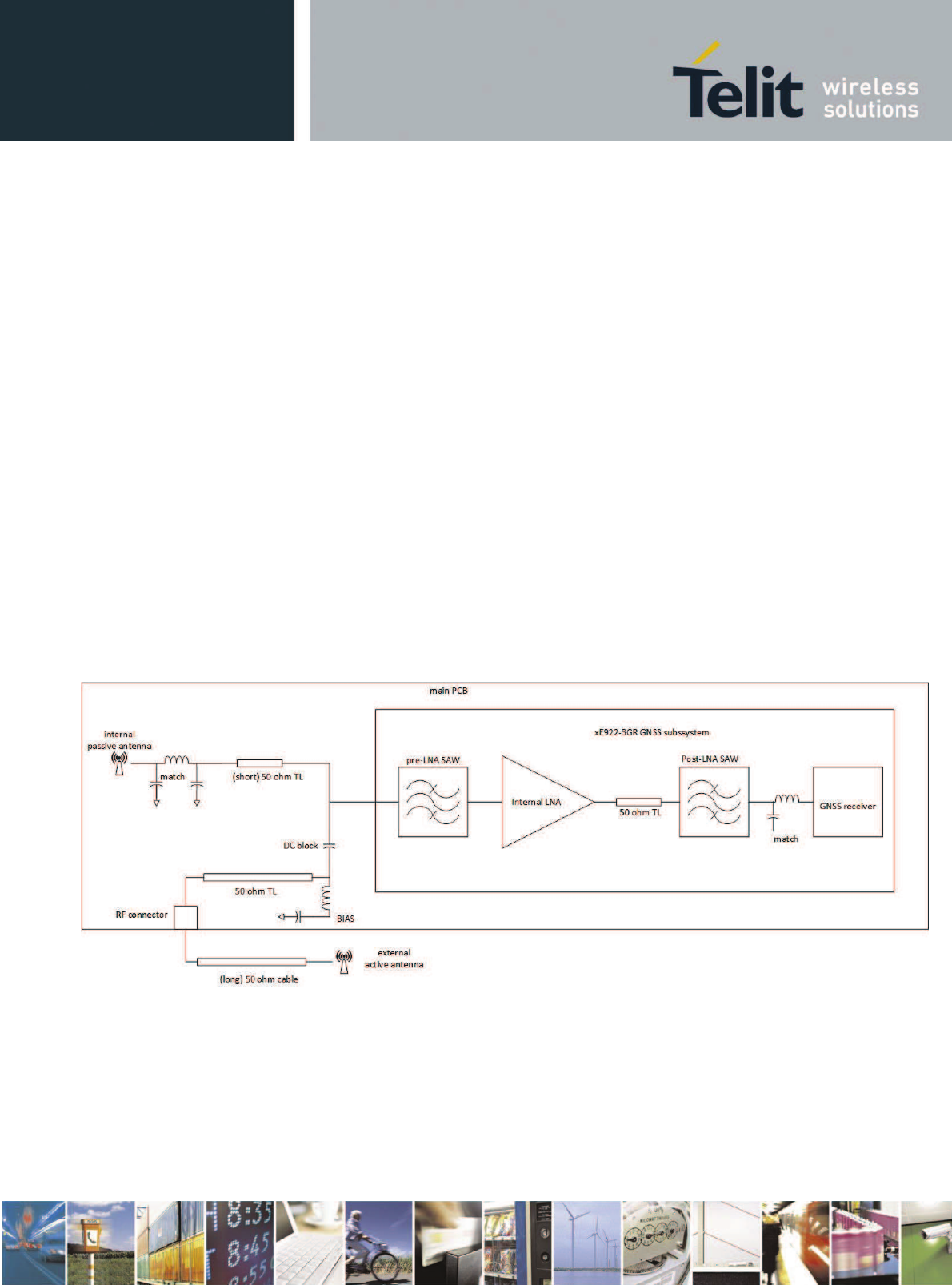

16.3. GNSS Antenna Requirements .................................... 93

16.3.1. Combined GNSS Antenna .......................................... 94

16.3.2. Linear and Patch GNSS Antenna ..................................... 94

16.3.3. Front End Design Considerations ..................................... 94

16.3.4. GNSS Antenna - PCB Line Guidelines ................................. 95

16.3.5. GNSS Antenna – Installation Guidelines ................................ 95

17. Mounting the module on your board .................................. 96

17.1. General .................................................... 96

17.2. Finishing & Dimensions ........................................ 96

17.3. Recommended foot print for the application main board .................... 97

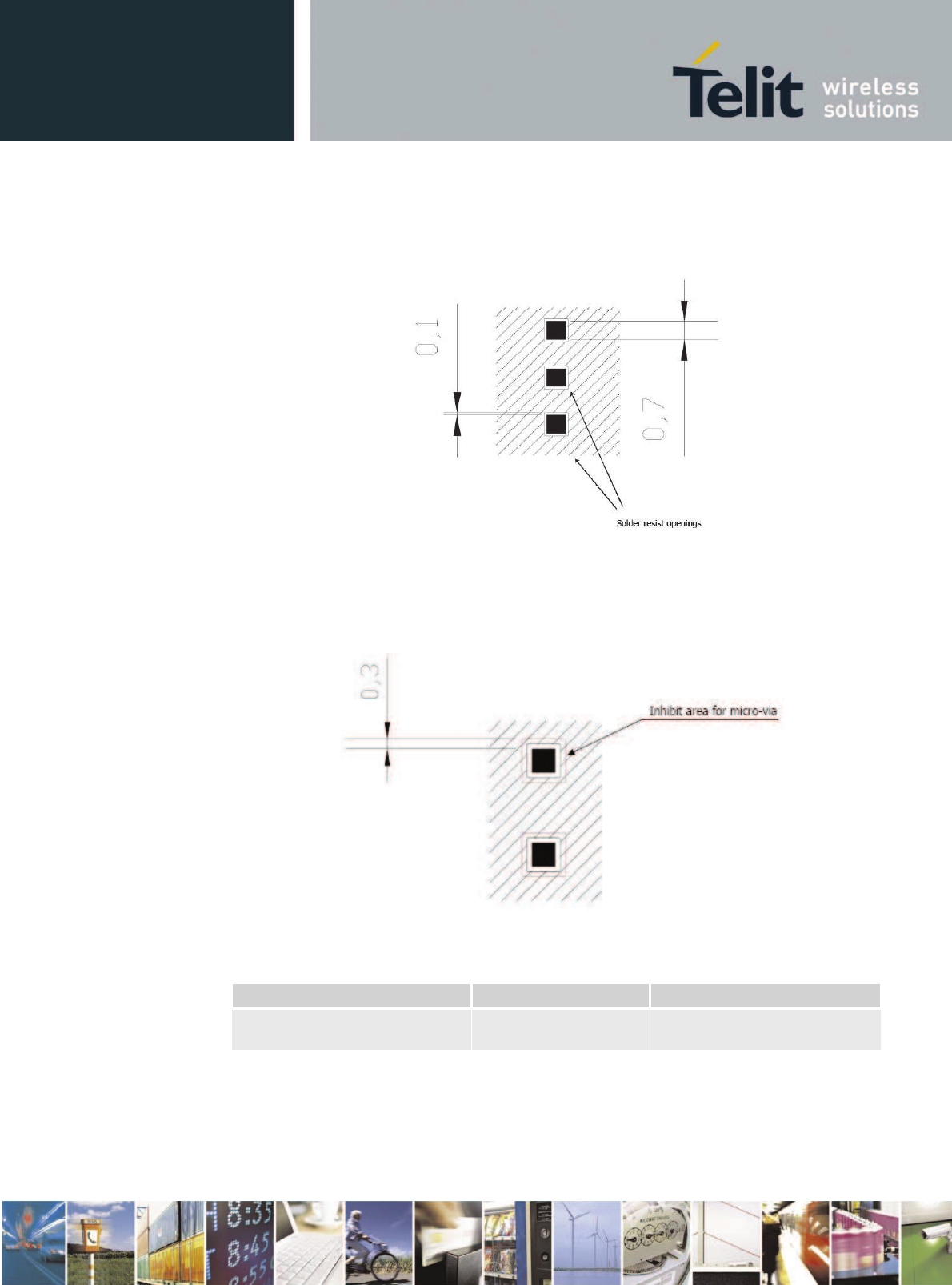

17.4. Stencil .................................................... 98

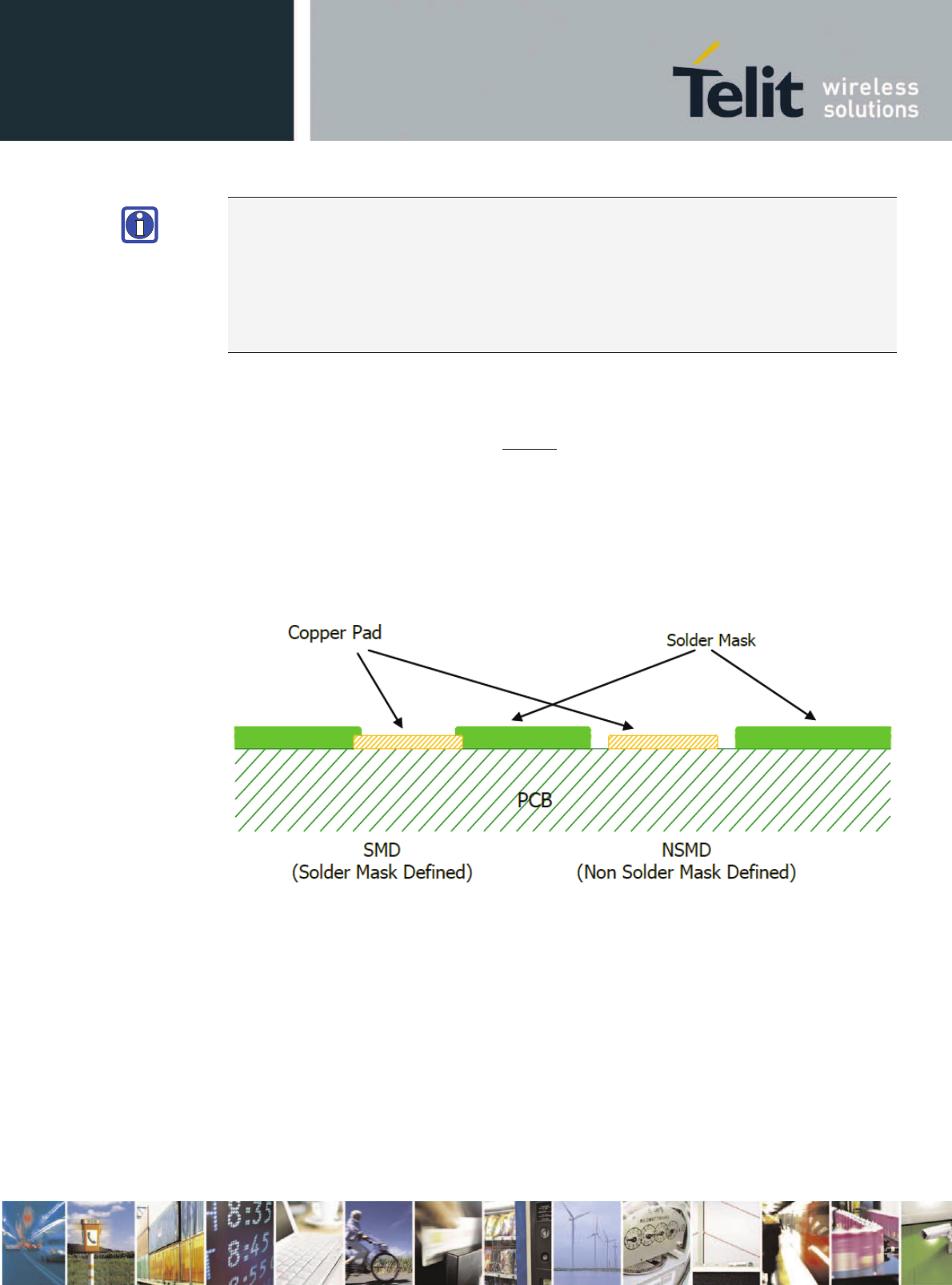

17.5. PCB Pad Design .............................................. 98

17.6. Recommendations for PCB Pad Dimensions (mm) ....................... 99

17.7. Solder Paste ................................................ 100

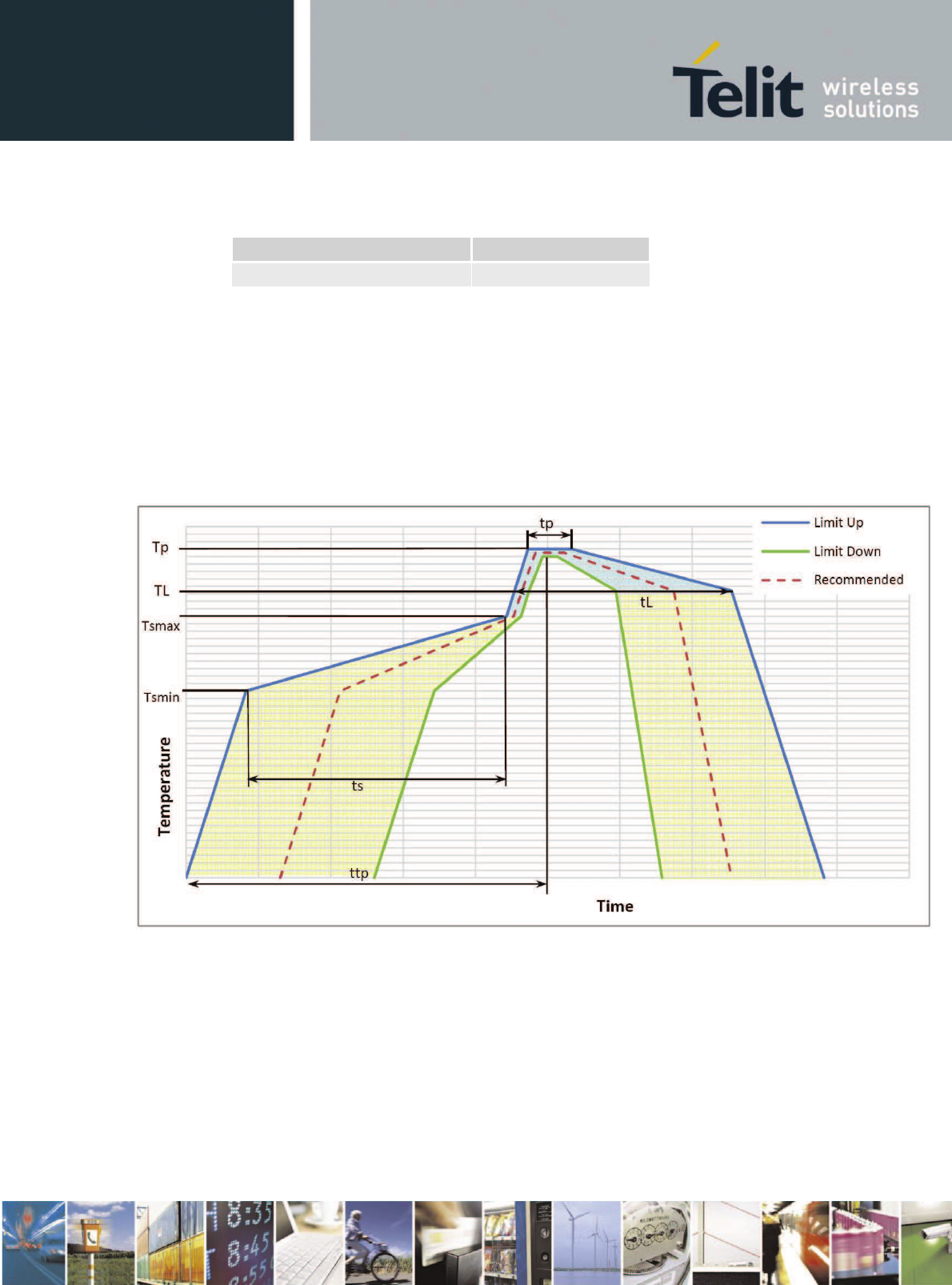

17.7.1. Solder Reflow .................................................. 100

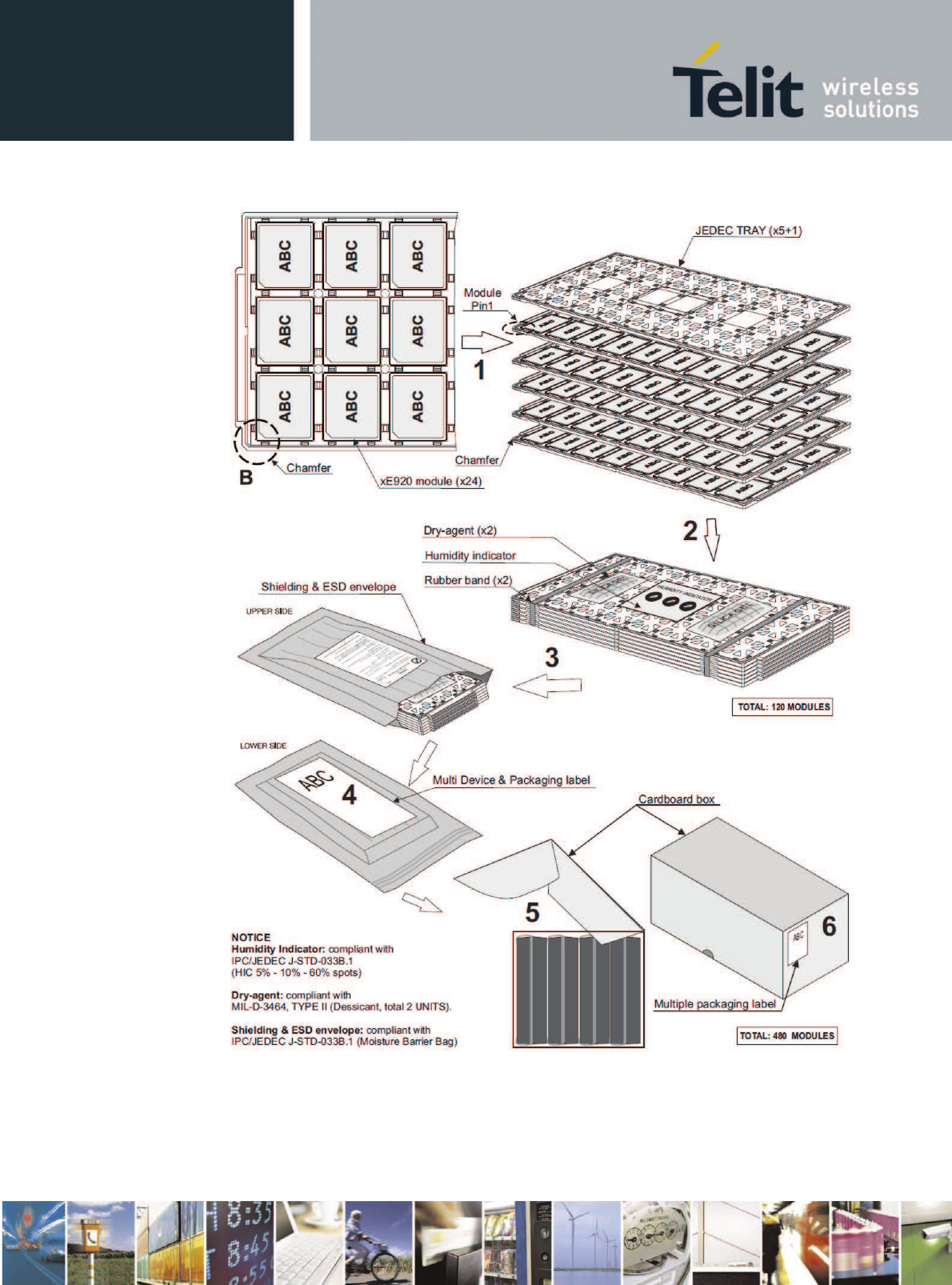

18. Packing system ................................................ 102

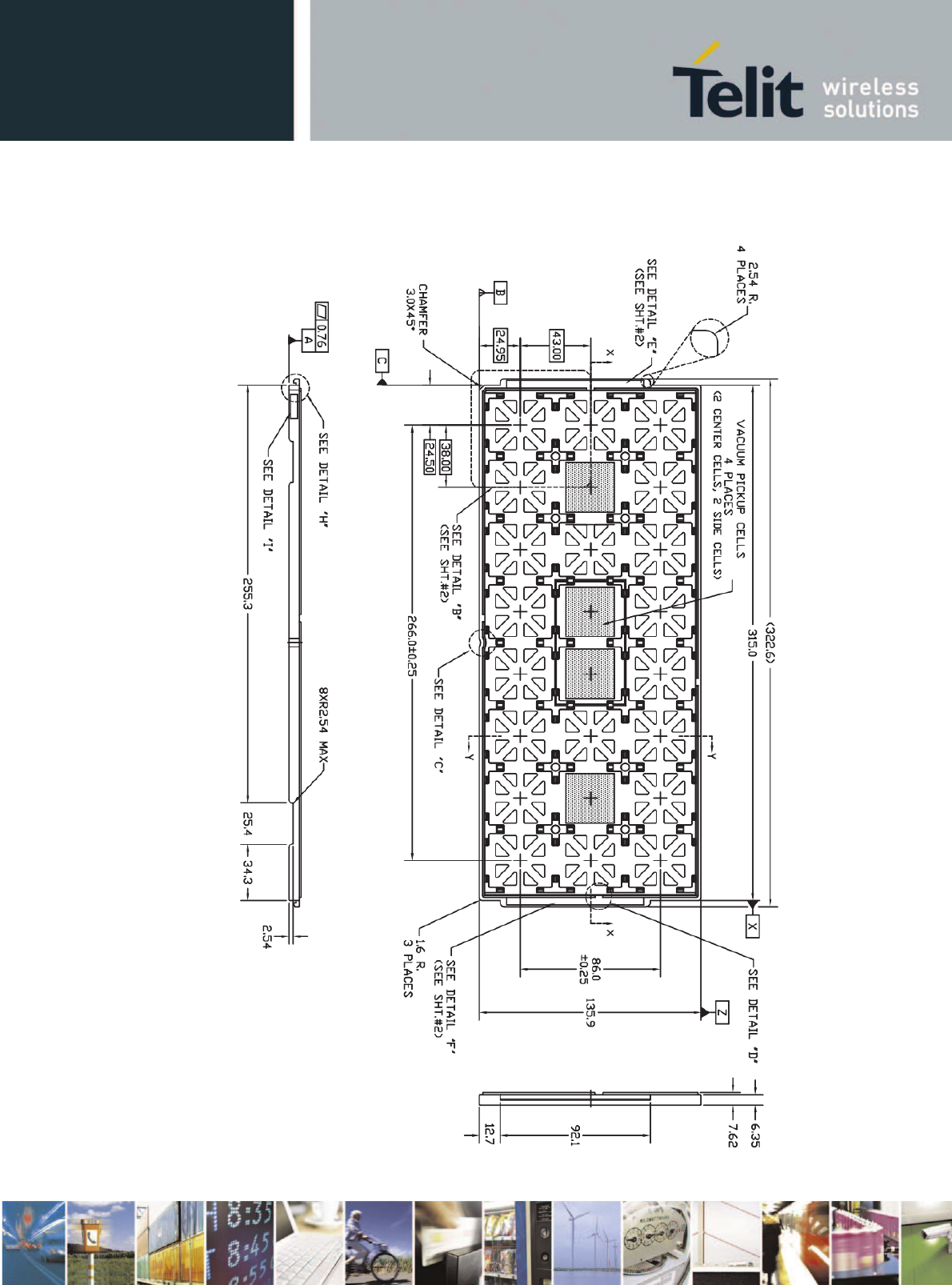

18.1. Tray Drawing .............................................. 104

18.2. Moisture Sensitivity .......................................... 105

19. Safety Recommendations ......................................... 106

20. Conformity assessment issues ...................................... 107

20.1. FCC/IC Regulatory notices ...................................... 107

20.1.1. Modification statement ............................................ 107

20.1.2. Interference statement ............................................. 107

20.1.3. RF exposure ................................................... 107

20.1.4. FCC Class B digital device notice ..................................... 108

20.1.5. Labelling Requirements for the Host device .............................. 108

20.2. 1999/5/EC Directive .......................................... 109

21. Document History .............................................. 112

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 9 of 112

1. Introduction

1.1. Scope

The aim of this document is to introduce Telit xE922-3GR modules as well as present possible

and recommended hardware solutions useful for developing a product based on the xE922-3GR

modules. All the features and solutions detailed are applicable to all xE922-3GR, where

“xE922-3GR” refers to the modules listed in the applicability table.

If a specific feature is applicable to a specific product, it will be clearly highlighted.

NOTICE:

The description text “xE922-3GR” refers to all modules listed in the APPLICABILITY TABLE 1.

In this document all the basic functions of a wireless module will be taken into account; for

each one of them a valid hardware solution will be suggested and usually incorrect solutions

and common errors to be avoided will be highlighted. Obviously this document cannot embrace

every hardware solution or every product that may be designed. Obviously avoiding invalid

solutions must be considered as mandatory. Whereas the suggested hardware configurations

need not be considered mandatory, the information given should be used as a guide and a

starting point for properly developing your product with the Telit xE922-3GR module.

NOTICE:

The integration of the GSM/GPRS/EGPRS/WCDMA/HSPA+/WiFi/BT/GNSS xE922-3GR

cellular module within user application must be done according to the design rules described in

this manual.

The information presented in this document is believed to be accurate and reliable. However,

no responsibility is assumed by Telit Communication S.p.A. for its use, such as any

infringement of patents or other rights of third parties which may result from its use. No

license is granted by implication or otherwise under any patent rights of Telit Communication

S.p.A. other than for circuitry embodied in Telit products. This document is subject to change

without notice.

1.2. Audience

This document is intended for Telit customers, especially system integrators, about to

implement their applications using the Telit xE922-3GR module.

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 10 of 112

1.3. Contact Information, Support

For general contact, technical support, to report documentation errors and to order manuals,

contact Telit’s Technical Support Center (TTSC) at:

TS-NORTHAMERICA@telit.com if located in North America

For other regions, Collabnet Telit web portal can be used at https://teamforge.telit.com (account

can be asked at support.collabnet@telit.com

Alternatively, use:

http://www.telit.com/en/products/technical-support-center/contact.php

For detailed information about where you can buy the Telit modules or for recommendations

on accessories and components visit:

http://www.telit.com

To register for product news and announcements or for product questions contact Telit’s

Technical Support Center (TTSC).

Our aim is to make this guide as helpful as possible. Keep us informed of your comments and

suggestions for improvements.

Telit appreciates feedback from the users about the information provided.

1.4. Text Conventions

Danger – This information MUST be followed or catastrophic equipment failure or bodily

injury may occur.

Caution or Warning – Alerts the user to important points about integrating the module, if

these points are not followed, the module and end user equipment may fail or malfunction.

Tip or Information – Provides advice and suggestions that may be useful when integrating

the module.

All dates are in ISO 8601 format, i.e. YYYY-MM-DD.

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 11 of 112

1.5. Supporting documents

· 1VV0301249_EVB USER GUIDE.pdf

· 1VV0301285_IFBD HW User Guide xE922-3GR.pdf

· 1VV0301324_MMI_EXT_CARD_xE922_3GR_HW USER GUIDE

· 80504NT11473A Thermal Guidelines.pdf

For further detailed information, HW/SW user manuals and application notes related to the INTEL chipset

applied for this RF module, please consult Intel Business Link Support (IBL): https://businessportal.intel.com

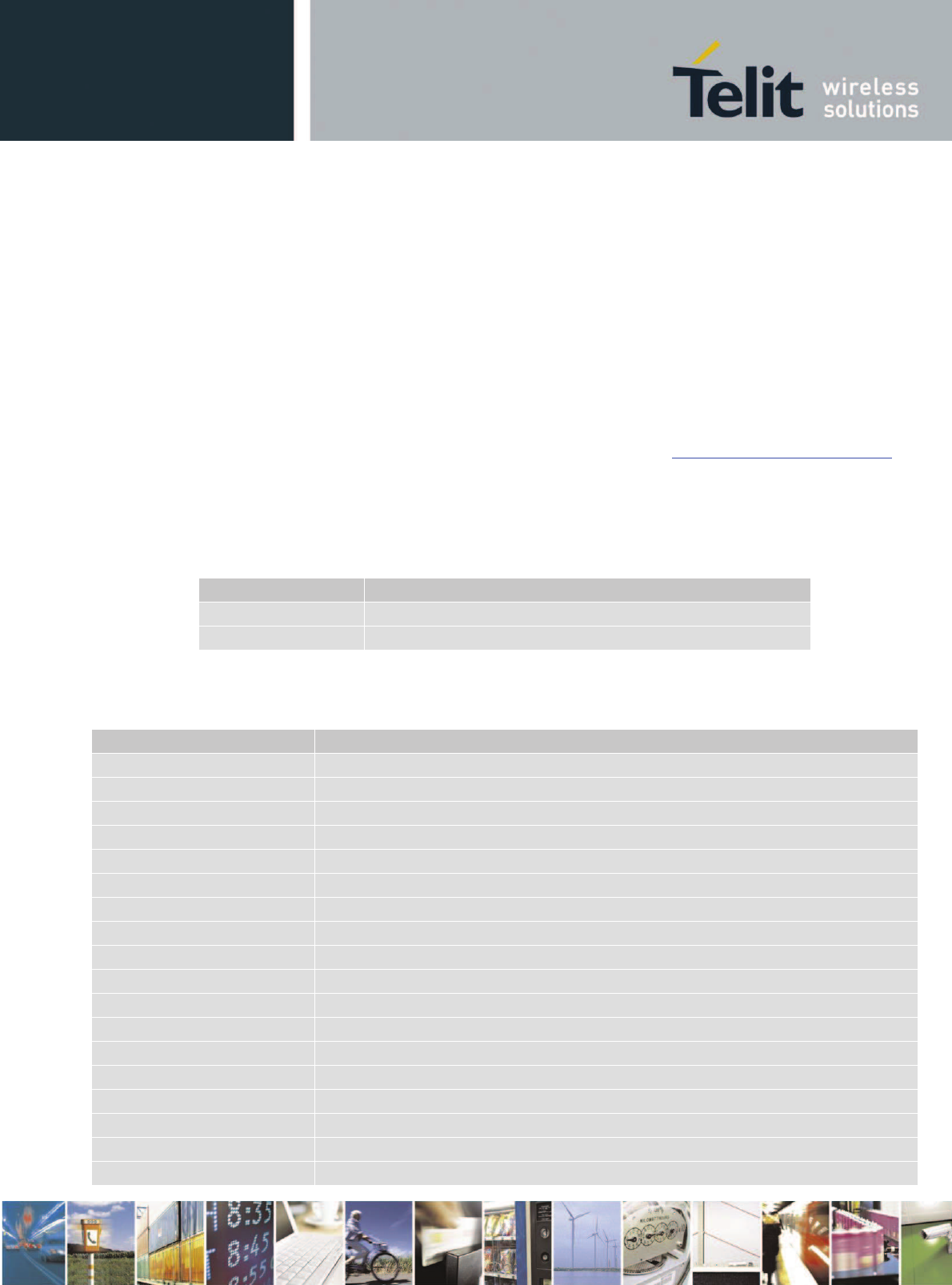

1.6. Product Variants

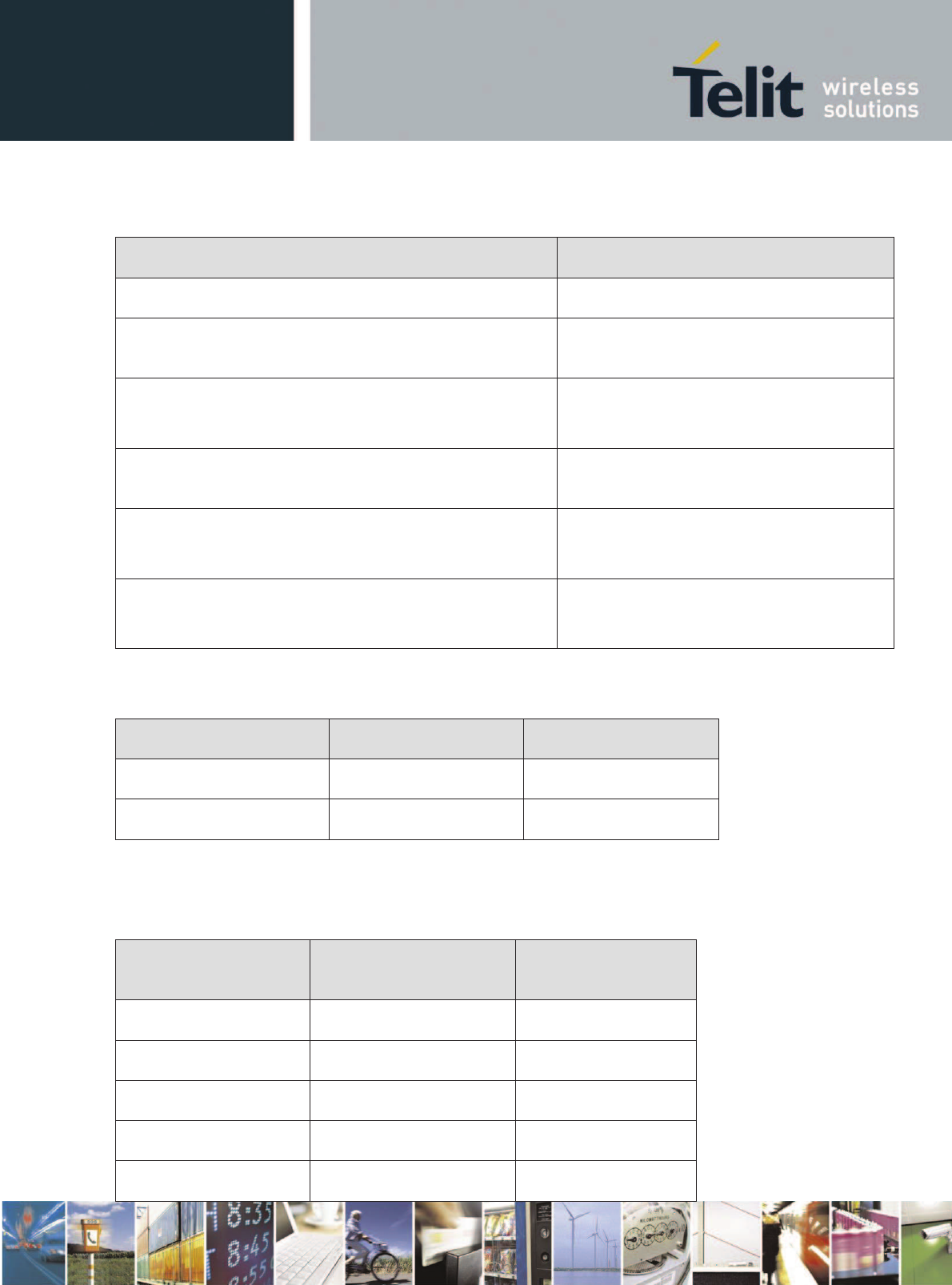

xE922-3GR is available in the following hardware variants:

Type Number

Description

HE922-3GR

GSM/GPRS/EGPRS/WCDMA/HSPA+/WiFi/BT/GNSS

WE922-3GR

WiFi/BT/GNSS

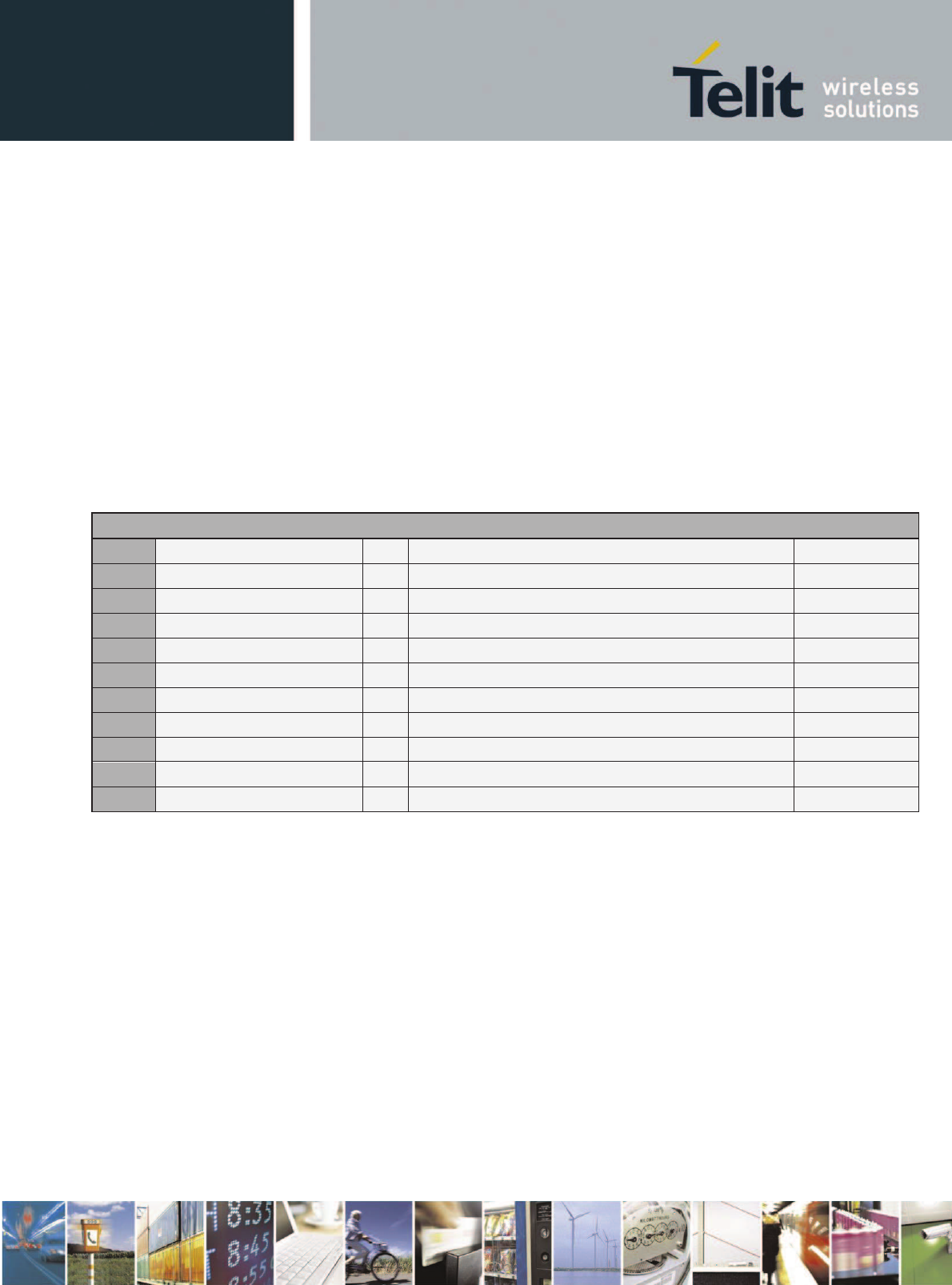

1.7. Abbreviations

Term

Definition

ABB

Analog baseband

ADC

Analog-to-digital converter

AE

Application-Enabled

AES-NI

Advanced Encryption Standard New Instructions

AFE

Audio FrontEnd

CABC

Content Adaptive Backlight Control

CDP (USB)

Charging downstream port

CEU

Configurable Encryption Unit

CSI

Camera serial interface

DAC

Digital-to-analog converter

DBB

Digital baseband

DCP (USB)

Dedicated charging port

DBP

dead battery provision

DSI

Display serial interface

DSDS

Dual Sim Dual Standby

EOC

End of charge

EDID

Extended display identification data

FDD

Frequency division duplex

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 12 of 112

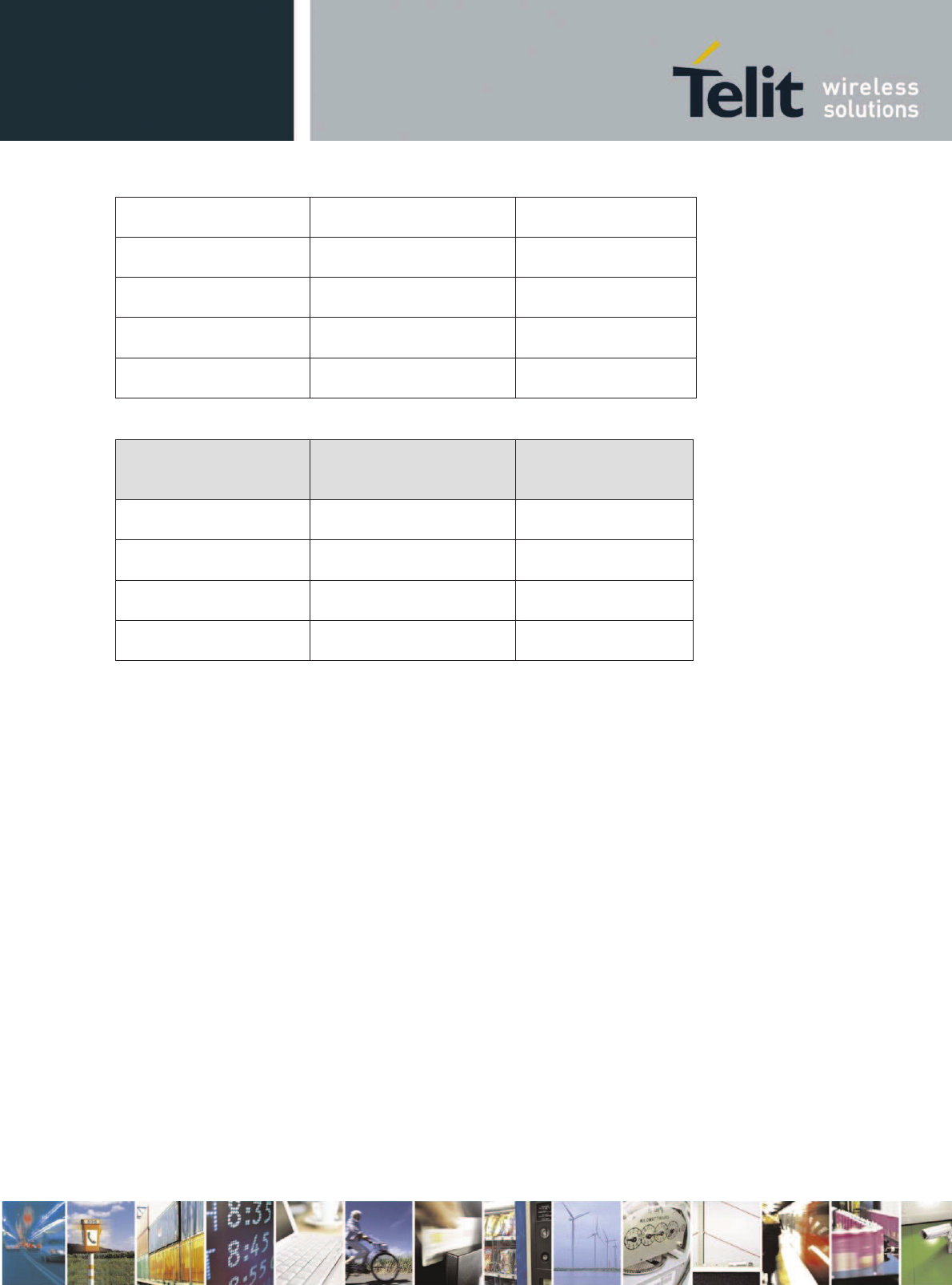

GLONASS

Global orbiting navigation satellite system

GNSS

Global navigation satellite system

GPIO

General-purpose input/output

GPRS

General packet radio services

GPS

Global positioning system

GSM

Global system for mobile communications

HMI

Human machine interface

I2C

Inter-integrated circuit

ISP

Image Signal Processor

IDI

Inter die interface

LE

Low Energy

LVDS

Low Voltage Differential Signaling

MIPI

Mobile Industry Processor Interface

MS

Microstrip line

PMU

Power management unit

SD

Secure digital

SDP (USB)

Standard downstream port

SL

Strip line

SIM

Subscriber identity module

SOC

System-On-Chip

SOC

State of charge

SMEP

Supervisor Mode Execution Privilege

SPI

Serial peripheral interface

TE

Tearing effect

UART

Universal asynchronous receiver transmitter

UMTS

Universal mobile telecommunications system

USB

Universal serial bus

USIF

Universal serial interface

VMM

Virtual machine manager

VT-x

Intel Virtual Technology

WCDMA

Wideband code division multiple access

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 13 of 112

2. General Product Description

2.1. Overview

Telit’s module family xE922-3GR is based on Intel’s IoTG Atom x3 Quad Core processor dual

chip platform.

DBB : SoC Atom x3

· CPU: Quad Core (Silvermont) 1.16 GHz

L1$ I/D 16KB/16KB ; L2$ 1MB

8-ch main application DMA / 4-ch secure DMA

Android 32bit, Linux Yocto 32bit

· GPU: GFX core modified Mali-450 MP4 600 MHz $128KB

· DSP : 2x TeakLite @277MHz

· Media Encode/Decode Engine: modified VeriSilicon Media Engine (dec G1/enc H1)

Video encoding:

• H.264 BP@level4.0, MP@level4.0, HP@level4.0

• Bit rate supported is from 10Kbps to 20Mbps

• JPEG Baseline

Video decoding:

• MPEG-1 Main Profile up to High Level

• MPEG-2 Main Profile up to High Level

• MPEG-4 Simple Profile up to Level 6, Advanced Profile up to Level 5

• H.264 up to HP Level 5.1, up to 1080p 30fps (yocto) /720p 50fps (android)

• HEVC Main Profile up to Level 4.1 High Tier, up to 1080p 30fps (yocto) /720p

50fps (android)

• VP6/VP8

• JPEG Baseline interleaved

· Security building blocks

ABB: AGOLD 620

· 2G/3G RF transceiver

· WLAN

· Bluetooth

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 14 of 112

· GNSS

· Audio

· Analog measurement

· Power management

The module incorporates the following key technologies:

· 2G/3G cellular subsystem

· GNSS subsystem

· WiFi and Bluetooth subsystems

· Display subsystem

· Camera subsystem

· Audio subsystem

· Power management

xE922-3GR is designed for commercial (0C to70C) & industrial (extended temperature -40C to

+85C) markets quality needs.

In its most basic use case, xE922-3GR can be applied as a wireless communication front-end for

M2M products, offering GNSS and mobile communication features to an external host CPU

through its rich interfaces.

The module supports data only communication, voice call is not supported.

xE922-3GR can further support customer software applications and security features. xE922-

3GR provides software application environment with sufficient system resources for creating

rich on board applications. Thanks to a dedicated application processor and embedded security

resources, product developers and manufacturers can create products which guarantee fraud

prevention and tamper evidence without extra effort for additional security precautions.

xE922-3GR can be self-sufficient and serve as a fully integrated IoT solution. In such a case,

customer would simply complement the module with a power supply, speaker amplifier,

microphone, antennae and an HMI (if applicable).

xE922-3GR is offered with different variants per the list in Section 1.6:

· HE922-3GR: Cellular/WiFi/BT/GNSS

· WE922-3GR: WiFi/BT/GNSS

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 15 of 112

2.2. General Functionality and Main Features

The xE922-3GR family of IoT modules features 2G/3G modem, GNSS and WiFi/BT

connectivity together with an on-chip powerful application processor and a rich set of

interfaces.

This overview sums all key interfaces offered by the module , consult the documentation on

INTEL’s IBL supporting website for actual implementation state.

A) Modem subsystem for data only communication (HE922-3GR variant only)

· 2G technology 3GPP TS 45.005

o GSM/GPRS/EDGE (multislot class 10)

note : only EDGE RX mode supported

o Quad band support (GSM850/E-GSM900/DCS1800/PCS1900)

· 3G technology 3GPP TS 25.101 rel 7

o WCDMA (HSDPA 21Mbps cat14 / HSUPA 5.76Mbps cat6)

o Quad band support ( band 1 / 2 / 5 / 8)

o Class3 power class

· Two (U)SIM ports – dual voltage 1.8/3V

ISO 7816-3 IC card standard

B) GNSS subsystem

§ GPS/GLONASS receiver

§ Assisted GNSS

§ SBAS: WAAS, EGNOS

C) WiFi/Bluetooth subsystem

· WiFi 802.11 b/g/n 1x1 (1-14, max channel width 20MHz)

· BT 4.0 & BLE

· Single antenna shared for WiFi and BT

· Up to 72.2Mbps OTA throughput, 50Mbps actual throughput

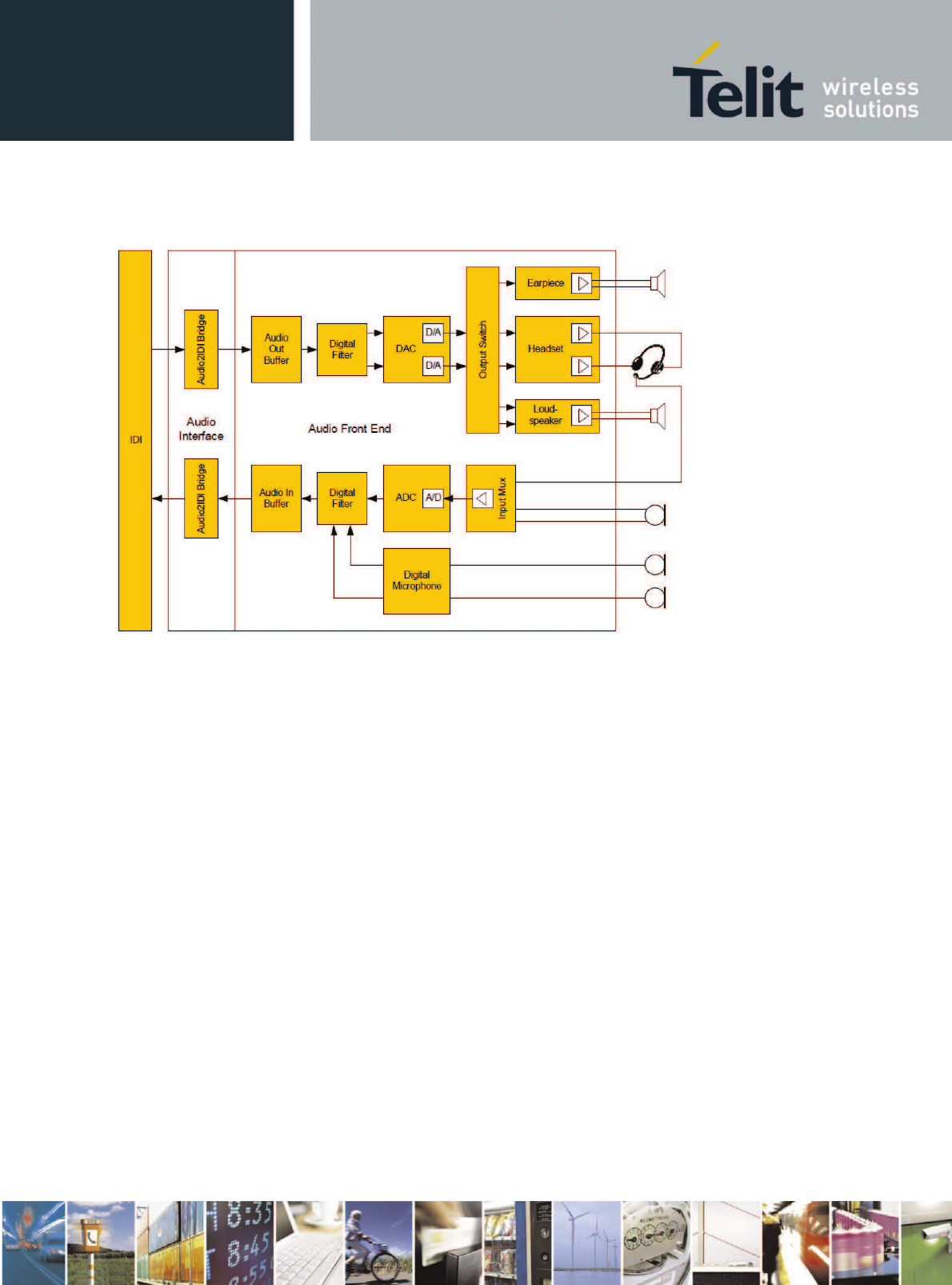

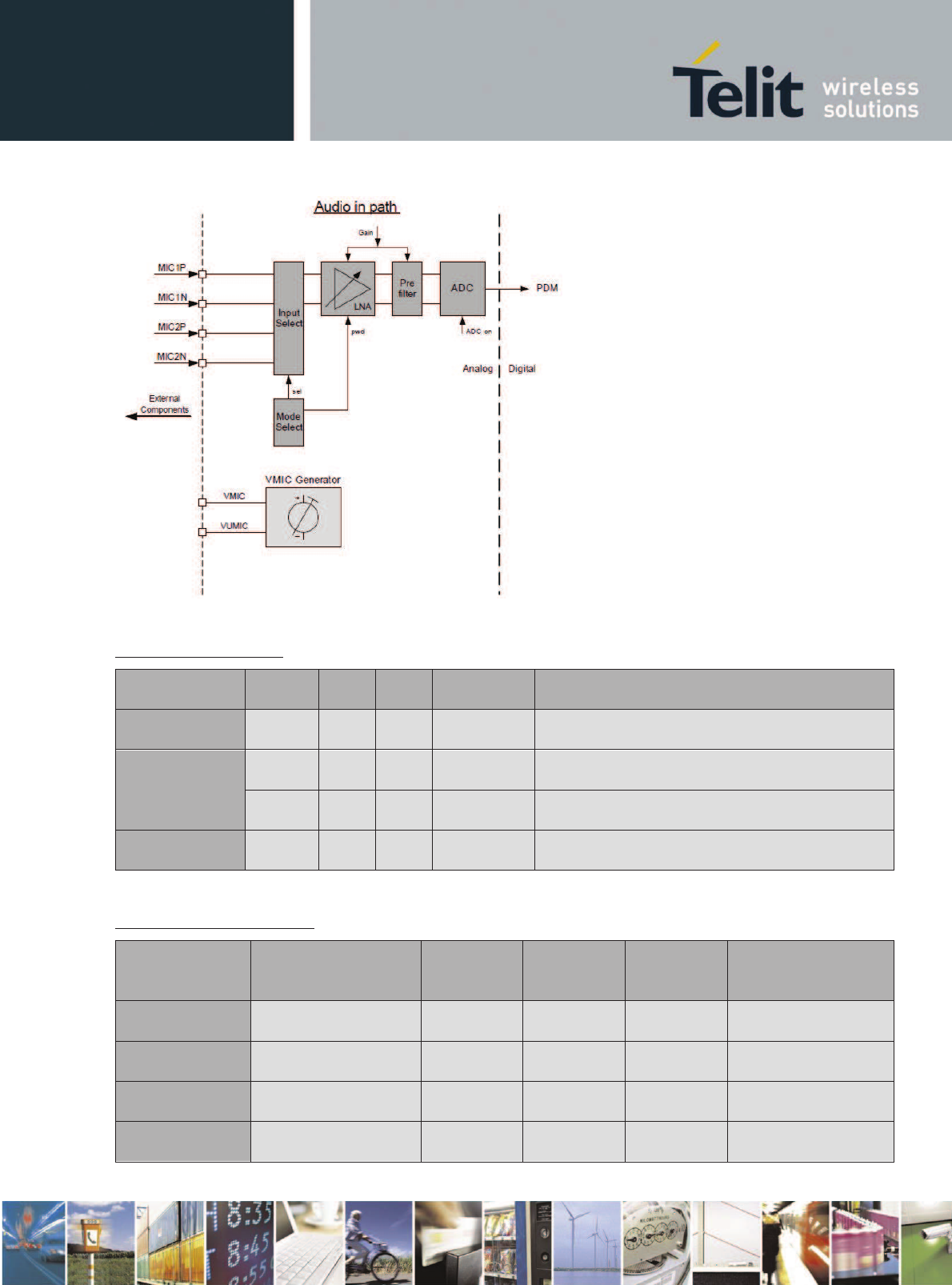

D) Audio subsystem

· Embedded analog codec

o 2x microphone inputs + bias supply

o 1x stereo headset output

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 16 of 112

o 1x mono earpiece output

o 1x mono speaker (classD 700mW/3.8V/8 ohm)

· Dual digital microphone

· I2S digital audio IO ( pinning multiplexed with USIF1 port)

E) Display subsystem

Up to 1080p, 24-bit color, 1080p 30fps (yocto) /720p 50fps (android)

· MIPI-DSI (one x4 lanes port, tearing effect timing control)

· LVDS (one x4 lanes port)

· 4 display layer

· Support color space conversion :YUV2RGB and RGB2YUV

· Support replication and dithering

· 2D Graphic Engine

· Backlight control (CABC input, BL feedback input, BL drive output)

· I2C port for touch panel control IC

F) Camera subsystem

Up to 13Mpix, 15 fps ( ISP throughput up to 221 Mpix/sec) (8Mpix, 25fps)

· 4 lanes MIPI-CSI for primary camera (up to 13Mpix/1080p)

· One lane MIPI-CSI for secondary camera (up to 5Mpix/720p)

· 1 camera at a time

· GPIO’s for camera control

· I2C port for camera subsystem control

· Camera auxiliary supply output

G) Power management

· External battery charger IC support

o I2C port dedicated to external charger IC control

o Dedicated GPIO’s

o Fuel gauge input, VBAT/DC sourcing sense ADC input

· Ability to supply the module from DC source without external battery charger

IC implementation

· Rich set of embedded power management functions are in place to permit

minimization of the powerconsumption of the system in all operating modes.

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 17 of 112

o Reduction of switching power consumption by clock gating.

o Reduction of leakage power by switching off non active logic.

o Dynamic Frequency Voltage Scaling reducing the supply voltage

depending on the perfomance requirements of the system

· The following system operating modes are defined :

o OFF : complete system switched off ( all context lost)

o WORKING : CPU executing scheduled tasks

o IDLE : CPU in power state HALT , waiting for interrupt

o DEEP SLEEP: CPU in power state DORMANT

H) Application processor

The Intel virtual machine manager (VMM) shares CPU resources of the quad core Atom

between the cellular DBB modem high level protocol implementation, the applied OS and

customer applications. Available BSP’s are 32bit Android and 32bit Linux (Yocto project).

The chipset external memory interface controller EMIC supports

· Low power LPDDR3 upto 2Gbyte

clock frequency up to 533MHz (data speed 1066 Mbps/pin)

· embedded MMC card interface eMMC4.51

clock frequency up to 52MHz ( data speed DDR 102 Mbps/pin)

(dataspeed DDR transfer)

Module embedded memory size implementation :

· FLASH eMMC: 8 Gbyte (x8 pin, data speed up to 833 Mbps)

· RAM LPDDR3: 1 Gbyte ( x32 pin, data speed up to 34112 Mbps)

I) Security capabilities of DBB:

Intergrated Trusted Executon Environment (TEE) based on Secure Virtual Machine and

HW Crypto Unit (CEU)

· Atom Quad Core:

VT-x2 / AES-NI / SMEP ( Supervisor Mode Execution Privilege)

· Extensible Secure Execution Environment:

HW crypto accelerator – CEU / 256K SRAM

· Configurable execution unit (CEU):

o DES/3DES

o AES(128,192,256)

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 18 of 112

o Exponentiation accelerator – supports RSA(1024.2048)

o Hashing engines : MD5, HMAC, SHA1/256

o True-RNG

· Secure memory : isolated memory region IMR for secure VM

· Secure boot : root of trust is SEC ROM

· Content protection : Widevine Level 1 DRM ( HW protected Video Path)

J) Rich set of module I/O interfaces, including:

· SDIO: SD 3.0, 1x 4bit, speed up to DDR50

only 1.8V supported

· SDMMC: 1x 4bit, default mode (26MHz)

including power supply (fixed 2.9V) and card detect

· USB2.0 (FS/HS DRD dual role device)

The USB port is typically used for:

o Flashing of firmware and module configuration

o Production testing

o Accessing the Application Processor’s filesystem

o AT command access

o High speed WWAN access to external host

o Diagnostic monitoring and debugging

o Communication between Java application environment and an

external host CPU

o NMEA data to an external host CPU

o Connect to USB peripherals or hubs (note: application note available

from chipset provider on USB hub connectivity)

· Peripheral Ports

These can be applied to support several sensors like : accelerometer , gyroscope,

magnetometer, proximity and ambient light sensors

Please consult Intel’s IBL Support website for AVL (approved vendor list), as well

for recommended implemenation and port assignment

· 3x I2C port full speed:

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 19 of 112

o I2C_AUX : auxiliary use

o I2C_CAM / I2C_TP : available when not applied for camera and/or

touchpad control

· USIF1 port: configurable as SPI or UART (up to 48MHz) (multiplexed with I2S)

· USIF2 port: configurable as SPI or UART (up to 26MHz)

· 26 general purpose GPIOs with at least 8 interrupts ( more can be available

depending on final product configuration)

· Analog audio I/F

· Antenna RF ports (GNSS, CELLULAR,WIFI/BT)

K) Form factor (40x34mm), 441 pin LGA

L) Single supply module. The module generates all its internal supply voltages.

M) Built-in RTC / backup supply pin for supercap

N) Two Operating temperature range specified for the xE922-3GR family:

· Commercial: 0 °C to +70 °C

· Industrial extended temperature: -40 °C to +85 °C

O) Cellular transmitter can work simultaneously with the transmitter in the 2.4GHz band. Only

one of the 2.4 GHz modes works at a given moment and it can work simultaneously with any

of the cellular modes.

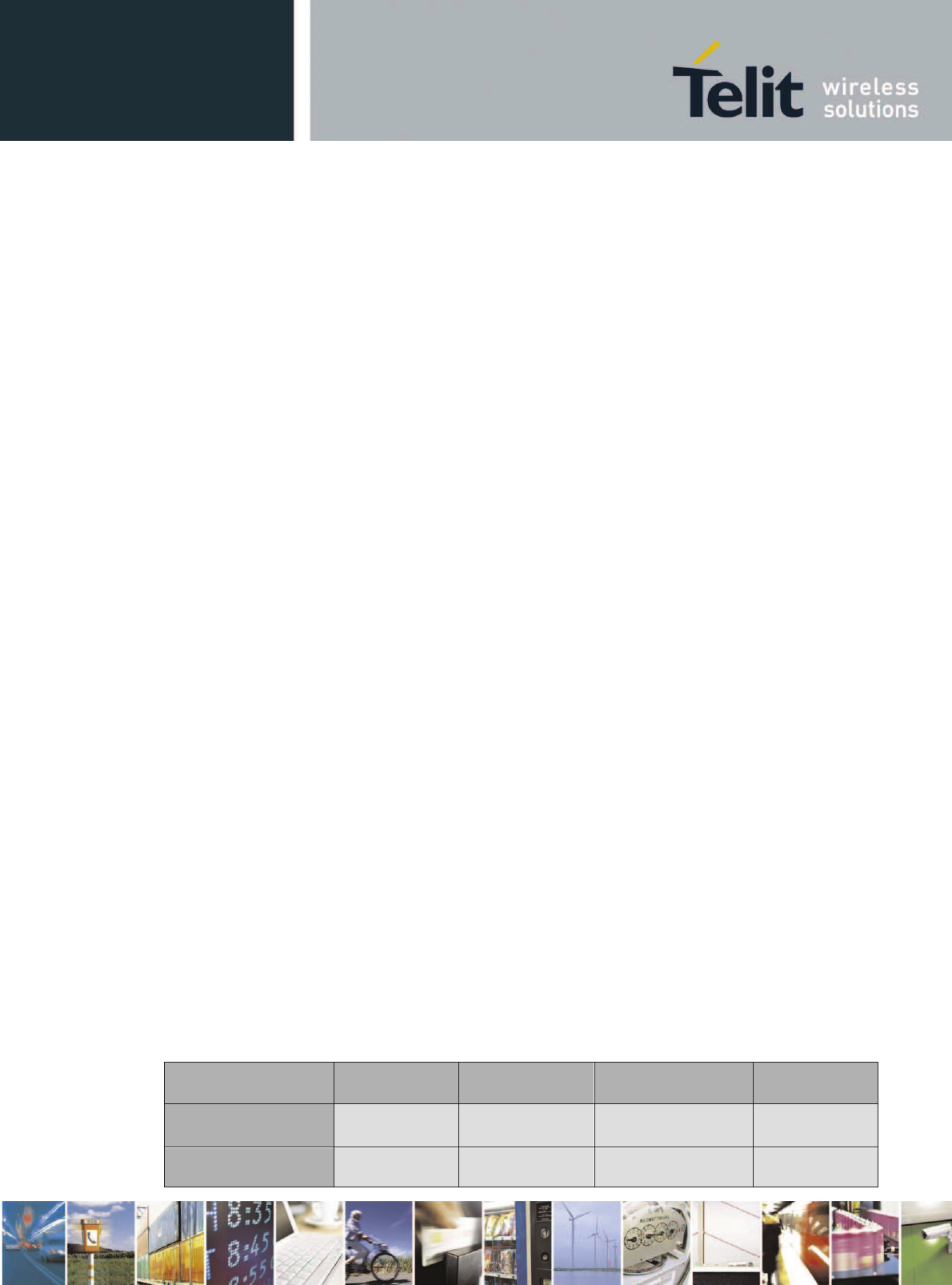

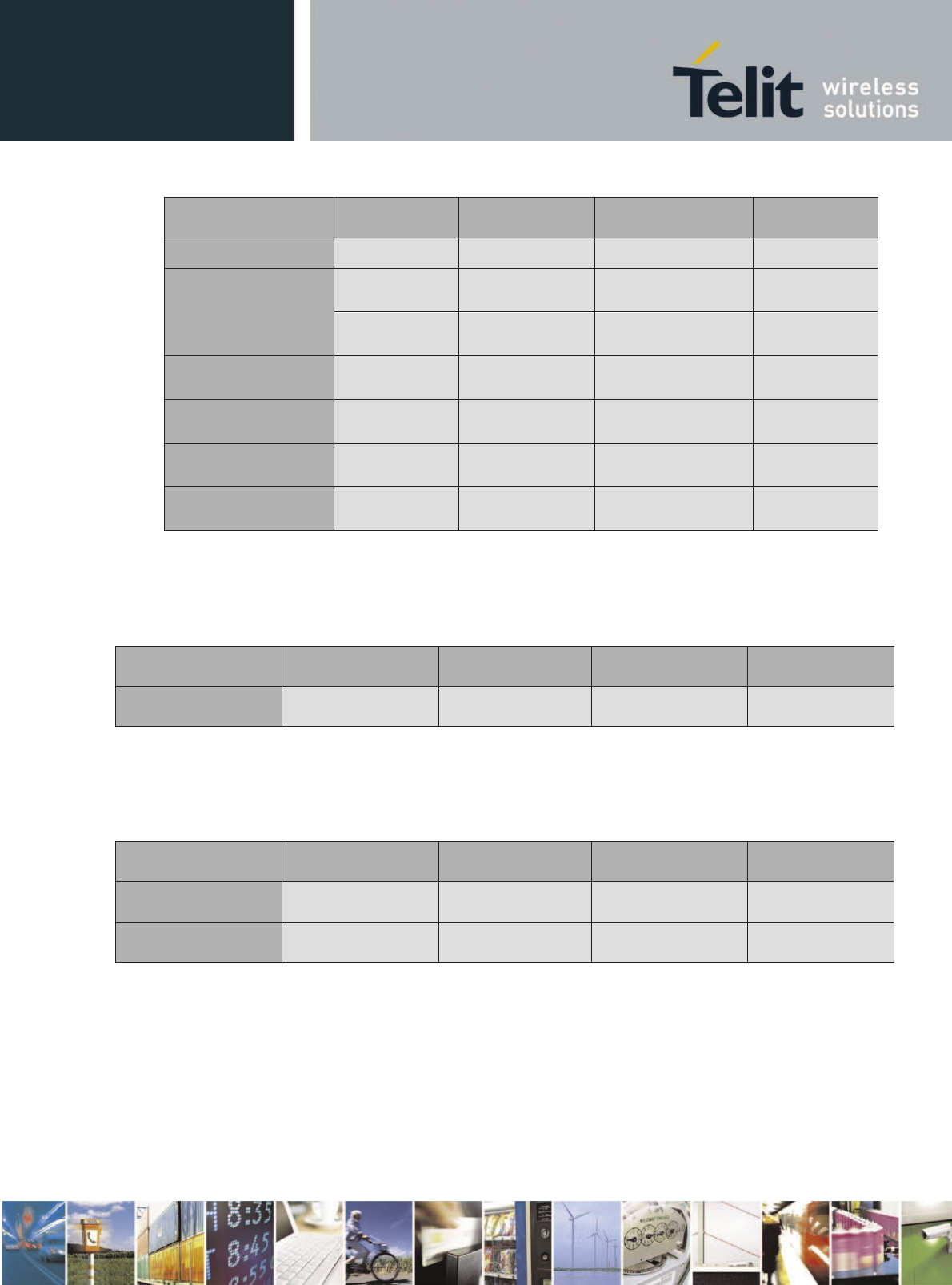

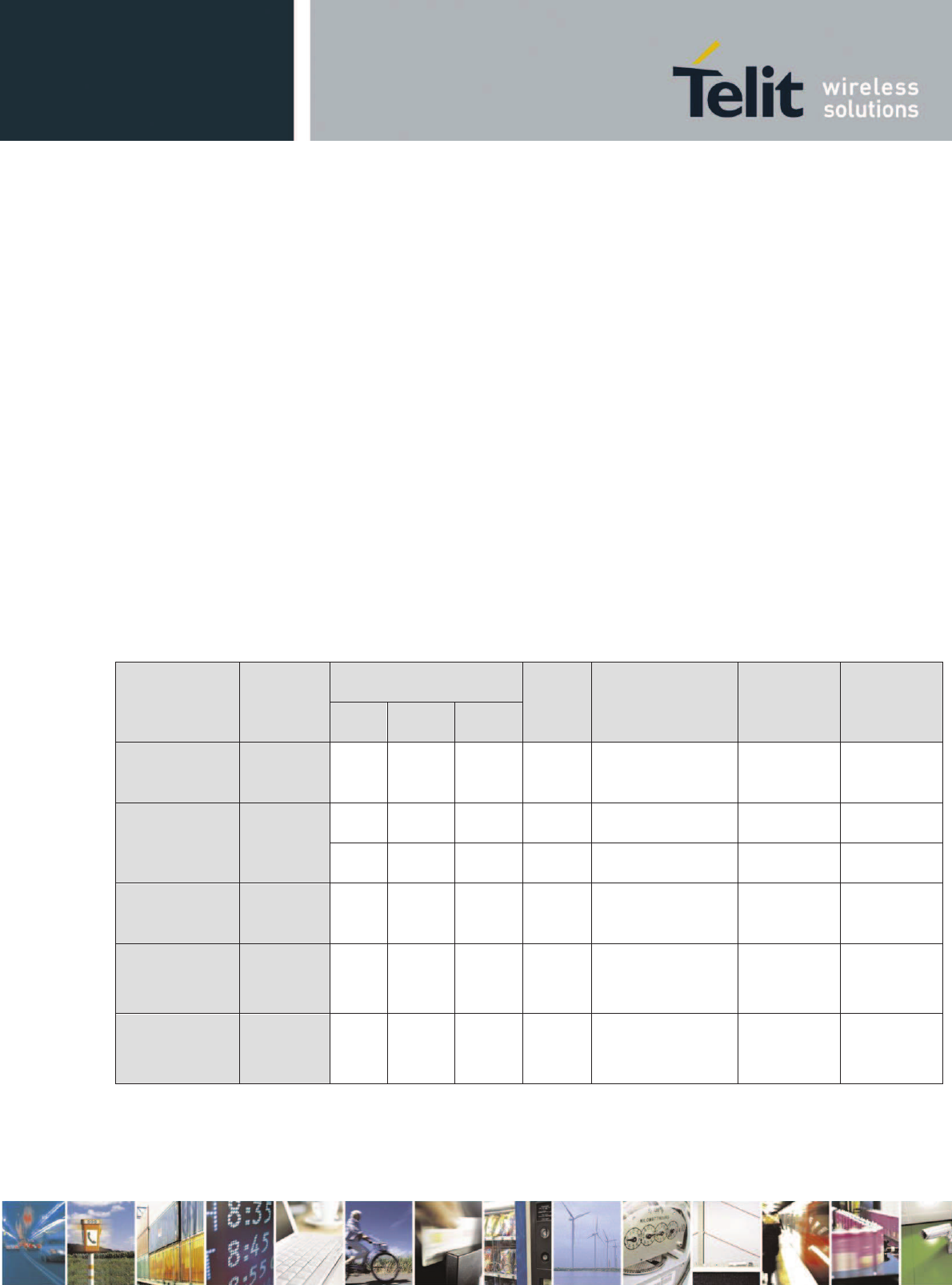

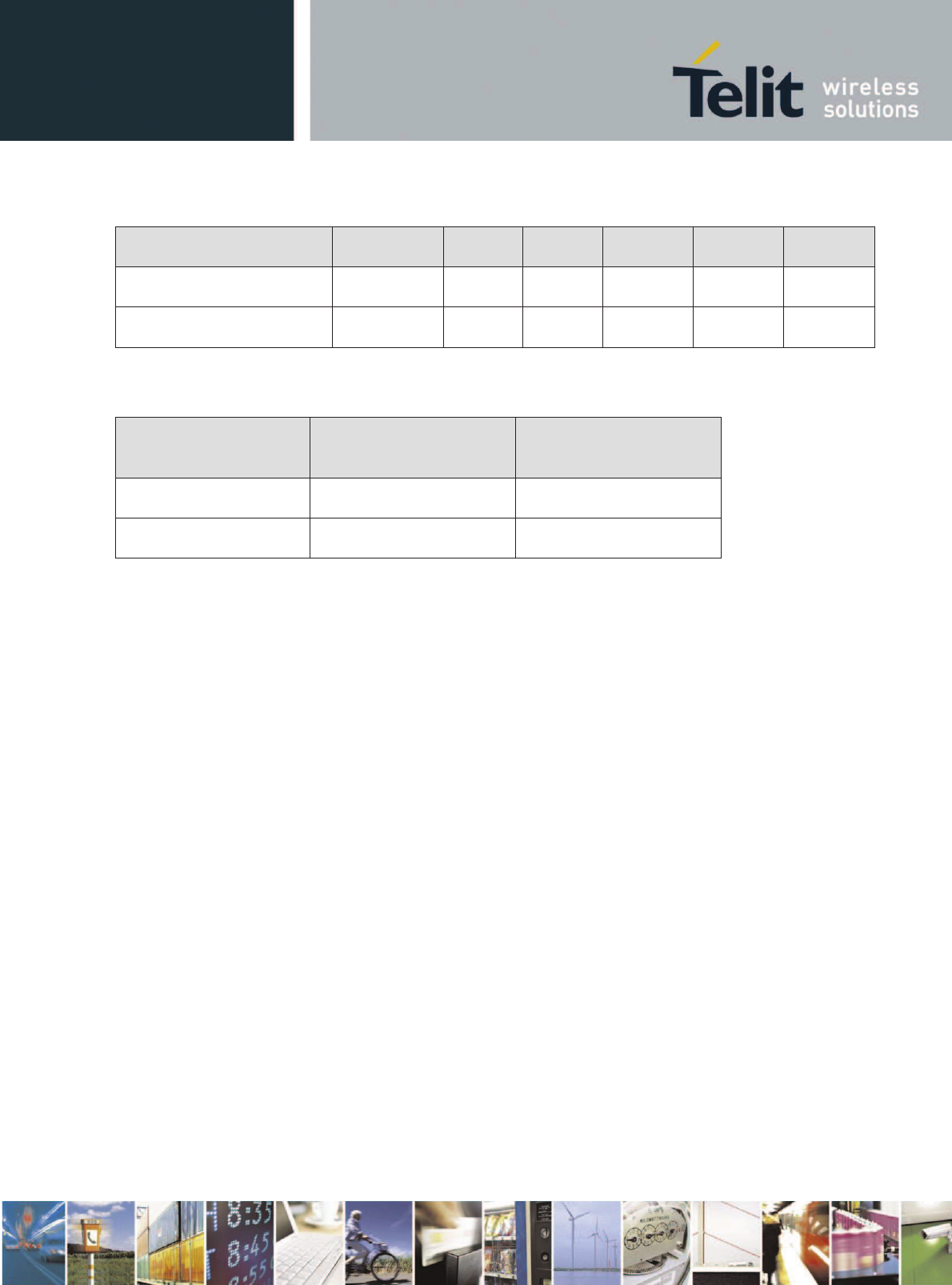

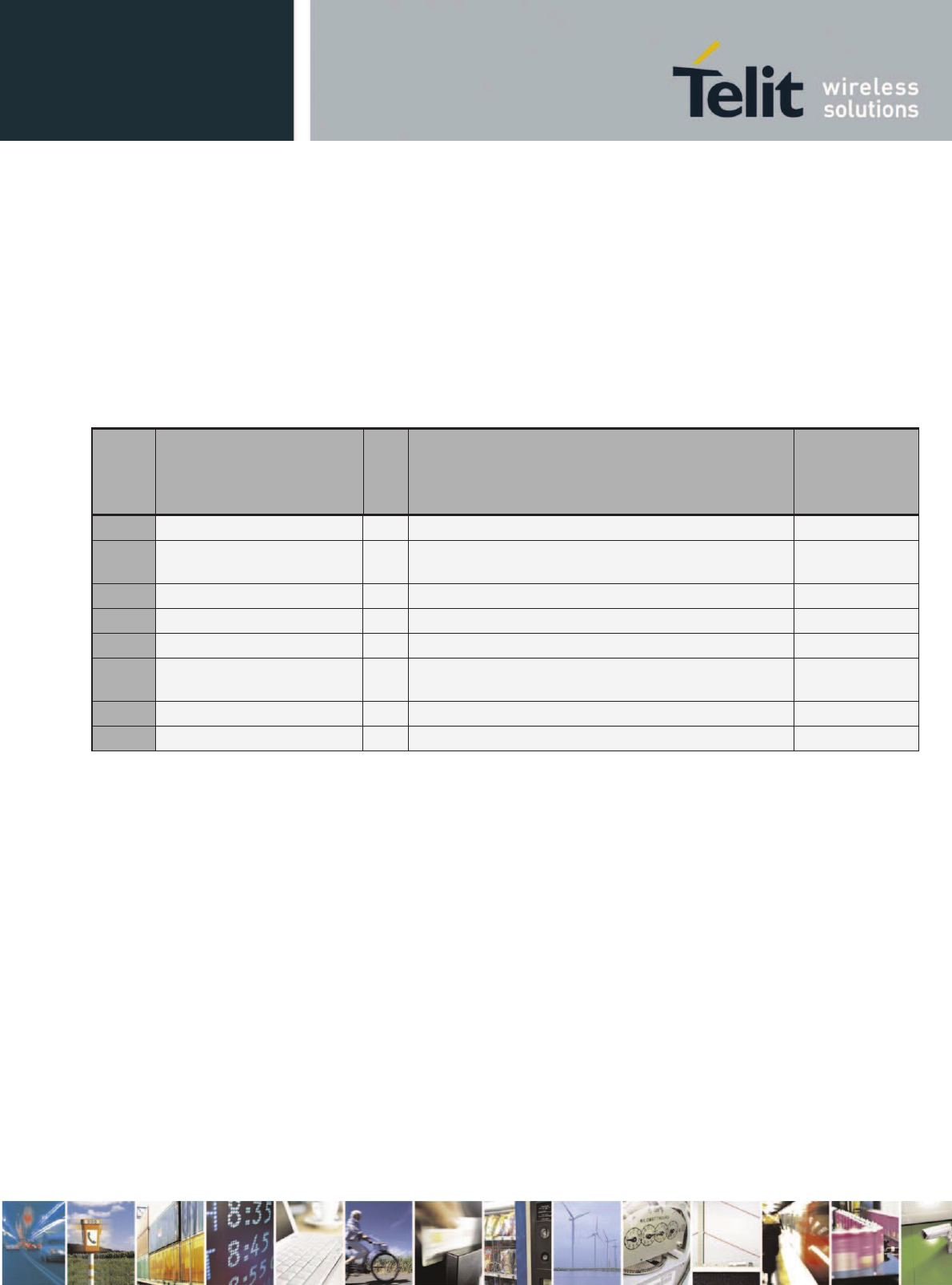

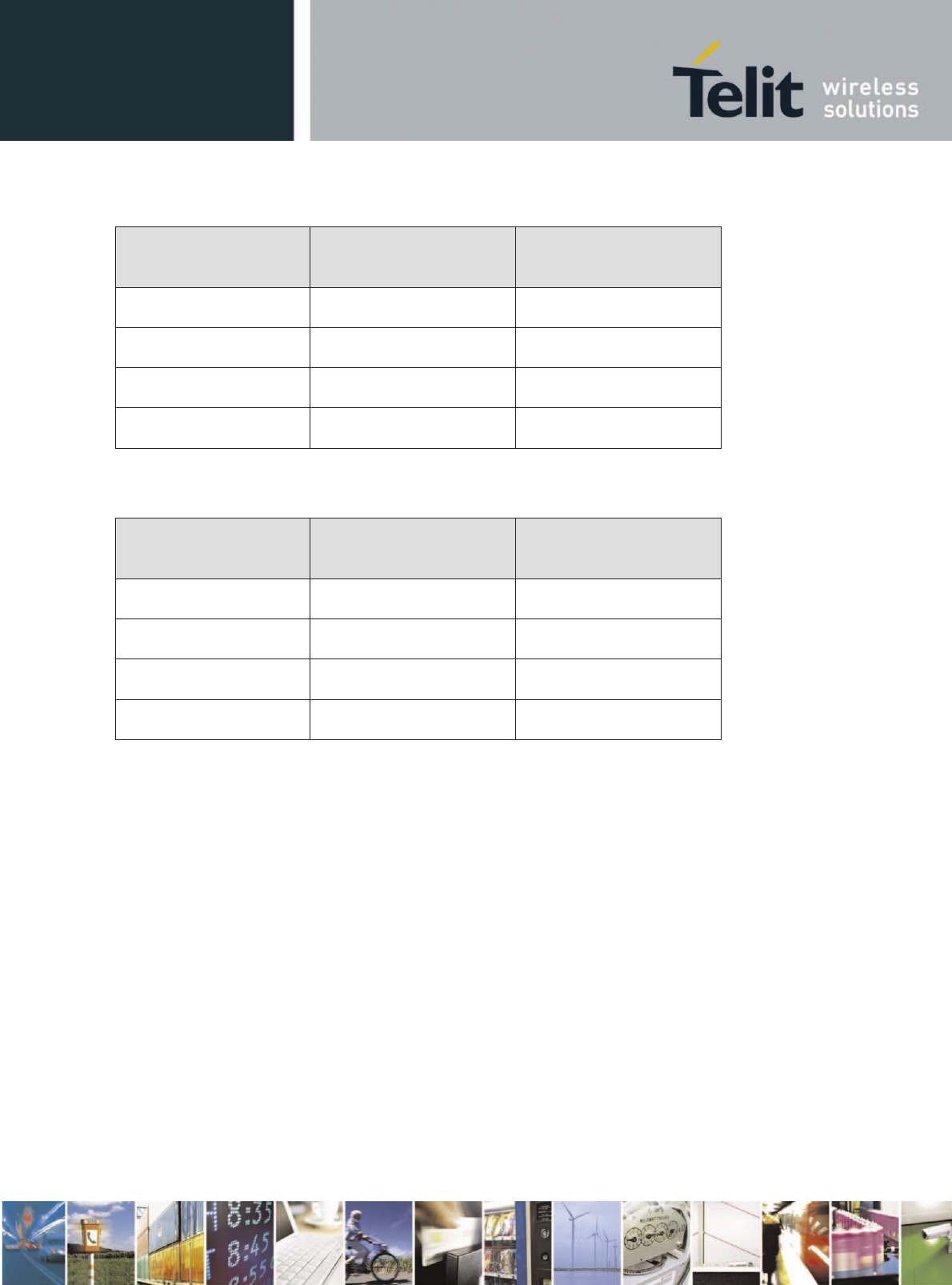

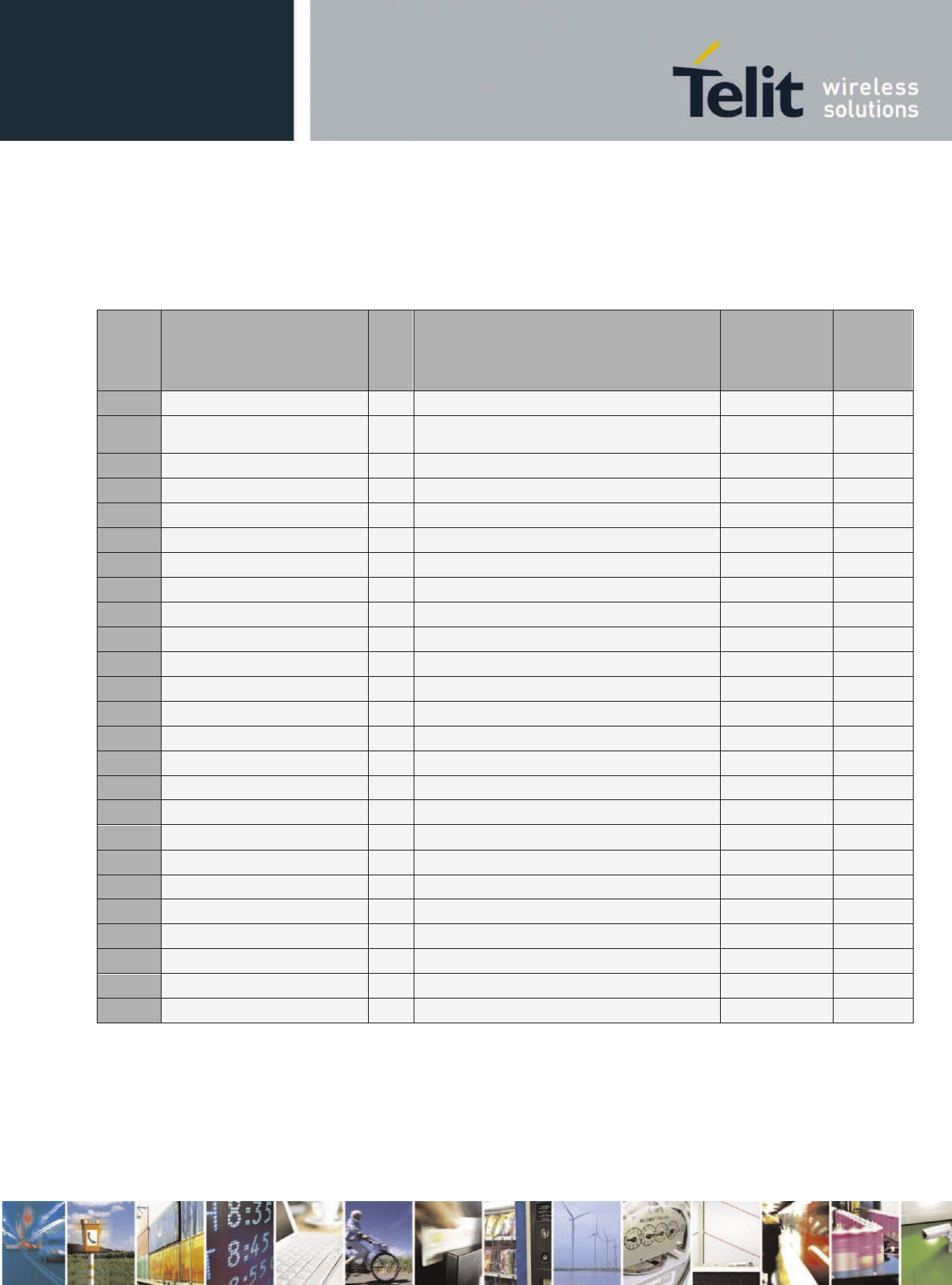

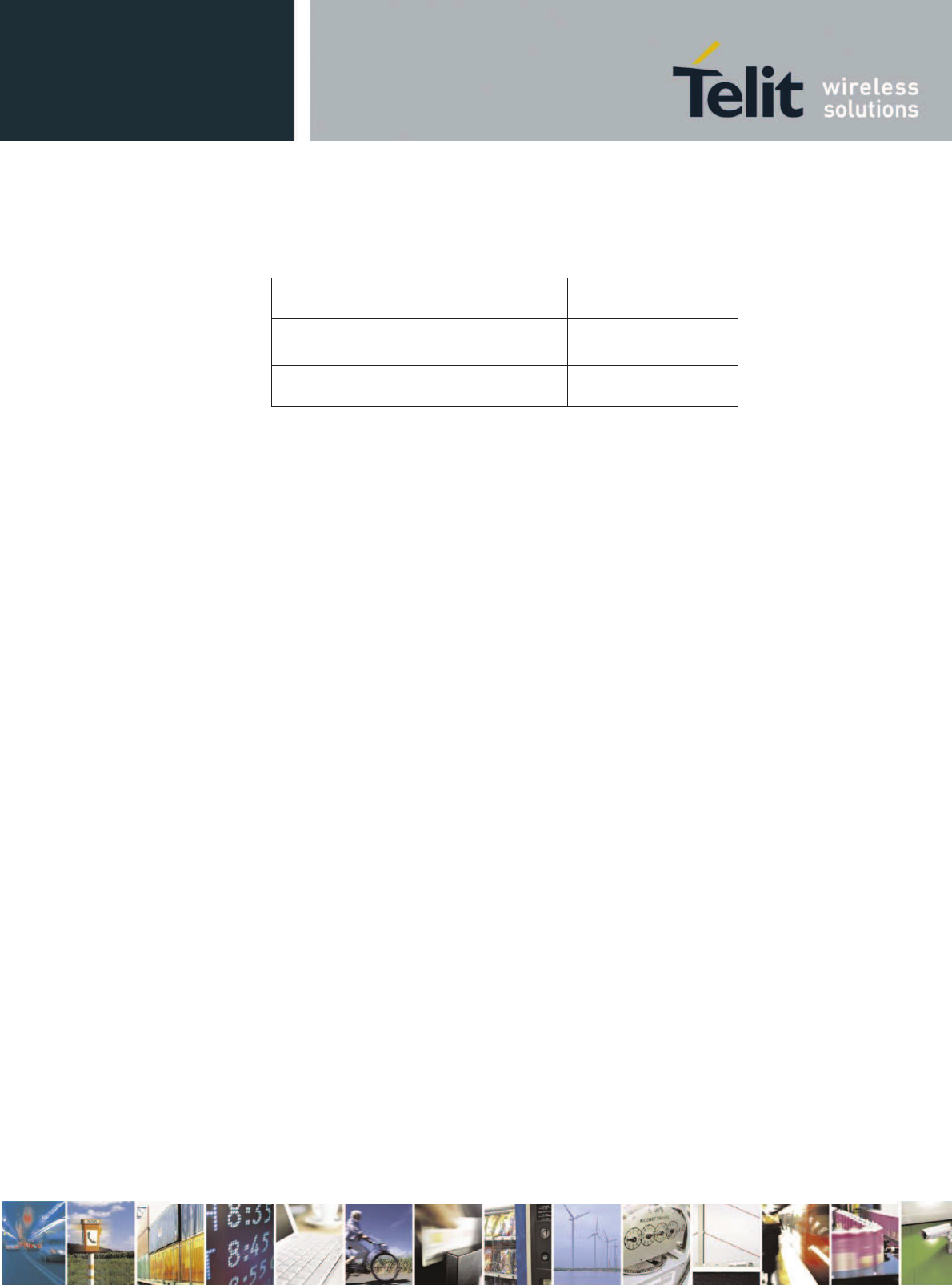

2.3. Reference table of RF bands characteristics

2.3.1. Cellular network:

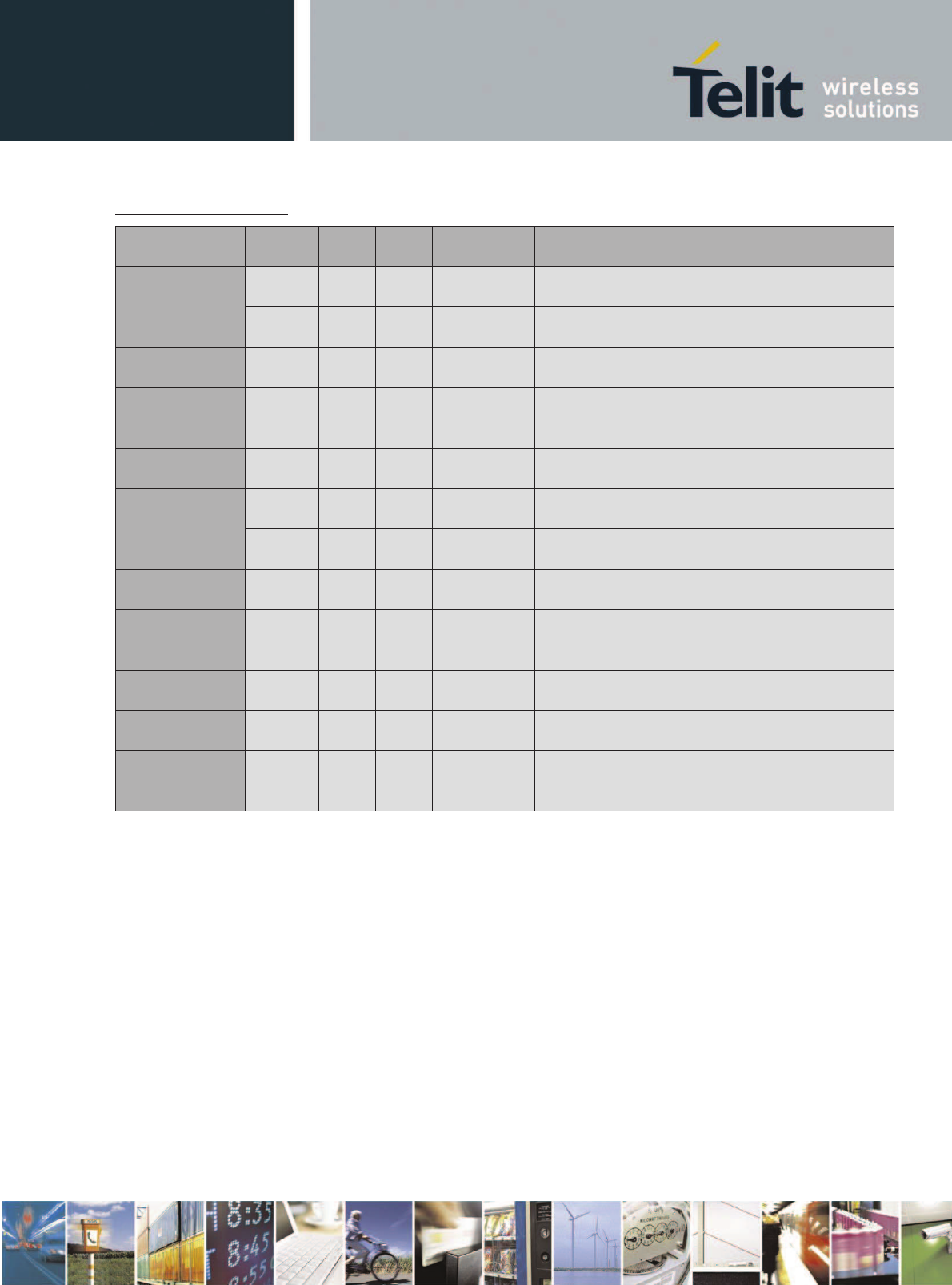

Mode

Freq. TX

(MHz)

Freq. RX (MHz)

Channels

TX

-

RX offset

PCS 1900

1850.2 ~ 1909.8

1930.2 ~ 1989.8

512 ~ 810

80MHz

DCS 1800

1710 ~ 1785

1805 ~ 1880

512 ~ 885

95MHz

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 20 of 112

Mode

Freq. TX

(MHz)

Freq. RX (MHz)

Channels

TX

-

RX offset

GSM 850

824.2 ~ 848.8

869.2 ~ 893.8

128 ~ 251

45MHz

EGSM 900

890 ~ 915

935 ~ 960

0 ~ 124

45 MHz

880 ~ 890

925 ~ 935

975 ~ 1023

45 MHz

WCDMA 2100

–

B1

1920 ~ 1980

2110 ~ 2170

Tx: 9612 ~ 9888

Rx: 10562 ~ 10838

190MHz

WCDMA 1900

–

B2

1850 ~ 1910

1930 ~ 1990

Tx: 9262 ~ 9538

Rx: 9662 ~ 9938

80MHz

WCDMA 850

– B5

824 ~ 849

869

~ 894

Tx: 4132 ~ 4233

Rx: 4357 ~ 4458

45MHz

WCDMA 900

– B8

880 ~ 915

925 ~ 960

Tx: 2712 ~ 2863

Rx: 2937 ~ 3088

45MHz

2.3.2. WiFi/Bluetooth

min typ max unit

Frequency range

2402

-

2482

MHz

2.3.3. GNSS

min

typ

max

unit

GPS

-

1575.5

-

MHz

Glonass

- 1602 - MHz

2.4. Applications

xE922-3GR modules can be used for all kind of IoT Gateways.

Example applications can be:

- Reduction of production overheads

- Smart management of productions

- Remote device monitoring

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 21 of 112

- Data retrieval to prevent terror attacks

-

2.5. Sensitivity

· 3G =< -110 dBm

· 2G CS1 =< -111 dBm

· 2G CS4 =< -103 dBm

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 22 of 112

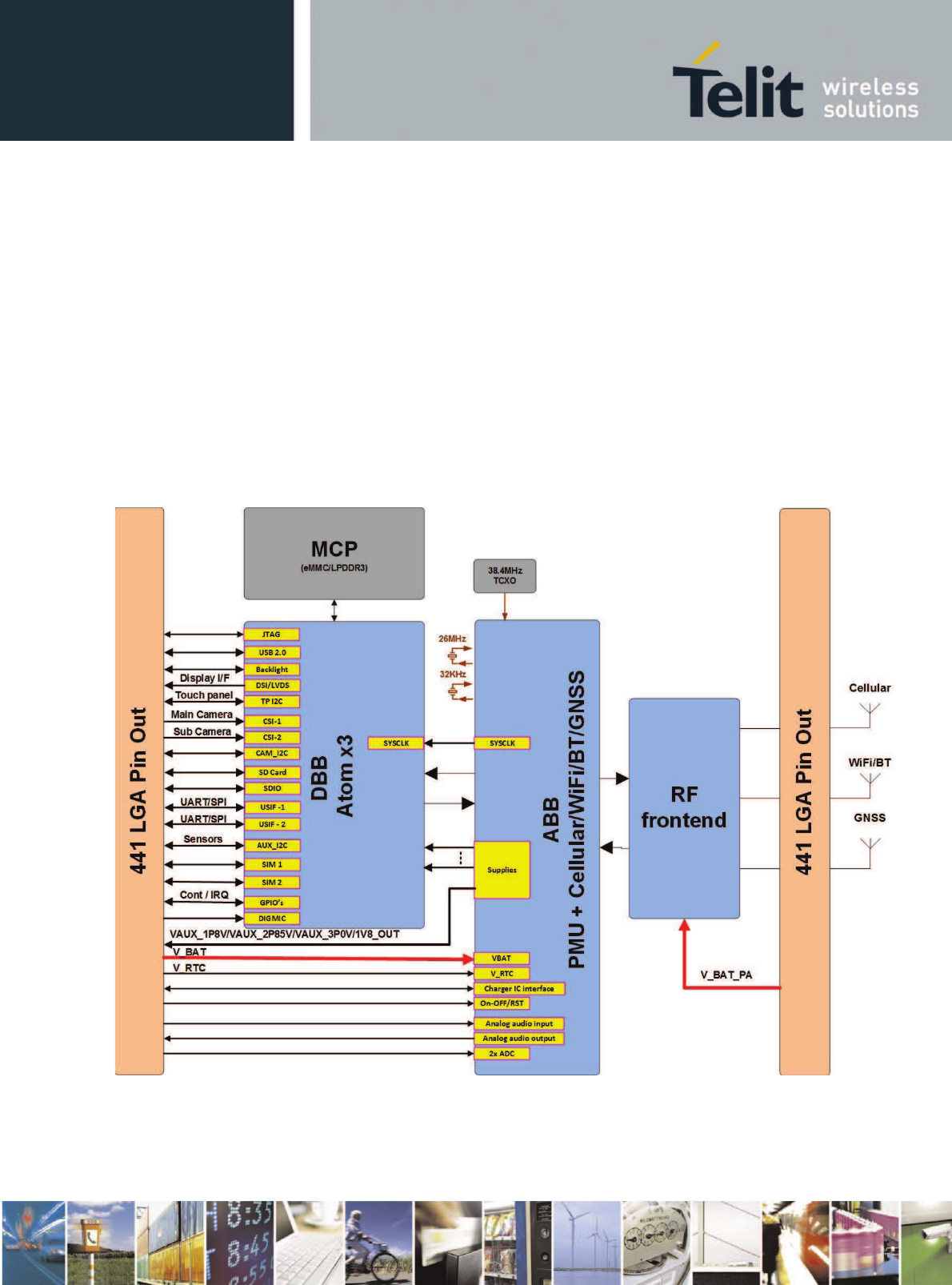

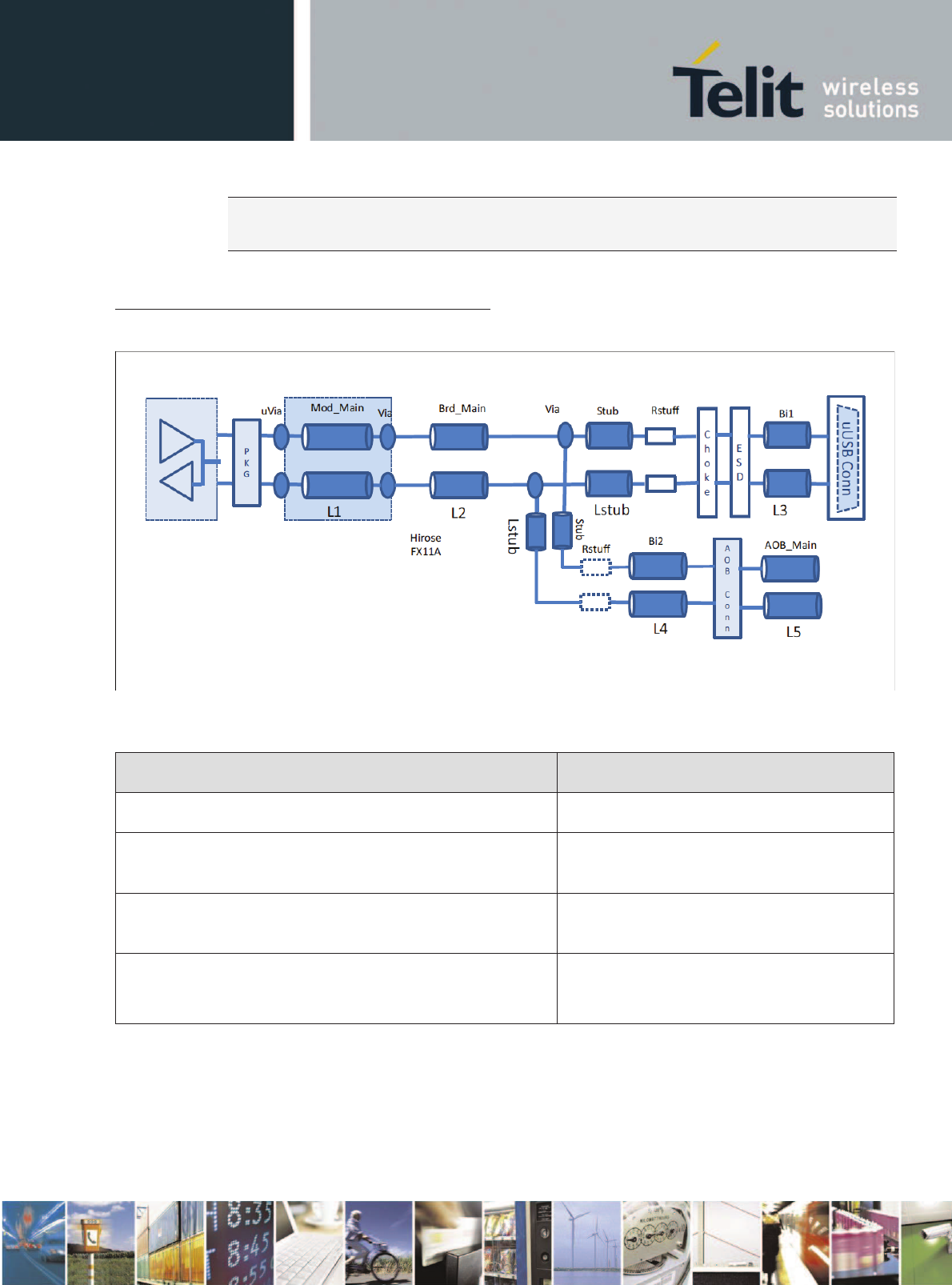

2.6. High level block Diagram

· Digital baseband DBB SoC:

Intel IoTG Atom x3 (quad-core CPU/GPU), multimedia & connectivity, cellular modem accelerators

MCP multi chip package memory subsystem ( eMMC+ LPDDR3)

· Analog baseband ABB :

Intel AG620 (WiFi-BT/cellular 2G/3G quad-band transceivers, GNSS receiver,power managemant

unit PMU, audio frontend AFE)

· RF front end SAW filters / power amplifiers

Figure 1

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 23 of 112

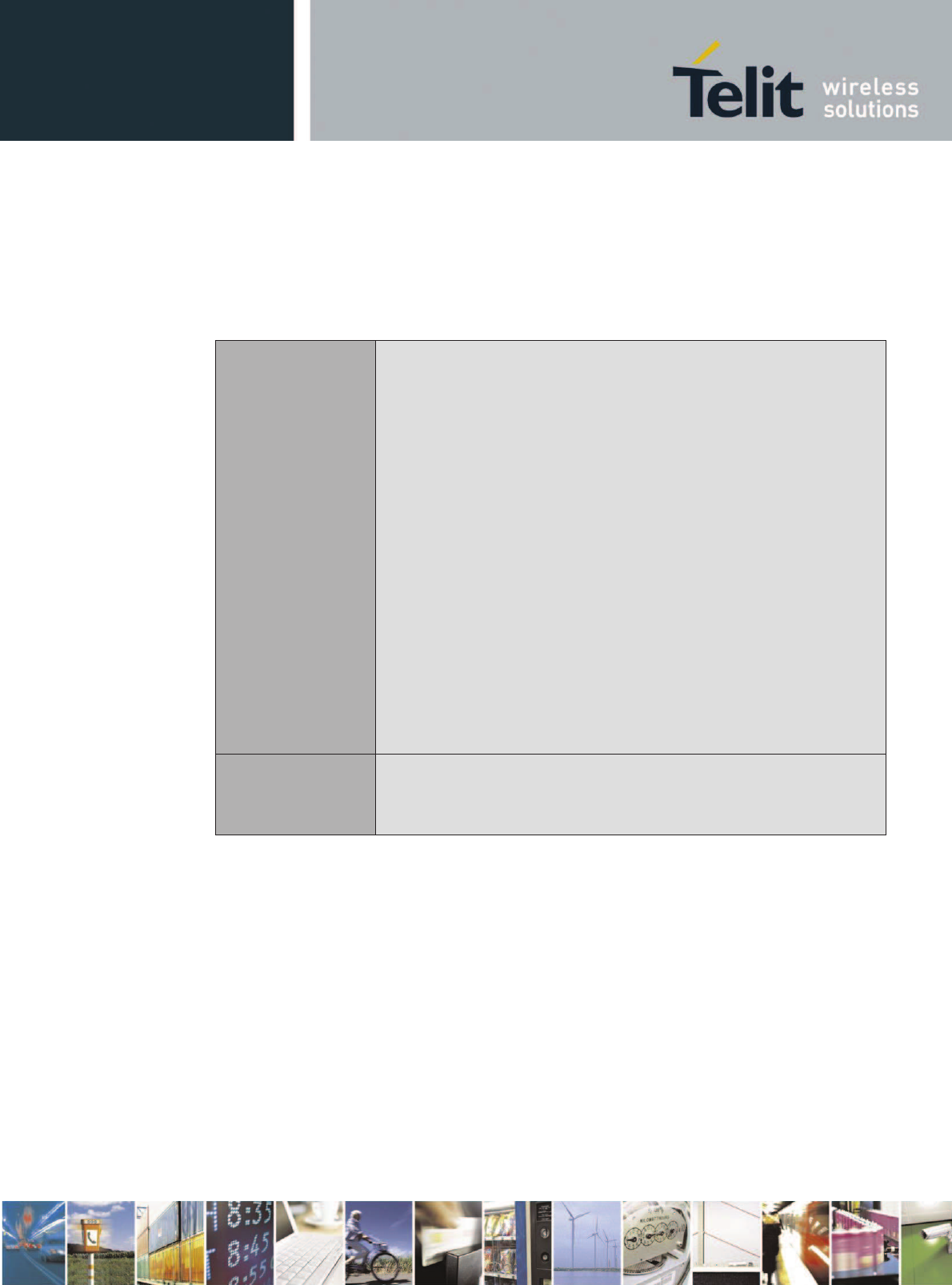

2.7. Environmental requirements

2.7.1. Temperature range

Operating

Temperature Range

-20 ~ +55

°C :

This range is defined by 3GPP (the global standard for

wireless mobile communication). Telit guarantees its modules to

comply with all the 3GPP requirements and to have full functionality

of the

module with in this range.

extended temperature

-40 ~ +85°C

& commercial temperature 0~+70°C

:

Telit guarantees full functionality within this range as well. However,

there may possibly be some performance deviations in this extended

range relative to

3GPP requirements,

which means: some RF

parameters may deviate from 3GPP specification in the order of few

dB. For example: receiver sensitivity or maximum output power may

be slightly degraded.

Even so, all the functionalities like

data connection, SMS

, USB

communication, UART activation etc. will be maintained, and the

effect of such degradations will not lead to malfunction.

Storage and non-

operating

Temperature Range

–40°C

~ +105°C

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 24 of 112

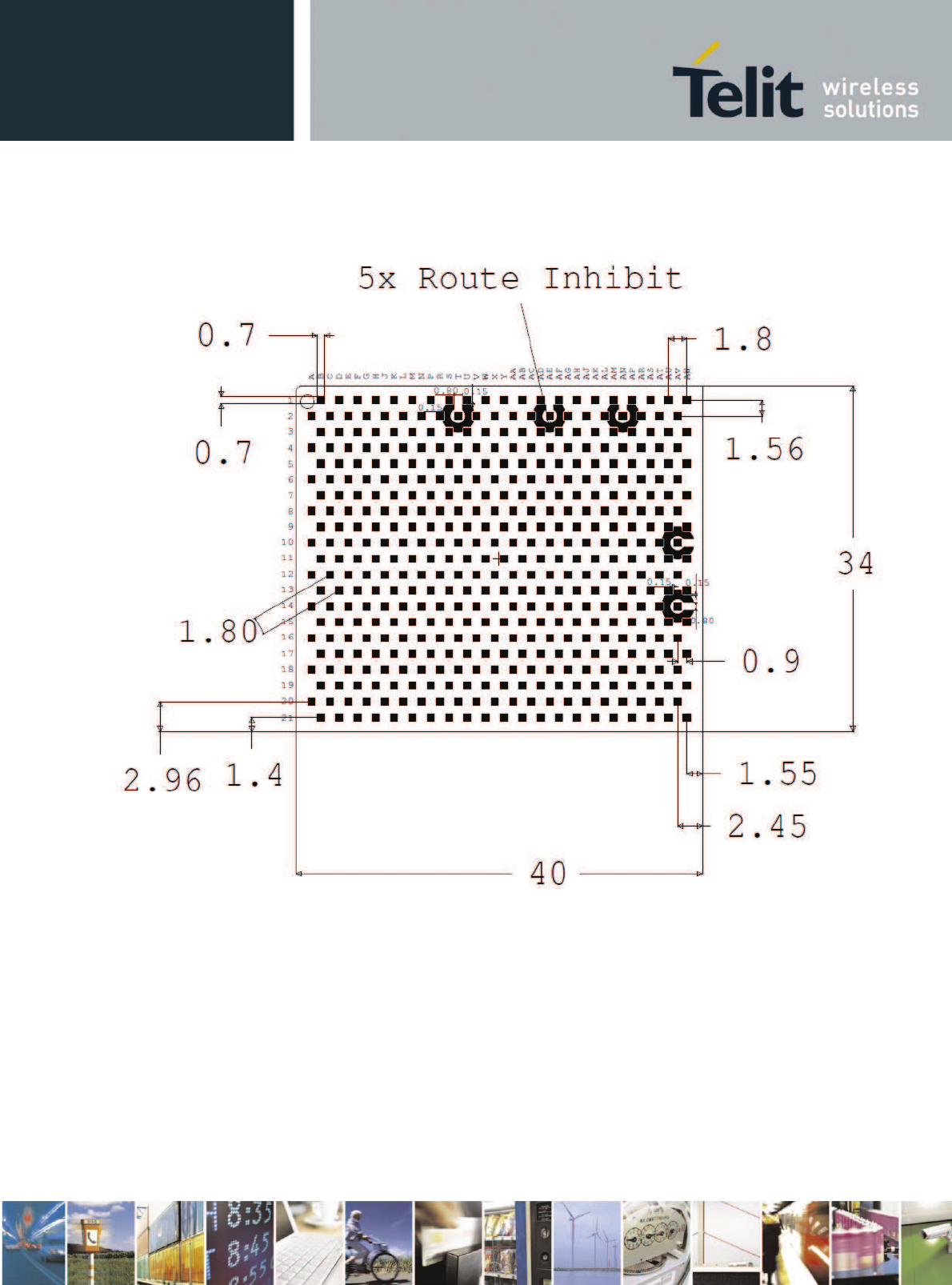

2.8. xE922-3GR Mechanical Specifications

2.8.1. Dimensions

The Telit xE922-3GR module overall dimensions are:

• Length: 34 mm, +/- 0.15 mm Tolerance

• Width: 40 mm, +/- 0.15 mm Tolerance

• Thickness: 3.0 mm, +/- 0.15 mm Tolerance

2.8.2. Weight

The nominal weight of the xE922-3GR module is 9.7 gram.

2.8.3. RoHS compliance

As a part of Telit corporate policy of environmental protection, the xE922-3GR complies with

the RoHS (Restriction of Hazardous Substances) directive of the European Union (EU directive

2011/65/EU).

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 25 of 112

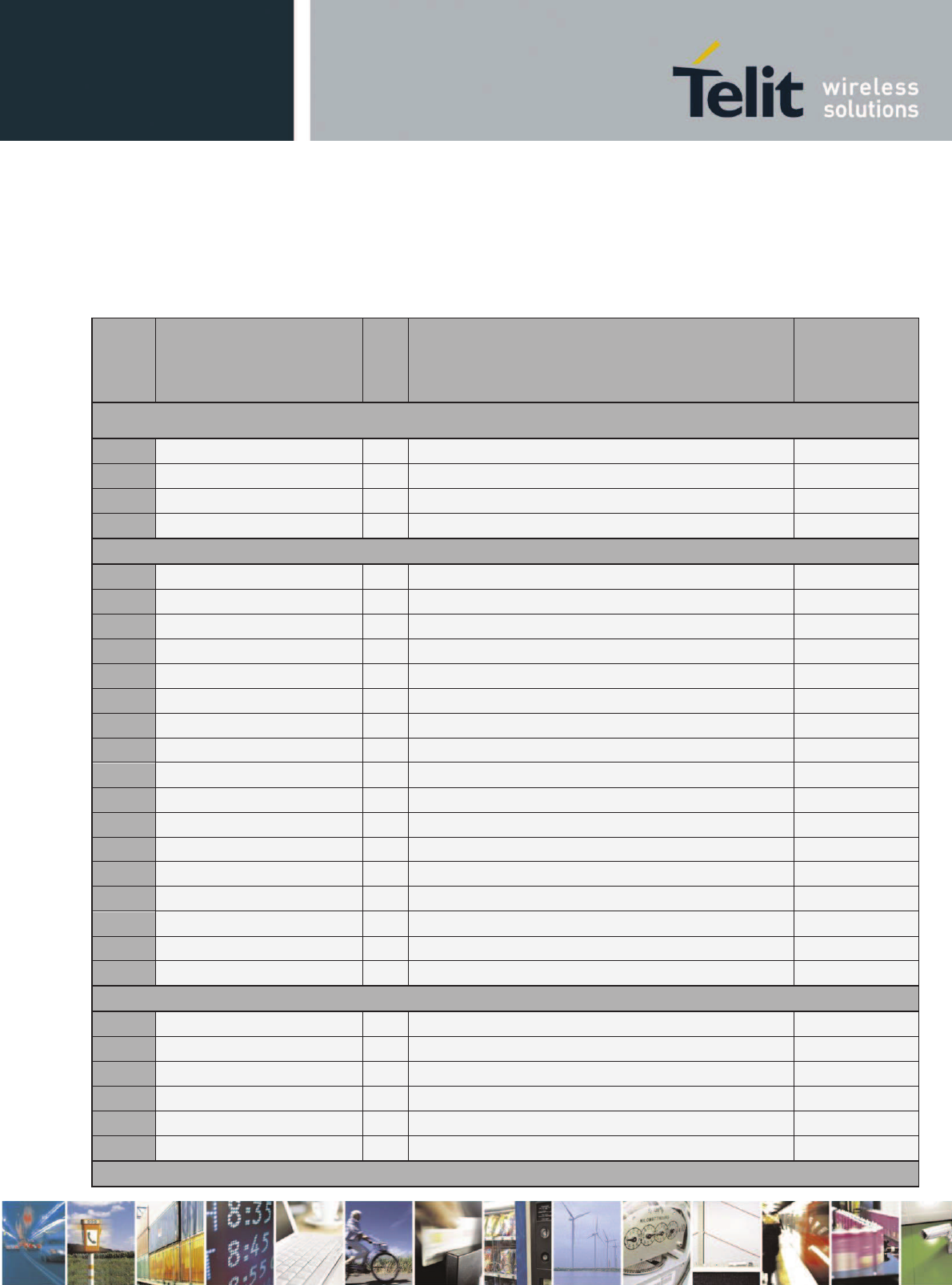

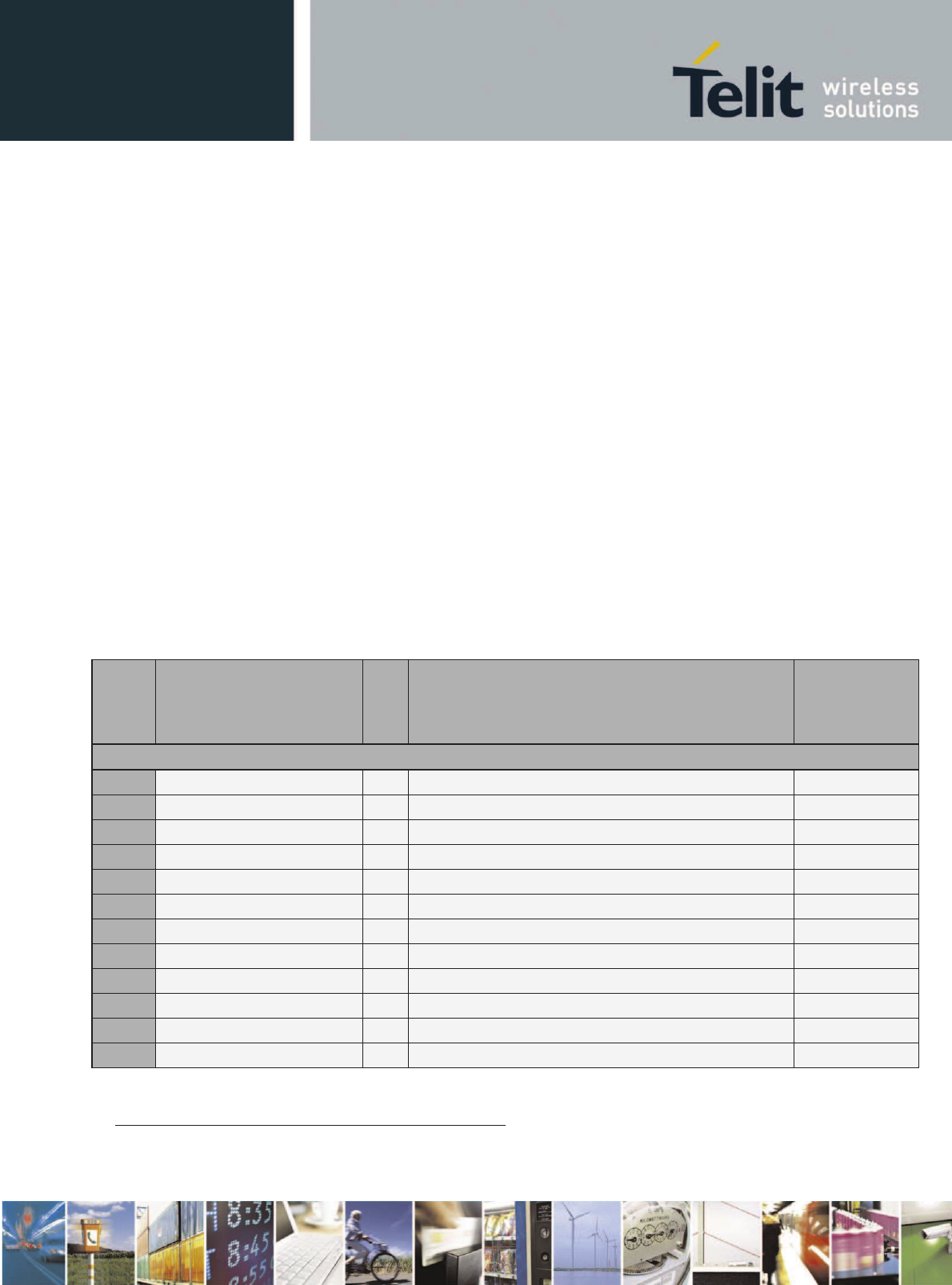

3. xE922-3GR Module pin out

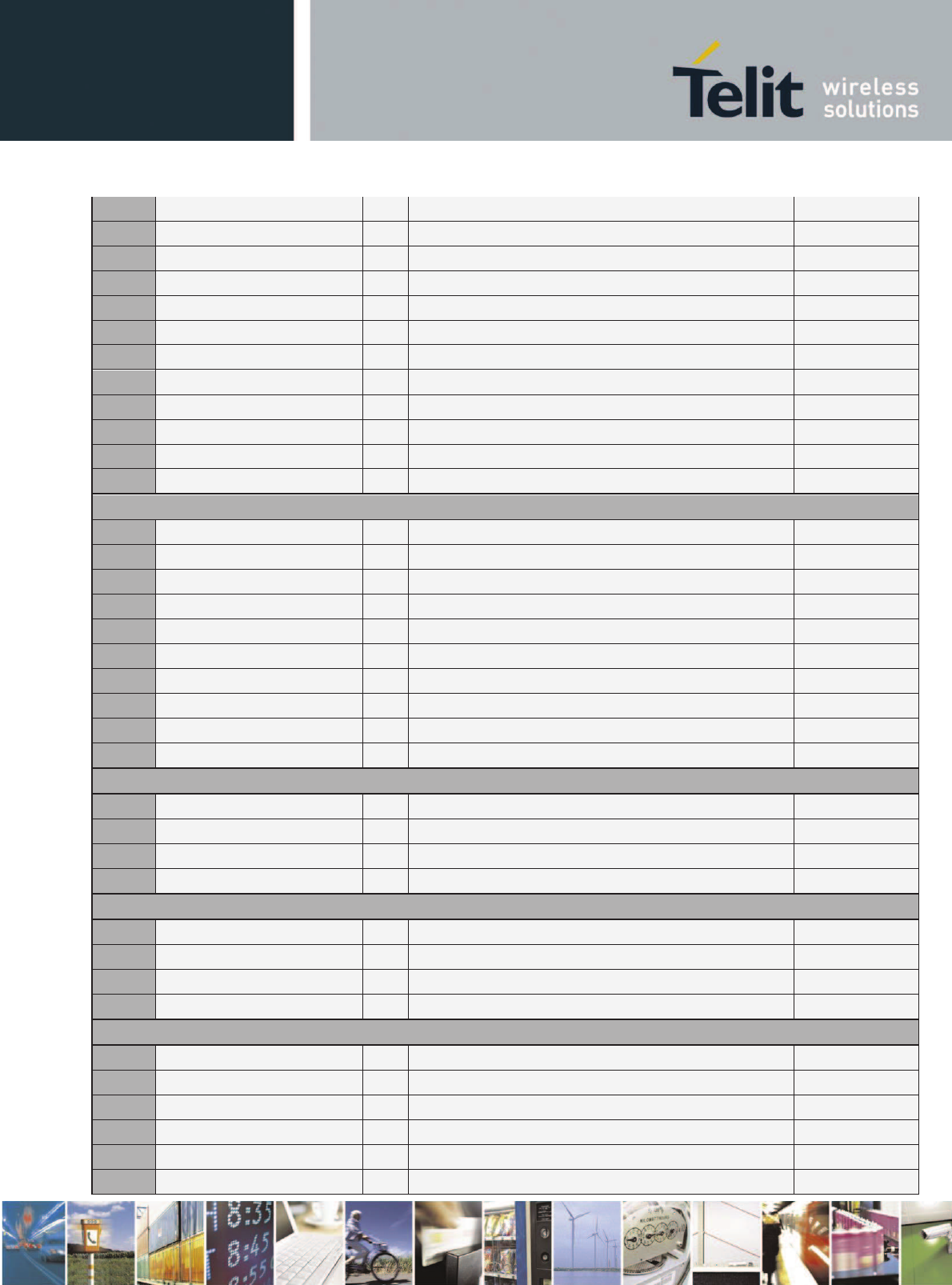

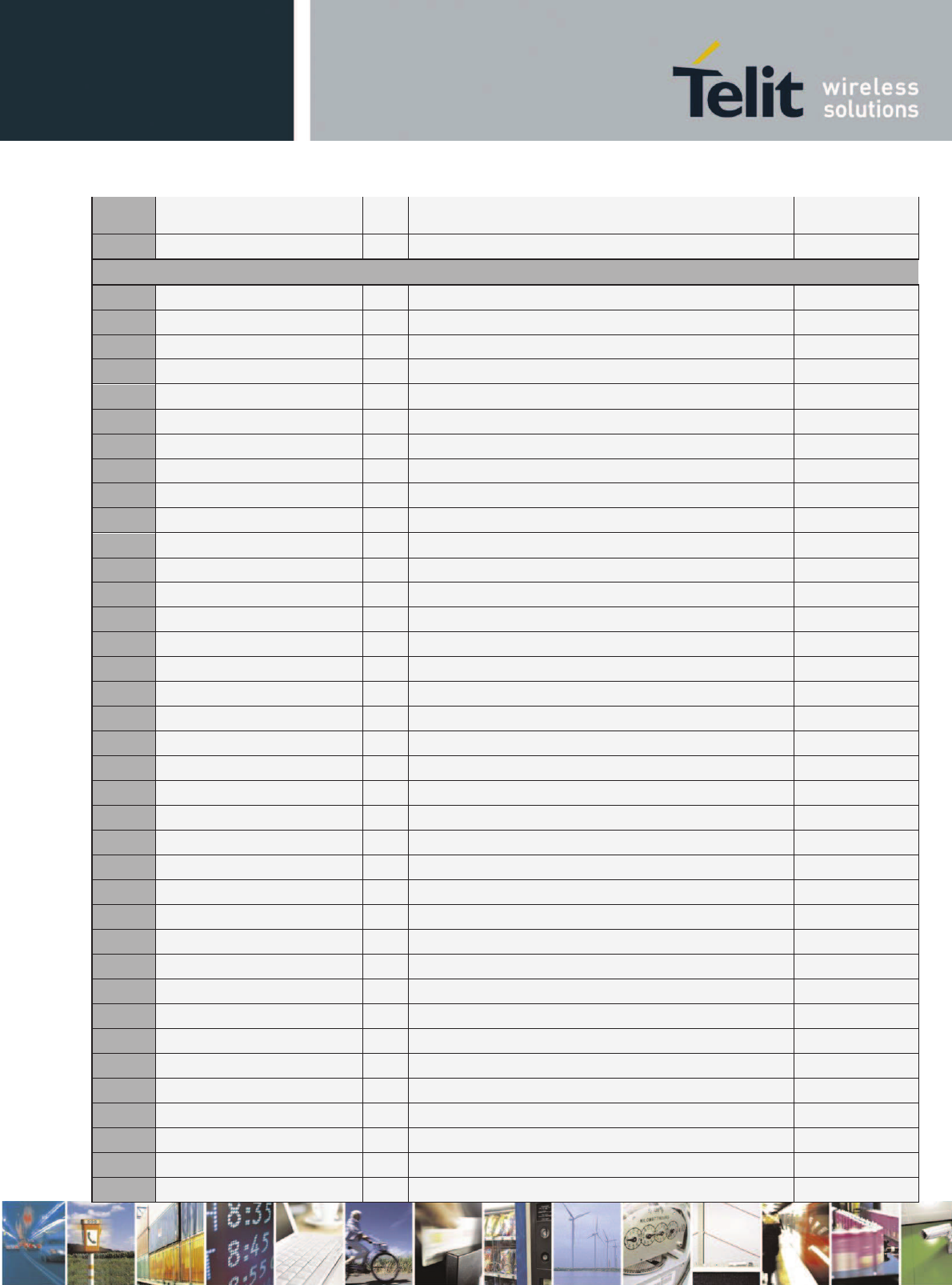

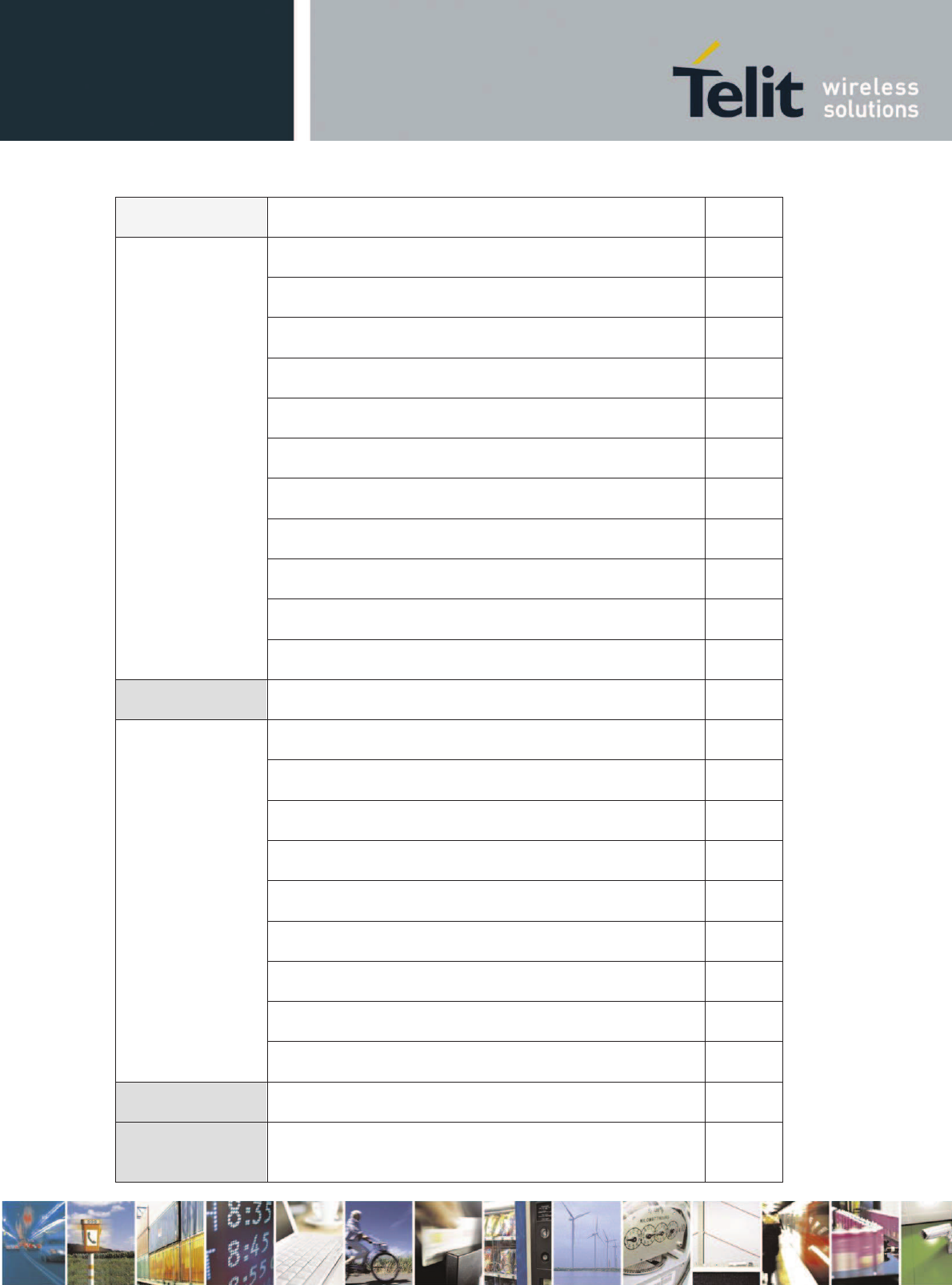

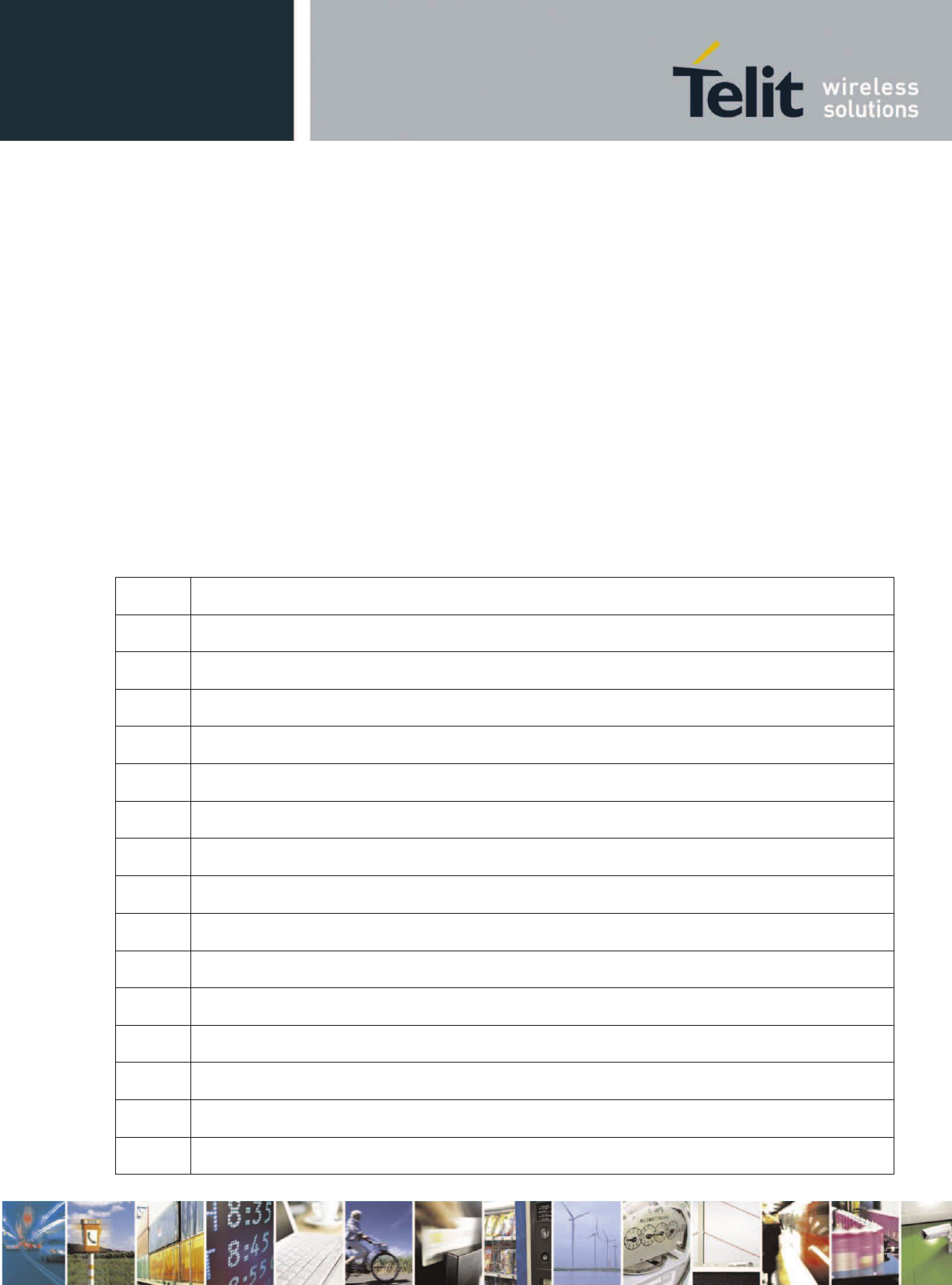

3.1. PIN table

PAD

Signal

I/O

descriptions Type

USB 2.0 Interface

W17

USB_ID

AI

USB_ID, USB DRD use

Analog

S17

USB_DP

I/O

USB differential Data (+)

Analog

U17

USB_DN

I/O

USB differential Data (-)

Analog

AR8

VBUS_DET

I

VBUS detection

Analog

Main Camera

D21

CSI1_DP0

AI

Main Camera CSI Data0 Input Positive

Analog

F21

CSI1_DN0

AI

Main Camera CSI Data0 Input Negative

Analog

M19

CSI1_DP1

AI

Main Camera CSI Data1 Input Positive

Analog

K19

CSI1_DN1

AI

Main Camera CSI Data1 Input Negative

Analog

F19

CSI1_DP2

AI

Main Camera CSI Data2 Input Positive

Analog

H19

CSI1_DN2

AI

Main Camera CSI Data2 Input Negative

Analog

E18

CSI1_DP3

AI

Main Camera CSI Data3 Input Positive

Analog

G18

CSI1_DN3

AI

Main Camera CSI Data3 Input Negative

Analog

C20

CSI1_CLKP

AI

Main Camera CSI Clock Positive

Analog

E20

CSI1_CLKN

AI

Main Camera CSI Clock Negative

Analog

P17

CAM_MCLK

O

Camera MCLK output

CMOS 1.8V

AM17

CAM_I2C_SDA

I/O

Camera I2C Data

CMOS 1.8V

AP17

CAM_I2C_SCL

I/O

Camera I2C Clock

CMOS 1.8V

A4

CAM1_PD

I/O

Main Camera Power Down / GPIO

CMOS 1.8V

G4

CAM1_RESET

I/O

Main Camera Reset / GPIO

CMOS 1.8V

B7

CAM1_FLASH

I/O

Main Camera Flash Triger

CMOS 1.8V

G6

CAM1_TORCH

I/O

Main Camera Torch Enable

CMOS 1.8V

Secondary Camera

A18

CSI2_DP

AI

Sub Camera CSI Data Input Positive

Analog

C18

CSI2_DN

AI

Sub Camera CSI Data Input Negative

Analog

B19

CSI2_CLKP

AI

Sub Camera CSI Clock Positive

Analog

D19

CSI2_CLKN

AI

Sub Camera CSI Clock Negative

Analog

H3

CAM2_PD

I/O

Sub Camera Power Down / GPIO

CMOS 1.8V

E4

CAM2_RESET

I/O

Sub Camera Reset / GPIO

CMOS 1.8V

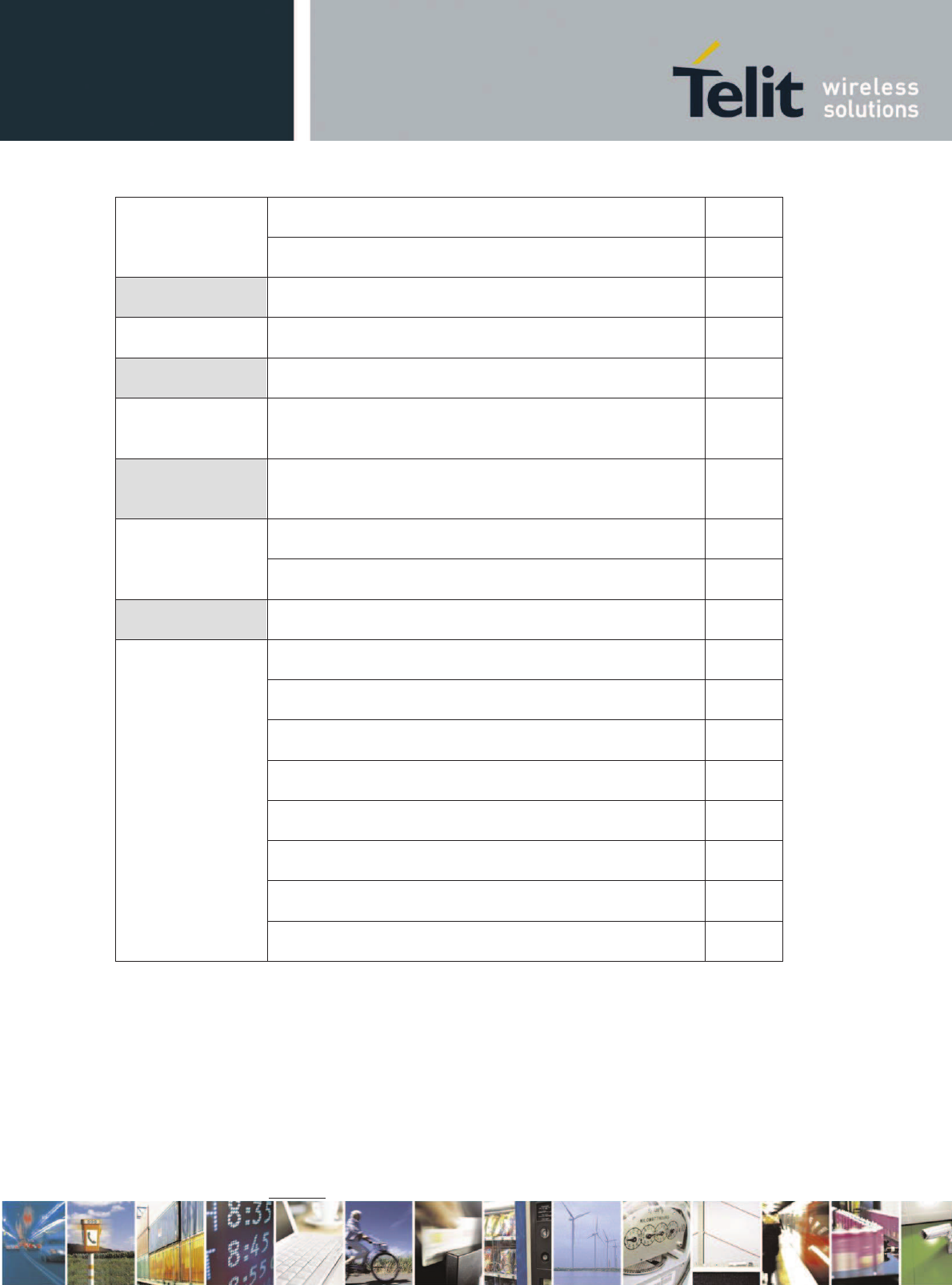

MIPI DSI Display Interface

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 26 of 112

S19

DSI_DP0

AO

LCD DSI Data_0 Positive

Analog

P19

DSI_DN0

AO

LCD DSI Data_0 Negative

Analog

R20

DSI_DP1

AO

LCD DSI Data_1 Positive

Analog

N20

DSI_DN1

AO

LCD DSI Data_1 Negative

Analog

L20

DSI_DP2

AO

LCD DSI Data_2 Positive

Analog

J20

DSI_DN2

AO

LCD DSI Data_2 Negative

Analog

K21

DSI_DP3

AO

LCD DSI Data_3 Positive

Analog

H21

DSI_DN3

AO

LCD DSI Data_3 Negative

Analog

M21

DSI_CLKP

AO

LCD DSI Clock Positive

Analog

P21

DSI_CLKN

AO

LCD DSI Clock Negative

Analog

AP11

LCD_RESET

I/O

LCD Reset / GPIO

CMOS 1.8V

AP9

LCD_TE

I/O

LCD Tearing effect input

CMOS 1.8V

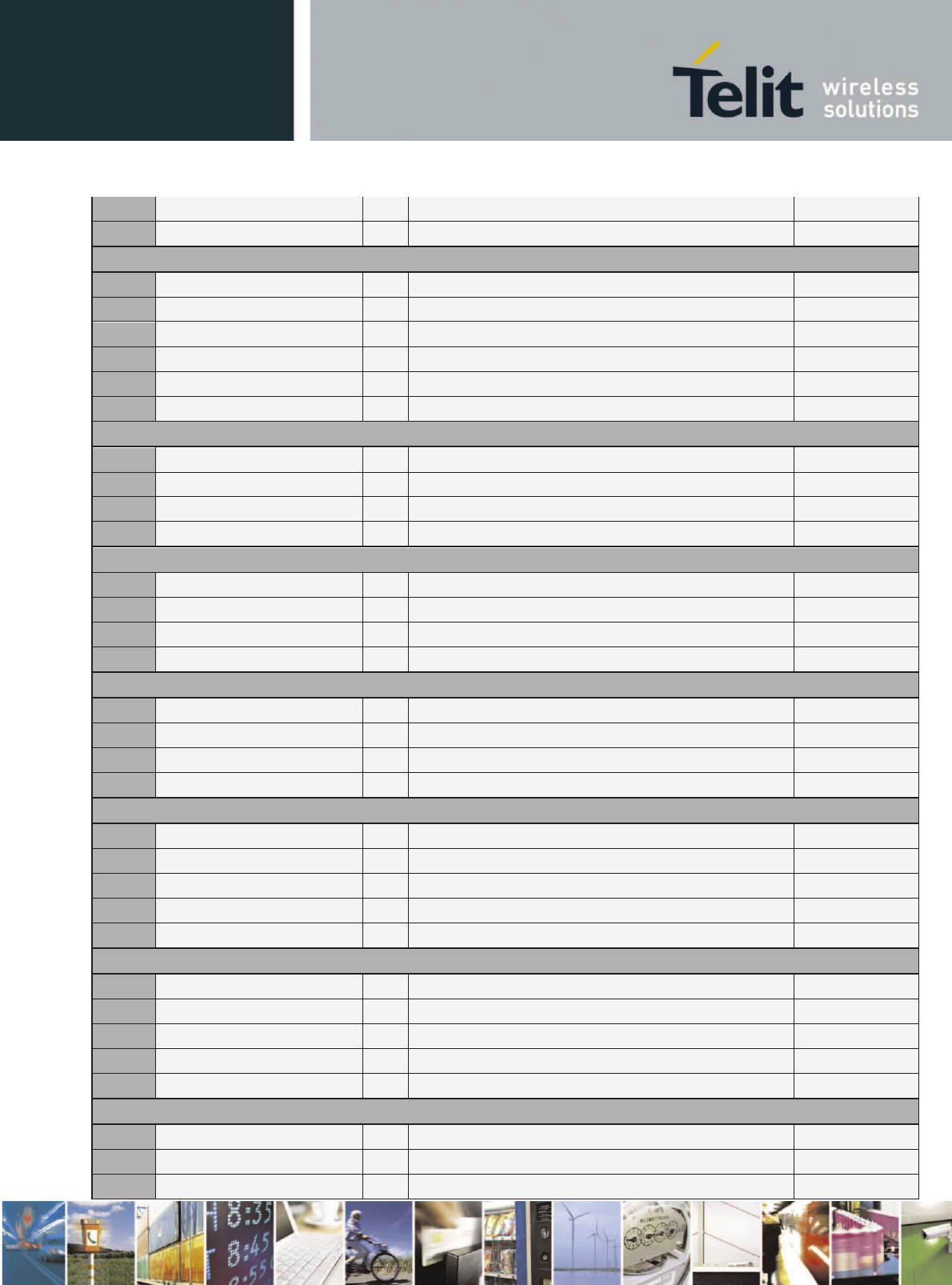

LVDS Display Interface

W19

LVDS_TA1P

AO

LVDS Data A Positive

Analog

U19

LVDS_TA1N

AO

LVDS Data A Negative

Analog

X18

LVDS_TB1P

AO

LVDS Data B Positive

Analog

V18

LVDS_TB1N

AO

LVDS Data B Negative

Analog

V20

LVDS_TC1P

AO

LVDS Data C Positive

Analog

T20

LVDS_TC1N

AO

LVDS Data C Negative

Analog

Y21

LVDS_TD1P

AO

LVDS Data D Positive

Analog

W21

LVDS_TD1N

AO

LVDS Data D Negative

Analog

U21

LVDS_TCLK1P

AO

LVDS Clock Positive

Analog

S21

LVDS_TCLK1N

AO

LVDS Clock Negative

Analog

LCD Backlight

AS15

CABC

AI

Content Adaptive Backlight Control

Analog

AS17

LEDFB_DP

AI

Backlight feedback Positive

Analog

AU17

LEDFB_DN

AI

Backlight feedback Negative

Analog

AP13

LEDDRV

AO

Backlight Drive

Analog

Touch Screen interface

AD17

TP_SDA

I/O

Touch panel I2C Data

CMOS 1.8V

AB17

TP_SCL

I/O

Touch panel I2C Clock

CMOS 1.8V

F7

TP_RESET

I/O

Touch panel Reset

CMOS 1.8V

F11

TP_IRQ

I/O

Touch panel Interrupt

CMOS 1.8V

SD/MMC Card Interface

AP15

VDD_SD

-

Power supply out for MMC card 1.8/3V

PWR out

J2

SD_CARD_DET

I

MMC card detect(active low)

CMOS_1.8V

F1

SD_DAT0

I/O

MMC card data 0

CMOS_1.8/3V

H1

SD_DAT1

I/O

MMC card data 1

CMOS_1.8/3V

K1

SD_DAT2

I/O

MMC card data 2

CMOS_1.8/3V

M1

SD_DAT3

O

MMC card data3

CMOS_1.8/3V

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 27 of 112

E2

SD_CLK

O

MMC card clock

CMOS_1.8/3V

G2

SD_CMD

I/O

MMC card command

CMOS_1.8/3V

SDIO Interface

L4

SDIO_CLK

I/O

CLK

CMOS 1.8V

P3

SDIO_CMD

I/O

CMD

CMOS 1.8V

P1

SDIO_DAT0

I/O

SD0

CMOS 1.8V

N2

SDIO_DAT1

I/O

SD1

CMOS 1.8V

M3

SDIO_DAT2

I/O

SD2

CMOS 1.8V

N4

SDIO_DAT3

I/O

SD3

CMOS 1.8V

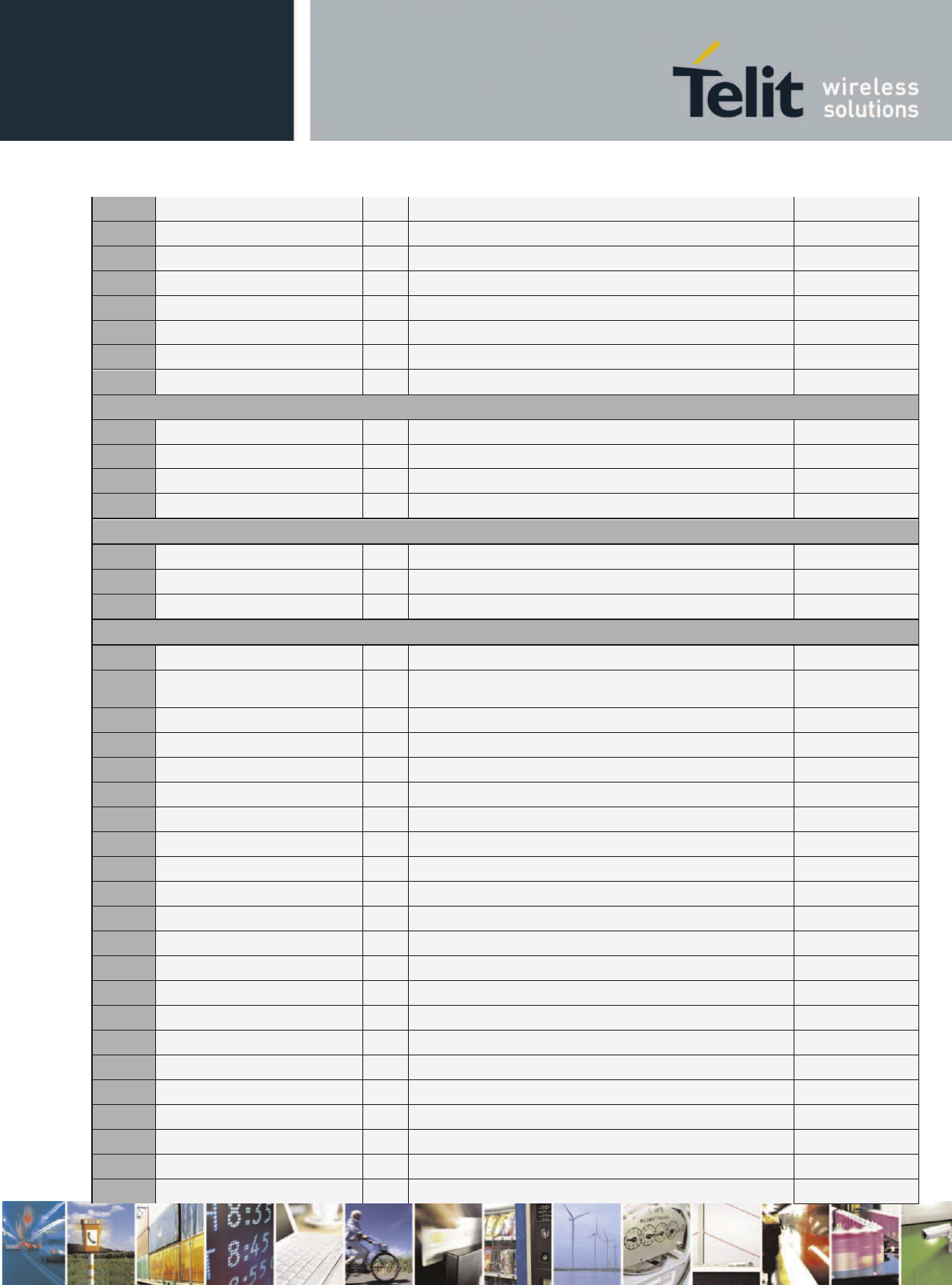

USIF 1 (UART/SPI)

W5

USIF1_RXD

I

UART1 / SPI1 Serial data input

CMOS 1.8V

Y5

USIF1_TXD

O

UART1 / SPI1 Serial data Output

CMOS 1.8V

S5

USIF1_SCLK

I/O

UART1 CTS / SPI1 SCLK

CMOS 1.8V

U5

USIF1_CS

O

UART1 RTS / SPI1 Chip Select

CMOS 1.8V

USIF 2 (UART/SPI)

AH3

USIF2_RXD

I

UART2 / SPI2 Serial data input

CMOS 1.8V

AE4

USIF2_TXD

O

UART2 / SPI2 Serial data Output

CMOS 1.8V

AD5

USIF2_SCLK

I/O

UART2 CTS / SPI2 SCLK

CMOS 1.8V

AJ2

USIF2_CS

O

UART2 RTS / SPI2 Chip Select

CMOS 1.8V

I2C Ports

AS1

AUX_I2C_SDA

I/O

I2C3 Data (AUX / Sensors)

CMOS 1.8V

AT2

AUX_I2C_SCL

I/O

I2C3 Clock (AUX / Sensors)

CMOS 1.8V

AC18

CHG_I2C_SCL

I/O

Charger I2C Clock

CMOS 1.8V

AE18

CHG_I2C_SDA

I/O

Charger I2C Data

CMOS 1.8V

SIM card interface 1

AM5

VSIM1

-

External SIM signal 1 – Power supply for the SIM

1.8 / 2.85V

AR6

SIMCLK1

O

External SIM signal 1 – Clock

1.8 / 2.85V

AN10

USIM1_DETECT

I

External SIM signal 1 – Card detect (Active low)

CMOS 1.8V

AT6

SIMIO1

I/O

External SIM signal 1 – Data I/O

1.8 / 2.85V

AN6

SIMRST1

O

External SIM signal 1 – Reset

1.8 / 2.85V

SIM card interface 2

AK3

VSIM2

-

External SIM signal 2 – Power supply for the SIM

1.8 / 2.85V

AS7

SIMCLK2

O

External SIM signal 2 – Clock

1.8 / 2.85V

AR10

USIM2_DETECT

I

External SIM signal 2 – Card detect (Active low)

CMOS 1.8V

AU7

SIMIO2

I/O

External SIM signal 2 – Data I/O

1.8 / 2.85V

AP7

SIMRST2

O

External SIM signal 2 – Reset

1.8 / 2.85V

Analog Audio

AK21

EP_P

AO

Differential Earpiece Positive

Analog

AM21

EP_N

AO

Differential Earpiece Negative

Analog

AG20

MICP1

AI

Earpiece microphone 1 signal input; phase+

Analog

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 28 of 112

AE20

MICN1

AI

Earpiece microphone 1 signal input; phase-

Analog

AF19

MICP2

AI

Headset microphone 2 signal input; phase+

Analog

AH19

MICN2

AI

Headset microphone 2 signal input; phase-

Analog

AJ18

VMIC_BIAS

AO

Analog Microphone bias

PWR out

AJ20

HP_OUT_R

AO

Headset Right Signal Out

Analog

AL20

HP_OUT_L

AO

Headset Left Signal Out

Analog

AH21

SPKR_LP

AO

Speaker Signal Out Positive

Analog

AF21

SPKR_LN

AO

Speaker Signal Out Negative

Analog

Digital microphone

AV12

DIG_MIC_CLK

DI

Digital microphone Clock Output

CMOS 1.8V

AN12

DIG_MIC_D1

DI

Digital microphone 1 signal input;

CMOS 1.8V

AT12

DIG_MIC_D2

DI

Digital microphone 2 Clock input;

CMOS 1.8V

AG18

MIC_VDD

AO

MEMS/DIG Microphone Power Supply

PWR out

RF Antenna

AE2

ANT_MAIN

A

Main Cellular RF antenna

RF

T2

ANT_GPS

A

GPS Antenna

RF

AV14

ANT_WIFI_BT

A

WiFi /BT Antenna

RF

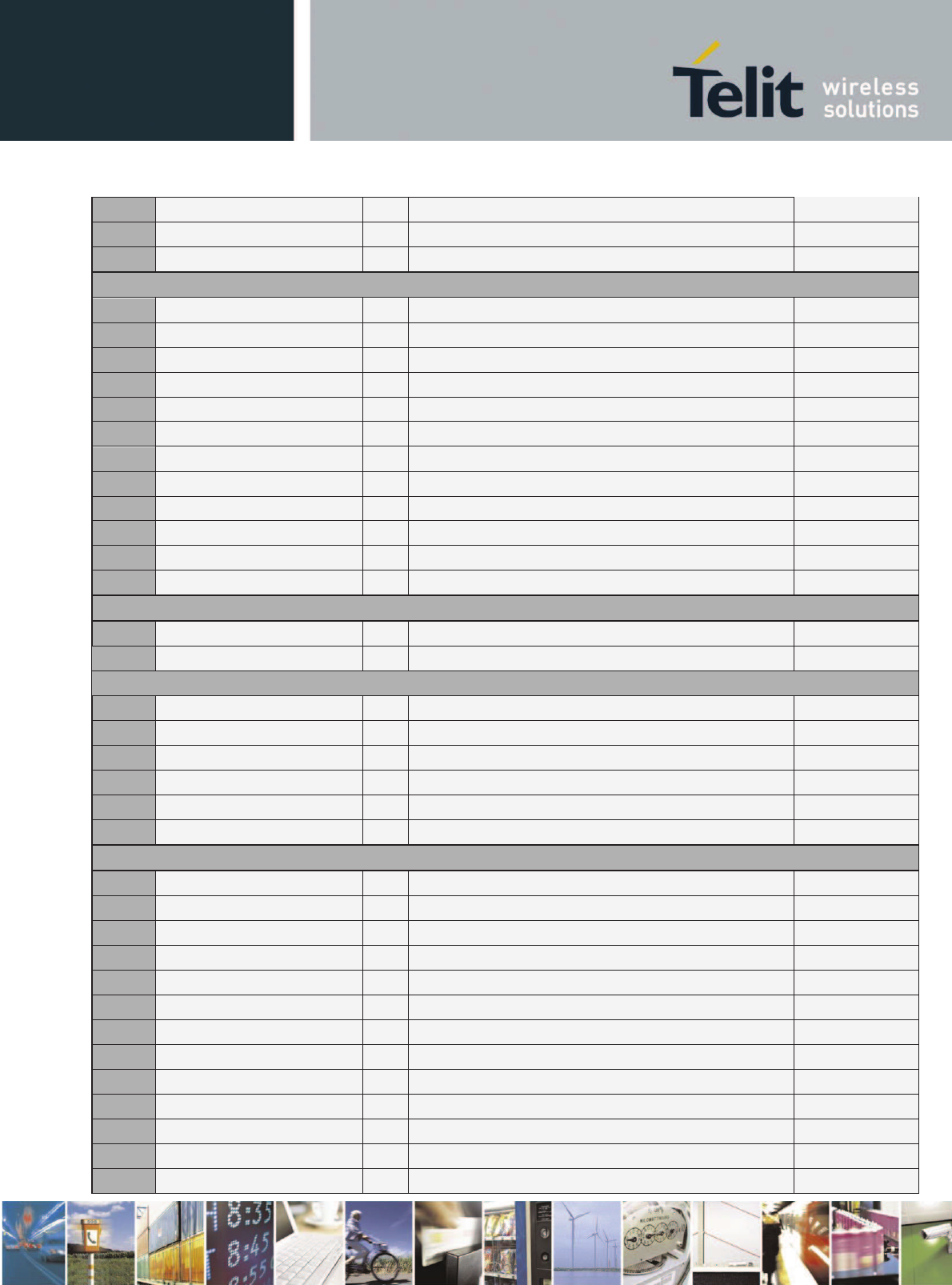

DIGITAL GPIO

AV8

GPIO0_EINT5

I/O

GPIO / External IRQ

CMOS 1.8V

AT8

GPIO1_EINT2

I/O

GPIO / External IRQ, Used for SoC USB ID WU from

Sleep

CMOS 1.8V

AS11

GPIO5_EINT7

I/O

GPIO / USB_FAULT IRQ

CMOS 1.8V

G10

GPIO44

I/O

GPIO

CMOS 1.8V

E10

GPIO45

I/O

GPIO

CMOS 1.8V

A10

GPIO46

I/O

GPIO

CMOS 1.8V

H9

GPIO47

I/O

GPIO

CMOS 1.8V

F9

GPIO48

I/O

GPIO

CMOS 1.8V

B9

GPIO49

I/O

GPIO

CMOS 1.8V

G8

GPIO50

I/O

GPIO

CMOS 1.8V

E8

GPIO51

I/O

GPIO

CMOS 1.8V

A8

GPIO52_EINT15

I/O

GPIO / External IRQ

CMOS 1.8V

H17

GPIO53

I/O

GPIO / MIPI Trace Clock

CMOS 1.8V

K5

GPIO54_EINT1

I/O

GPIO / External IRQ

CMOS 1.8V

G14

GPIO55_EINT15

I/O

GPIO / External IRQ

CMOS 1.8V

H7

GPIO56

I/O

GPIO

CMOS 1.8V

B11

GPIO57_EINT9

I/O

GPIO / External IRQ

CMOS 1.8V

D11

GPIO58_EINT2

I/O

GPIO / External IRQ

CMOS 1.8V

E6

GPIO63_EINT8

I/O

GPIO / External IRQ

CMOS 1.8V

A6

GPIO64_EINT13

I/O

GPIO / External IRQ

CMOS 1.8V

H5

GPIO65

I/O

GPIO

CMOS 1.8V

F5

GPIO66_EINT15

I/O

GPIO / External IRQ

CMOS 1.8V

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 29 of 112

B5

GPIO67_EINT0

I/O

GPIO / External IRQ

CMOS 1.8V

F3

GPIO72_EINT9

I/O

GPIO / External IRQ

CMOS 1.8V

B3

GPIO73_EINT10

I/O

GPIO / External IRQ

CMOS 1.8V

Miscellaneous Functions

AR16

ON_OFF

I

Power ON/OFF

AU5

MAIN_RESET_IN

I

MAIN_RESET

AR14

LED_CURSINK

I

GP LED Driver (Sink)

AS5

HW_KEY

I

Product ID for Production testing

AN8

GNSS_FTA

Used internally (do not connect)

AN14

CHG_RST_OUT

O

External Charger Reset

AB21

CHG_INT_IN

I

Charger IRQ

AN16

CHG_POK_IN

I

Charger Power OK indication

AW17

VBUS_PWR_EN

O

Enable External VBUS source for DRD

AV16

FG_IBATP

I

Battery Fuel Gauge Positive

AT16

FG_IBATN

I

Battery Fuel Gauge Negative

AM19

ADC_VBATMEAS

I

Battery/DC-supply measurement ADC

ADC Ports

AL18

ADC_IN0

AI

Analog to Digital converter (Batt ID)

Analog

AK19

ADC_IN1

AI

Analog to Digital converter (Batt Temp)

Analog

JTAG

AT4

JTAG_TDO

O

JTAG

CMOS 1.8V

AN4

JTAG_TDI

I

JTAG

CMOS 1.8V

AR4

JTAG_TMS

I

JTAG

CMOS 1.8V

AV4

JTAG_TCK

O

JTAG

CMOS 1.8V

AW5

JTAG_TRST

O

JTAG

CMOS 1.8V

AW3

JTAG_RTCK

I

JTAG

CMOS 1.8V

Power Supply In / OUT

AR18

V_BAT_1

-

Main power supply for Baseband

PWR in

AS19

V_BAT_2

-

Main power supply for Baseband

PWR in

AR20

V_BAT_3

-

Main power supply for Baseband

PWR in

AT20

V_BAT_4

-

Main power supply for Baseband

PWR in

AV20

V_BAT_5

-

Main power supply for Baseband

PWR in

AS21

V_BAT_6

-

Main power supply for Baseband

PWR in

AU21

V_BAT_7

-

Main power supply for Baseband

PWR in

AV18

V_BAT_PA_1

-

Main power supply for PA

PWR in

AT18

V_BAT_PA_2

-

Main power supply for PA

PWR in

AU19

V_BAT_PA_3

-

Main power supply for PA

PWR in

AK17

1V8_OUT

-

1.8V Supply / Reference for external peripherals

PWR out

AA18

VAUX_1P8V

-

Camera 1.8V or auxiliary configurable power supply

PWR out

AH17

VAUX_2P85V

-

Camera 2.85V or auxiliary configurable power supply

PWR out

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 30 of 112

AA4

VAUX_3P0V

-

Auxiliary 3.0V power supply (shared with internal

eMMC supply)

PWR out

AA20

V_RTC

-

RTC backup

PWR in

GND

A2

GND

-

GROUND

A14

GND

-

GROUND

A20

GND

-

GROUND

B1

GND

-

GROUND

B13

GND

-

GROUND

B21

GND

-

GROUND

C4

GND

-

GROUND

C6

GND

-

GROUND

C8

GND

-

GROUND

C10

GND

-

GROUND

C12

GND

-

GROUND

D1

GND

-

GROUND

D3

GND

-

GROUND

D5

GND

-

GROUND

D7

GND

-

GROUND

D9

GND

-

GROUND

D13

GND

-

GROUND

E16

GND

-

GROUND

F17

GND

-

GROUND

G20

GND

-

GROUND

H11

GND

-

GROUND

H13

GND

-

GROUND

H15

GND

-

GROUND

J4

GND

-

GROUND

J6

GND

-

GROUND

J8

GND

-

GROUND

J10

GND

-

GROUND

J12

GND

-

GROUND

J14

GND

-

GROUND

J16

GND

-

GROUND

J18

GND

-

GROUND

K3

GND

-

GROUND

K7

GND

-

GROUND

K9

GND

-

GROUND

K11

GND

-

GROUND

K13

GND

-

GROUND

K15

GND

-

GROUND

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 31 of 112

L2

GND

-

GROUND

L6

GND

-

GROUND

L8

GND

-

GROUND

L10

GND

-

GROUND

L12

GND

-

GROUND

L14

GND

-

GROUND

L16

GND

-

GROUND

M5

GND

-

GROUND

M7

GND

-

GROUND

M9

GND

-

GROUND

M11

GND

-

GROUND

M13

GND

-

GROUND

M15

GND

-

GROUND

M17

GND

-

GROUND

N6

GND

-

GROUND

N8

GND

-

GROUND

N10

GND

-

GROUND

N12

GND

-

GROUND

N14

GND

-

GROUND

N16

GND

-

GROUND

P7

GND

-

GROUND

P9

GND

-

GROUND

P11

GND

-

GROUND

P13

GND

-

GROUND

P15

GND

-

GROUND

R2

GND

-

GROUND

R6

GND

-

GROUND

R8

GND

-

GROUND

R10

GND

-

GROUND

R12

GND

-

GROUND

R14

GND

-

GROUND

R16

GND

-

GROUND

S1

GND

-

GROUND

S3

GND

-

GROUND

S7

GND

-

GROUND

S9

GND

-

GROUND

S11

GND

-

GROUND

S13

GND

-

GROUND

S15

GND

-

GROUND

T6

GND

-

GROUND

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 32 of 112

T8

GND

-

GROUND

T10

GND

-

GROUND

T12

GND

-

GROUND

T14

GND

-

GROUND

T16

GND

-

GROUND

U1

GND

-

GROUND

U3

GND

-

GROUND

U7

GND

-

GROUND

U9

GND

-

GROUND

U11

GND

-

GROUND

U13

GND

-

GROUND

U15

GND

-

GROUND

V2

GND

-

GROUND

V6

GND

-

GROUND

V8

GND

-

GROUND

V10

GND

-

GROUND

V12

GND

-

GROUND

V14

GND

-

GROUND

V16

GND

-

GROUND

W7

GND

-

GROUND

W9

GND

-

GROUND

W11

GND

-

GROUND

W13

GND

-

GROUND

W15

GND

-

GROUND

X4

GND

-

GROUND

X6

GND

-

GROUND

X8

GND

-

GROUND

X10

GND

-

GROUND

X12

GND

-

GROUND

X14

GND

-

GROUND

X16

GND

-

GROUND

X20

GND

-

GROUND

Y7

GND

-

GROUND

Y9

GND

-

GROUND

Y11

GND

-

GROUND

Y13

GND

-

GROUND

Y15

GND

-

GROUND

Y19

GND

-

GROUND

AA6

GND

-

GROUND

AA8

GND

-

GROUND

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 33 of 112

AA10

GND

-

GROUND

AA12

GND

-

GROUND

AA14

GND

-

GROUND

AA16

GND

-

GROUND

AB5

GND

-

GROUND

AB7

GND

-

GROUND

AB9

GND

-

GROUND

AB11

GND

-

GROUND

AB13

GND

-

GROUND

AB15

GND

-

GROUND

AC2

GND

-

GROUND

AC6

GND

-

GROUND

AC8

GND

-

GROUND

AC10

GND

-

GROUND

AC12

GND

-

GROUND

AC14

GND

-

GROUND

AC16

GND

-

GROUND

AC20

GND

-

GROUND

AD1

GND

-

GROUND

AD3

GND

-

GROUND

AD7

GND

-

GROUND

AD9

GND

-

GROUND

AD11

GND

-

GROUND

AD13

GND

-

GROUND

AD15

GND

-

GROUND

AD21

GND

-

GROUND

AE6

GND

-

GROUND

AE8

GND

-

GROUND

AE10

GND

-

GROUND

AE12

GND

-

GROUND

AE14

GND

-

GROUND

AE16

GND

-

GROUND

AF1

GND

-

GROUND

AF3

GND

-

GROUND

AF5

GND

-

GROUND

AF7

GND

-

GROUND

AF9

GND

-

GROUND

AF11

GND

-

GROUND

AF13

GND

-

GROUND

AF15

GND

-

GROUND

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 34 of 112

AF17

GND

-

GROUND

AG2

GND

-

GROUND

AG4

GND

-

GROUND

AG6

GND

-

GROUND

AG8

GND

-

GROUND

AG10

GND

-

GROUND

AG12

GND

-

GROUND

AG14

GND

-

GROUND

AG16

GND

-

GROUND

AH5

GND

-

GROUND

AH7

GND

-

GROUND

AH9

GND

-

GROUND

AH11

GND

-

GROUND

AH13

GND

-

GROUND

AH15

GND

-

GROUND

AJ4

GND

-

GROUND

AJ6

GND

-

GROUND

AJ8

GND

-

GROUND

AJ10

GND

-

GROUND

AJ12

GND

-

GROUND

AJ14

GND

-

GROUND

AJ16

GND

-

GROUND

AK5

GND

-

GROUND

AK7

GND

-

GROUND

AK9

GND

-

GROUND

AK11

GND

-

GROUND

AK13

GND

-

GROUND

AK15

GND

-

GROUND

AL2

GND

-

GROUND

AL4

GND

-

GROUND

AL6

GND

-

GROUND

AL8

GND

-

GROUND

AL10

GND

-

GROUND

AL12

GND

-

GROUND

AL14

GND

-

GROUND

AL16

GND

-

GROUND

AM1

GND

-

GROUND

AM3

GND

-

GROUND

AM7

GND

-

GROUND

AM9

GND

-

GROUND

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 35 of 112

AM11

GND

-

GROUND

AM13

GND

-

GROUND

AM15

GND

-

GROUND

AN18

GND

-

GROUND

AN20

GND

-

GROUND

AP1

GND

-

GROUND

AP3

GND

-

GROUND

AP19

GND

-

GROUND

AP21

GND

-

GROUND

AR2

GND

-

GROUND

AS3

GND

-

GROUND

AT10

GND

-

GROUND

AT14

GND

-

GROUND

AU1

GND

-

GROUND

AU3

GND

-

GROUND

AU9

GND

-

GROUND

AU11

GND

-

GROUND

AU13

GND

-

GROUND

AU15

GND

-

GROUND

AV2

GND

-

GROUND

AV6

GND

-

GROUND

AW1

GND

-

GROUND

AW7

GND

-

GROUND

AW9

GND

-

GROUND

AW11

GND

-

GROUND

AW13

GND

-

GROUND

AW15

GND

-

GROUND

AW19

GND

-

GROUND

AW21

GND

-

GROUND

RFU

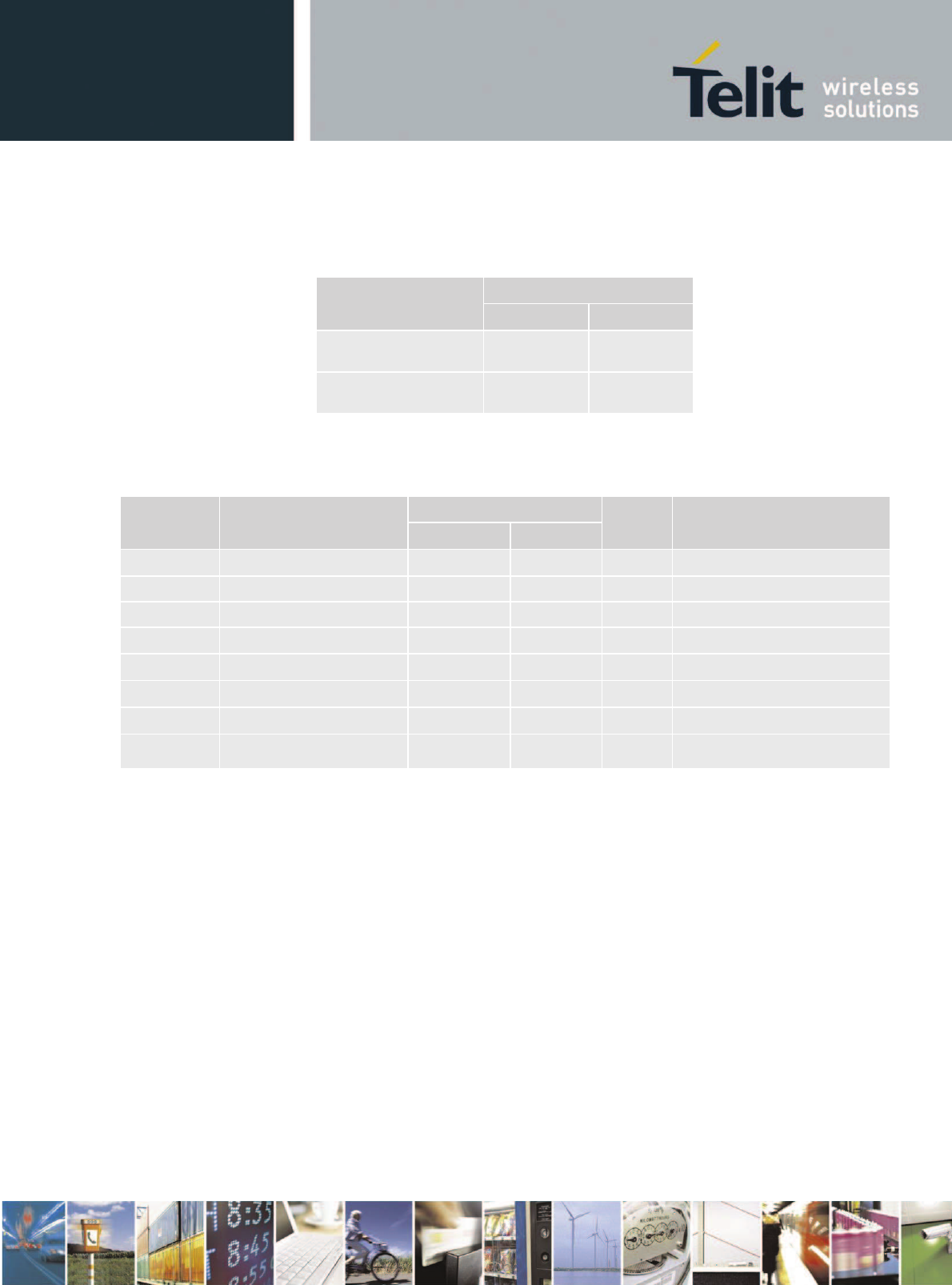

D17

RFU1

-

B17

RFU2

-

C16

RFU3

-

A16

RFU4

-

C2

RFU5

-

AS13

RFU6

-

K17

RFU7

-

AS9

RFU8

-

AN2

RFU9

-

AK1

RFU10

-

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 36 of 112

AH1

RFU11

-

P5

RFU12

-

R4

RFU13

-

T4

RFU14

-

V4

RFU15

-

AP5

RFU16

-

W3

RFU17

-

Y3

RFU18

-

AB3

RFU19

-

AC4

RFU20

-

X2

RFU21

-

AA2

RFU22

-

W1

RFU23

-

Y1

RFU24

-

AB1

RFU25

-

C14

RFU26

-

G16

RFU27

-

A12

RFU28

-

F15

RFU29

-

G12

RFU30

-

E12

RFU31

-

E14

RFU32

-

F13

RFU33

-

D15

RFU34

-

B15

RFU35

-

T18

RFU36

-

R18

RFU37

-

N18

RFU38

-

L18

RFU39

-

AR12

RFU40

-

Y17

RFU41

-

AB19

RFU42

-

AD19

RFU43

-

AV10

RFU44

-

NOTE:

Unless otherwise specified, RFU pins must be left unconnected (Floating).

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 37 of 112

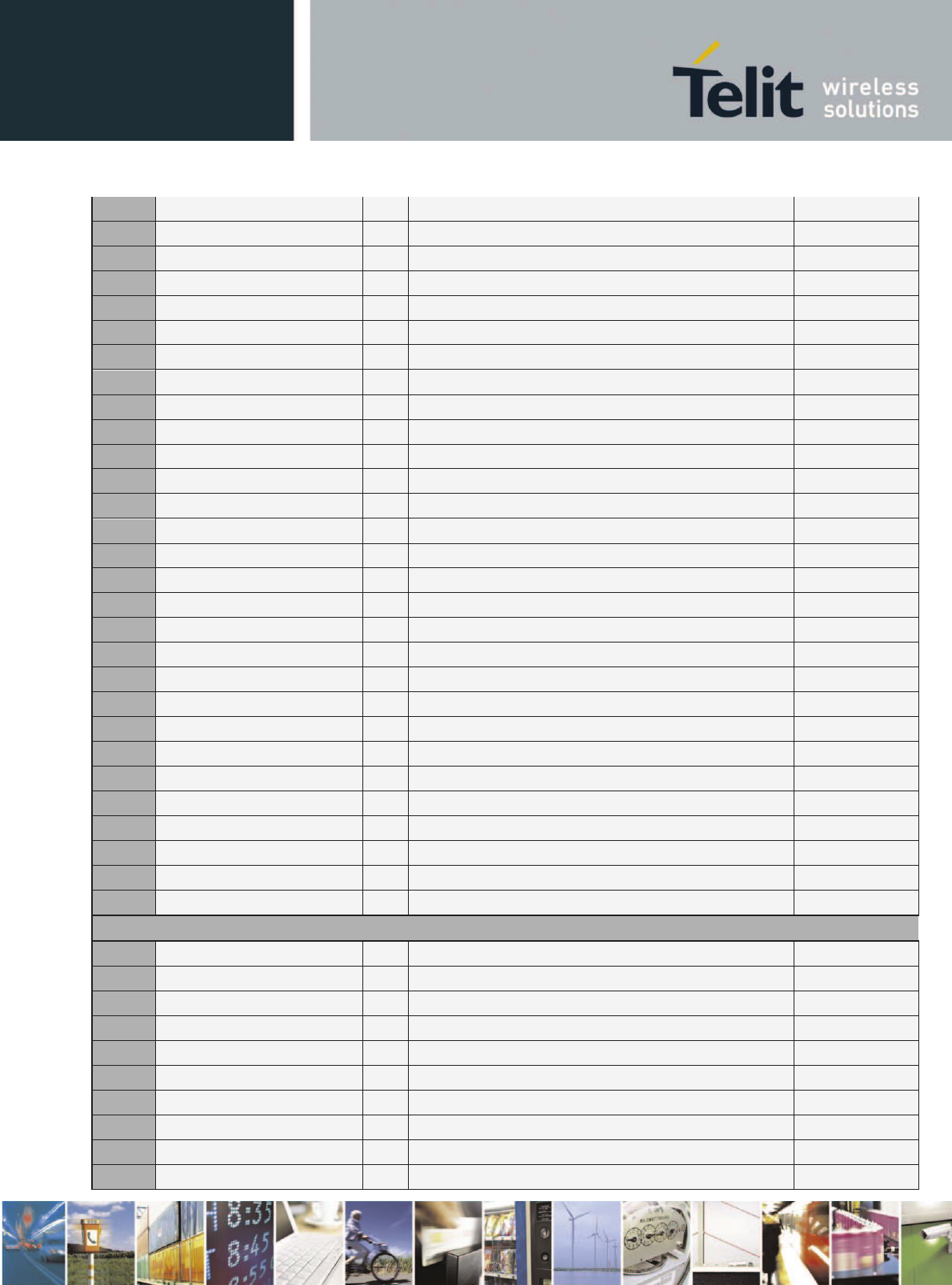

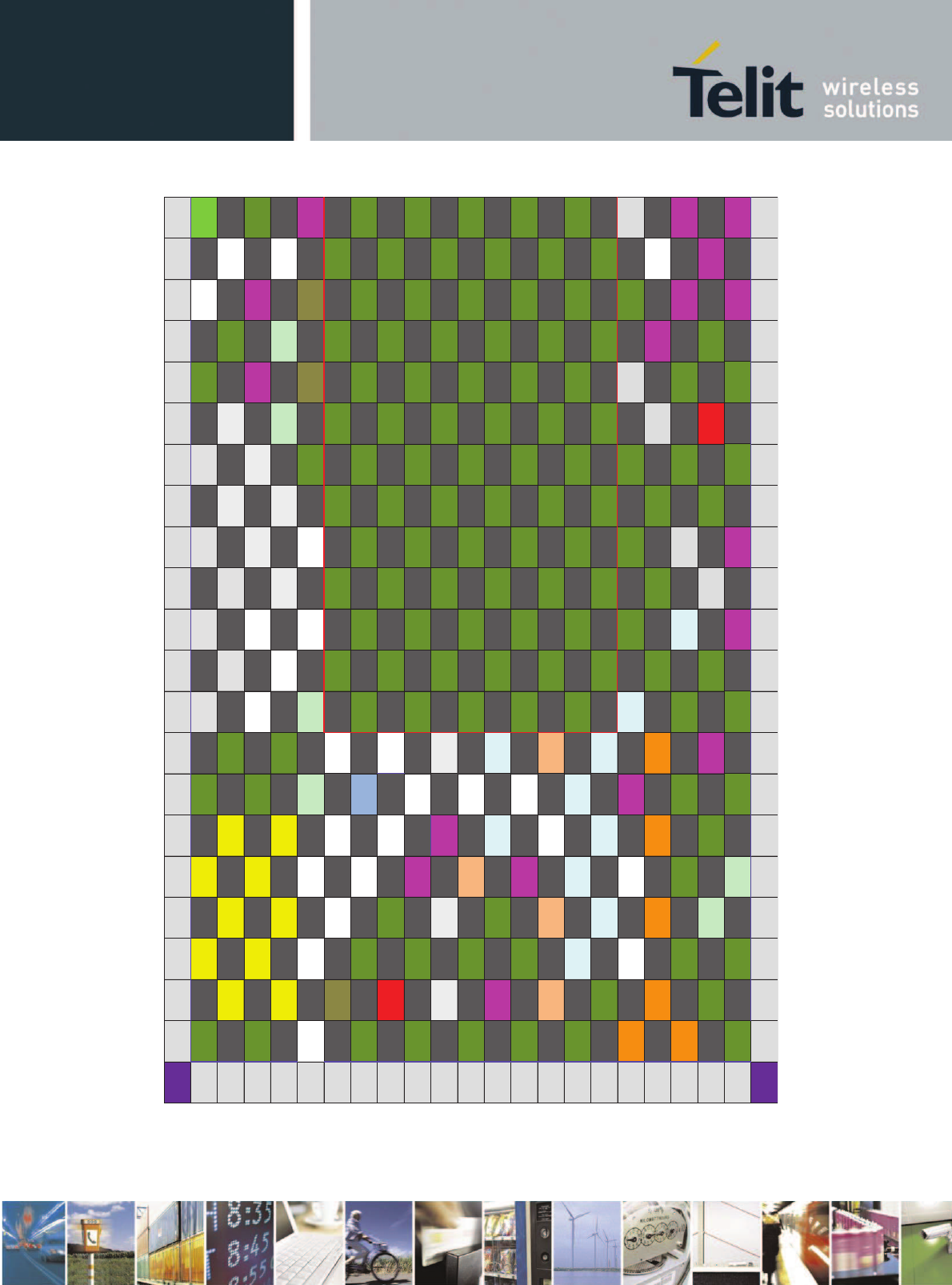

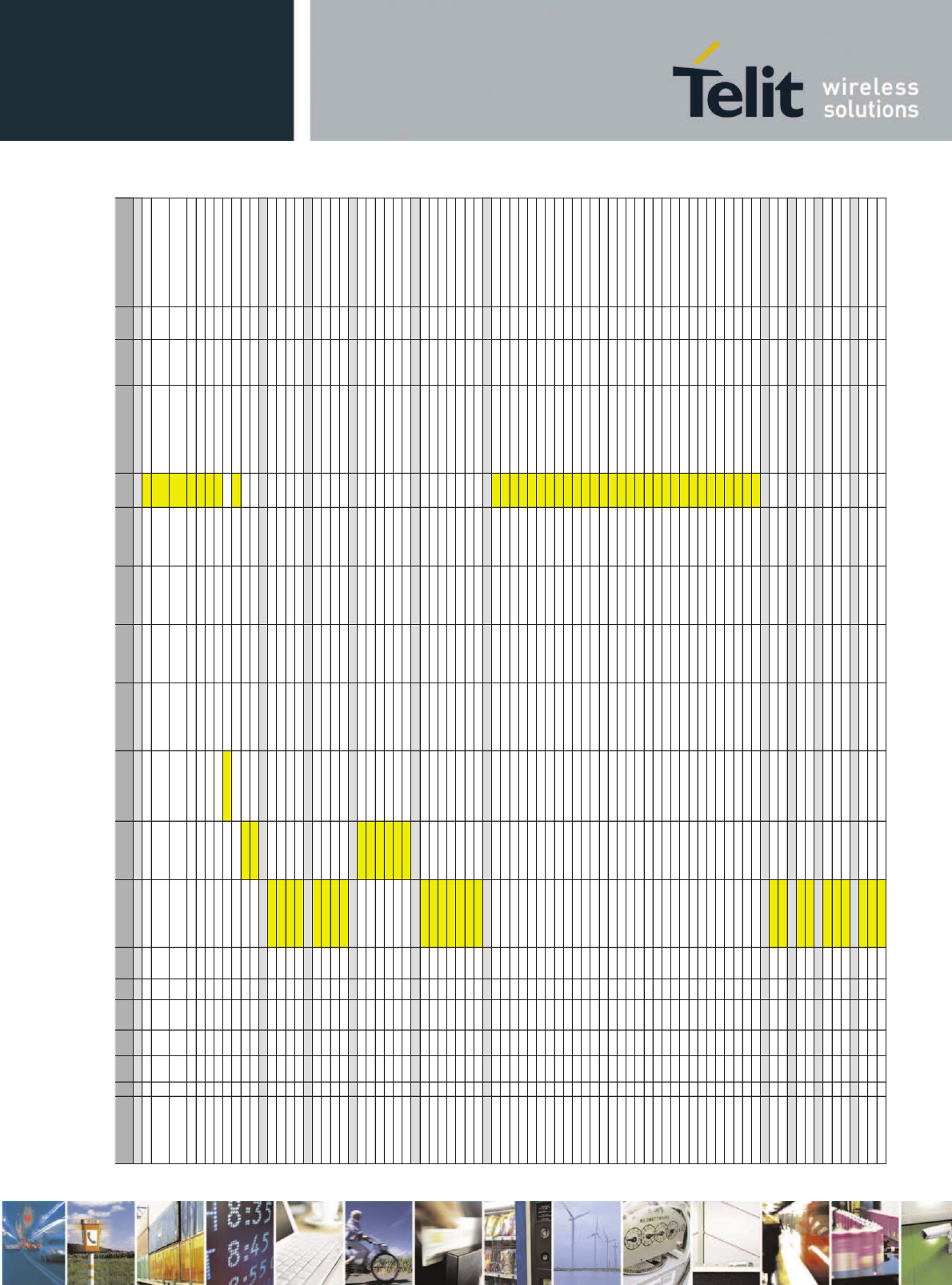

3.2. LGA Pads Layout

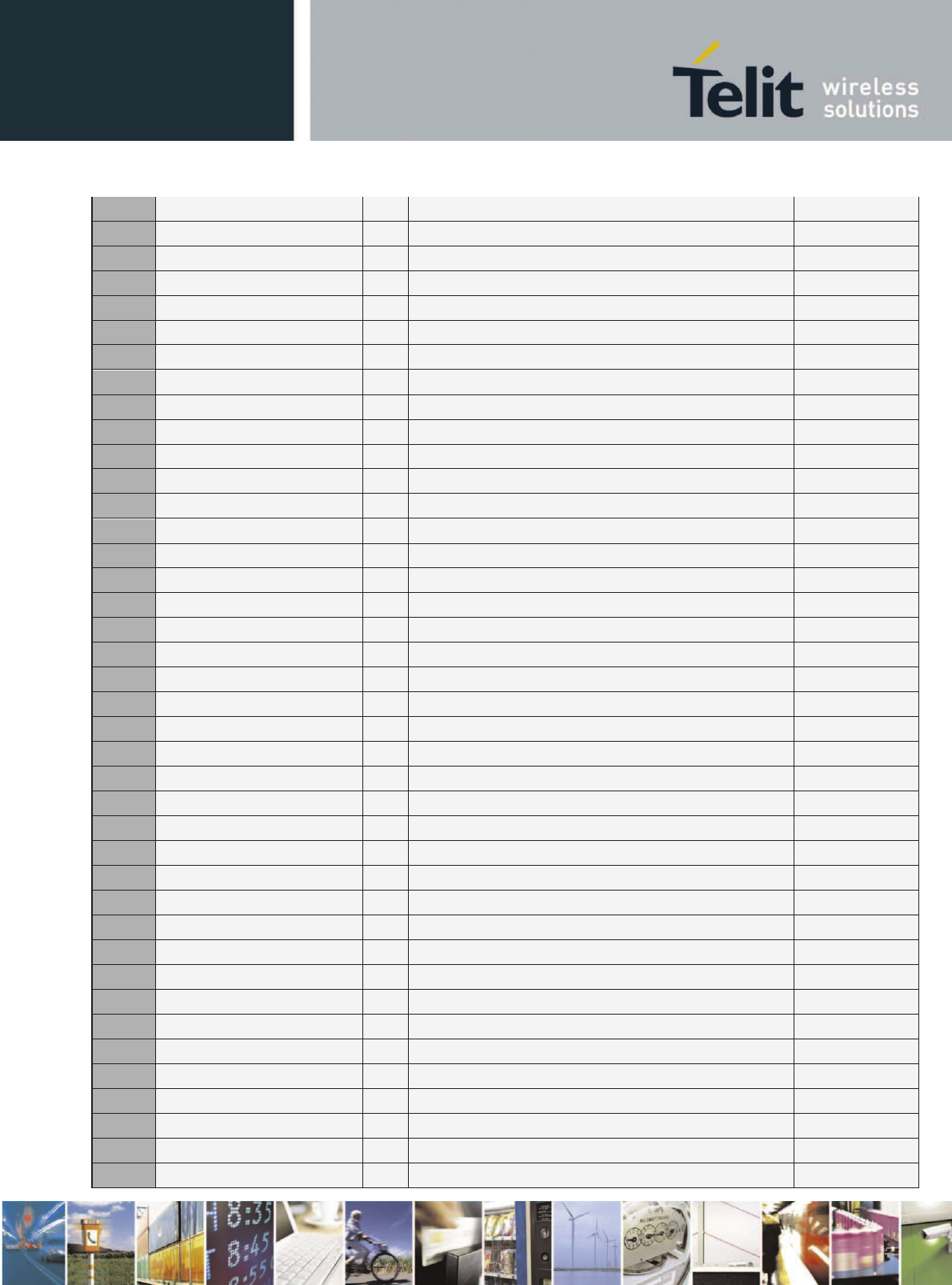

A B C D E F G H J K L M N P R S T U V W X

1GND GND SD_DAT0 SD_DAT1 SD_DAT2 SD_DAT3 SDIO_DAT0 GND GND RFU23

2GND RFU5 SD_CLK SD_CMD SD_CARD_DE

TGND SDIO_DAT1 GND ANT_GPS GND RFU21

3GPIO73_EINT1

0GND GPIO72_EINT9 CAM2_PD GND SDIO_DAT2 SDIO_CMD GND GND RFU17

4CAM1_PD GND CAM2_RESET CAM1_RESET GND SDIO_CLK SDIO_DAT3 RFU13 RFU14 RFU15 GND

5GPIO67_EINT0 GND GPIO66_EINT1

5GPIO65 GPIO54_EINT1 GND RFU12 USIF1_SCLK USIF1_CS USIF1_RXD

6GPIO64_EINT1

3GND GPIO63_EINT8 CAM1_TORCH GND GND GND GND GND GND GND

7CAM1_FLASH GND TP_RESET GPIO56 GND GND GND GND GND GND

8GPIO52_EINT1

5GND GPIO51 GPIO50 GND GND GND GND GND GND GND

9GPIO49 GND GPIO48 GPIO47 GND GND GND GND GND GND

10 GPIO46 GND GPIO45 GPIO44 GND GND GND GND GND GND GND

11 GPIO57_EINT9 GPIO58_EINT2 TP_IRQ GND GND GND GND GND GND GND

12 RFU28 GND RFU31 RFU30 GND GND GND GND GND GND GND

13 GND GND RFU33 GND GND GND GND GND GND GND

14 GND RFU26 RFU32 GPIO55_EINT1

5GND GND GND GND GND GND GND

15 RFU35 RFU34 RFU29 GND GND GND GND GND GND GND

16 RFU4 RFU3 GND RFU27 GND GND GND GND GND GND GND

17 RFU2 RFU1 GND GPIO53 RFU7 GND CAM_MCLK USB_DP USB_DN USB_ID

18 CSI2_DP CSI2_DN CSI1_DP3 CSI1_DN3 GND RFU39 RFU38 RFU37 RFU36 LVDS_TB1N

LVDS_TB1P

19 CSI2_CLKP CSI2_CLKN CSI1_DP2 CSI1_DN2 CSI1_DN1 CSI1_DP1 DSI_DN0 DSI_DP0 LVDS_TA1N LVDS_TA1P

20 GND CSI1_CLKP CSI1_CLKN GND DSI_DN2 DSI_DP2 DSI_DN1 DSI_DP1 LVDS_TC1N LVDS_TC1P GND

21 GND CSI1_DP0 CSI1_DN0 DSI_DN3 DSI_DP3 DSI_CLKP DSI_CLKN LVDS_TCLK1N LVDS_TCLK1P LVDS_TD1N

A B C D E F G H J K L M N P R S T U V W X

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 38 of 112

Y AA AB AC AD AE AF AG AH AJ AK AL AM AN AP AR AS AT AU AV AW

RFU24 RFU25 GND GND RFU11 RFU10 GND GND AUX_I2C_SDA GND GND 1

RFU22 GND ANT_MAIN GND USIF2_CS GND RFU9 GND AUX_I2C_SCL GND 2

RFU18 RFU19 GND GND USIF2_RXD VSIM2 GND GND GND GND JTAG_RTCK 3

VAUX_3P0V RFU20 USIF2_TXD GND GND GND JTAG_TDI JTAG_TMS JTAG_TDO JTAG_TCK 4

USIF1_TXD GND USIF2_SCLK GND GND GND VSIM1 RFU16 HW_KEY

MAIN_RESET_I

NJTAG_TRST 5

GND GND GND GND GND GND SIMRST1 SIMCLK1 SIMIO1 GND 6

GND GND GND GND GND GND GND SIMRST2 SIMCLK2 SIMIO2 GND 7

GND GND GND GND GND GND GPIO7 VBUS_DET GPIO1_EINT2 GPIO0_EINT5 8

GND GND GND GND GND GND GND LCD_TE RFU8 GND GND 9

GND GND GND GND GND GND

USIM1_DETEC

T

USIM2_DETEC

TGND RFU44 10

GND GND GND GND GND GND GND LCD_RESET GPIO5_EINT7 GND GND 11

GND GND GND GND GND GND DIG_MIC_D1 RFU40 DIG_MIC_D2 DIG_MIC_CLK 12

GND GND GND GND GND GND GND LEDDRV RFU6 GND GND 13

GND GND GND GND GND GND CHG_RST_OU

TLED_CURSINK GND ANT_WIFI 14

GND GND GND GND GND GND GND VDD_SD CABC GND GND 15

GND GND GND GND GND GND CHG_POK_IN ON_OFF FG_IBATN FG_IBATP 16

RFU41 TP_SCL TP_SDA GND VAUX_2P85V 1V8_OUT CAM_I2C_SDA CAM_I2C_SCL LEDFB_DP LEDFB_DN

VBUS_PWR_E

N17

VAUX_1P8V CHG_I2C_SCL CHG_I2C_SDA MIC_VDD VMIC_BIAS ADC_IN0 GND V_BAT_1 V_BAT_PA_2 V_BAT_PA_1 18

GND RFU42 RFU43 MICP2 MICN2 ADC_IN1

ADC_VBATME

AS GND V_BAT_2 V_BAT_PA_3 GND 19

V_RTC GND MICN1 MICP1 HP_OUT_R HP_OUT_L GND V_BAT_3 V_BAT_4 V_BAT_5 20

LVDS_TD1P

CHG_INT_IN GND SPKR_LN SPKR_LP EP_P EP_N GND V_BAT_6 V_BAT_7 GND 21

Y AA AB AC AD AE AF AG AH AJ AK AL AM AN AP AR AS AT AU AV AW

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 39 of 112

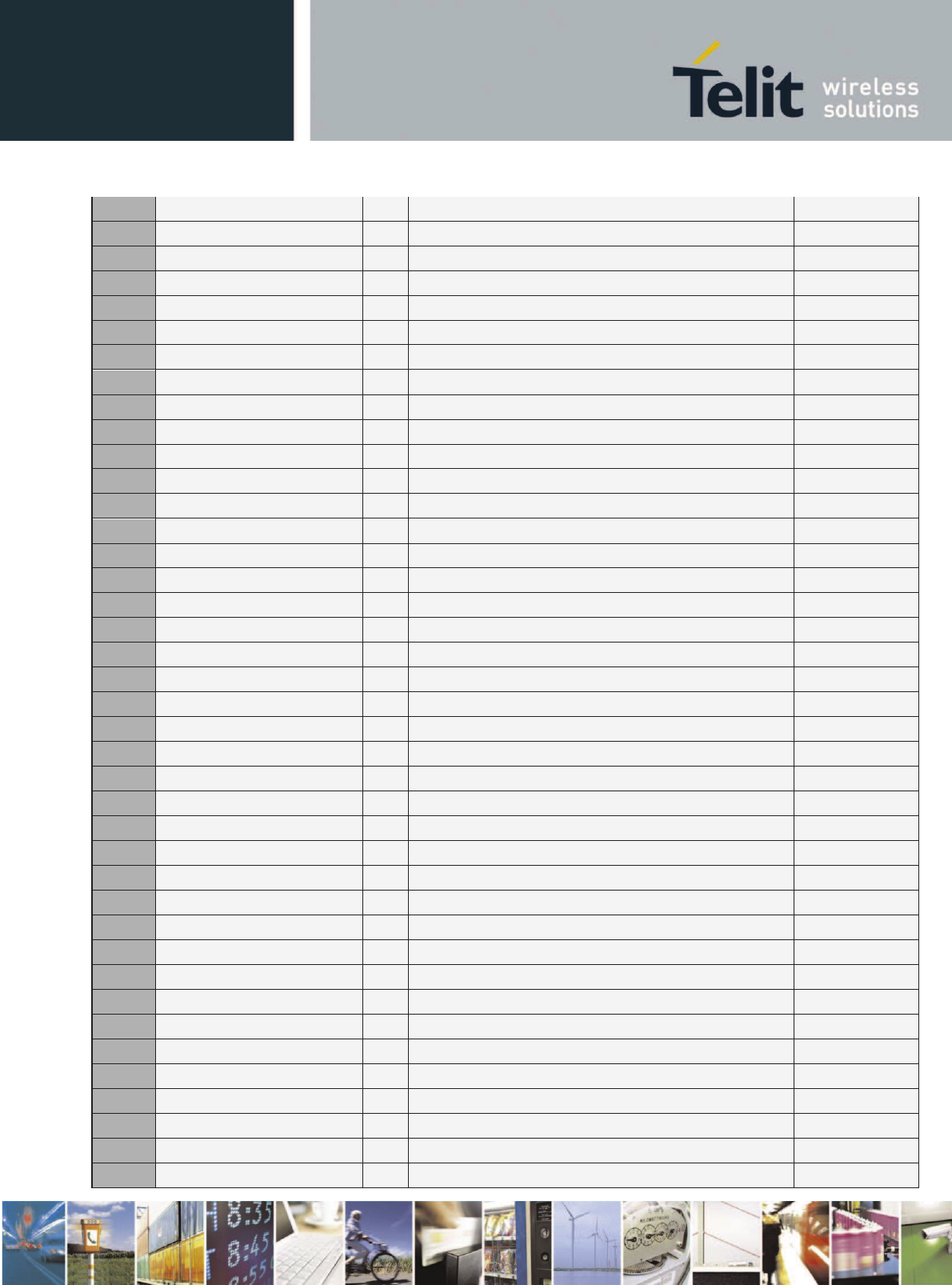

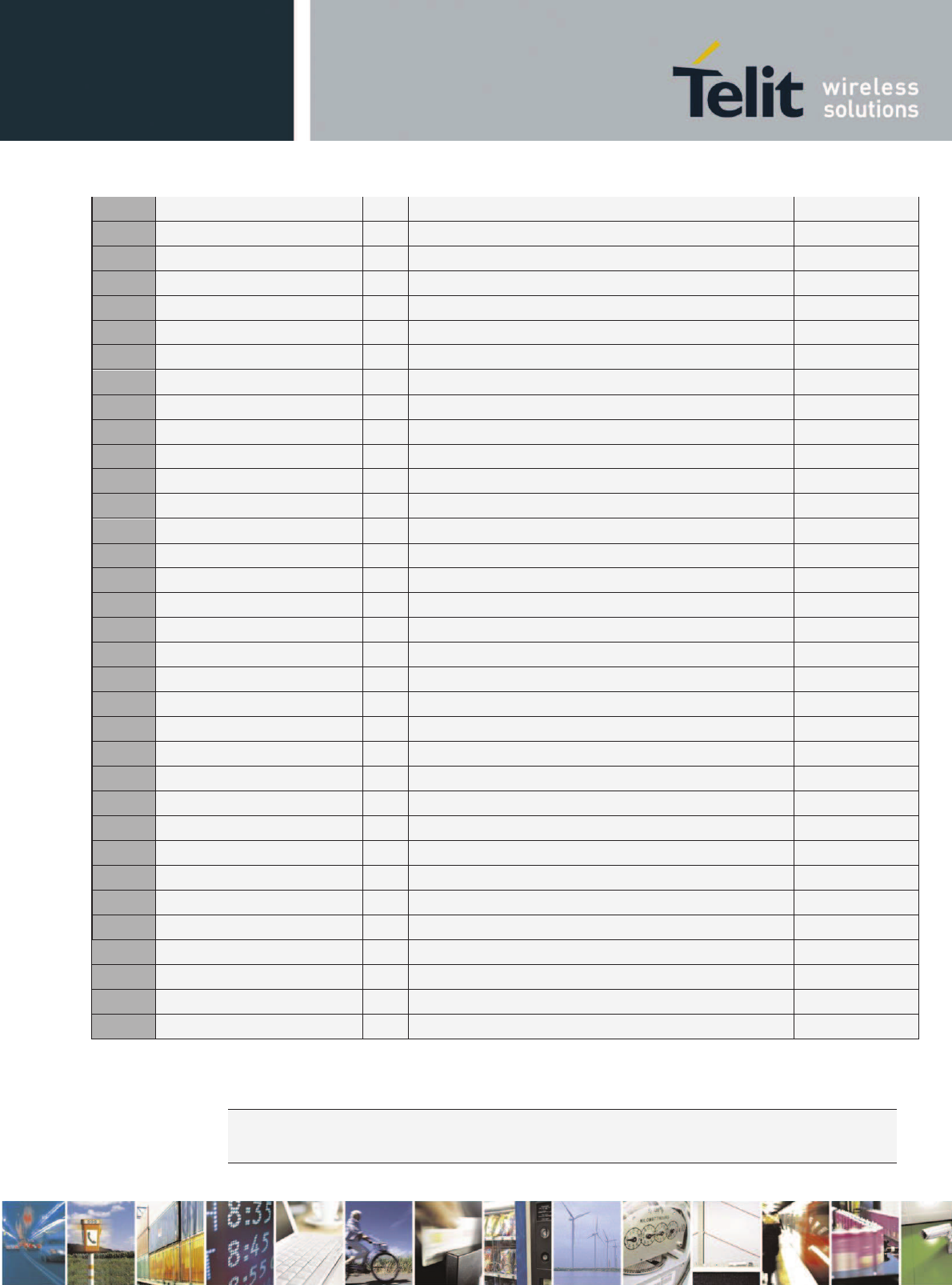

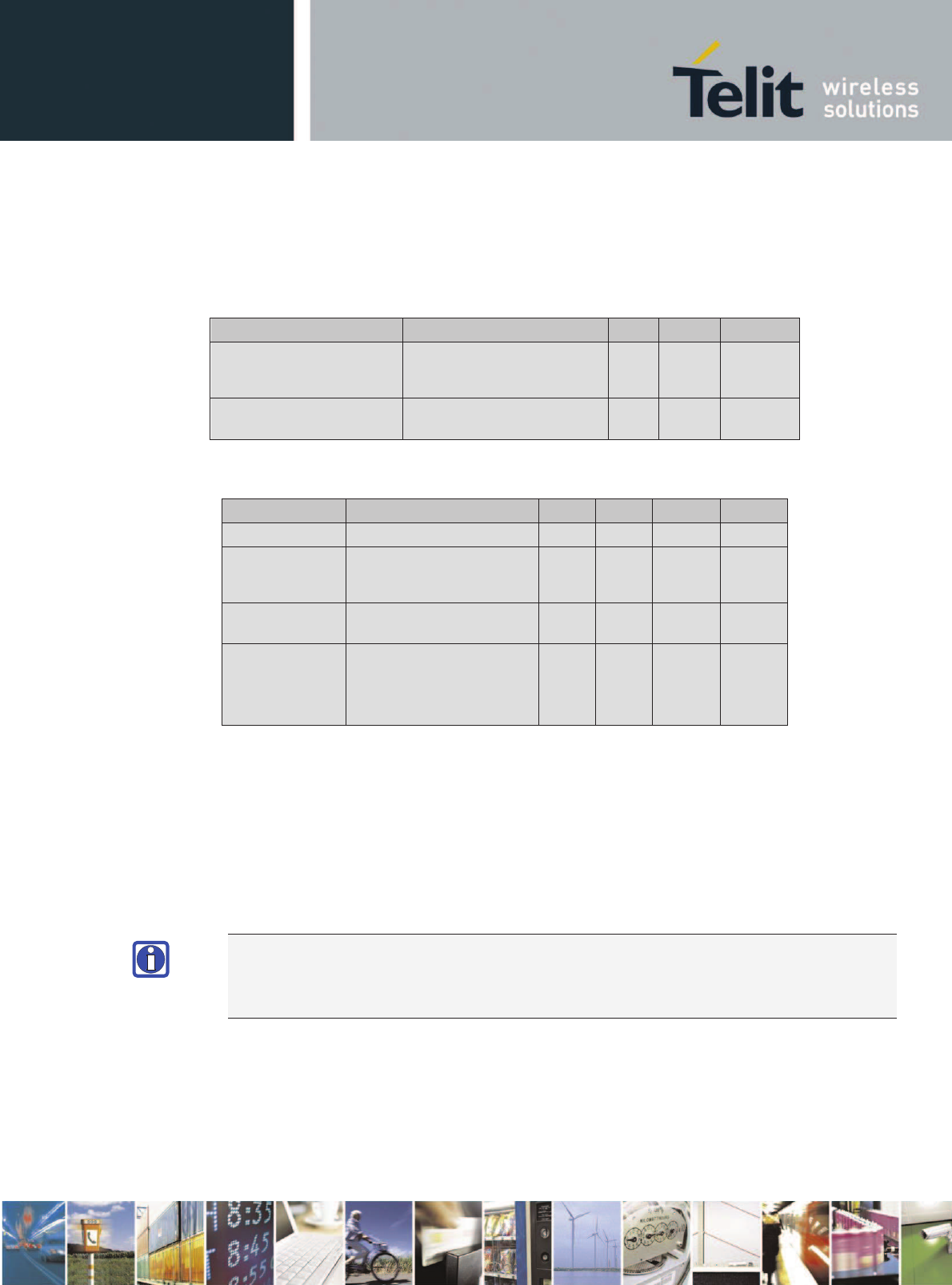

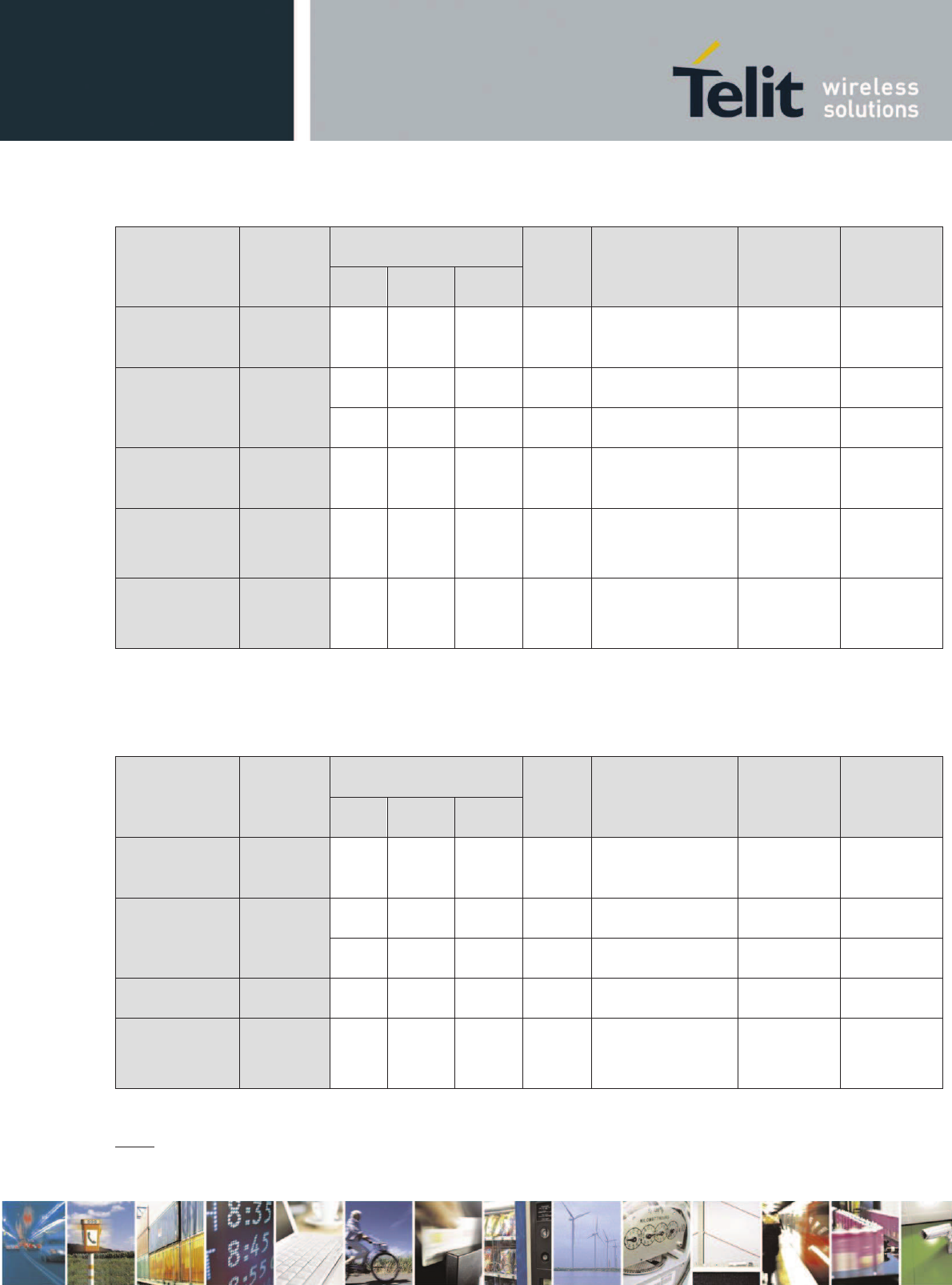

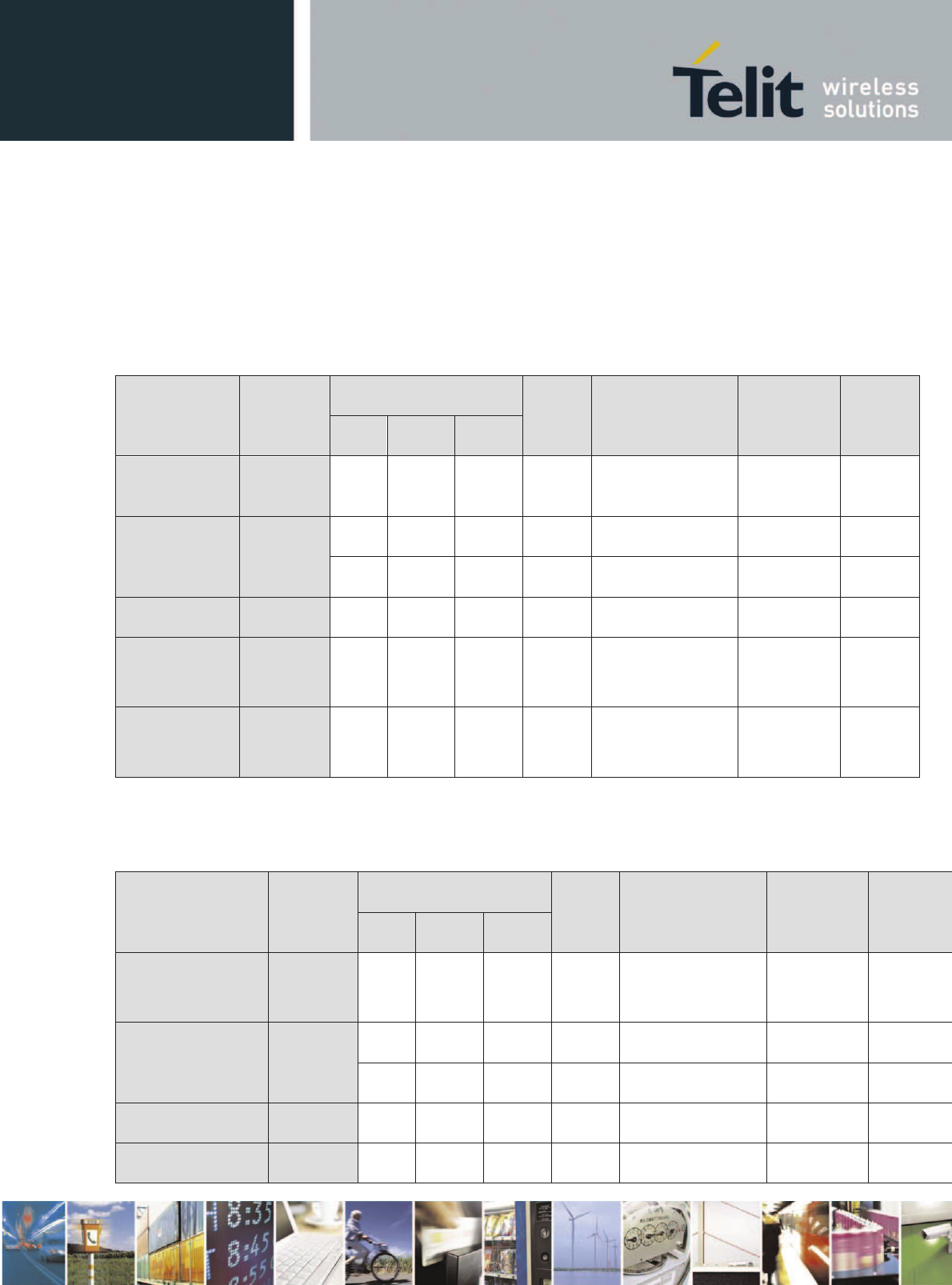

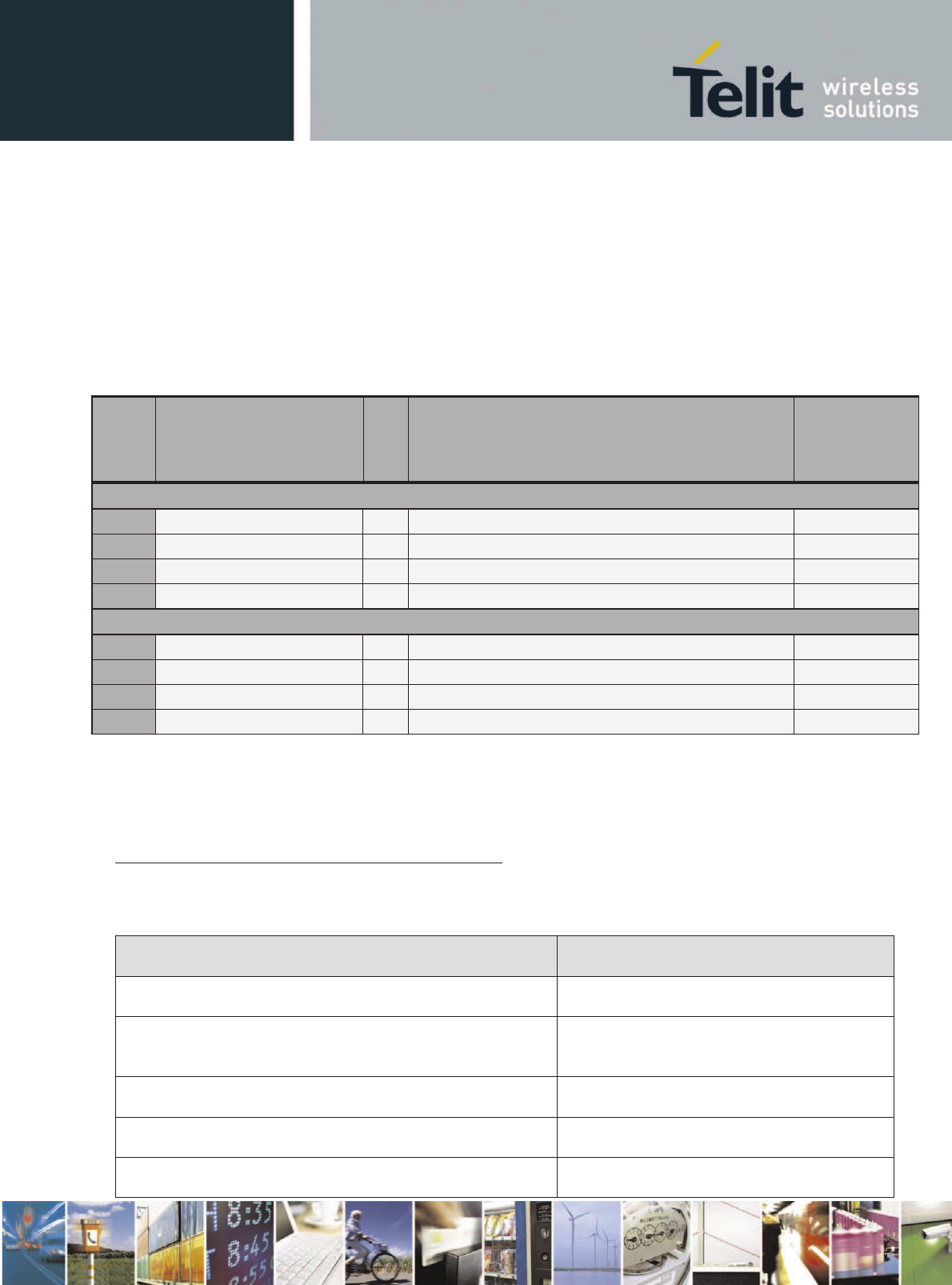

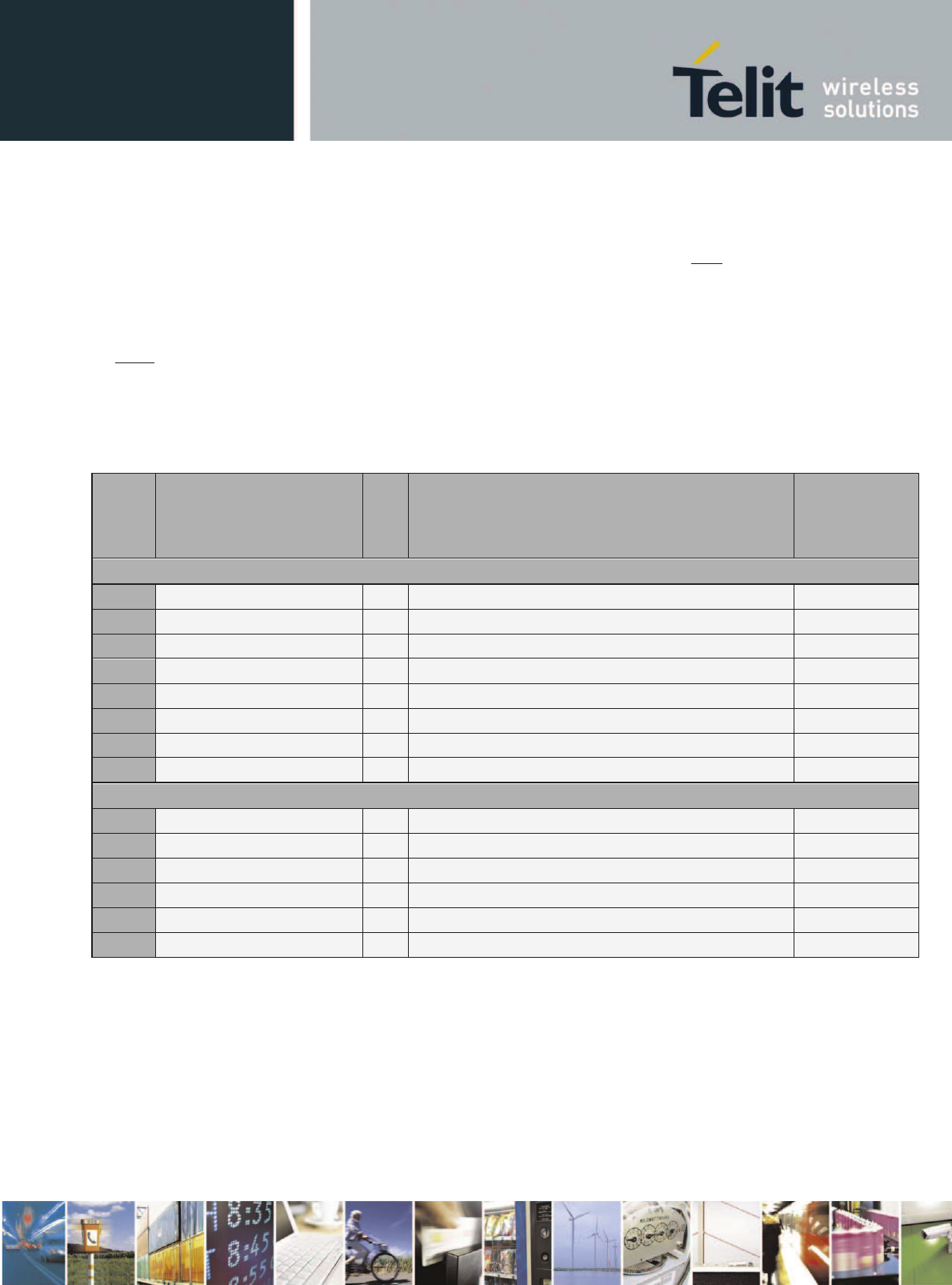

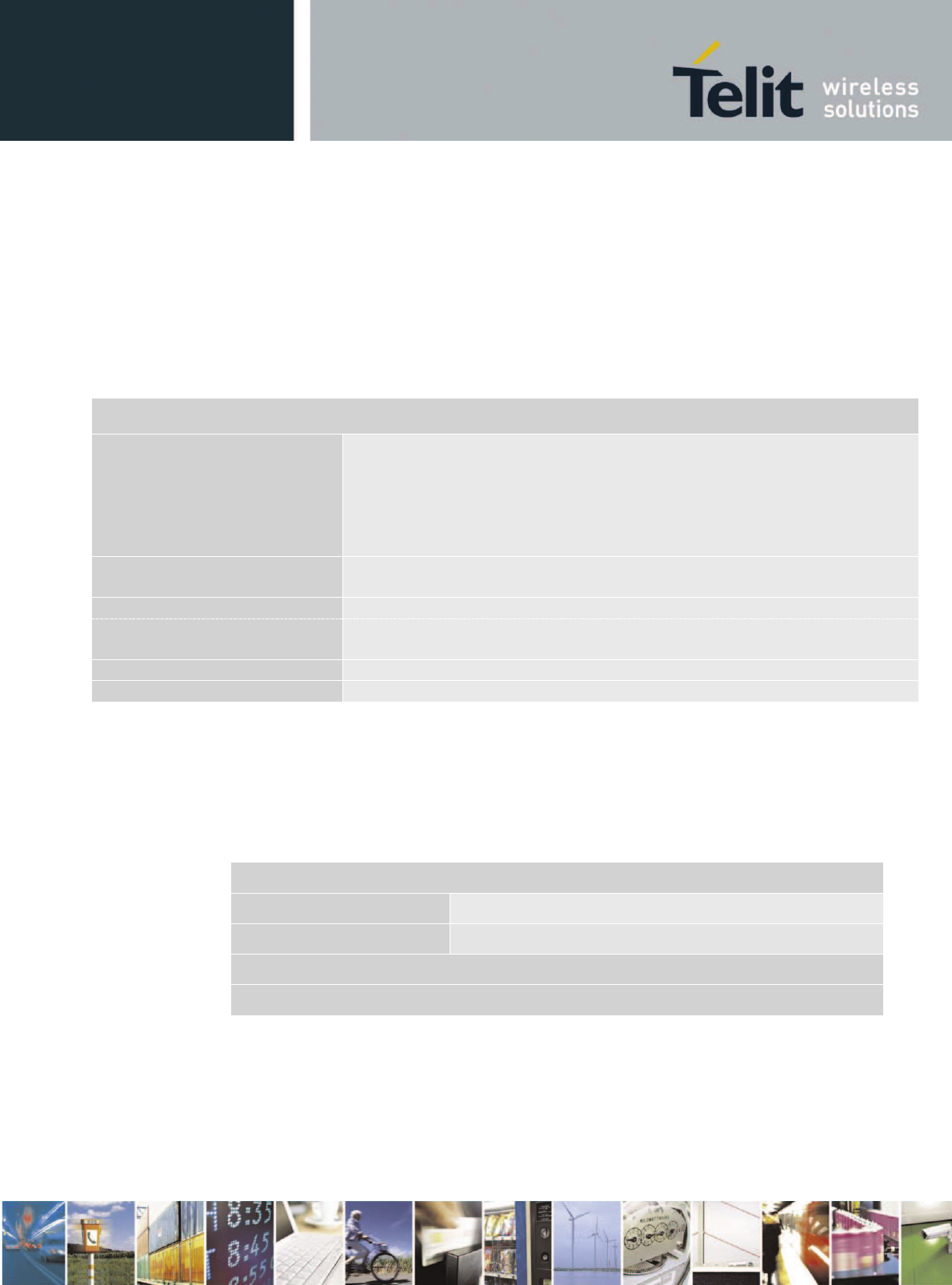

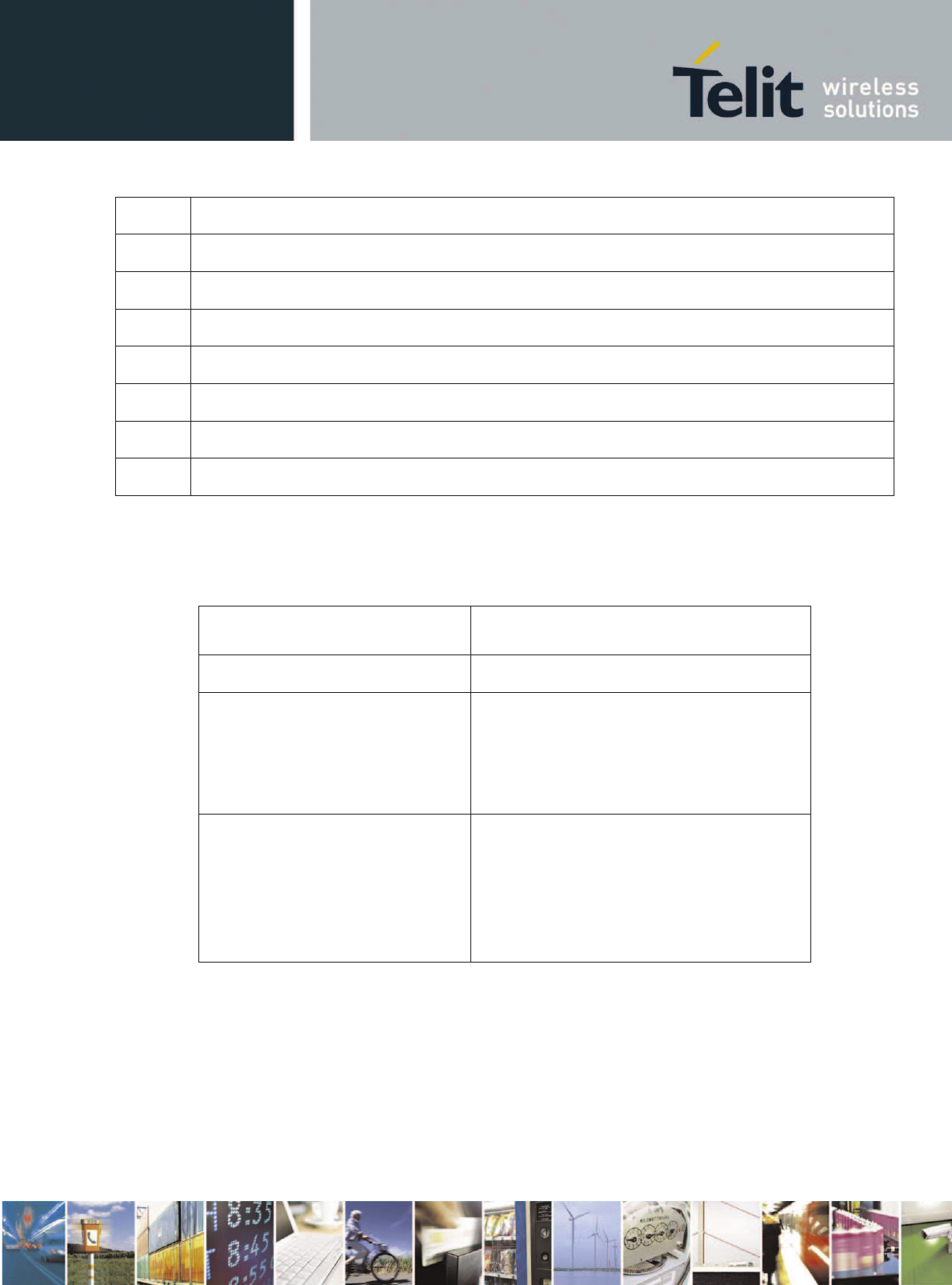

4. Electrical specifications

4.1. Absolute maximum ratings – not operational

A deviation from listed below values range may harm the xE922-3GR module.

Symbol

Parameter

Min

Max

Unit

VBATT

battery supply voltage on

pin VBATT

-0.3

+5.5

[V]

VBATT_PA

battery supply voltage on

pin VBATT_PA

-0.3

+6.0

[V]

4.2. Recommended operating conditions

Symbol

Parameter

Min

Typ

Max

Unit

Tcase

Case temperature (1)

-40

+25

+85

[°C]

VBATT

Battery supply voltage on

pin VBATT

3.6

3.8

4.2

[V]

VBATT_PA

Battery supply voltage on

pin VBATT_PA

3.6

3.8

4.2

[V]

IBATT_PA

+ I

BATT

Peak current to be used to

dimension decoupling

capacitors on pin

VBATT_PA

-

2

-

[A]

(1) Tcase case temperature: measured at top side shield of module

4.3. Logic Level Specifications

Unless otherwise specified, all the interface circuits of the xE922-3GR are 1.8V CMOS logic.

Only few specific interfaces (such as USIM) are capable of dual voltage I/O.

The following table shows the logic level specifications used in the Telit xE922-3GR

interface circuits:

NOTE:

Do not connect xE922-3GR’s digital logic signal directly to OEM’s digital logic signal with a

level higher than 2.1V for 1.8V CMOS signals.

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 40 of 112

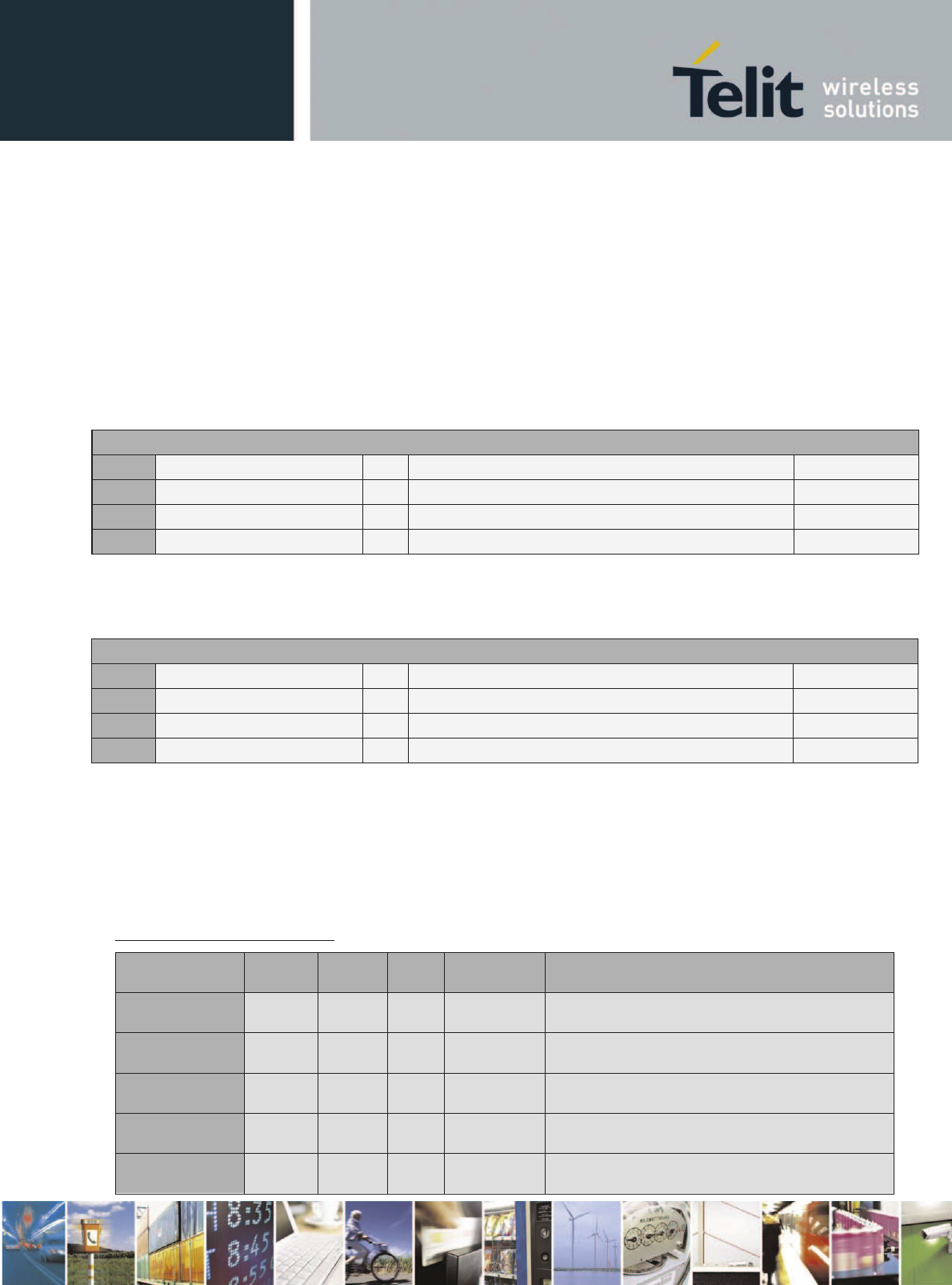

For 1.8V CMOS signals:

Absolute Maximum Ratings - Not Functional

Parameter

xE922-3GR

Min

Max

Input level on any

digital pin when on

-0.3V

+2.16V

Input voltage on

analog pins when on

-0.3V

+2.16 V

Operating Range - Interface levels (1.8V CMOS)

Parameter

xE922-3GR

Unit

condition

Min

Max

V

IH

Input high level

1.3V

2.1V

[V]

V

IL

Input low level

-0.3V

0.5V

[V]

V

OH

Output high level

1.6V

[V]

Ioh= 0.1 mA

V

OL

Output low level

0.2V

[V]

Ioh = -0.1mA

IIL

Low-level input current

1.5

[µA]

no PU/PD

IIH

High-level input current

1.3

[µA]

no PU/PD

RPU/PD

pull up/down resistance

7.2

45

[kΩ]

I_source/sink

GPIO drive strength

2

12

[mA]

Configurable 2,4,8,12 mA

Vdrv_HIGH=1.62V/LOW=0.18V

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 41 of 112

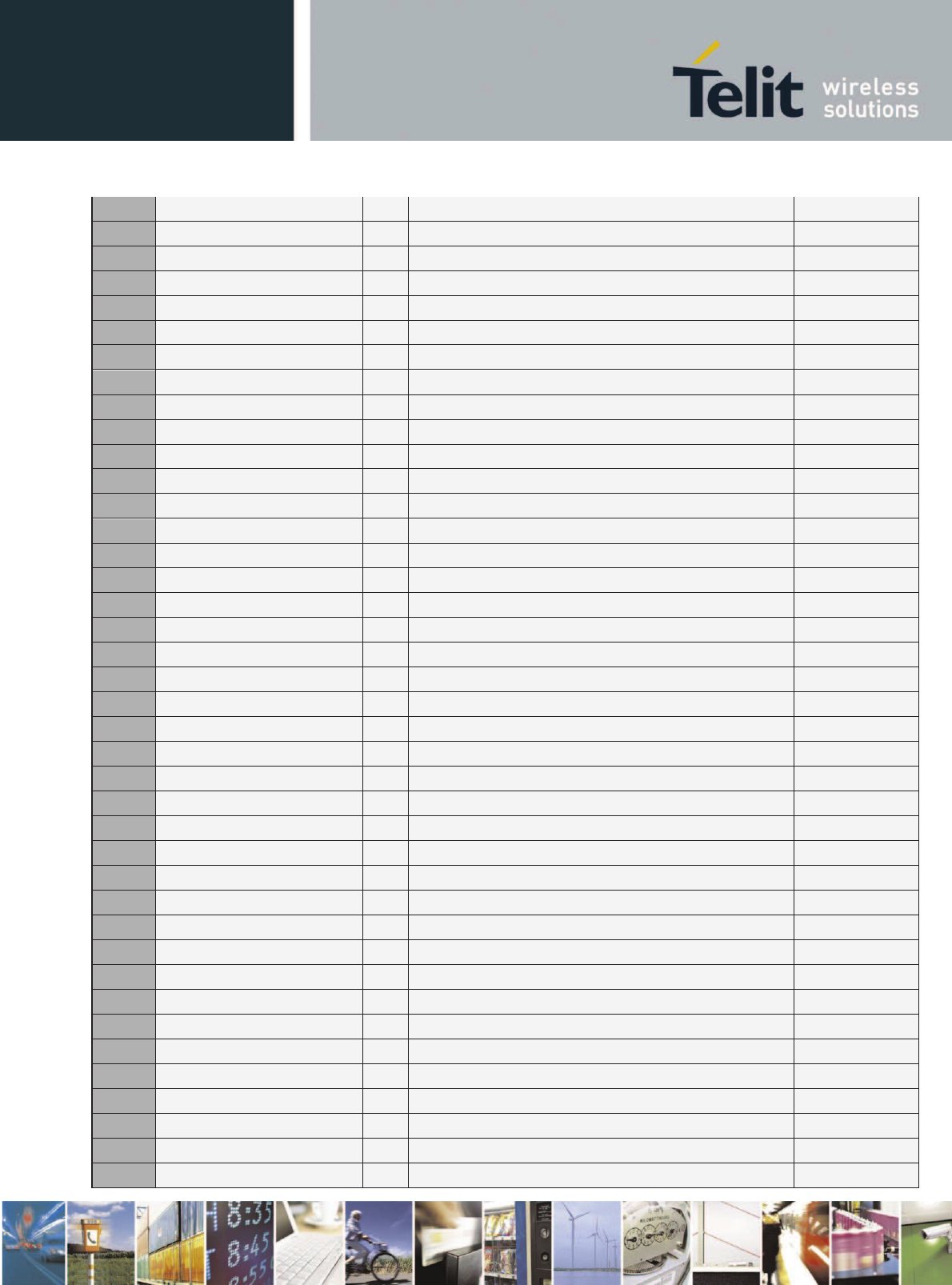

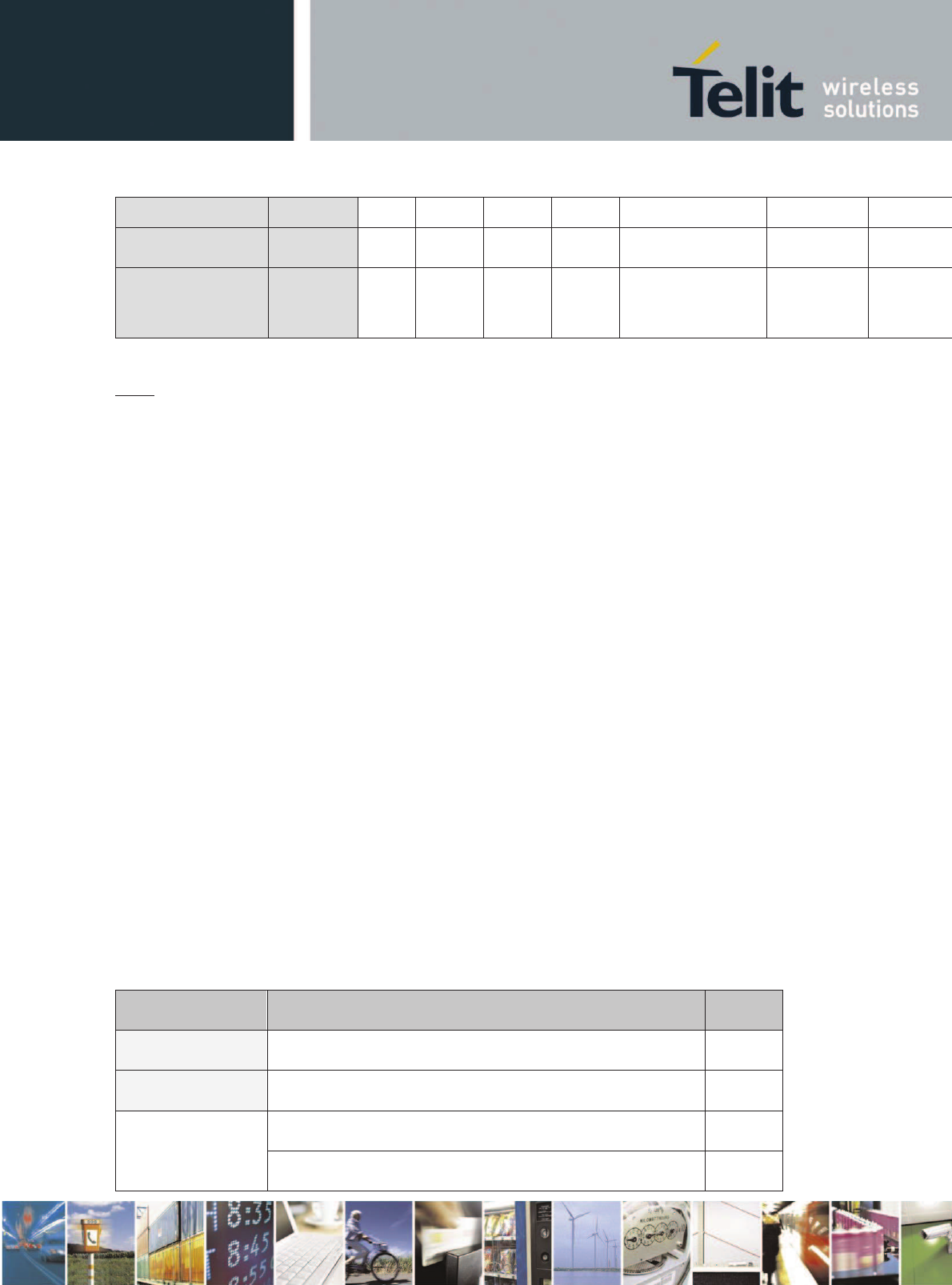

5. Power supply

5.1. Input supply

There are 2 input power supplies defined on the xE922-3GR module,

V_BAT, V_BAT_PA.

V_BAT_PA pin supplies transmit RF front end (RFFE) power amplifiers (PA) of the cellular network

(2G/3G) connection feature of the module.

V_BAT pin supplies the remaining module circuitry, distributed via an internal power management unit

(PMU).

Although defined separately, V_BAT and V_BAT_PA can be connected together. The split implementation

allows for separate power consumption characterization of the RFFE as well as optional noise filtering

network to isolate V_BAT from the typical bursty character of V_BAT_PA in 2G mode operation.

NOTE:

In GSM

/GPRS mode, RF transmission is not continuous and is packed into bursts at a base

frequency of about 216 Hz with relative current peaks as high as about 2 A.

Therefore the power

supply must be designed to withstand these current peaks

(from V_BAT_PA input supply pin)

without big voltage drops; this means that both the electrical design

(current rating and/or

decoupling buffer capacitors)

and the board layout must be designed for this current flow. If

the layout of the PCB is not well

designed, a strong noise floor is generated on the ground. This

will reflect on all the audio paths producing an audible annoying noise at 216 Hz; if the voltage

drops during the peaks, current absorption is too high. The device may even shut down as a

consequence of the supply voltage drop.

xE922-3GR Hardware User Guide

1VV0301272 Rev.0.8 2017-01-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights

Reserved. Page 42 of 112

Both V_BAT_PA and V_BAT are protected by Zener transient voltage suppressor diodes internal the module.

Although the internal transient suppressor also protects for reverse polarized input supply application, its max

power dissipation is limited as well.

For performance specification of this protection please consult the datasheet. (DF3A6.8FUT1 / ON

Semiconductor)

A low ESR buffer capacitor of adequate capacity must be provided on the application main board in order to

cut the current absorption peaks (either from system load or during cellular load TX slots , up to 2 A), taking

into account the sourcing power supply circuitry implementation is limited qua current rating and/or transient

response timing. The buffer capacitor must be selected in order to guarantee at all time V_BAT > BUV

battery under voltage (typical 3.0V).

For information, the total ‘distributed’ capacitance already present inside the module:

· V_BAT_PA : 33uF

· V_BAT : 82uF

5.2. Output supply

5.2.1. Linear voltage regulators

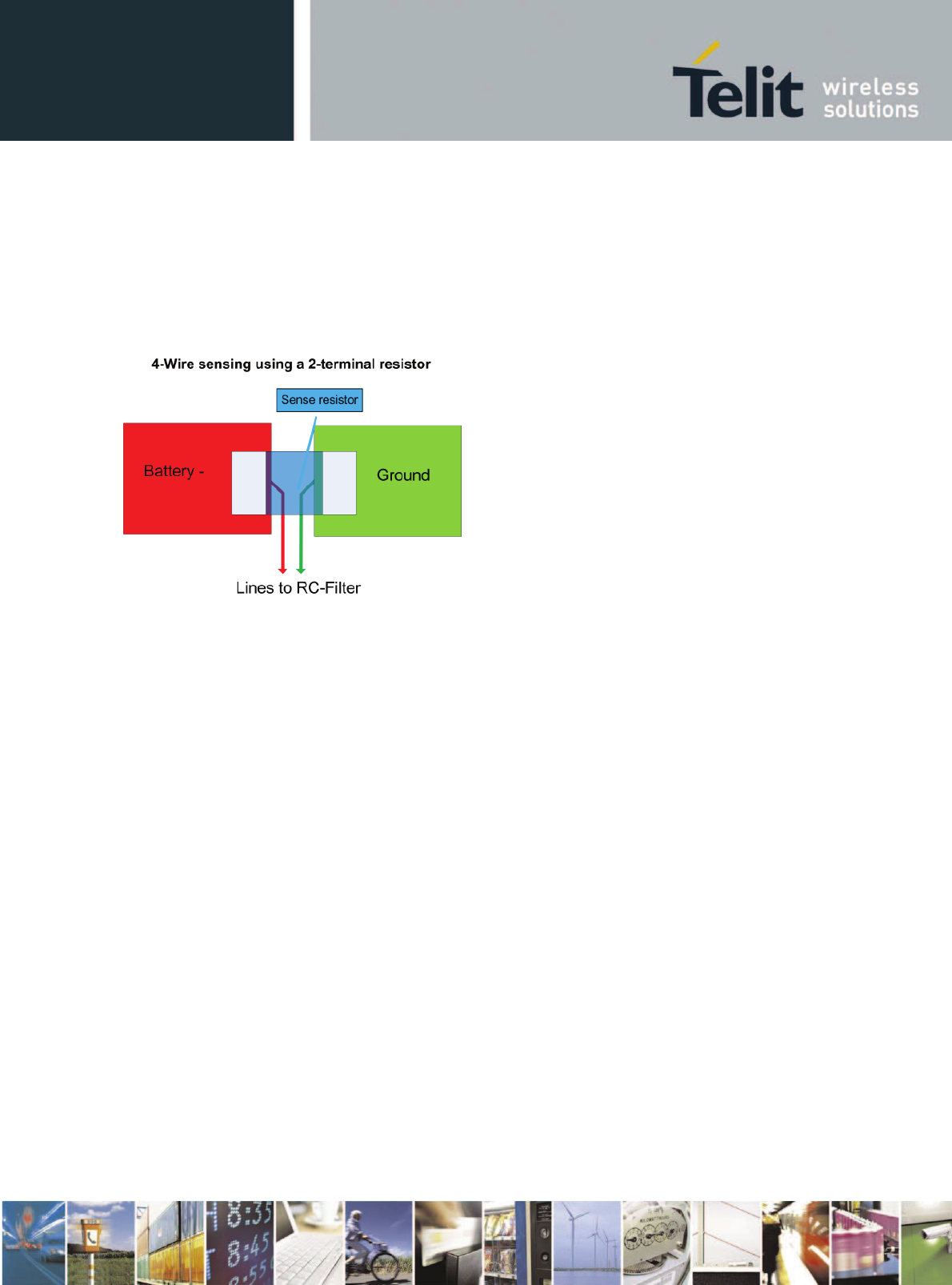

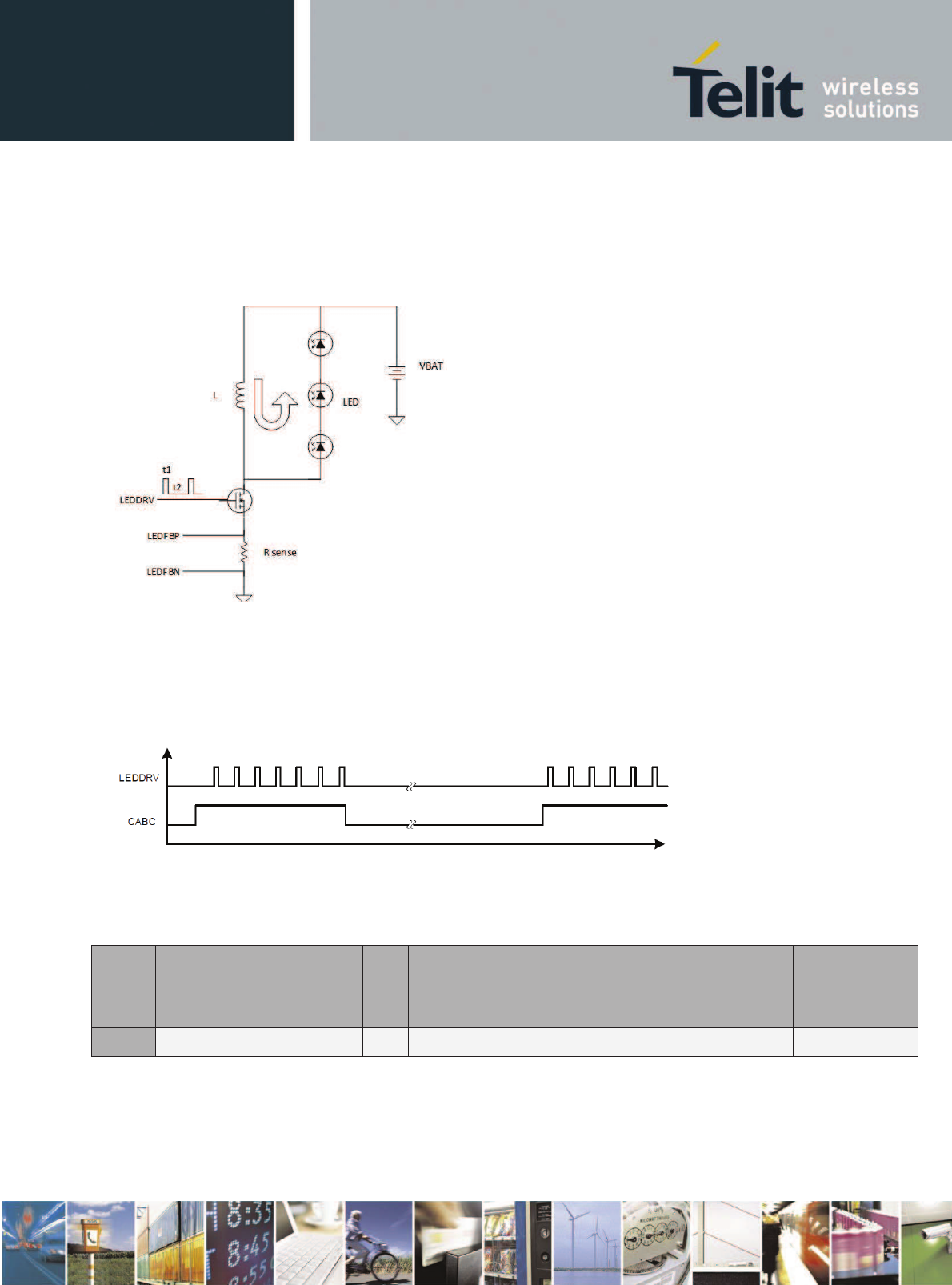

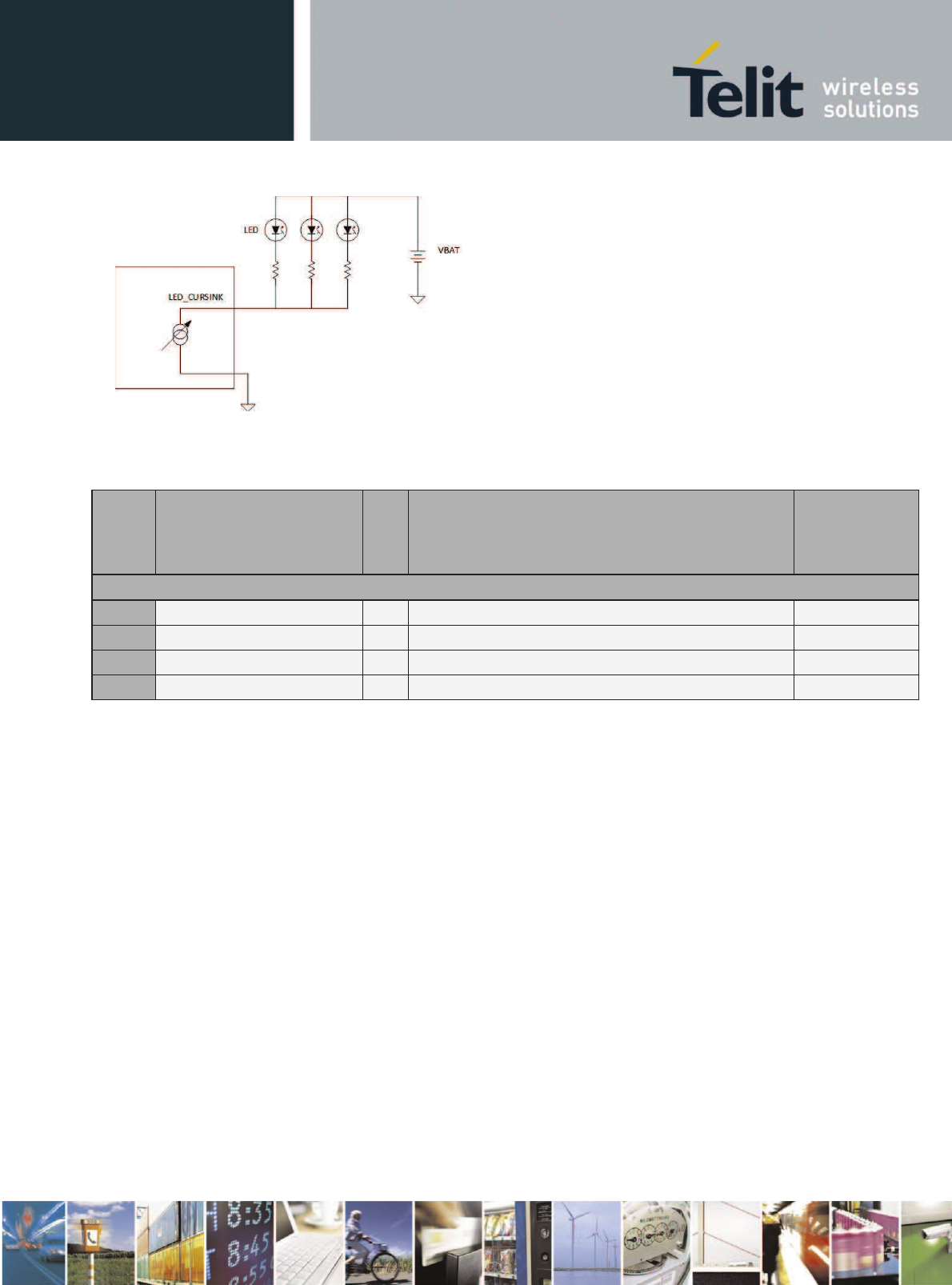

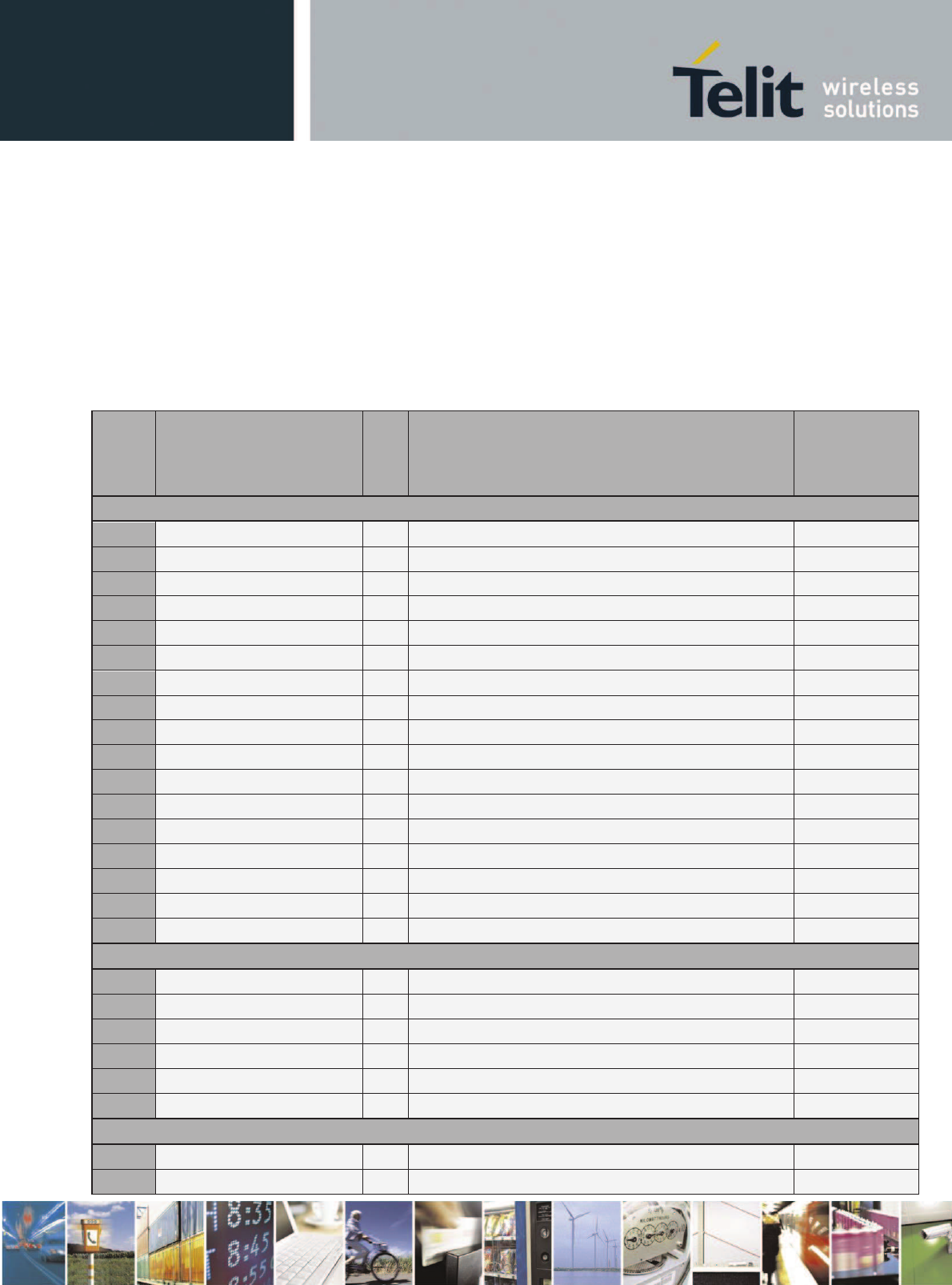

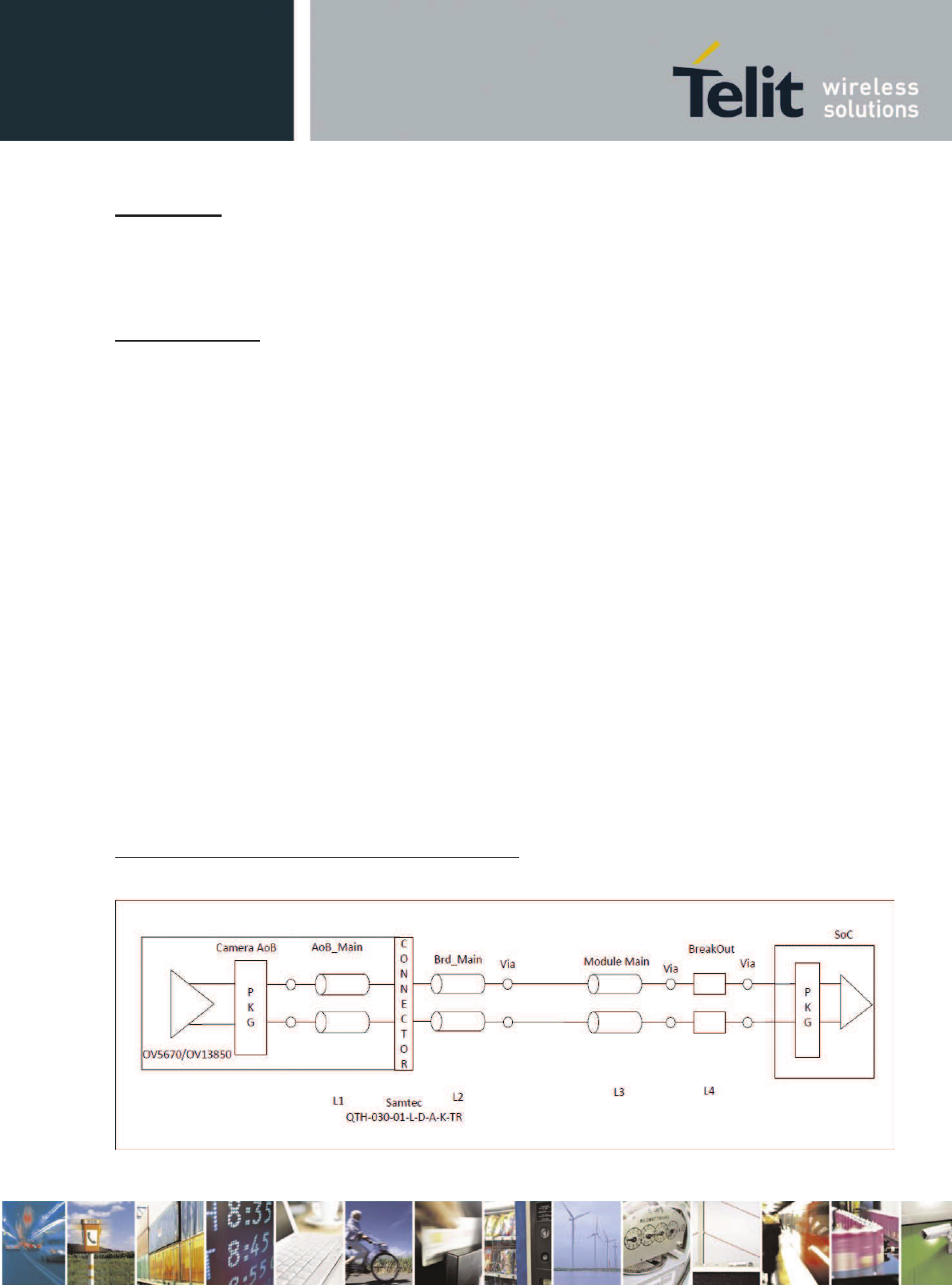

5.2.1.1. VAUX_1P8V