Toshiba Tw40F80 Technical Training Manual Toc

TW40F80 to the manual 9d699d9e-c699-44ff-a762-9b3b908906d0

2014-12-13

: Toshiba Toshiba-Tw40F80-Technical-Training-Manual-131341 toshiba-tw40f80-technical-training-manual-131341 toshiba pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 101 [warning: Documents this large are best viewed by clicking the View PDF Link!]

- Contents

- Section I: Outline 6

- 1. FEATURE 6

- 2. MERITS OF BUS SYSTEM

- 3. SPECIFICATIONS 7

- 4. FRONT VIEW 8

- 5. Rear View

- 6. Remote Control View

- 7. CHASSIS LAYOUT

- 8. CONSTRUCTION OF CHASSIS 12

- section ii: tuner, if/mts/s. pro module

- 1. CIRCUIT BLOCK

- 2. PoP TUNER

- section iii: channel selection circuit

- 1. OUTLINE OF CHANNEL SELECTION CIRCUIT SYSTEM

- 2. OPERATION OF CHANNEL SELECTION CIRCUIT

- 3. MICROCOMPUTER

- 4. MICROCOMPUTER TERMINAL FUNCTION

- 5. EEPROM (QA02)

- 6. ON SCREEN FUNCTION

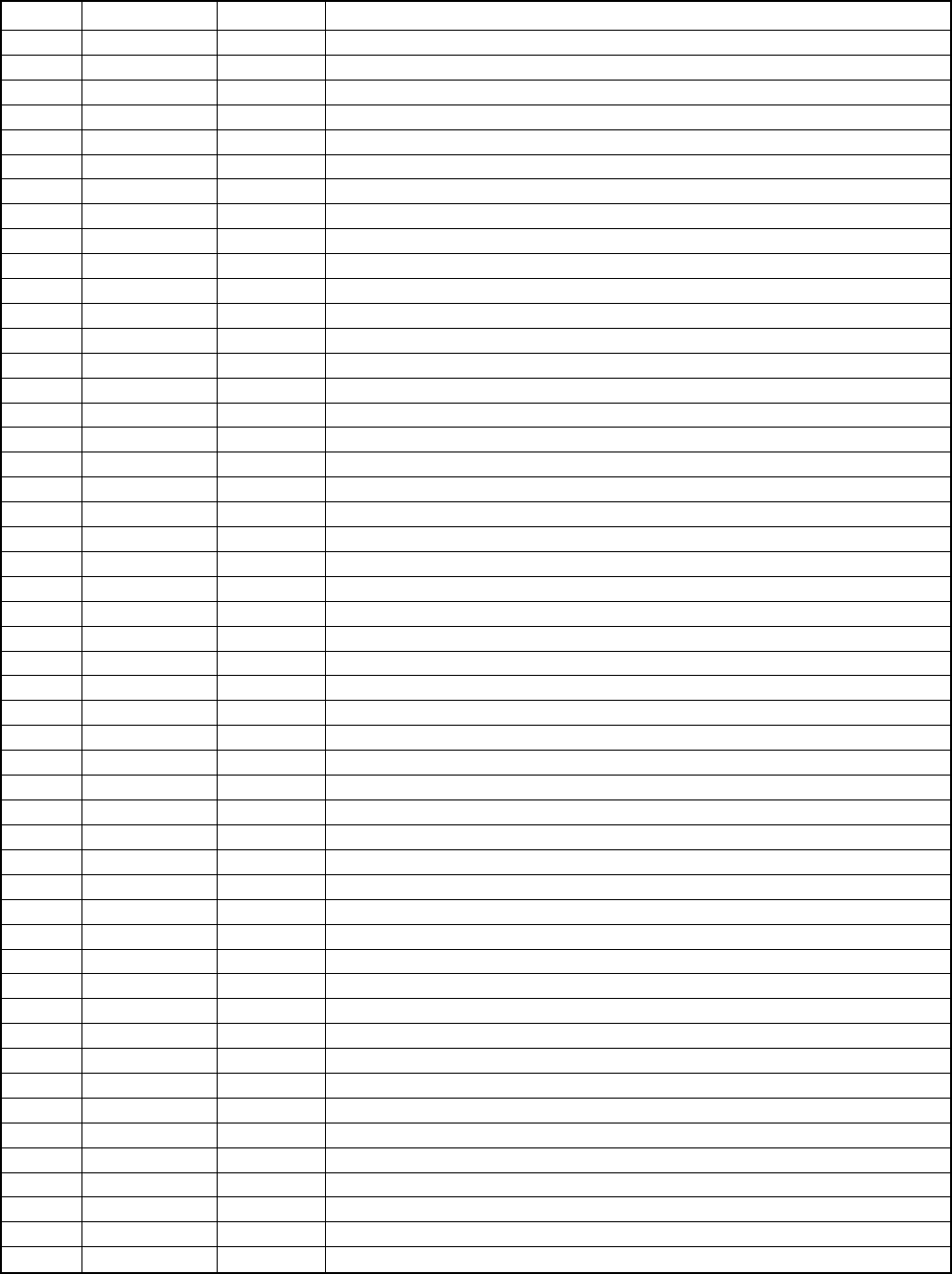

- 7. SYSTEM BLOCK DIAGRAM

- 8. LOCAL KEY DETECTION METHOD

- 9. REMOTE CONTROL CODE ASSIGNMENT

- 10. ENTERING TO SERVICE MODE

- 11. TEST SIGNAL SELECTION

- 12. SERVICE ADJUSTMENT

- 13. FAILURE DIAGNOSIS PROCEDURE

- 14. TROUBLESHOOTING CHART

- section iv: dvd switch circuit

- 1. dvd switch block diagram

- 2. OUTLINE

- section v: wac circuit

- 1. outline

- 2. CIRCUIT OPERATION

- 3. BLOCK DIAGRAM

- 4. WIDE ASPECT CONVERSION CIRCUIT FAILURE ANALYSIS PROCEDURES

- section vi: dual circuit

- 1. Outline

- 2. Principles of Operation

- 3. SYSTEM COMPONENT DIAGRAM OF DUAL UNIT

- 4. Circuit Operation

- 5. TERMINAL FUNCTION, DESCRIPTION AND BLOCK DIAGRAM OF Main IC

- section vii: 3-dimension y/c separator circuit

- 1. outline

- 2. CIRCUIT DESCRIPTION

- section viii: vertical output circuit

- 1. OUTLINE

- 2. V OUTPUT CIRCUIT

- 3. Protection Circuit for V Deflection Stop

- 4. RASTER POSITION SWITCHING CIRCUIT

- section ix: horizontal deflection circuit

- 1. OUTLINE

- 2. HORIZONTAL DRIVE CIRCUIT

- 3. BASIC OPERATION OF HORIZONTAL DRIVE

- 4. HORIZONTAL OUTPUT CIRCUIT

- 5. HIGH VOLTAGE GENERATION CIRCUIT

- 6. High Voltage Circuit

- 7. X-RAY PROTECTION CIRCUIT

- 8. OVER CURRENT PROTECTION CIRCUIT

- section x: deflection distortion correction circuit

- (side dpc circuit)

- 1. DEFLECTION DISTORTION CORRECTION IC (TA8859CP)

- 2. DIODE MODULATOR CIRCUIT

- 3. ACTUAL CIRCUIT

- section xi: digital convergence circuit

- 1. OUTLINE

- 2. CIRCUIT DESCRIPTION

- 3. PICTURE ADJUSTMENT

- 4. Case study

- 5. TROUBLESHOOTING

- 6. CONVERGENCE OUTPUT CIRCUIT

- 7. Convergence troubleshooting chart

TECHNICAL TRAINING MANUAL

N5SS CHASSIS

NTDPJTV05

TW40F80

PROJECTION TELEVISION

Only the different points from the training manual “N5SS chassis” with its file

No. 026-9506 are described on this manual.

For other parts common with “N5SS chassis”, please refer to the original manual

with its file No. 026-9506.

©1997 TOSHIBA AMERICA CONSUMER PRODUCTS, INC.

NATIONAL SERVICE DIVISION

TRAINING DEPARTMENT

1420-B TOSHIBA DRIVE

LEBANON, TENNESSEE 37087

PHONE: (615)449-2360

FAX: (615)444-7520

www.toshiba.com/tacp

Contents

SECTION I: OUTLINE................................................................................................ 6

1. FEATURE.................................................................................................................... 6

2. MERITS OF BUS SYSTEM...................................................................................... 6

3. SPECIFICATIONS..................................................................................................... 7

4. FRONT VIEW ........................................................................................................... 8

5. REAR VIEW ............................................................................................................... 9

6. REMOTE CONTROL VIEW.................................................................................. 10

7. CHASSIS LAYOUT.................................................................................................. 11

8. CONSTRUCTION OF CHASSIS ........................................................................... 12

SECTION II: TUNER, IF/MTS/S. PRO MODULE ................................................ 13

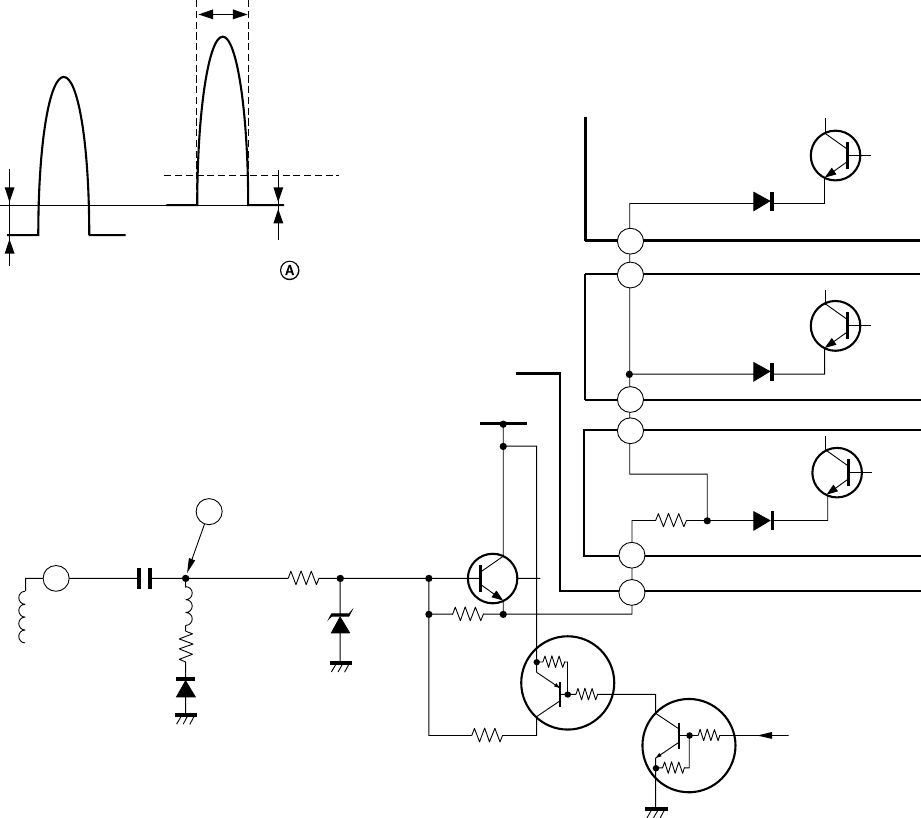

1. CIRCUIT BLOCK ................................................................................................... 13

2. POP TUNER ............................................................................................................. 17

SECTION III: CHANNEL SELECTION CIRCUIT ............................................... 18

1. OUTLINE OF CHANNEL SELECTION CIRCUIT SYSTEM .......................... 18

2. OPERATION OF CHANNEL SELECTION CIRCUIT ...................................... 18

3. MICROCOMPUTER............................................................................................... 19

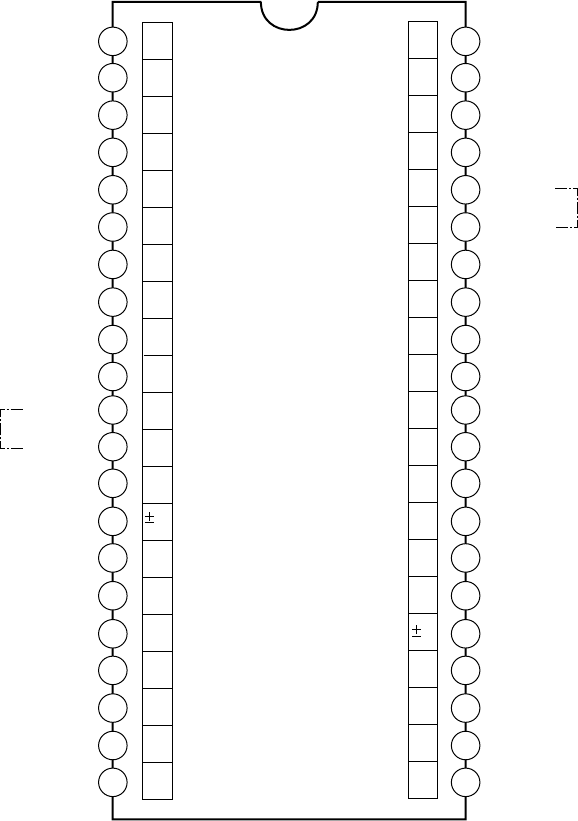

4. MICROCOMPUTER TERMINAL FUNCTION.................................................. 20

5. EEPROM (QA02) ..................................................................................................... 22

6. ON SCREEN FUNCTION....................................................................................... 22

7. SYSTEM BLOCK DIAGRAM................................................................................ 23

8. LOCAL KEY DETECTION METHOD ................................................................ 24

9. REMOTE CONTROL CODE ASSIGNMENT ..................................................... 25

10. ENTERING TO SERVICE MODE ...................................................................... 28

11. TEST SIGNAL SELECTION ............................................................................... 28

12. SERVICE ADJUSTMENT .................................................................................... 28

13. FAILURE DIAGNOSIS PROCEDURE ............................................................... 29

14. TROUBLESHOOTING CHART .......................................................................... 32

SECTION IV: DVD SWITCH CIRCUIT ................................................................. 35

1. DVD SWITCH BLOCK DIAGRAM ...................................................................... 35

2. OUTLINE.................................................................................................................. 36

Contents Page 1

SECTION V: WAC CIRCUIT .................................................................................... 37

1. OUTLINE.................................................................................................................. 37

2. CIRCUIT OPERATION .......................................................................................... 37

3. BLOCK DIAGRAM ................................................................................................. 42

4. WIDE ASPECT CONVERSION CIRCUIT FAILURE ANALYSIS

PROCEDURES......................................................................................................... 43

SECTION VI: DUAL CIRCUIT ................................................................................ 45

1. OUTLINE.................................................................................................................. 45

2. PRINCIPLES OF OPERATION............................................................................. 45

3. SYSTEM COMPONENT DIAGRAM OF DUAL UNIT ...................................... 46

4. CIRCUIT OPERATION .......................................................................................... 47

5. TERMINAL FUNCTION, DESCRIPTION AND BLOCK DIAGRAM OF

MAIN IC.................................................................................................................... 51

SECTION VII: 3-DIMENSION Y/C SEPARATOR CIRCUIT .............................. 58

1. OUTLINE.................................................................................................................. 58

2. CIRCUIT DESCRIPTION ...................................................................................... 58

SECTION VIII: VERTICAL OUTPUT CIRCUIT.................................................. 60

1. OUTLINE.................................................................................................................. 60

2. V OUTPUT CIRCUIT.............................................................................................. 61

3. PROTECTION CIRCUIT FOR V DEFLECTION STOP ................................... 64

4. RASTER POSITION SWITCHING CIRCUIT .................................................... 66

SECTION IX: HORIZONTAL DEFLECTION CIRCUIT .................................... 67

1. OUTLINE.................................................................................................................. 67

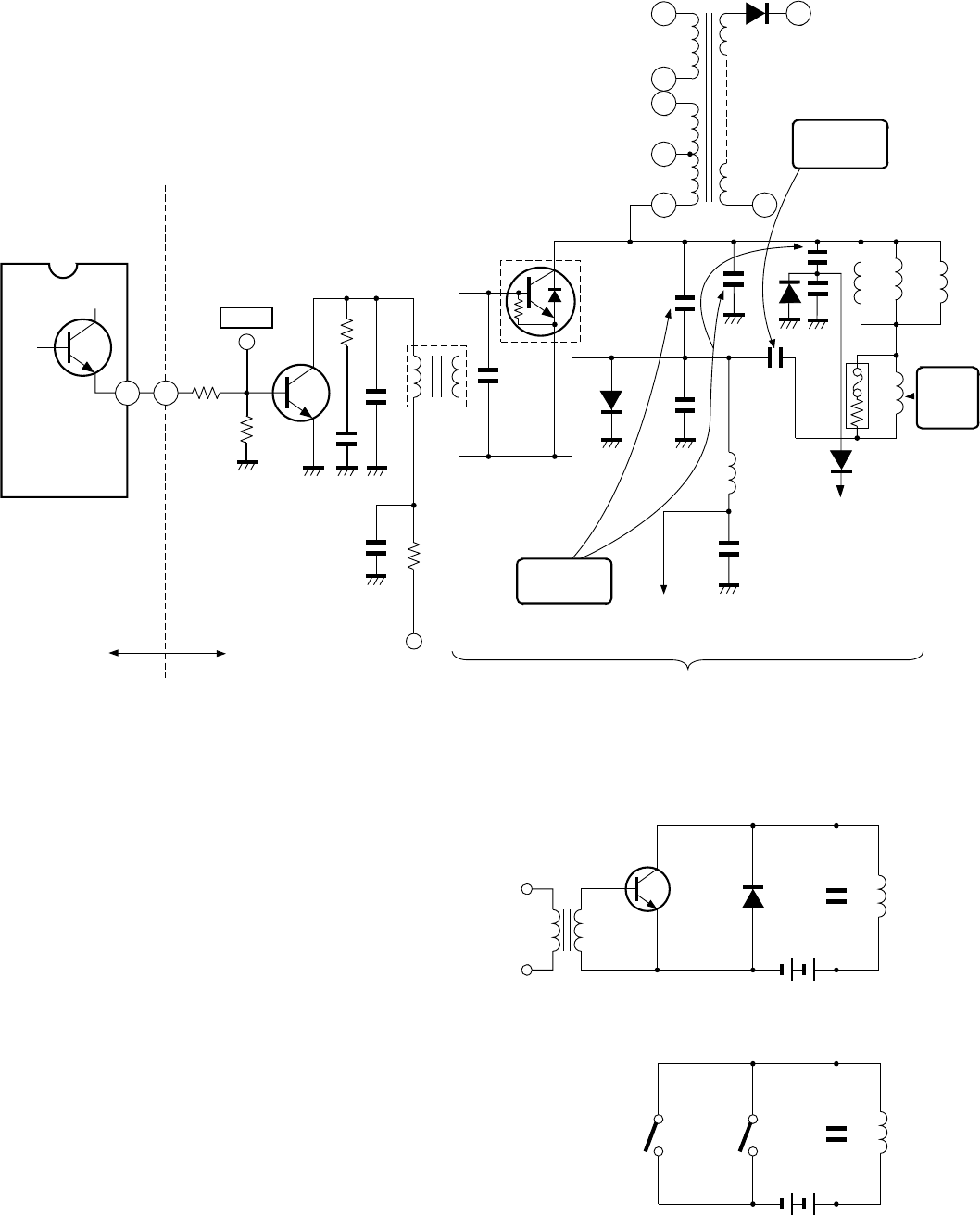

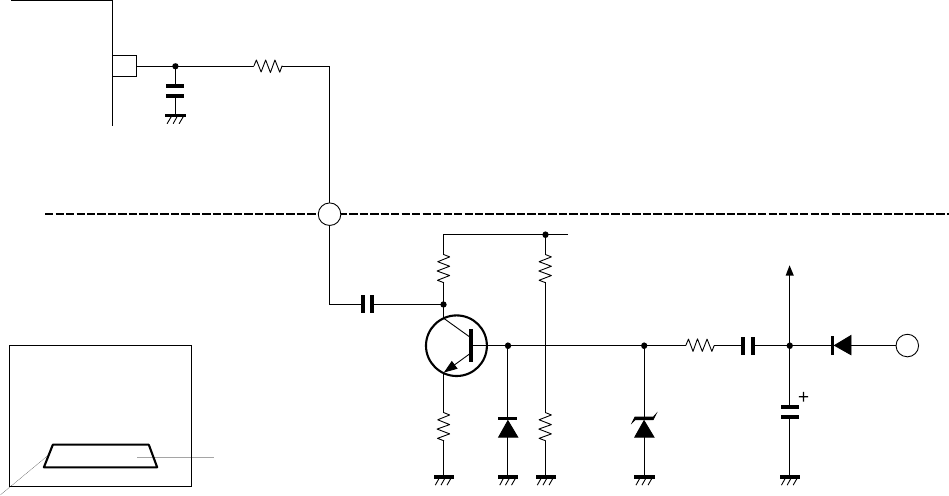

2. HORIZONTAL DRIVE CIRCUIT......................................................................... 67

3. BASIC OPERATION OF HORIZONTAL DRIVE............................................... 67

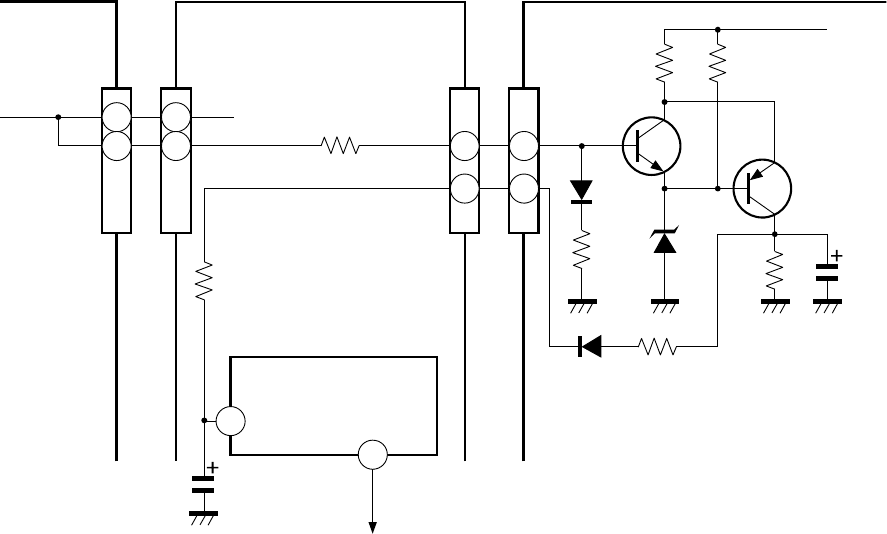

4. HORIZONTAL OUTPUT CIRCUIT ..................................................................... 69

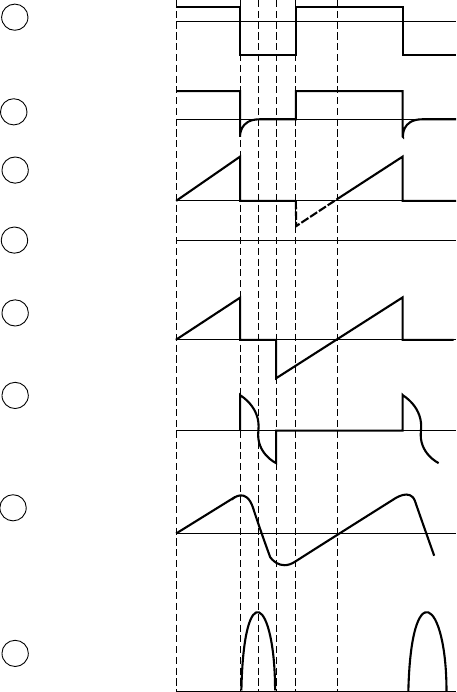

5. HIGH VOLTAGE GENERATION CIRCUIT ....................................................... 76

6. HIGH VOLTAGE CIRCUIT ................................................................................... 78

7. X-RAY PROTECTION CIRCUIT.......................................................................... 80

8. OVER CURRENT PROTECTION CIRCUIT ...................................................... 81

Contents Page 2

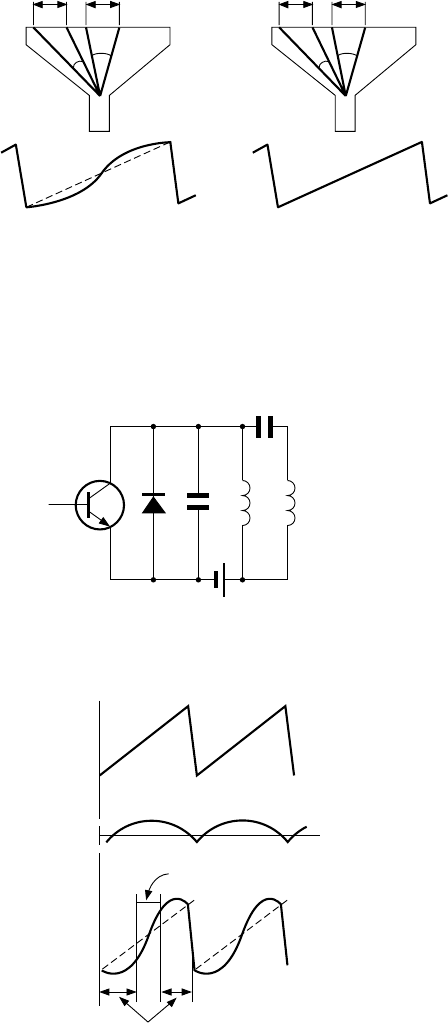

SECTION X: DEFLECTION DISTORTION CORRECTION CIRCUIT

(SIDE DPC CIRCUIT)............................................................................................... 82

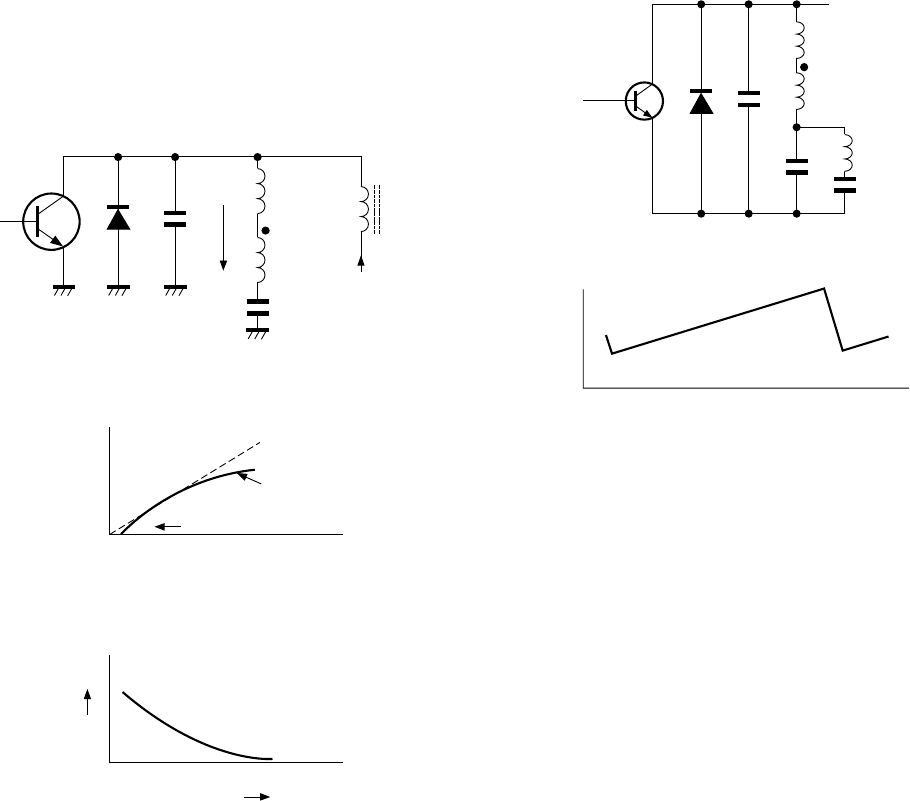

1. DEFLECTION DISTORTION CORRECTION IC (TA8859CP) ....................... 82

2. DIODE MODULATOR CIRCUIT ......................................................................... 83

3. ACTUAL CIRCUIT.................................................................................................. 84

SECTION XI: DIGITAL CONVERGENCE CIRCUIT ......................................... 87

1. OUTLINE.................................................................................................................. 87

2. CIRCUIT DESCRIPTION ...................................................................................... 87

3. PICTURE ADJUSTMENT ...................................................................................... 89

4. CASE STUDY ........................................................................................................... 97

5. TROUBLESHOOTING ........................................................................................... 98

6. CONVERGENCE OUTPUT CIRCUIT................................................................. 99

7. CONVERGENCE TROUBLESHOOTING CHART ......................................... 101

Contents Page 3

OVERALL BLOCK DIAGRAM................................................................................102

5

2. MERITS OF BUS SYSTEM

2-1. Improved Serviceability

Most of the adjustments previously made by resetting vari-

able resistors and/or capacitors can be made on the new chas-

sis by operating the remote control and seeing the results on

the TV screen. This allows seeing adjustments to be made

without removing servicing speed and efficiency.

2-2. Reduction of Parts Count

The use of digital-to-analog converters built into the ICs,

allowing them to be controlled by software, has eliminated

or reduced the requirement for many discrete parts such as

potentiometers and trimmers, etc.

2-3. Quality Control

This central control of the adjustment data makes it easier to

understand, analyze, and review the data, thus improving

quality of the product.

***

1. FEATURE

The TW40F80 is a first PJ-TV with a wide screen aspect

ratio of 16:9 we introduce to North U.S.A. markets.

As the basic chassis N5SS chassis is used.

The future of the model TW40F80 is the use of the N5SS

chassis. This chassis introduces a new bus system, devel-

oped by the PHILIPS company, called the I2C (or IIC) bus.

IIC stands for Inter-Integrated Circuit control. This bus co-

ordinates the transfer of data and control between ICs inside

the TV. It is a bi-directional serial bus consisting of two lines,

named SDA (Serial DATA), and SCL (Serial CLOCK). This

bus control system is made possible through the use of digi-

tal-to analog converters built into the ICs, allowing them to

be addressed and controlled by strings of digital instructions.

The TW40F80 is a first wide TV with a double window sys-

tem we introduce to North U.S.A. markets.

The size of the main and sub screens separated in left and

right on the screen is the same as each other. So it is possible

to enjoy two programs or video and TV program at the same

time.

The sub screen is equipped wit 9 screen search function and

this is very convenient convenient to search a program you

desire.

Note:

Only the different points from the manual

“N5SS Chassis” with its file No. 026-9506

are described on this manual. For other parts

common with “N5SS Chassis”, please refer

to the original manual with its File No. 026-

9506.

SECTION I: OUTLINE

6

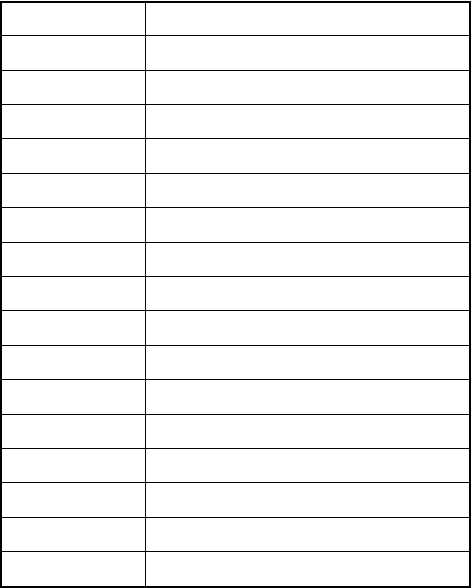

C-Chassis

Model TW56F80 TW40F80 TP61F90 TP61F80 TP55F80 TP55F81 TP50F90 TP50F60 TP50F61 TP50F50 TP50F51

CRT 7" 7" 7" 7" 7" 7" 7" 7" 7" 7" 7"

CRT Source Hitach Hitach Hitach Hitach Hitach Hitach Hitach Hitach Hitach Hitach Hitach

Remote H/U Intell Univ Intell Univ Univ Univ Intell Univ Univ. A-Univ A-Univ

RMT Keys 52 key 36 key 52 key 36 key 36 key 36 key 52 key 36 key 36 key 42 key 42 key

PIP 2-TN 2-TN 2-TN 2-TN 2-TN 2-TN 2-TN 2-TN 2-TN 1-TN 1-TN

Dolby Surr ProLgc ProLgc Dy-Sur Dy-Sur Dy-Sur ProLgc

Surround Dsp4Ch ●Dsp4Ch Dsp4Ch Dsp4Ch Dsp4Ch Dsp4Ch ●●●●

SAP ●●●●●●●●●●●

Cyclone

SBS ●●●●●●●●●●●

Audio (W) 28W 28W 28W 28W 28W 28W 28W 28W 28W 28W 28W

Center +20W 20W 20W

Rear +20W 20W 20W 20W 20W 20W

Comb-Filter 3D-Y/C 3D-Y/C 3D-Y/C 3D-Y/C DIG DIG DIG DIG DIG DIG DIG

DQF ●●●●

Scan-Modul ●●●●●●●●●●●

VCC ●●

Black-Expan ●●●●●●●●●●●

Color-D.E ●●●●●●●●●●●

Pic-Prefer ●●●●●●●●●●●

Color-Temp ●●●●●●●●●●●

Flesh-Tone ●●●●●●●●●●●

Nois-Reduce ●●●●●●●●●●●

Hori-Resolu 800 800 800 800 800 800 800 800 800 800 800

Fav-Channel ●●●●●●●●●●●

Ch-Label ●●●●●●●●●●●

3-Language ●●●●●●●●●●●

Clock ●●●●●●●●●●●

Ch-Lock/Off ●●●●●●●●●●●

C.Caption ●●●●●●●●●●●

EDS ● ●●● ●●●●

New-OSD ●●●●●●●●●

S/Sight ●● ●

S-Video In 1+1 1+1 1+1 1+1 1+1 1+1 1+1 1+1 1+1 1 1

AV-In/Out 1+2/1 1+2/1 1+2/1 1+2/1 1+2/1 1+2/1 1+2/1 1+2/1 1+2/1 2/1 2/1

Front-Term ●●●●●●●●●

A(Var)-Out ●●●●●●●●●●●

2RF-Term ●●●●●●●●●

SPK-Term ●●●●●●●●●●●

PIP Audio ●●

C-Ch-Input ●●●

E/Jack

S/S-Jack ●● ●

IR-B & 75W●● ●

Adapter ●●●●●●●●●●●

Rod-Antenna

SPK-Box ●●● ●

EZ RMT ●● ●

Cabinet TW56D90 40W30E TP61E90 TP61E80 TP55E80 TP55E81 New New New New New

3. SPECIFICATIONS

GENERALSOUNDPICTURE

OTHERS

TERMINALACCE

*

7

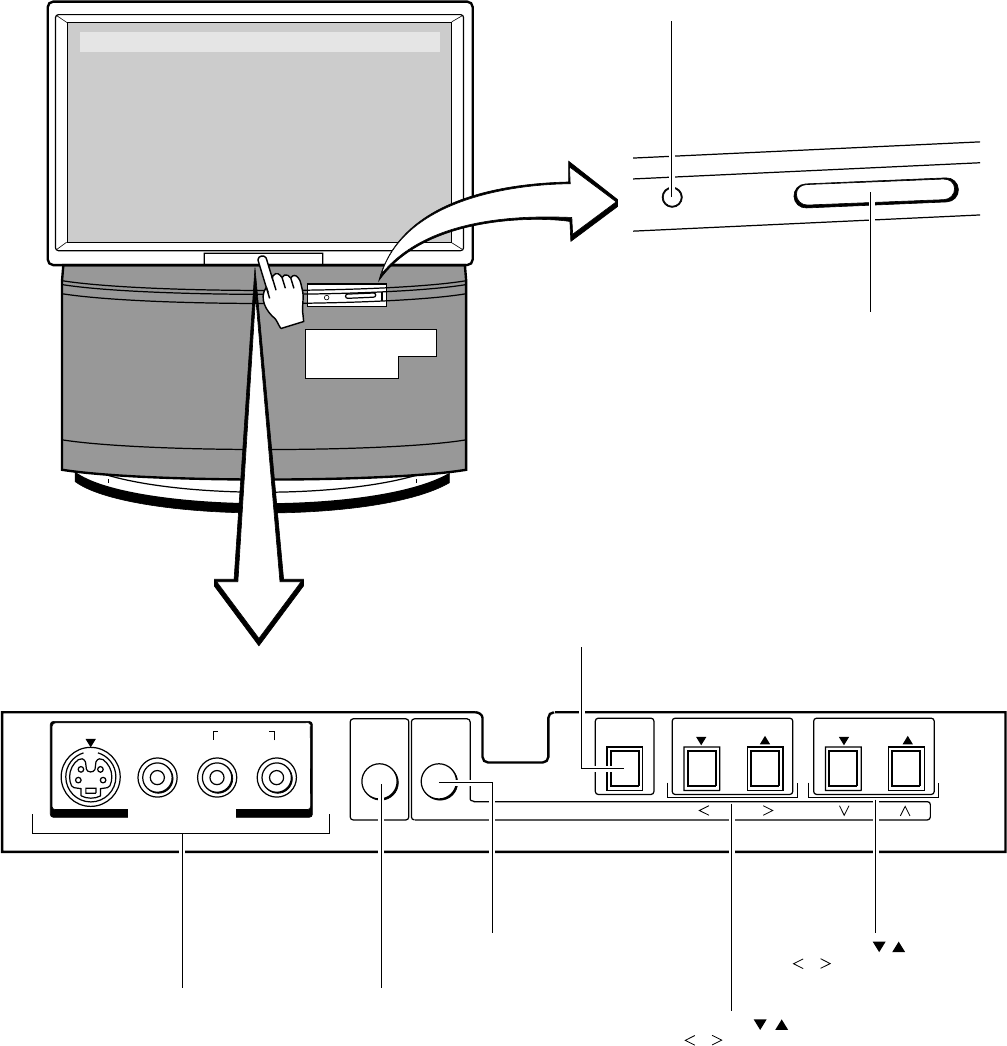

4. FRONT VIEW

Fig. 1-1

Note: [No] Owner's manual page.

POWER

DEMO

MENU

ANT/

VIDEO

ENTER

VOLUME CHANNEL

POWER indicator

POWER button

Press to open

the door.

Behind the door

ANT / VIDEO button **

ENTER button

S-VIDEO VIDEO

L/MCNO R

AUDIO

IN-VIDEO 3

VIDEO 3 INPUTS DEMO button

MENU button CHANNEL / buttons

/ buttons

VOLUME / buttons

/ buttons

8

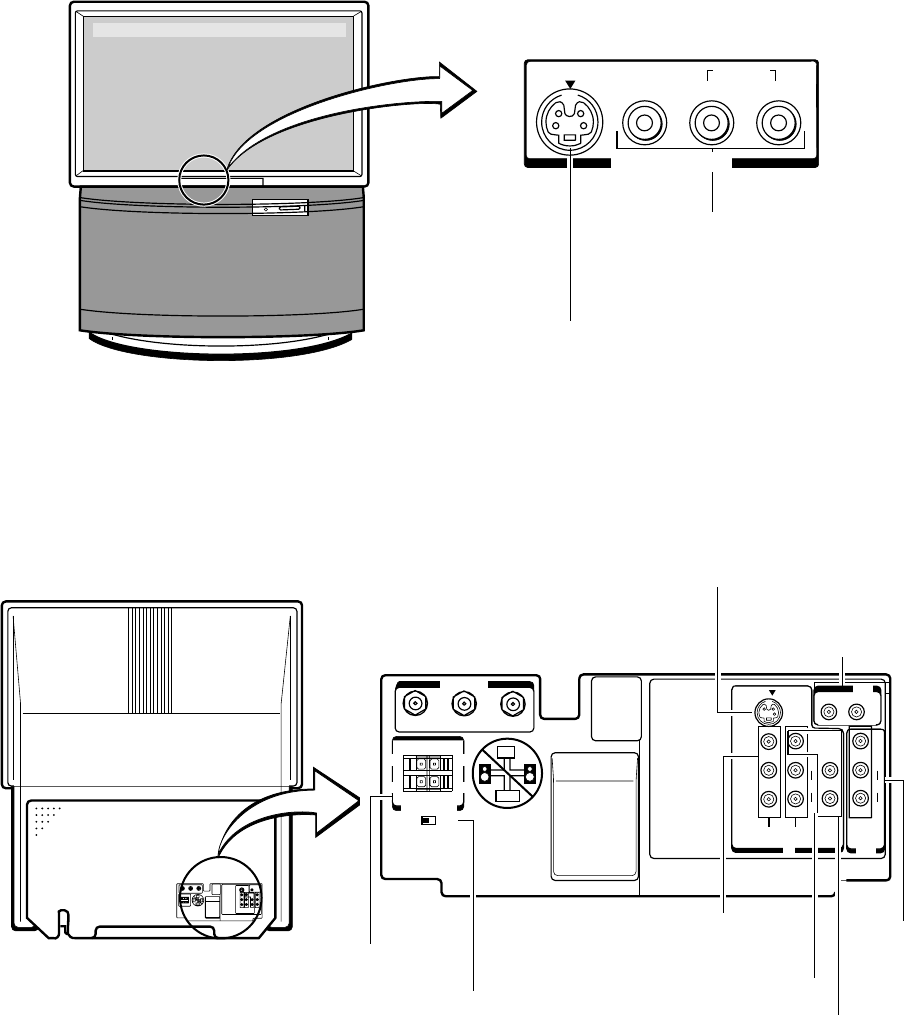

5. REAR VIEW

S-VIDEO VIDEO

L/MCNO R

AUDIO

IN-VIDEO 3

VIDEO / AUDIO INPUT jacks (VIDEO 3)

S-VIDEO INPUT jack (VIDEO 3)

Behind the door

TV front

Fig. 1-2

EXT SPEAKER

EXT INT

ANT (75 ½)

TV

AMP

L

VIDEO/AUDIO

R

VIDEO1

VIDEO

AUDIO

L

Y

S-VIDEO

C4

AUDIO

R

VIDEO

AMP

R

VIDEO

VIDEO2 DVD

L

RVAR

ACC

AMP

NCUT

MAIN SPEAKER

(+)

(Ð)

(+)

(Ð)

EXTERNAL

SPEAKER

terminal MAIN

SPEAKER

switch

VIDEO / AUDIO

INPUT jacks

(VIDEO 1)

VIDEO / AUDIO

INPUT jacks

(VIDEO 2) DVD INPUT

jacks

VIDEO /

AUDIO

OUTPU

T

jacks

S-VIDEO INPUT jack

(VIDEO 1)

VARIABLE AUDIO

OUTPUT jacks

TV rear

Fig. 1-3

9

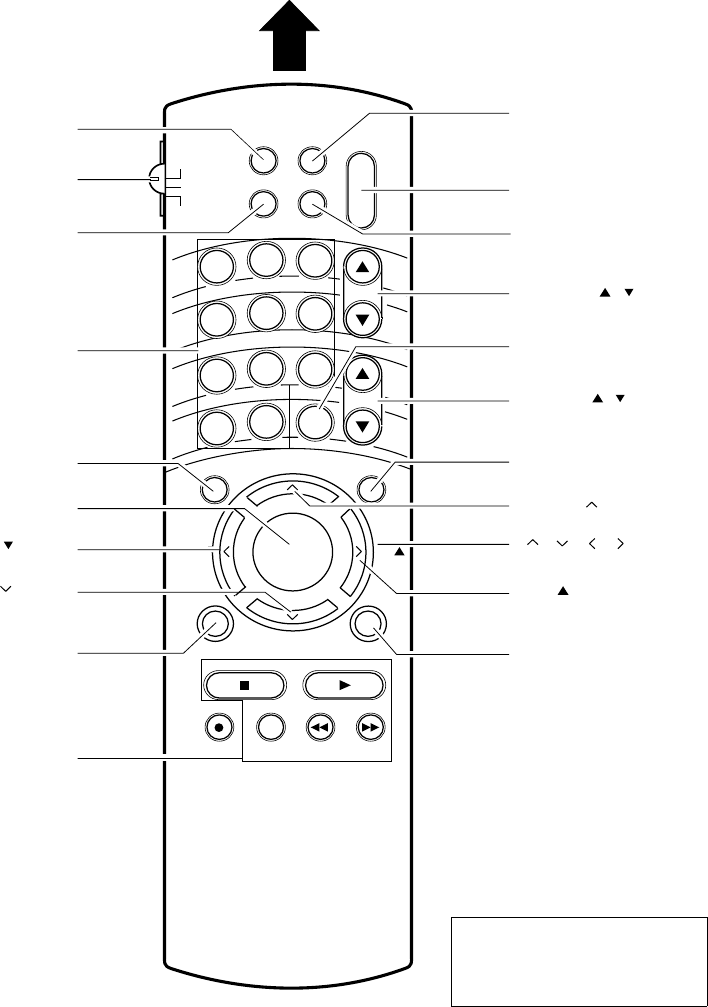

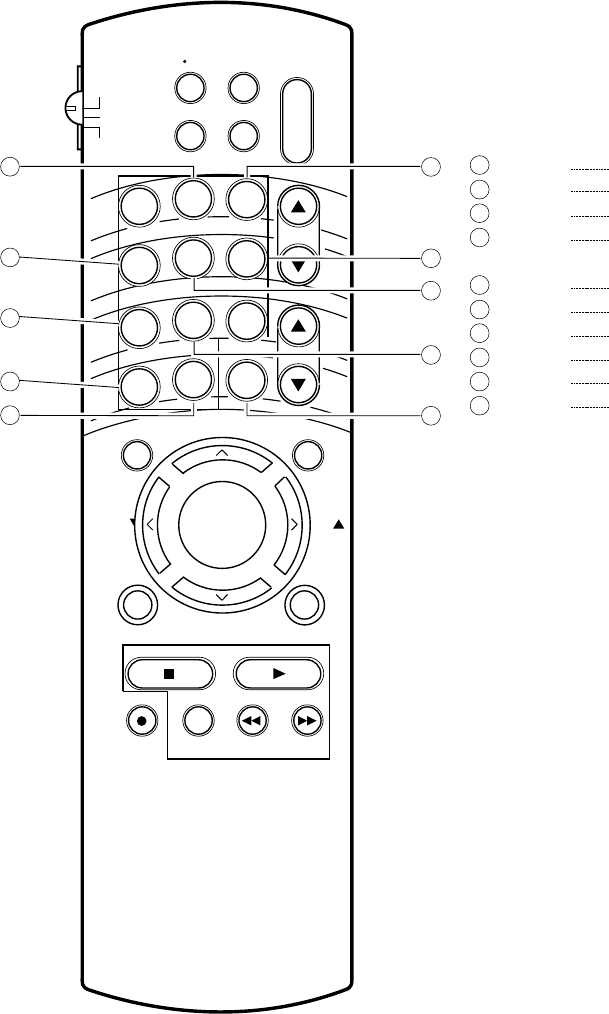

6. REMOTE CONTROL VIEW

ADV/

POP CH

ADV/

POP CH

23

56

89

4

7

¥

0

ENT

PIC -SIZE

TV/VIDEO

RECALL

POWER

CH

VOL

CH RTN

EDS MENU

FAV FAV

EXITRESET

STOP SCURCE PLAY POP

REC TV/VCR REW FF

CH SEARCH

STILL SWAP

MUTE

1

ENTER

TOSHIBA

RECALL* [ 26 ]

POWER [ 20 ]

MUTE* [ 26 ]

CHANNEL / [ 25 ]

CH RTN* [ 26 ]

VOLUME / [ 25 ]

MENU [ 18 ]

POP CH * [ 40 ]

///[ 18 ]

RESET * [ 33 ]

POP functions* [40]

(For " TV " and " CABLE " positions)

POP CH * [ 40 ]

FAN * [ 46 ]

ENTER [ 19 ]

EDS* [ 27 ]

Channel Number* [ 25 ]

TV / VIDEO* [ 55 ]

TV / CABLE / VCR switch [ 15 ]

Set to " TV " to control the TV.

TIMER* [ 38, 39 ]

EXIT * [ ON ]

Owner's Manual page

* These function do not have

duplicate locations on the TV.

They can be controlled only by

the Remote Control.

FAN * [ 46 ]

Aim at the remote sensor on the TV

100

TV

CABLE

VCR

Fig. 1-4

Note: [No] Owner's Manual page.

10

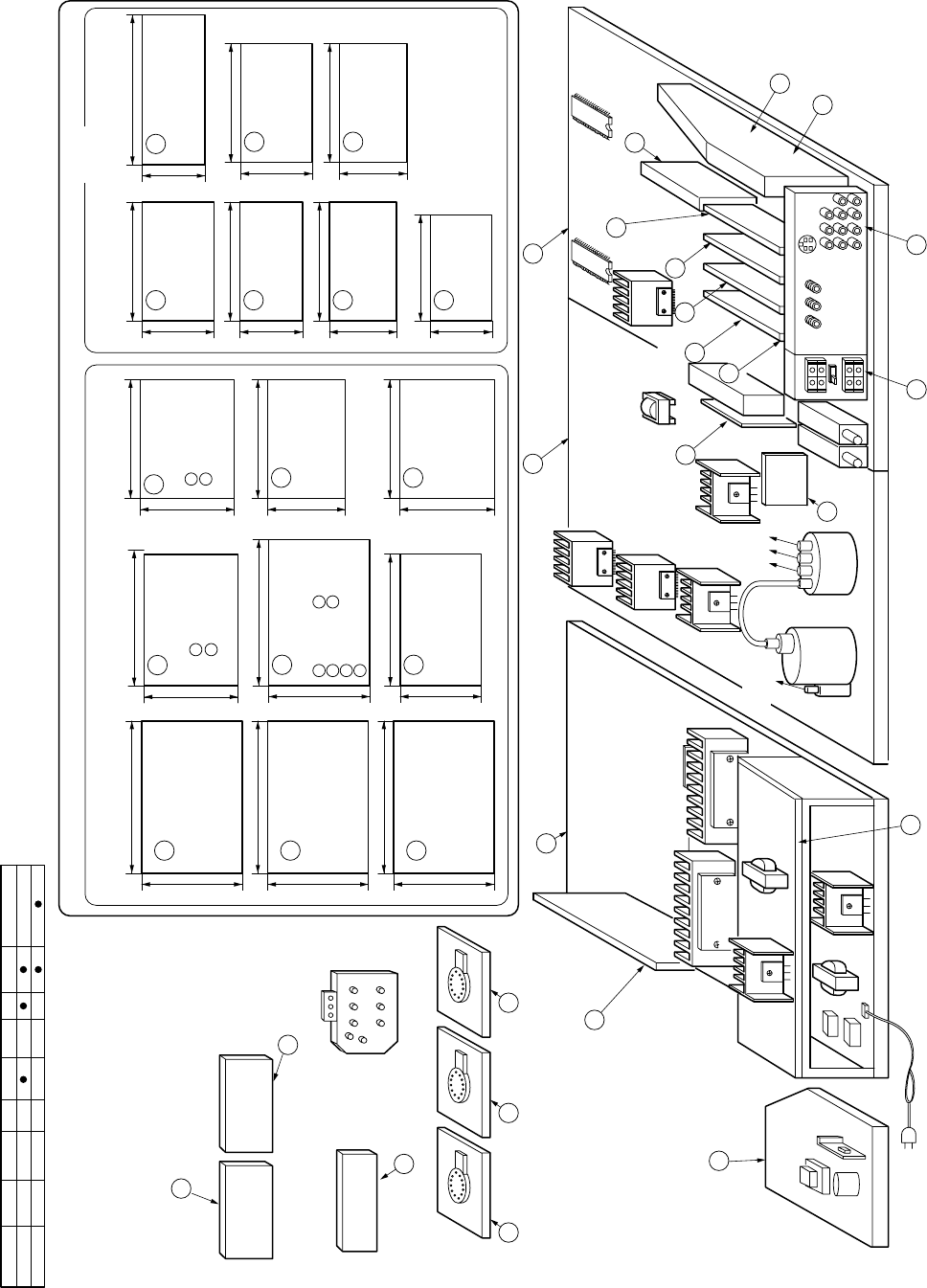

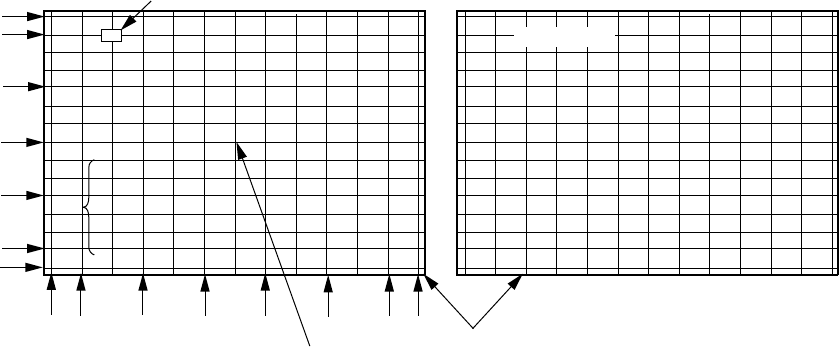

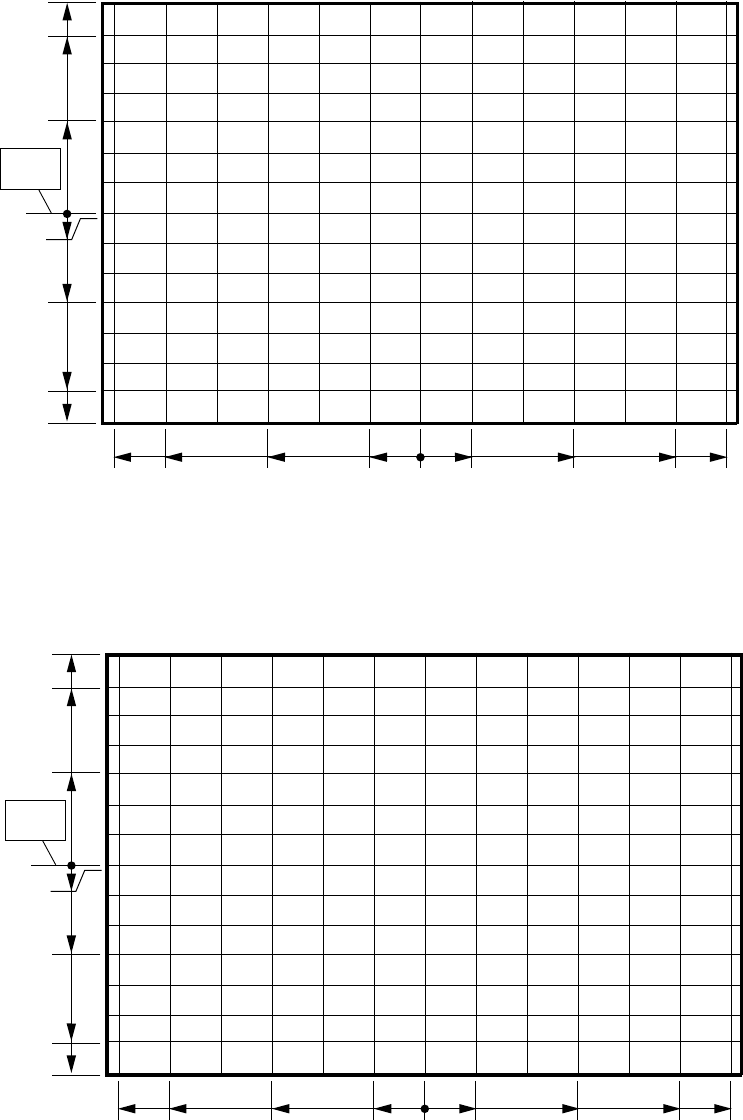

7. CHASSIS LAYOUT

-3 :

CRT-D(B)

5

-2 :

CRT-D(G)

5

-1 :

CRT-D(R)

5

- 6 : SVM

5FOCUS PACK

- 4 : FRONT-LED

5

- 5 : FRONT-CON

5

: POWER 1

6

F.B.T

J-BOX

To CRT

To FOCUS

PACK

330

294

: MAIN

1

1pc

330

294

: DEFELECTION

2

1pc

330

294

: CONV / POWER2

3

1pc

249

165

: AV.EXT SPK

4

1pcs

249

165

: POWER 1

6

1pc

330

249

:

CRT-1pcs

D/FRONT/SHV

5

4

-1: A.V

4

-2: SPEAKER

5

-1: CRTÐD ( R )

5

-2: CRTÐD ( G )

5

-3: CRTÐD ( B )

5

-4: FRONT LED

5

-5: FRONT CON

5

-6: SVH

7

-1: NEW OSD

7

-2: FRONT SURROUND

249

165

: NEW OSD/

FRONT SURROUND

7

2pcs

249

165

: SW DVD

8

4pcs

249

249

: POWER S.S

9

2pcs

242

160

: DIGITAL

CONVER

10

2pcs

CHIP DOUBLE FACED

TW56F80 ONLY

242

139

:DUAL

11

2pcs

CHIP DOUBLE FACED

242

155

:3D Y/C

12

2pcs

CHIP DOUBLE FACED

189

139

:MAC

13 4pcs

CHIP DOUBLE

FACED

330

139

:AUDIO LIVE

14

6pcs

CHIP SINGLE FACED

242

126

:SIARSIGHT

15

1pcs

CHIP DOUBLE FACED

242

113

:DOLBY PRO

16

2pcs

CHIP DOUBLE FACED

MODE1

TW40F80

TW56F80

TUNER DOLBY DSP F.SUR COHB FDS N.OSD STARSIGHT

2

2PRO 4CH

3DYC

3DYC

POWER STARSIGHT

(TW56F80 ONLY)

9

: DIGITAL

CONVER

10

: CONVERTER/POWER 2

3

REAR ANP

(TW56F80 ONLY)

CENTER AMP

(TW56F80 ONLY)

: SW DVD

8

- 3 : DPC

4

- 2 : SPEAKER

4- 1 : A/V

4

DOLBY

PRO

16

-2:

FRO.

SURR

7

YCS

12 - 6

: DUAL

11

: AUTOLIVE

14

:WAC

13

: MAIN

1

: DEFLECTION

2

: STARSIGHT

15

- 1: NEW OSD

7

TW56F80 ONLY

TW56F80 ONLY

(chip)

PC BOARD

Fig. 1-5

11

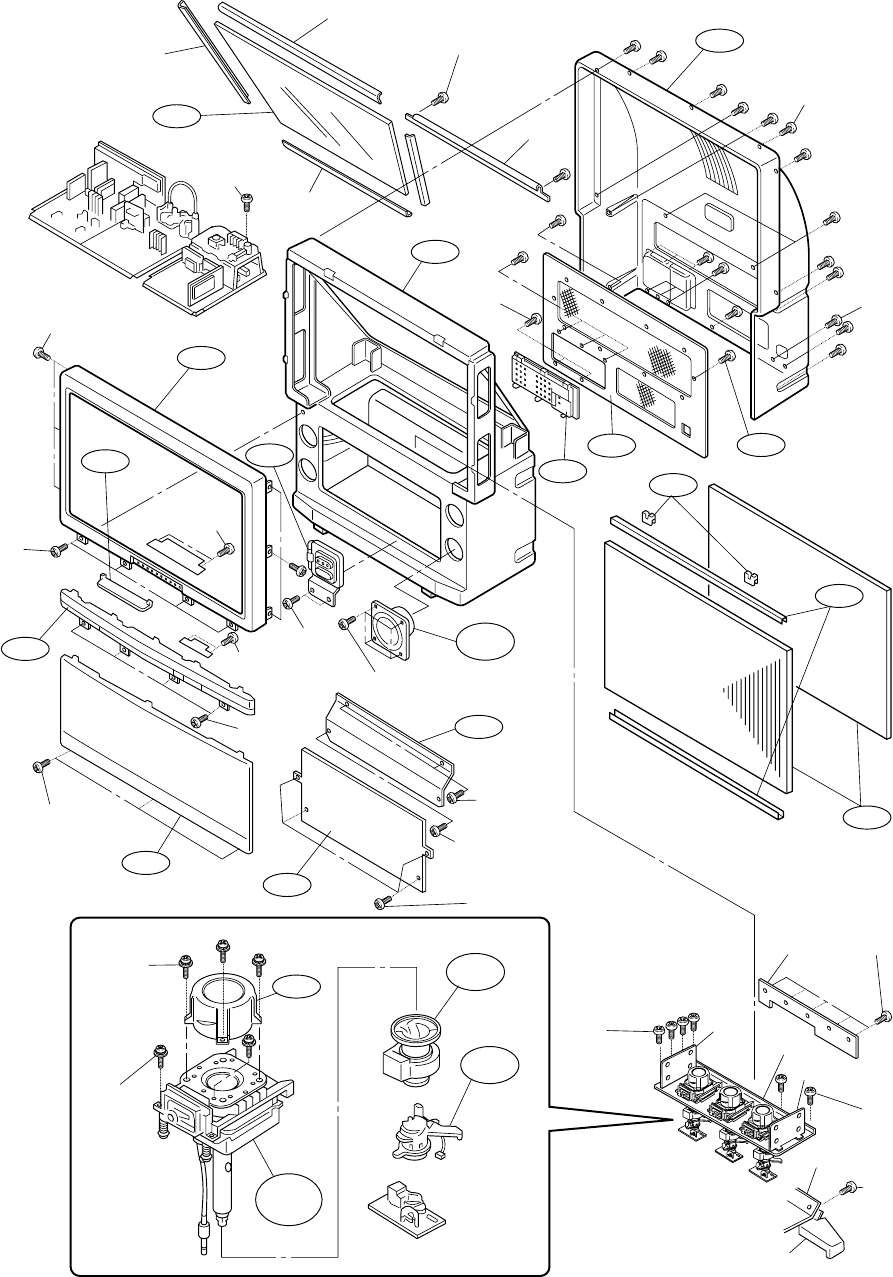

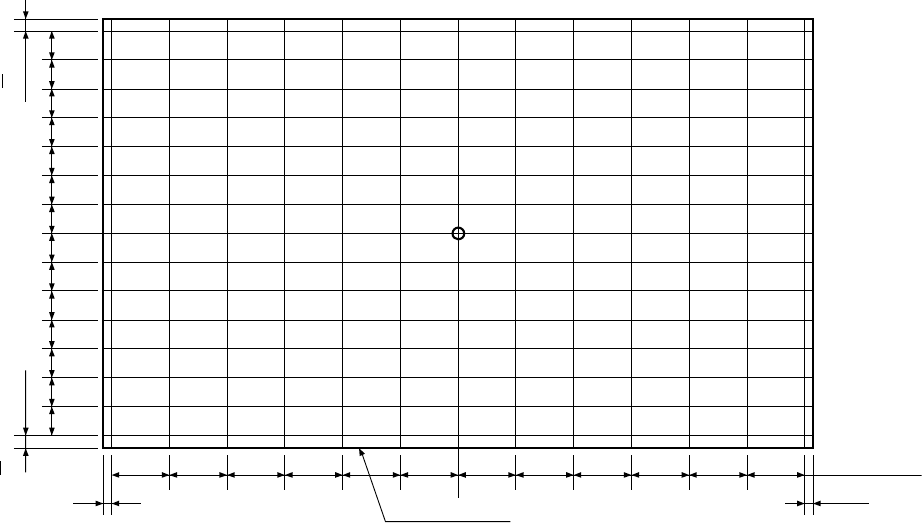

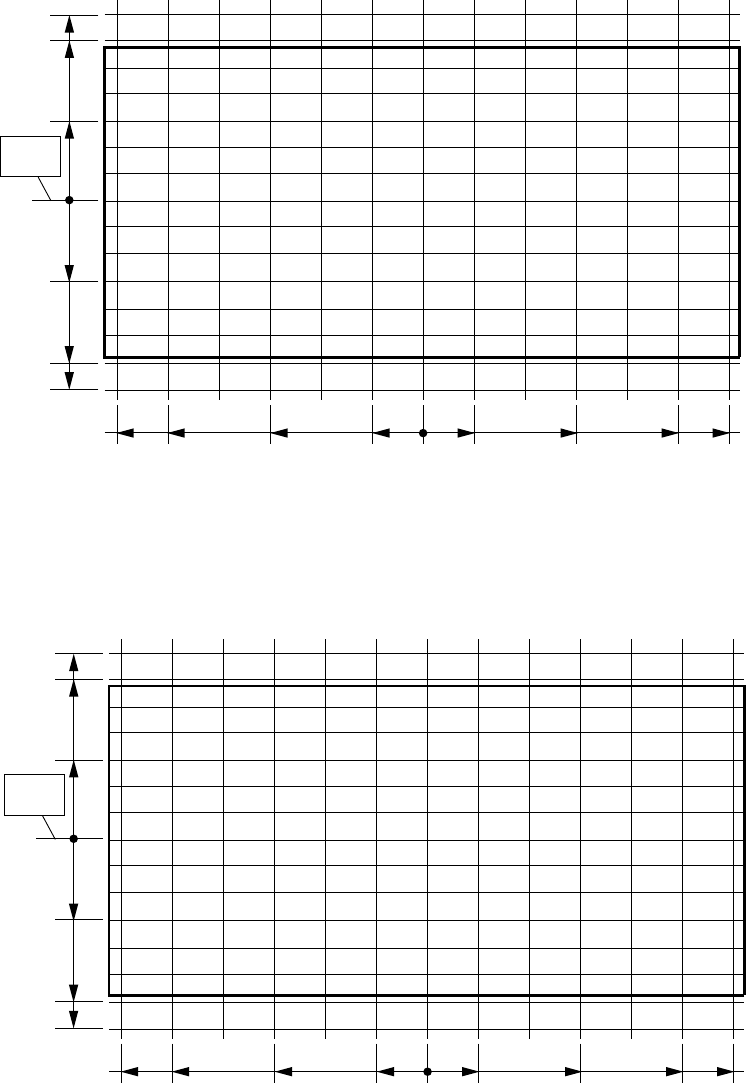

8. CONSTRUCTION OF CHASSIS

A110

A110B

2pcs

K601

A520

PP 5x18

4pcs

A110A

A126

A505

BIDT2

4x12 2pcs

A101

A401

A522

BIDT2

4X12 18pcs

A517

A353

A517

PBI 4X16

8pcs

B202

A351

A512

BIDT2

4x12 6pcs

A201

A902 Z410

A

502

PMM 4x16

4

pcs

A521

BRT TBS 4x16

2pcs

W661~

W664

PMM 4x16

2pcs

A506

BRB TBS

4x16 4pcs

A508

BIDT2

4x12 2pcs

A523

PMM 4x16

2pcs

A509

BTA 4x16 4pcs

A106

A102

A501

BTA 4x16 16pcs

A202

A516

PMS 3.8x28

3pcs

A515

PMM 4X16

4pcs

A205

A127

A128

K511

A519

BIDT2

4x12

5pcs

A107

A104

A105

A508

BIDT2

4x12

4pcs

A513

BIDT2

4x12

A104

A108

A105

A503

PMM

4x16

8pcs

L462~

L464

L472~

L474

K103

A511

PP4x14

4pcs

A510

BRBTB

5x16

4pcs

V901R

V902G

V903B

Fig. 1-6

12

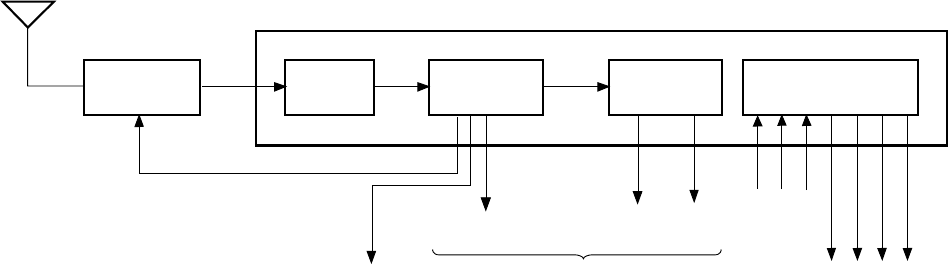

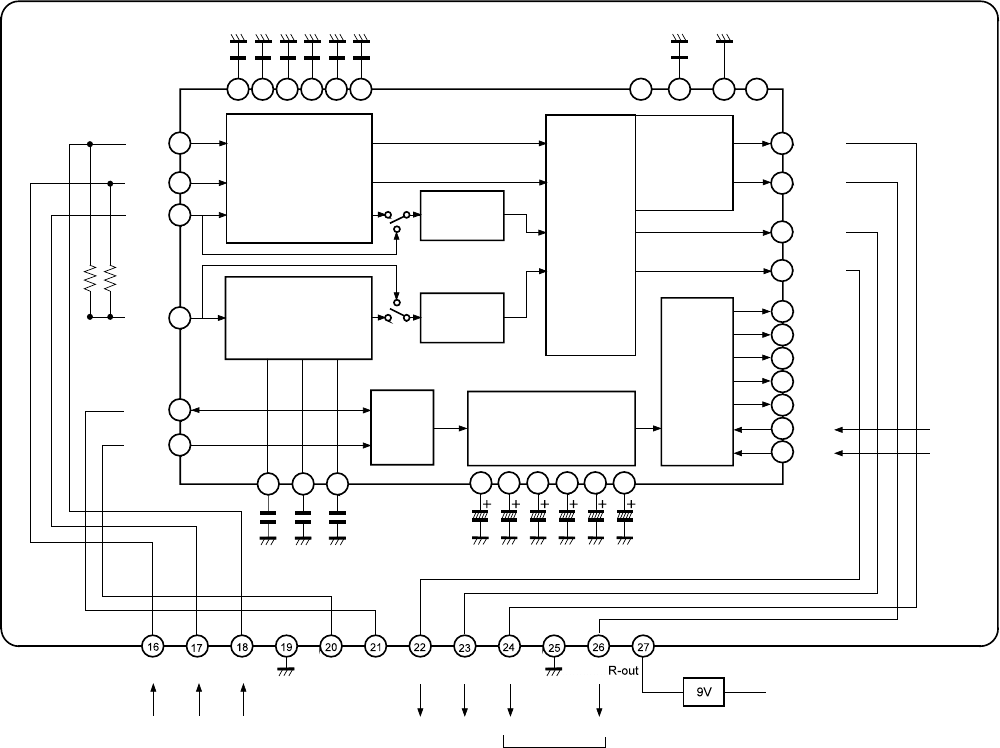

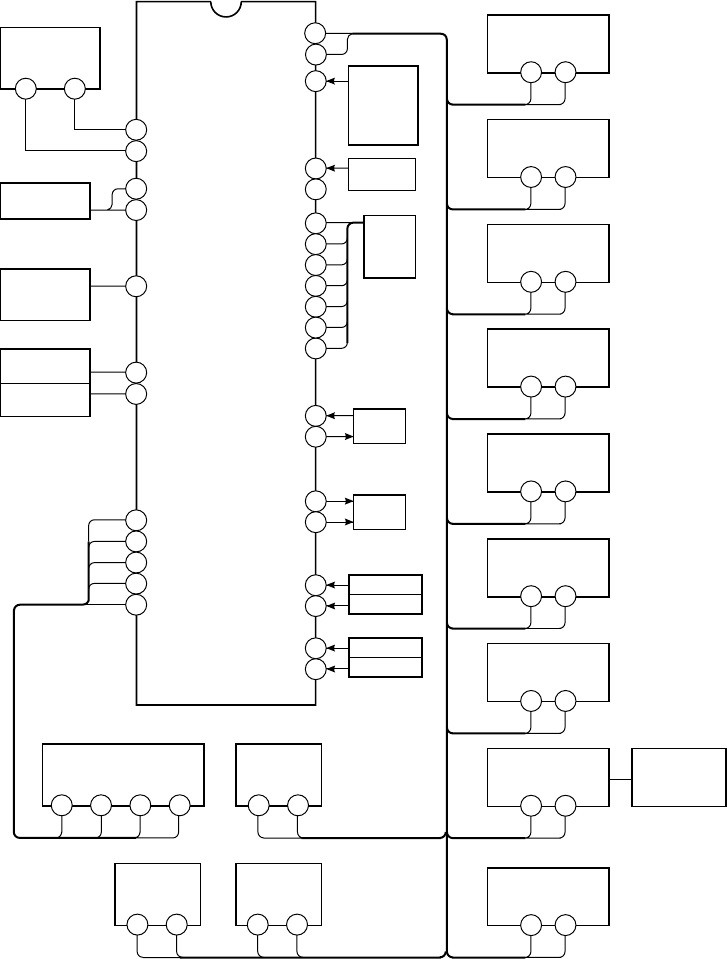

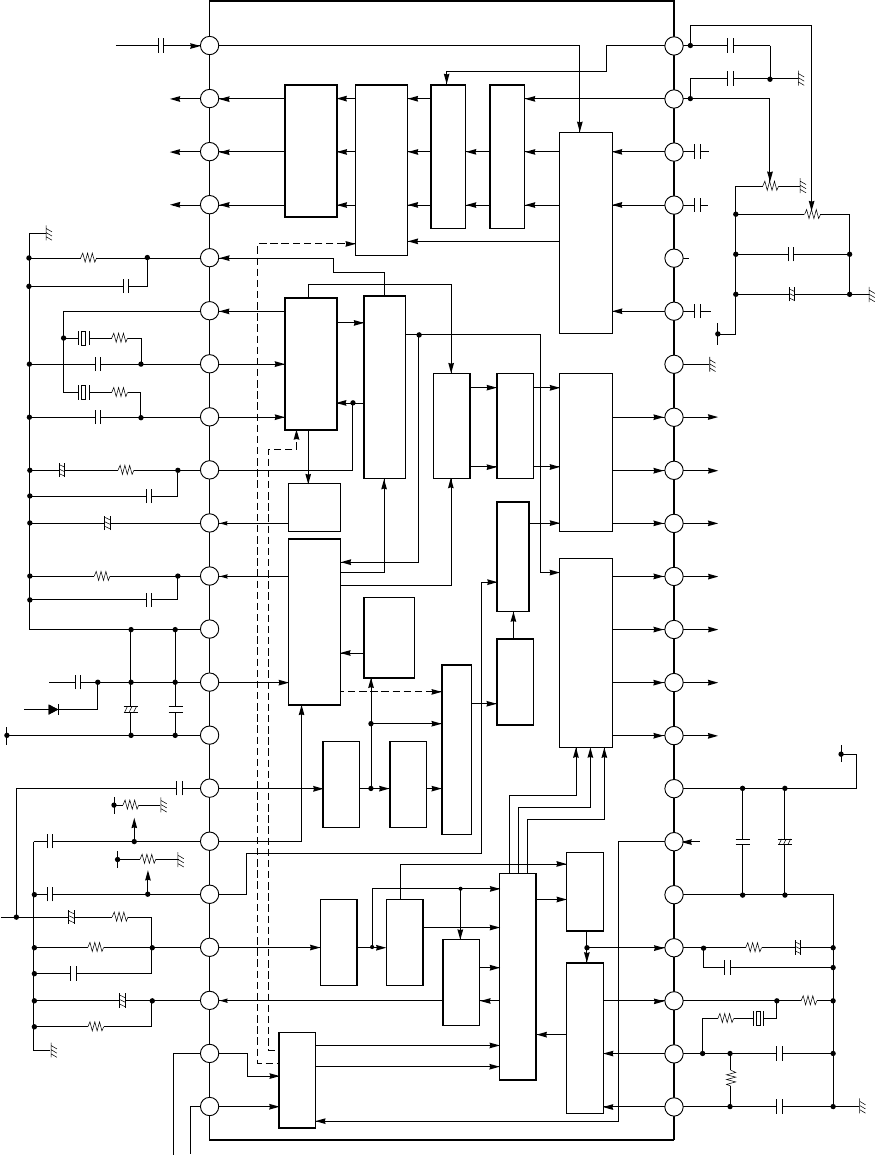

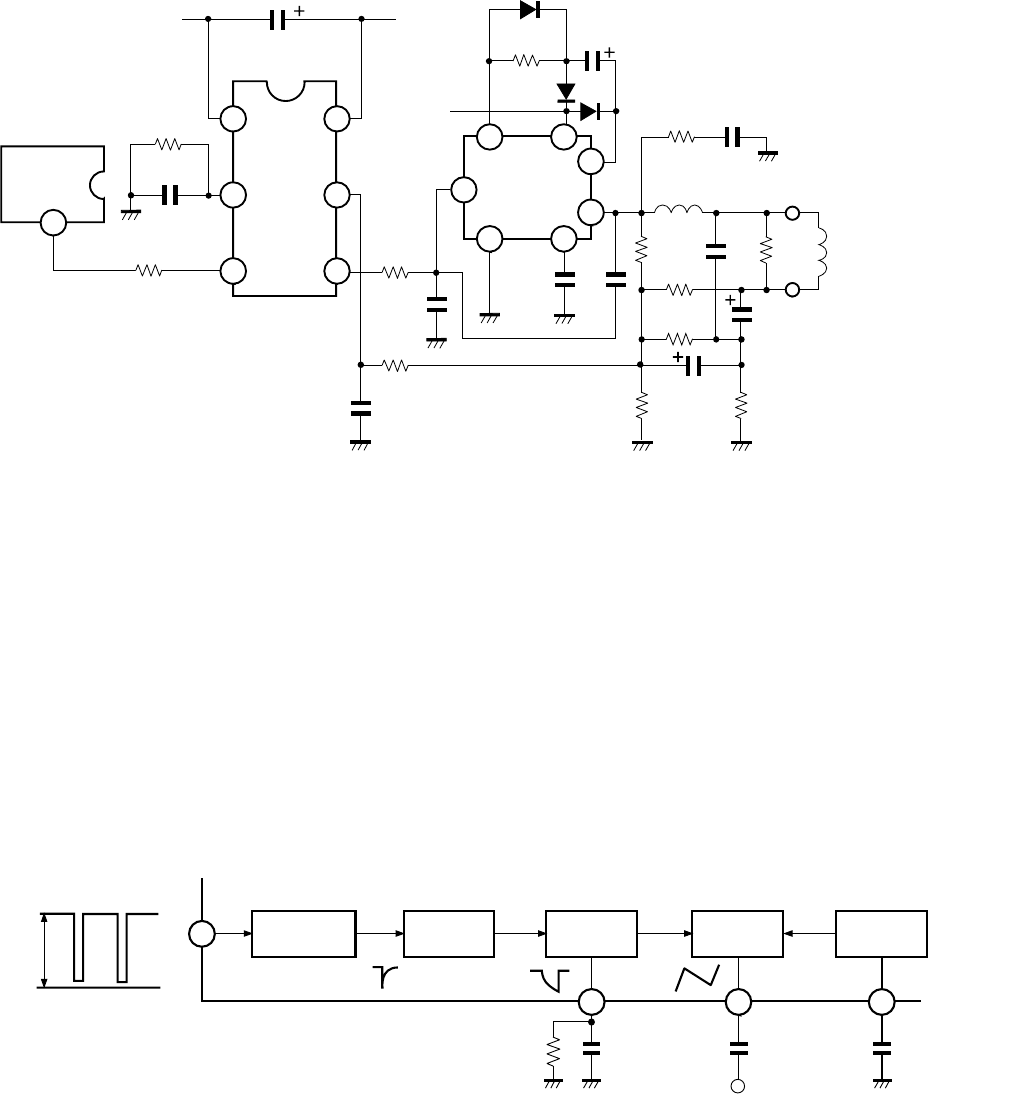

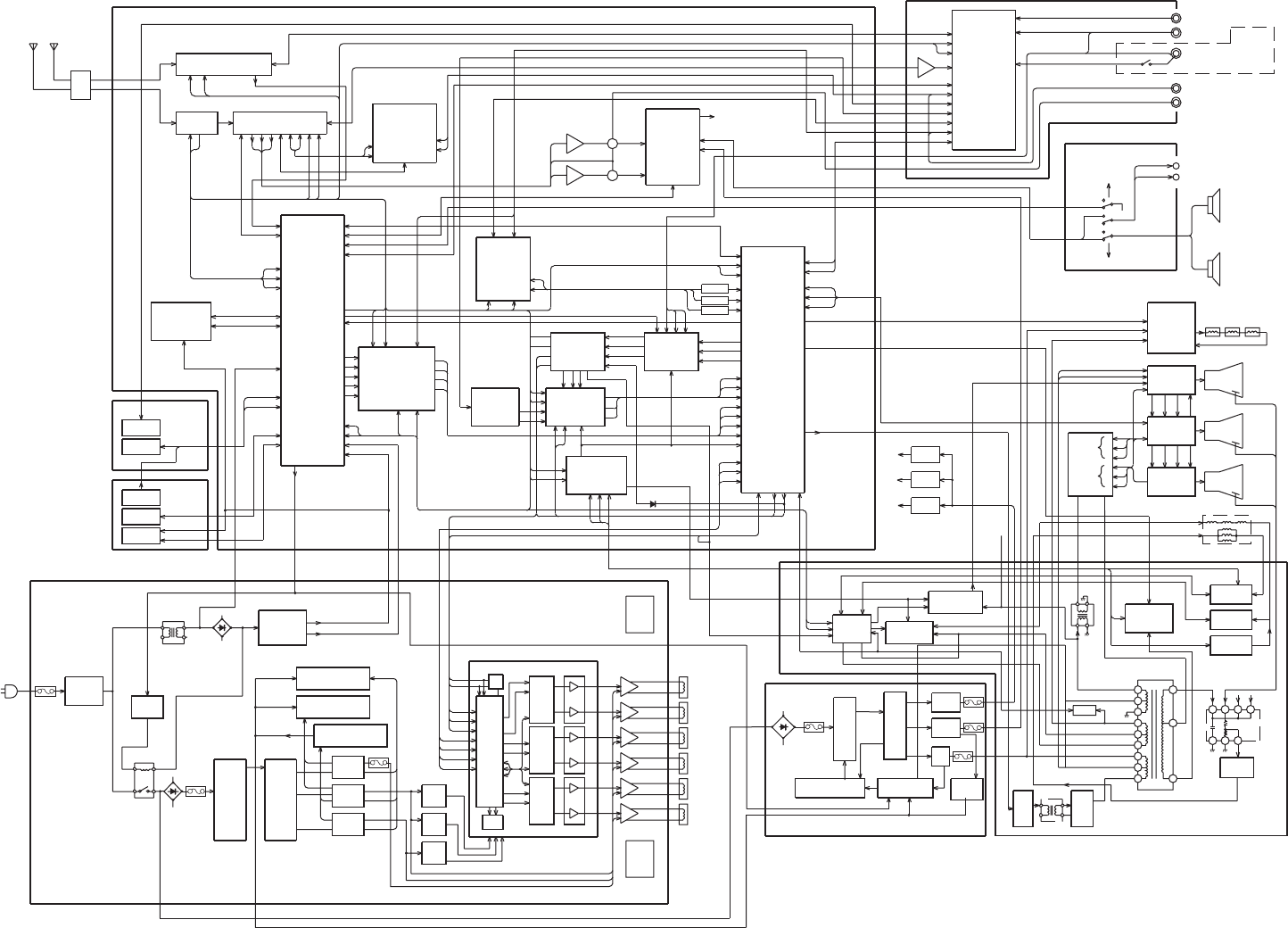

1. CIRCUIT BLOCK

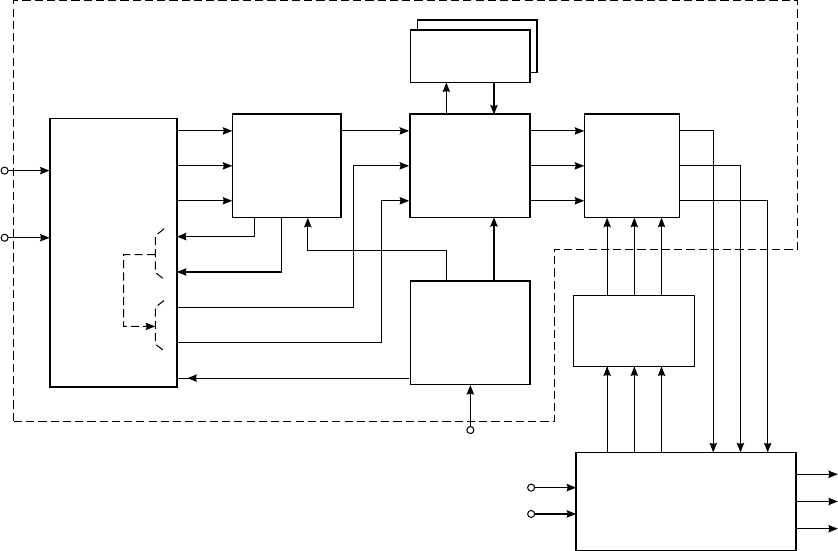

Fig. 2-1 Block diagram

1-1. Outline

(1) RF signals sent from an antenna are converted into in-

termediate frequency band signals (video: 45.75 MHz,

audio: 41.25 MHz) in the tuner. (Hereafter, these sig-

nals are called IF signals.)

(2) The IF signals are band-limited in passing through a

SAW filter.

(3) The IF signals band-limited are detected in the VIF

circuit to develop video and AFT signals.

(4) The band-limited IF signals are detected in the SIF cir-

cuit and the detected output is demodulated by the au-

dio multiplexer, developing R and L channel outputs.

These outputs are fed to the A/V switch circuit.

(5) A sound processor (S.PRO.) is provided.

1-2. Major Features

(1) The VIF/SIF circuit is fabricated into a small module

by using chip parts considerably.

(2) As the tuner, EL466L that which contains an integrated

PLL circuit is employed.

(3) Wide band double SAW filter F1802R used.

(4) FS (frequency synthesizer) type channel selection sys-

tem employed.

EL466L

Tuner

RF AGC

IF/MTS/S.PRO Module MVUS34S

SIF

output

Sound

Multiplex

Circuit

SAW

Filter

VIF/SIF

Circuit S.PRO Circuit

AFT output

TP12

Video output

To A/V switch circuit

TV

R-OUT

TV

L-OUT

C-IN

R-IN L-IN

R-OUT L-OUT (L+R)

-OUT

C-OUT

(5) VIF/SIF circuit uses PLL sync detection system to

improve performances shown below:

• Telop buzz in video over modulation

• DP, DG characteristics (video high-fidelity repro-

duction)

• Cross color characteristic (coloring phenomenon

at color less high frequency signal objects)

(6) HIC SBX1637A-22 is used in the audio multiplexer

circuit to minimize the size with increased performance.

(7) As a sound control processor, TA1217N is used. I2C-

bus data control the DAC inside the IC to perform

switching of the audio multiplexer modes.

SECTION II: TUNER, IF/MTS/S. PRO MODULE

13

1-3. Audio Multiplex Demodulation Circuit

The sound multiplex composite signal FM-detected in the

PIF circuit enters pin 12 of HIC (hybrid IC) in passing

through the separation adjustment VR RV2 and amplified.

After the amplification, the signal is split into two: one en-

ters a de-emphasis circuit, and only the main signal with the

L-R signal and a SAP signal removed enters the matrix cir-

cuit. At the same time, the other passes through various fil-

ters and trap circuits, and the L-R signal is AM-demodu-

lated, and the SAP is FM-demodulated.

Then, both are fed to the matrix circuit. At the same time,

each of the stereo pilot signal fH and the SAP pilot signal

5fH is also demodulated to obtain an identification voltage.

With the identification voltage thus obtained and the user

control voltage are used to control the matrix.

The audio signals obtained by demodulating the sound mul-

tiplex signal develop at pin 10 and 11 of HIC and develop

the terminals of 12 and 14 of the module.

MVUS34S

MPX

Out DAC-out1

(SURR ON/OFF) DAC-out2

(RFSW)

TV

R-Out TV

L-Out

910 11 12 13 14 15

Stereo 0V SAP 0V OFF 0V

Other 5V Other 5V ON 9V

RF1 0V

RF2 9V

To AV select circuit

Monitor the input

pin for multiplex

sound IC

TV waveform detection

output (R) TV waveform detection

output (L)

Fig. 2-2 Block diagram of MVUS34S

Table 2-1 Matrix for broadcasting conditions and

reception mode

Broad- Switching Output OSD display

casted mode 12 pin 14 pin Stereo SAP

(R) (L)

Stereo STE R L •–

SAP R L •–

MONO L+R L+R •–

Mono STE L+R L+R – –

SAP L+R L+R – –

MONO L+R L+R – –

Stereo STE R L ••

+ SAP SAP SAP ••

SAP MONO L+R L+R ••

Mono STE L+R L+R – •

+ SAP SAP SAP – •

SAP MONO L+R L+R – •

Note:

Of the mode selection voltages, switching voltages for STE,

SAP, MONO do not output outside the module.

They are used inside the module to control the BUS.

• : Available, – : Not available

14

1-4. A.PRO Section (Audio Processor)

The S.PRO section has following functions.

(1) Woofer processing (L+R output)

(2) High band, low band, balance control

(3) Sound volume control, cyclone level control

(4) Cyclone ON/OFF

All these processing are carried out according to the BUS

signals sent from a microcomputer.

Fig. 2-3 shows a block diagram of the A.PRO IC.

TA1217N

Lin

Rin

Cin

Win

SDA

SCL

TONE CONTROL

LPF

Center

LEVEL

Woofer

LEVEL

VOLUME

BALANCE

I C

2

D/A

CONV

I/O

L out

R out

C out

W out

SAP Ident.

STE Ident.

R-in C-in L-in SCL SDA W-out O-out L-out

From From From

A/V Dolby A/V

to Q670 to Q640 to Q670 to Q670

Via QS101

731 24 23 22 19

26

25

18

10

30 9 828

127

29 22 32 36

456

17

16

15

14

13

12

11

34

30

2

3

20

21

Fig. 2-3 A.PRO block diagram

15

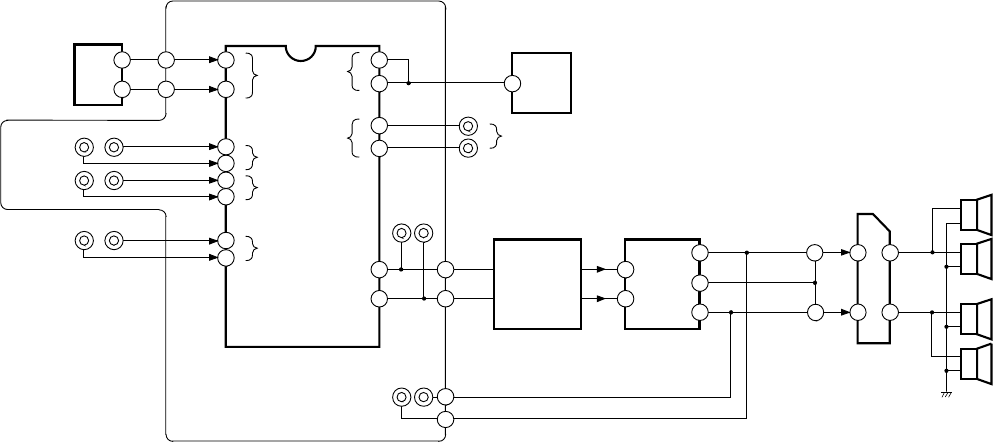

Fig. 2-4

Configuration of the audio circuit and signal flow are given

in Fig. 2-4

A/V PCB

ICV01

VIF+MTS+S.PRO

MODULE

R

L

R

L

L

R

L

R

L

R

L

R

L

R

MOTHER

TV

CHILD

TV

PIP

OUTPUT

VIDEO 1

VIDEO 2

VIDEO 3

FOR POP

IF MODULE

AUDIO

L

R

PIP OUT

(AUDIO)

VIDEO 1

VIDEO 2

OR

DVD

VIDEO 3

(FRONT INPUT)

R L

R L

R L

R

L

VIDEO

OUTPUT

TERMINAL

VARIABLE

AUDIO OUTPUT

TERMINAL

RL

FRONT

SURROUND

UNIT

VIF+MTS+A.PRO

MODULE

R

L

R

L

Q601 R

L

R OUT

L OUT

W OUT

12

14

EQ

ER

AS

AR

AI

AJ

6

7

11

13

3

9

15

17

29

31

2

1

35

37

16

18

25

24

22

2

5

11

7

+

+

(TW40F80 NOT USE)

16

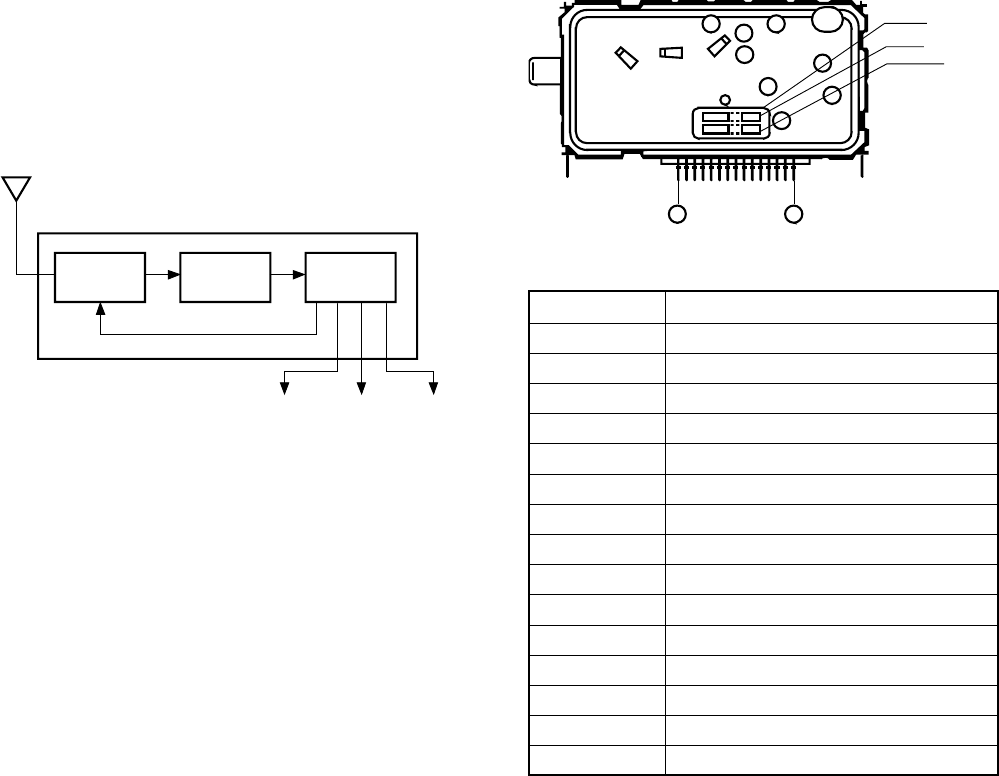

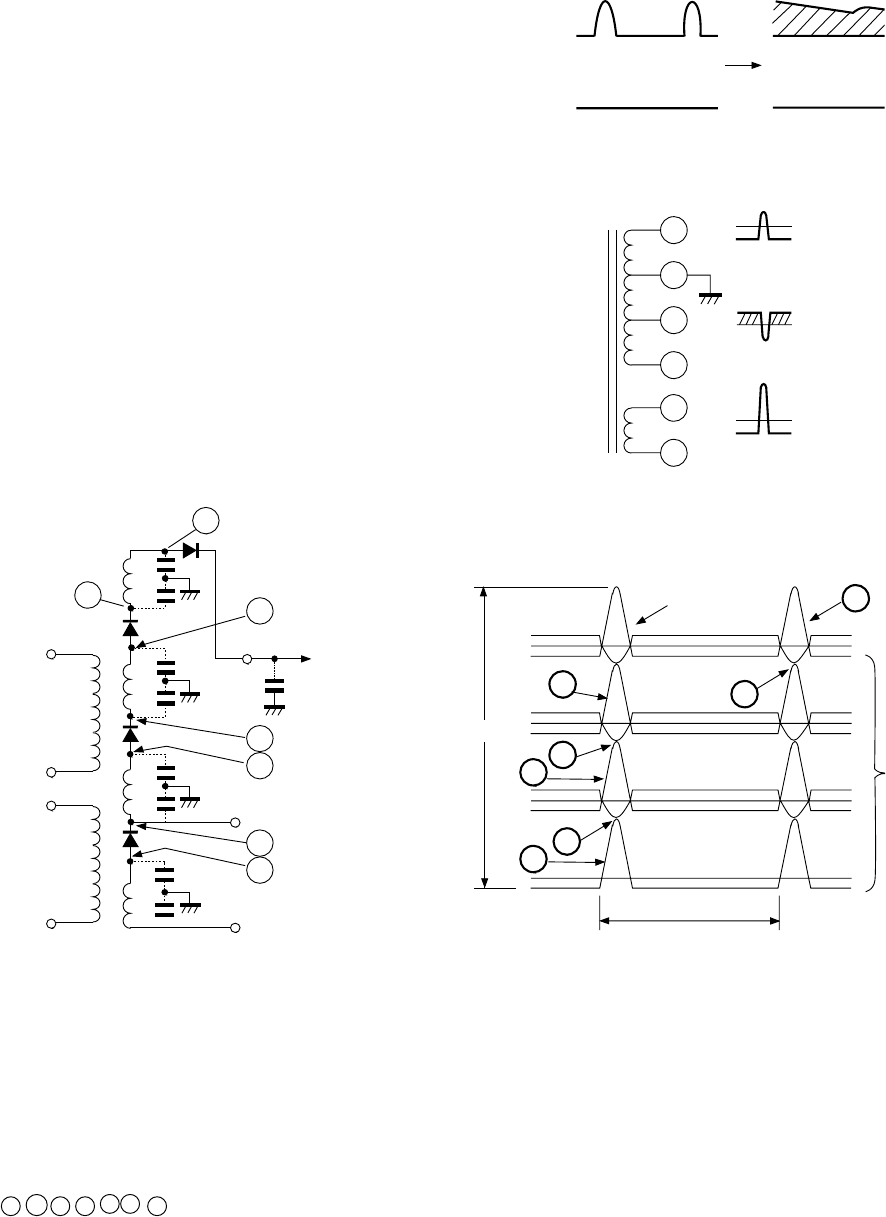

2. POP TUNER

TUNER

SECTION

SAW

FILTER VIF/SIF

CIRCUIT

RF AGC

AFT

OUTPUT

VIDEO

OUTPUT

AUDIO

OUTPUT

Fig. 2-5

2-1. Outline

The POP tuner (EL922L) consists of a tuner and an IF block

integrated into one unit. The tuner receives RF signals in-

duced on an antenna and develops an AFT output, video

output, and audio output.

The tuner has receive channels of 181 as in the tuner for the

main screen and it is also controlled through the I2C-bus.

As the IC for the IF, a PLL complete sync detection plus

audio inter carrier system are employed.

Label

Name

Lot No.

115

Fig. 2-6 Tuner terminal layout

Terminal No. Name

1NC

2 32V

3 S-CLOCK

4 S-DATA

5NC

6 ADDRESS

75V

8 RF AGC

99V

10 AUDIO

11 GND

12 AFT

13 NC

14 GND

15 VIDEO

17

POP and Double Window signal processing (QY03), IC for

closed caption control (QM01), IC for WAC control (QX01),

IC for 3D-YCS (QZ01), IC for AUTOLIVE (QK06).

Differences from N5SS chassis are as follows;

1. On-screen function inside microcomputer is used. Sepa-

rate IC is not used for on-screen.

2. The microcomputer does not have the closed caption

function, but controls separate IC for closed caption.

3. The system uses two channels of I2C bus. One is only

for non-volatile memory.

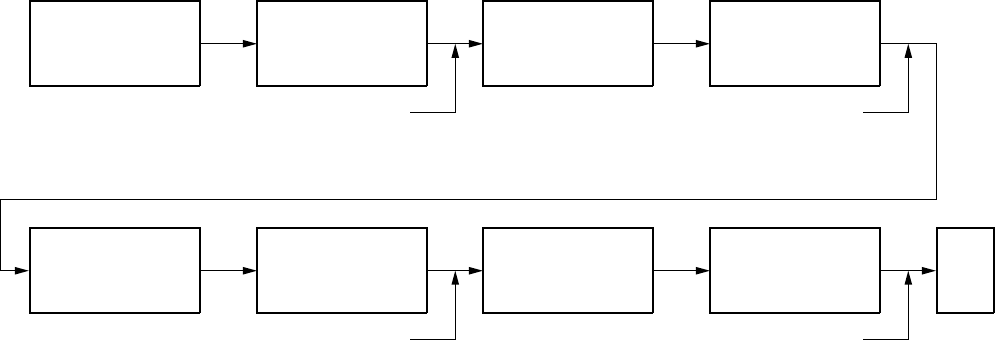

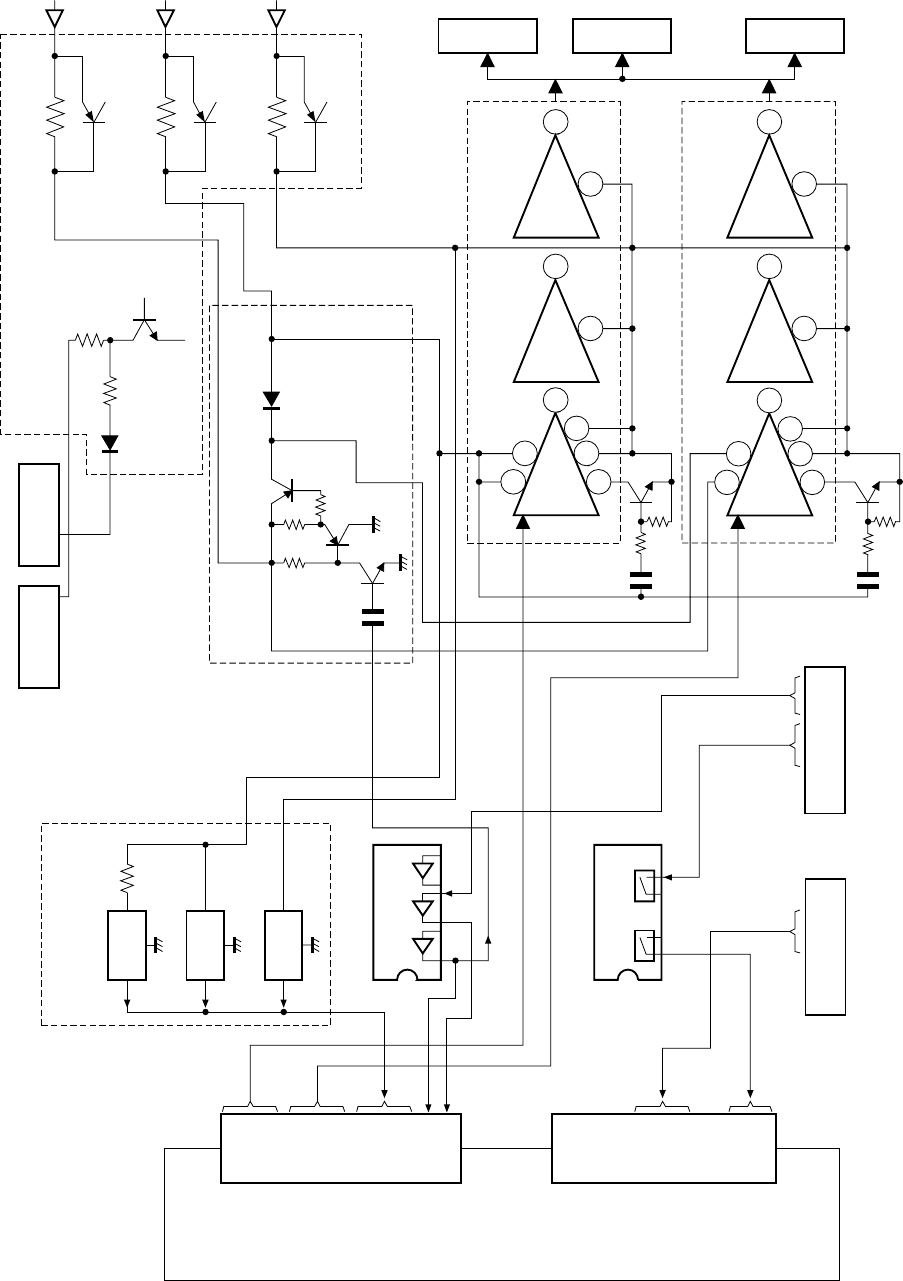

1. OUTLINE OF CHANNEL SELECTION CIRCUIT SYSTEM

The channel selection circuit in the N5SS chassis employs

a bus system which performs a central control by connect-

ing a channel selection microcomputer to a control IC in

each circuit block through control lines called a bus. In the

bus system which controls each IC, the I2C bus system (two

line bus system) developed by Philips Co. Ltd. in the Neth-

erlands has been employed.

The ICs controlled by the I2C bus system are: IC for V/C/D

signal processing (Q501), IC for A/V switching (QV01), IC for

non volatile memory (QA02), Main and sub U/V tuners (H001,

HY01), IC for deflection distortion correction (Q302), IC for

Toshiba made 8 bit microcomputer TLCS-870 series for TV

receiver, TMP87CS38N-3320 is employed for QA01.

With this microcomputer, each IC and circuit shown below

are controlled.

(1) CONTROL OF VIDEO/CHROMA/DEF SIGNAL

PROCESS IC (Q501 Toshiba TA1222AN)

• Adjustments for uni-color, brightness, tint, color

gain, sharpness and PIP uni-color

• Setting of adjustment memory values for sub-

brightness, sub-color and sub-tint, etc.

• Setting of memory values for video parameters such

as white balance (RGB cutoff, GB drive) and

gcorrection, etc.

• Setting of video parameters of video modes (Stan-

dard, Movie, Memory)

(2) CONTROL OF A/V SWITCH IC (QV01 Toshiba

TA1218N)

• Performs source switching for main screen and sub

screen

• Performs source switching for TV and three video

inputs

(3) CONTROL OF NON-VOLATILE MEMORY IC

(QA02 Microchip 24LC08BI/P)

• Memorizes data for video and audio signal adjust-

ment values, volume and woofer adjustment val-

ues, external input status, etc.

• Memorizes adjustment data for white balance (RGB

cutoff, GB drive), sub-brightness, sub color, sub

tint, etc.

• Memorizes deflection distortion correction value

data adjusted for each unit.

SECTION III: CHANNEL SELECTION CIRCUIT

2. OPERATION OF CHANNEL SELECTION CIRCUIT

(4) CONTROL OF U/V TUNER UNIT (H001 Toshiba

ELA12L, HY01 Toshiba EL922L)

• A desired channel can be tuned by transferring a

channel selection frequency data (divided ratio data)

to the I2C bus type frequency synthesizer equipped

in the tuner, and by setting a band switch data which

selects the UHF or VHF band.

(5) CONTROL OF DEFLECTION DISTORTION COR-

RECTION IC (Q302 Toshiba TA8859P)

• Sets adjustment memory value for vertical ampli-

tude, linearity, horizontal amplitude, parabola, cor-

ner, trapezoid distortion.

(6) CONTROL OF POP & Double Window SIGNAL PRO-

CESS IC (QY03 Toshiba TC9092AF, QY91 Sony

CXP85116B-514Q)

• Controls ON/OFF and 9 pictures serch of POP.

(7) CONTROL OF CLOSED CAPTION/EDS (QM01

Motorola XC144144P)

• Controls Closed Caption/EDS.

(8) CONTROL OF WAC (QX01 Toshiba TC9097F)

• Controls Wide Aspect.

(9) CONTROL OF 3D-YCS (QZ01 Toshiba TC9086F)

• Controls ON/OFF of 3 Dimension Y/C separator.

(10) CONTROL OF VERTICAL AMPLITUDE (QK06

Toshiba TMP87CM36N)

• Controls Wide Mode.

(11) CONTROL OF OSD (Do not I2C BUS) (QR60 Fujitsu

MB90091)

• Controls of OSD Menu.

18

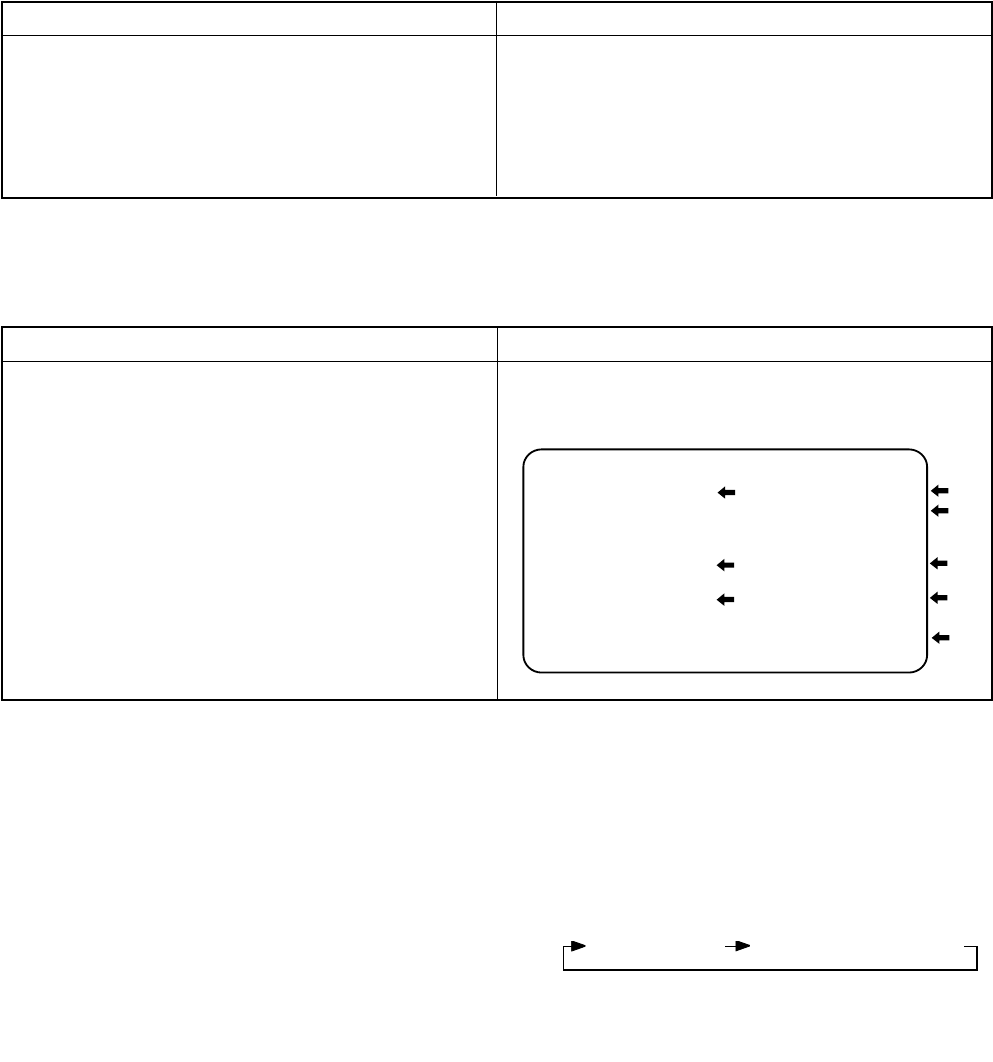

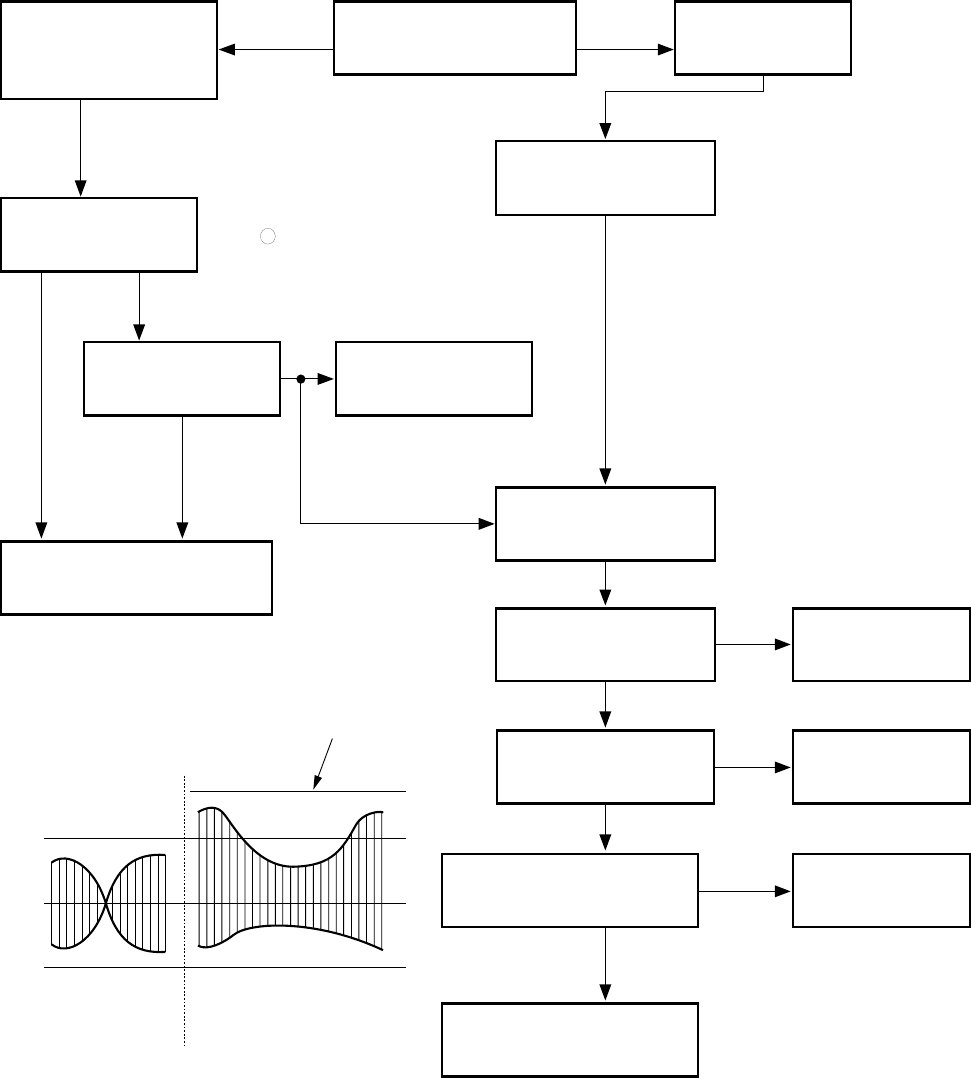

Fig. 3-1

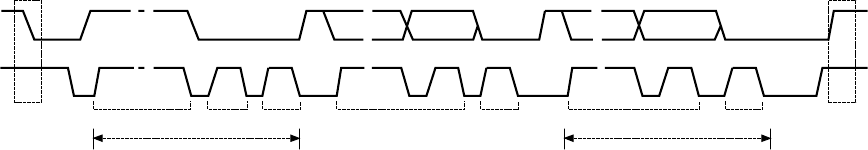

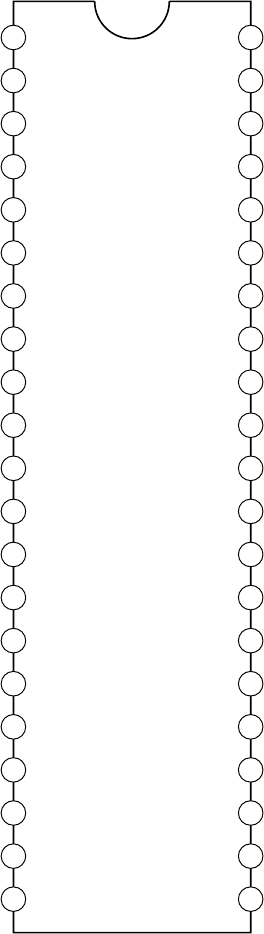

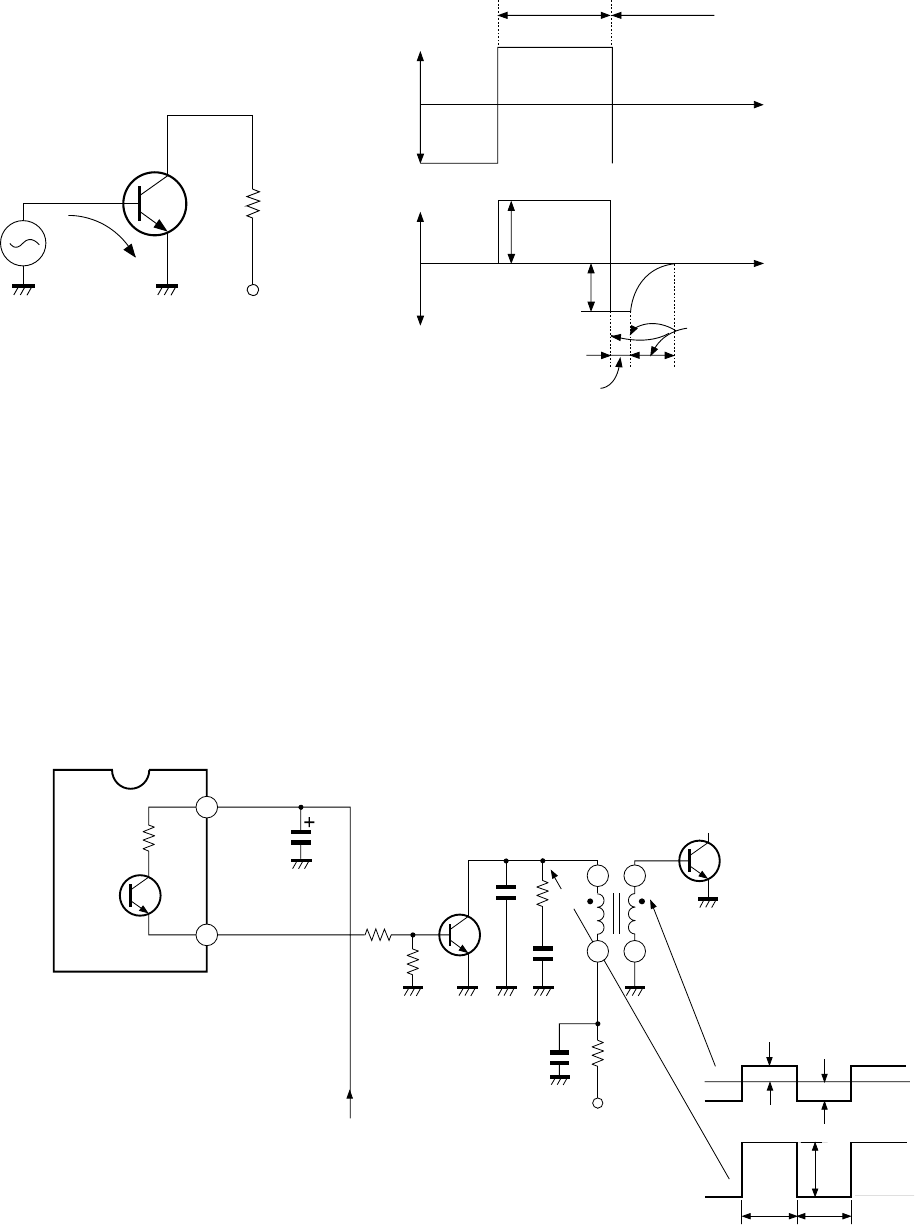

3. MICROCOMPUTER

Microcomputer TMP87CS38N-3320 has 60k byte of ROM

capacity and equipped with OSD function inside.

The specification is as follow.

• Type name : TMP87CS38N-3320

• ROM : 60k byte

• RAM : 2k byte

• Processing speed : 0.5m s (at 8MHz with Shortest com-

mand)

• Package : 42 pin shrink DIP

•I

2

C-BUS : two channels

• PWM : 14 bit x 1, 7 bit x 9

• ADC : 8 bit x 6 (Successive comparison system, Conver-

sion time 20ms)

IIC device controls through I2C bus. (Timing chart : See Fig.

3-1)

• LED uses big current port for output only.

• For clock oscillation, 8MHz ceramic oscillator is used.

•I

2

C has two channels. One is for EPROM only.

• Self diagnosis function which utilizes ACK function of

I2C is equipped

• Function indication is added to service mode.

• Remote control operation is equipped, and the control

by set no touch is possible. (Bus connector in the con-

ventional bus chassis is deleted.)

• Substantial self diagnosis function

(1) B/W composite video signal generating function

(micom inside, green crossbar added)

(2) Generating function of audio signal equivalent to

1kHz (micom inside)

(3) Detecting function of power protection circuit opera-

tion

(4) Detecting function of abnormality in IIC bus line

(5) Functions of LED blink indication and OSD indica-

tion

(6) Block diagnosis function which uses new VCD and

AV SW

SDA

SCL 1 - 7 891 - 7 891 - 7 89

Start

condition Stop

condition

Address R/W Ack Data Ack DATA Ack

Approx.180µSSome device may have no data,

or may have data with several

bytes continuing.

19

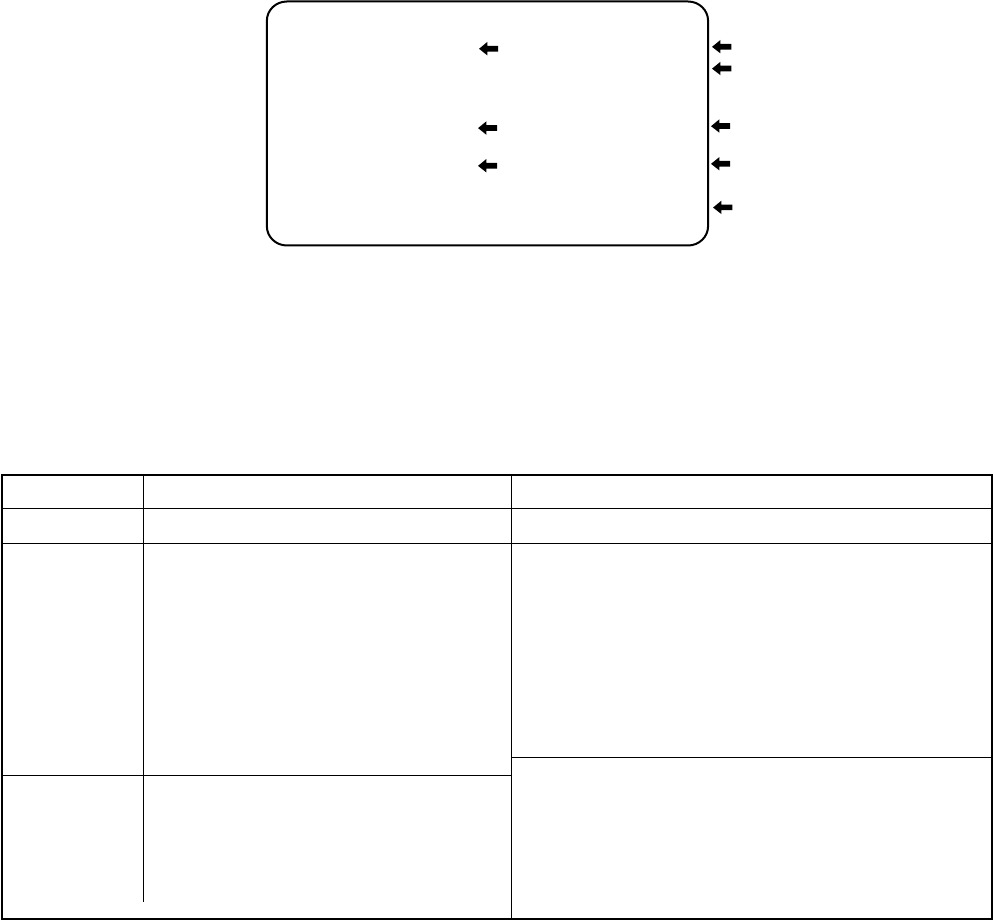

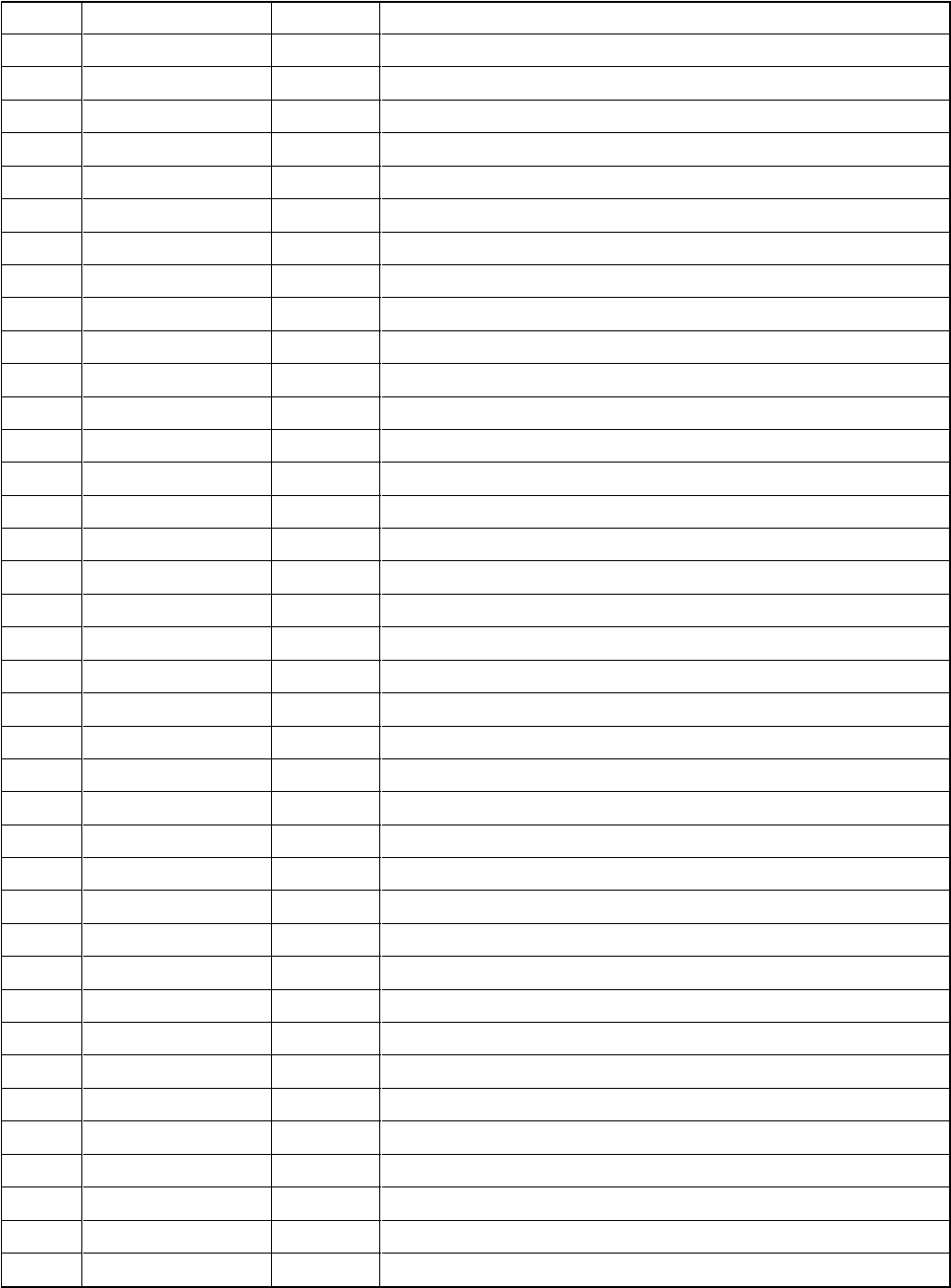

Fig. 3-2

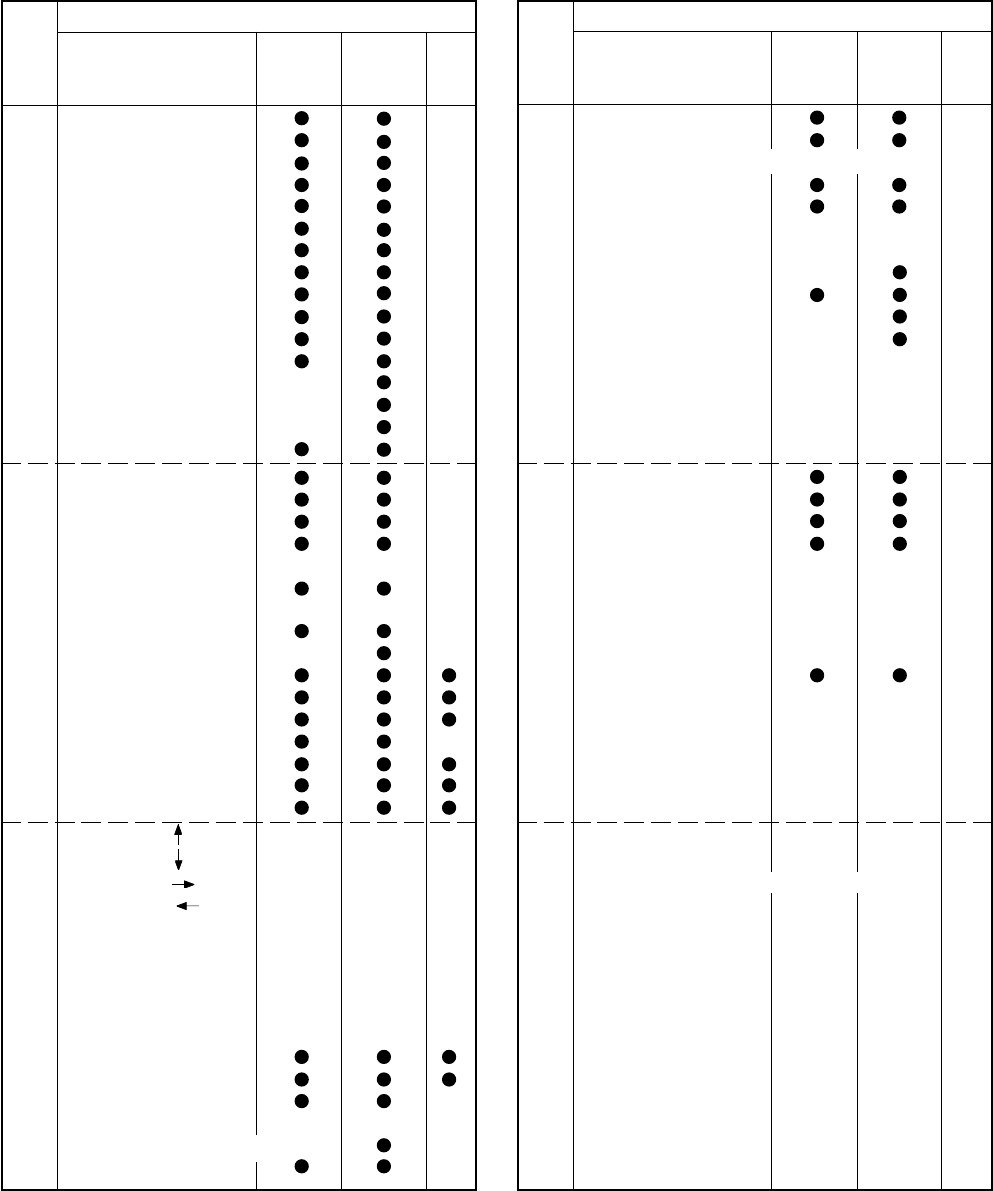

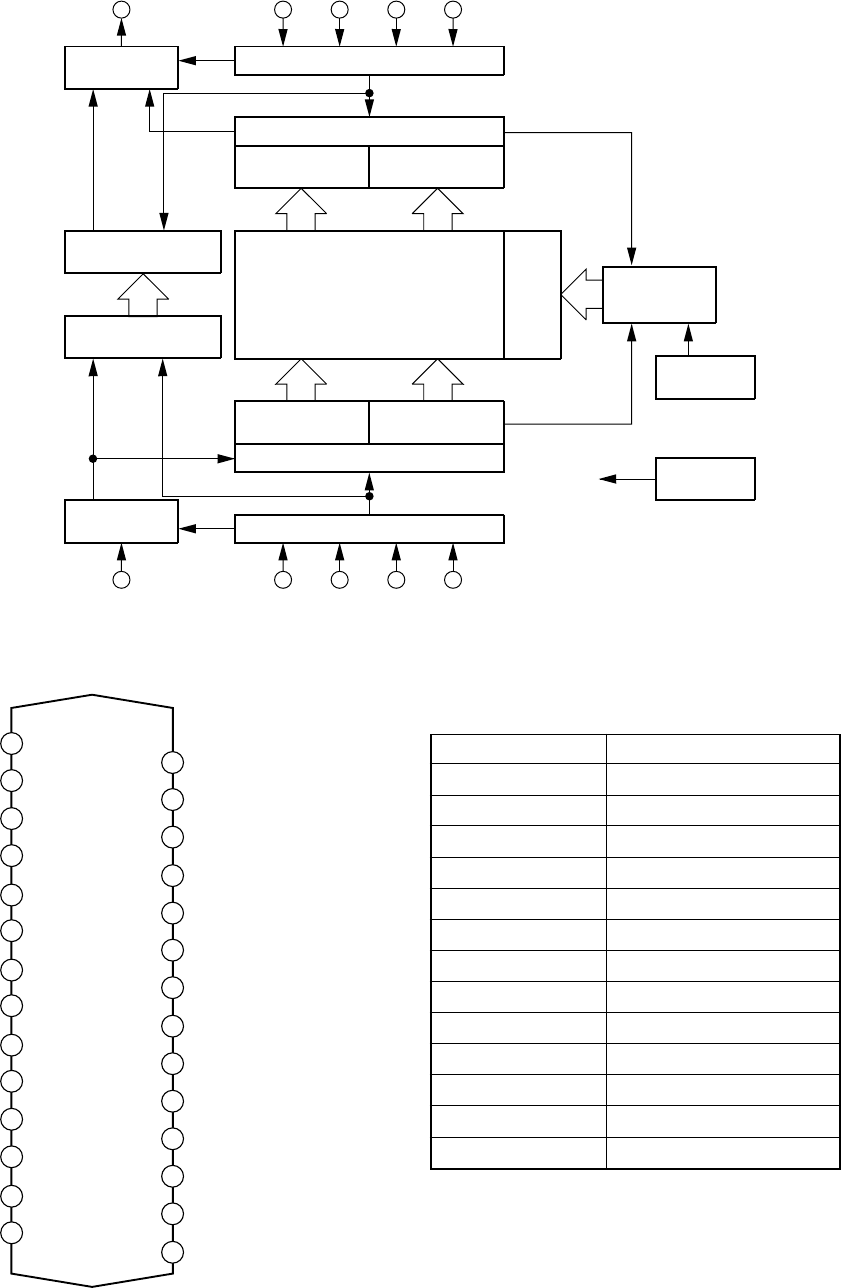

4. MICROCOMPUTER TERMINAL FUNCTION

TMP87CS38N3320 (QA01)

I

O

O

O

O

O

O

O

I

O

IO

I

0

I

I

I

I

O

O

I

I

I

IO

O

I

I

I

I

O

I

I

O

I

I

0

O

I

O

O

GND

P40 (PWM0)

P41 (PWM1)

P42 (PWM2)

P43 (PWM3)

P44 (PWM4)

P45 (PWM5)

P46 (PWM6)

P47 (PWM7)

P50 (PWM8/TC2)

P51 (SCL1)

P52 (SDA1)

P53 (AINO/TC1)

P54 (AIN1)

P55 (AIN2)

P56 (AIN3)

P60 (AIN4)

P61 (AIN5)

P62

P63

VSS

VDD

P57

P32

P57

SDA0

SCL0

(TC3)P31

(RXIN)P30

P20

RESET

XOUT

XIN

TEST

0SC2

0SC1

VD

OSD RESET

DATA

BUSY

CS

CLK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

GND

BAL

REM OUT

MUTE

SP MUTE

NC

POWER

LED

SSRST

DVD CONT

SCL0

SDA0

SYNC VCD

PIPRST

AFT2

AFT1

KEY-A

KEY-B

SGV

SGA

GND

IIC

-BUS

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

VDD

ACP

SS VD

I C STOP

SDA1

SCL1

SYNC AV1

RMT IN

EXT SP

RESET

XOUT

XIN

GND

0SC1

0SC2

VSYNC

OSD RESET

DATA

BUSY

CS

CLK

IIC-

BU

S

2

20

<< MICROCOMPUTER TERMINAL NAME AND OPERATION LOGIC >>

No. Terminal Name Function In/Out Logic Remarks

1 GND 0V

2 BAL INPUT BALANCE Out PWM out

3 REM OUT REMOTE CONTROL Out Remote control output

SIGNAL OUT

4 MUTE SOUND MUTE OUT Out Sound mute output

5 SP MUTE SPEAKER MUTE Out In muting = H

6 DEF POW Out

7 POWER POWER ON/OFF OUT Out Power control In ON = H

8 LED POWER LED OUTPUT Out Power LED on-control

LED lighting = L

9 SS RST STARSIGHT RESET Out Reset = L 0V

10 DVD CONT DVD CONTROL Out DVD = L, Other = H 0V

11 SCL0 IIC BUS CLOCK OUT Out IIC bus clock output 0

12 SDA0 IIC BUS DATA IN/OUT In/Out IIC bus data input/output 0

13 SYNC VCD H SYNC INPUT In Main picture H. sync signal input

14 PIP RST PIP RESET Out Reset = L

15 AFT2 IN In Sub tuner AFT S-curve input

16 AFT1 UV MAIN S-CURVE In Main tuner AFT S-curve

SIGNAL signal input

17 KEY A LOCAL KEY INPUT In Local key detection: 0 to 5V

18 KEY B LOCAL KEY INPUT In Local key detection: 0 to 5V

19 SGV TEST SIGNAL OUT Out Test signal output In normal = L 0V

20 SGA TEST AUDIO OUT Out Test audio output In normal = L 0V

21 VSS POWER GROUNDING — 0V: Gounding voltage 0V

22 CLK CLOCK OSD Out At display on: Pulse

23 CS CHIP SELECT Out At display on: Pulse

24 BUSY BUSY OSD In At display on: Pulse

25 DATA DATA OSD Out At display on: Pulse

26 OSD RESET RESET OSD Out Reset = L

27 VSYNC In VSYNC Pulse

28 OSC1 DISPLAY CLOCK Out 4.5MHz Pulse

29 OSC2 DISPLAY CLOCK In Pulse

30 TEST TEST MODE In GND fixed 0V

31 XIN SYSTEM CLOCK In System clock input 8MHz pulse

32 XOUT SYSTEM CLOCK Out System clock output 8MHz 8MHz pulse

33 RESET SYSTEM RESET In System reset input (In reset = L) 5V

34 EXT SP EXTERNAL SPEAKER In EXTERNAL = L, INT = H

35 RMT IN REMOTE CONTROL In In remote control pulse input = L In reception of

SIGNAL INPUT remote pulse

36 SYNC AV1 HSYNC INPUT In External H. sync signal input Pulse

37 SCL1 IIC BUS CLOCK OUT Out IIC bus clock output 1 Pulse

38 SDA1 IIC BUS DATA IN/OUT In/Out IIC bus data input/output 1 Pulse

39 I2C STP IIC BUS STOP In STOP = L

40 SS VD STARSIGHT VD In VSYNC for Starsight Pulse

41 ACP NSYNC INPUT In AC pulse input

42 VDD POWER — 5V 5V

21

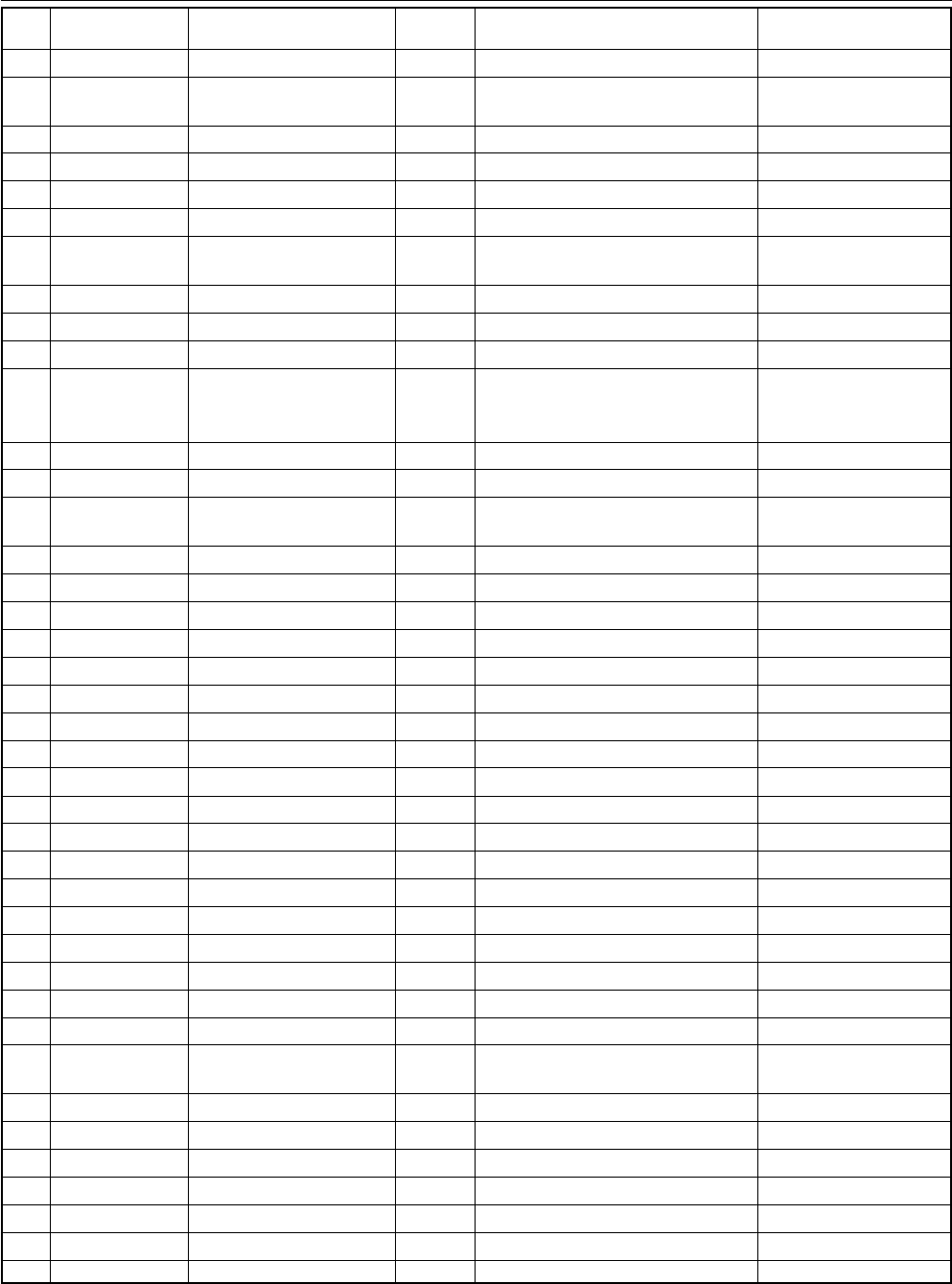

5. EEPROM (QA02)

EEPROM (Non volatile memory) has function which, in spite

of power-off, memorizes the such condition as channel se-

lecting data, last memory status, user control and digital pro-

cessor data. The capacity of EEPROM is 8k bits.

Fig. 3-3

A0

A1

A2

Vss

Vcc + 5V

NC

SCL

SDA

I

2

C-BUS line

Device adress

GND

EEPROM(QA02)

1

2

3

4

8

7

6

5

Fig. 3-4

6. ON SCREEN FUNCTION

The OSD system of TW40F80 employs the external OSD

IC (QR60, MB90091) to obtain high quality OSD.

54

56

58

55

16

64

59

60

61

22

23

24

25

26

R OUT

G OUT

B OUT

SCLK

SCS

TRE

SIN

RESET

VOB2

VIDEO

(YM)

CLK

CS

BUSY

DATA

OSD RESET

QR60 MB90091QA01 Microprocessor

QR60 is controlled by the microprocessor QA01 with the

exclusive control signals of CLK, DATA, CS, BUSY, RE-

SET.

Type name is 24LC08BI/P or ST24C08CB6, and those are

the same in pin allocation and function, and are exchange-

able each other. This IC controls through I2C bus. The power

supply of EEPROM and MICOM is common. Pin function

of EEPROM is shown in Fig. 3-3.

22

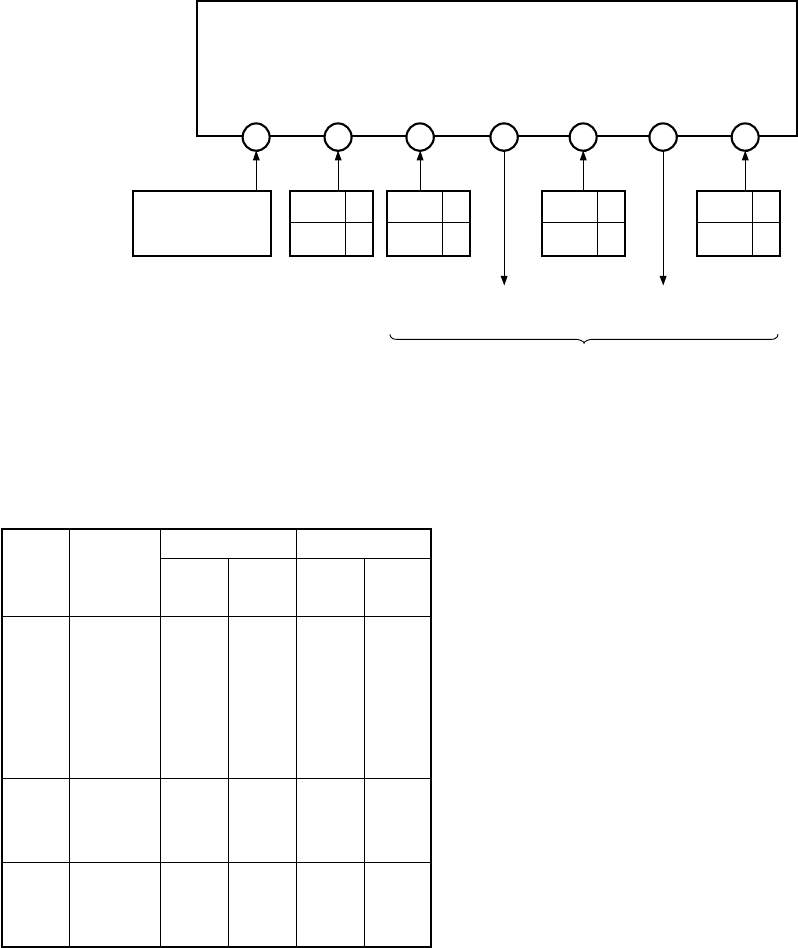

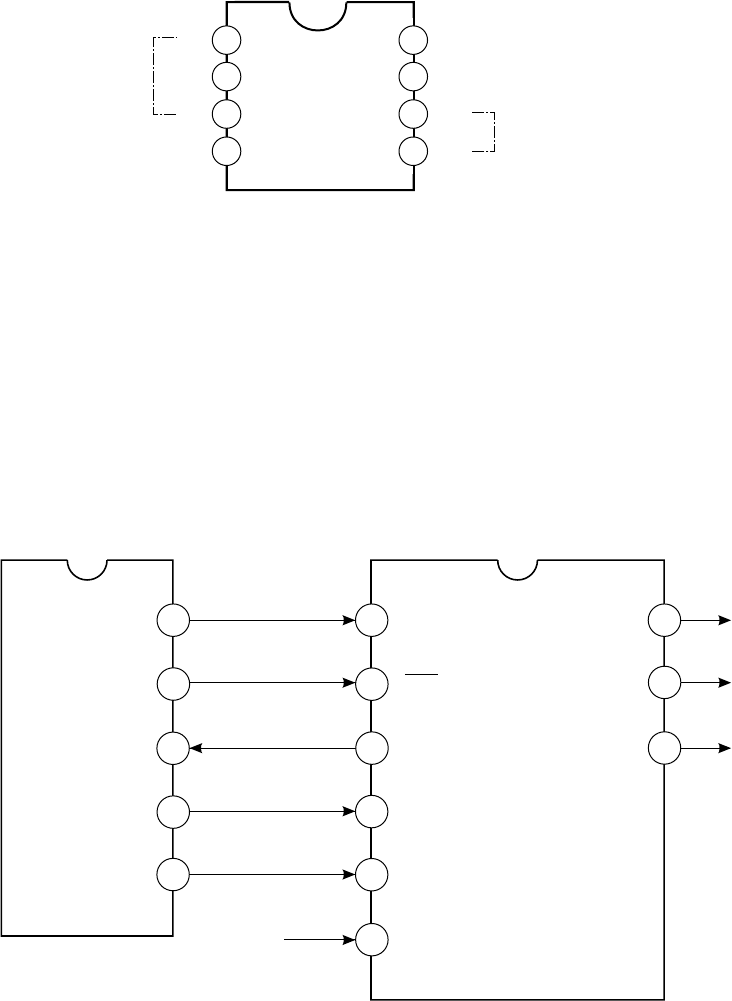

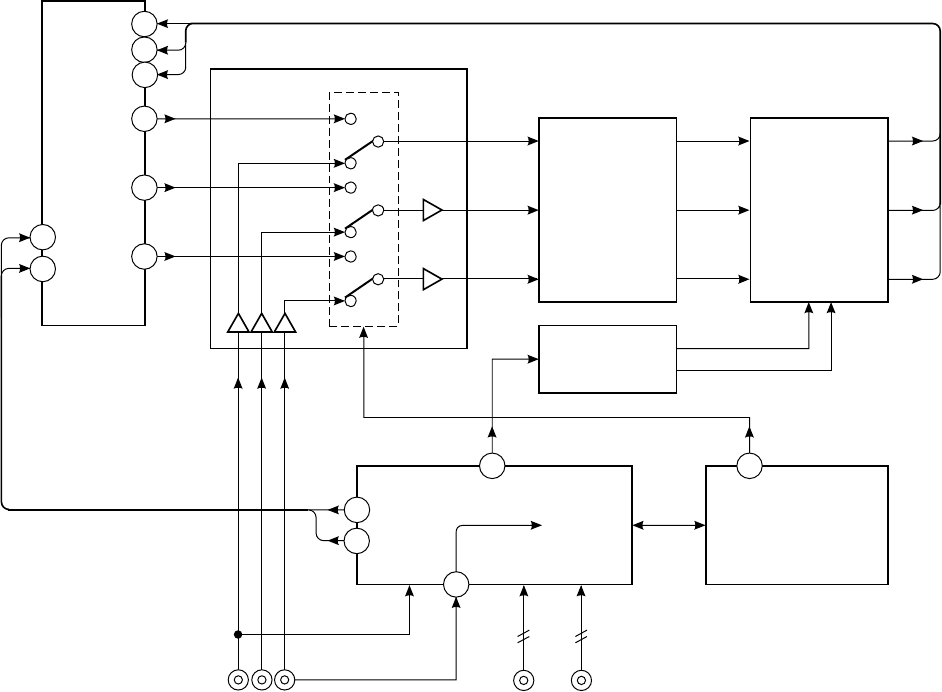

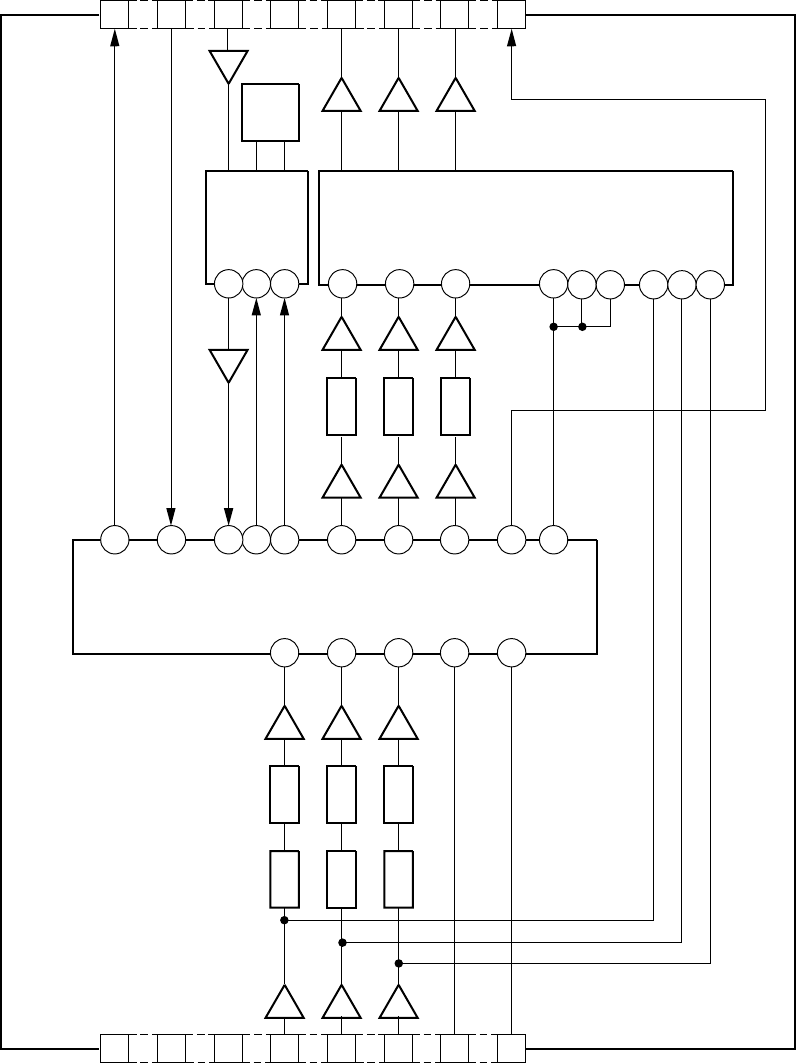

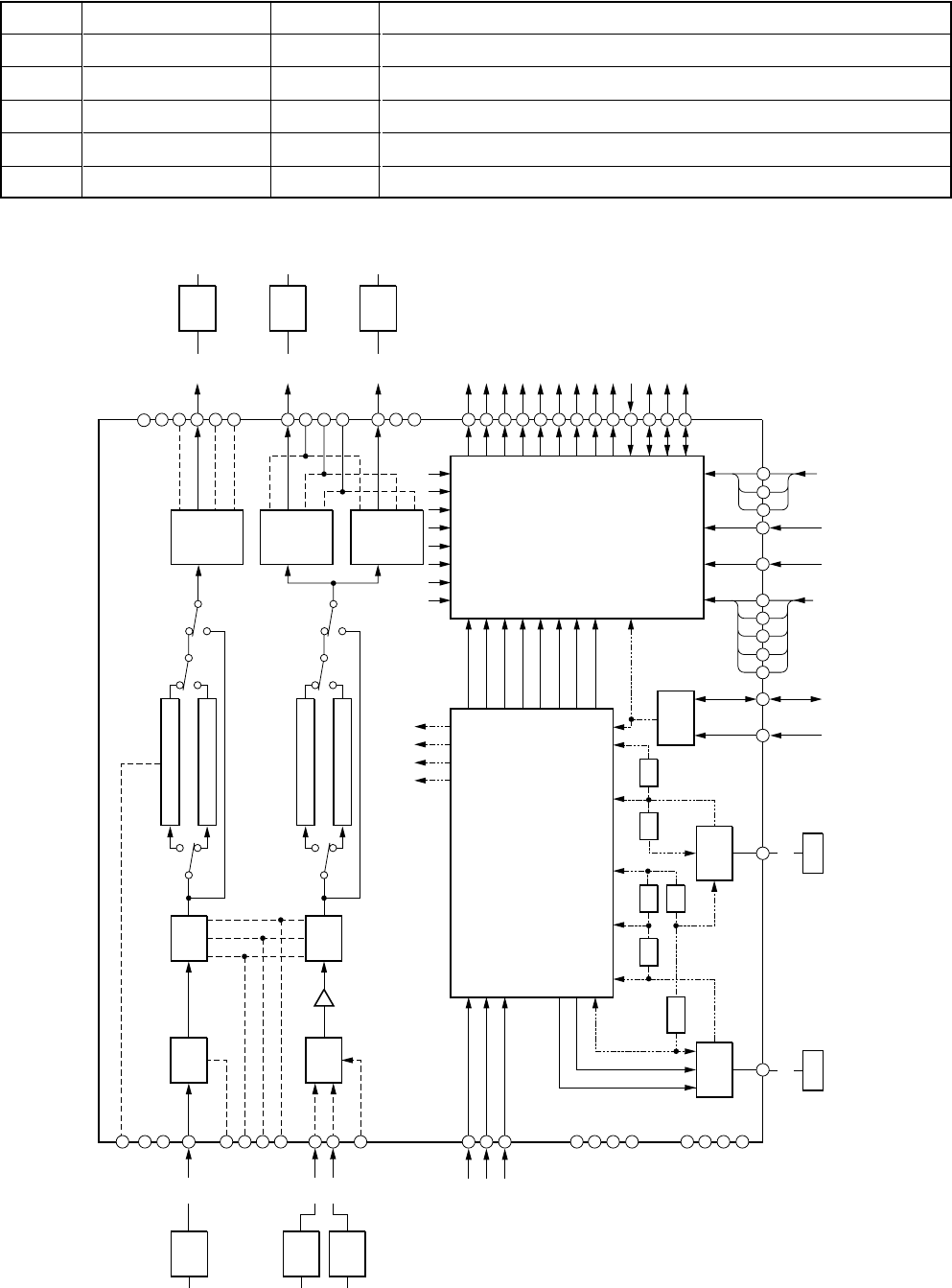

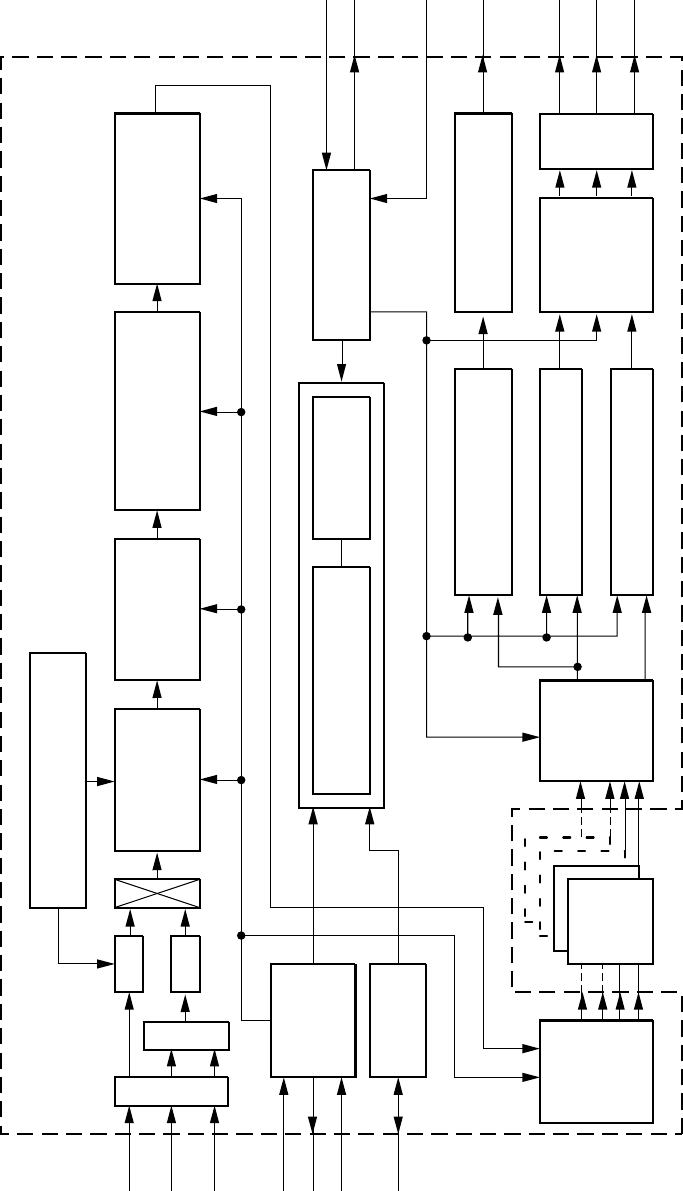

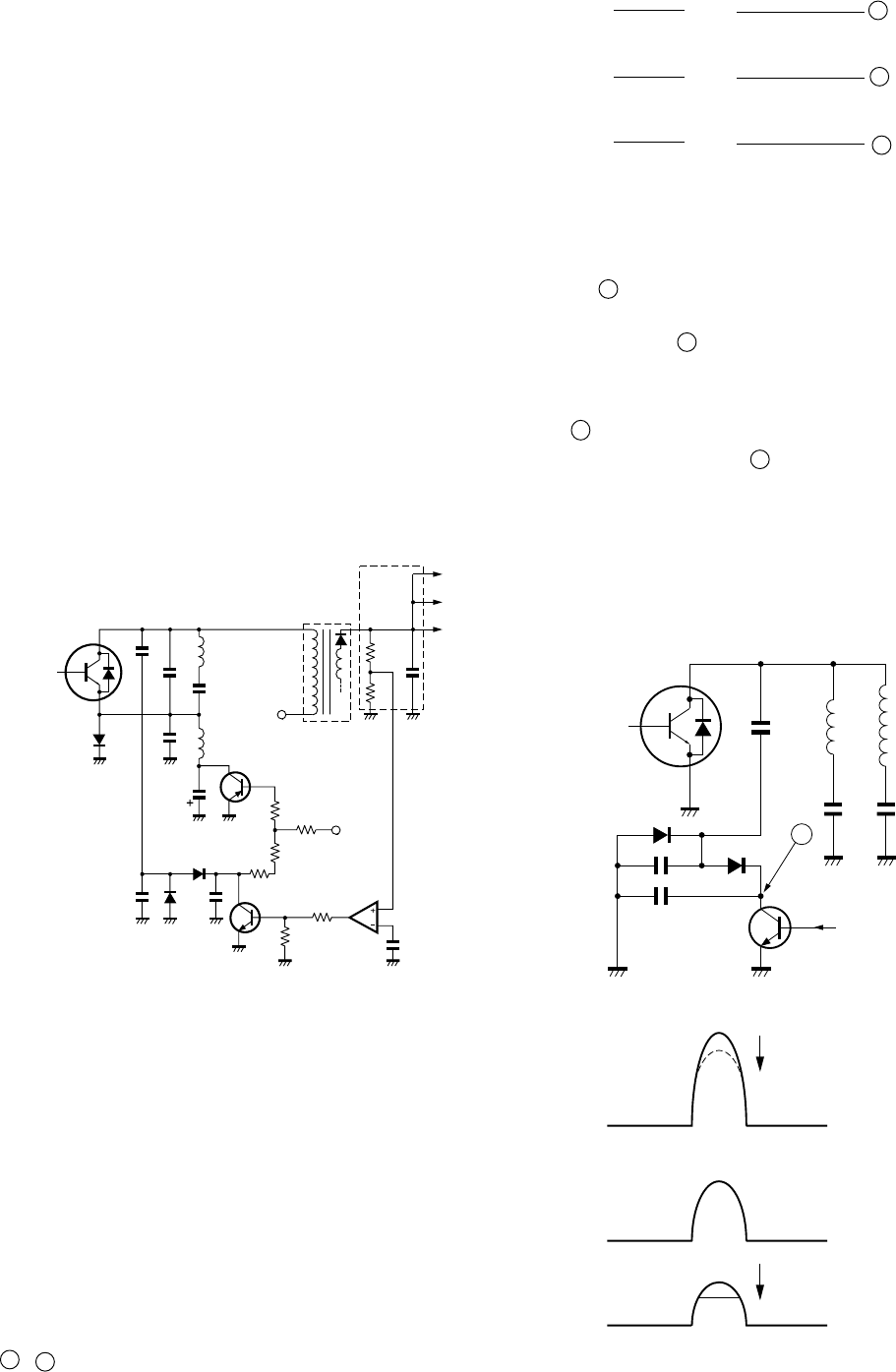

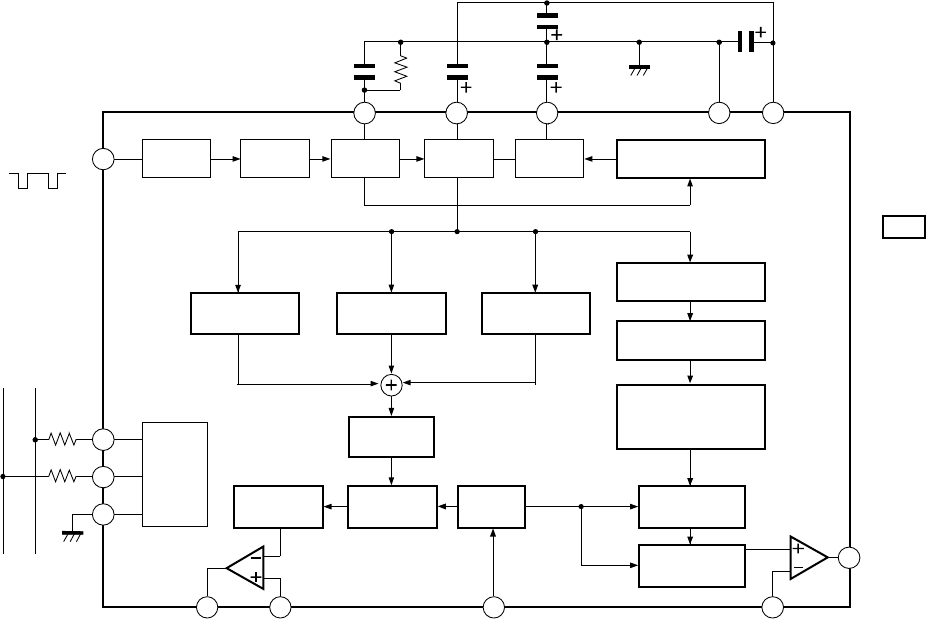

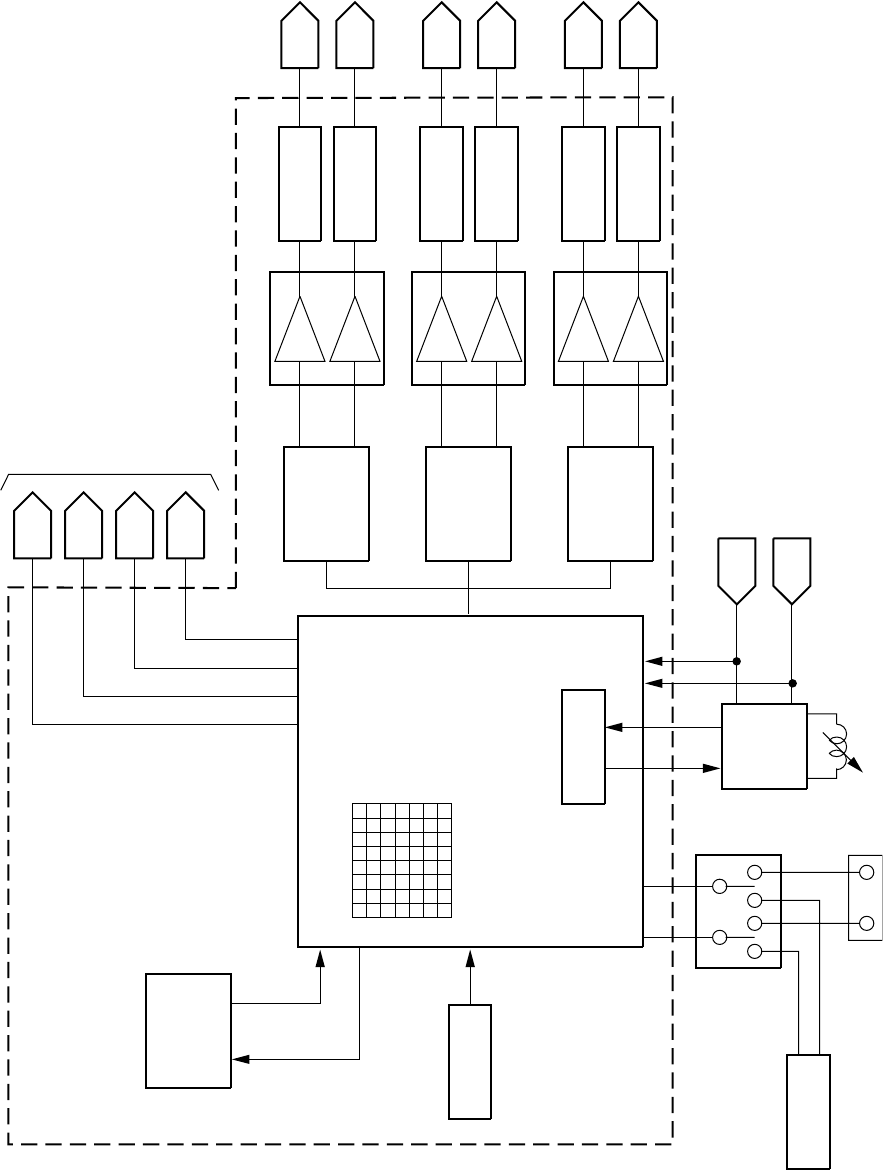

7. SYSTEM BLOCK DIAGRAM

SCL 0

11

SDA 0

12

VSYNC

27

INT4

40

RMT OUT

3

MUTE

4

SP MUTE

5

V.sync

pulse

Audio mute

Speaker

mute

Remote

controller

output

6

5

QA02

Memory

24LC08BI/P

SDA SCL

DATA

25

CLK

22

CS

23

BUSY

24

RESET

26

15

14

QH30

C/C,EDS

XC144144P

SDA SCL

5856

CS BUSY

55

DATA

54

CLK

QR60

OSD

MB90091

59

60

QX01

WAC

TC9097F

SDA SCL

43

44

Q701

CONVER

T7K64

SDA SCL

HO01

SDA SCL

Main U/V tuner

ELA12L

HY01

SDA SCL

Sub U/V tuner

EL922L

2827

Q501

SDA SCL

VCD

TA1222AN

2021

HO02

SDA SCL

IF/MPX/A.PRO

MVUS5345

25

24

QV01

SDA SCL

AV SW

TA1218N

DPC unit

1920

QZ01

SDA SCL

YCS

TC9086F

QY91

SDA SCL

DUAL micro-

processor

39

40

QK06

SDA SCL

AUTO LIVE

38

SDA 1

37

SCL 1

35

RMT Remote

controller

light

receiving

unit

17

KEY-A Key

switch

33

RST

42

VDD

1

GND

21

VSS

7

POWER

31

XIN

8

LED

41

ACP

Power

supply

circuit

32

XOUT 8MHz

Clock

19

SGV

20

SGA

Signal

output

36

SYNC-AV1

16

AFT1 IN

Main screen

Sync det.

AFT det.

13

SYNC-AV2

2

AFT2 IN

Sub screen

Sync det.

AFT det.

18

KEY-B

QY03

POP

TC9092F

DATA CLK

QA01

TMP87CS38N-XXXX

Fig. 3-5

23

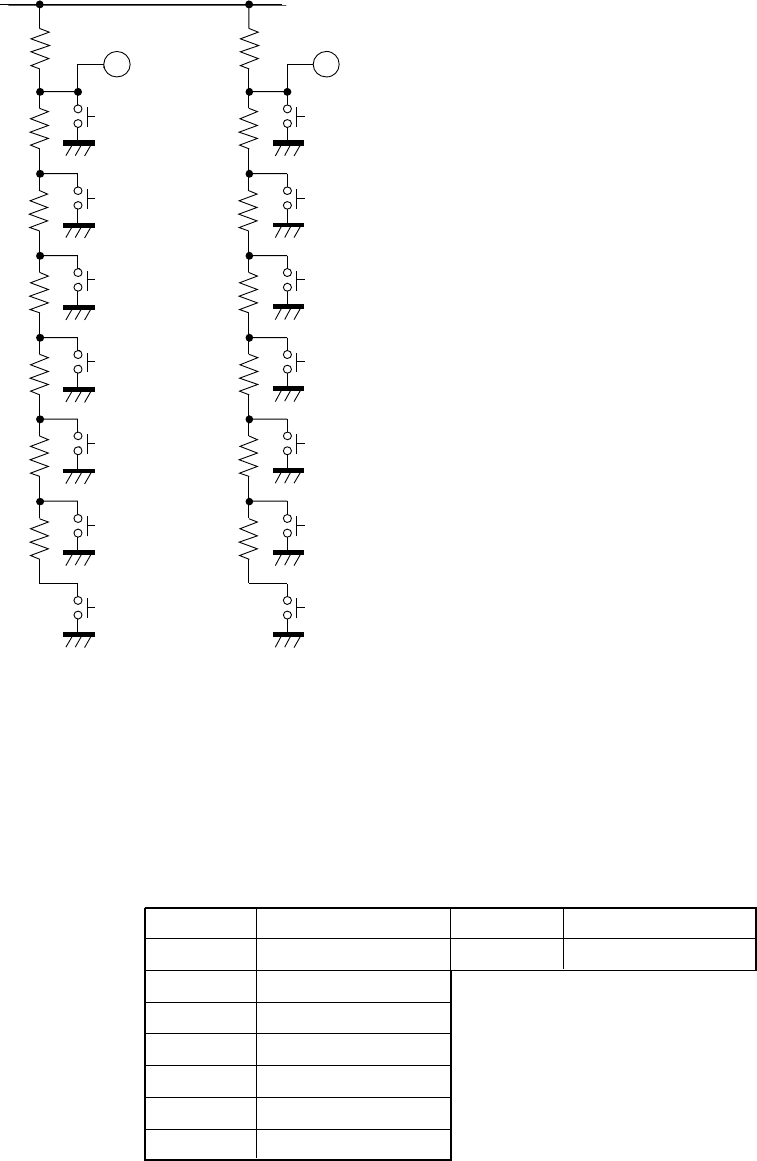

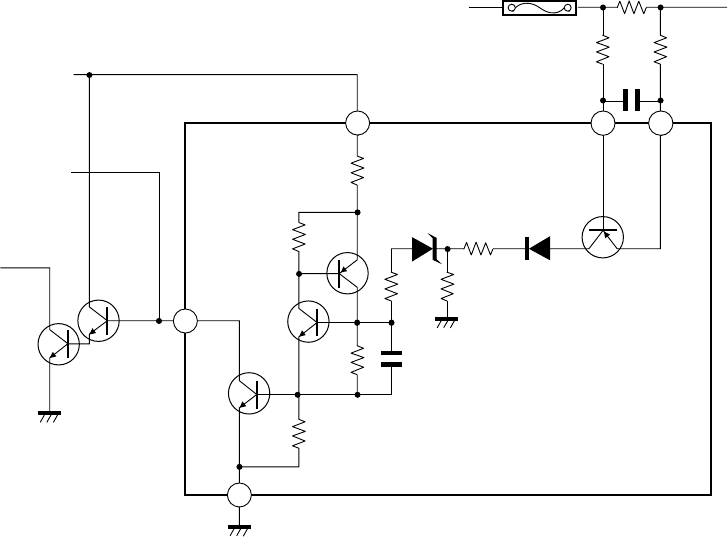

8. LOCAL KEY DETECTION METHOD

Local key detection in the N5SS chassis is carried out by

using analog like method which detects a voltage appears at

local key input terminals (pins 17 and 18) of the microcom-

puter when a key is pushed. With this method using two

local key input terminals (pins 17 and 18), key detection up

to maximum 14 keys will be carried out.

The circuit diagram shown left is the local key circuit. As

can be seen from the diagram, when one of keys among SA-

01 to SA-08 is pressed, each of two input terminals (pins 17

and 18) developes a voltage VIN corresponding to the key

pressed. (The voltage measurement and key identification

are carried out by an A/D converter inside the microproces-

sor and the software.

17 18

SA08

SA06

SA05

SA07

SA01

SA02

SA03

SA04

Fig. 3-6 Local key assignment

Table 3-1 Local key assignment

Key No. Function Key No. Function

SA-02 POWER SA-01

DEMO START/STOP

SA-03 CH UP

SA-04 CH DN

SA-05 VOL UP

SA-06 VOL DN

SA-07 ANT/VIDEO, ADV

SA-08 MENU

24

9. REMOTE CONTROL CODE ASSIGNMENT

Custom codes are 40-BFH (TV set for North U.S.A.)

Code Applicable Applicable Conti-

Function to remote to TV set nuity

control

50H PIP STILL

51H PIP ON/OFF

52H Do not use. Old type core power ON

53H PIP SWAP

54H PIC SIZE

55H DSP F/R

56H WIDE/SCROLL

57H CAPTION

58H EXIT

59H CYCLONE, SBS

5AH SET UP

5BH OPTION

5CH SUB WOOFER UP

5DH

SUB WOOFER DOWN

5EH

5FH

80H MENU

81H EDS

82H ADV UP

83H ADV DWN

84H

85H GUIDE

86H THEME

87H LIST

88H PIP CONTROL

89H ENTER/TUNE

8AH PAGE UP

8BH DATA UP

8CH PAGE DN

8DH DATA DN

8EH CANCEL

8FH REC

90H

91H

92H Do not use. Old type core power ON

93H

94H

95H

96H

97H NOISE CLEAN

98H

99H

9AH PIP VOLUME UP

9BH

9CH PIP CONTROL

9DH

9EH PIP VOLUME DOWN

9FH

Custom codes are 40-BFH (TV set for North U.S.A.)

Code Applicable Applicable Conti-

Function to remote to TV set nuity

control

00H 0 Channel

01H 1 Channel

02H 2 Channel

03H 3 Channel

04H 4 Channel

05H 5 Channel

06H 6 Channel

07H 6 Channel

08H 8 Channel

09H 8 Channel

0AH 100 Channel

0BH ANT 1/2

0CH RESET

0DH AUDIO

0EH PICTURE/FUNC

0FH TV/VIDEO

10H MUTE

11H CHANNEL SEARCH

12H POWER

13H MTS

14H ADD/ERASE

15H TIMER/CLOCK

16H AUTO PROGRAM

17H CHANNEL RETURN

18H DSP/SUR (TV/CATV)

19H CONTROL UP

1AH VOLUME UP

1BH CHANNEL UP

1CH RECALL

1DH CONTROL DOWN

1EH VOLUME DOWN

1FH CHANNEL DOWN

40H PIP LOCATE

41H PIP LOCATE

42H PIP LOCATE

43H PIP LOCATE

44H CARVER

45H SURROUND UP

46H SURROUND DOWN

47H VOCAL ZOOM

48H CHANNEL LOCK

49H

4AH PIP CHANNEL UP

4BH PIP CHANNEL DOWN

4CH PIP STILL/RELEASE

4DH

PIP ZOOM, ZOOM SIZE

4EH PIP LOCATE (CH SEARCH)

4FH PIP SOURCE

25

Custom codes are 40-BFH (TV set for North U.S.A.)

Code Applicable Conti-

Function to TV set nuty

D0H

D1H

D2H Do not use. Old type core power ON

D3H

D4H

D5H

D6H

D7H PIP VIDEO ADJ.

D8H STILL, FRAME ADVANCE

D9H

DAH SPEED

DBH

DCH ZOOM

DDH

DEH

DFH

E0H

PINCUTION/EW CORER (PARA/CNR)

E1H

VERTICAL S-CUVE CORRECTION/

VERTICAL M-CURVE

CORRECTION (VSC/FVC)

E2H

E3H

E4H

E5H

E6H

E7H

E8H

E9H

EAH

HORIZONTAL WIDTH (WID/PARA)

EBH

TRAPEZOIDE CORRECTION (TRAP)

ECH TEST TONE

EDH DOLBY

EEH

3 DIMENTIONAL Y/C SEPARATION

EFH DPC

E0H

STANDARD (HEIGHT LINEARITY) (VLIN/HIT)

E1H

WIDE (HEIGHT ® LINEARITY) (VLIN)

F2H SCROOL

F3H

WIDE 1, 2, 3

F4H

F5H

F6H

F7H

F8H

F9H

FAH

FBH

FCH

FDH

FEH

FFH

Custom codes are 40-BFH (TV set for North U.S.A.)

Code Applicable Conti-

Function to TV set nuty

A0H SUB-BRIGHT ADJUSTMENT

A1H G. DRIVE ADJUSTMENT

A2H B. DRIVE ADJUSTMENT

A3H

A4H

CUTOFF DRIVE 40H INITIALIZING,

HORIZONTAL ONE LINE

A5H R. CUTOFF ADJUSTMENT

A6H G. CUTOFF ADJUSTMENT

A7H B. CUTOFF ADJUSTMENT

A8H

MEMORY ALL AREA INITIALIZE

A9H PIP BRIGHT ADJUSTMENT

AAH SUB CONTRAST ADJUSTMENT

ABH

HOR, VER PICTURE POSITON ADJUSTMENT

ACH SUB COLOR ADJUSTMENT

ADH SUB TINT ADJUSTMNET

AEH ADJUSTMENT-UP

AFH ADJUSTMENT-DOWN

B0H

HORIZONTAL ONE LINE: SERVICE

B1H DSP ON/OFF

B2H TEXT-1

B3H

TV/PIP VIDEO CHANGE-OVER

B4H CAPTION-1

B5H

B6H

B7H TV/CABLE CHANGE-OVER IN

SAME TIME ON MAN AND SUB

B8H HOTEL SETTING MENU

B9H DATA 4 TIMES SPEED UP

BAH DATA 4 TIMES SPEED DOWN

BBH

CHANGE-OVER OF HOTEL/NORMAL

BCH PIP CENTER

BDH M MODE

BEH CAPTON OFF

BFH ALL CHANNEL PRESET

C0H

C1H DIRECT WIDE 1

C2H DIRECT FULL

C3H

C4H

C5H

C6H

C7H

C8H

C9H

CAH

CBH

CCH

CDH

CEH

CFH

26

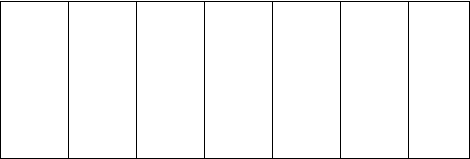

MODELS

CN35F90

CN35F95

CX35F70

TW56F80

TW40F80

TP61F90

TP61F80

TP55F80

TP55F81

TP50F90

TP50F60

TP50F61

D7

0

0

1

0

1

0

0

0

0

0

1

1

D6

*

*

*

*

*

*

*

*

*

*

*

*

D5

0

0

0

0

0

0

0

0

0

0

0

0

D4

0

0

1

0

1

0

1

1

1

0

1

1

D2

0

0

0

0

0

0

0

0

0

0

0

0

D1

0

0

1

1

1

1

1

1

1

1

1

1

D3

*

*

*

*

*

*

*

*

*

*

*

*

D0

*

*

*

*

*

*

*

*

*

*

*

*

HEX

00H

00H

02H

02H

92H

02H

12H

12H

12H

02H

92H

92H

D7

0

0

0

0

0

0

0

0

0

0

0

0

D6

0

0

0

0

0

0

0

0

0

0

0

0

D5

0

0

0

0

0

0

0

0

0

0

0

0

D4

0

0

0

1

1

1

1

1

1

1

1

1

D2

0

0

0

1

0

1

0

0

0

1

0

0

D3

0

0

0

1

1

1

0

0

0

0

0

0

D0

*

*

*

*

*

*

*

*

*

*

*

*

HEX

00H

00H

00H

1CH

18H

1CH

18H

10H

10H

14H

10H

10H

D1

*

*

*

*

*

*

*

*

*

*

*

*

OPT0 OPT1

Normal 0/Free run 1

NON0/CONV1

NON0/3DYC

NON0/DOLBY1

NOT USED

NOT USED

DSP0/SRD1

NOT USED

PP0/MP1

SS/0 NONSS/1

NOT USED

Normal 0/f0 STOP 1

CYC0/SBS1

NOT USED

MODE:

Fixed

Normal00

STD: 01

HRC: 10

1RC: 11

9-1. Optional Setting for Each Model

• When the character generation is changed from

MB90091-107 TO MB90091-108, D5 bit of OPT0 in

the design data should be set to “1”.

27

10. ENTERING TO SERVICE MODE

1. PROCEDURE

(1) Press once MUTE key of remote hand unit to indicate

MUTE on screen.

(2) Press again MUTE key of remote hand unit to keep

pressing until the next procedure.

(3) In the status of above (2), wait for disappearing of in-

dication on screen.

(4) In the status of above (3), press MENU (Channel set-

ting) key on TV set.

2. Service mode is not memorized as the last-memory.

3. During service mode, indication S is displayed at upper

right corner on screen.

11. TEST SIGNAL SELECTION

1. In OFF state of test signal, SGA terminal (Pin 20) and

SGV terminal (Pin 21) are kept “L” condition.

2. The function of VIDEO test signal selection is cyclically

changed with VIDEO key (remote unit).

12. SERVICE ADJUSTMENT

1. ADJUSTMENT MENU INDICATION ON/OFF :

MENU key (on TV set)

2. During display of adjustment menu, the followings are

effective.

a) Selection of adjustment item :

POS UP/DN key (on TV/remote unit)

b) Adjustment of each item :

VOL UP/ DN key (on TV / remote unit)

c) Direct selection of adjustment item

R CUTOFF : 1 POS (remote unit)

G CUTOFF : 2 POS (remote unit)

B CUTOFF : 3 POS (remote unit)

d) Data setting for PC unit adjustment

SUB CONTRAST : 4 POS (remote unit)

SUB COLOR : 5 POS (remote unit)

SUB TINT : 6 POS (remote unit)

e) Horizontal line ON/OFF : VIDEO (on TV set)

f) Test signal selection : VIDEO (remote unit)

* In service mode, serviceable items are limited.

3. Test audio signal ON / OFF : 8 POS (remote unit)

* Test audio signal : 1 kHz

4. Self check display : 9 POS (remote unit)

* Cyclic display (including ON/OFF)

5. Initialization of memory :

CALL (remote unit) + POS UP (on TV set)

6. Initialization of self check data :

CALL (remote unit) + POS DN (on TV set)

7. BUS OFF :

CALL (remote unit) + VOL UP (on TV set)

Test Signal No.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Name of Pattern

Signal OFF

All black signal + R single color (OSD)

All black signal + G single color (OSD)

All black signal + B single color (OSD)

All black signal

All white signal

W/B

Black cross bar

White cross bar

Black cross hatch

White cross hatch

White cross dot

Black cross dot

H signal (bright area)

H signal (dark area)

Black cross + G signal color

(3) SGA (audio test signal) output should be square wave

of 1 kHz.

Table 3-2

28

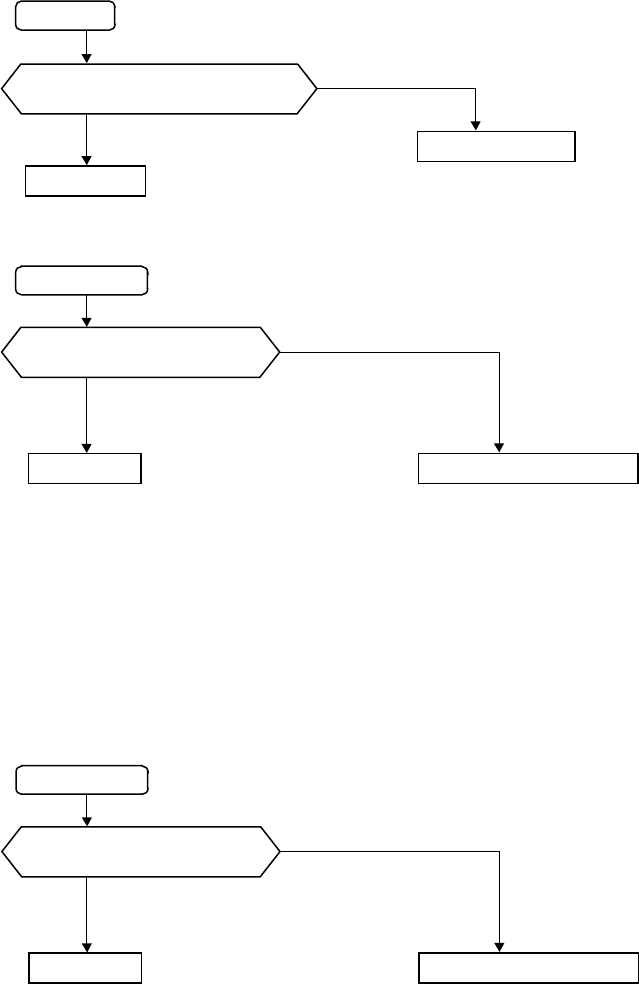

13. FAILURE DIAGNOSIS PROCEDURE

Model of N5SS chassis is equipped with self diagnosis func-

tion inside for trouble shooting.

13-1. Contents to be Confirmed by Customer

Contents of self diagnosis

Contents of self diagnosis

< Countermeasure in case that phonomenon always arises >

B. Detection of shortage in BUS line.

C. Check of comunication status in BUS line.

D. Check of signal line by sync signal detection.

E. Indication of part code of microcomputer (QA01).

F. Number of operation of power protection circuit.

Display items and actual operation

Display items and actual operation

(Example of screen display)

SELF CHECK

Part coce of QA01

Number of operation of

power protection circuit

Short check of bus line

Communication check of

busline

NO. 239XXXX

POWER: 000000

BUS LINE: OK

BUS CONT: OK

BLOCK: UV V1 V2

QV01, QV01S

E

F

B

C

D

Table 3-3

Contents of self diagnosis

A. DISPLAY OF FAILURE INFORMATION IN NO

PICTURE (Condition of display)

1. When power protection circuit operates;

2. When I2C-BUS line is shorted;

Display items and actual operation

Power indicator lamp blinks and picture does not come.

1. Power indicator red lamp blinks. (0.5 seconds interval)

2. Power indicator red lamp blinks. (1 seconds interval)

If these indication appears, repairing work is required.

13-2. Contents to be Confirmed in Service Work (Check in self diagnosis mode)

Table 3-4

13-3. Executing Self Diagnosis Function

[CAUTION]

(1) When executing block diagnosis, get the desired input

mode (U/V BS VIDEO1, 2, 3) screen, and then enter

the self diagnosis mode.

(2) When diagnos other input mode, do again diagnosis

operation.

13-3-1. Procedure

(1) Set to service mode.

(2) Pressing “9” key on remote unit displays self diagno-

sis result on screen.

Every pressing changes mode as below.

(3) To exit from service mode, turn power off.

SERVICE mode SELF DIAGNOSIS mode

29

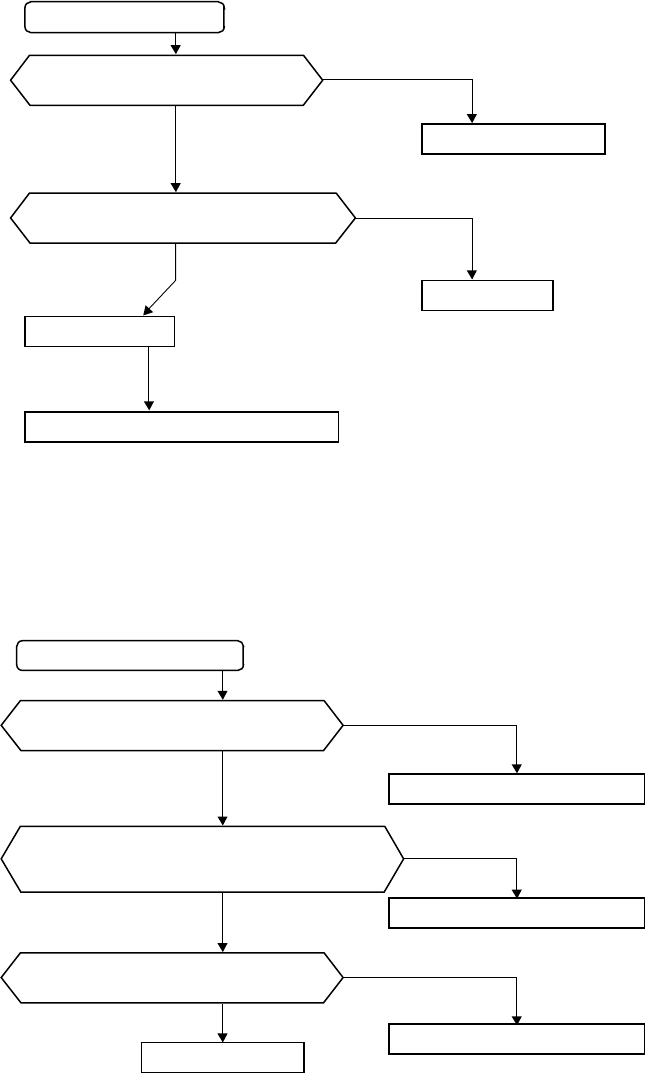

13-4. Understanding Self Diagnosis Indication

In case that phenomenon always arises. See Fig. 3-7 .

(Example of screen display)

SELF CHECK

Part coce of QA01

Number of operation of

power protection circuit

Short check of bus line

Communication check of

busline

NO. 239XXXX

POWER: 000000

BUS LINE: OK

BUS CONT: OK

BLOCK: UV V1 V2

QV01, QV01S

E

F

B

C

D

Table 3-5

Item

BUS LINE

BUS CONT

BLOCK: UV1

UV2

V1

V2

Contents

Detection of bus line short

Communication state of bus line

The sync signal part in each video signal

supplied from each block is detected.

Then by checking the existence or non of sync

part, the result of self diagnosis is displayed

on screen. Besides, when “9” key on remote

unit is pressed, diagnosis operation is first

executed once.

Instruction of results

Indication of OK for normal result, NG for abnormal

Indication of OK for normal result

Indication of failure place in abnormality

(Failure place to be indicated)

QA02 NG, H001 NG, Q501 NG, H002 NG, QV01 NG, Q302

NG, QY02 NG, HY01 NG, QD04 NG, QM01 NG, Q701 NG

Note:

The indication of failure place is only one place though

failure places are plural. When repair of a failure place

finishes, the next failure place is indicated. (The order of

priority of indication is left side.)

*Indication by color

• Normal block : Green

• Non diagnosis block : Cyan

Fig. 3-7

30

13-4-1. Clearing method of self diagnosis result

In the error count state of screen, press “CHANNEL DOWN”

button on TV set pressing “DISPLAY” button on remote unit.

CAUTION:

All ways keep the following caution, in the state of service

mode screen.

• Do not press “CHANNEL UP” button. This will cause

initialization of memory IC. (Replacement of memory

IC is required.)

• Do not initialize self diagnosis result. This will change

user adjusting contents to factory setting value. (Adjust-

ment is required.)

13-4-2. Method utilizing inner signal

(VIDEO INPUT 1 terminal should be open.)

(1) With service mode screen, press VIDEO button on re-

mote unit. If inner video signal can be received, QV01

and after are normal.

(2) With service mode screen, press “8” button on remote

unit. If sound of 1 kHz can be heard, QV01 and after

are normal.

* By utilizing signal of VIDEO input terminal, each circuit

can be checked. (Composite video signal, audio signal)

White

Yellow Cyan Green Magenta Red Blue

(COLOR BAR SIGNAL)

Color elements are positioned in sequence of

high brightness.

31

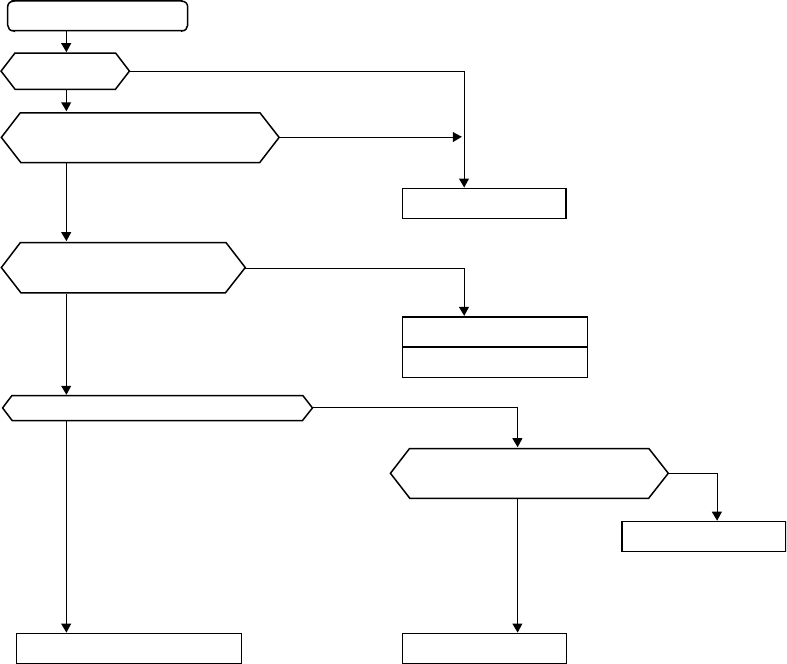

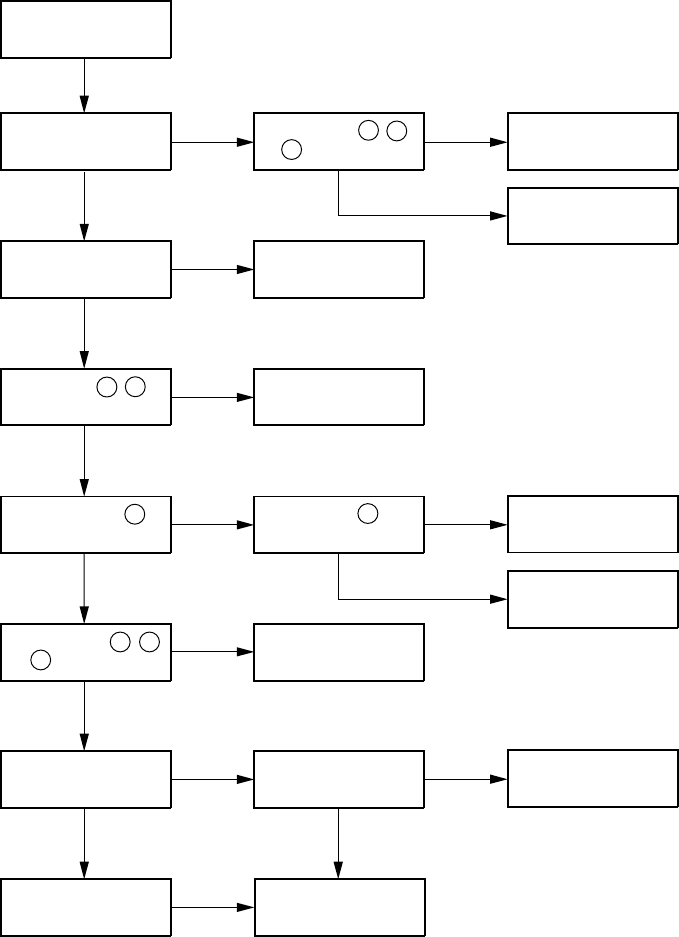

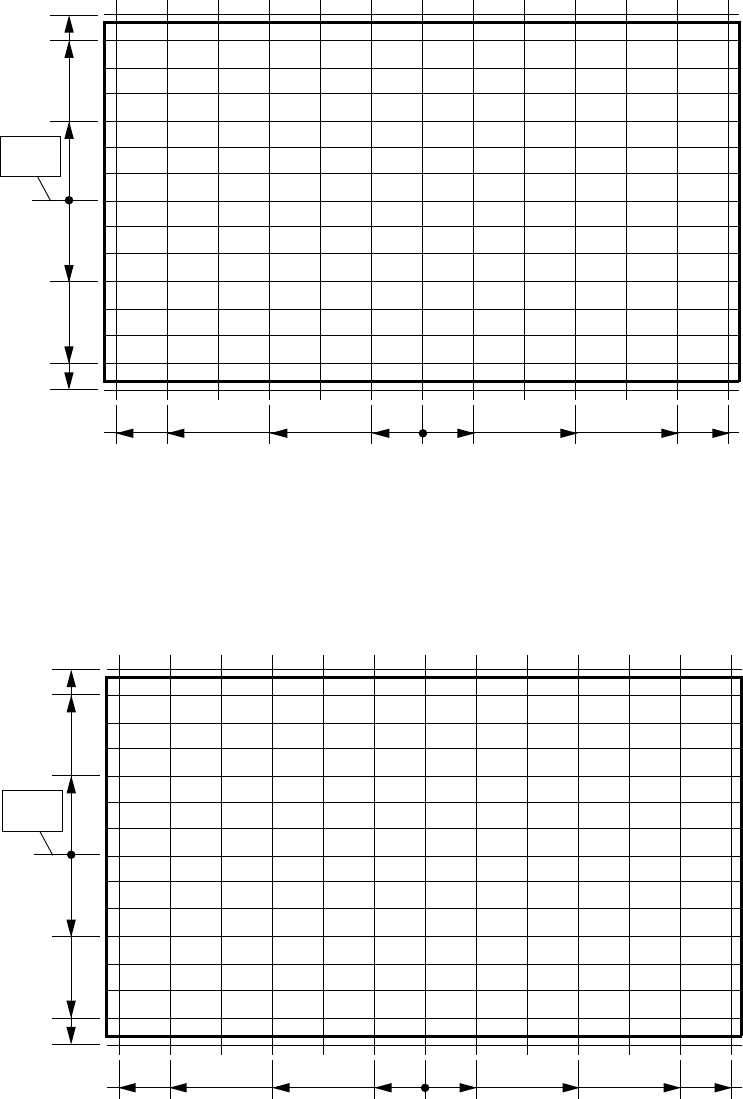

14. TROUBLESHOOTING CHART

14-1. TV does Not Turned ON

TV does not turned on.

Relay sound

Check of voltage at pin 7 of QA01

(DC 5V).

8MHz oscillation waveform

at pin 32 of QA01.

Pulse output at pins 37 and 38 of QA01.

Check relay driving circuit.

Check power circuit.

Check OSC circuit.

Replace QA01.

Voltage check at pin 32 of QA01

(DC 5V)

Check reset circuit.

Replace QA01.

YES

NG

NG

NG

NG

OK

NO

OK

OK

OK

32

14-2. No Acception of KEY-IN

14-3. No Picture (Snow Noise)

NG

OK

No picture

Voltage at pins of +5V, and 32V.

Check H001. Check tuner power circuit.

Key on TV

Voltage change at pins 17, 18 of

QA01 (5V to 0V).

Replace QA01.

Check key-in circuit.

NG

OK

NG

OK

Remote unit key

Pulse input at pin 35 of QA01,

When remote unit key is pressed.

Replace QA01

Check tuner power circuit.

33

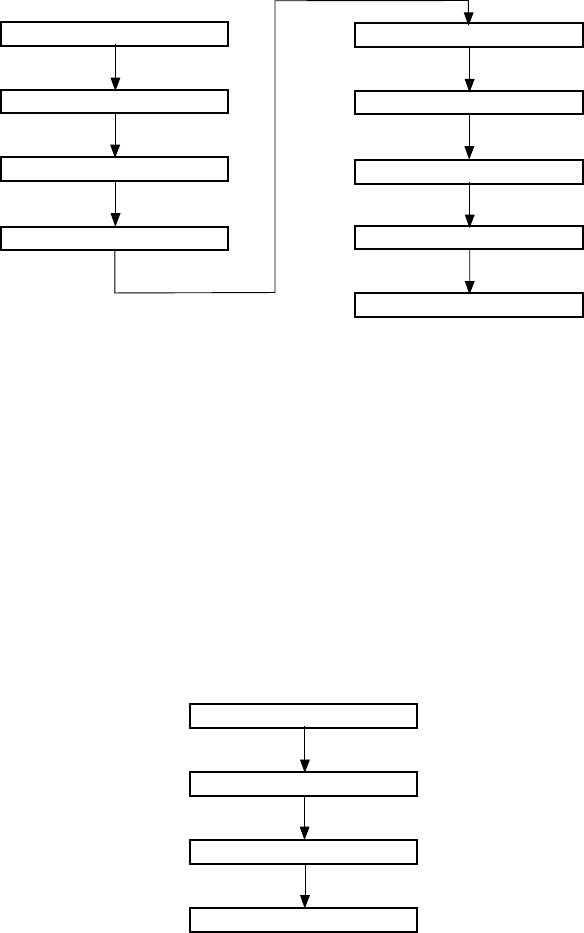

14-5. No Indication On Screen

14-4. Memory Circuit Check

NG

NG

OK

OK

OK

No indication on screen.

Check of RESET at 5V.

Check of CLK, CS, BUSY, DATA at

pin 22, 23, 24, 25 of QA01.

"H" = 5V or puls?

Check of character signal at pin 59, 60, 61

of QR60 (5V(p-p)).

Check V/C/D circuit.

Replace QA01 or QR60 or QR63.

Replace QA01 or QR60.

Replace QR60.

NG

NG

NG

OK

OK

Memory circuit check

Voltage check at pin 8 of QA02 (5V).

Pulse input at pins 5 and 6 of QA02

in memorizing operation.

Replace QA02.

Adjust items of TV set adjustment.

Note: Use replacement parts for QA02.

Check power circuit.

Check QA01.

34

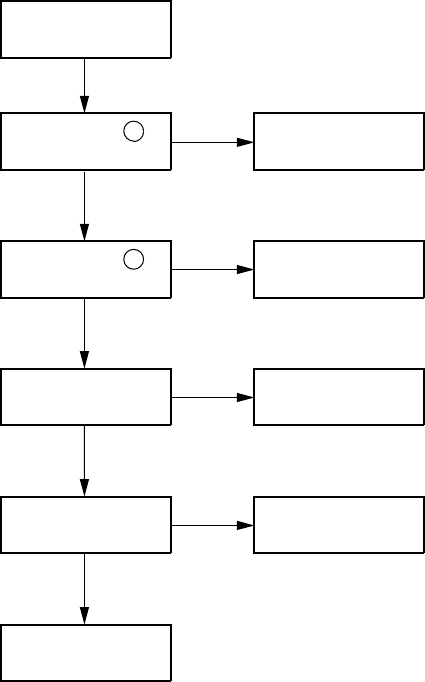

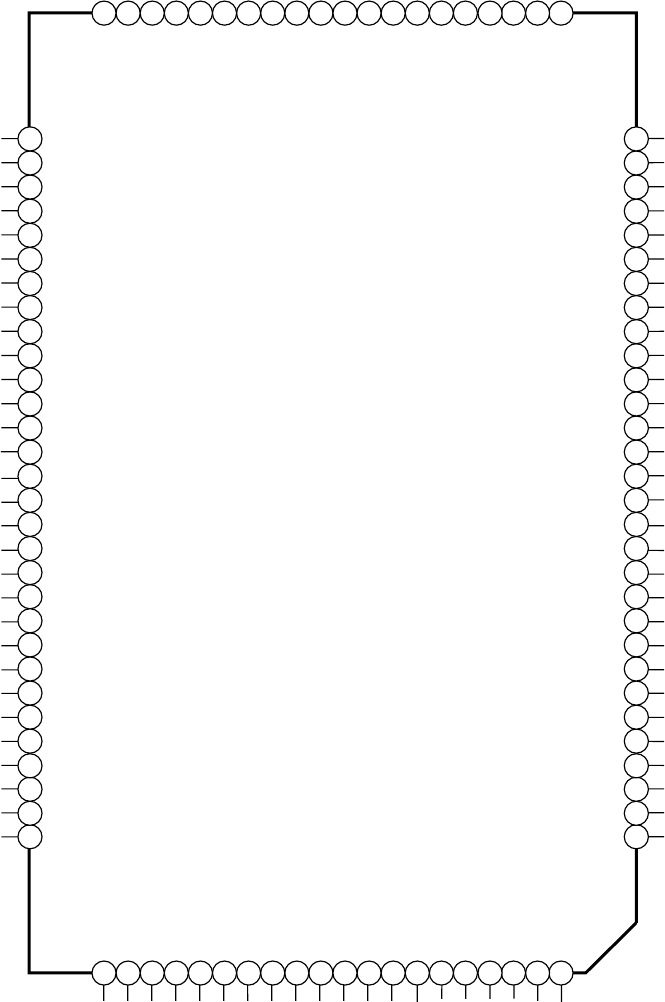

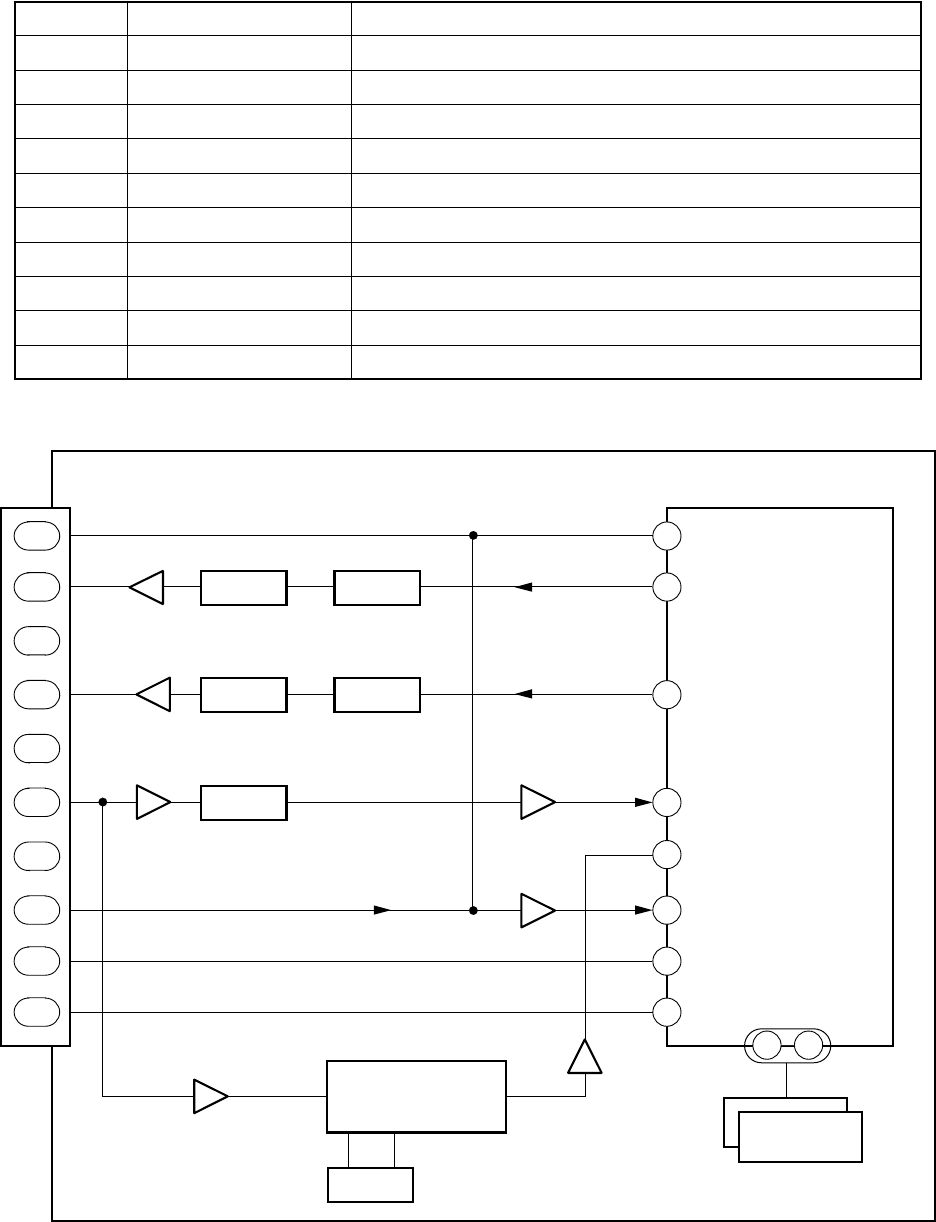

1. DVD SWITCH BLOCK DIAGRAM

53

52

51

4

5

6

13

15

C

Y

Y

Q

I

Y

Q

I

DVD SWITCH UNIT

QW01 TC4053BP

L

H

L

H

L

H

WAC UNIT

Y

Q (B - Y)

I (R- Y)

Y

Q

I

Y

Q

IYC

DUAL UNIT

Sub V.

Sub Y.

Sub C.

ZY01 Y/C SEPARATOR

42

Sub V.

36

34

Y

C

QV01 AV SW

TA1218N

21

VIDEO

3VIDEO

1

Insertion detection

10

DVD CONTROL

I C BUS

2

QA01

MAICROPROCESSOR

"L" = Normal

"H" = DVD

VIDEO2/

DVD

Q501 VCD

TA1222AN

I C BUS

2

MAIN

Y, Cr, Cb

Fig. 4-1

SECTION IV: DVD SWITCH CIRCUIT

35

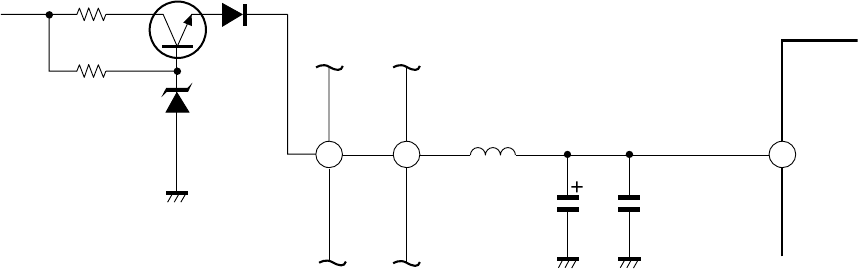

2. OUTLINE

In this model, the DVD input terminals are provided in or-

der to receive the color difference signals (Y, Cr, Cb) out-

put from a DVD player.

The luminance (Y) signal input for DVD input uses the

VIDEO input terminal in common with the VIDEO 2 input.

The terminals for color difference signal inputs Cr (R – Y)

and Cb (B – Y) are used exclusively.

The input identification for VIDEO 2 and DVD is carried

out by setting pin 21 of QV01 TA1218N (AV SW IC) from

“L” to “H” when the cable is connected to the Cb input ter-

minal with a switch equipped.

The main microprocessor QA01 sets pin 10 of QA01 from

“L” to “H” through I2C bus when pin 21 of AW SW IC

develops “H”.

Cb input

Open : at Cb input

RV26

75

RV27

10k

RV28 100k

+9v

Cb to DVD SW uni

t

21

QV01 TA1218N

Fig. 4-2

36

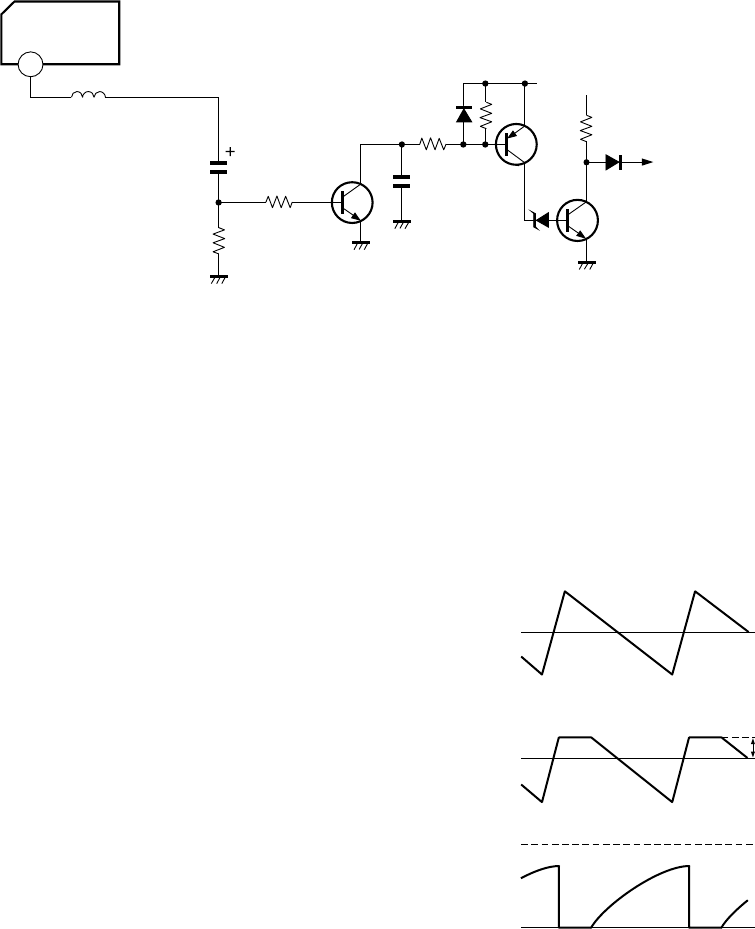

1. OUTLINE

A wide aspect conversion (hereafter called WAC) process (3/4

compression process in 4:3 mode and 1/2 compression process

on left screen in double window mode) is performed inside the

WAC unit (PB6348) in TW40F80.

Screen modes for TF40F80 contain THEATER WIDE1, THE-

ATER WIDE 2, THEATER WIDE3, FULL, NORMAL and

DOUBLE WINDOW modes. The video signal compression is

carried out only when either the NORMAL or DOUBLE WIN-

DOW mode is selected. In the modes other than the NORMAL

and DOUBLE WINDOW mode, the video signal input to WAC

unit is output without performing any process.

The screen in the DOUBLE WINDOW mode creates a single

screen by superimposing the left screen processed in the WAC

unit on the right screen processed in the DUAL unit.

On the left screen, the video signal sent is time-compressed to 1/

2 in horizontal direction to fit in the left half of the wide screen

with 16:9 aspect ratio. In this case, a black level of DC is at-

tached on the right half of the screen in this circuit. However,

this is superimposed on the right screen, so nothing is visible on

the screen.

In the normal screen, the video signal is 3/4 time-compressed

and side panels in the black level are added on sides of the screen.

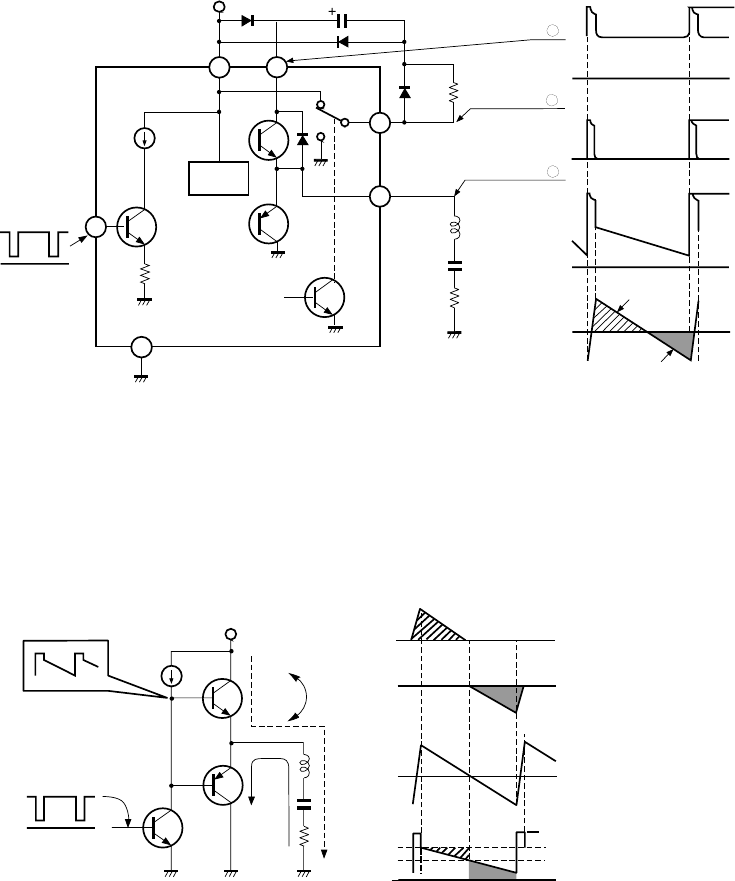

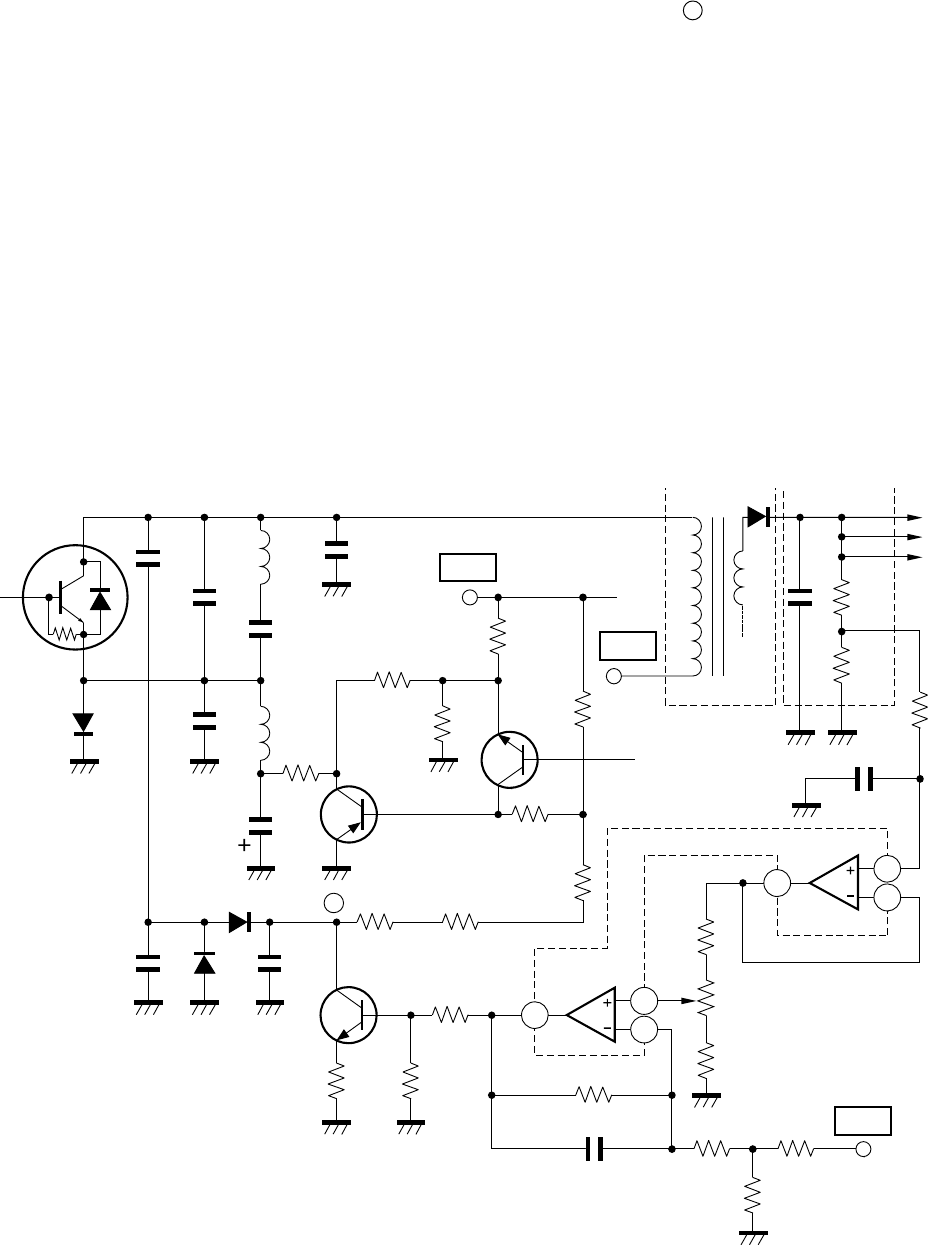

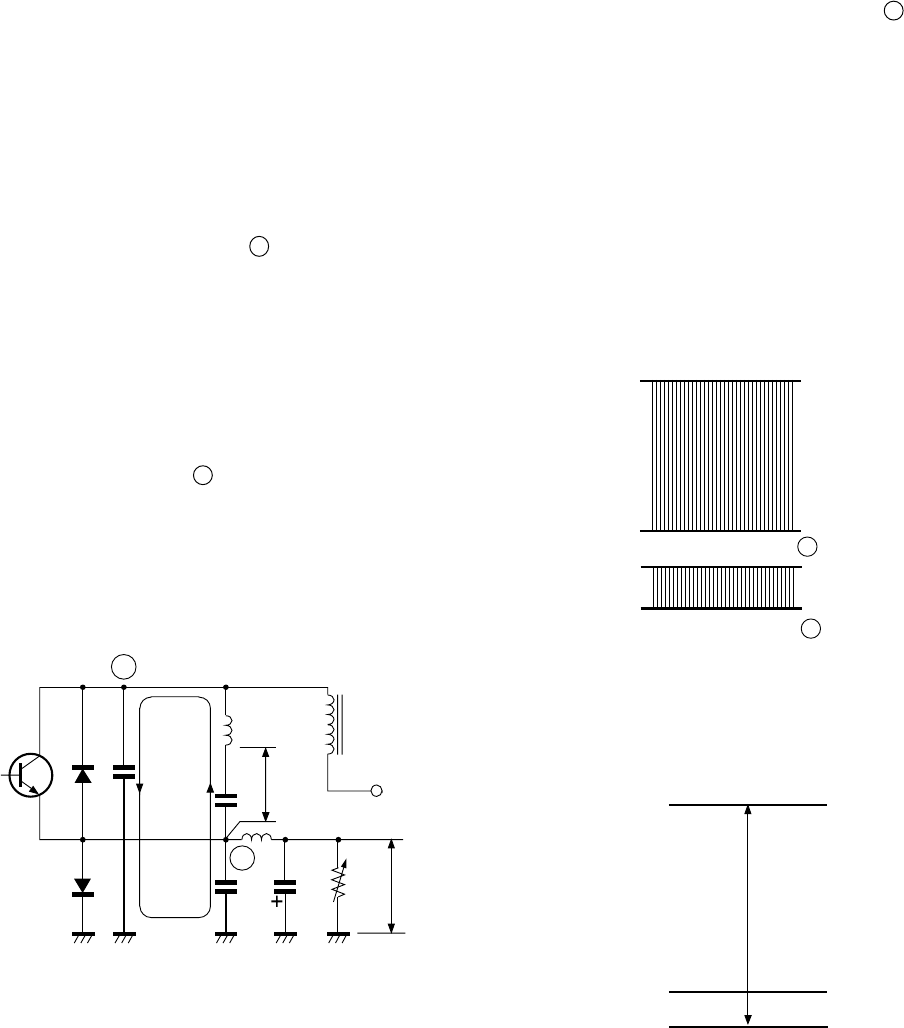

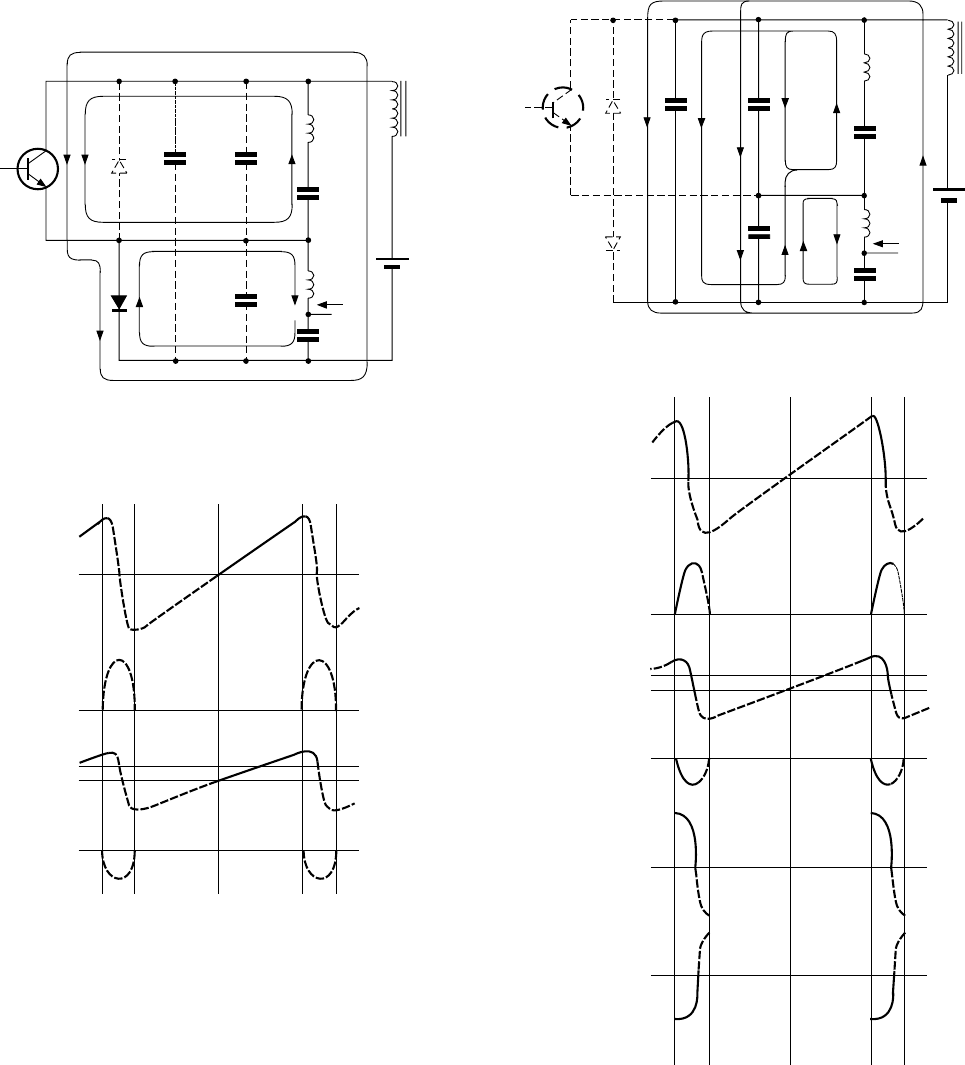

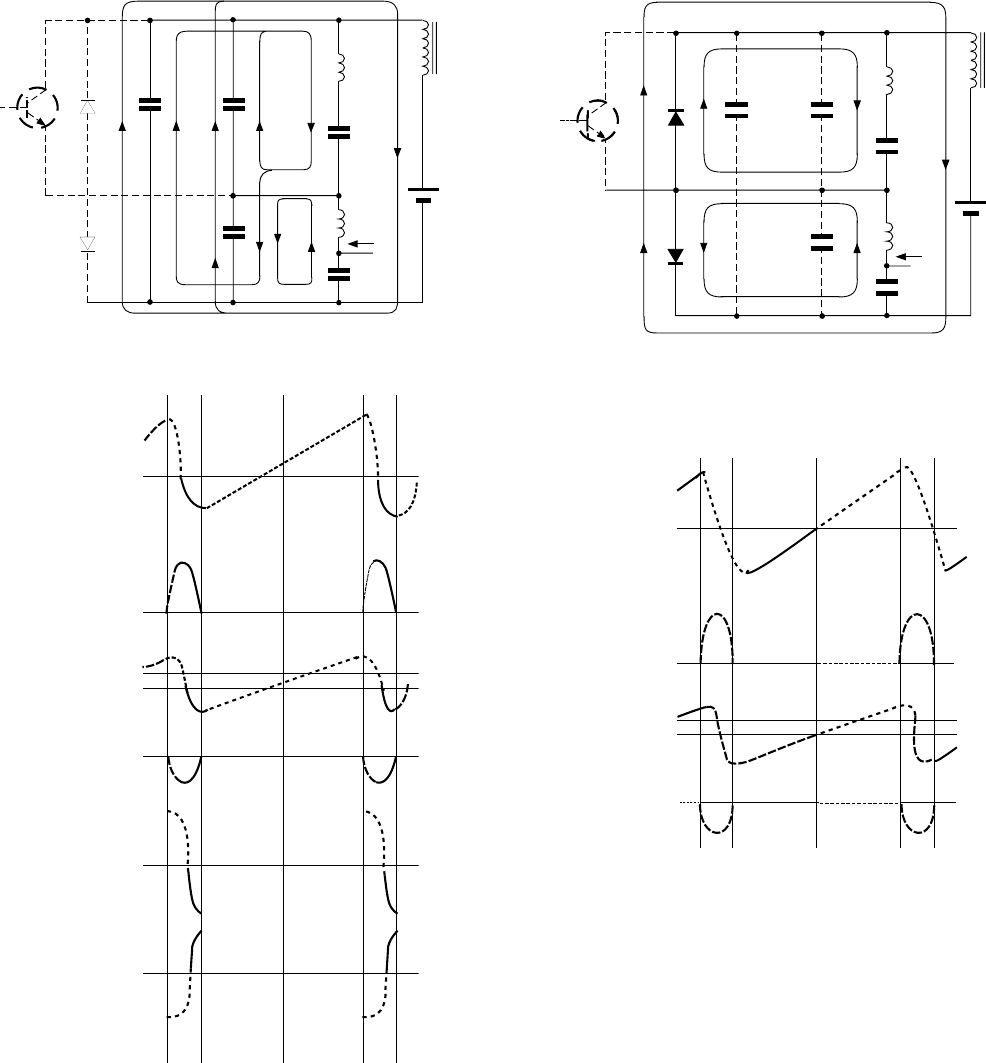

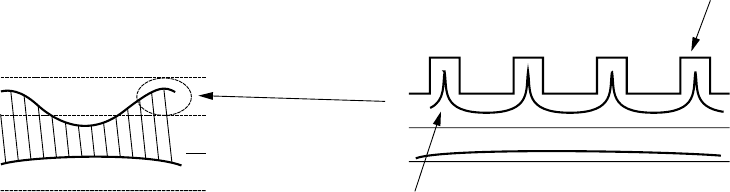

2. CIRCUIT OPERATION

2-1. Configuration

The WAC unit consists of a wide aspect conversion IC (QX01,

TC9097F, working as a central device), clock generation IC

(QX02, TA8667F), switch IC (QX03, TC4053BF), and periph-

eral circuits (LPF, AMP, emitter follower, etc.). The QX01

(TC9097F) contains an A/D converter, D/A converter, clamp cir-

cuit, VCO circuit, etc. and performs compression process, etc.

inside the IC for analog video signals entered according to con-

trols through IIC bus, thus providing the signal as an analog sig-

nal.

2-2. Operation

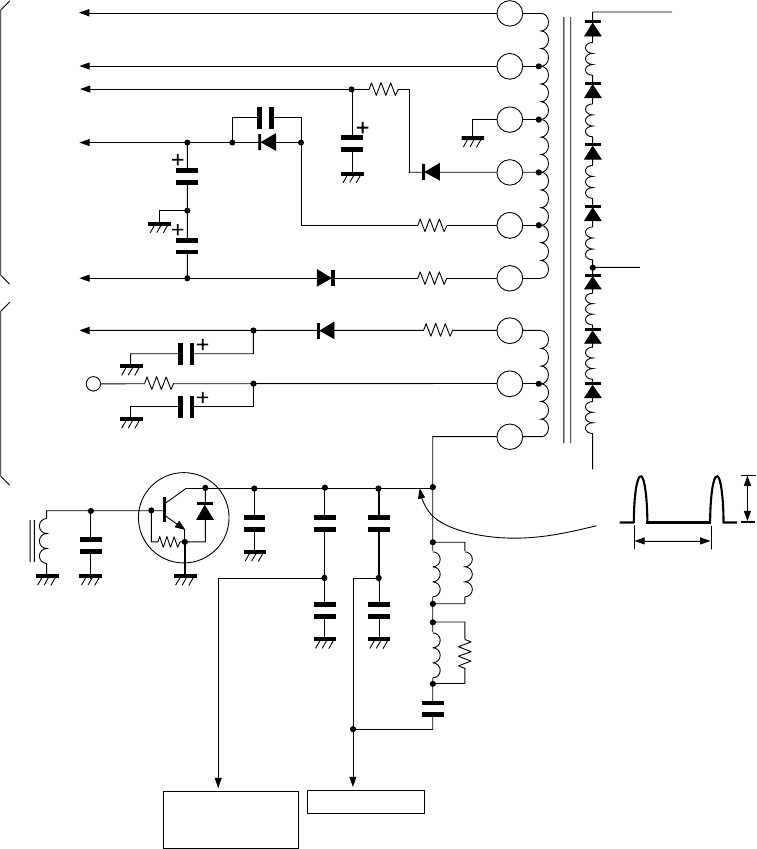

2-2-1. Signal Flow

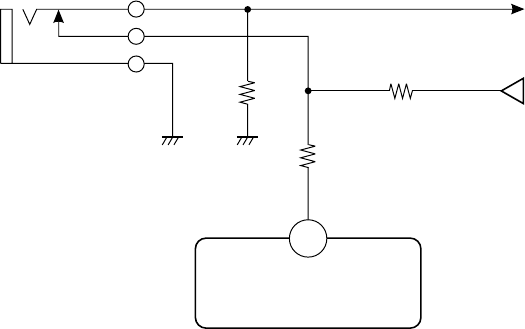

Fig. 5-1 shows a block diagram of this circuit. A Y signal en-

tered through pin 6 of PX01 passes a low pass filter an a 6 dB

amplifier, and enters pin 3 of QX01. On the other hand, I and Q

signals enter through pin 4 and 5 of PX01,

and pass a low pass filter and amplifiers in the same way as the

Y signal, and enter pins 1 and 78 of QX01 respectively.

The Y , I and Q signals entered are clamped by built-in clamp

circuit, converted into digital signals by the built-in A/D con-

verter. Moreover, their read/write operations are rated up by twice

or 3/4 times to perform a compression process of 1/2 or 3/4

times inside the built-in line memory. And then, a black level

signal is added to the open area (right half, or both sides of

screen). Next, the signal is converted to an analog Y, I, and Q

signals by a built-in D/A converter and output from pins 17, 13,

and 9. Parameters of 1/2, 3/4 phase of the video signal, phase of

the side panel, etc. are controlled through I2C bus, control sig-

nals of which enters from pins 7 and 8 of PX01.

Thus processed signals are fed to a low pass filter to remove

high frequency noises generated in QX01 and then fed to the

QX03 switching IC. The compressed signal and a not compressed

signal entered from PX01 are directly fed to QX03, and switched

by a signal showing compression/not compression (NCS = out-

put from pin 61 of QX01 and fed to the receive unit through

pins 5, 6, and 7 of PX02.

2-2-2. Clock Generation

The system clock for QX01 is generated by QX02 according to

an H reference signal supplied from pin 3 of PX02 and fed to

QX01 through QX19 and QX40. (The frequency is adjusted to

28.7 ± 0.2 MHz with LX18).

The compressing operation is carried out by setting the write

clock to 1/2 or 3/4 times by the built-in VCO with the reading

clock fed to pin 47 of QX01.

2-2-3. Timing Pulse Generation

Moreover, the WAC unit generates following timing pulses.

(1) VPout

Reference signal entered through pin 2 of PX02 enters pin

3 of QX01, and outputs at pin 8 of PX02 after delayed by

an amount required. The vertical reference signal is out-

put in modes other than the normal and double window

and fed to the vertical circuit. Accordingly, the raster be-

comes an horizontal one when the unit is disconnected.

(2) HVBLK

This pulse is a timing pulse showing a black extension

mask period in the normal and double window modes. It

outputs at pin 1 of PX02 and enters pin 30 of Q501 in the

receive unit.

SECTION V: WAC CIRCUIT

37

LPF

AMP

QX28 QX29 LX14 etc

QX26 QX27 LX13 etc

QX10

QX15

ISI

QSI Y WA

I WA

Q WA

I TH

Q TH

Y TH

YSI

IBC QSO

ISO

YSO

HRE

VMO

RCK

VDI

VBL

IBD

QX13

QX11

QX06 LX12 etc

1

151

17

13

9

VDP 57

NCS 61

12

2

5

52

47

78

3

59

60

2

3

4

5

6

7

8

I

Q

Y

9V-2

PX01

5V-3

GND

I IN

Q IN

Y IN

SCL 2

S

DA 2

1

2

3

4

5

6

7

8

LPF

AMP

LPF LPF

LX15 etc

LX16 etc

LX17 etc

LPF

LPF

AMP

QX20

QX22

QX24

10

11

18

QX21

QX19

ADJ LX18

QX18

HVBLK

PX02

VD IN

HD IN

GND

YD

ID

QD

VP OU

T

QX23

QX25

50

30

QX30

QX31

QX32

9

10

11

1

3

13

QX01

TC9097F

QX02 TA8667F

QX03 TC4053BF

Fig. 5-1 Wide aspect conversion unit block diagram (PB6348)

38

• Pin Function

Fig. 5-2 Pin function of TC9097F (QFP 80 pin)

25

1ISI

VRA2

YSI

NC

VBC

VRD2

VBD4

VDD3(DA2)

QSO

NC

VBD3

VSS3(DA2)

ISO

VRD1

NC

VDD2(DA1)

YSO

VBD2

VSS2(DA1)

VBD1

VSS4(VCO1)

VBV

NC

VFL1

BCP(TDI5)

NC

SE42(TDI6)

NCS(TDI7)

SDA

SCL

ACP(TMO0)

VDP(TMO1)

ISL(TMO2)

NC

QSL(TMO3)

SPT(TMO4)

VMO(TMO5)

HRF(TMO6)

VBL(TMO7)

NC

HBL(TMO8)

RCK

WCK

VDD(DIG)

NC

VSS5(VCO2)

NC

VFL2

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

VDD4(VCO1)

VLM

VDD(DIG)

HDI

NC

VDI

RESET

NC

NC

TST0

TST1

TST2

NC

HDF

VSS(DIG)

VDD5(VCO2)

VSS1(AD)

VBA

QSI

VBM

NC

VRA1

VDD1(AD)

NC

NC

VSS(DIG)

NC

TDI0

TDI1

TDI2

TDI3

TDI4

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65

39

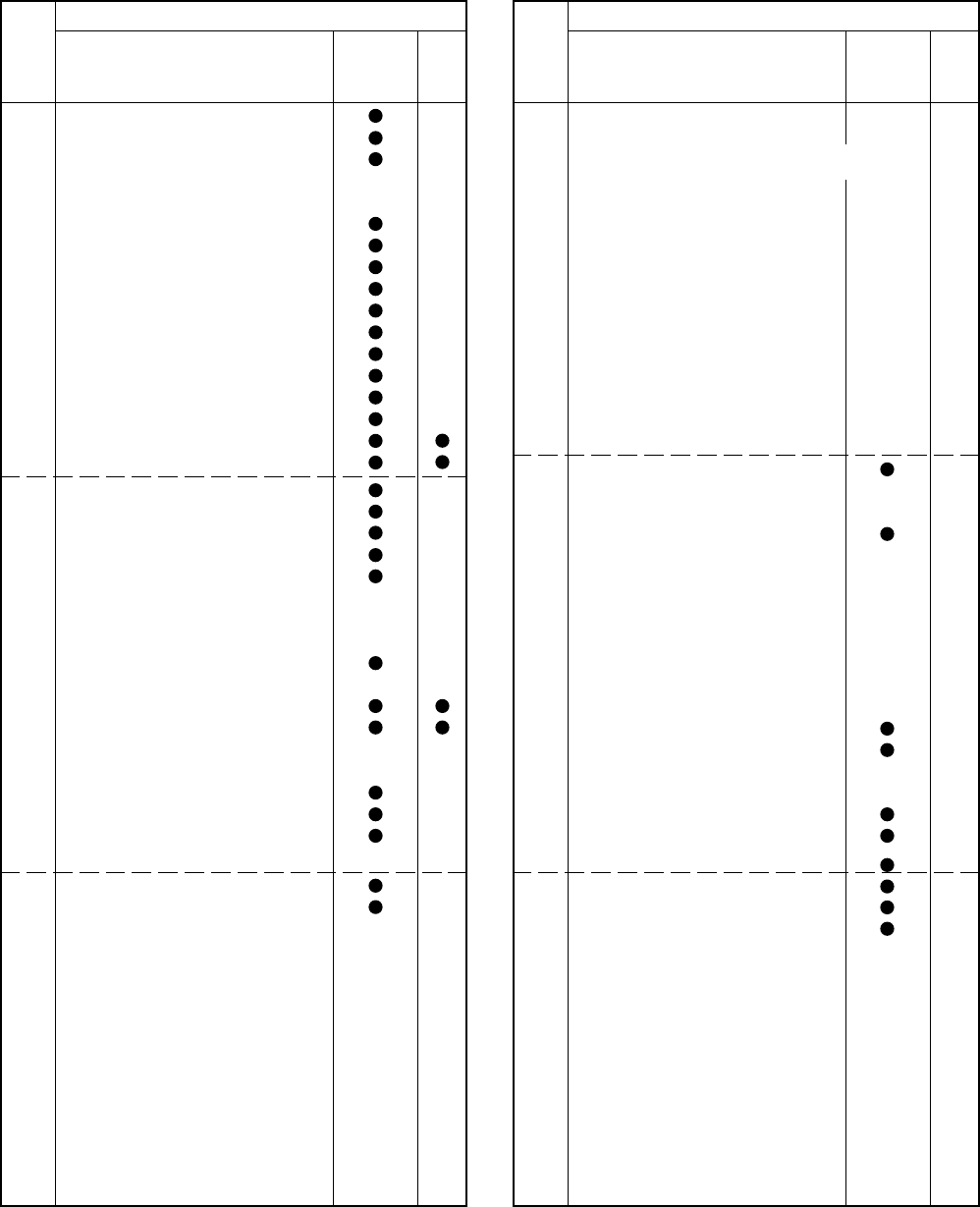

Table 5-1 Names and functions of TC9097F

I/O

I

–

I

–

–

–

–

–

O

–

–

–

O

–

–

–

O

–

–

–

–

–

I

–

–

–

–

I

–

I

I

–

–

I

I

I

–

Name

ISI

VRA2

YSI

NC

VBC

VBD2

VBD4

AVDD

QSO

NC

VBD3

AGND

ISO

VRD1

NC

AVDD

YSO

VBD2

AGND

VBD1

AGND

NC

VFV

VFL1

AVDD

VLM

VDD

HDI

NC

VD1

RESET

NC

NC

TST0

TST1

TST2

NC

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

Function

I color signal input

Reference voltage (low level) for AD1, AD2

Y signal input

–

Bias for clamp 1

Reference voltage for DA2, DA3

Bias 2 (high level) for DA2, DA3

Analog power

Q color signal output

–

Bias 2 (low level) for DA2, DA3

Analog ground

I signal output

Reference voltage for DA1

–

Analog power

Y signal output

Bias 1 (high level) for DA1

Analog ground

Bias 2 (high level) for DA1

Analog ground

–

Connected to VSS or VDD

Connected to VDD

Analog power

1/2 VDD for line memory

Digital power

Composite sync signal input

–

V sync signal input

Reset input (Normally: High level, Reset: Low level)

–

–

Test mode setting (normally connected to VSS)

Test mode setting (normally connected to VSS)

Test mode setting (normally connected to VDD)

–

40

No.

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

I/O

I

–

–

I

–

–

–

–

–

O

–

–

–

O

–

–

–

O

–

–

–

–

–

I

–

–

–

–

I

–

I

I

–

–

I

I

I

–

Name

HDF

GND

AVDD

VFL2

NC

AGND

CKSEL

VDD

WCK

RCK

HBL

NC

VBL

HRF

VMO

SPT

QSL

NC

ISL

VDP

ACP

SCL

SDA

NCS

SE42

NC

BCP

TD14

TD13

TD12

TD11

TD10

NC

GND

NC

NC

AVDD

VRA1

Function

Ext. H sync signal input

Digital ground

Analog power

Loop filter for VCO2

–

Analog ground

VDD

Digital power

Ext. clock input (memory write clock)

Ext. clock input (memory read clock)

H blanking signal

V blanking signal

H AFC reference signal

H AFC mask signal

Side panel timing signal

Q signal select pulse

–

I signal select pulse

V drive pulse

Later stage clamp pulse

I2C SCL signal input

I2C SDA signal input/output

Prefilter switch signal 1

Prefilter switch signal 2

–

Prestage clamp pulse output

Test input (normally connected to VSS)

Test input (normally connected to VSS)

Test input (normally connected to VSS)

Test input (normally connected to VSS)

Test input (normally connected to VSS)

–

Digital ground

Analog power

Reference voltage for AD1, AD2

41

I/O

–

–

I

–

–

No.

76

77

78

79

80

Name

NC

VBM

QSI

VBA

AGND

Function

–

Bias for MPX, clamp 2

Q color signal input

Bias for AD1, AD2

Analog ground

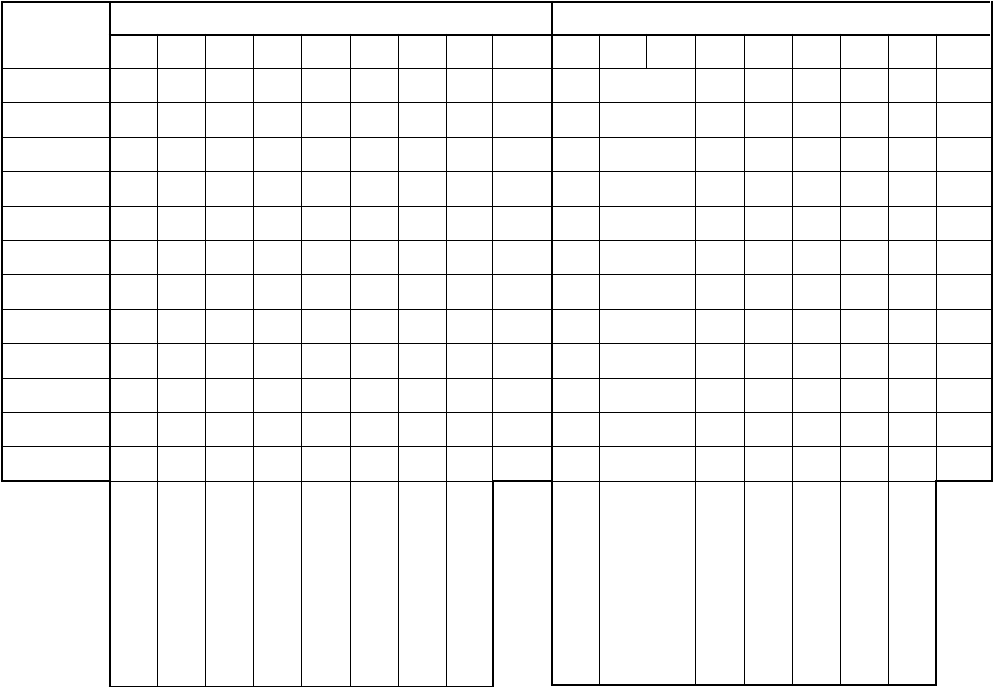

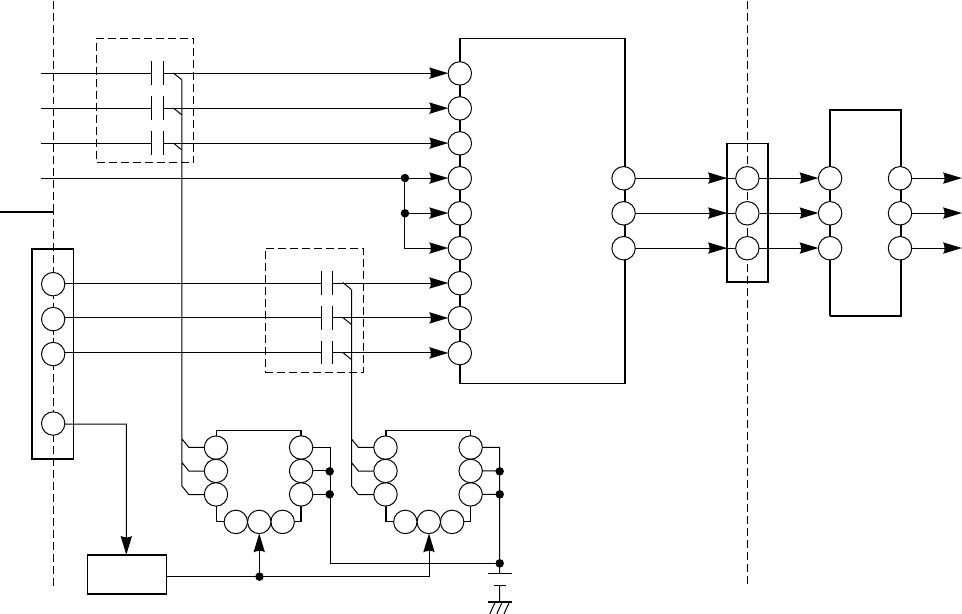

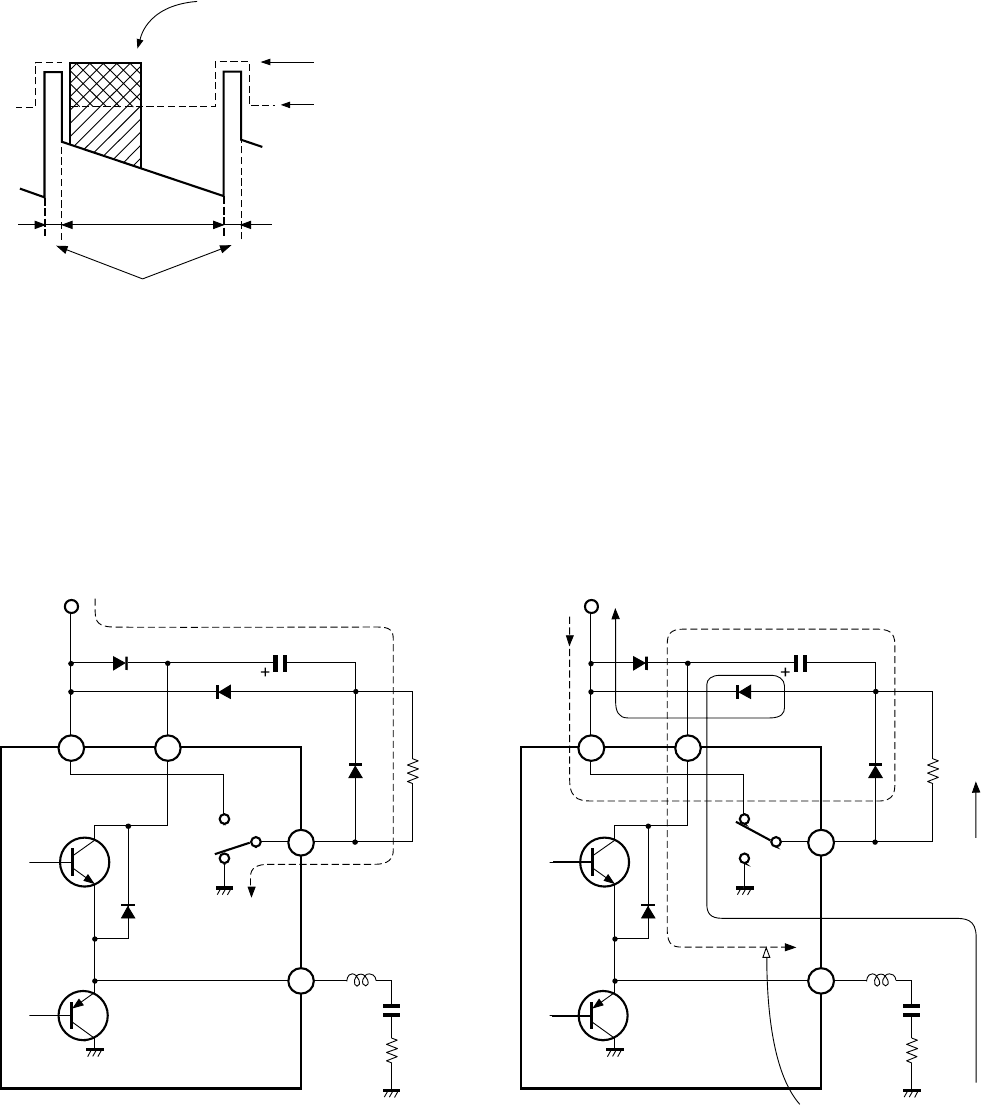

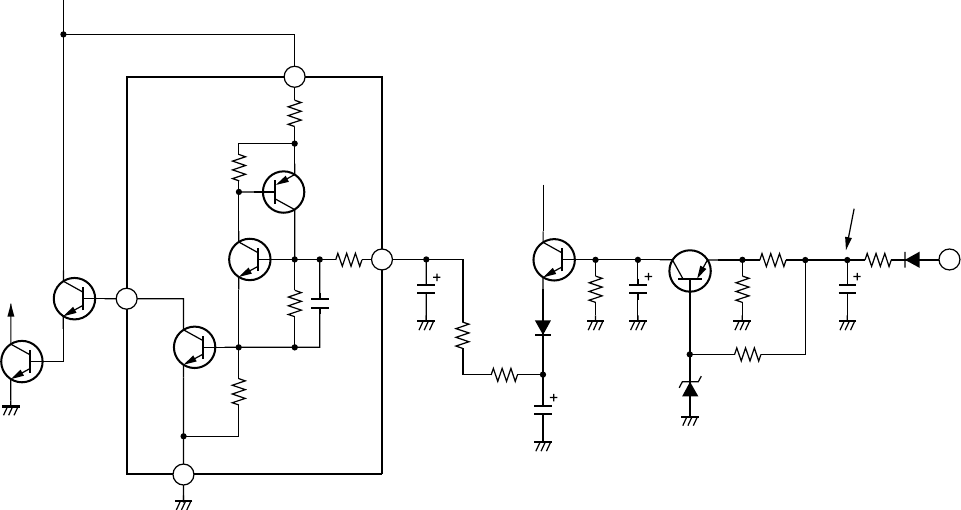

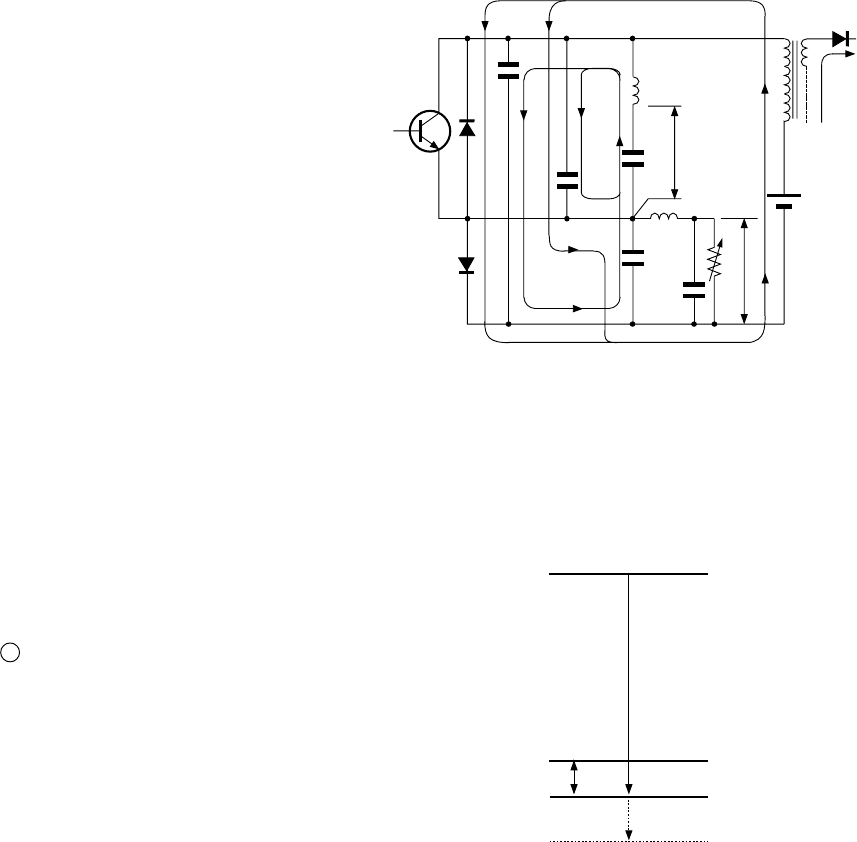

3. BLOCK DIAGRAM

1/2

MPX

&

CLAMP2

1/456

1/2

1/2

VCO2

1/2 1/2

I

2

C BUS

DECODER

VCO1

VSS5(VCO2)

VSS4(VCO1)

VDD4(VCO1)

VSS(Digital)

VDD(Digital)

VDD(Digital)

VBM

VRA2

VBA

VRA1

VBC

VSS1(AD)

VDD1(AD)

VLM

HDF

HDI

VDI

VSS(Digital)

VDD5(VCO2)

CLAMP1

AD2

AD1

TEST

CIRCUIT

TIMING

CONTROLER

LINE MEMORY (624x8)

LINE MEMORY (624x8)

DA1

VDD2(DA1)

VSS2(DA1)

VBD1

VBD2

VRD2

VBD3

HBL(TMO8)

VBL(TMO7)

HRF(TMO6)

VMO(TMO5)

SPT(TMO4)

QSL(TMO3)

ISL(TMO2)

VDP(TMO1)

ACP(TMO0)

SCL

NCS(TDI7)

SE42(TDI6)

BCP(TDI5)

VRD1

VBD4

YSO Y

DA2

DA3

LINE MEMORY (1248x8)

LINE MEMORY (1248x8)

POST

FILTER

ISO I

POST

FILTER

VDD3(DA2&3)

VSS3(DA2&3)

QSO Q

POST

FILTER

QSI

ISI

IPRE

FILTER

YSI

YPRE

FILTER

QPRE

FILTER

TST

RCK

WCK

TDI

SDA

SCL

VFL2

FILTER