Motorola Coldfire Mcf5281 Users Manual 5282UM

MCF5282 to the manual e9f134fe-e16d-4974-b62a-d3be4b7a3ce2

2015-01-23

: Motorola Motorola-Coldfire-Mcf5281-Users-Manual-271786 motorola-coldfire-mcf5281-users-manual-271786 motorola pdf

Open the PDF directly: View PDF ![]() .

.

Page Count: 816 [warning: Documents this large are best viewed by clicking the View PDF Link!]

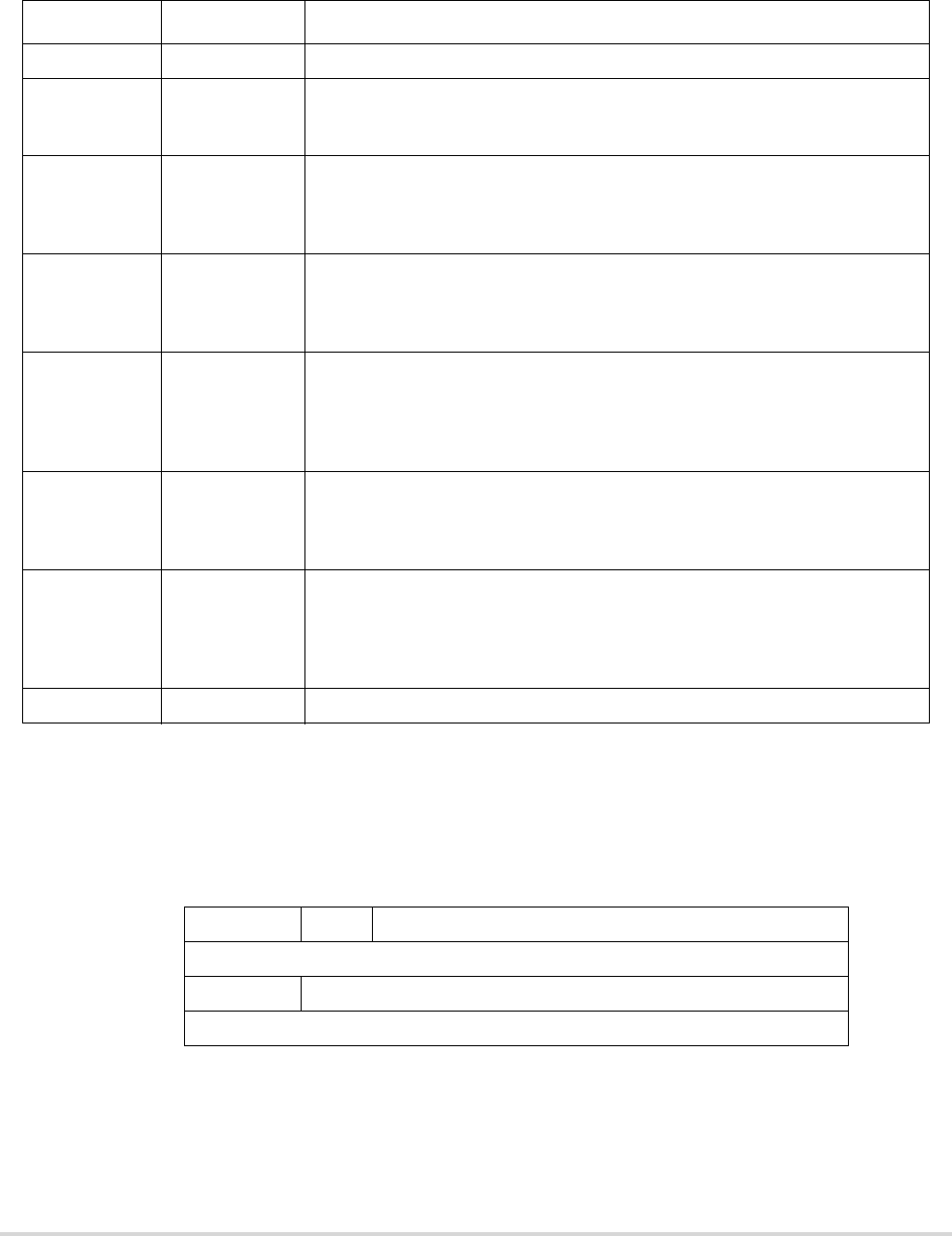

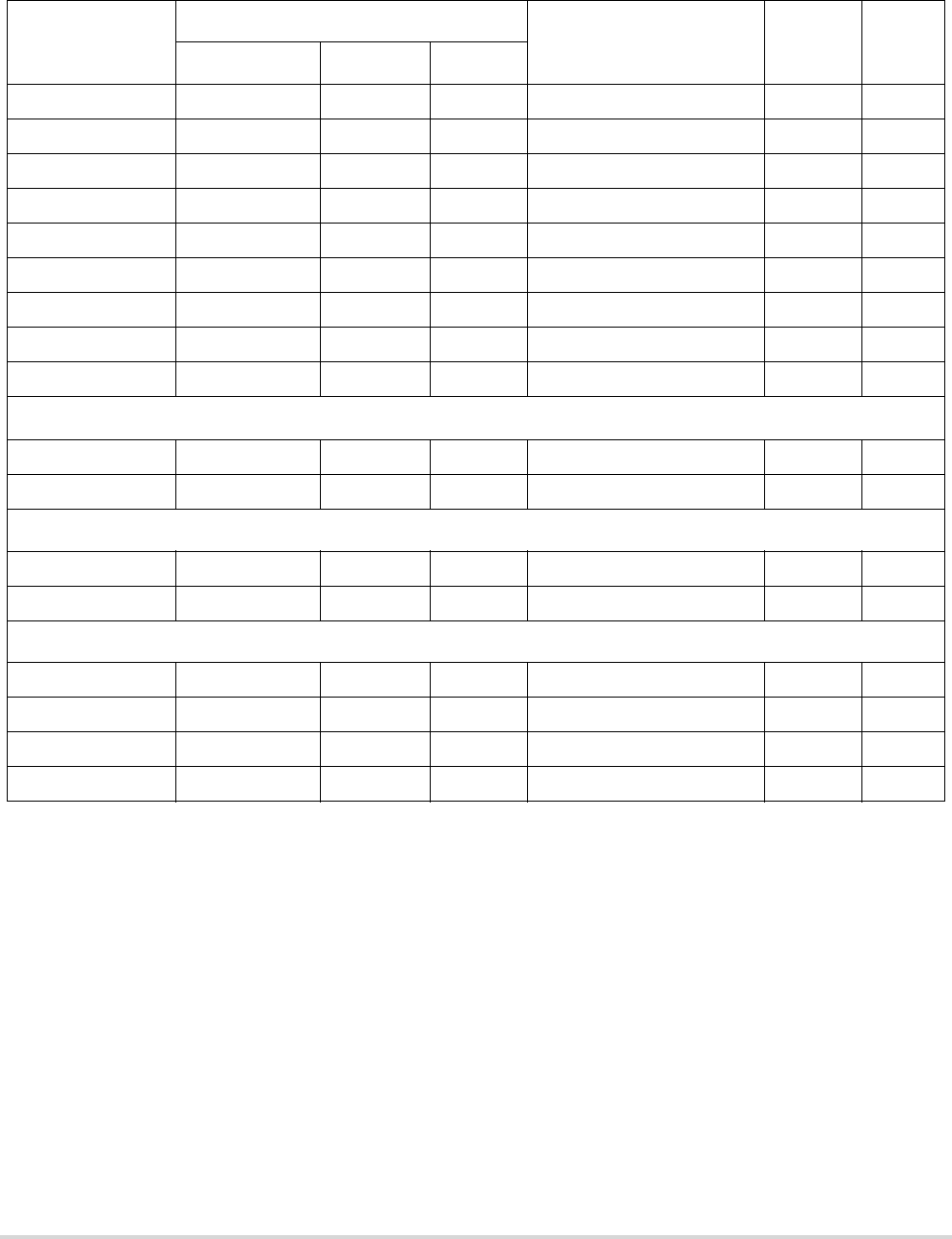

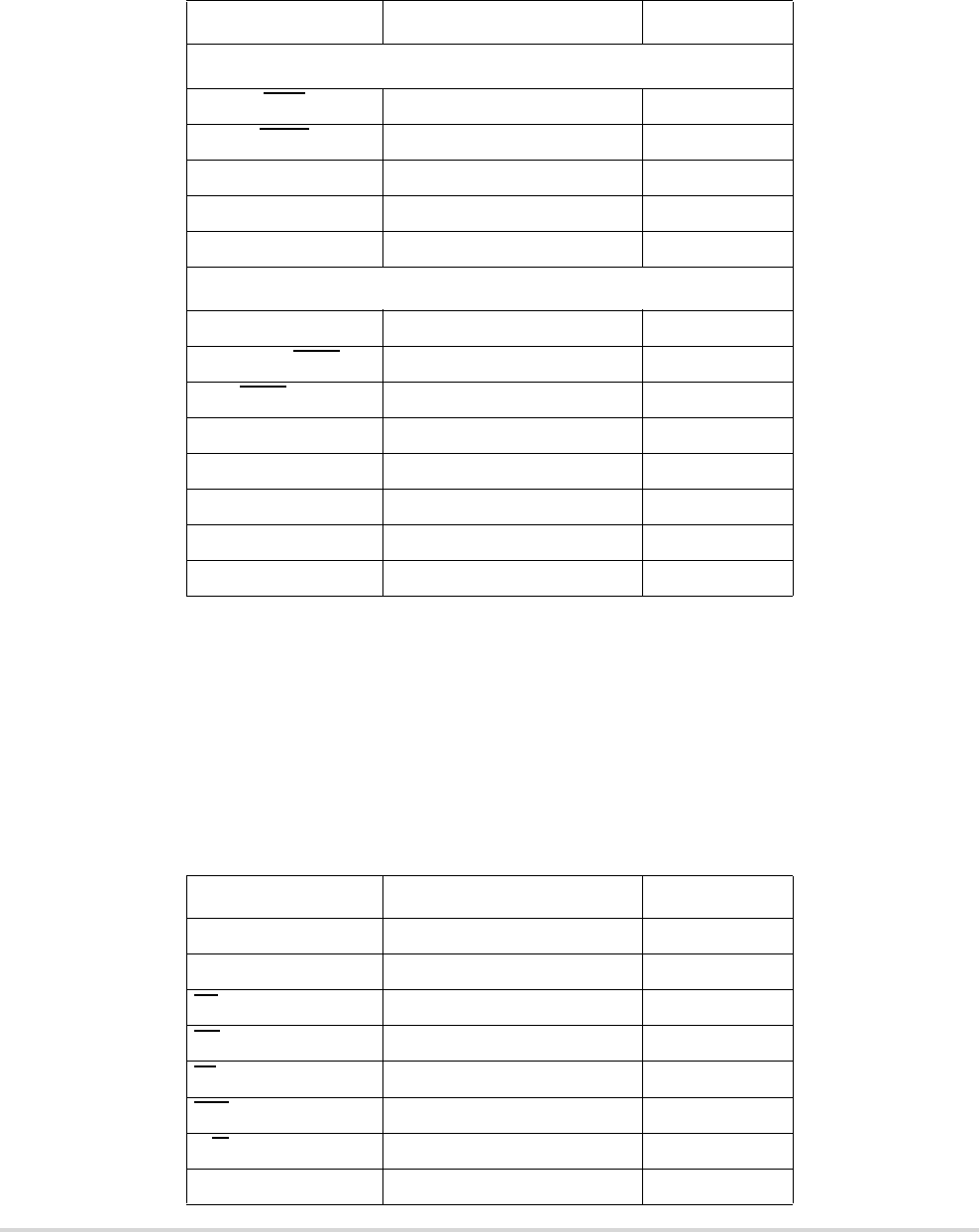

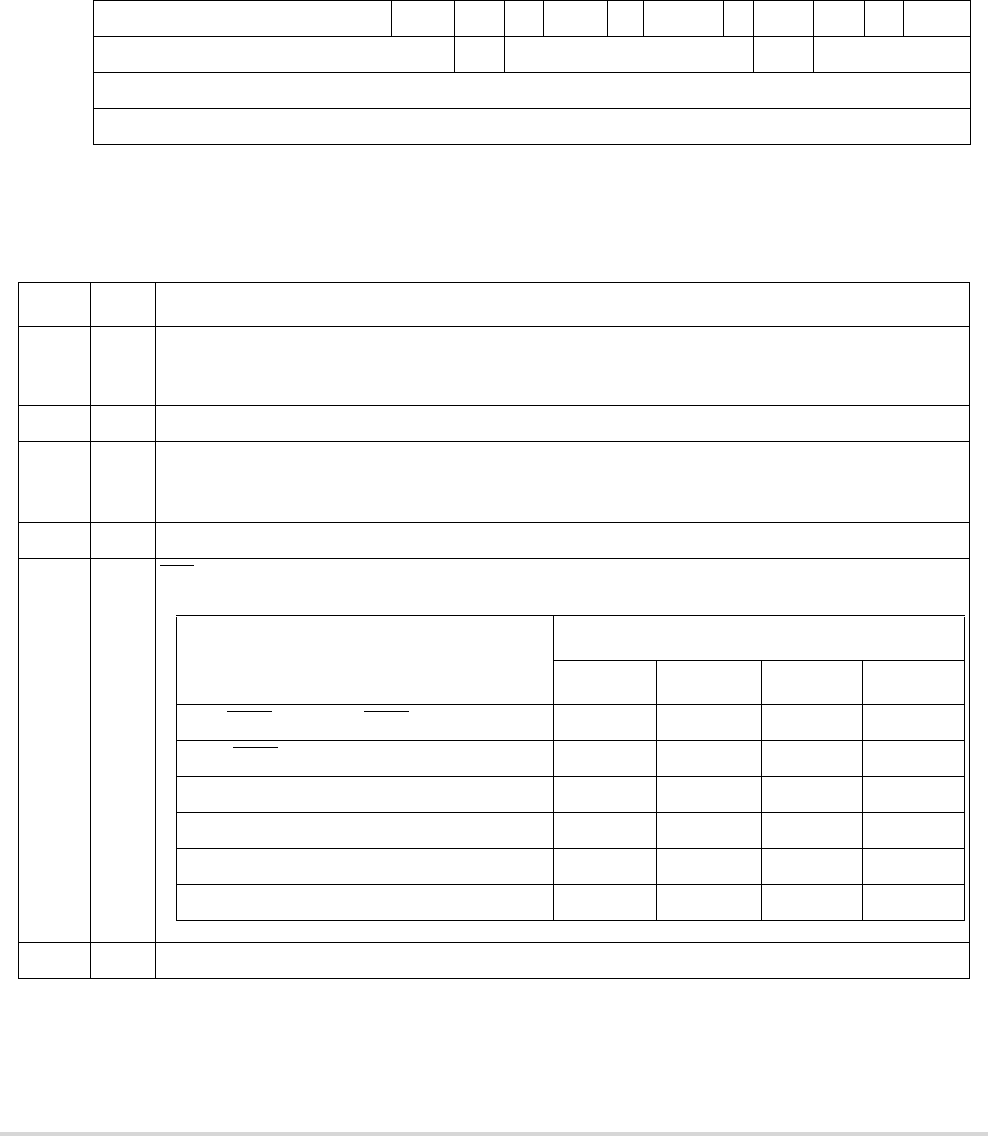

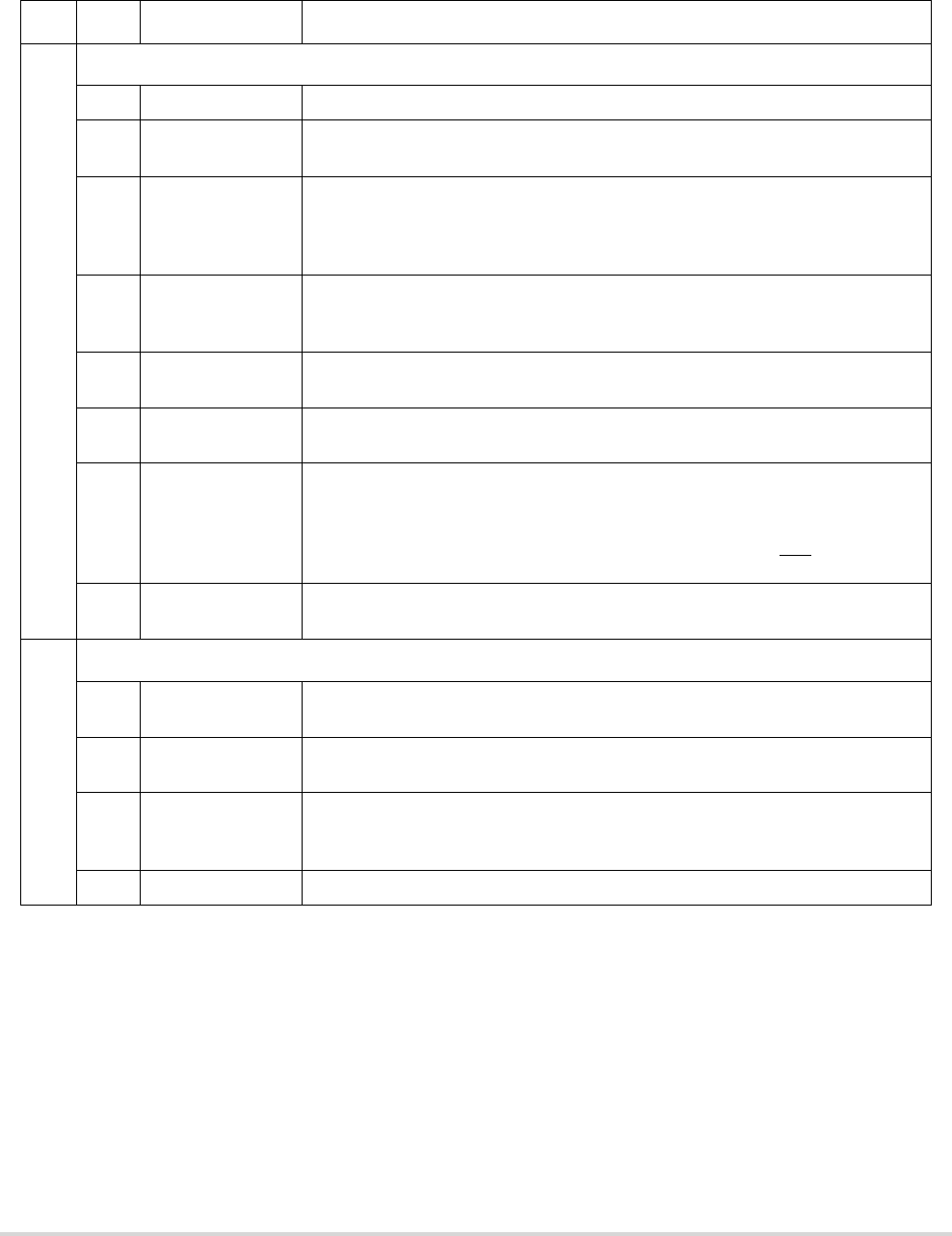

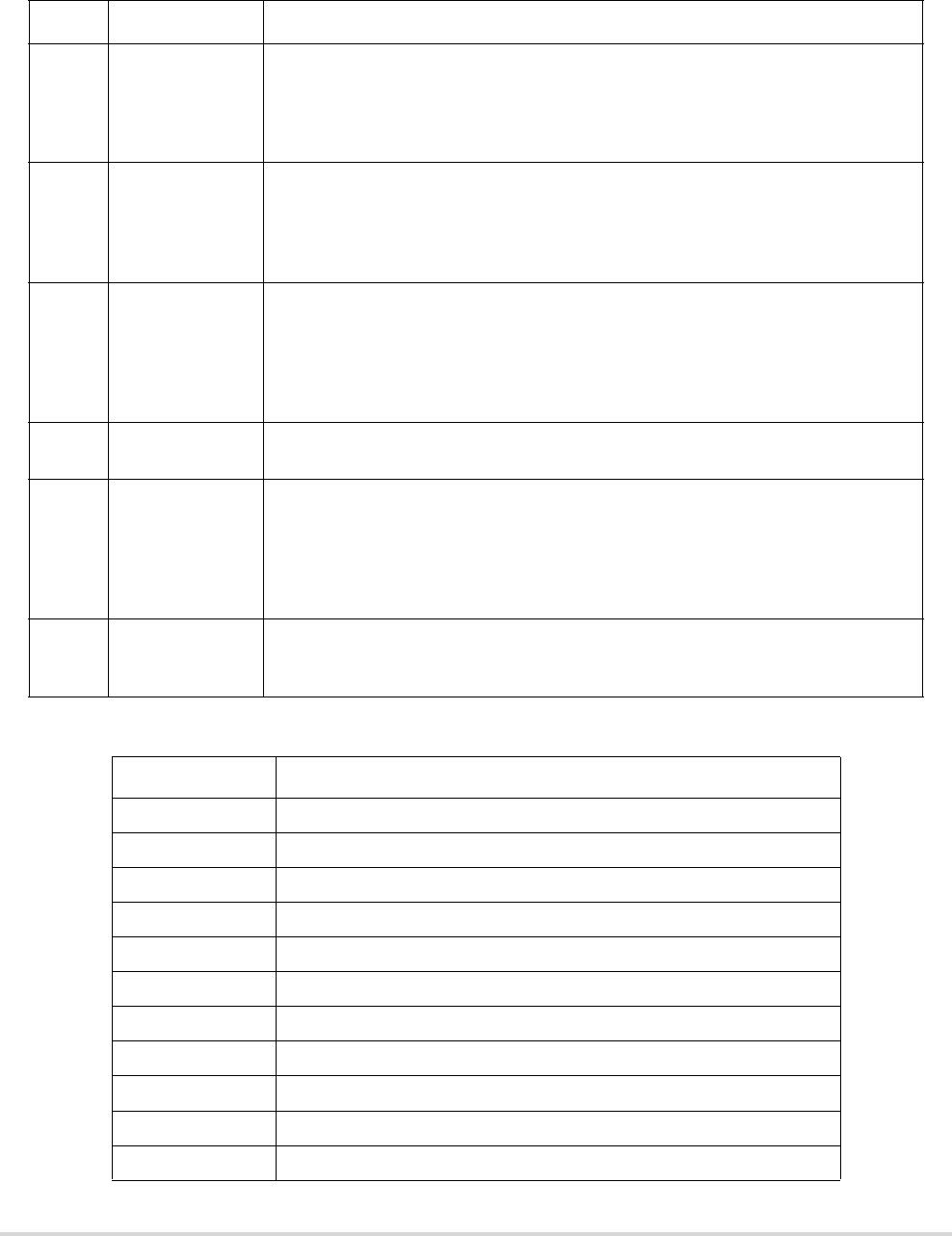

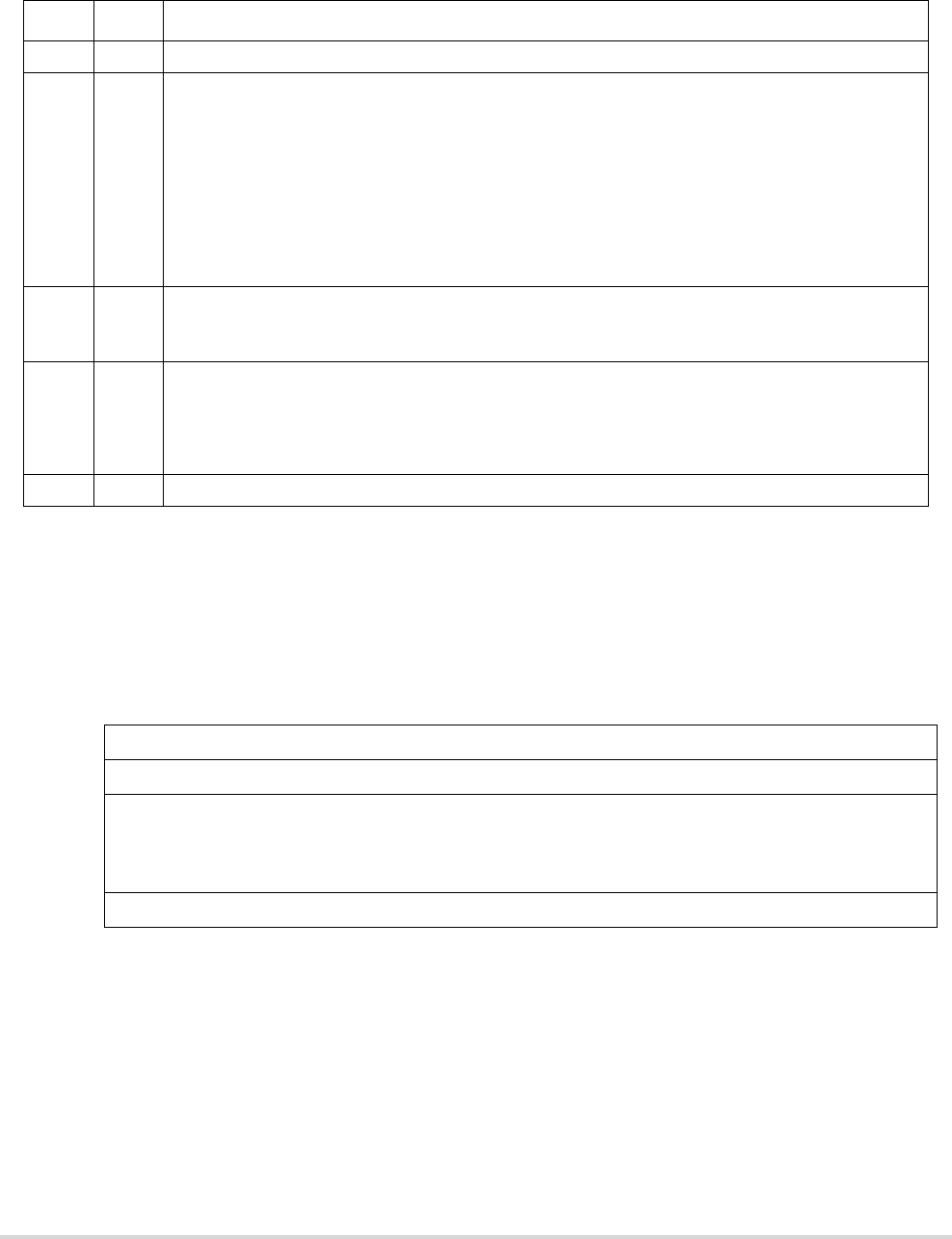

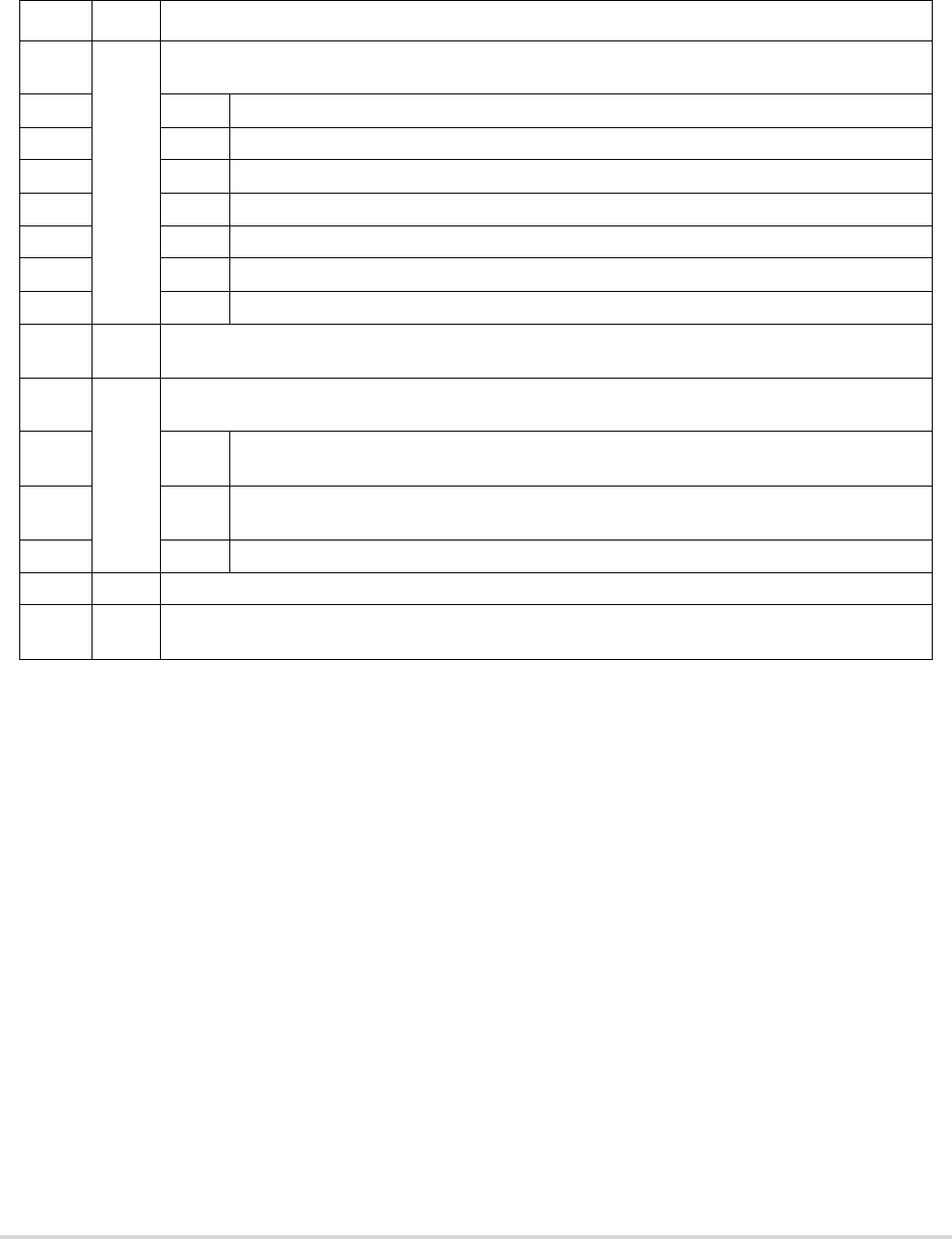

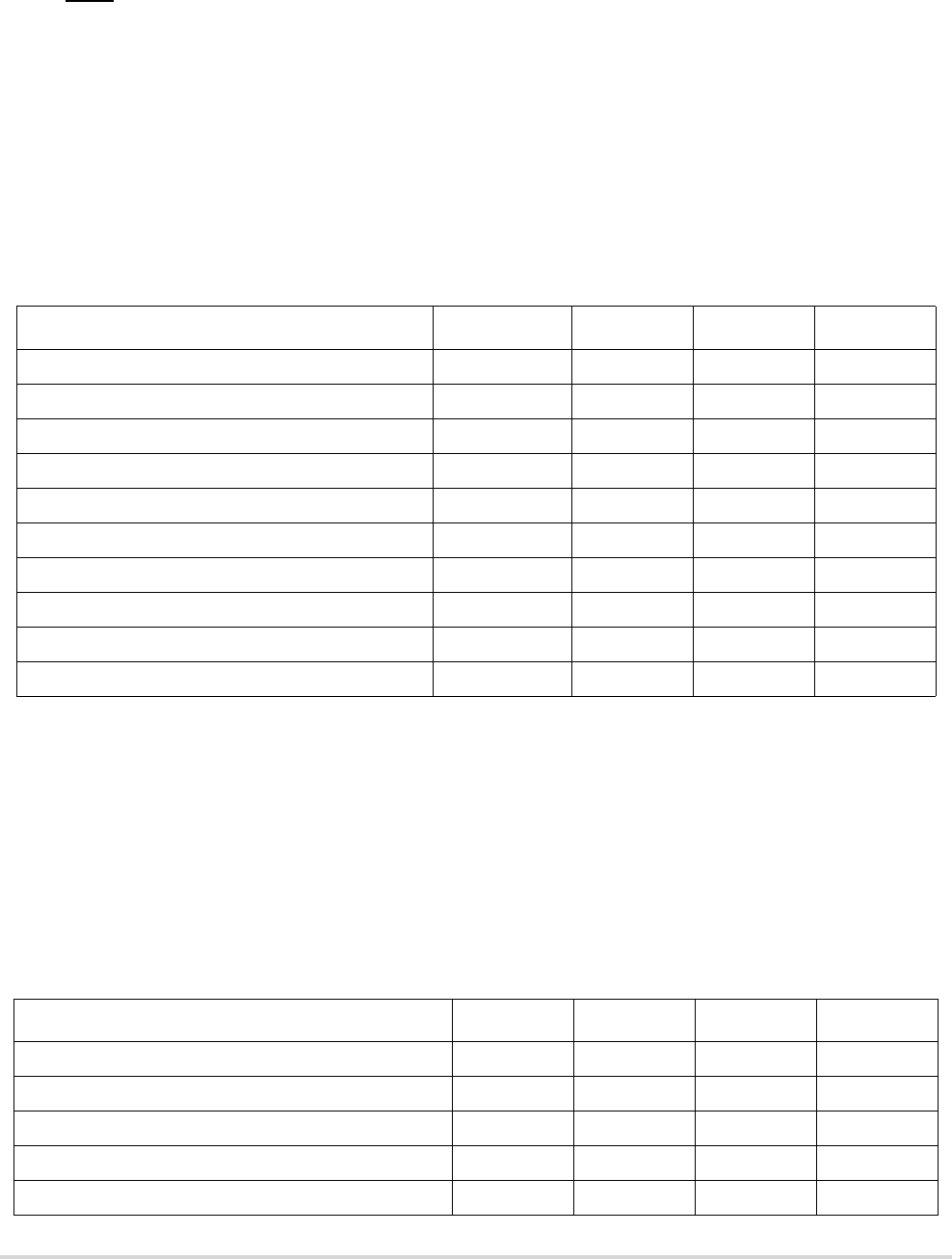

- About This Book

- Chapter 1 Overview

- 1.1 MCF5282 Key Features

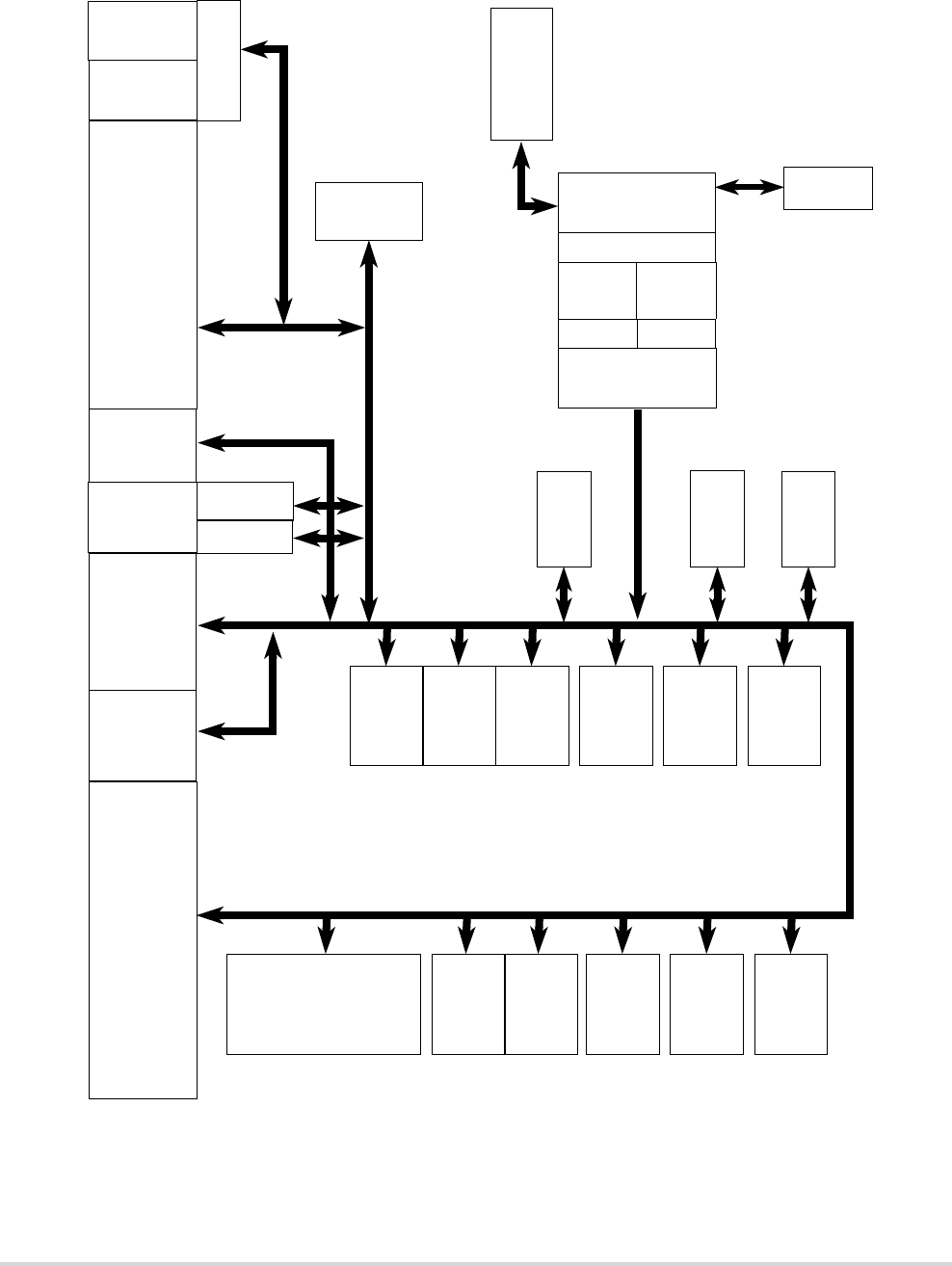

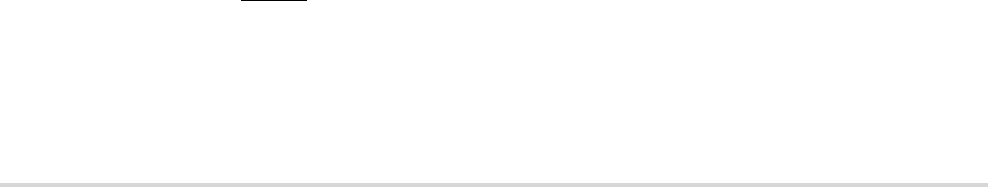

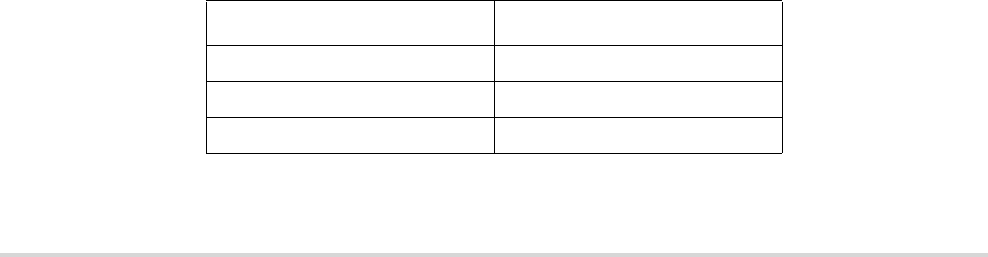

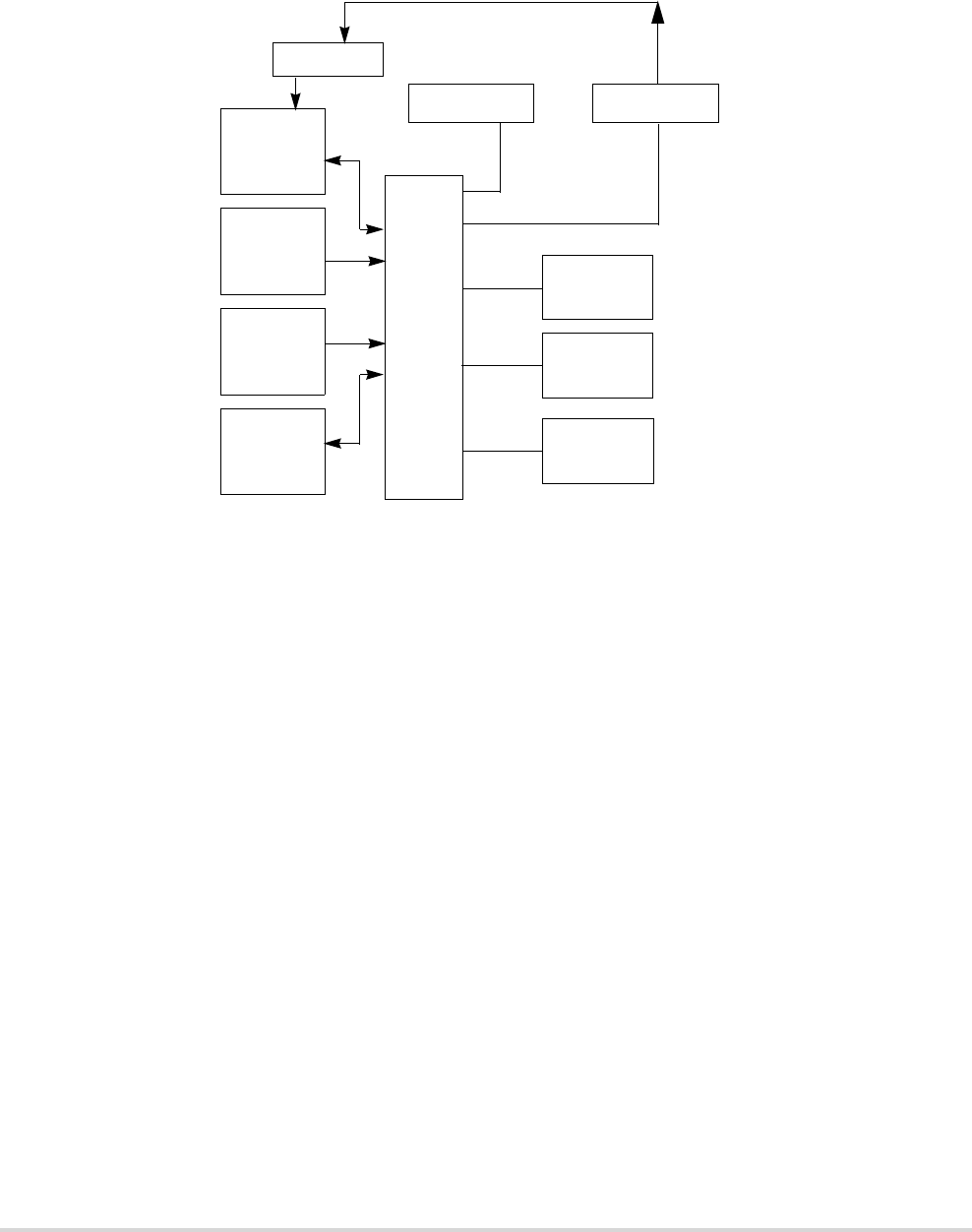

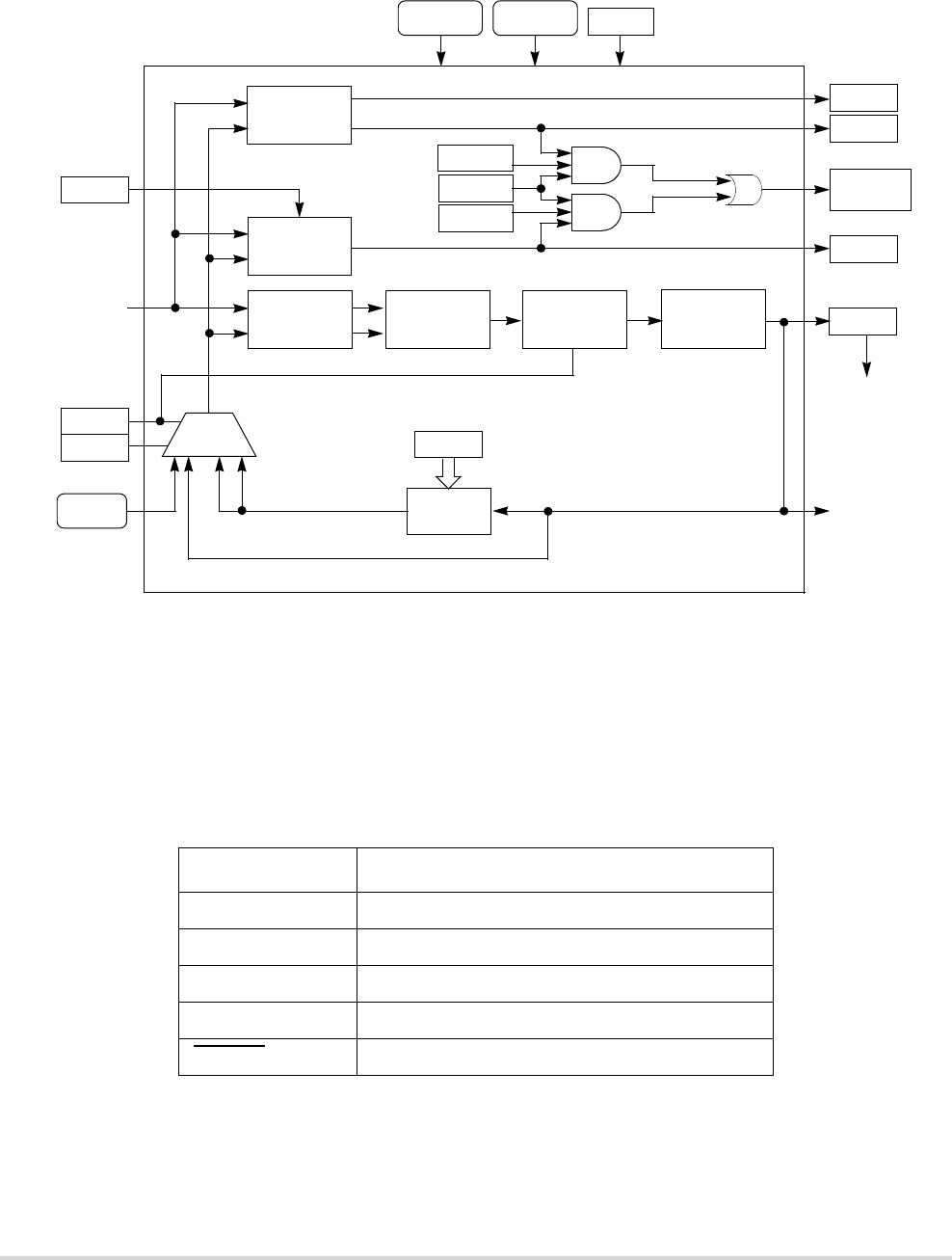

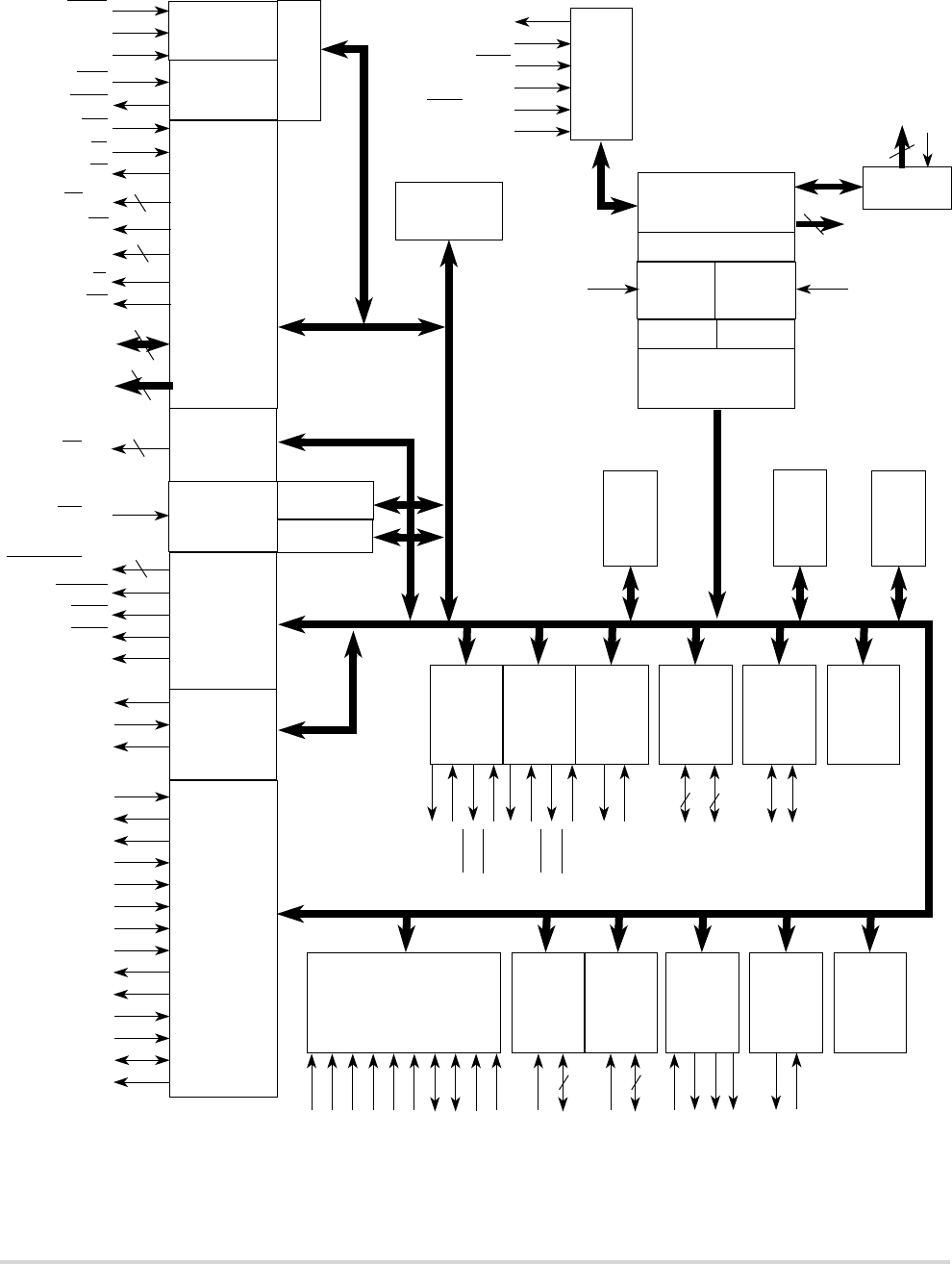

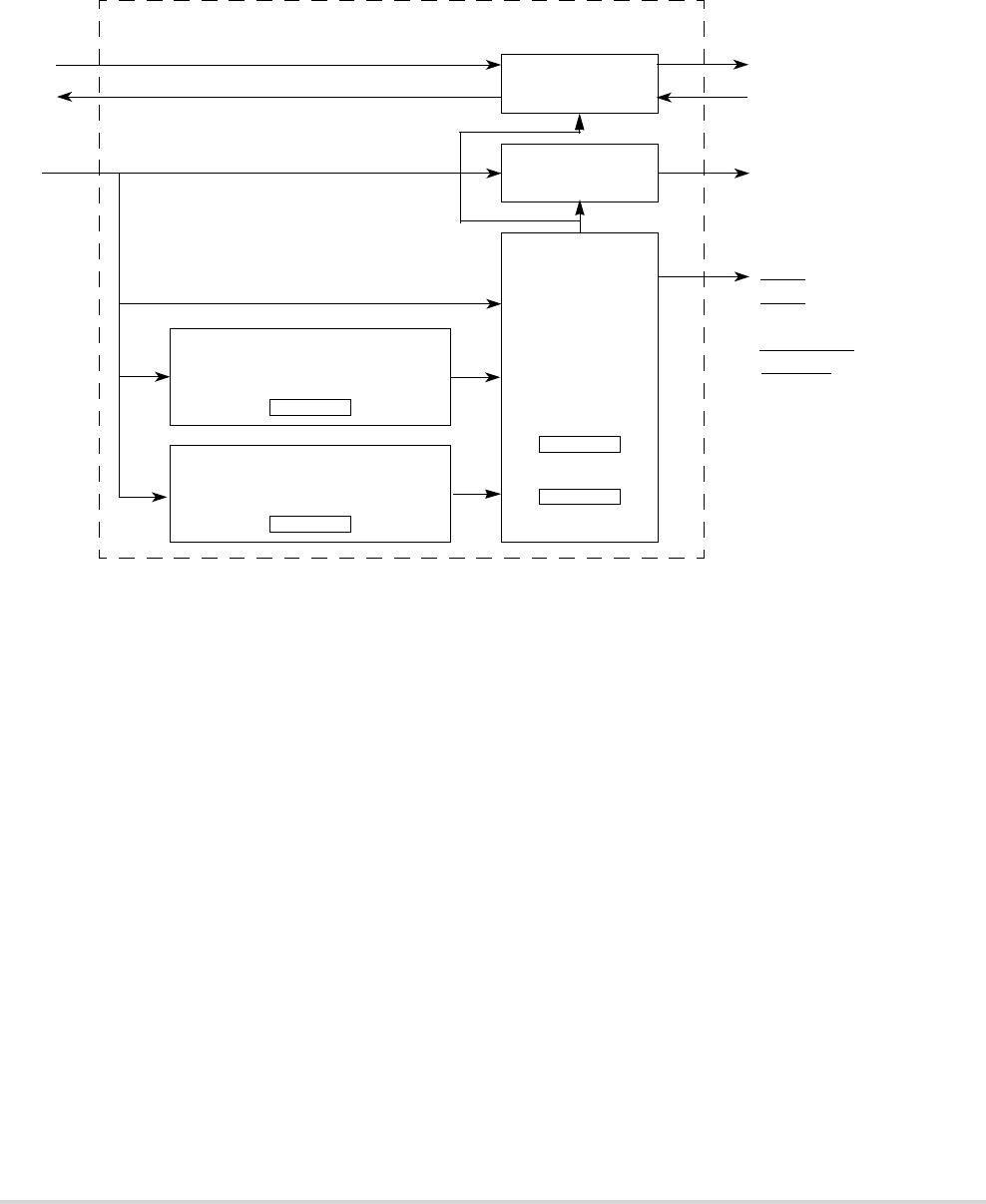

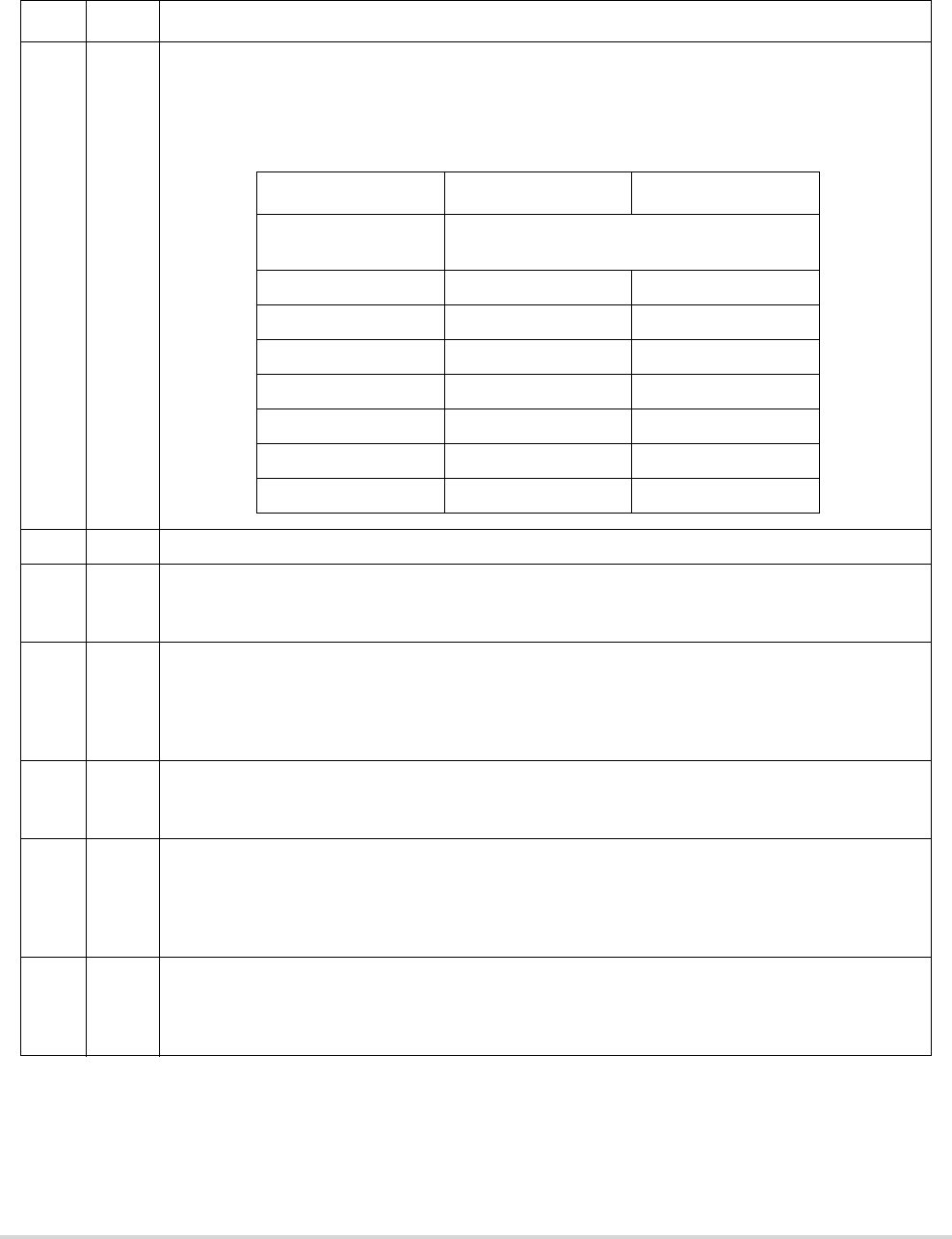

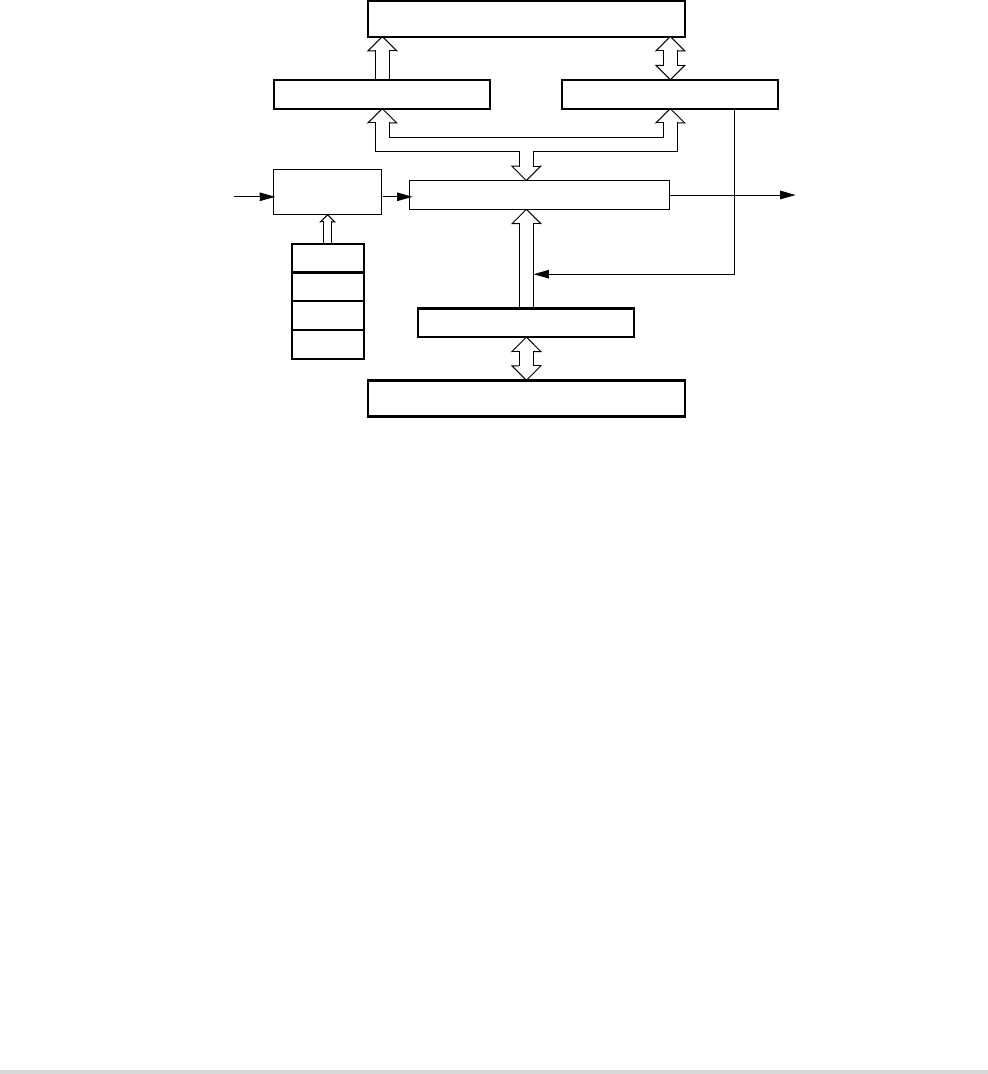

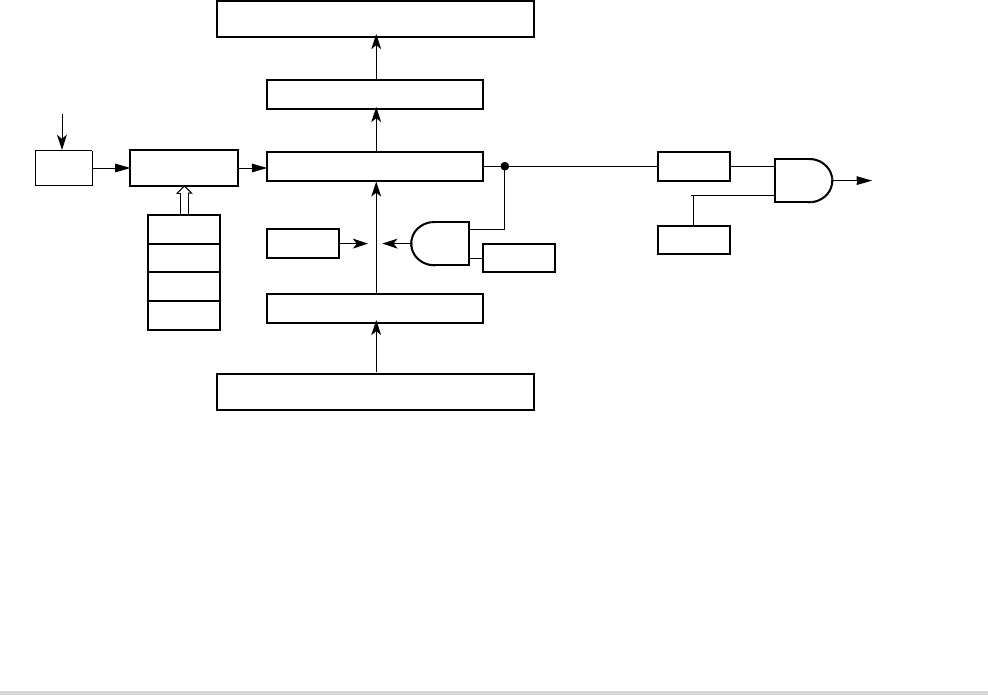

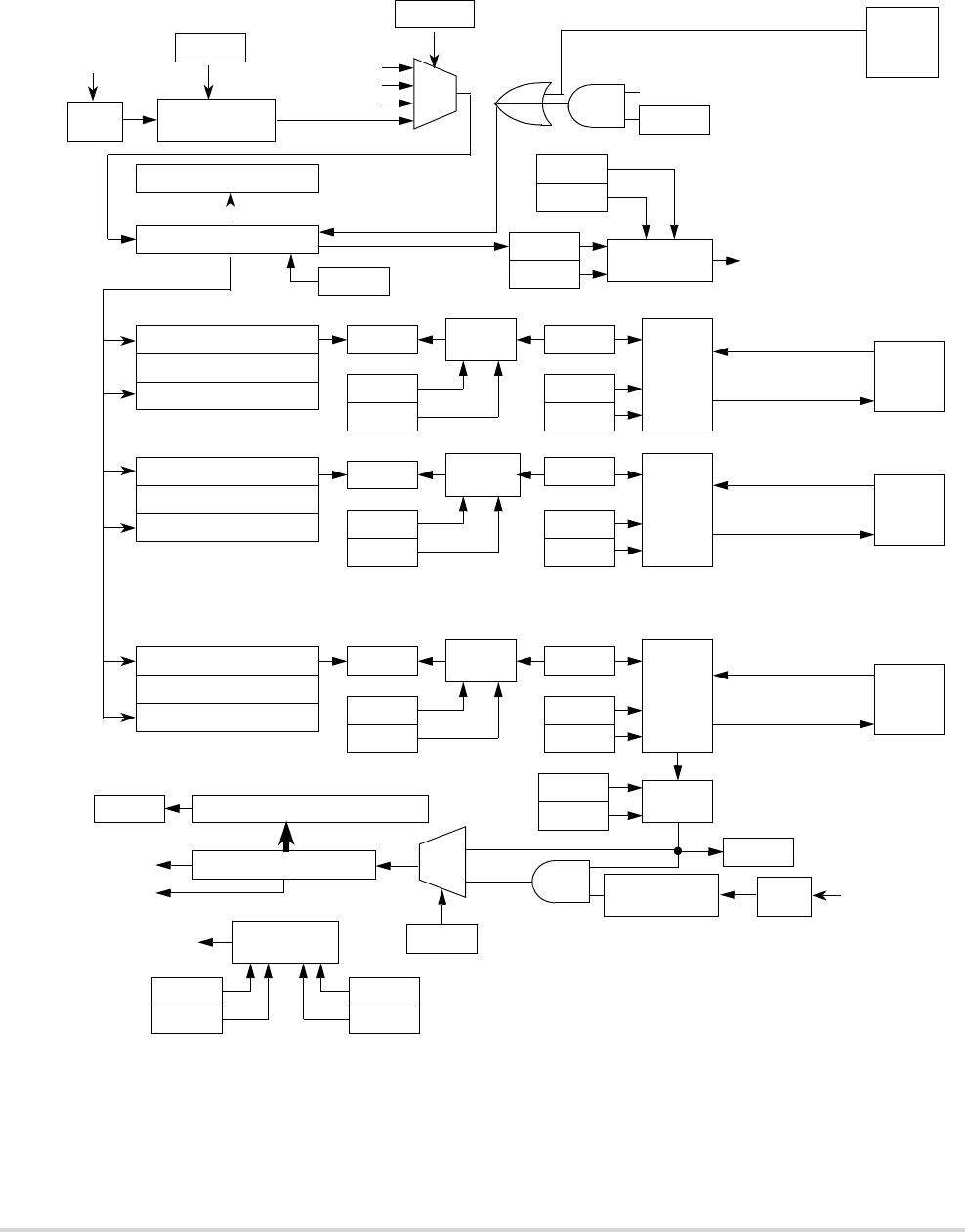

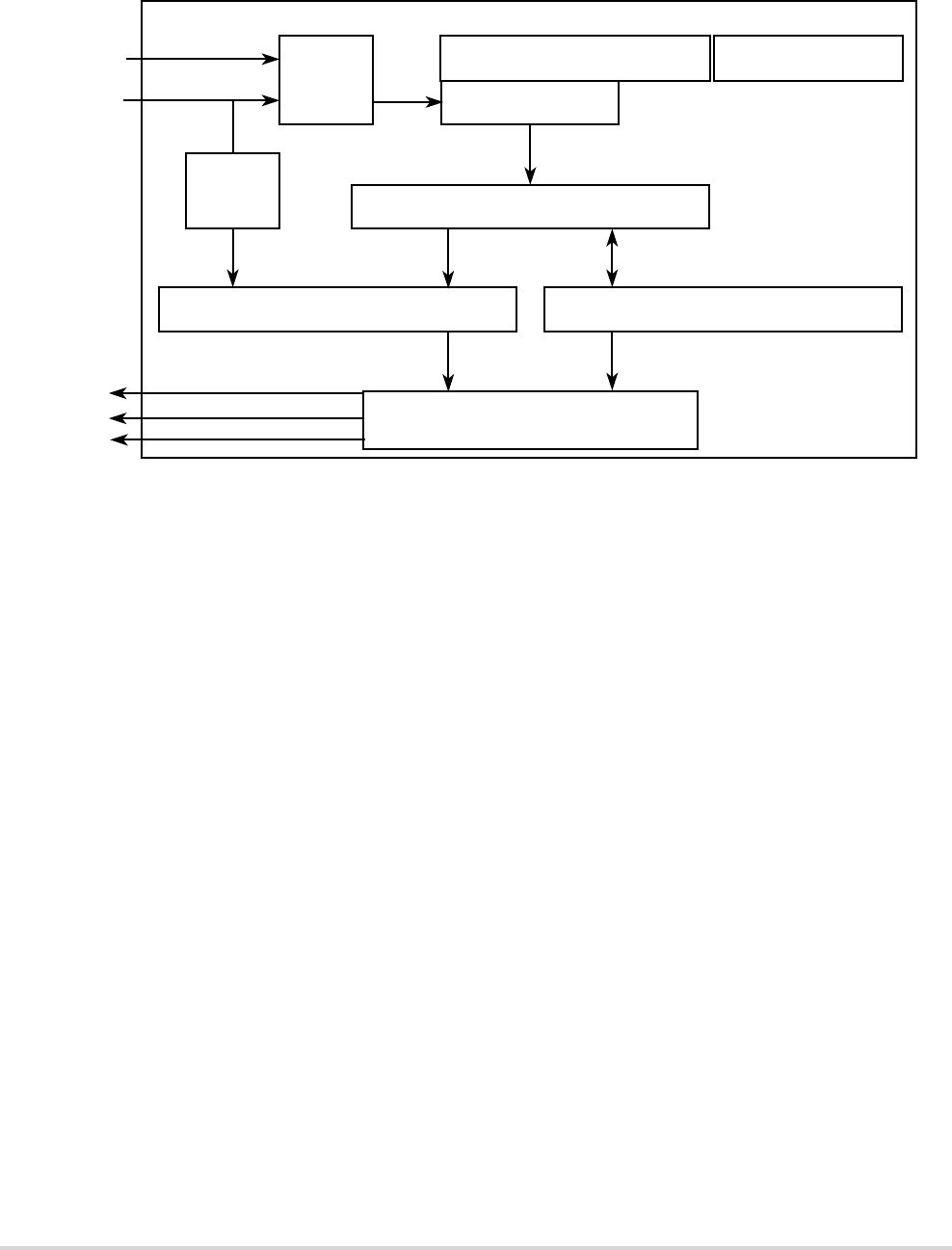

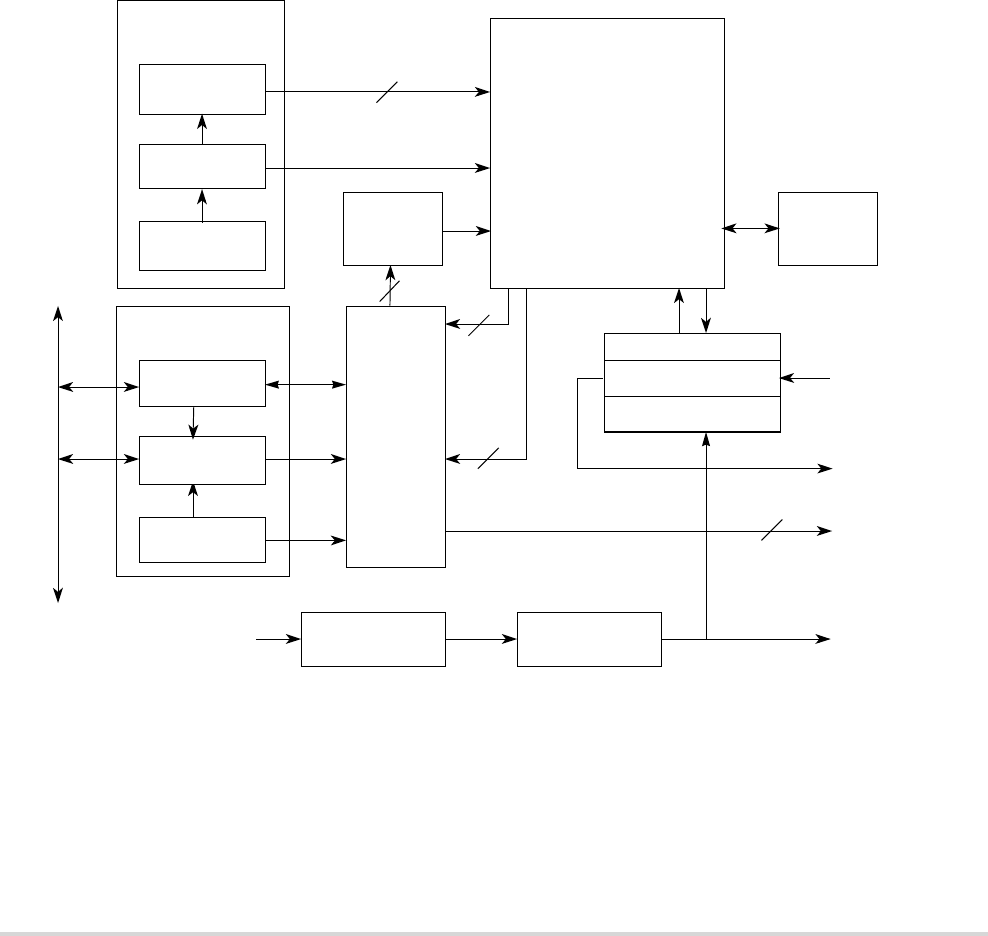

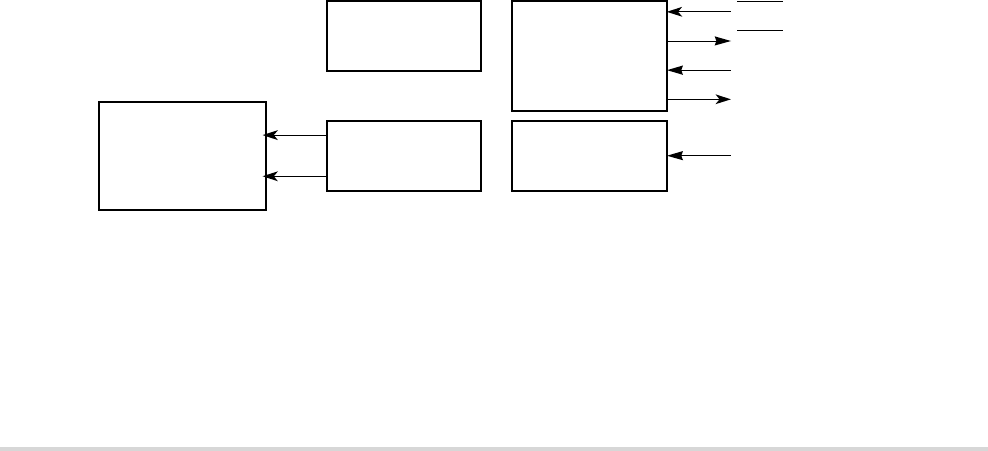

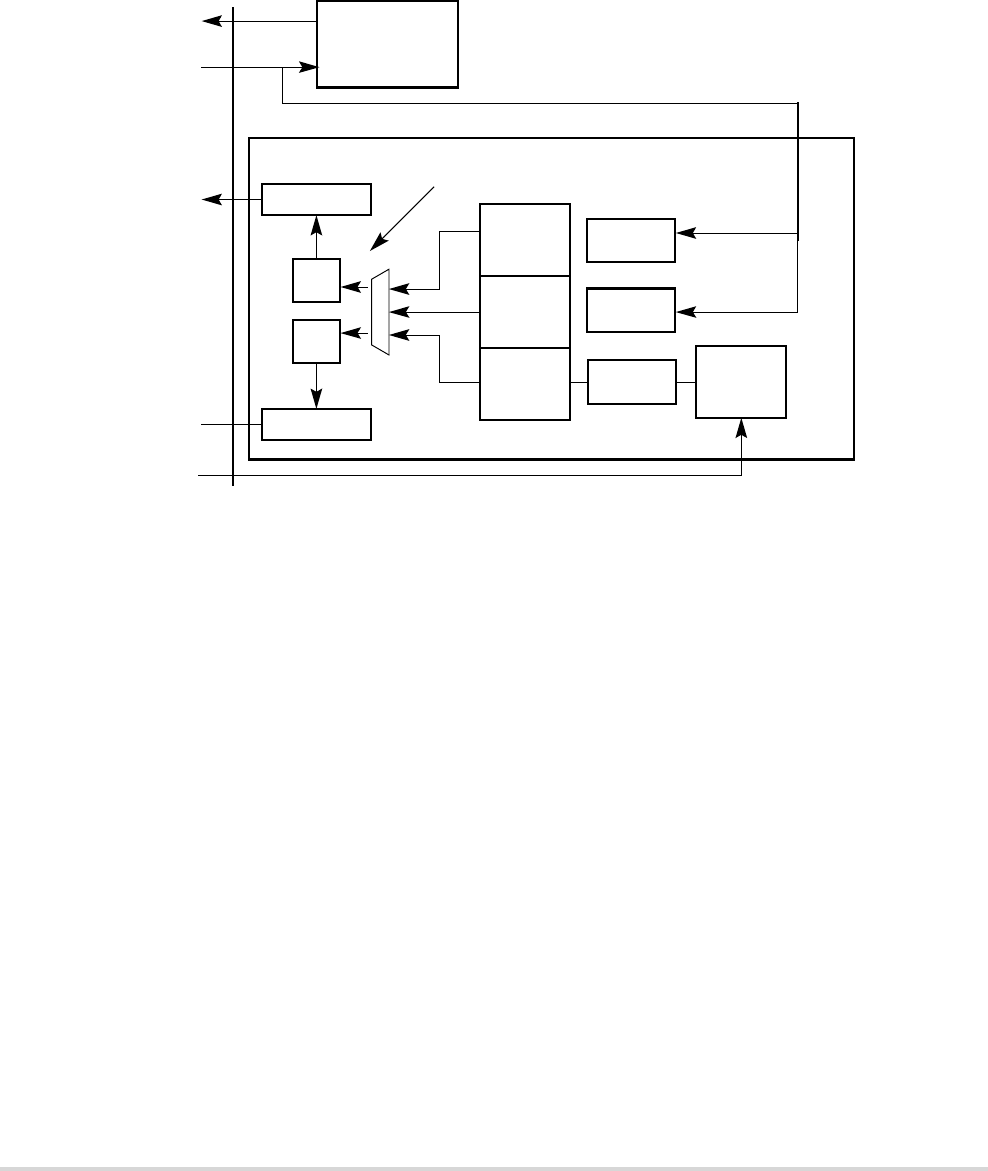

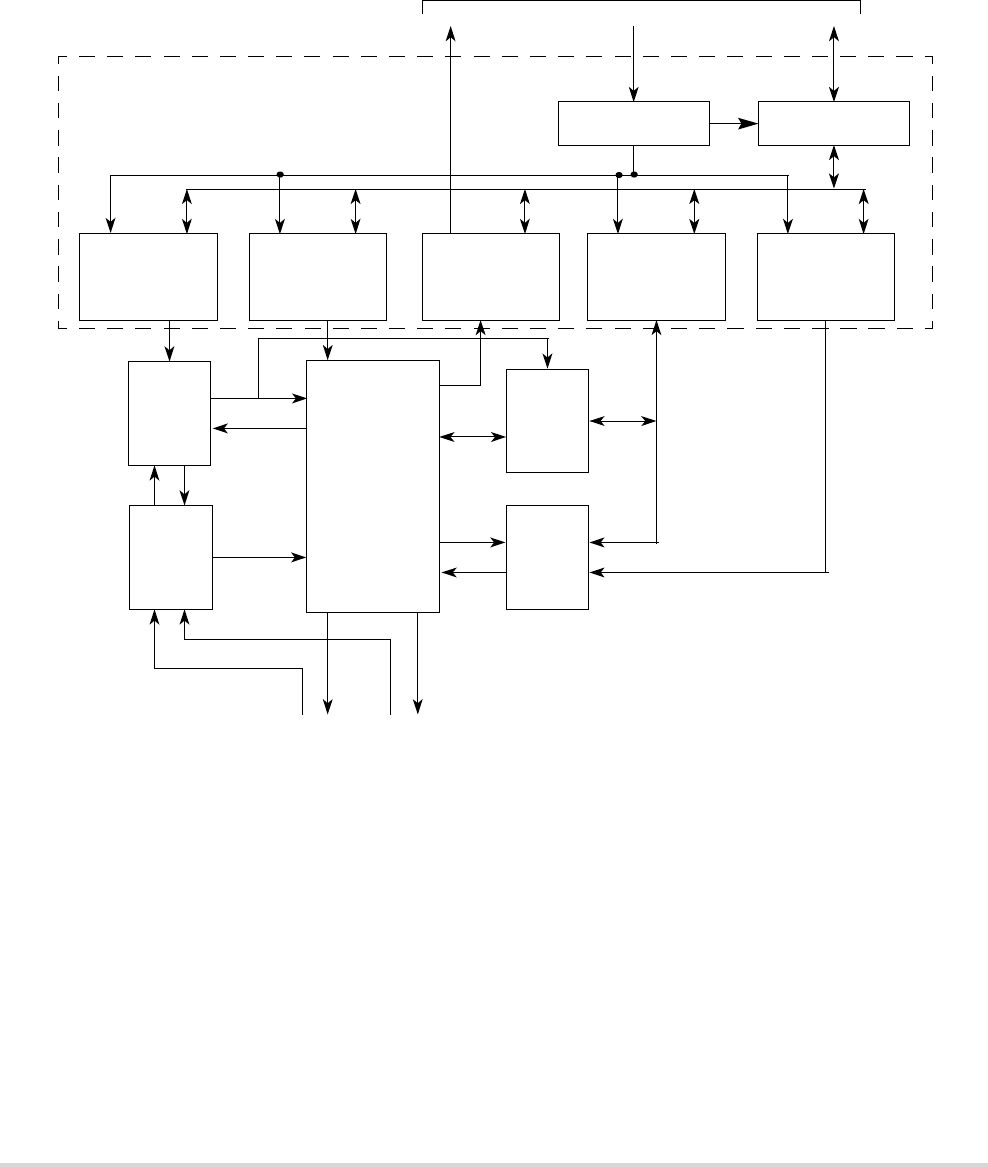

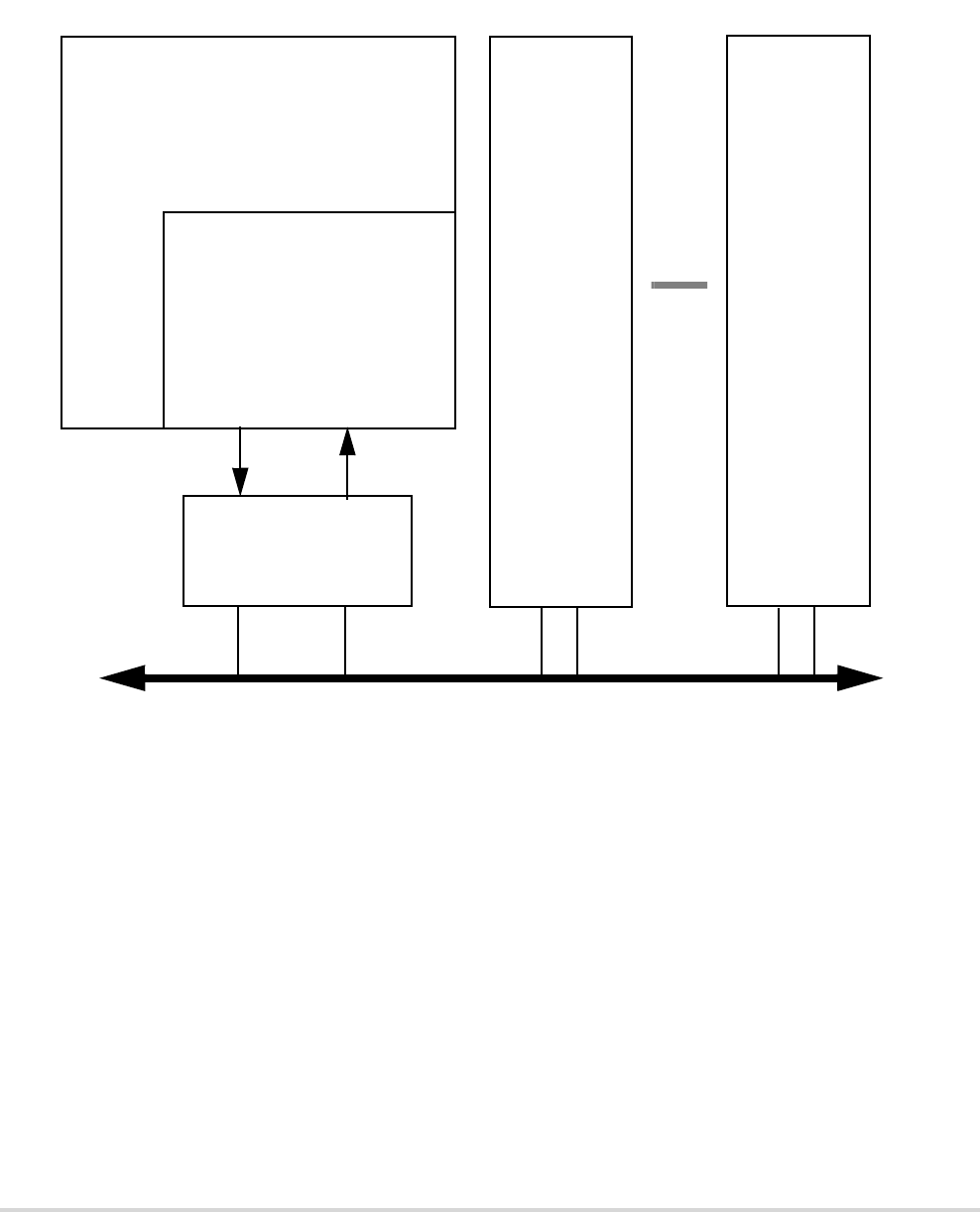

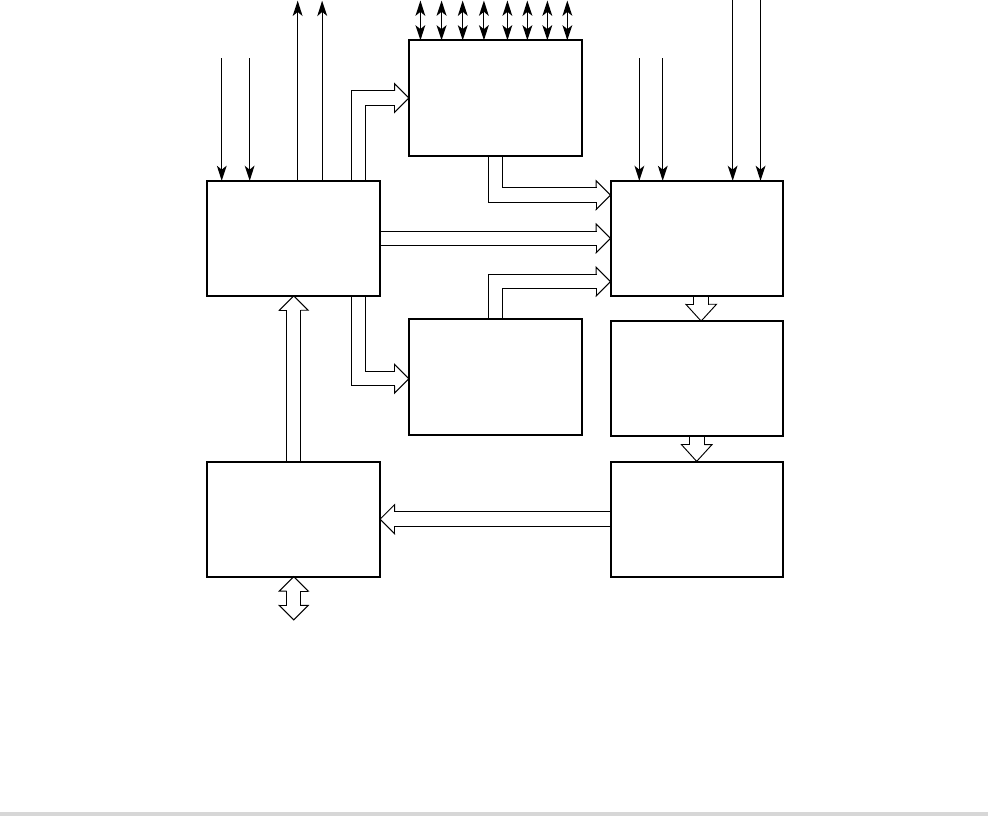

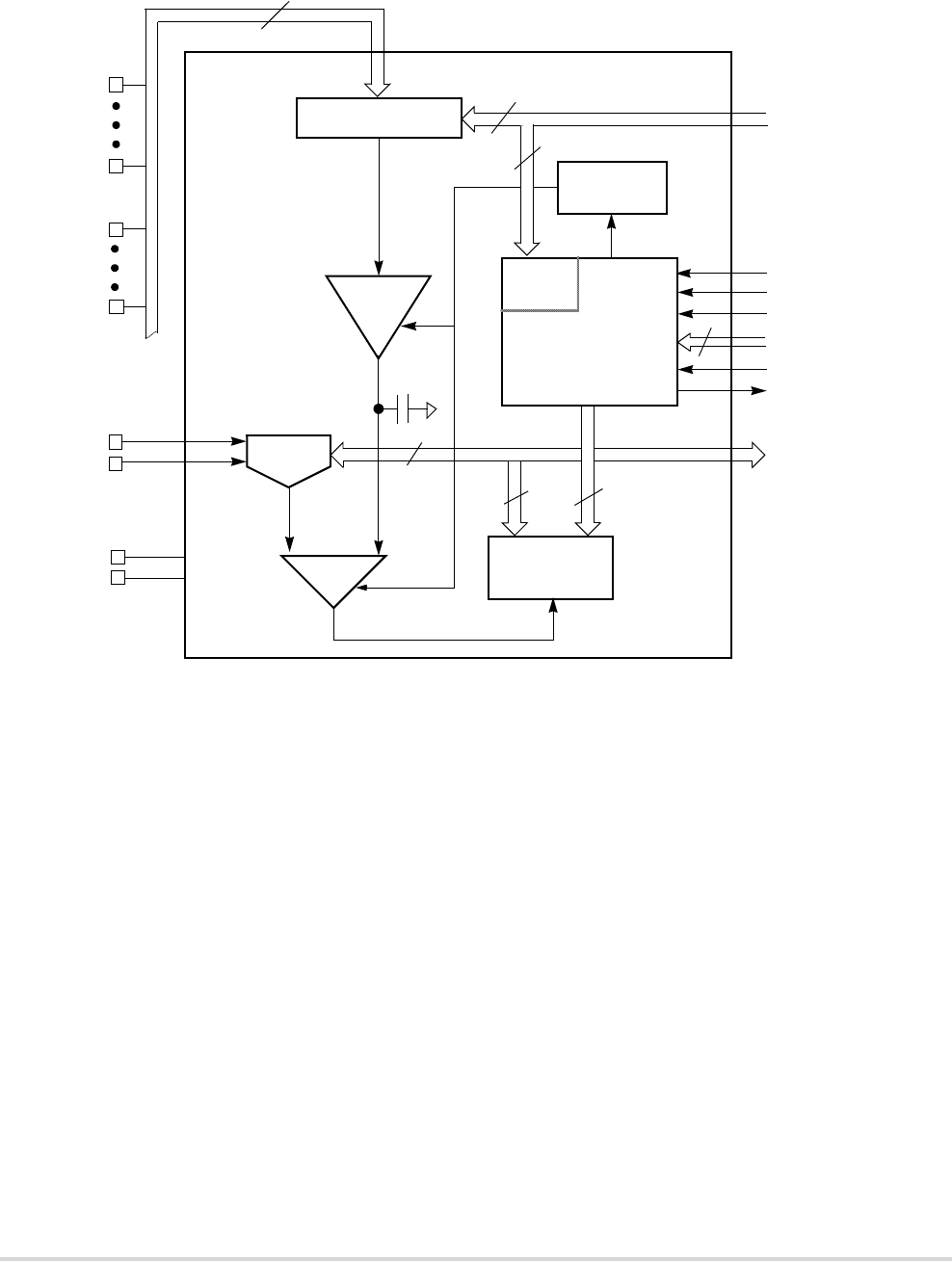

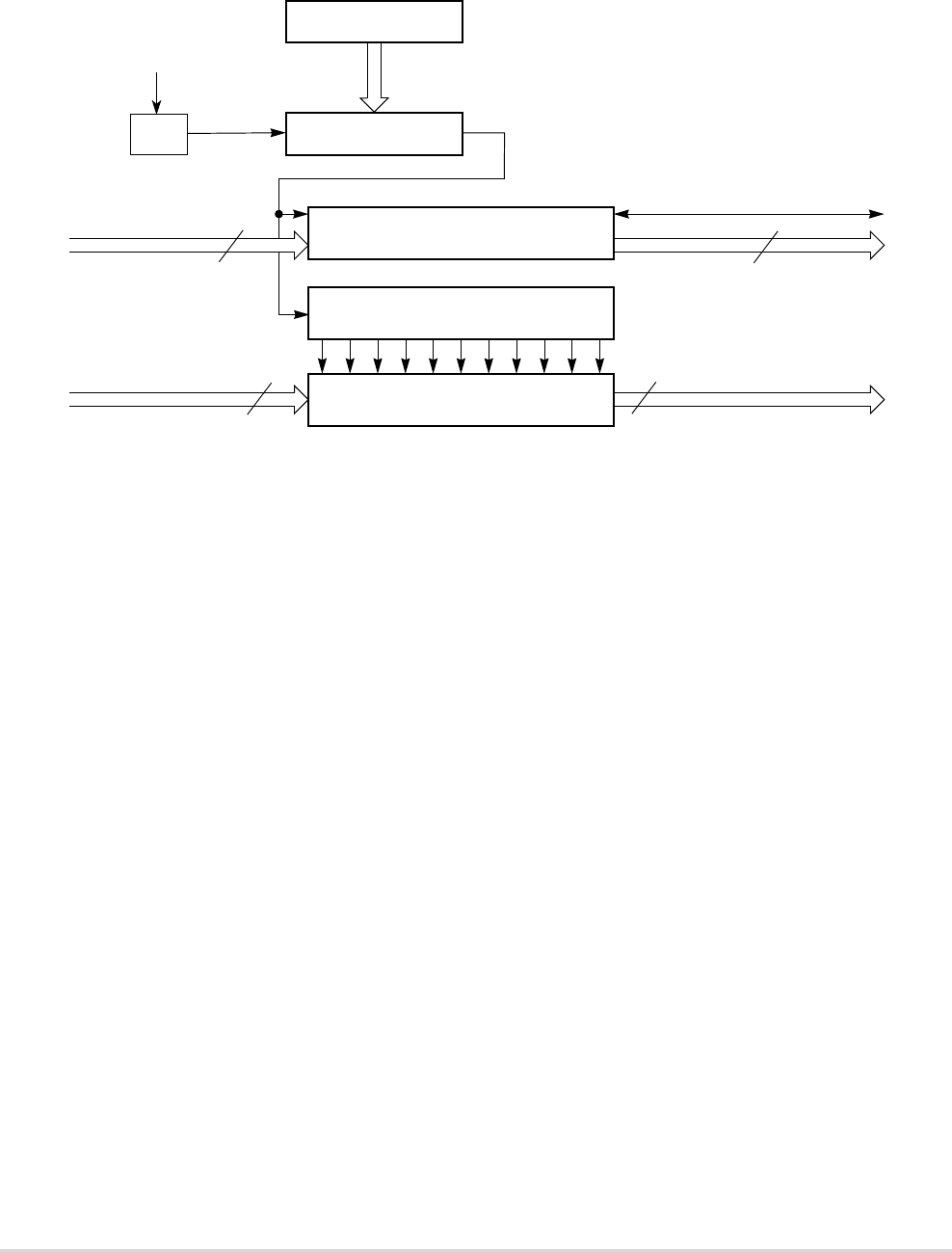

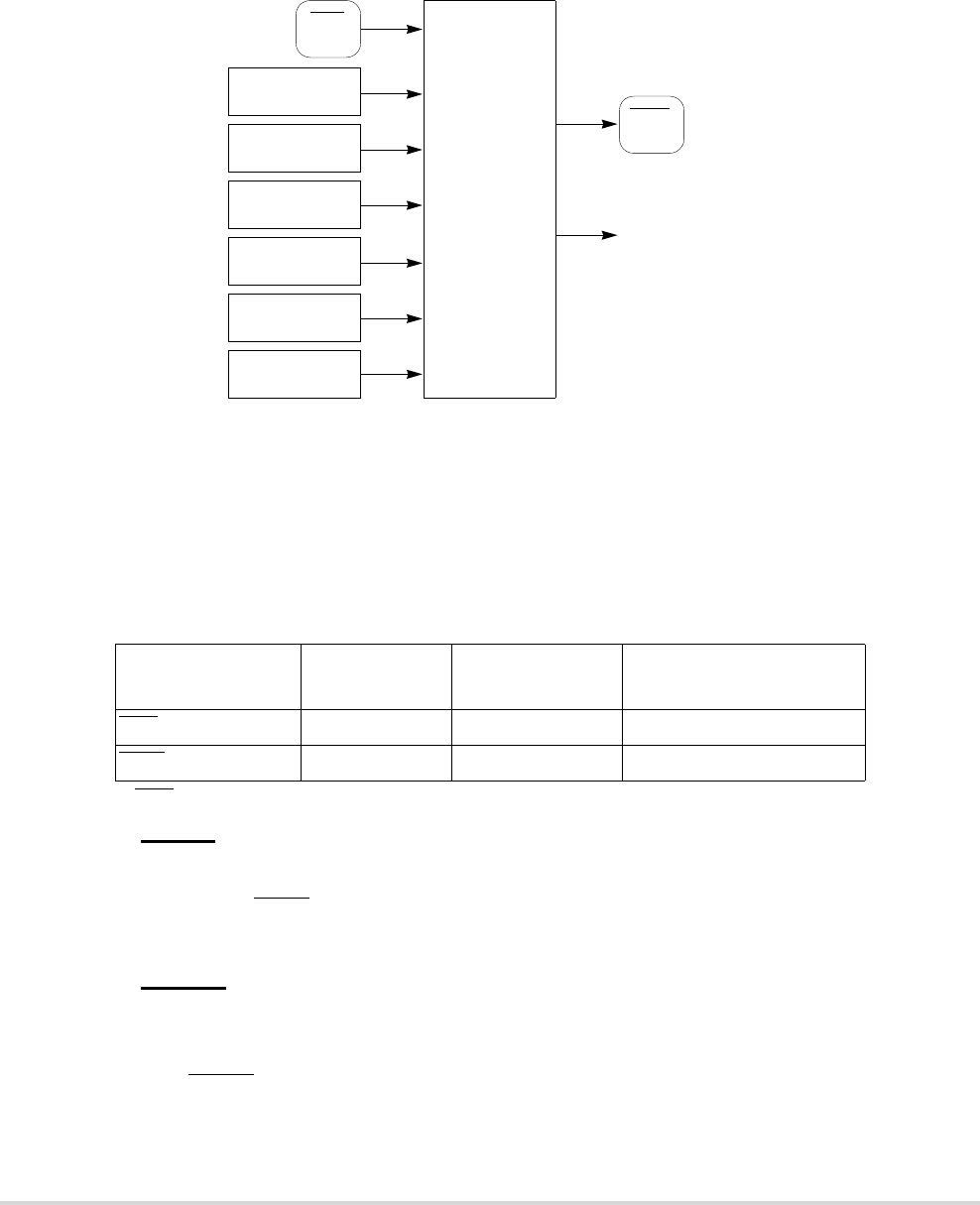

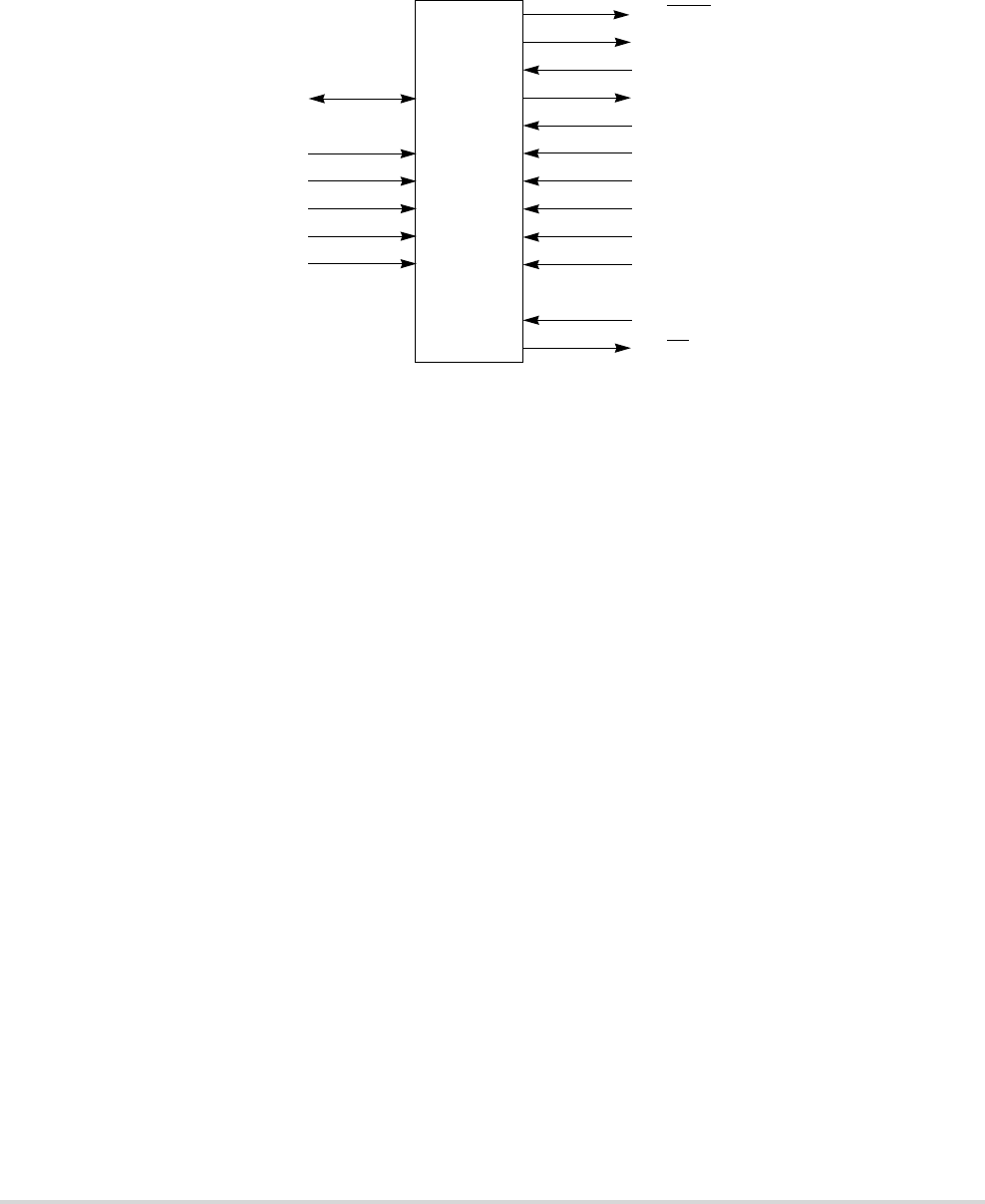

- Figure 1-1. MCF5282 Block Diagram

- 1.1.1 Version 2 ColdFire Core

- 1.1.2 System Control Module

- 1.1.3 External Interface Module (EIM)

- 1.1.4 Chip Select

- 1.1.5 Power Management

- 1.1.6 General Input/Output Ports

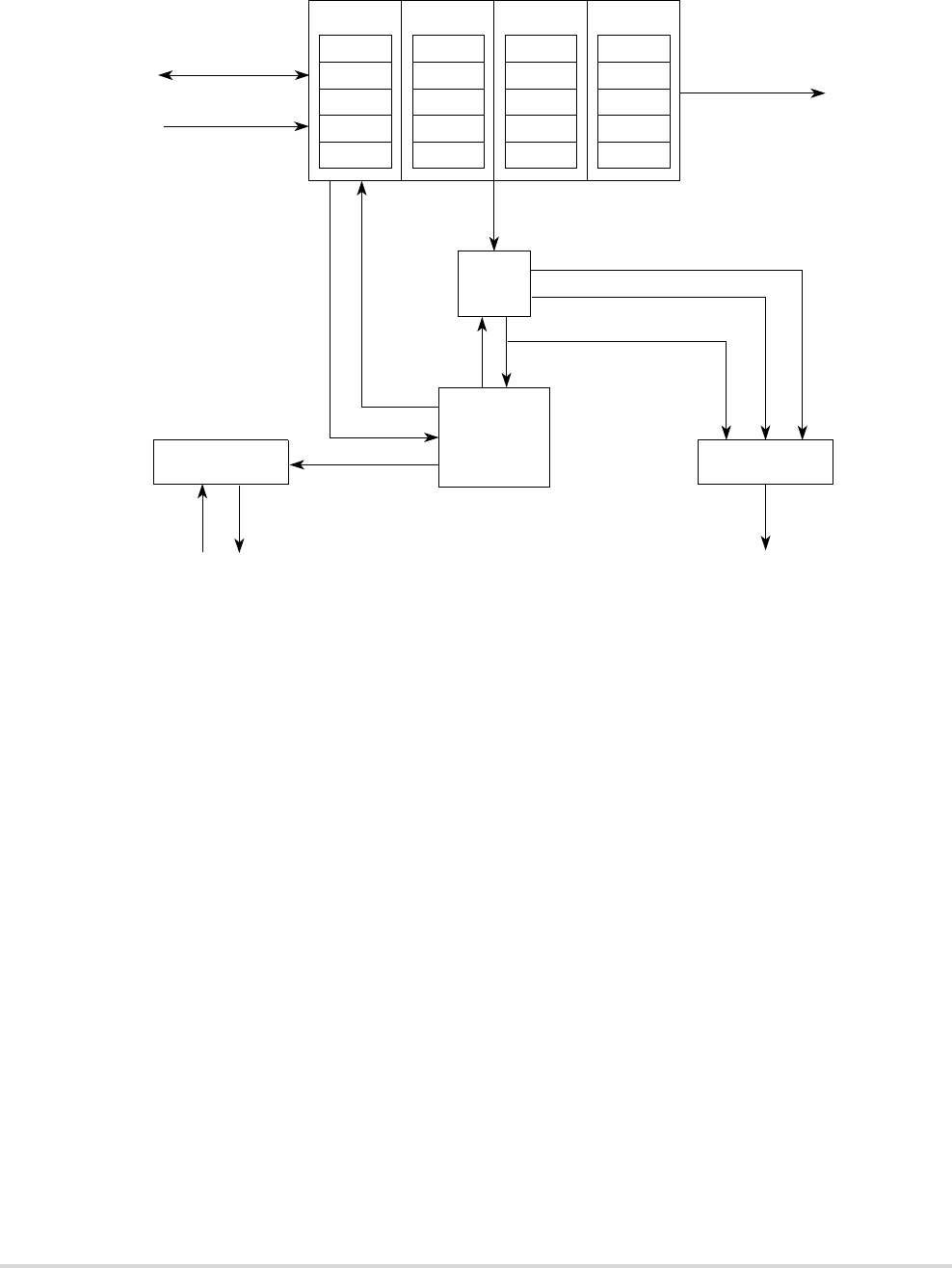

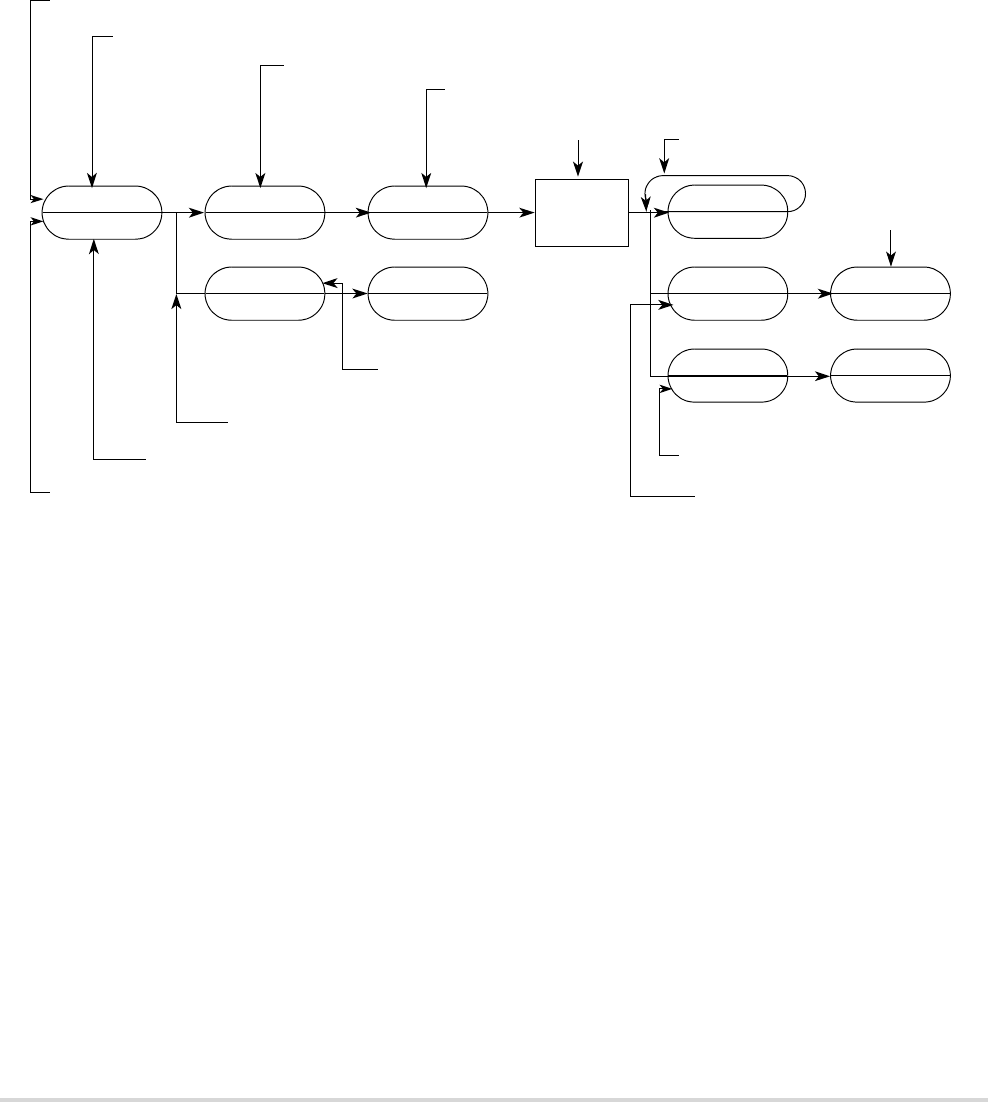

- 1.1.7 Interrupt Controllers (INTC0/INTC1)

- 1.1.8 SDRAM Controller

- 1.1.9 Test Access Port

- 1.1.10 UART Modules

- 1.1.11 DMA Timers (DTIM0-DTIM3)

- 1.1.12 General-Purpose Timers (GPTA/GPTB)

- 1.1.13 Periodic Interrupt Timers (PIT0-PIT3)

- 1.1.14 Software Watchdog Timer

- 1.1.15 Phase Locked Loop (PLL)

- 1.1.16 DMA Controller

- 1.1.17 Reset

- 1.2 MCF5282-Specific Features

- 1.1 MCF5282 Key Features

- Chapter 2 ColdFire Core

- 2.1 Processor Pipelines

- 2.2 Processor Register Description

- 2.2.1 User Programming Model

- 2.2.2 EMAC Programming Model

- 2.2.3 Supervisor Programming Model

- 2.3 Programming Model

- 2.4 Additions to the Instruction Set Architecture

- 2.5 Exception Processing Overview

- 2.6 Exception Stack Frame Definition

- 2.7 Processor Exceptions

- 2.7.1 Access Error Exception

- 2.7.2 Address Error Exception

- 2.7.3 Illegal Instruction Exception

- 2.7.4 Divide-By-Zero

- 2.7.5 Privilege Violation

- 2.7.6 Trace Exception

- 2.7.7 Unimplemented Line-A Opcode

- 2.7.8 Unimplemented Line-F Opcode

- 2.7.9 Debug Interrupt

- 2.7.10 RTE and Format Error Exception

- 2.7.11 TRAP Instruction Exception

- 2.7.12 Interrupt Exception

- 2.7.13 Fault-on-Fault Halt

- 2.7.14 Reset Exception

- 2.8 Instruction Execution Timing

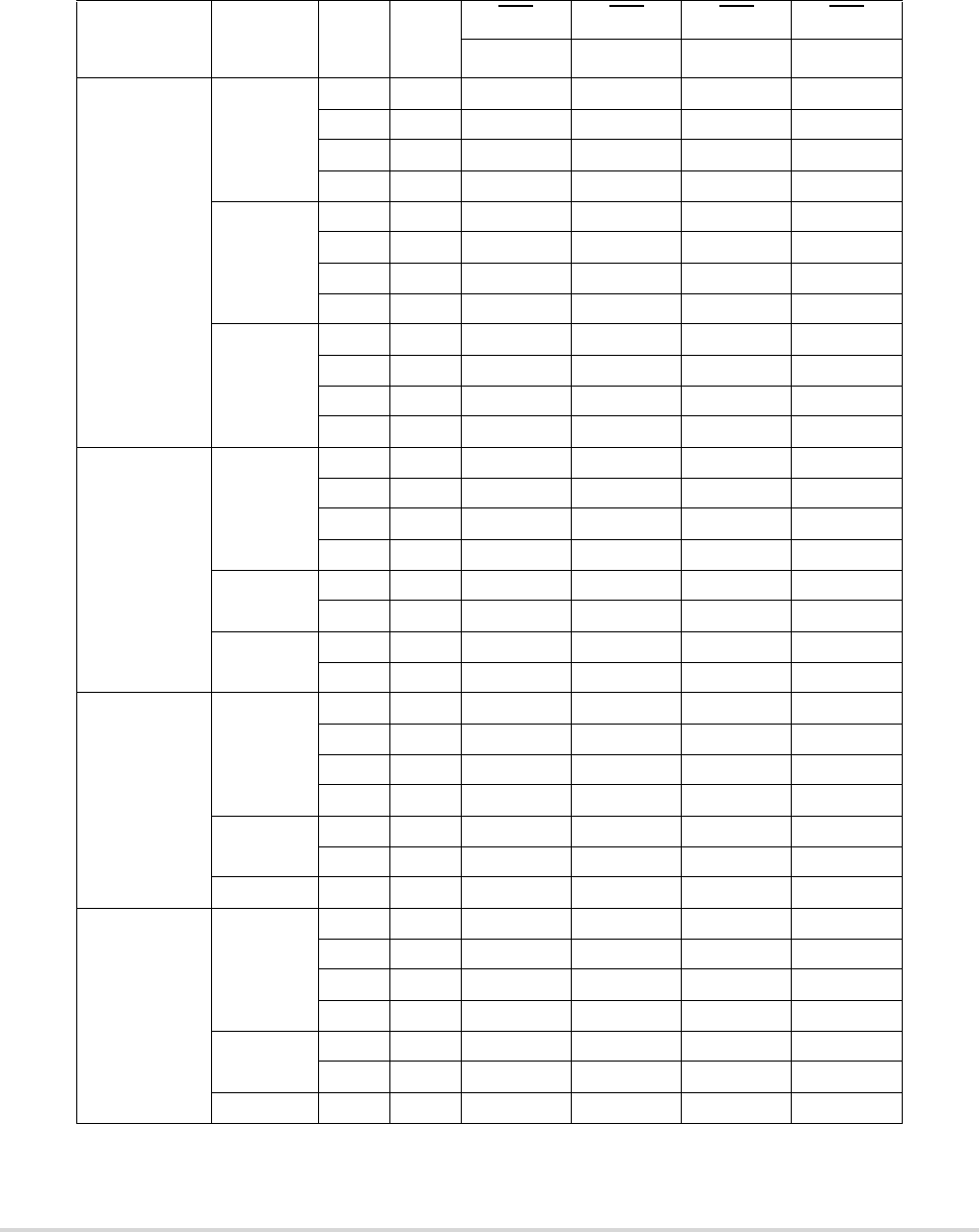

- 2.9 Standard One Operand Instruction Execution Times

- 2.10 Standard Two Operand Instruction Execution Times

- 2.11 Miscellaneous Instruction Execution Times

- 2.12 EMAC Instruction Execution Times

- 2.13 Branch Instruction Execution Times

- 2.14 ColdFire Instruction Set Architecture Enhancements

- Chapter 3 Enhanced Multiply-Accumulate Unit (EMAC)

- Chapter 4 Cache

- Chapter 5 Static RAM (SRAM)

- Chapter 6 ColdFire Flash Module (CFM)

- 6.1 Features

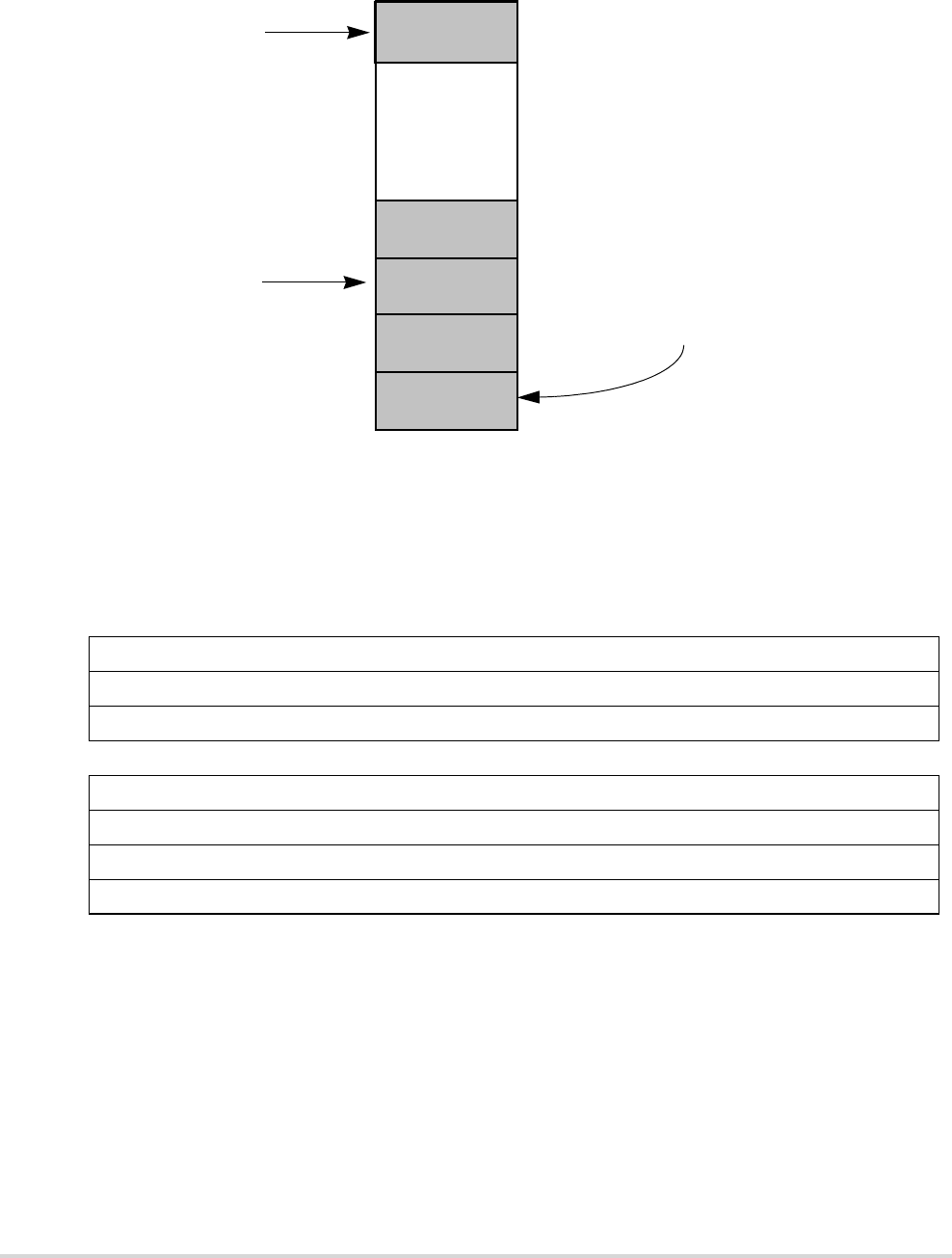

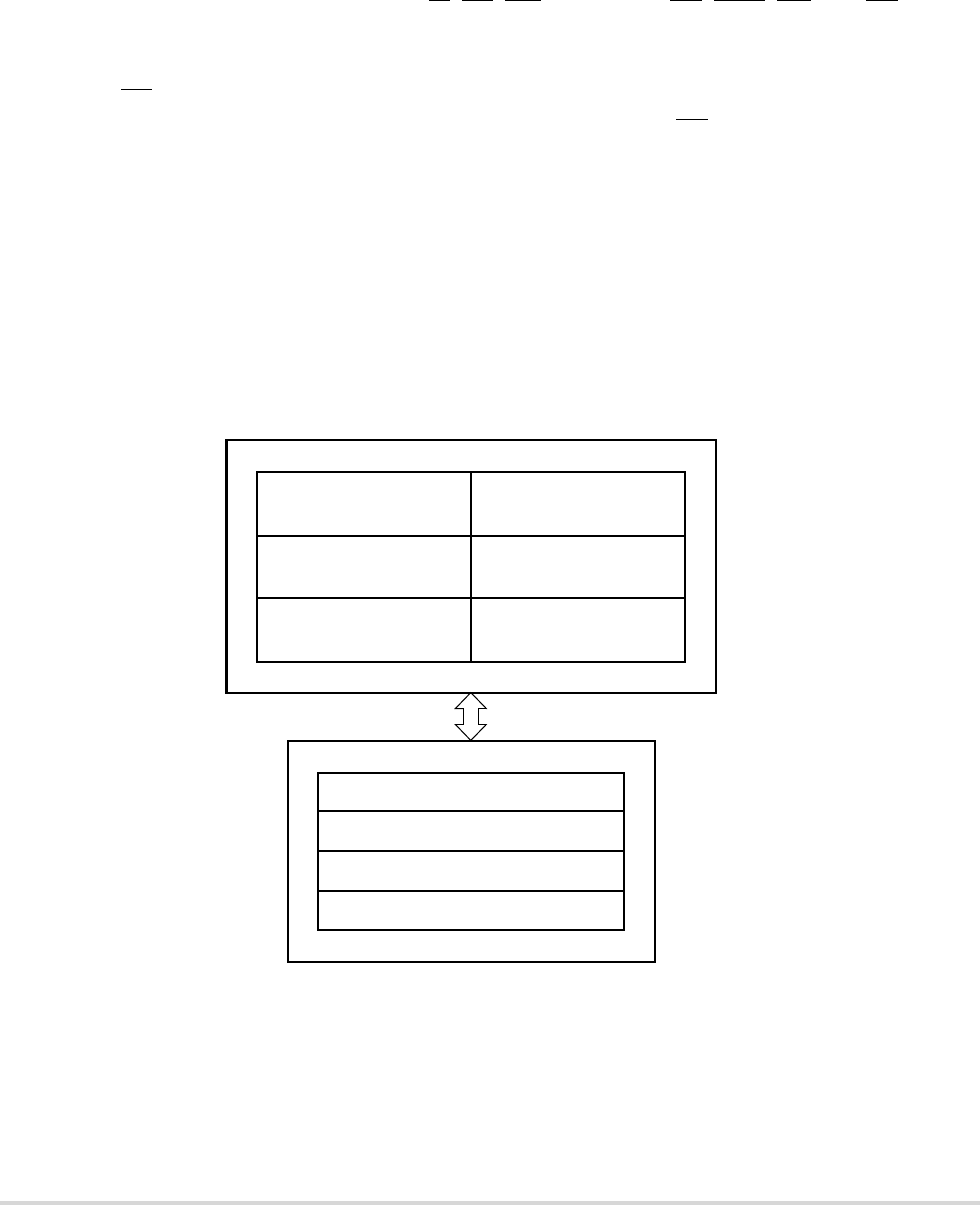

- 6.2 Block Diagram

- 6.3 Memory Map

- Figure 6-2. CFM Array Memory Map

- 6.3.1 CFM Configuration Field

- 6.3.2 Flash Base Address Register (FLASHBAR)

- 6.3.3 CFM Registers

- 6.3.4 Register Descriptions

- 6.3.4.1 CFM Configuration Register (CFMCR)

- 6.3.4.2 CFM Clock Divider Register (CFMCLKD)

- 6.3.4.3 CFM Security Register (CFMSEC)

- 6.3.4.4 CFM Protection Register (CFMPROT)

- 6.3.4.5 CFM Supervisor Access Register (CFMSACC)

- 6.3.4.6 CFM Data Access Register (CFMDACC)

- 6.3.4.7 CFM User Status Register (CFMUSTAT)

- 6.3.4.8 CFM Command Register (CFMCMD)

- 6.4 CFM Operation

- 6.5 Flash Security Operation

- 6.6 Reset

- 6.7 Interrupts

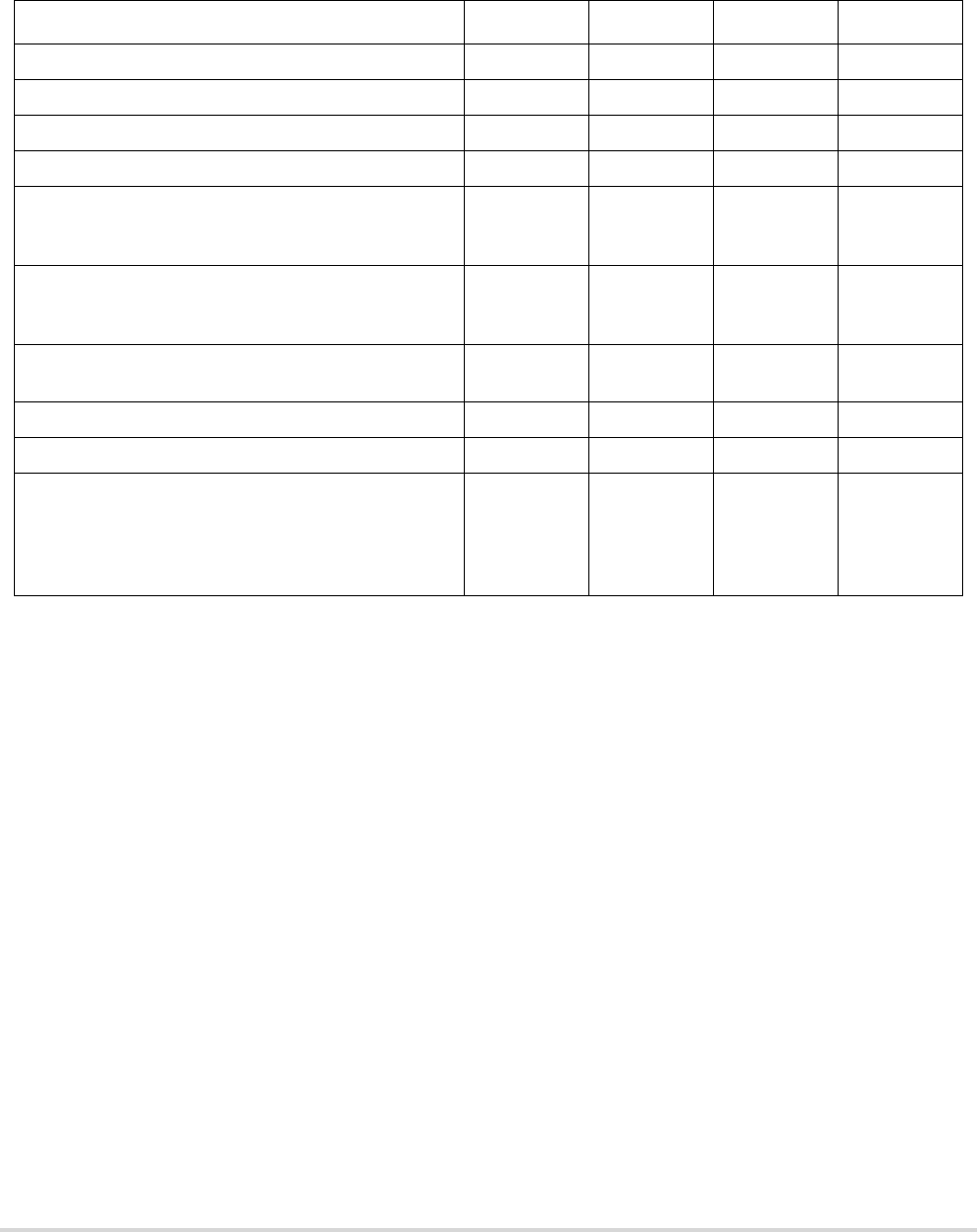

- Chapter 7 Power Management

- 7.1 Features

- 7.2 Memory Map and Registers

- 7.3 Functional Description

- 7.3.1 Low-Power Modes

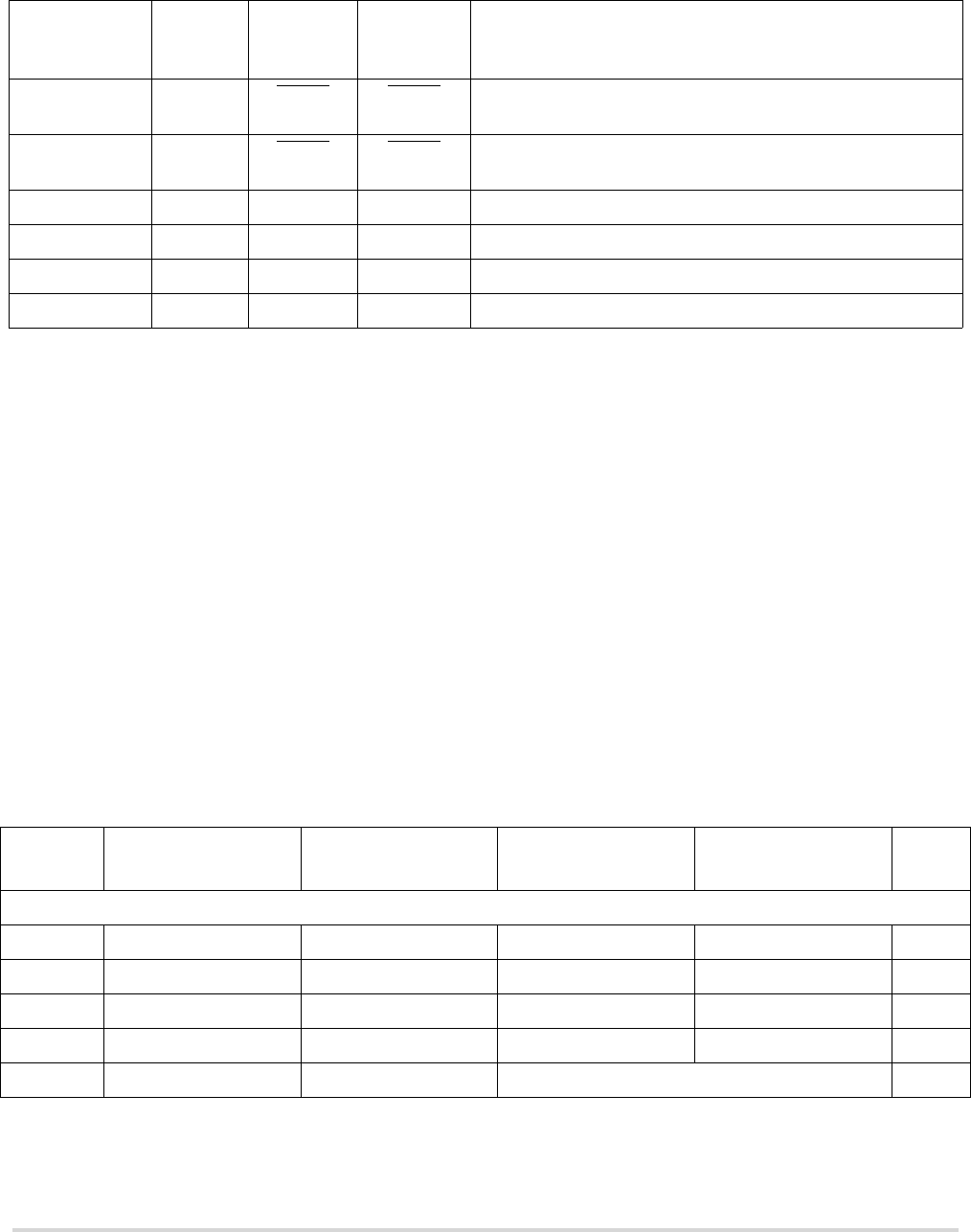

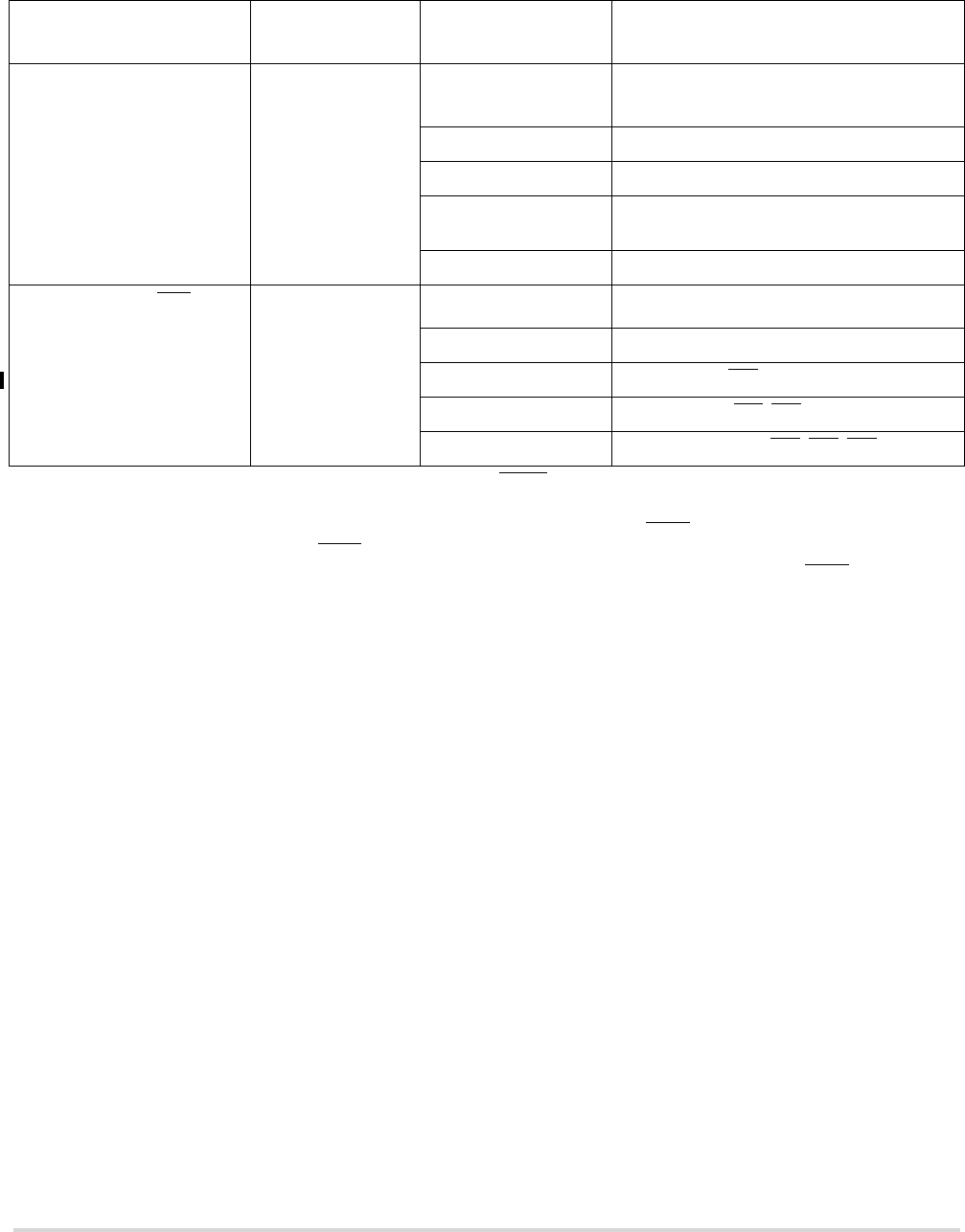

- 7.3.2 Peripheral Behavior in Low-Power Modes

- 7.3.2.1 ColdFire Core

- 7.3.2.2 Static Random-Access Memory (SRAM)

- 7.3.2.3 Flash

- 7.3.2.4 System Control Module (SCM)

- 7.3.2.5 SDRAM Controller (SDRAMC)

- 7.3.2.6 Chip Select Module

- 7.3.2.7 DMA Controller (DMAC0-DMA3)

- 7.3.2.8 UART Modules (UART0, UART1, and UART2)

- 7.3.2.9 I2C Module

- 7.3.2.10 Queued Serial Peripheral Interface (QSPI)

- 7.3.2.11 DMA Timers (DMAT0-DMAT3)

- 7.3.2.12 Interrupt Controllers (INTC0, INTC1)

- 7.3.2.13 Fast Ethernet Controller (FEC)

- 7.3.2.14 I/O Ports

- 7.3.2.15 Reset Controller

- 7.3.2.16 Chip Configuration Module

- 7.3.2.17 Clock Module

- 7.3.2.18 Edge Port

- 7.3.2.19 Watchdog Timer

- 7.3.2.20 Programmable Interrupt Timers (PIT0, PIT1, PIT2 and PIT3)

- 7.3.2.21 Queued Analog-to-Digital Converter (QADC)

- 7.3.2.22 General Purpose Timers (GPTA and GPTB)

- 7.3.2.23 FlexCAN

- 7.3.2.24 ColdFire Flash Module

- 7.3.2.25 BDM

- 7.3.2.26 JTAG

- 7.3.3 Summary of Peripheral State During Low-Power Modes

- Chapter 8 System Control Module (SCM)

- 8.1 Overview

- 8.2 Features

- 8.3 Memory Map and Register Definition

- 8.4 Register Descriptions

- 8.5 Internal Bus Arbitration

- 8.6 System Access Control Unit (SACU)

- Chapter 9 Clock Module

- 9.1 Features

- 9.2 Modes of Operation

- 9.3 Low-power Mode Operation

- 9.4 Block Diagram

- 9.5 Signal Descriptions

- 9.6 Memory Map and Registers

- 9.7 Functional Description

- 9.7.1 System Clock Modes

- 9.7.2 Clock Operation During Reset

- 9.7.3 System Clock Generation

- 9.7.4 PLL Operation

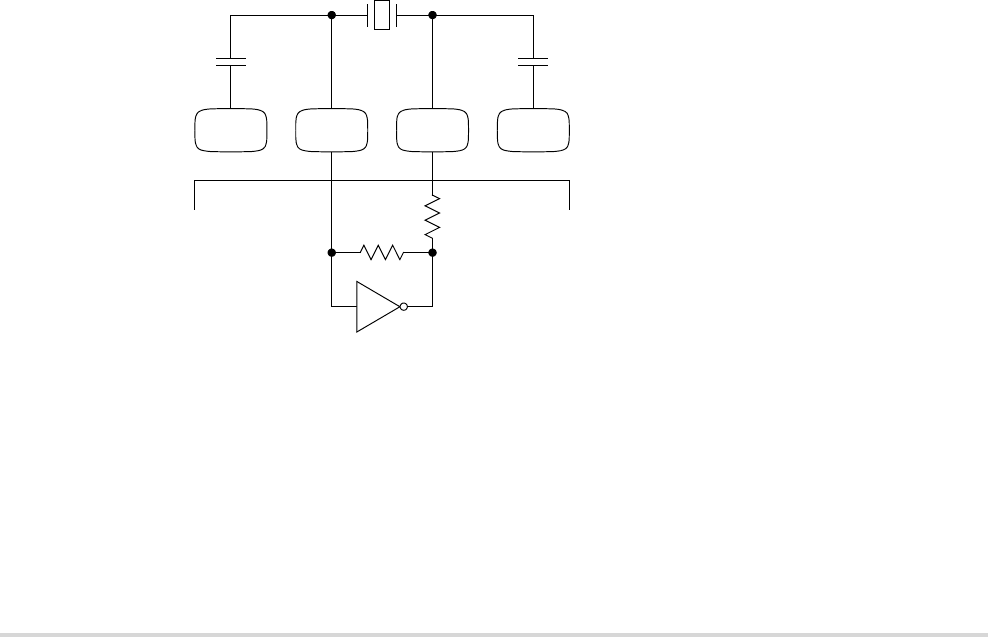

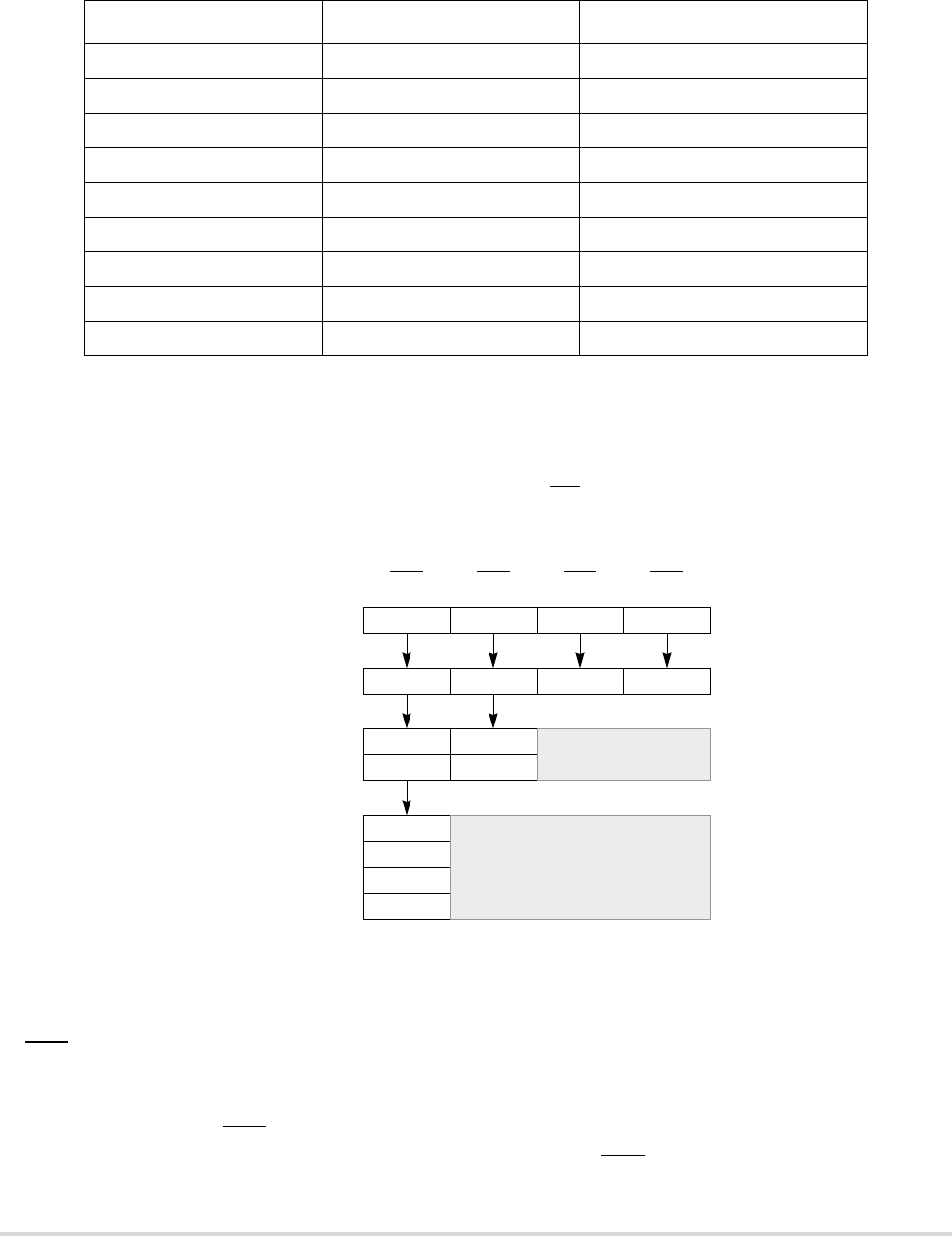

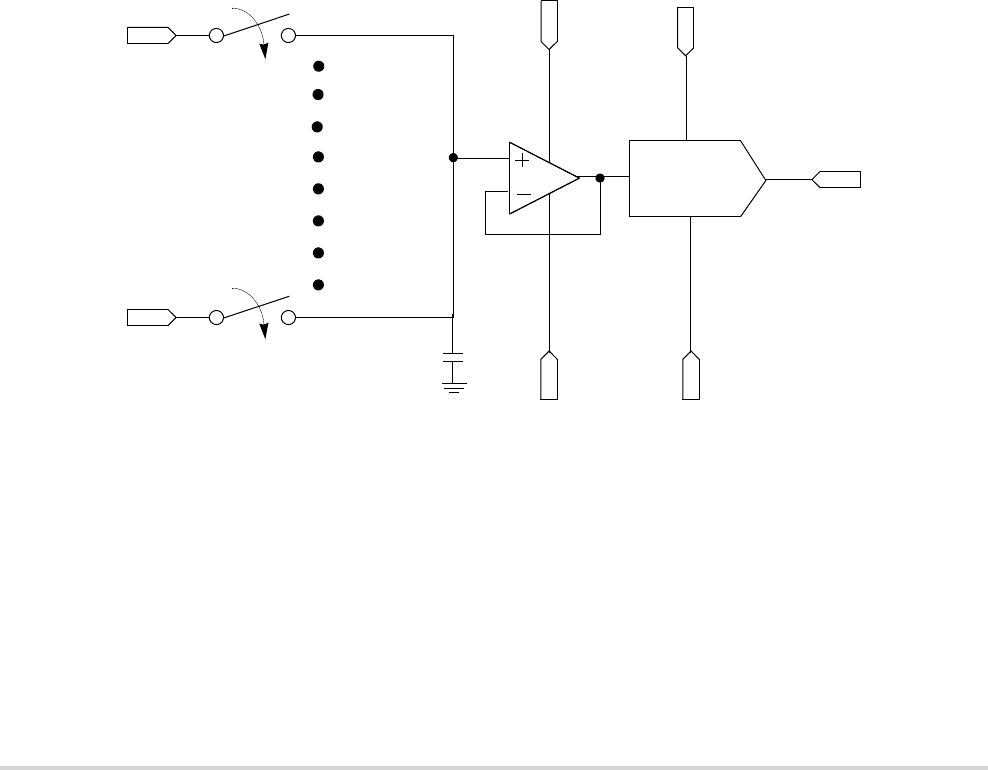

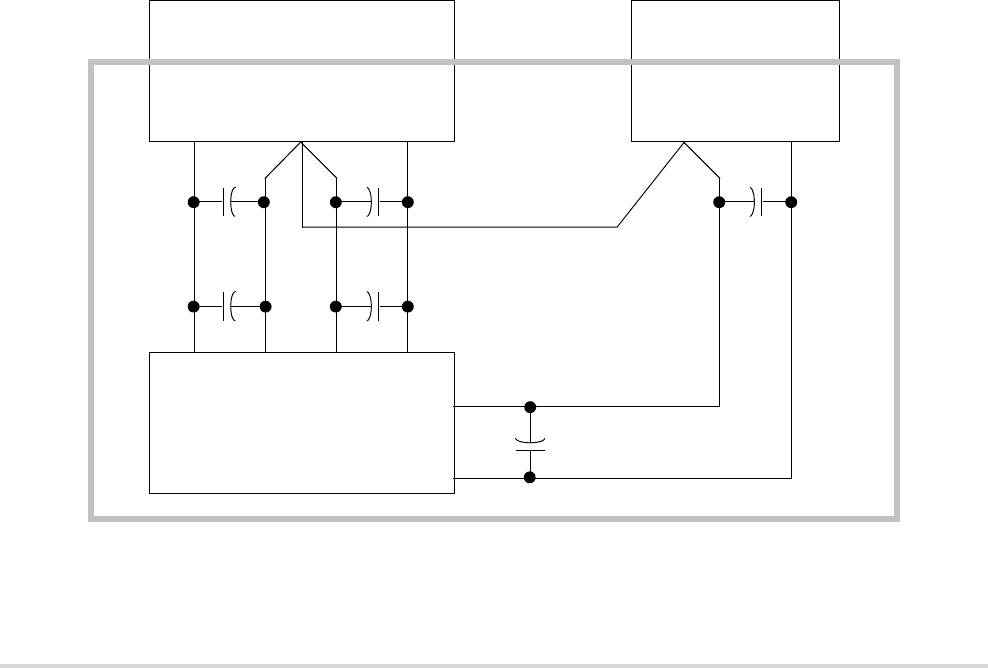

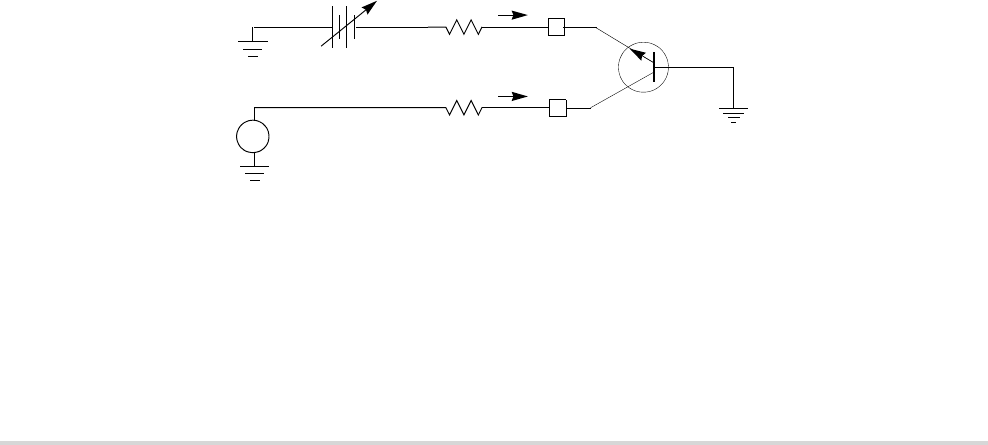

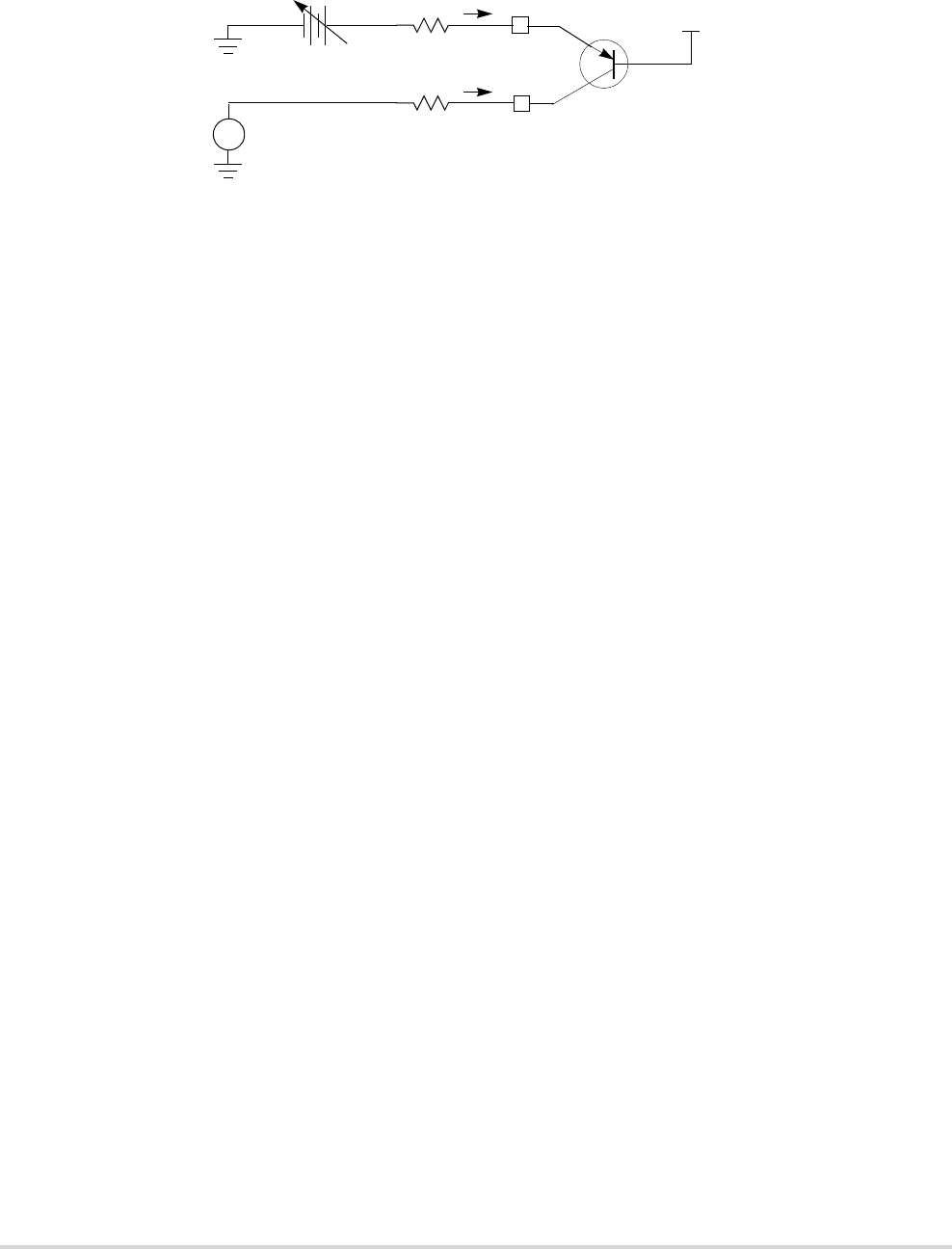

- Figure 9-5. Crystal Oscillator Example

- 9.7.4.1 Phase and Frequency Detector (PFD)

- 9.7.4.2 Charge Pump/Loop Filter

- 9.7.4.3 Voltage Control Output (VCO)

- 9.7.4.4 Multiplication Factor Divider (MFD)

- 9.7.4.5 PLL Lock Detection

- 9.7.4.6 PLL Loss of Lock Conditions

- 9.7.4.7 PLL Loss of Lock Reset

- 9.7.4.8 Loss of Clock Detection

- 9.7.4.9 Loss of Clock Reset

- 9.7.4.10 Alternate Clock Selection

- 9.7.4.11 Loss of Clock in Stop Mode

- Chapter 10 Interrupt Controller Modules

- 10.1 68K/ColdFire Interrupt Architecture Overview

- 10.2 Memory Map

- 10.3 Register Descriptions

- 10.3.1 Interrupt Pending Registers (IPRHn, IPRLn)

- 10.3.2 Interrupt Mask Register (IMRHn, IMRLn)

- 10.3.3 Interrupt Force Registers (INTFRCHn, INTFRCLn)

- 10.3.4 Interrupt Request Level Register (IRLRn)

- 10.3.5 Interrupt Acknowledge Level and Priority Register (IACKLPRn)

- 10.3.6 Interrupt Control Register (ICRnx, (x = 1, 2,..., 63))

- 10.3.7 Software and Level n IACK Registers (SWIACKR, L1IACK-L7IACK)

- 10.4 Prioritization Between Interrupt Controllers

- 10.5 Low-Power Wakeup Operation

- Chapter 11 Edge Port Module (EPORT)

- 11.1 Introduction

- 11.2 Low-Power Mode Operation

- 11.3 Interrupt/General-Purpose I/O Pin Descriptions

- 11.4 Memory Map and Registers

- Chapter 12 Chip Select Module

- 12.1 Overview

- 12.2 Chip Select Module Signals

- 12.3 Chip Select Operation

- 12.4 Chip Select Registers

- Chapter 13 External Interface Module (EIM)

- 13.1 Features

- 13.2 Bus and Control Signals

- 13.3 Bus Characteristics

- 13.4 Data Transfer Operation

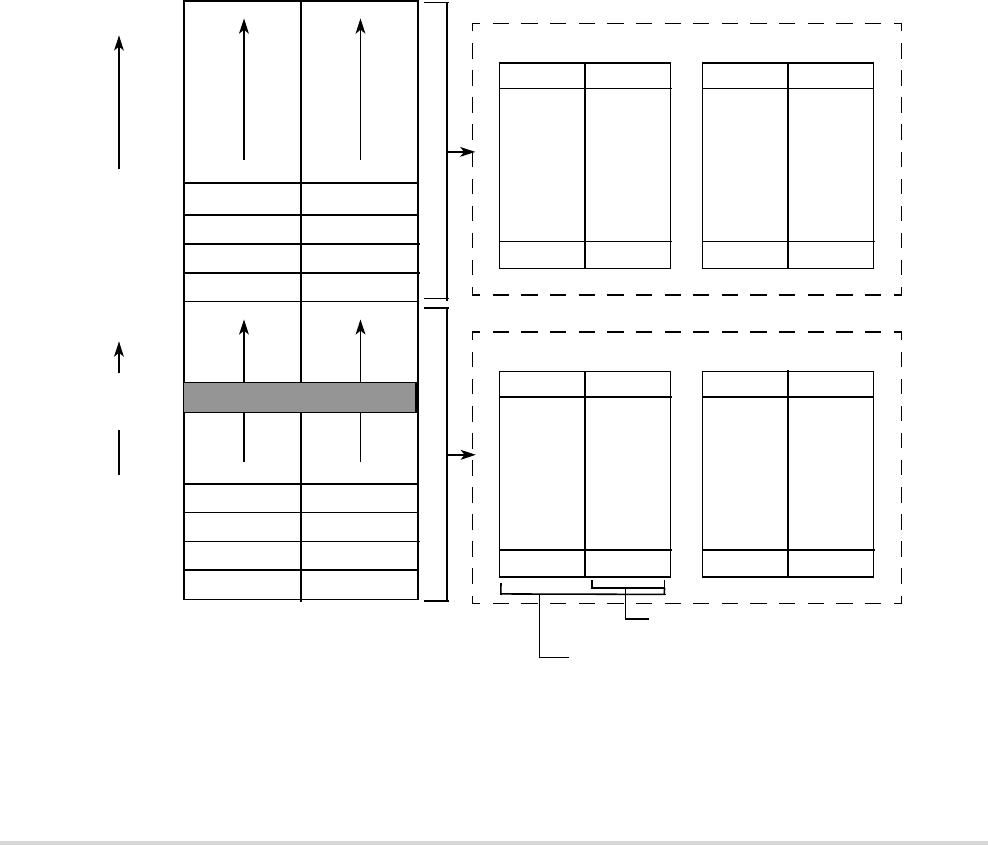

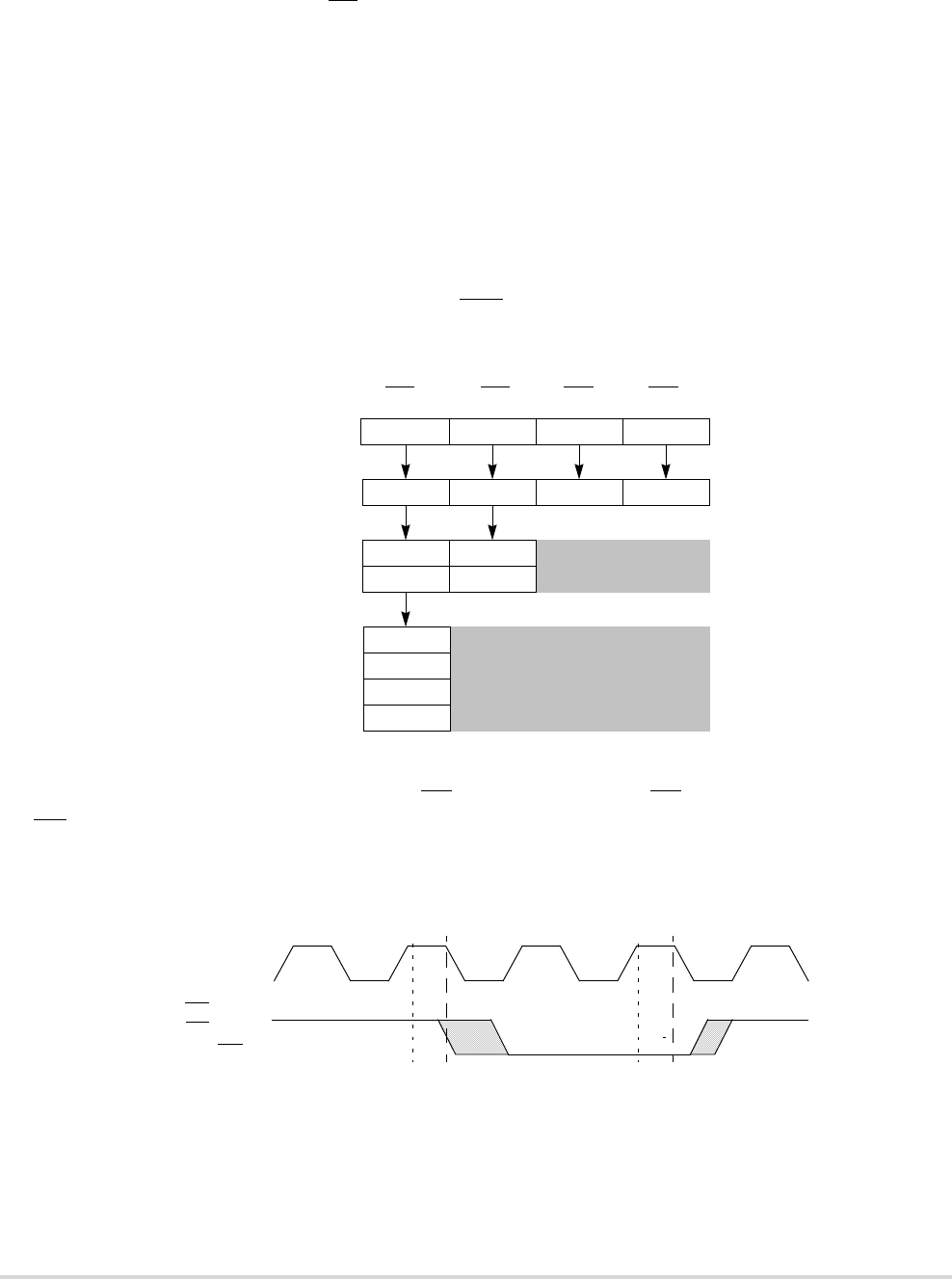

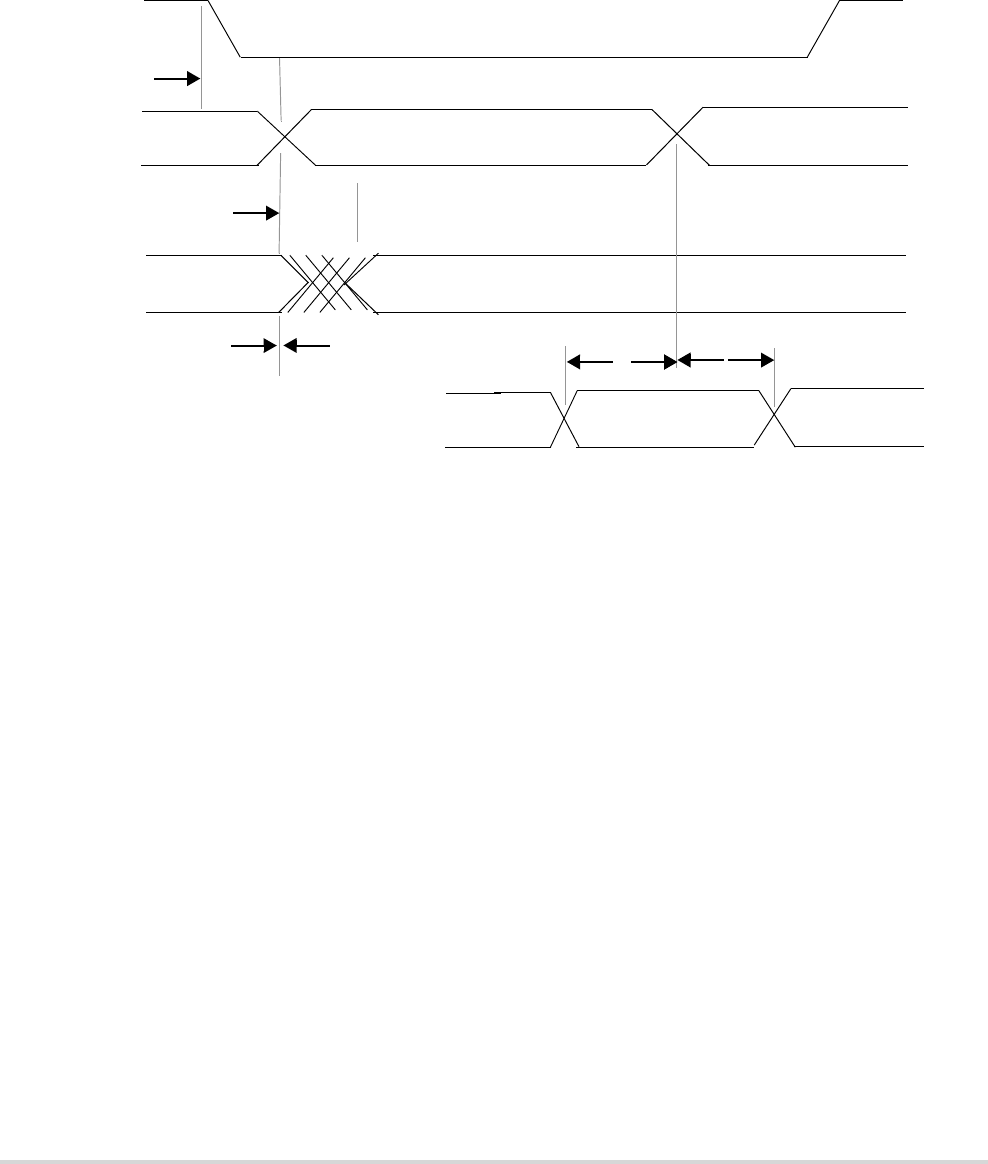

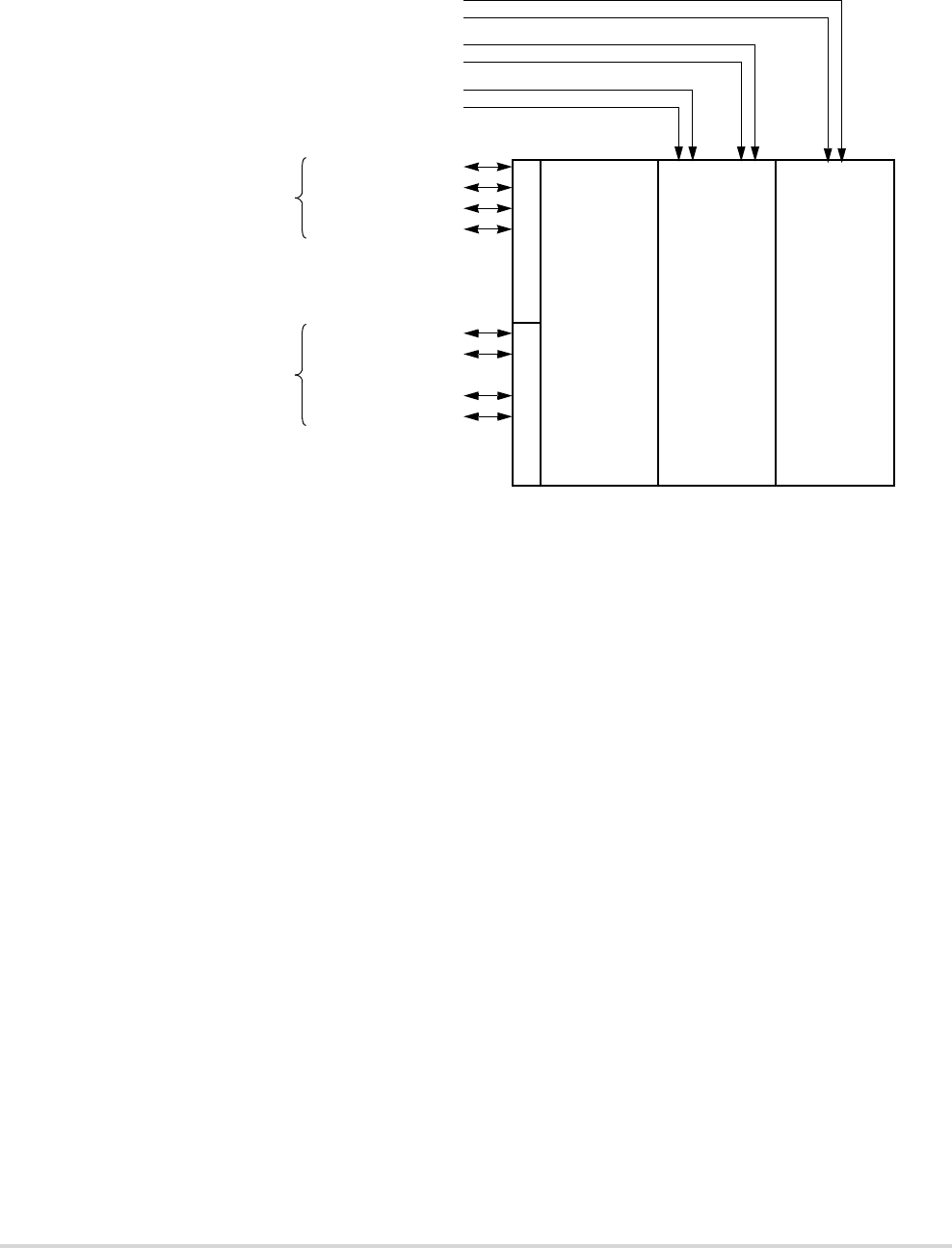

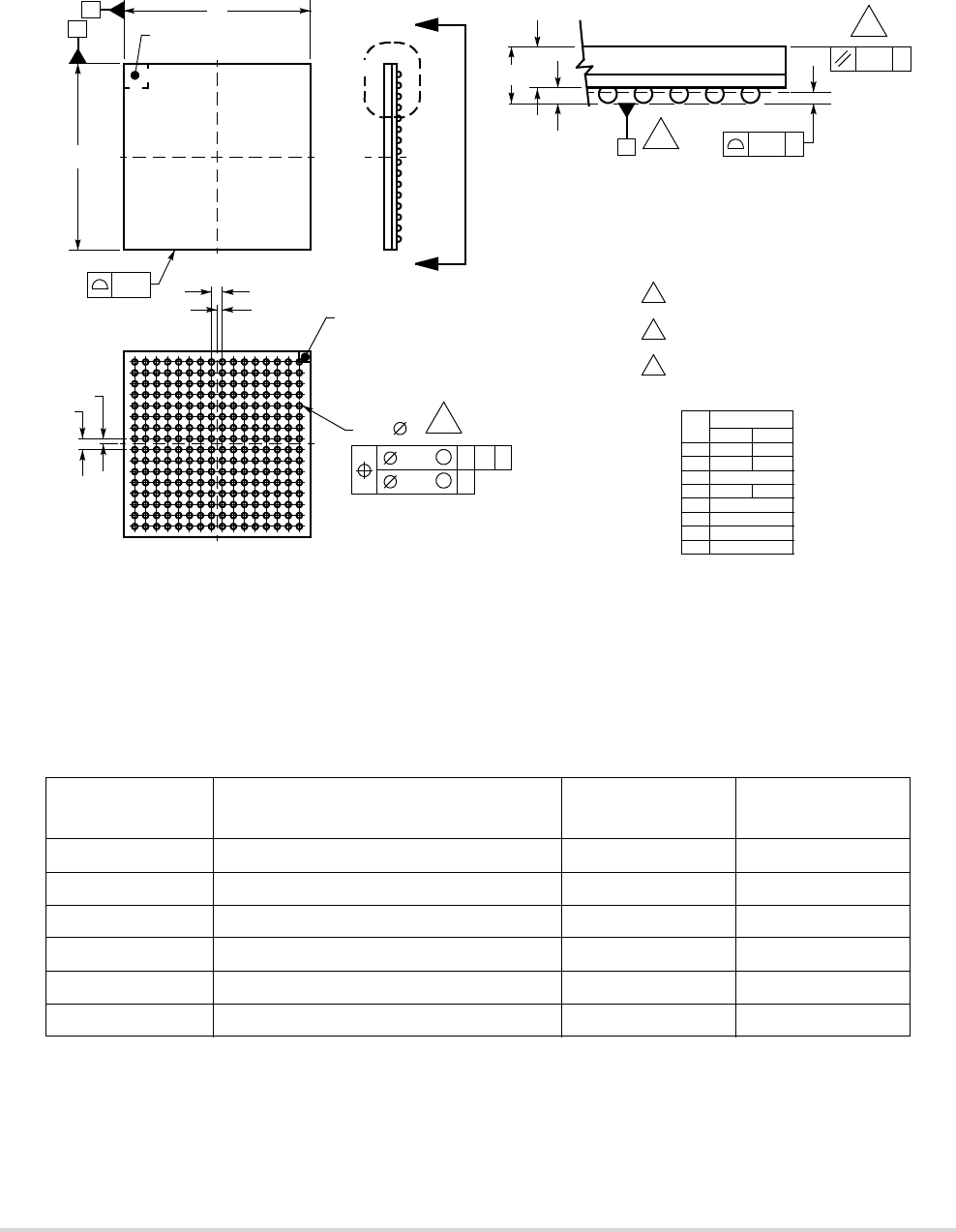

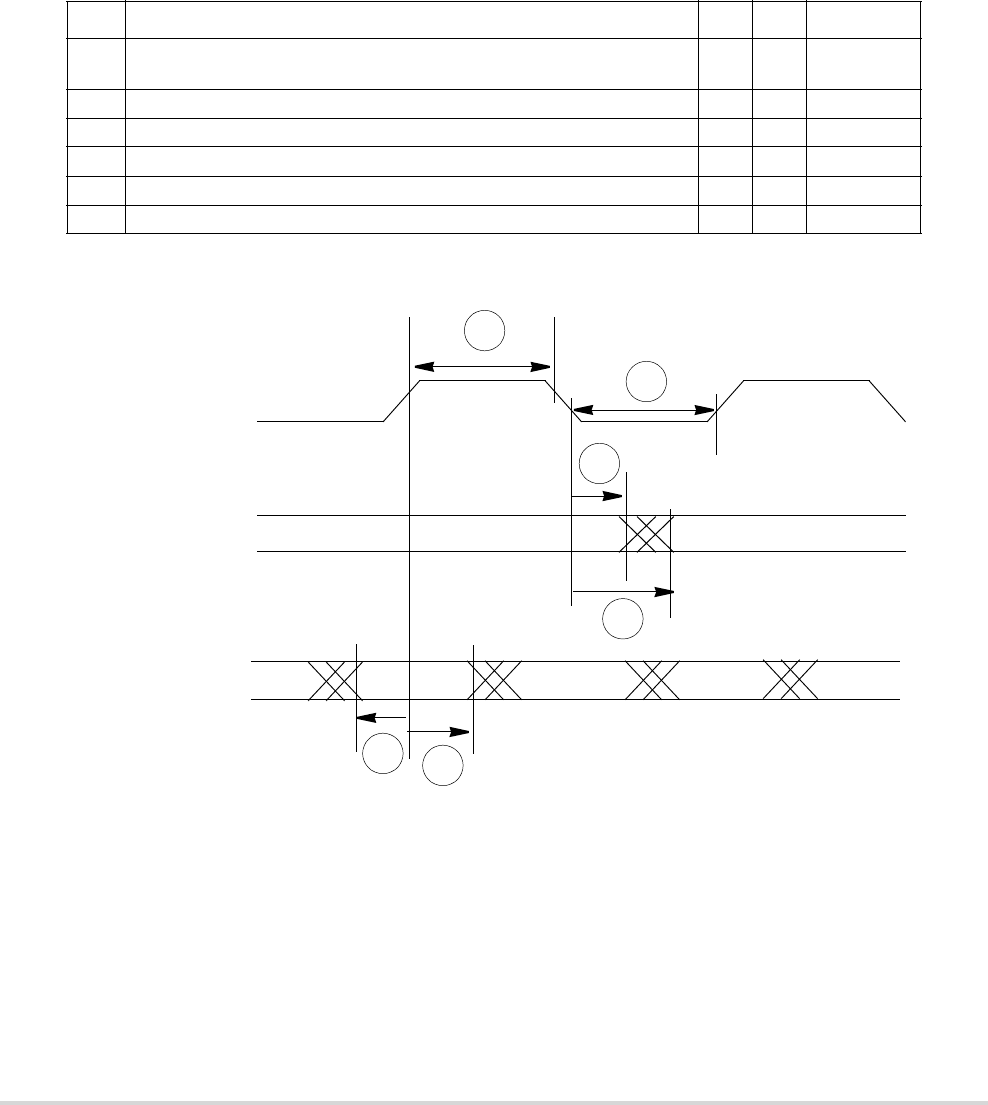

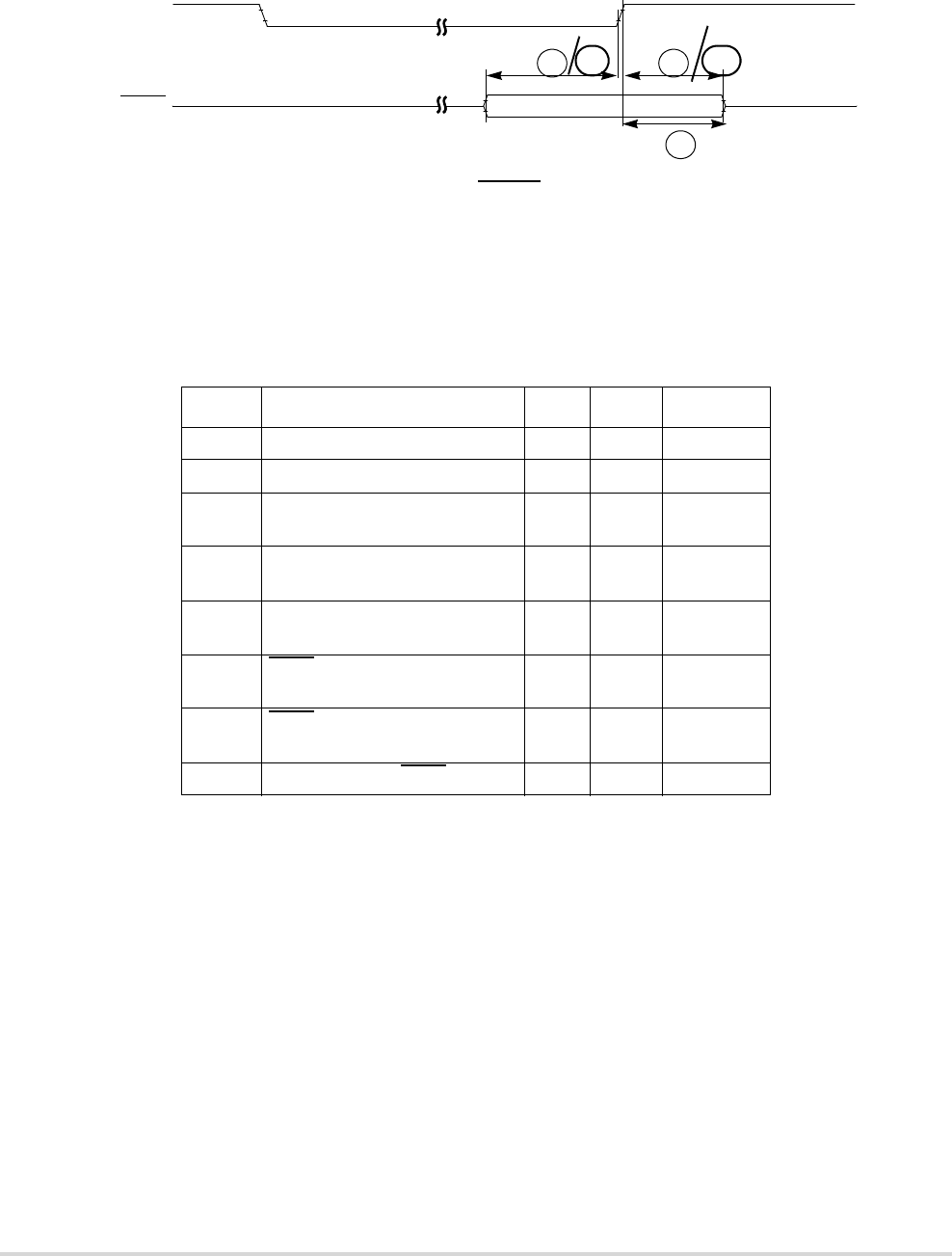

- Figure 13-2. Connections for External Memory Port Sizes

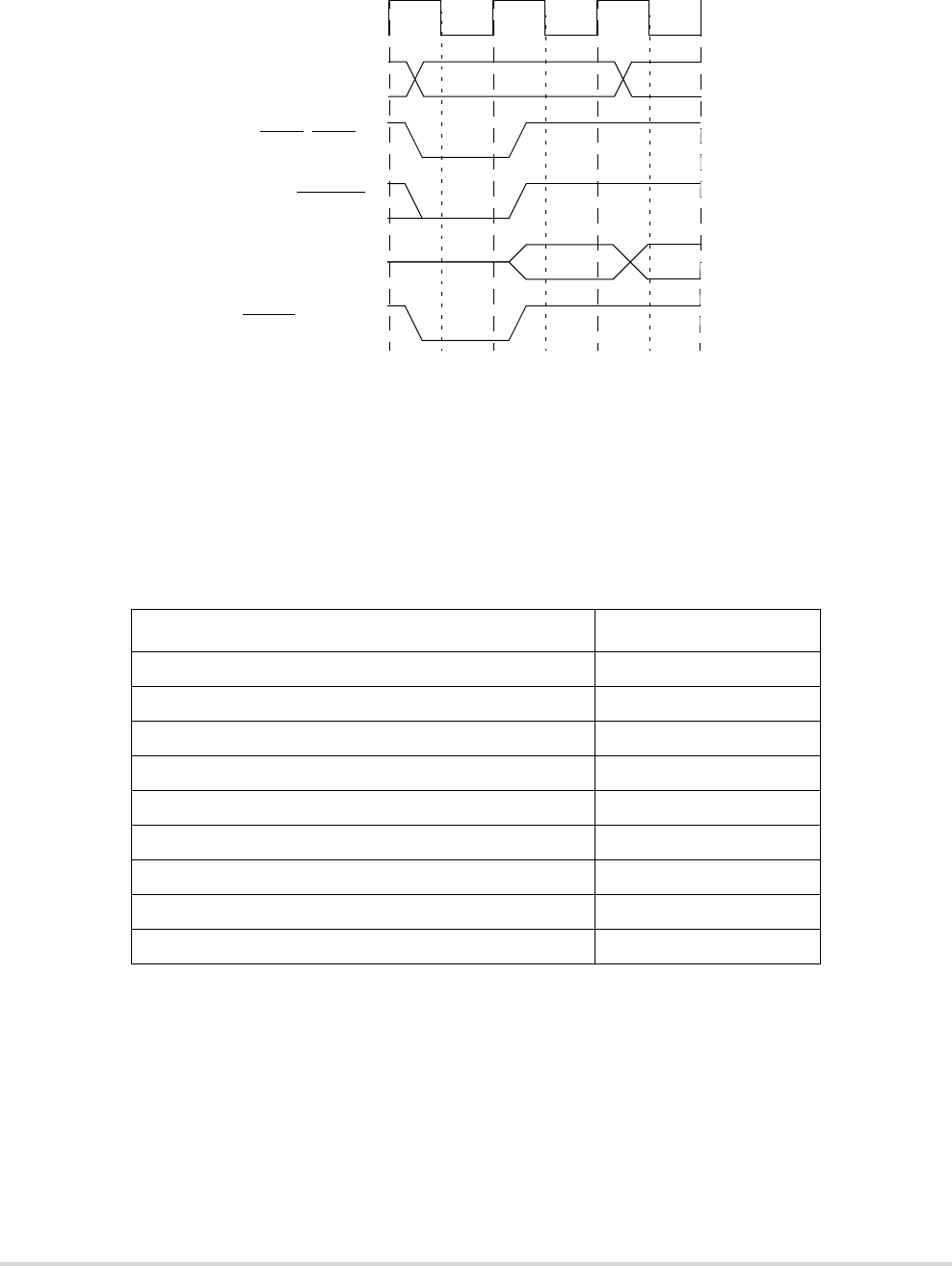

- Figure 13-3. Chip-Select Module Output Timing Diagram

- 13.4.1 Bus Cycle Execution

- 13.4.2 Data Transfer Cycle States

- 13.4.3 Read Cycle

- 13.4.4 Write Cycle

- 13.4.5 Fast Termination Cycles

- 13.4.6 Back-to-Back Bus Cycles

- 13.4.7 Burst Cycles

- 13.5 Misaligned Operands

- Chapter 14 Signal Descriptions

- 14.1 Overview

- 14.2 MCF5282 External Signals

- 14.2.1 External Interface Module (EIM) Signals

- 14.2.1.1 Address Bus (A[23:0])

- 14.2.1.2 Data Bus (D[31:0])

- 14.2.1.3 Byte Strobes (BS[3:0])

- 14.2.1.4 Output Enable (OE)

- 14.2.1.5 Transfer Acknowledge (TA)

- 14.2.1.6 Transfer Error Acknowledge (TEA)

- 14.2.1.7 Read/Write (R/W)

- 14.2.1.8 Transfer Size(SIZ[1:0])

- 14.2.1.9 Transfer Start (TS)

- 14.2.1.10 Transfer In Progress (TIP)

- 14.2.1.11 Chip Selects (CS[6:0])

- 14.2.2 SDRAM Controller Signals

- 14.2.3 Clock and Reset Signals

- 14.2.4 Chip Configuration Signals

- 14.2.5 External Interrupt Signals

- 14.2.6 Ethernet Module Signals

- 14.2.6.1 Management Data (EMDIO)

- 14.2.6.2 Management Data Clock (EMDC)

- 14.2.6.3 Transmit Clock (ETXCLK)

- 14.2.6.4 Transmit Enable (ETXEN)

- 14.2.6.5 Transmit Data 0 (ETXD0)

- 14.2.6.6 Collision (ECOL)

- 14.2.6.7 Receive Clock (ERXCLK)

- 14.2.6.8 Receive Data Valid (ERXDV)

- 14.2.6.9 Receive Data 0 (ERXD0)

- 14.2.6.10 Carrier Receive Sense (ECRS)

- 14.2.6.11 Transmit Data 1-3 (ETXD[3:1])

- 14.2.6.12 Transmit Error (ETXER)

- 14.2.6.13 Receive Data 1-3 (ERXD[3:1])

- 14.2.6.14 Receive Error (ERXER)

- 14.2.7 Queued Serial Peripheral Interface (QSPI) Signals

- 14.2.8 FlexCAN Signals

- 14.2.9 I2C Signals

- 14.2.10 UART Module Signals

- 14.2.11 General Purpose Timer Signals

- 14.2.12 DMA Timer Signals

- 14.2.13 Analog-to-Digital Converter Signals

- 14.2.13.1 QADC Analog Input (AN0/ANW)

- 14.2.13.2 QADC Analog Input (AN1/ANX)

- 14.2.13.3 QADC Analog Input (AN2/ANY)

- 14.2.13.4 QADC Analog Input (AN3/ANZ)

- 14.2.13.5 QADC Analog Input (AN52/MA0)

- 14.2.13.6 QADC Analog Input (AN53/MA1)

- 14.2.13.7 QADC Analog Input (AN55/TRIG1)

- 14.2.13.8 QADC Analog Input (AN56/TRIG2)

- 14.2.14 Debug Support Signals

- 14.2.14.1 JTAG_EN

- 14.2.14.2 Development Serial Clock/Test Reset (DSCLK/TRST)

- 14.2.14.3 Breakpoint/Test Mode Select (BKPT/TMS)

- 14.2.14.4 Development Serial Input/Test Data (DSI/TDI)

- 14.2.14.5 Development Serial Output/Test Data (DSO/TDO)

- 14.2.14.6 Test Clock (TCLK)

- 14.2.14.7 Debug Data (DDATA[3:0])

- 14.2.14.8 Processor Status Outputs (PST[3:0])

- 14.2.15 Test Signals

- 14.2.16 Power and Reference Signals

- 14.2.16.1 QADC Analog Reference (VRH, VRL)

- 14.2.16.2 QADC Analog Supply (VDDA, VSSA)

- 14.2.16.3 PLL Analog Supply (VDDPLL, VSSPLL)

- 14.2.16.4 QADC Positive Supply (VDDH)

- 14.2.16.5 Power for Flash Erase/Program (VPP)

- 14.2.16.6 Power and Ground for Flash Array (VDDF, VSSF)

- 14.2.16.7 Standby Power (VSTBY)

- 14.2.16.8 Positive Supply (VDD)

- 14.2.16.9 Ground (VSS)

- 14.2.1 External Interface Module (EIM) Signals

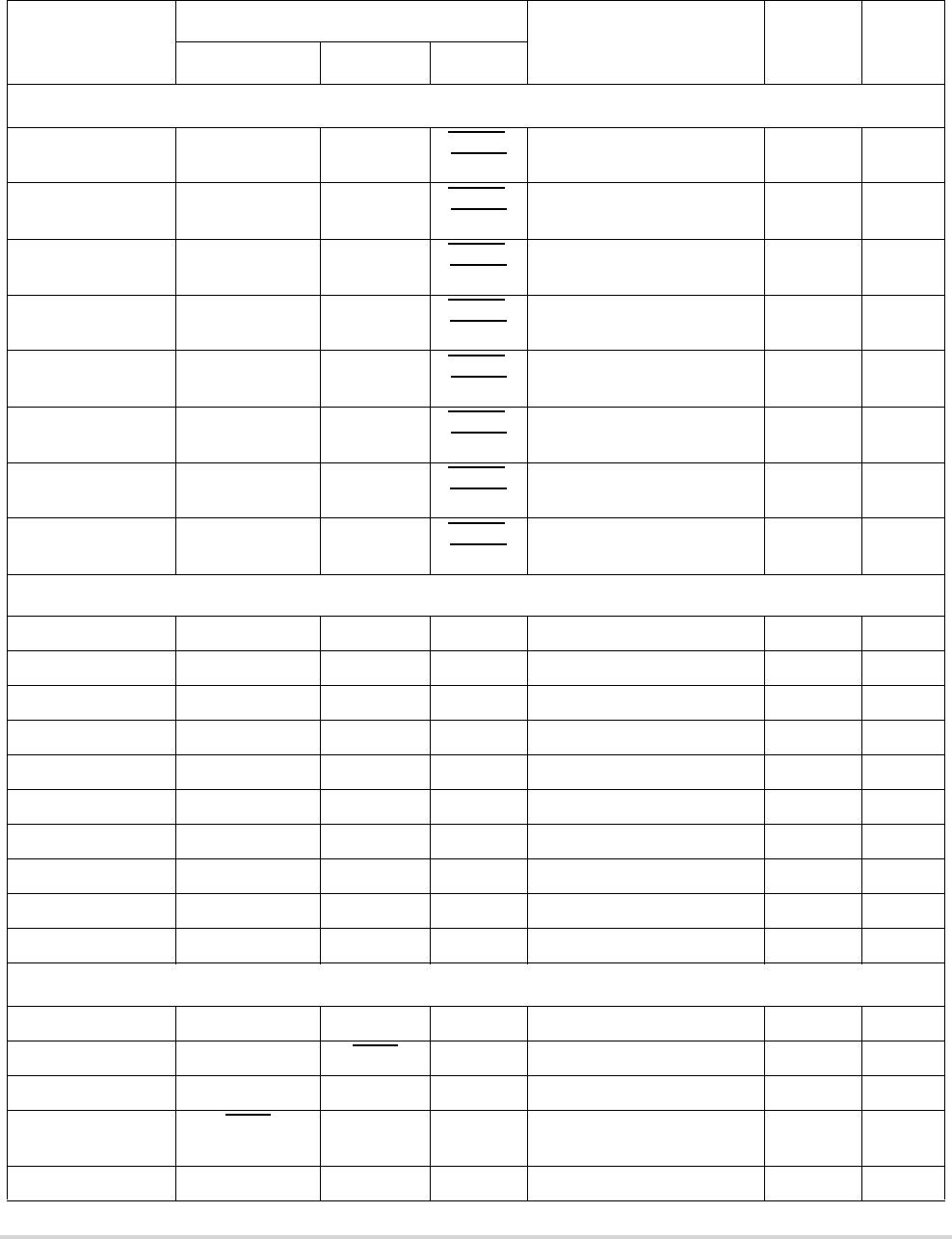

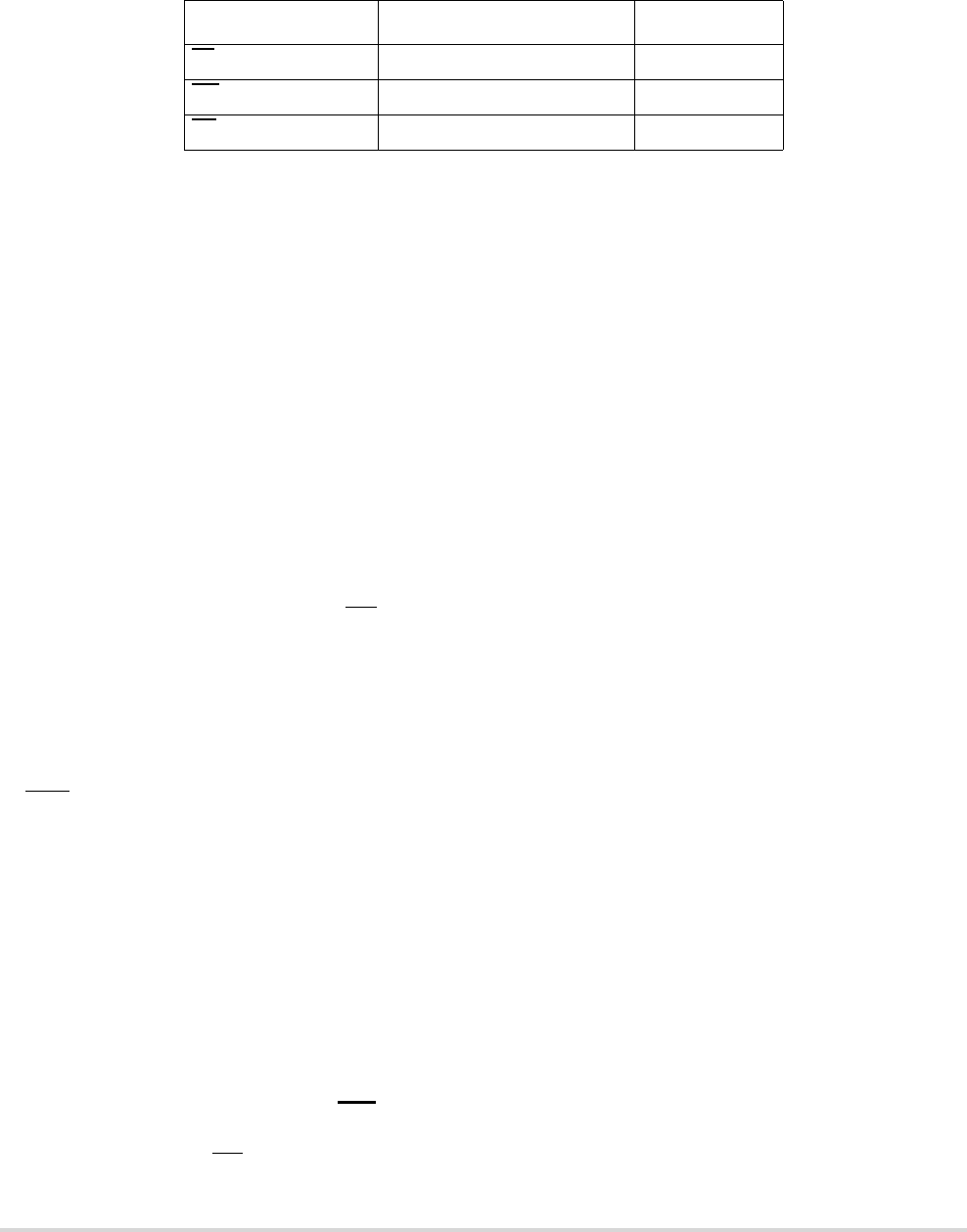

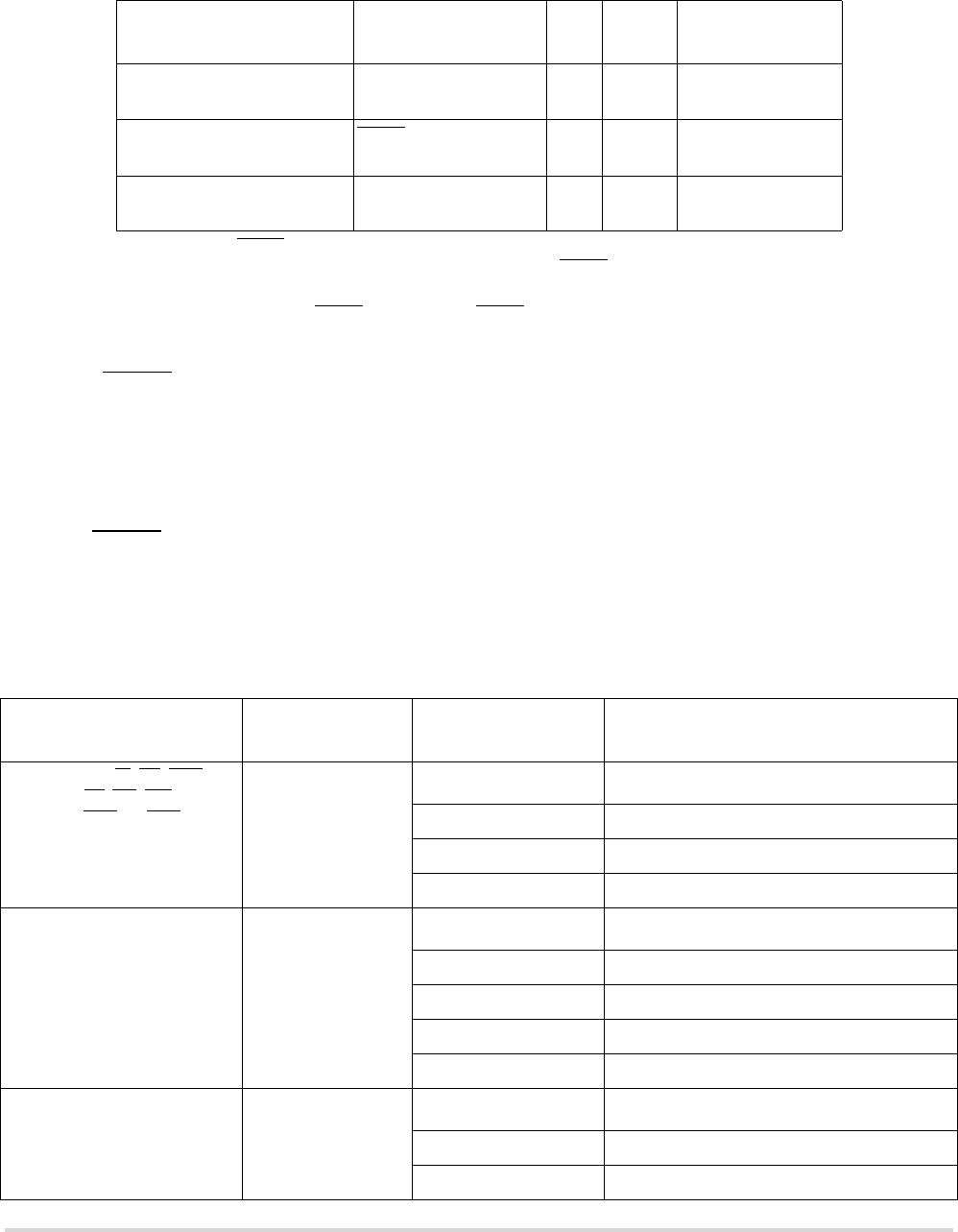

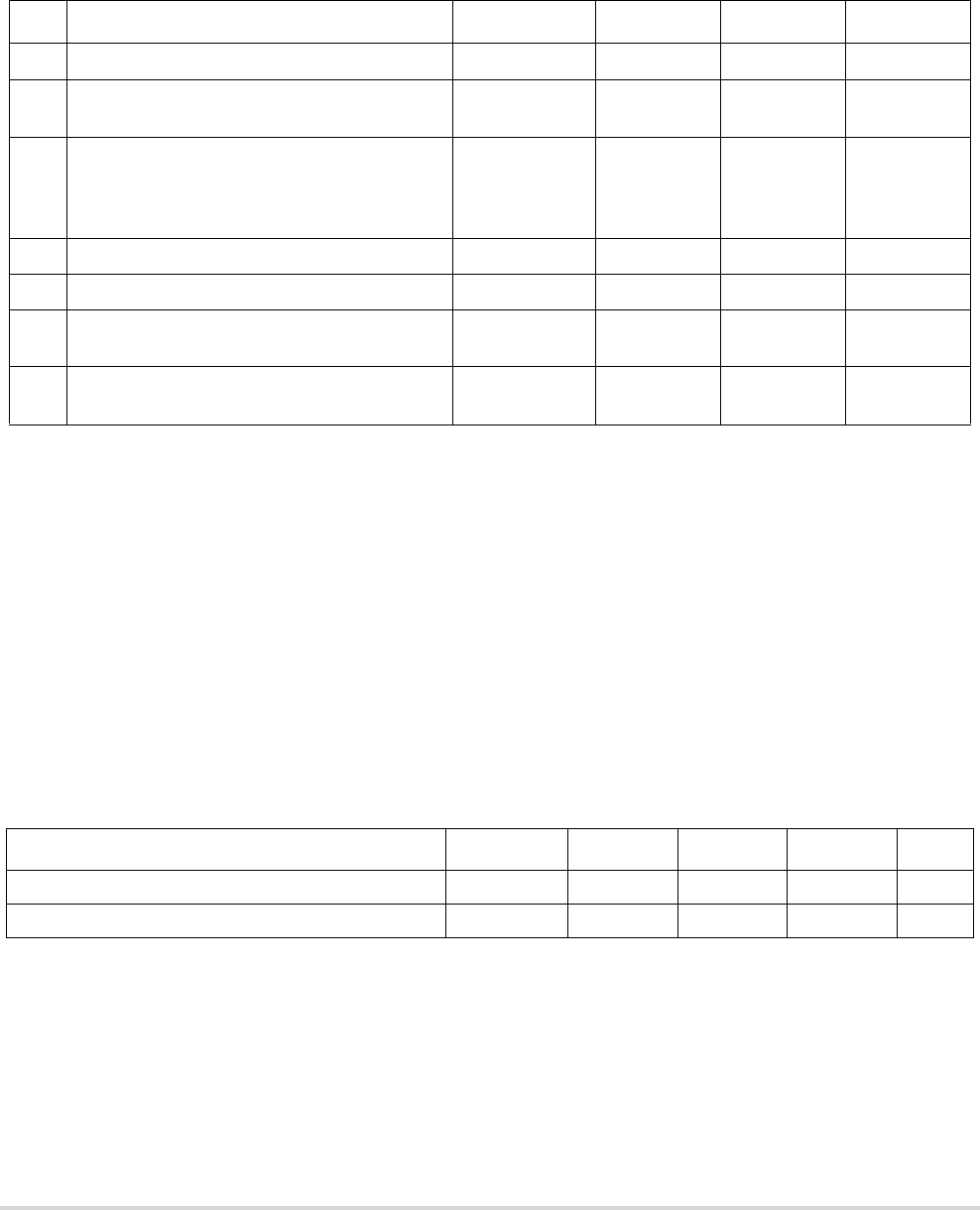

- Chapter 15 Synchronous DRAM Controller Module

- 15.1 Overview

- 15.2 SDRAM Controller Operation

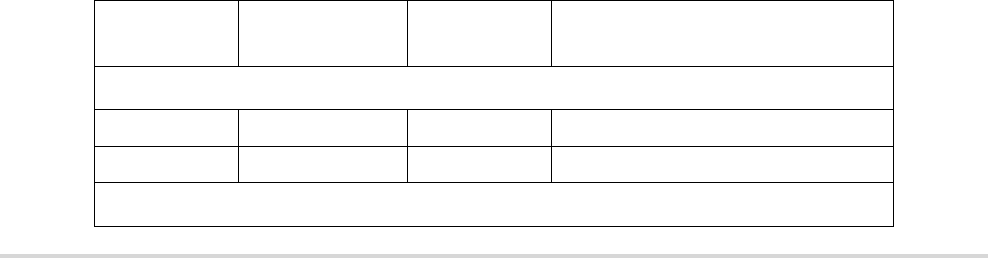

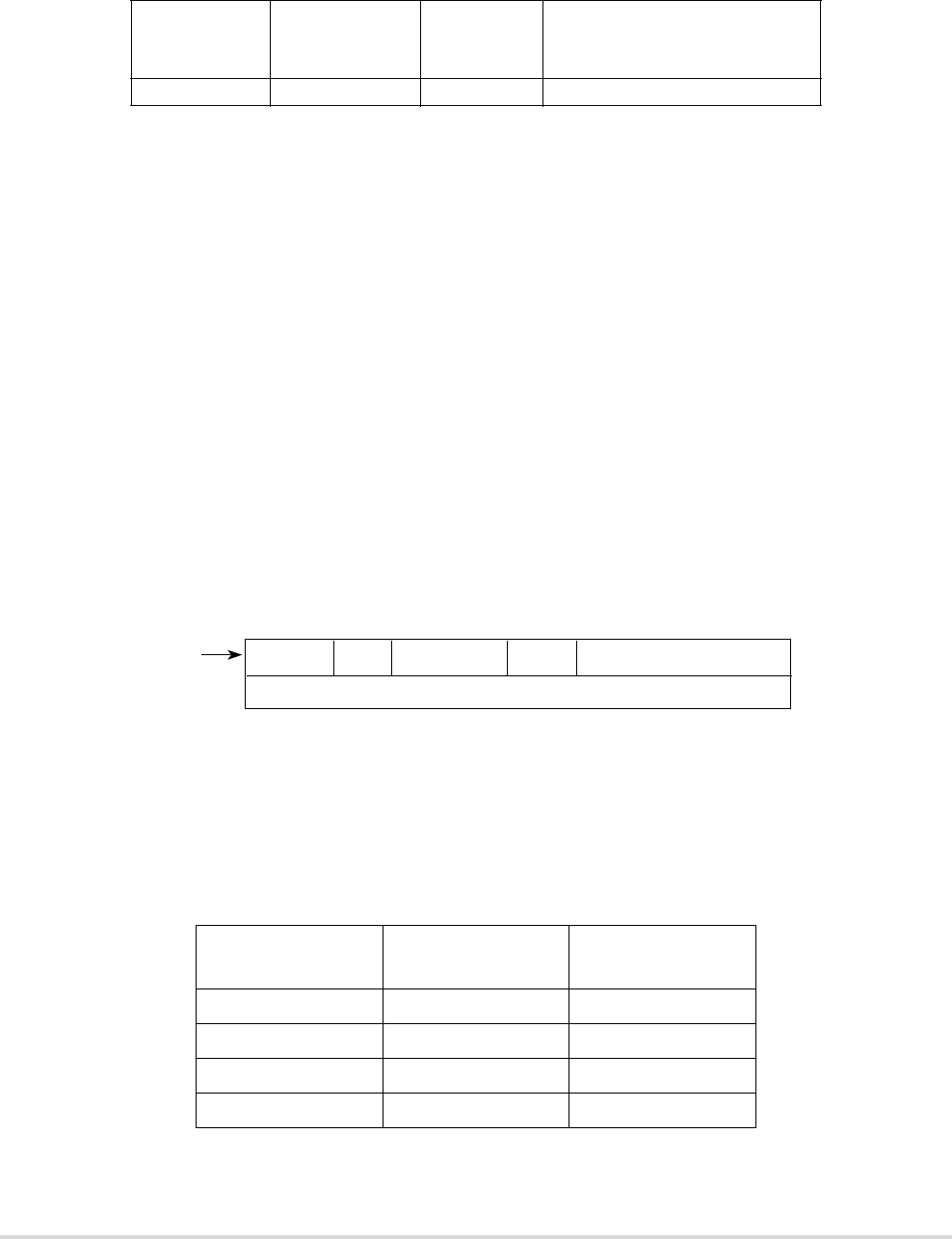

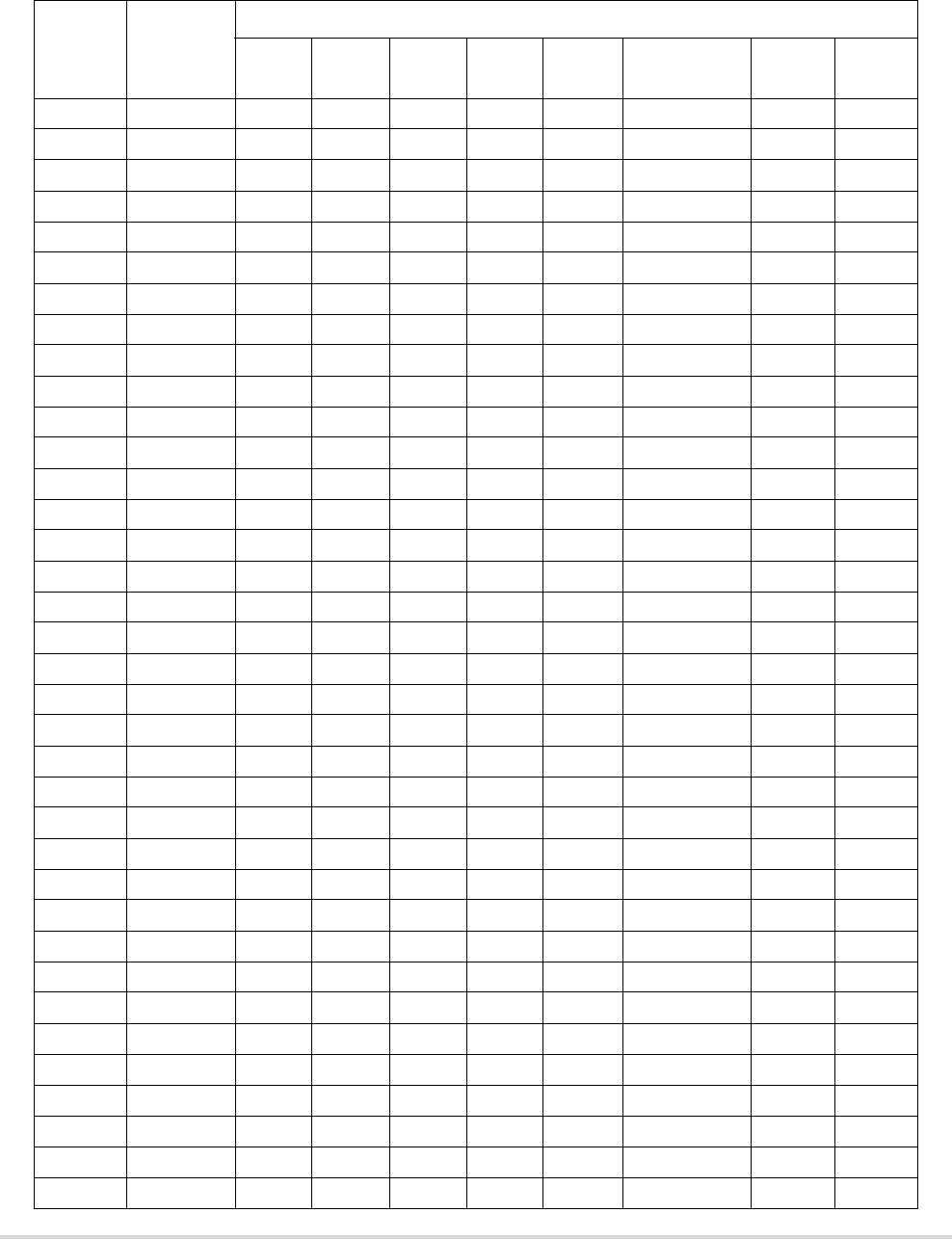

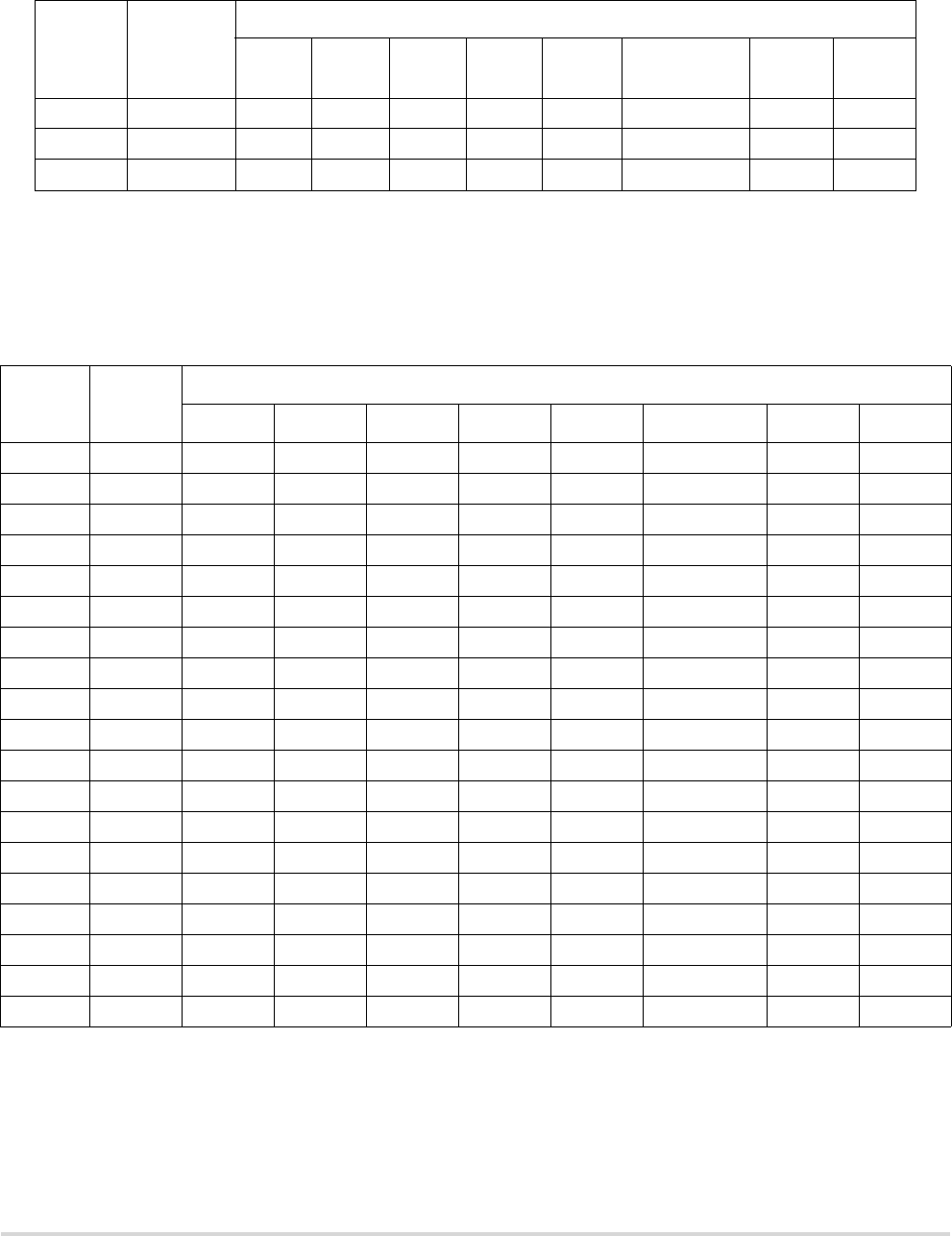

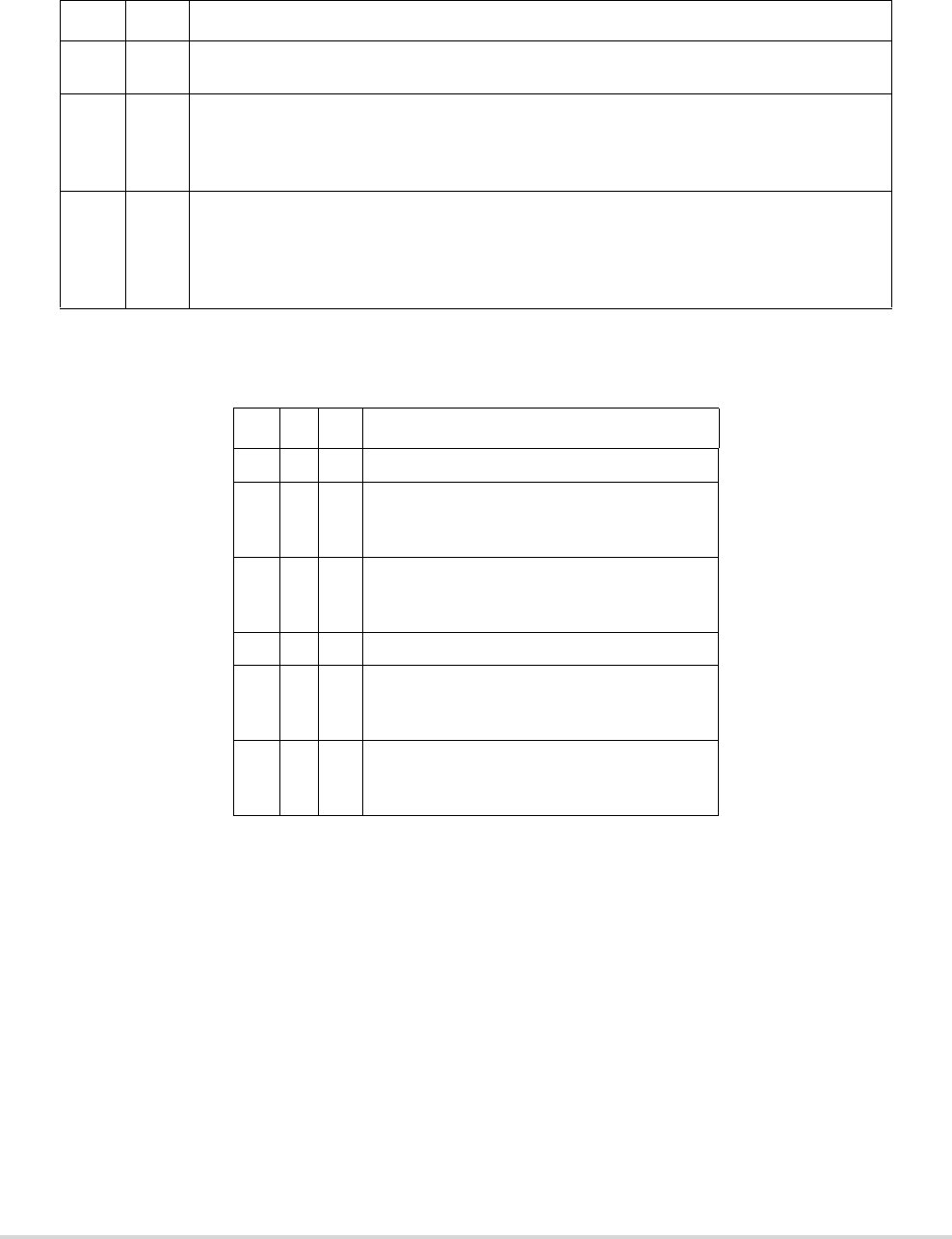

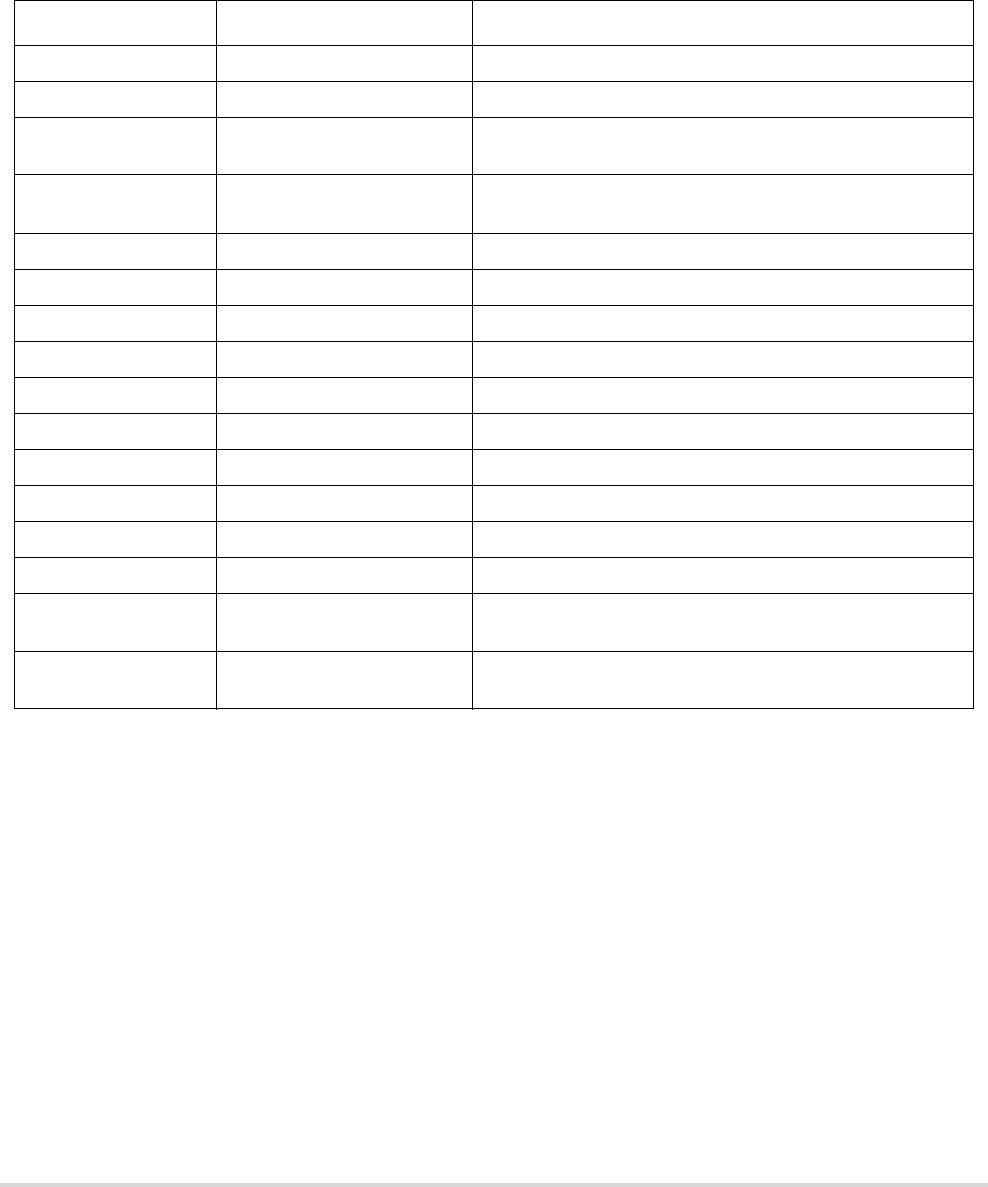

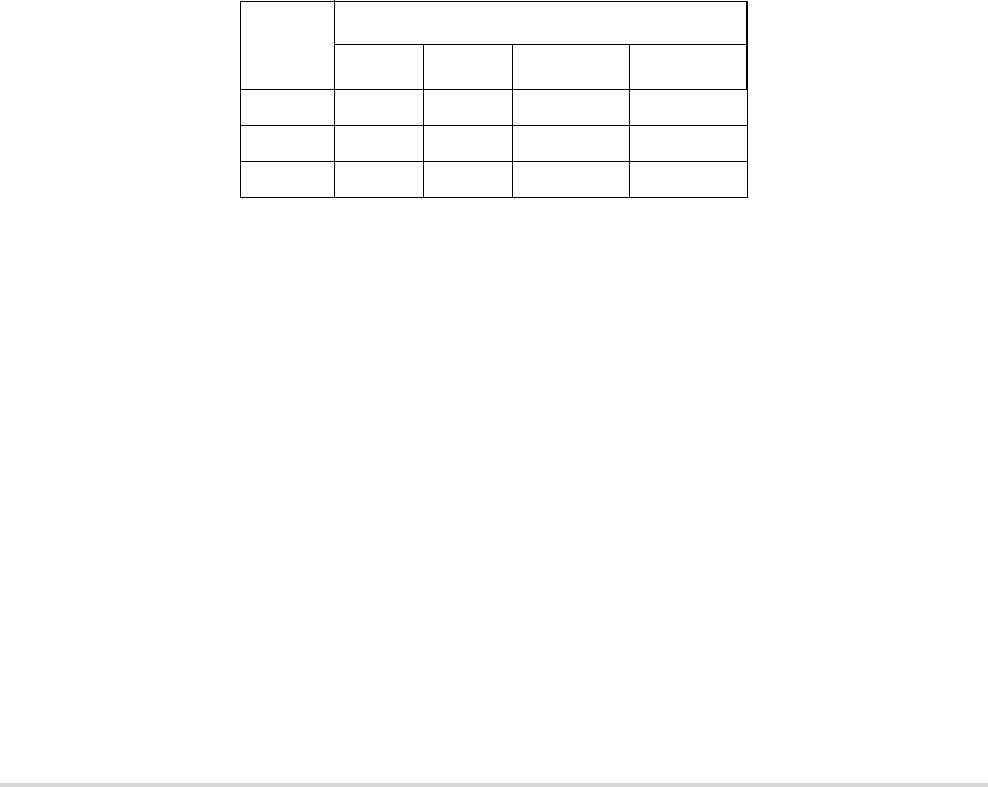

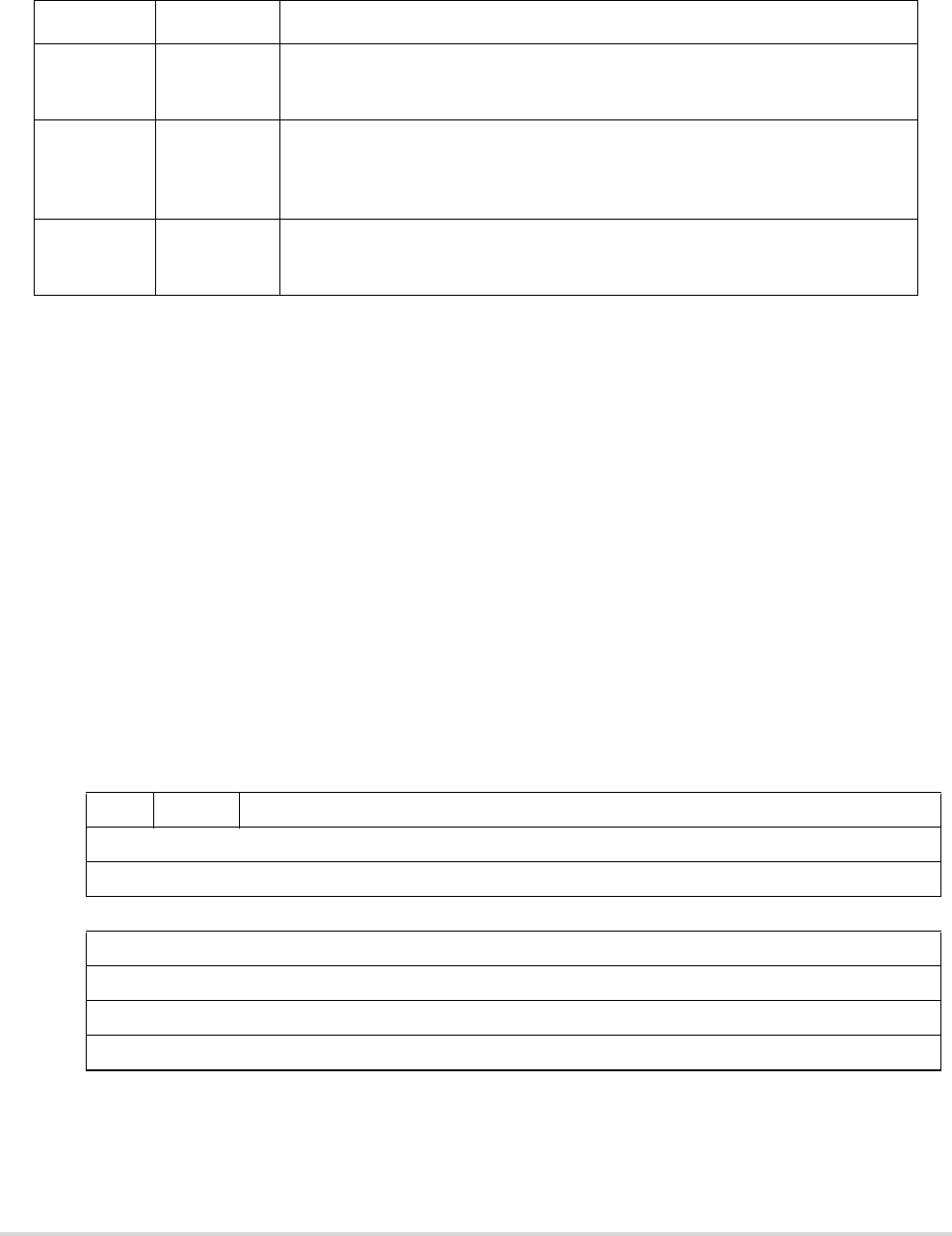

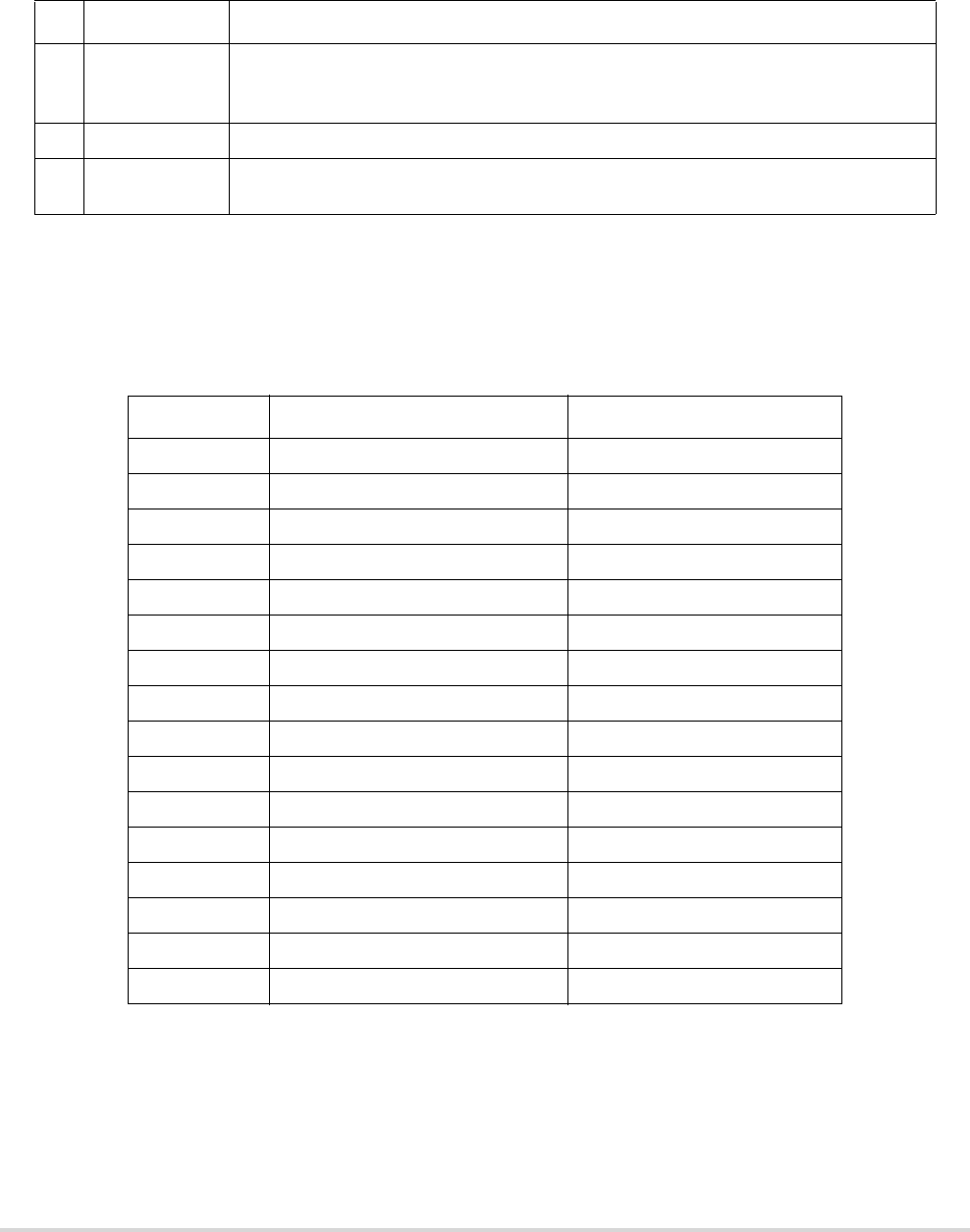

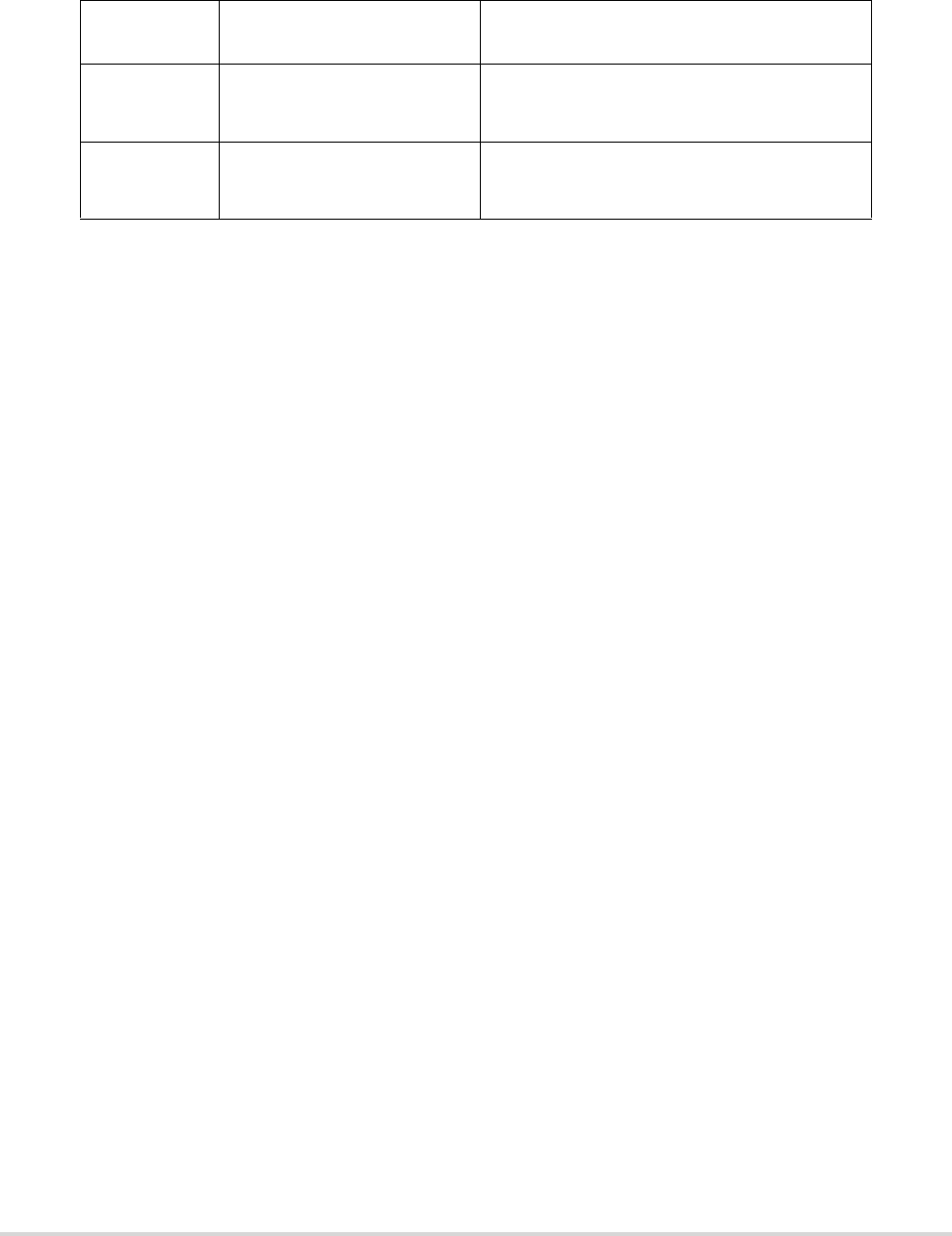

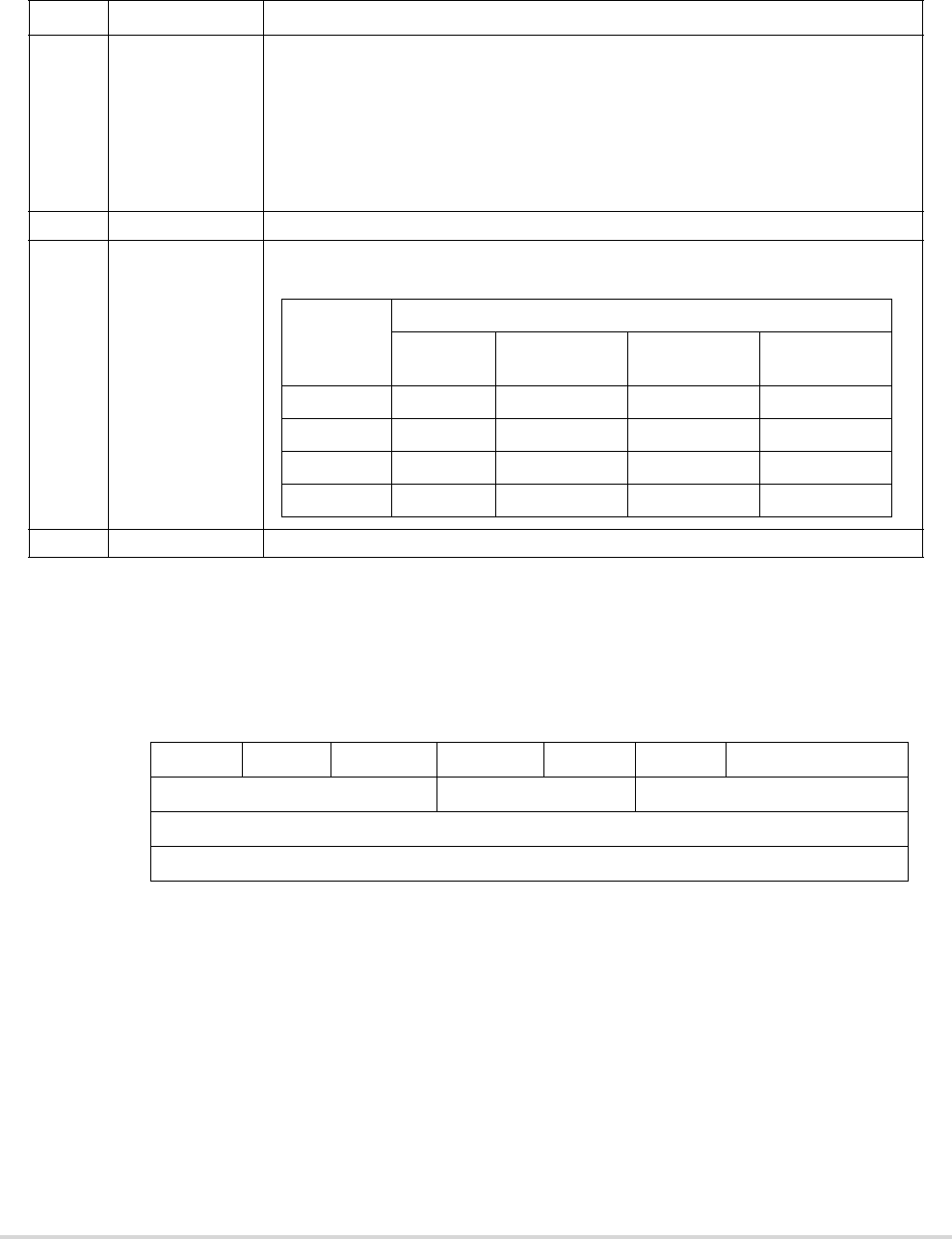

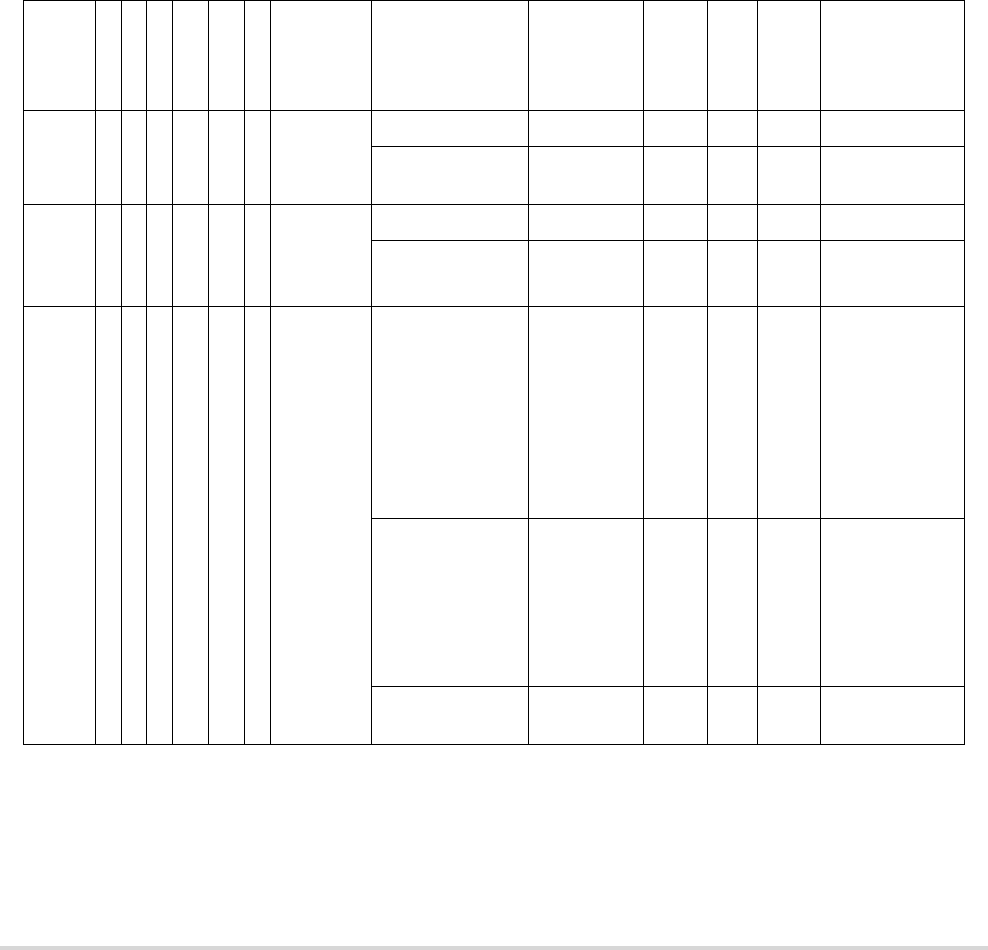

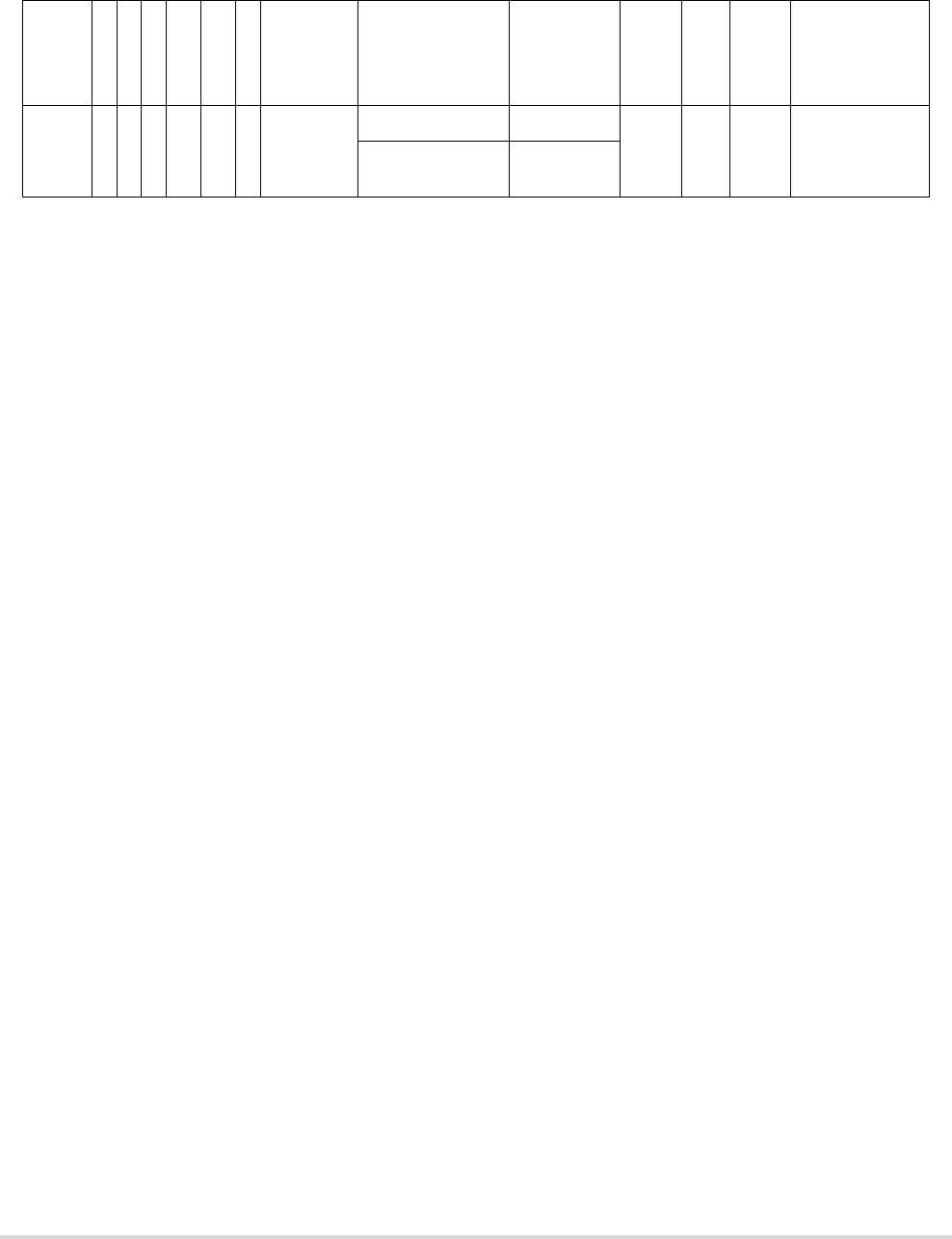

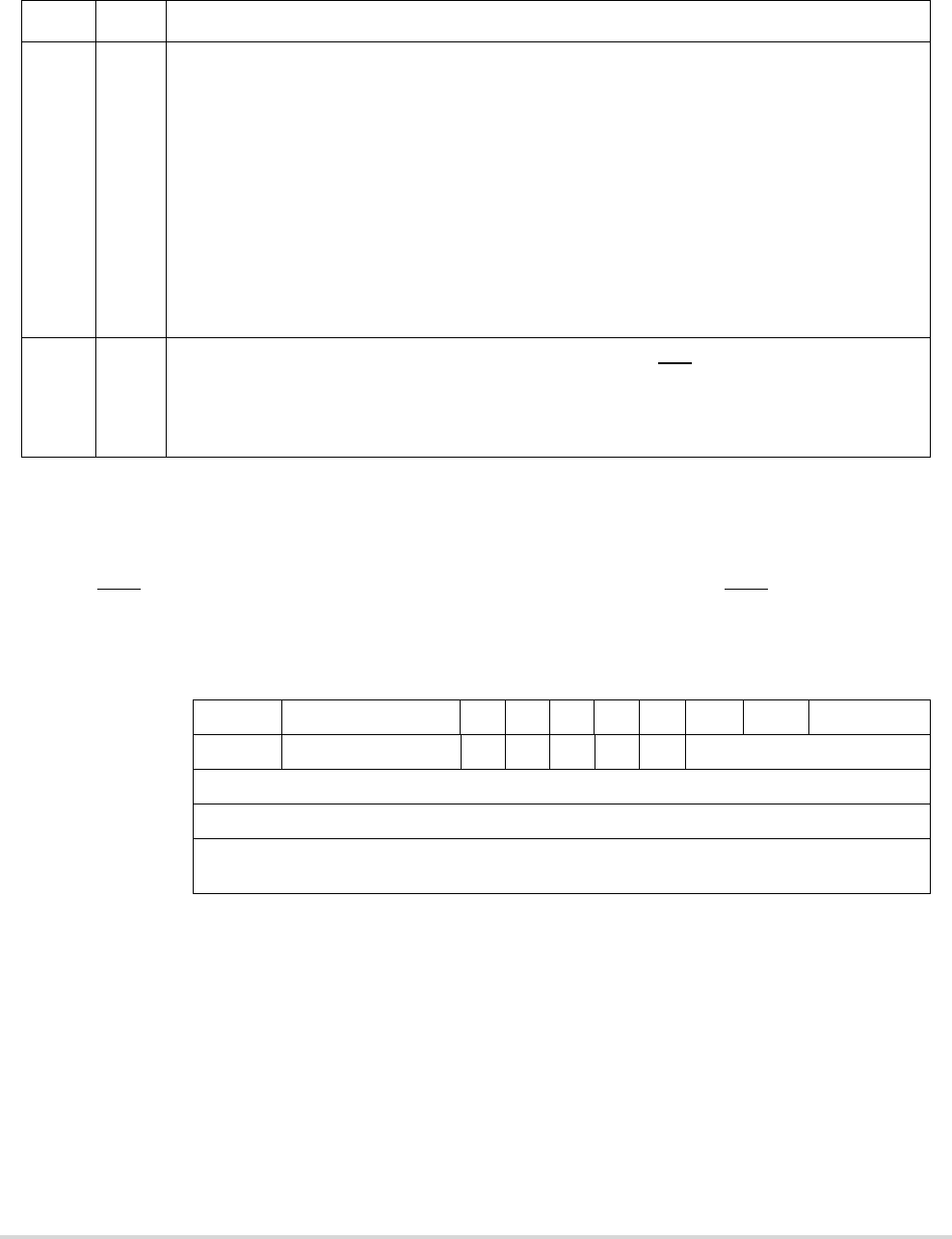

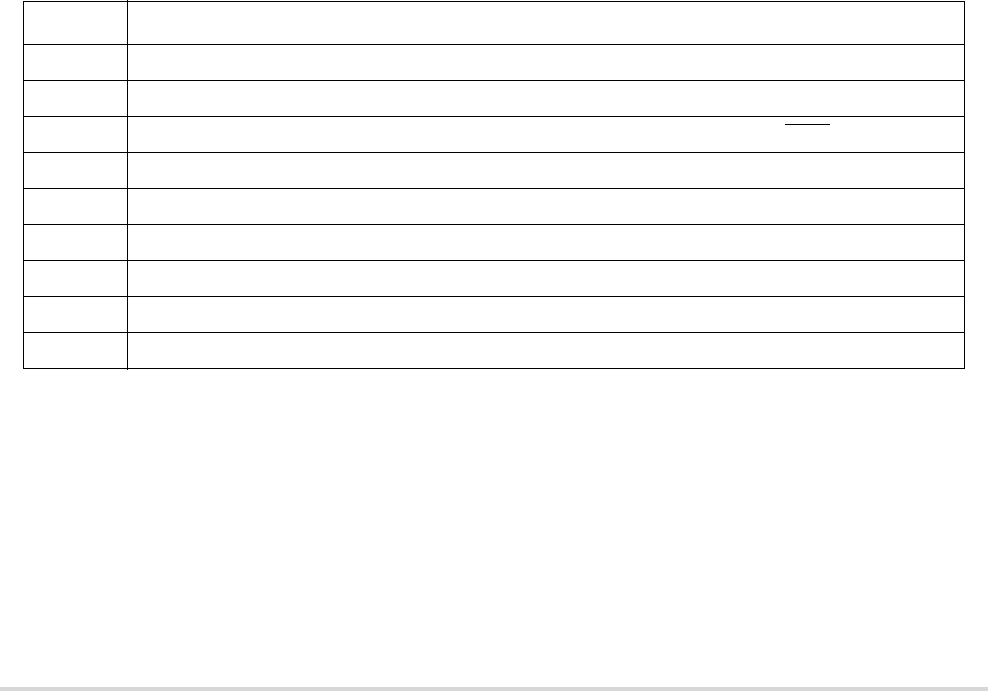

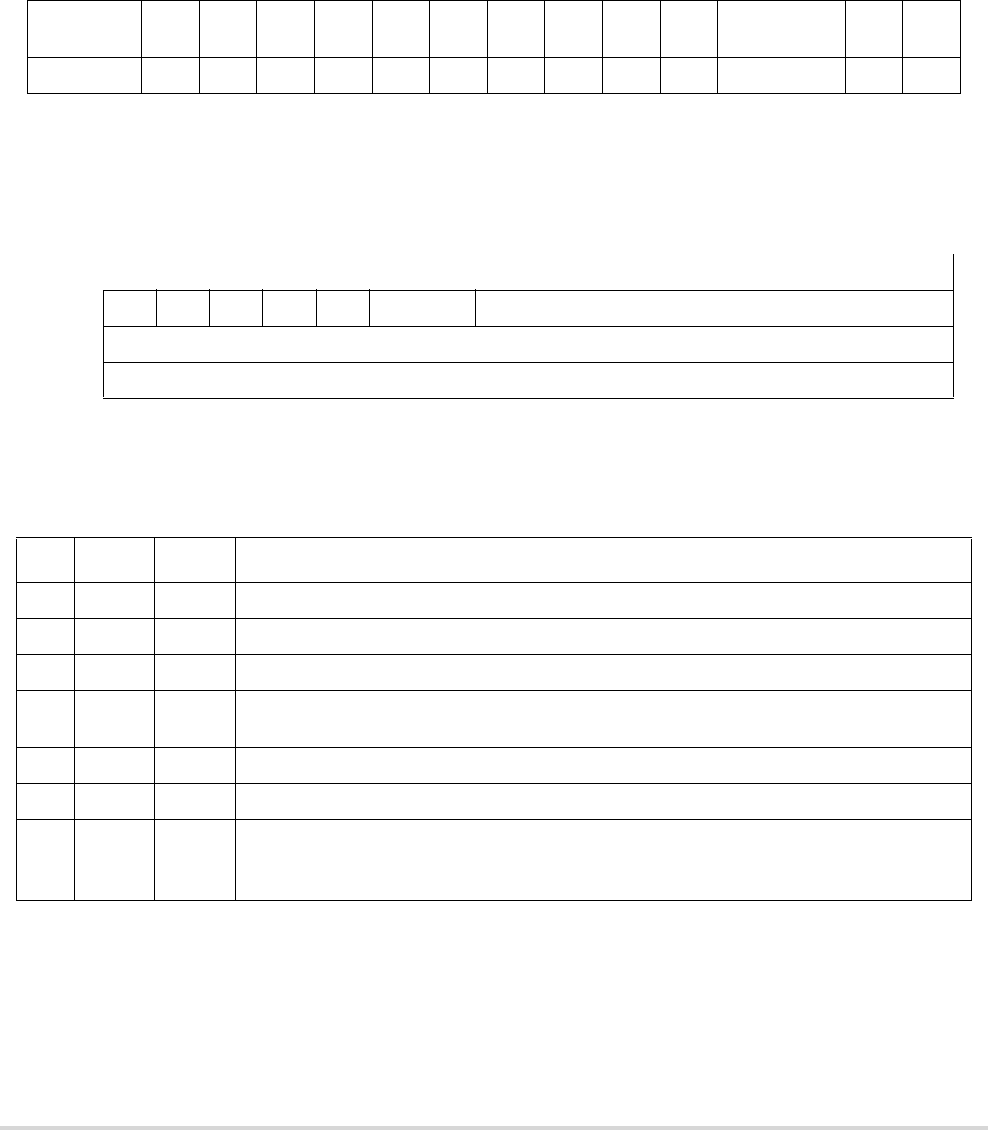

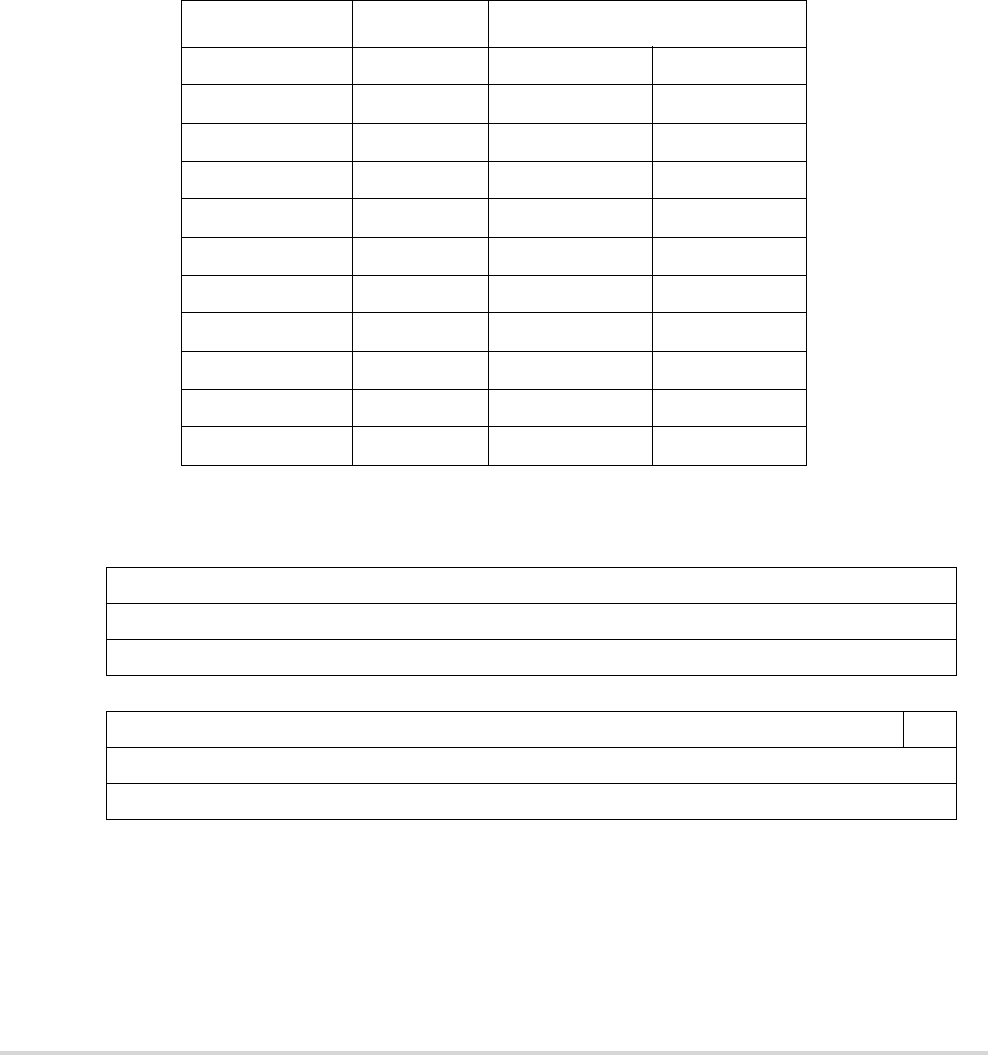

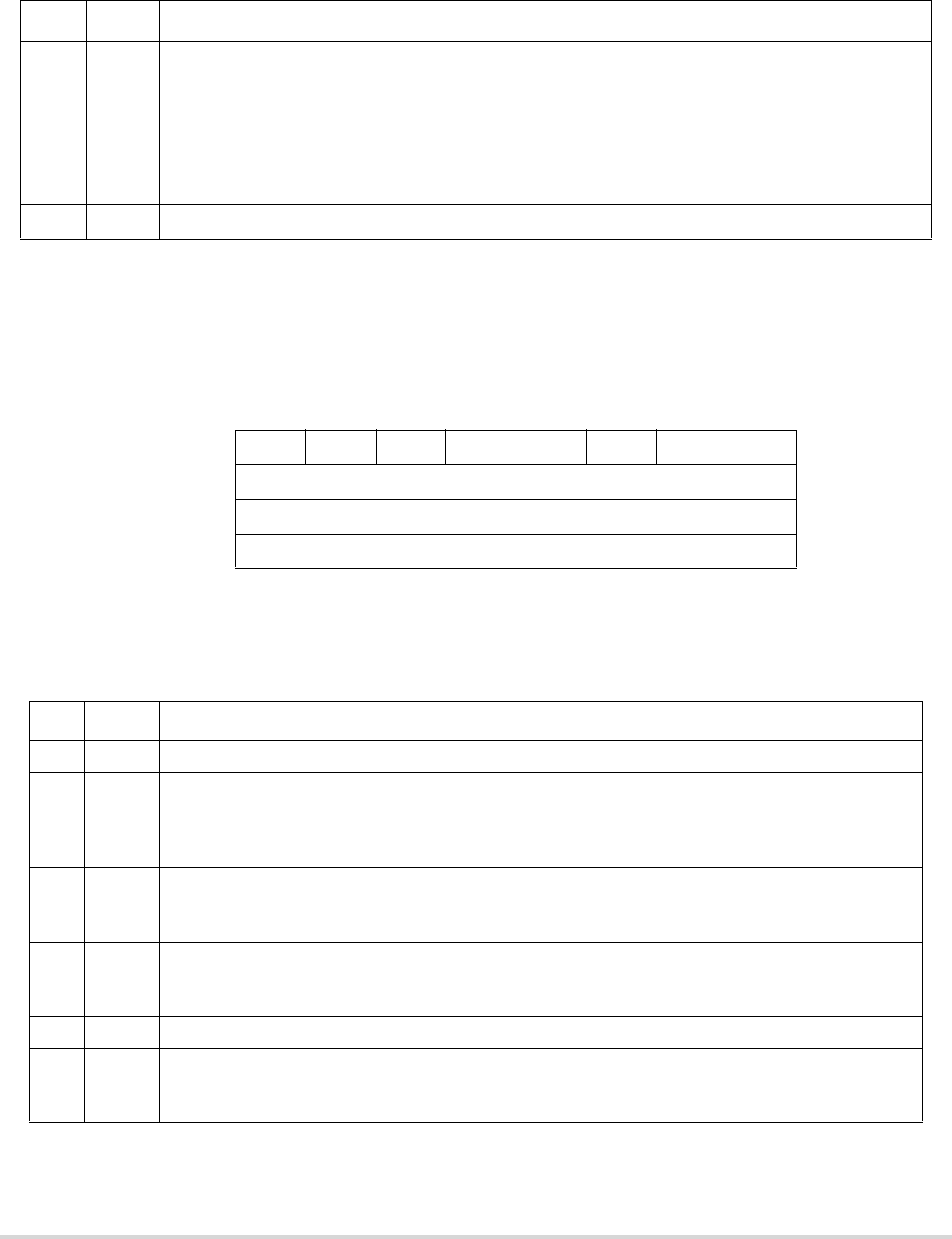

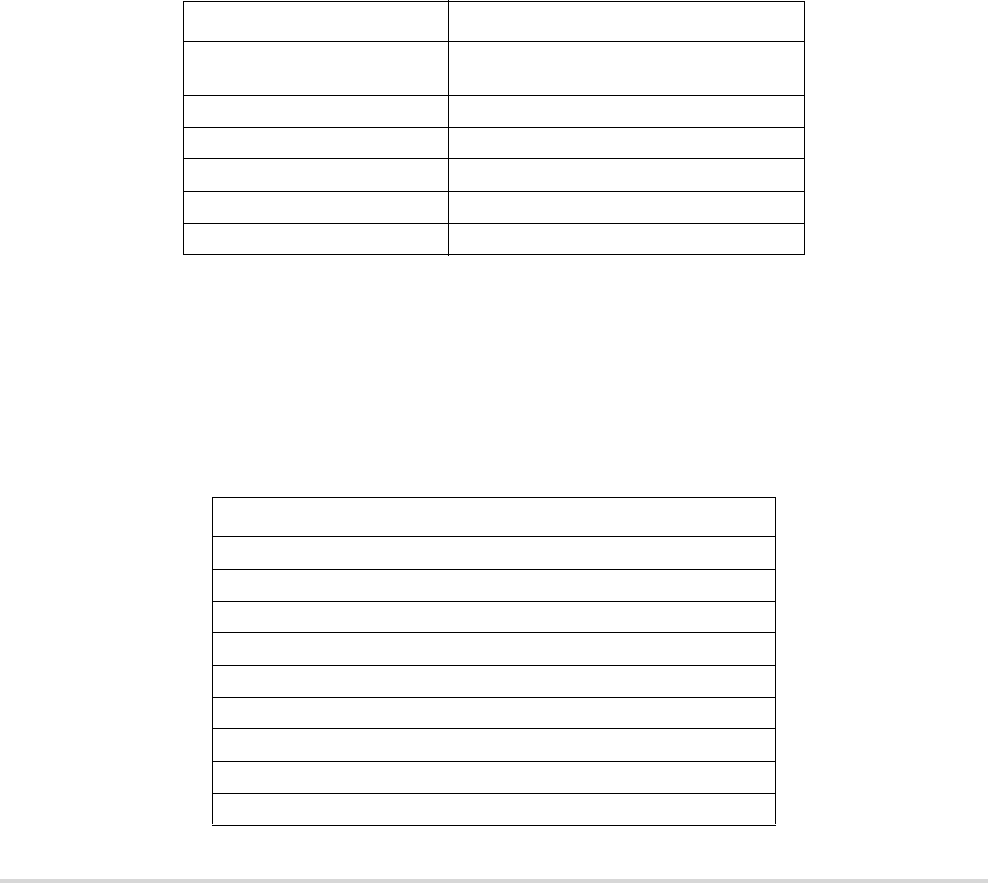

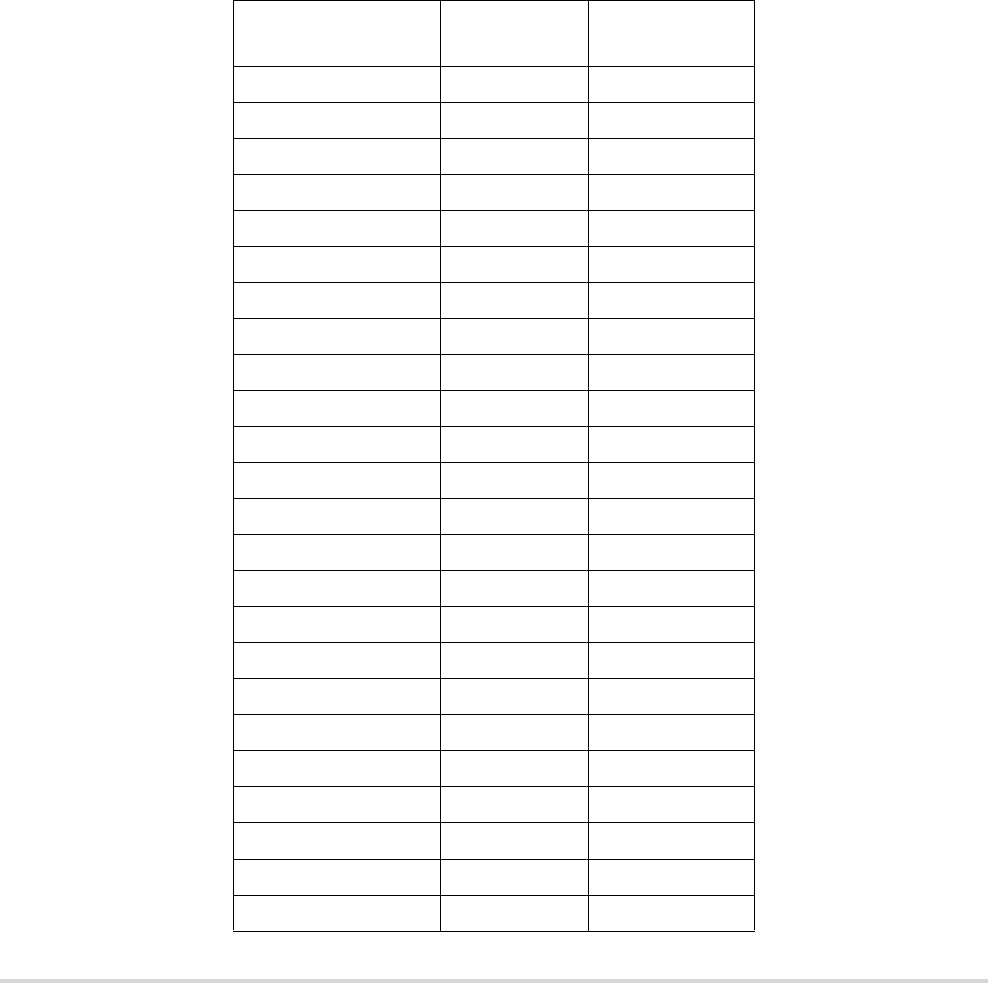

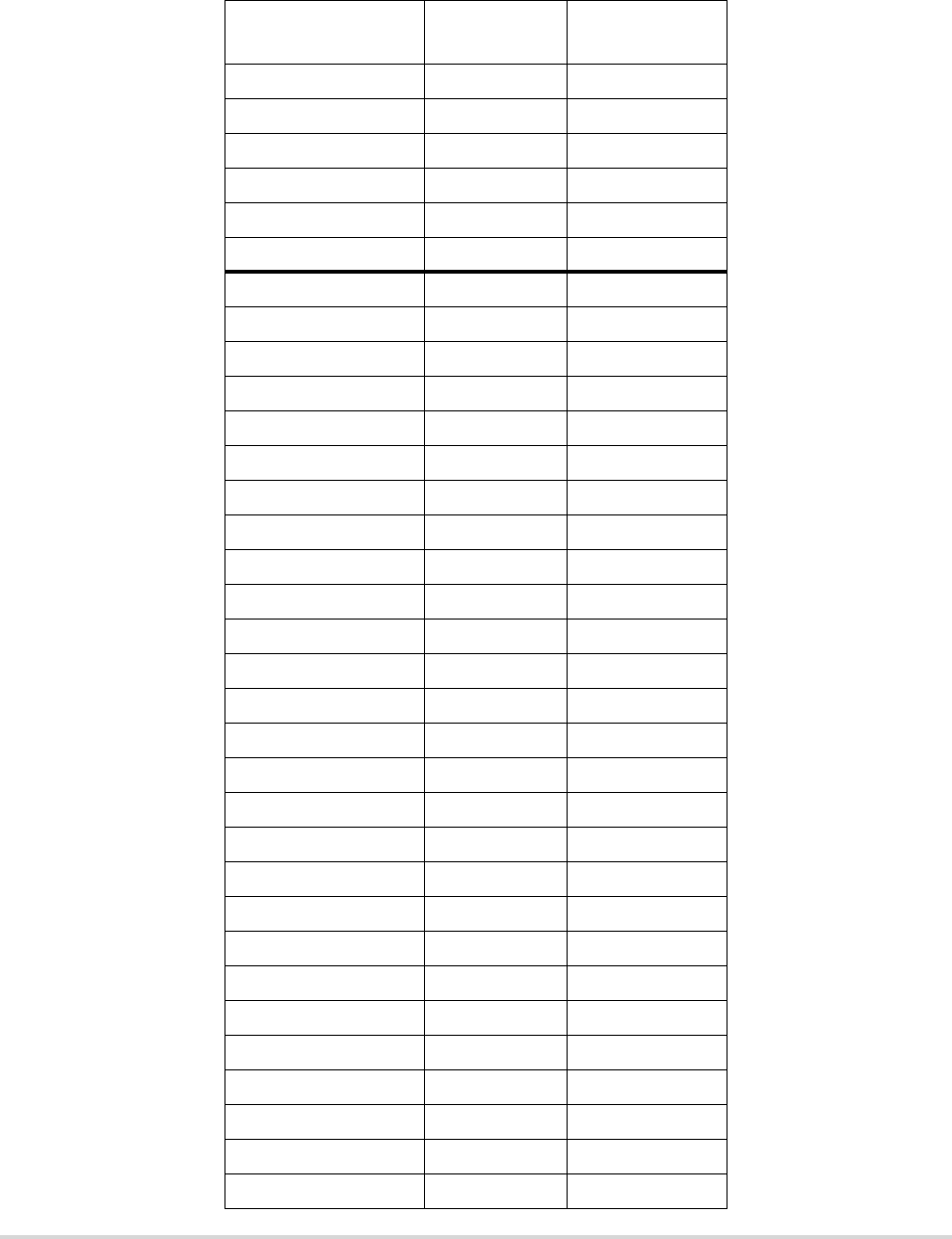

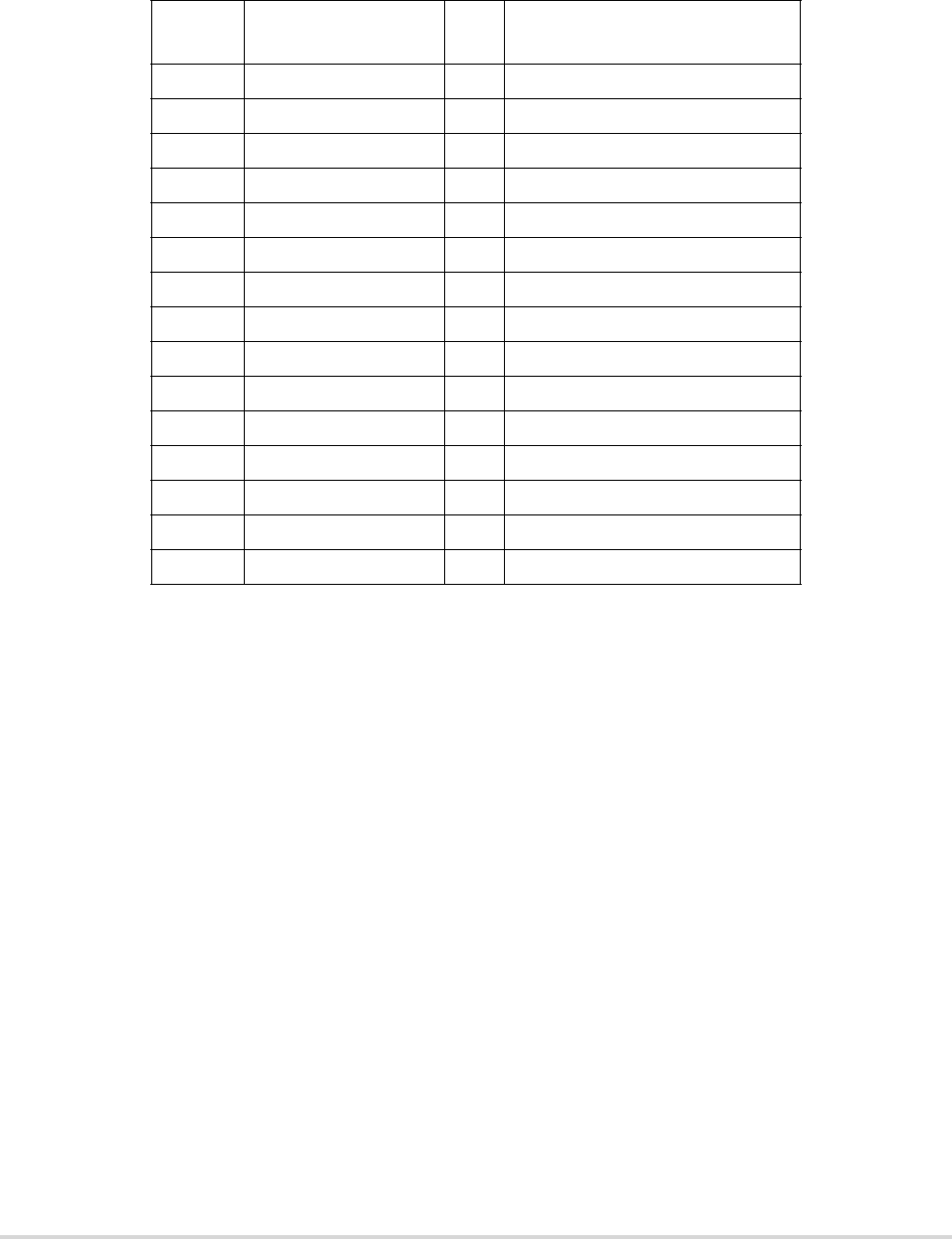

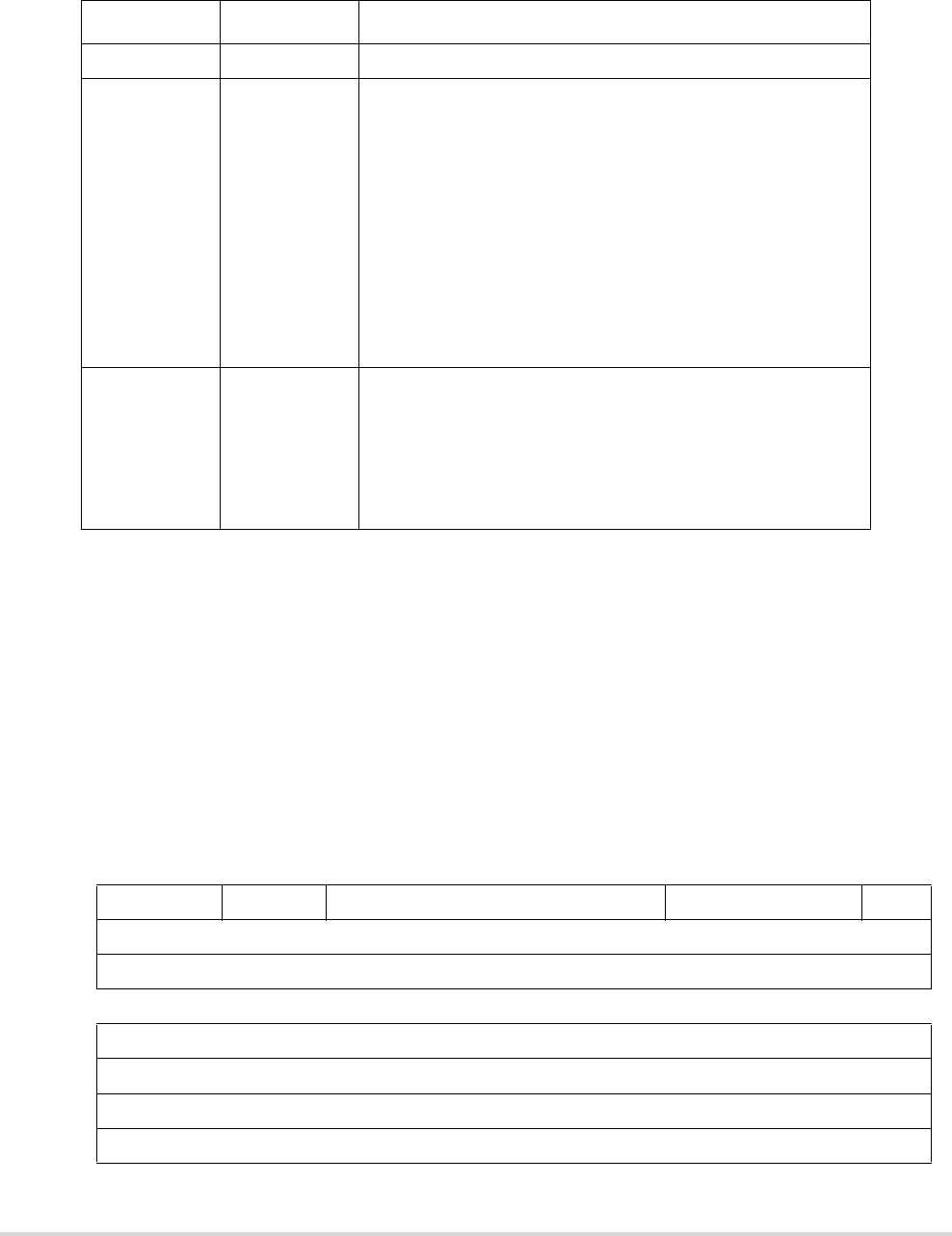

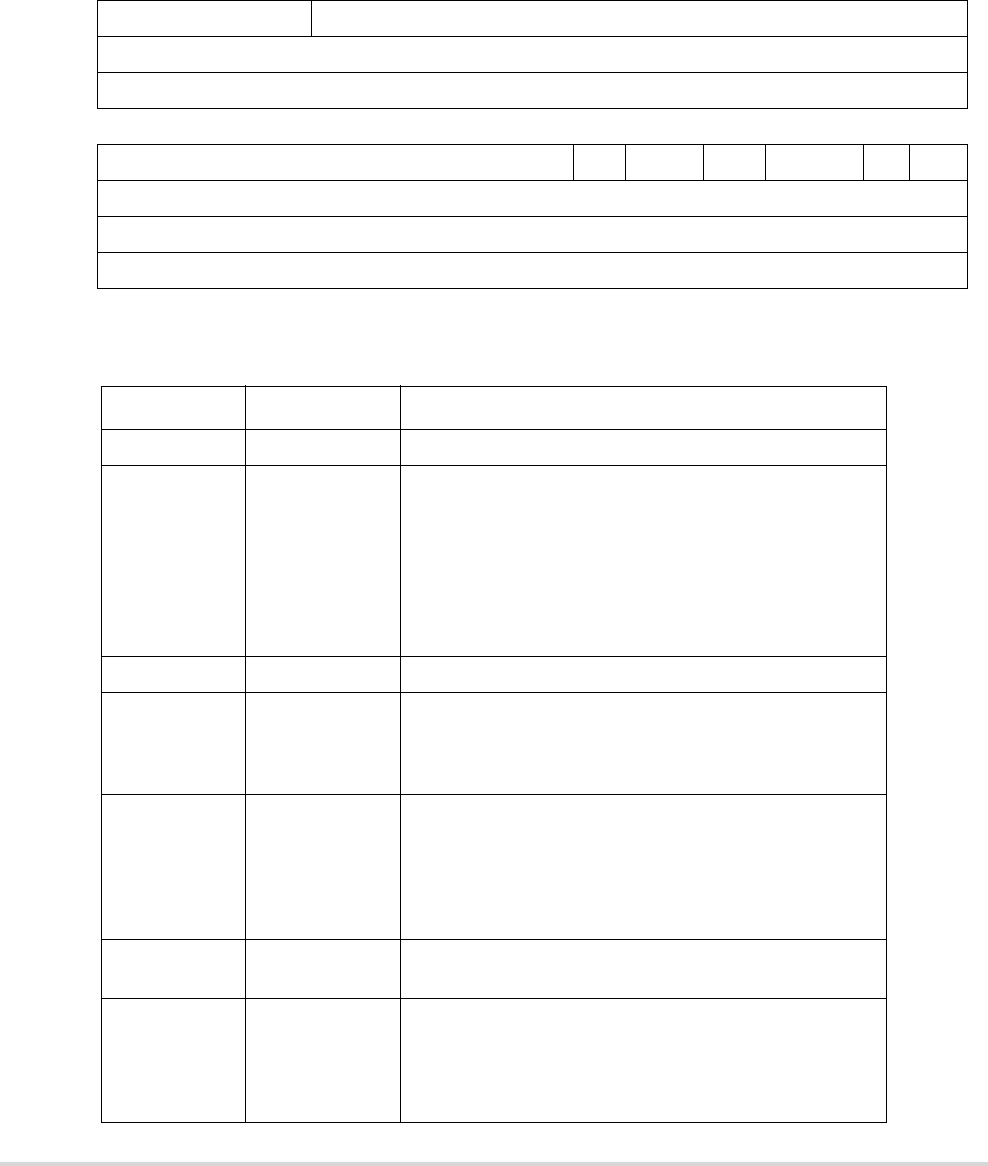

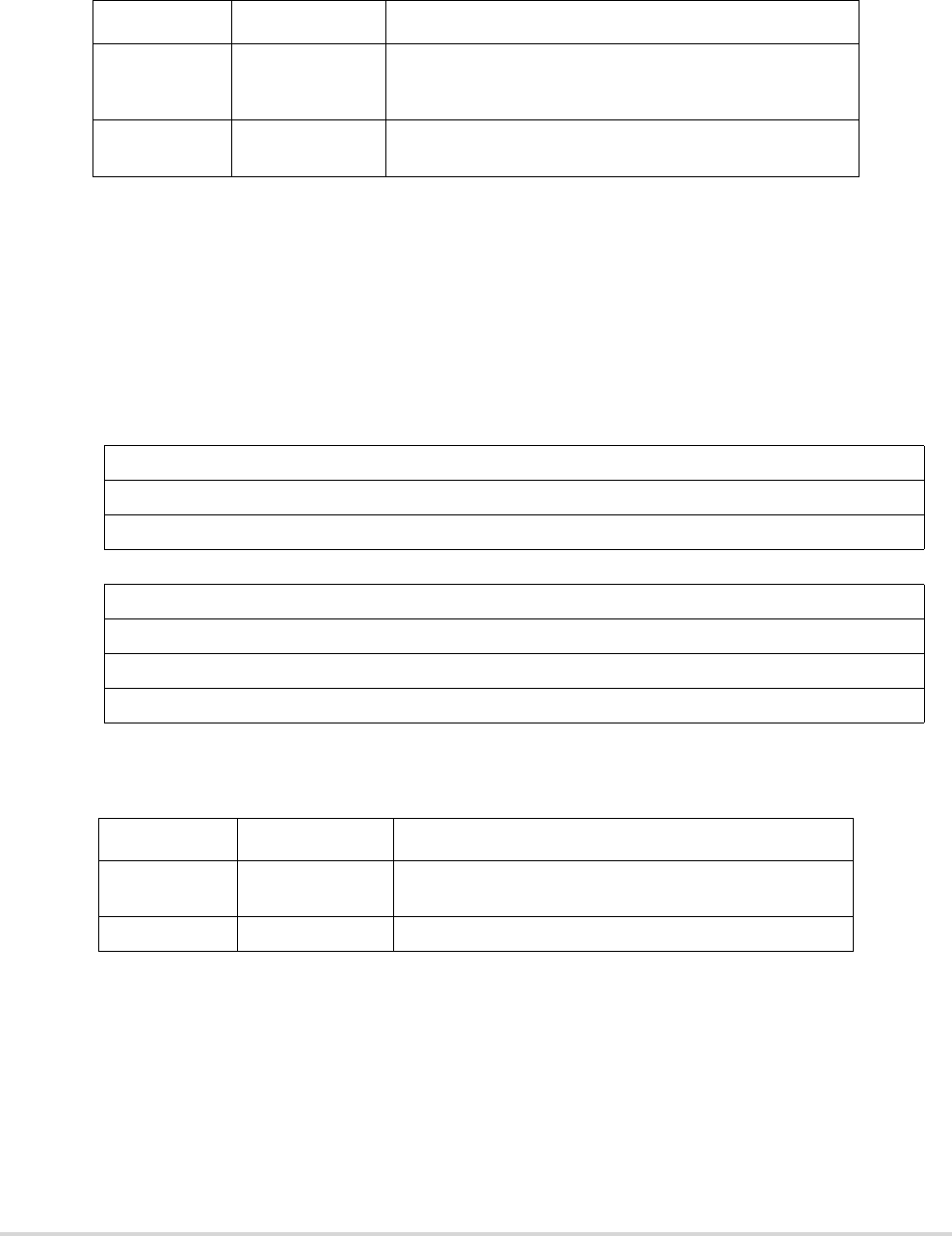

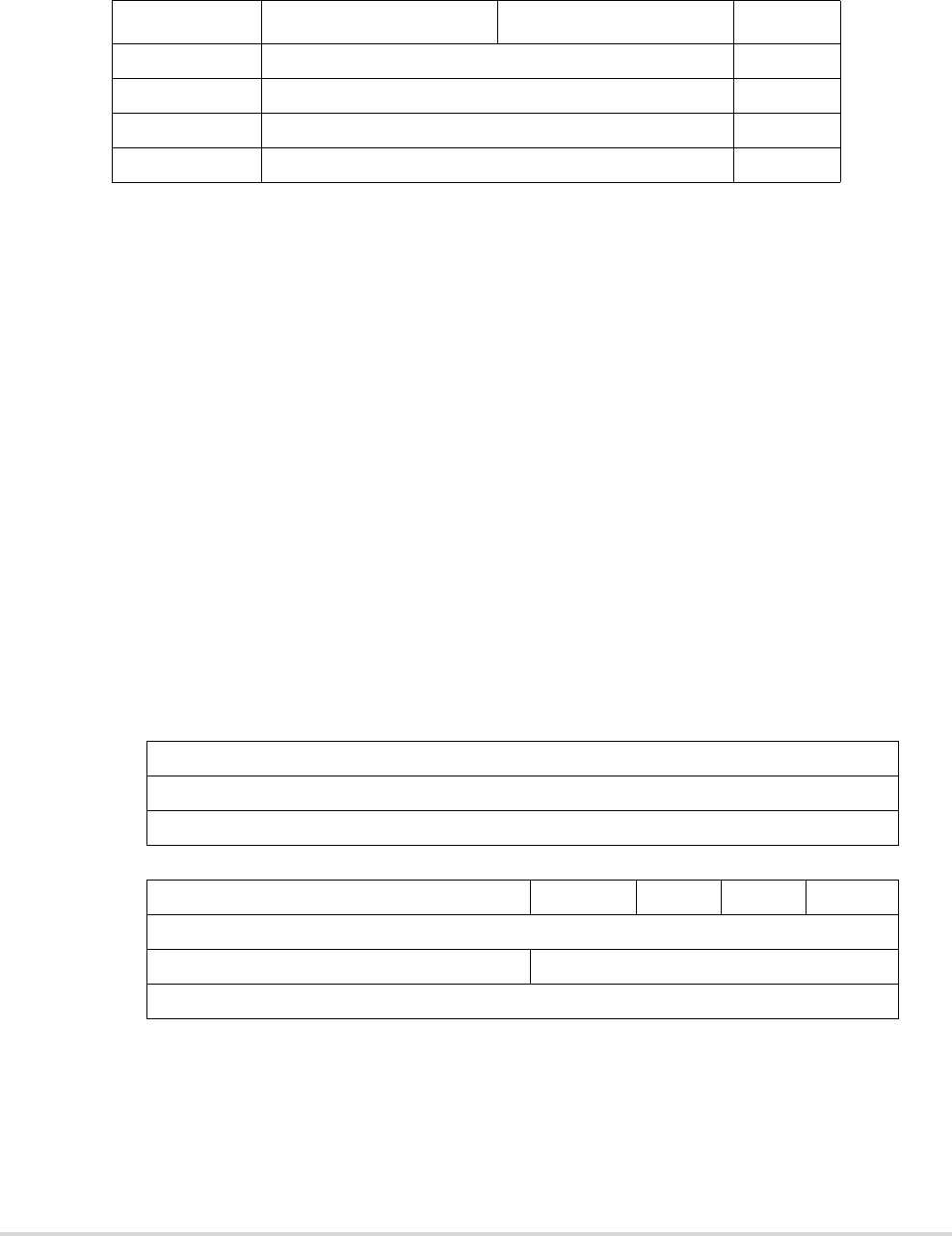

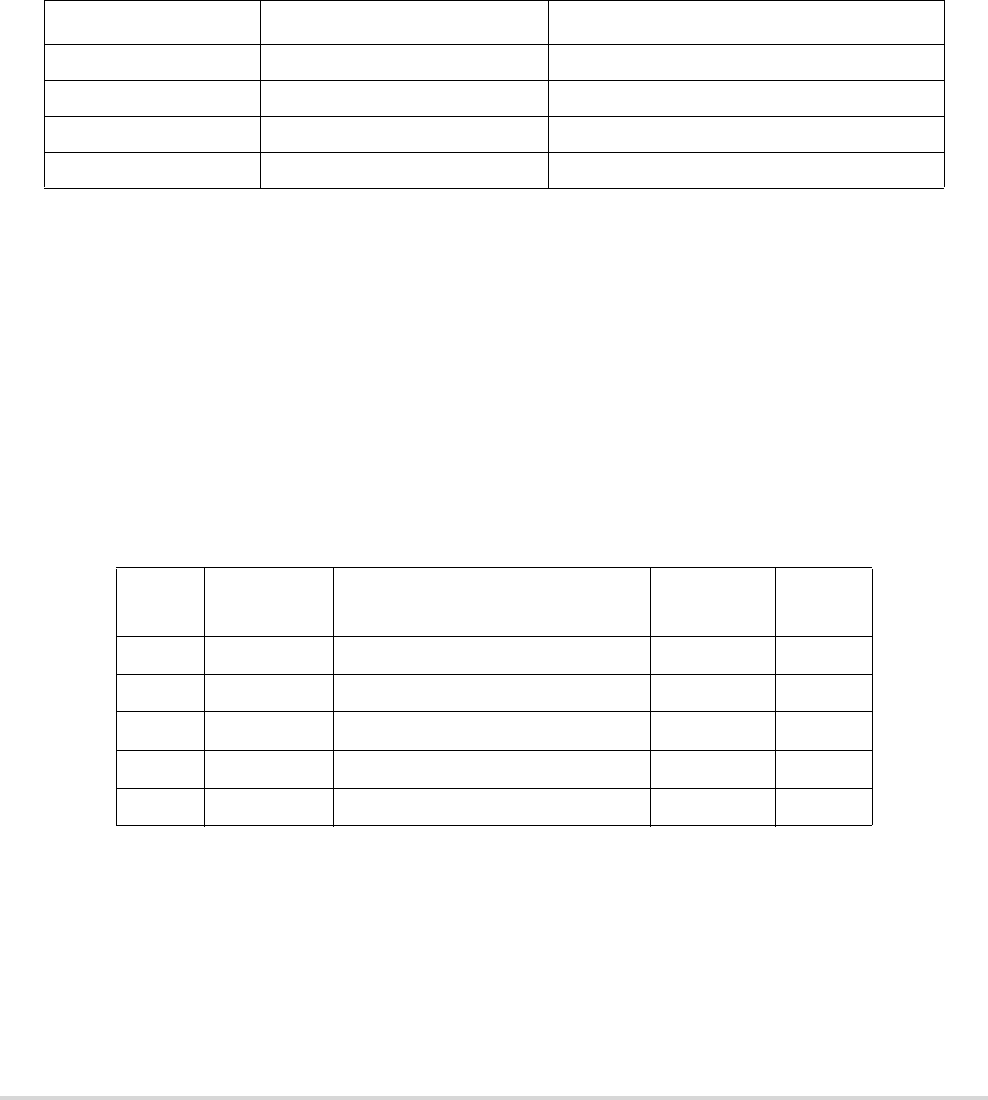

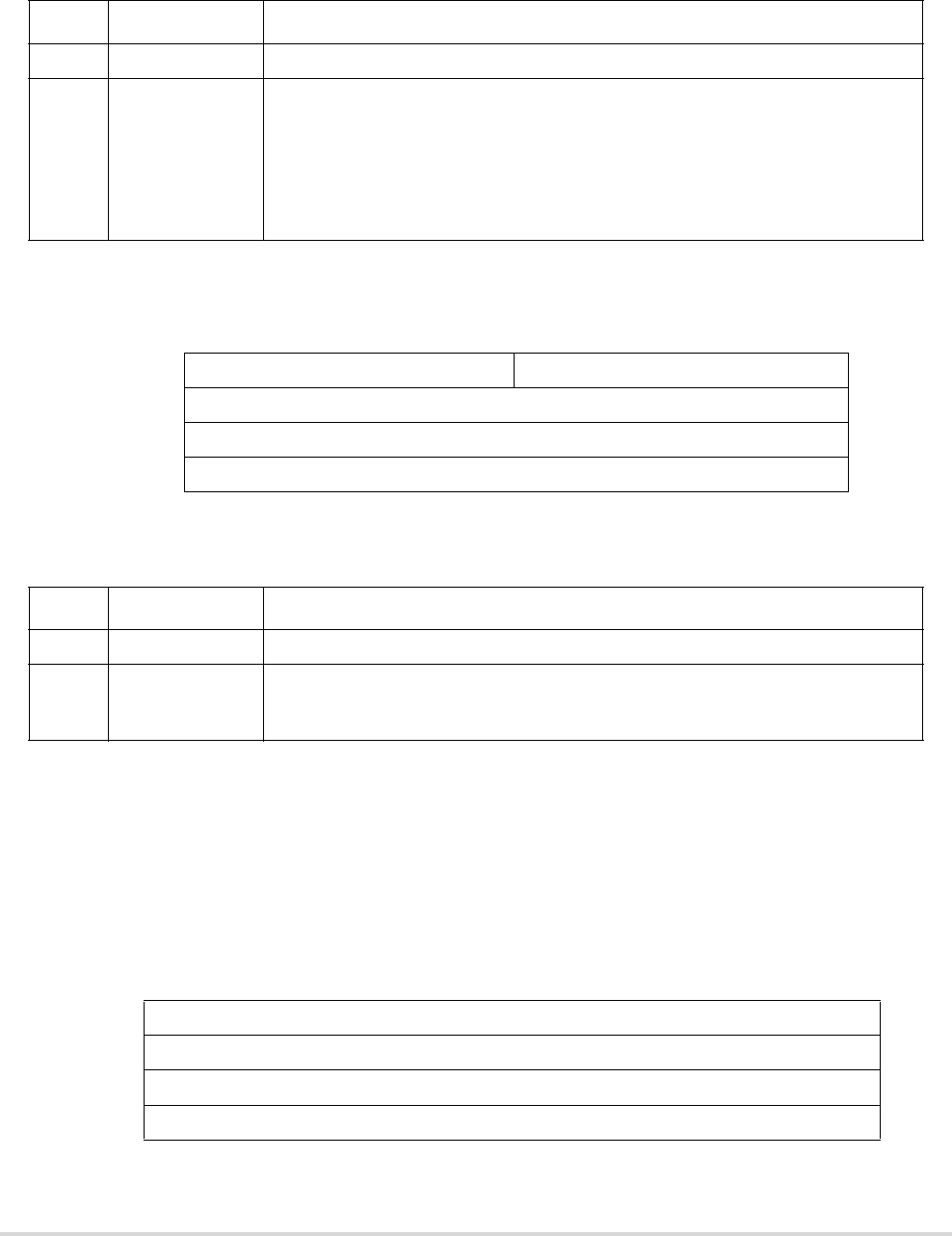

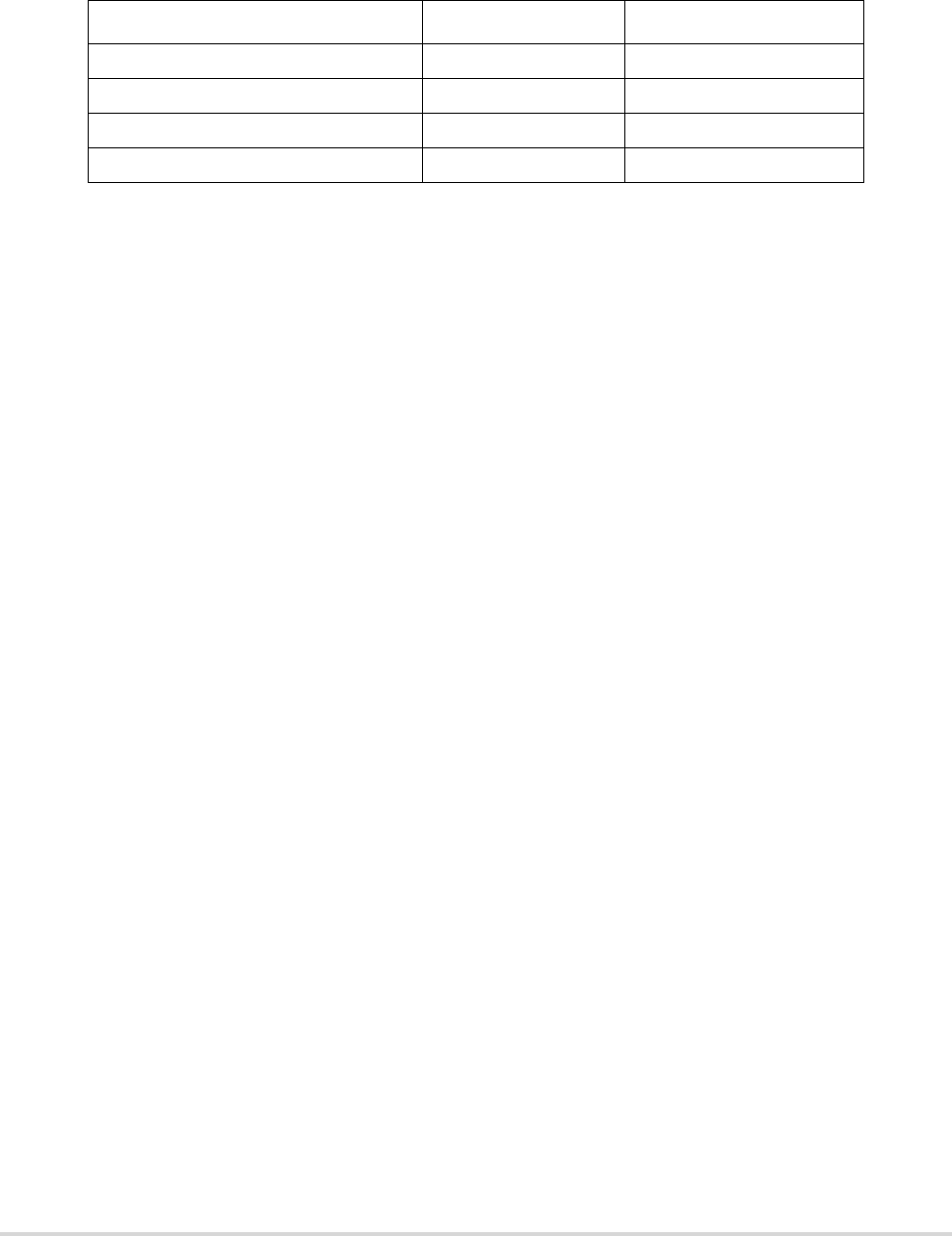

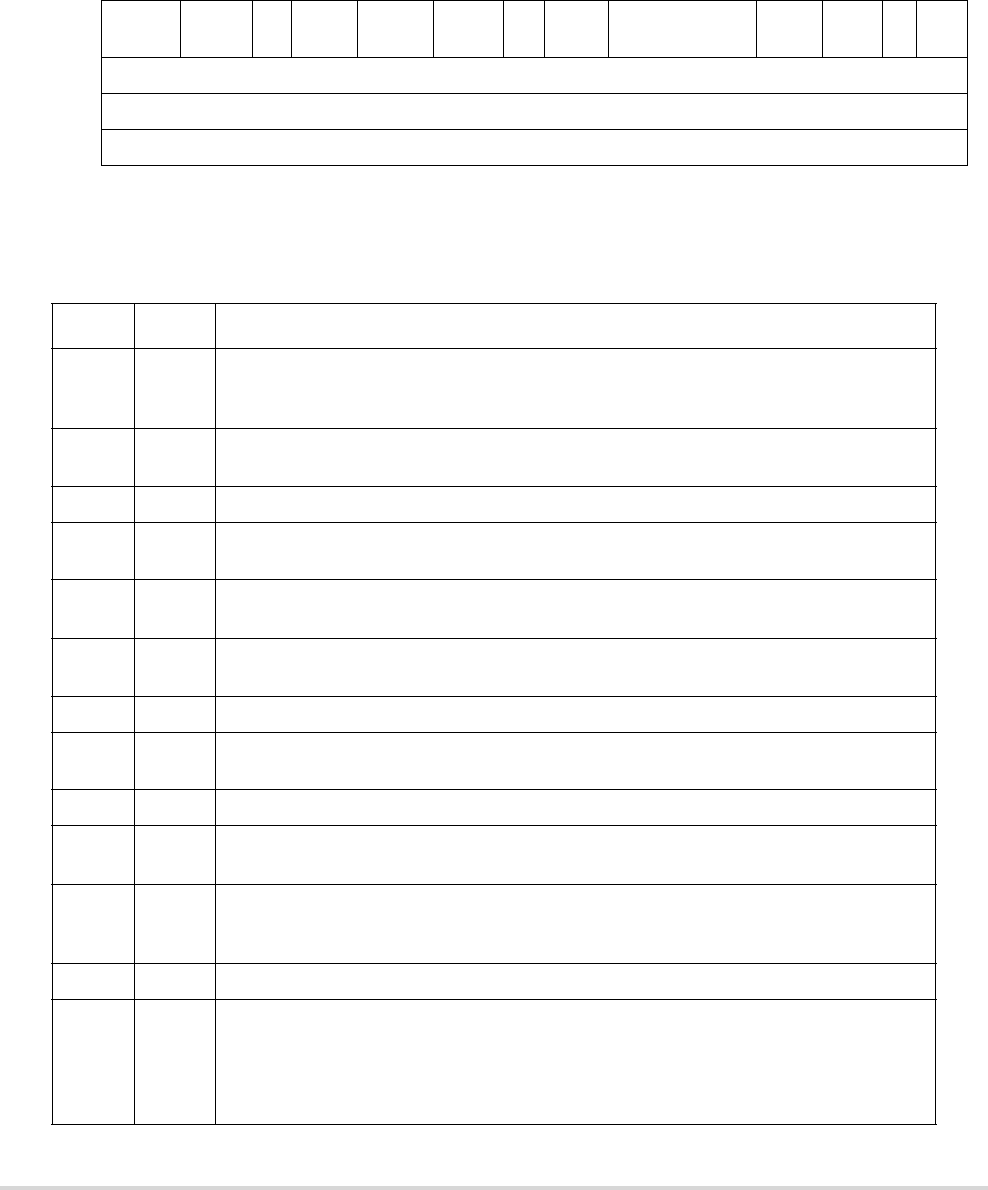

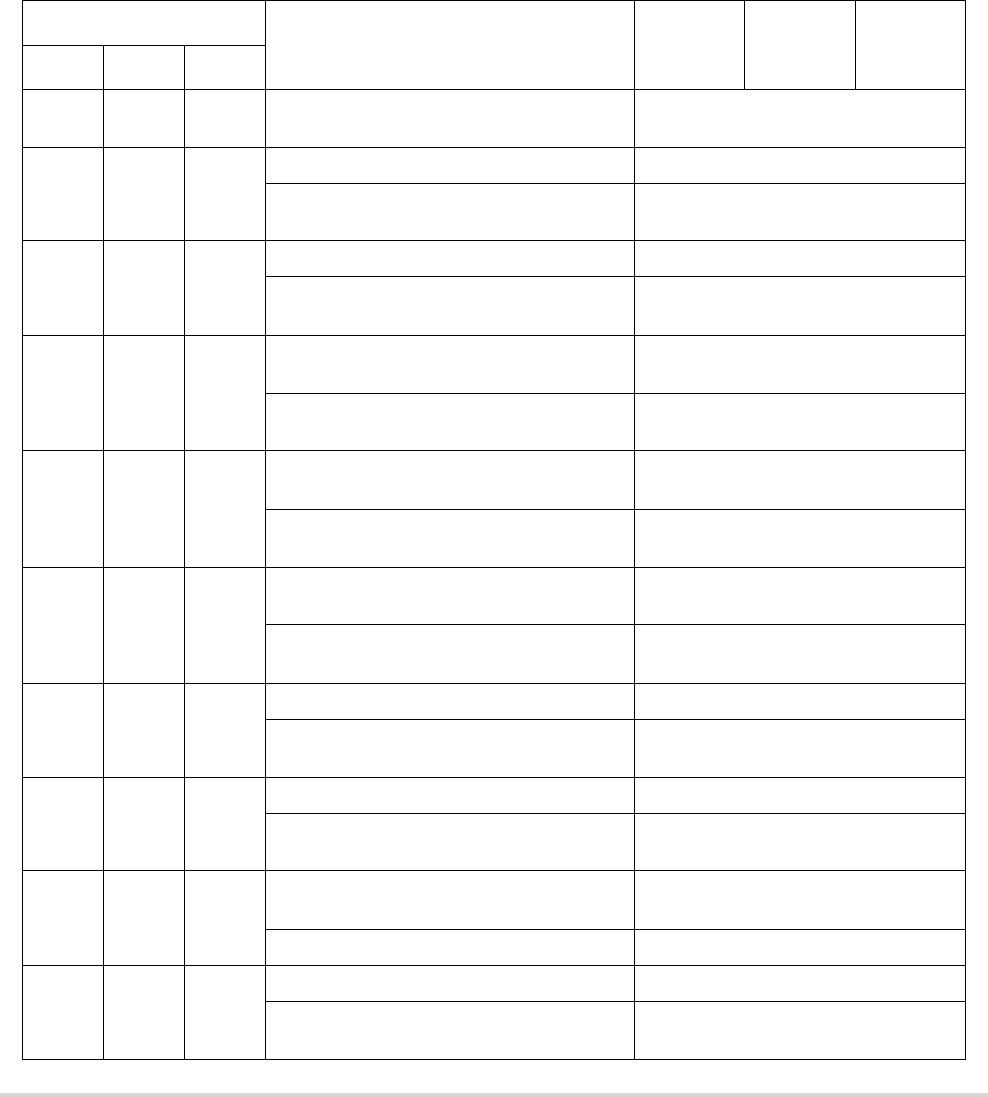

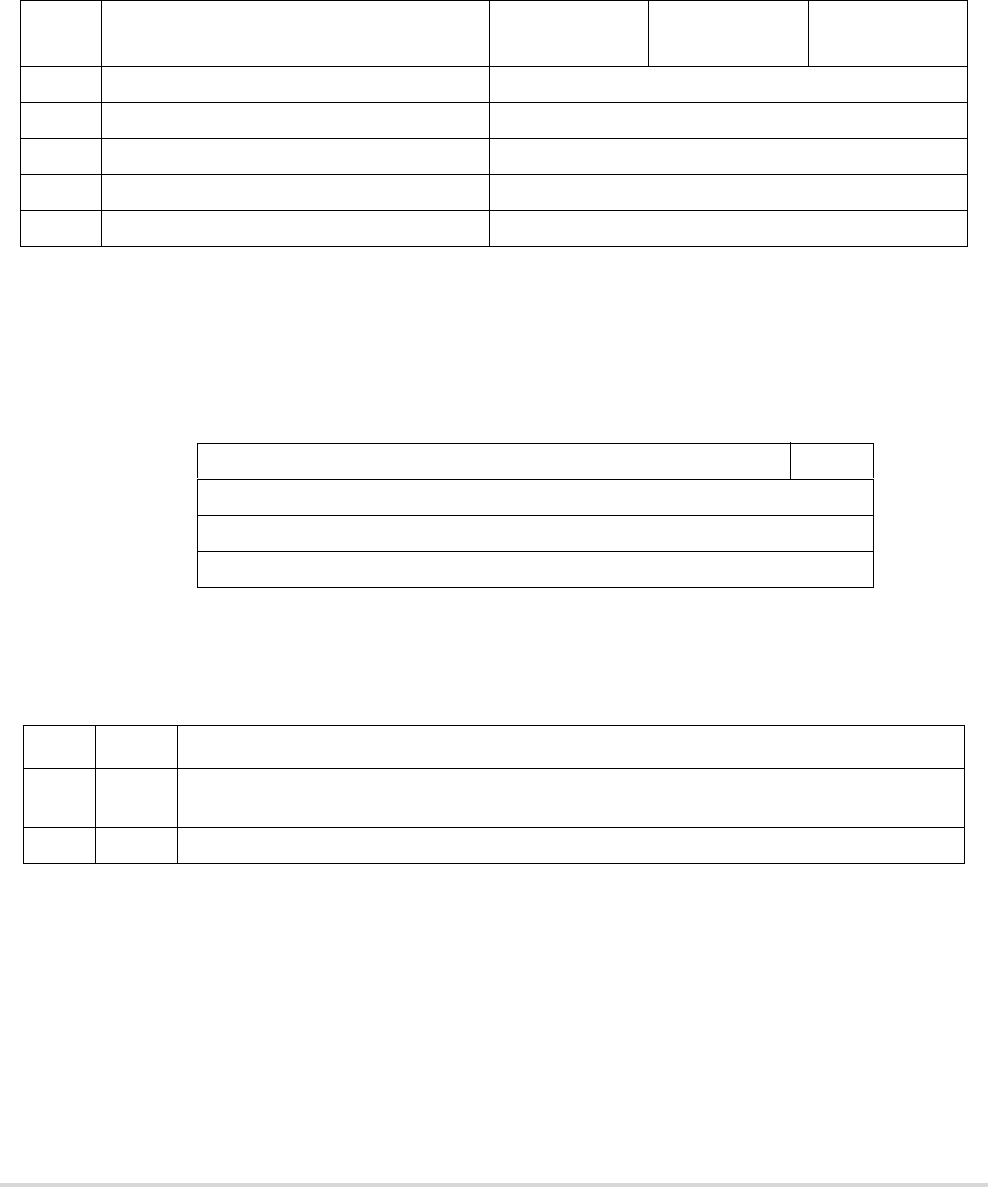

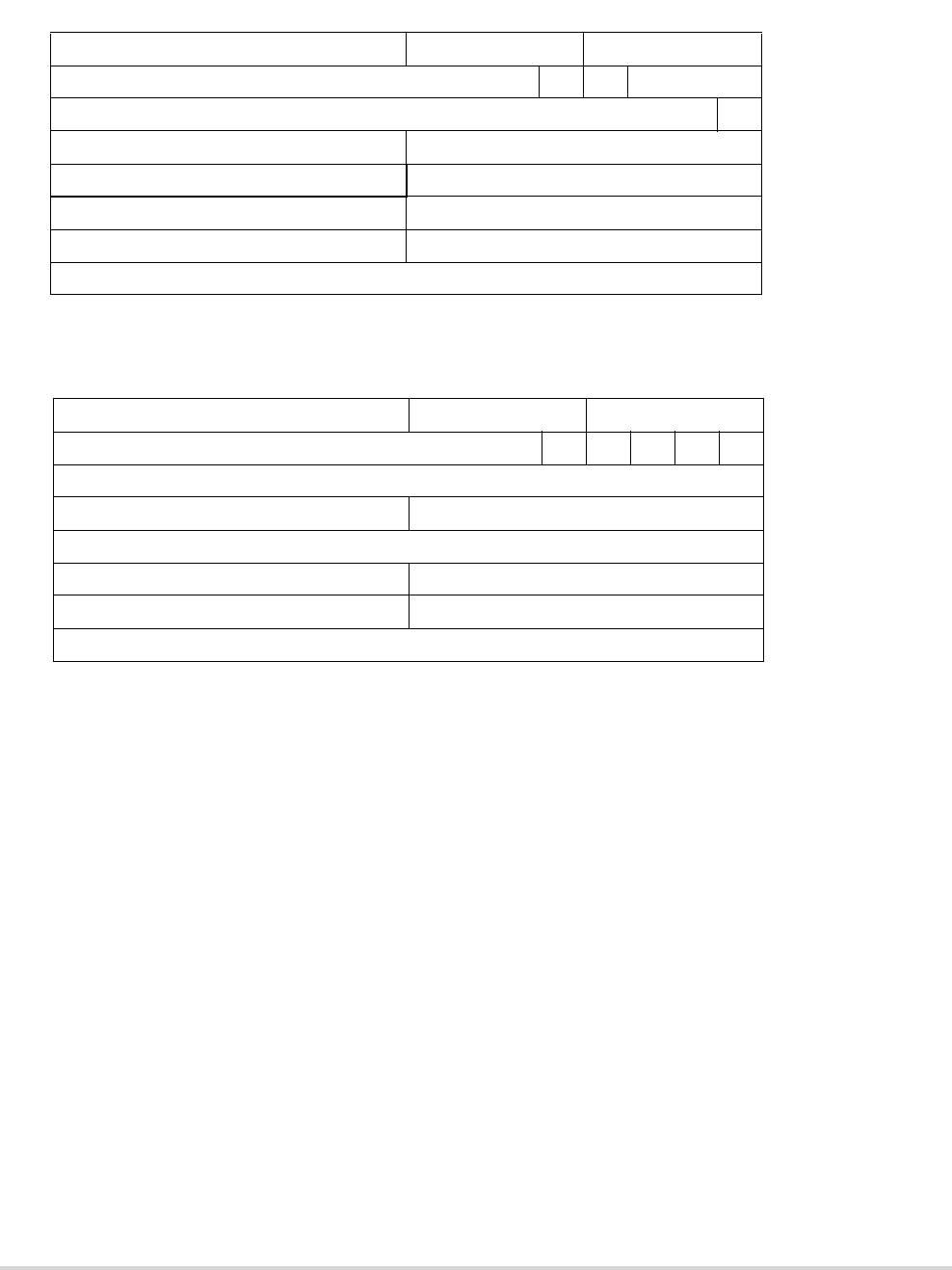

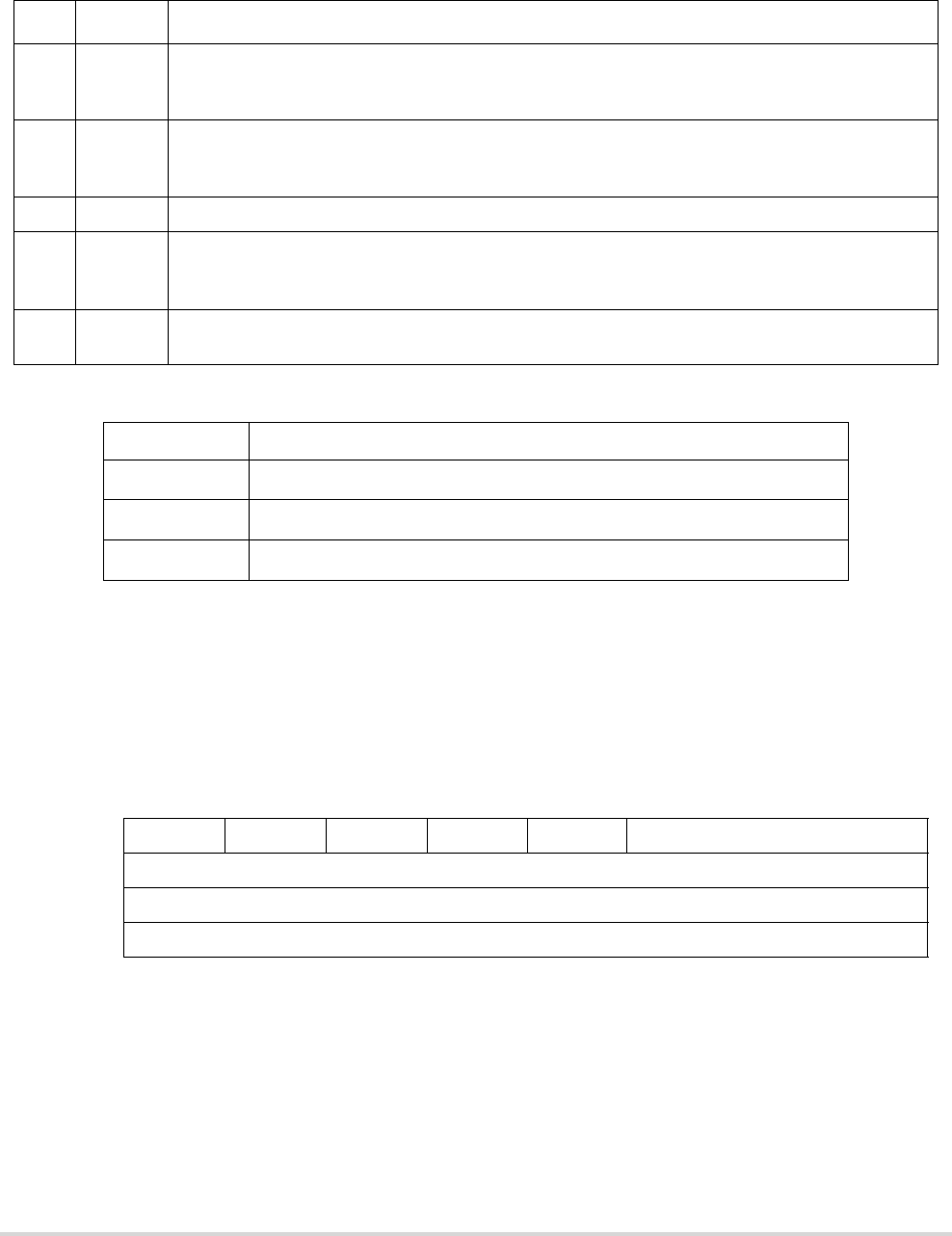

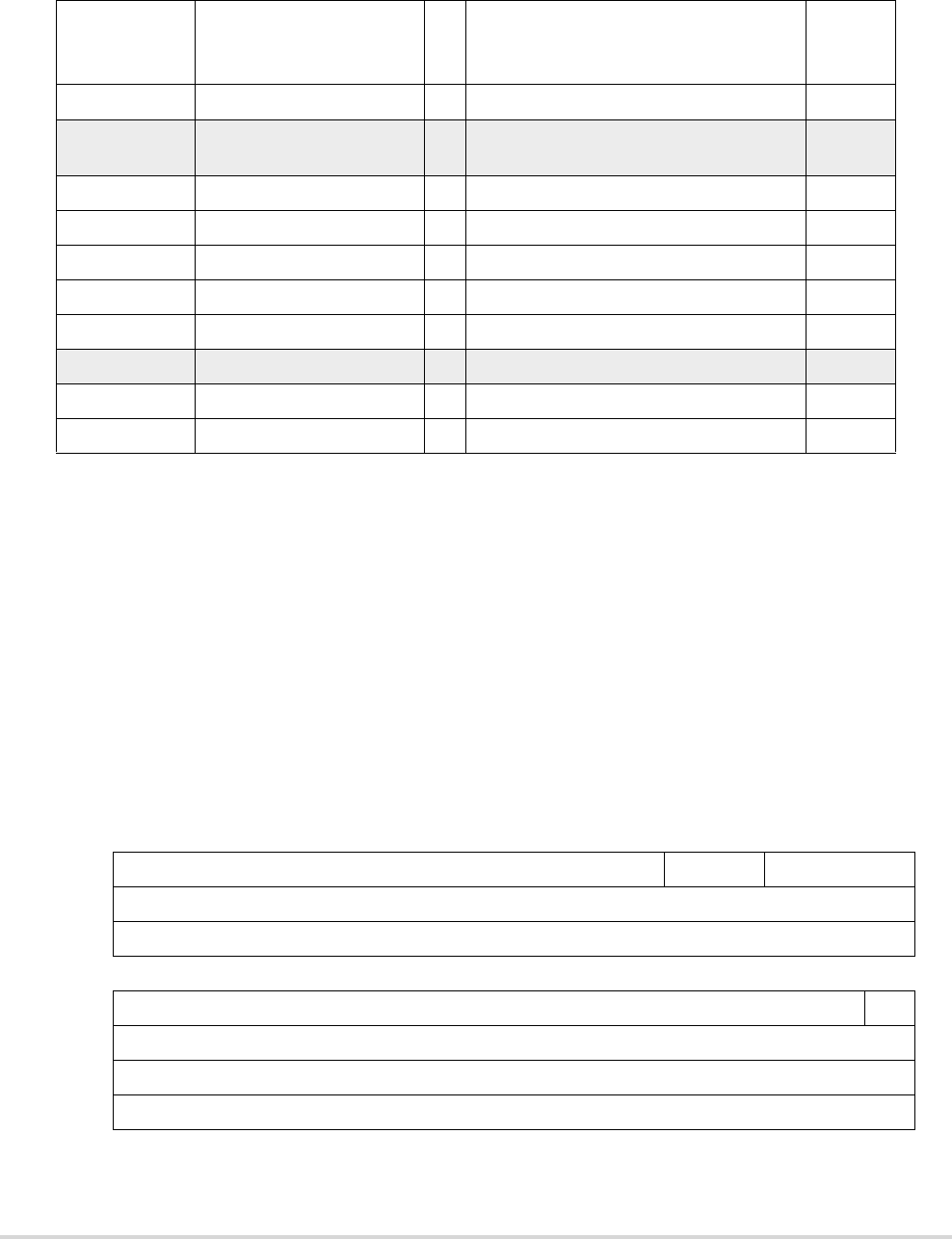

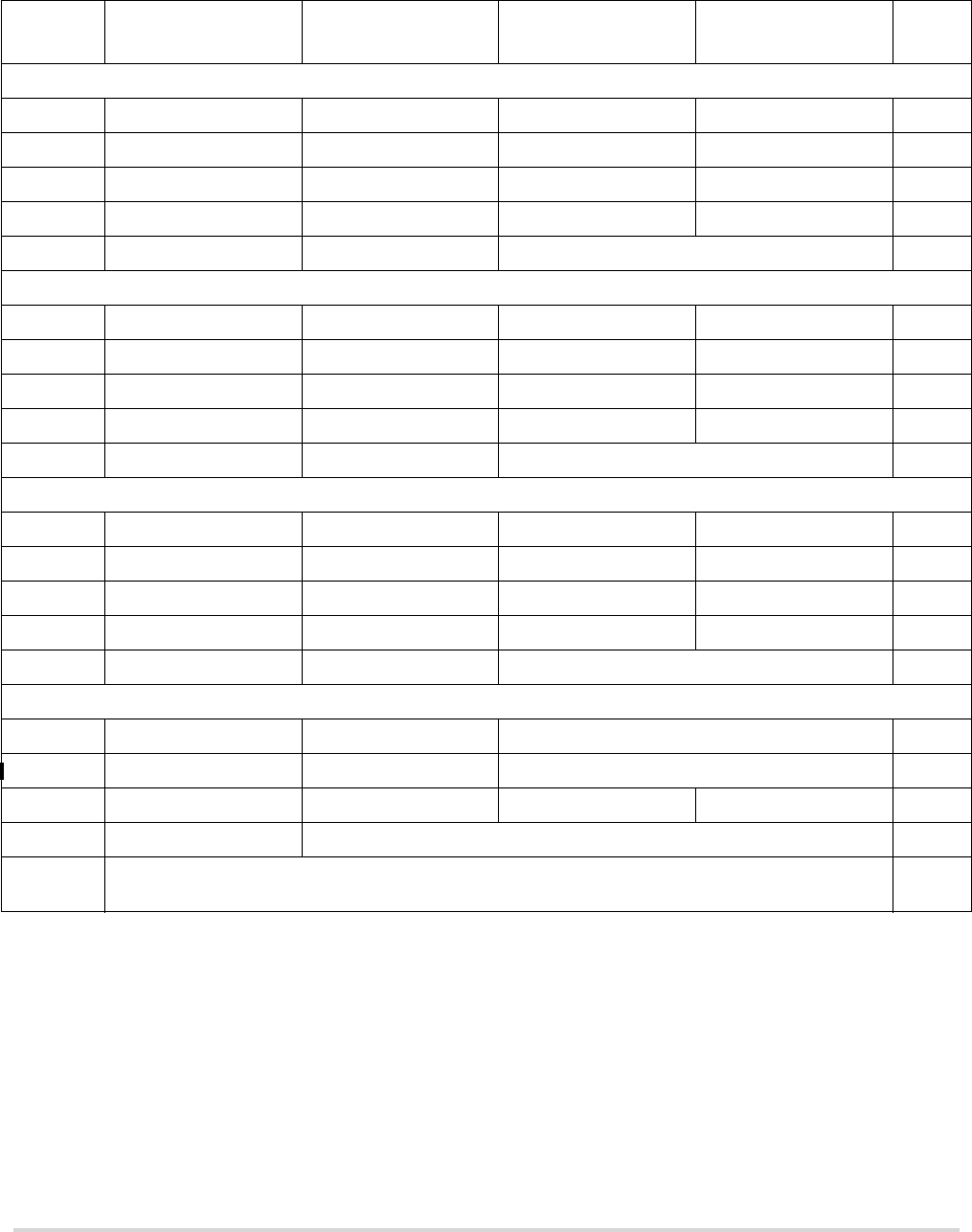

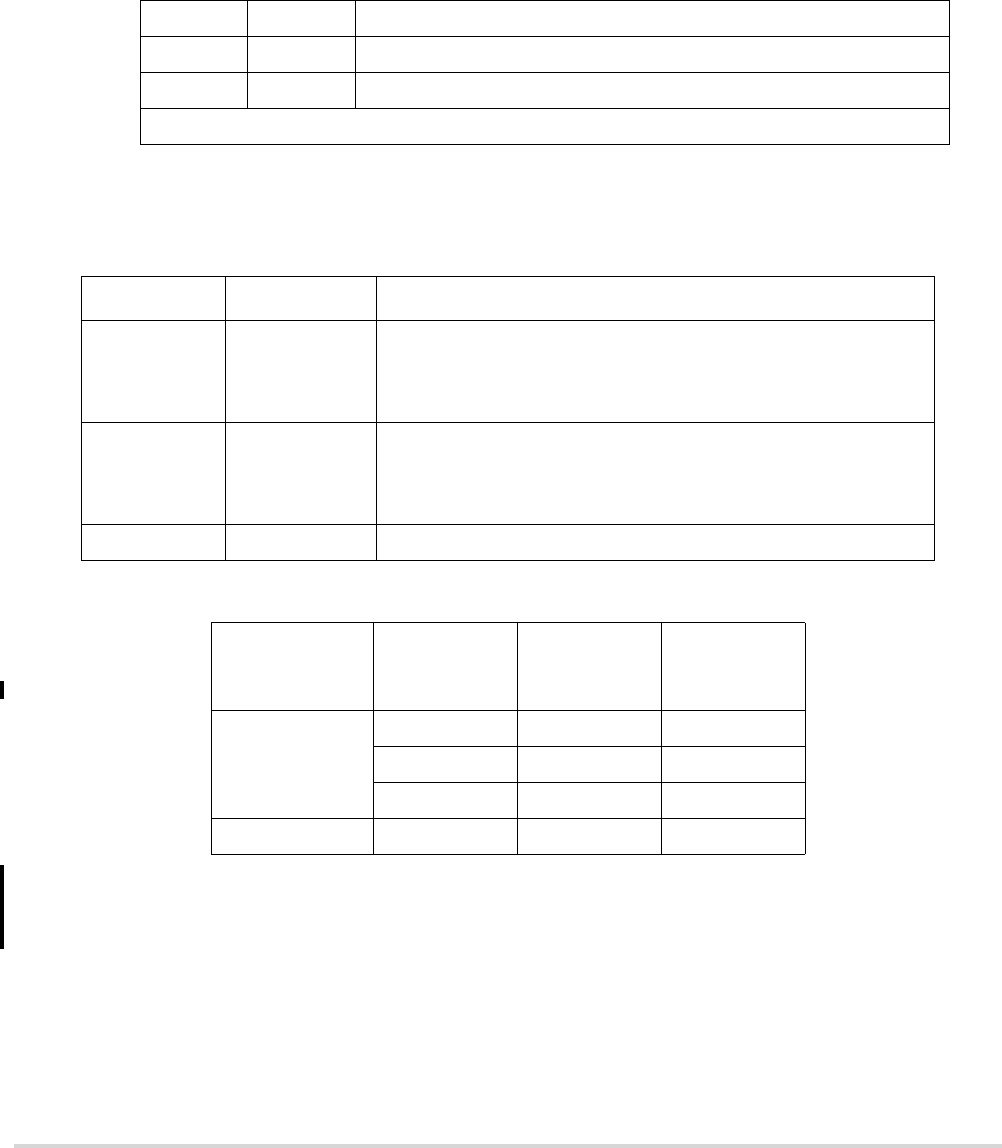

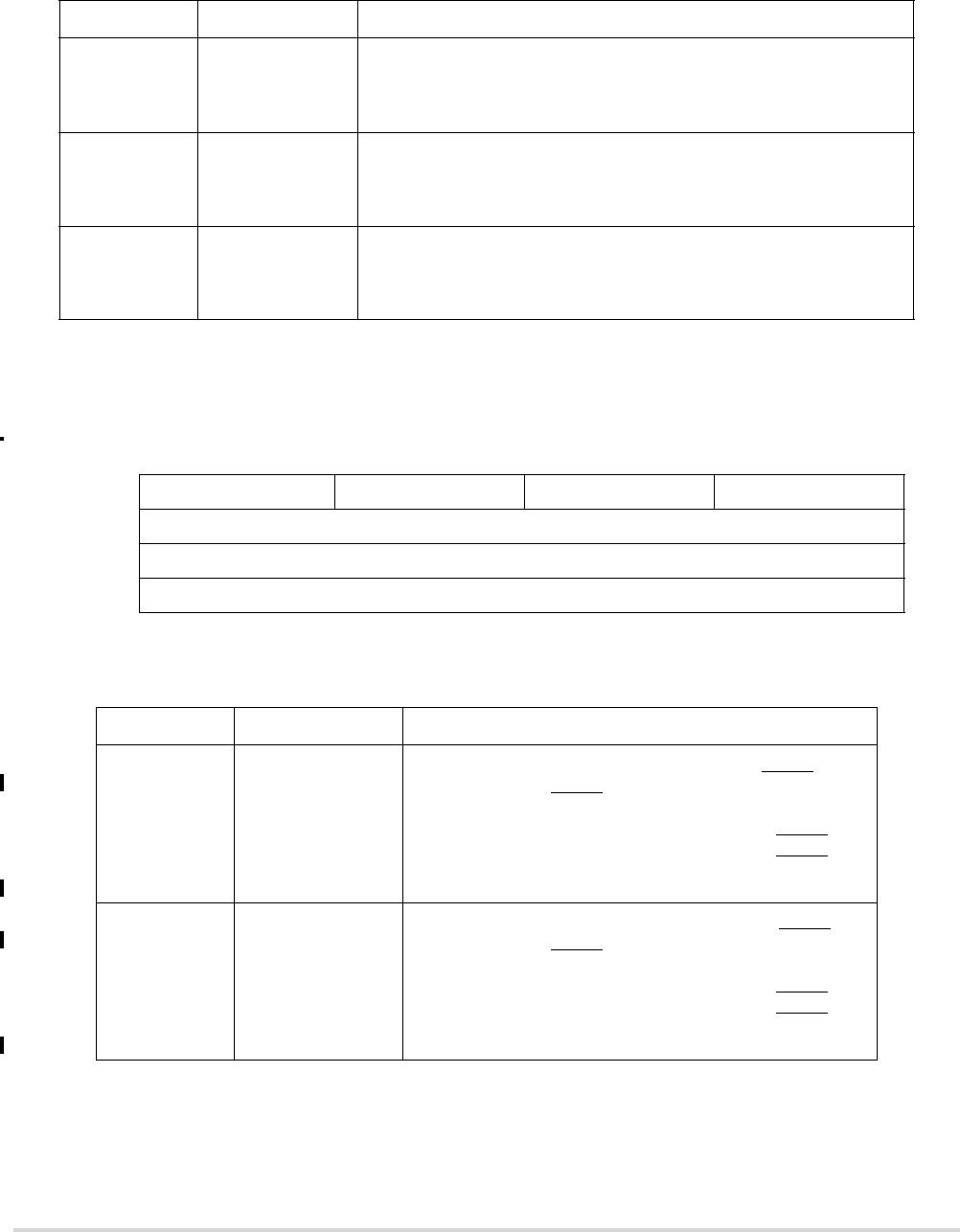

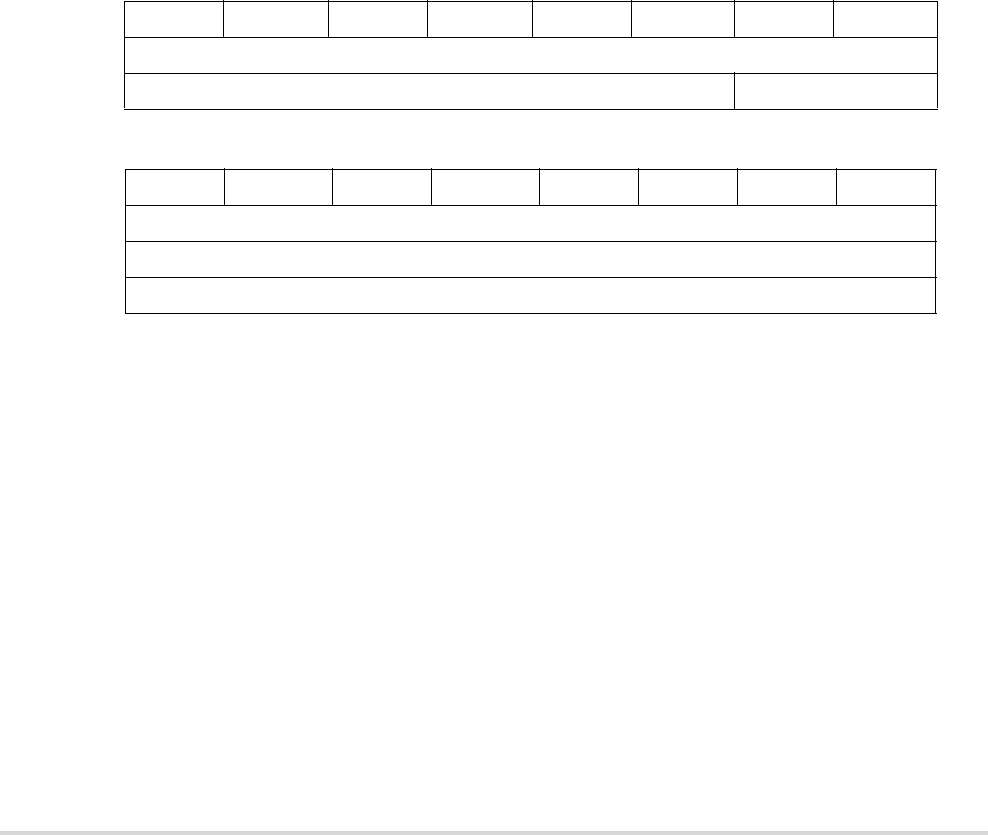

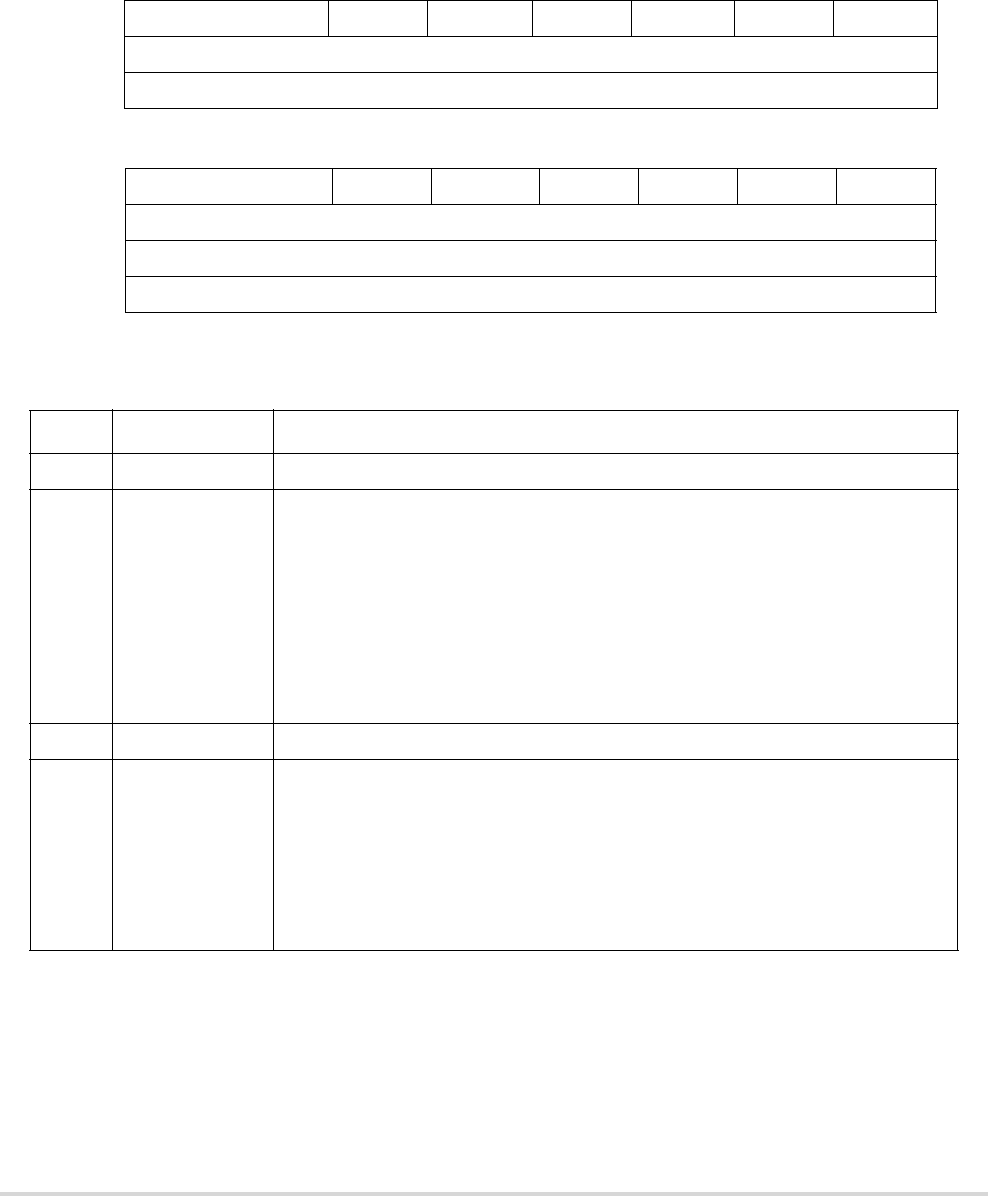

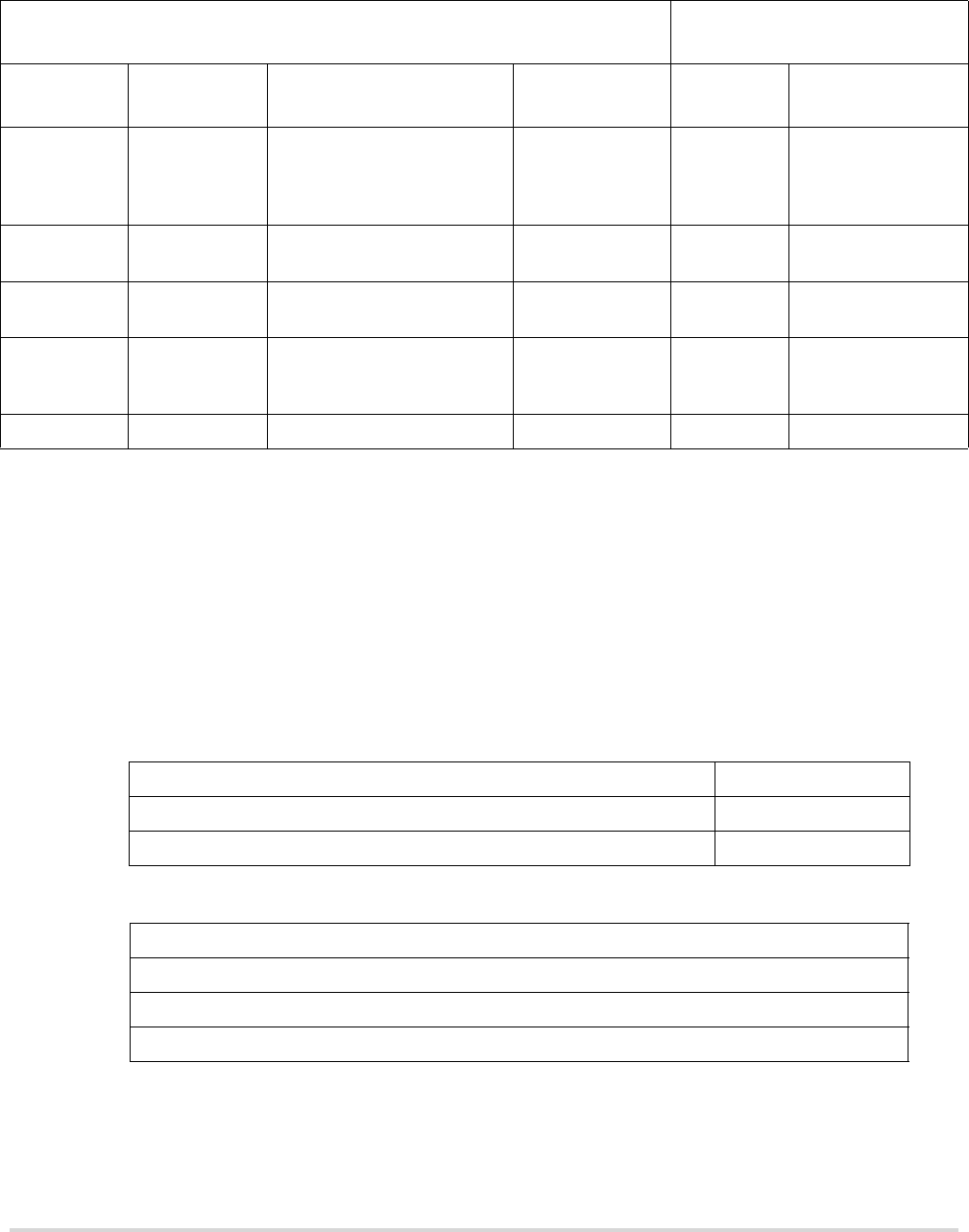

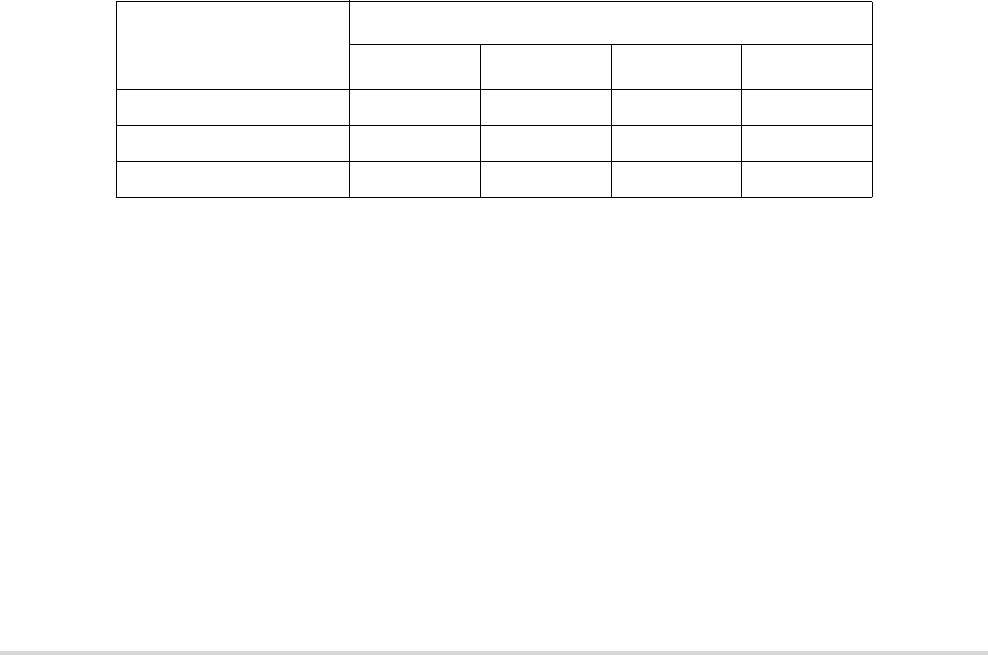

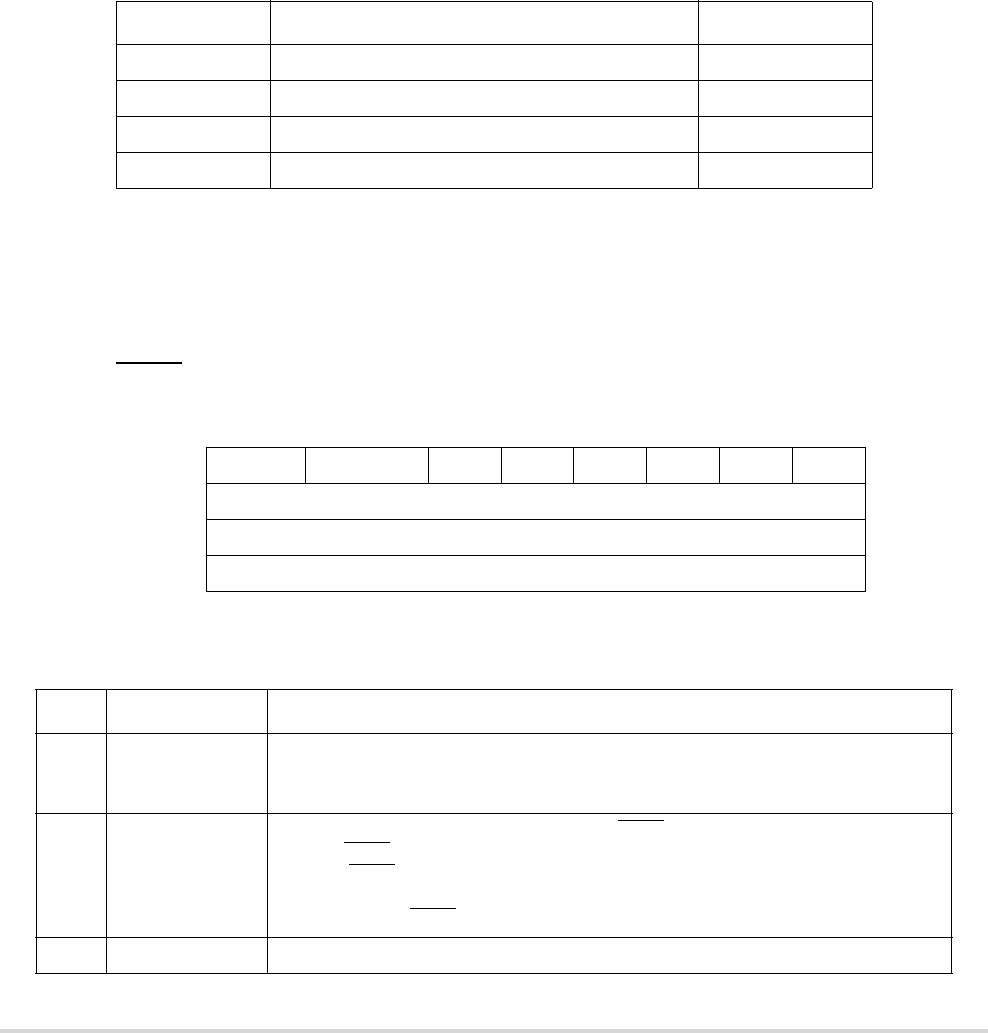

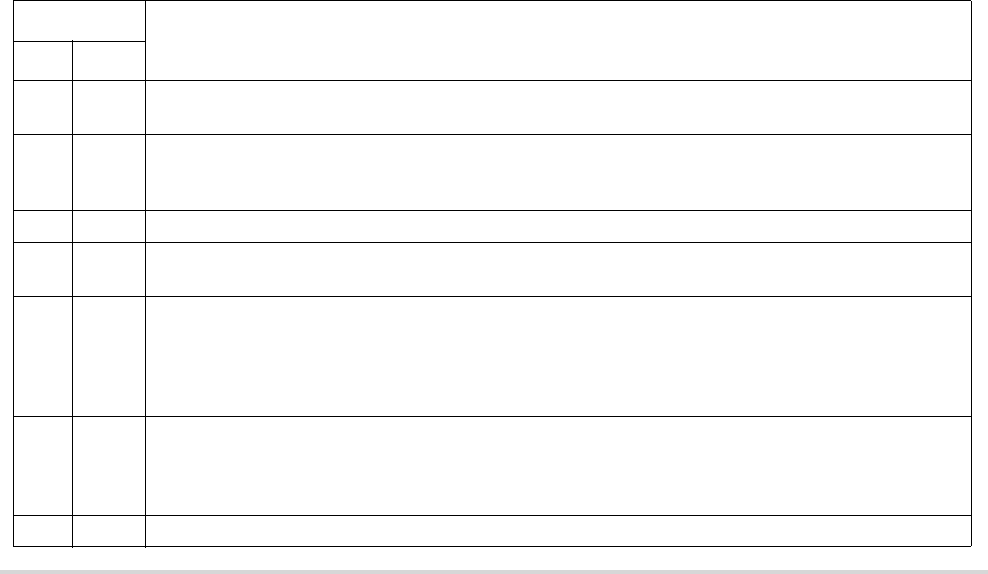

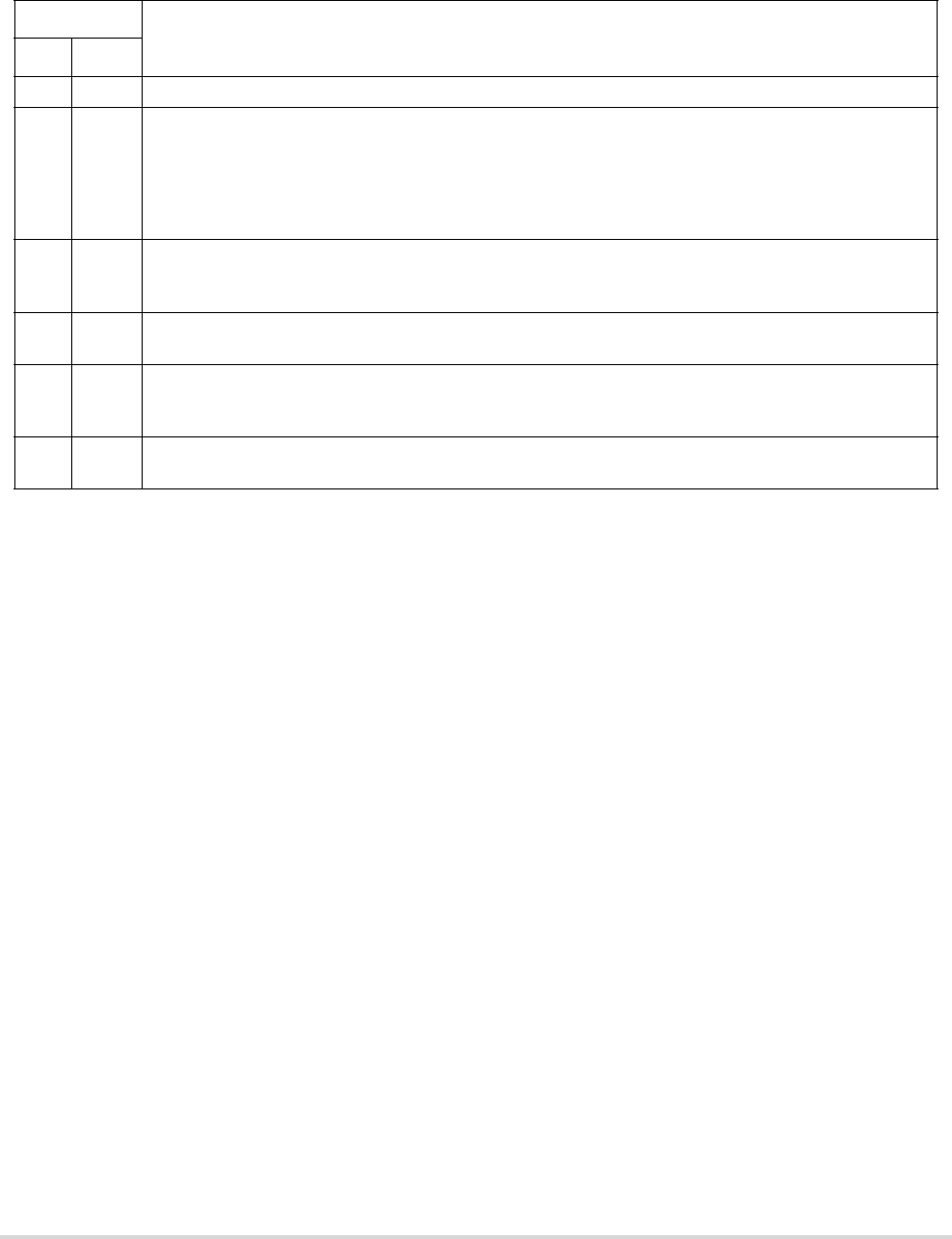

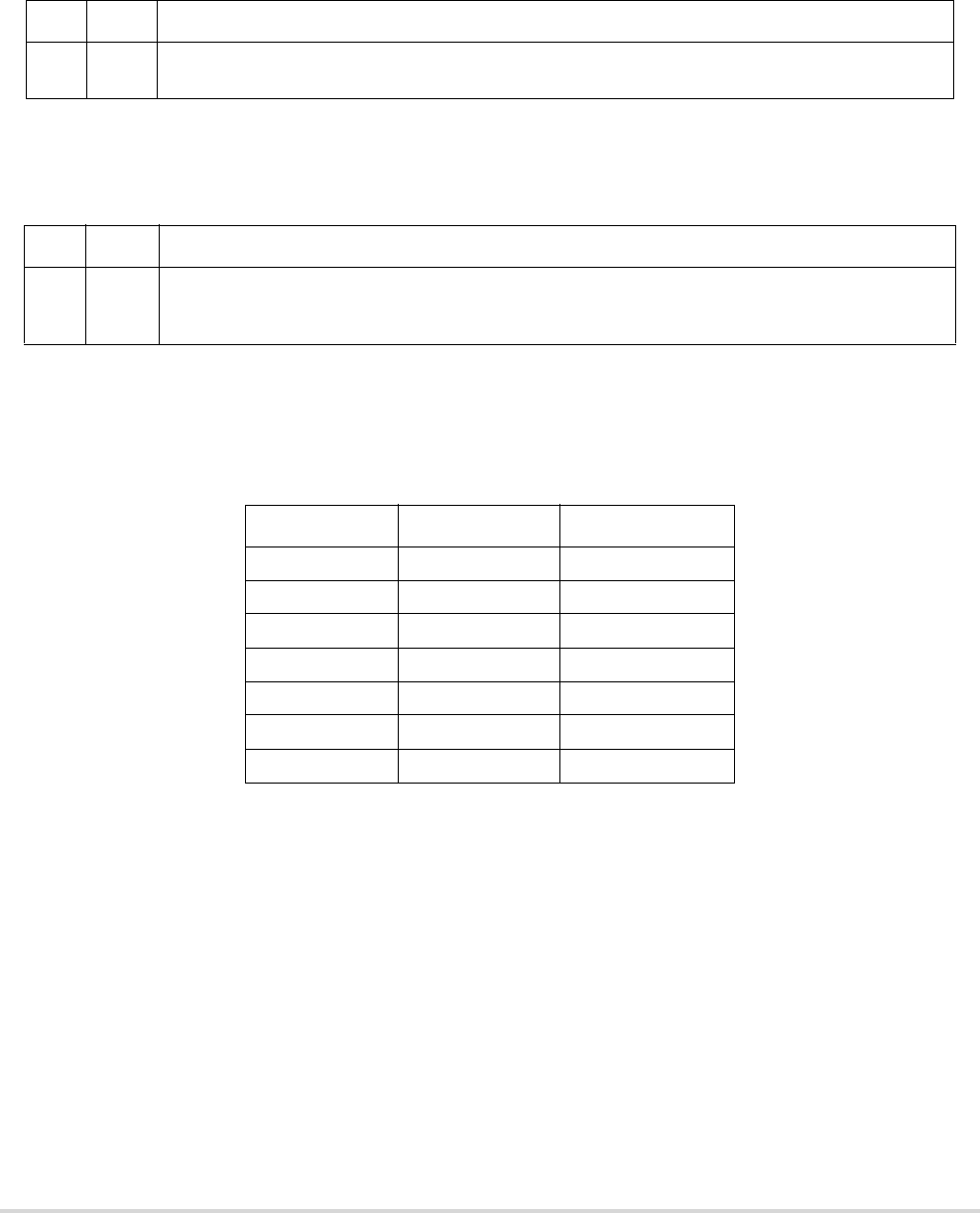

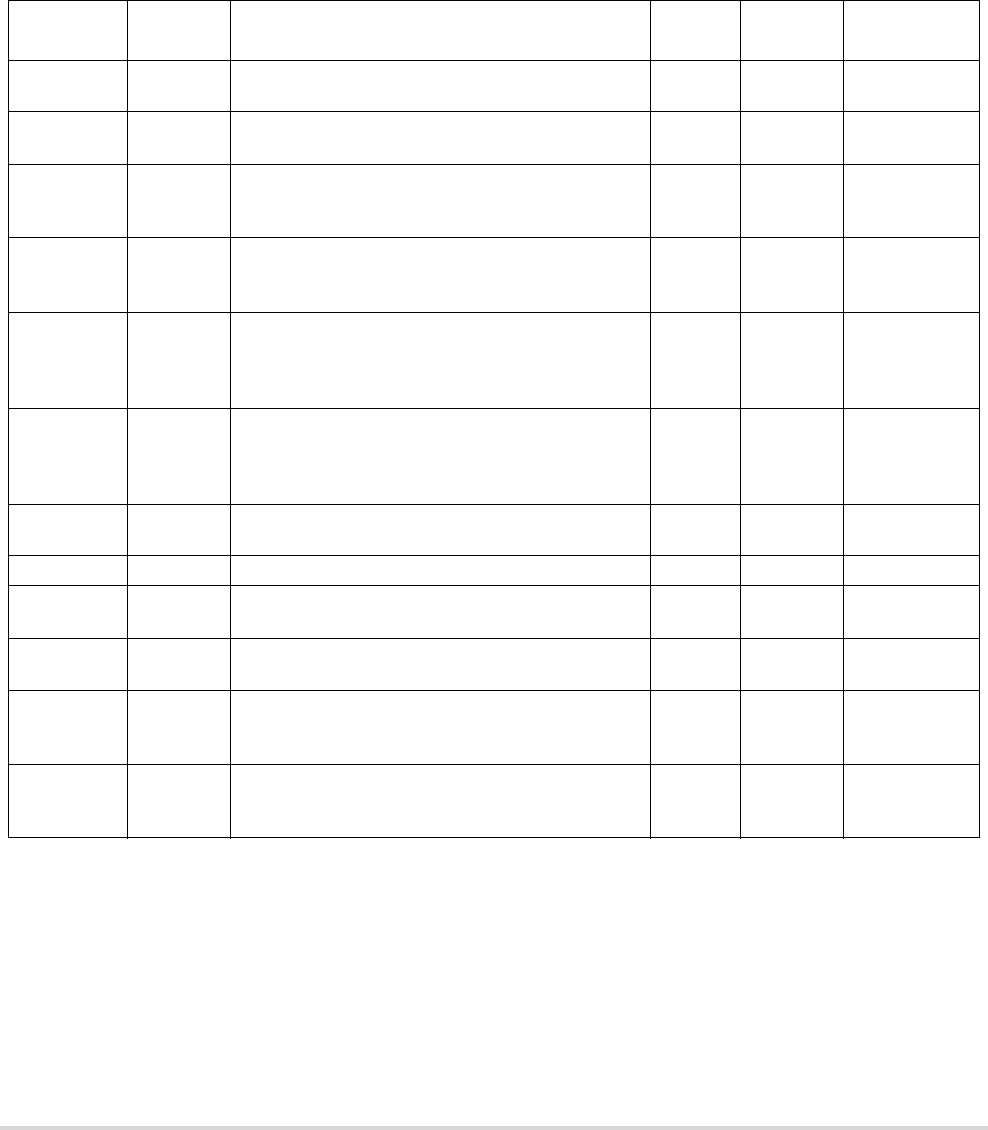

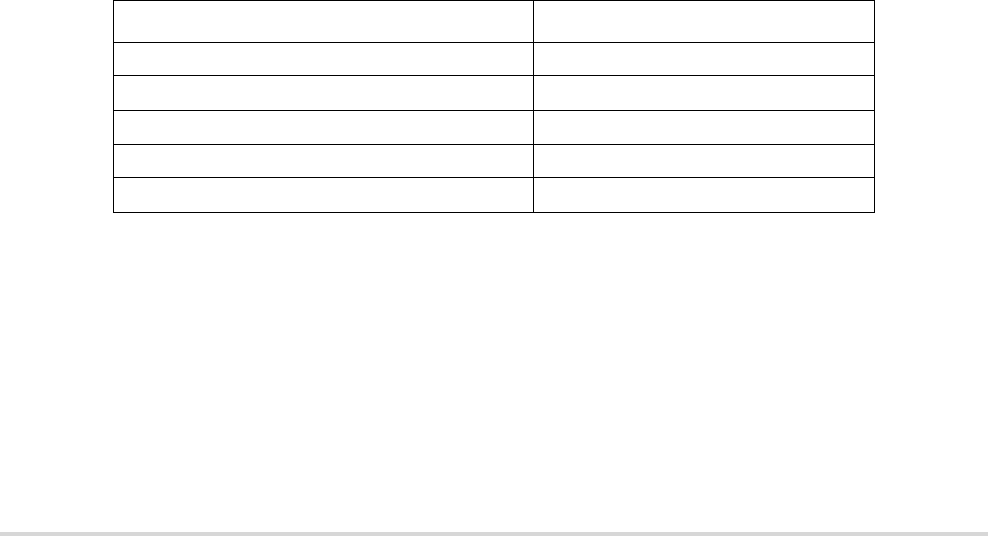

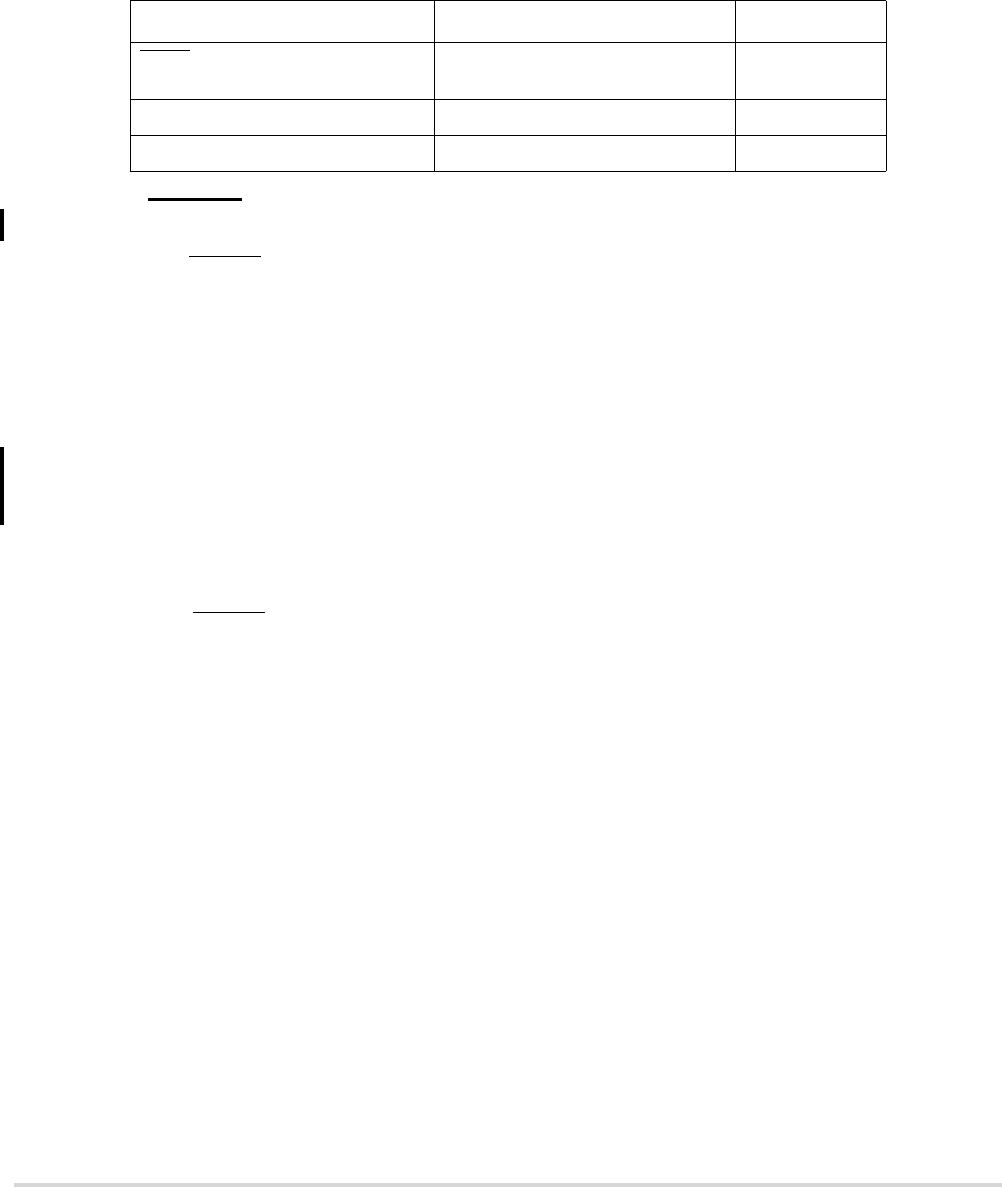

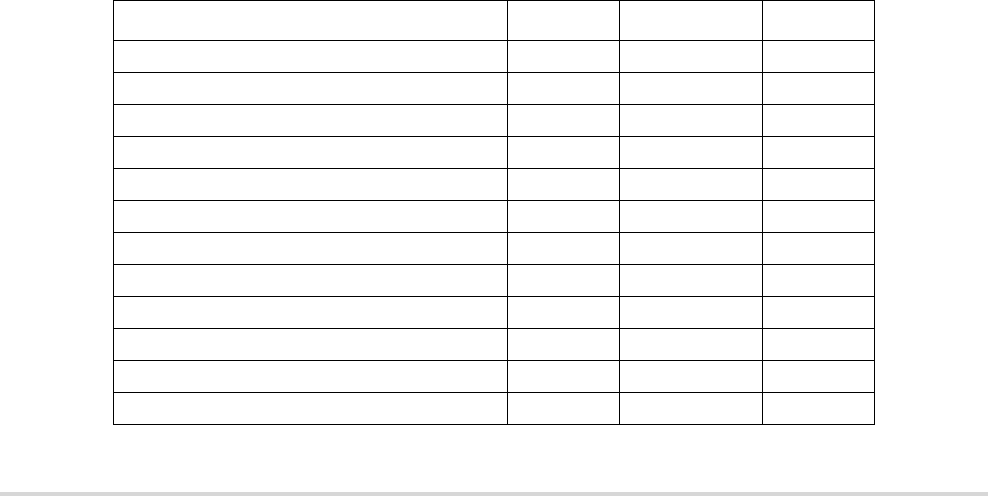

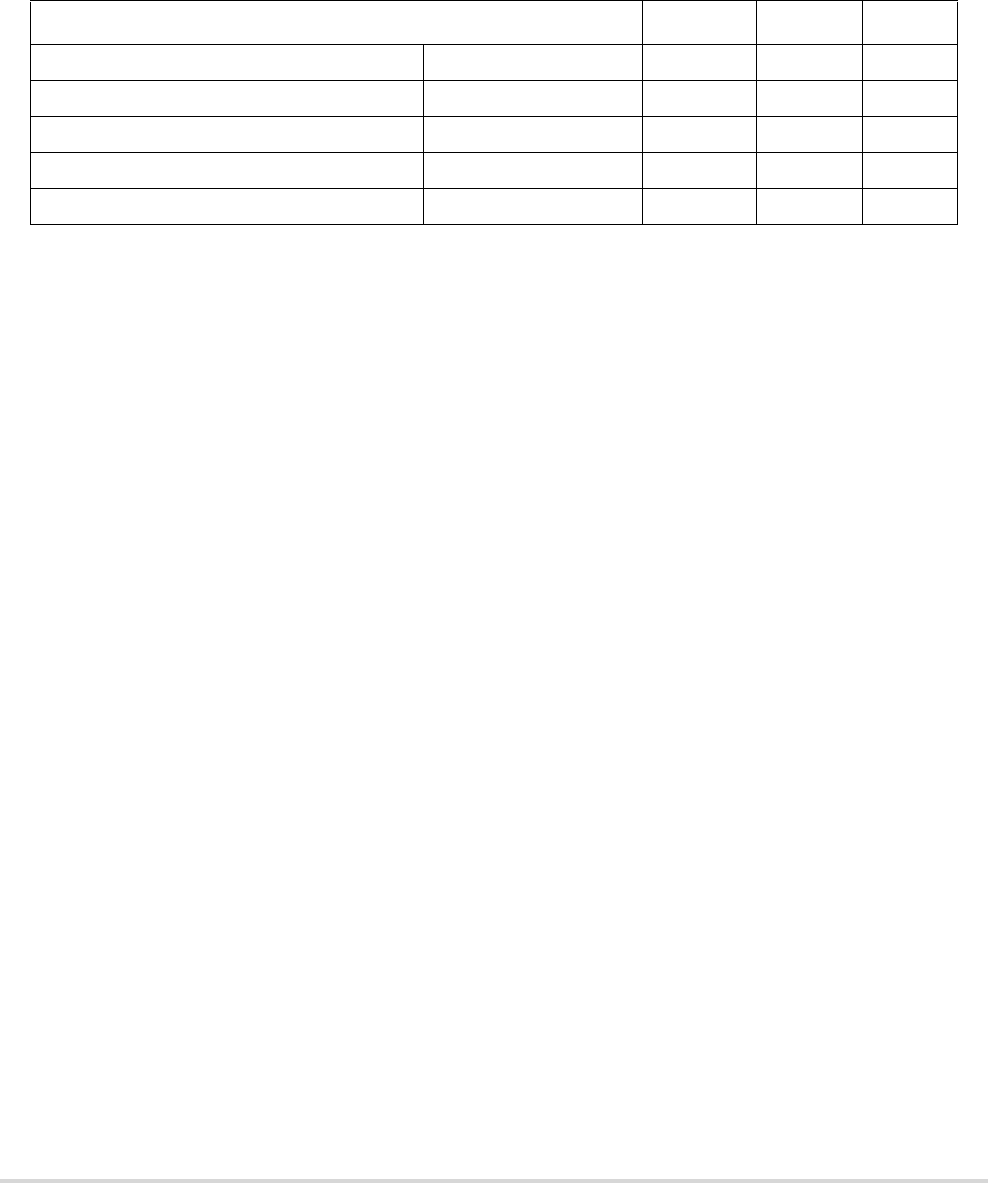

- Table 15-1. SDRAM Commands

- 15.2.1 DRAM Controller Signals

- 15.2.2 Memory Map for SDRAMC Registers

- 15.2.3 General Synchronous Operation Guidelines

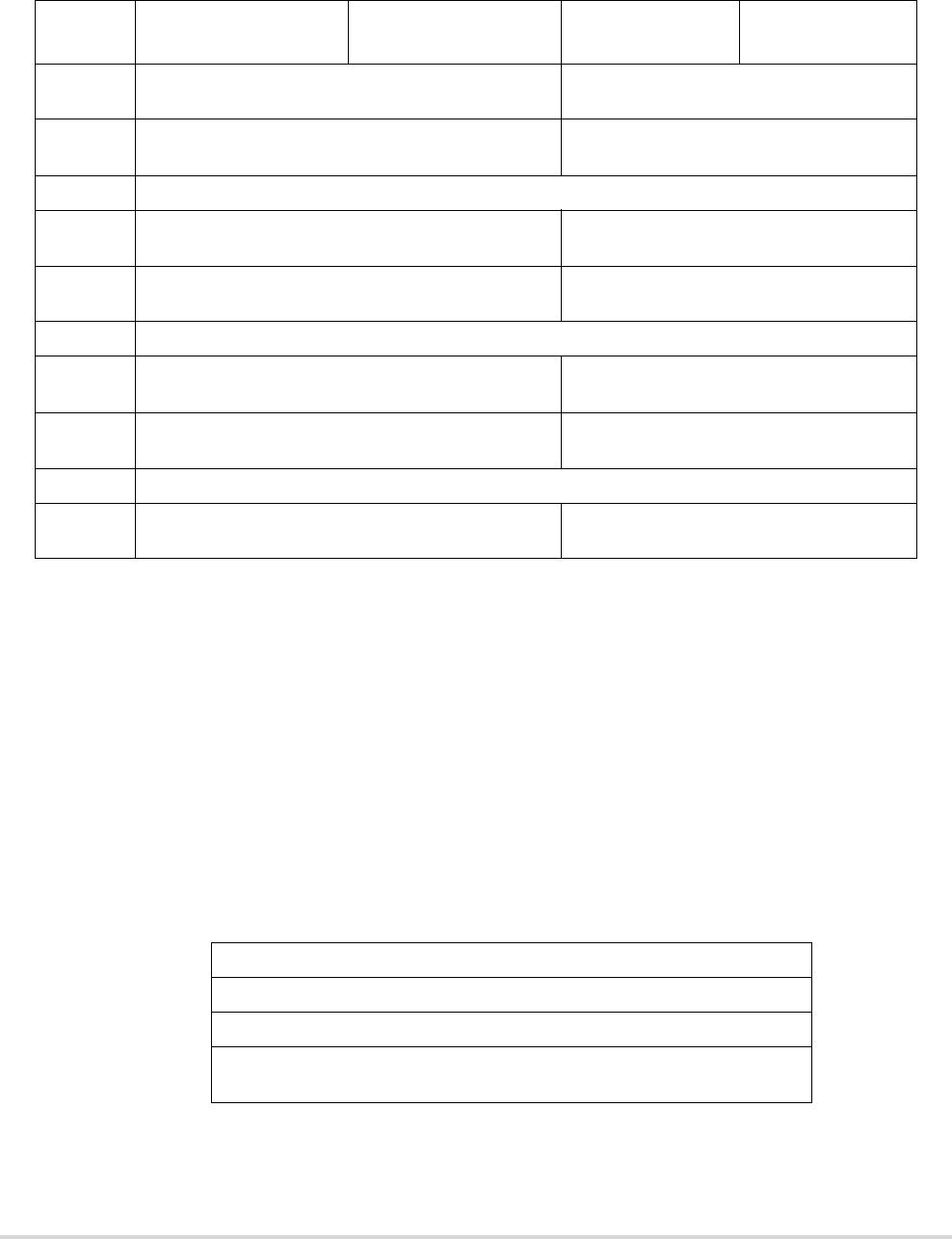

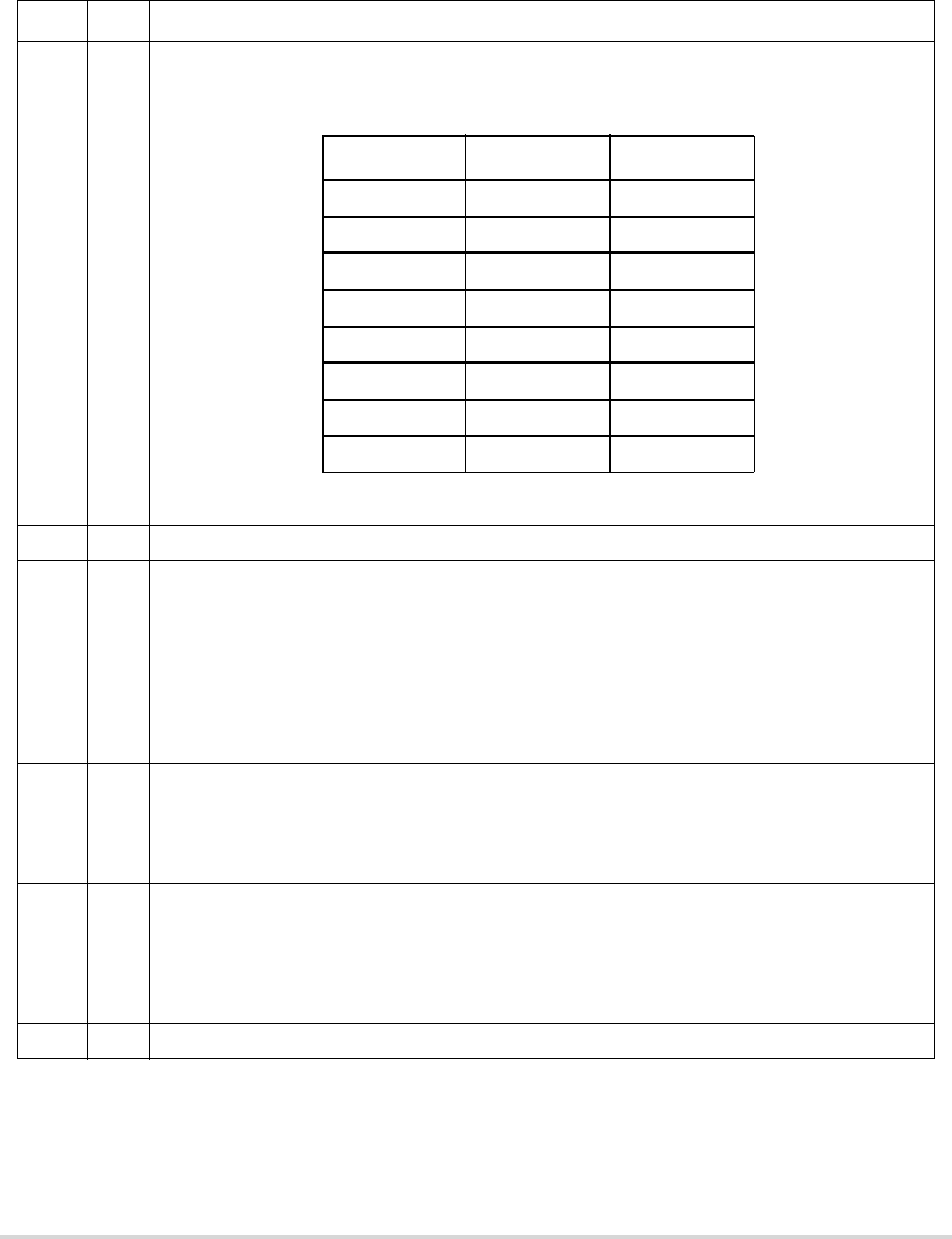

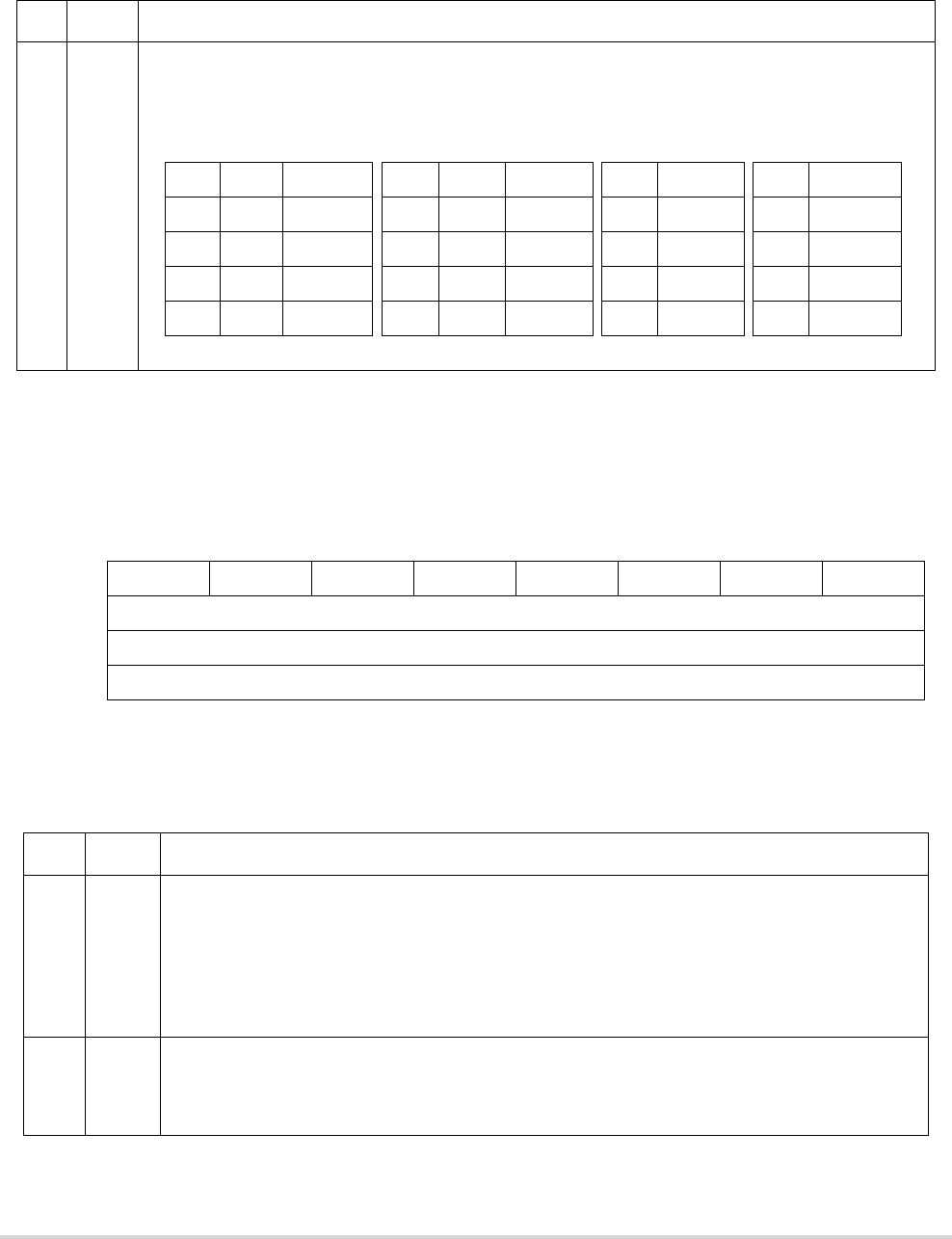

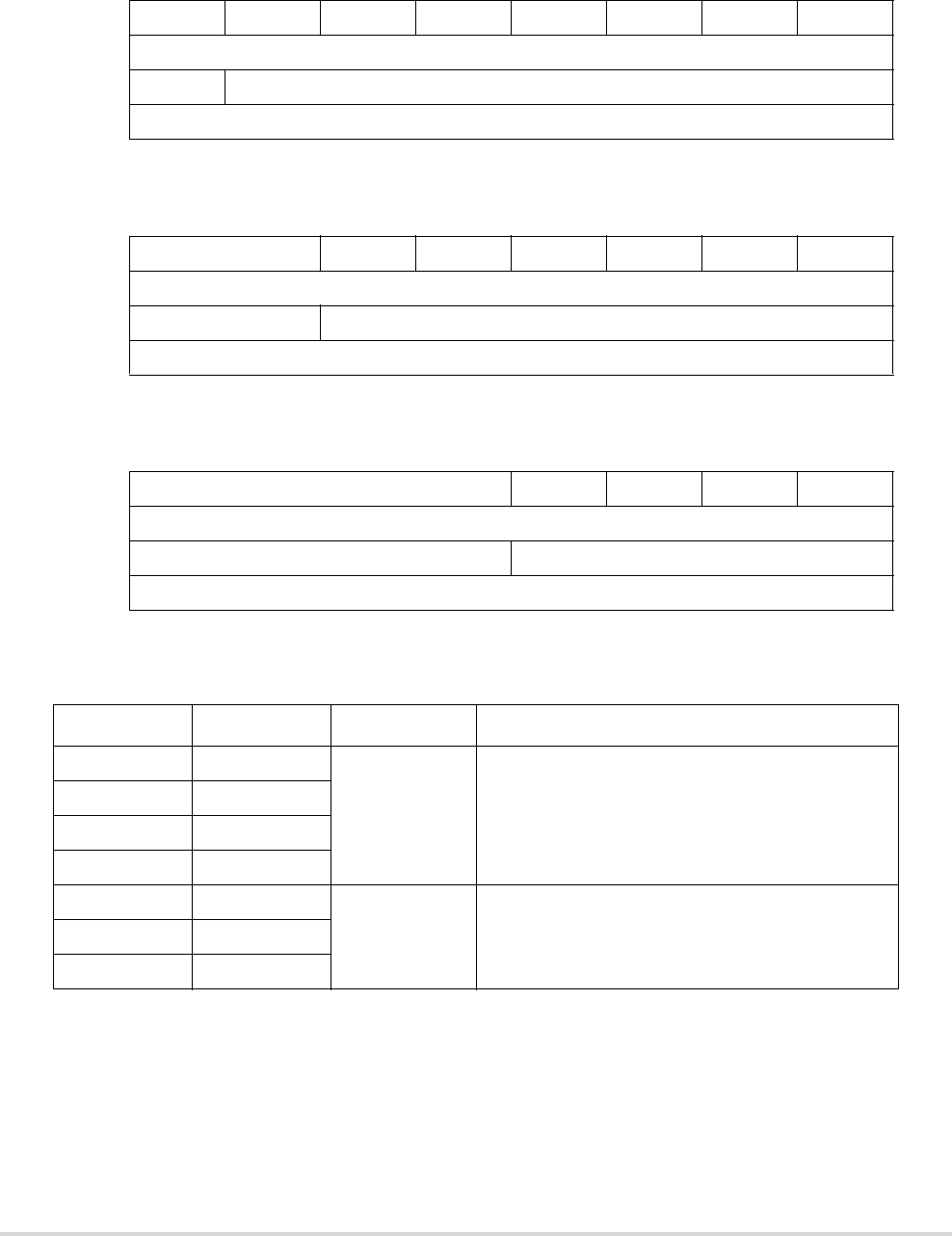

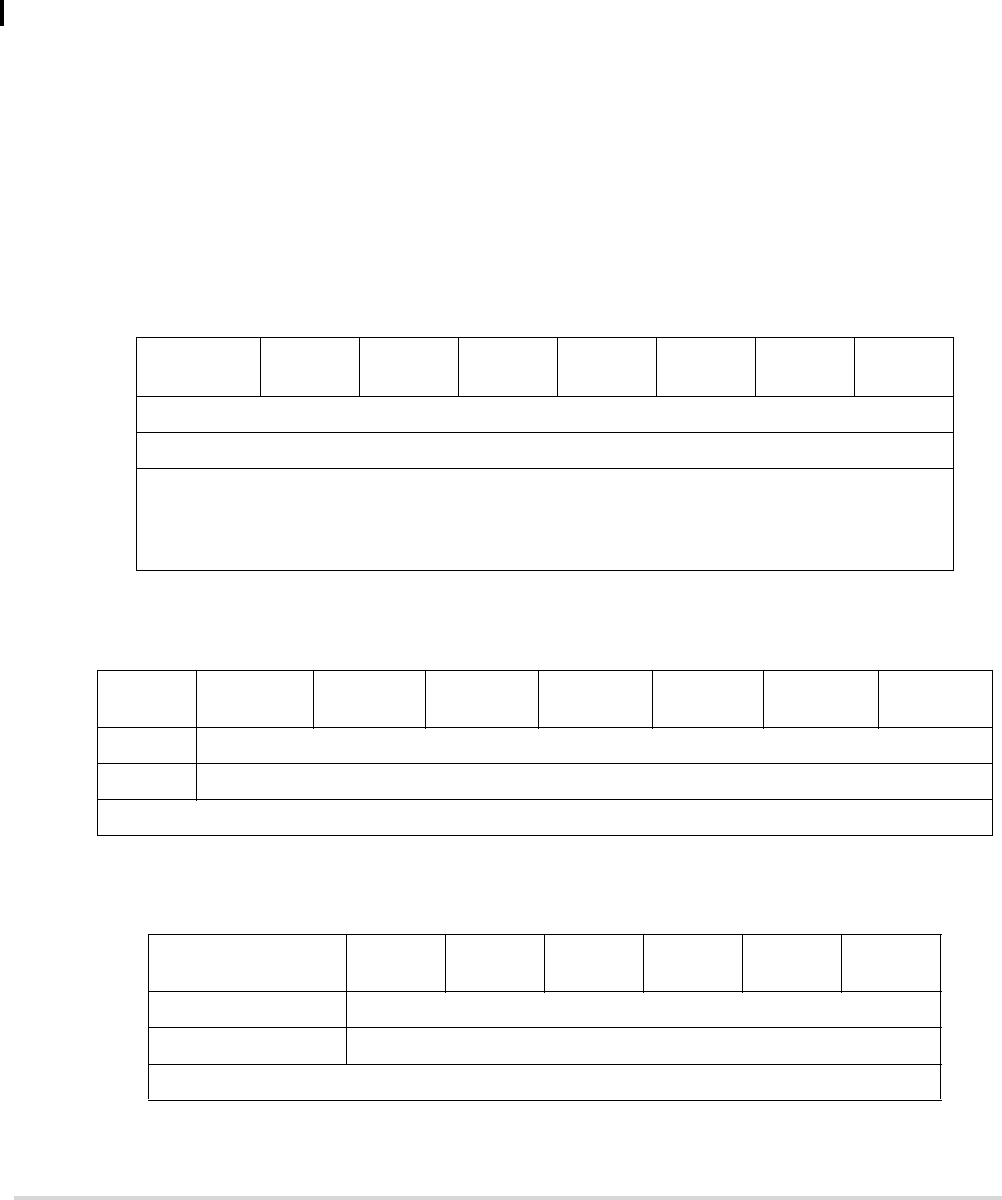

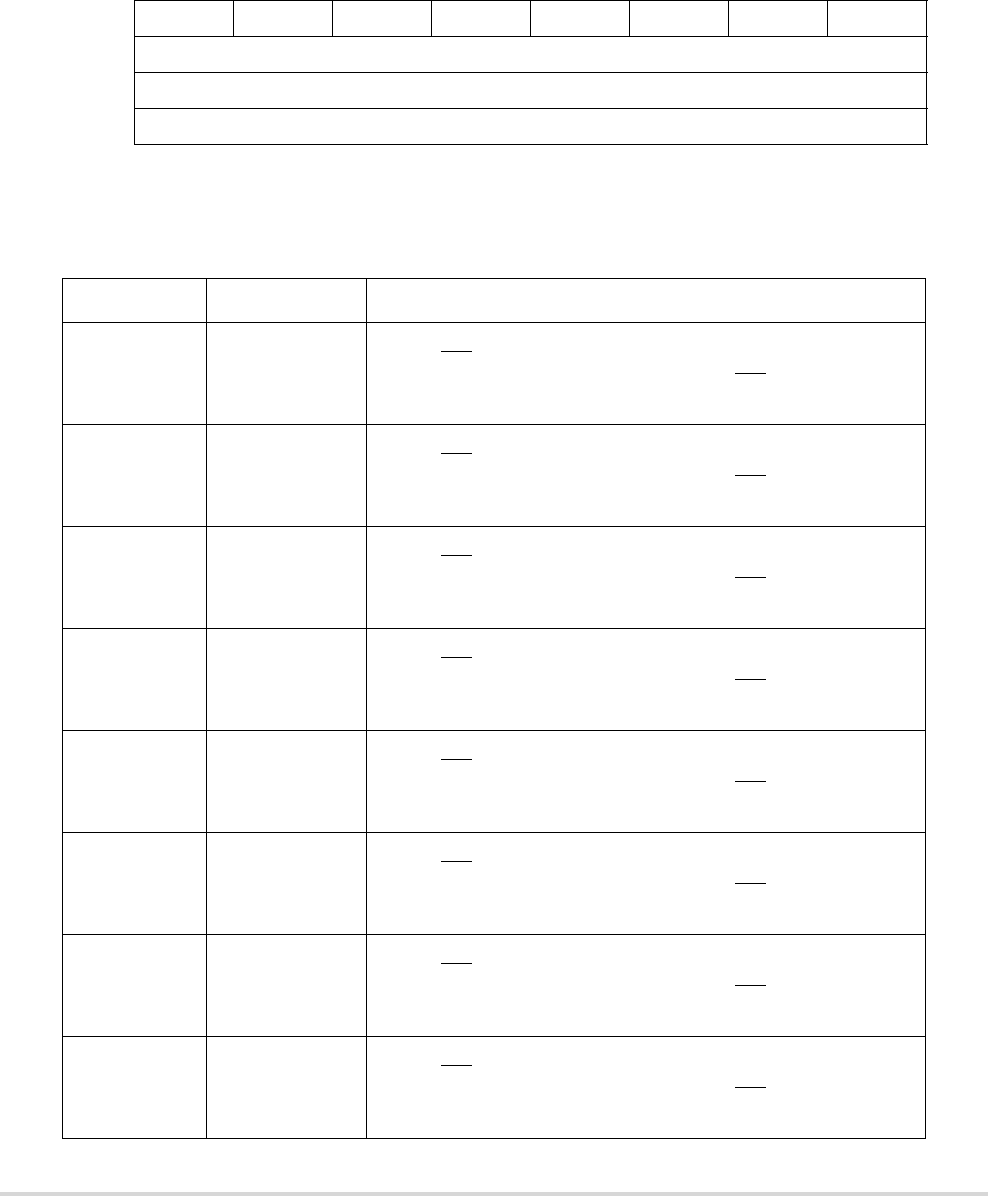

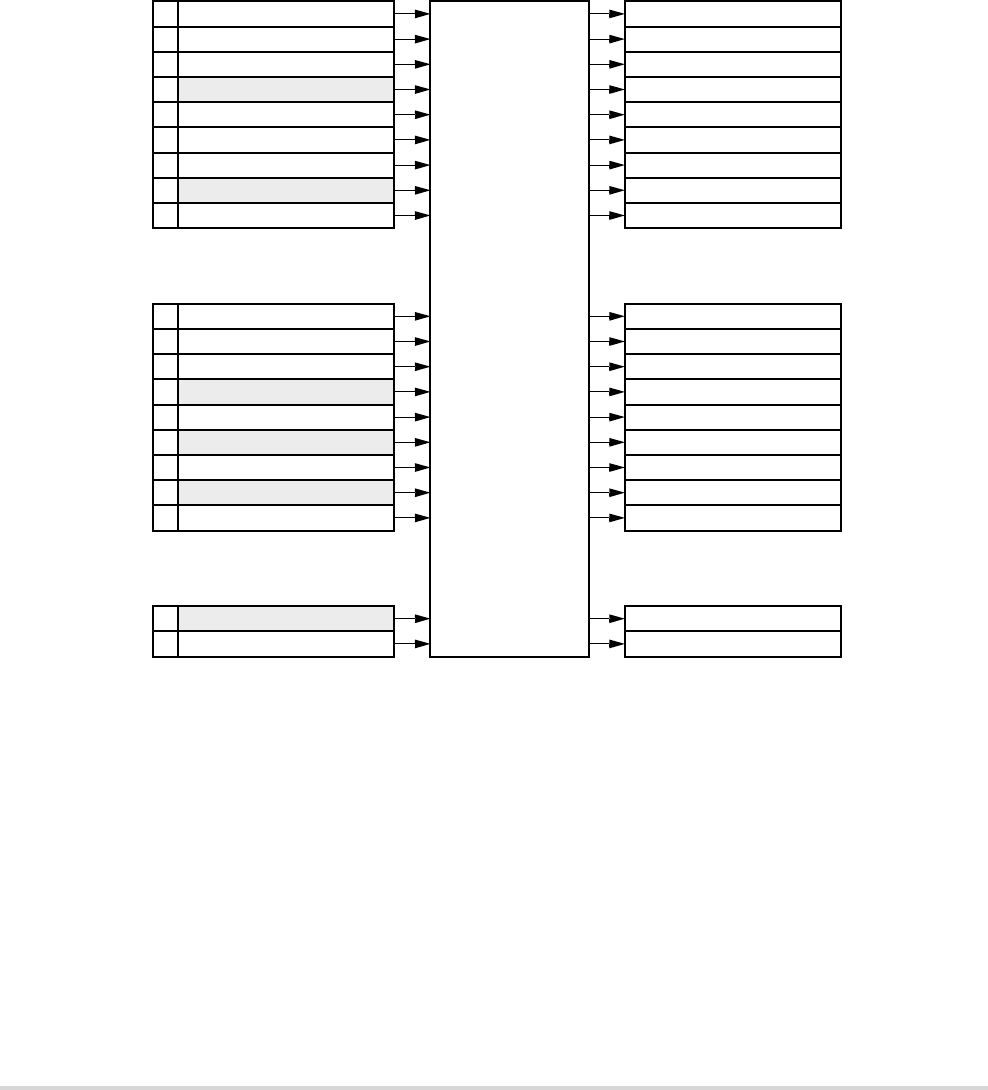

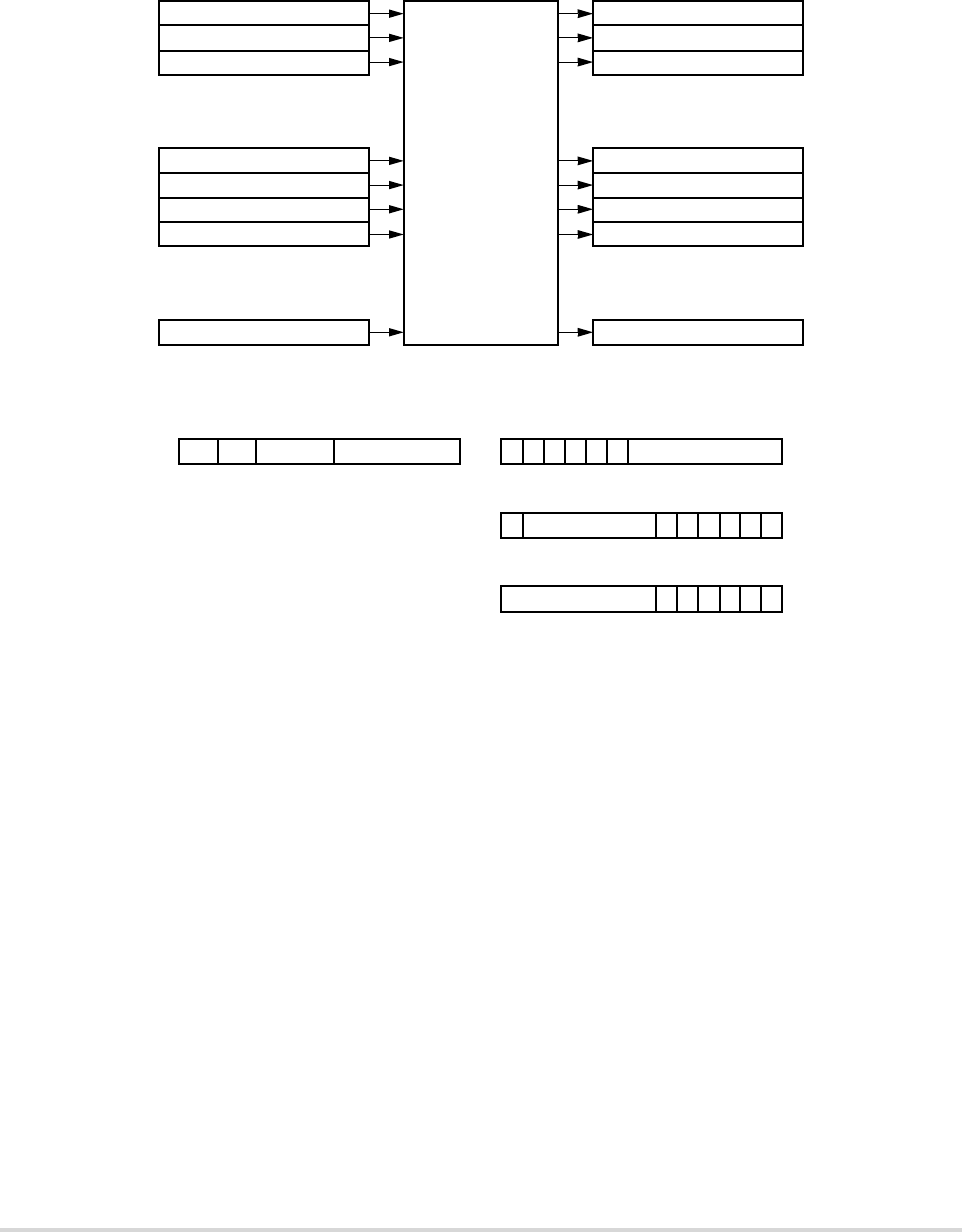

- 15.2.3.1 Address Multiplexing

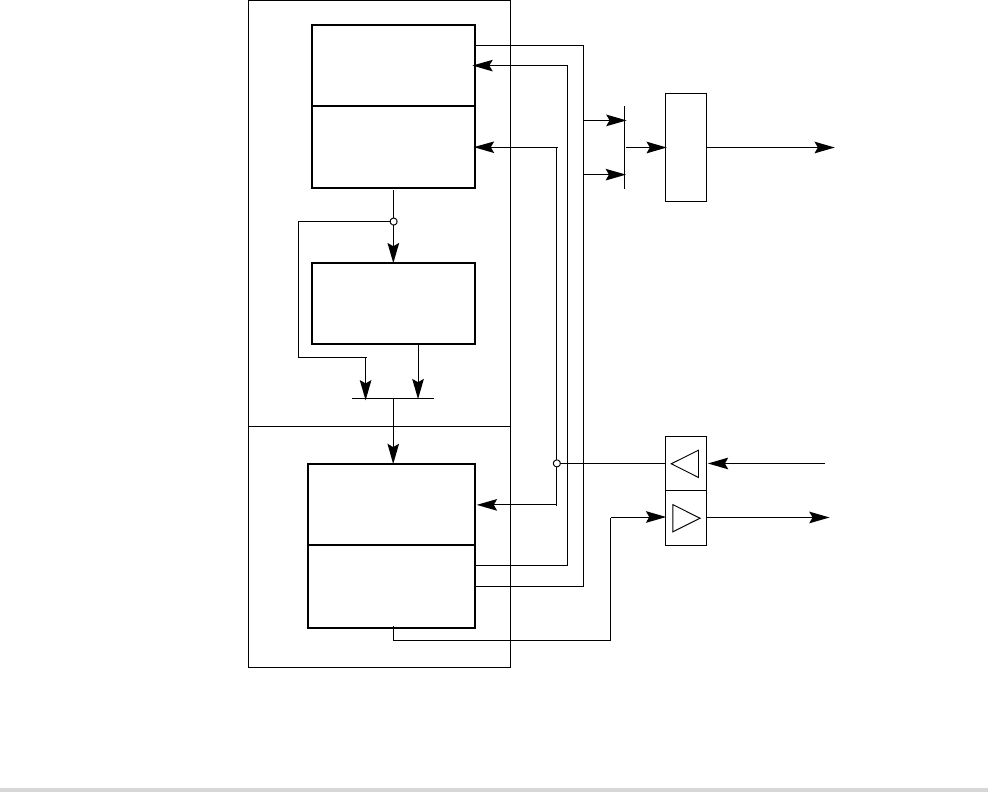

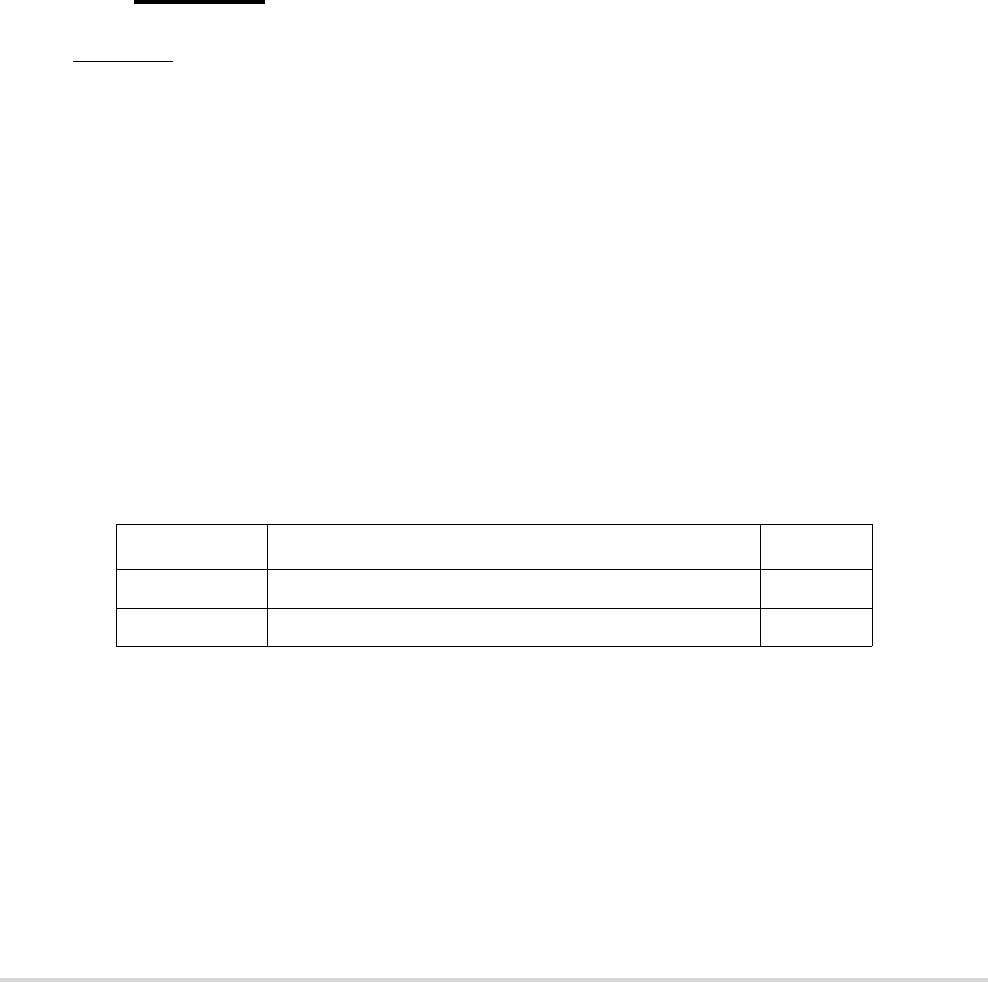

- Table 15-7. Generic Address Multiplexing Scheme

- Table 15-8. MCF5282 to SDRAM Interface (8-Bit Port, 9-Column Address Lines)

- Table 15-9. MCF5282 to SDRAM Interface (8-Bit Port,10-Column Address Lines)

- Table 15-10. MCF5282 to SDRAM Interface (8-Bit Port,11-Column Address Lines)

- Table 15-11. MCF5282 to SDRAM Interface (8-Bit Port,12-Column Address Lines)

- Table 15-12. MCF5282 to SDRAM Interface (8-Bit Port,13-Column Address Lines)

- Table 15-13. MCF5282 to SDRAM Interface (16-Bit Port, 8-Column Address Lines)

- Table 15-14. MCF5282 to SDRAM Interface (16-Bit Port, 9-Column Address Lines)

- Table 15-15. MCF5282 to SDRAM Interface (16-Bit Port, 10-Column Address Lines)

- Table 15-16. MCF5282 to SDRAM Interface (16-Bit Port, 11-Column Address Lines)

- Table 15-17. MCF5282 to SDRAM Interface (16-Bit Port, 12-Column Address Lines)

- Table 15-18. MCF5282 to SDRAM Interface (16-Bit Port, 13-Column-Address Lines)

- Table 15-19. MCF5282 to SDRAM Interface (32-Bit Port, 8-Column Address Lines)

- Table 15-20. MCF5282 to SDRAM Interface (32-Bit Port, 9-Column Address Lines)

- Table 15-21. MCF5282 to SDRAM Interface (32-Bit Port, 10-Column Address Lines)

- Table 15-22. MCF5282 to SDRAM Interface (32-Bit Port, 11-Column Address Lines)

- Table 15-23. MCF5282 to SDRAM Interface (32-Bit Port, 12-Column Address Lines)

- 15.2.3.2 SDRAM Byte Strobe Connections

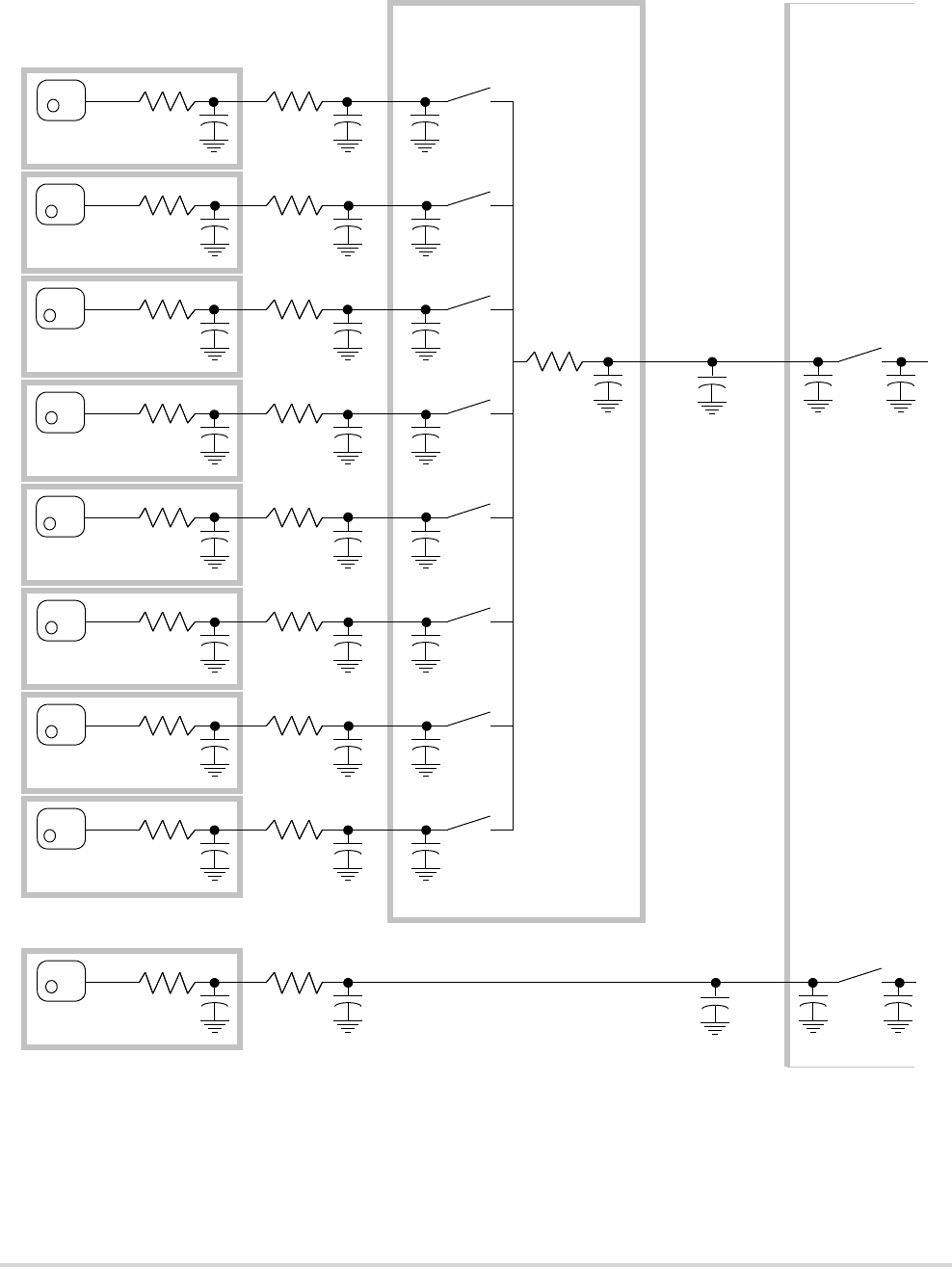

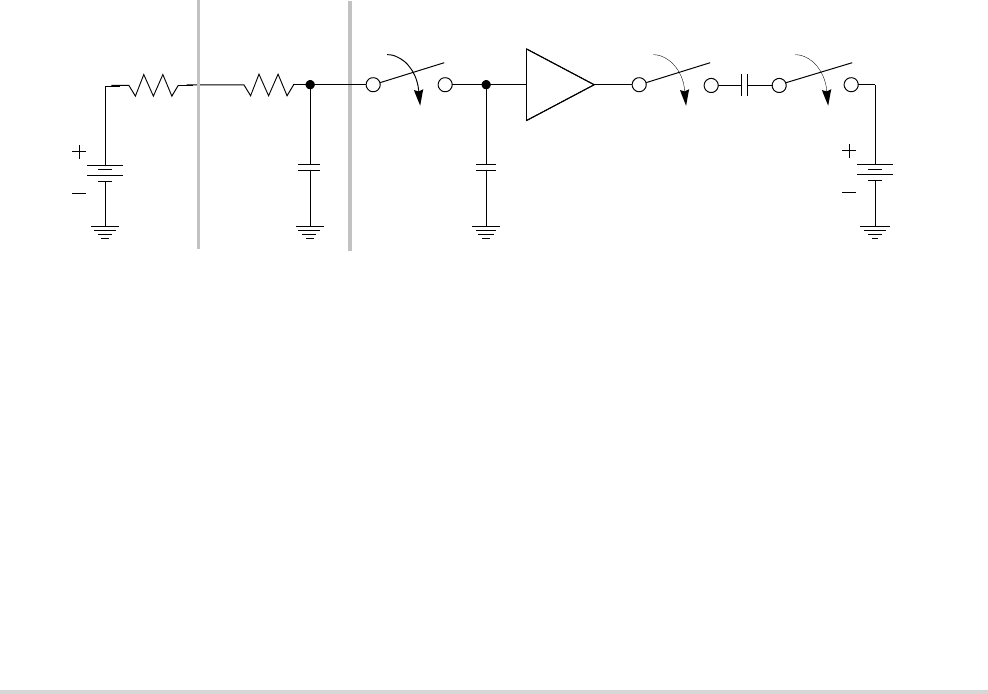

- 15.2.3.3 Interfacing Example

- 15.2.3.4 Burst Page Mode

- 15.2.3.5 Auto-Refresh Operation

- 15.2.3.6 Self-Refresh Operation

- 15.2.3.1 Address Multiplexing

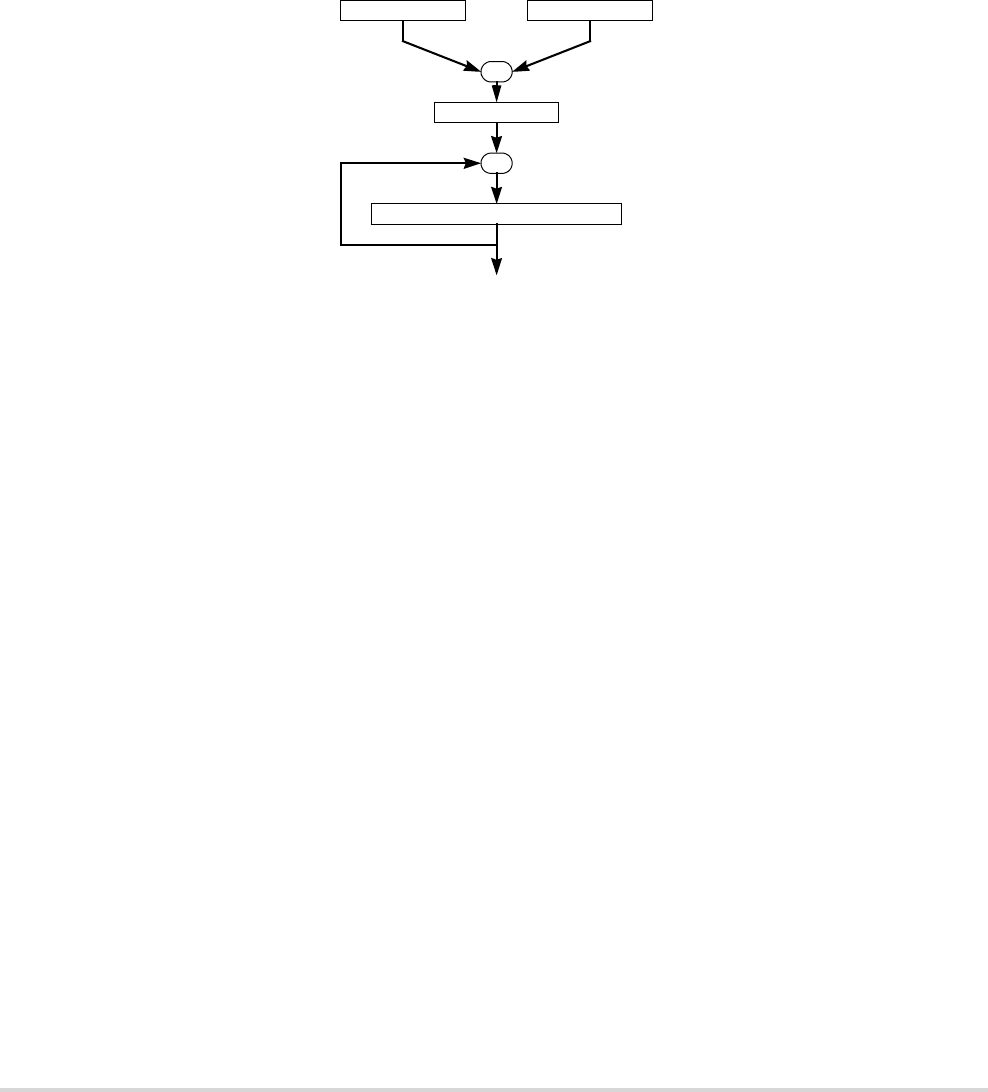

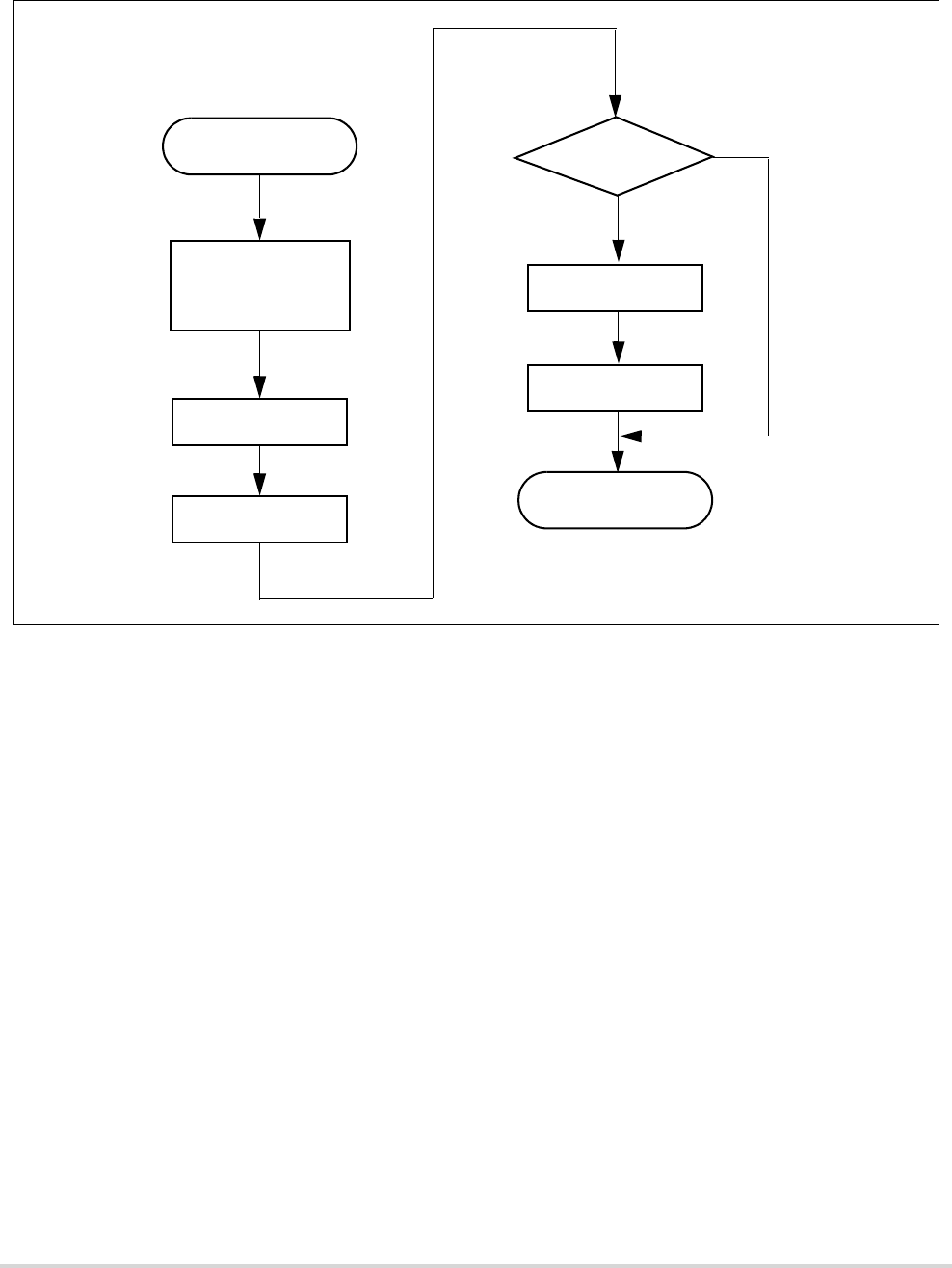

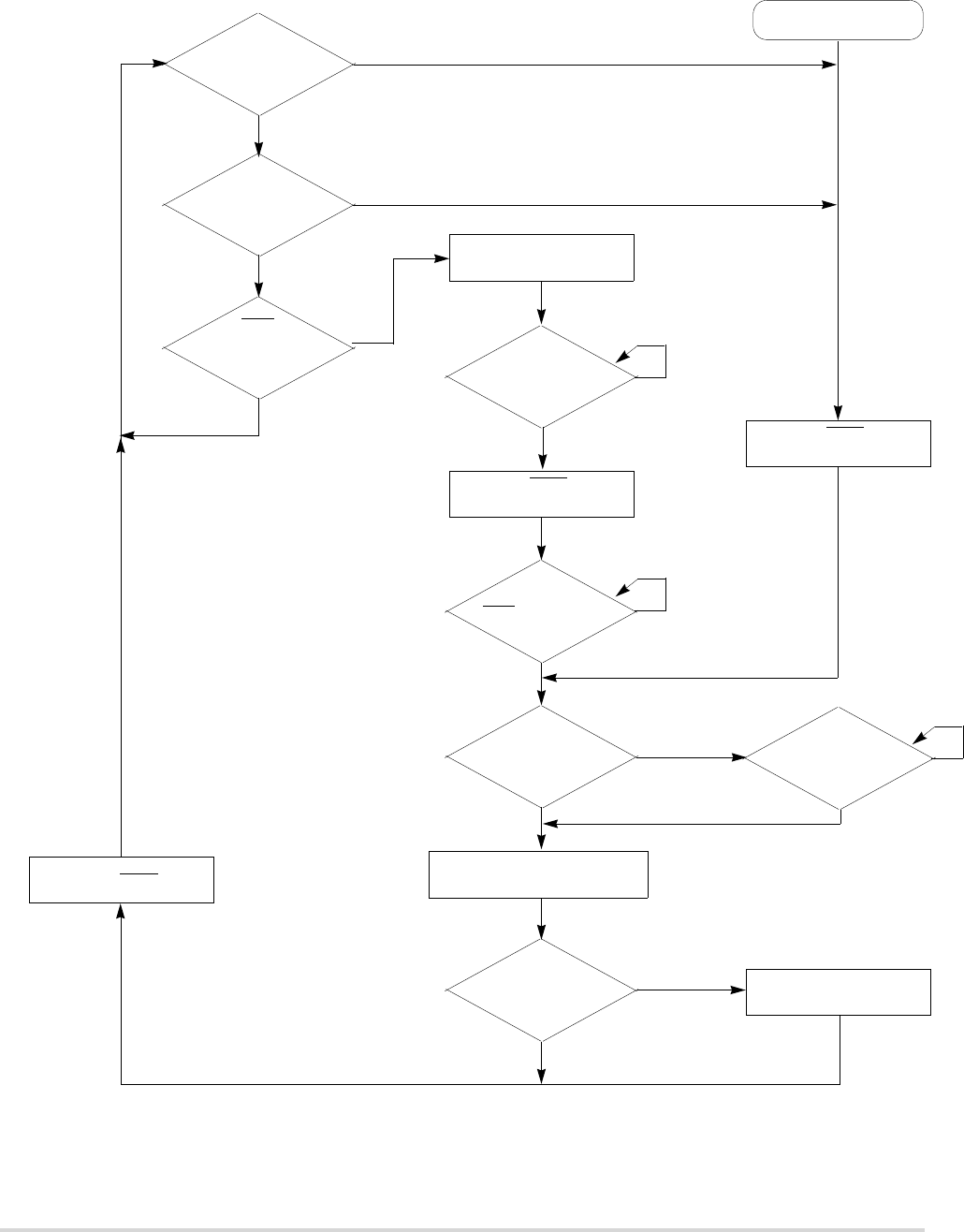

- 15.2.4 Initialization Sequence

- 15.3 SDRAM Example

- Chapter 16 DMA Controller Module

- 16.1 Overview

- 16.2 DMA Request Control (DMAREQC)

- 16.3 DMA Transfer Overview

- 16.4 DMA Controller Module Programming Model

- 16.5 DMA Controller Module Functional Description

- Chapter 17 Fast Ethernet Controller (FEC)

- 17.1 Overview

- 17.2 Modes of Operation

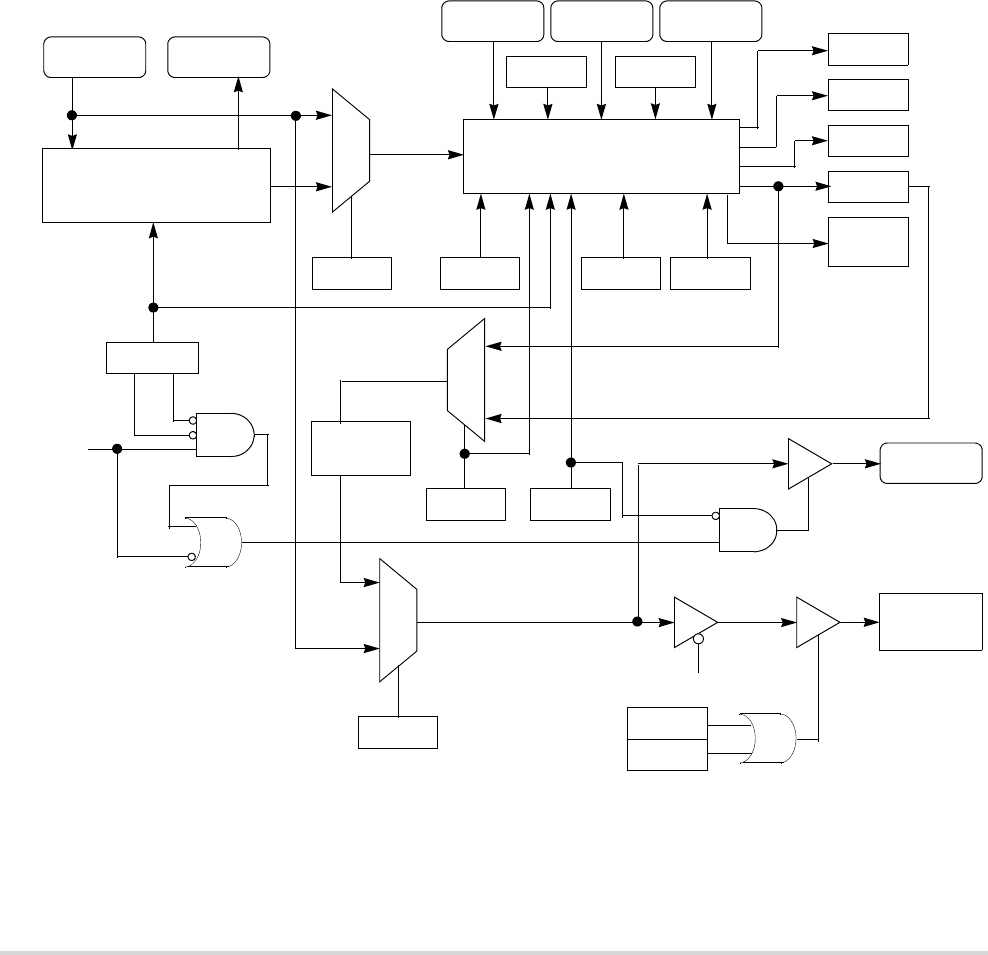

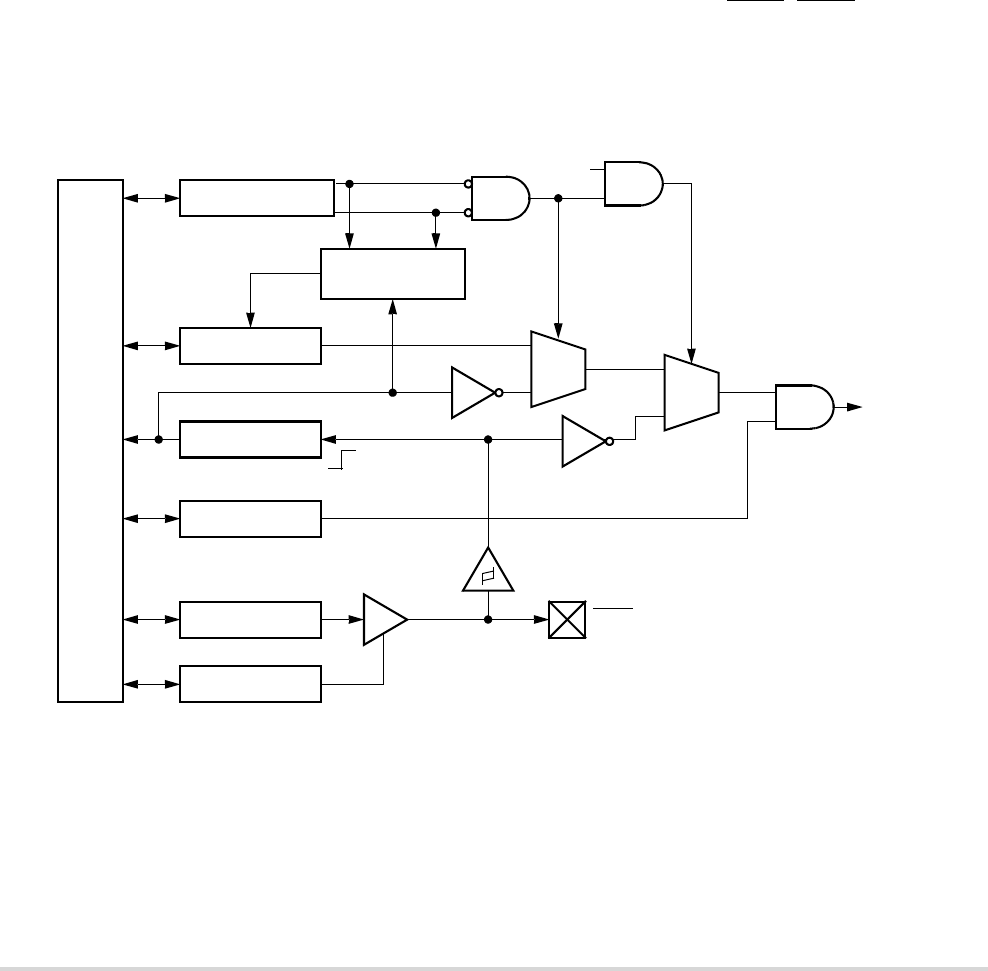

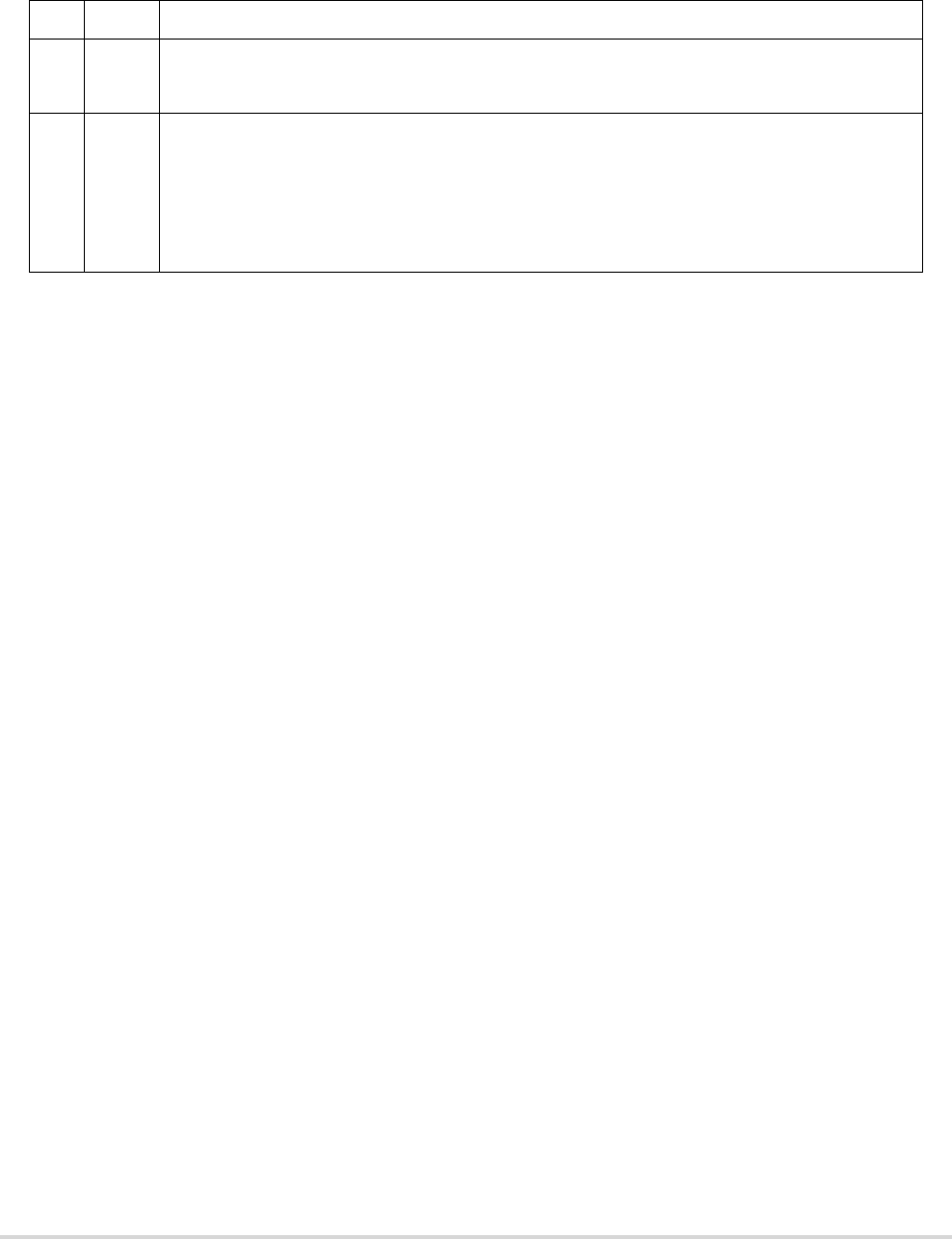

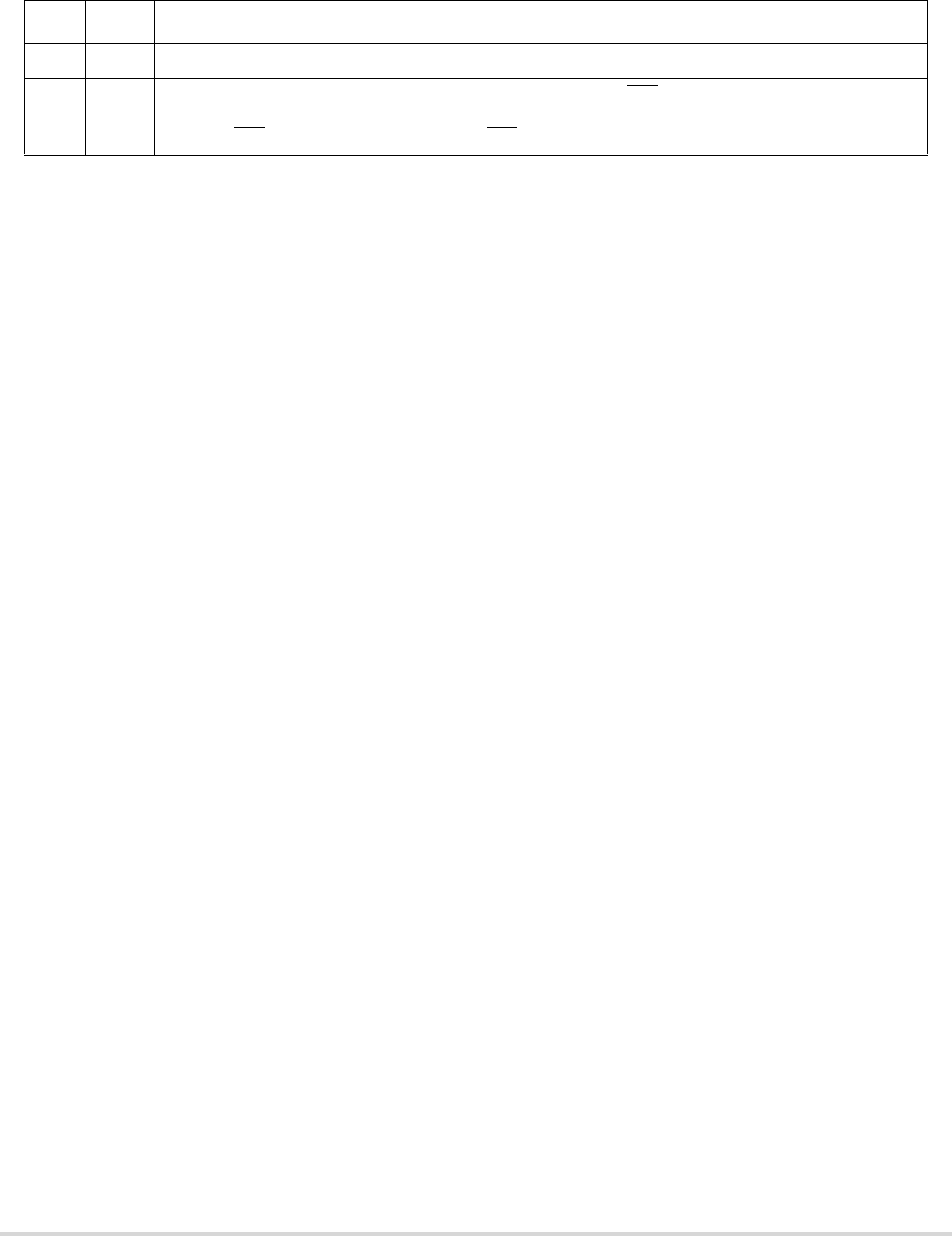

- 17.3 FEC Top-Level Functional Diagram

- 17.4 Functional Description

- 17.4.1 Initialization Sequence

- 17.4.2 User Initialization (Prior to Asserting ECR[ETHER_EN])

- 17.4.3 Microcontroller Initialization

- 17.4.4 User Initialization (After Asserting ECR[ETHER_EN])

- 17.4.5 Network Interface Options

- 17.4.6 FEC Frame Transmission

- 17.4.7 FEC Frame Reception

- 17.4.8 Ethernet Address Recognition

- 17.4.9 Hash Algorithm

- 17.4.10 Full Duplex Flow Control

- 17.4.11 Inter-Packet Gap (IPG) Time

- 17.4.12 Collision Handling

- 17.4.13 Internal and External Loopback

- 17.4.14 Ethernet Error-Handling Procedure

- 17.5 Programming Model

- 17.5.1 Top Level Module Memory Map

- 17.5.2 Detailed Memory Map (Control/Status Registers)

- 17.5.3 MIB Block Counters Memory Map

- 17.5.4 Registers

- 17.5.4.1 Ethernet Interrupt Event Register (EIR)

- 17.5.4.2 Interrupt Mask Register (EIMR)

- 17.5.4.3 Receive Descriptor Active Register (RDAR)

- 17.5.4.4 Transmit Descriptor Active Register (TDAR)

- 17.5.4.5 Ethernet Control Register (ECR)

- 17.5.4.6 MII Management Frame Register (MMFR)

- 17.5.4.7 MII Speed Control Register (MSCR)

- 17.5.4.8 MIB Control Register (MIBC)

- 17.5.4.9 Receive Control Register (RCR)

- 17.5.4.10 Transmit Control Register (TCR)

- 17.5.4.11 Physical Address Low Register (PALR)

- 17.5.4.12 Physical Address High Register (PAUR)

- 17.5.4.13 Opcode/Pause Duration Register (OPD)

- 17.5.4.14 Descriptor Individual Upper Address Register (IAUR)

- 17.5.4.15 Descriptor Individual Lower Address (IALR)

- 17.5.4.16 Descriptor Group Upper Address (GAUR)

- 17.5.4.17 Descriptor Group Lower Address (GALR)

- 17.5.4.18 FIFO Transmit FIFO Watermark Register (TFWR)

- 17.5.4.19 FIFO Receive Bound Register (FRBR)

- 17.5.4.20 FIFO Receive Start Register (FRSR)

- 17.5.4.21 Receive Descriptor Ring Start (ERDSR)

- 17.5.4.22 Transmit Buffer Descriptor Ring Start (ETSDR)

- 17.5.4.23 Receive Buffer Size Register (EMRBR)

- 17.6 Buffer Descriptors

- Chapter 18 Watchdog Timer Module

- Chapter 19 Programmable Interrupt Timer Modules (PIT0-PIT3)

- Chapter 20 General Purpose Timer Modules (GPTA and GPTB)

- 20.1 Features

- 20.2 Block Diagram

- 20.3 Low-Power Mode Operation

- 20.4 Signal Description

- 20.5 Memory Map and Registers

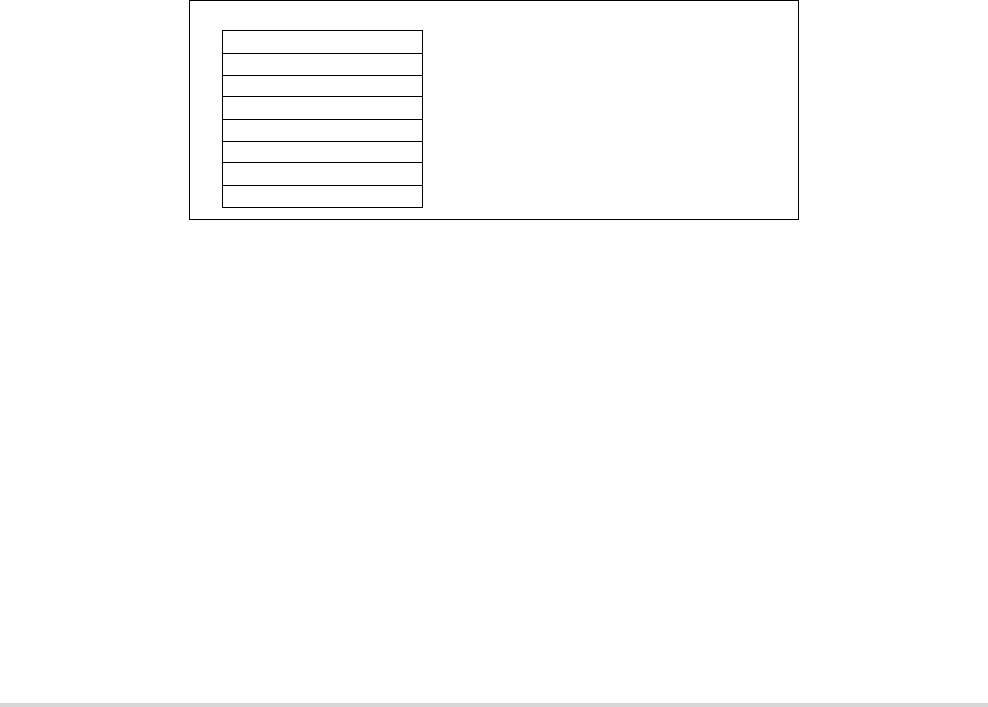

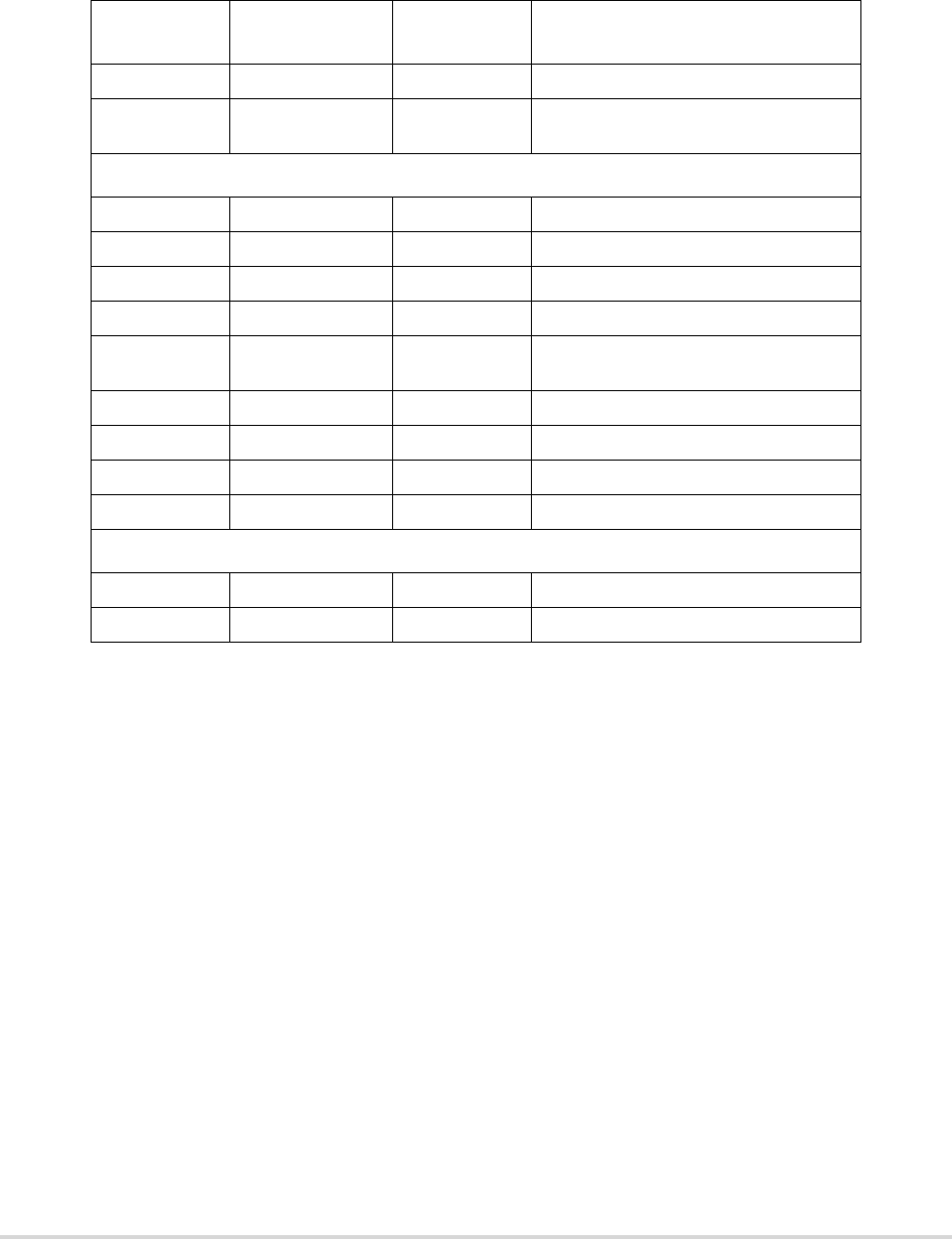

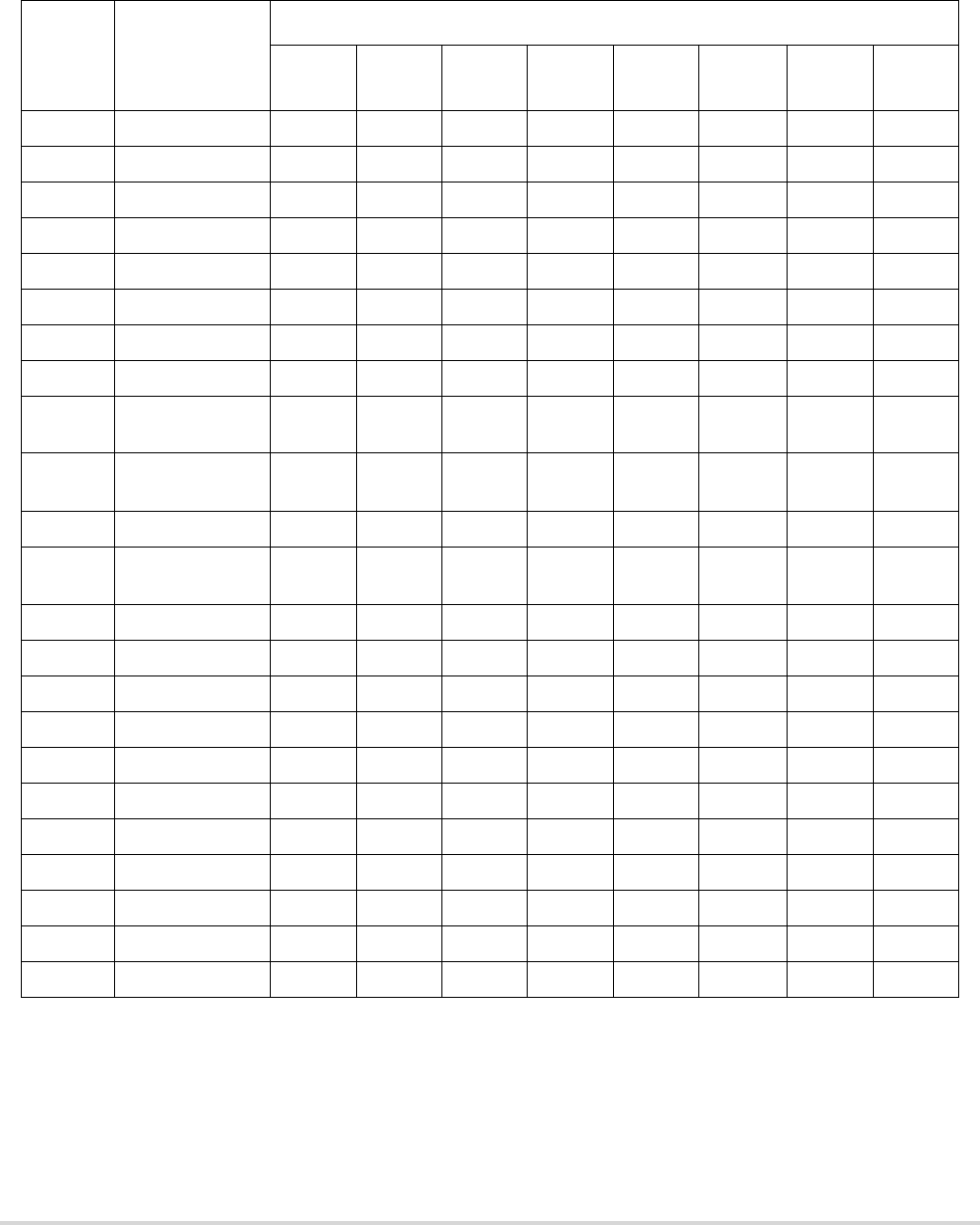

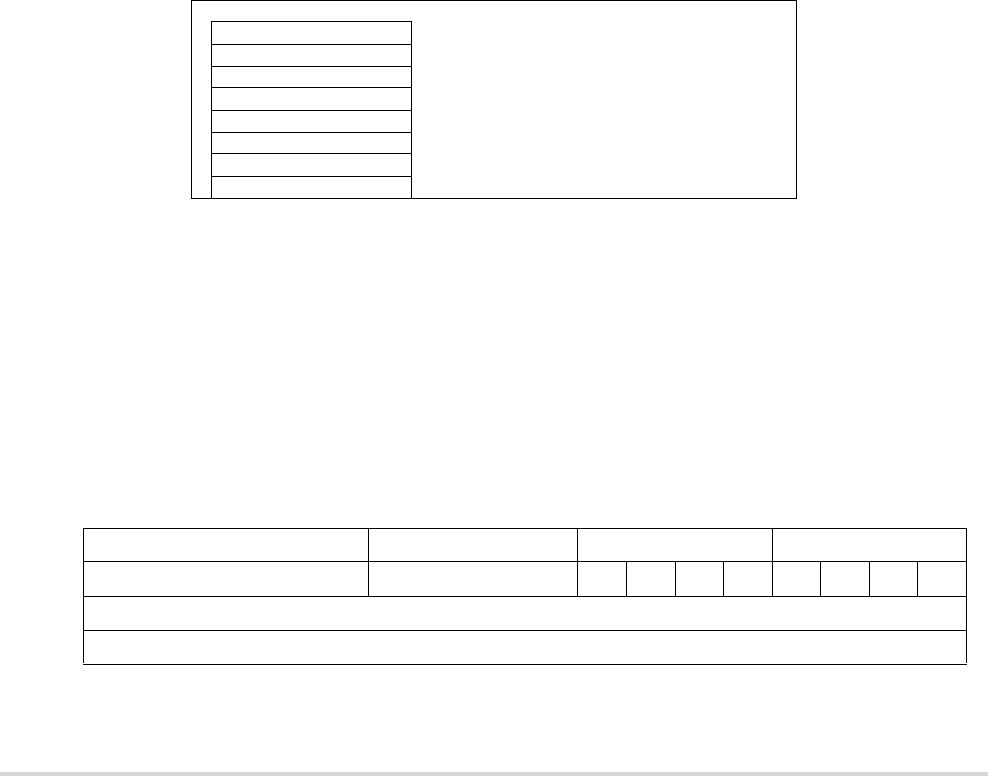

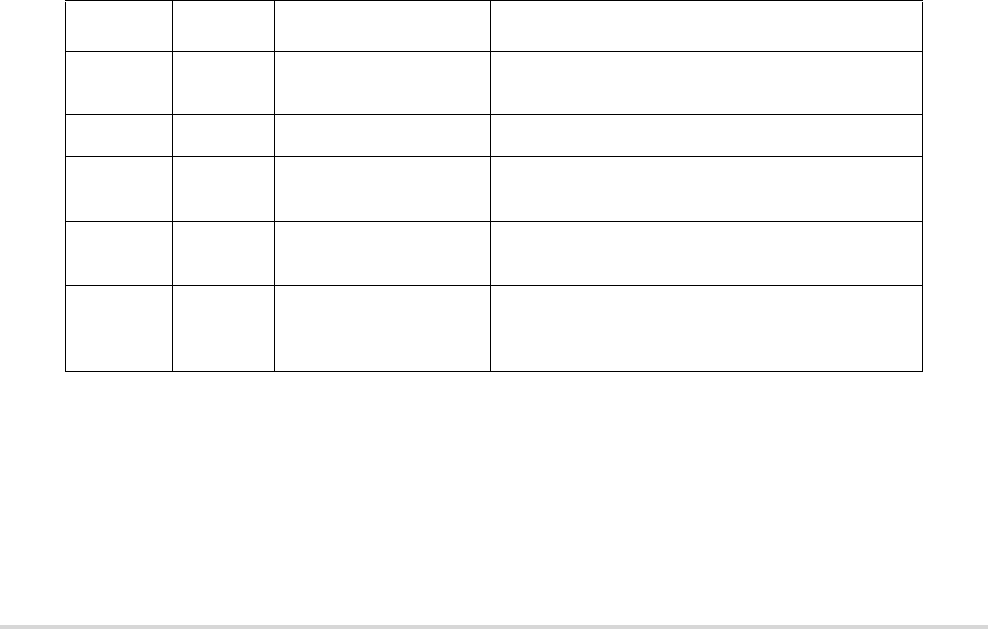

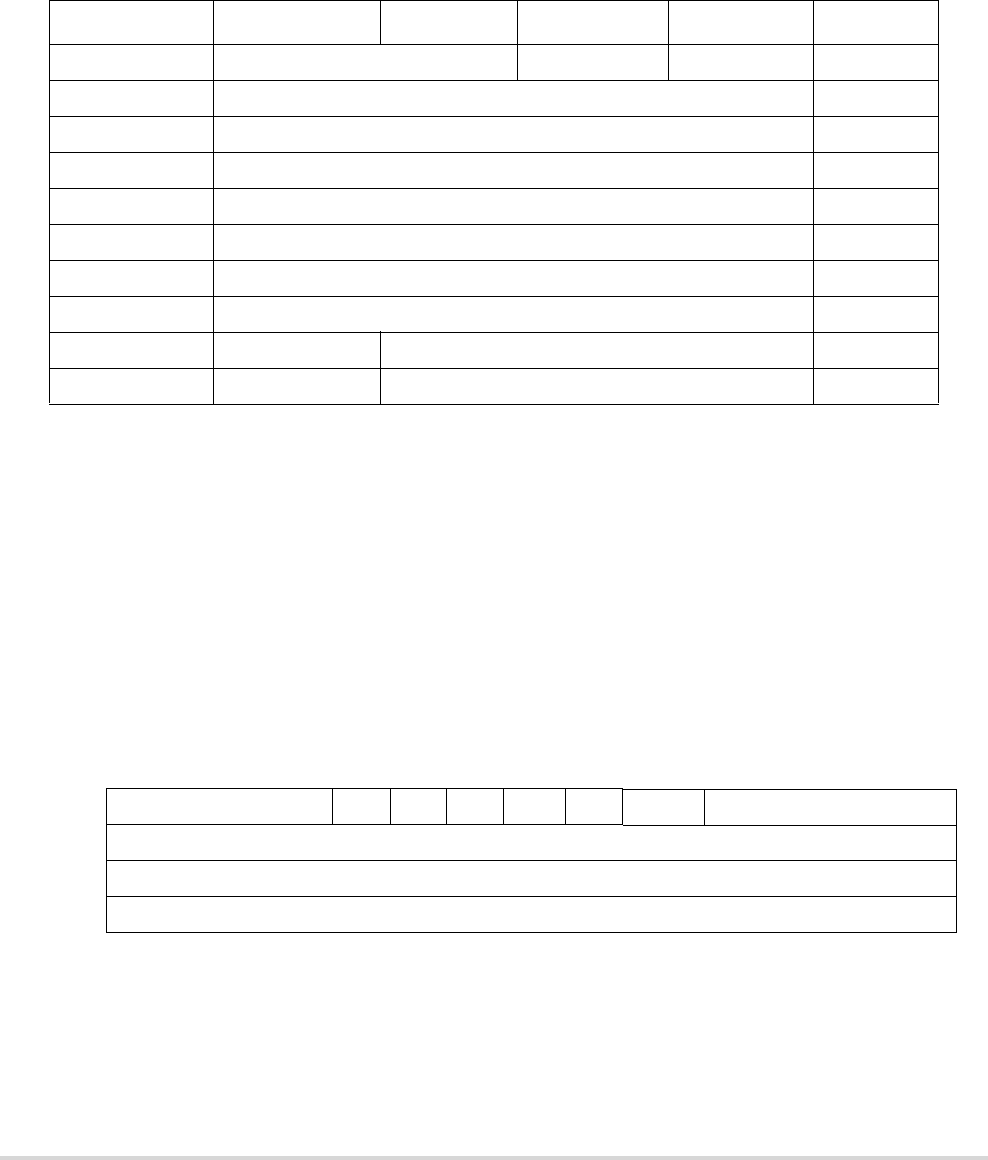

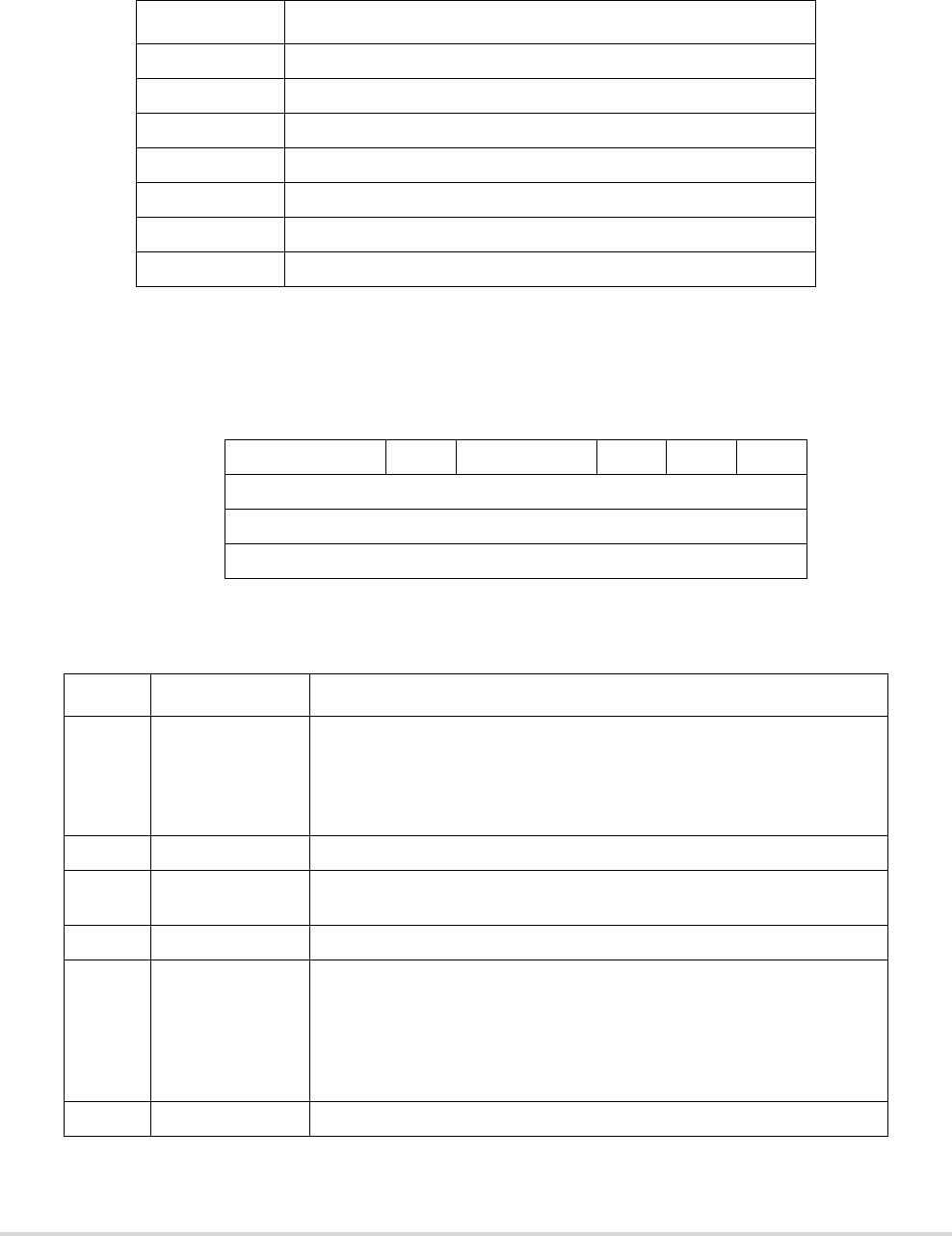

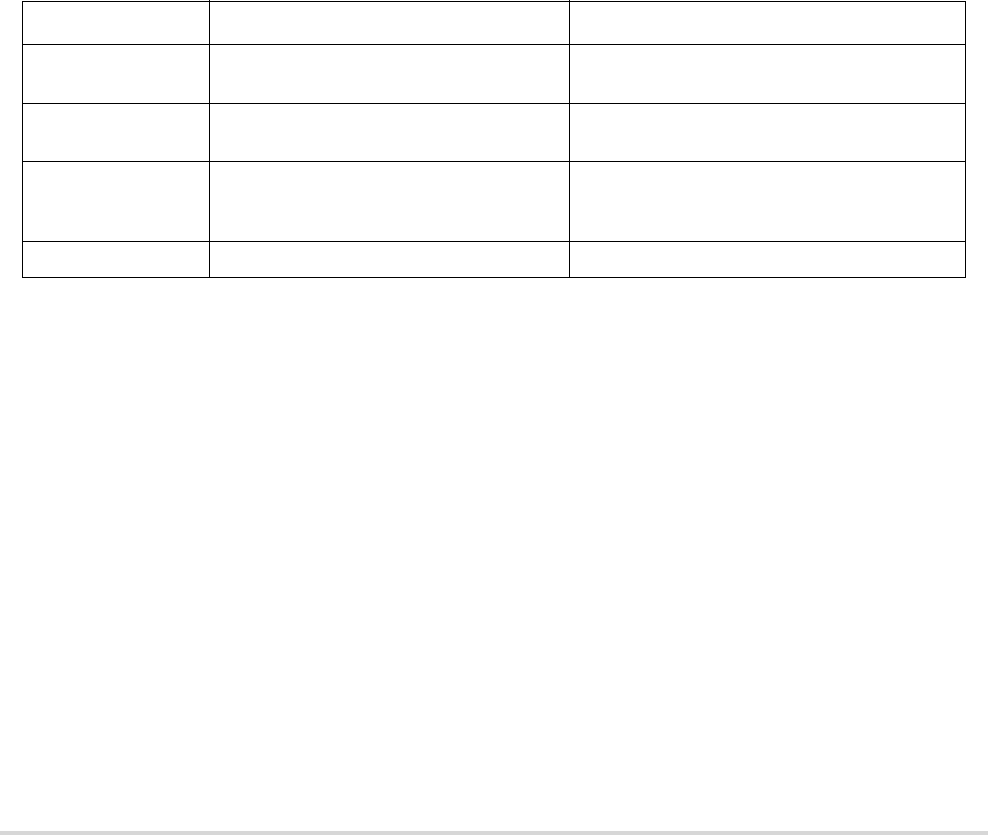

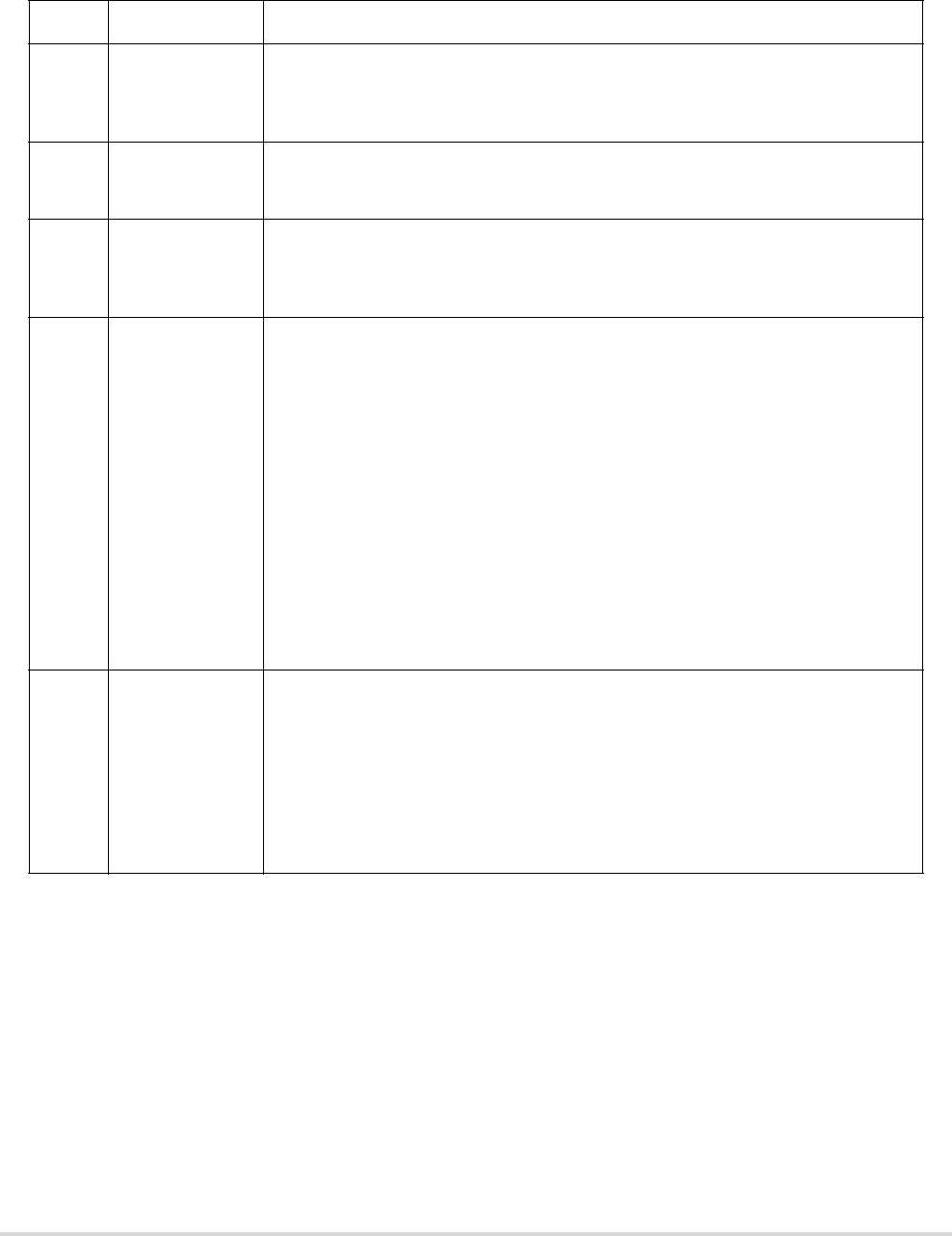

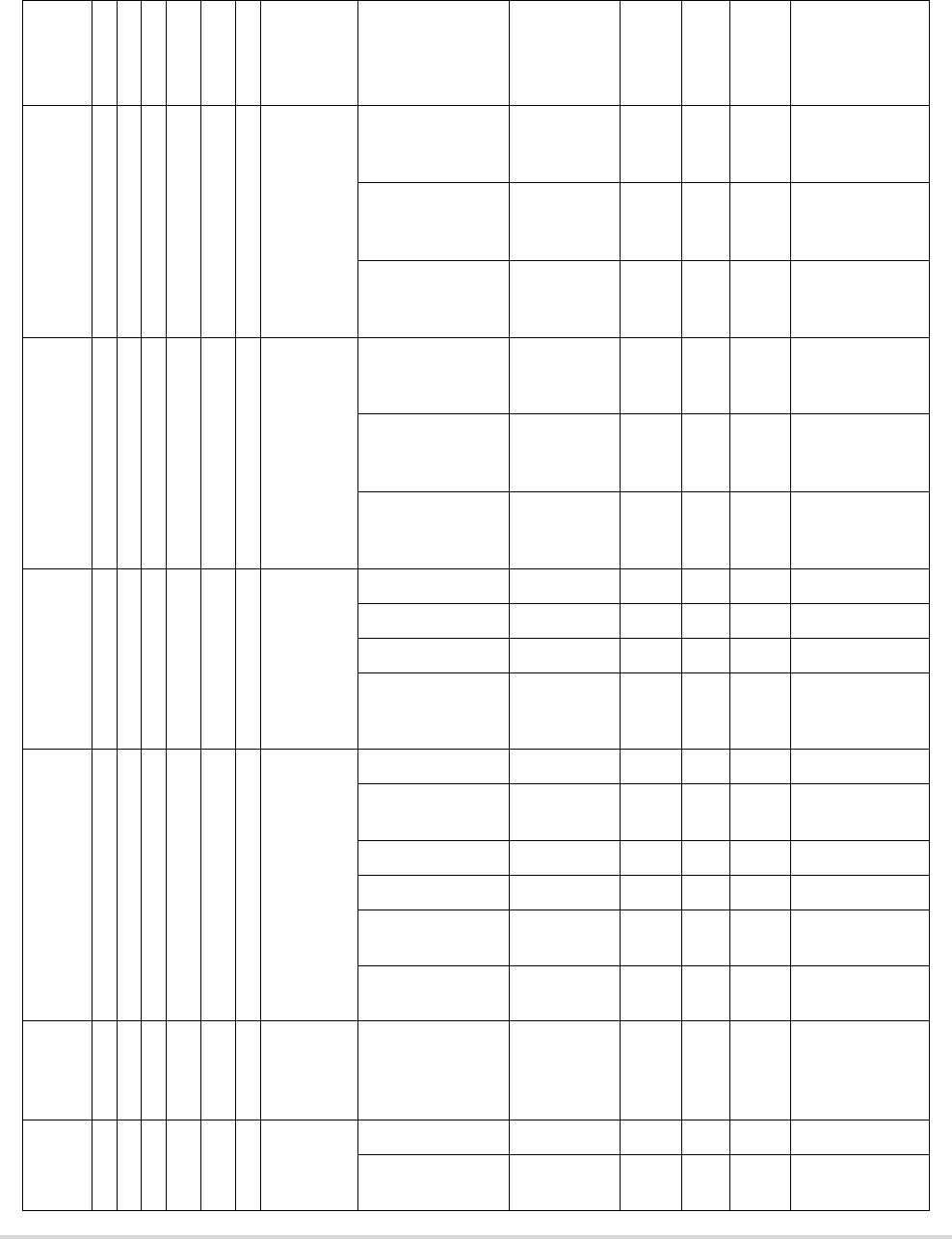

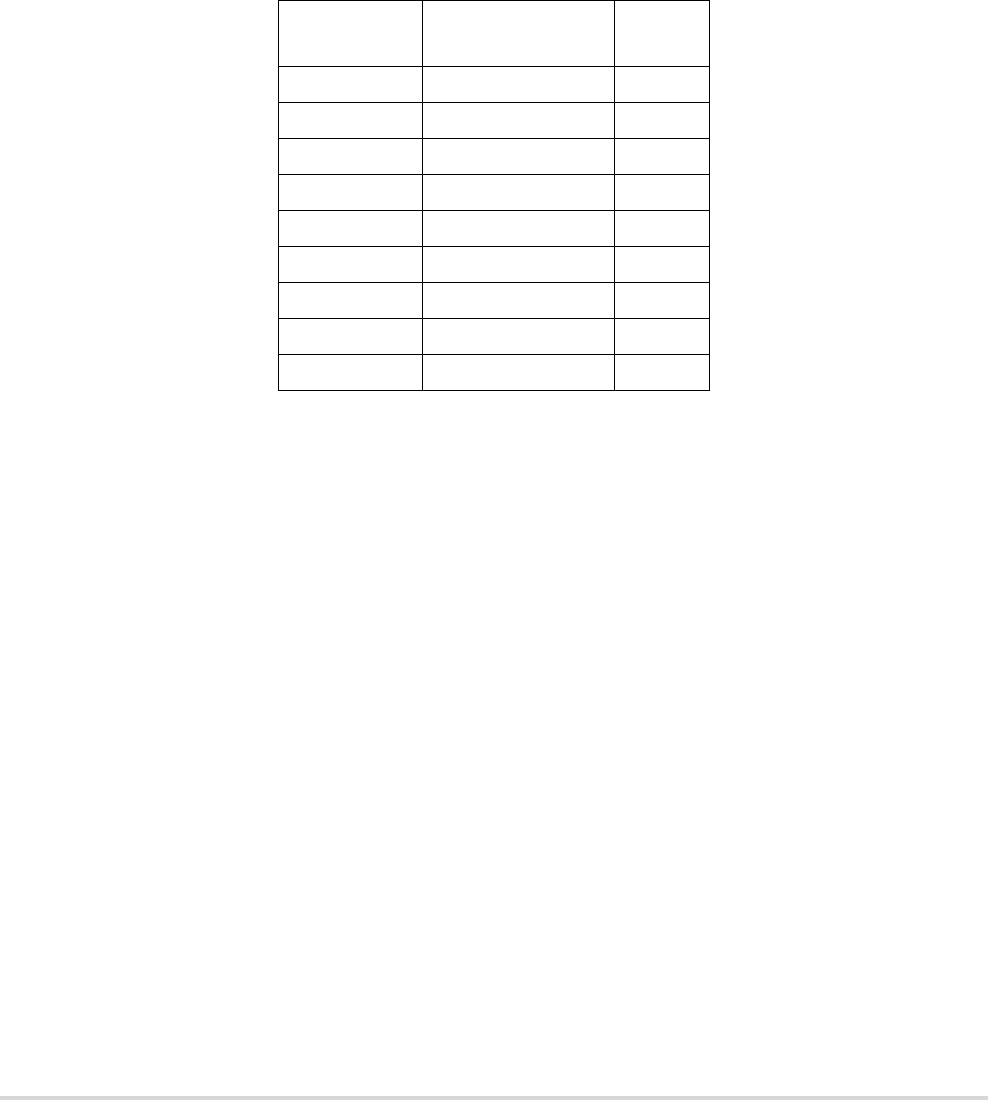

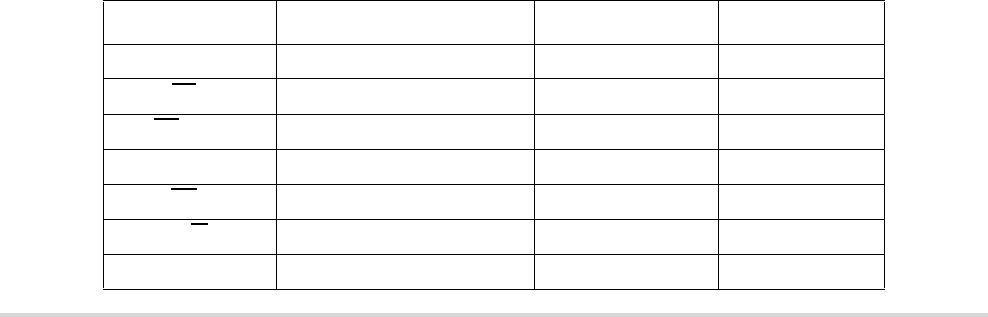

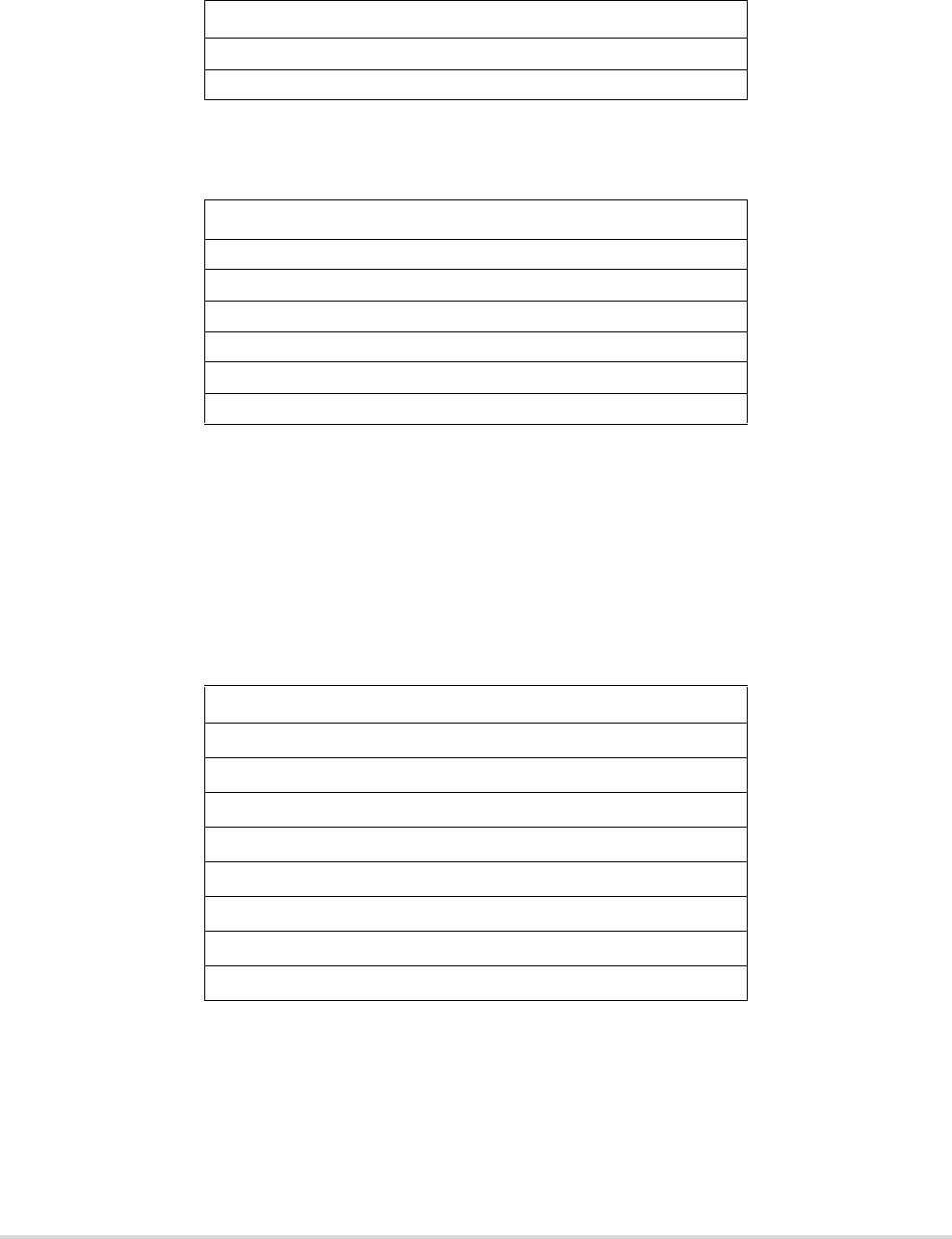

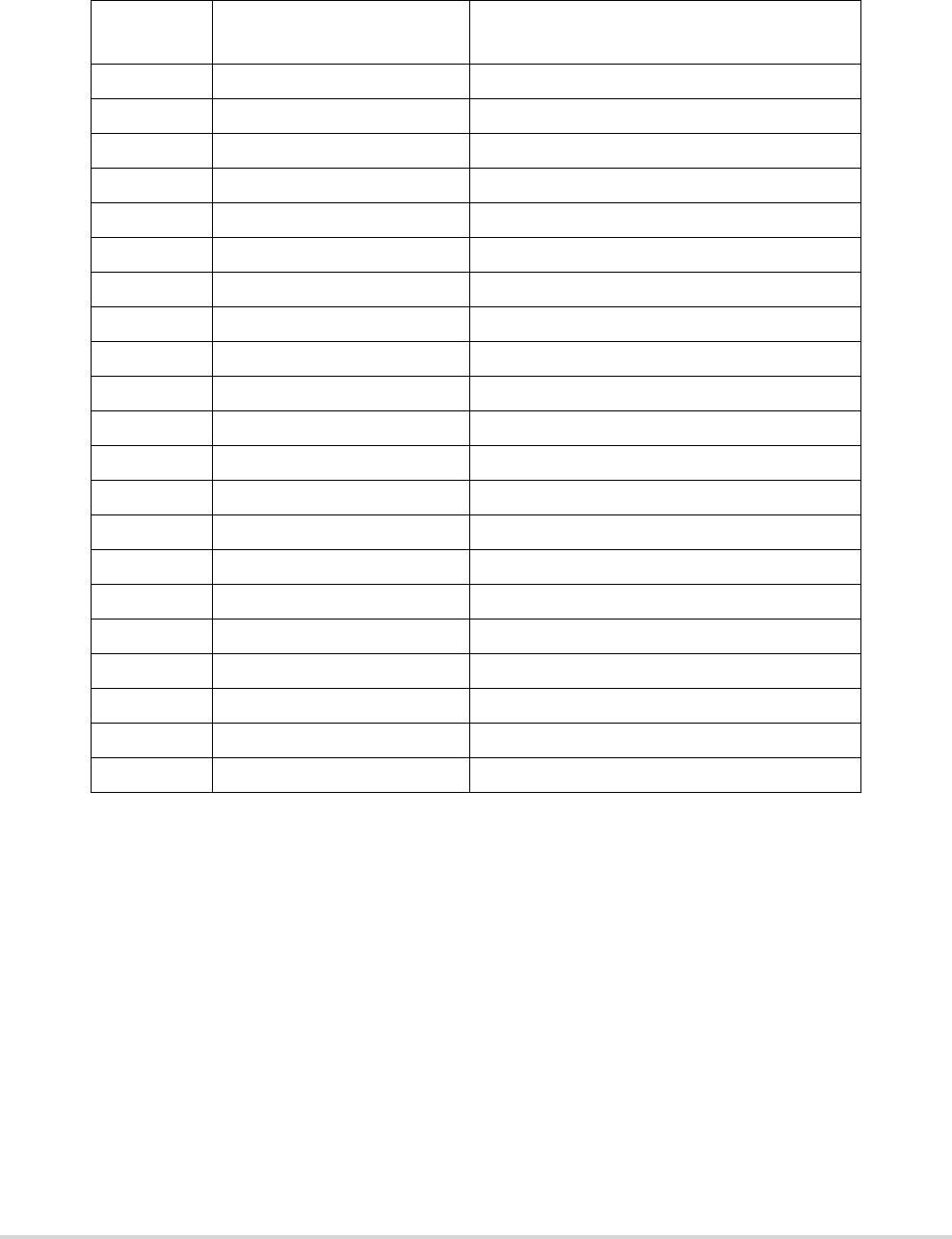

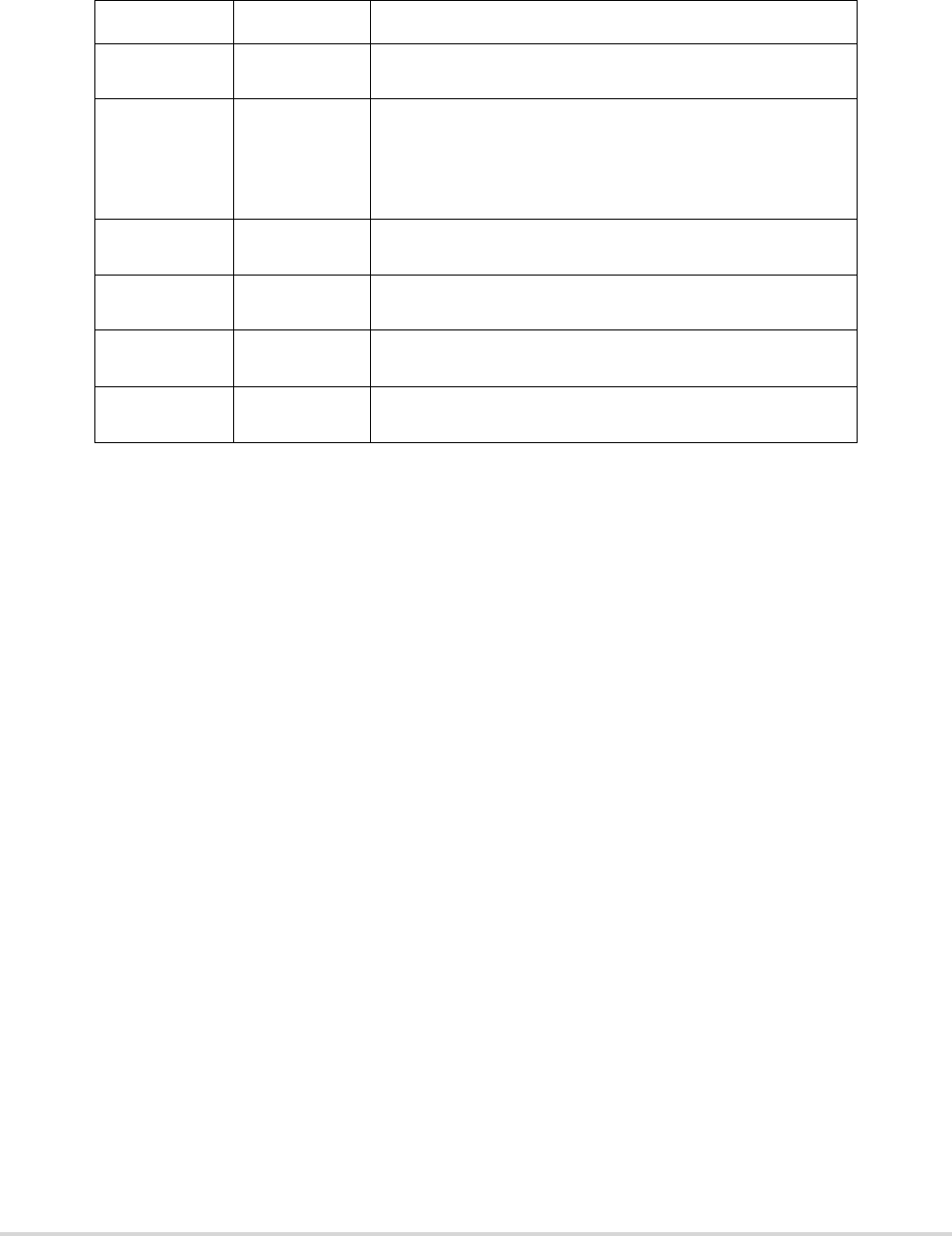

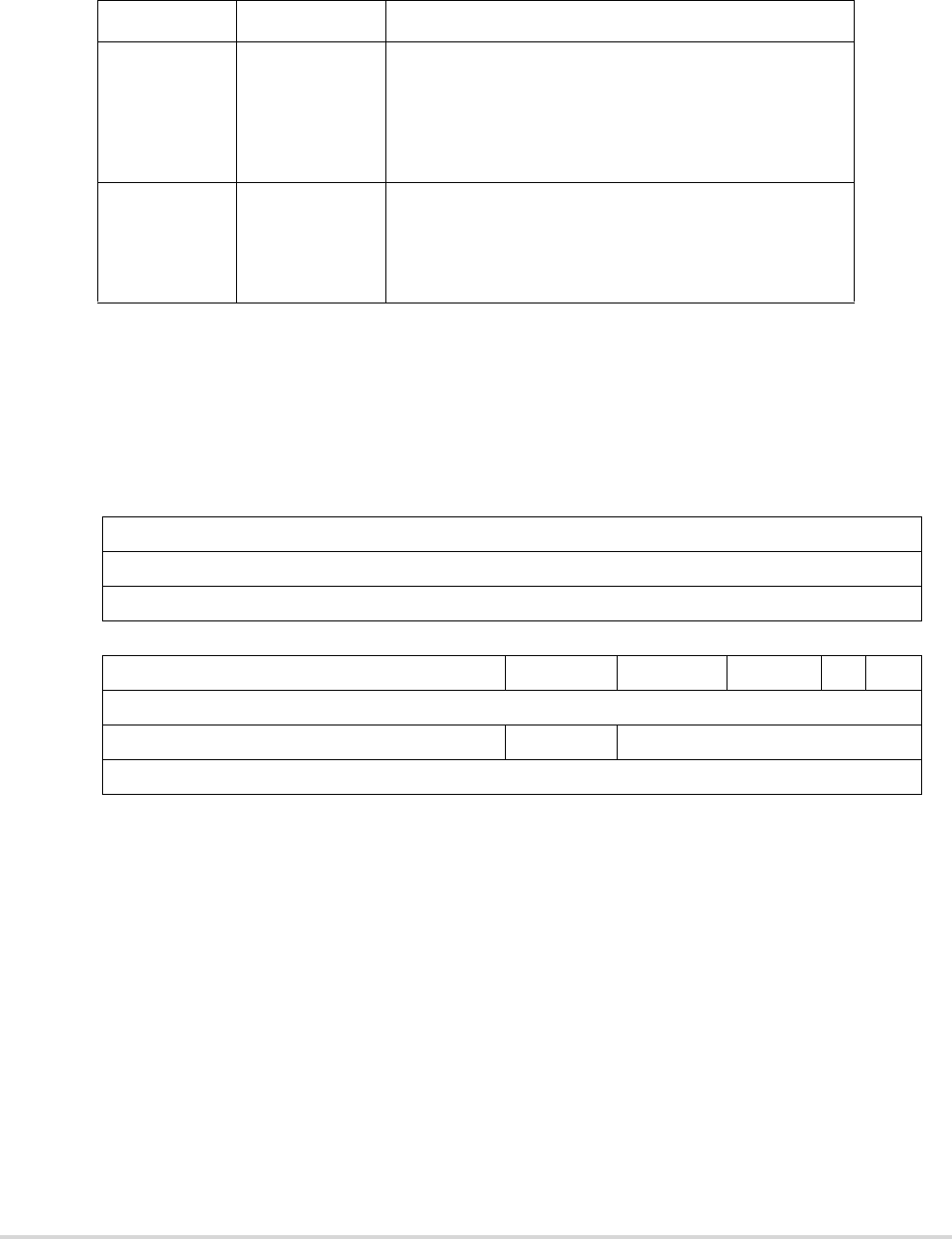

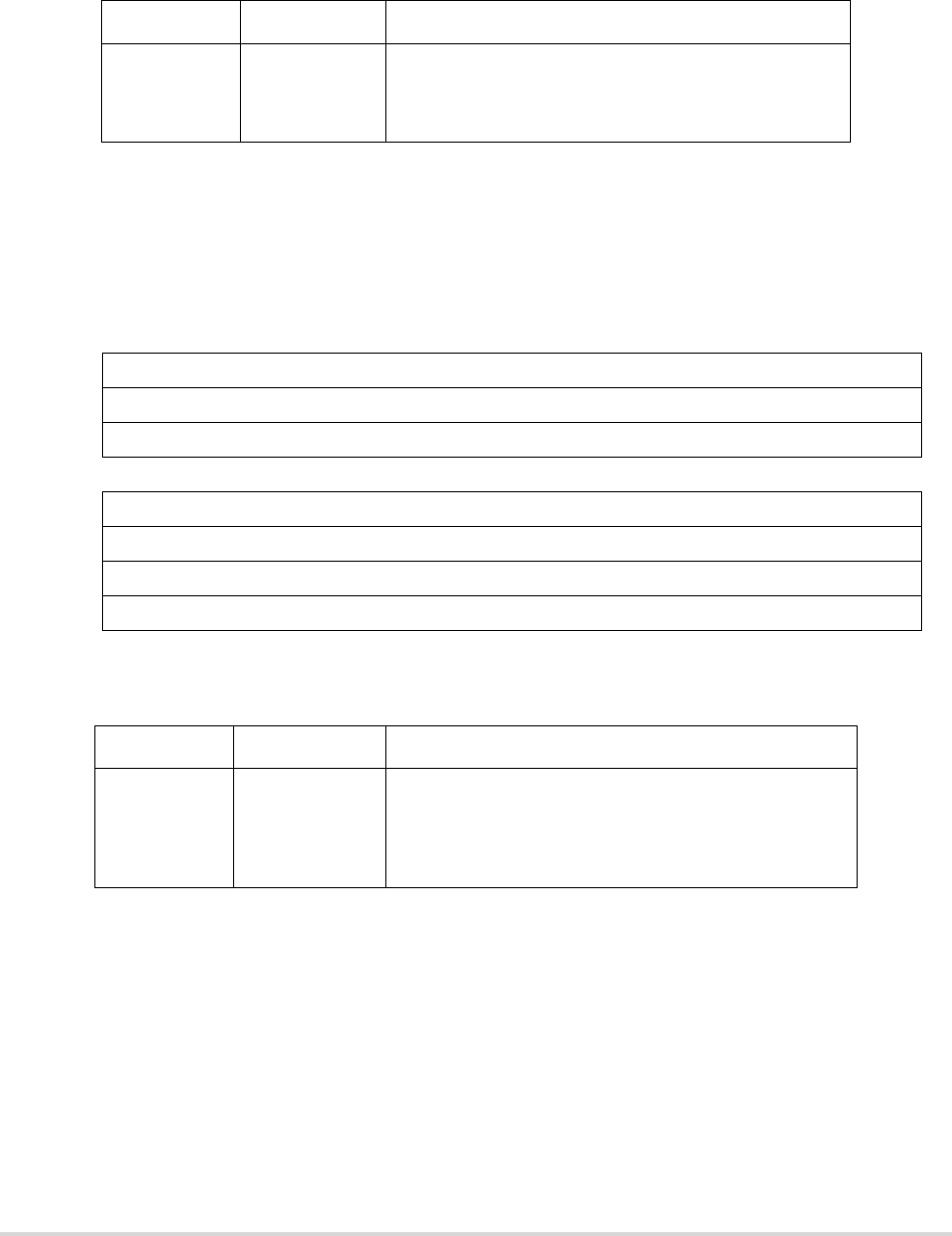

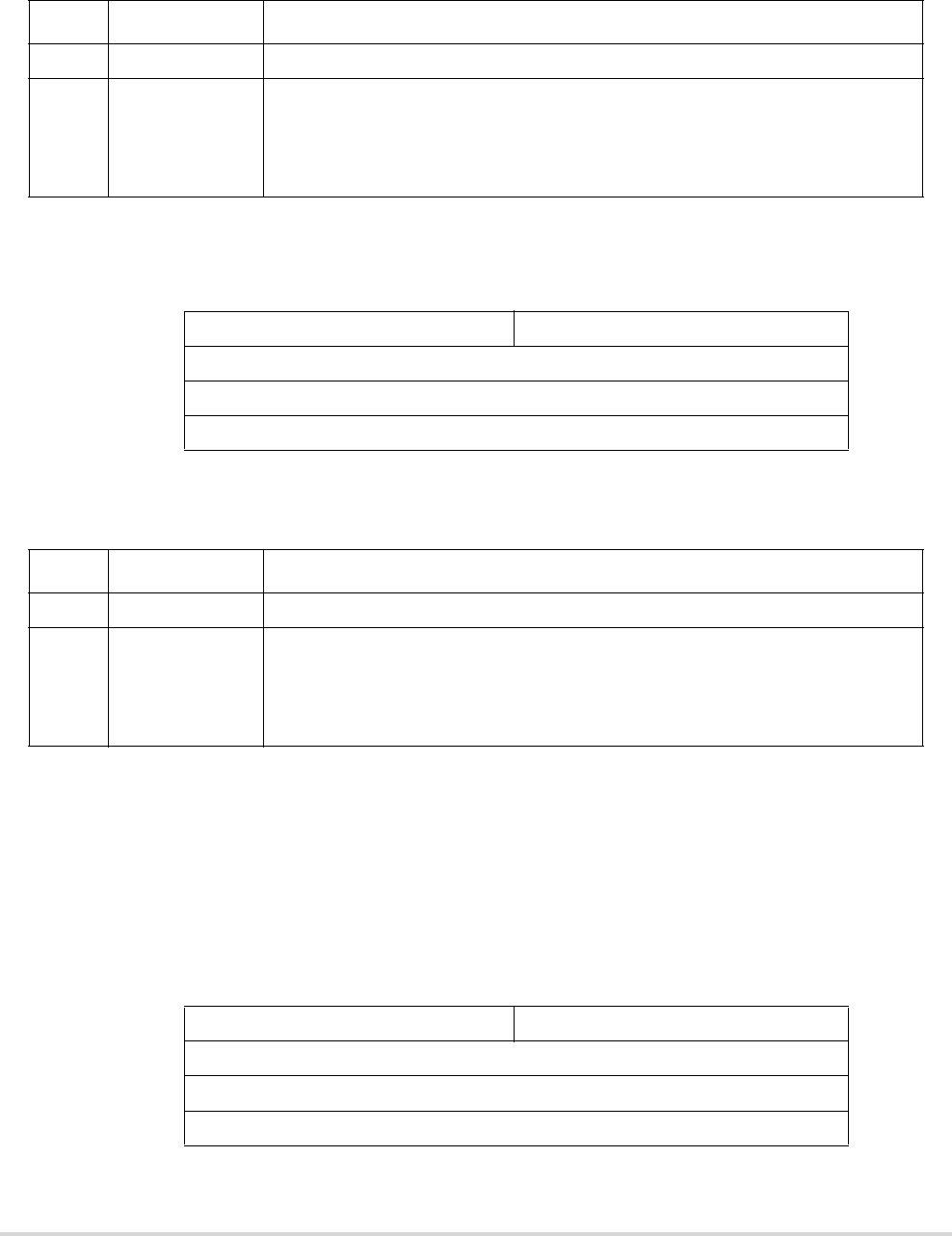

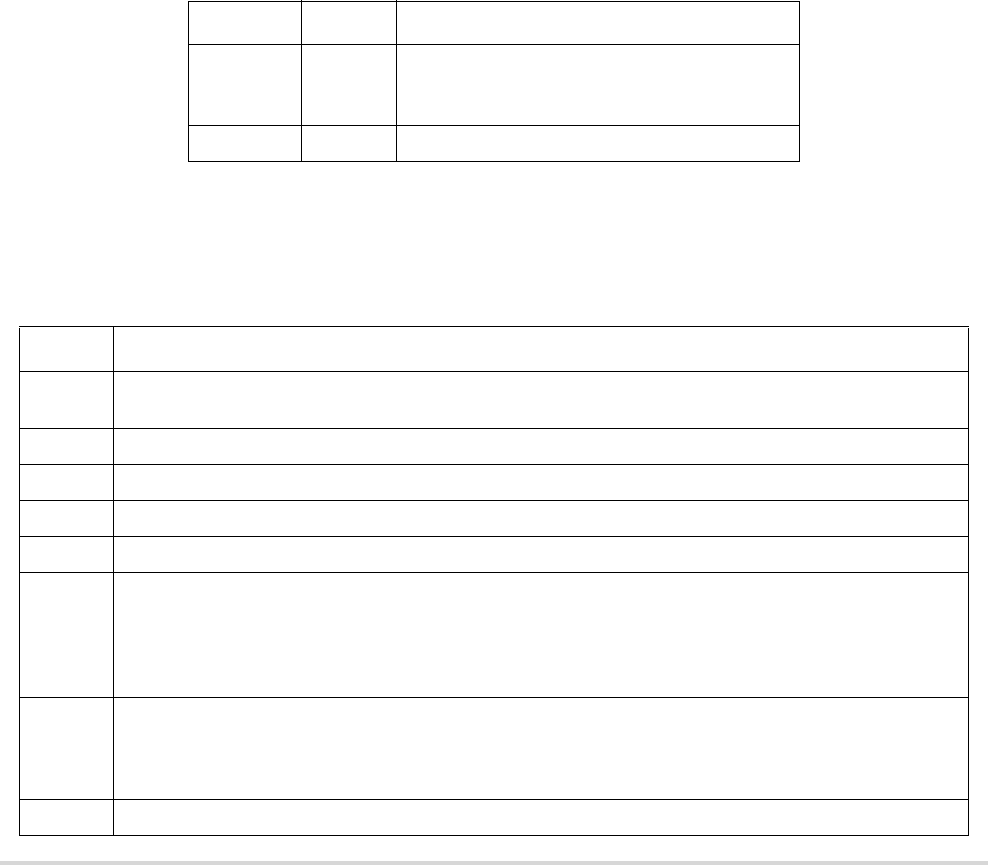

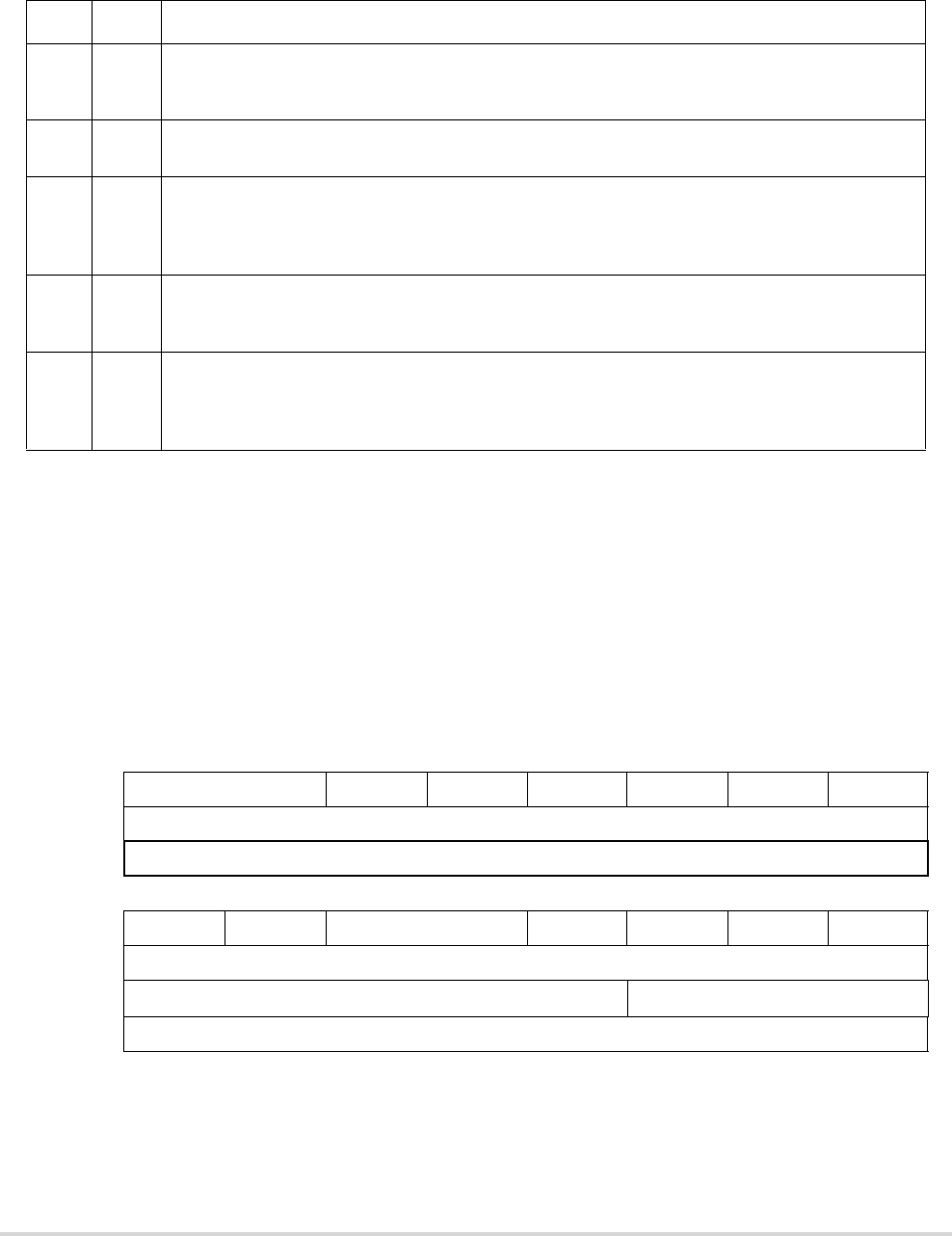

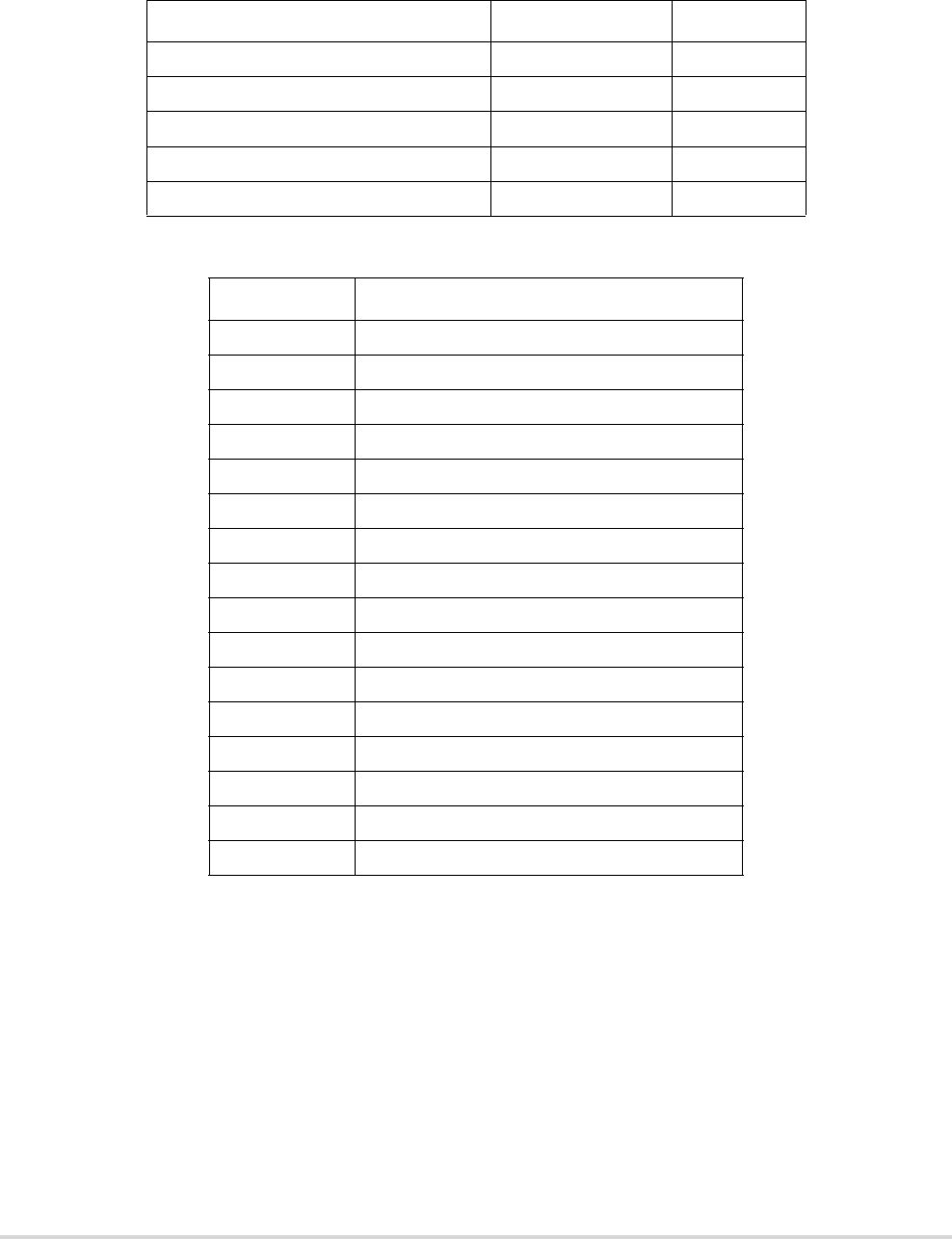

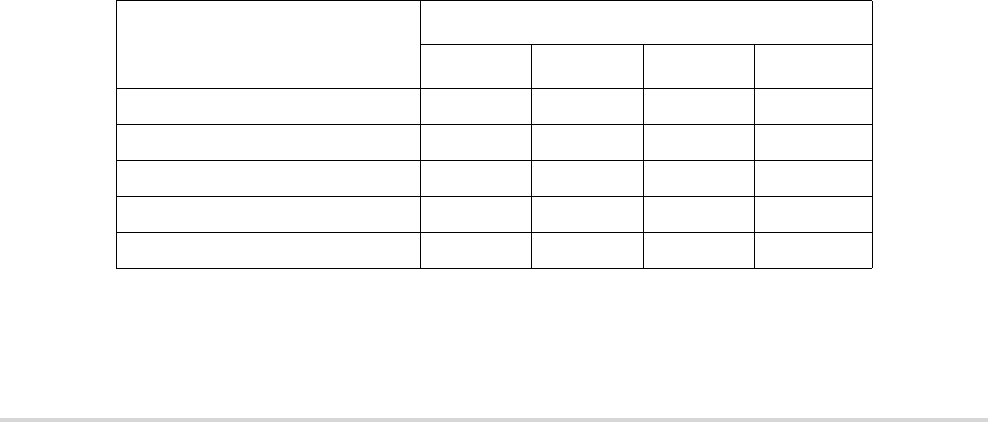

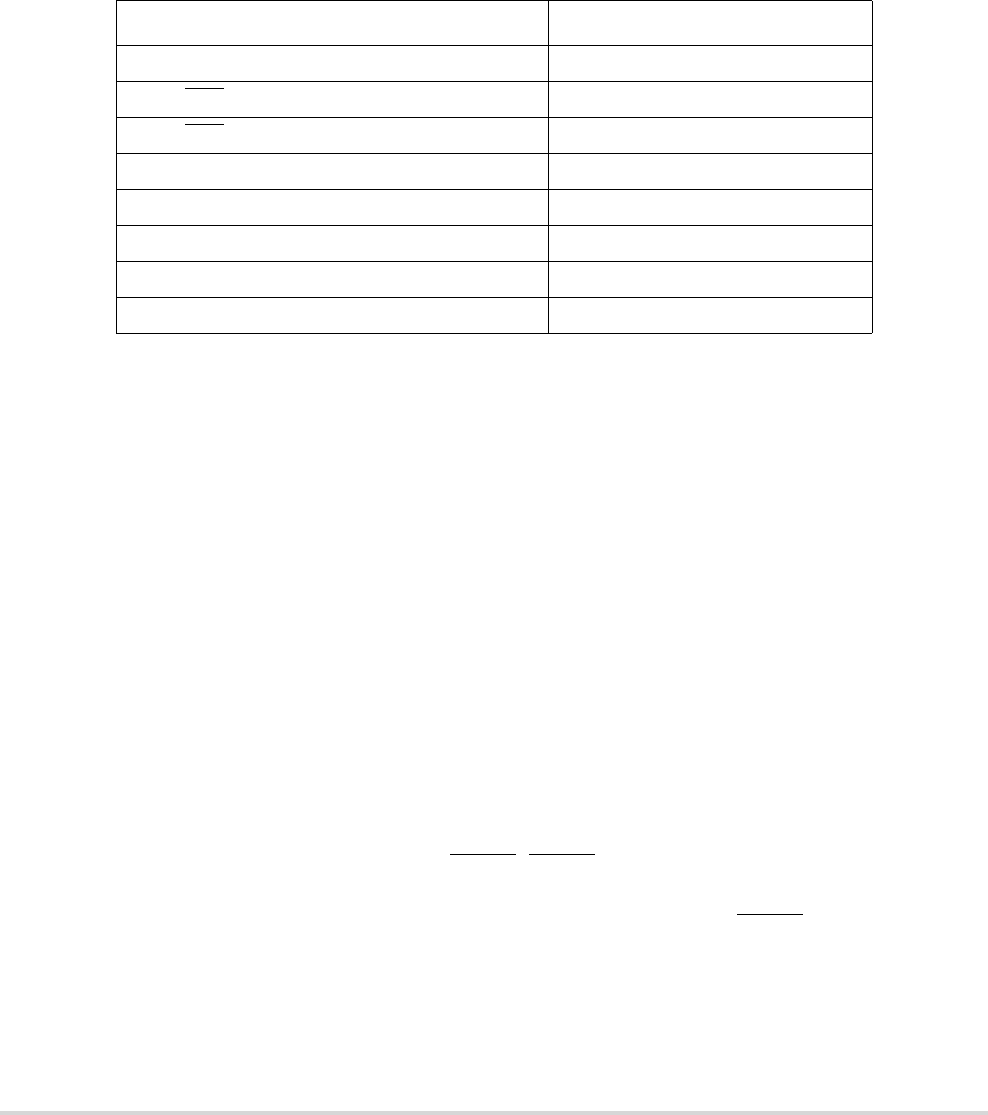

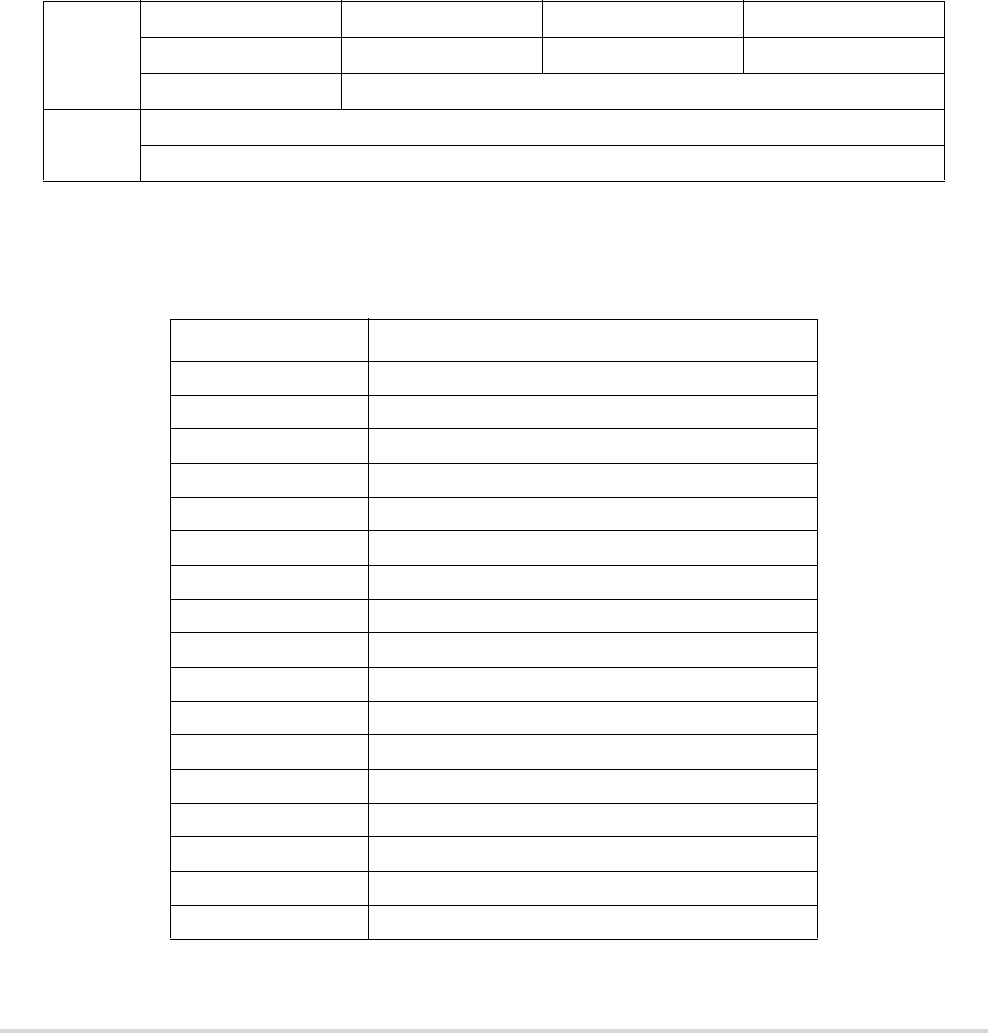

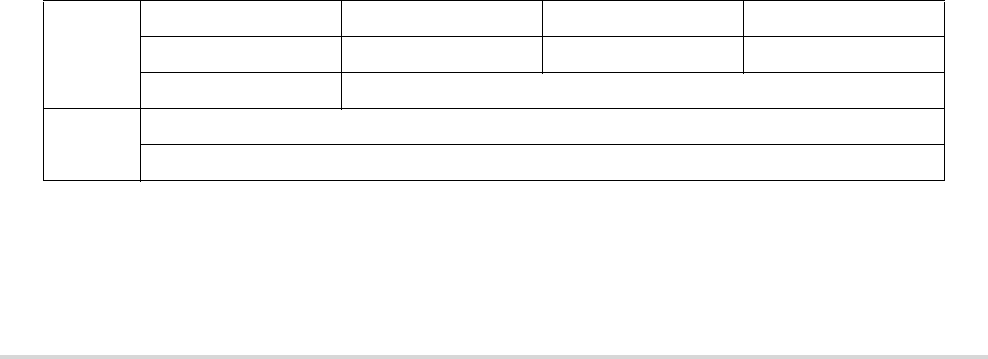

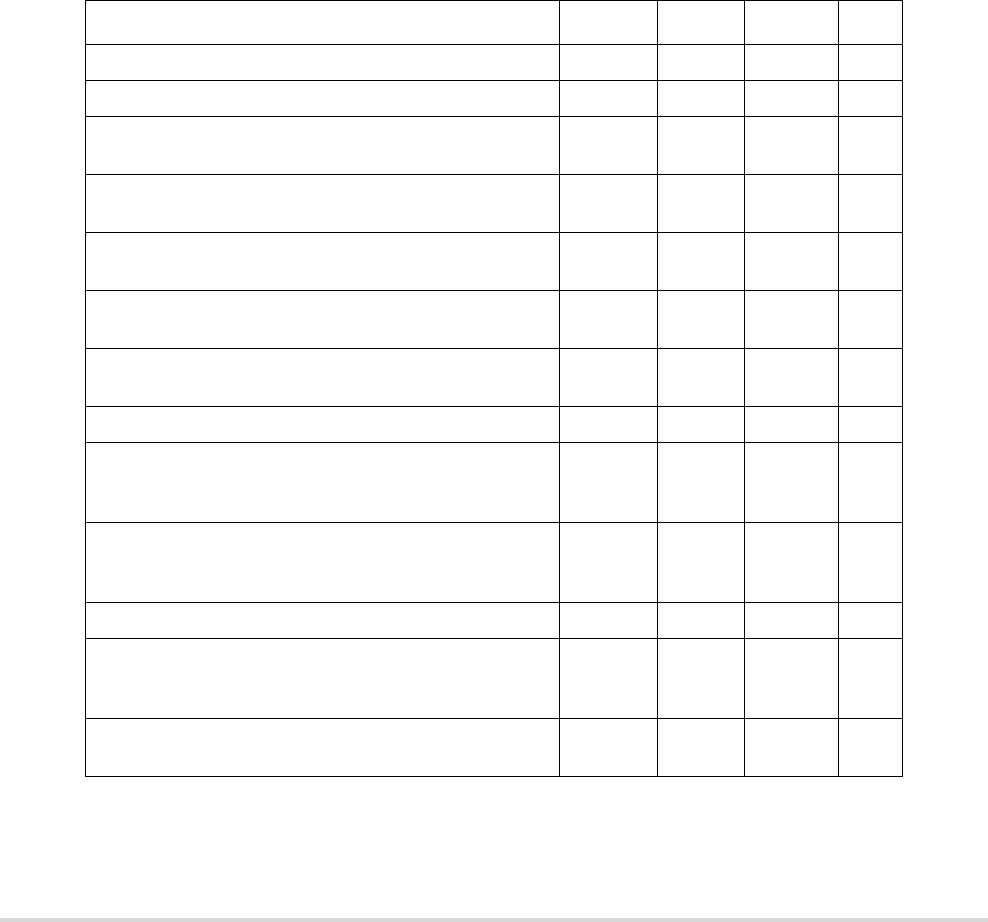

- Table 20-3. GPT Modules Memory Map (continued)

- 20.5.1 GPT Input Capture/Output Compare Select Register (GPTIOS)

- 20.5.2 GPT Compare Force Register (GPCFORC)

- 20.5.3 GPT Output Compare 3 Mask Register (GPTOC3M)

- 20.5.4 GPT Output Compare 3 Data Register (GPTOC3D)

- 20.5.5 GPT Counter Register (GPTCNT)

- 20.5.6 GPT System Control Register 1 (GPTSCR1)

- 20.5.7 GPT Toggle-On-Overflow Register (GPTTOV)

- 20.5.8 GPT Control Register 1 (GPTCTL1)

- 20.5.9 GPT Control Register 2 (GPTCTL2)

- 20.5.10 GPT Interrupt Enable Register (GPTIE)

- 20.5.11 GPT System Control Register 2 (GPTSCR2)

- 20.5.12 GPT Flag Register 1 (GPTFLG1)

- 20.5.13 GPT Flag Register 2 (GPTFLG2)

- 20.5.14 GPT Channel Registers (GPTCn)

- 20.5.15 Pulse Accumulator Control Register (GPTPACTL)

- 20.5.16 Pulse Accumulator Flag Register (GPTPAFLG)

- 20.5.17 Pulse Accumulator Counter Register (GPTPACNT)

- 20.5.18 GPT Port Data Register (GPTPORT)

- 20.5.19 GPT Port Data Direction Register (GPTDDR)

- 20.6 Functional Description

- 20.7 Reset

- 20.8 Interrupts

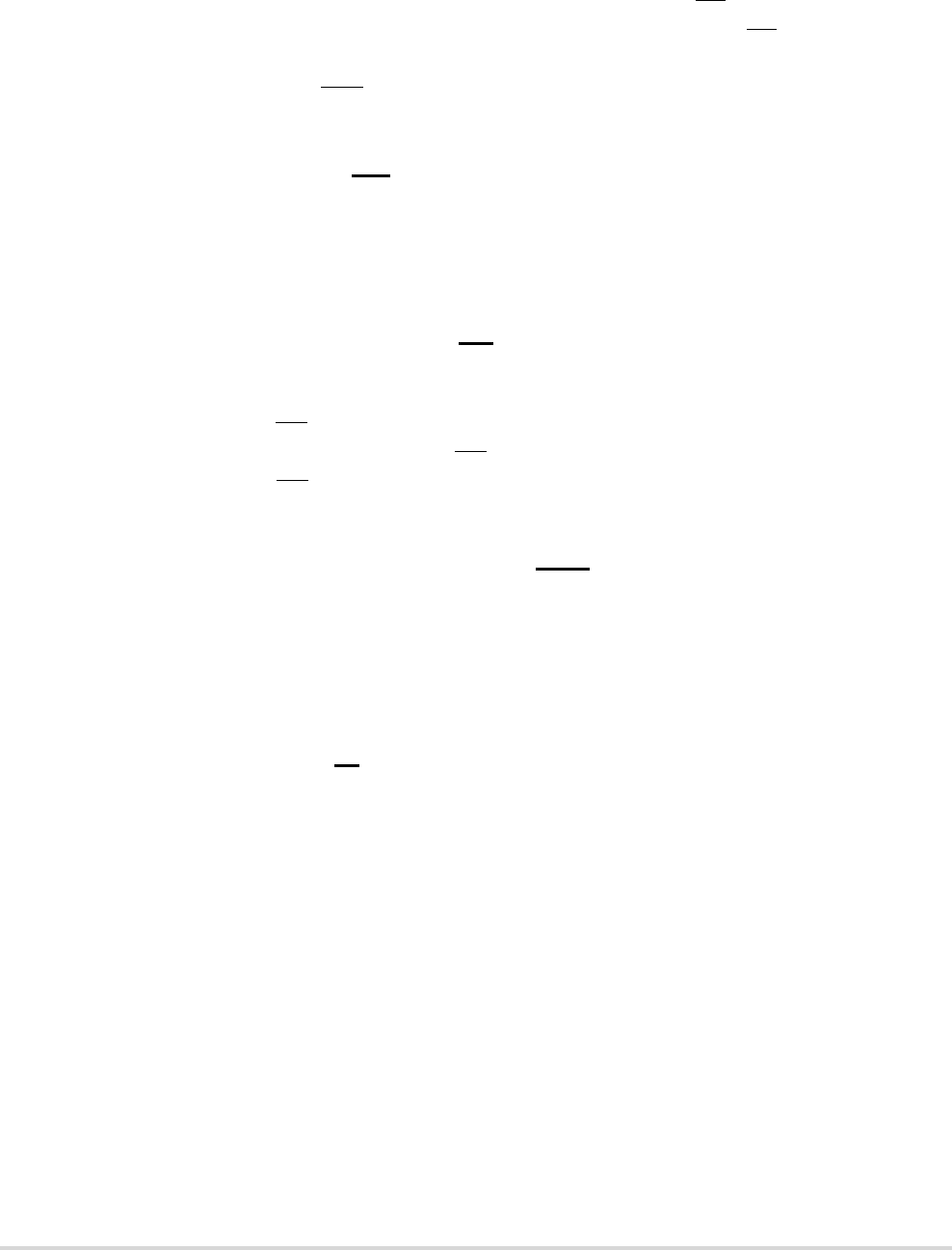

- Chapter 21 DMA Timers (DTIM0-DTIM3)

- 21.1 Overview

- 21.2 DMA Timer Programming Model

- 21.2.1 Prescaler

- 21.2.2 Capture Mode

- 21.2.3 Reference Compare

- 21.2.4 Output Mode

- 21.2.5 Memory Map

- 21.2.6 DMA Timer Mode Registers (DTMRn)

- 21.2.7 DMA Timer Extended Mode Registers (DTXMRn)

- 21.2.8 DMA Timer Event Registers (DTERn)

- 21.2.9 DMA Timer Reference Registers (DTRRn)

- 21.2.10 DMA Timer Capture Registers (DTCRn)

- 21.2.11 DMA Timer Counters (DTCNn)

- 21.3 Using the DMA Timer Modules

- Chapter 22 Queued Serial Peripheral Interface (QSPI) Module

- 22.1 Overview

- 22.2 Features

- 22.3 Module Description

- 22.4 Operation

- 22.5 Programming Model

- Chapter 23 UART Modules

- 23.1 Overview

- 23.2 Serial Module Overview

- 23.3 Register Descriptions

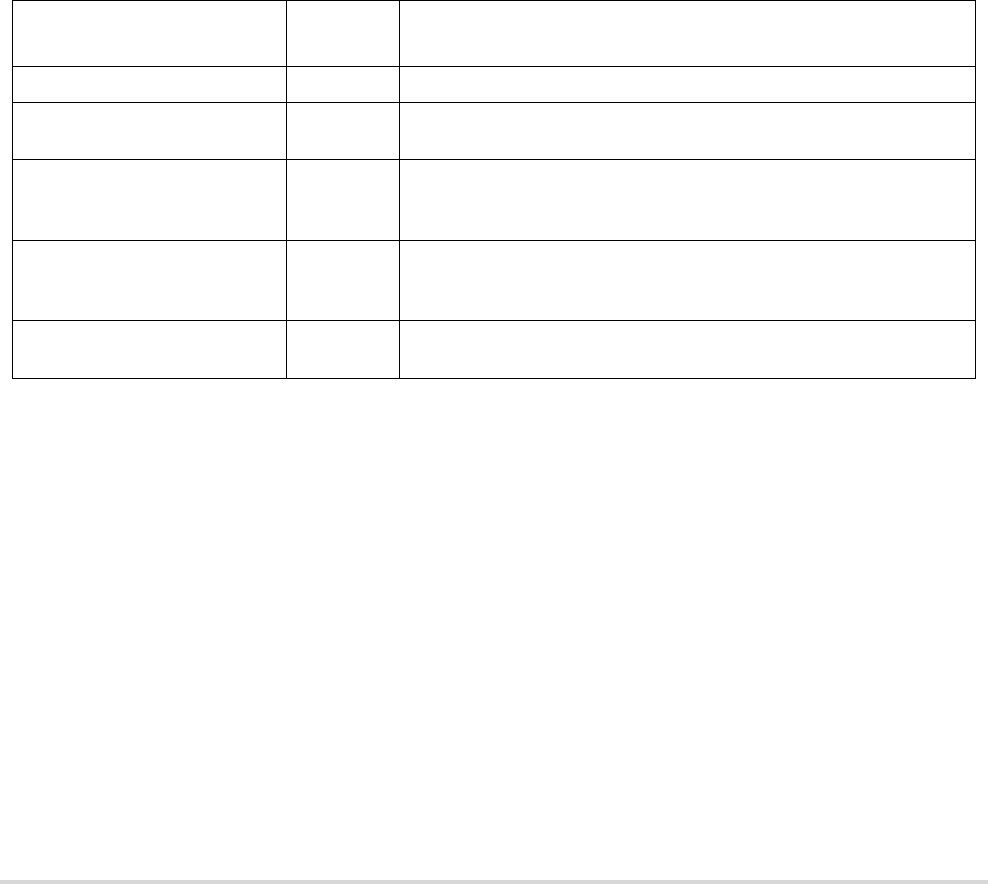

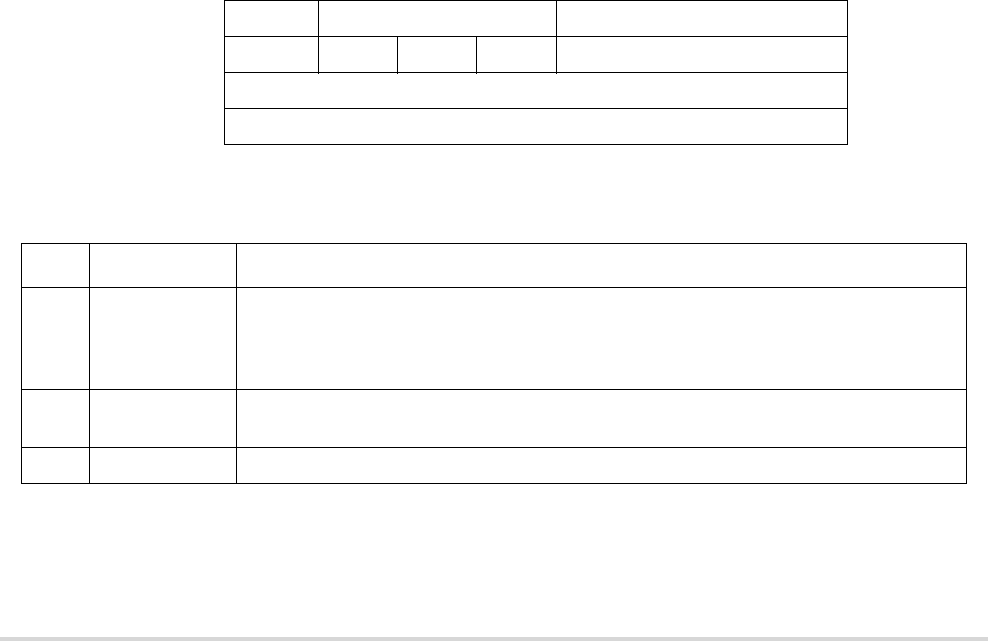

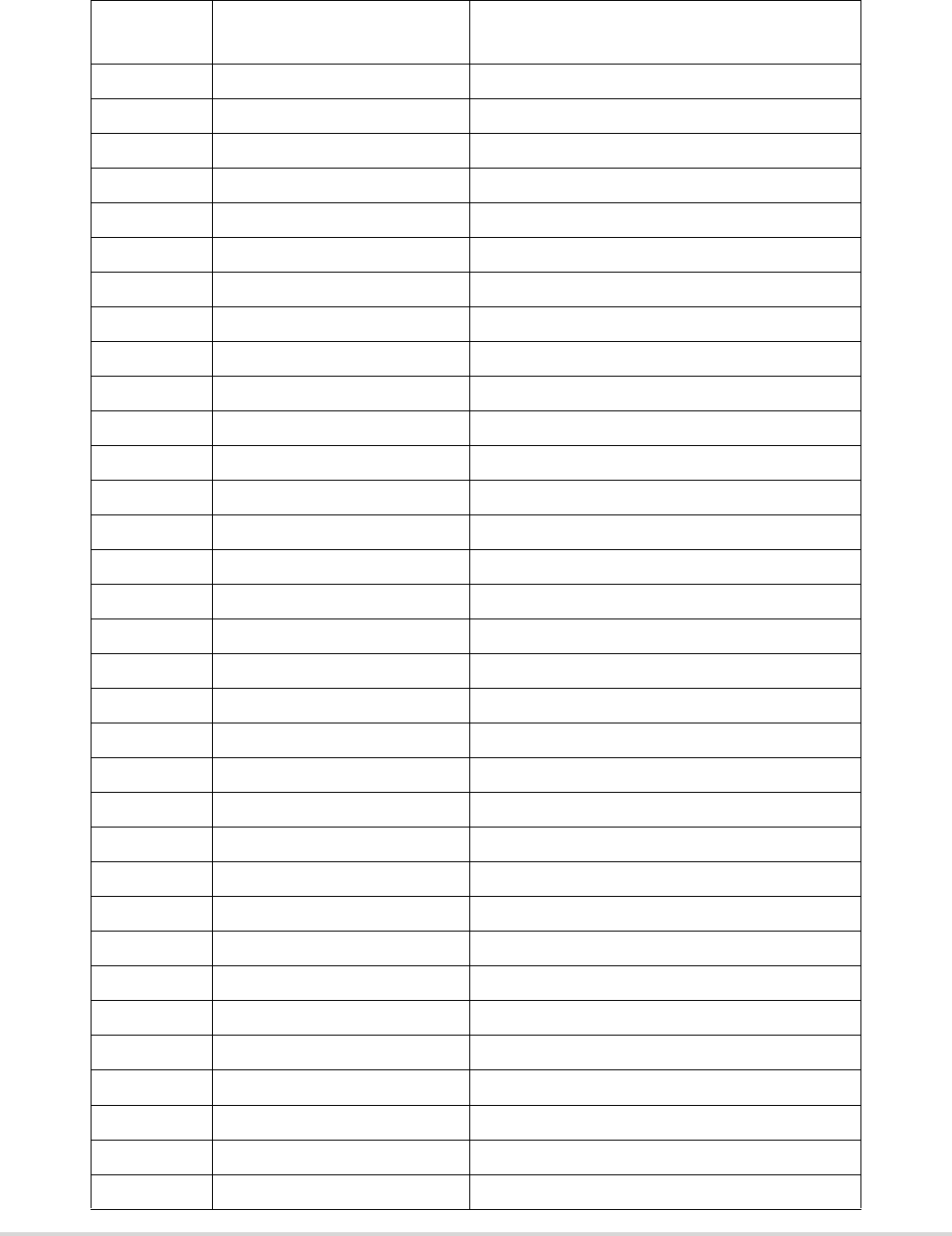

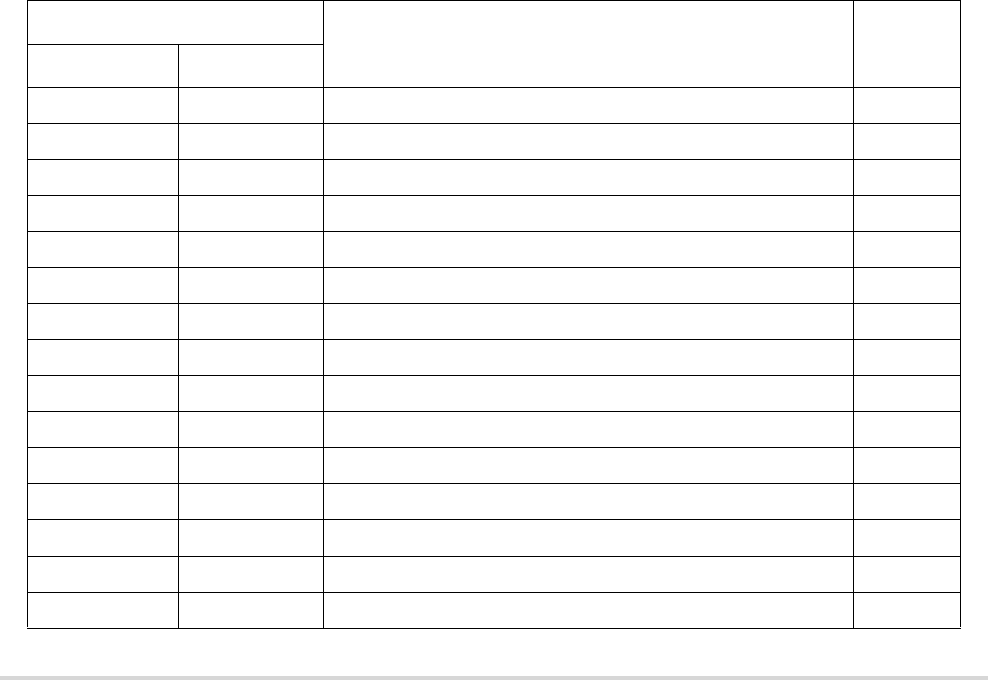

- Table 23-1. UART Module Memory Map (continued)

- 23.3.1 UART Mode Registers 1 (UMR1n)

- 23.3.2 UART Mode Register 2 (UMR2n)

- 23.3.3 UART Status Registers (USRn)

- 23.3.4 UART Clock Select Registers (UCSRn)

- 23.3.5 UART Command Registers (UCRn)

- 23.3.6 UART Receive Buffers (URBn)

- 23.3.7 UART Transmit Buffers (UTBn)

- 23.3.8 UART Input Port Change Registers (UIPCRn)

- 23.3.9 UART Auxiliary Control Register (UACRn)

- 23.3.10 UART Interrupt Status/Mask Registers (UISRn/UIMRn)

- 23.3.11 UART Baud Rate Generator Registers (UBG1n/UBG2n)

- 23.3.12 UART Input Port Register (UIPn)

- 23.3.13 UART Output Port Command Registers (UOP1n/UOP0n)

- 23.4 UART Module Signal Definitions

- 23.5 Operation

- Chapter 24 I2C Interface

- 24.1 Overview

- 24.2 Interface Features

- 24.3 I2C System Configuration

- 24.4 I2C Protocol

- 24.5 Programming Model

- 24.6 I2C Programming Examples

- Chapter 25 FlexCAN

- 25.1 Features

- 25.2 The CAN System

- 25.3 Message Buffers

- 25.3.1 Message Buffer Structure

- 25.3.2 Message Buffer Memory Map

- 25.4 Functional Overview

- 25.5 Programmer’s Model

- 25.5.1 CAN Module Configuration Register (CANMCR)

- 25.5.2 FlexCAN Control Register 0 (CANCTRL0)

- 25.5.3 FlexCAN Control Register 1 (CANCTRL1)

- 25.5.4 Prescaler Divide Register (PRESDIV)

- 25.5.5 FlexCAN Control Register 2 (CANCTRL2)

- 25.5.6 Free Running Timer (TIMER)

- 25.5.7 Rx Mask Registers

- 25.5.8 FlexCAN Error and Status Register (ESTAT)

- 25.5.9 Interrupt Mask Register (IMASK)

- 25.5.10 Interrupt Flag Register (IFLAG)

- 25.5.11 FlexCAN Receive Error Counter (RXECTR)

- 25.5.12 FlexCAN Transmit Error Counter (TXECTR)

- Chapter 26 General Purpose I/O Module

- 26.1 Introduction

- 26.2 External Signal Description

- 26.3 Memory Map/Register Definition

- 26.3.1 Register Overview

- 26.3.2 Register Descriptions

- 26.3.2.1 Port Output Data Registers (PORTn)

- 26.3.2.2 Port Data Direction Registers (DDRn)

- 26.3.2.3 Port Pin Data/Set Data Registers (PORTnP/SETn)

- 26.3.2.4 Port Clear Output Data Registers (CLRn)

- 26.3.2.5 Port B/C/D Pin Assignment Register (PBCDPAR)

- 26.3.2.6 Port E Pin Assignment Register (PEPAR)

- 26.3.2.7 Port F Pin Assignment Register (PFPAR)

- 26.3.2.8 Port J Pin Assignment Register (PJPAR)

- 26.3.2.9 Port SD Pin Assignment Register (PSDPAR)

- 26.3.2.10 Port AS Pin Assignment Register (PASPAR)

- 26.3.2.11 Port EH/EL Pin Assignment Register (PEHLPAR)

- 26.3.2.12 Port QS Pin Assignment Register (PQSPAR)

- 26.3.2.13 Port TC Pin Assignment Register (PTCPAR)

- 26.3.2.14 Port TD Pin Assignment Register (PTDPAR)

- 26.3.2.15 Port UA Pin Assignment Register (PUAPAR)

- 26.4 Functional Description

- 26.5 Initialization/Application Information

- Chapter 27 Queued Analog-to-Digital Converter (QADC)

- 27.1 Features

- 27.2 Block Diagram

- 27.3 Modes of Operation

- 27.4 Signals

- 27.5 Memory Map

- 27.6 Register Descriptions

- 27.6.1 QADC Module Configuration Register (QADCMCR)

- 27.6.2 QADC Test Register (QADCTEST)

- 27.6.3 Port Data Registers (PORTQA and PORTQB)

- 27.6.4 Port QA and QB Data Direction Register (DDRQA and DDRQB)

- 27.6.5 Control Registers

- 27.6.6 Status Registers

- 27.6.7 Conversion Command Word Table (CCW)

- 27.6.8 Result Registers

- 27.7 Functional Description

- 27.7.1 Result Coherency

- 27.7.2 External Multiplexing

- 27.7.3 Analog Subsystem

- 27.8 Digital Control Subsystem

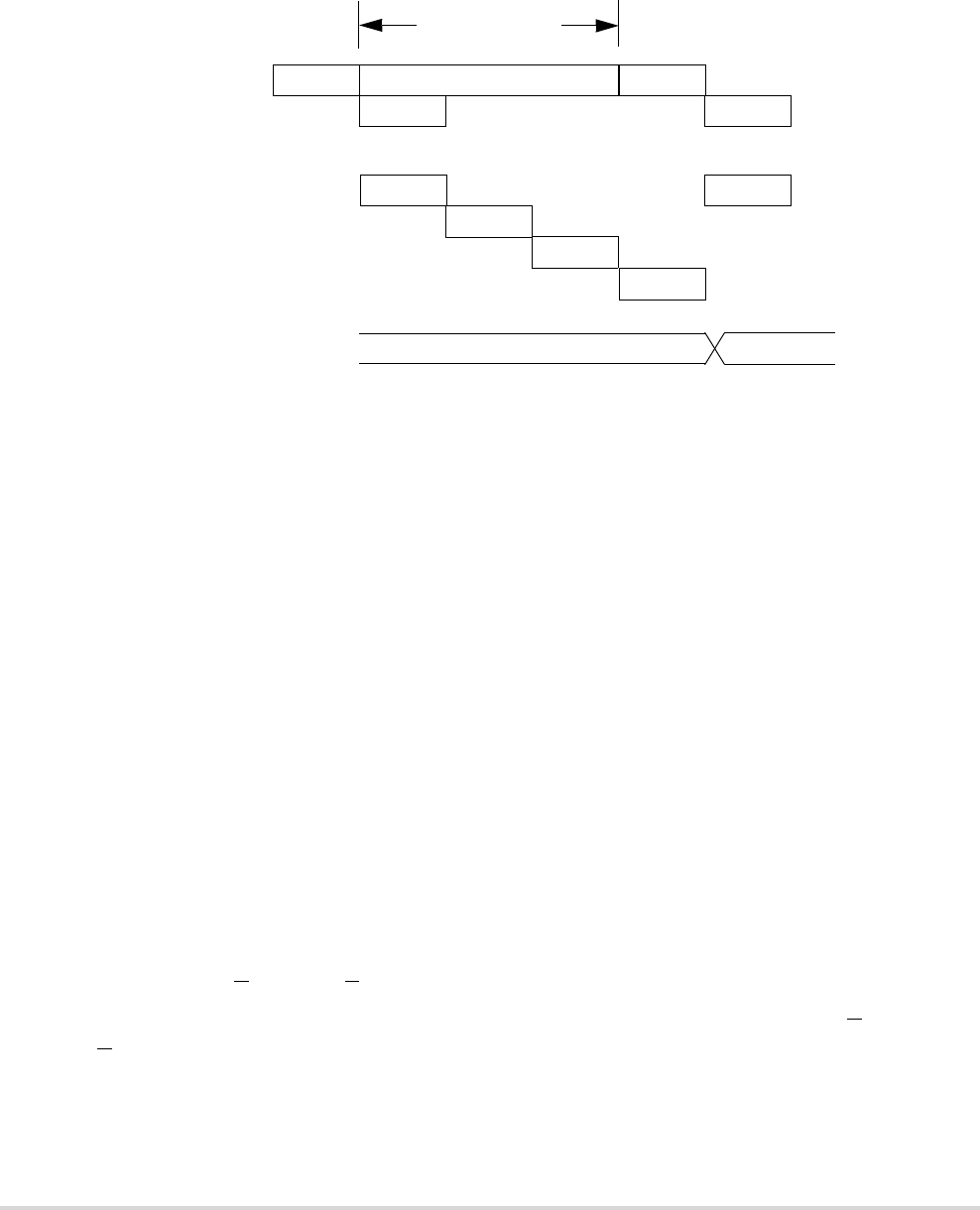

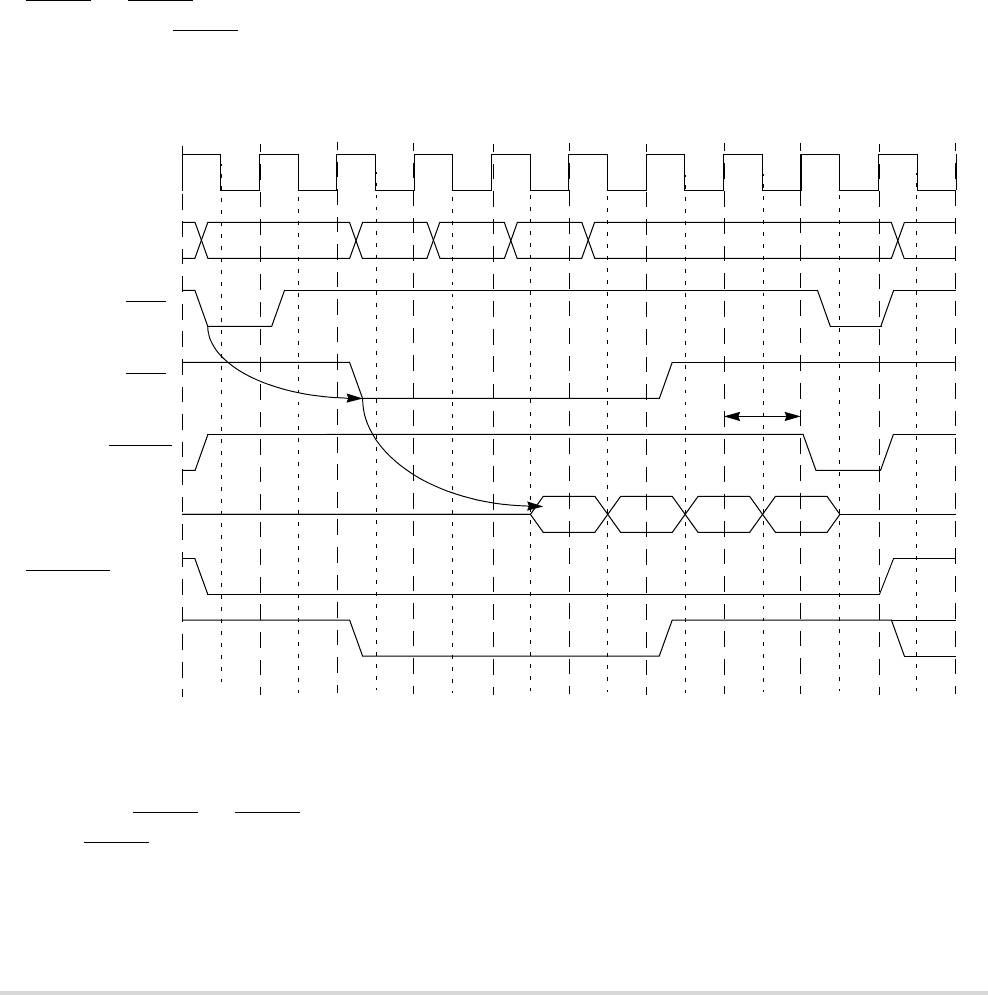

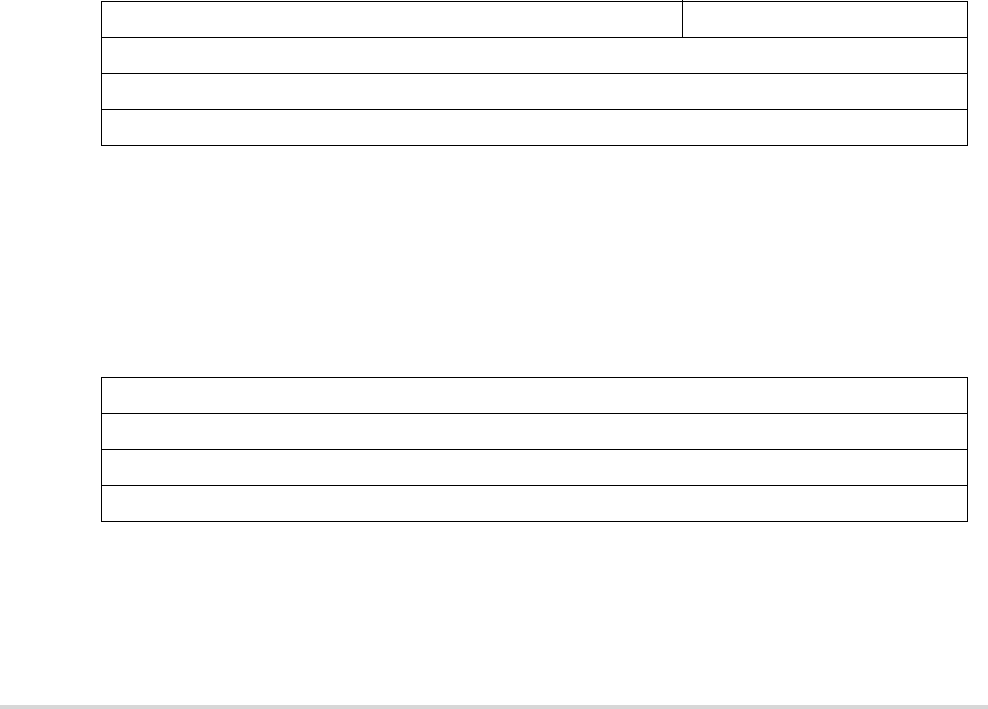

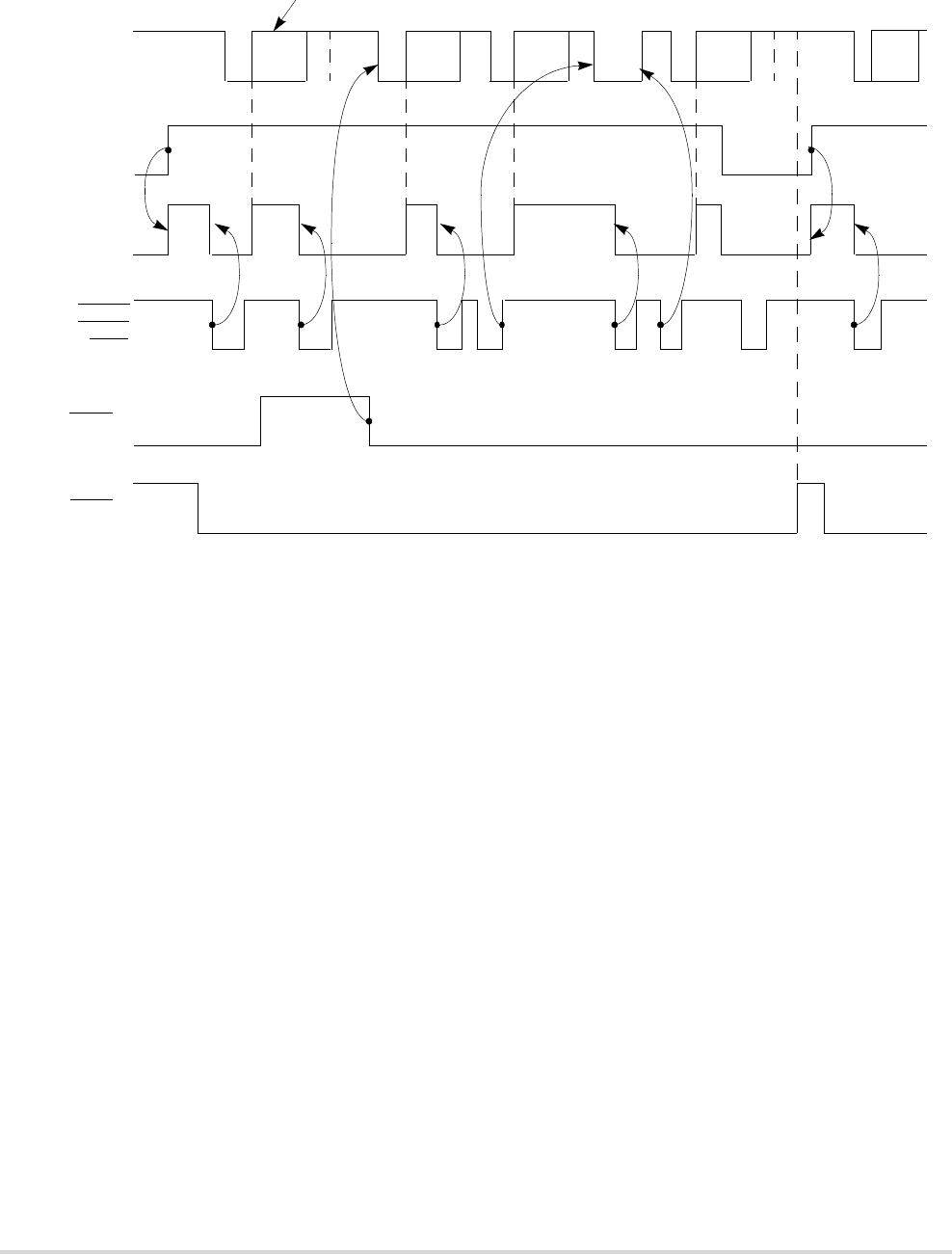

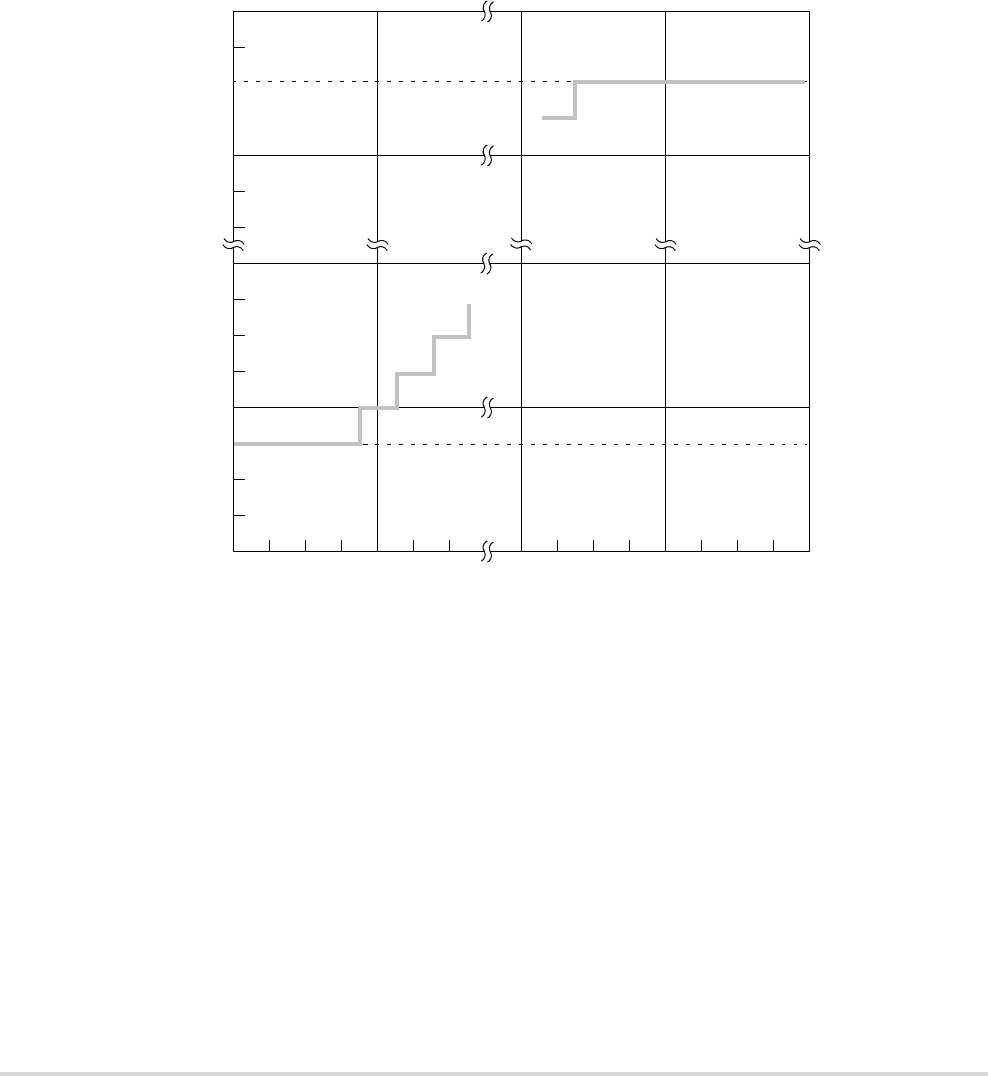

- 27.8.1 Queue Priority Timing Examples

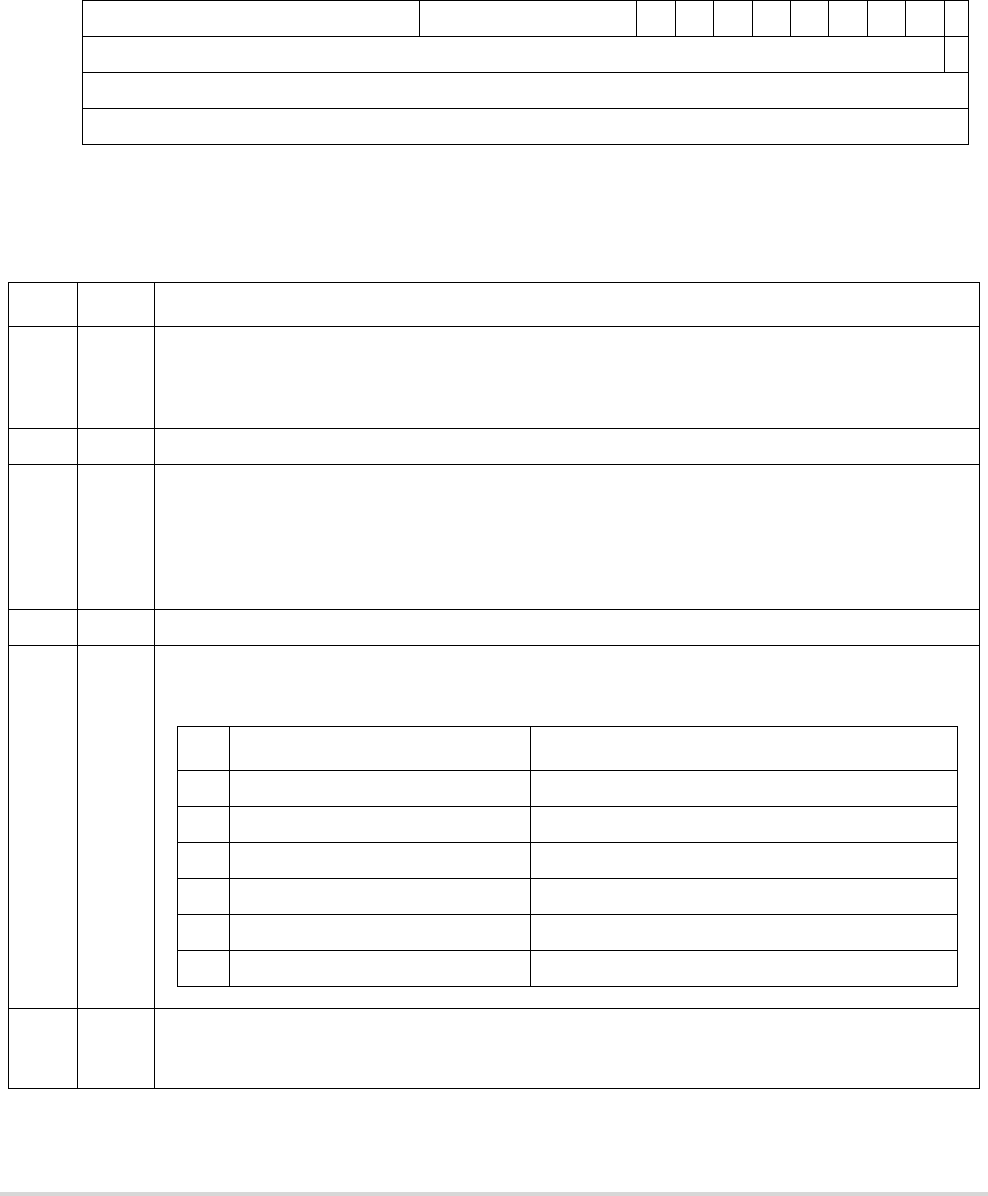

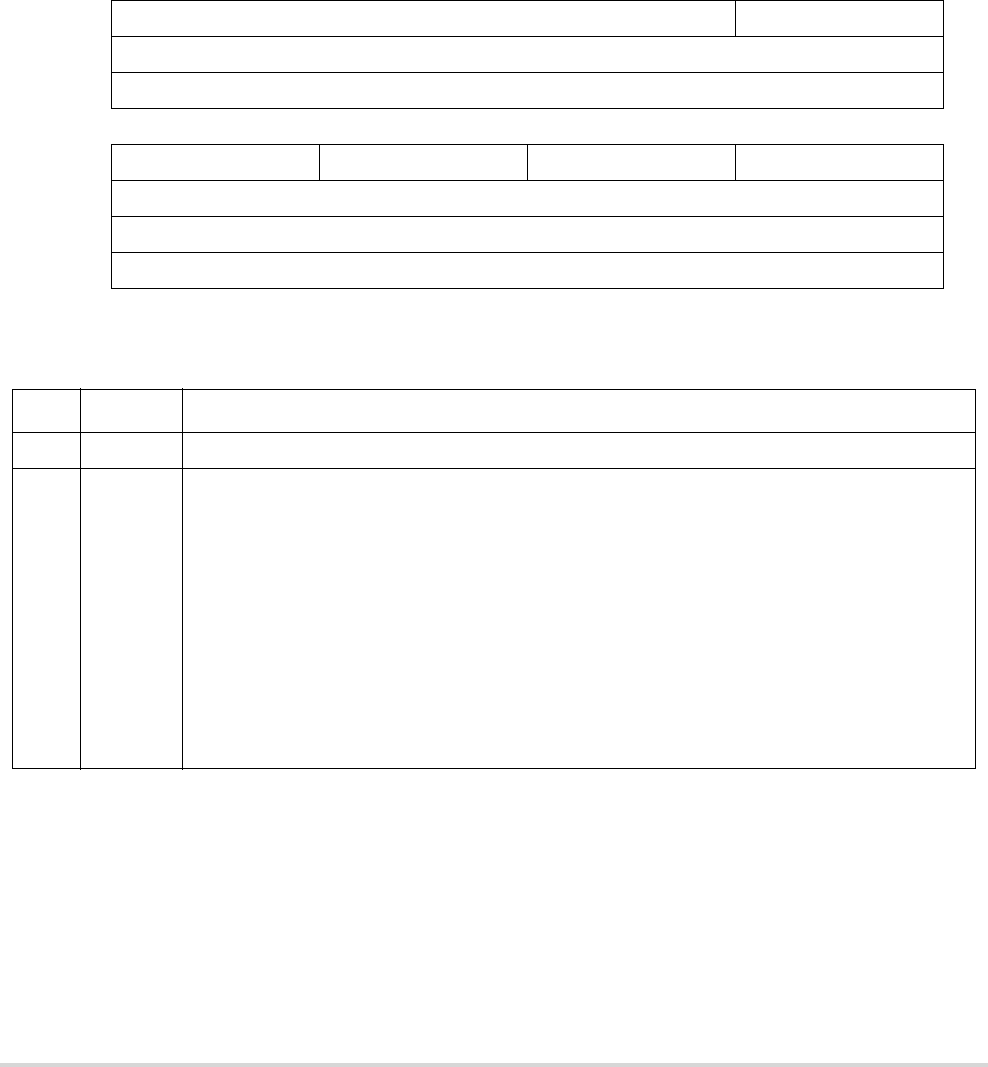

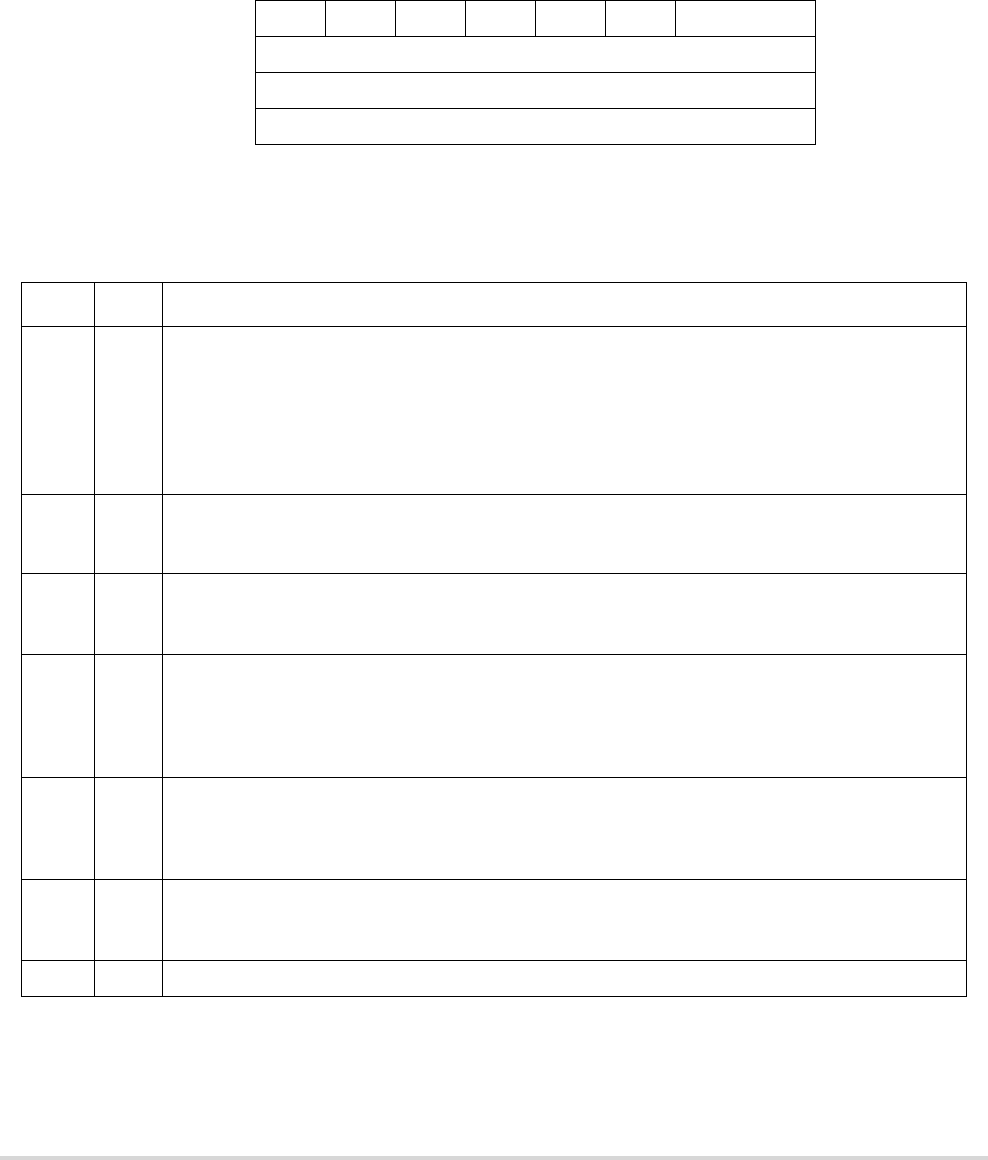

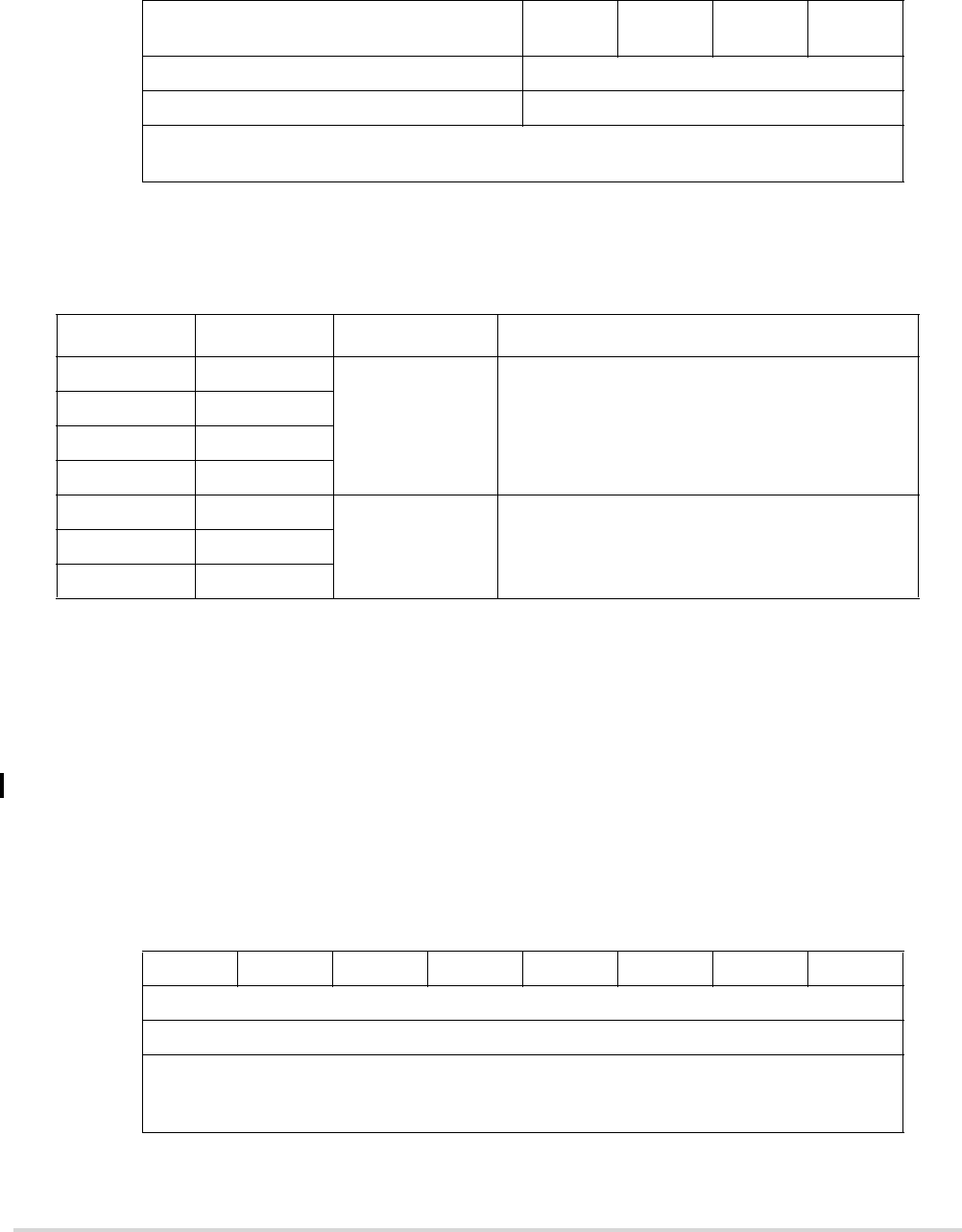

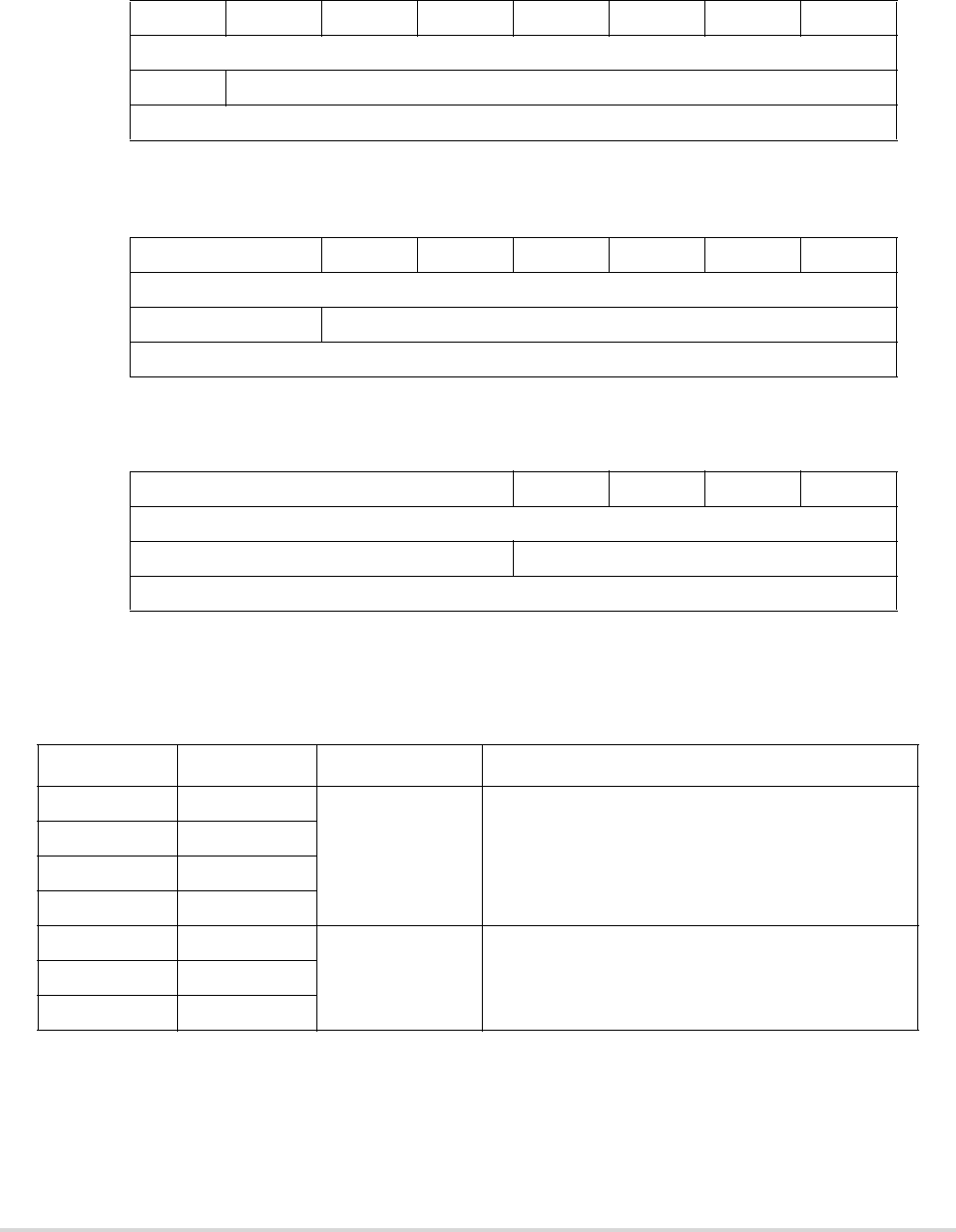

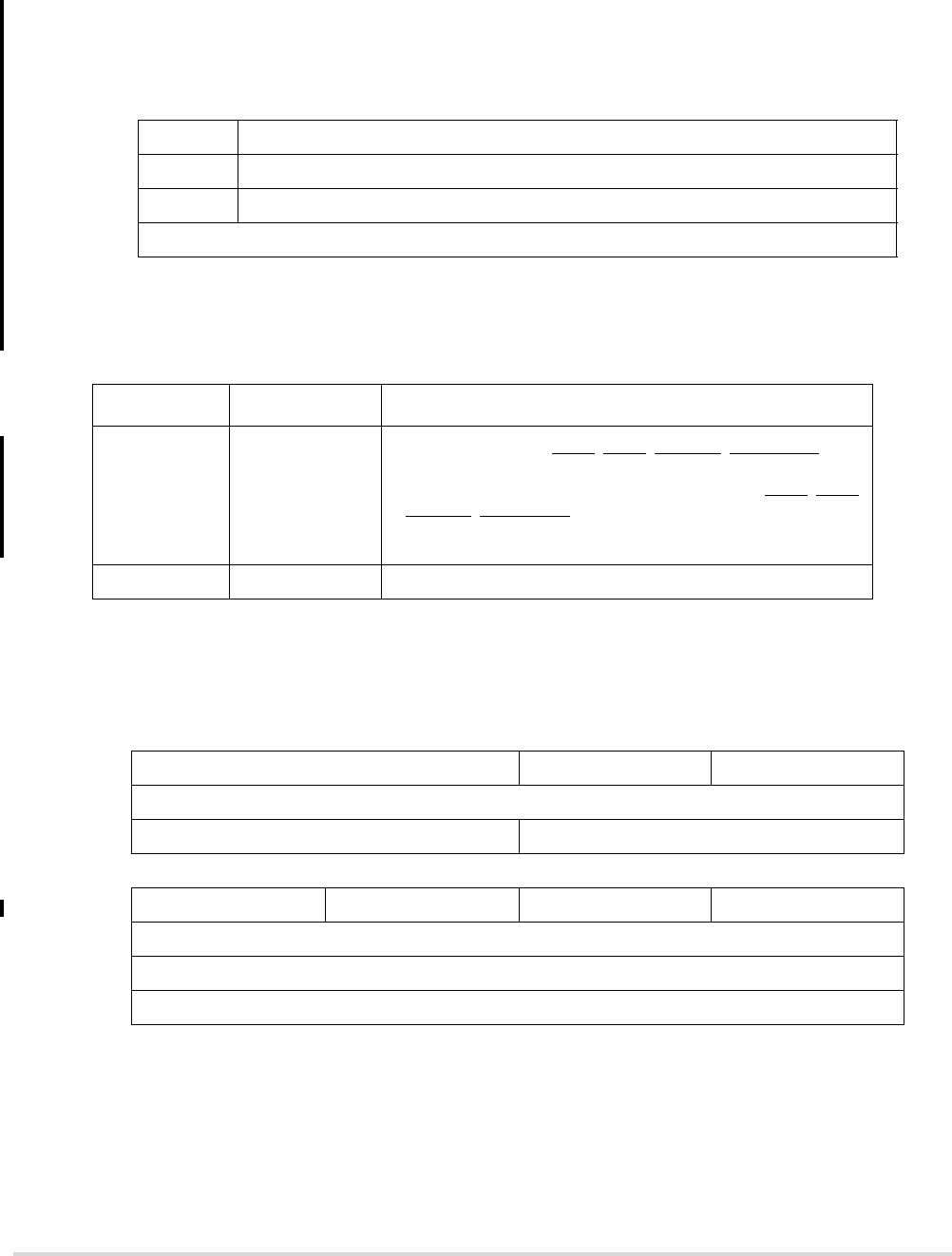

- 27.8.1.1 Queue Priority

- 27.8.1.2 Queue Priority Schemes

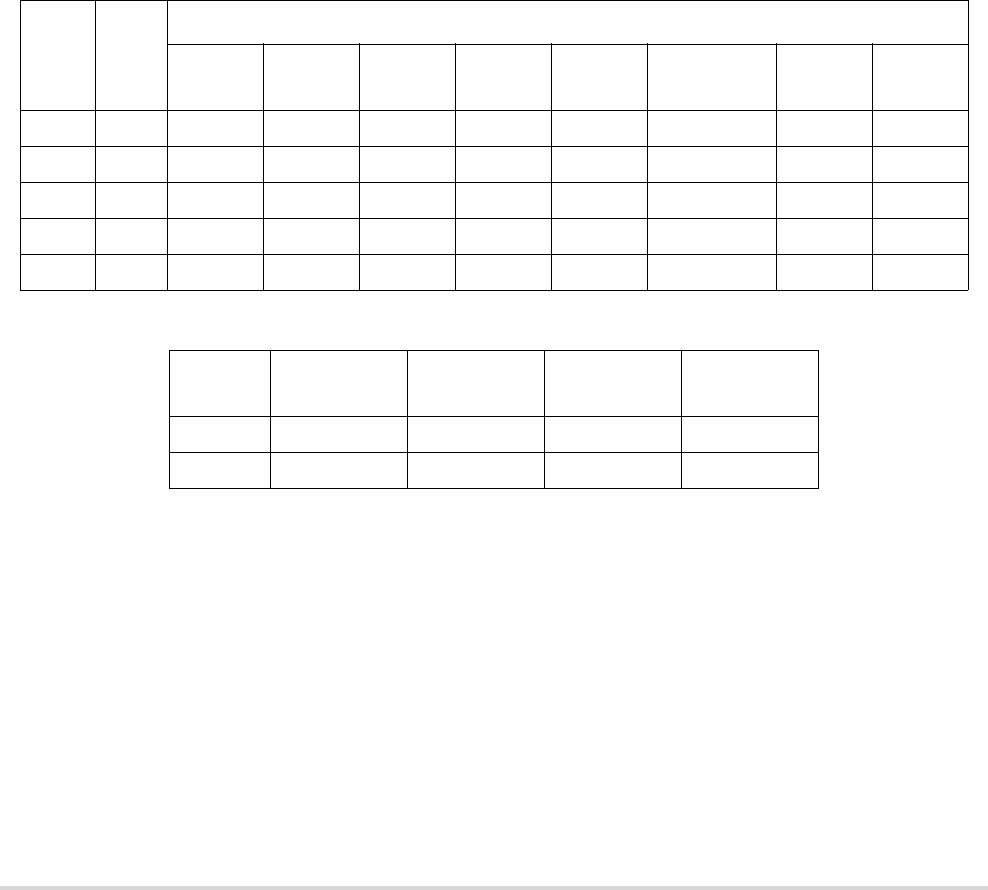

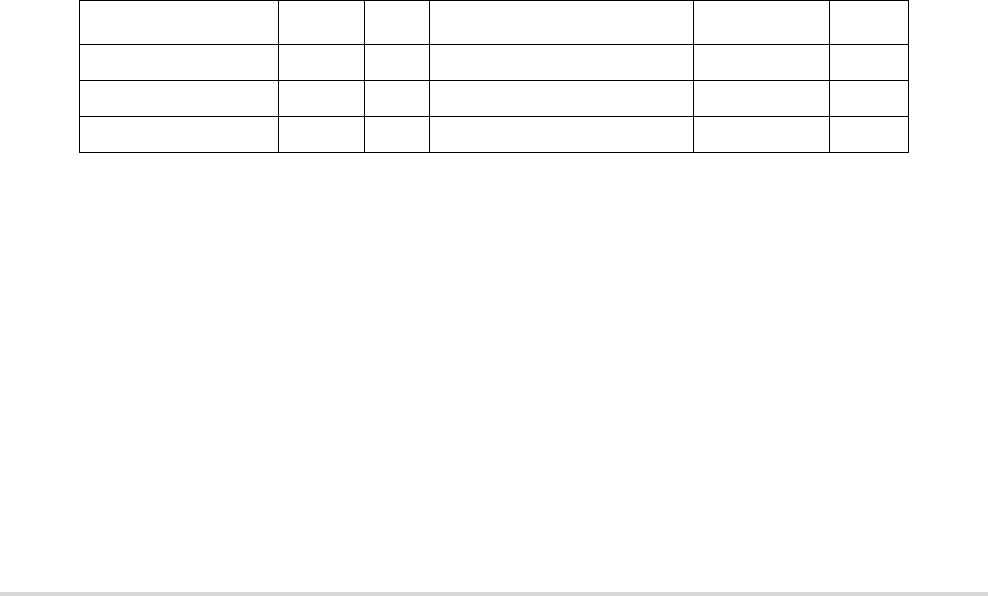

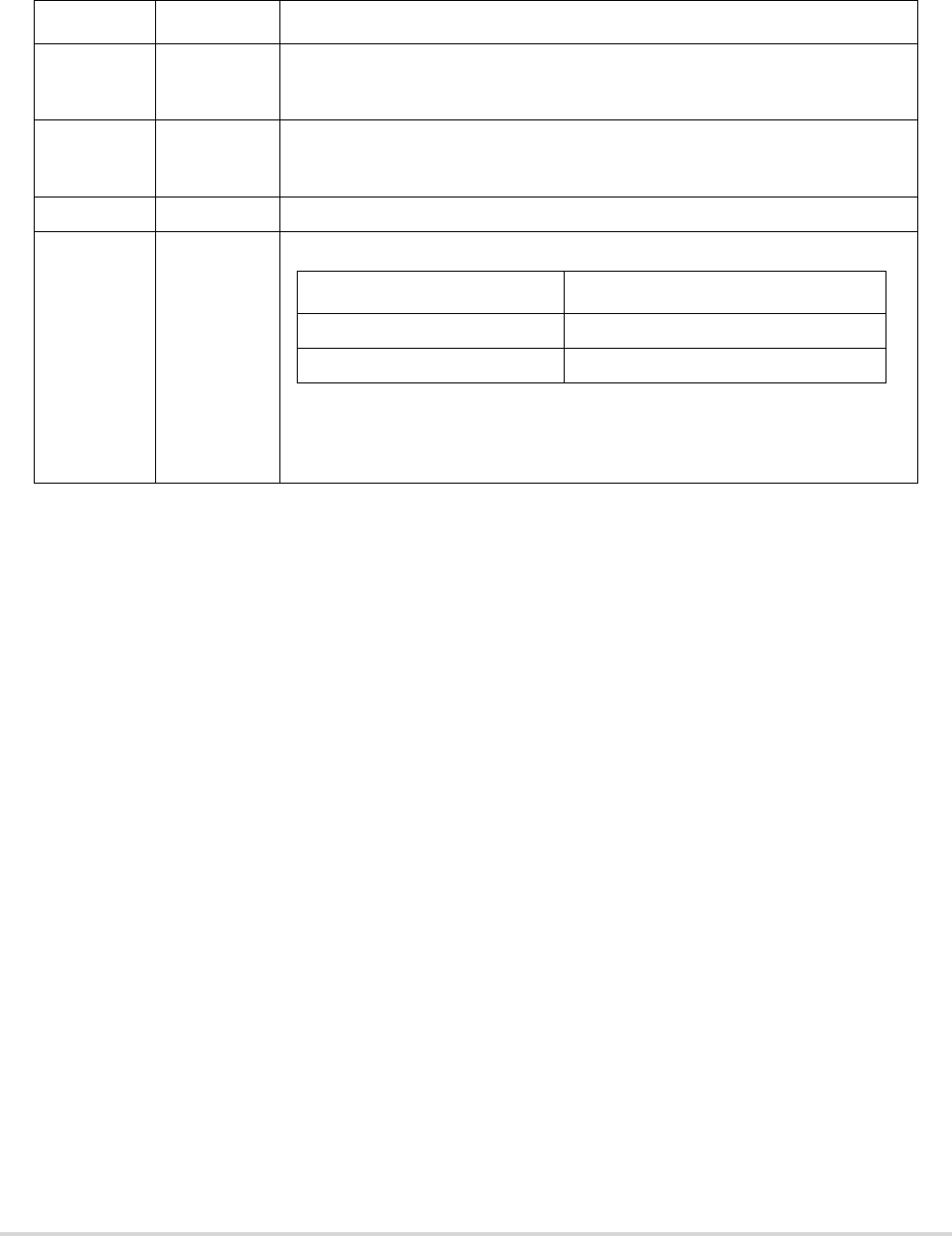

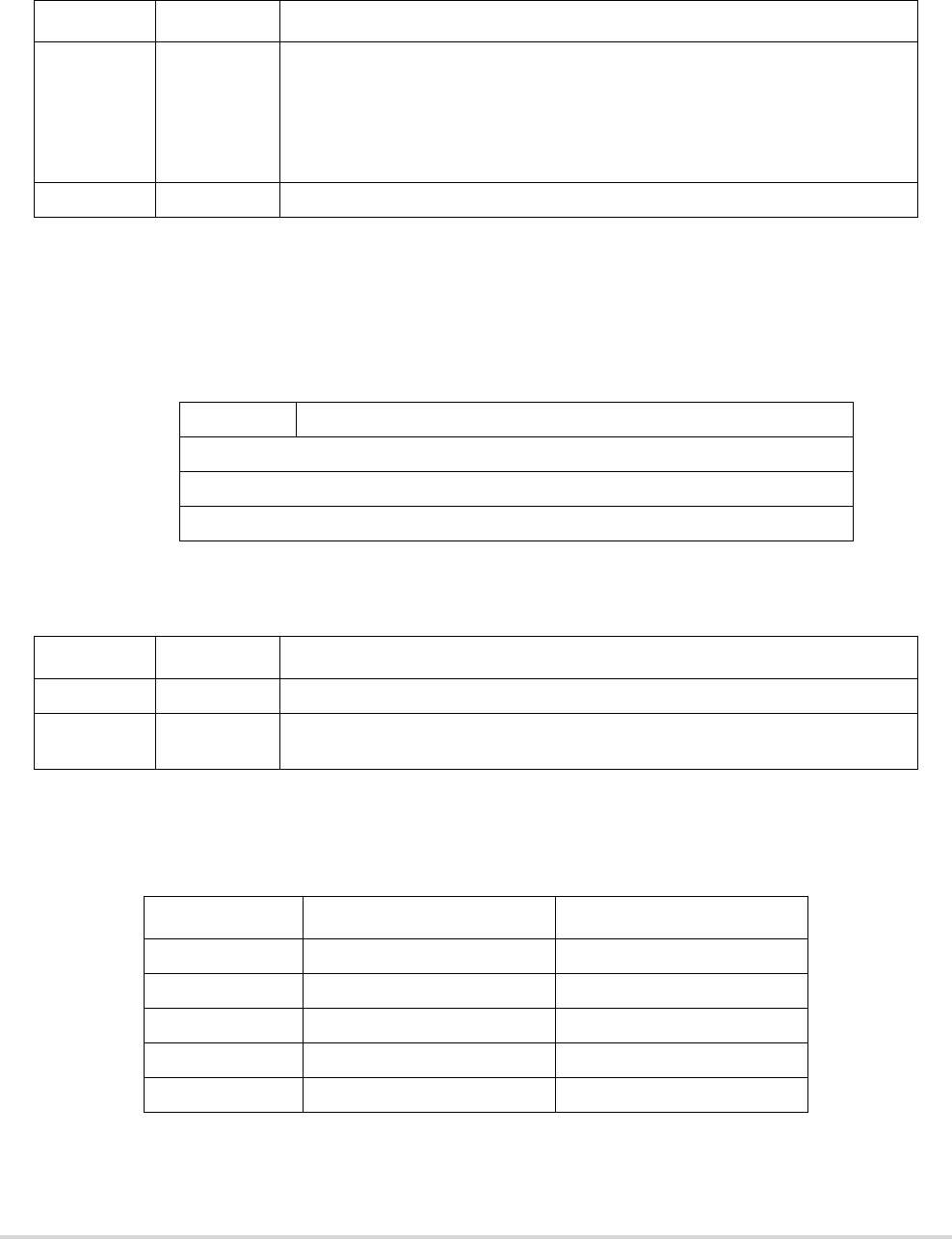

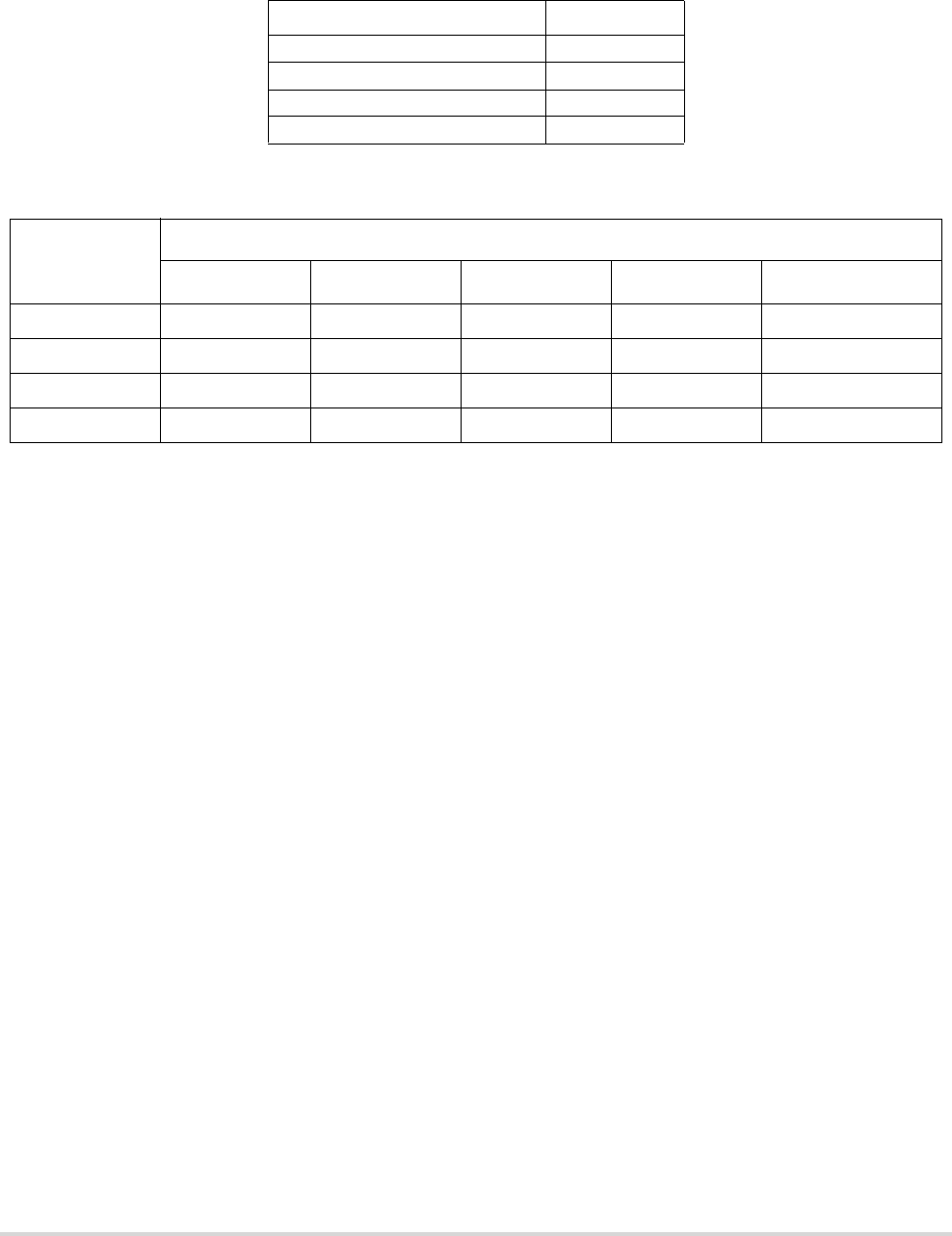

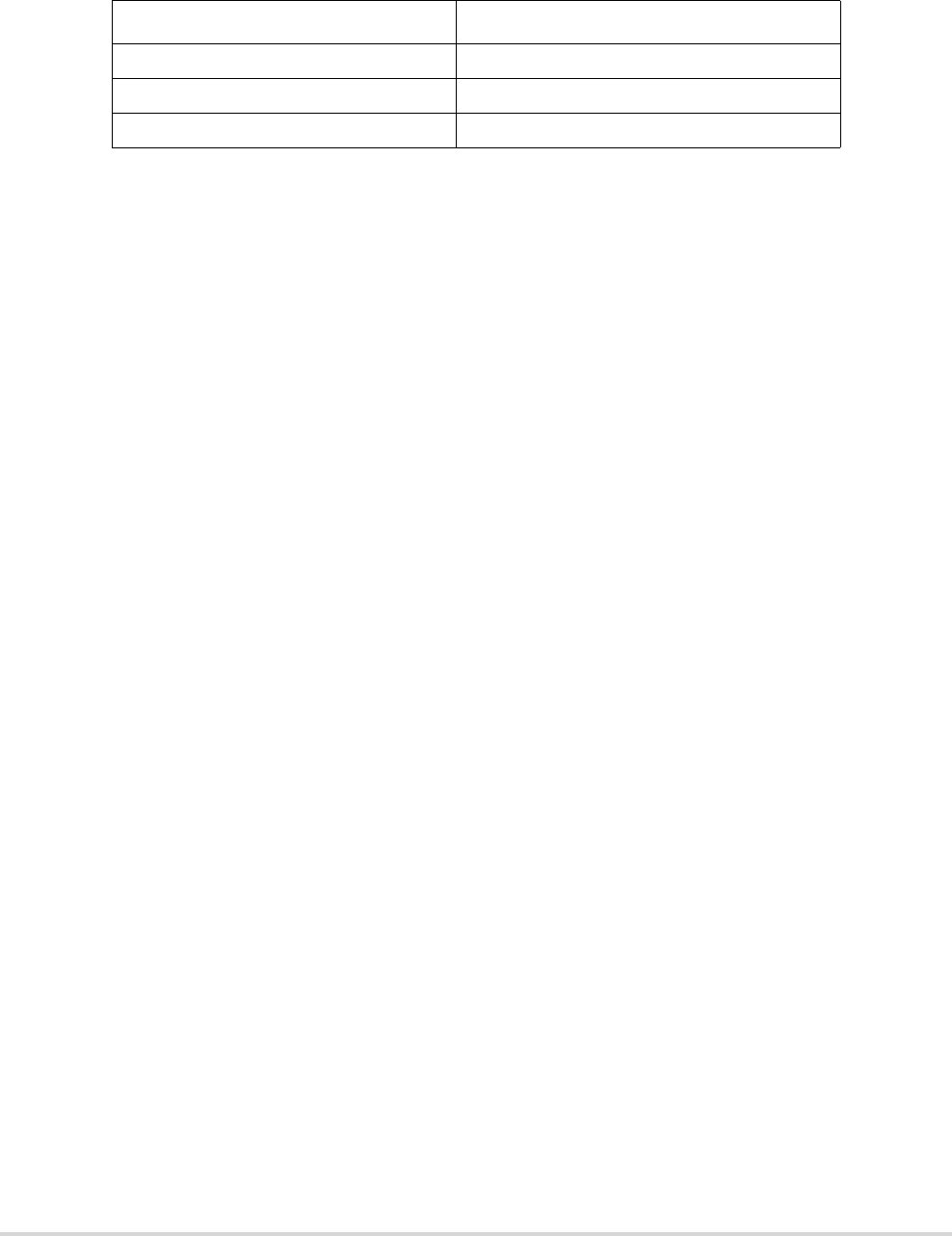

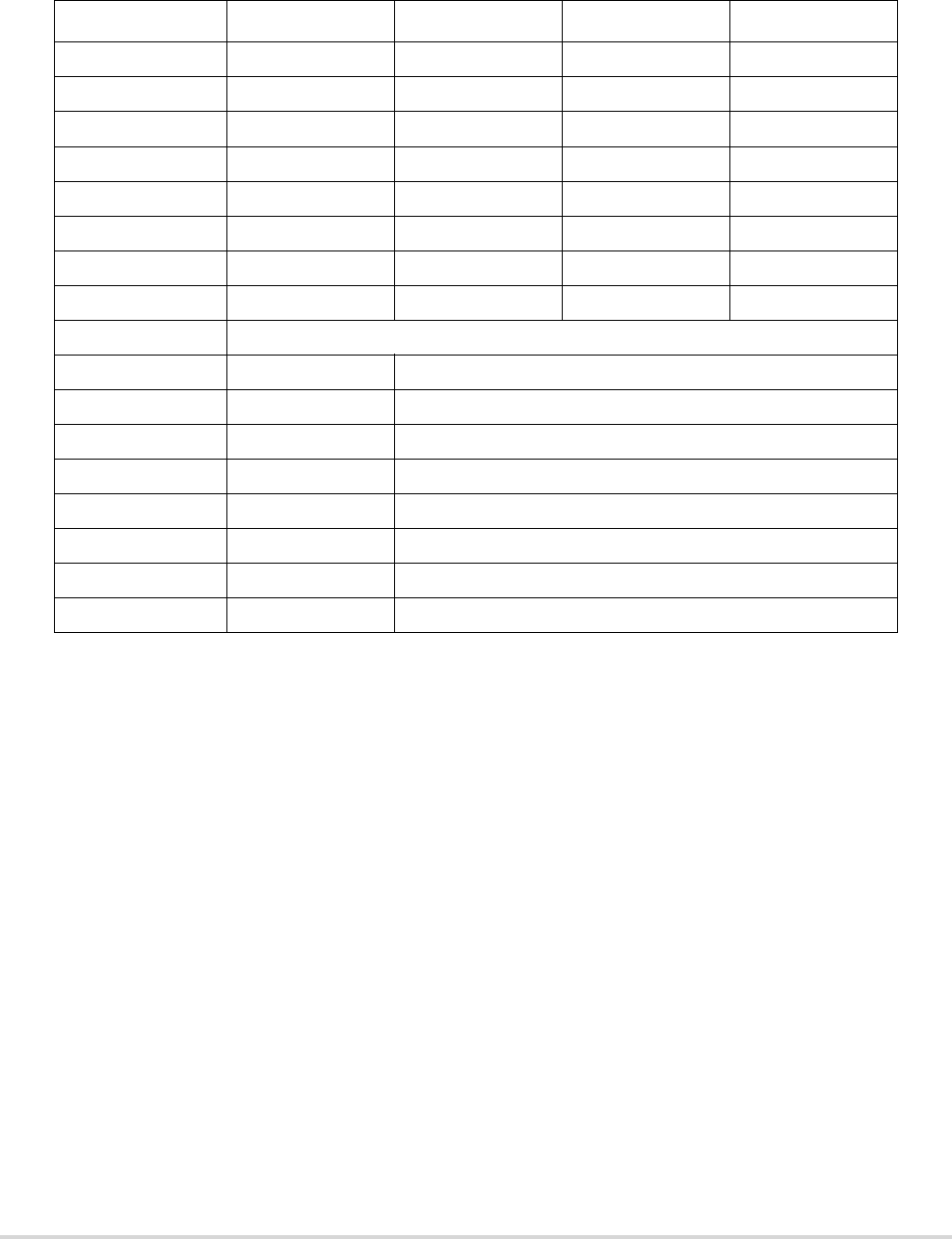

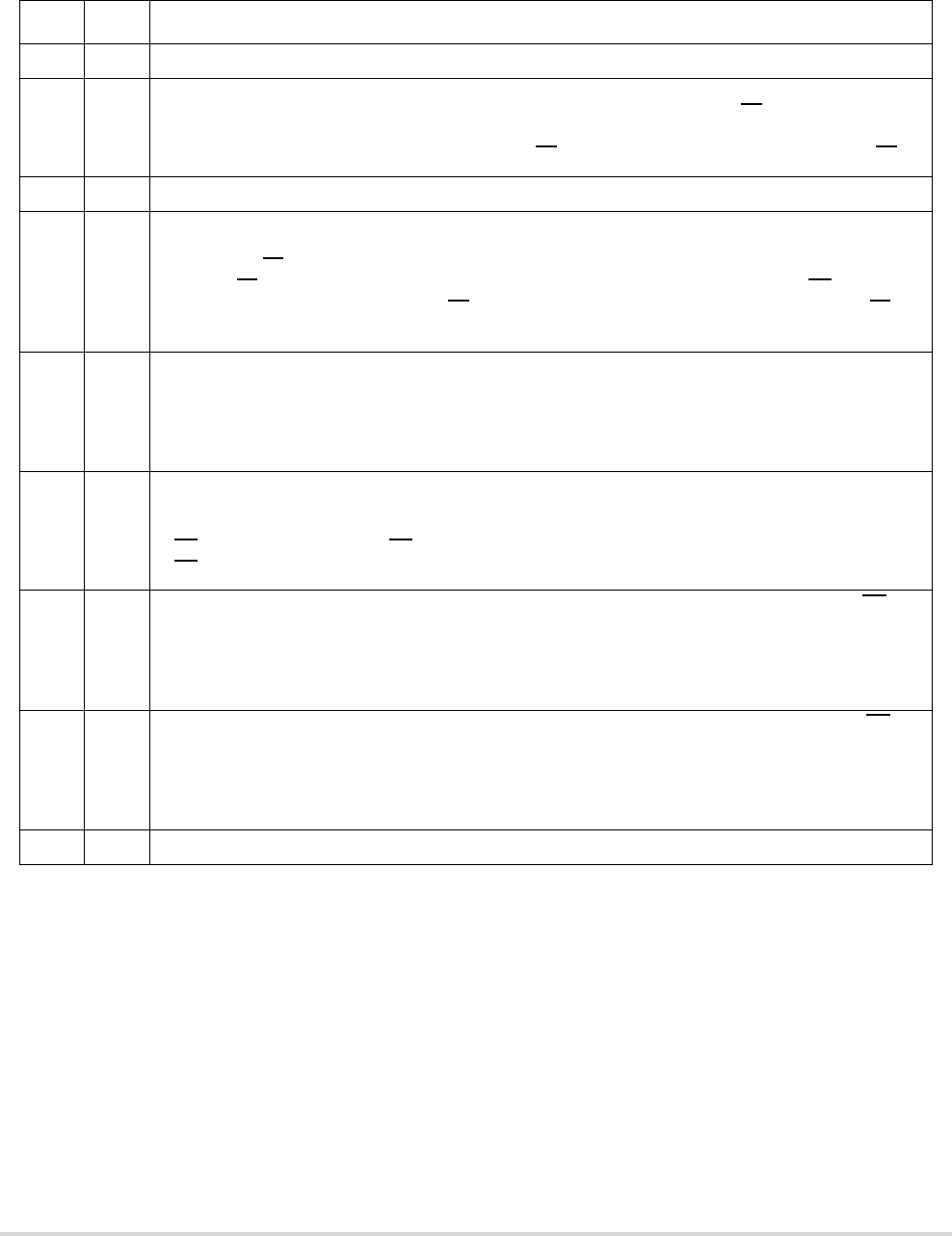

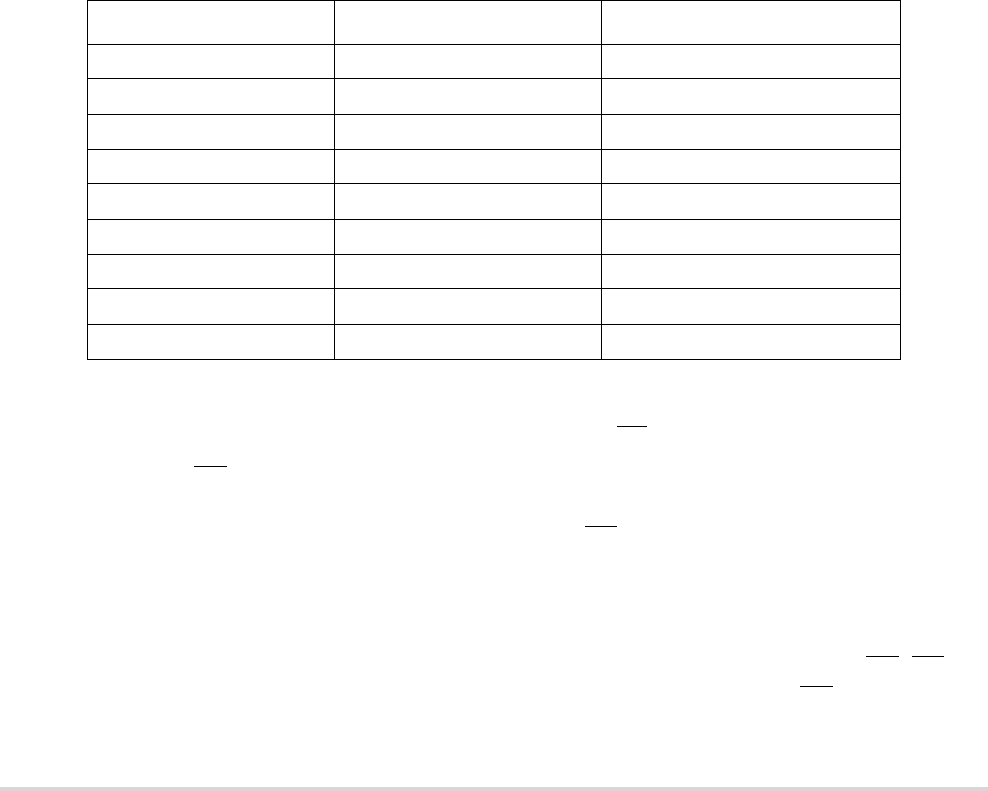

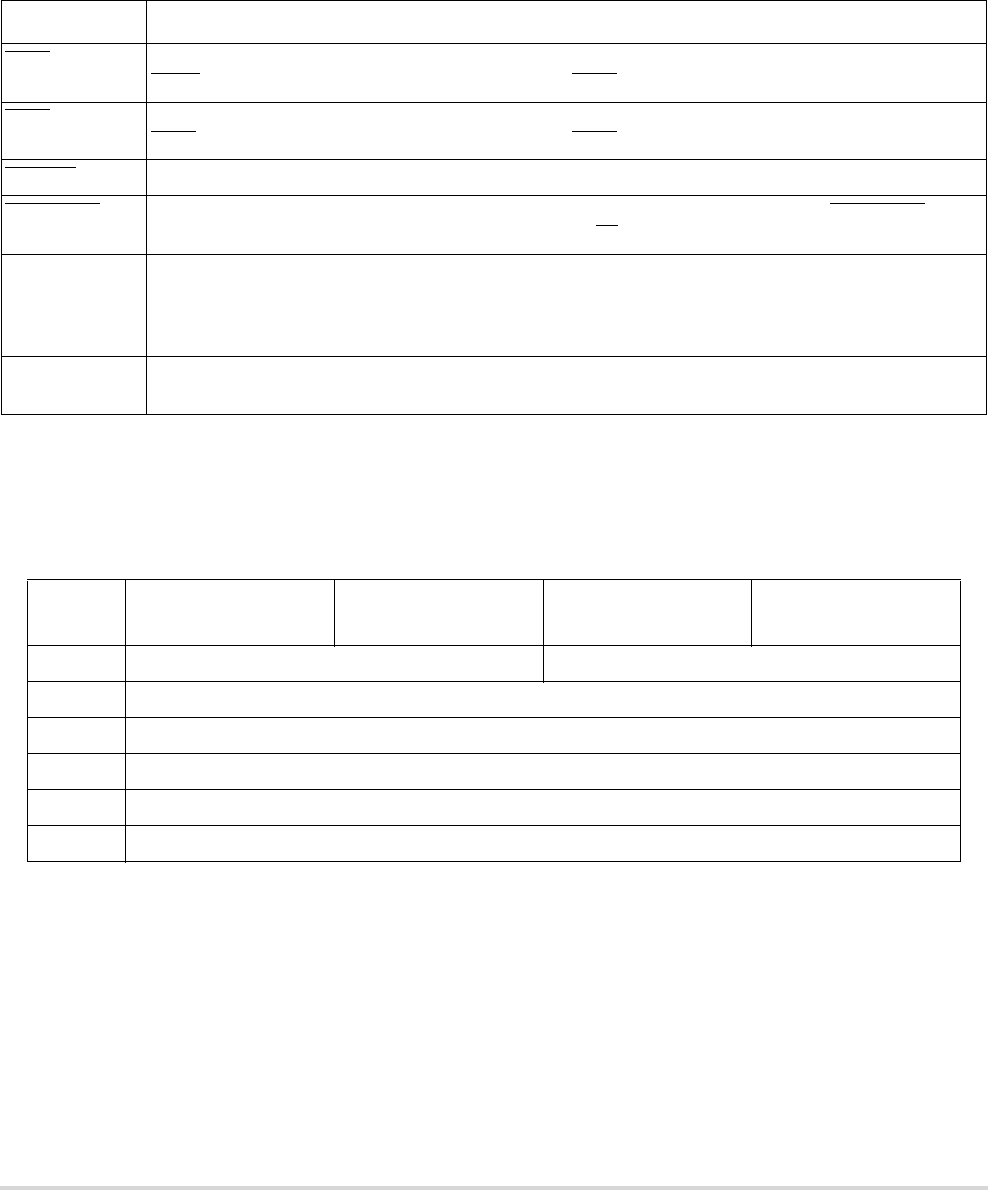

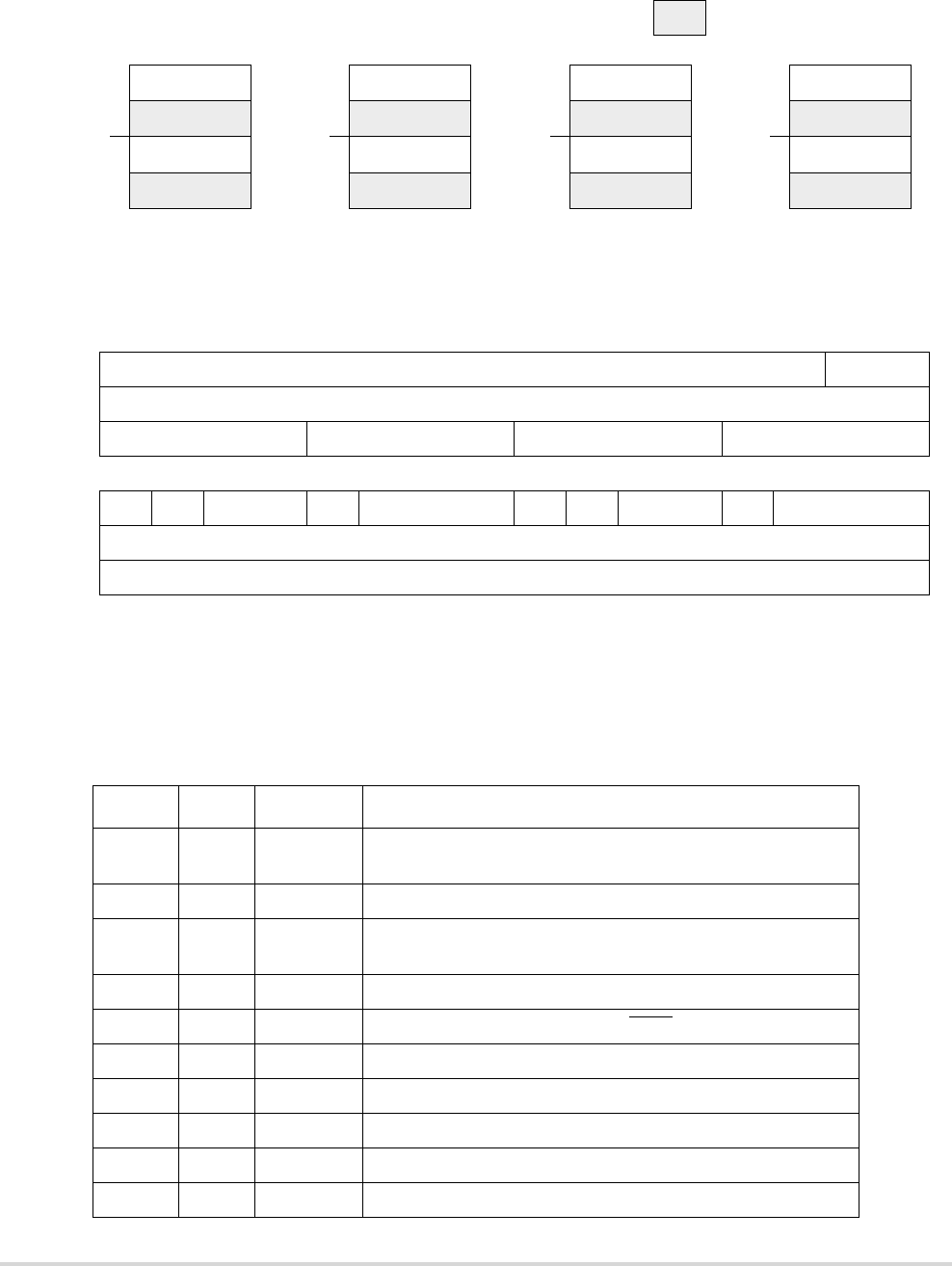

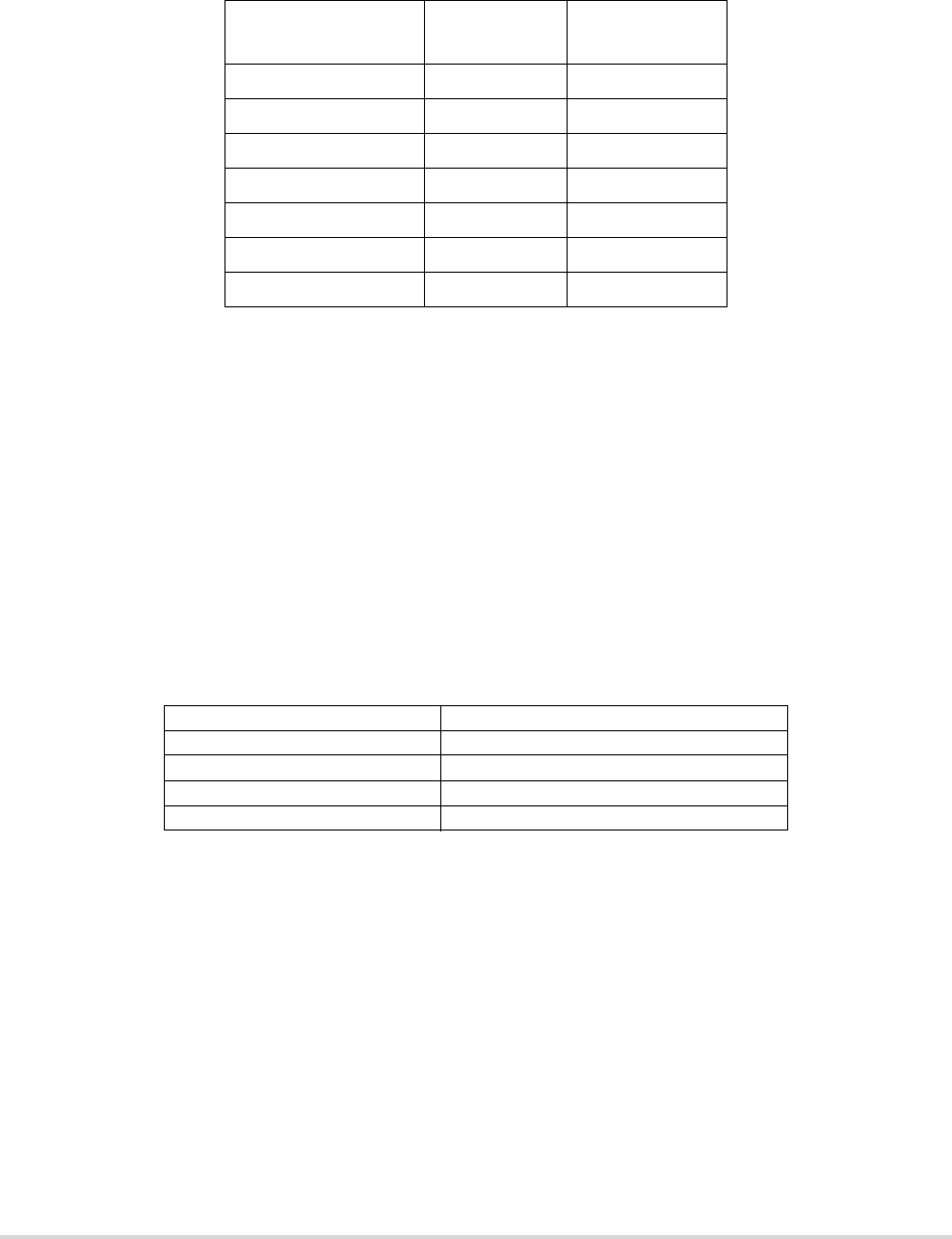

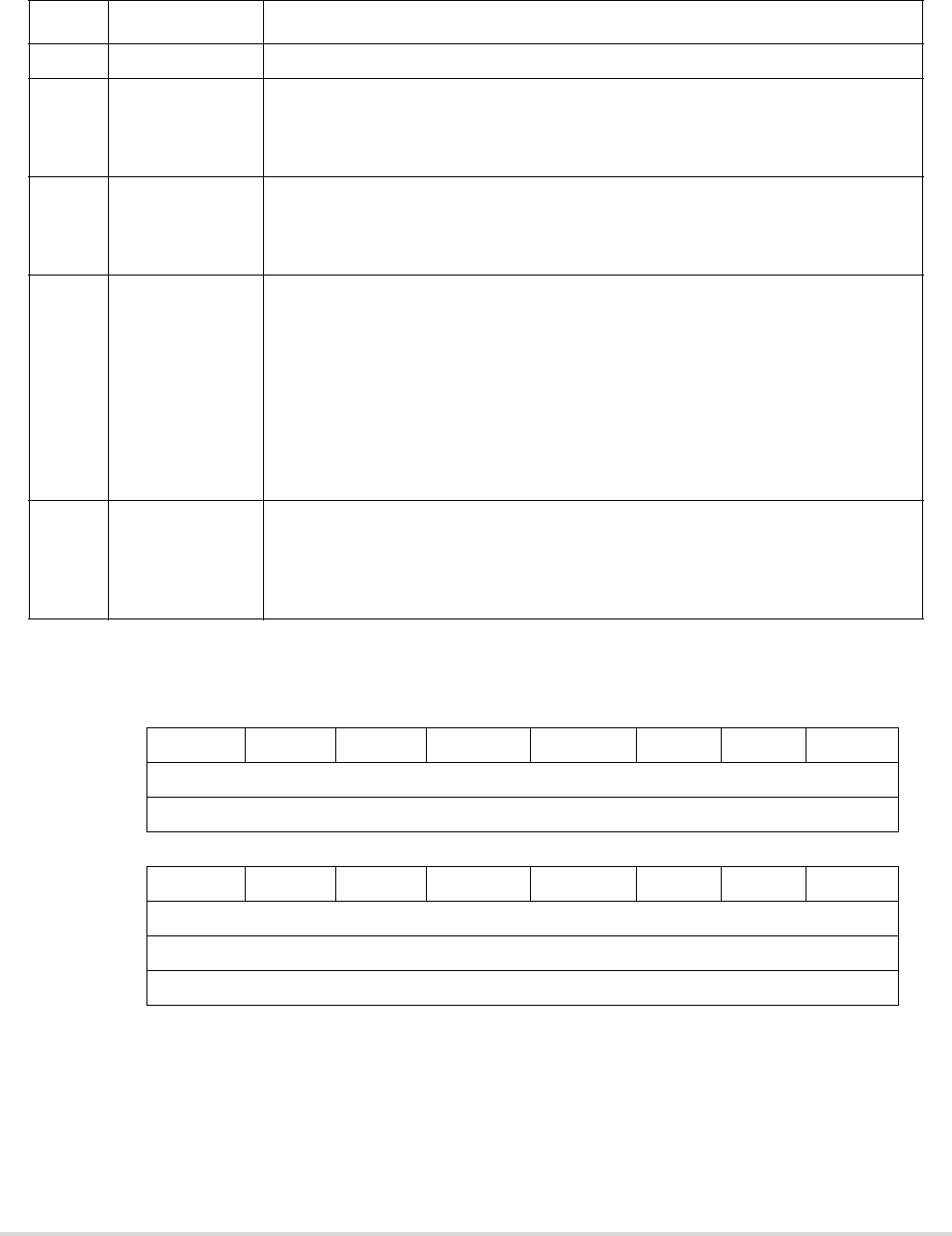

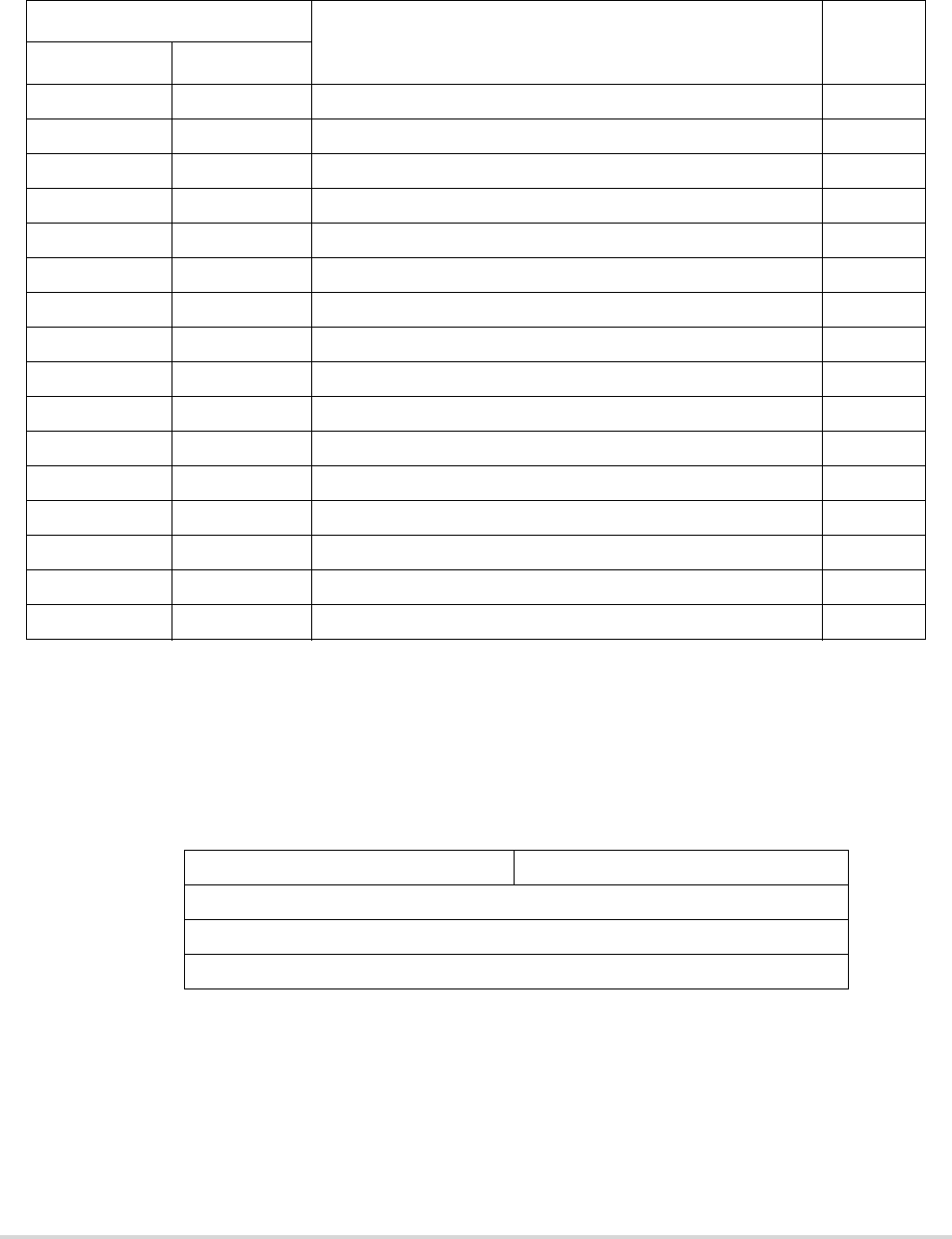

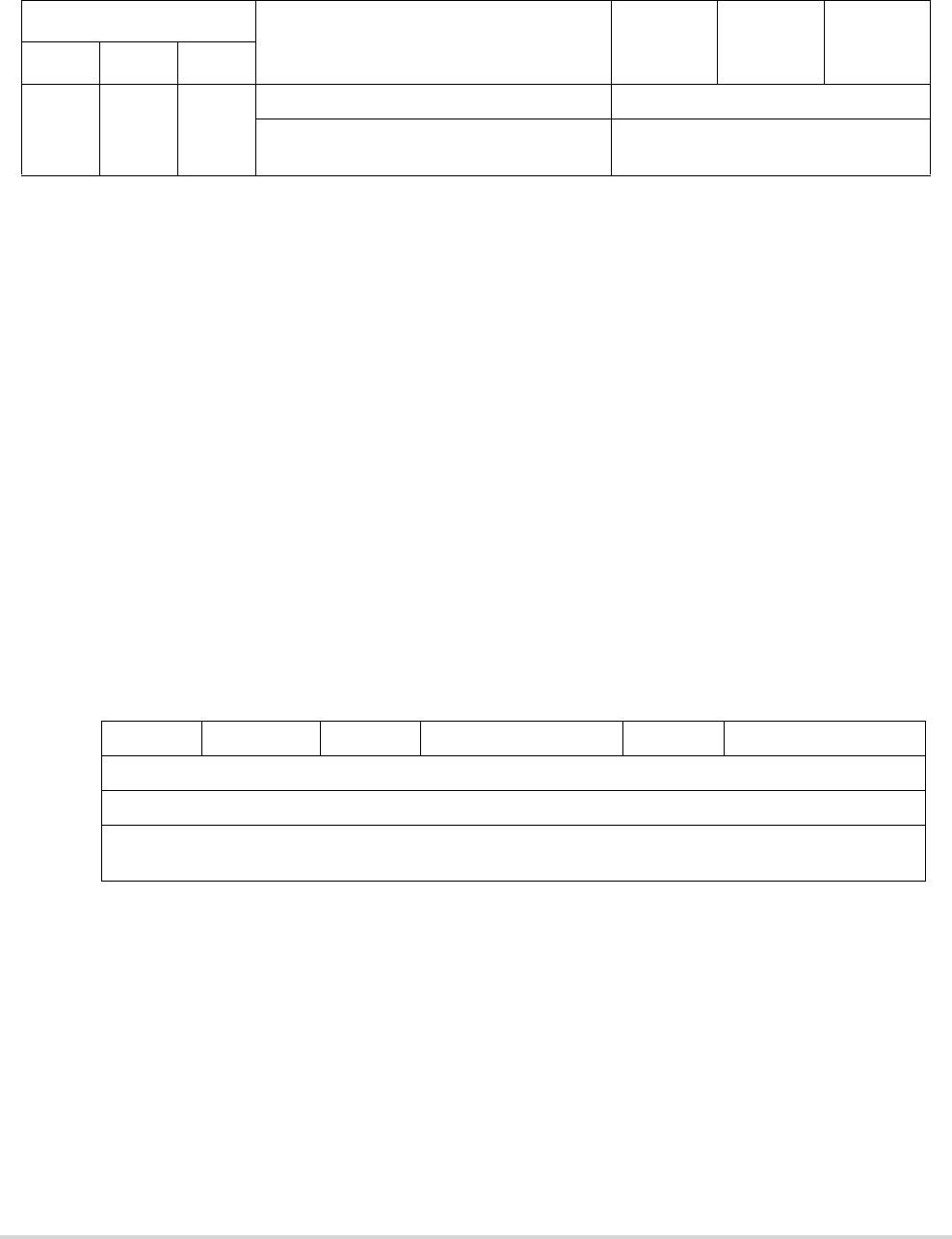

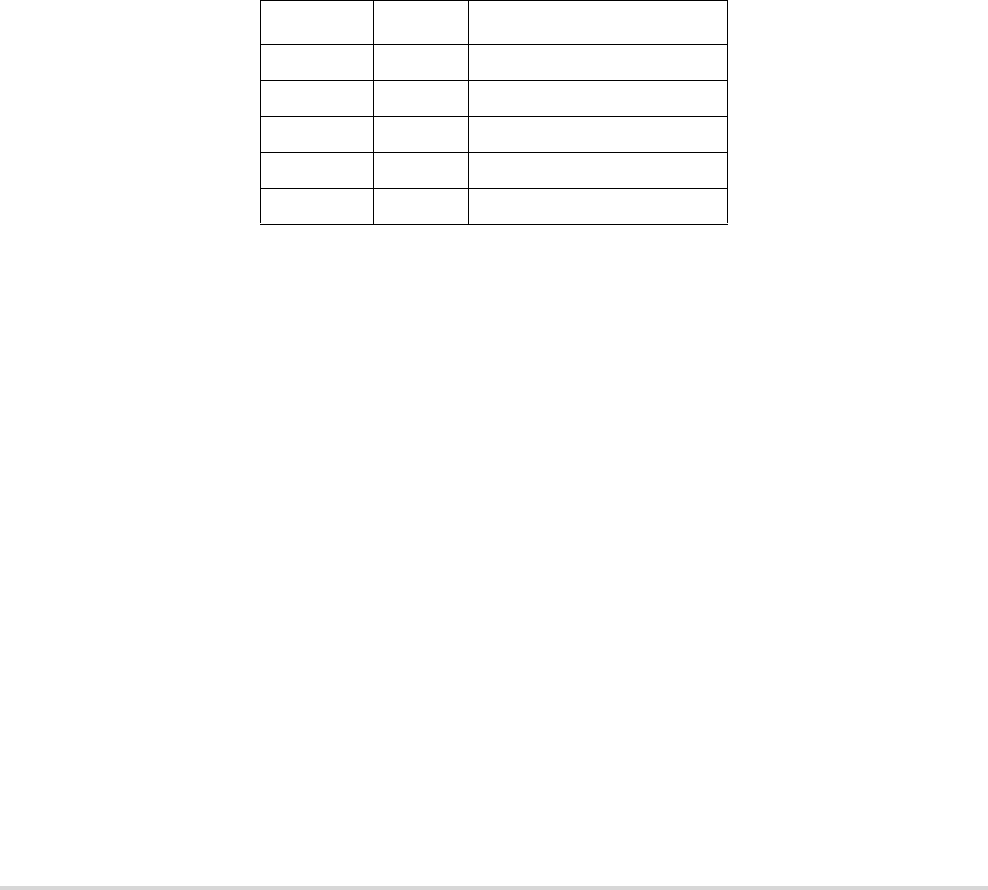

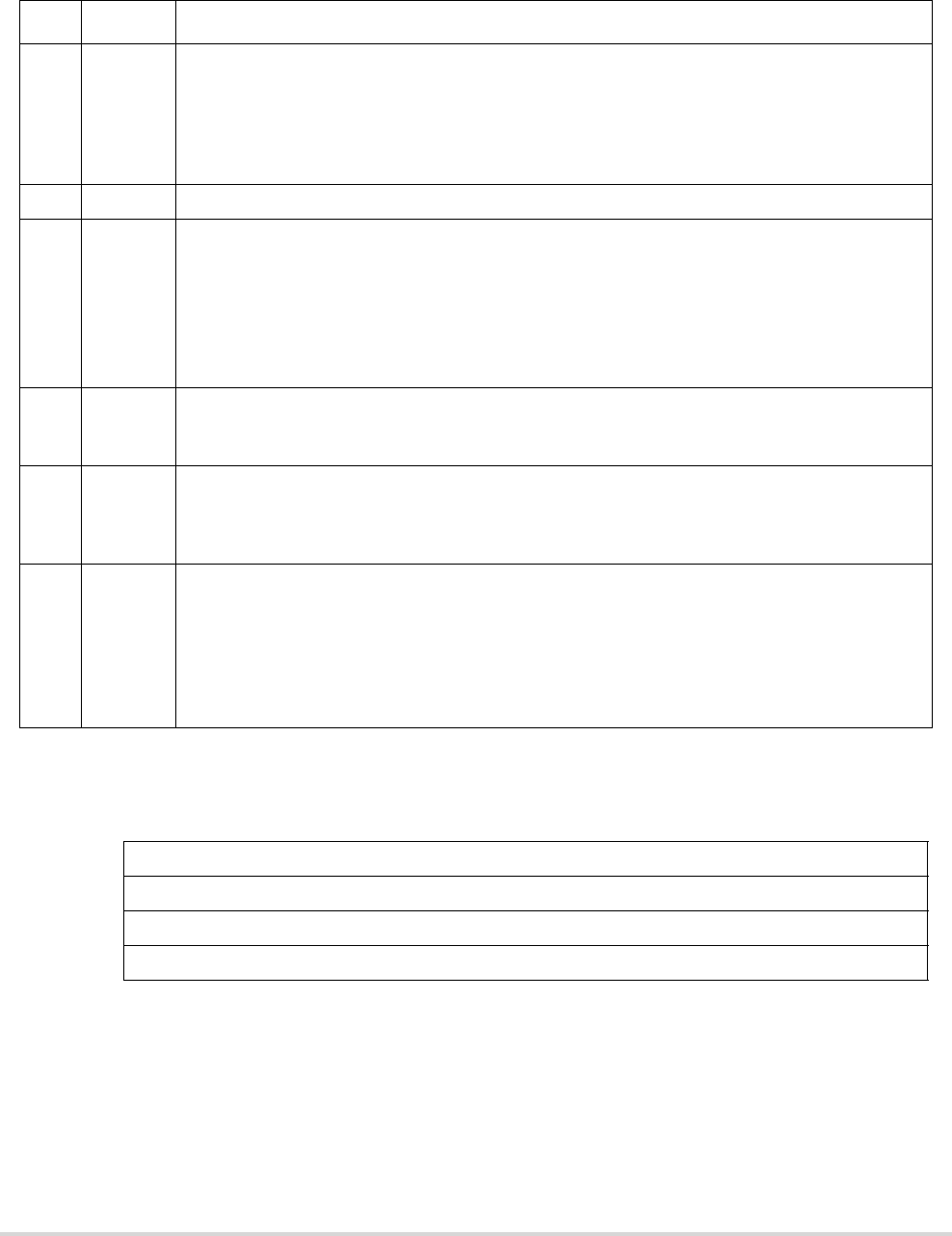

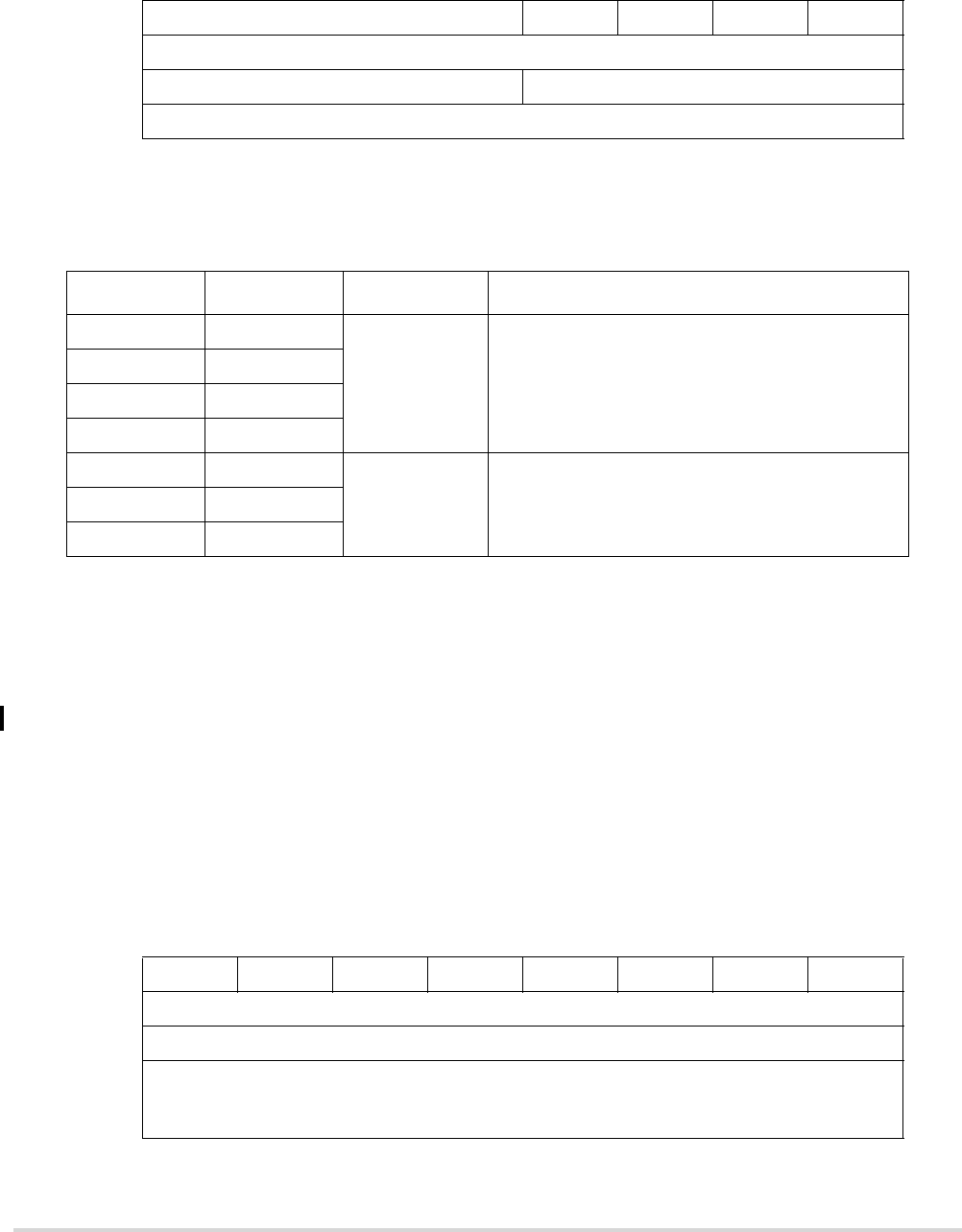

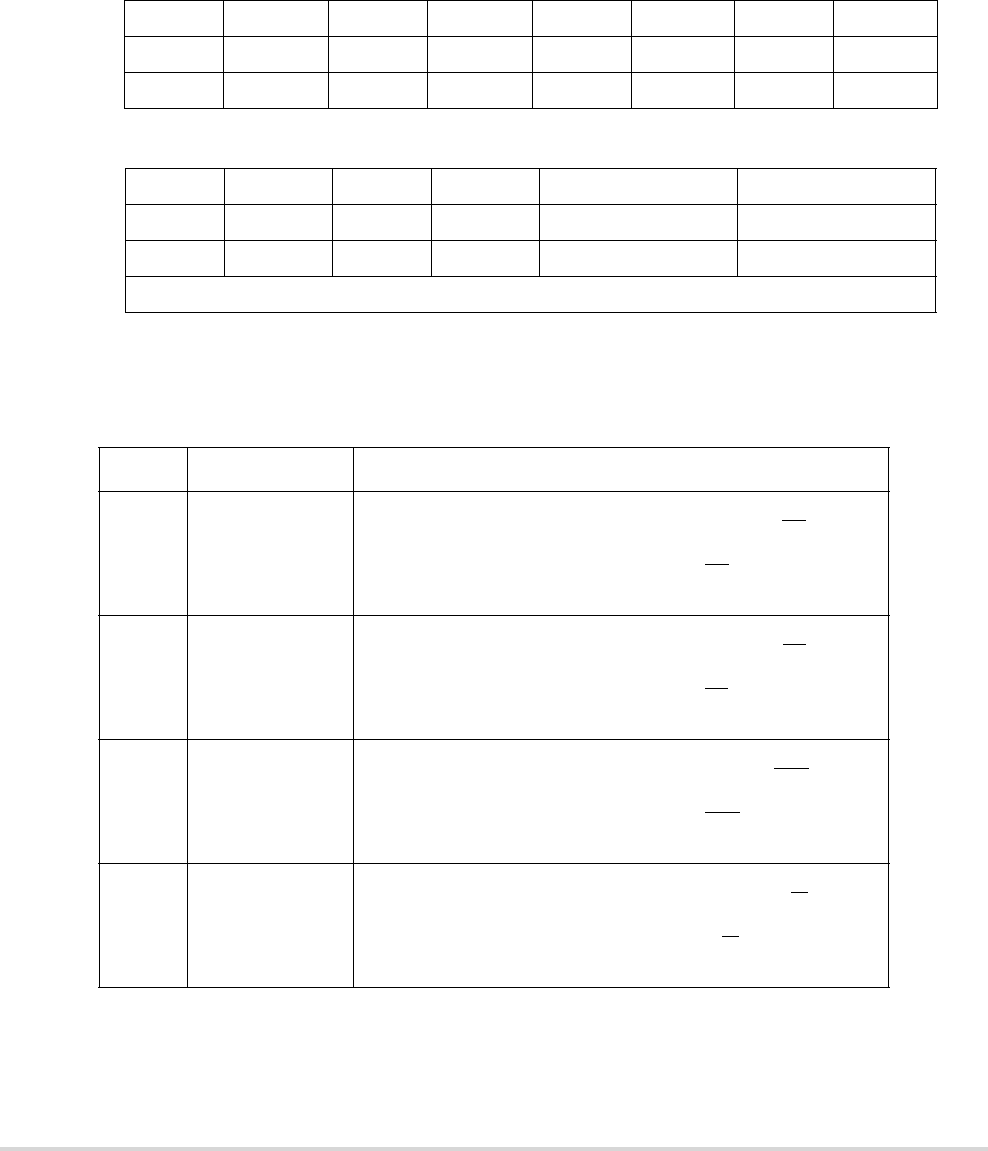

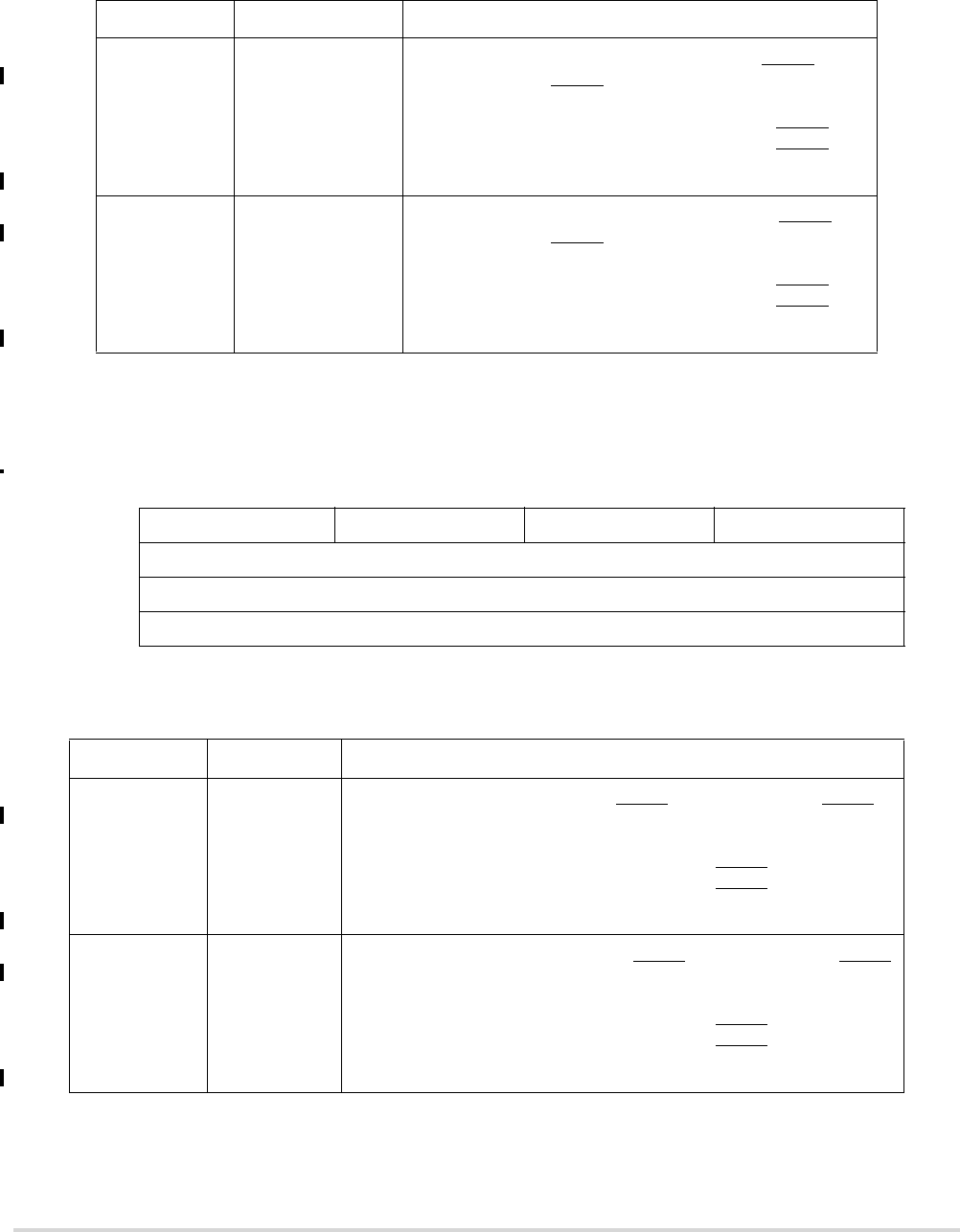

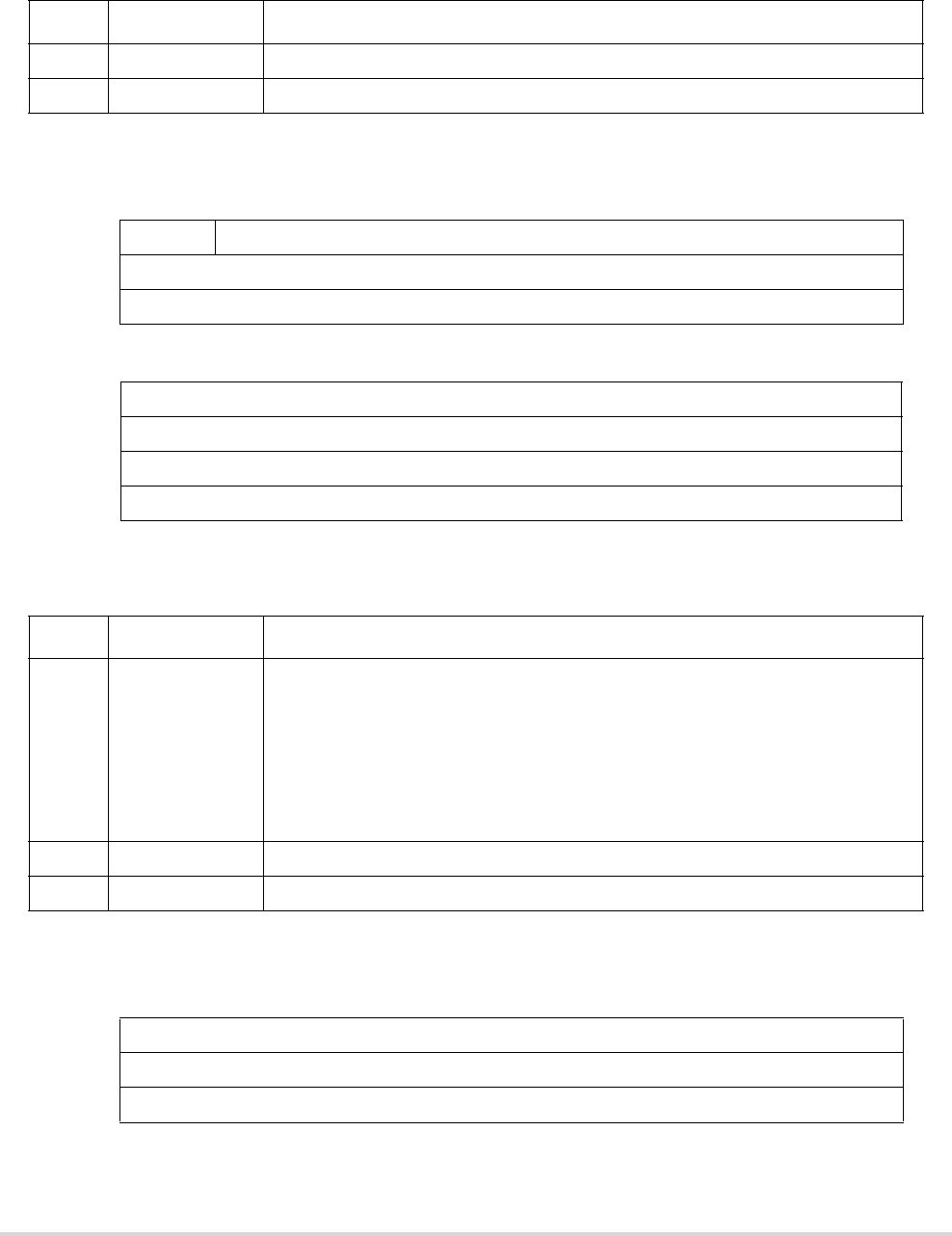

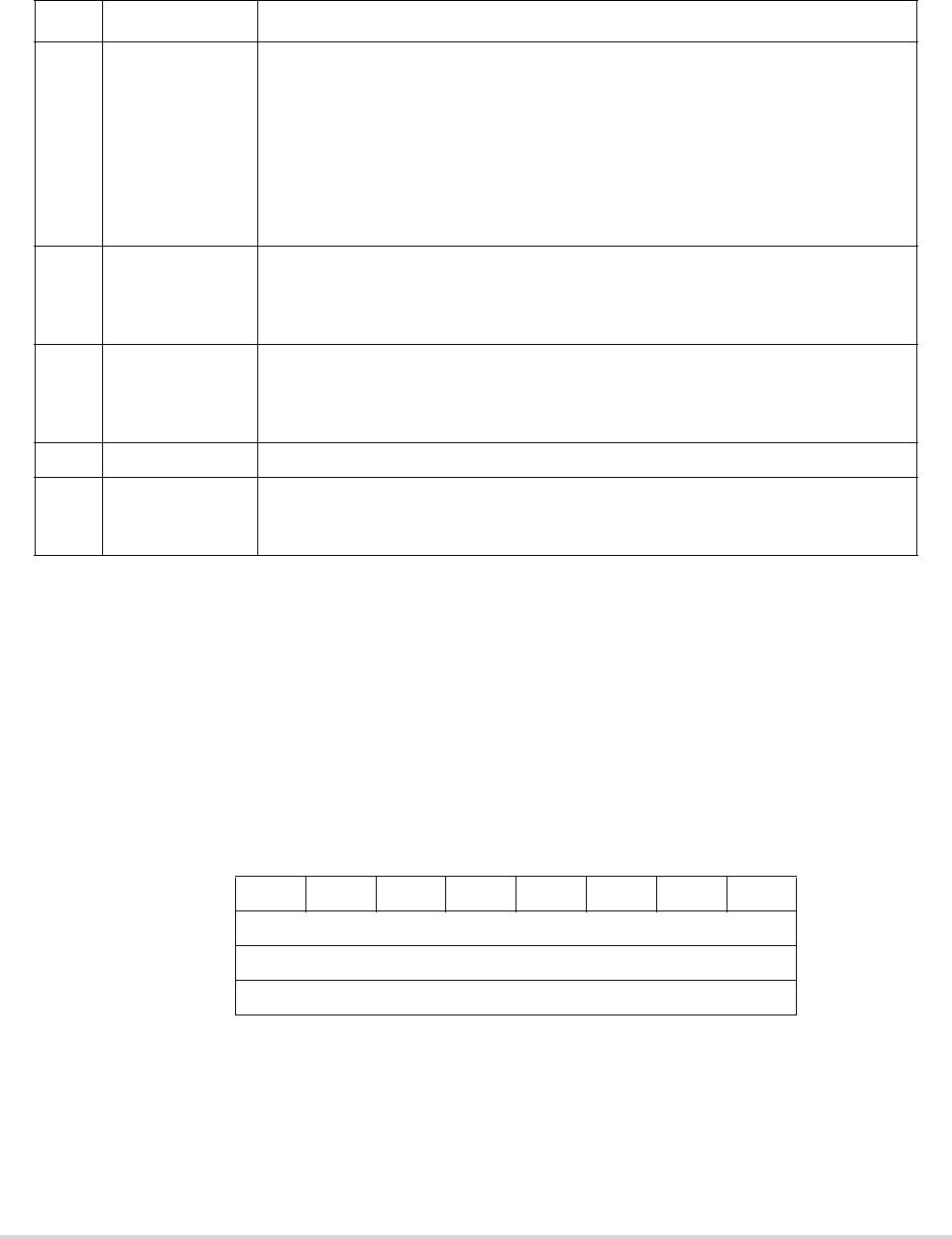

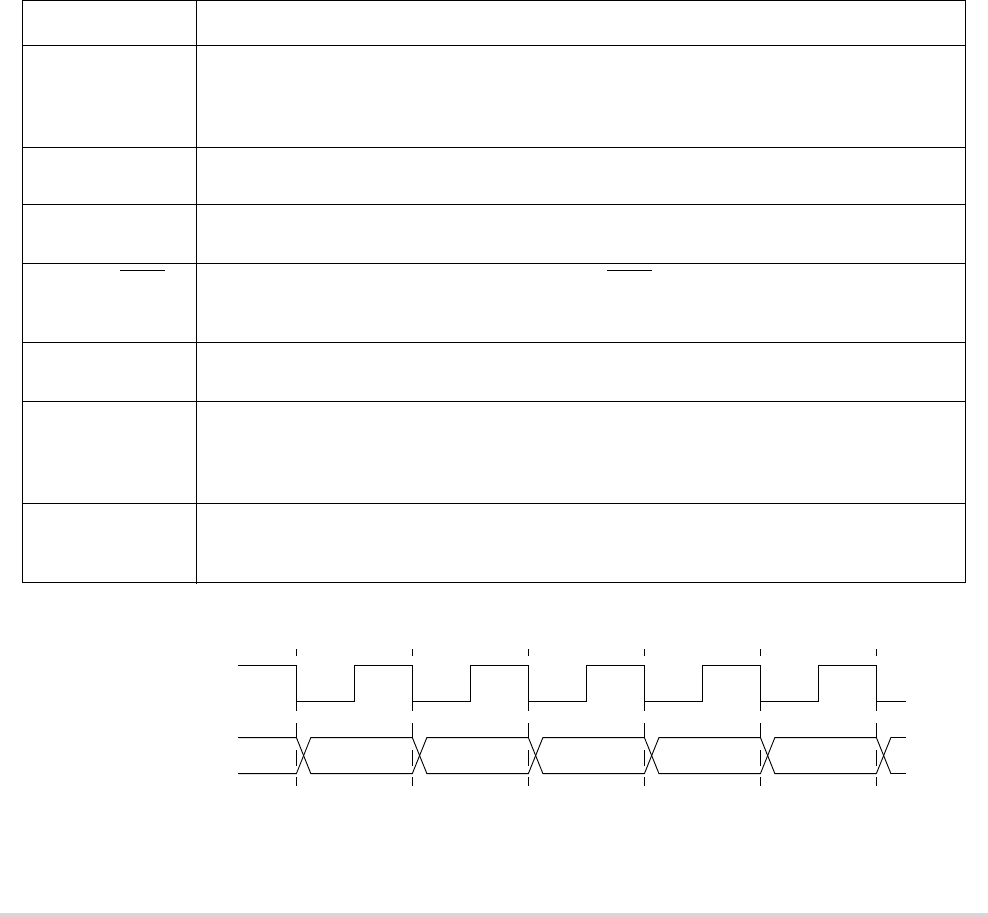

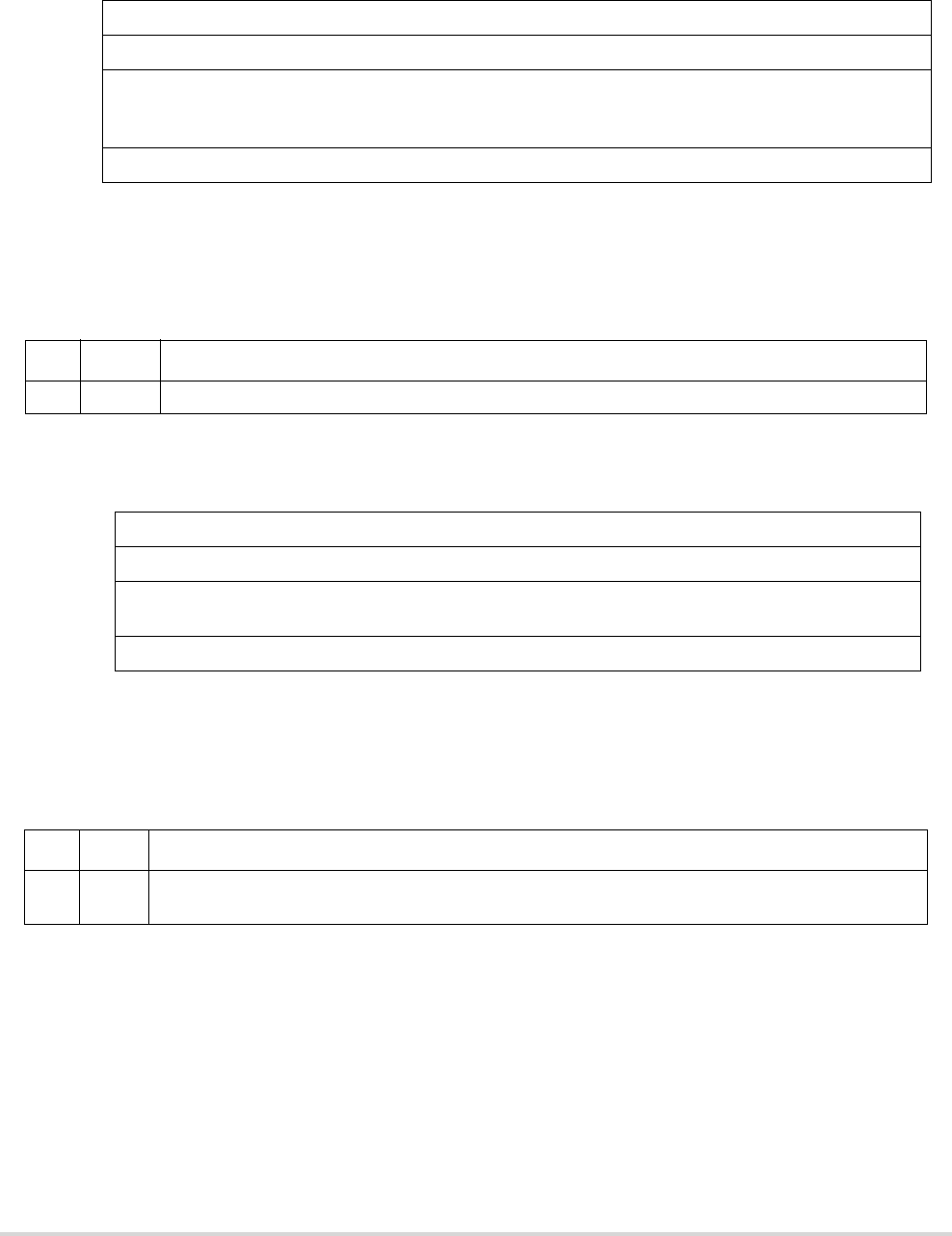

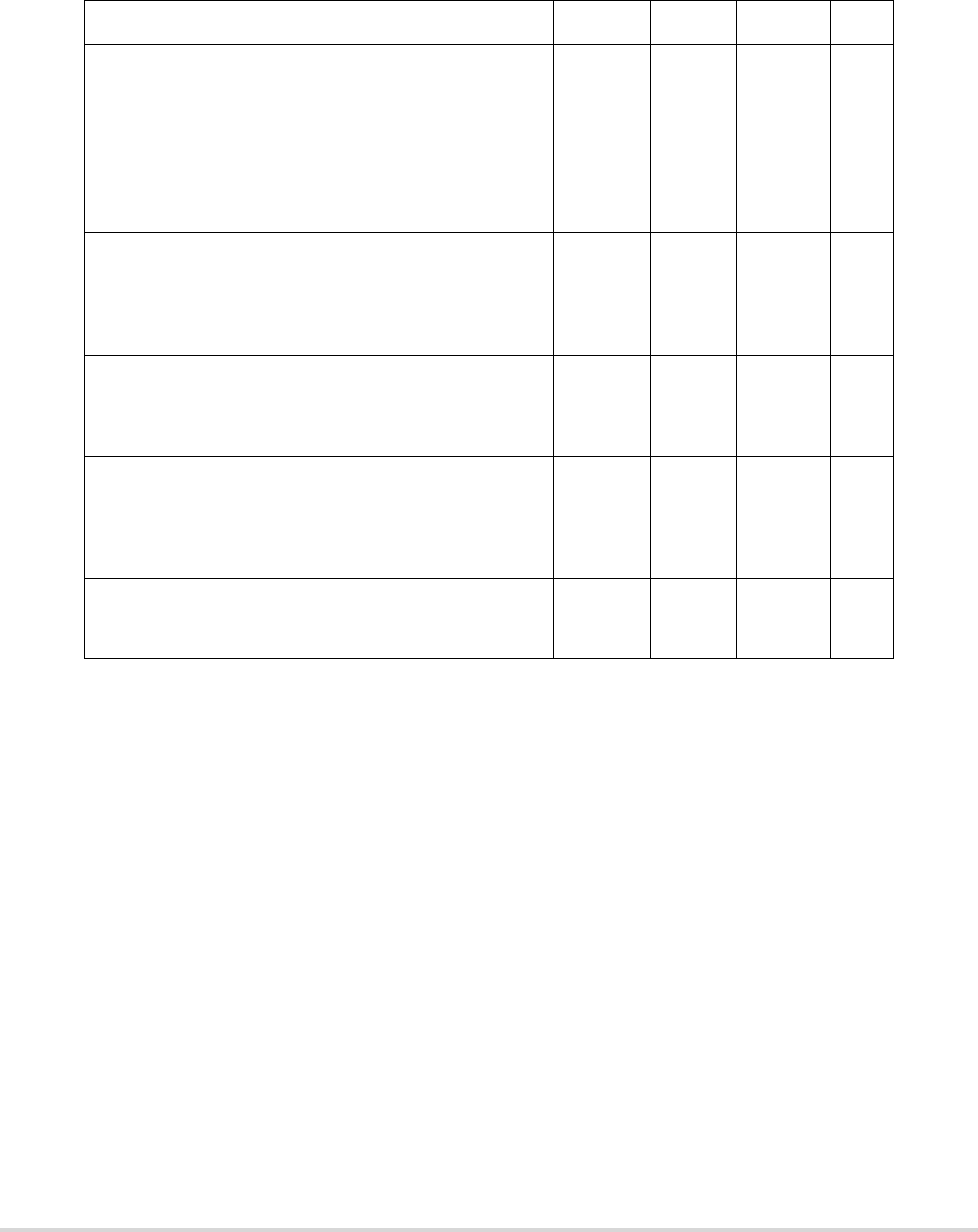

- Table 27-22. Trigger Events

- Table 27-23. Status Bits

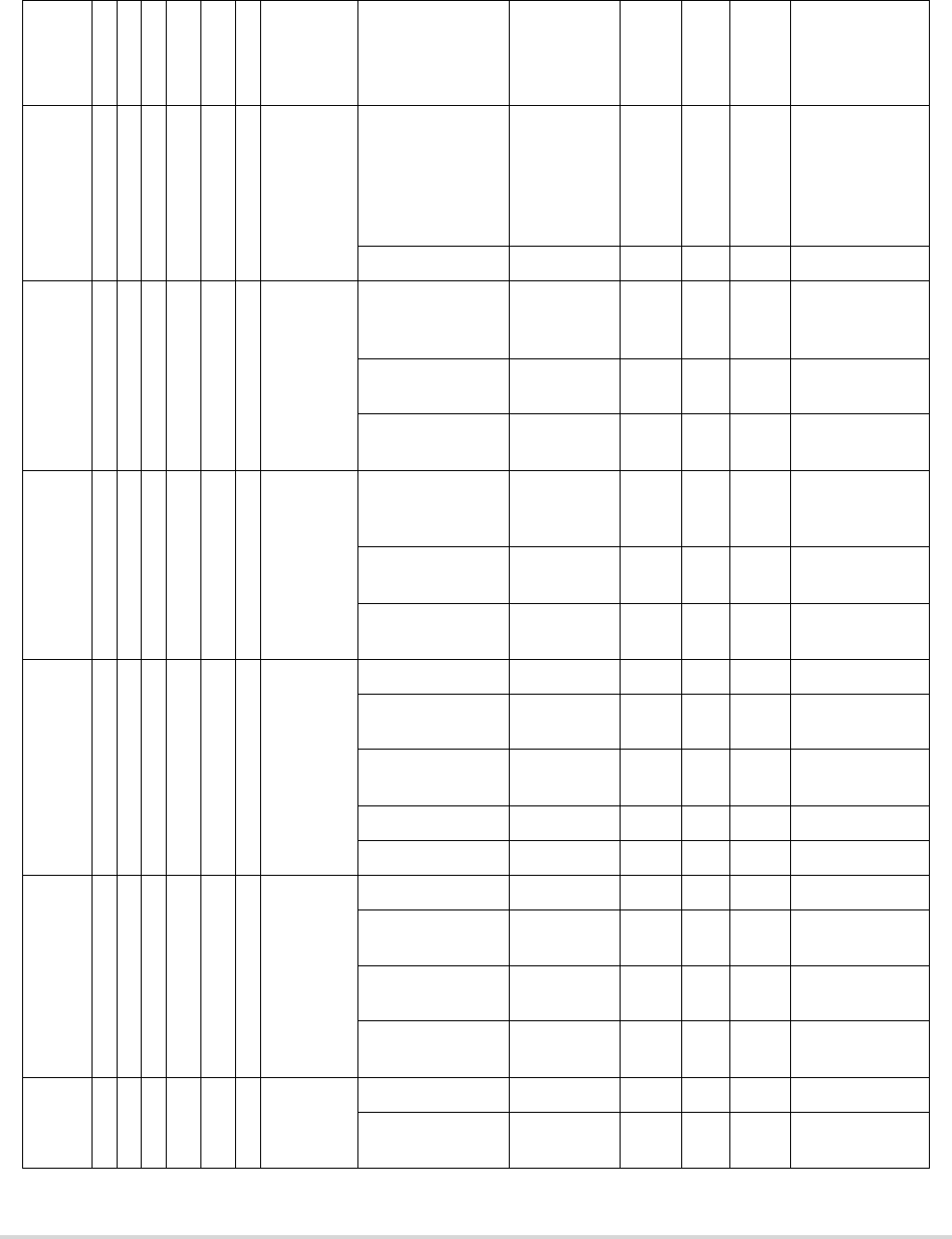

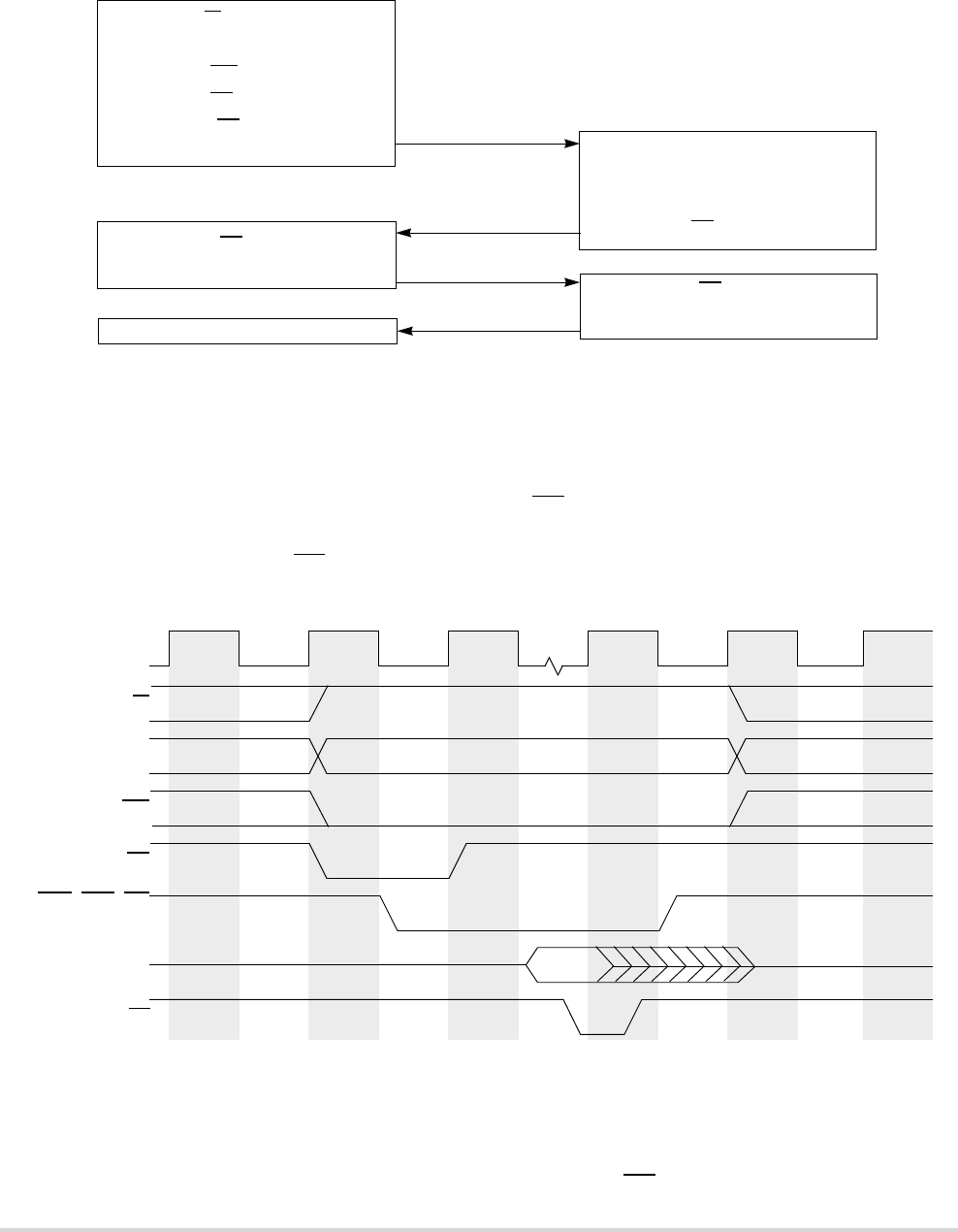

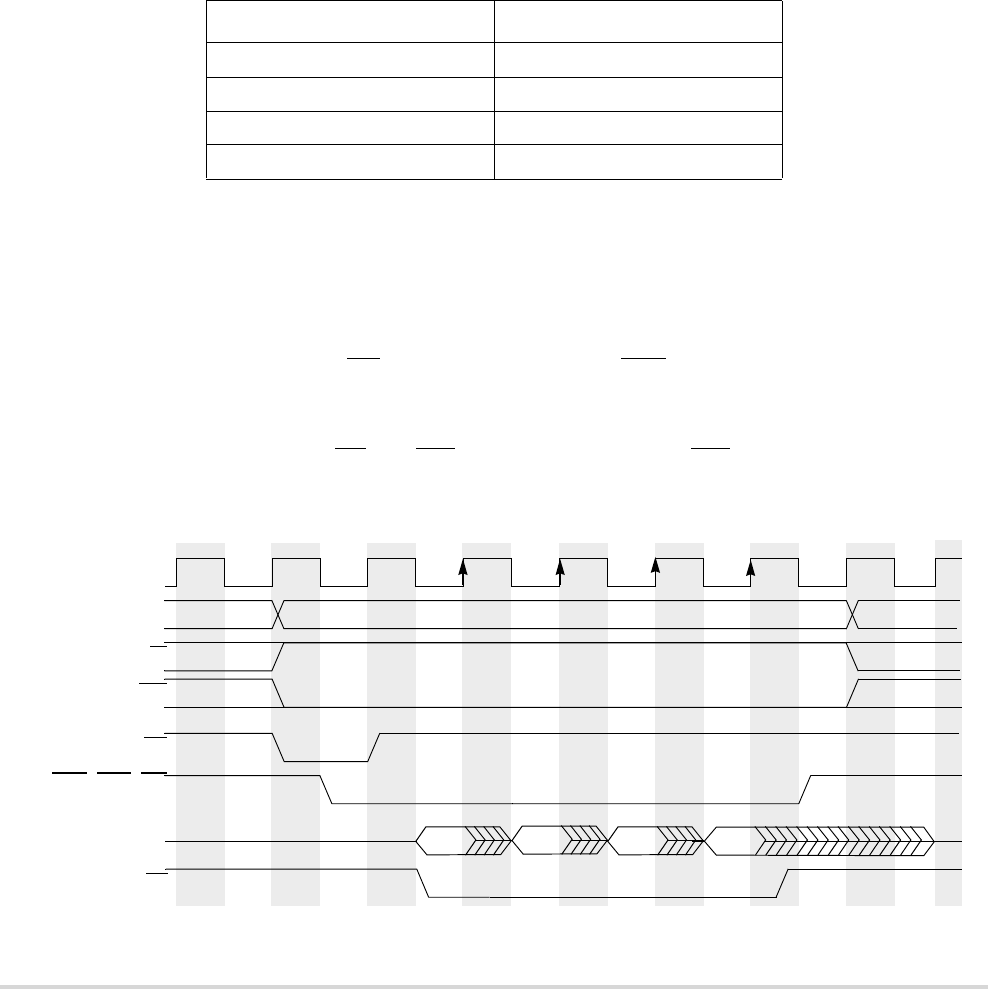

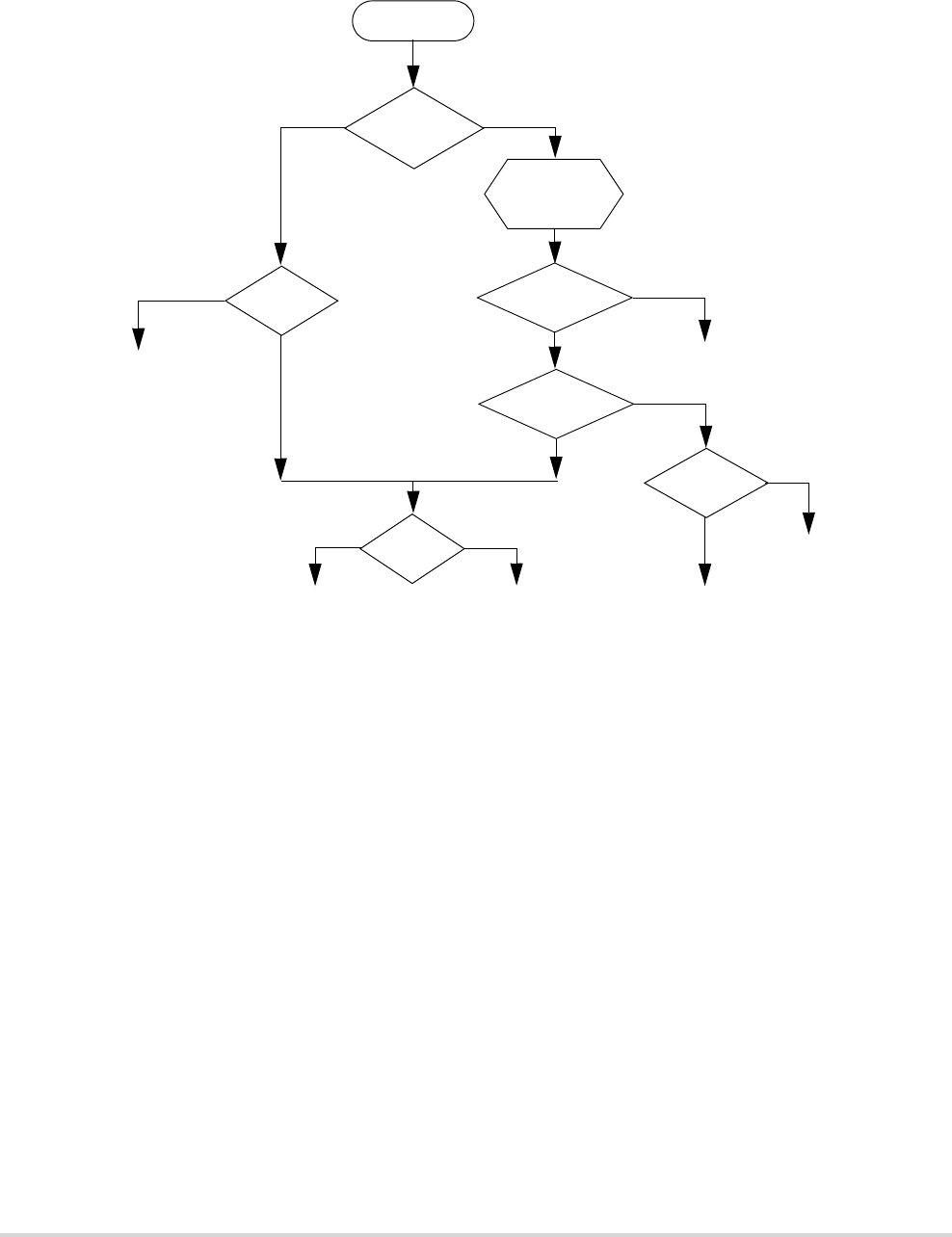

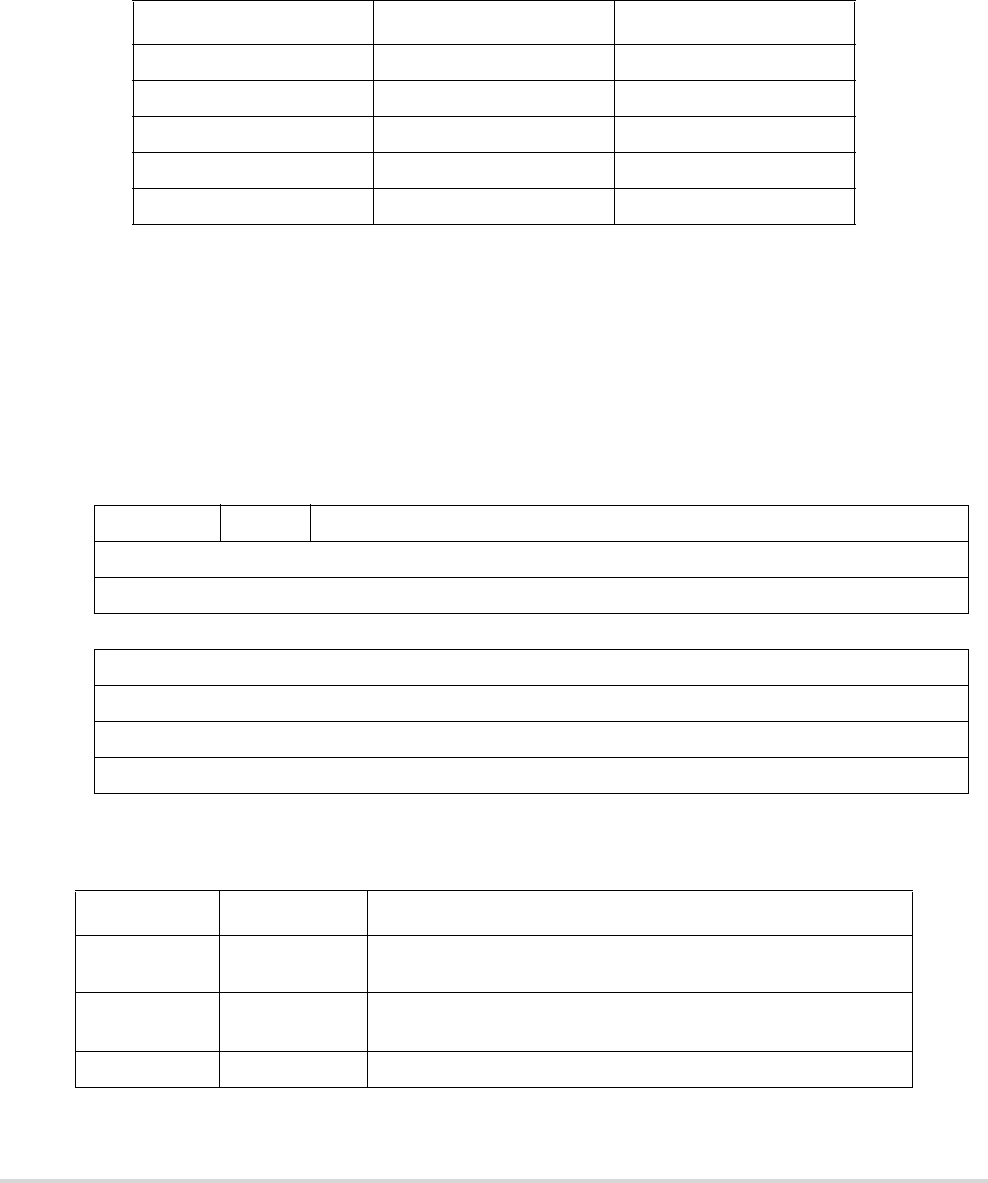

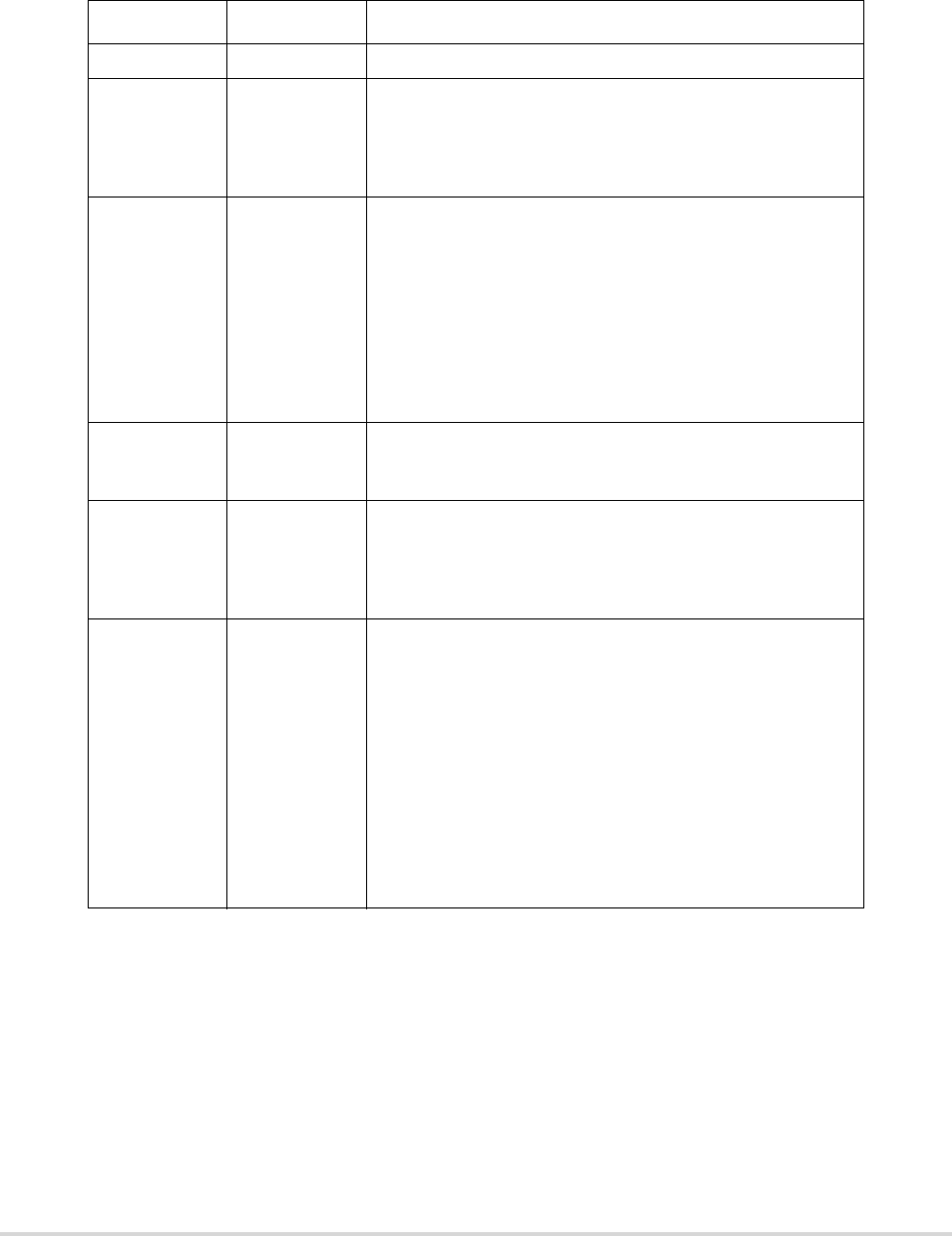

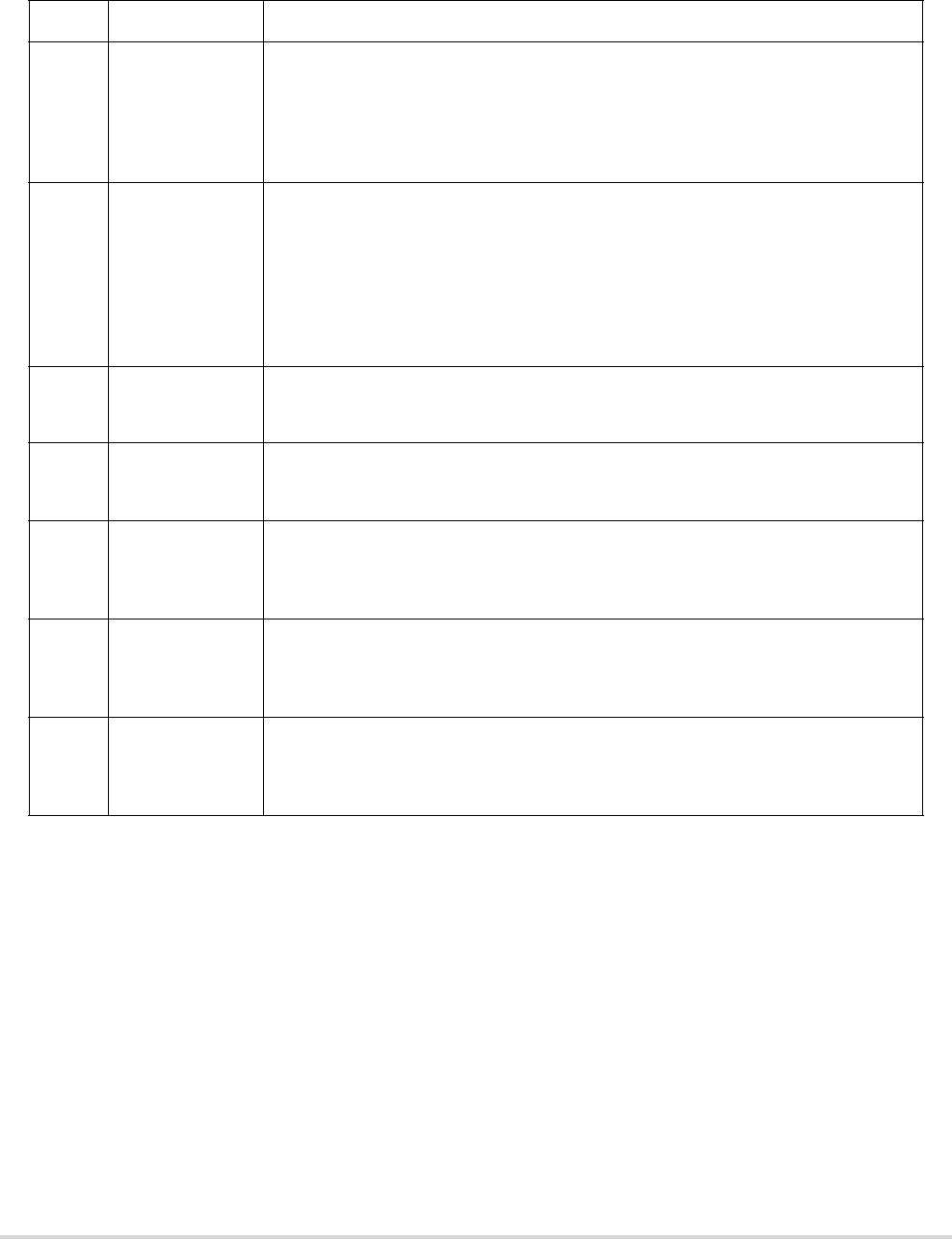

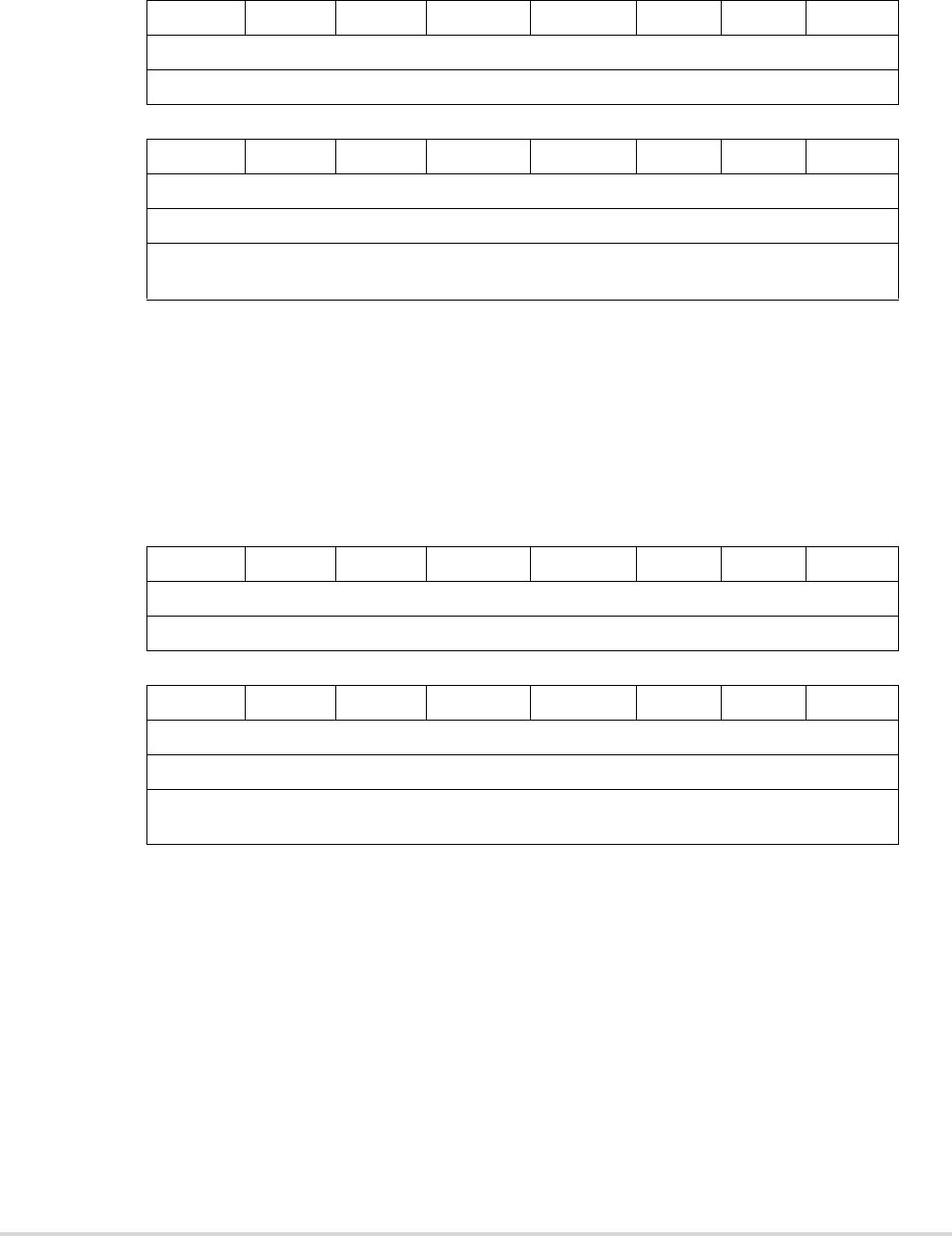

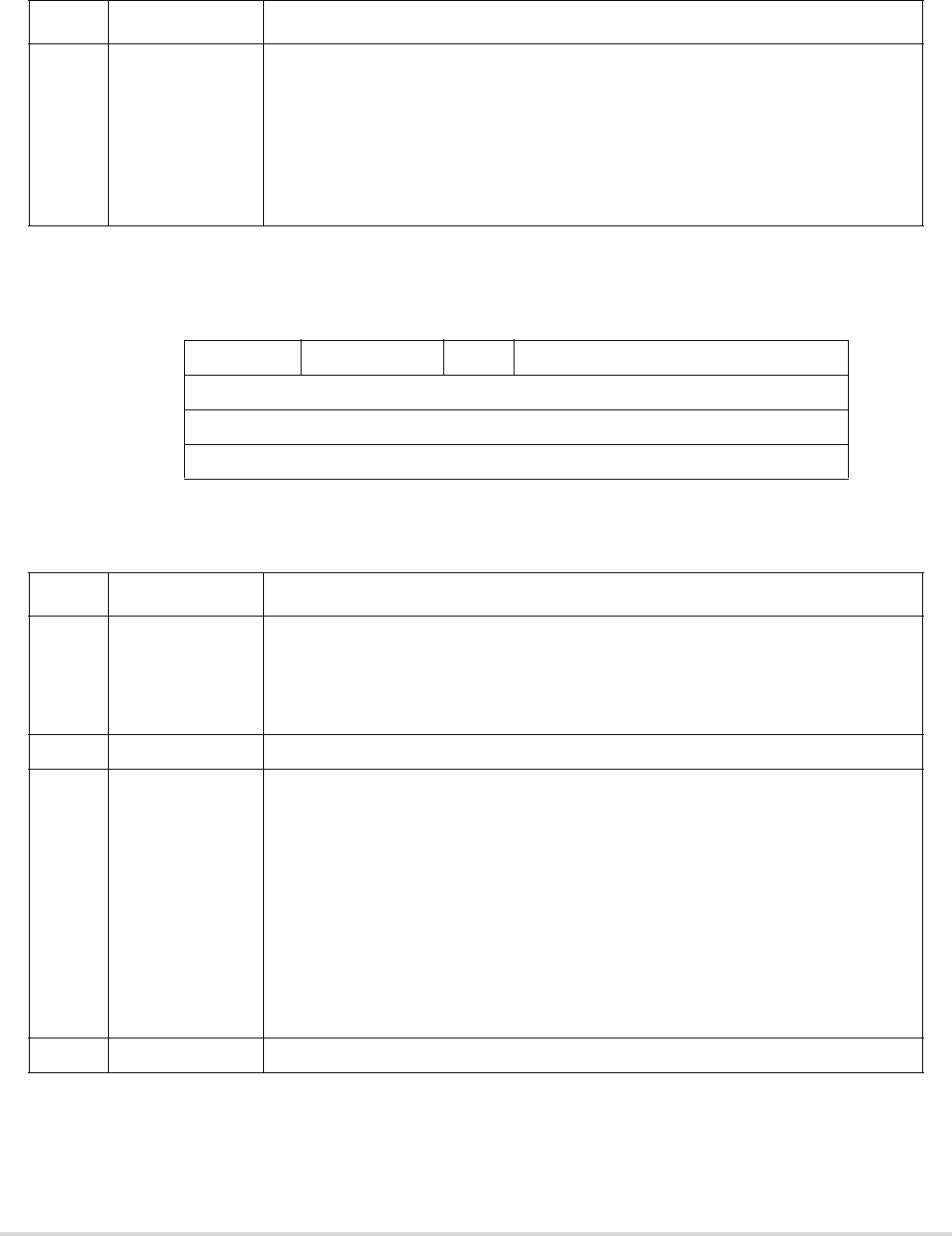

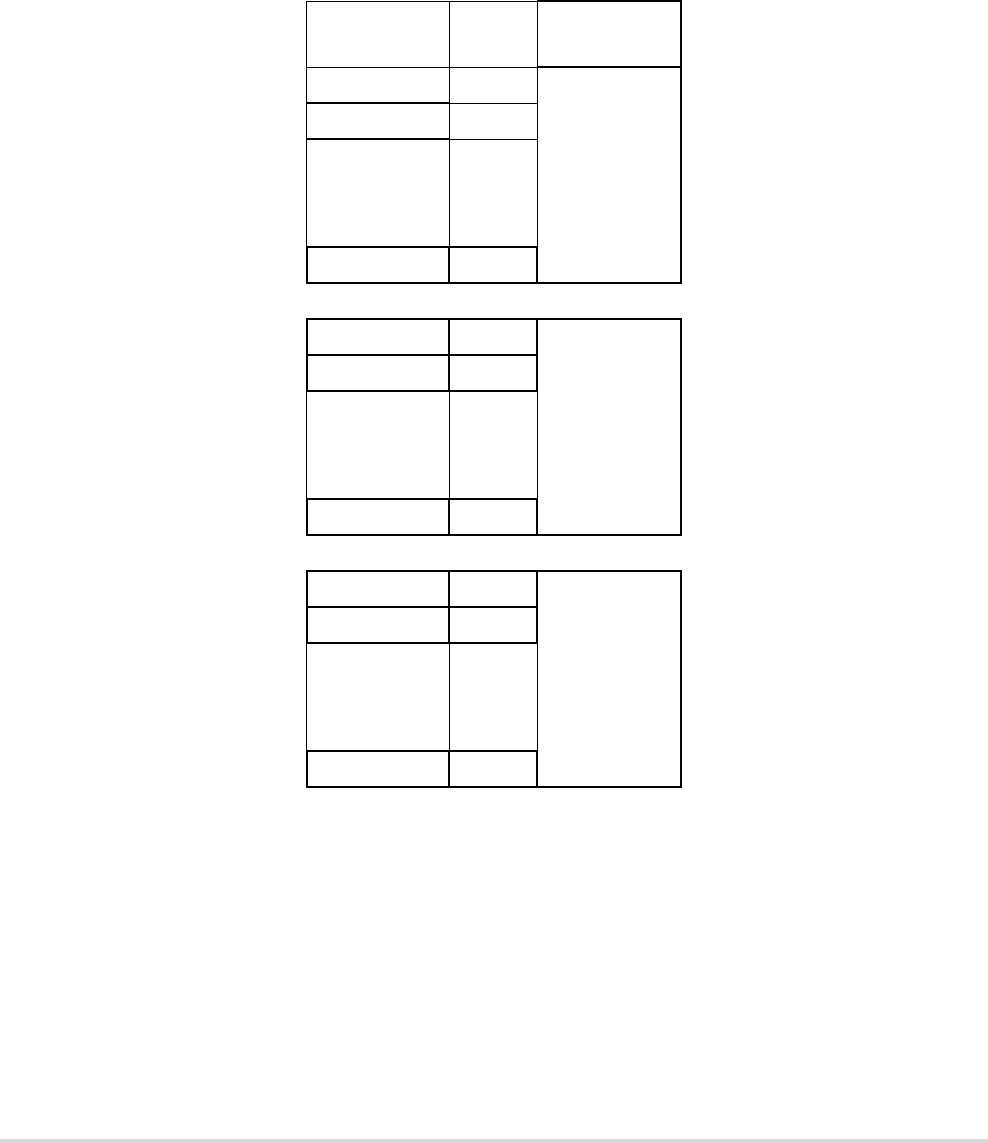

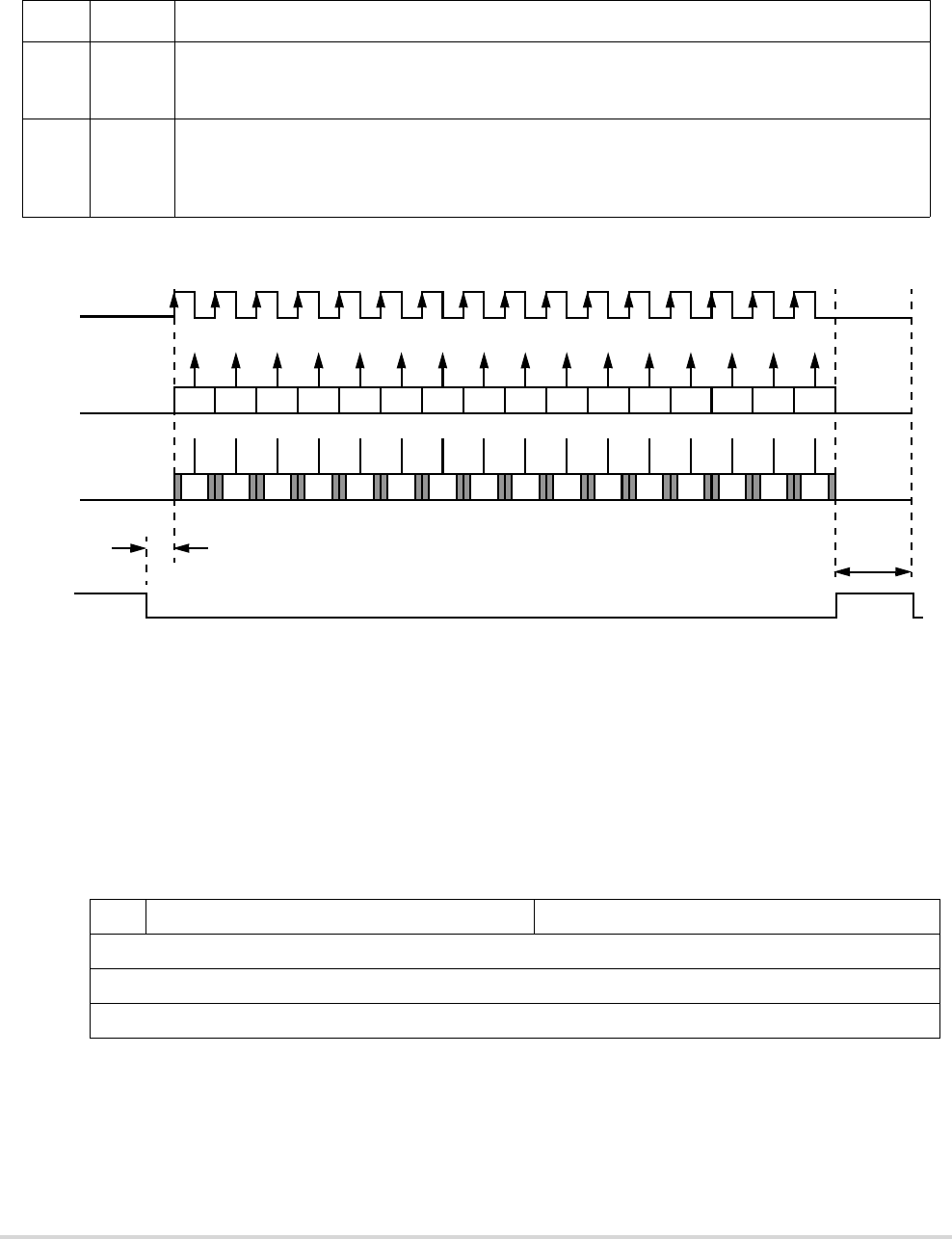

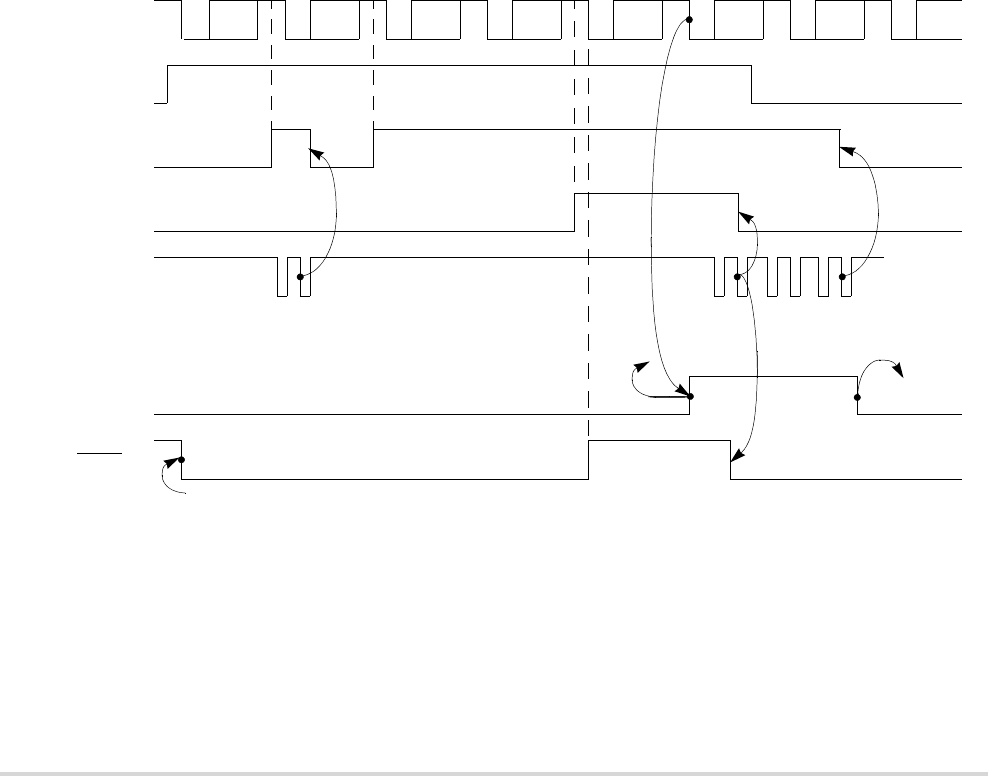

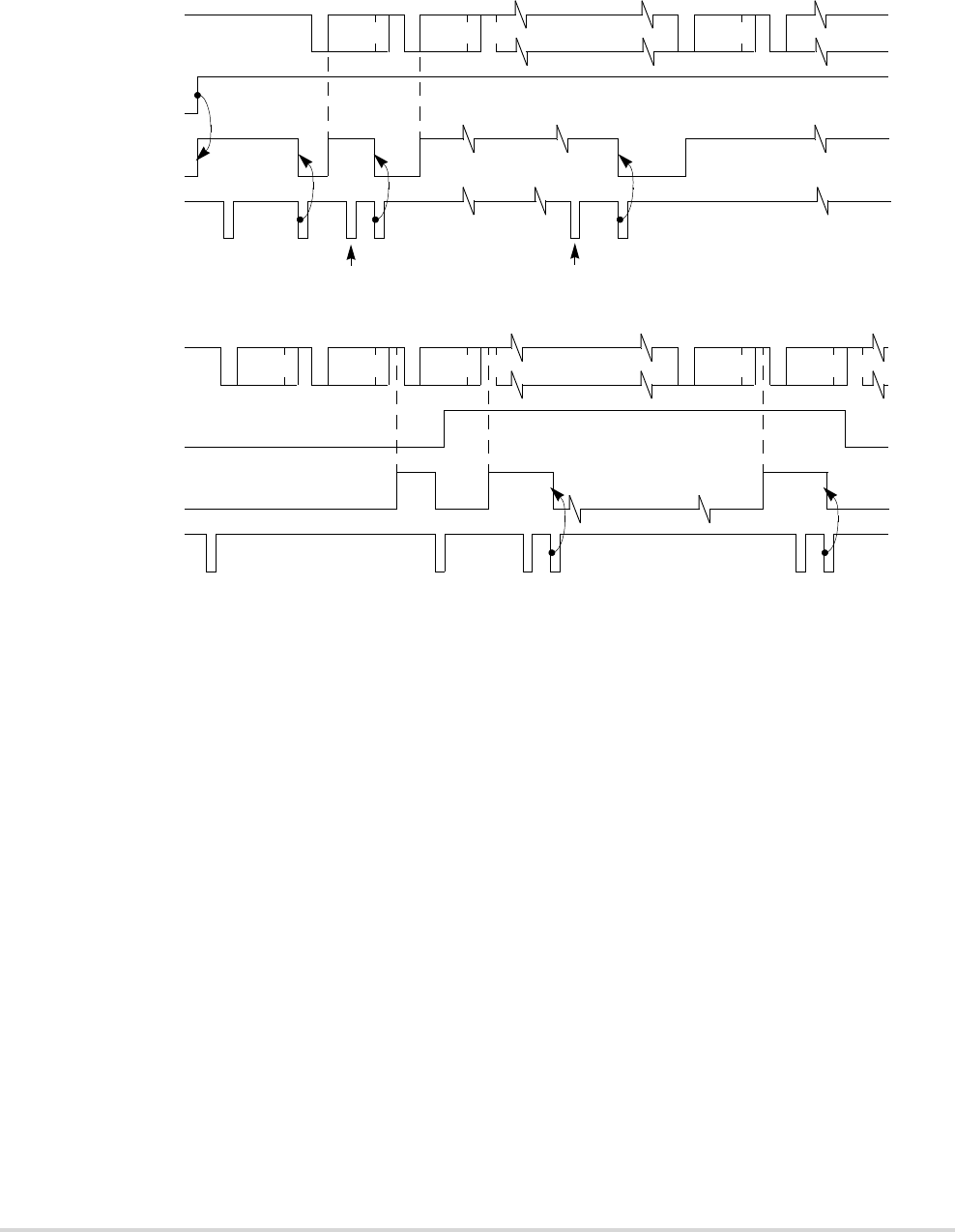

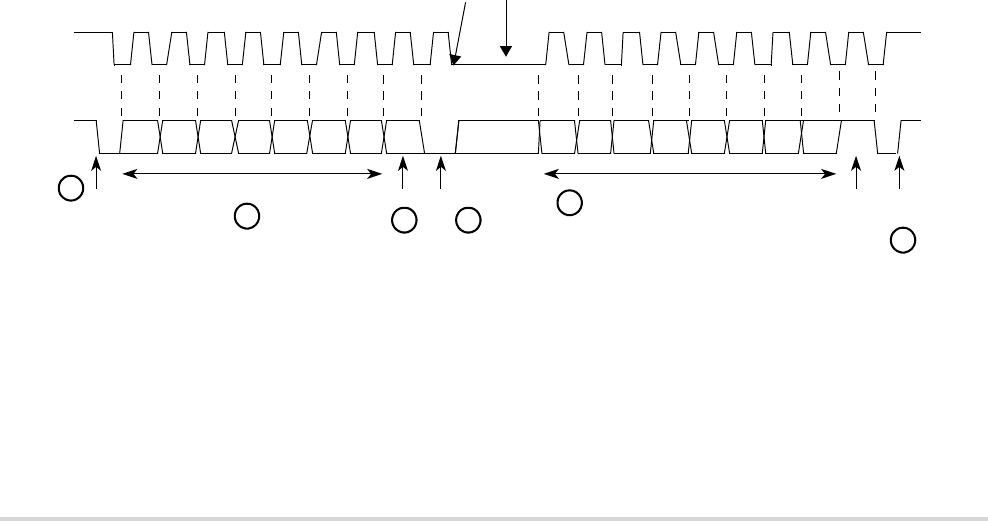

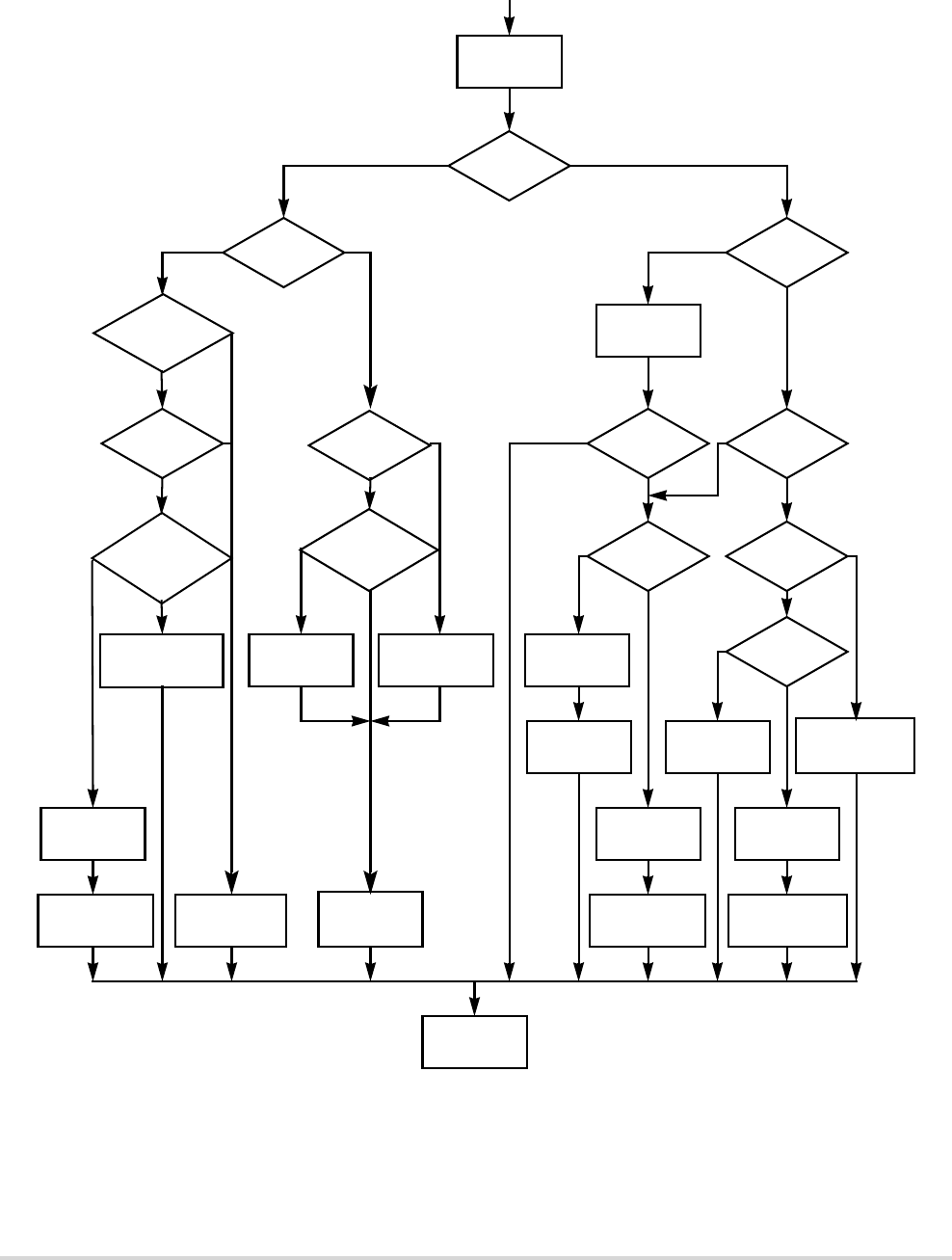

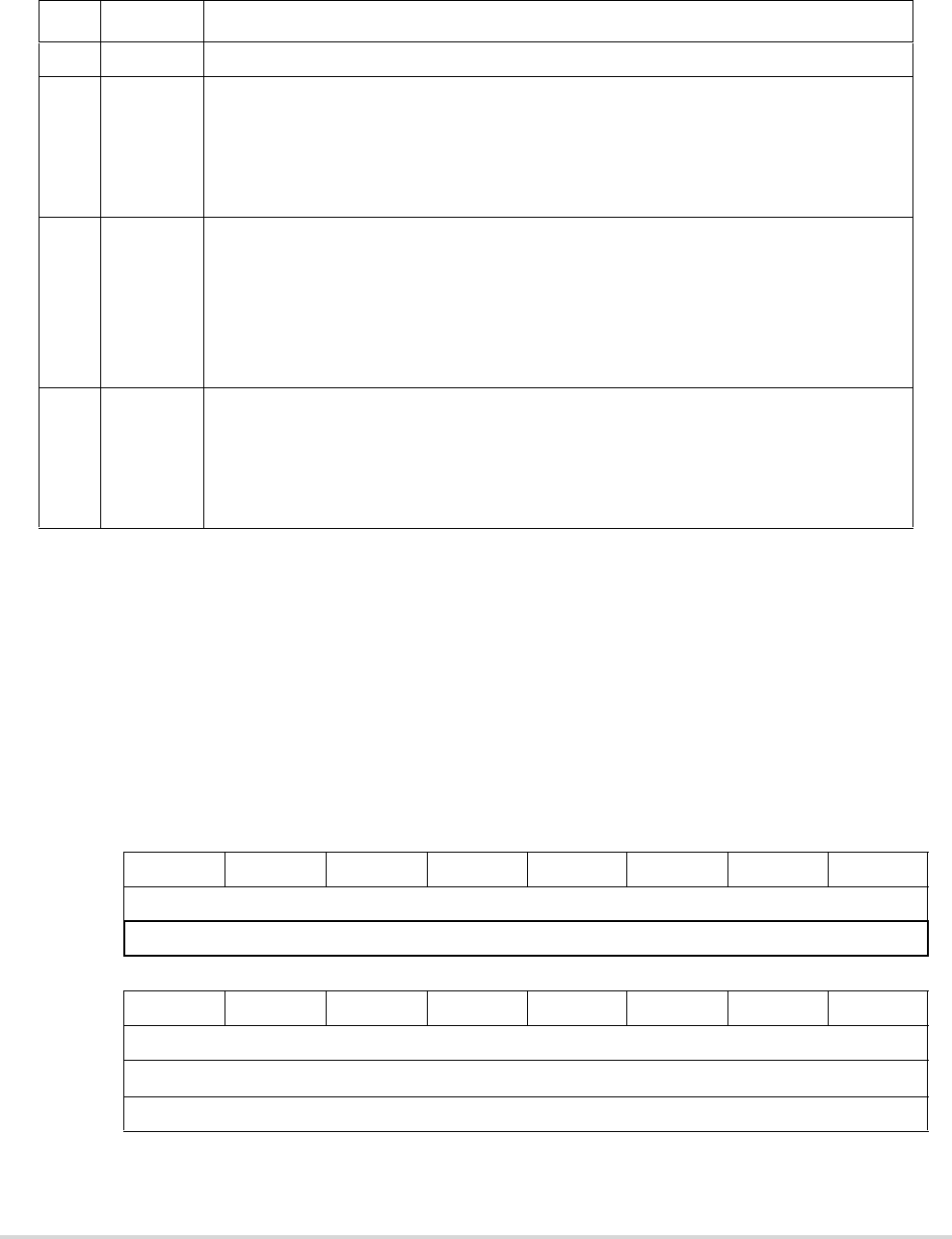

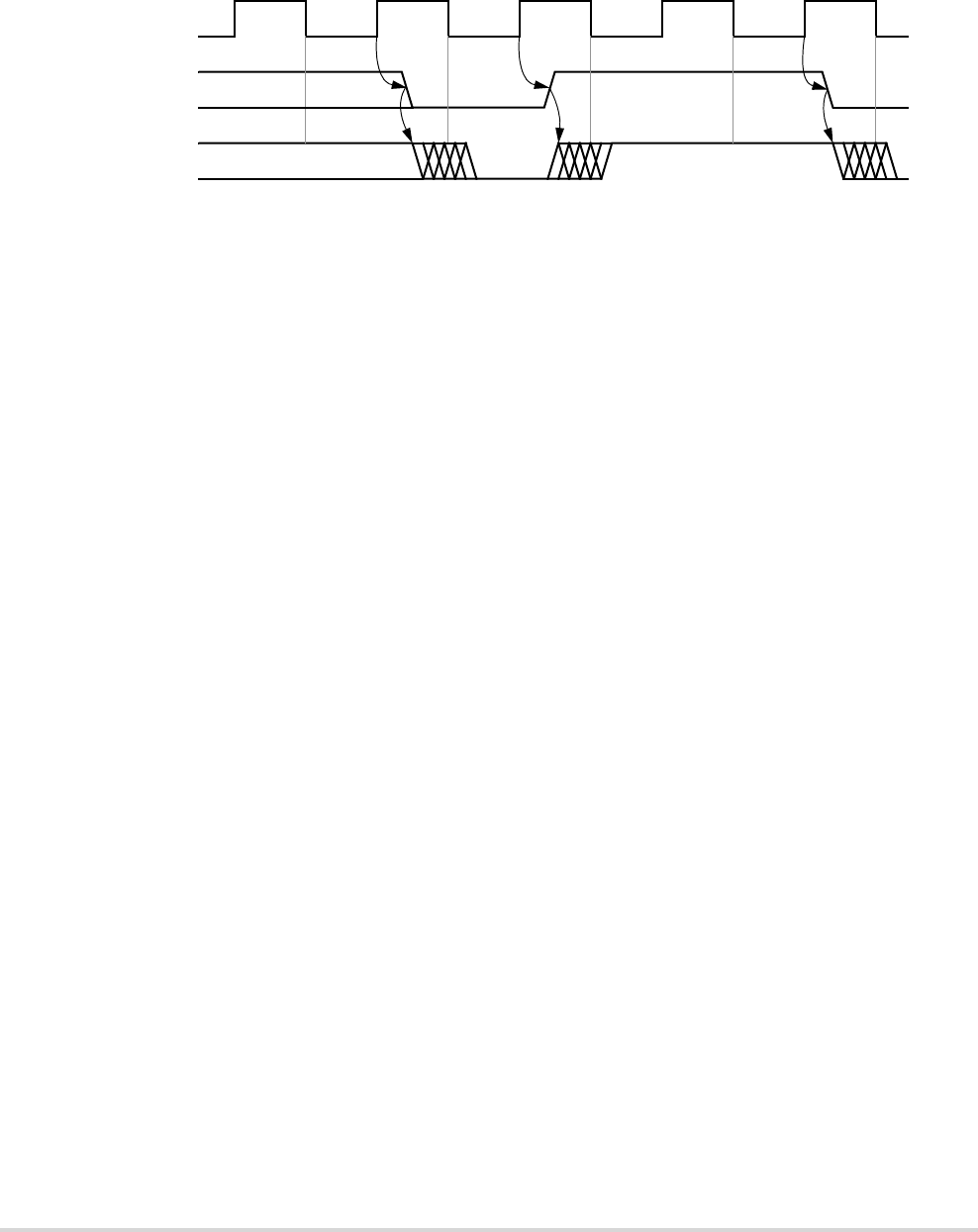

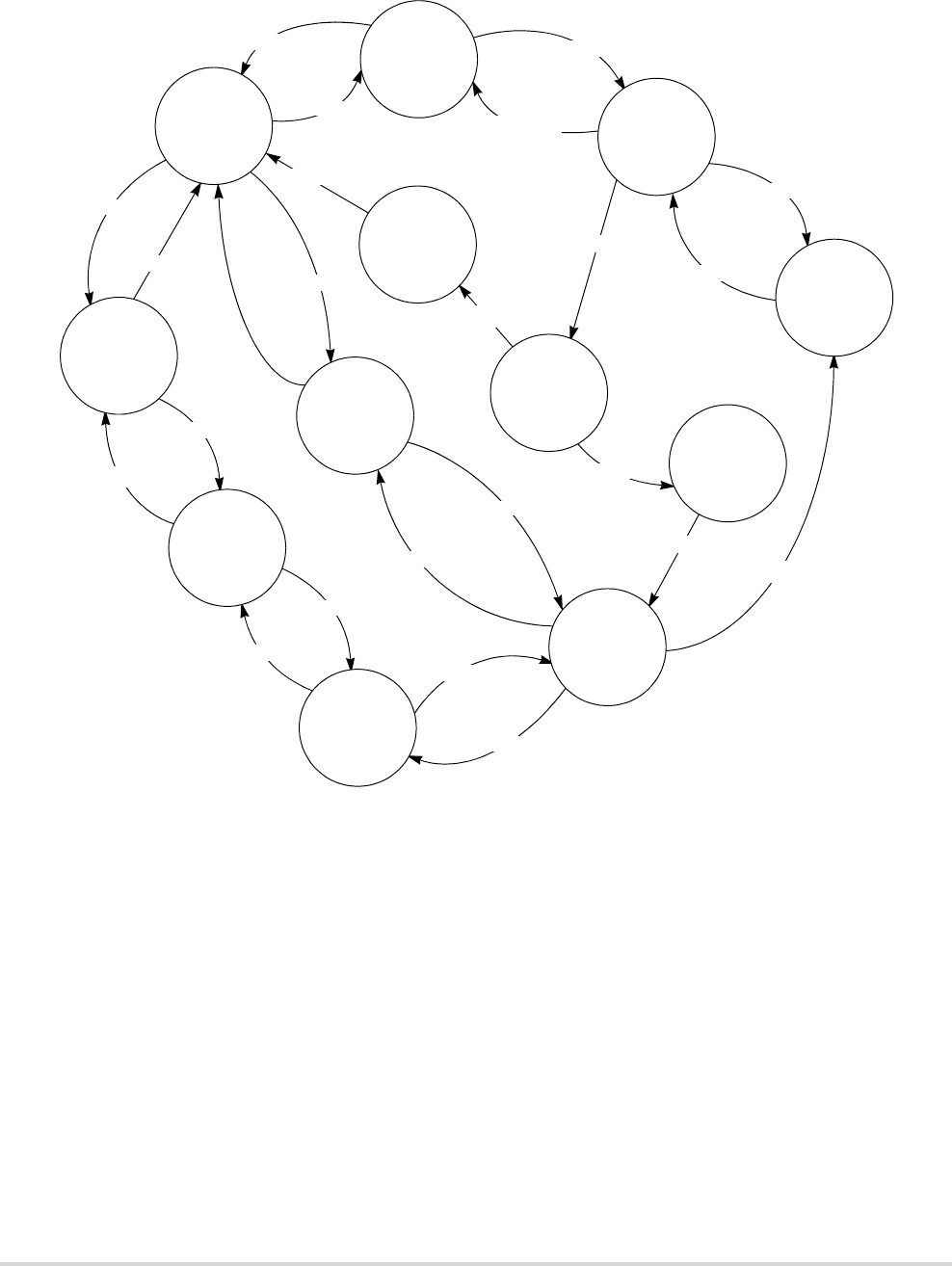

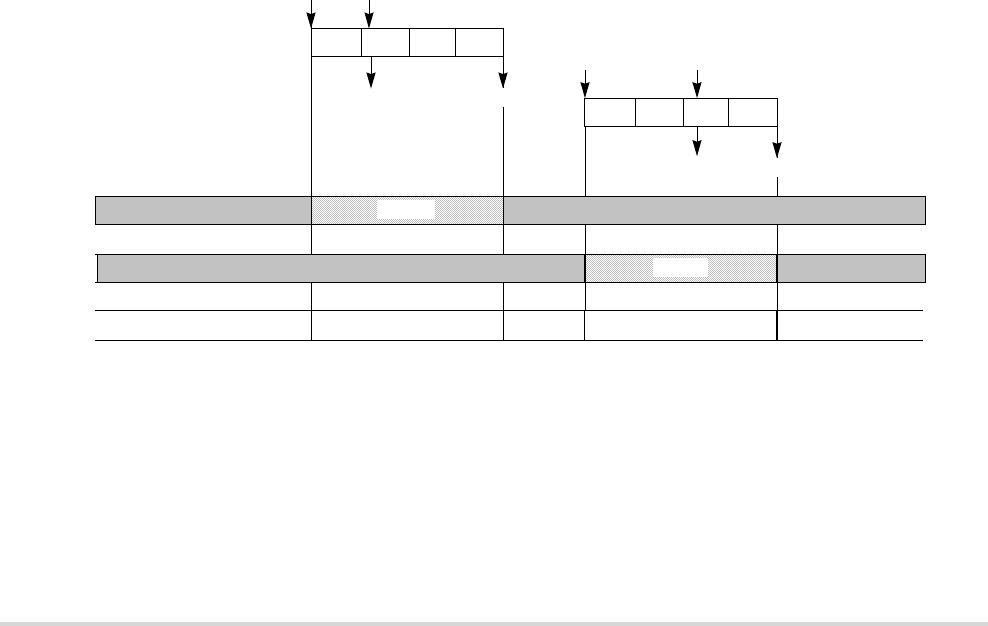

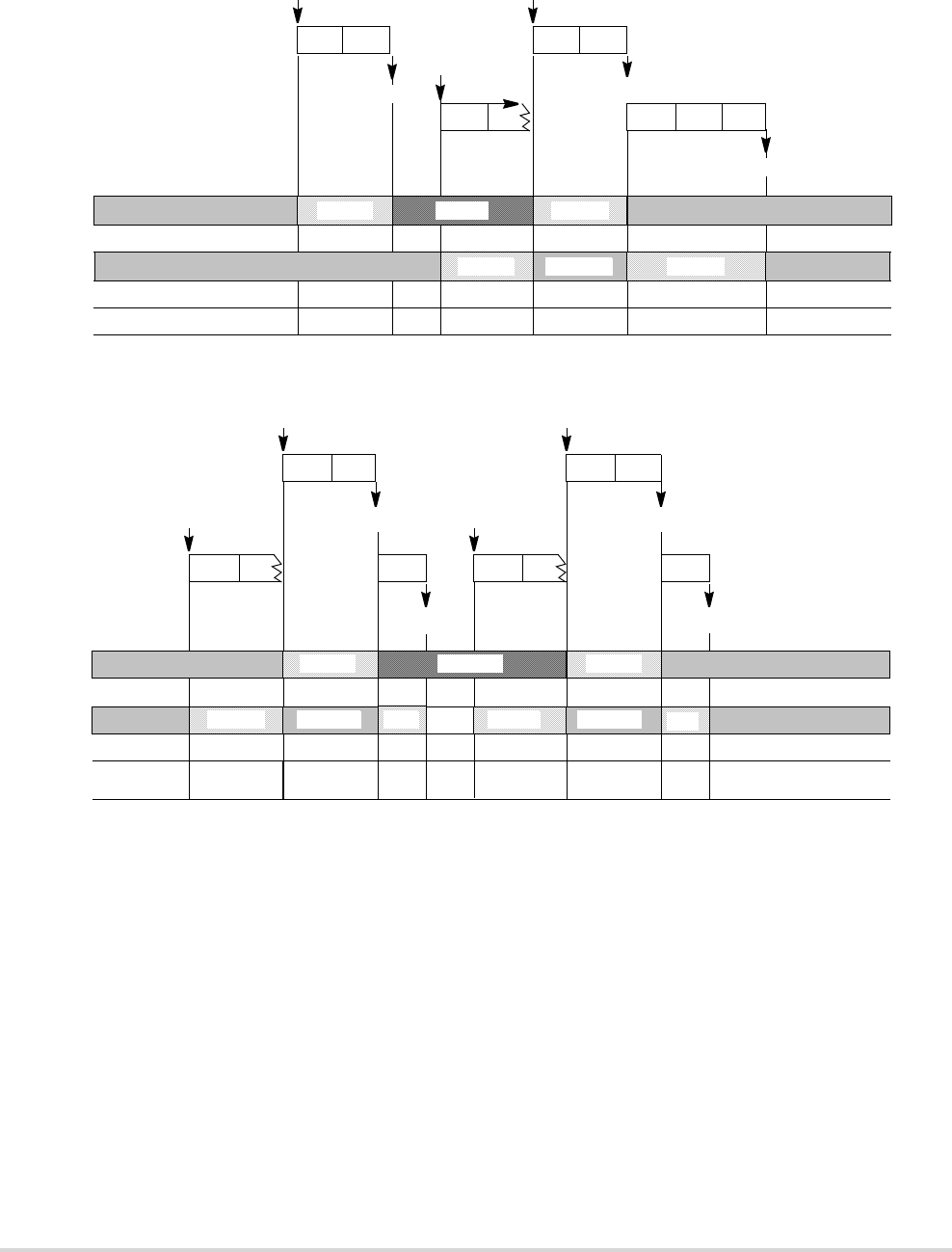

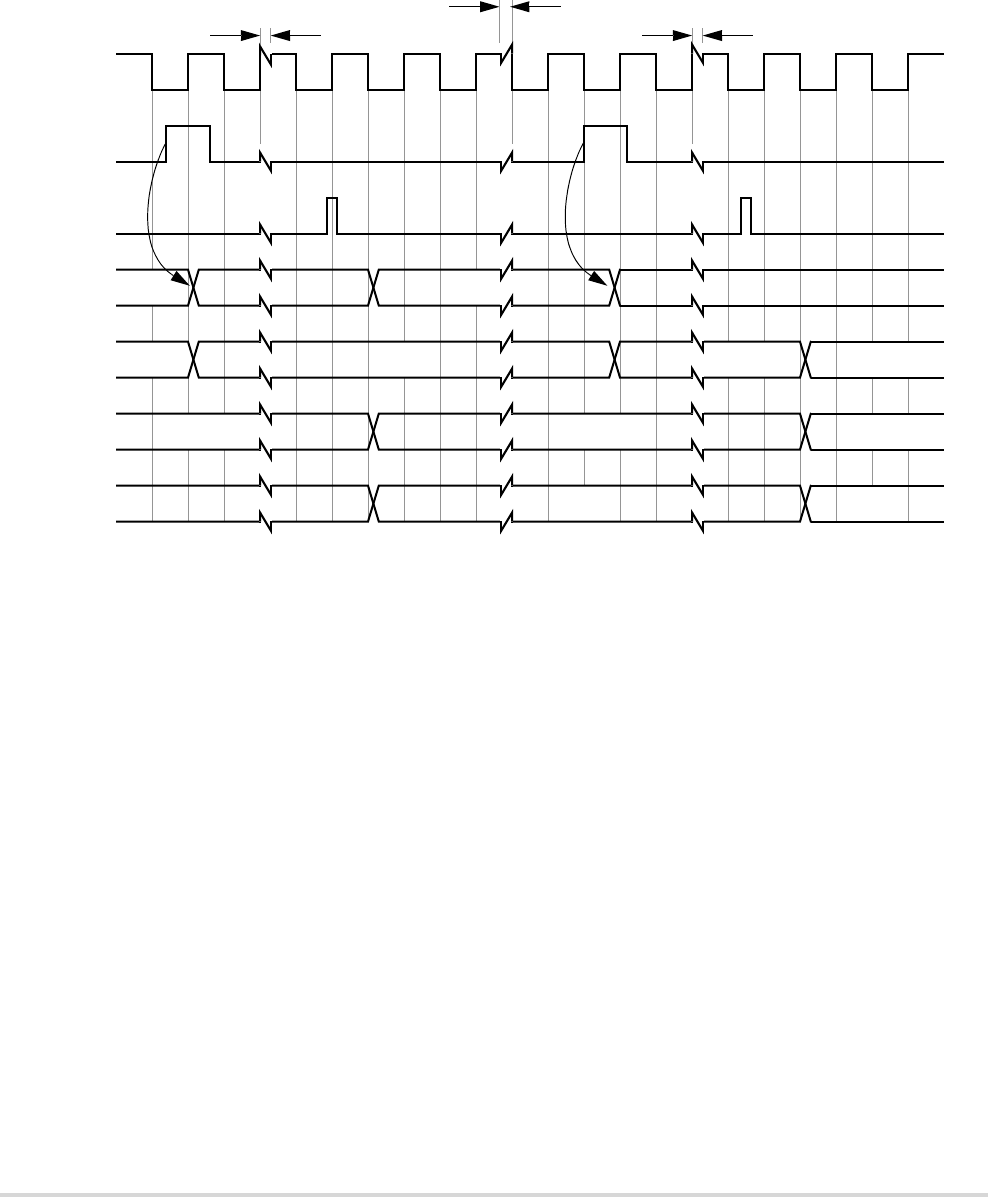

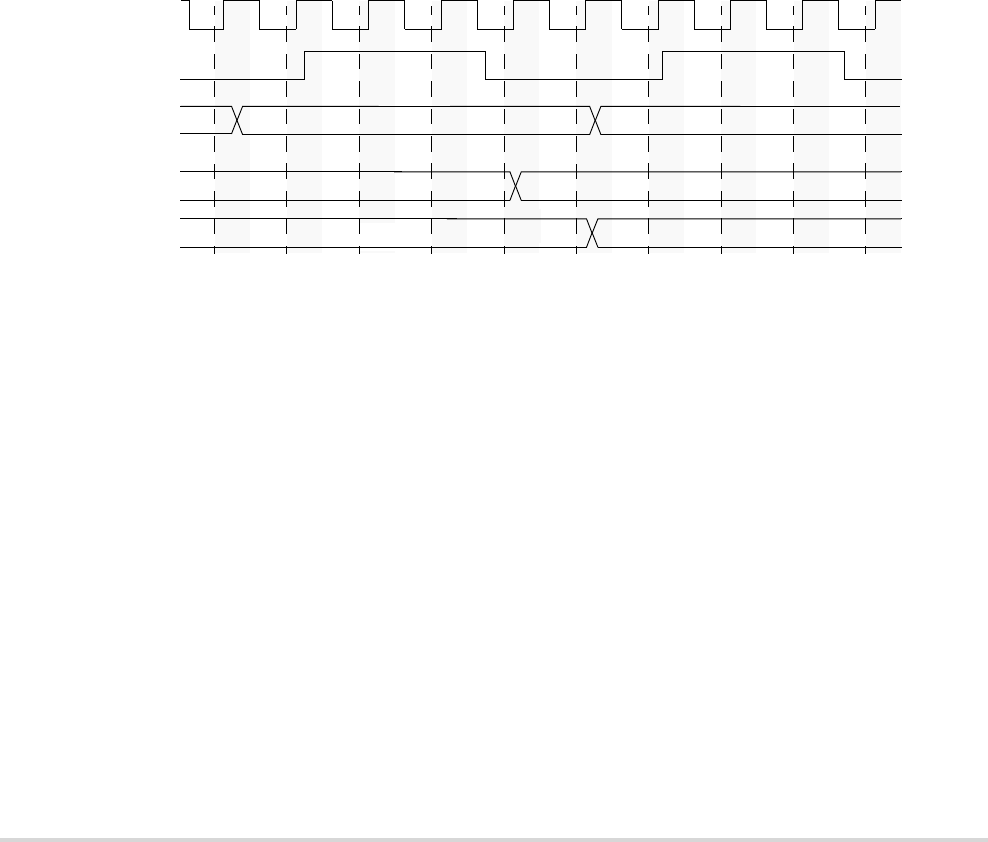

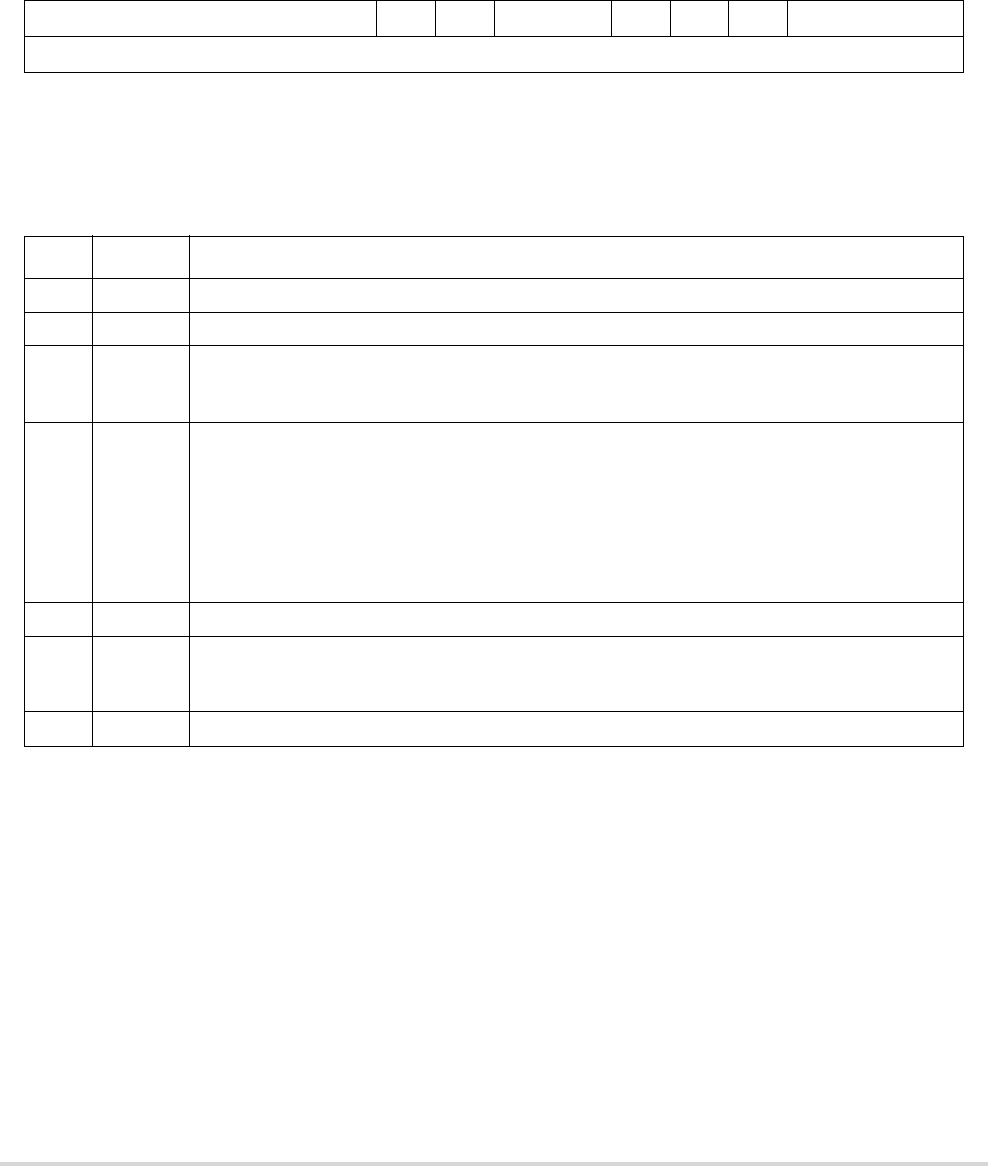

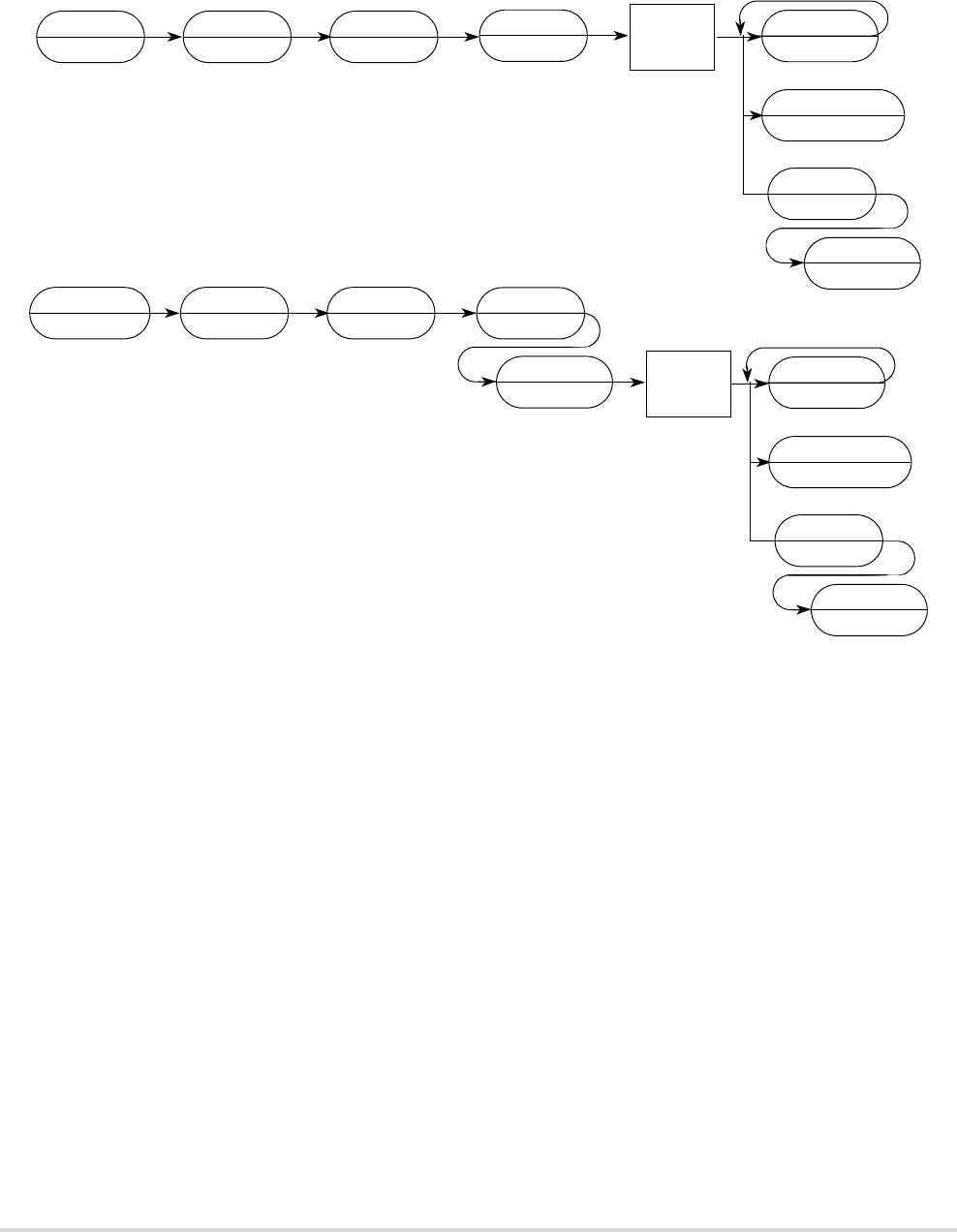

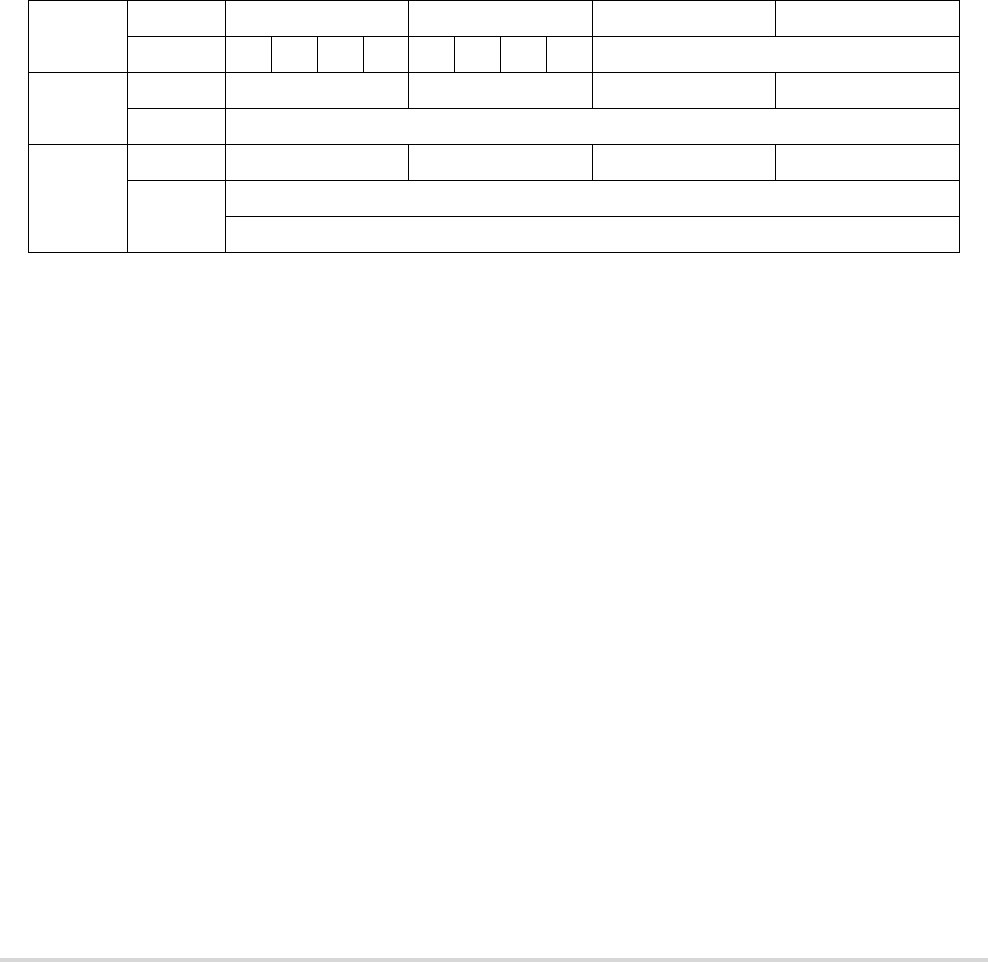

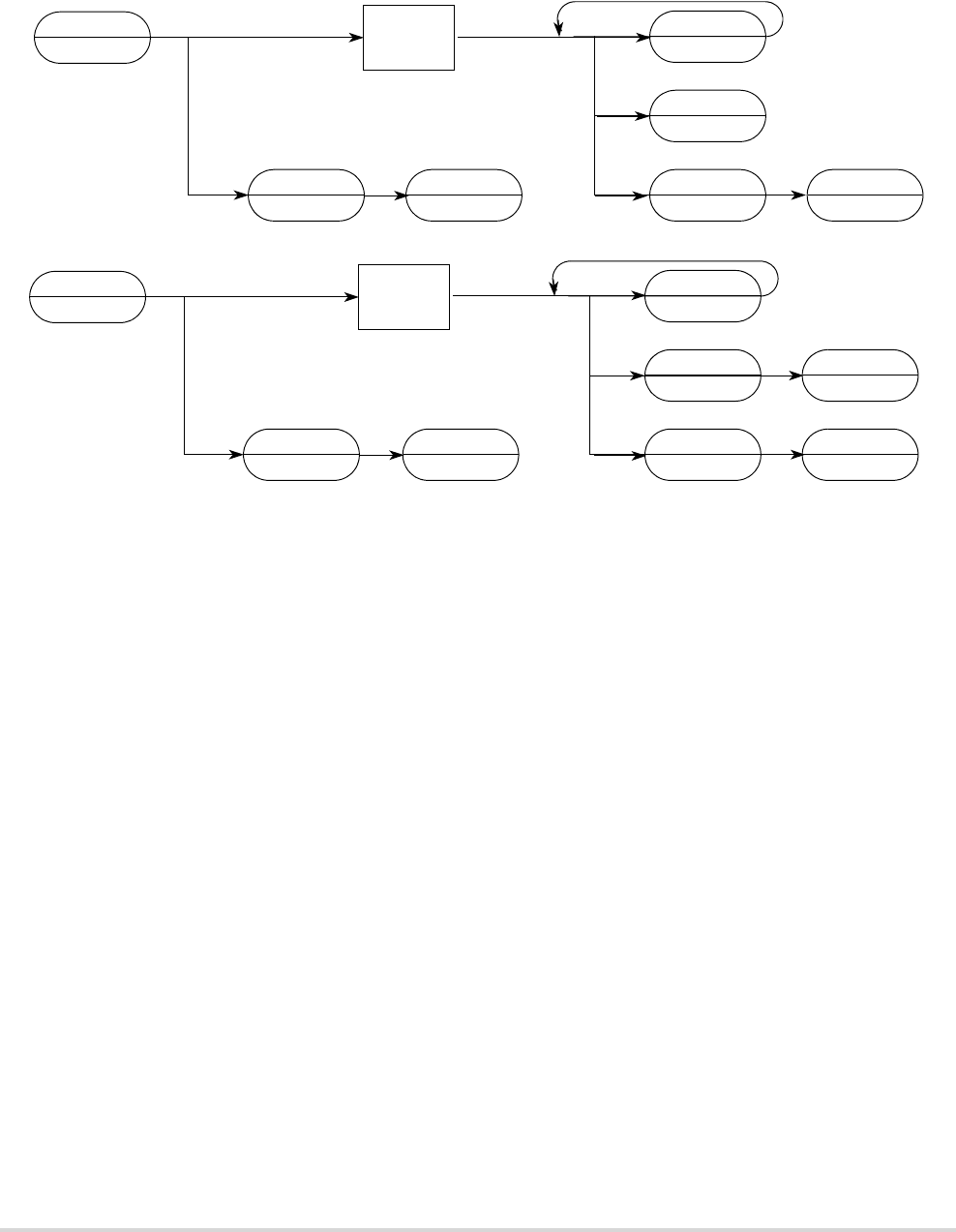

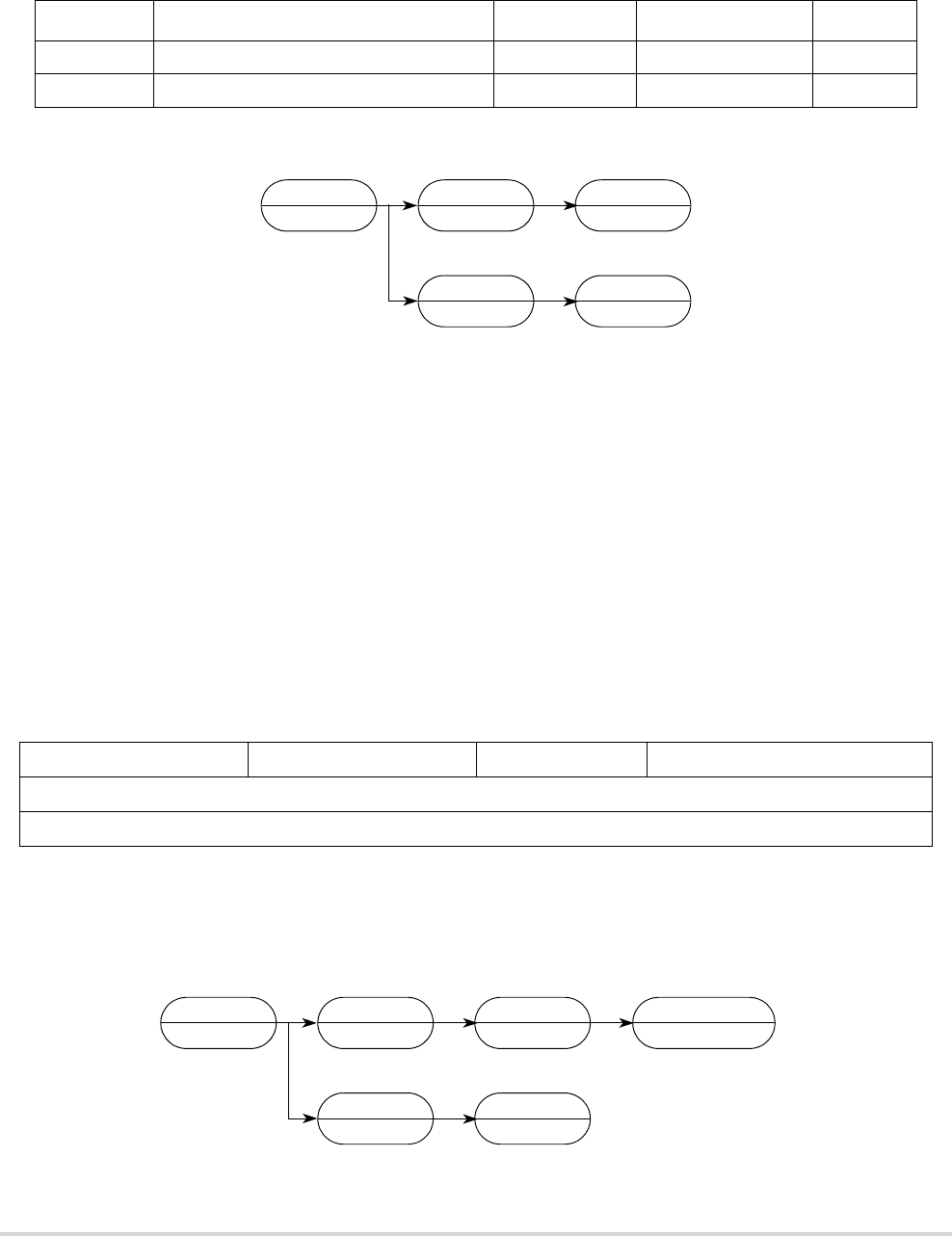

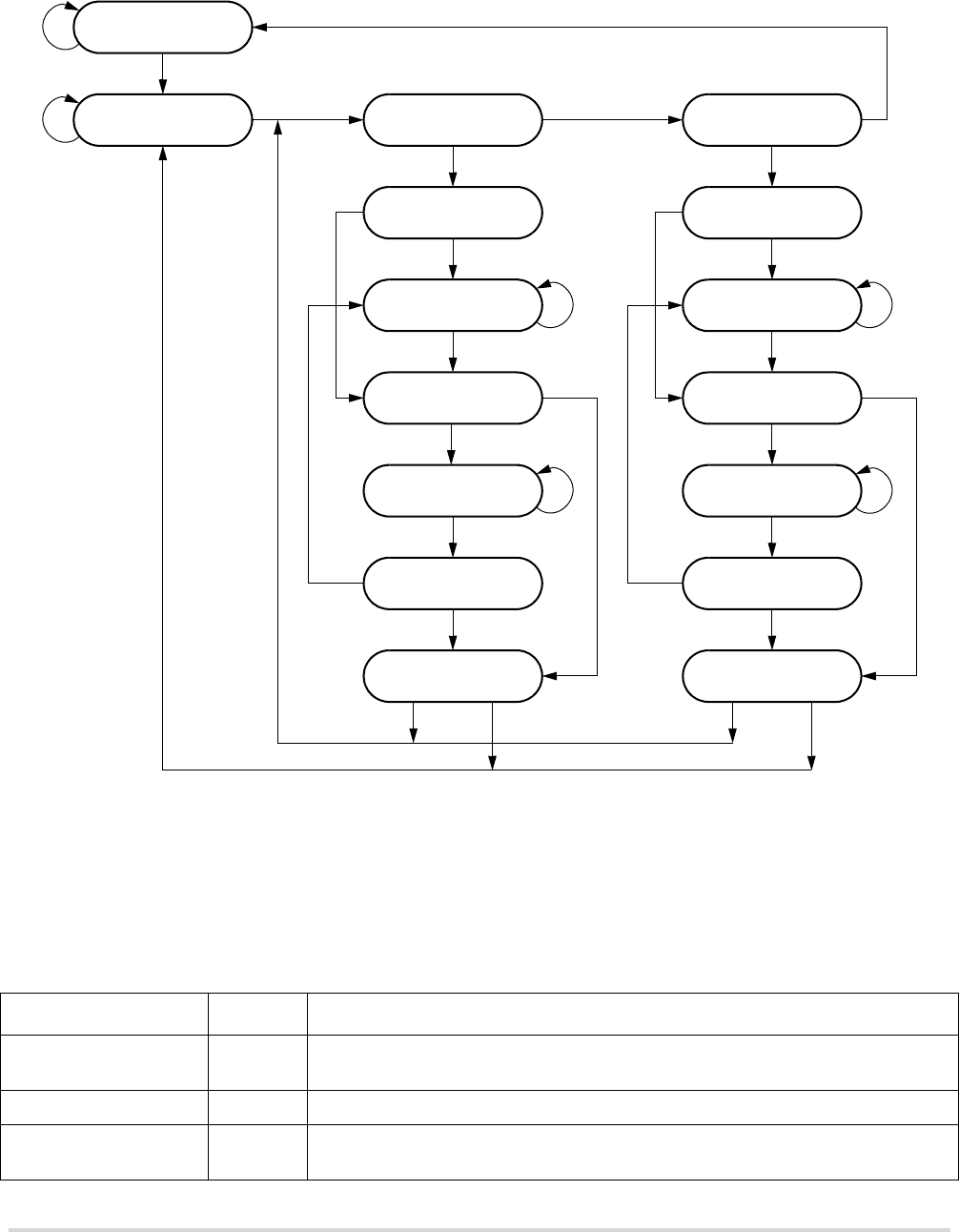

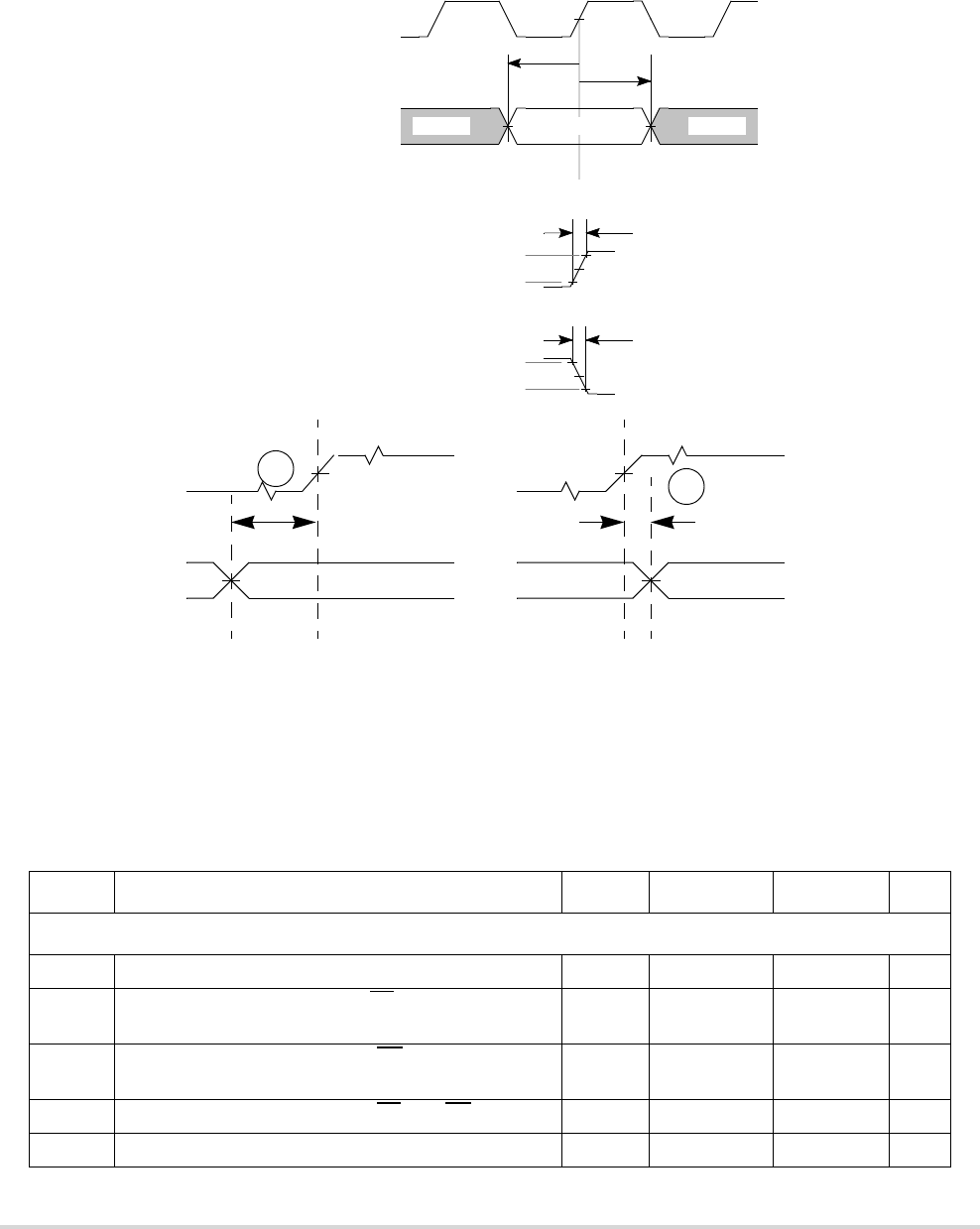

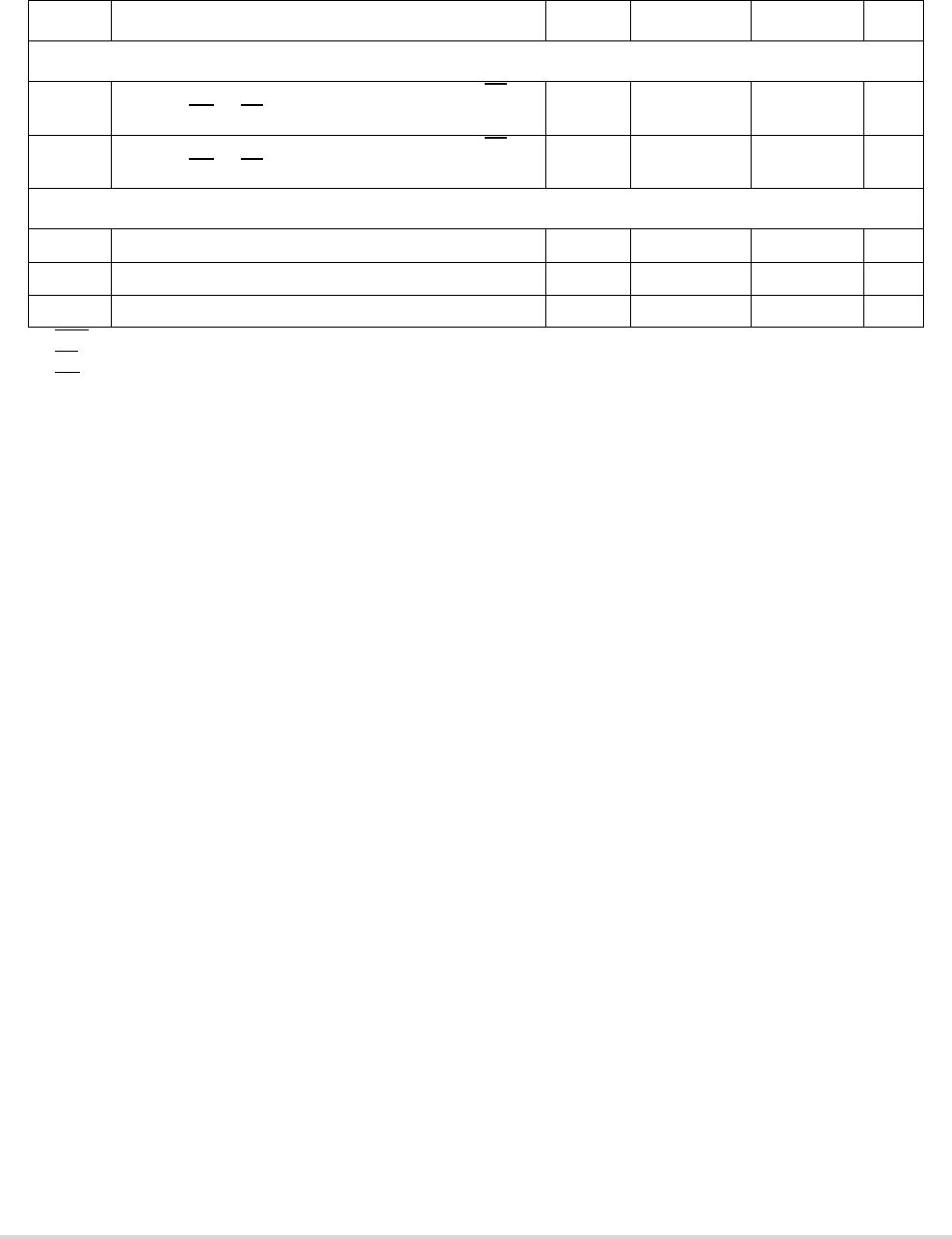

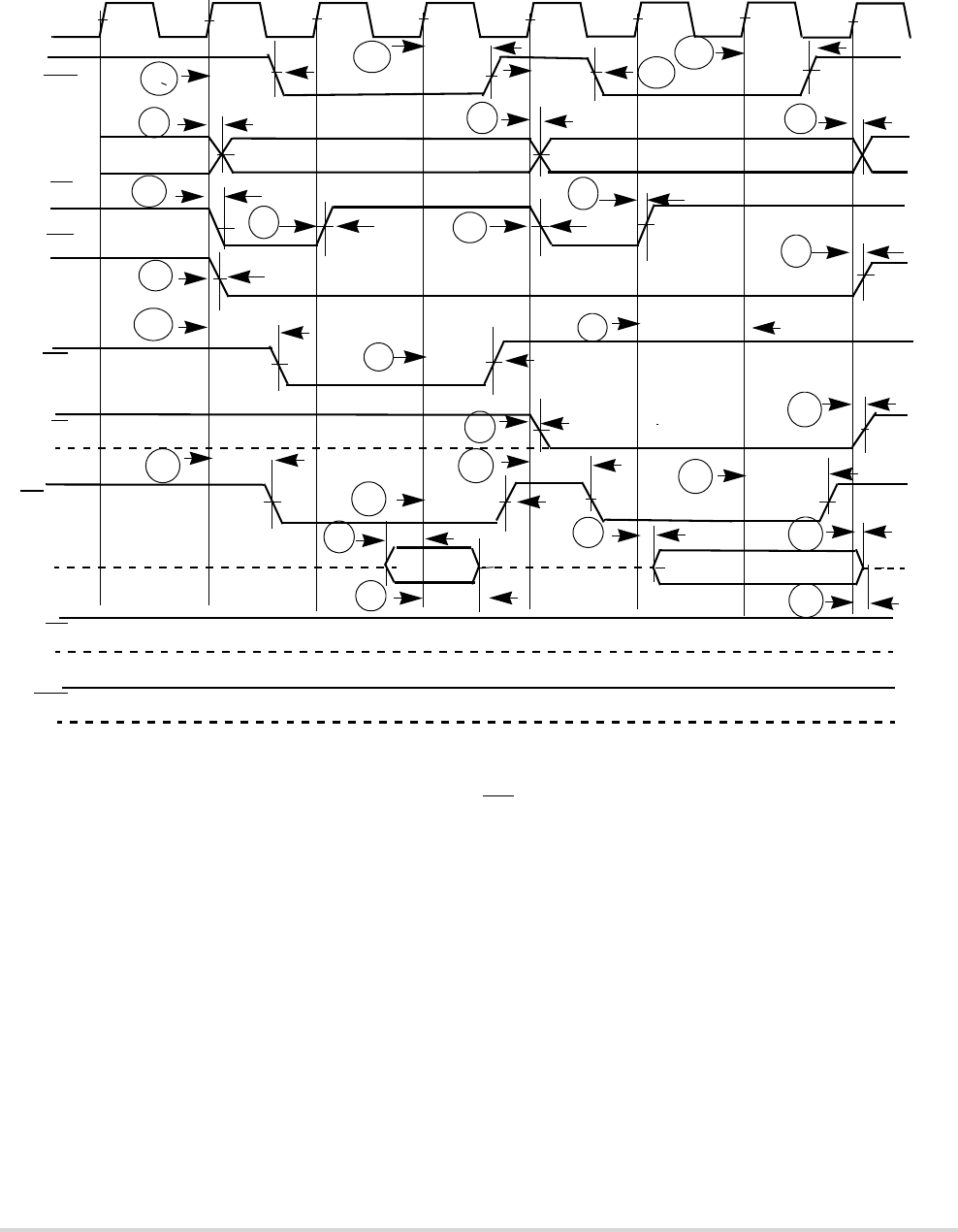

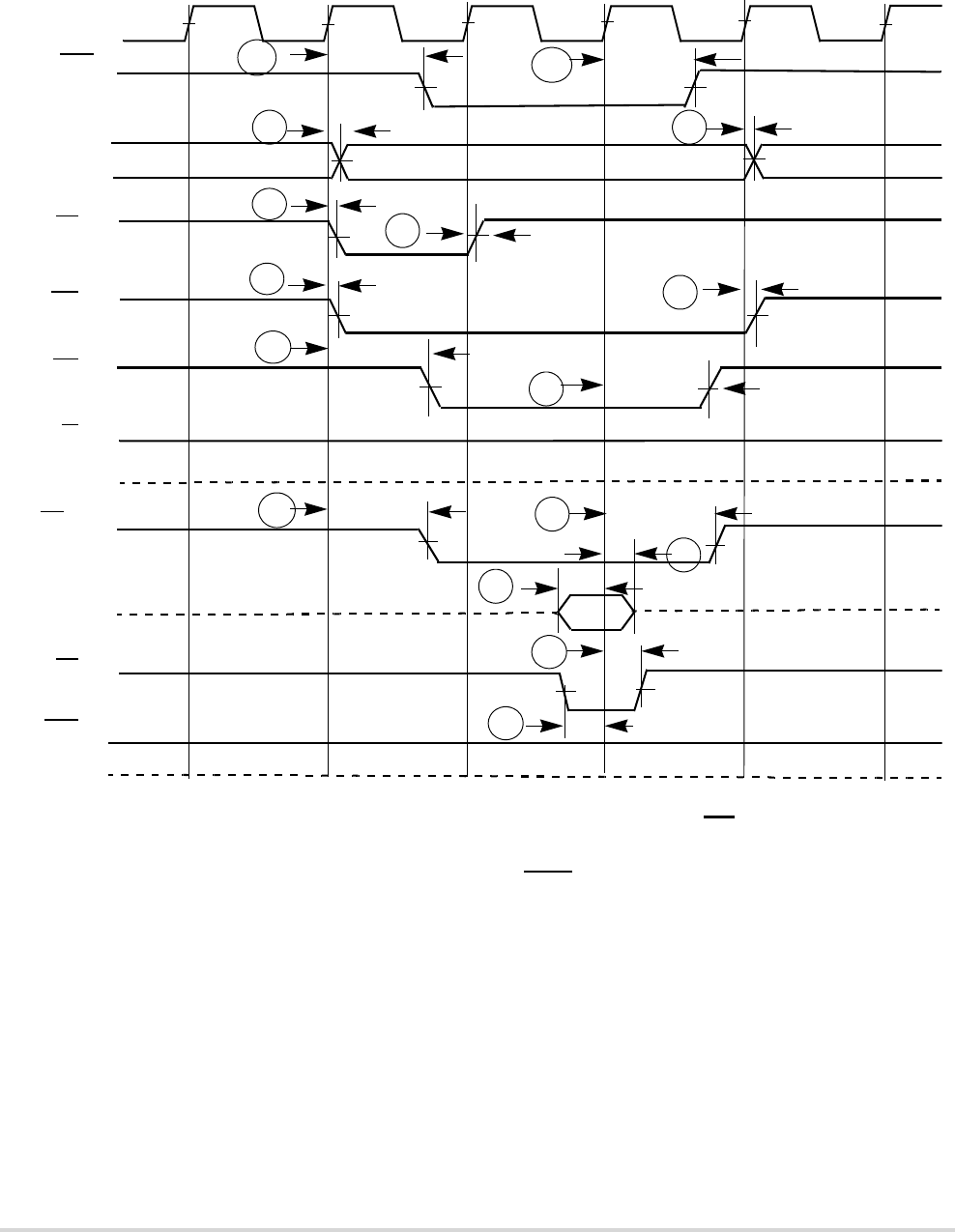

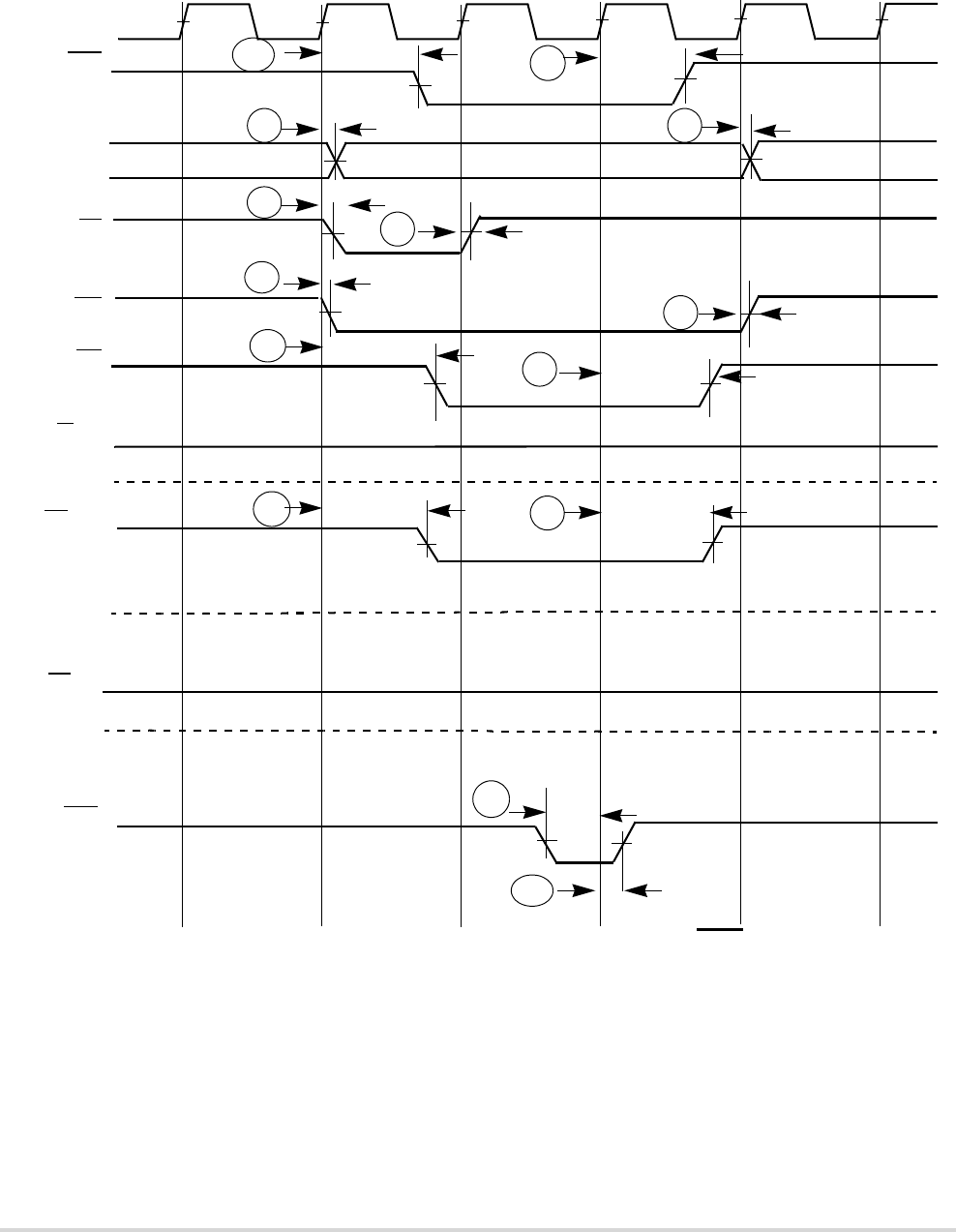

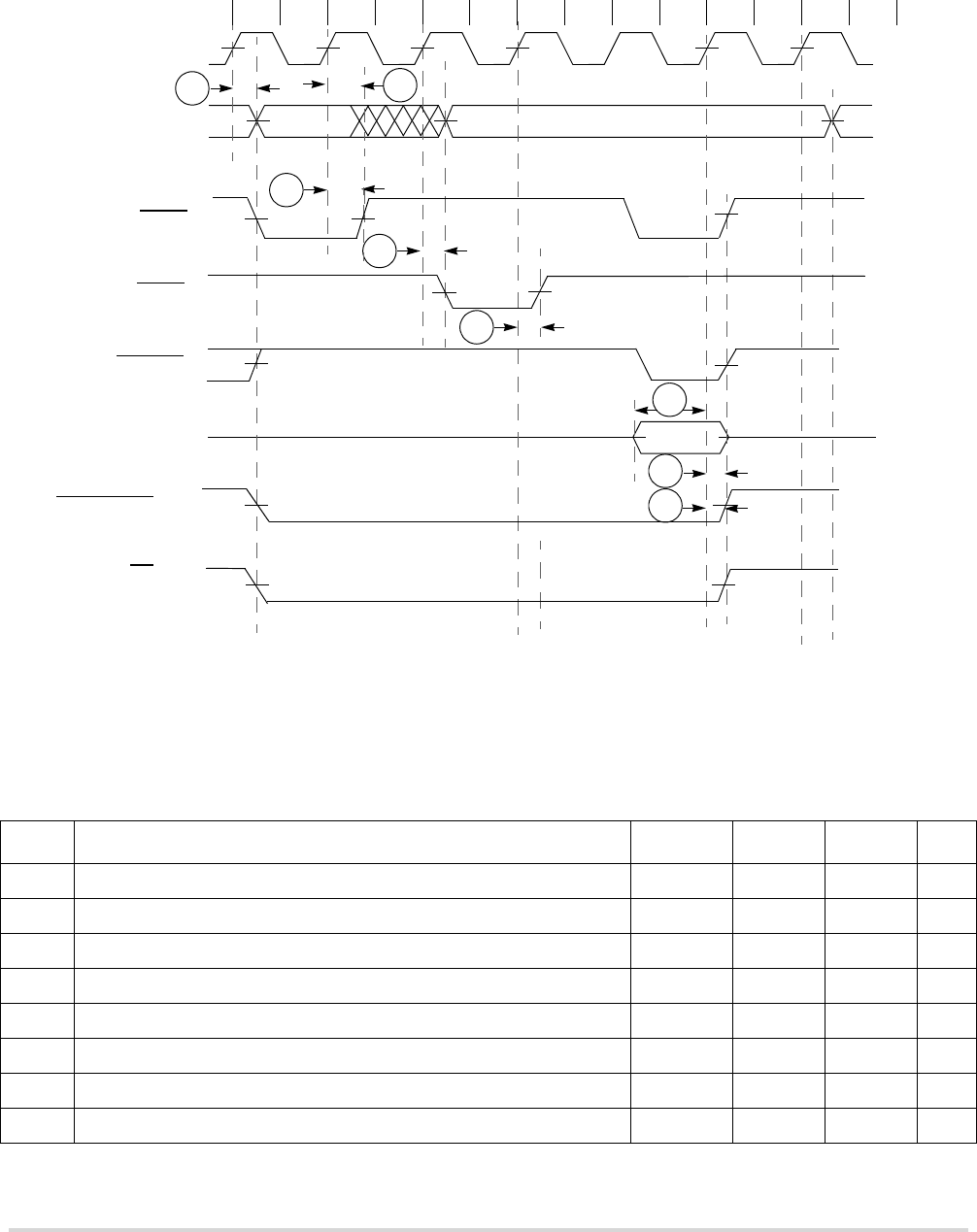

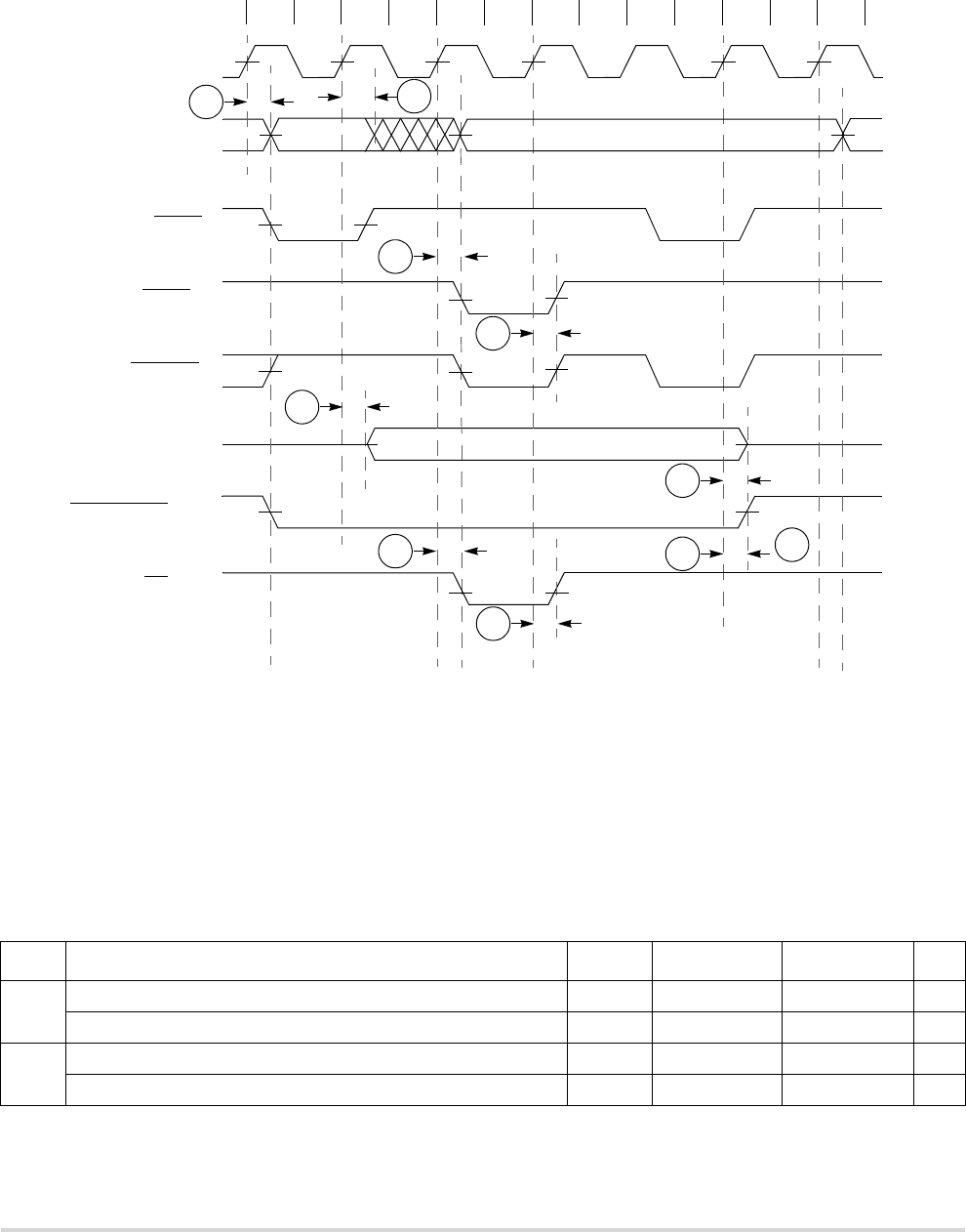

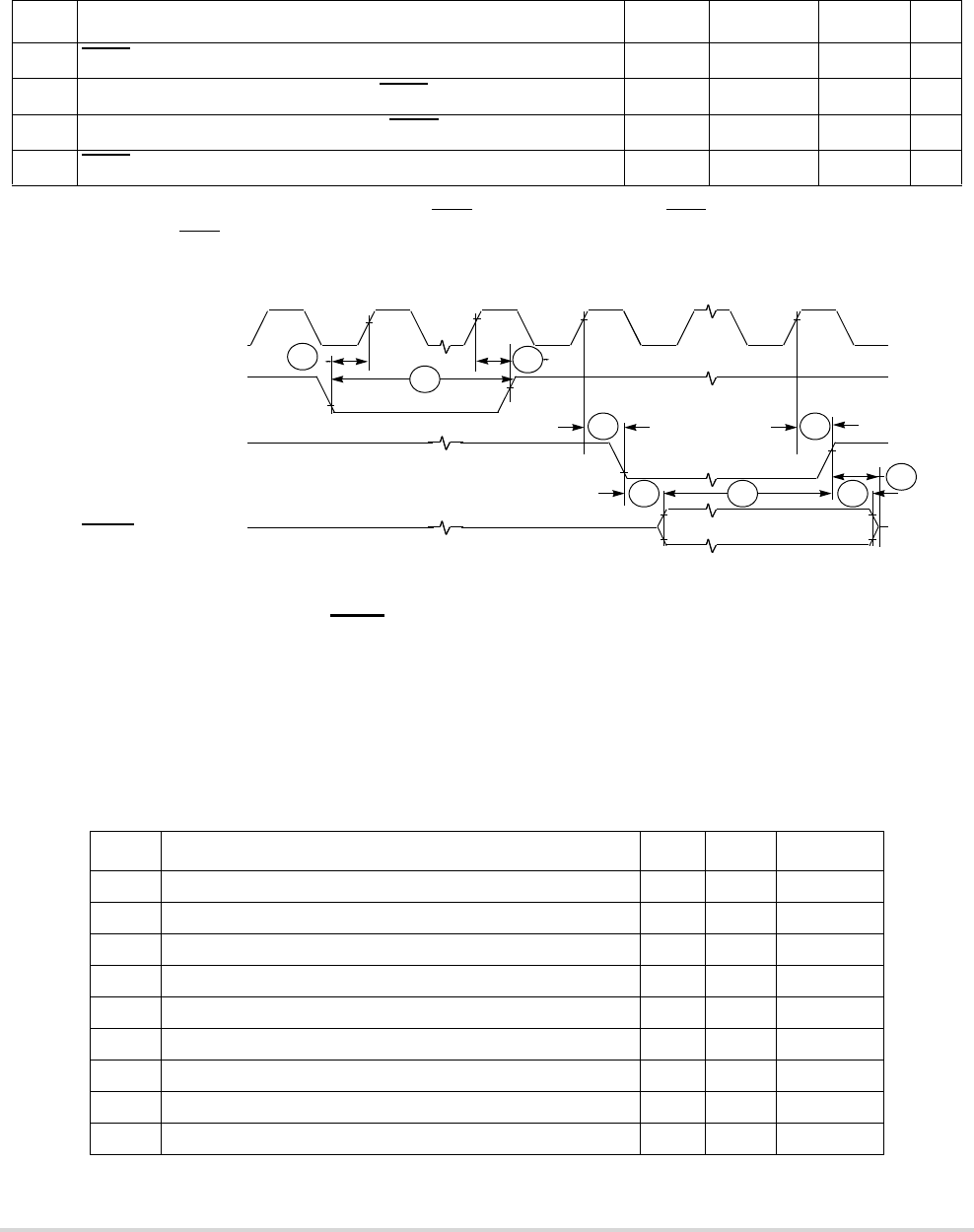

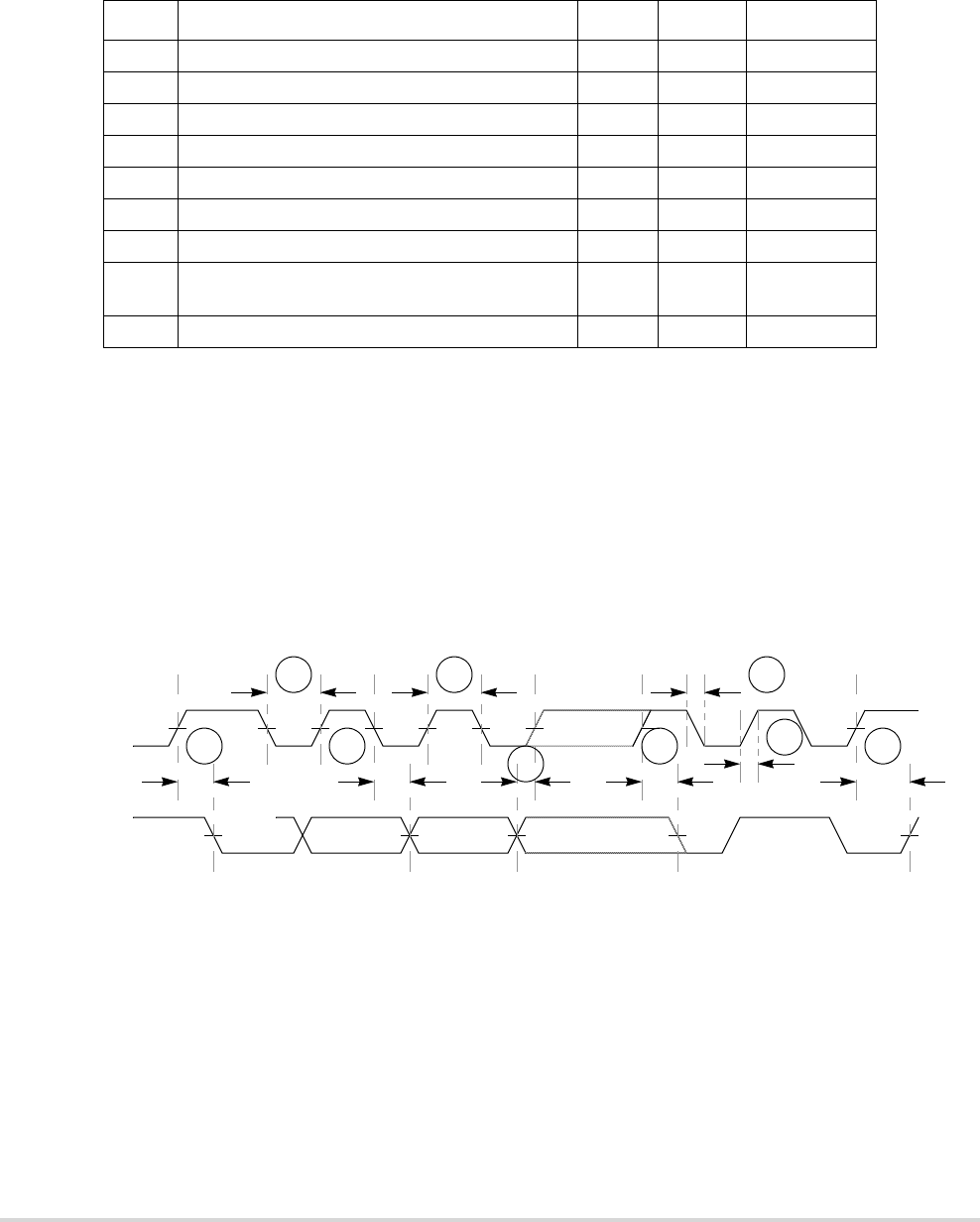

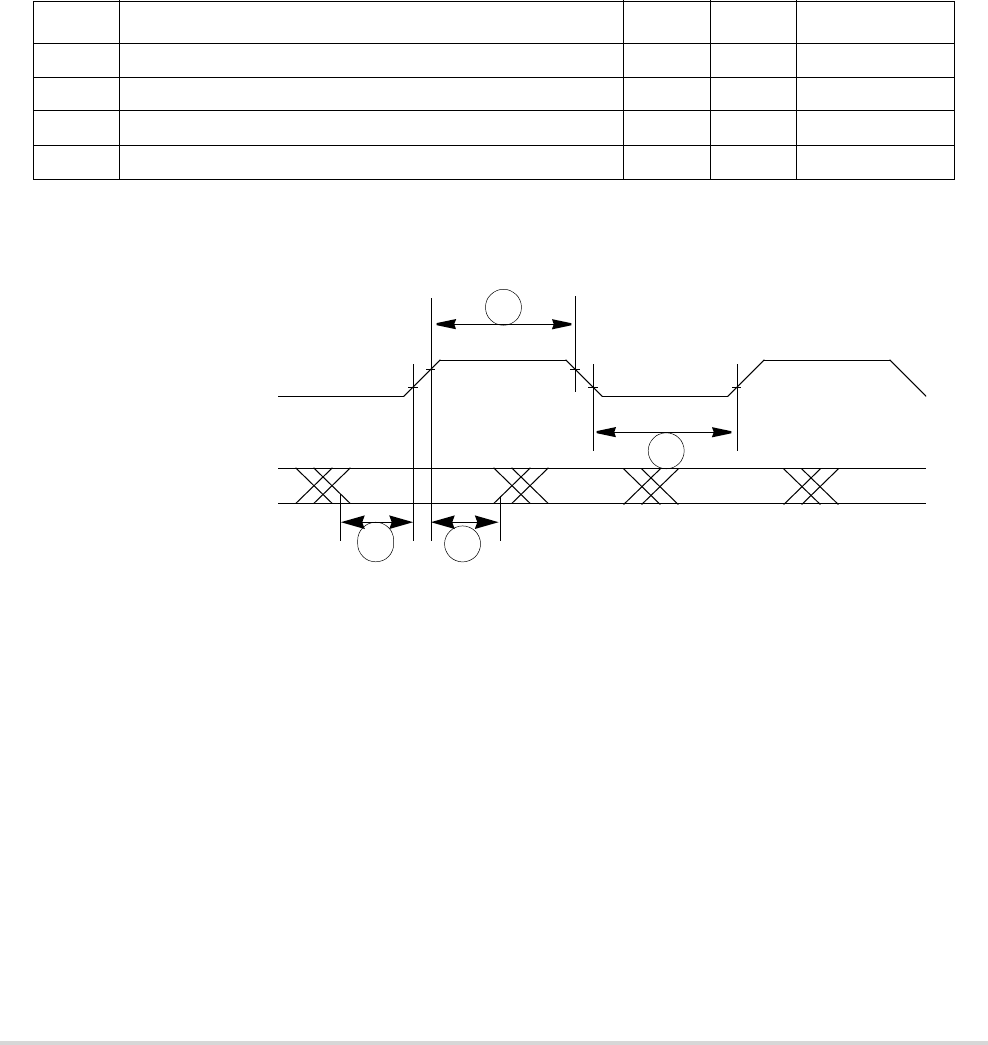

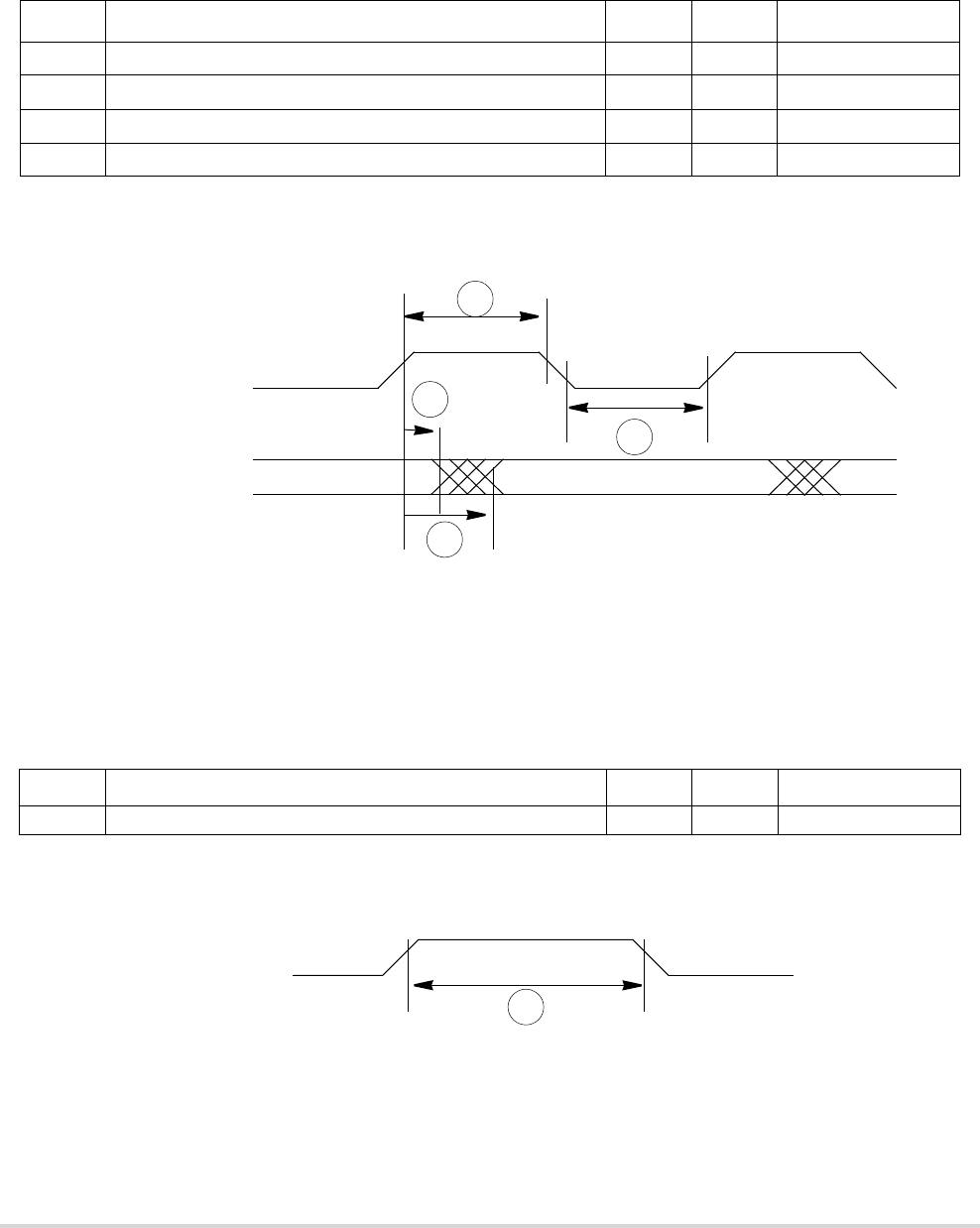

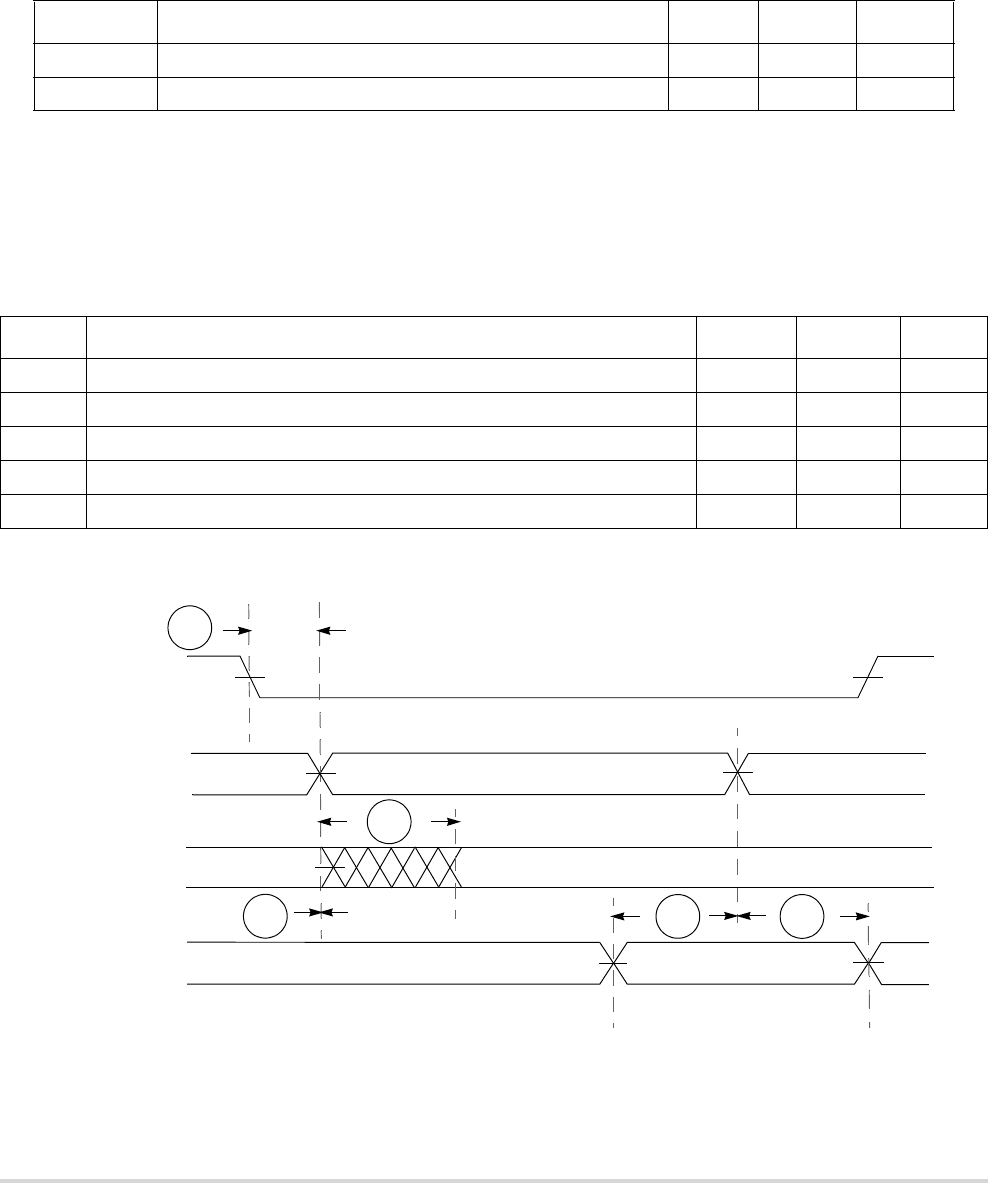

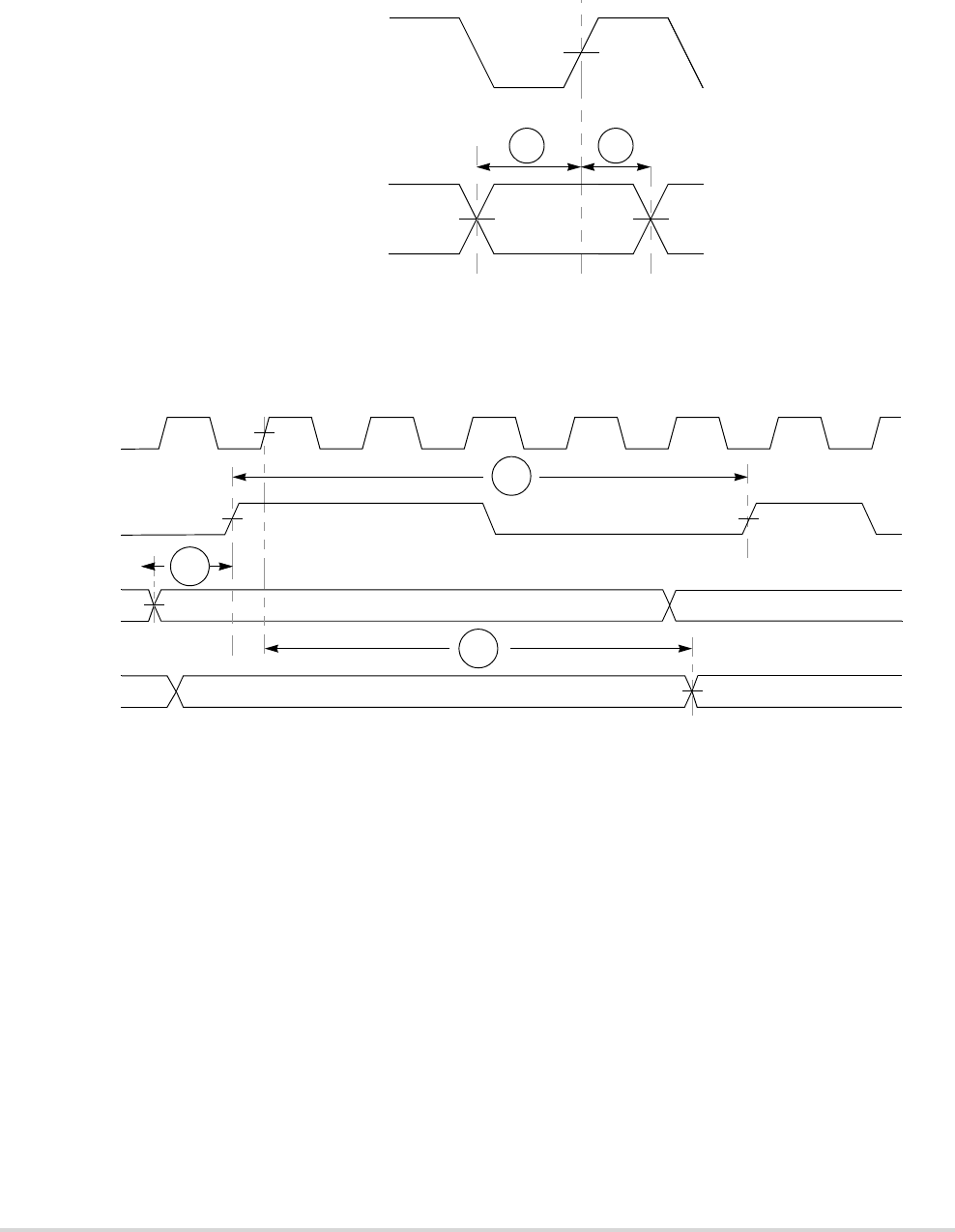

- Figure 27-23. CCW Priority Situation 1

- Figure 27-24. CCW Priority Situation 2

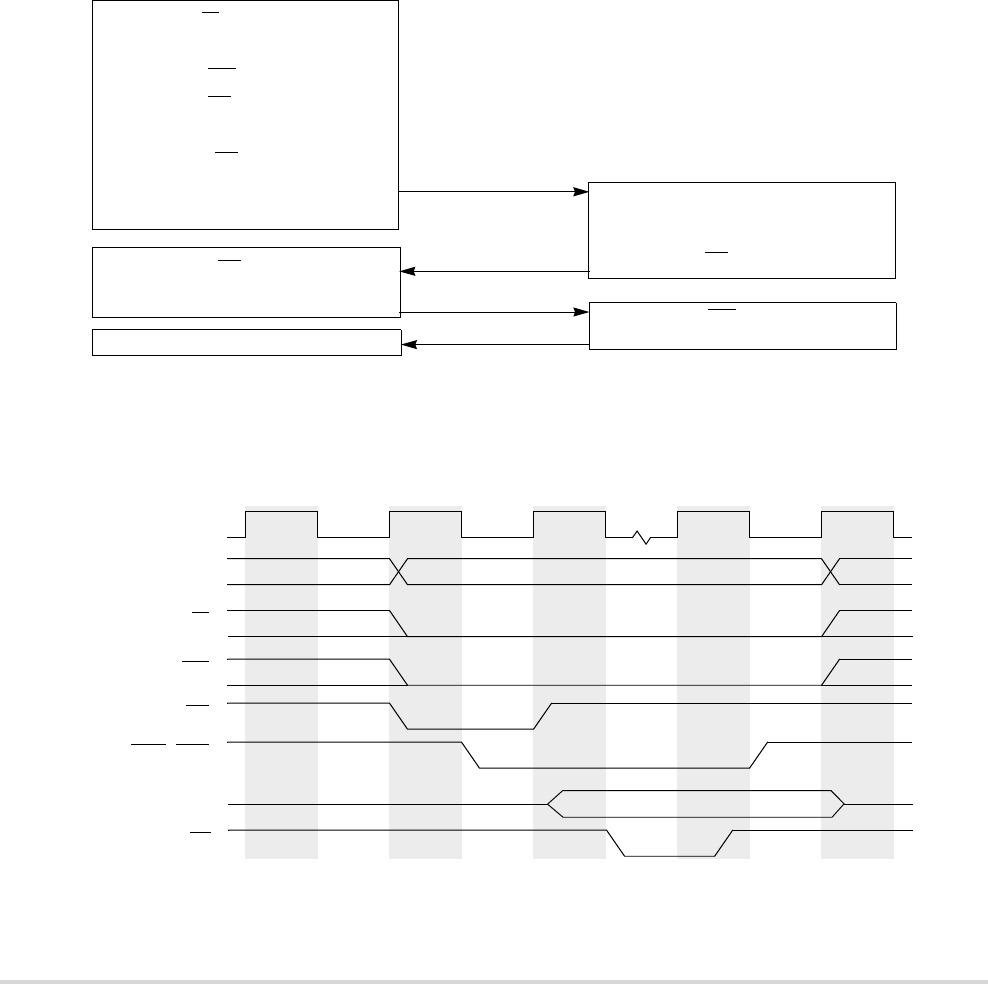

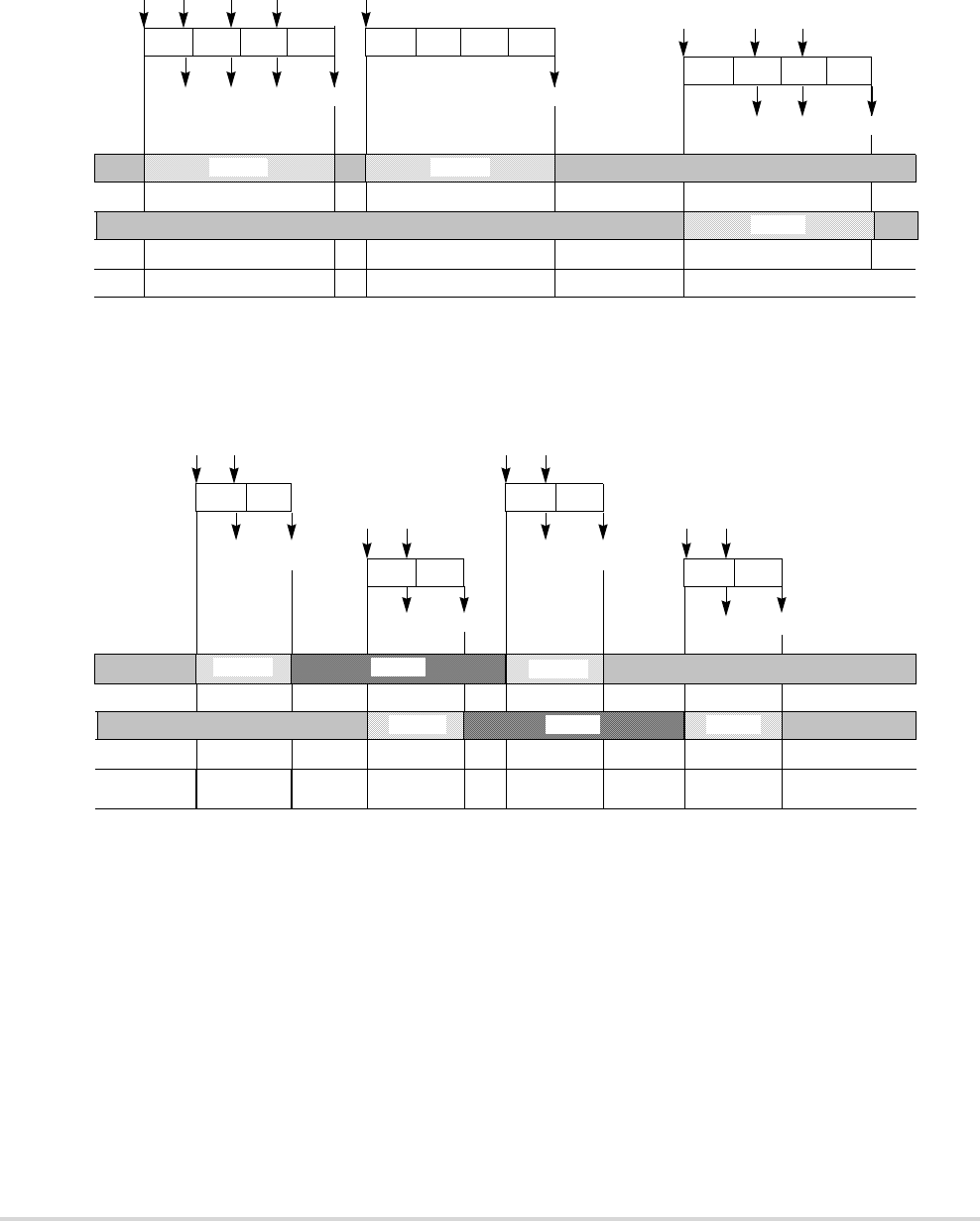

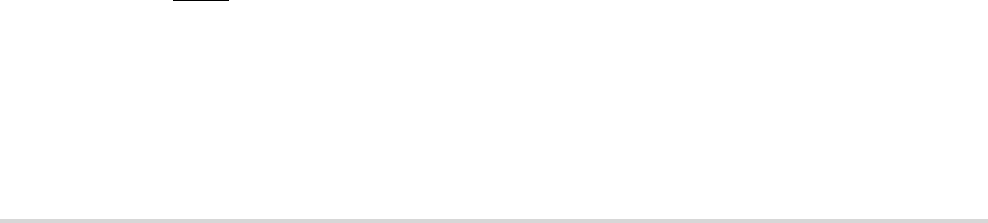

- Figure 27-25. CCW Priority Situation 3

- Figure 27-26. CCW Priority Situation 4

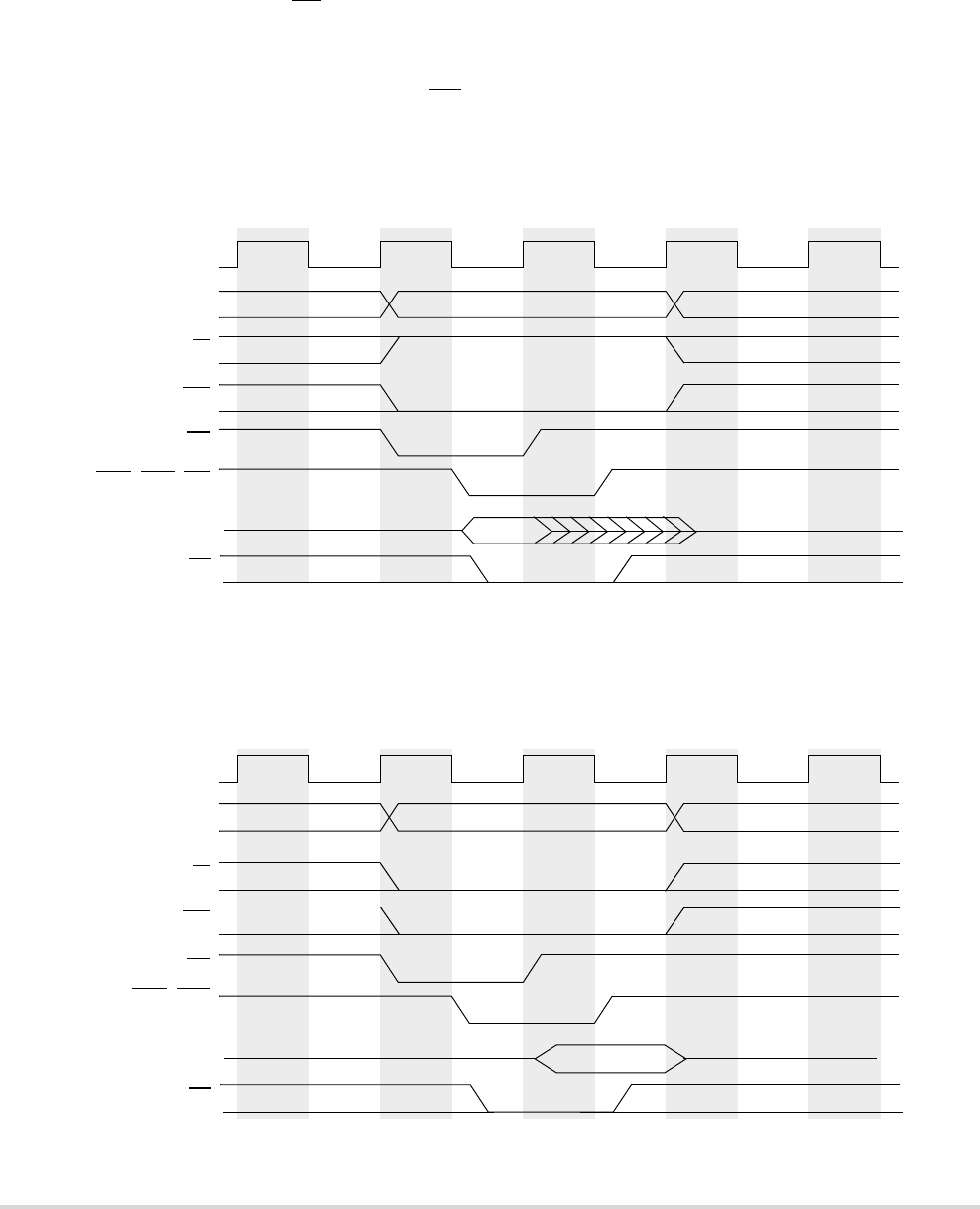

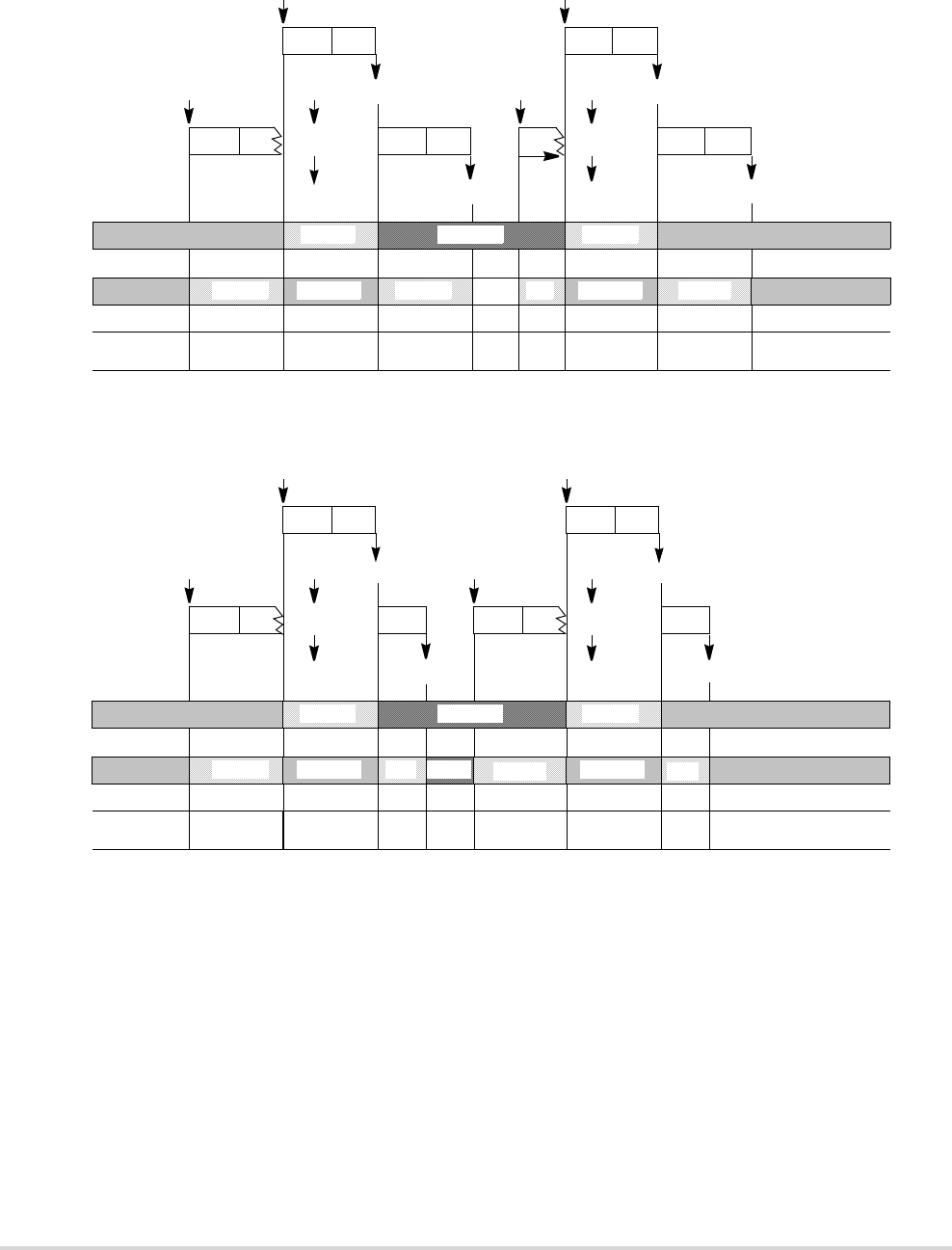

- Figure 27-27. CCW Priority Situation 5

- Figure 27-28. CCW Priority Situation 6

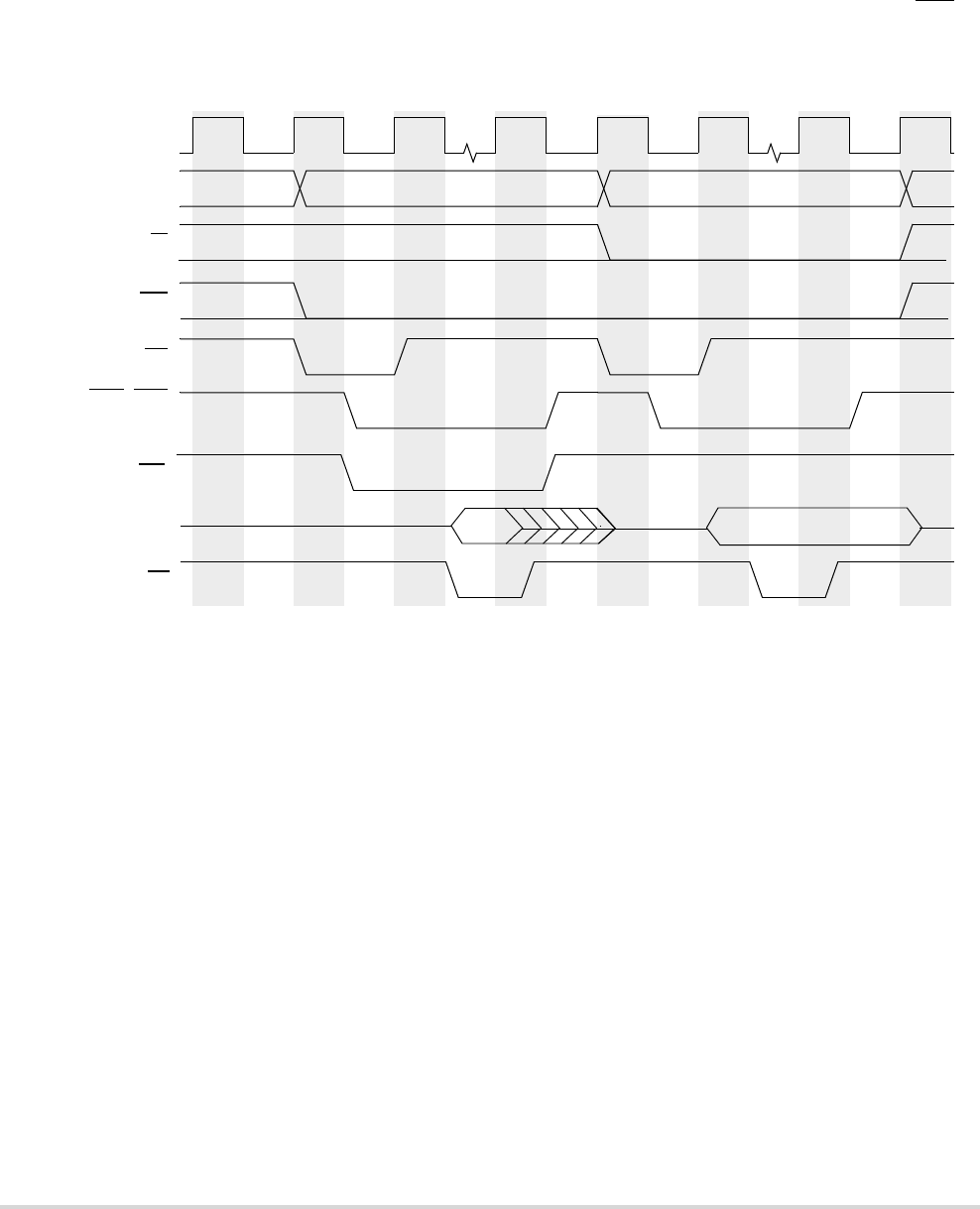

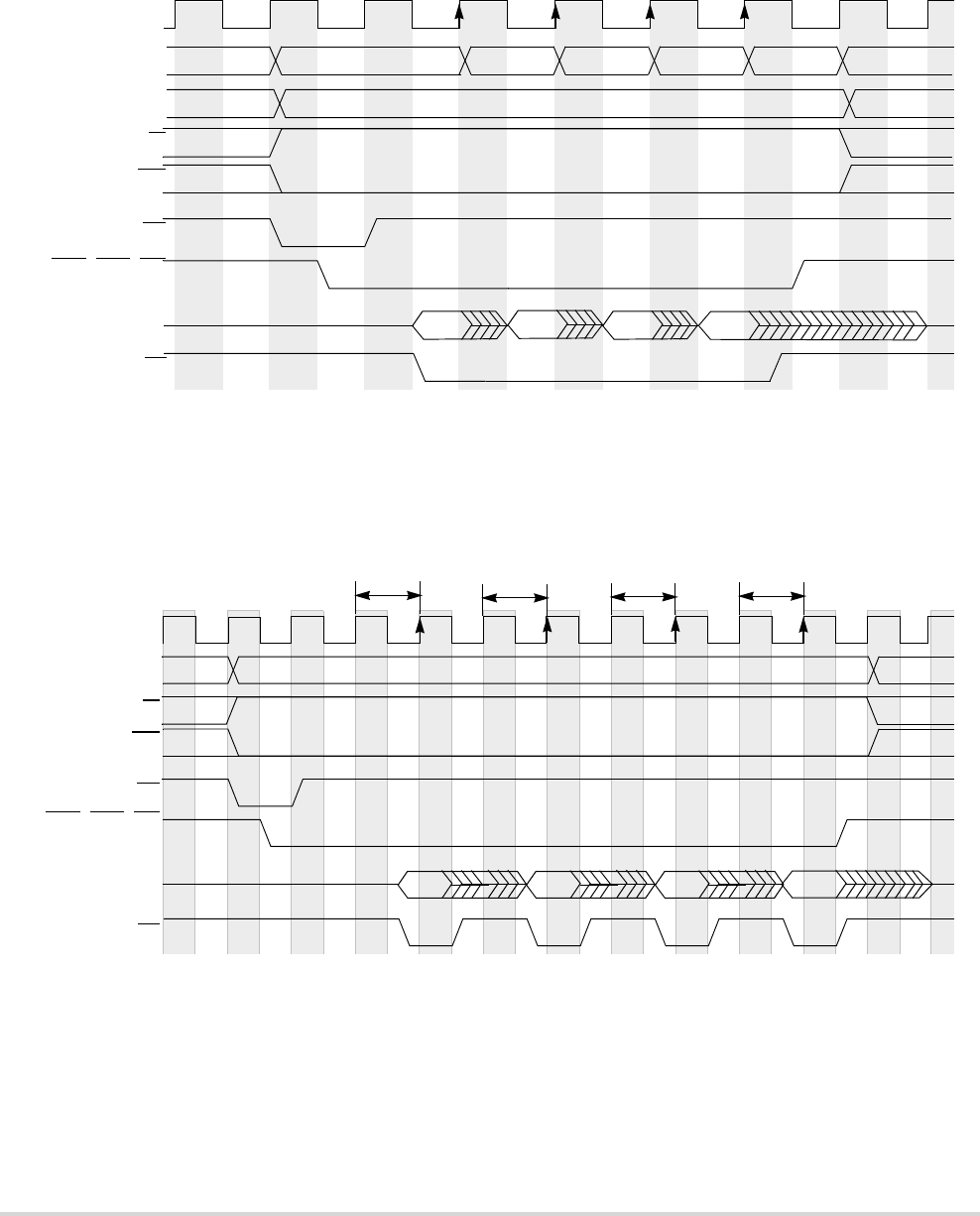

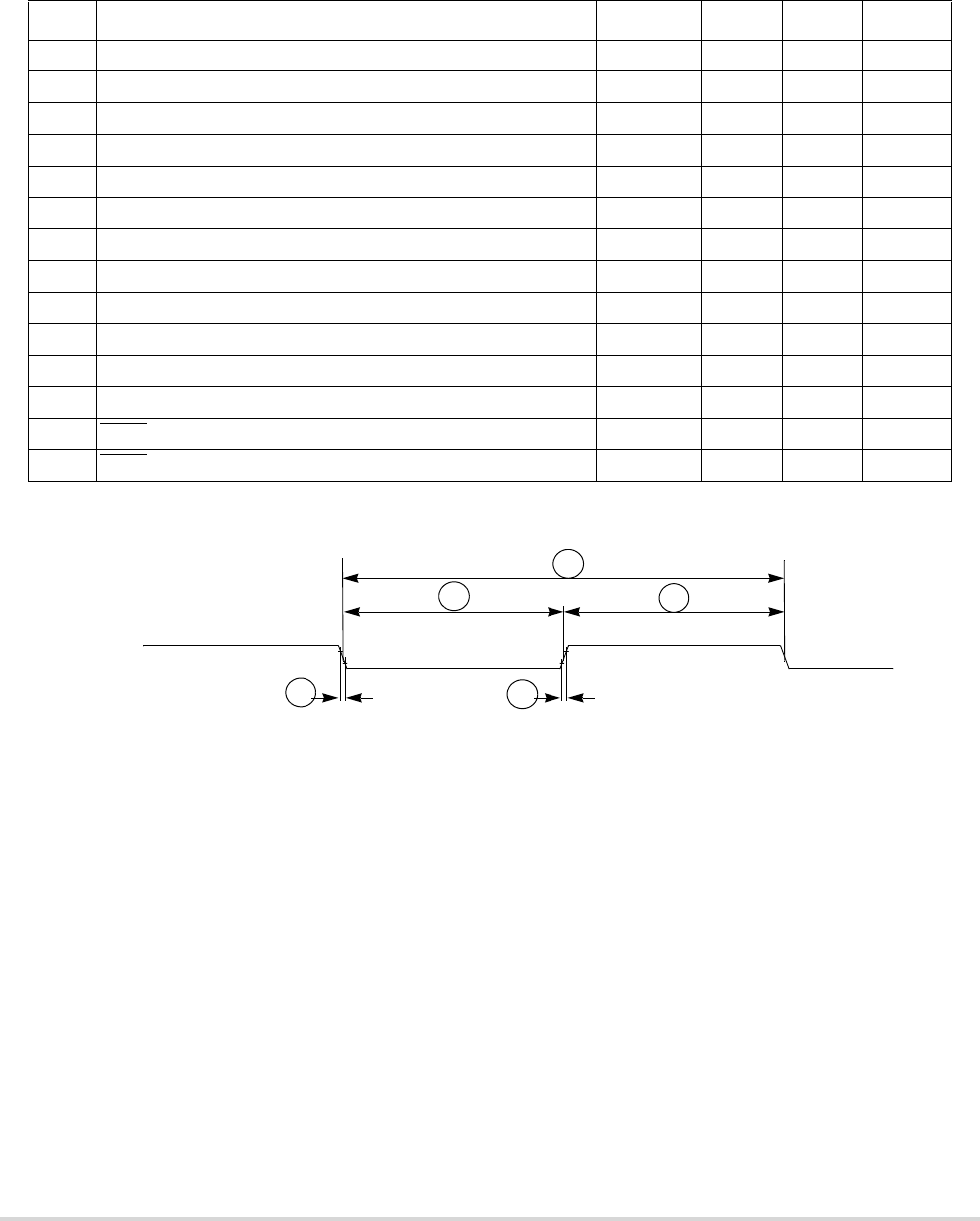

- Figure 27-29. CCW Priority Situation 7

- Figure 27-30. CCW Priority Situation 8

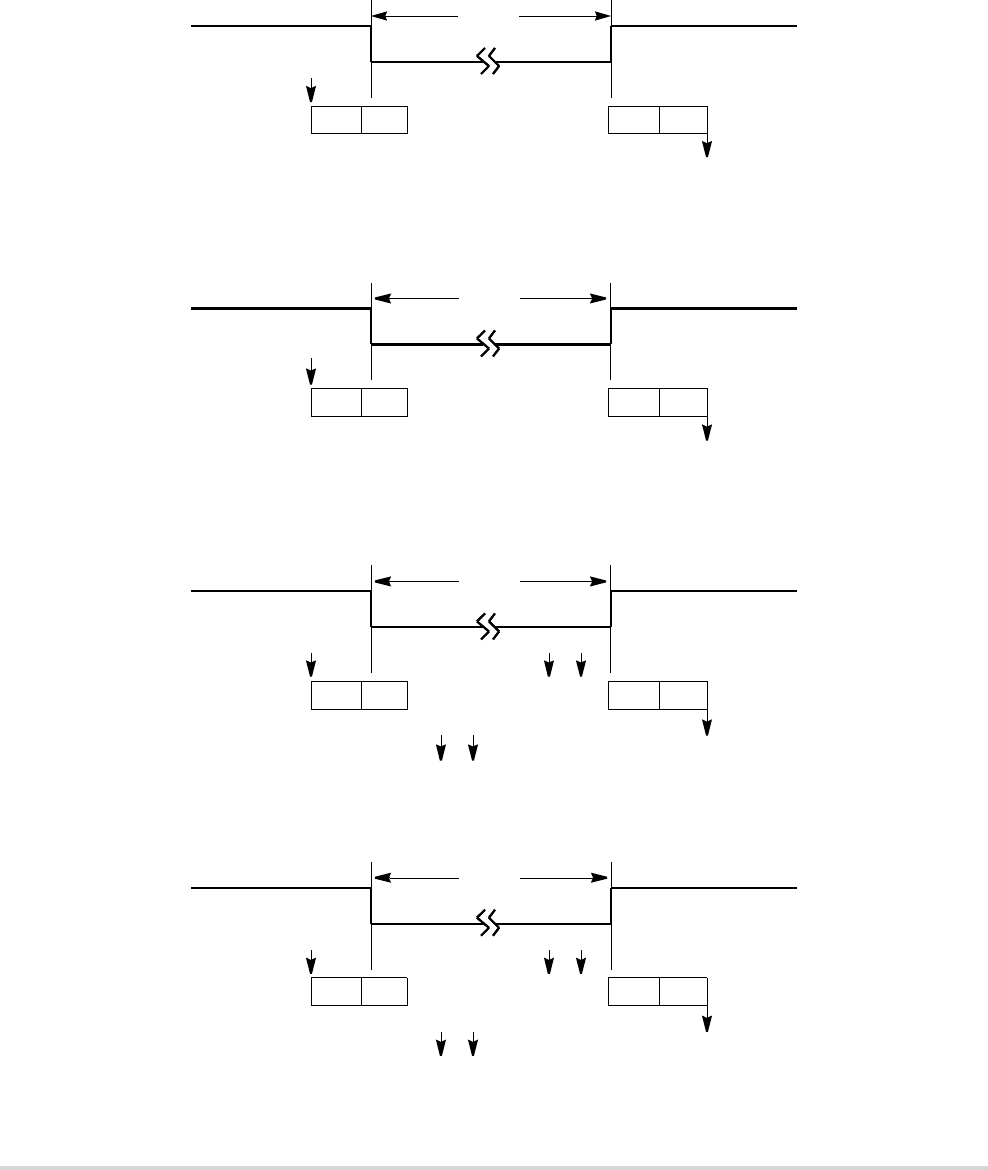

- Figure 27-31. CCW Priority Situation 9

- Figure 27-32. CCW Priority Situation 10

- Figure 27-33. CCW Priority Situation 11

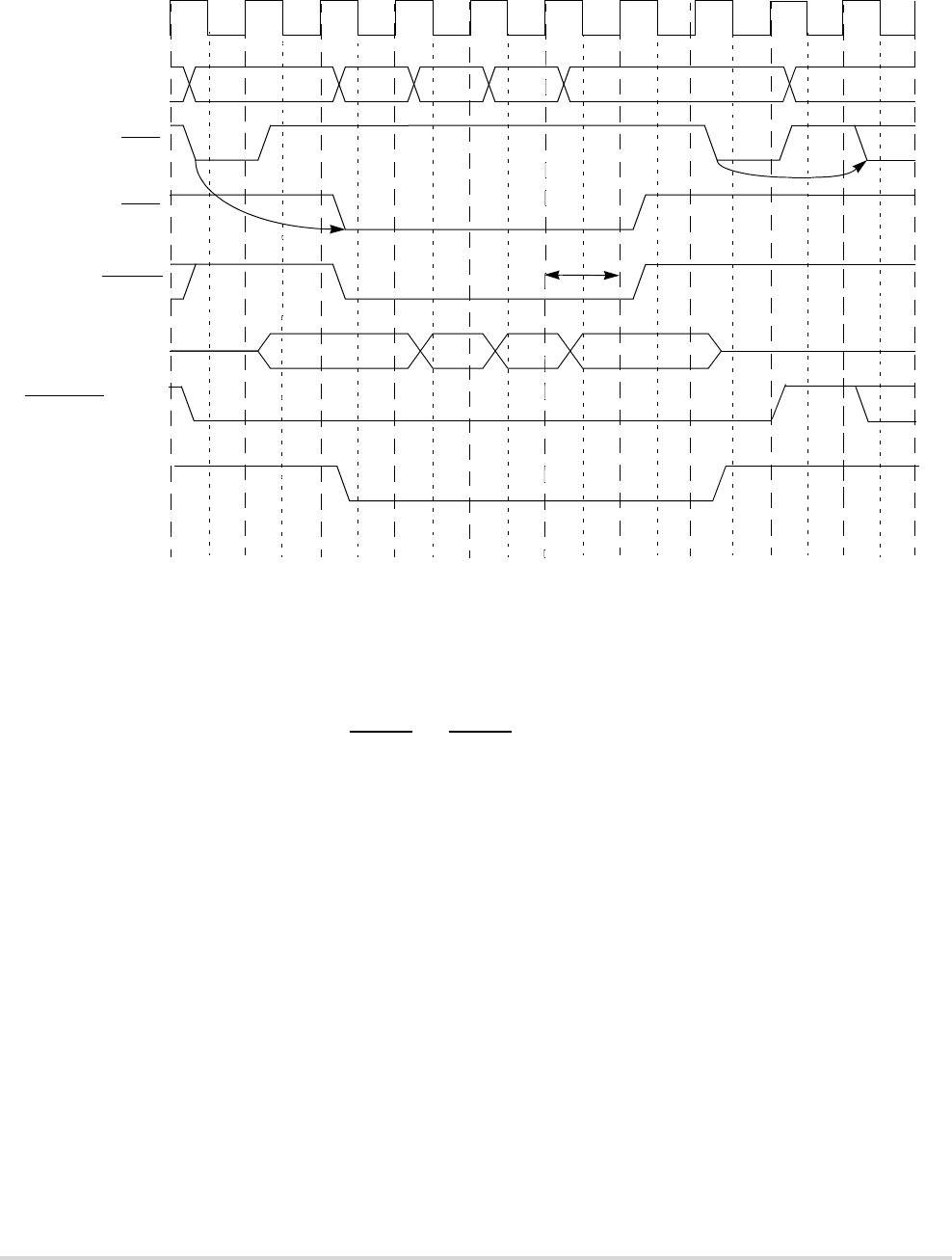

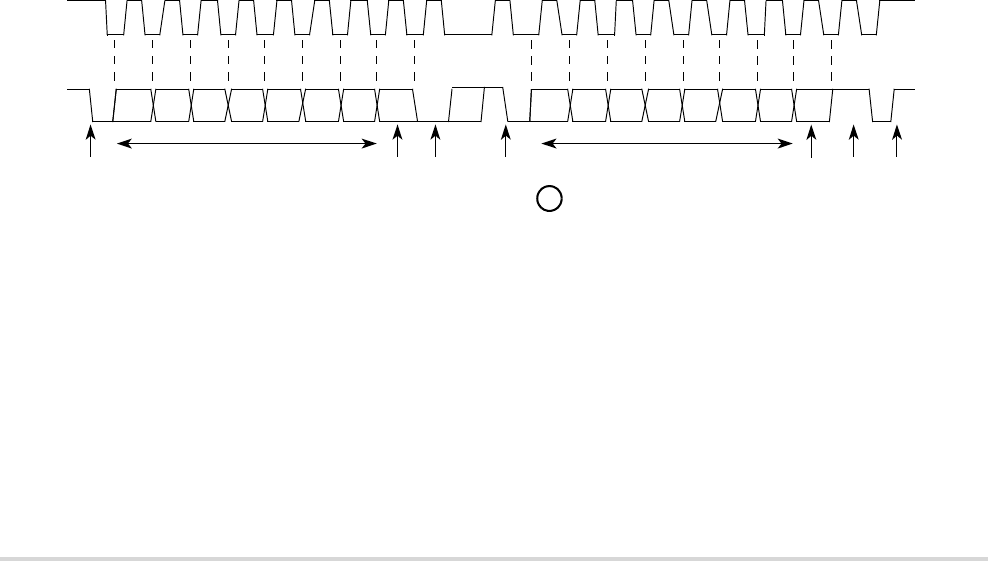

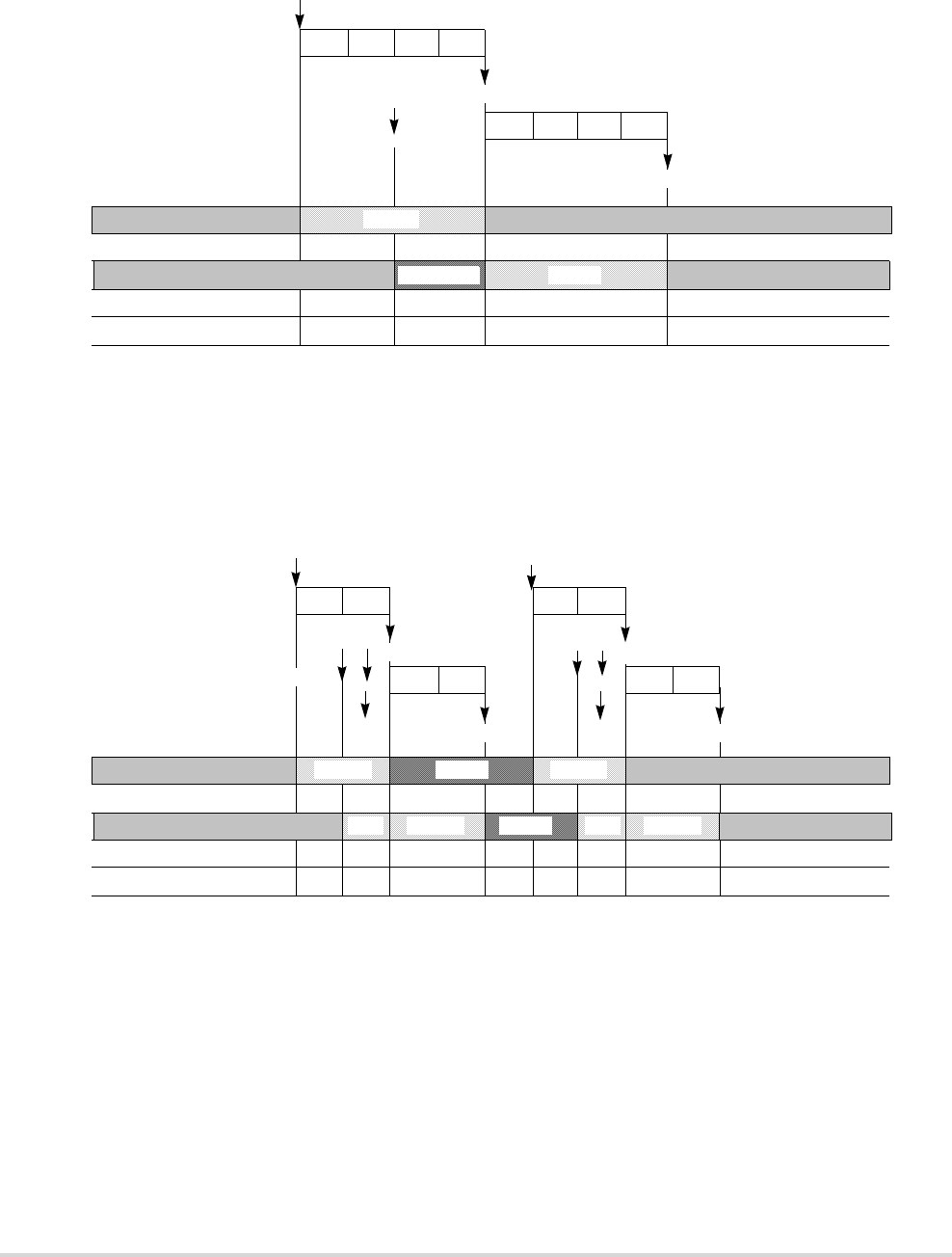

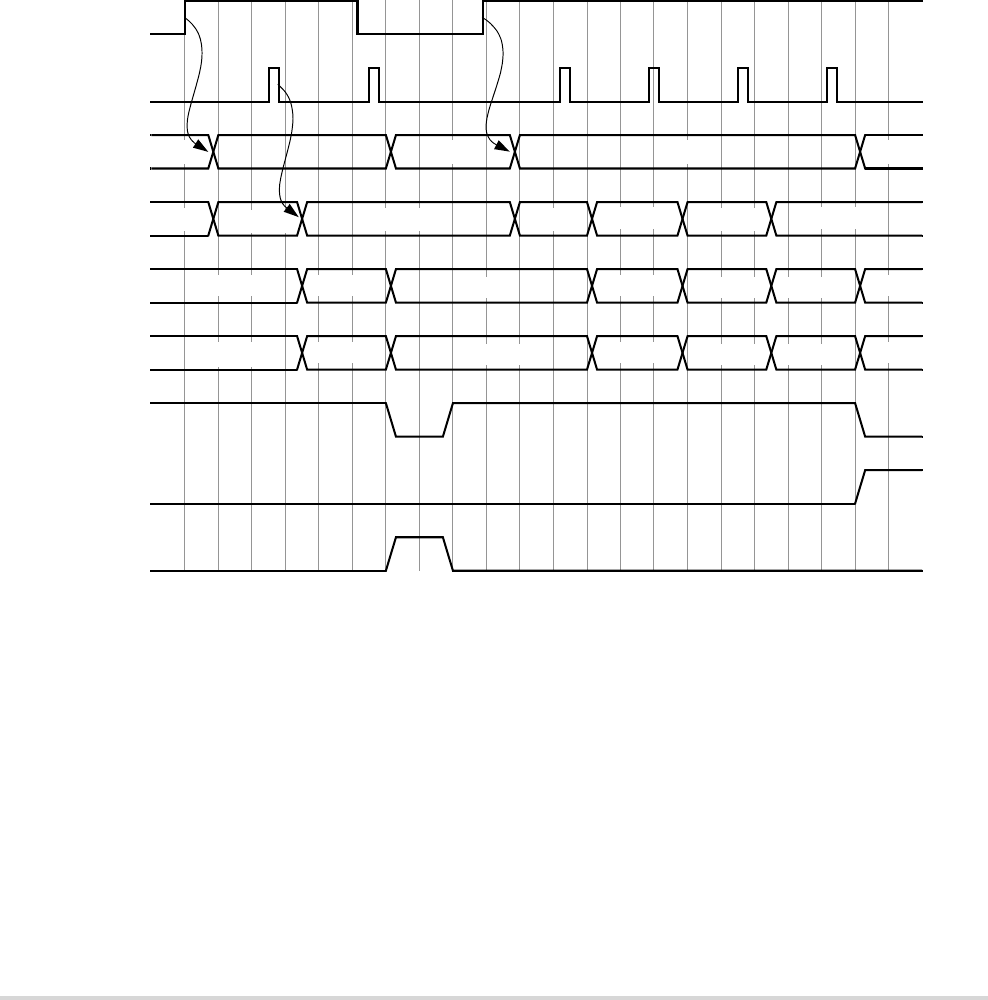

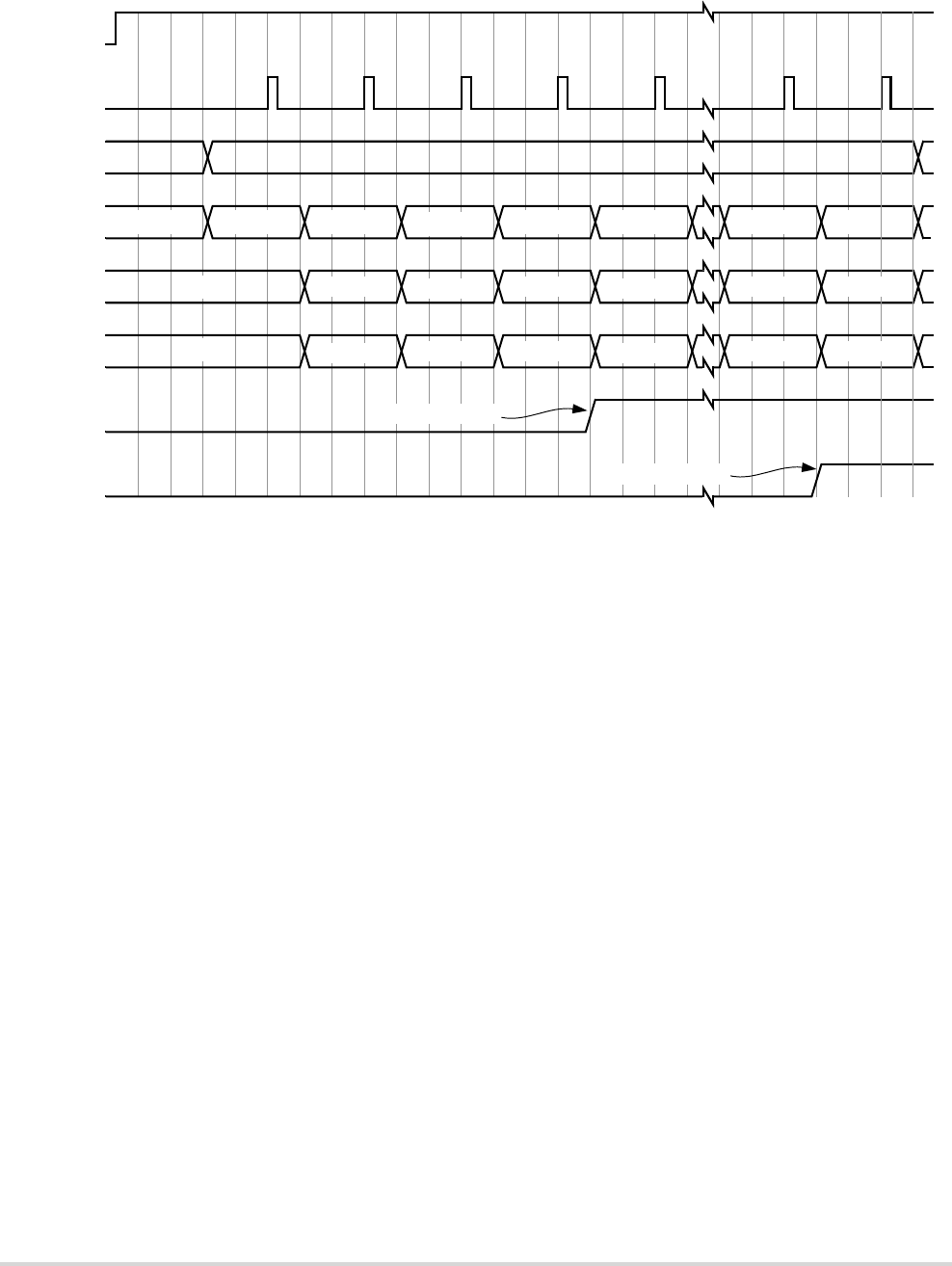

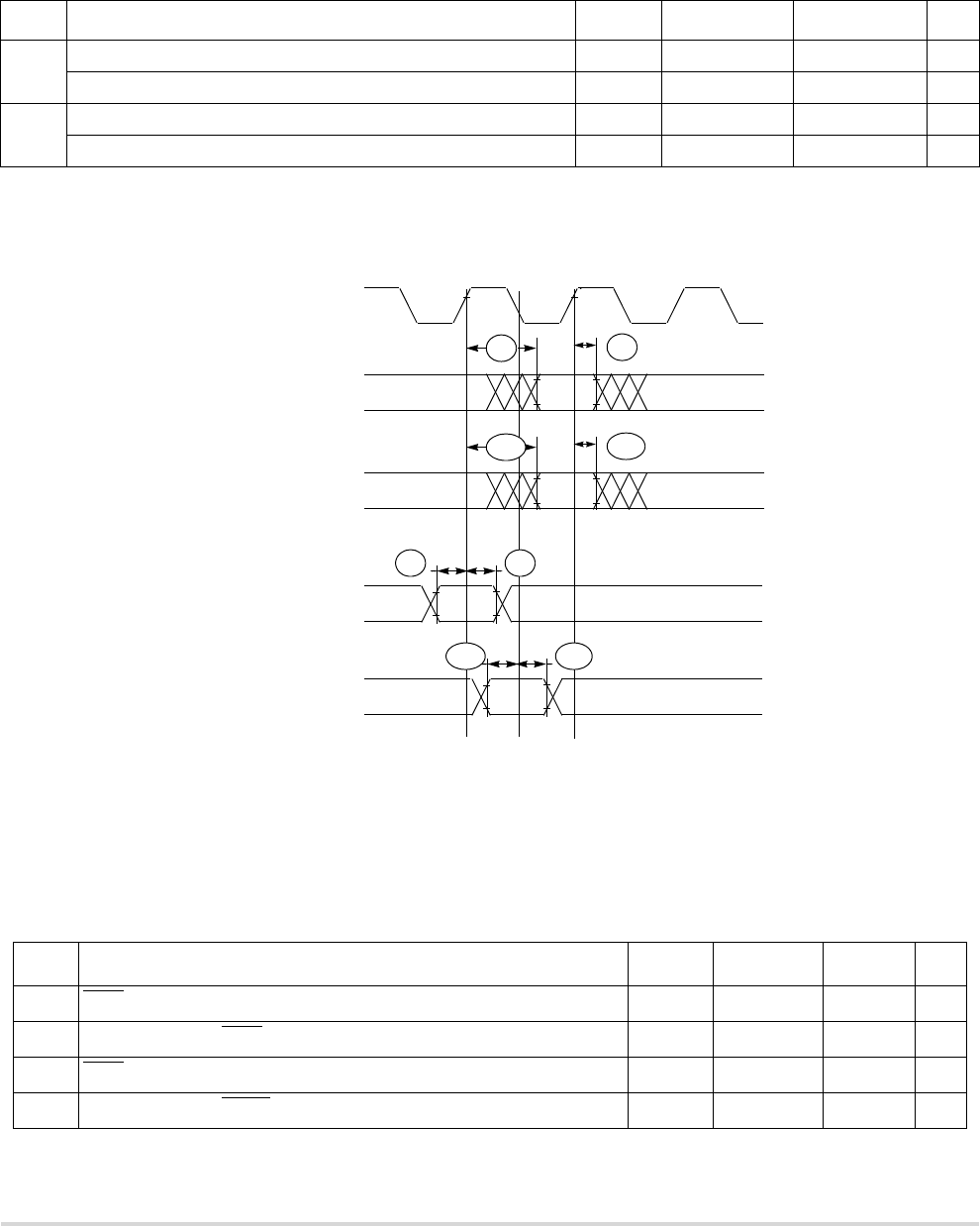

- Figure 27-34. CCW Freeze Situation 12

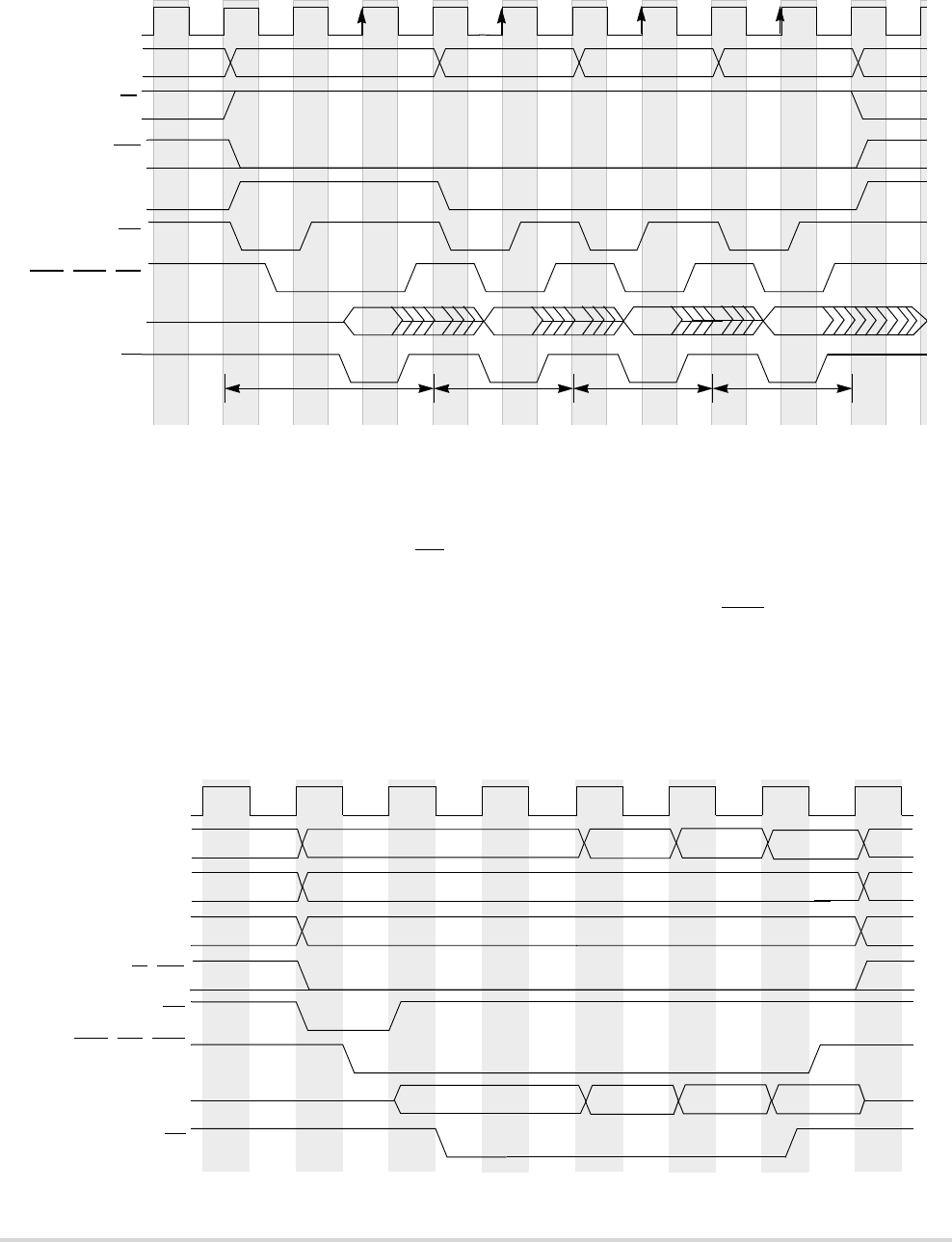

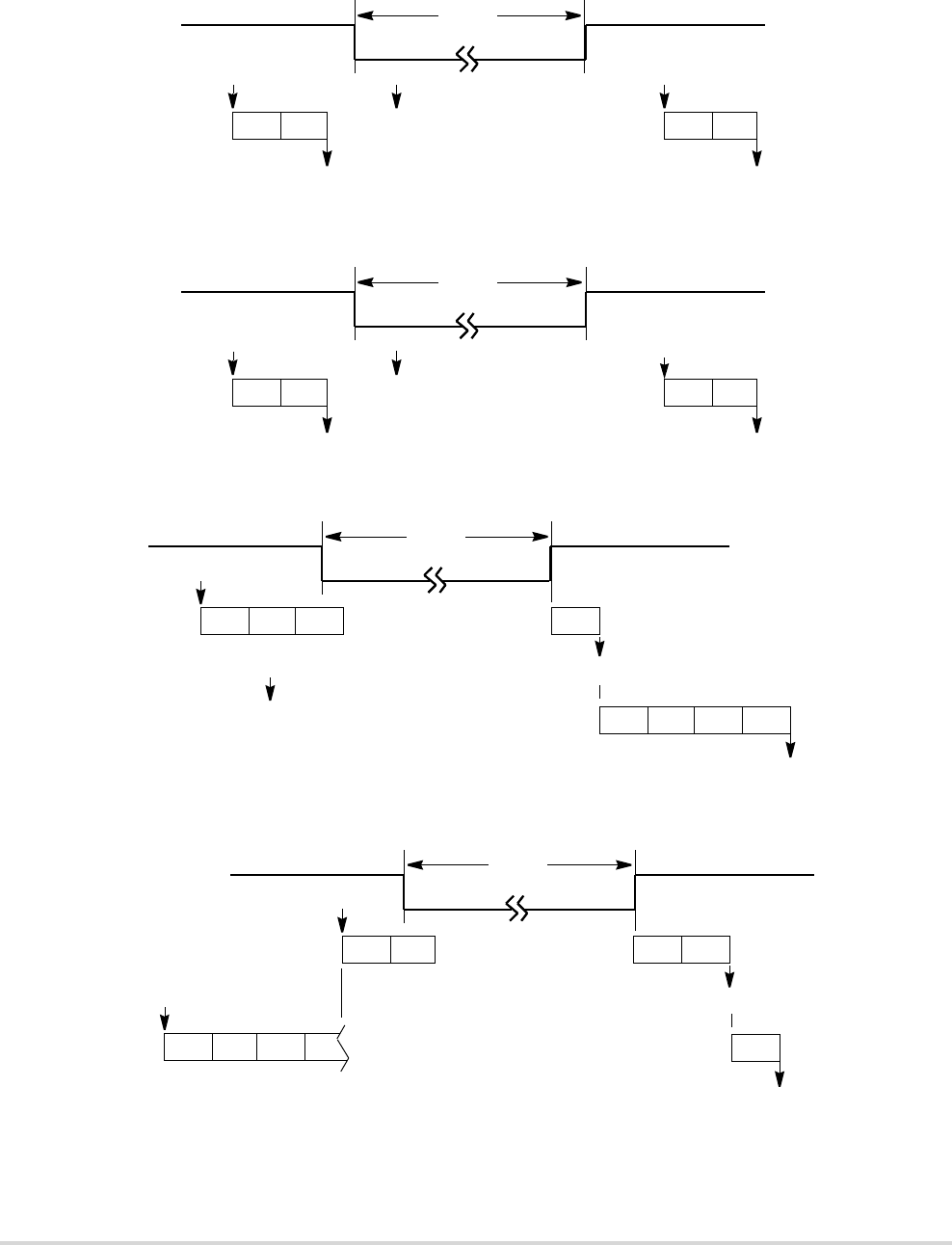

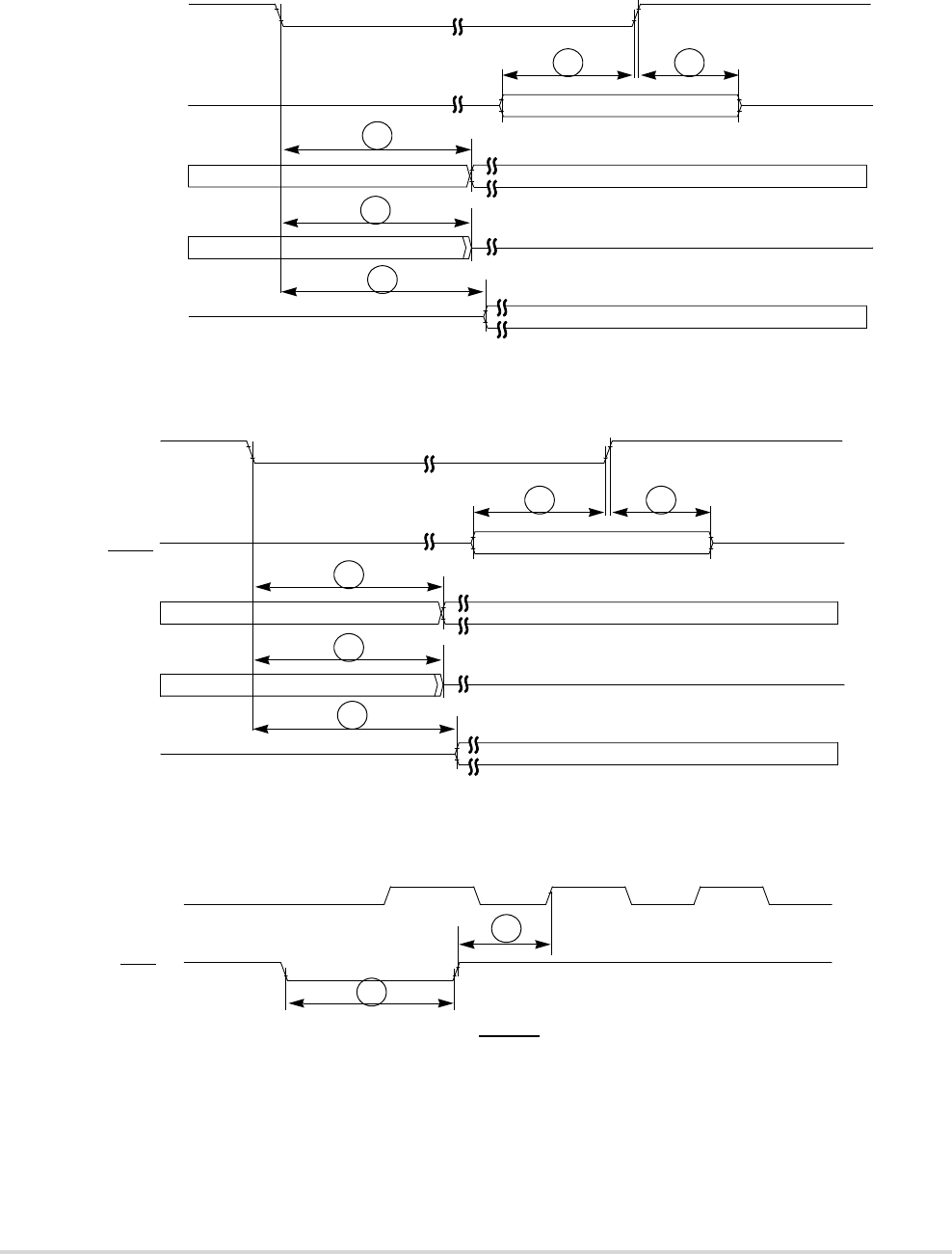

- Figure 27-35. CCW Freeze Situation 13

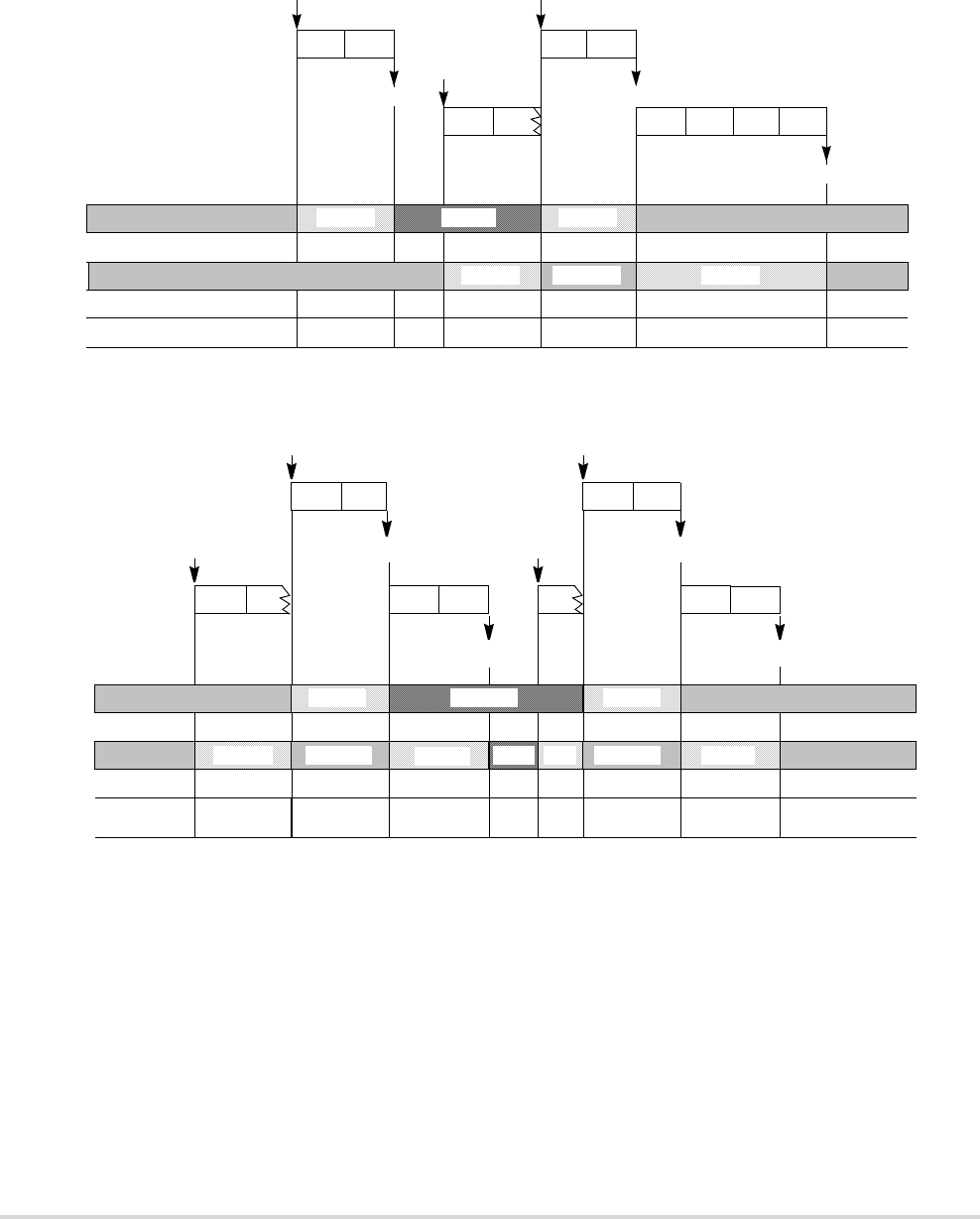

- Figure 27-36. CCW Freeze Situation 14

- Figure 27-37. . CCW Freeze Situation 15

- Figure 27-38. CCW Freeze Situation 16

- Figure 27-39. CCW Freeze Situation 17

- Figure 27-40. CCW Freeze Situation 18

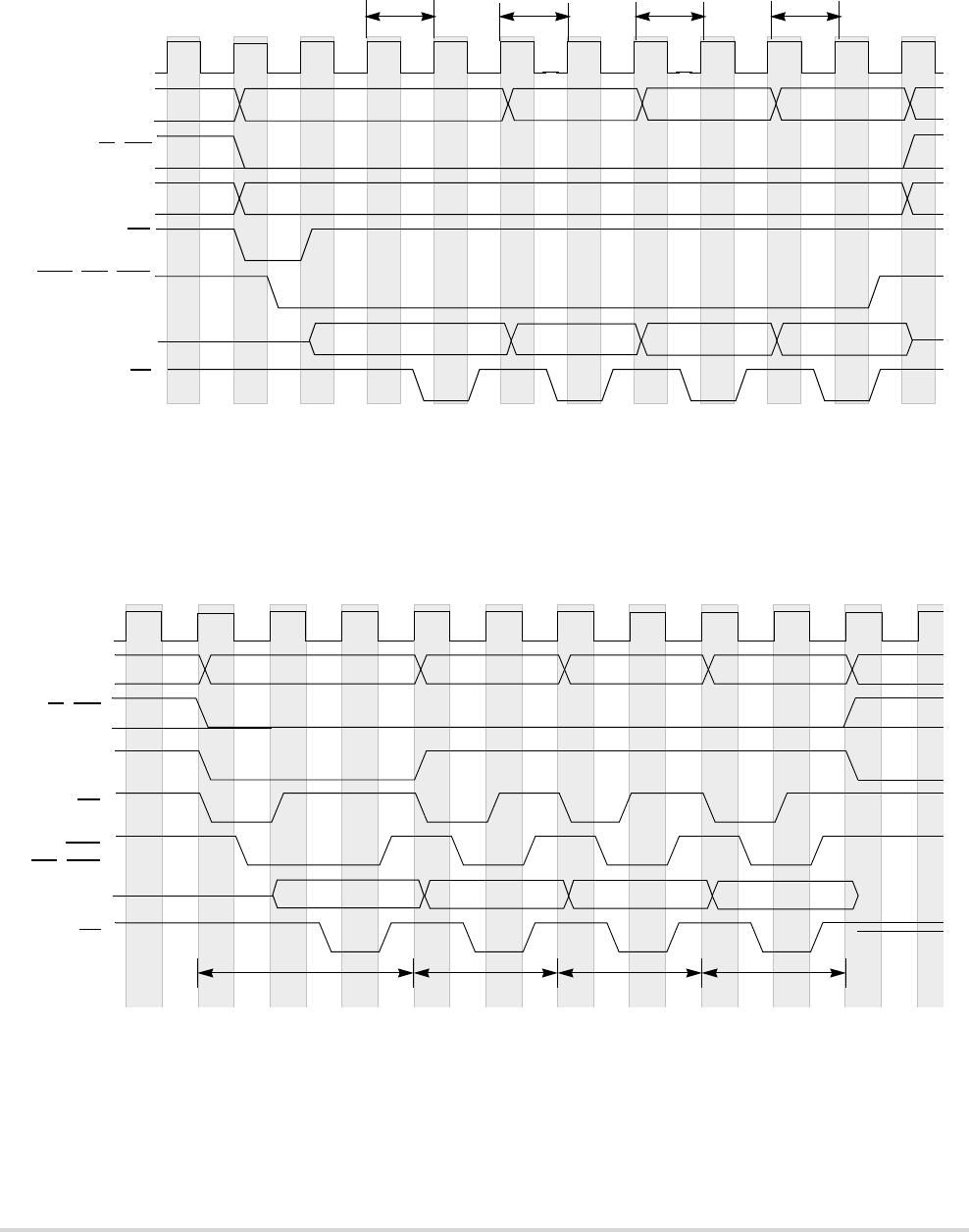

- Figure 27-41. CCW Freeze Situation 19

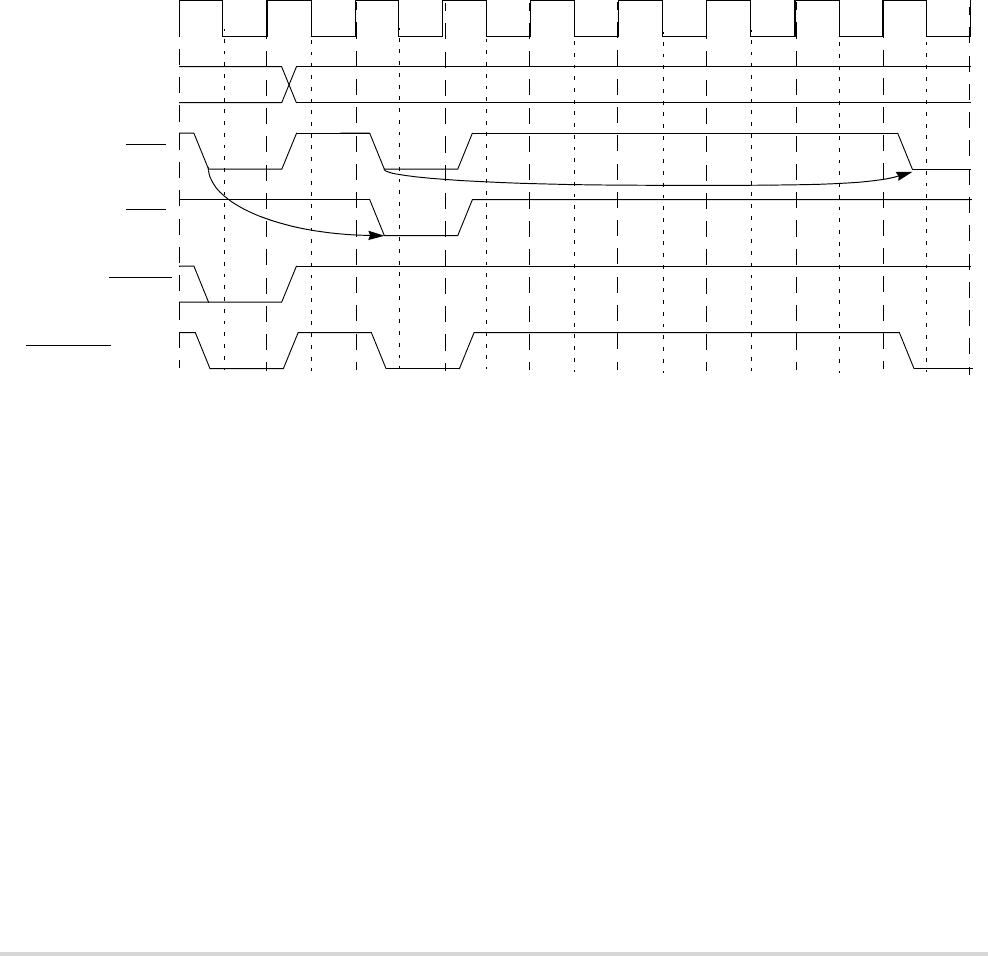

- 27.8.2 Boundary Conditions

- 27.8.3 Scan Modes

- 27.8.4 Disabled Mode

- 27.8.5 Reserved Mode

- 27.8.6 Single-Scan Modes

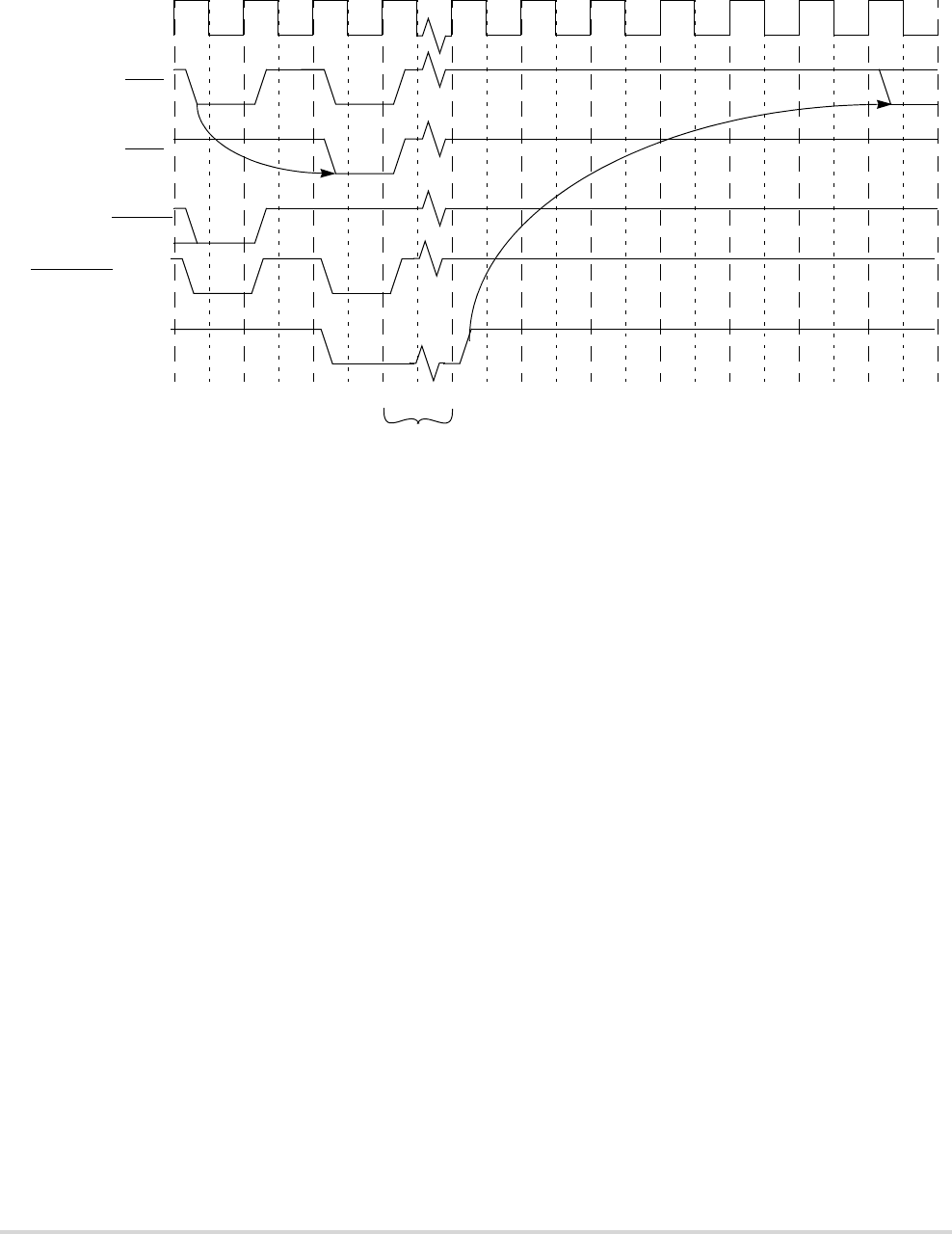

- 27.8.7 Continuous-Scan Modes

- 27.8.8 QADC Clock (QCLK) Generation

- 27.8.9 Periodic/Interval Timer

- 27.8.10 Conversion Command Word Table

- 27.8.11 Result Word Table

- 27.8.1 Queue Priority Timing Examples

- 27.9 Signal Connection Considerations

- 27.10 Interrupts

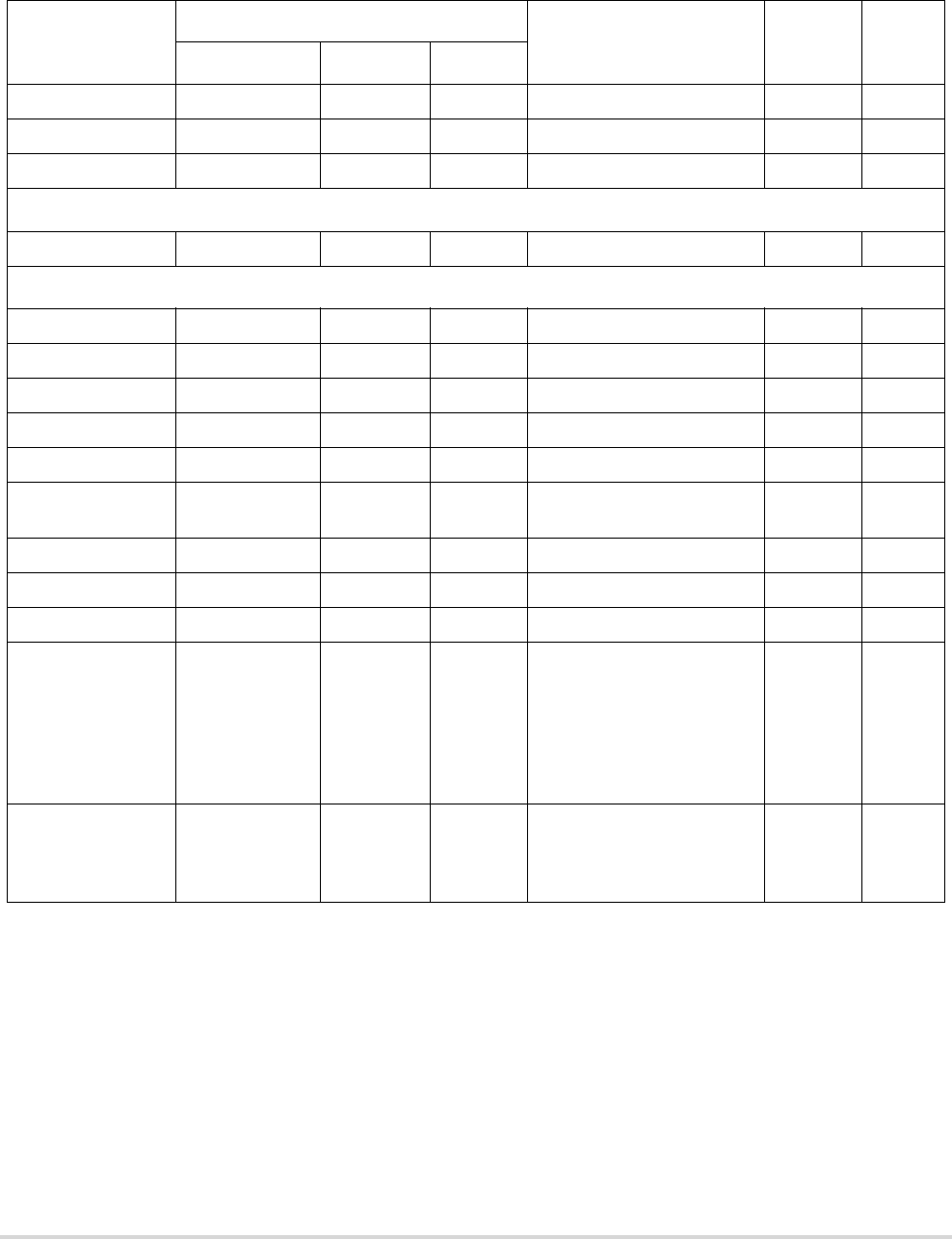

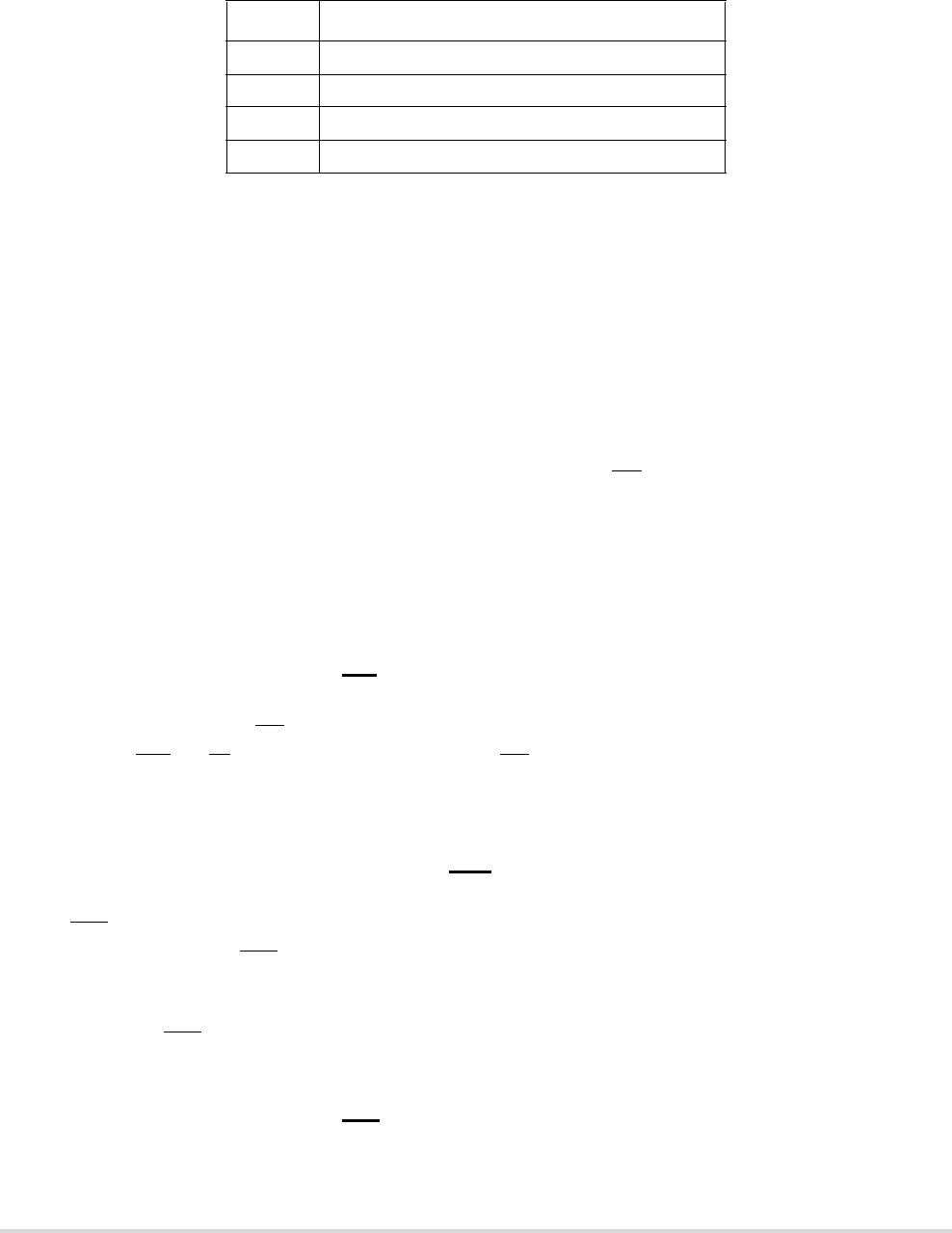

- Chapter 28 Reset Controller Module

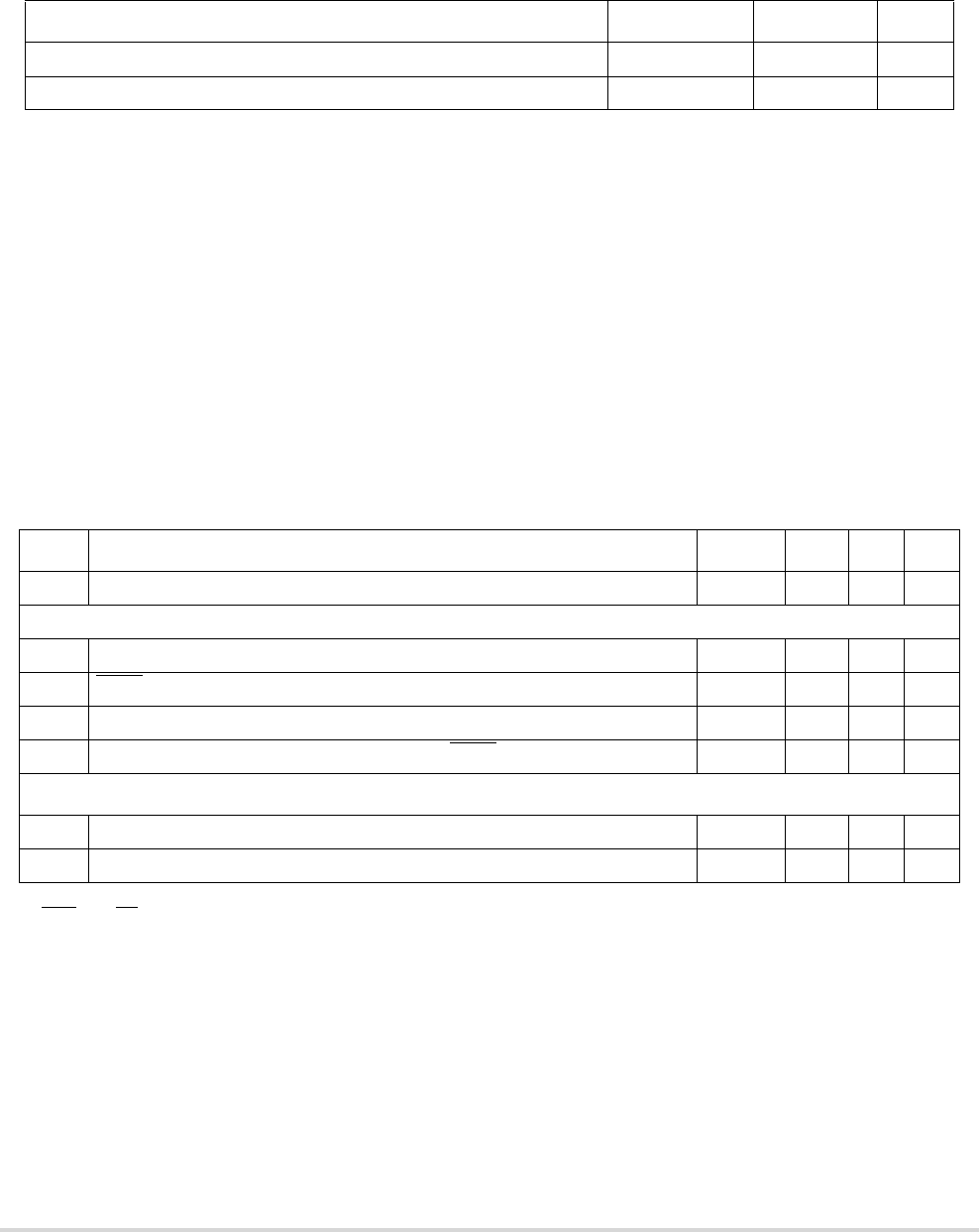

- Chapter 29 Debug Support

- 29.1 Overview

- 29.2 Signal Description

- 29.3 Real-Time Trace Support

- 29.4 Programming Model

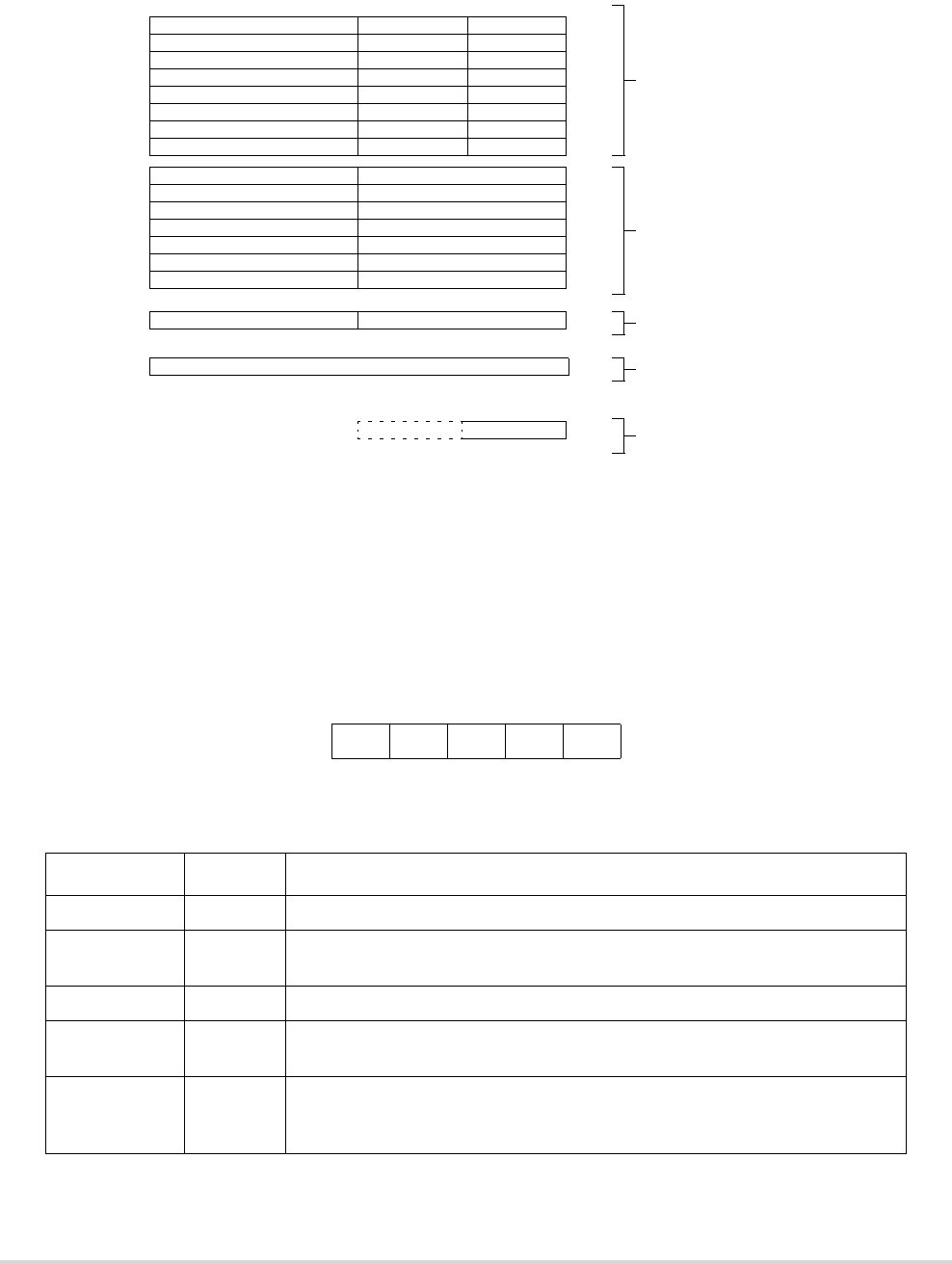

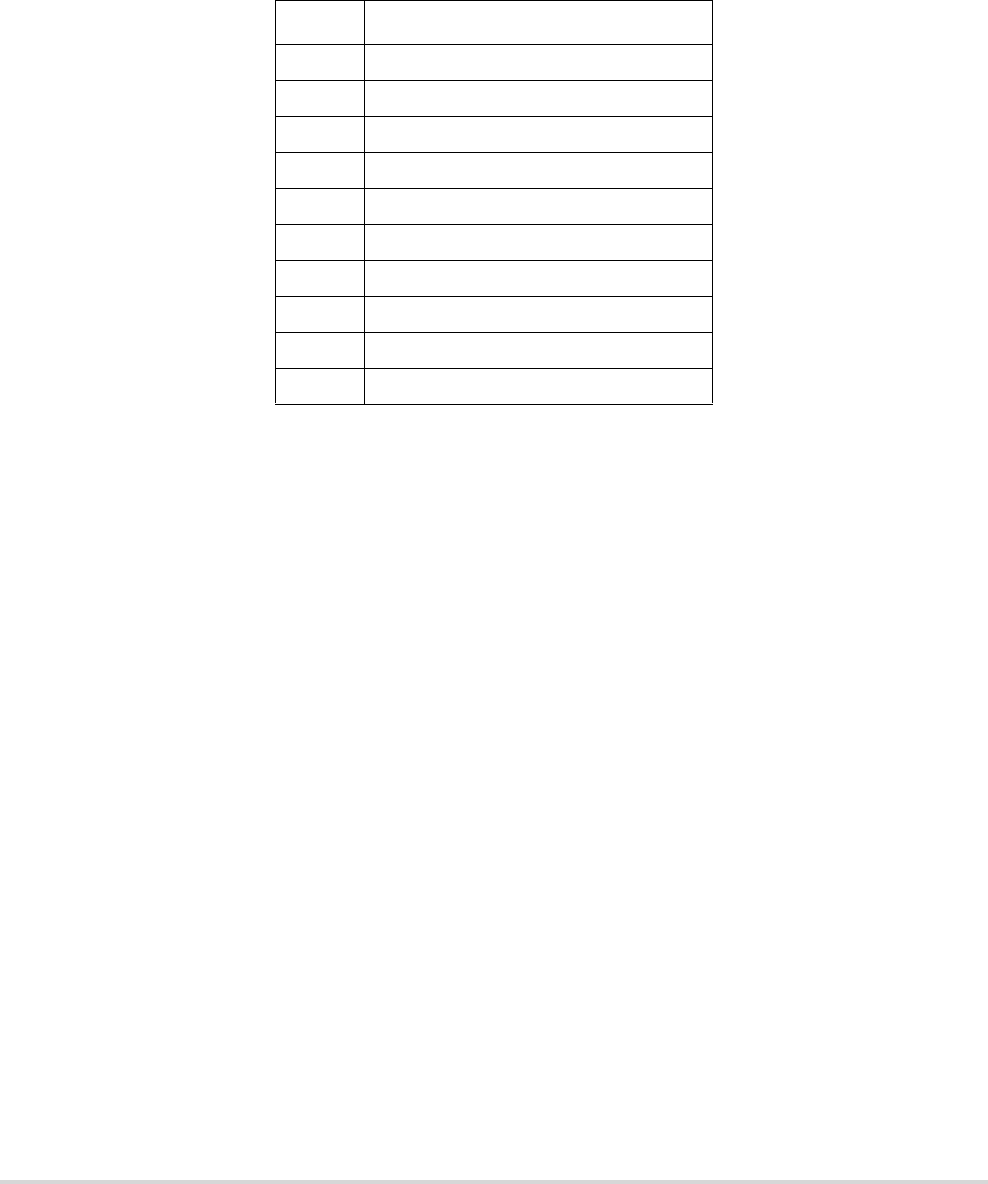

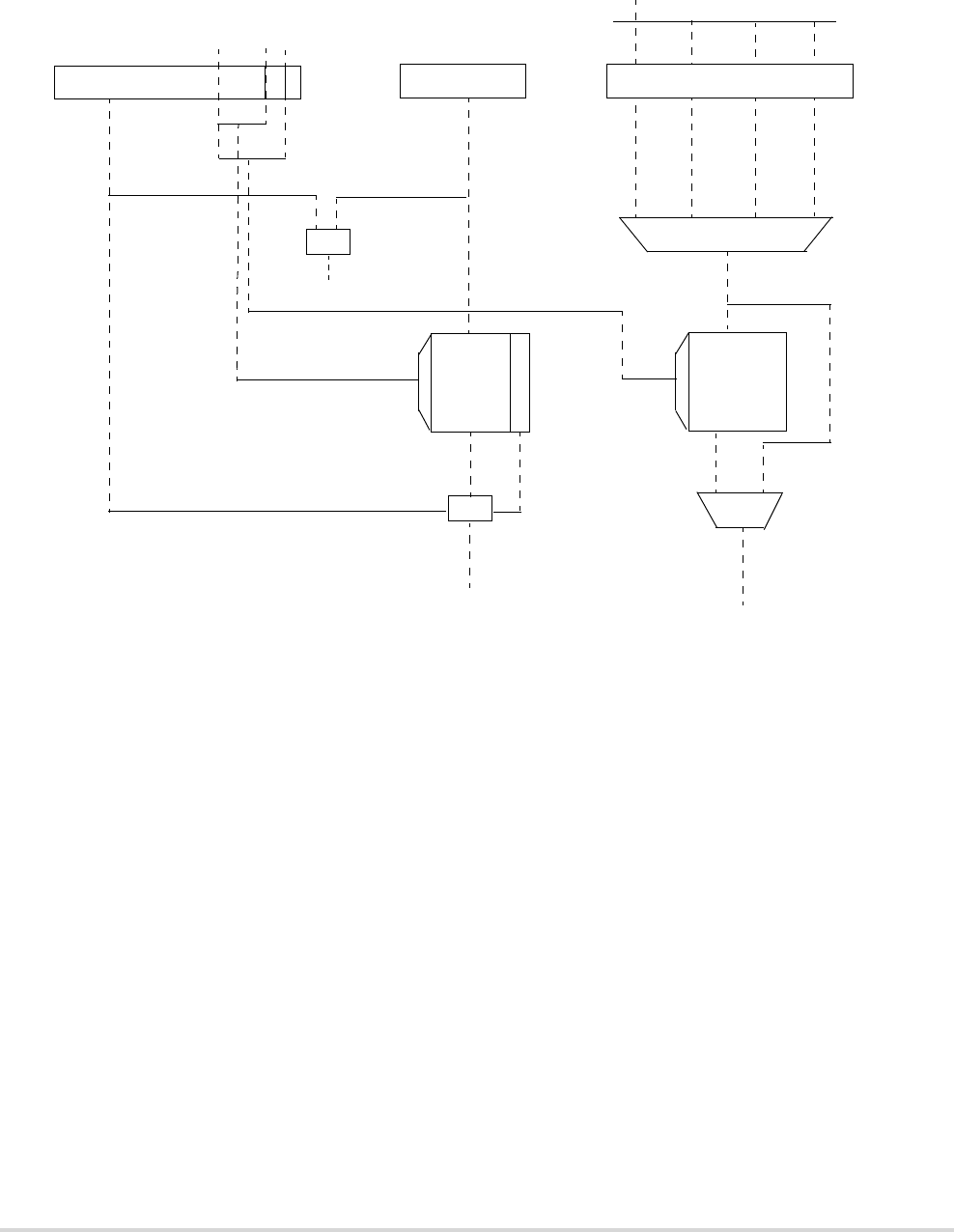

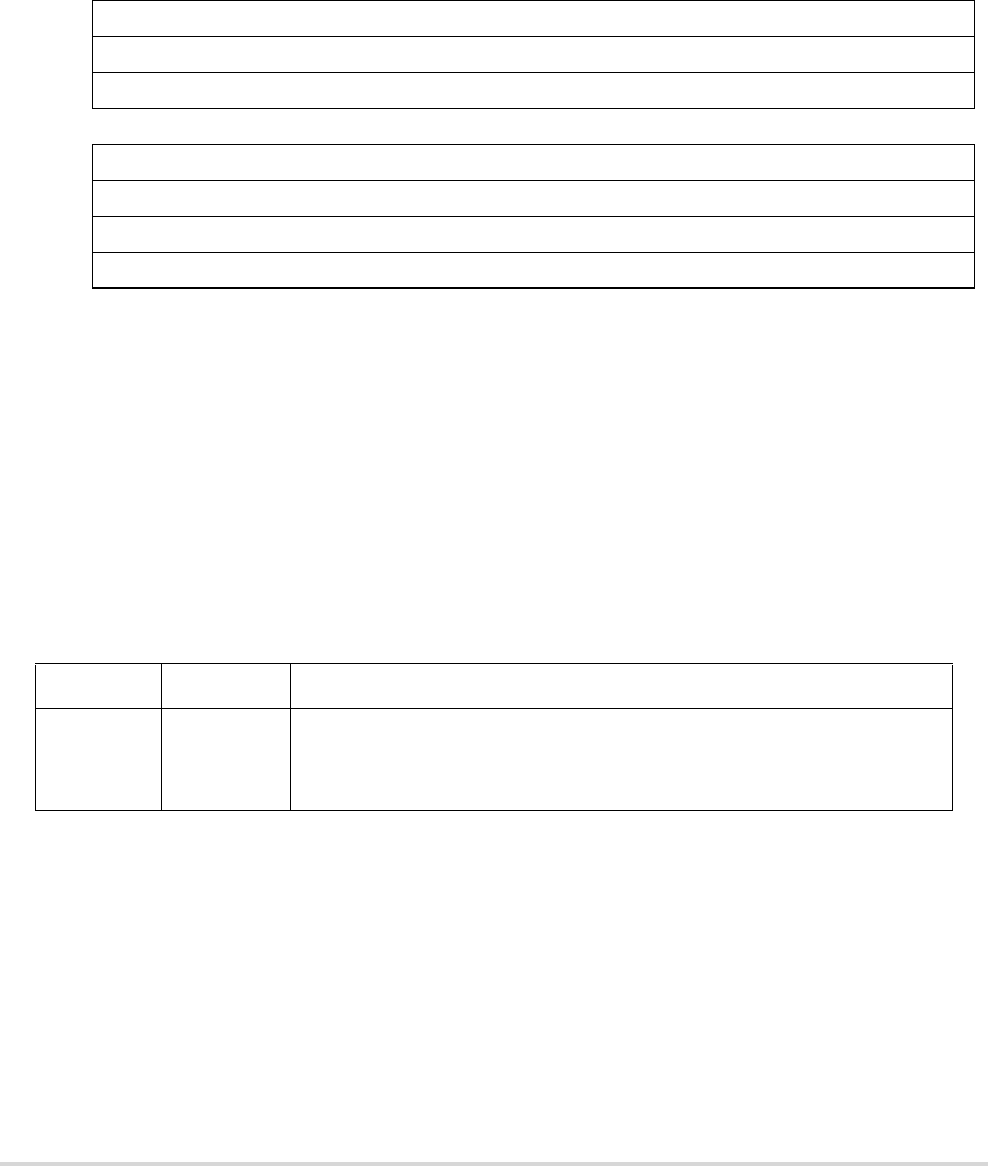

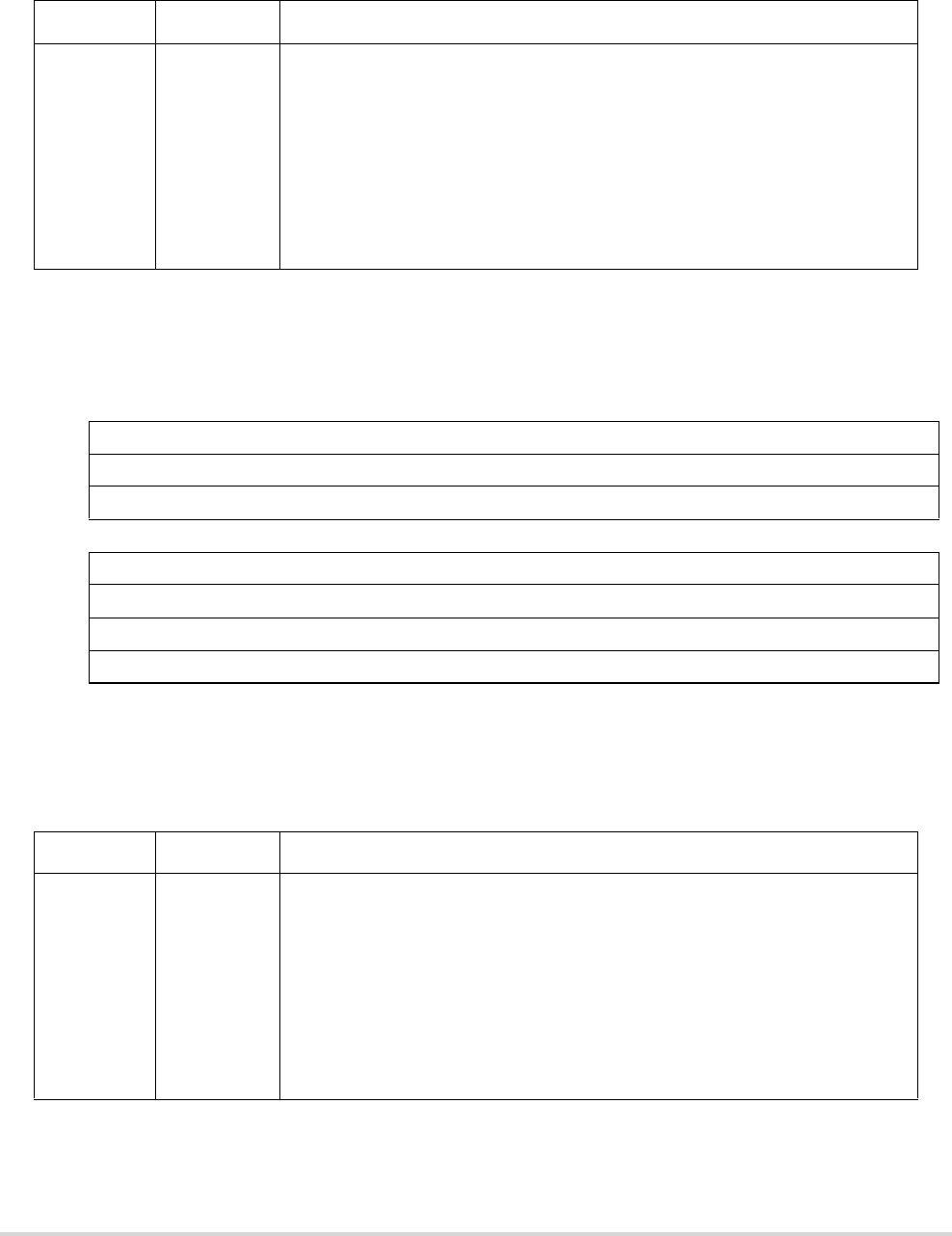

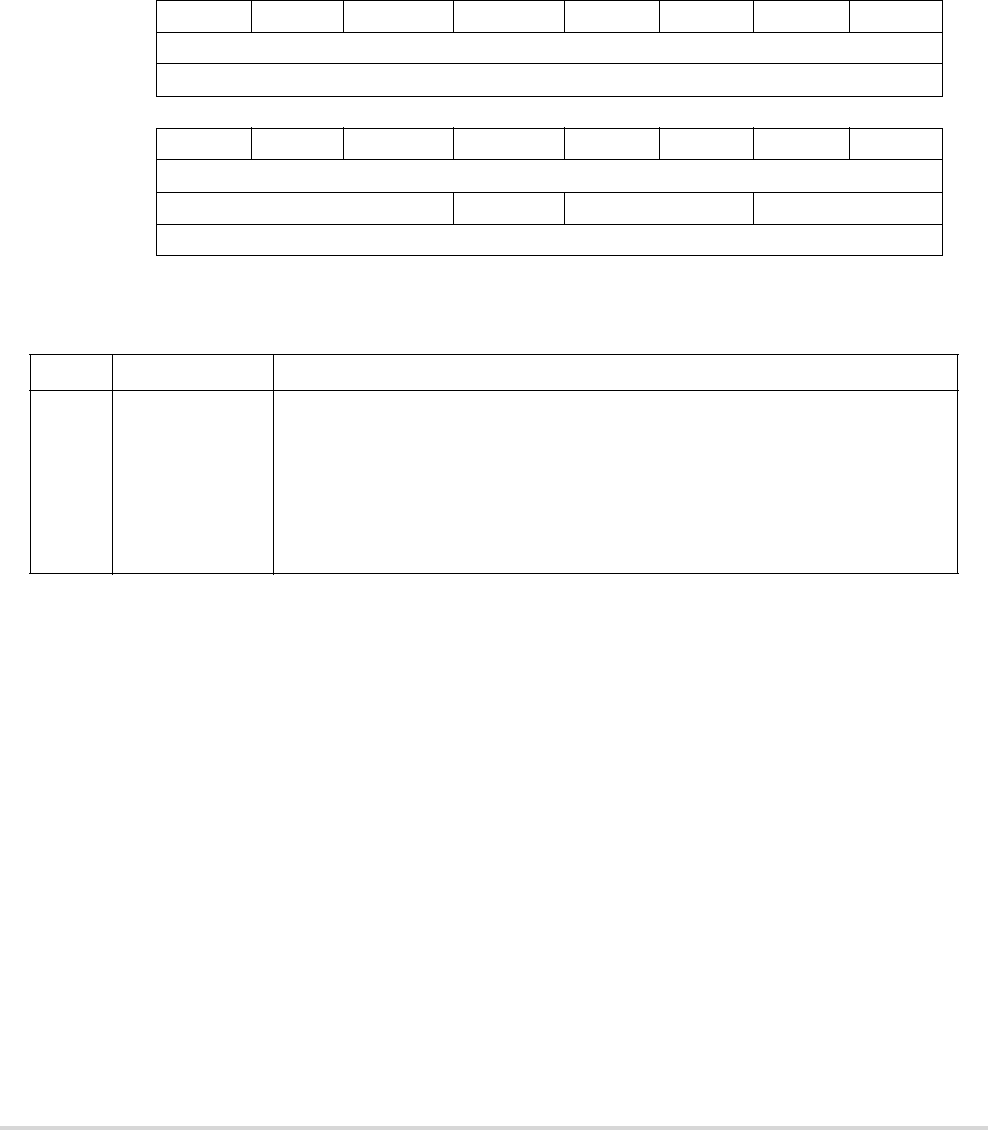

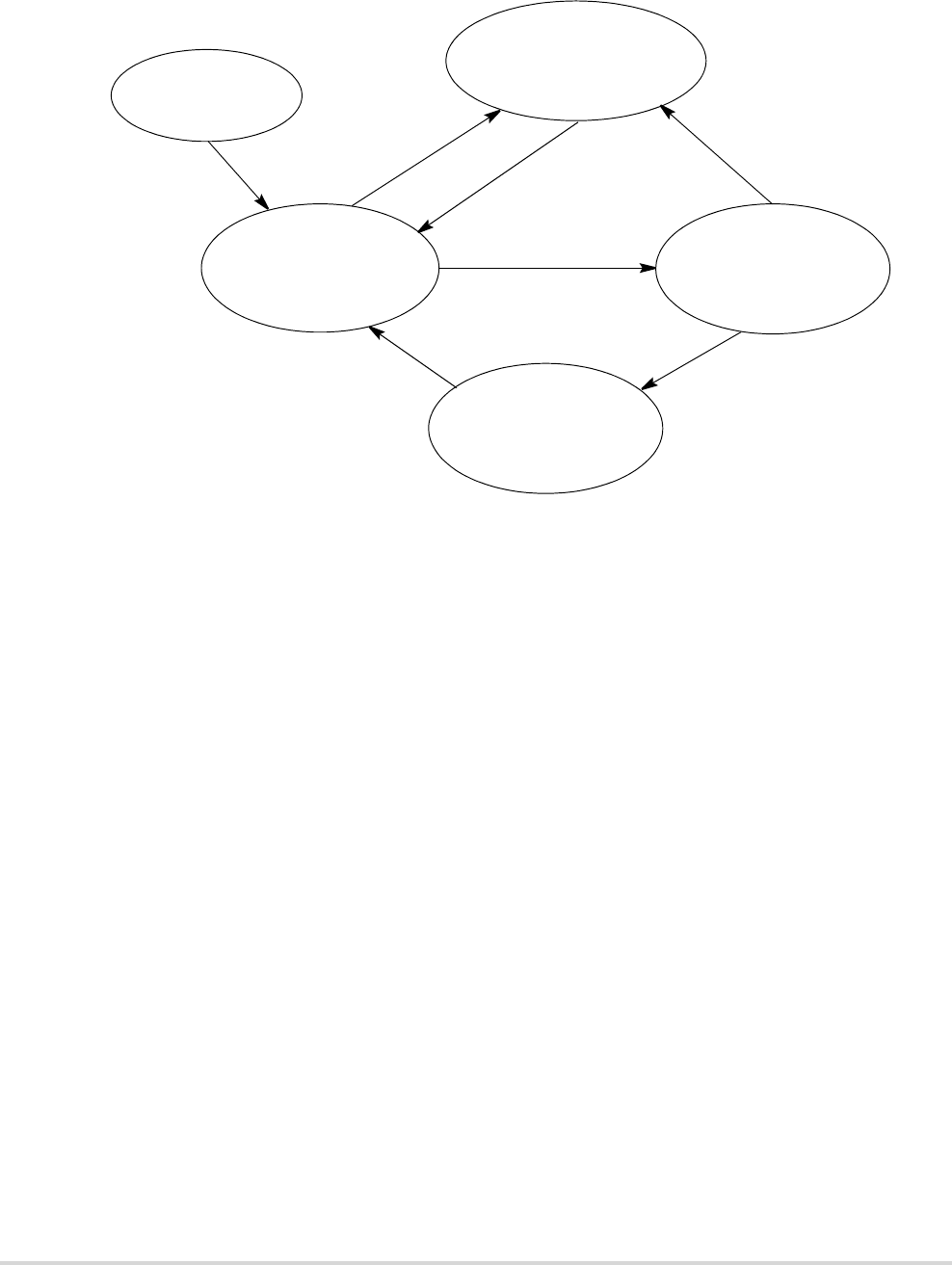

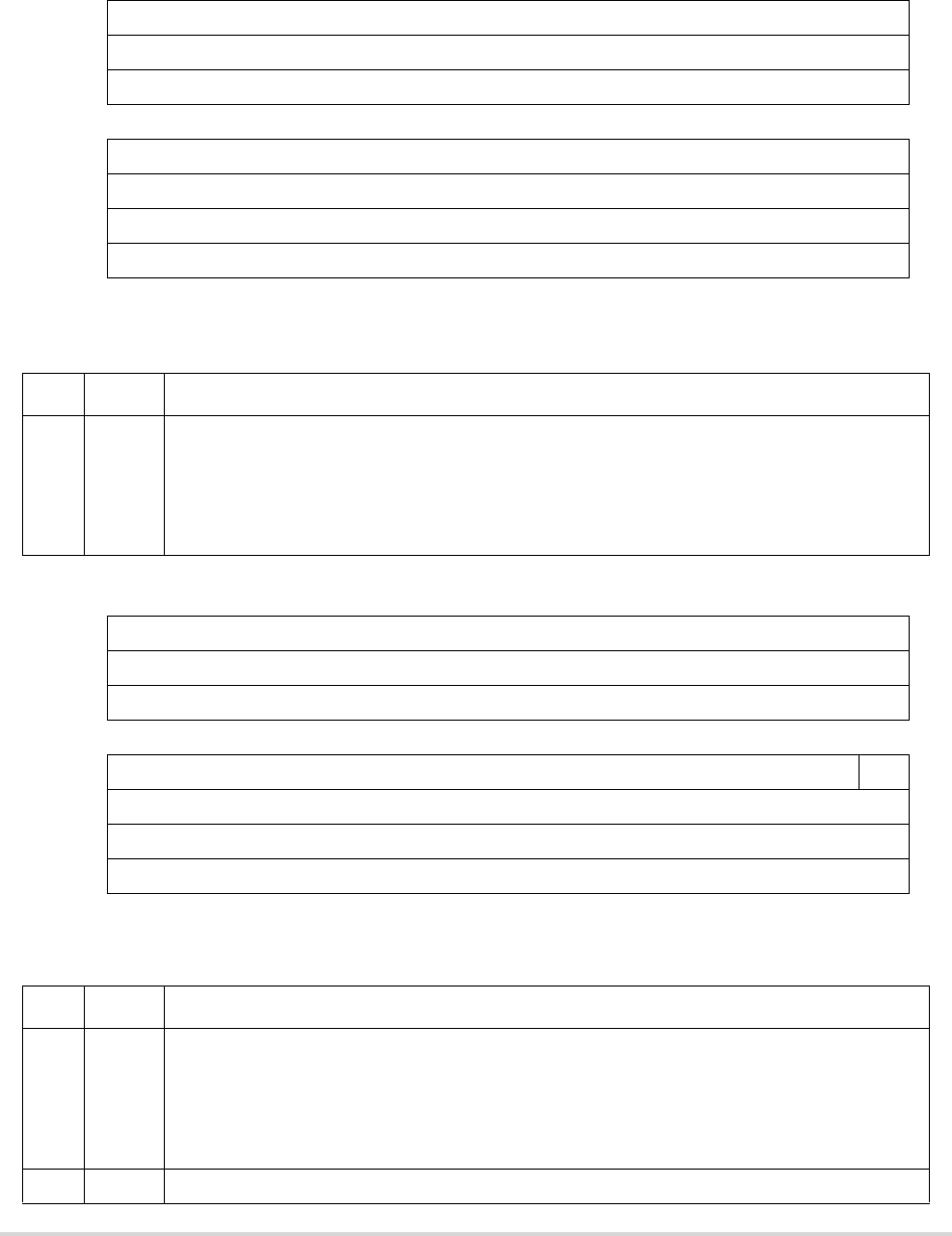

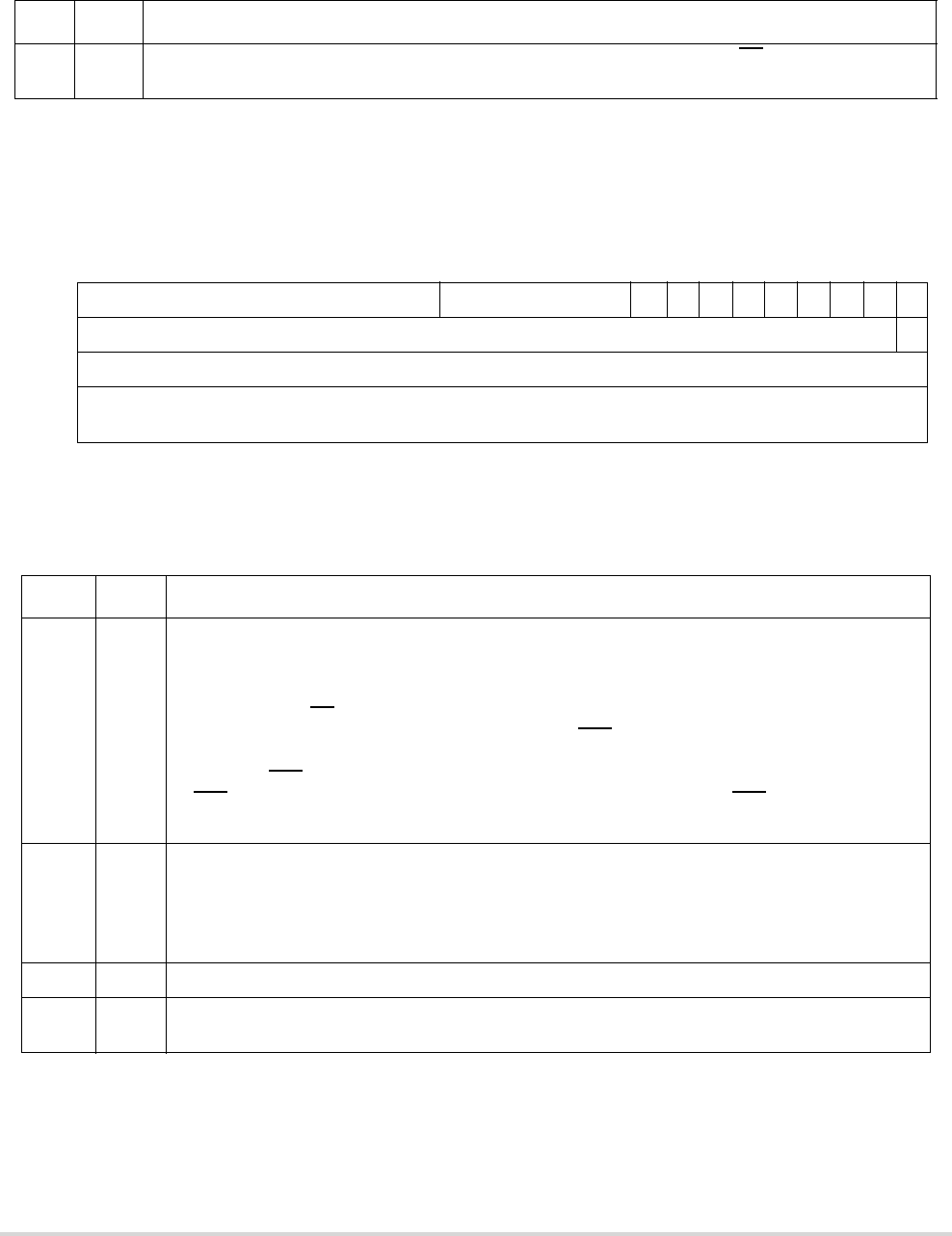

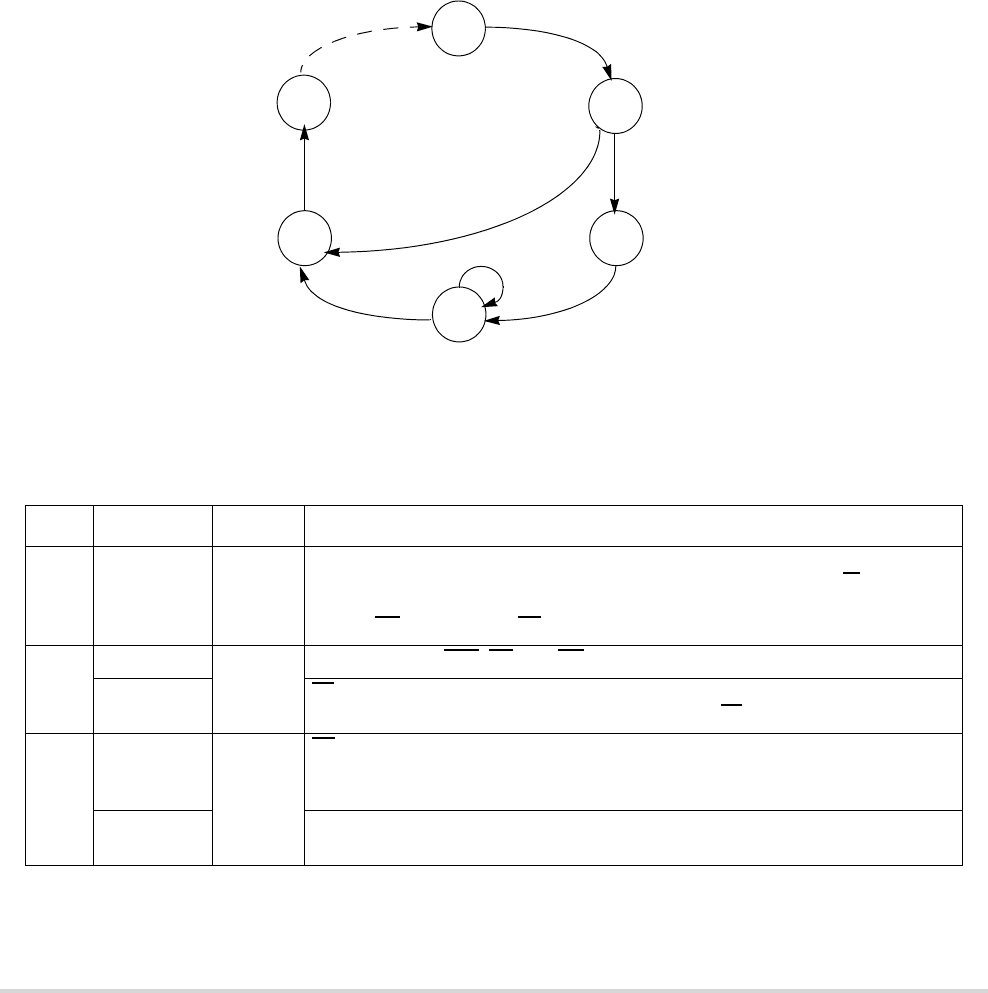

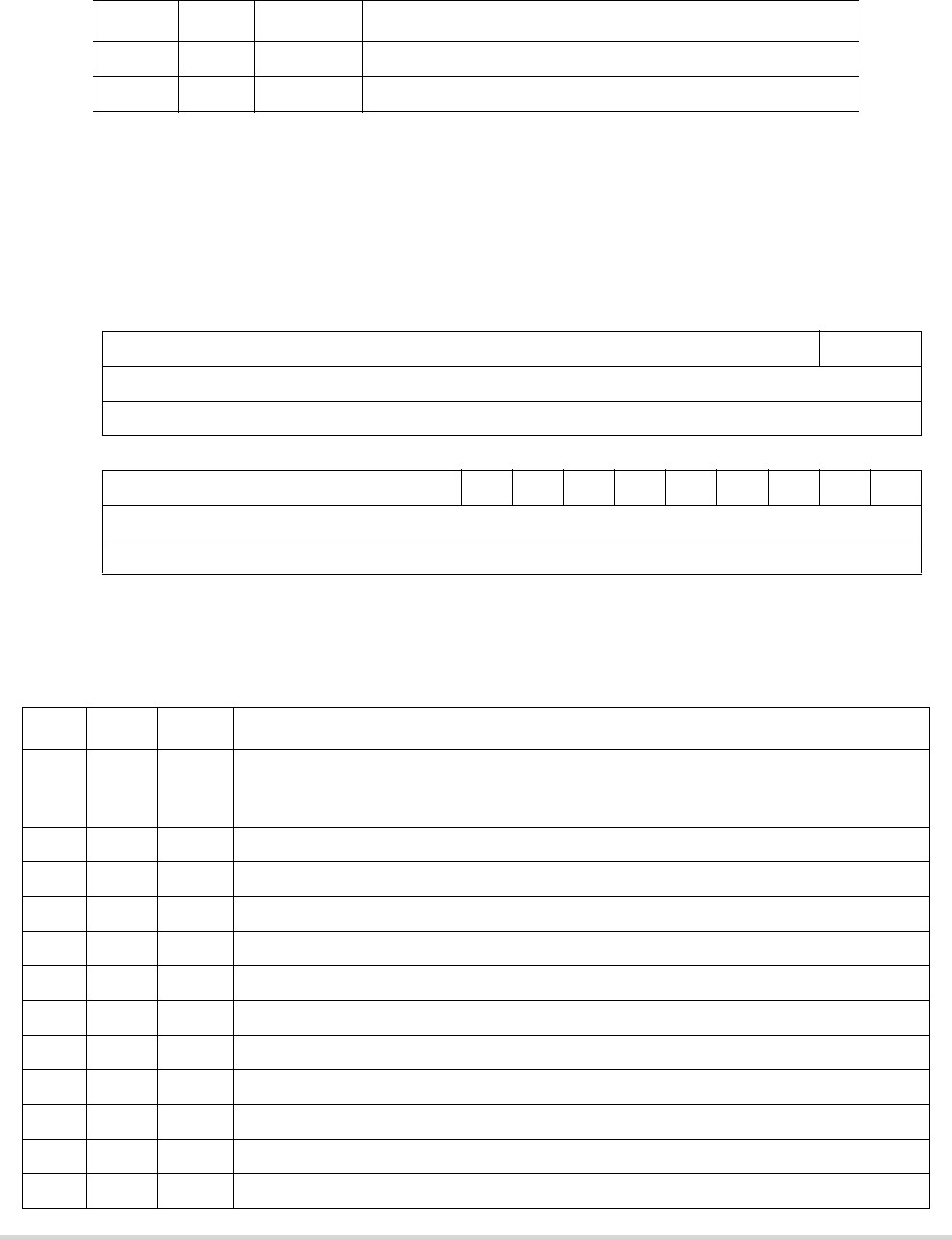

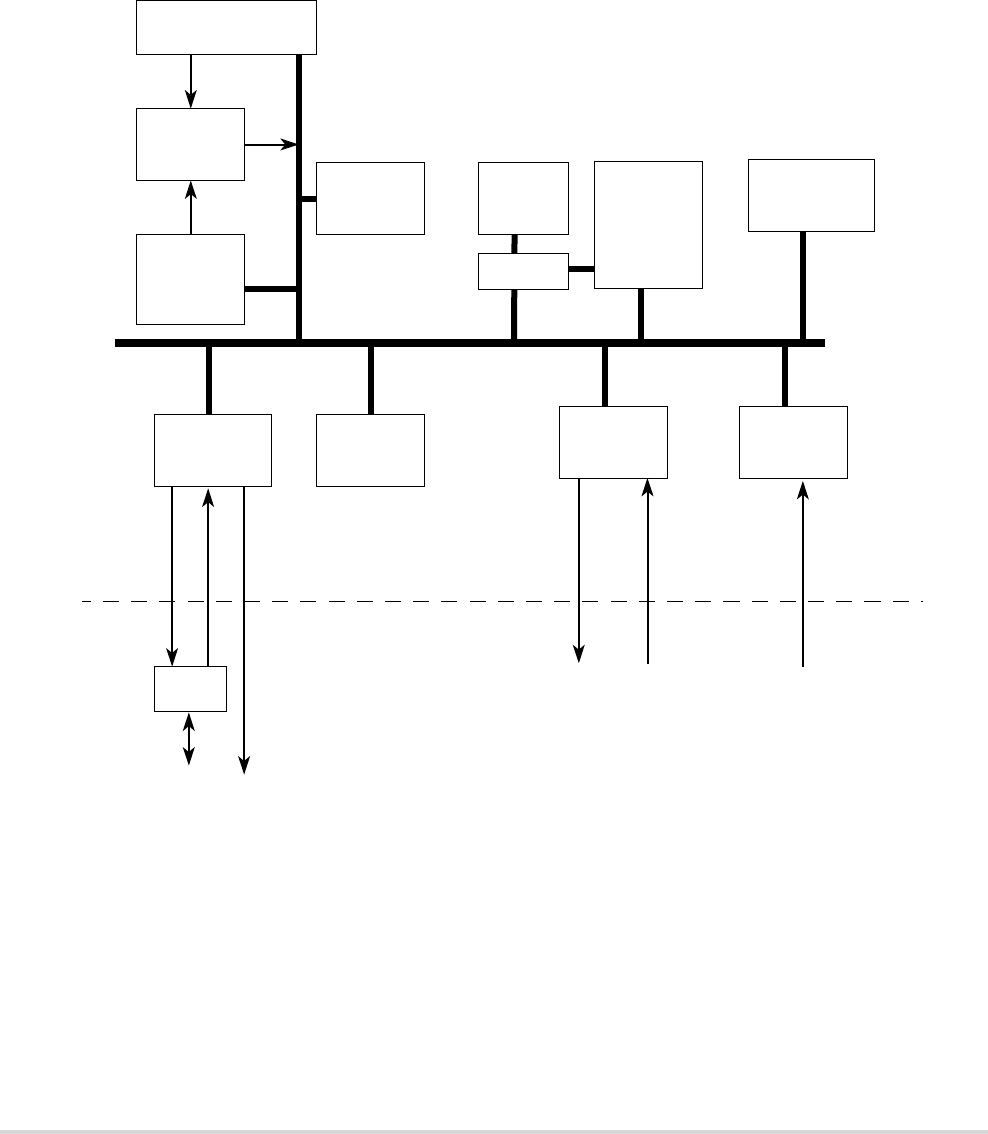

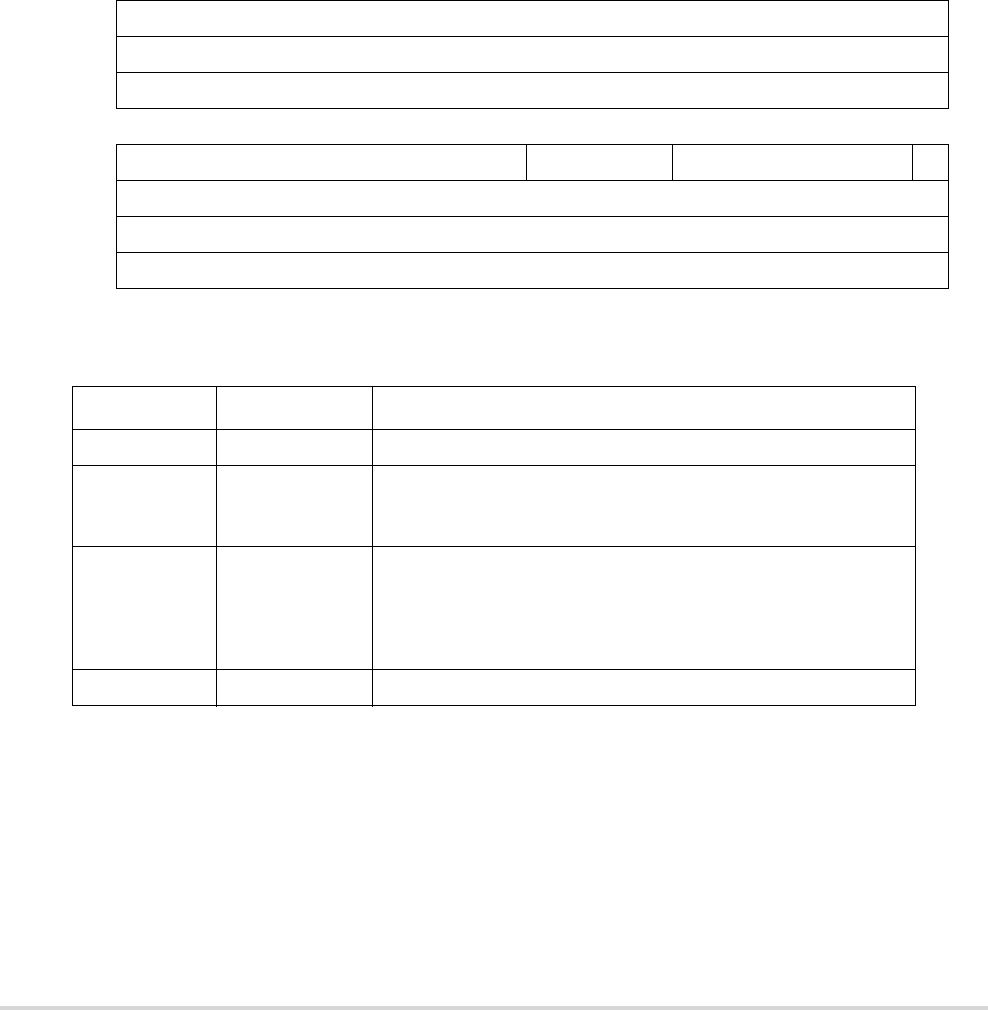

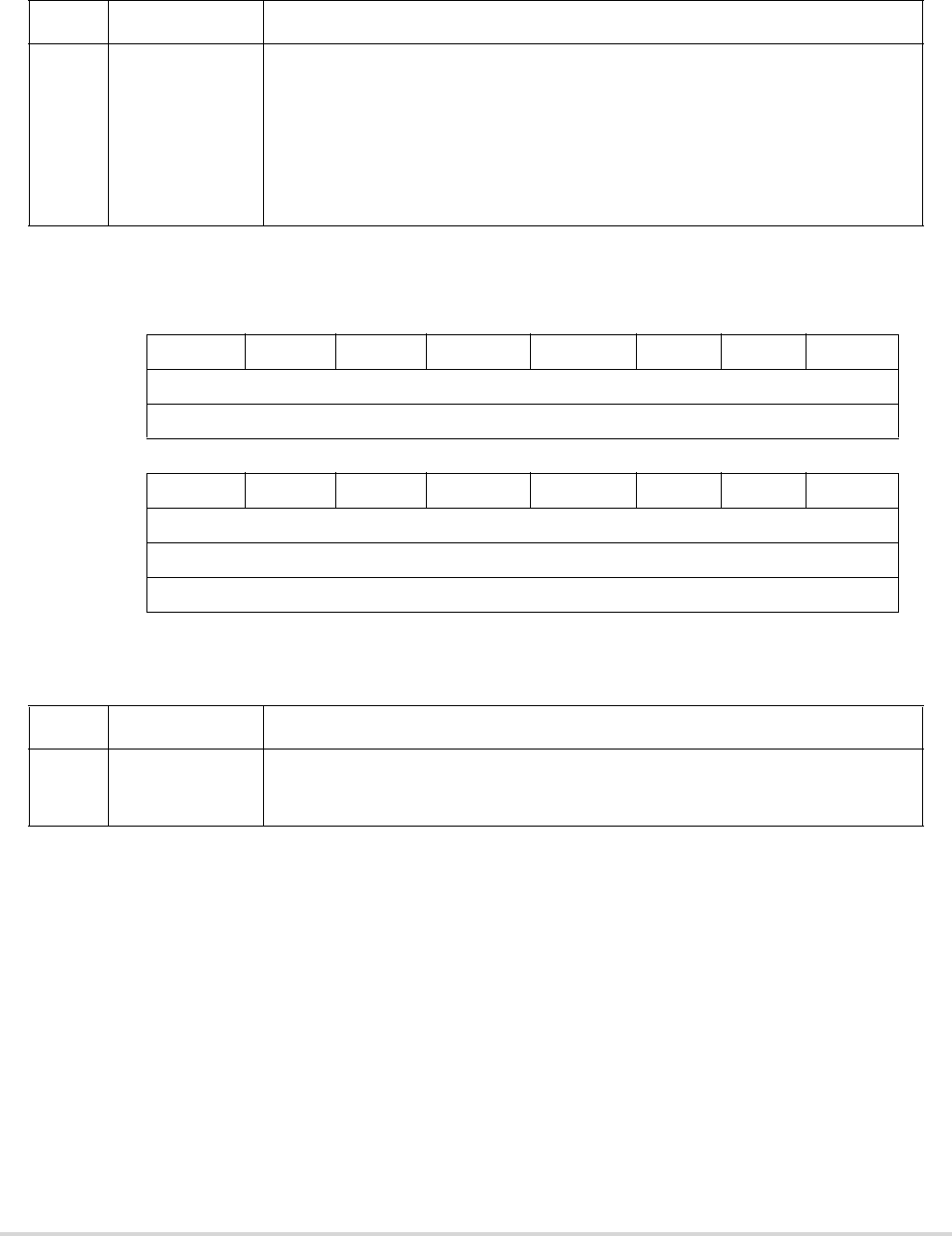

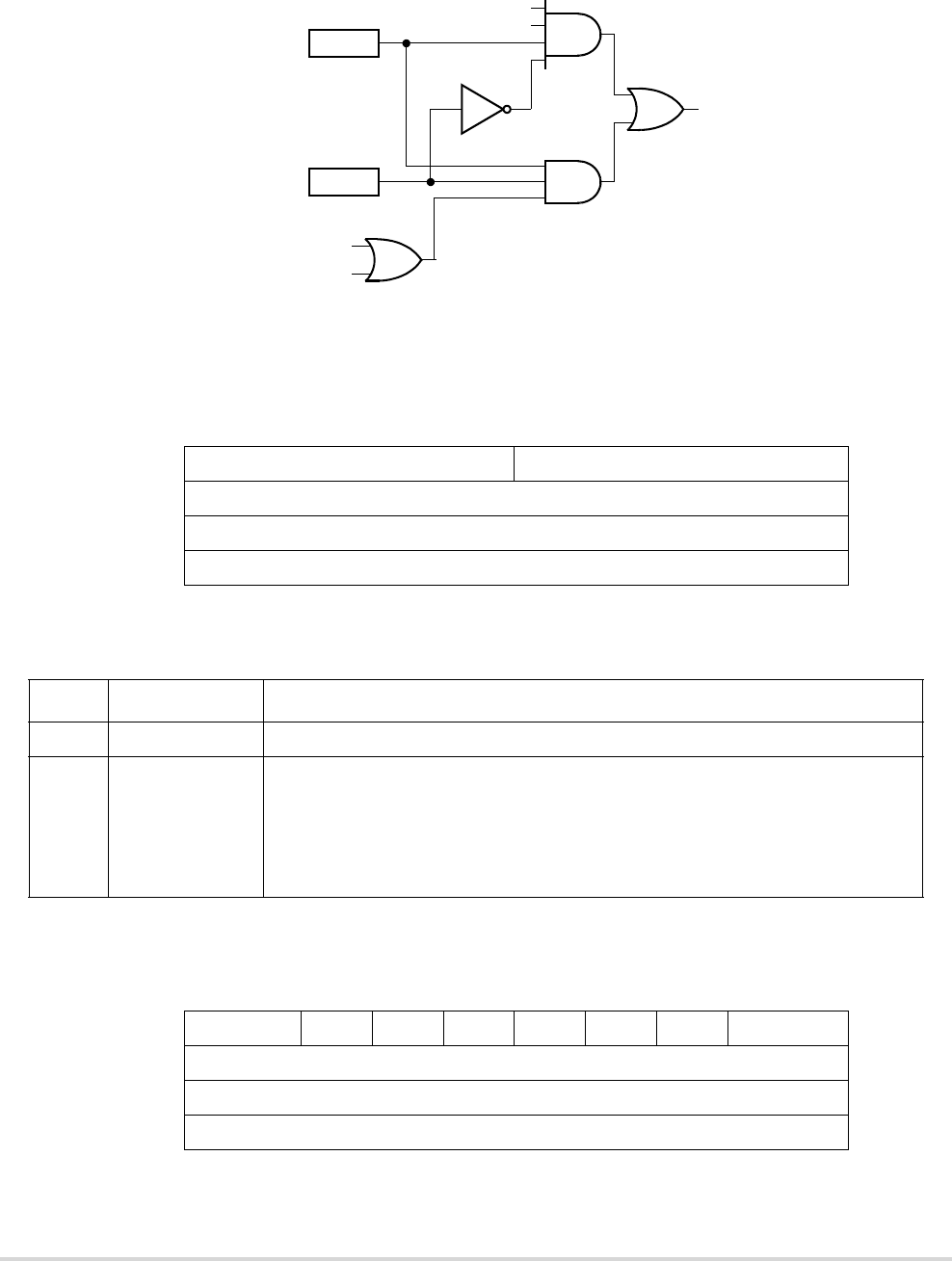

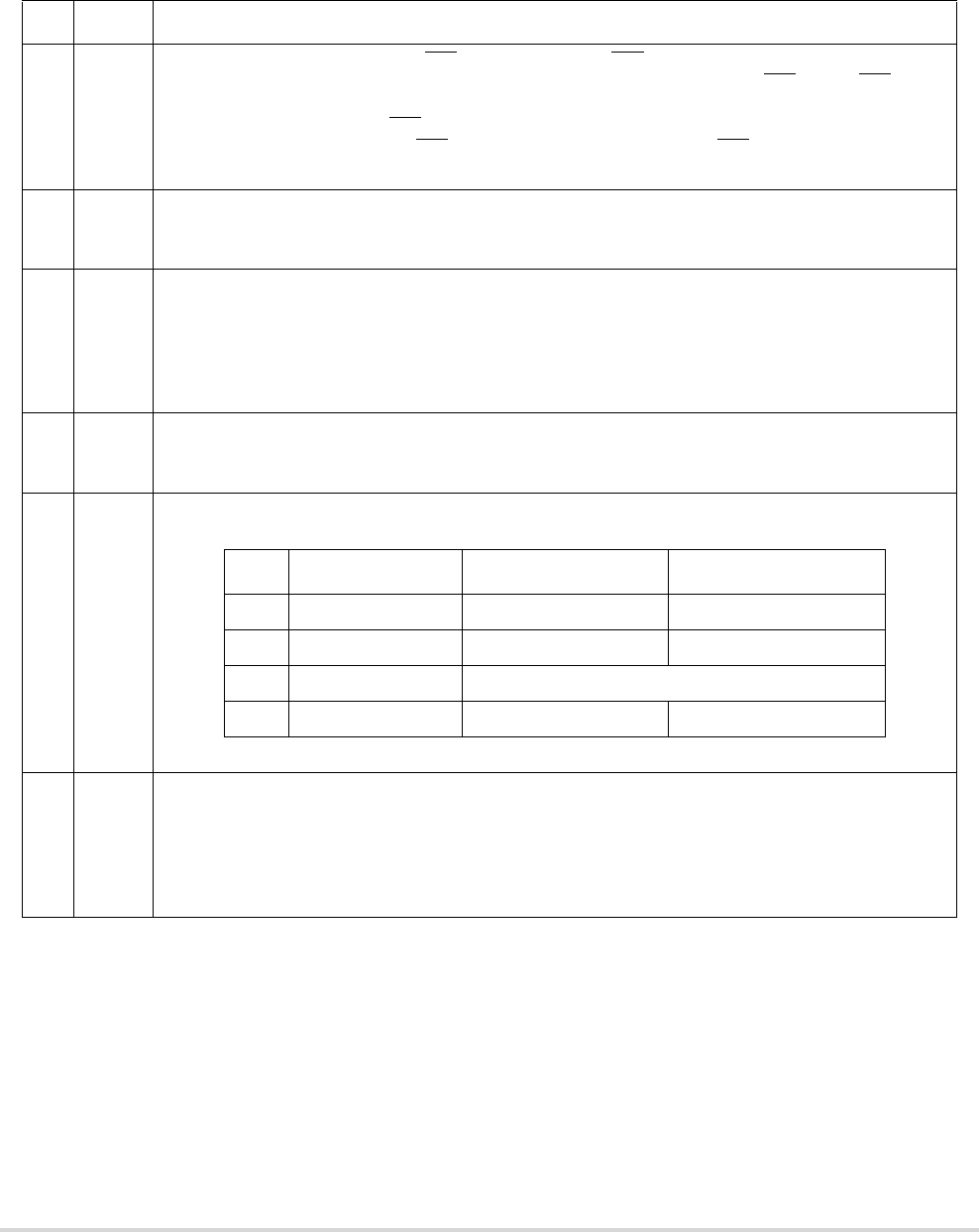

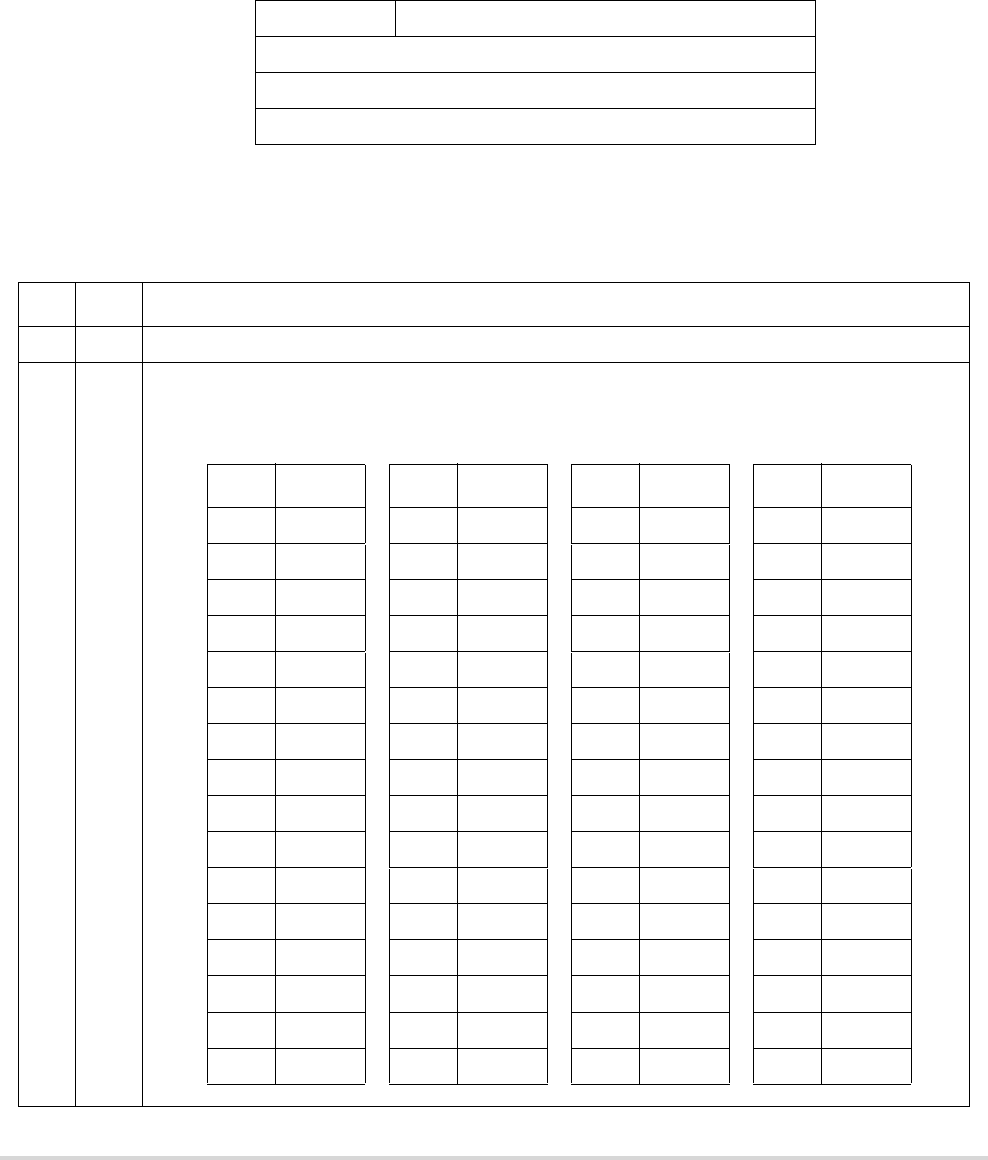

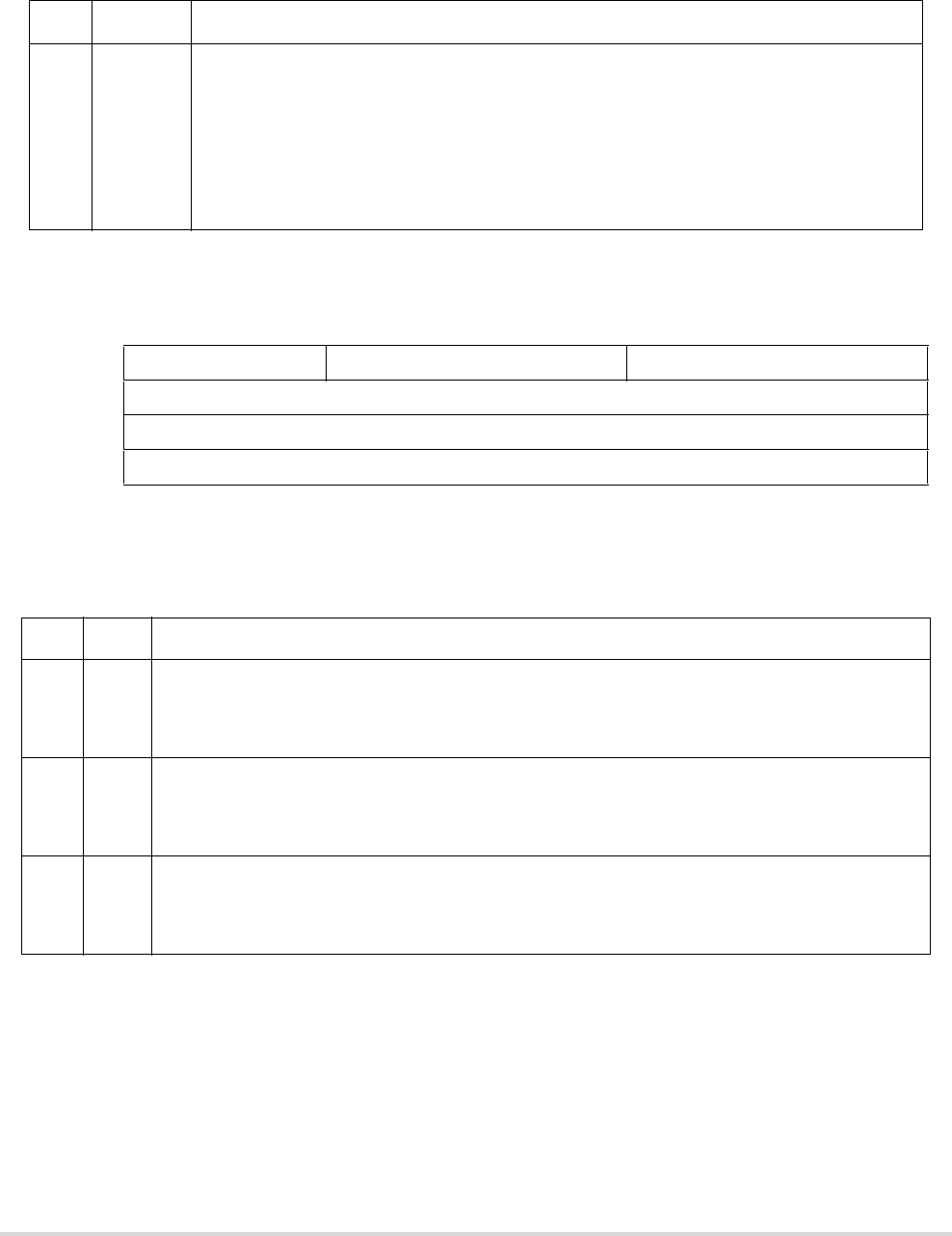

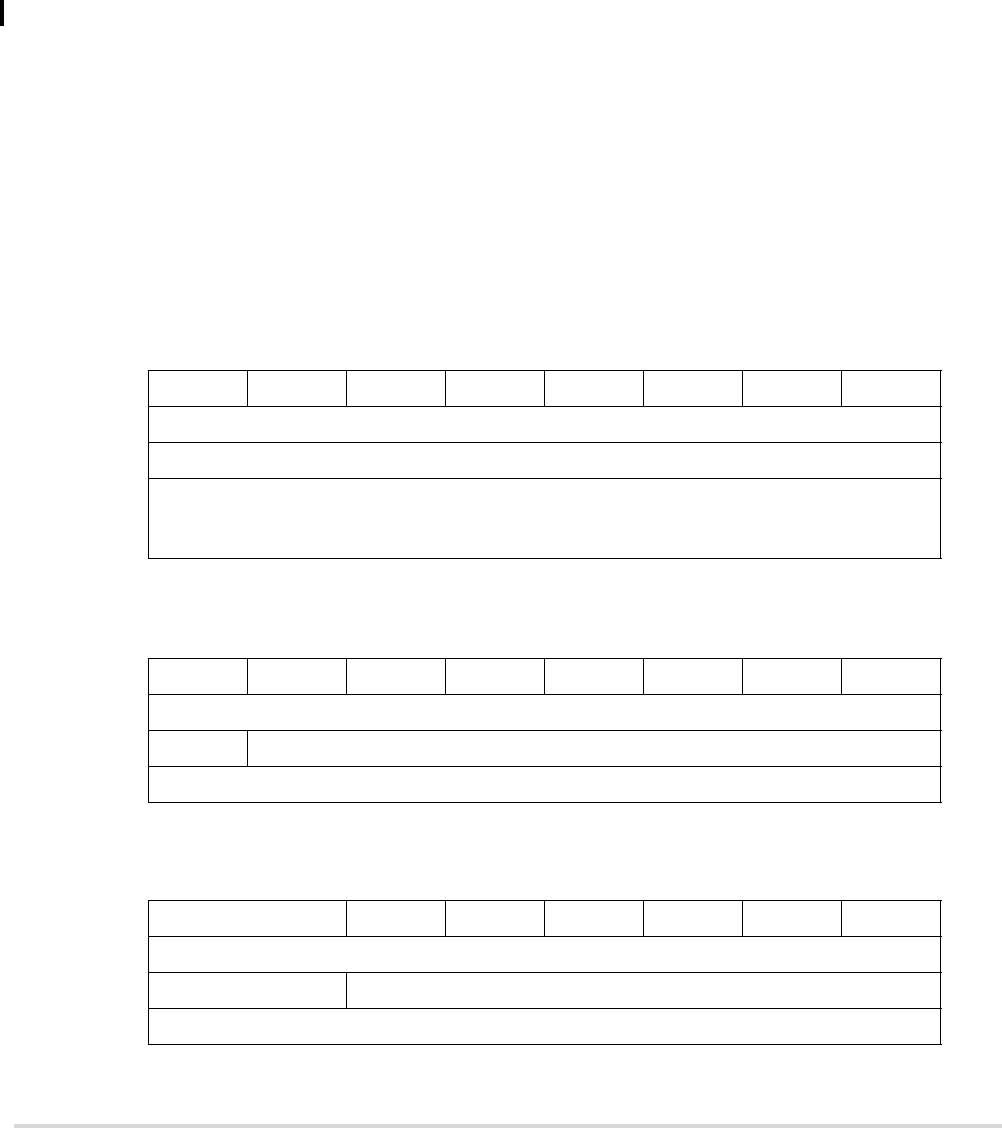

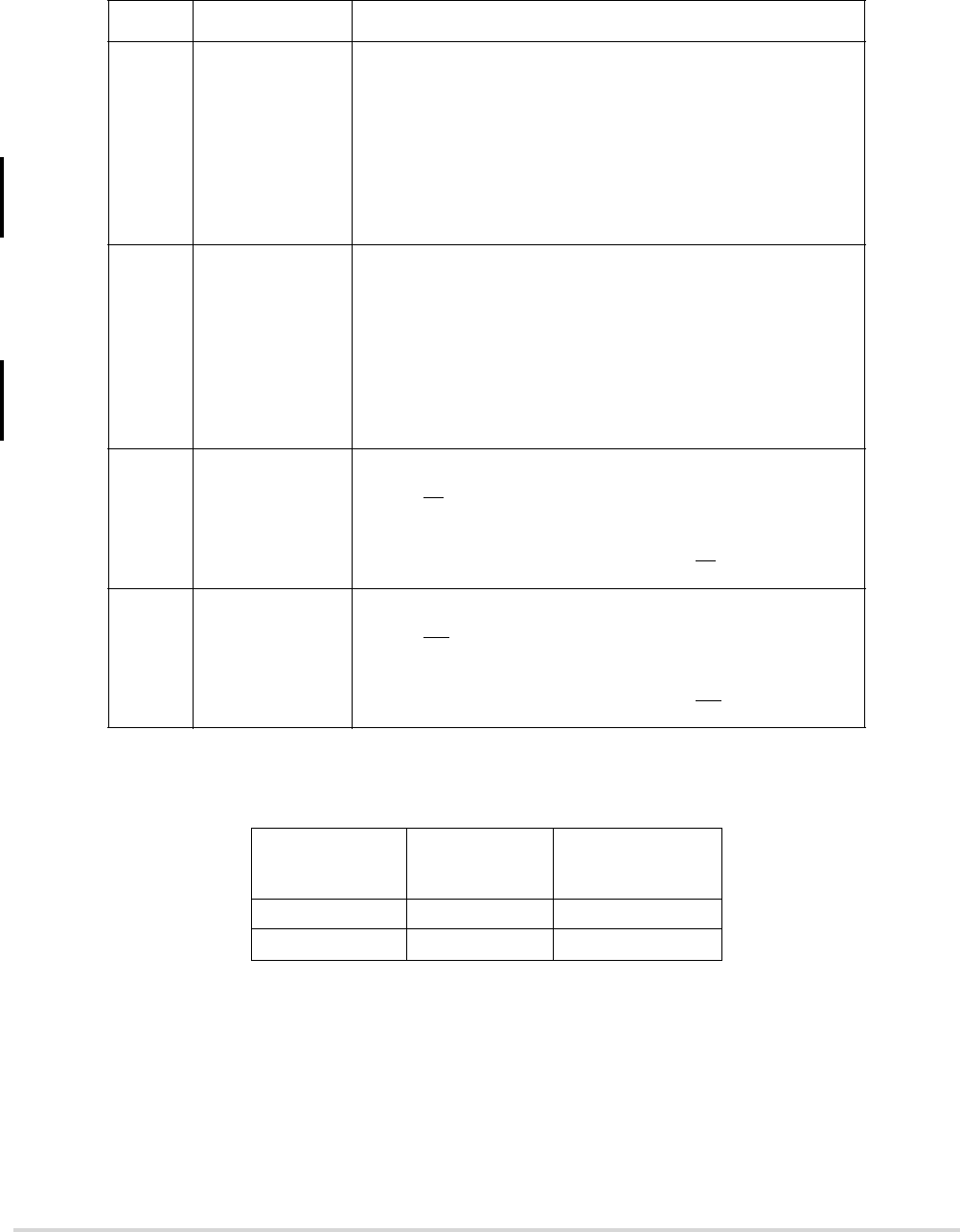

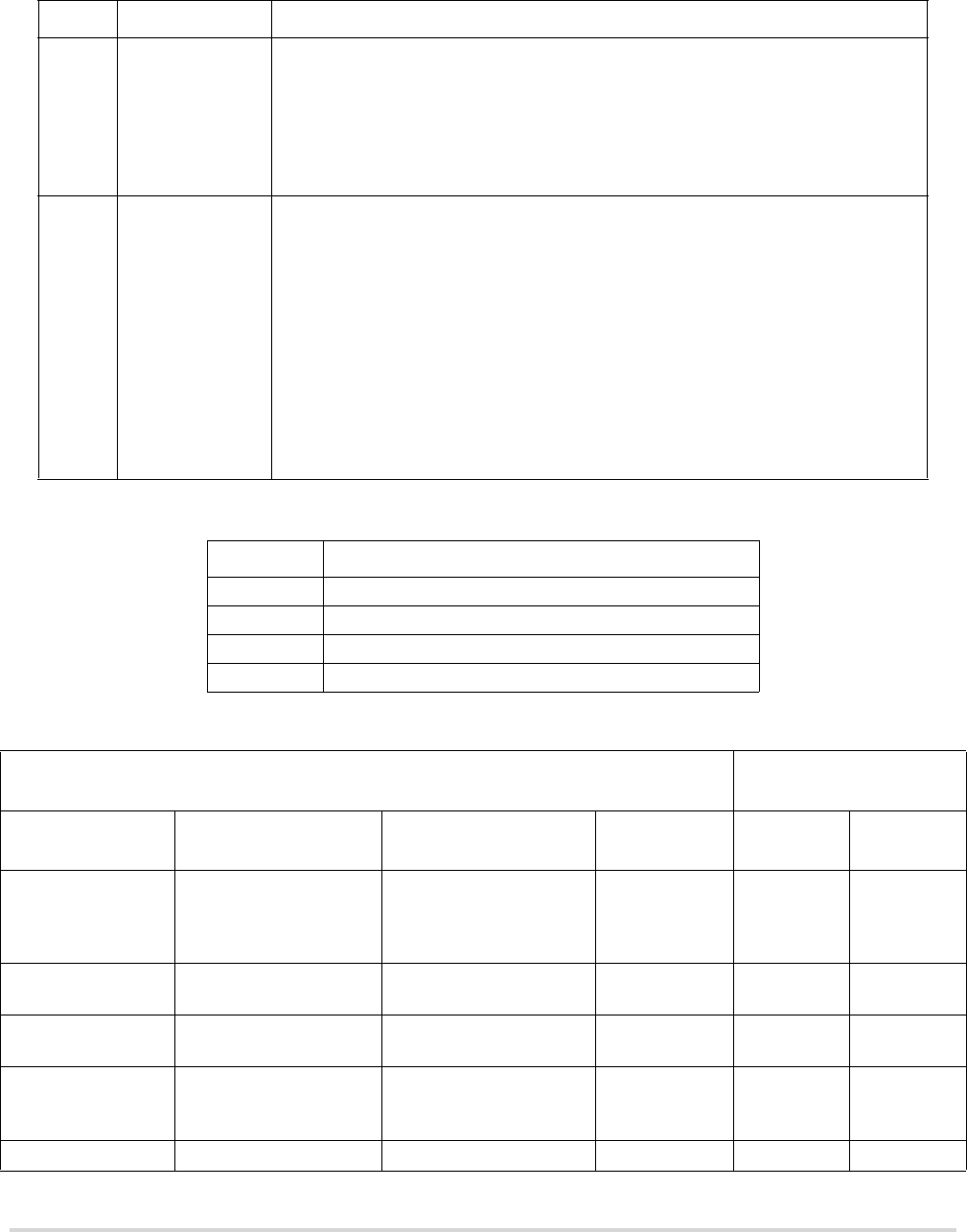

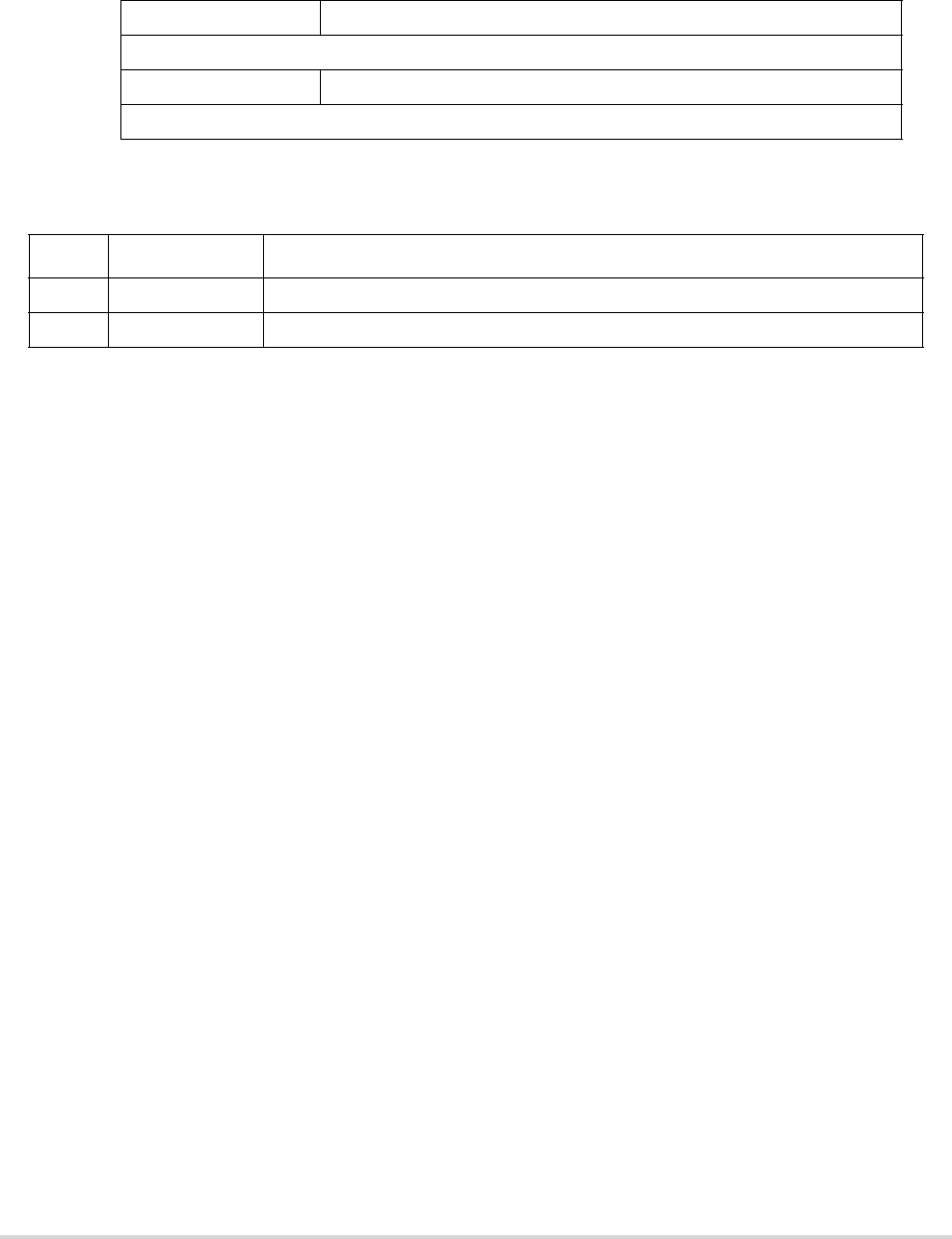

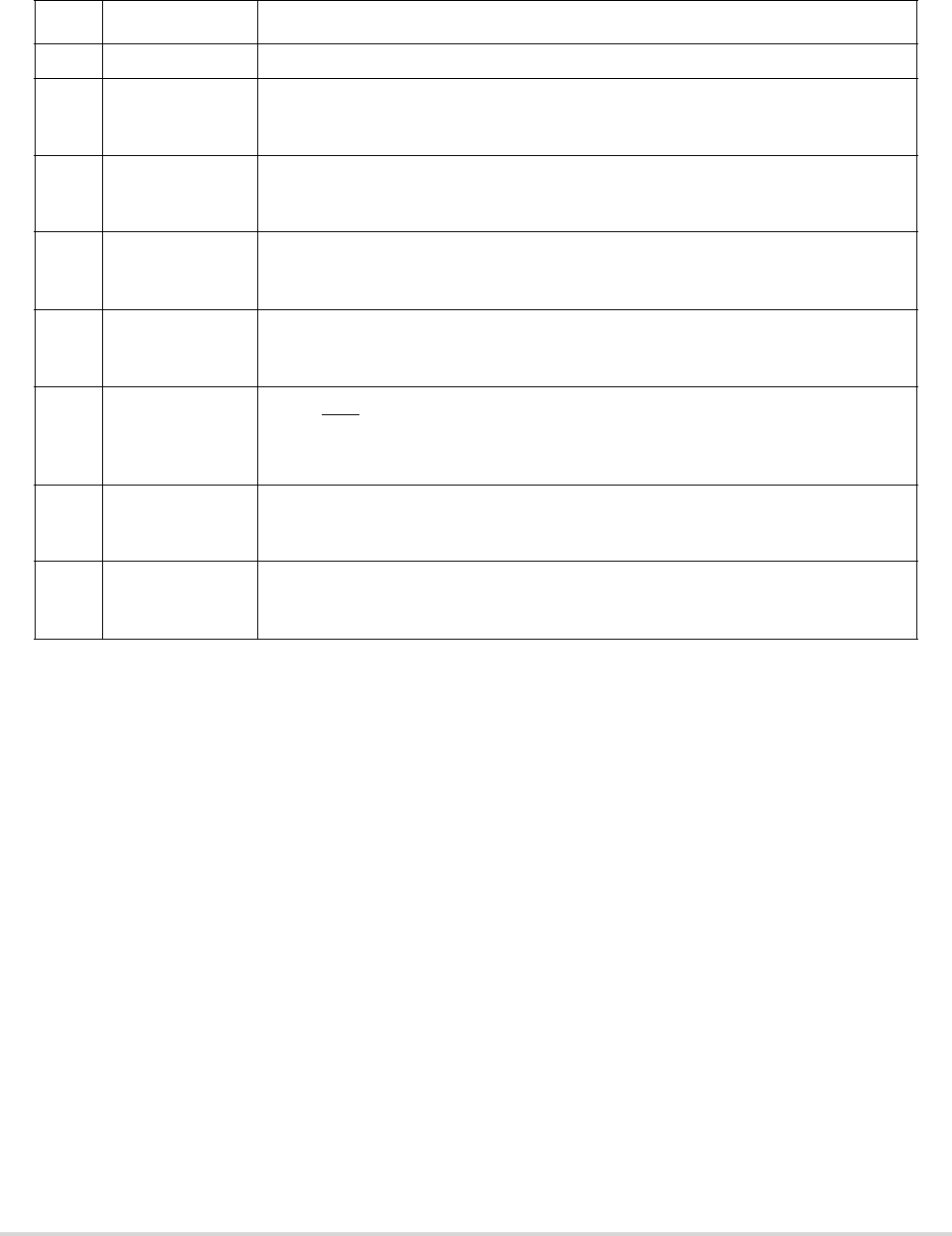

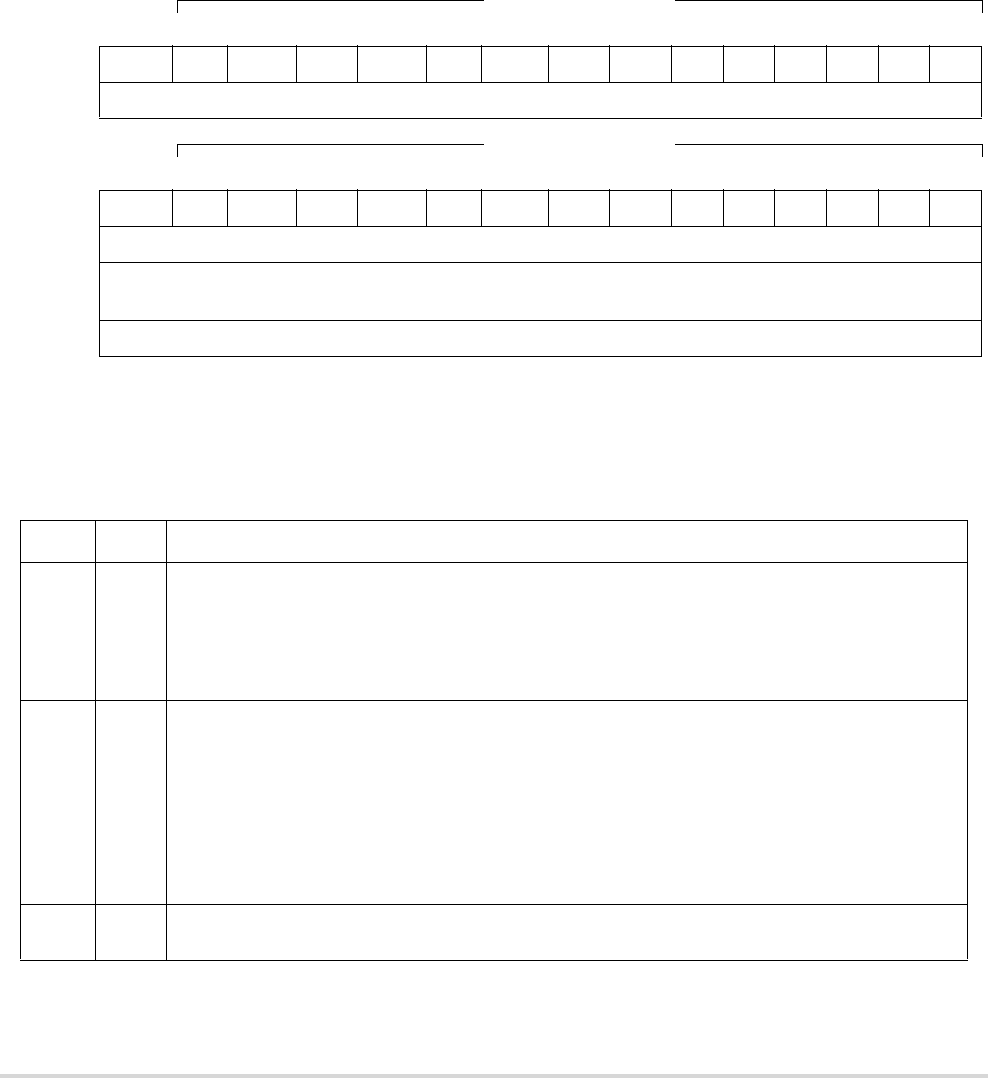

- Figure 29-4. Debug Programming Model

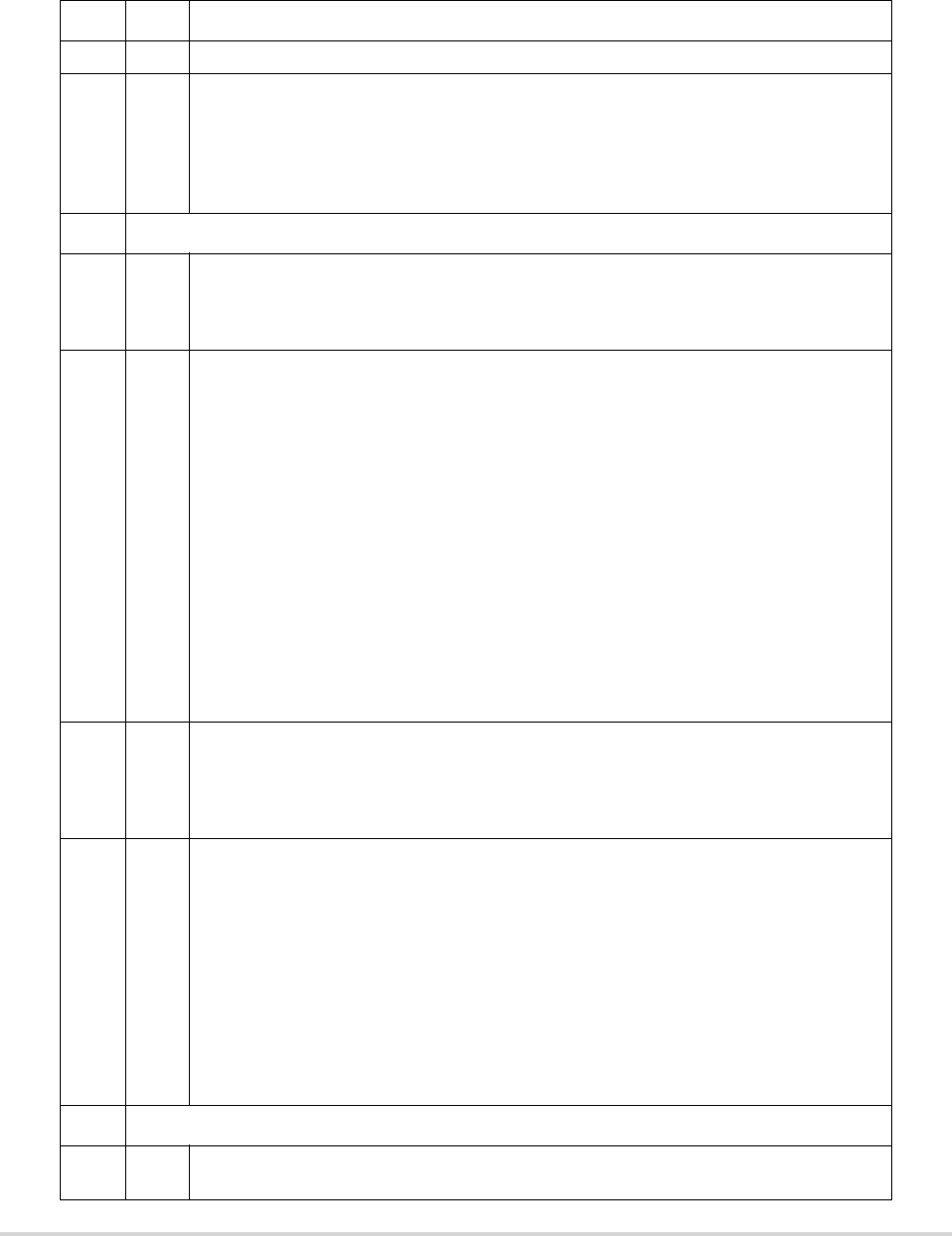

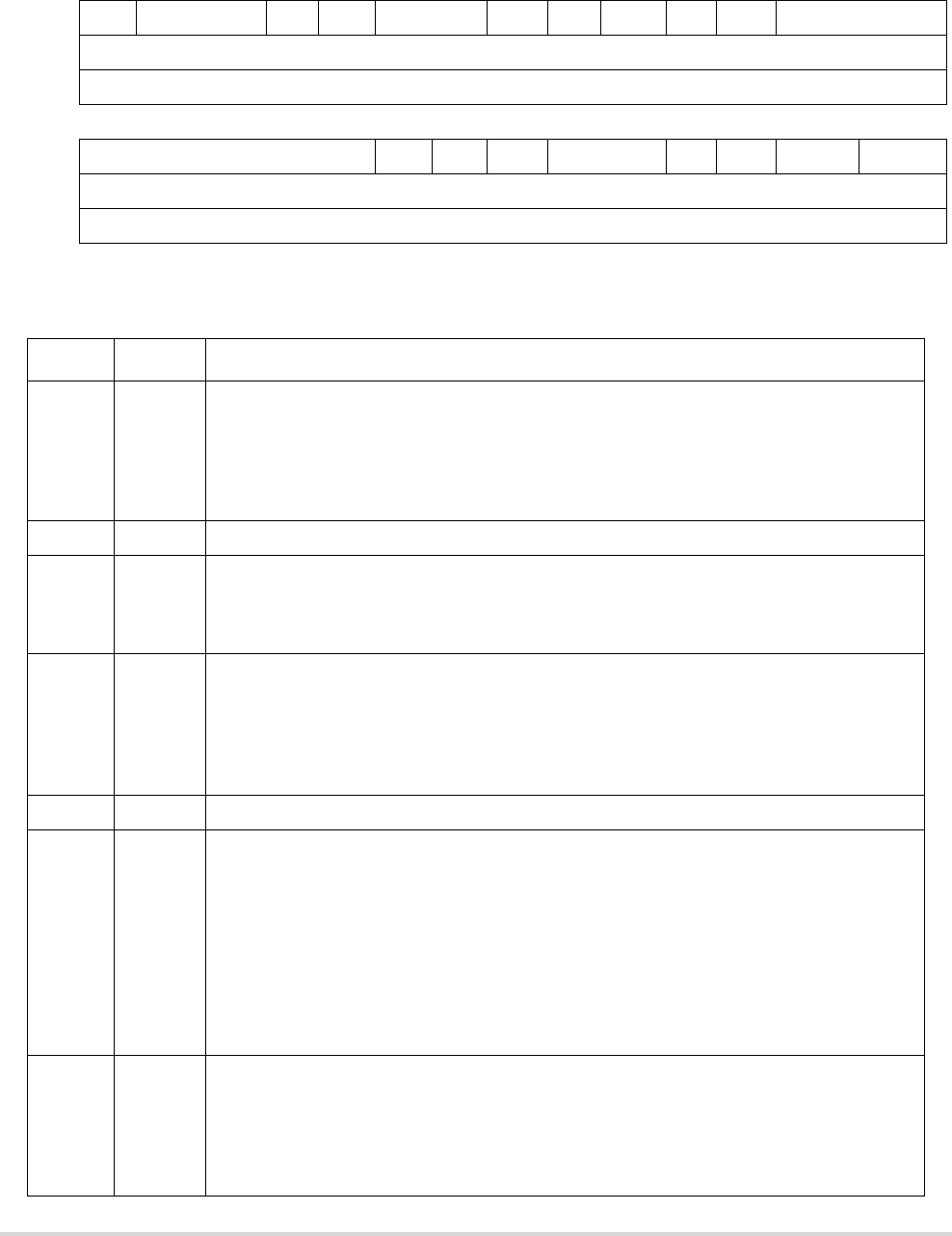

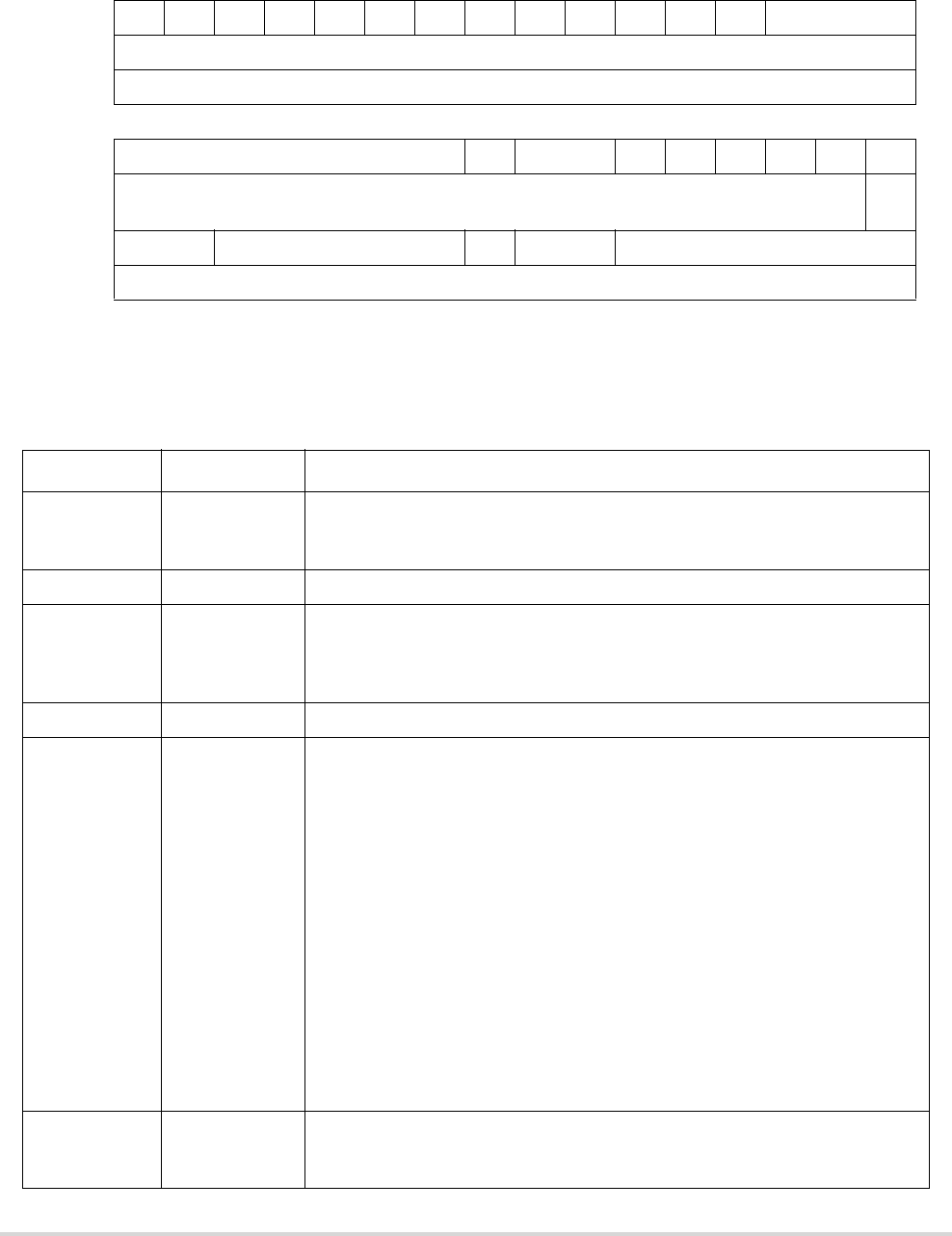

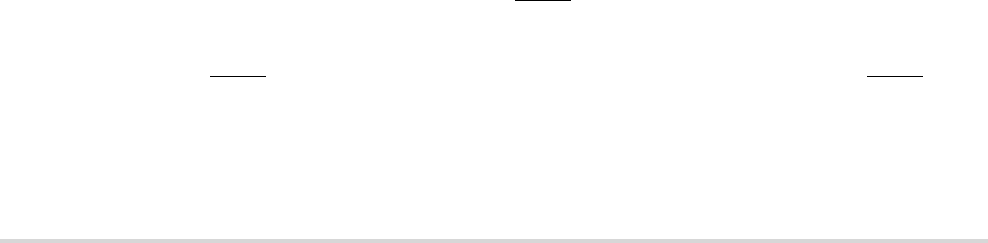

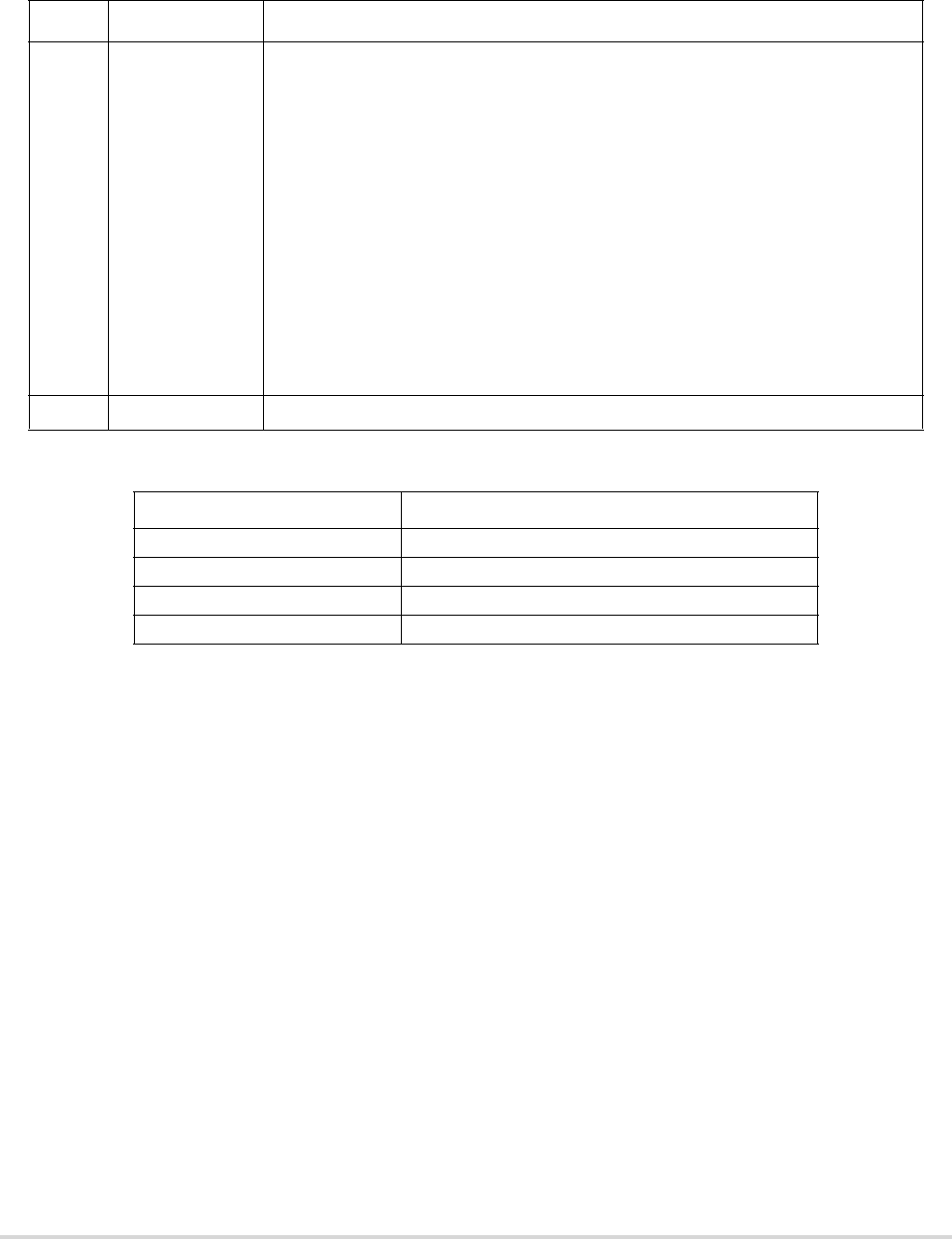

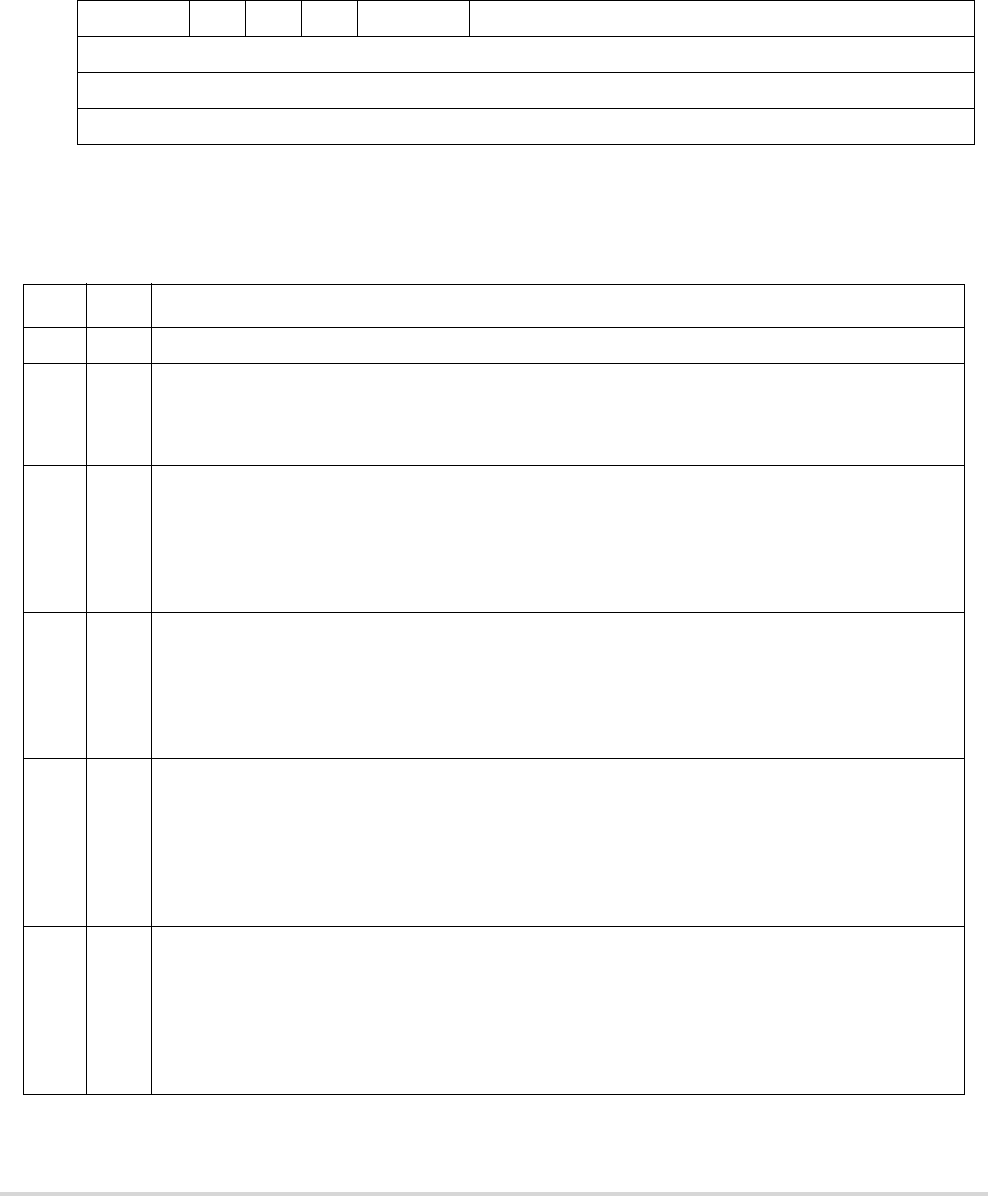

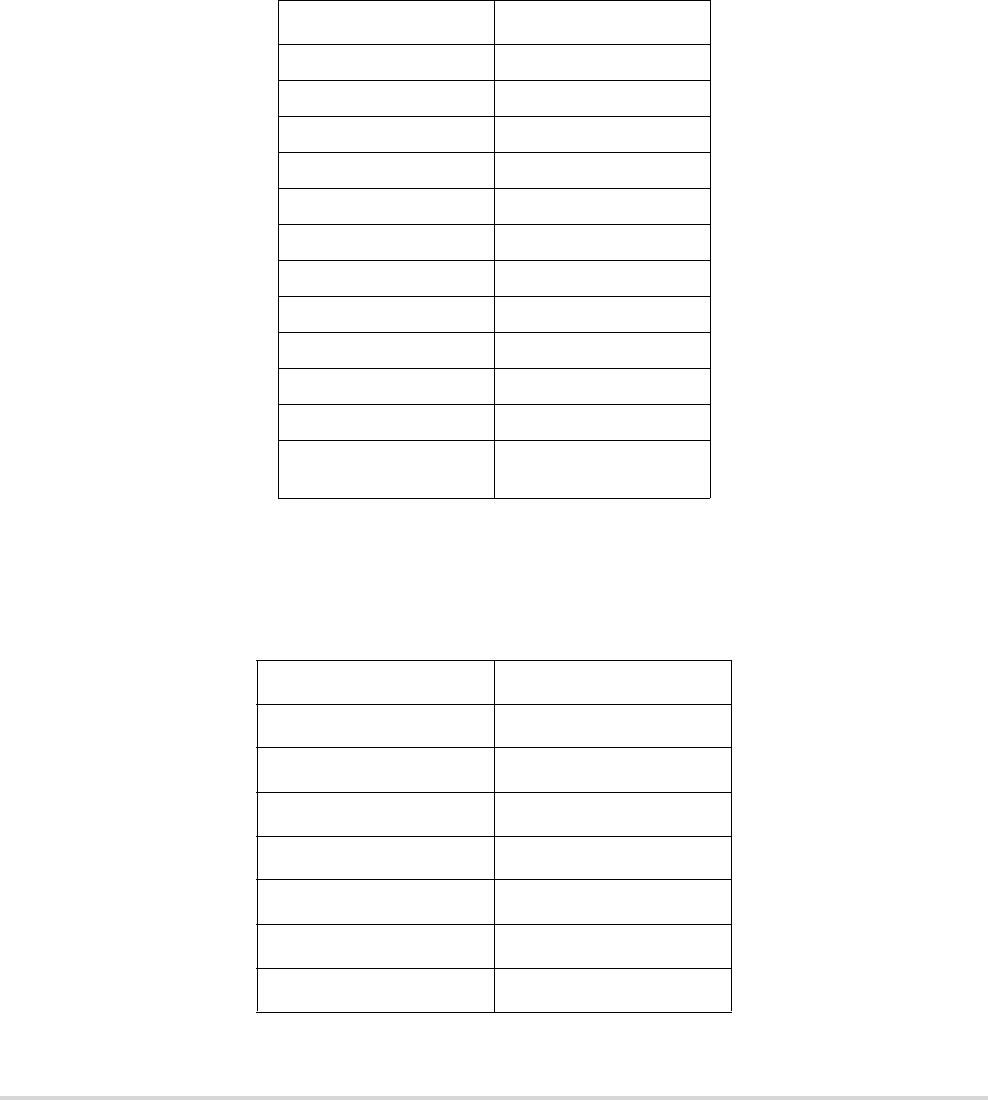

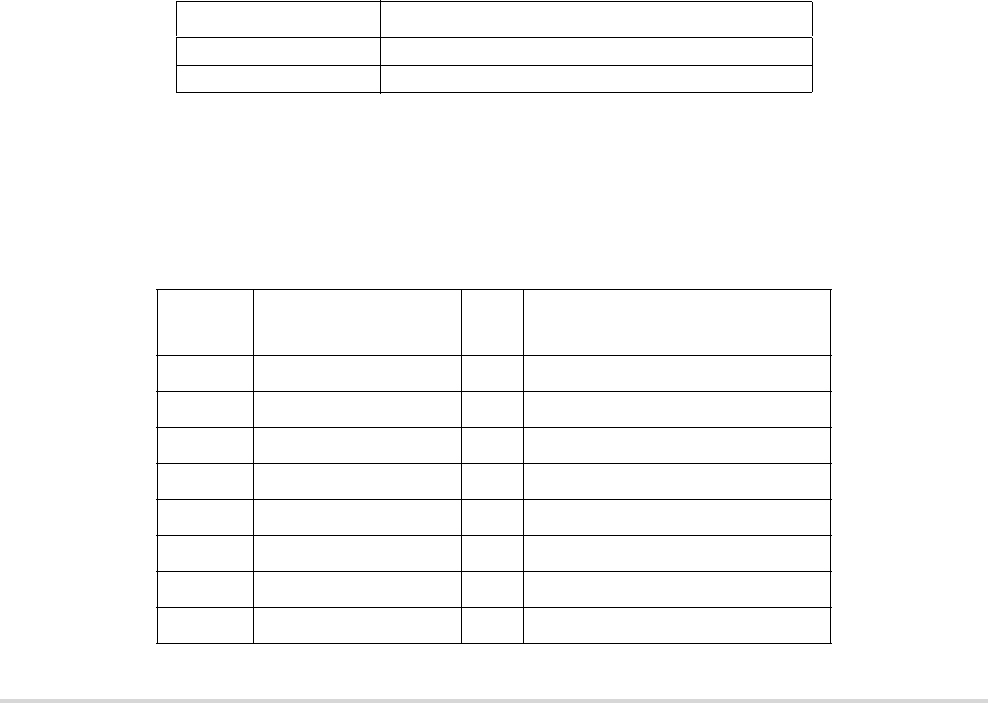

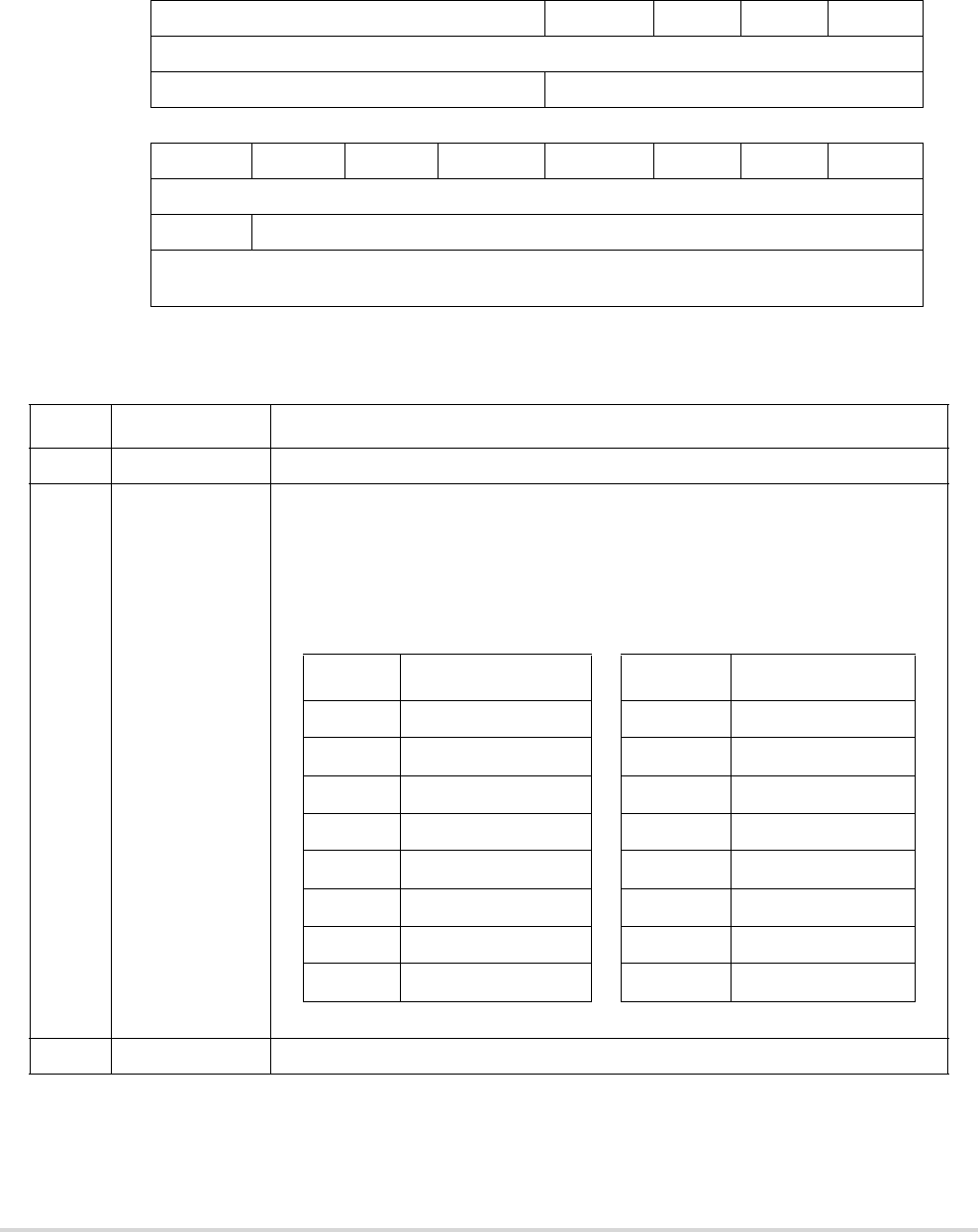

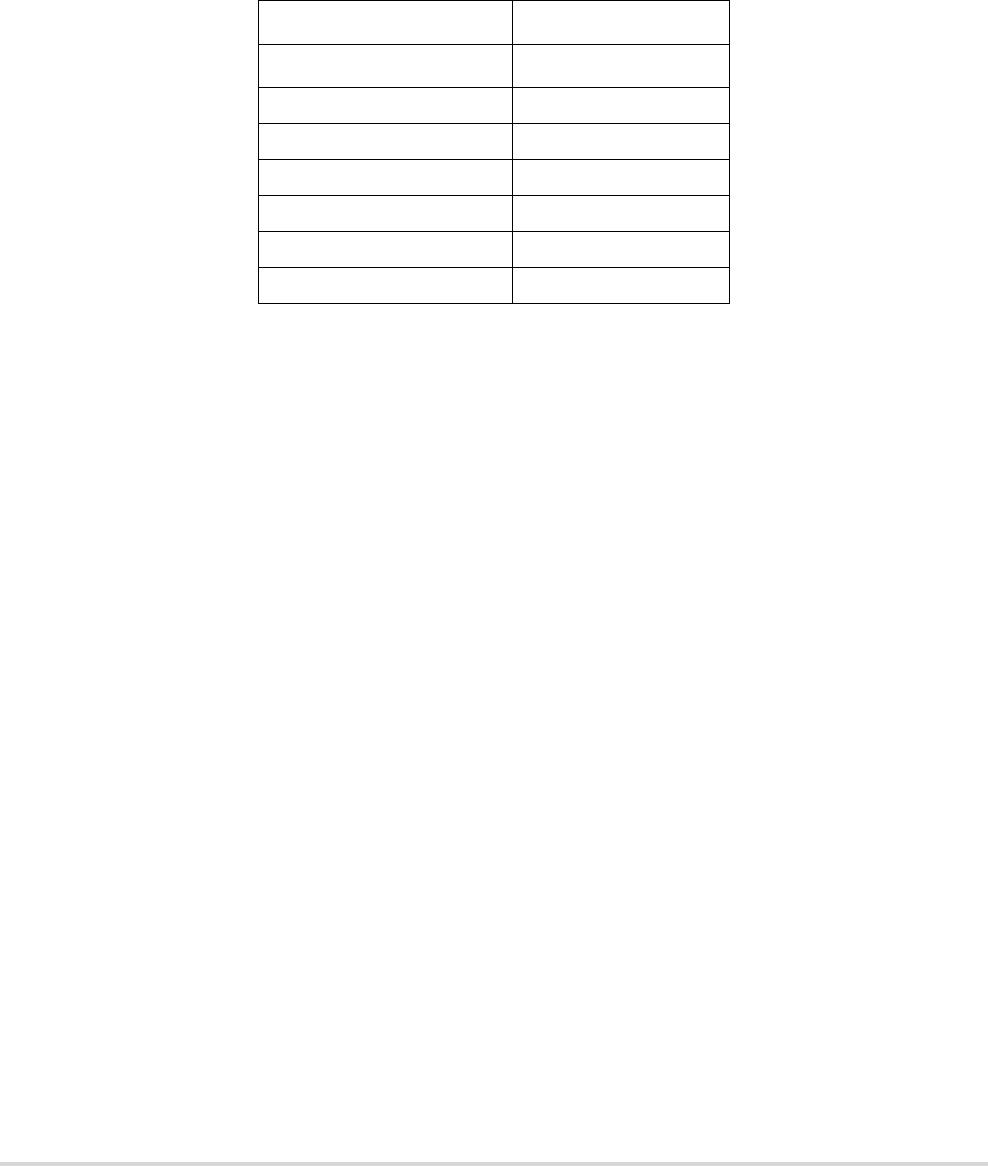

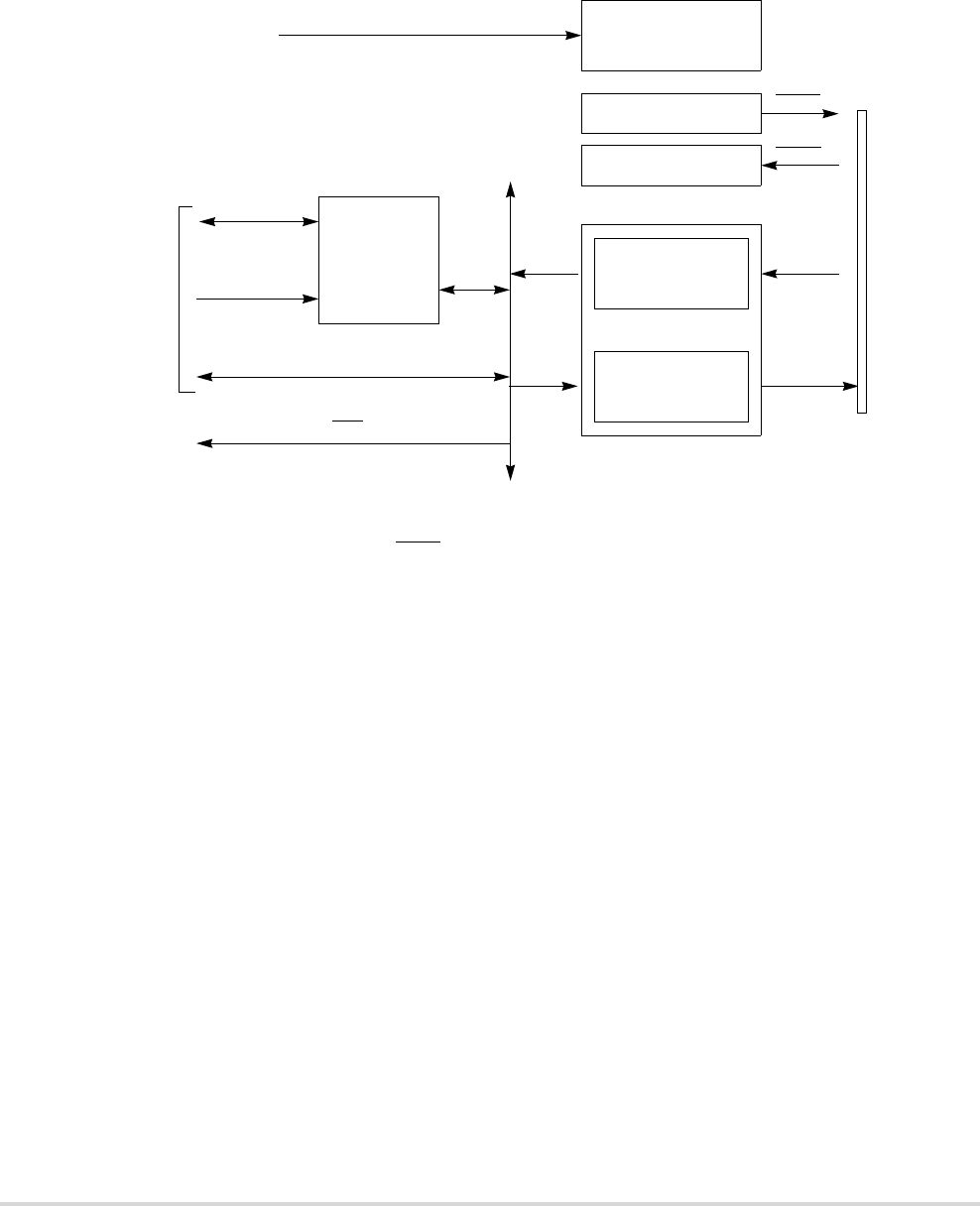

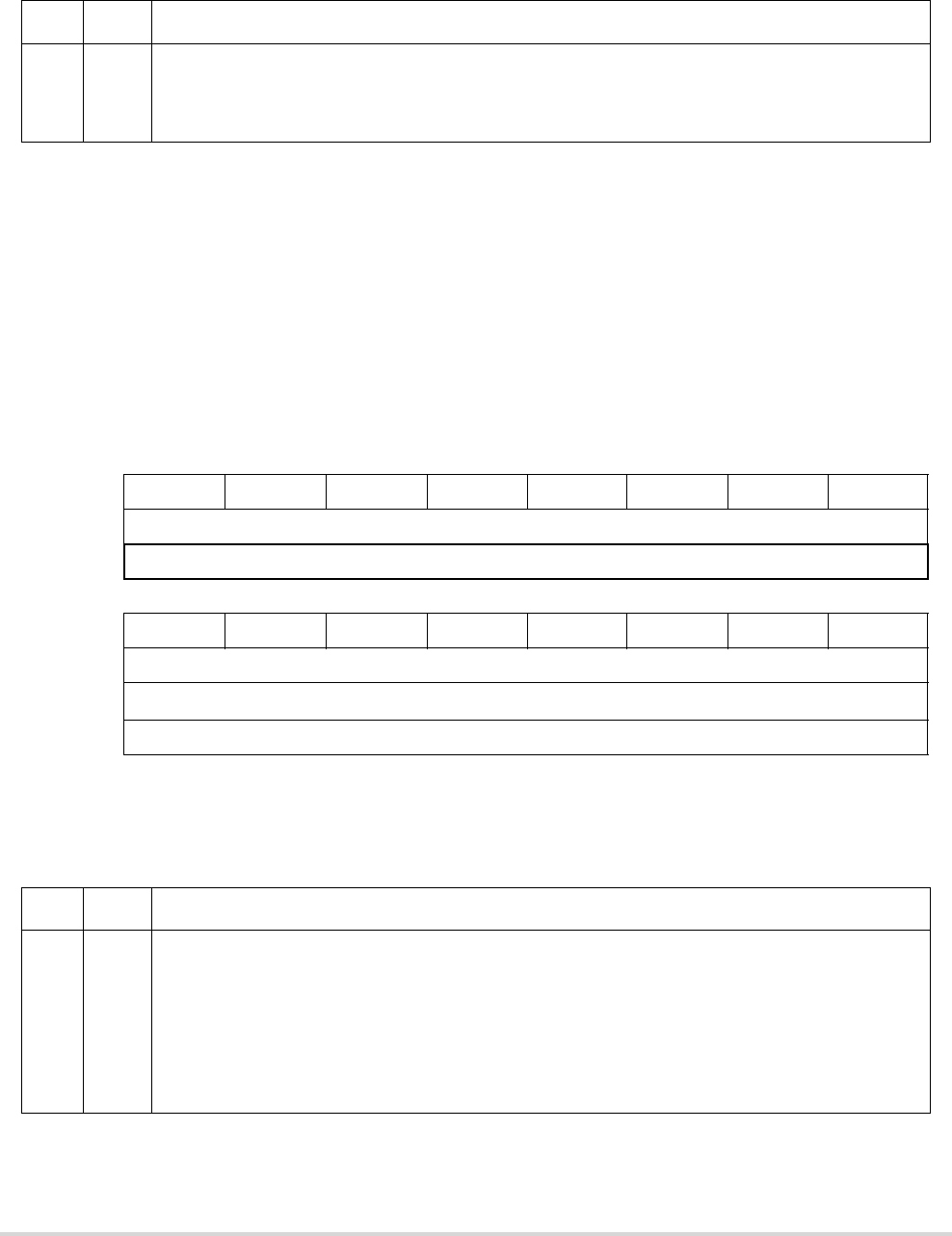

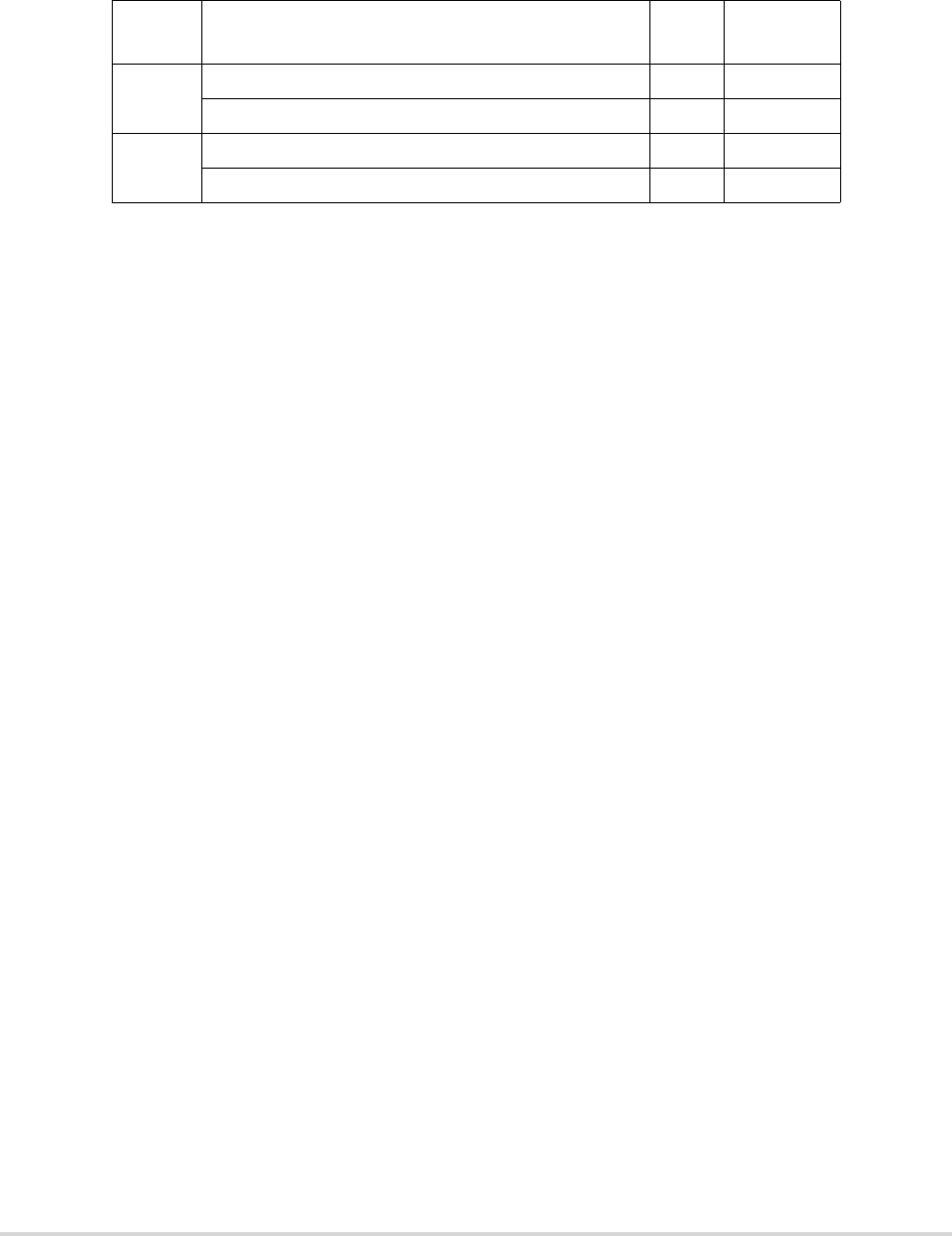

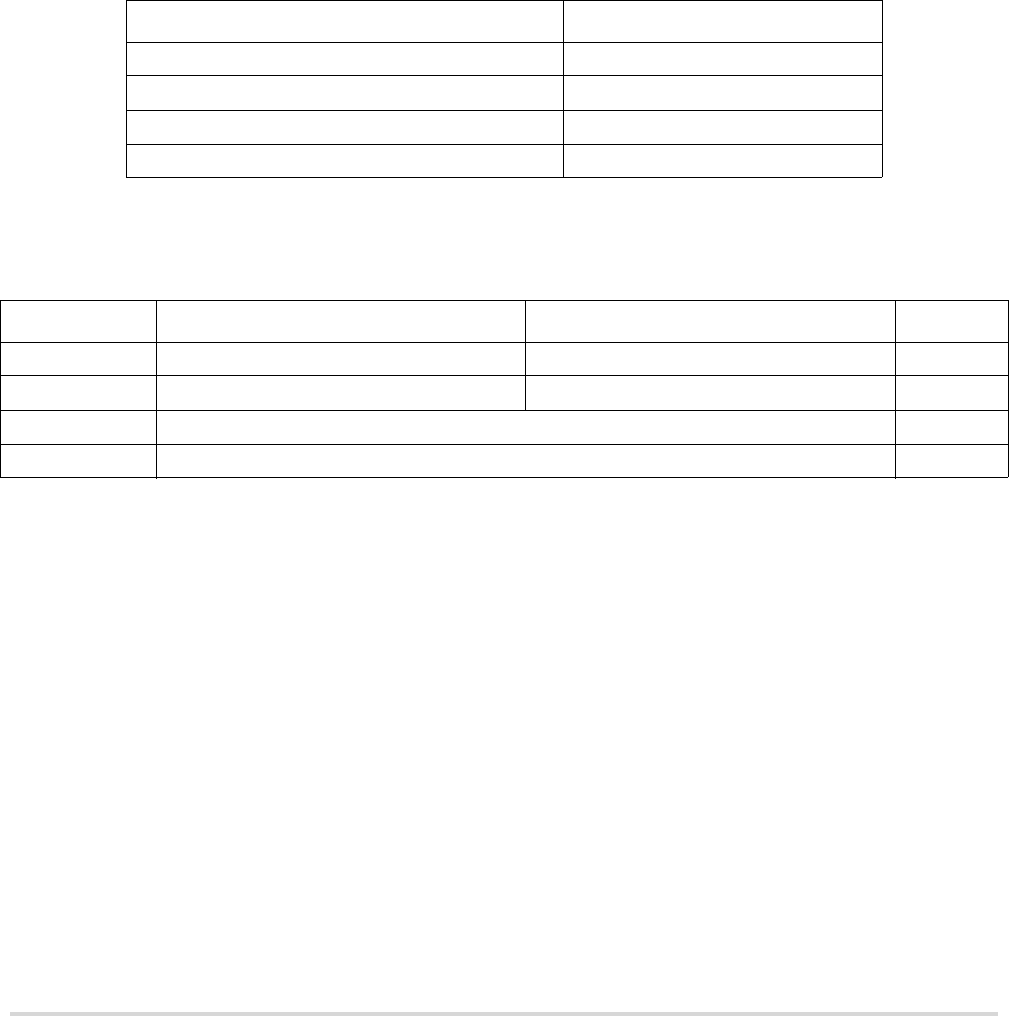

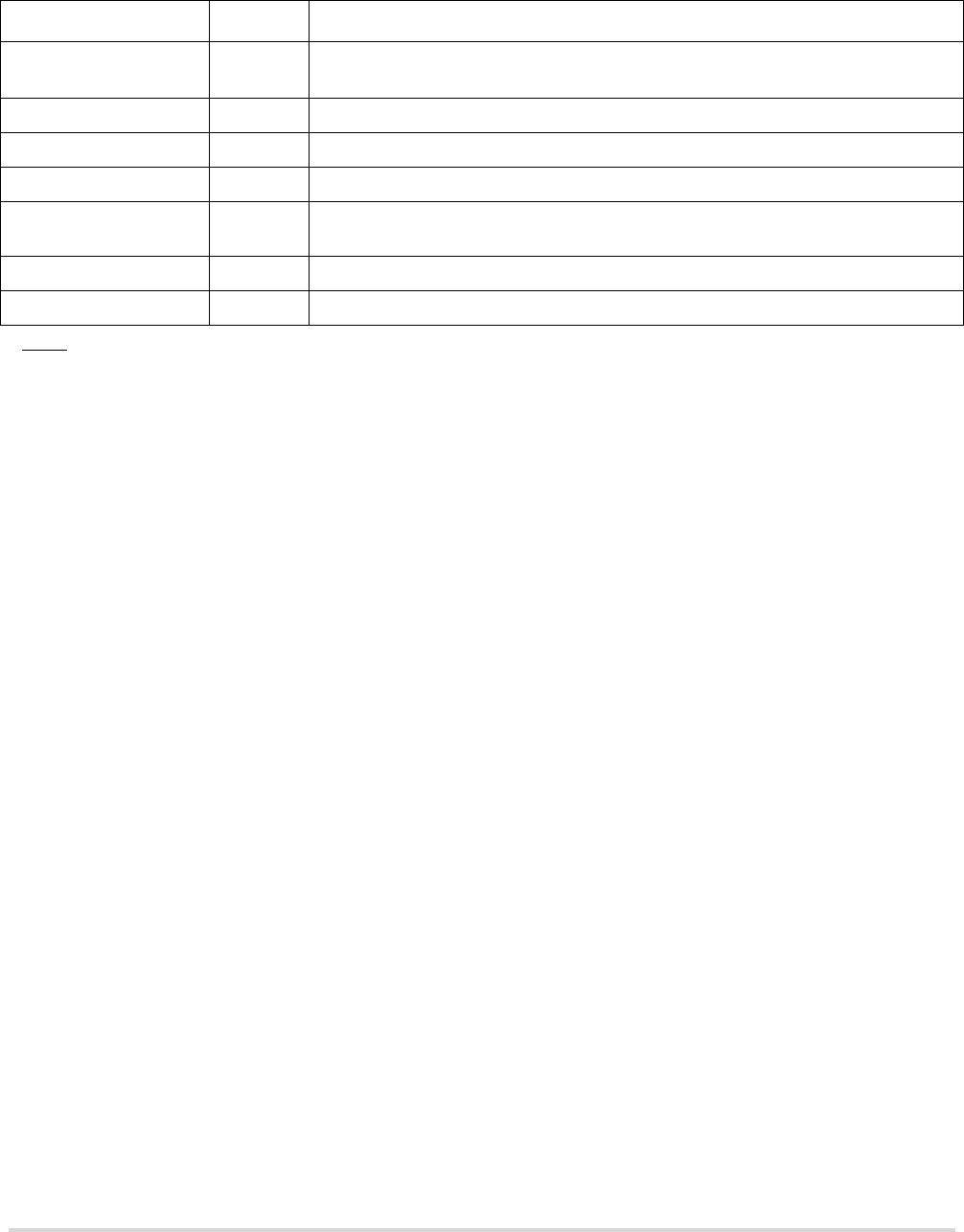

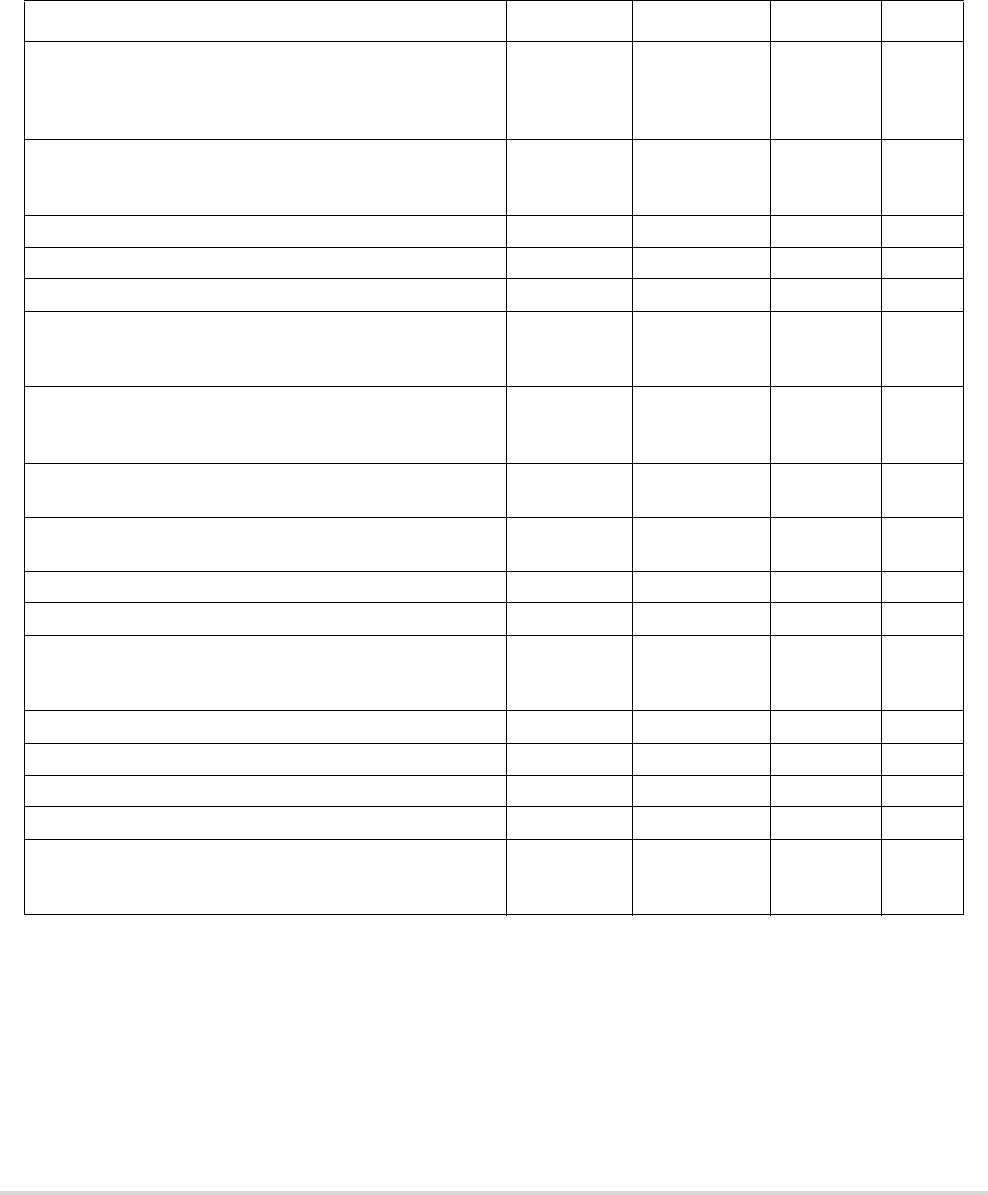

- Table 29-3. BDM/Breakpoint Registers

- 29.4.1 Revision A Shared Debug Resources

- 29.4.2 Address Attribute Trigger Register (AATR)

- 29.4.3 Address Breakpoint Registers (ABLR, ABHR)

- 29.4.4 Configuration/Status Register (CSR)

- 29.4.5 Data Breakpoint/Mask Registers (DBR, DBMR)

- 29.4.6 Program Counter Breakpoint/Mask Registers (PBR, PBMR)

- 29.4.7 Trigger Definition Register (TDR)

- 29.5 Background Debug Mode (BDM)

- 29.5.1 CPU Halt

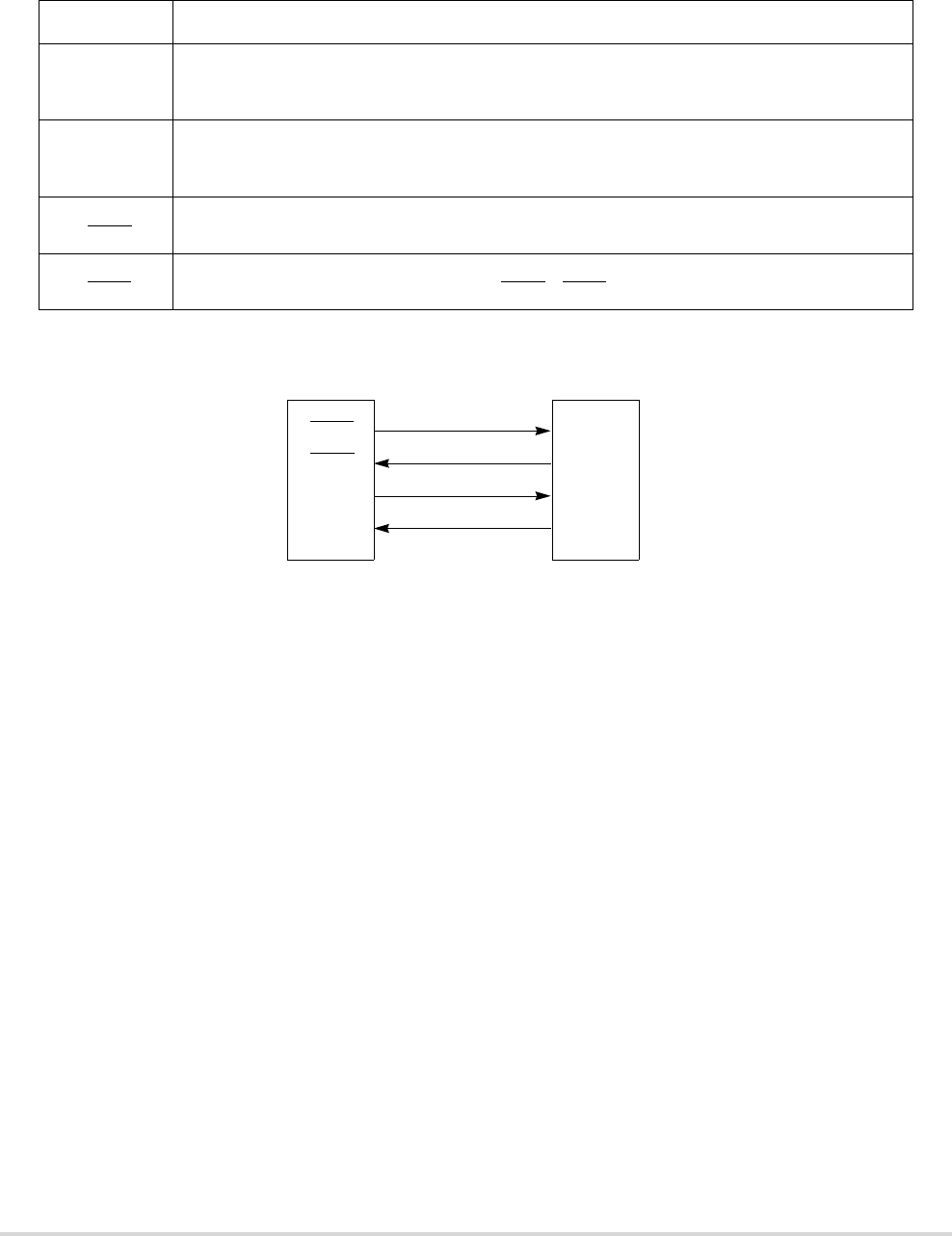

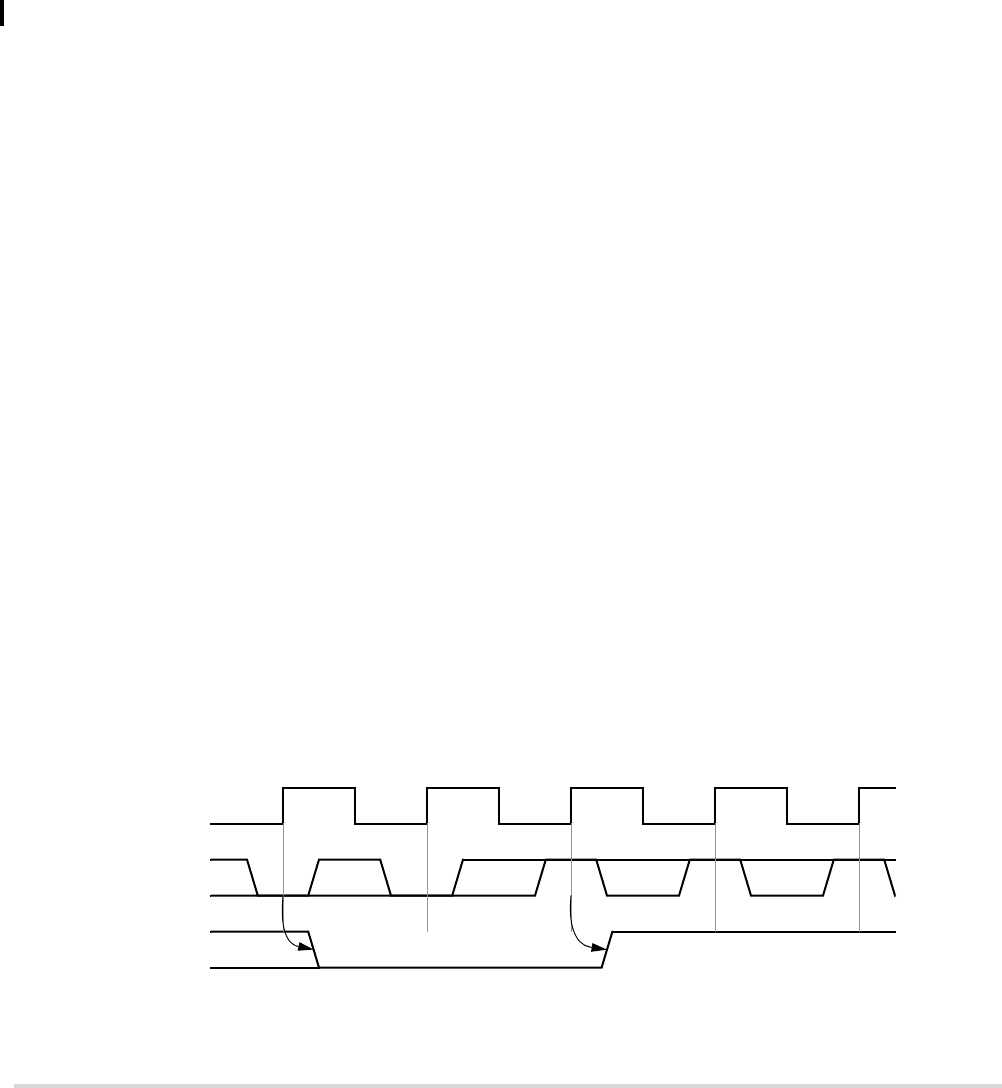

- 29.5.2 BDM Serial Interface

- 29.5.3 BDM Command Set

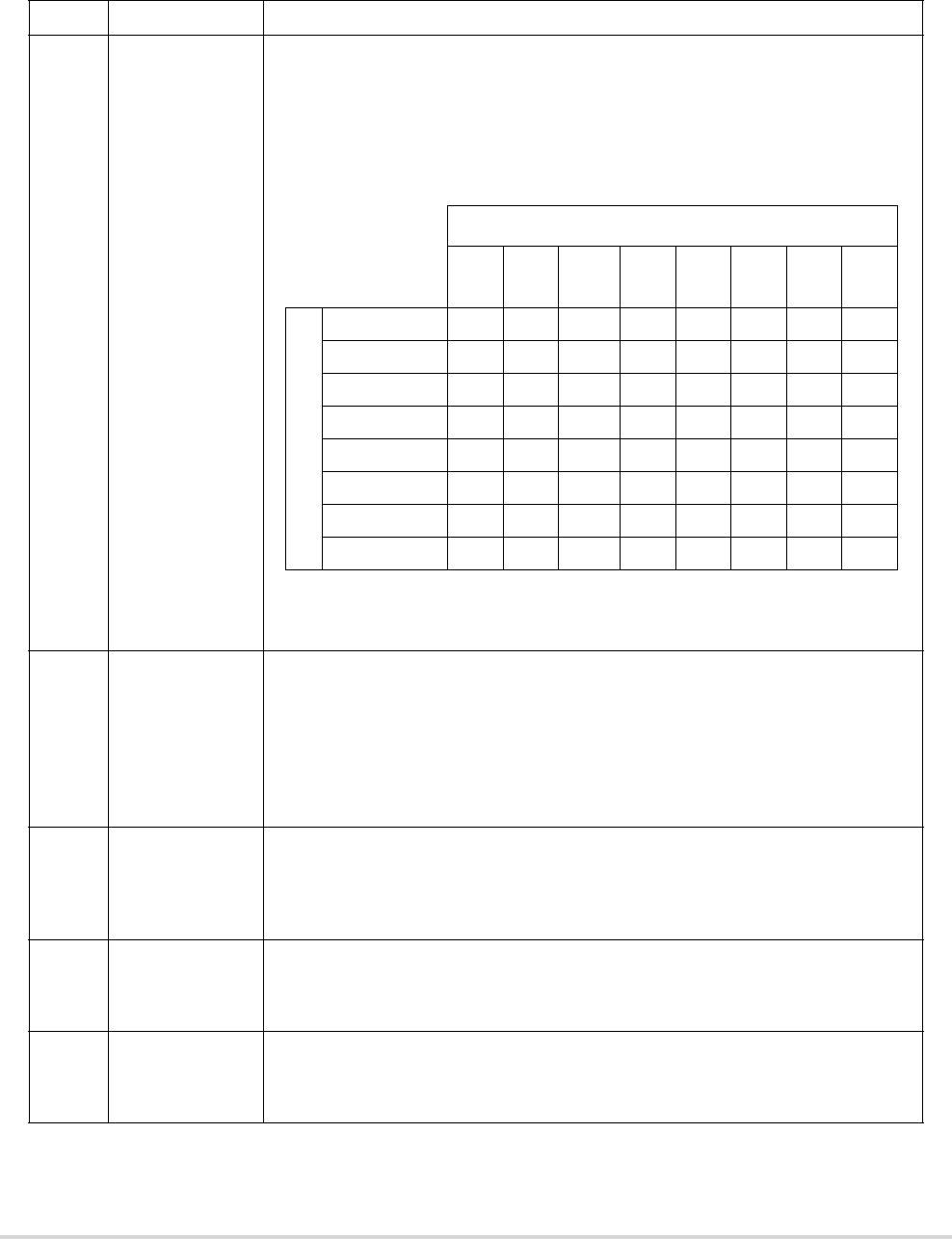

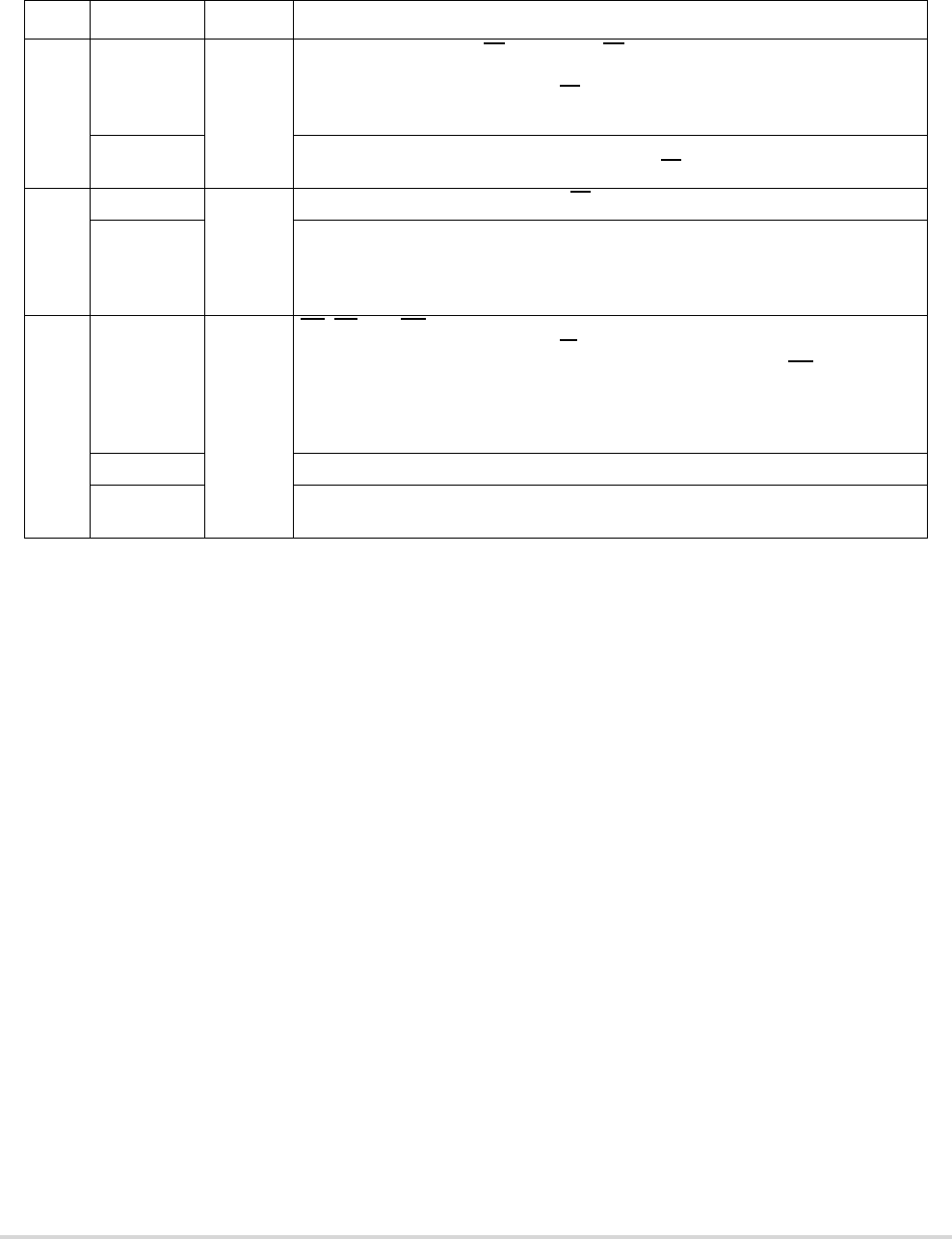

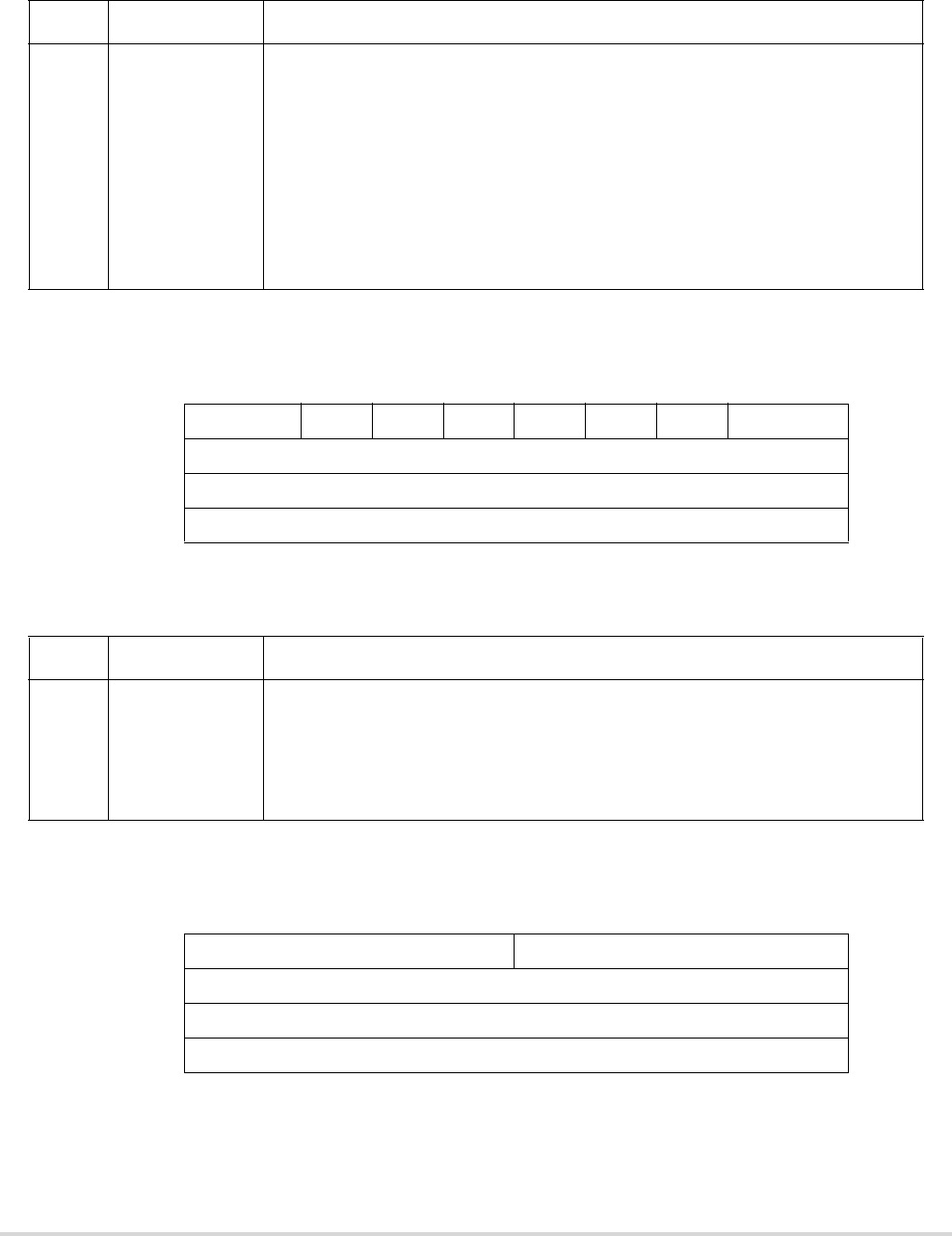

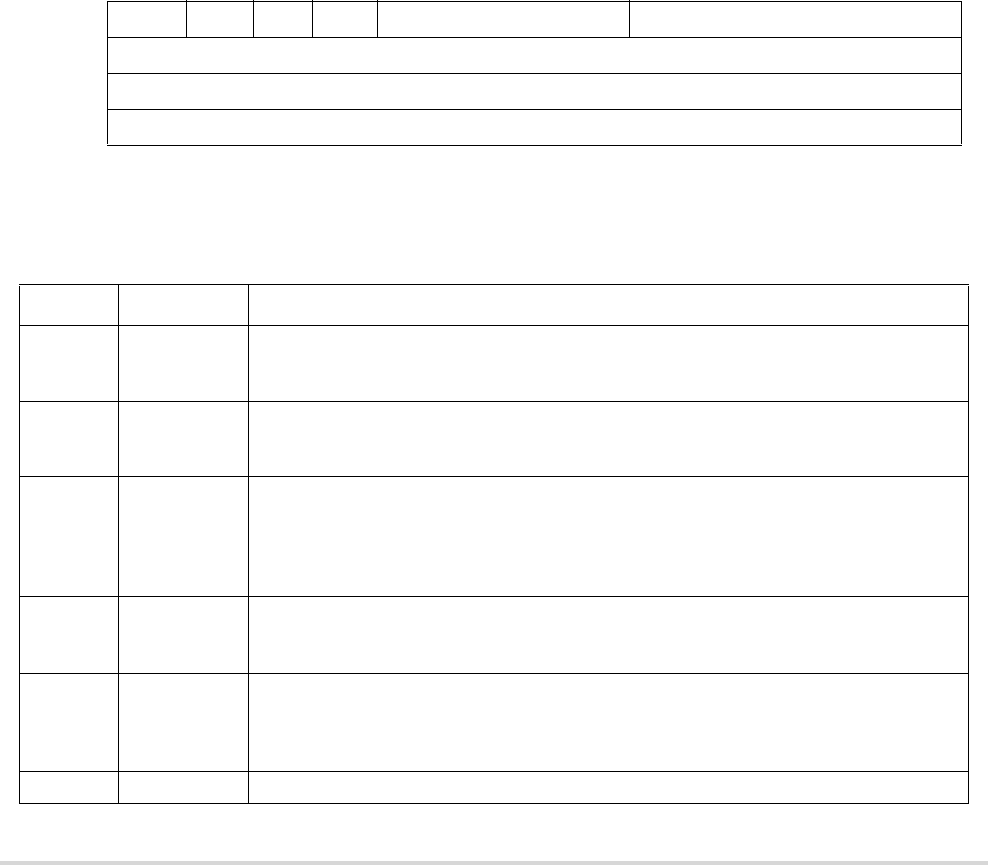

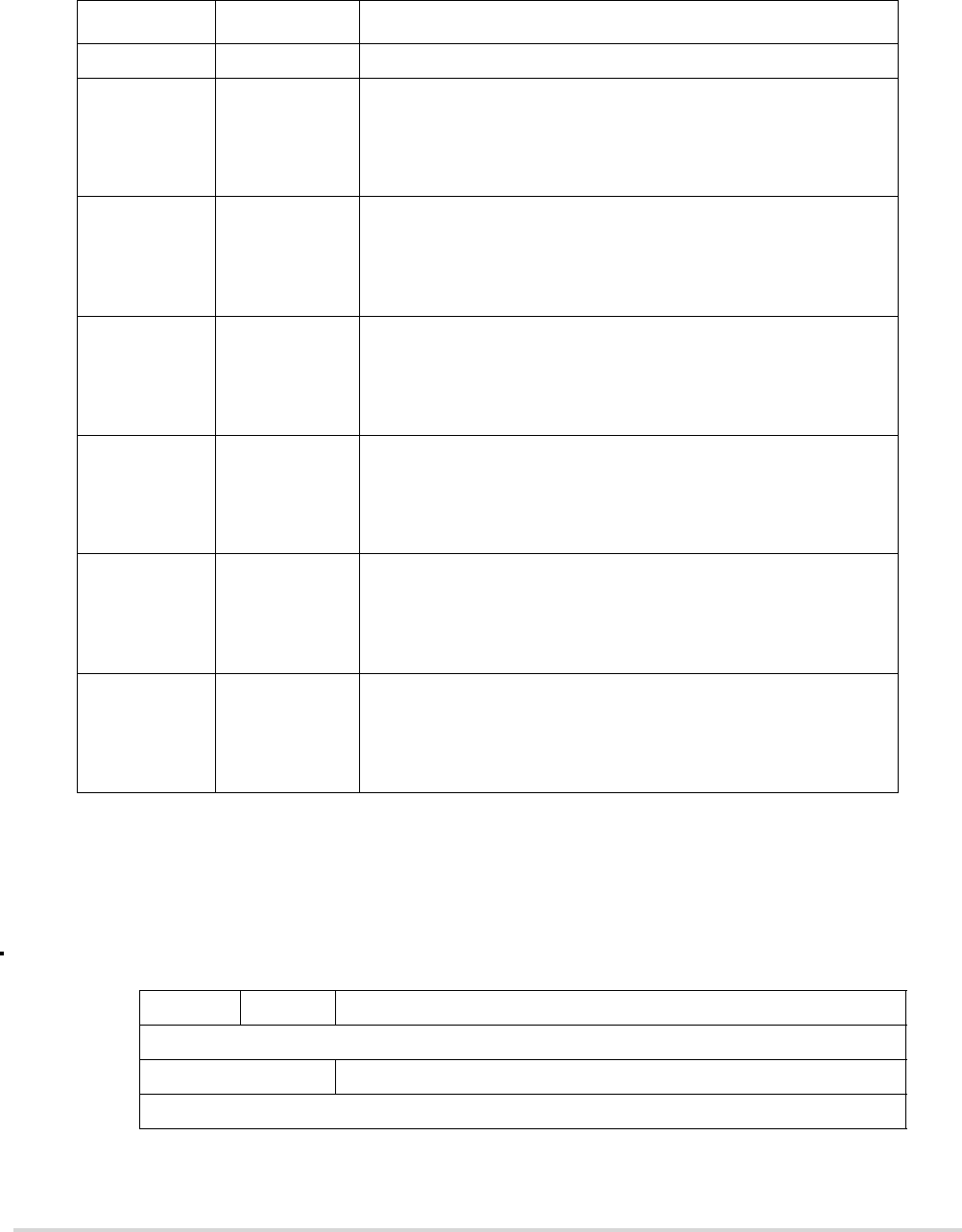

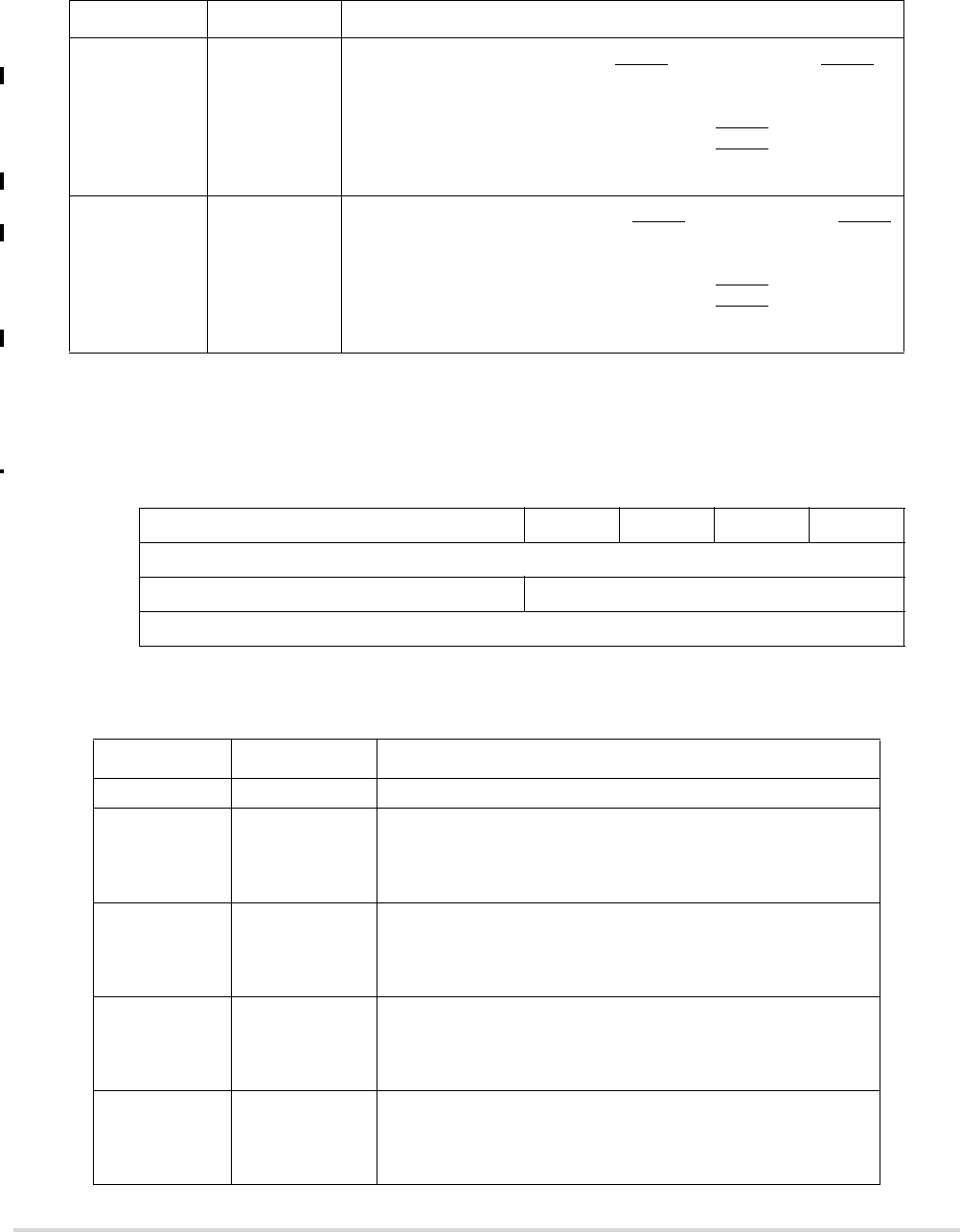

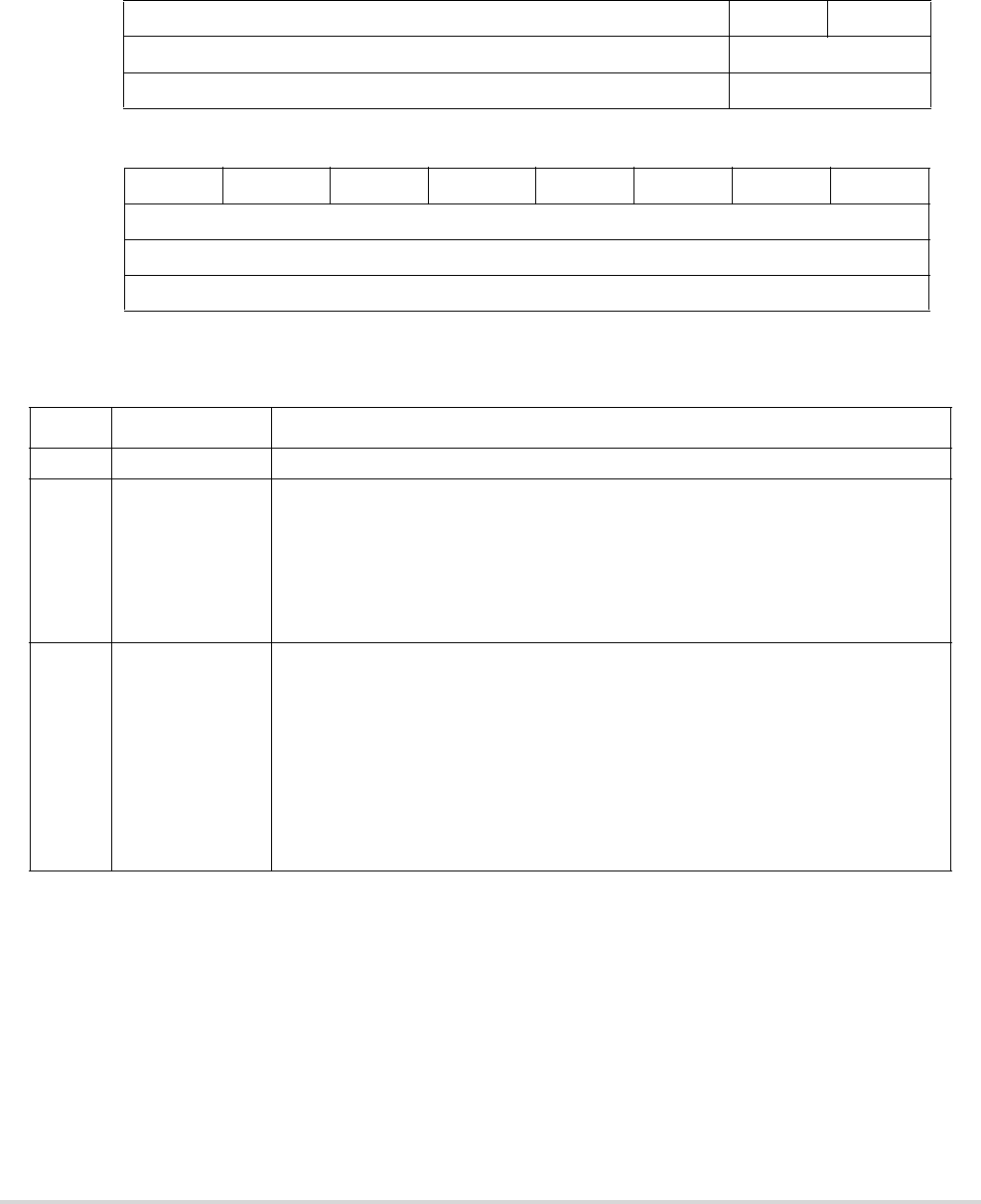

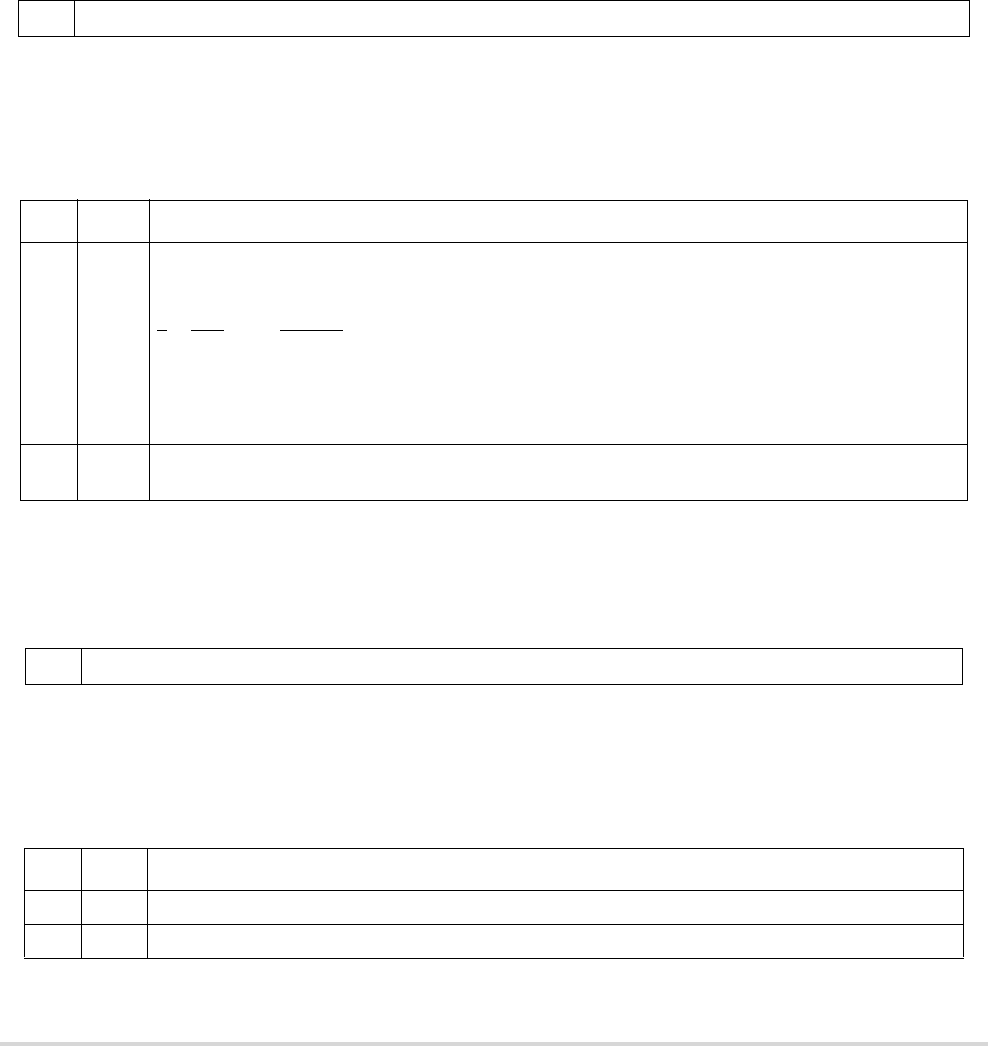

- Table 29-17. BDM Command Summary

- 29.5.3.1 ColdFire BDM Command Format

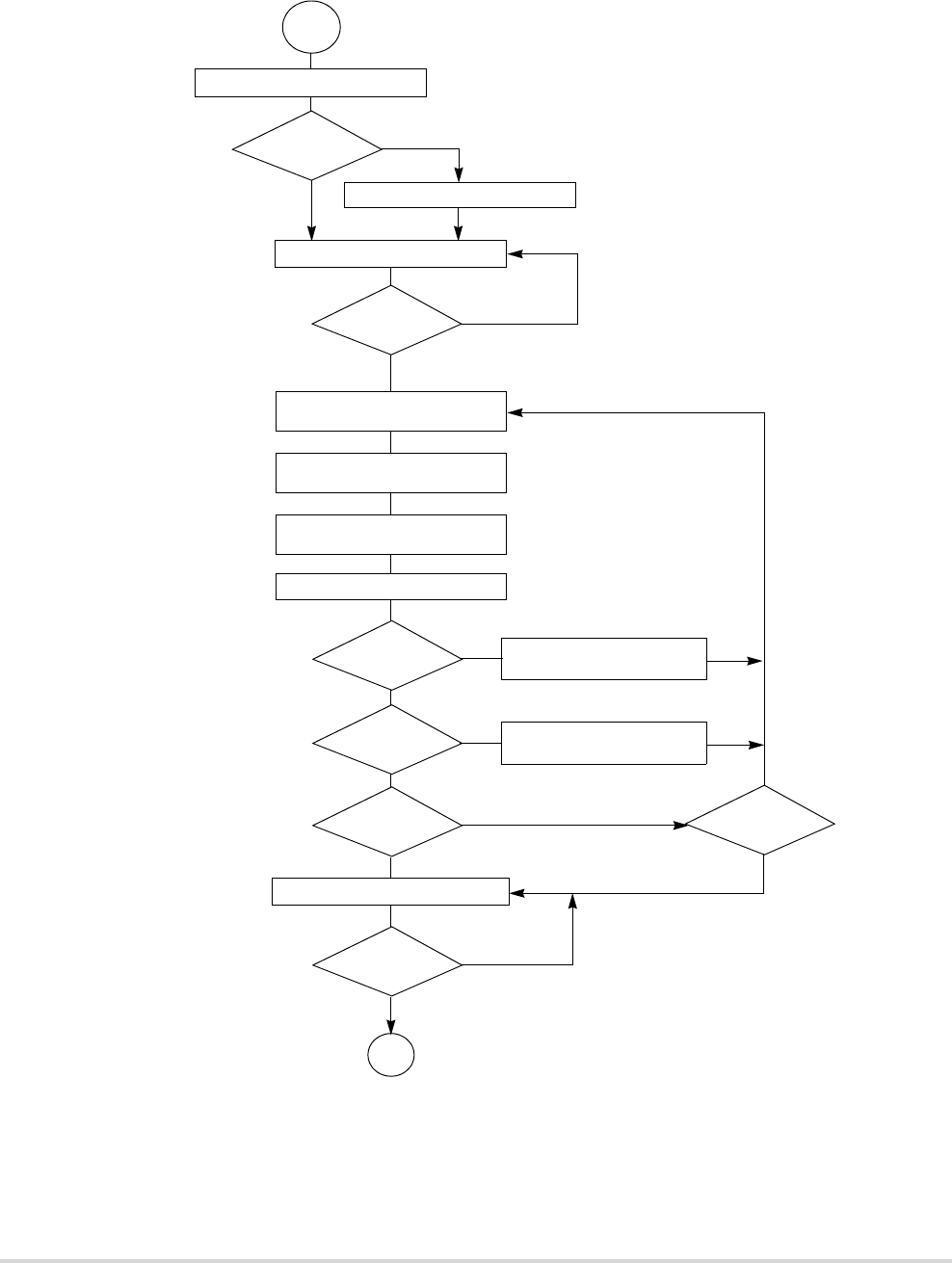

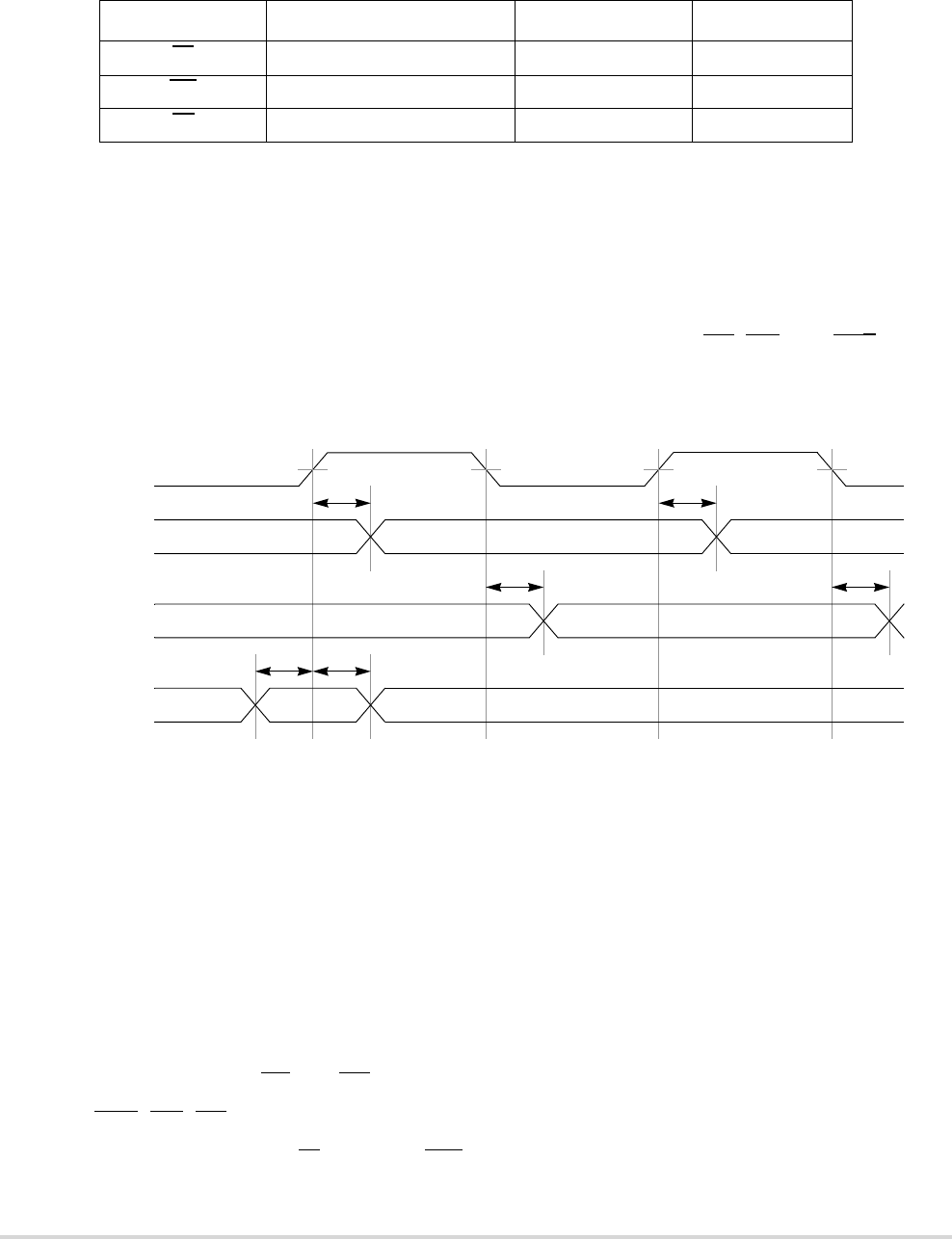

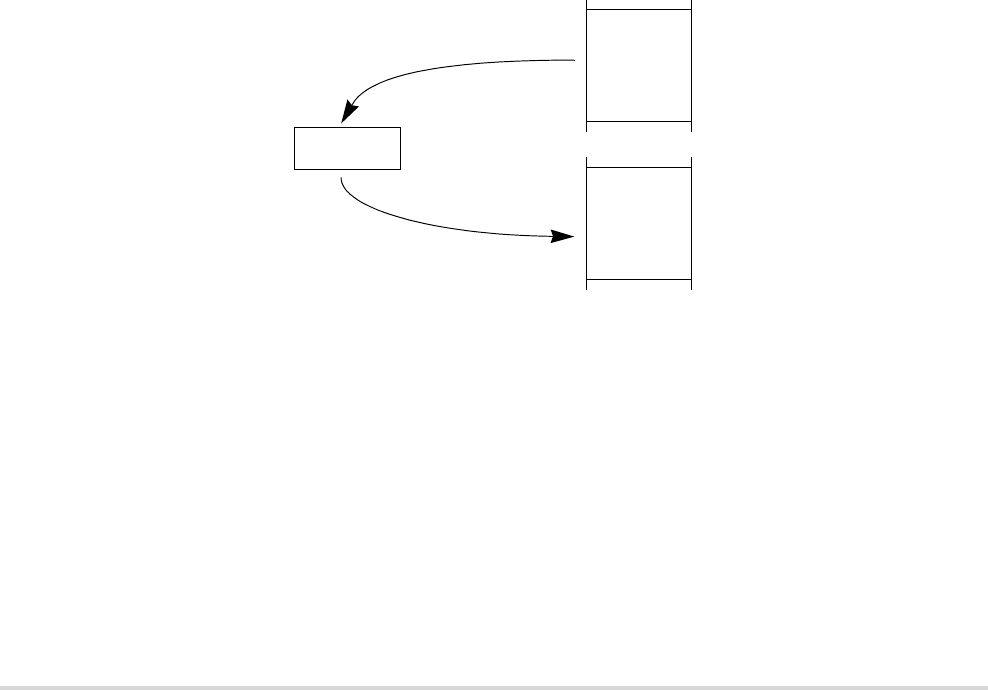

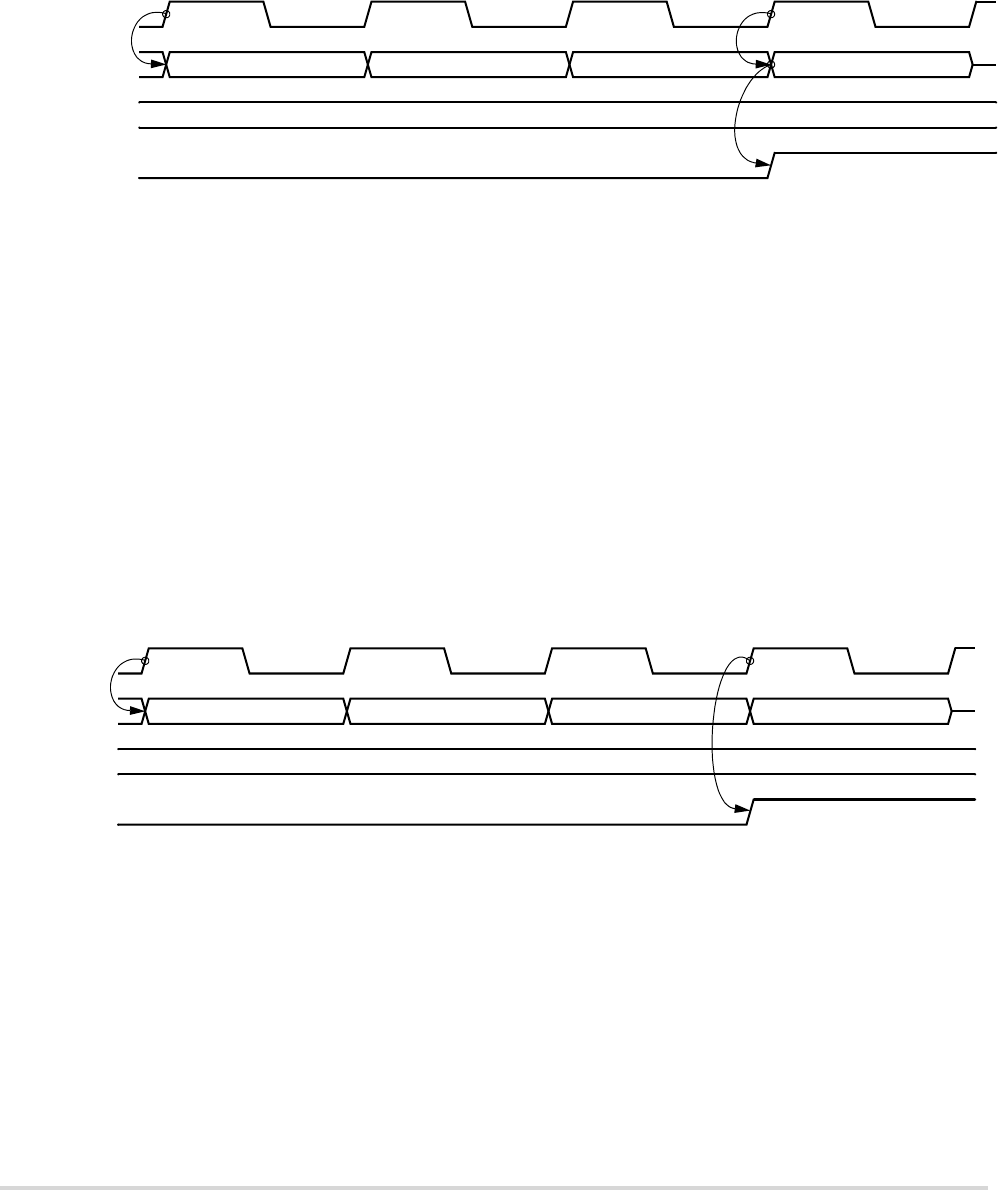

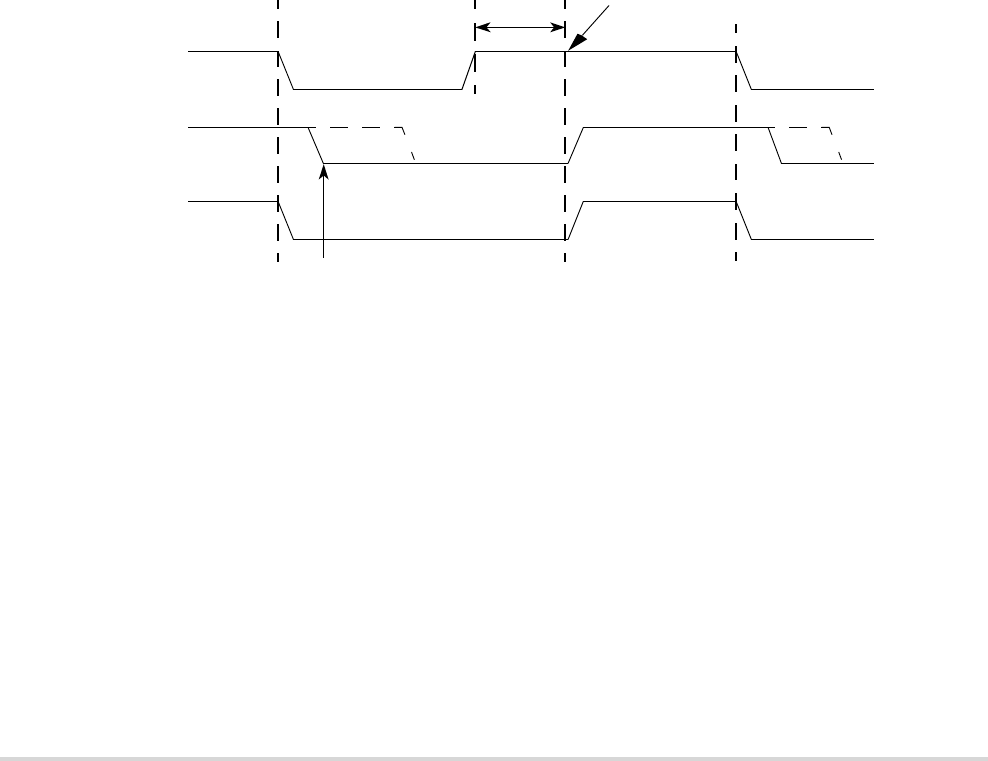

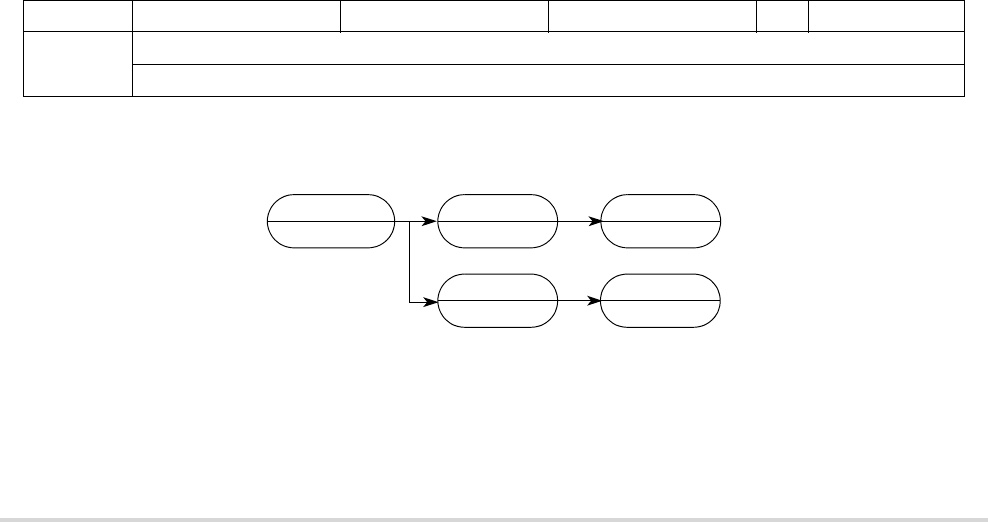

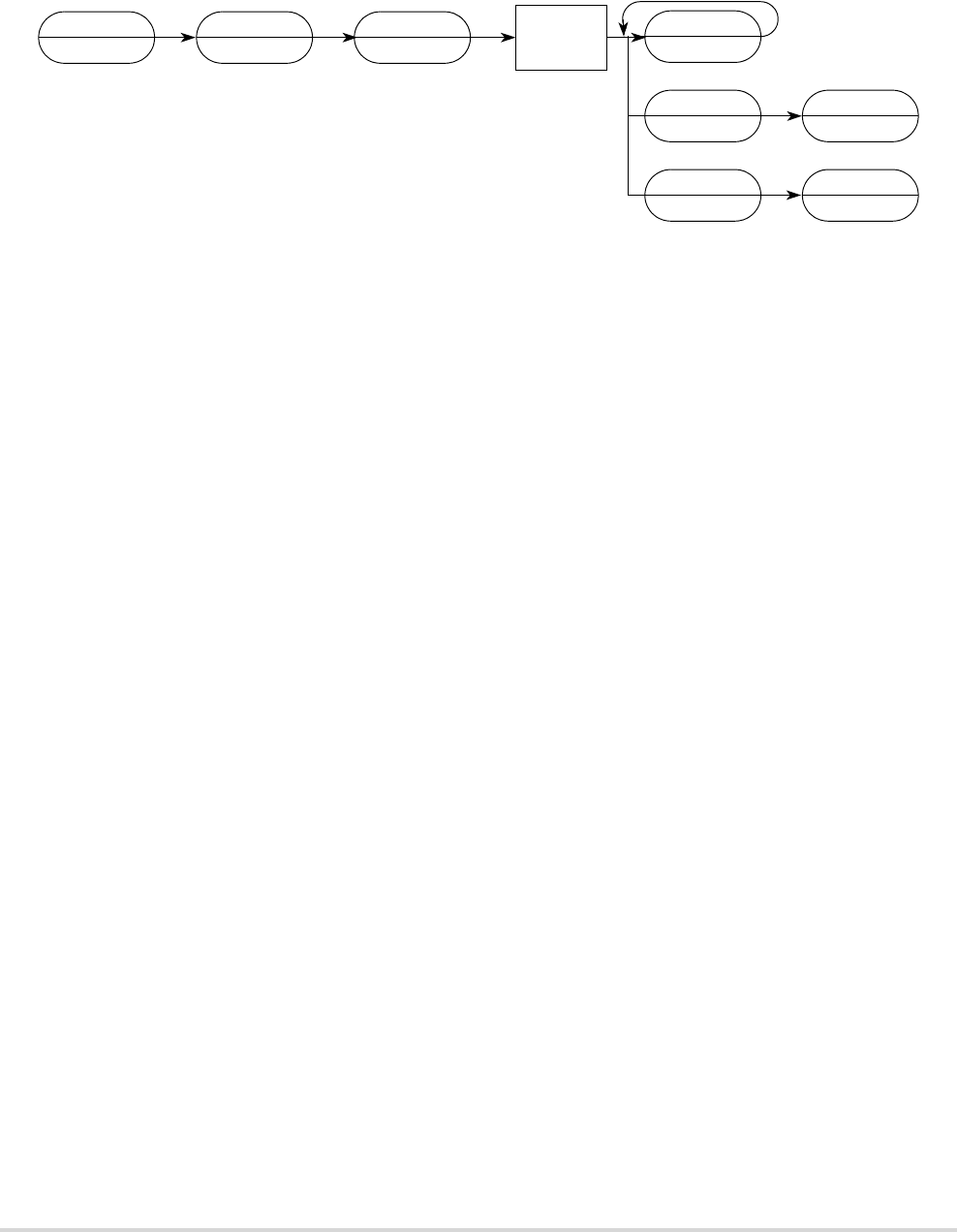

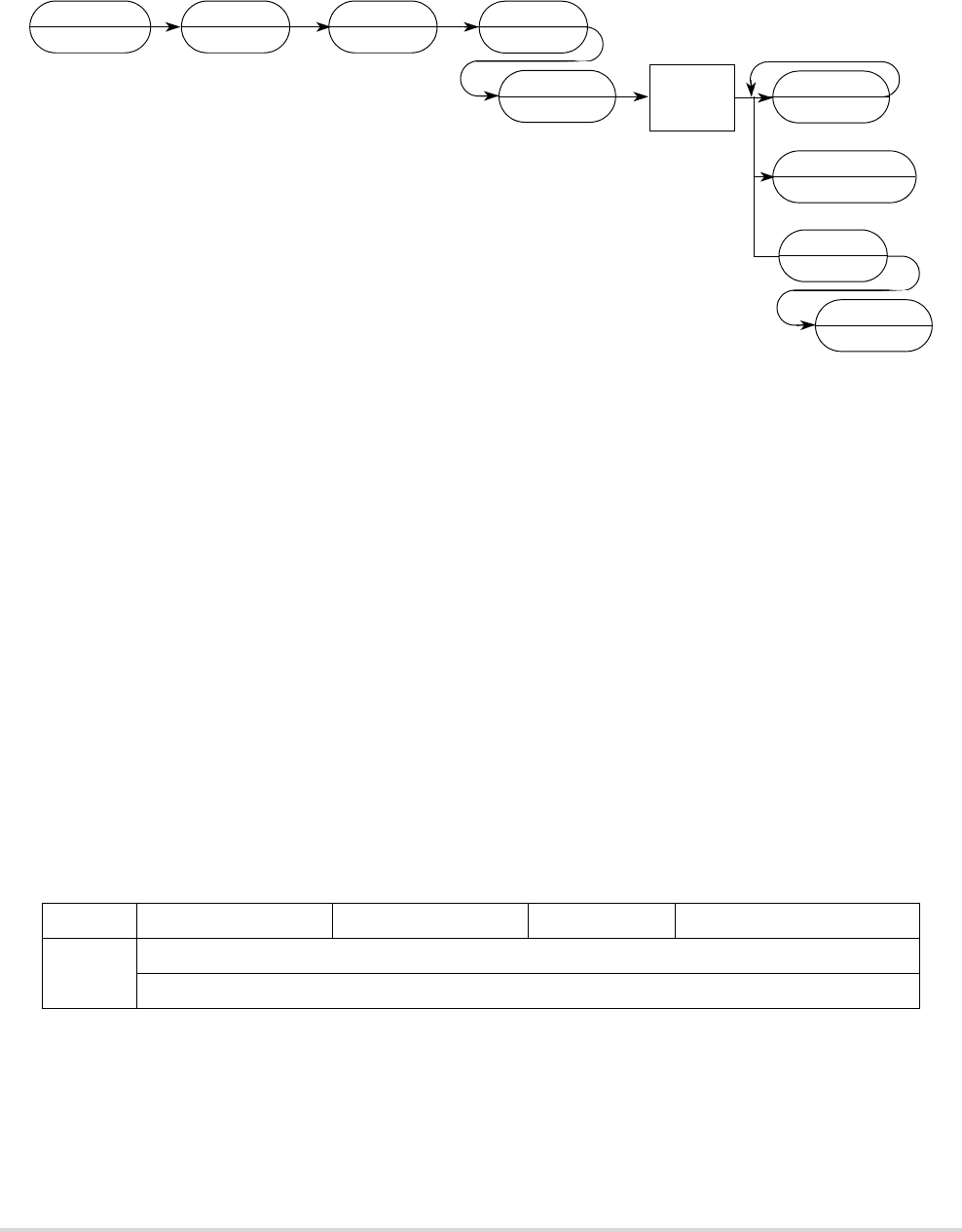

- 29.5.3.2 Command Sequence Diagrams

- 29.5.3.3 Command Set Descriptions

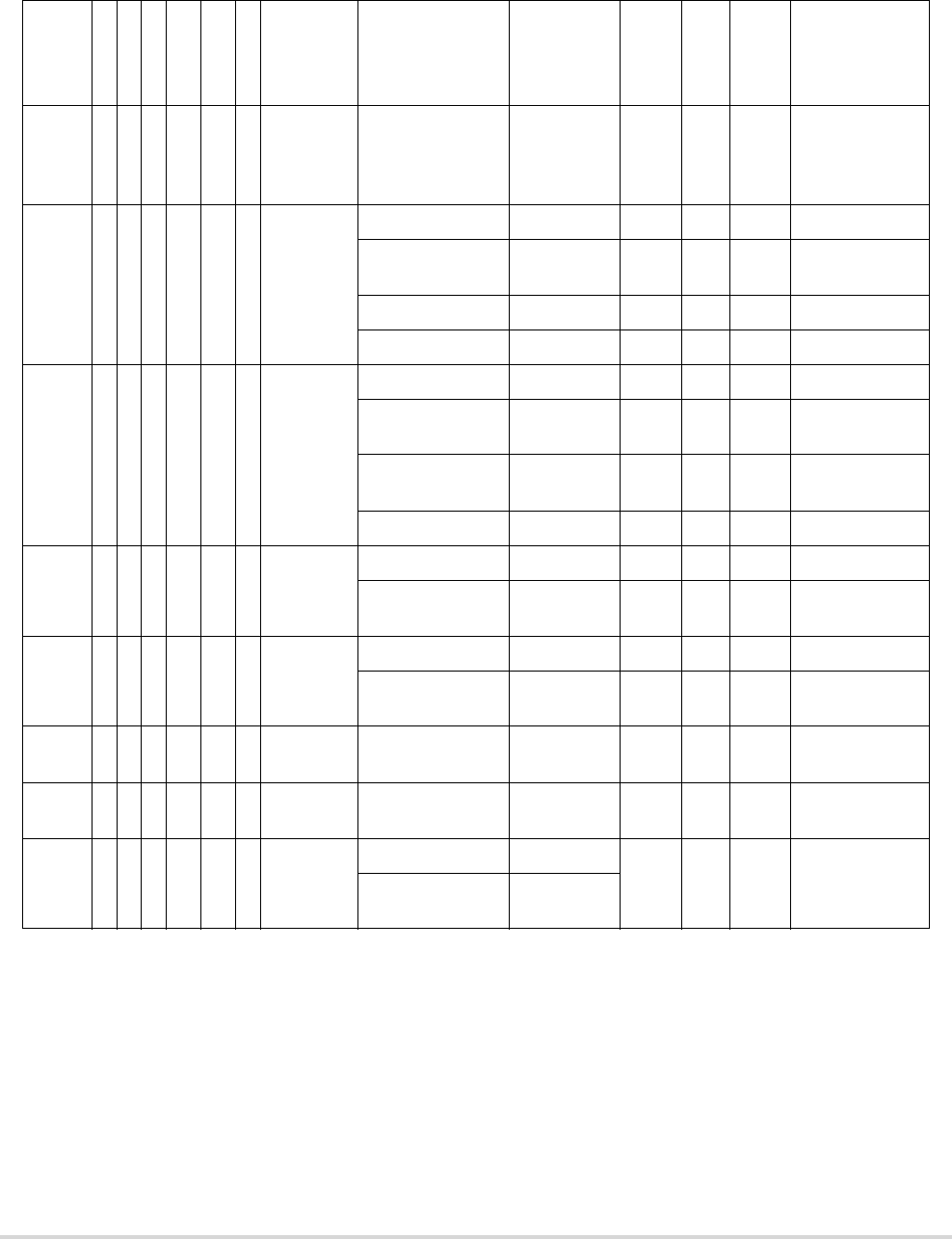

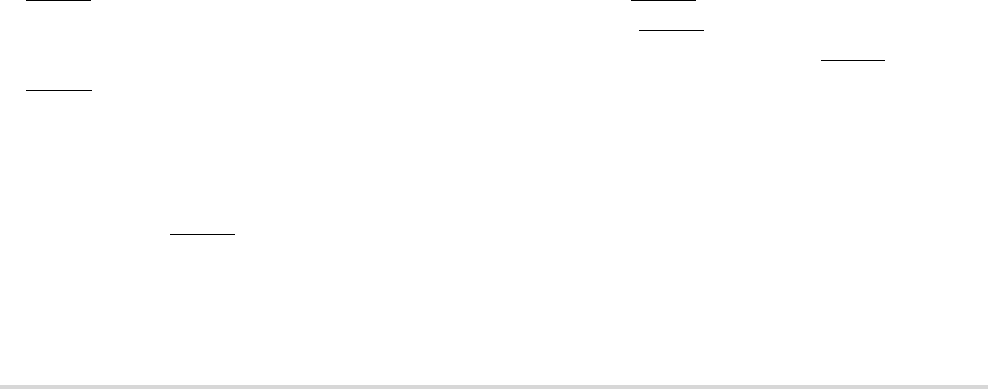

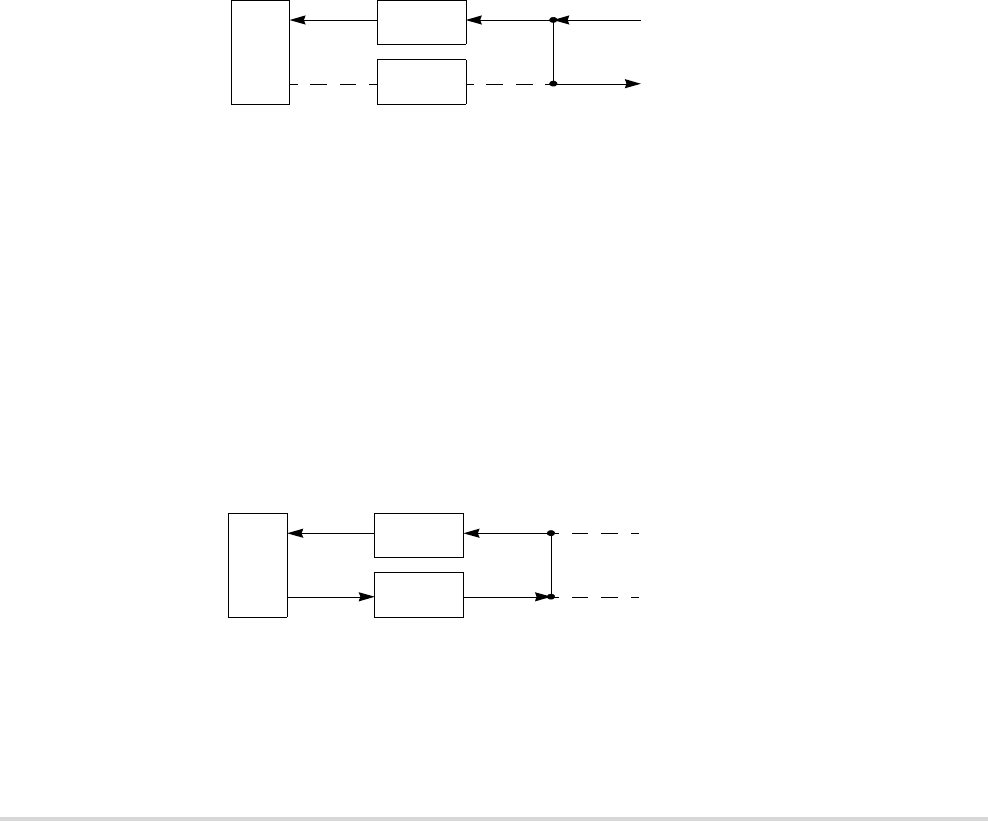

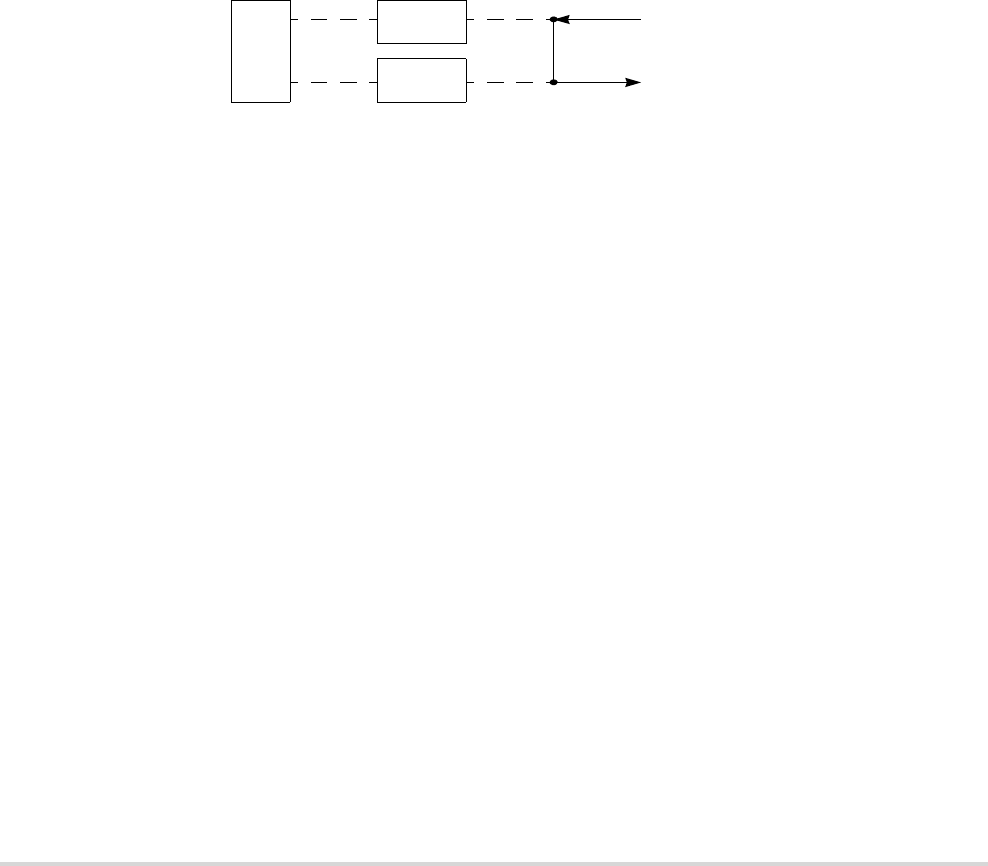

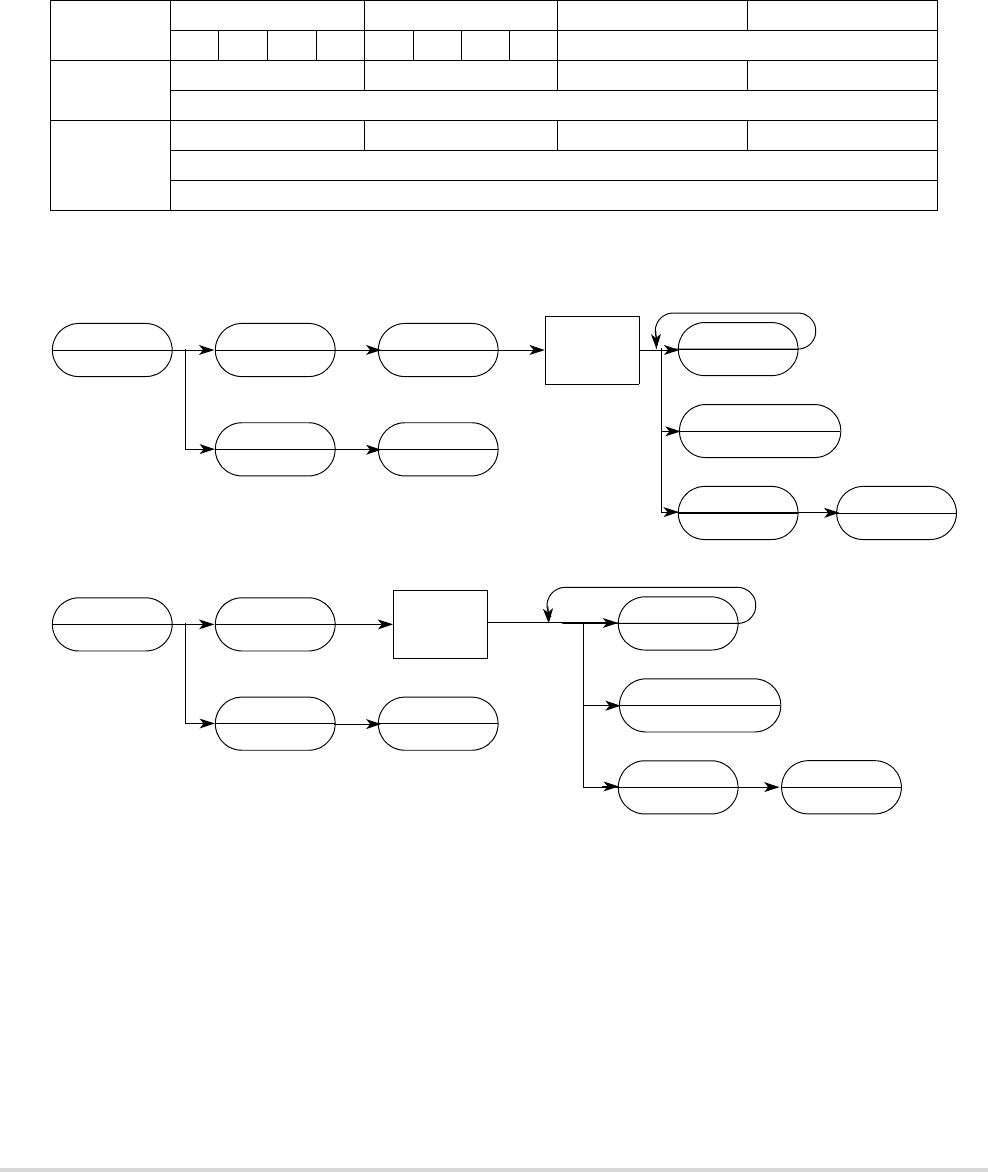

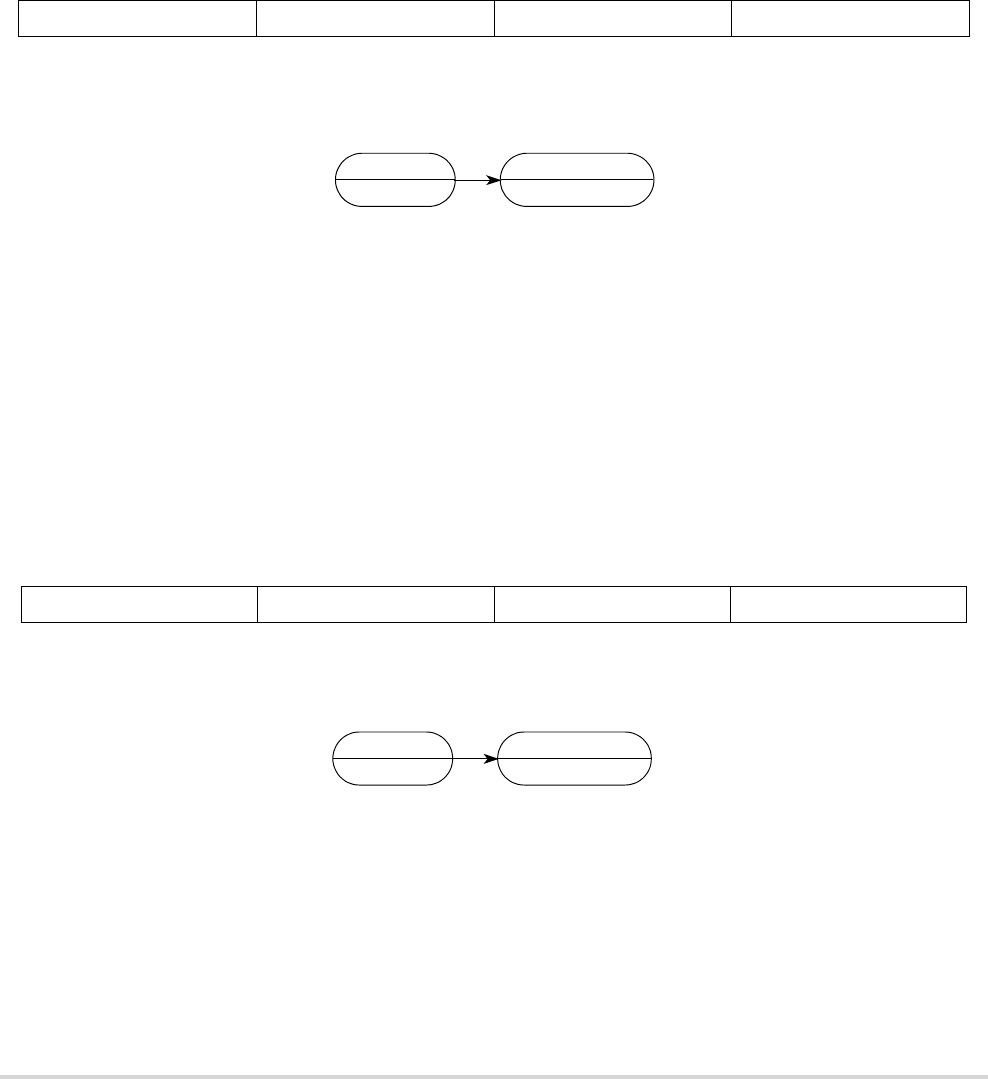

- Figure 29-17. rareg/rdreg Command Format

- Figure 29-18. rareg/rdreg Command Sequence

- Figure 29-19. wareg/wdreg Command Format

- Figure 29-20. wareg/wdreg Command Sequence

- Figure 29-21. read Command/Result Formats

- Figure 29-22. read Command Sequence

- Figure 29-23. write Command Format

- Figure 29-24. write Command Sequence

- Figure 29-25. dump Command/Result Formats

- Figure 29-26. dump Command Sequence

- Figure 29-27. fill Command Format

- Figure 29-28. fill Command Sequence

- Figure 29-29. go Command Format

- Figure 29-30. go Command Sequence

- Figure 29-31. nop Command Format

- Figure 29-32. nop Command Sequence

- Figure 29-33. rcreg Command/Result Formats

- Table 29-19. Control Register Map

- Figure 29-34. rcreg Command Sequence

- Figure 29-35. wcreg Command/Result Formats

- Figure 29-36. wcreg Command Sequence

- Figure 29-37. rdmreg Command/Result Formats

- Table 29-20. Definition of DRc Encoding-Read

- Figure 29-38. rdmreg Command Sequence

- Figure 29-39. wdmreg BDM Command Format

- Figure 29-40. wdmreg Command Sequence

- 29.6 Real-Time Debug Support

- 29.7 Processor Status, DDATA Definition

- 29.8 Motorola-Recommended BDM Pinout

- Chapter 30 Chip Configuration Module (CCM)

- 30.1 Features

- 30.2 Modes of Operation

- 30.3 Block Diagram

- 30.4 Signal Descriptions

- 30.5 Memory Map and Registers

- 30.6 Functional Description

- 30.7 Reset

- 30.8 Interrupts

- Chapter 31 IEEE 1149.1 Test Access Port (JTAG)

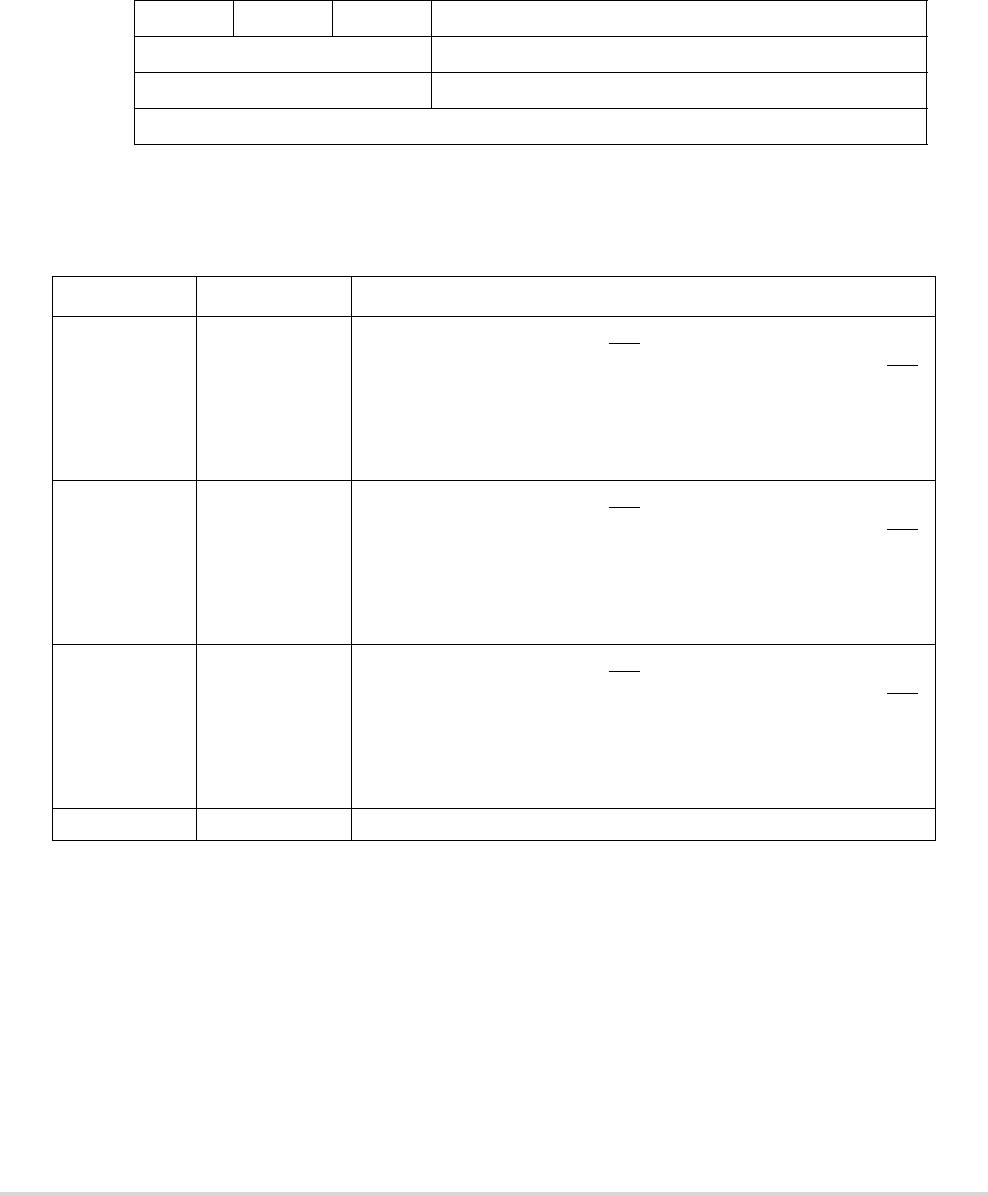

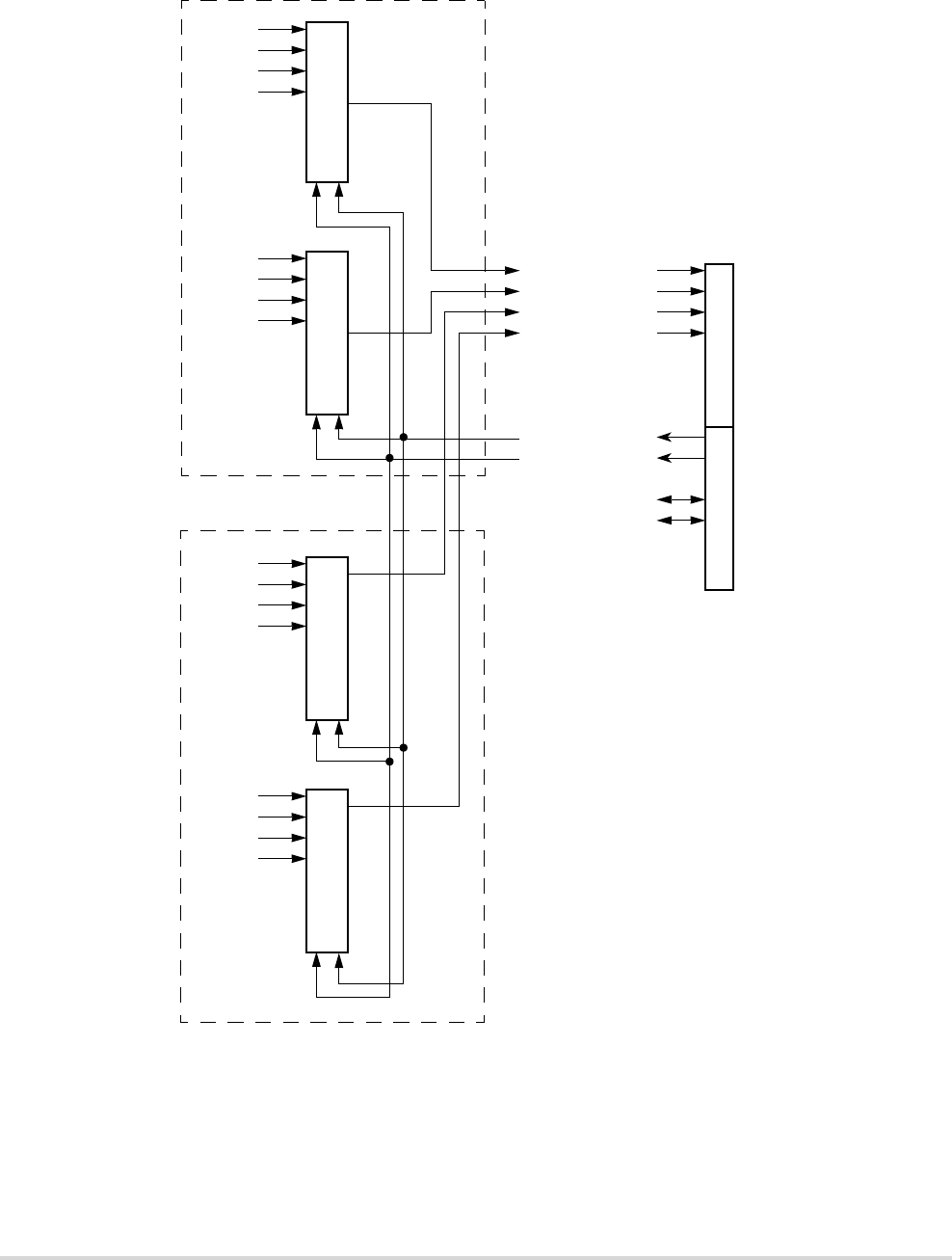

- Figure 31-1. JTAG Block Diagram

- 31.1 Features

- 31.2 Modes of Operation

- 31.3 External Signal Description

- 31.3.1 Detailed Signal Description

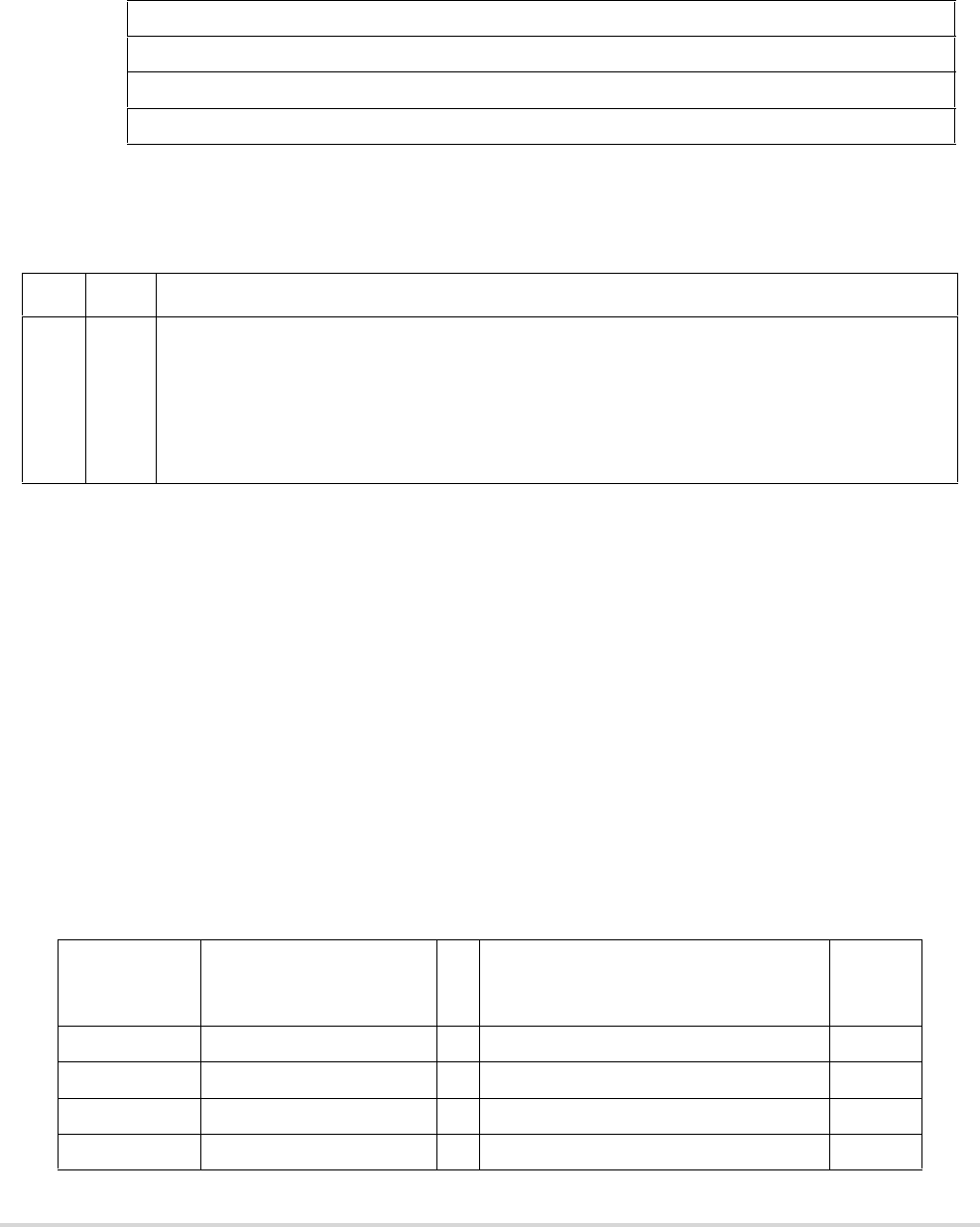

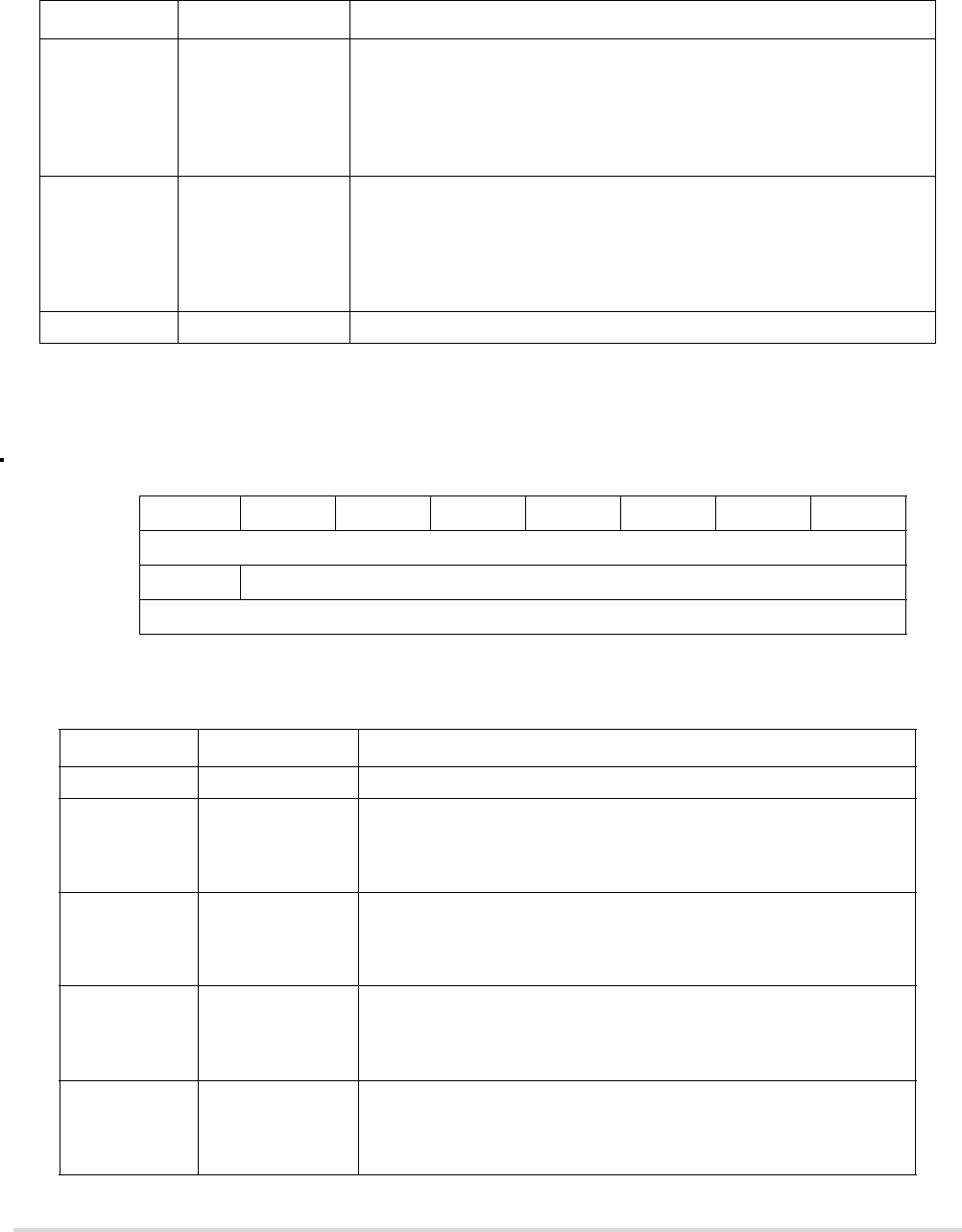

- Table 31-1. Signal Properties

- 31.3.1.1 JTAG_EN - JTAG Enable

- 31.3.1.2 TCLK - Test Clock Input

- 31.3.1.3 TMS/BKPT - Test Mode Select / Breakpoint

- 31.3.1.4 TDI/DSI - Test Data Input / Development Serial Input

- 31.3.1.5 TRST/DSCLK - Test Reset / Development Serial Clock

- 31.3.1.6 TDO/DSO - Test Data Output / Development Serial Output

- 31.3.1 Detailed Signal Description

- 31.4 Memory Map/Register Definition

- 31.5 Functional Description

- 31.5.1 JTAG Module

- 31.5.2 TAP Controller

- 31.5.3 JTAG Instructions

- Table 31-5. JTAG Instructions (continued)

- 31.5.3.1 External Test Instruction (EXTEST)

- 31.5.3.2 IDCODE Instruction

- 31.5.3.3 SAMPLE/PRELOAD Instruction

- 31.5.3.4 TEST_LEAKAGE Instruction

- 31.5.3.5 ENABLE_TEST_CTRL Instruction

- 31.5.3.6 HIGHZ Instruction

- 31.5.3.7 LOCKOUT_RECOVERY Instruction

- 31.5.3.8 CLAMP Instruction

- 31.5.3.9 BYPASS Instruction

- 31.6 Initialization/Application Information

- Chapter 32 Mechanical Data

- Chapter 33 Electrical Characteristics

- 33.1 Maximum Ratings

- 33.2 Thermal Characteristics

- 33.3 DC Electrical Specifications

- 33.4 Phase Lock Loop Electrical Specifications

- 33.5 QADC Electrical Characteristics

- 33.6 Flash Memory Characteristics

- 33.7 External Interface Timing Characteristics

- 33.8 Processor Bus Output Timing Specifications

- 33.9 General Purpose I/O Timing

- 33.10 Reset and Configuration Override Timing

- 33.11 I2C Input/Output Timing Specifications

- 33.12 Fast Ethernet AC Timing Specifications

- 33.13 DMA Timer Module AC Timing Specifications

- 33.14 QSPI Electrical Specifications

- 33.15 JTAG and Boundary Scan Timing

- 33.16 Debug AC Timing Specifications

- Appendix A Register Memory Map

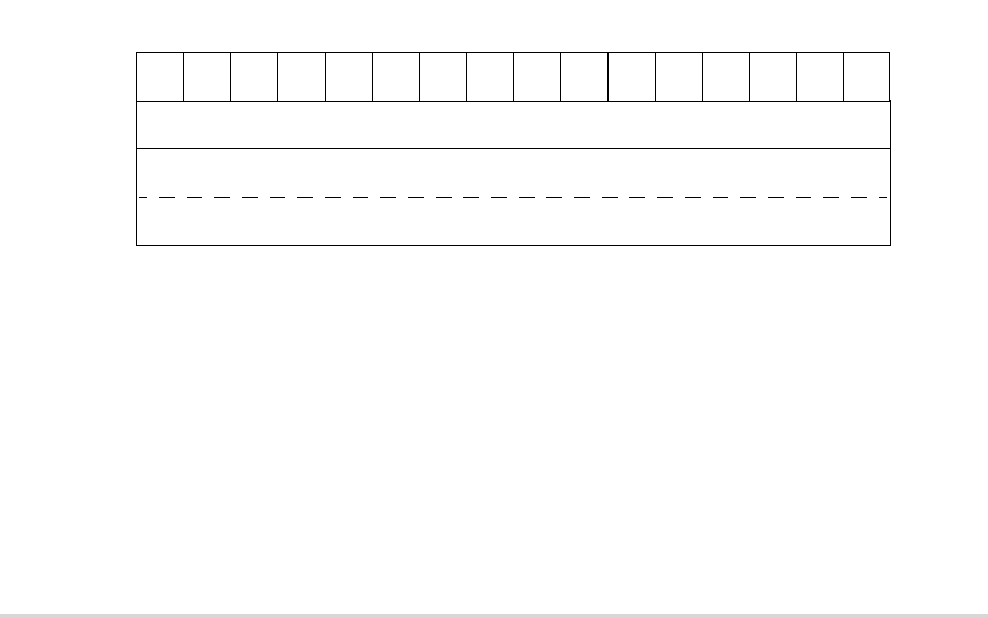

MCF5282UM/D

Rev. 2

1/2004

MCF5282 ColdFire

®

Microcontroller User’s Manual

Devices Supported:

MCF5281

HOW TO REACH US:

USA/EUROPE/LOCATIONS NOT LISTED:

Motorola Literature Distribution;

P.O. Box 5405

Denver, Colorado 80217

1-800-521-6274 or 480-768-2130

JAPAN:

Motorola Japan Ltd.;

SPS, Technical Information Center,

3-20-1, Minami-Azabu Minato-ku,

Tokyo 106-8573 Japan

81-3-3440-3569

ASIA/PACIFIC:

Motorola Semiconductors H.K. Ltd.;

Silicon Harbour Centre

2 Dai King Street,

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

852-26668334

HOME PAGE:

http://motorola.com/semiconductors

Motorola and the Stylized M Logo are registered in the U.S. Patent and Trademark Office. digital

dna is a trademark of Motorola, Inc. All other product or service names are the property of their

respective owners. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 2004

Information in this document is provided solely to enable system and software implementers to use

Motorola products. There are no express or implied copyright licenses granted hereunder to design

or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein.

Motorola makes no warranty, representation or guarantee regarding the suitability of its products

for any particular purpose, nor does Motorola assume any liability arising out of the application or

use of any product or circuit, and specifically disclaims any and all liability, including without

limitation consequential or incidental damages. “Typical” parameters which may be provided in

Motorola data sheets and/or specifications can and do vary in different applications and actual

performance may vary over time. All operating parameters, including “Typicals” must be validated

for each customer application by customer’s technical experts. Motorola does not convey any

license under its patent rights nor the rights of others. Motorola products are not designed,

intended, or authorized for use as components in systems intended for surgical implant into the

body, or other applications intended to support or sustain life, or for any other application in which

the failure of the Motorola product could create a situation where personal injury or death may

occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized

application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries,

affiliates, and distributors harmless against all claims, costs, damages, and expenses, and

reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use, even if such claim alleges that Motorola was

negligent regarding the design or manufacture of the part.

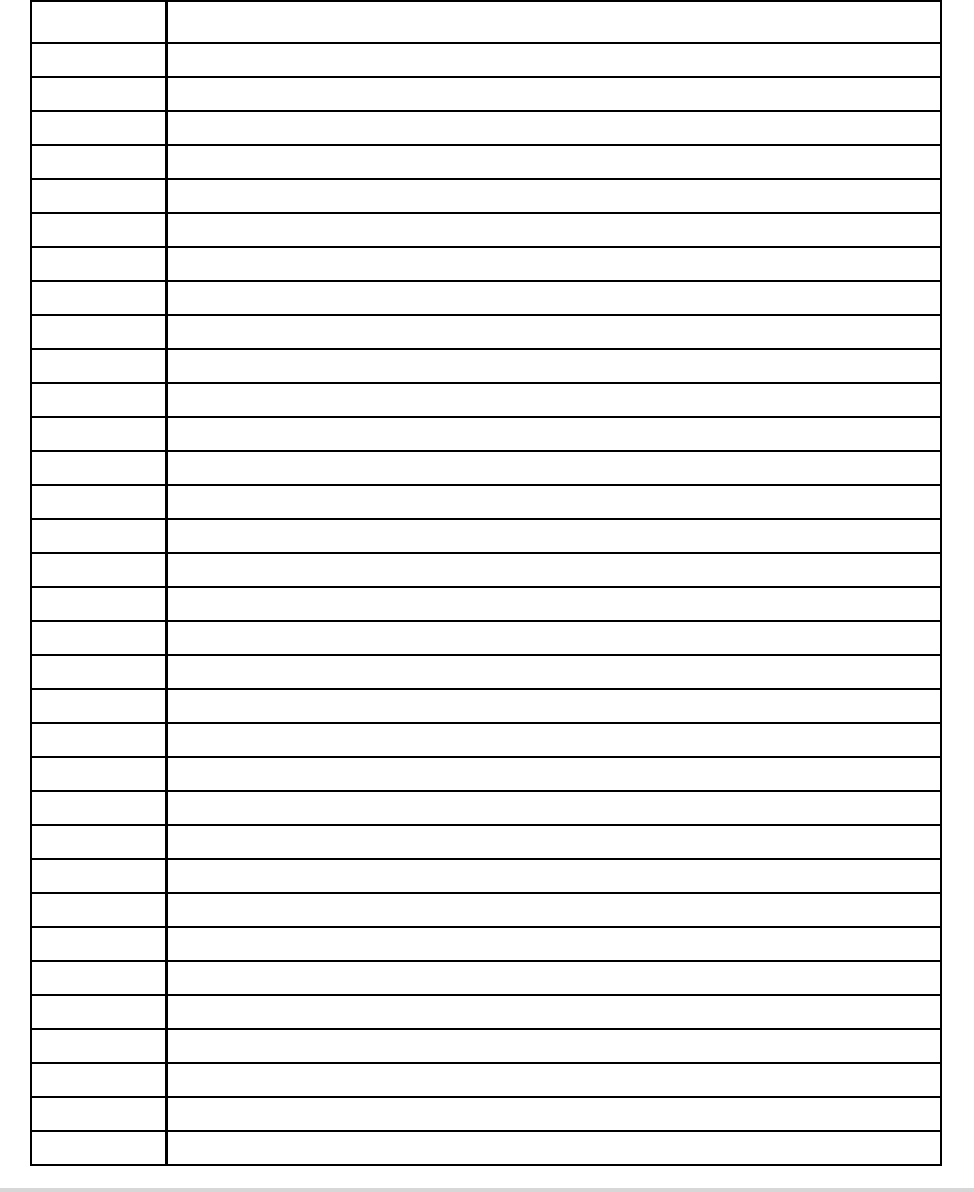

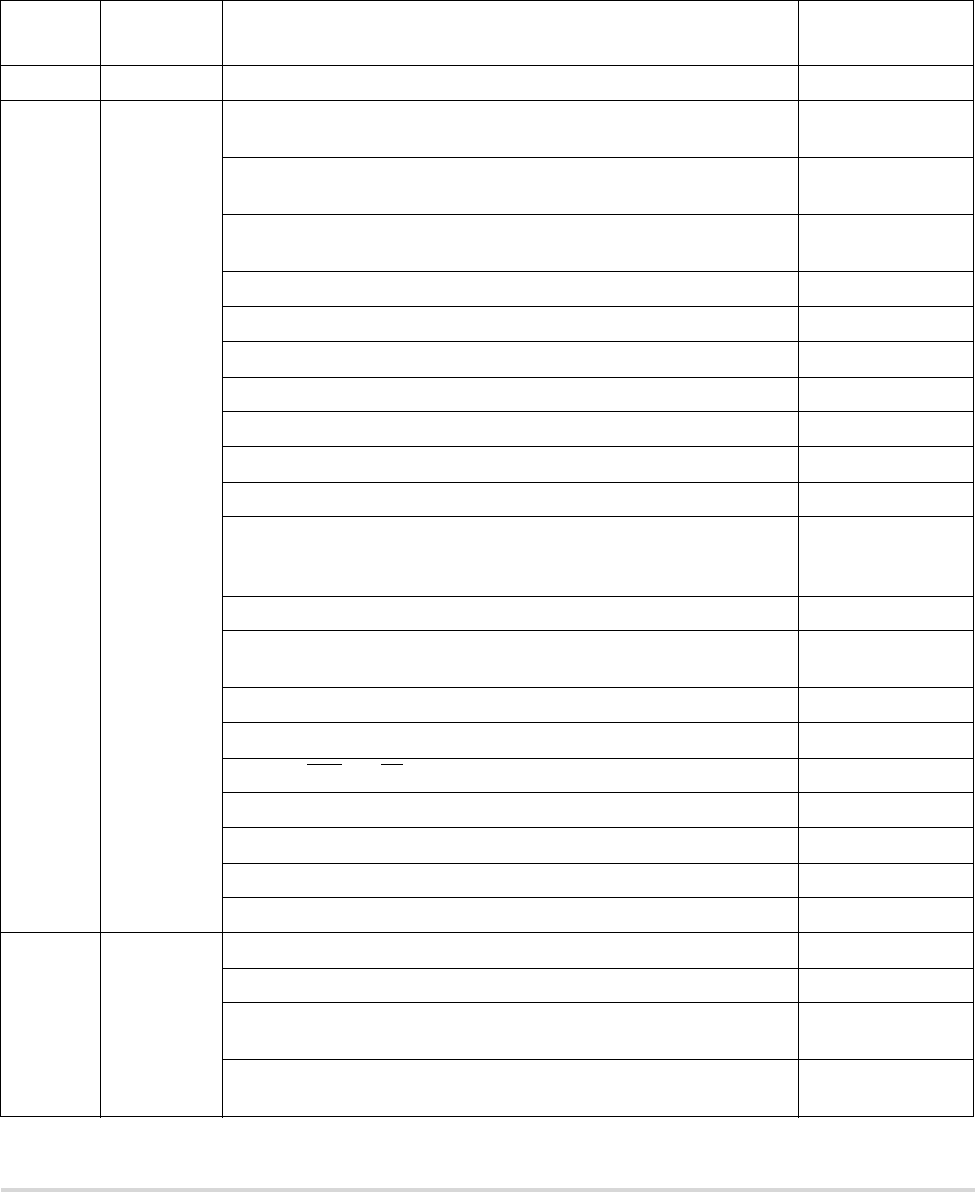

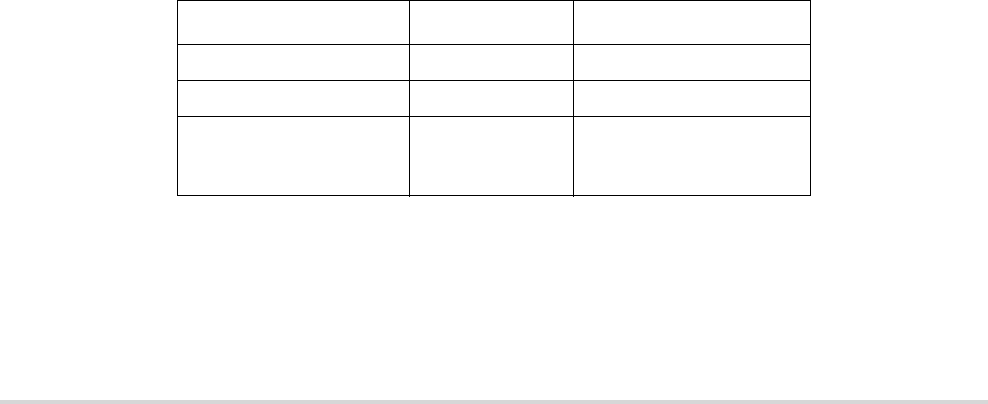

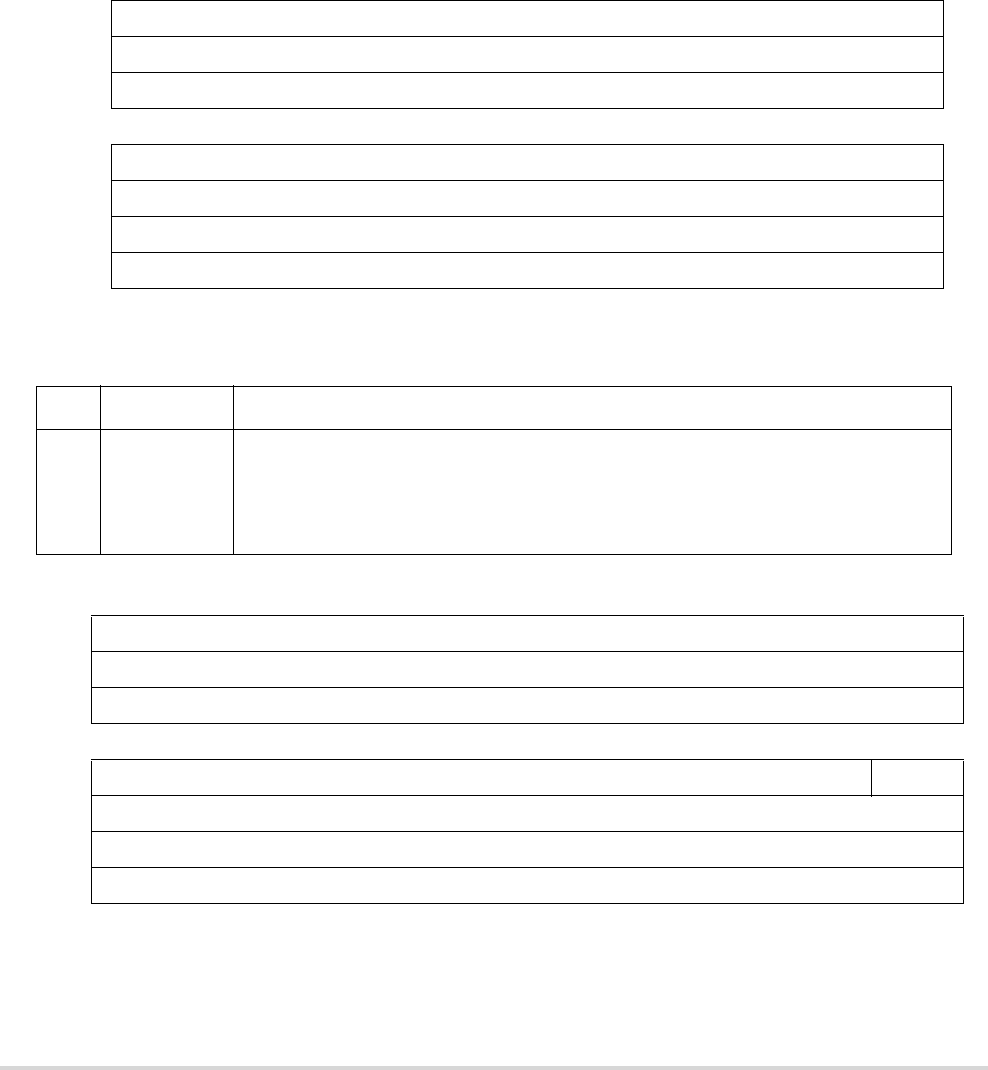

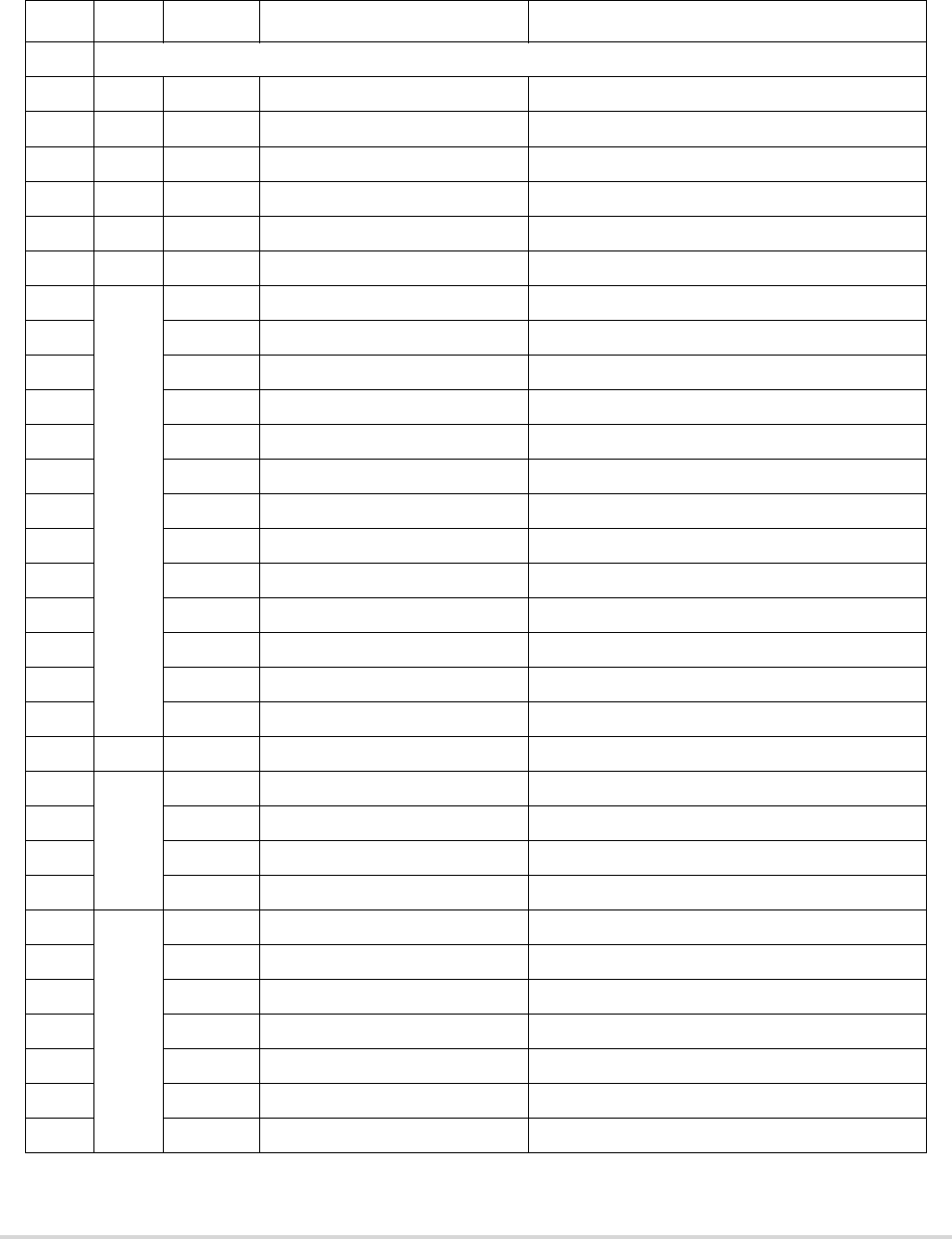

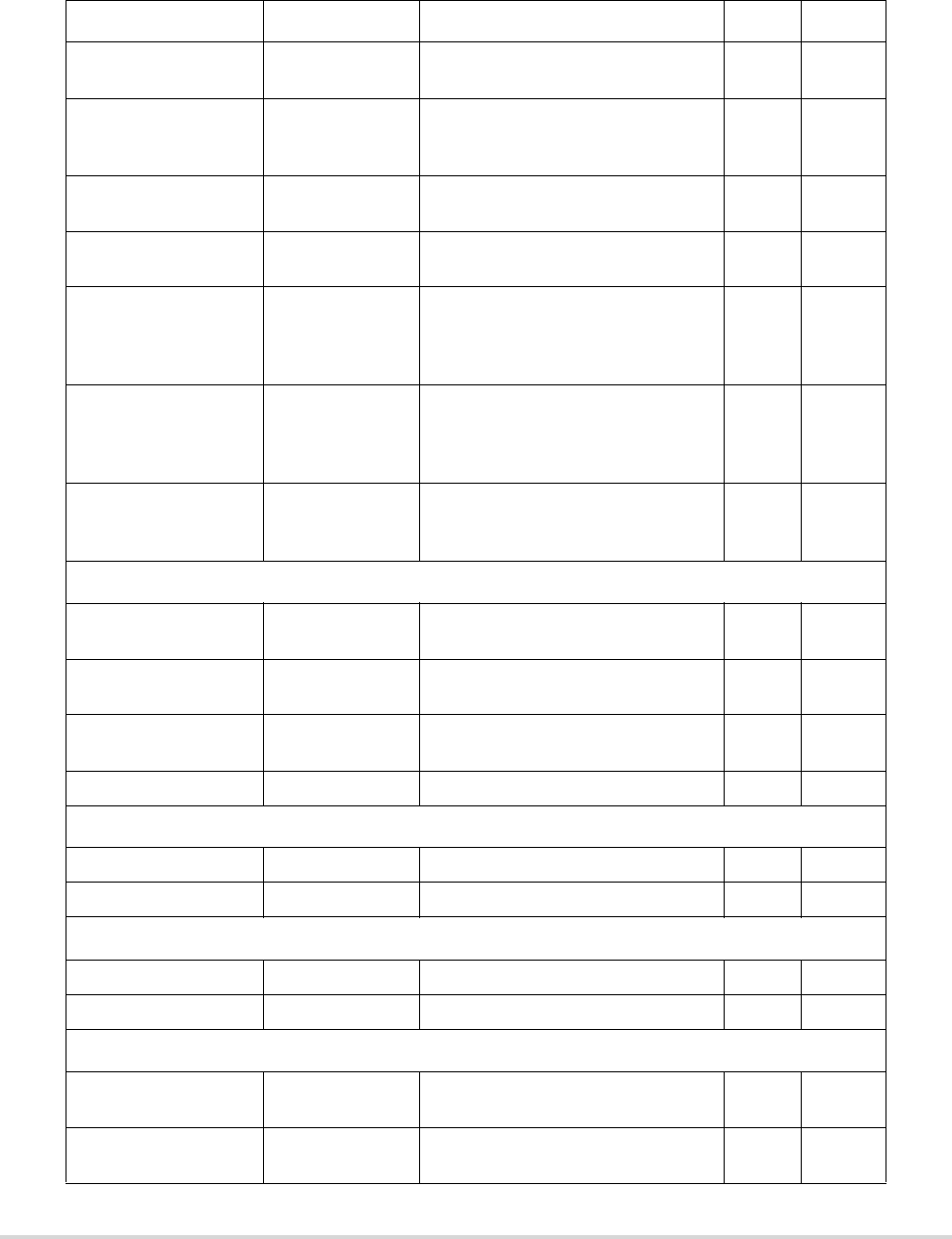

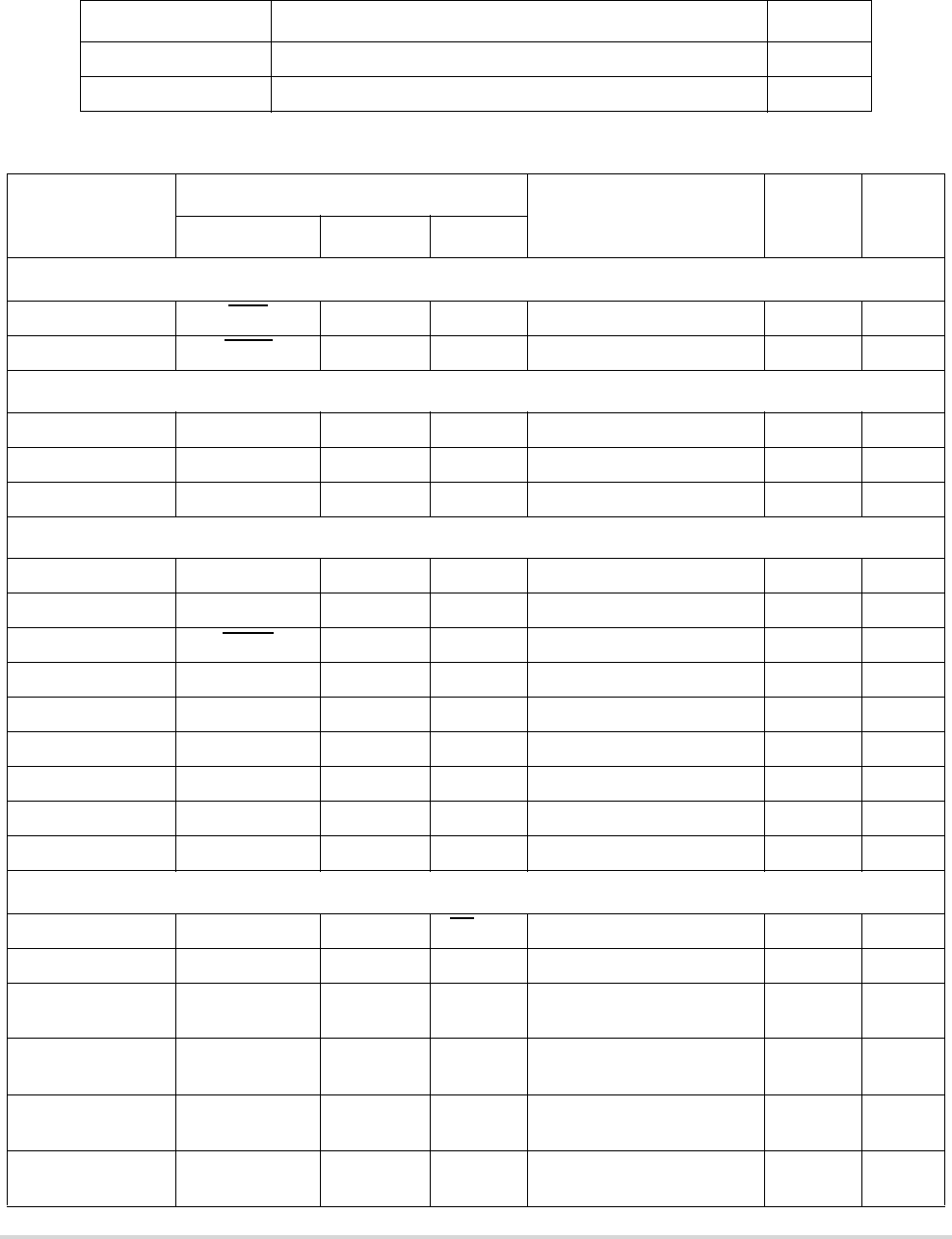

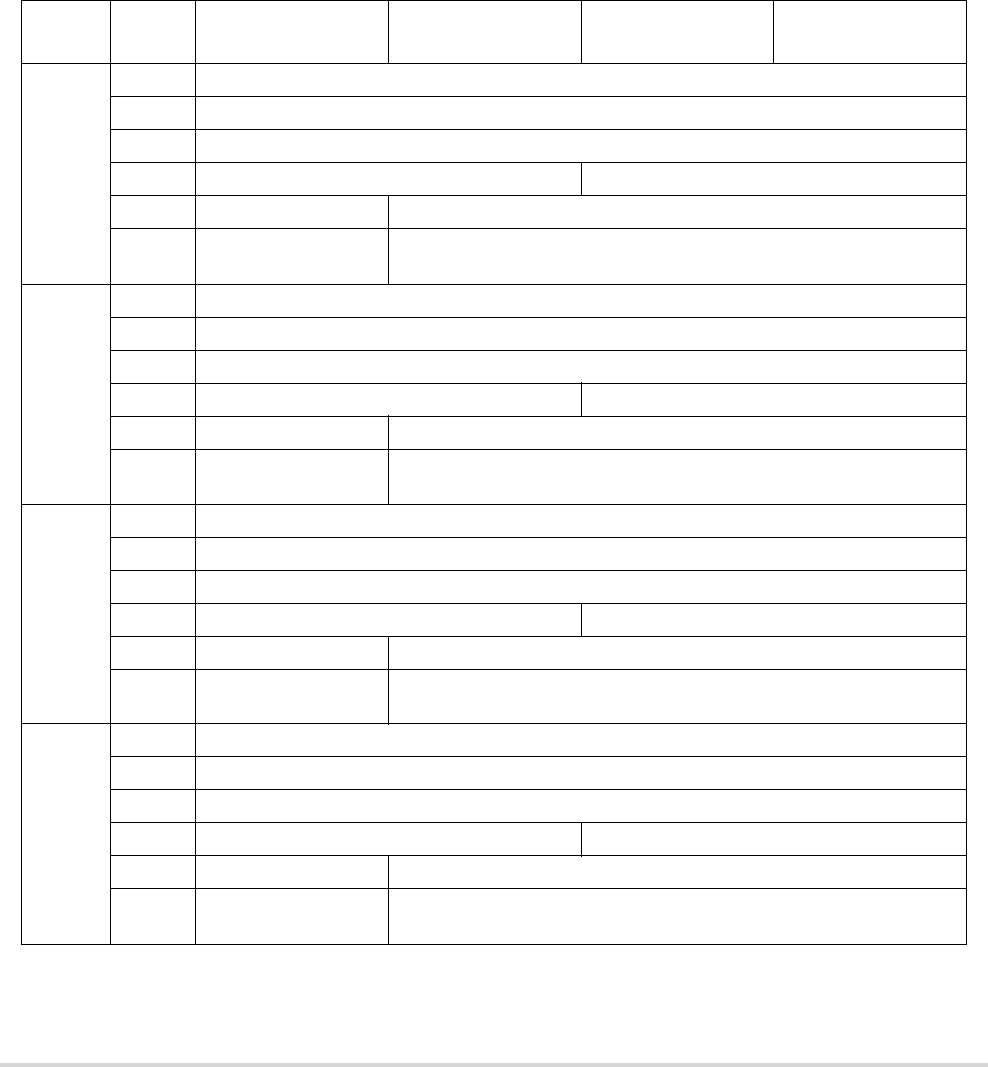

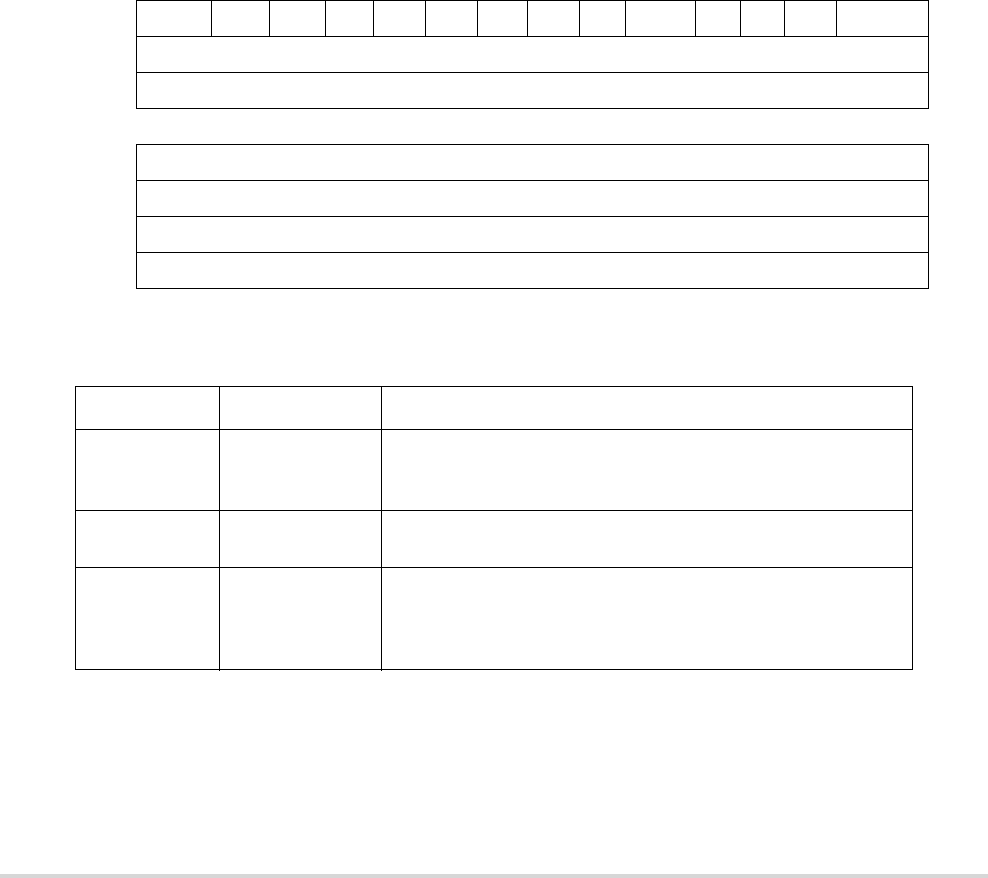

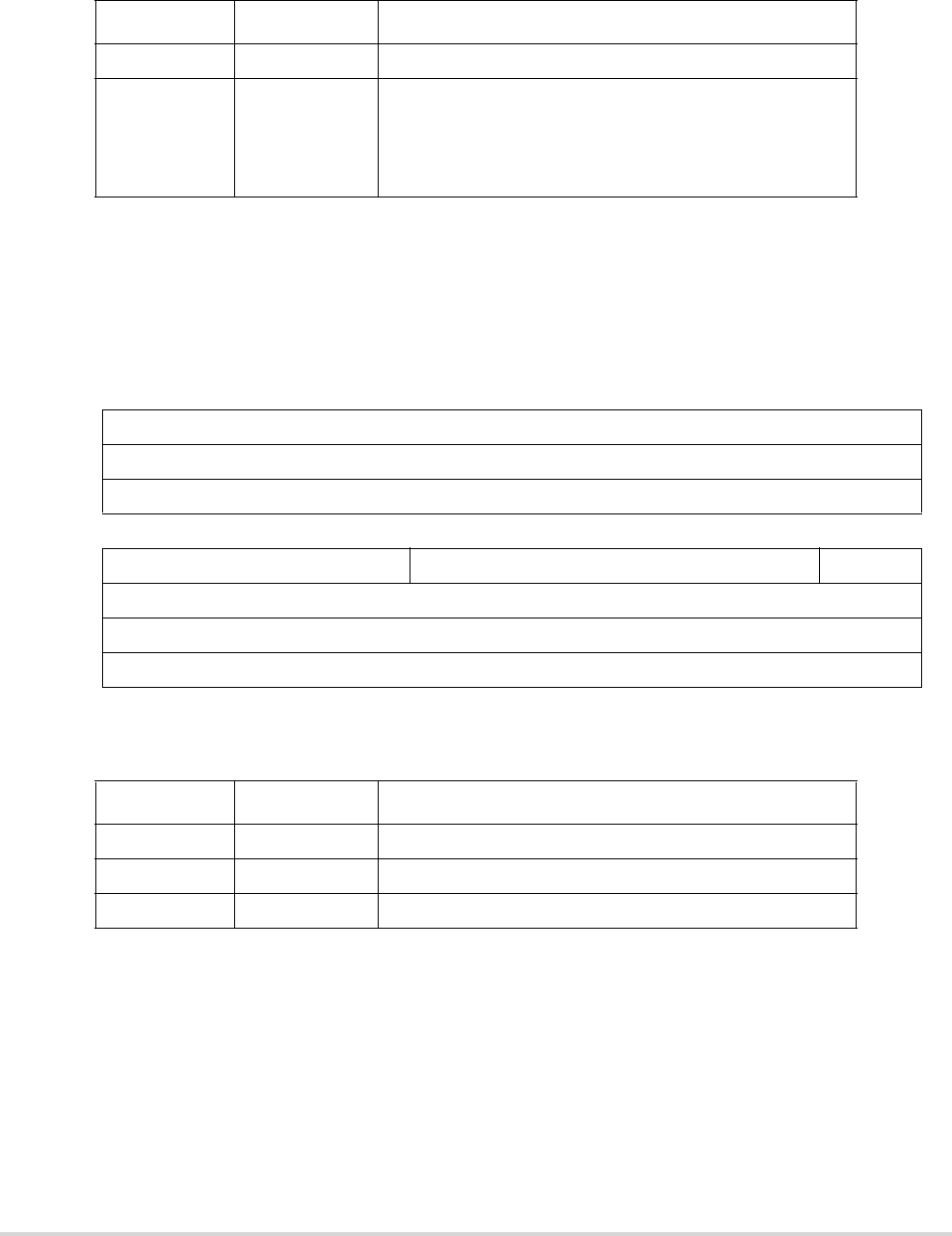

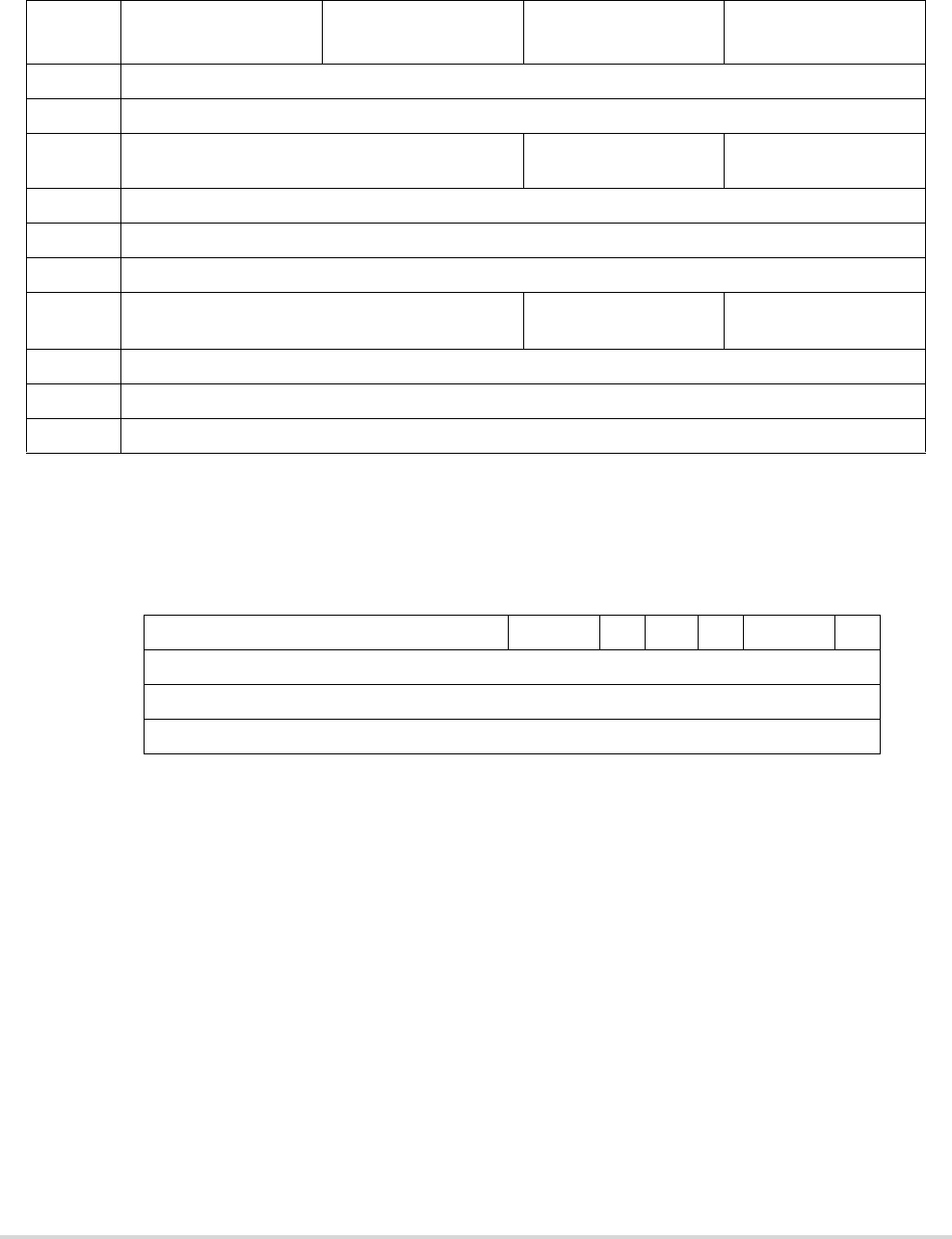

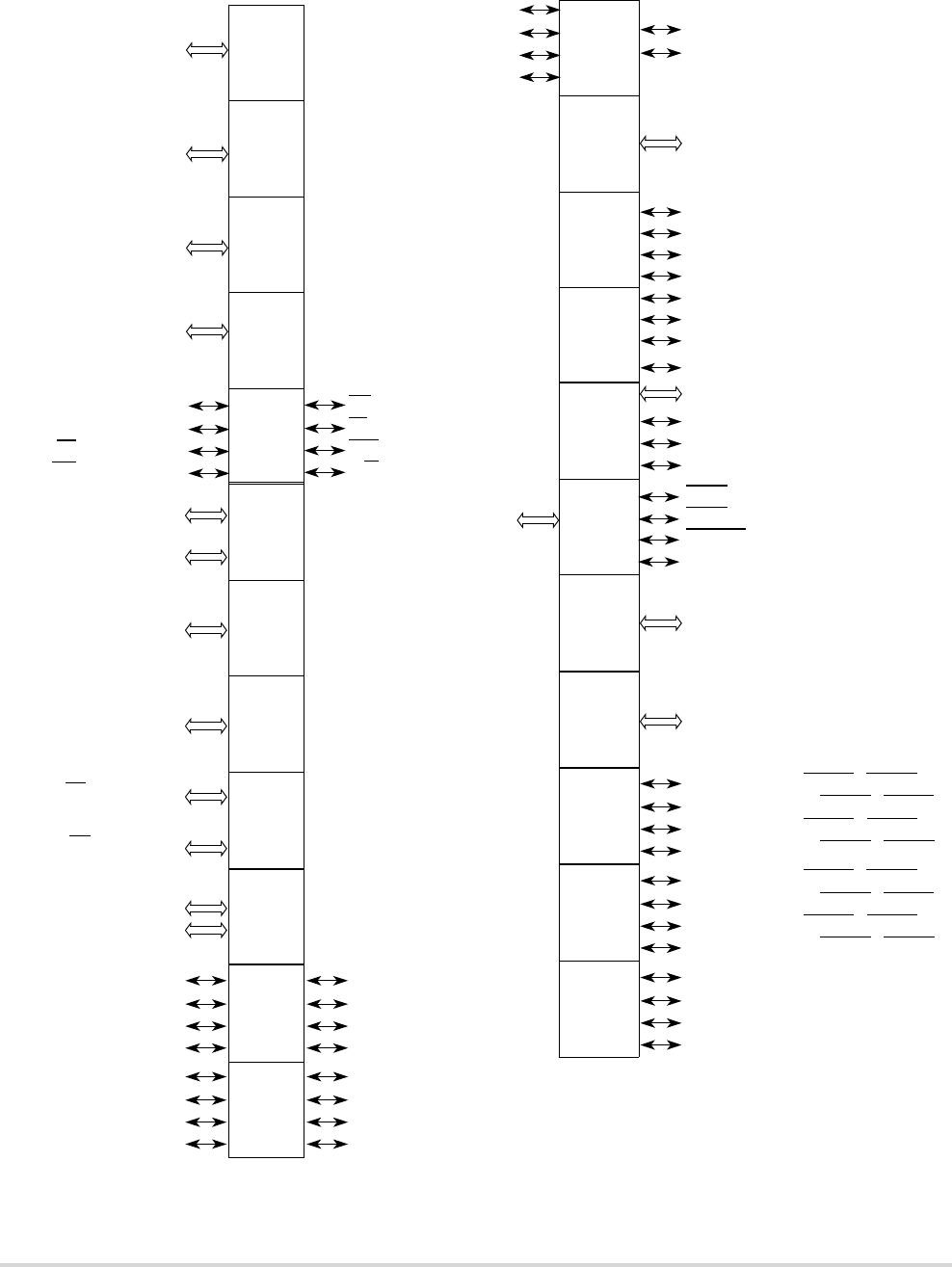

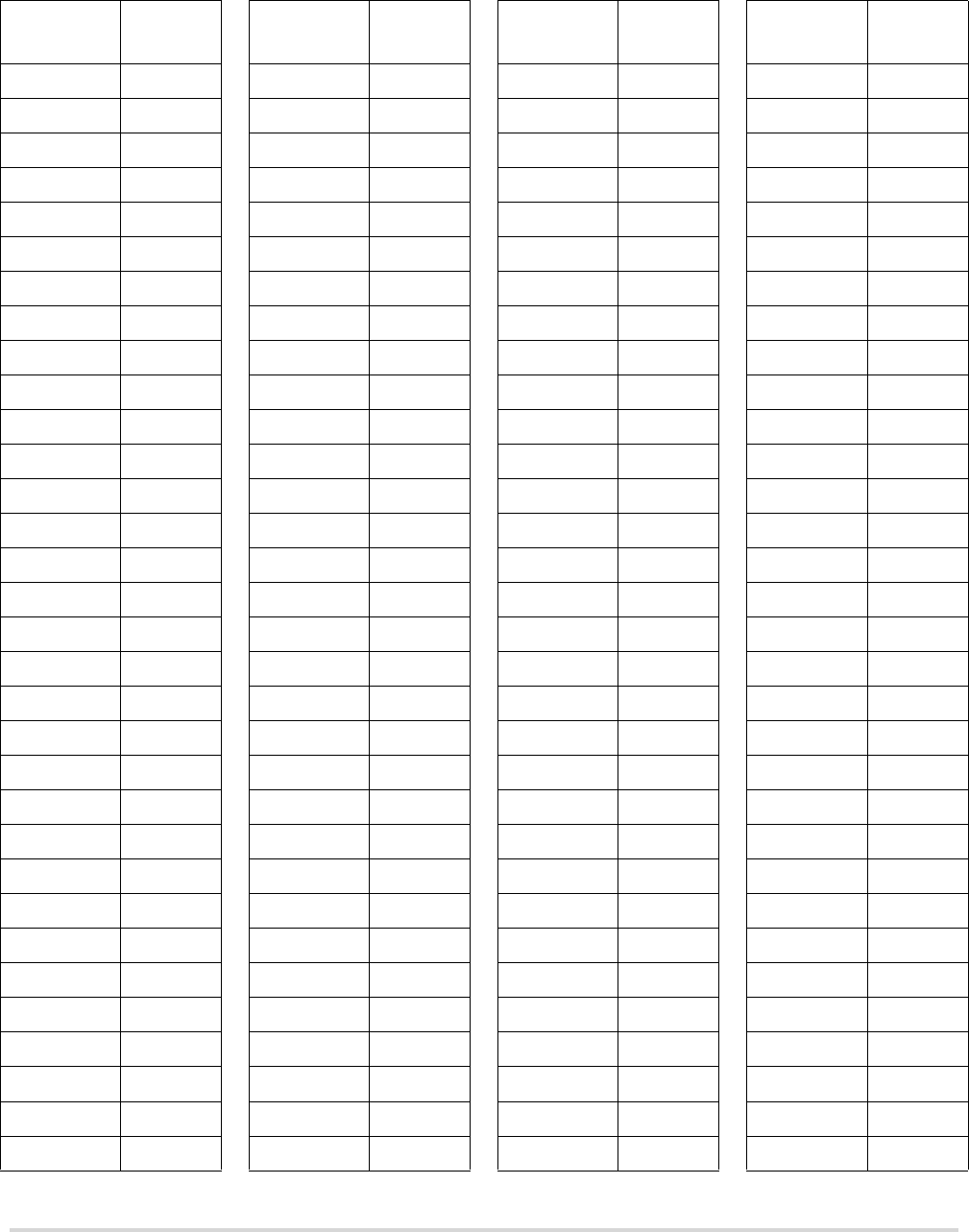

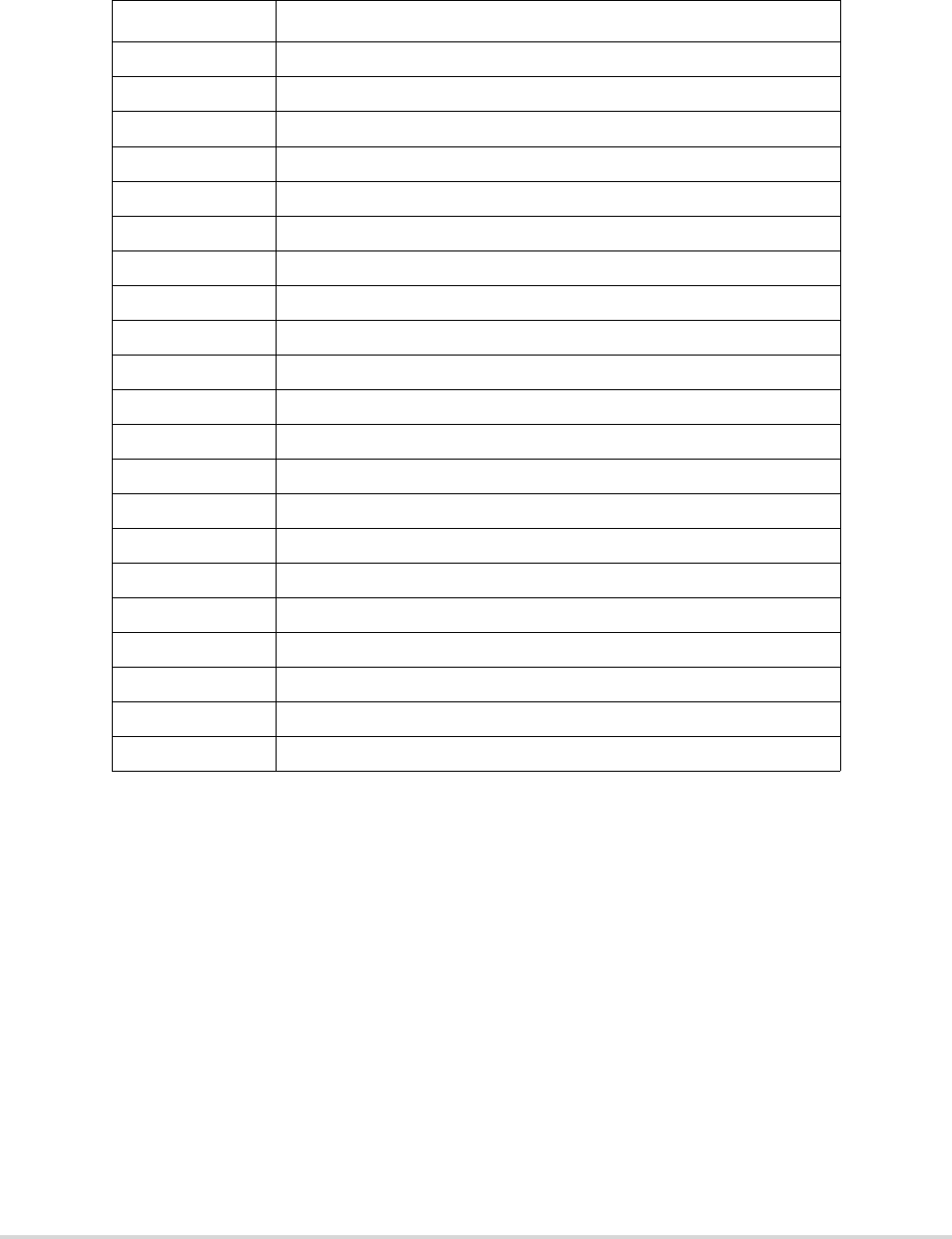

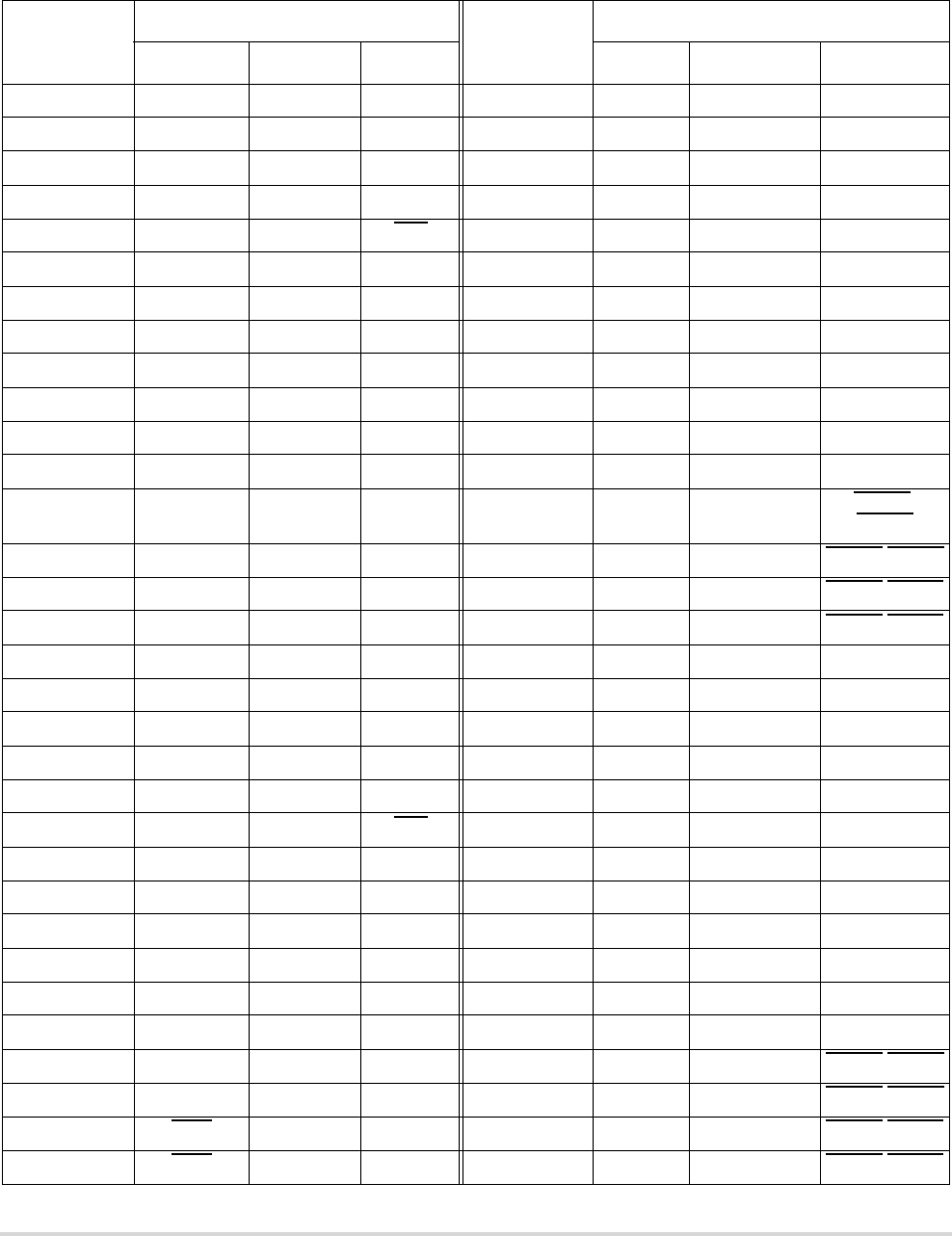

Overview

ColdFire Core

Enhanced Multiply-Accumulate Unit (EMAC)

Cache

Static RAM (SRAM)

ColdFire Flash Module (CFM)

Power Management

System Control Module (SCM)

Clock Module

Interrupt Controller Modules

Edge Port Module (EPORT)

Chip Select Module

External Interface Module (EIM)

Synchronous DRAM Controller Module

DMA Controller Module

Fast Ethernet Controller (FEC)

Watchdog Timer Module

Programmable Interrupt Timer (PIT) Modules

General Purpose Timer (GPT) Modules

FlexCAN Module

General Purpose I/O Module

I2C Module

3

4

5

7

8

9

10

11

12

13

15

16

17

18

19

24

6

20

25

26

21

23

22

DMA Timers

Queued Serial Peripheral Interface Module (QSPI)

UART Modules

1

2

27

28

29

30

31

32

33

A

Chip Configuration Module (CCM)

Queued Analog-to-Digital Converter (QADC)

Reset Controller Module

Debug Support

IEEE 1149.1 Test Access Port (JTAG)

Mechanical Data

Electrical Characteristics

Appendix A: List of Memory Maps

IND

Index

Signal Descriptions 14

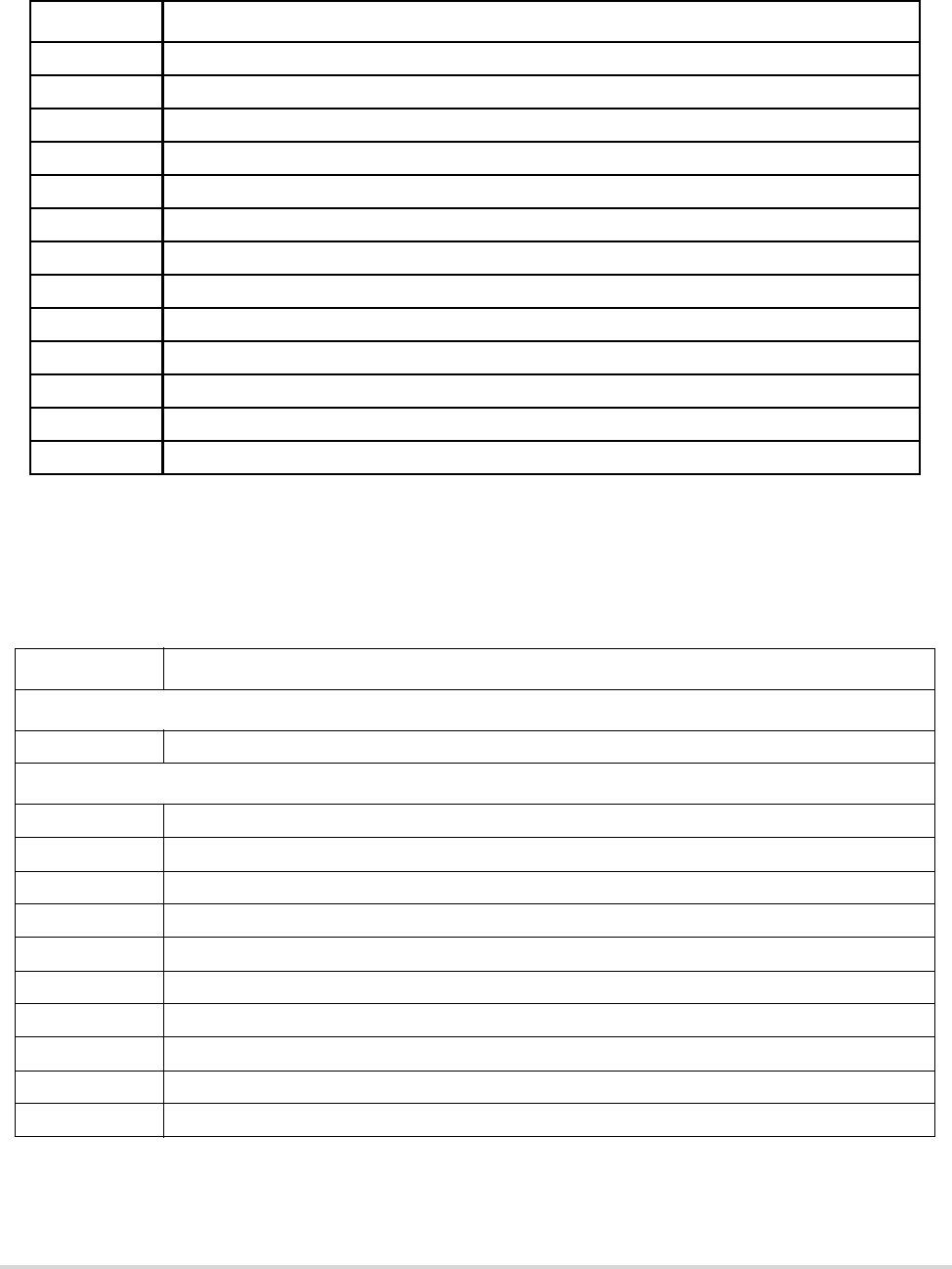

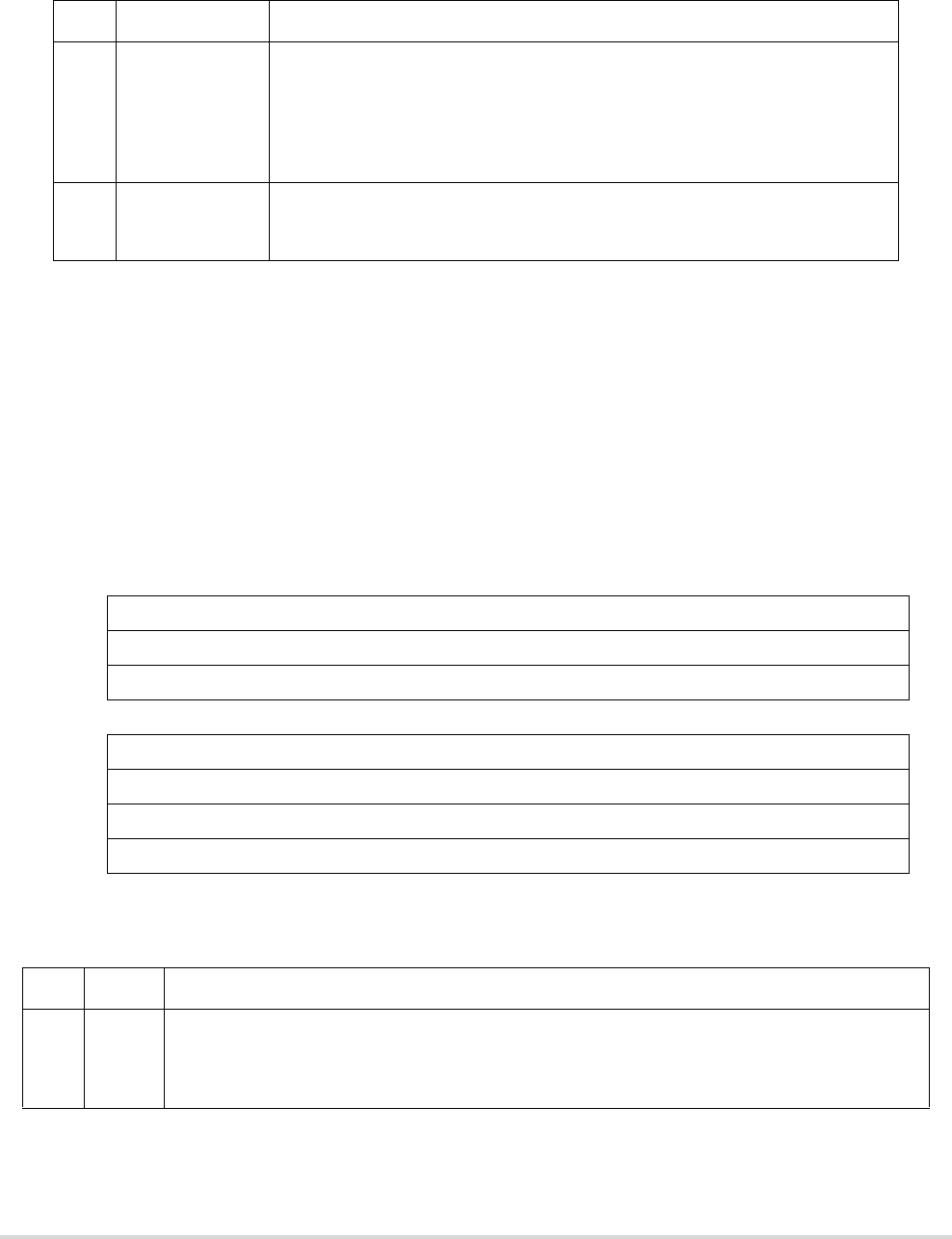

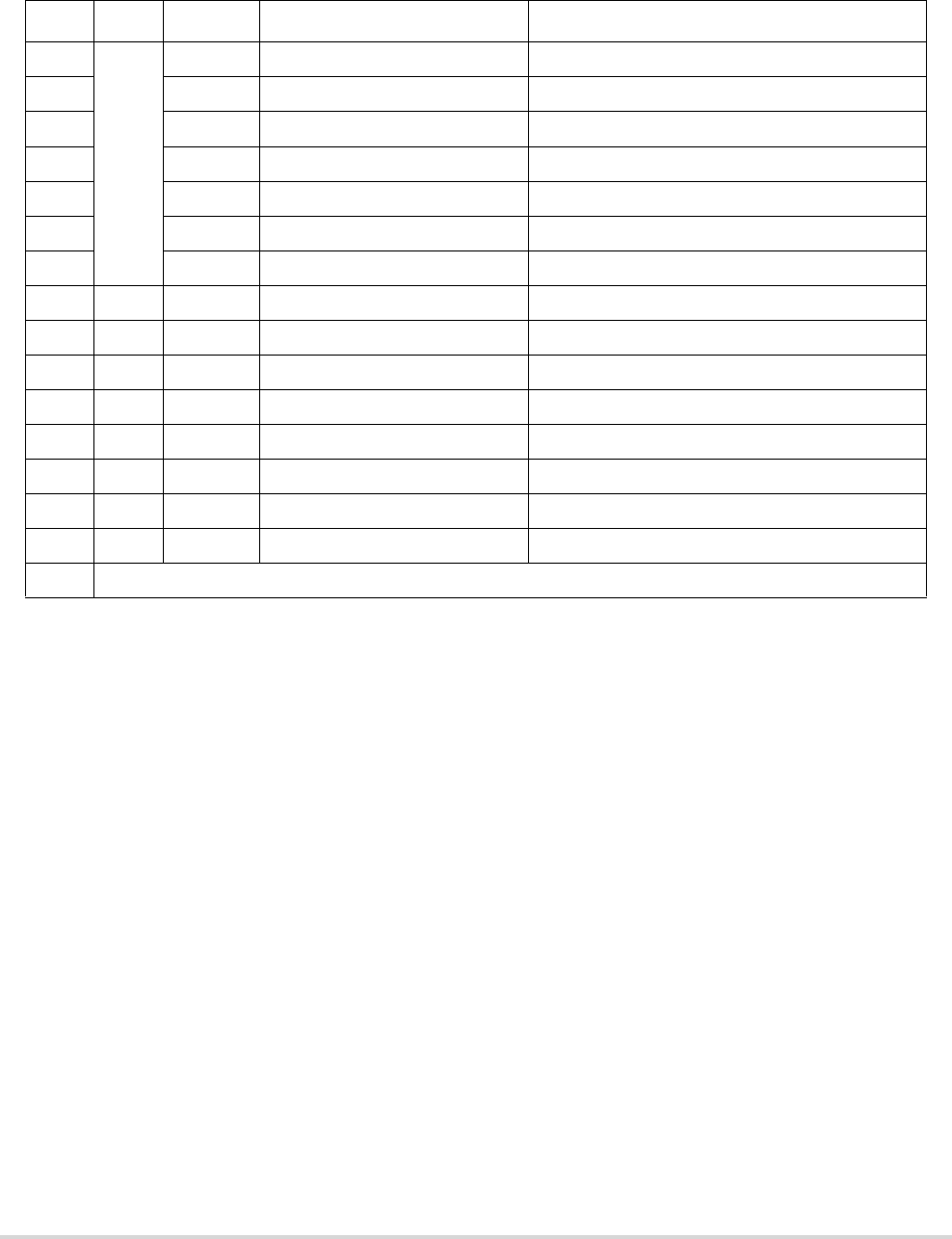

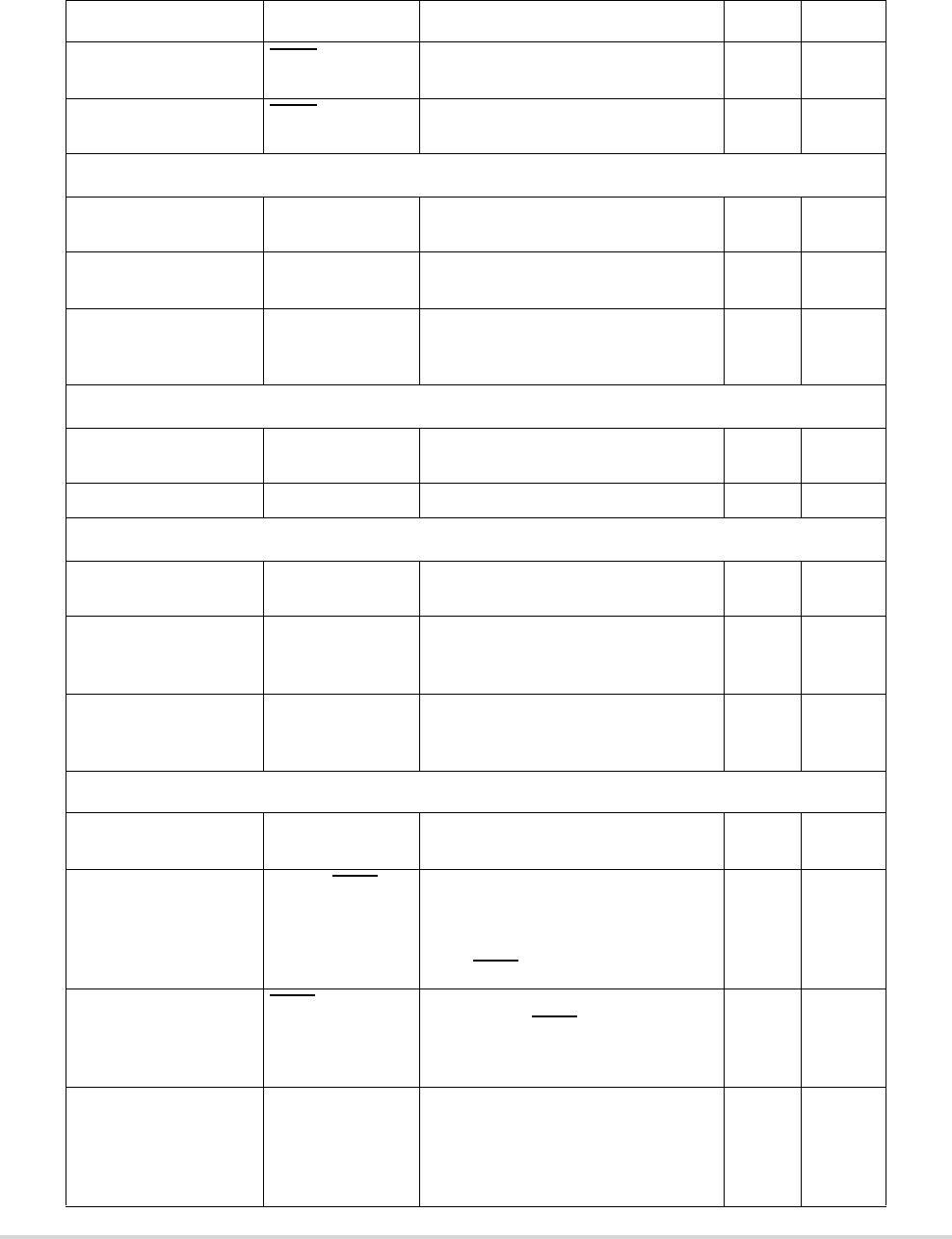

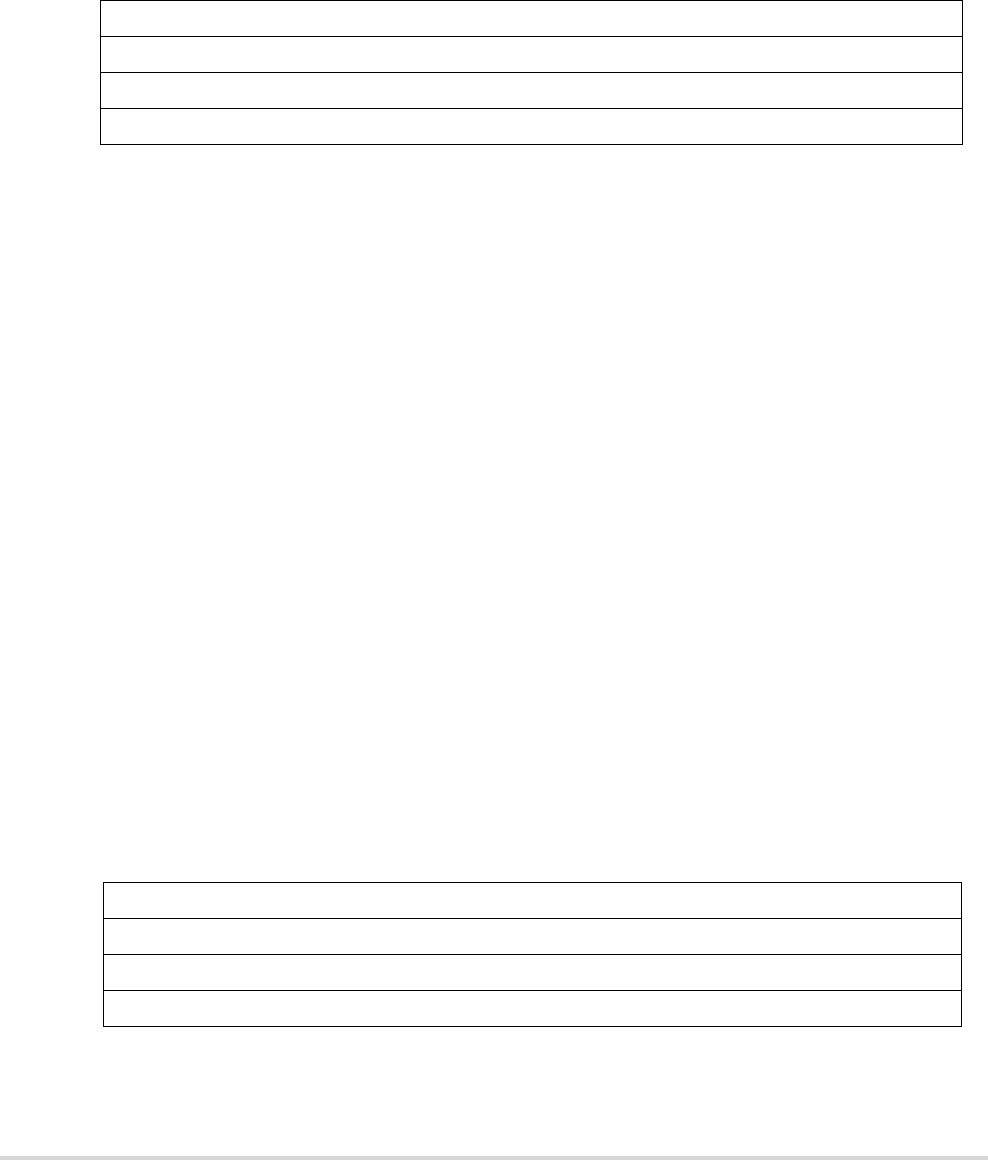

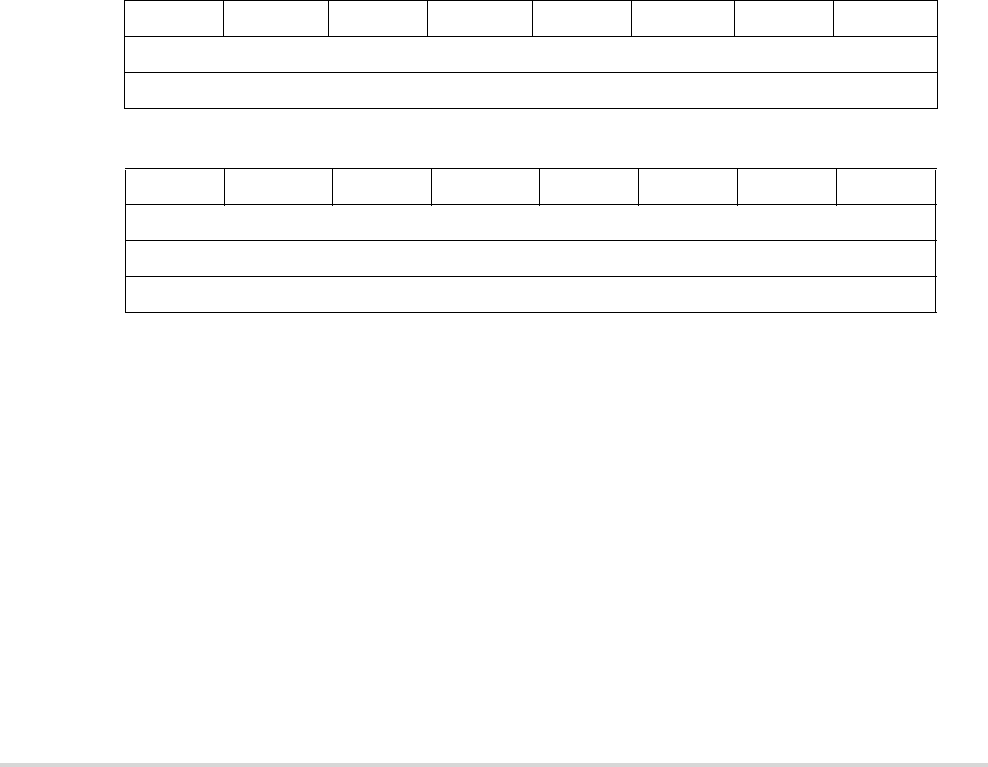

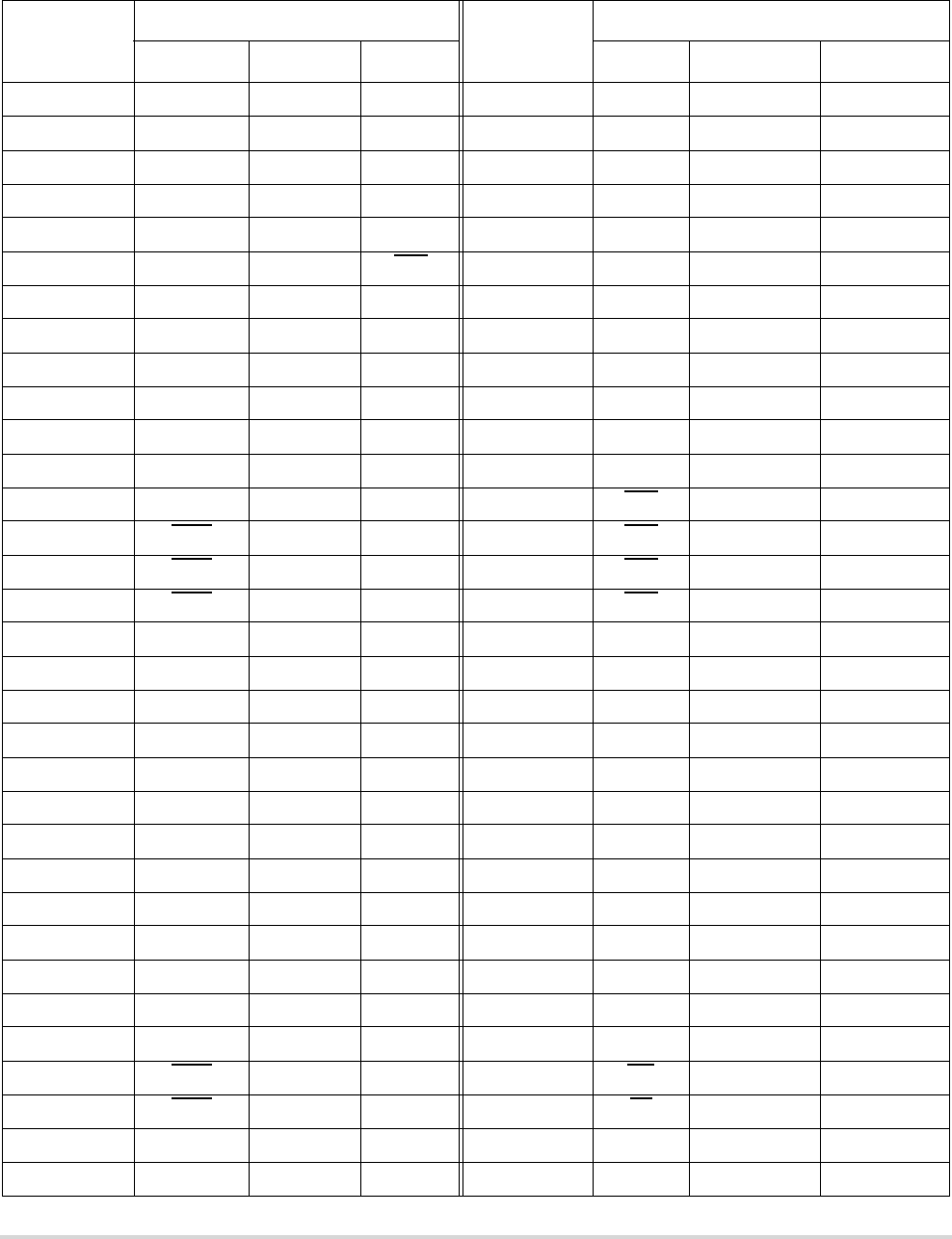

Overview

ColdFire Core

Enhanced Multiply-Accumulate Unit (EMAC)

Cache

Static RAM (SRAM)

ColdFire Flash Module (CFM)

Power Management

System Control Module (SCM)

Clock Module

Interrupt Controller Modules

Edge Port Module (EPORT)

Chip Select Module

External Interface Module (EIM)

Signal Descriptions

Synchronous DRAM Controller Module

DMA Controller Module

Fast Ethernet Controller (FEC)

Watchdog Timer Module

Programmable Interrupt Timer (PIT) Modules

General Purpose Timer (GPT) Modules

FlexCAN Module

General Purpose I/O Module

I2C Module

3

4

5

7

8

9

10

11

12

13

14

15

16

17

18

19

24

6

20

25

26

21

23

22

DMA Timers

Queued Serial Peripheral Interface Module (QSPI)

UART Modules

1

2

27

28

29

30

31

32

33

A

Chip Configuration Module (CCM)

Queued Analog-to-Digital Converter (QADC)

Reset Controller Module

Debug Support

IEEE 1149.1 Test Access Port (JTAG)

Mechanical Data

Electrical Characteristics

Appendix A: List of Memory Maps

IND Index

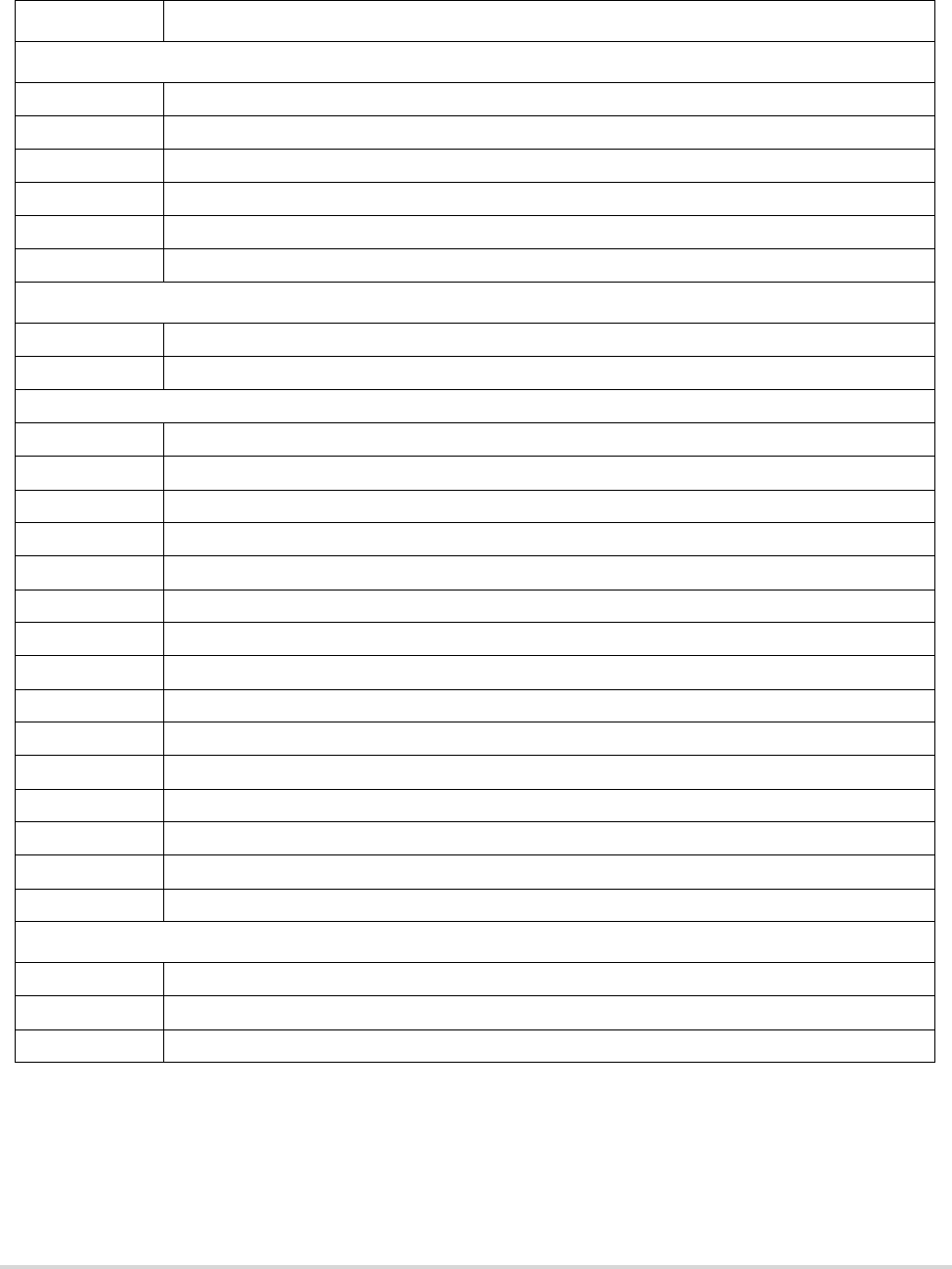

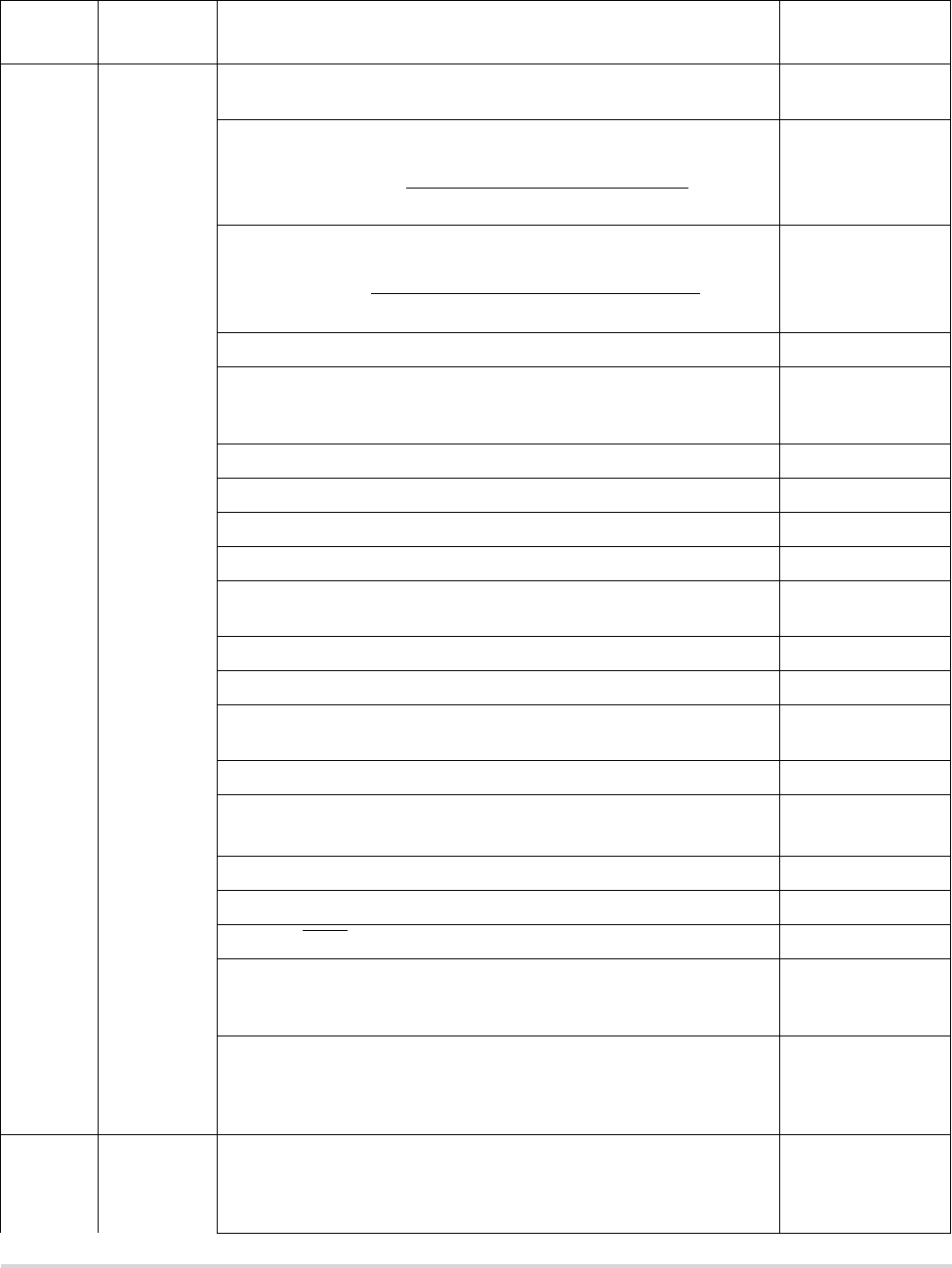

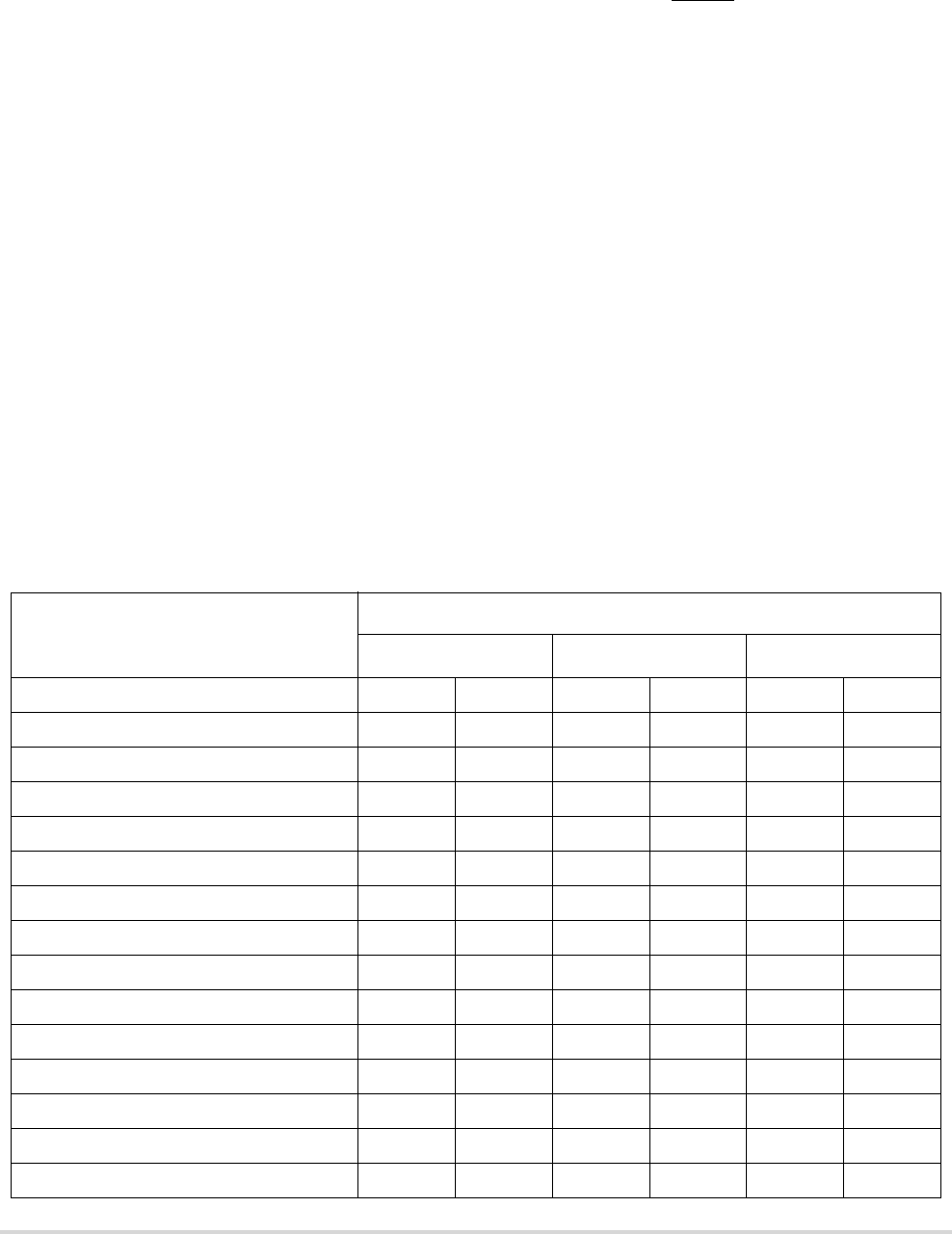

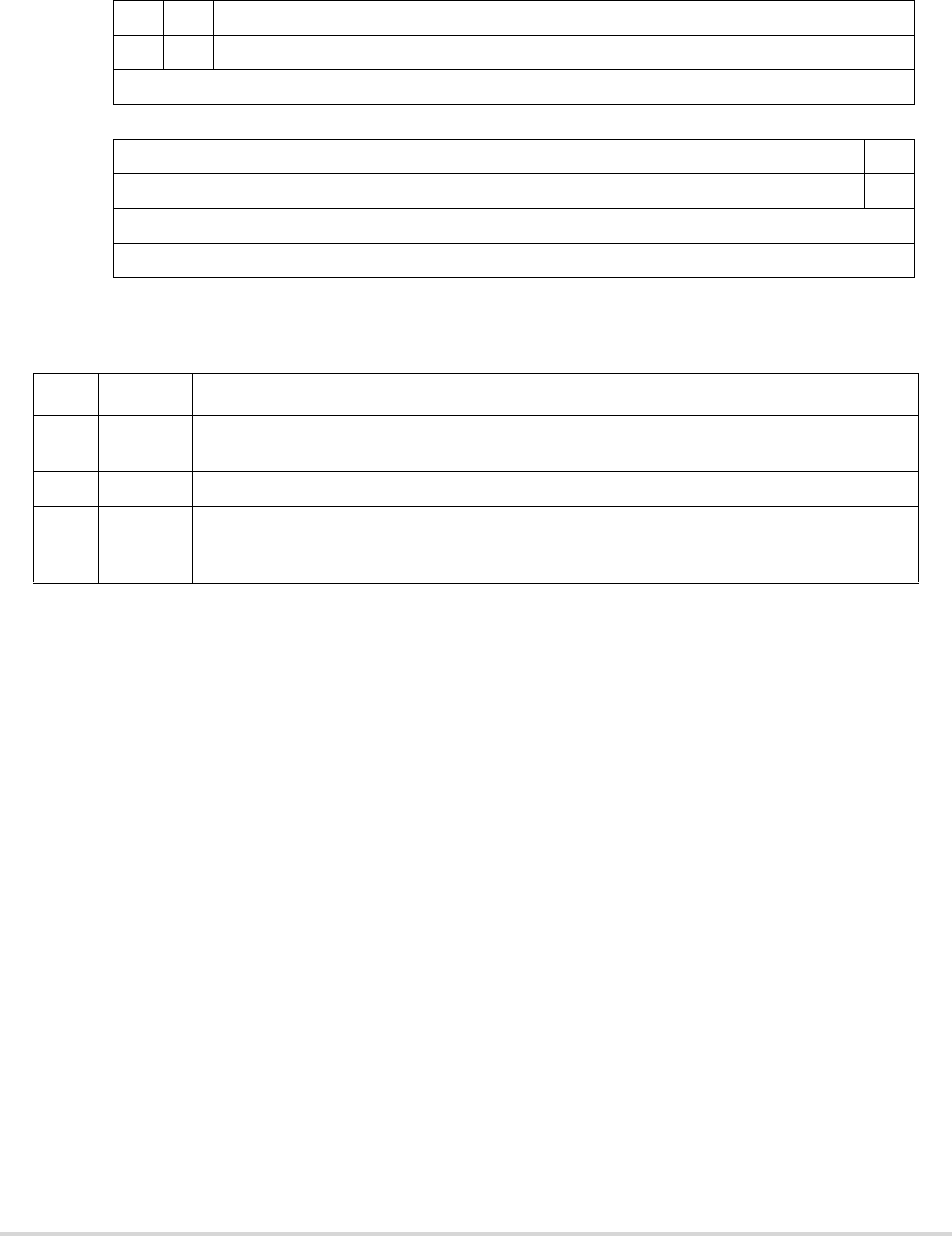

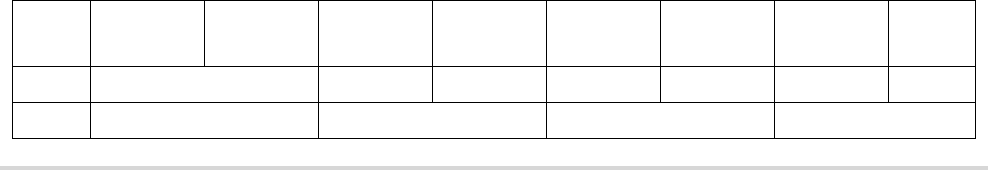

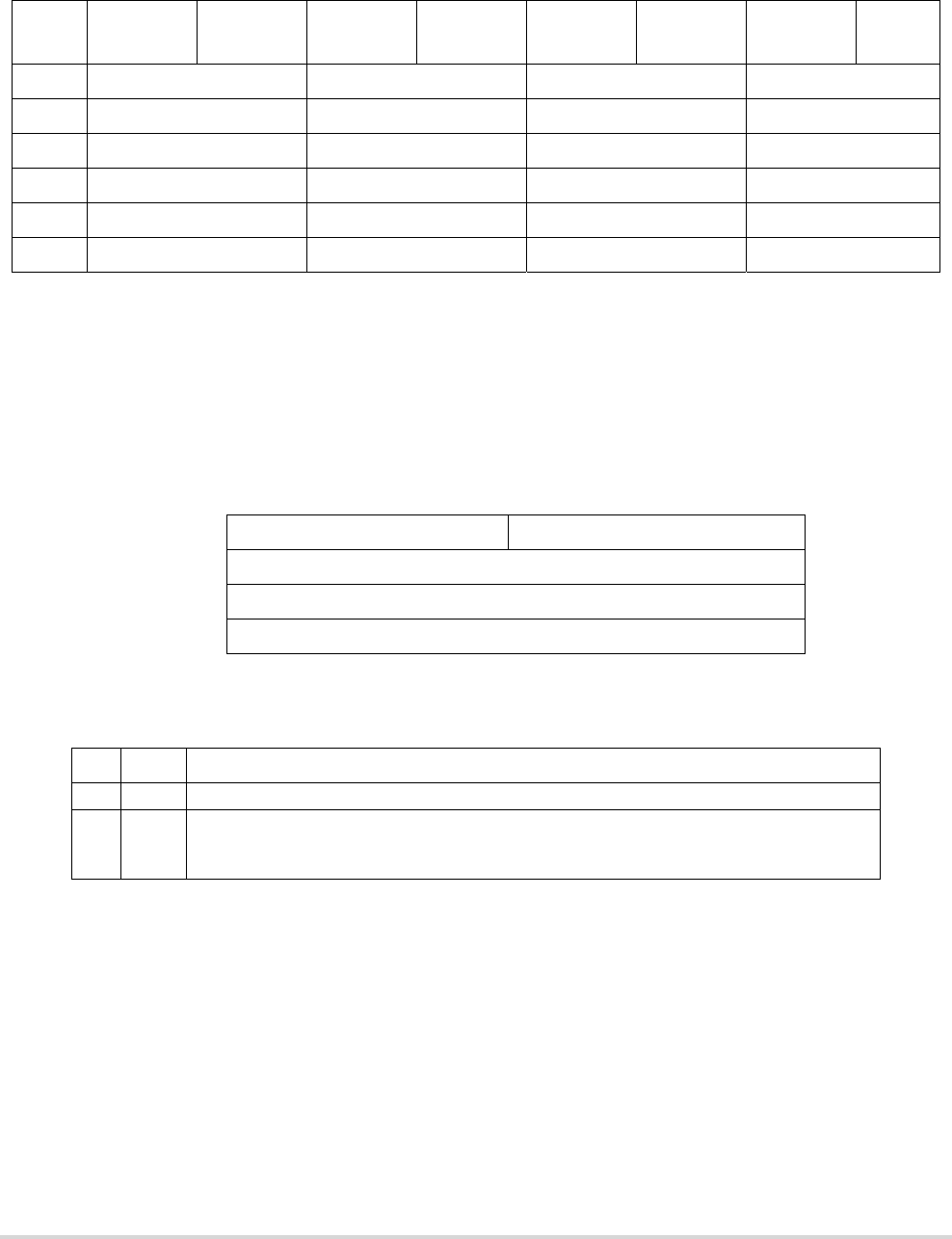

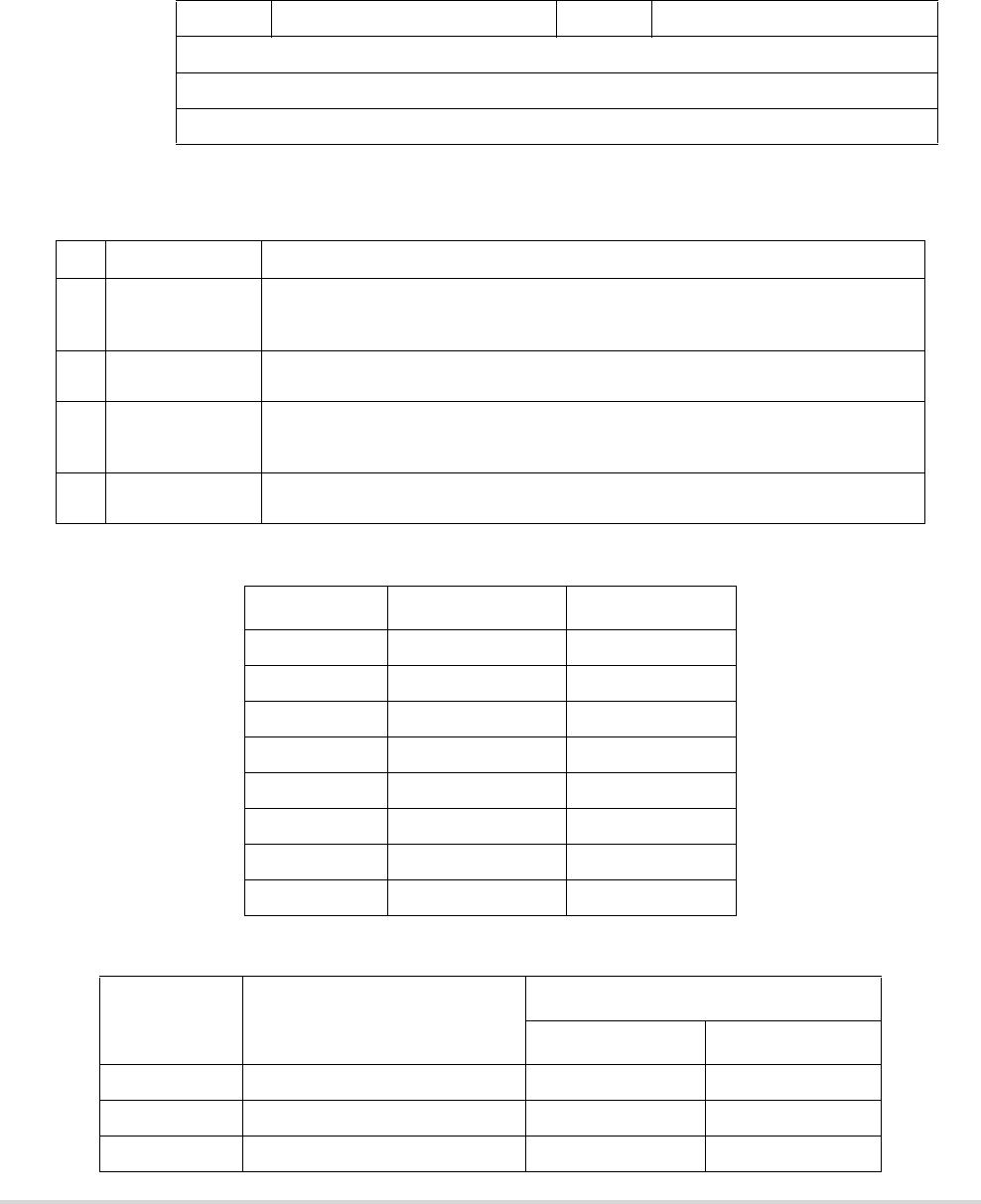

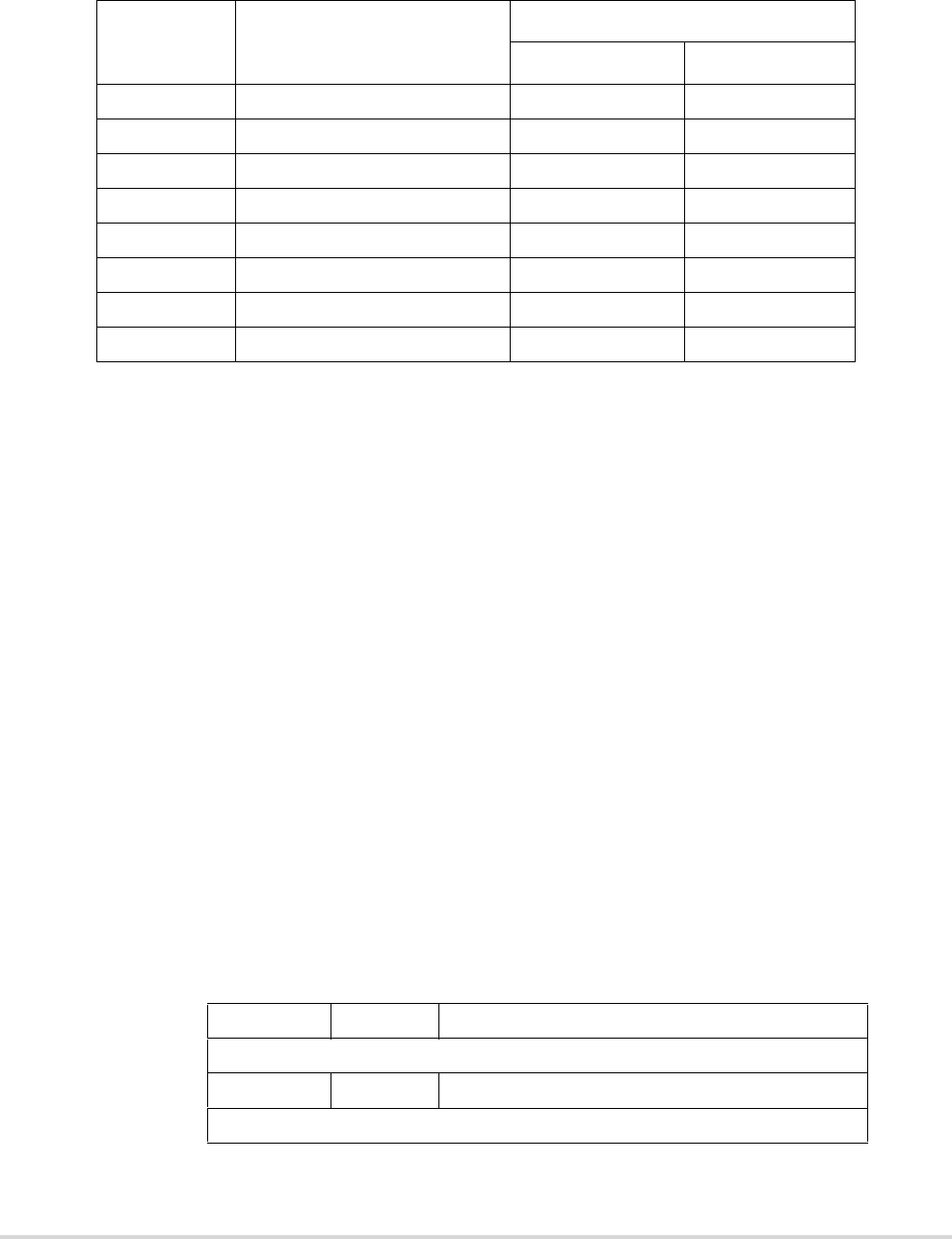

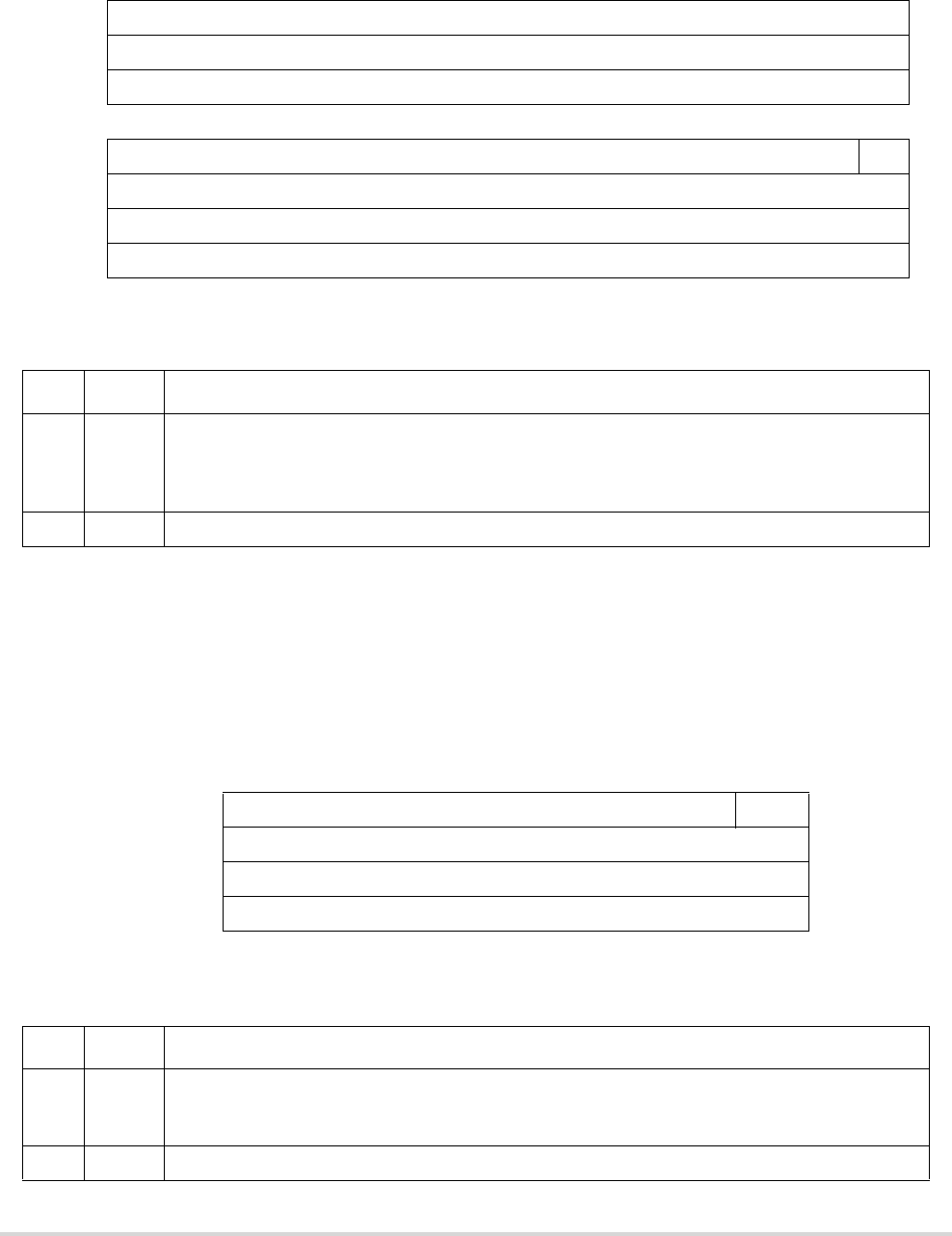

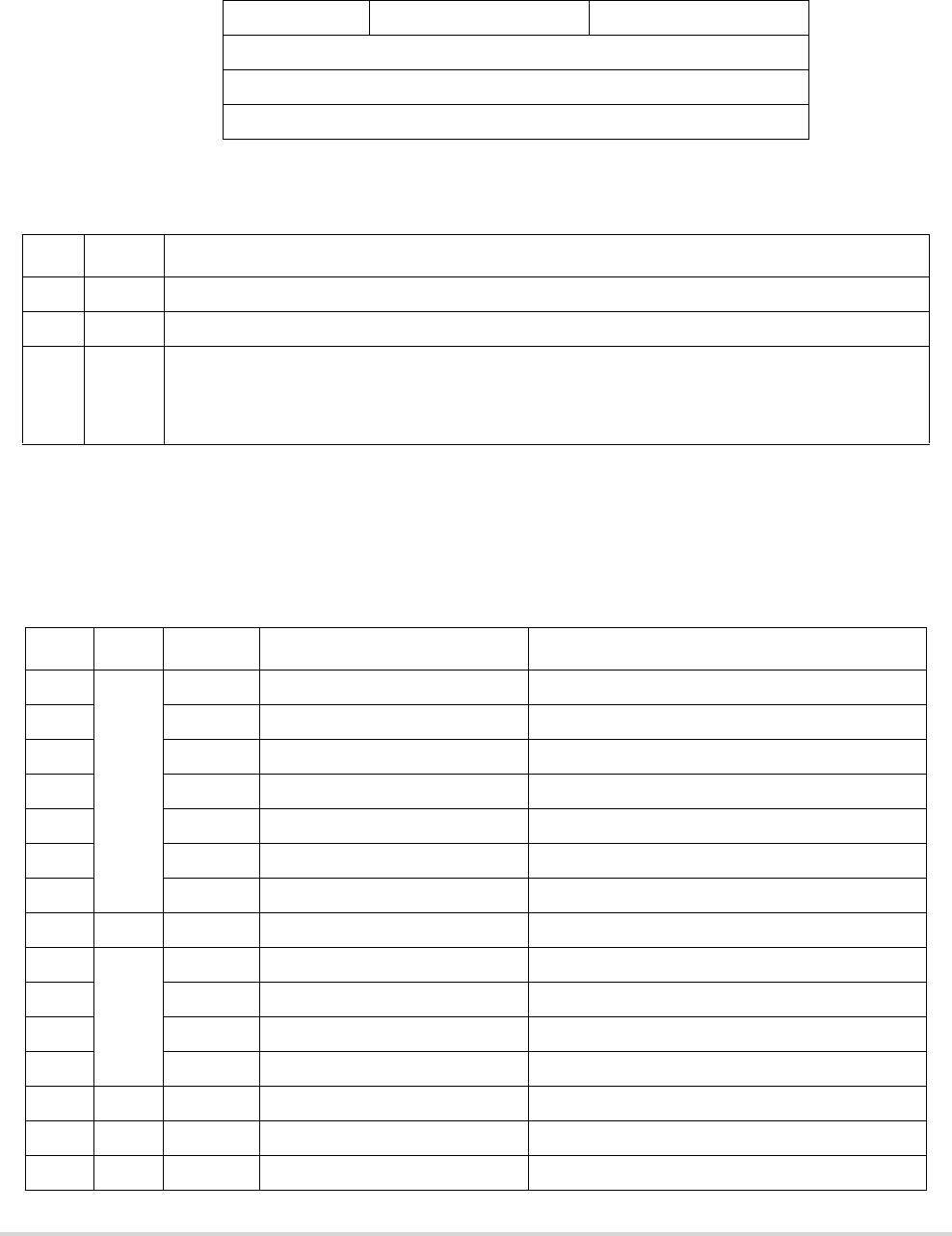

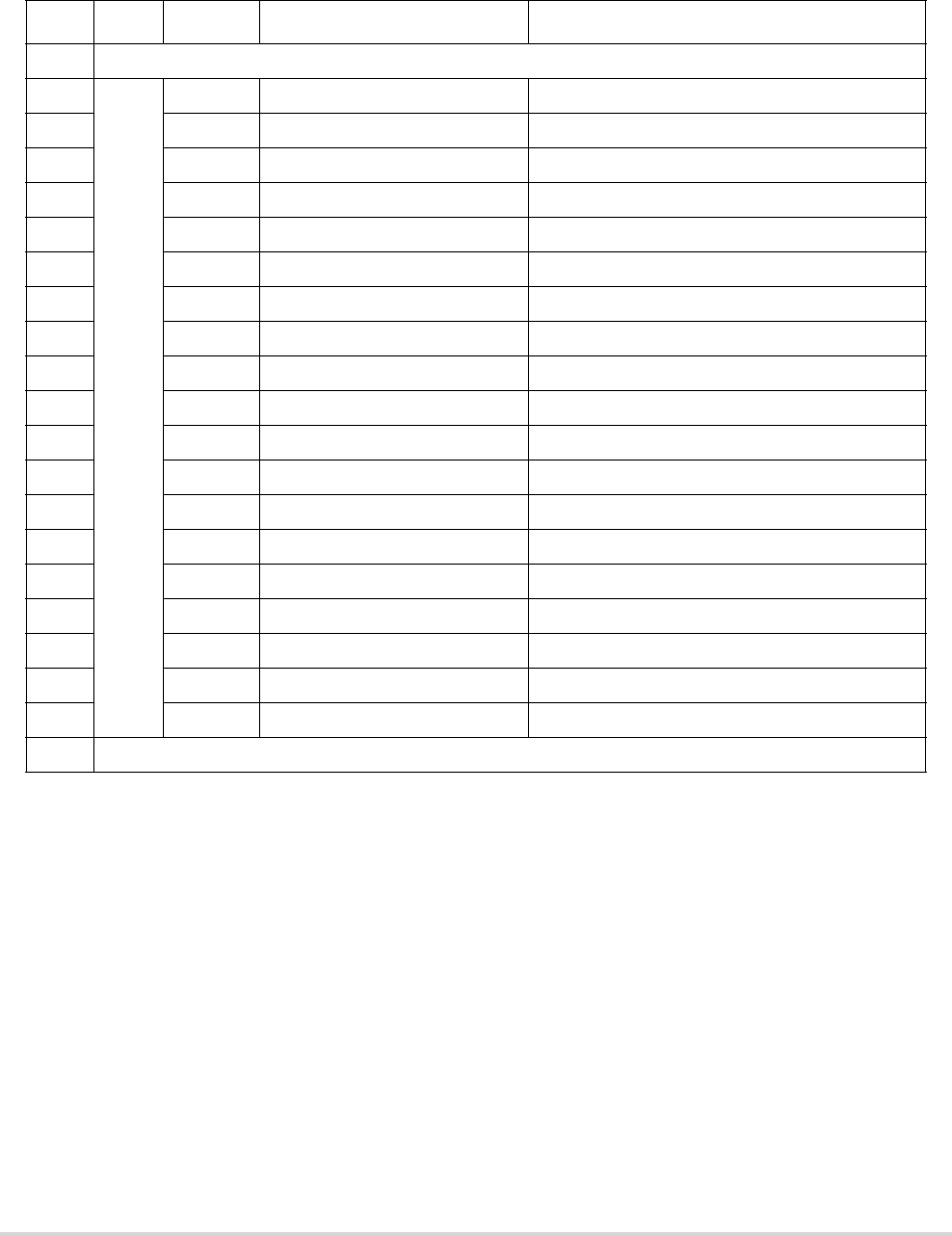

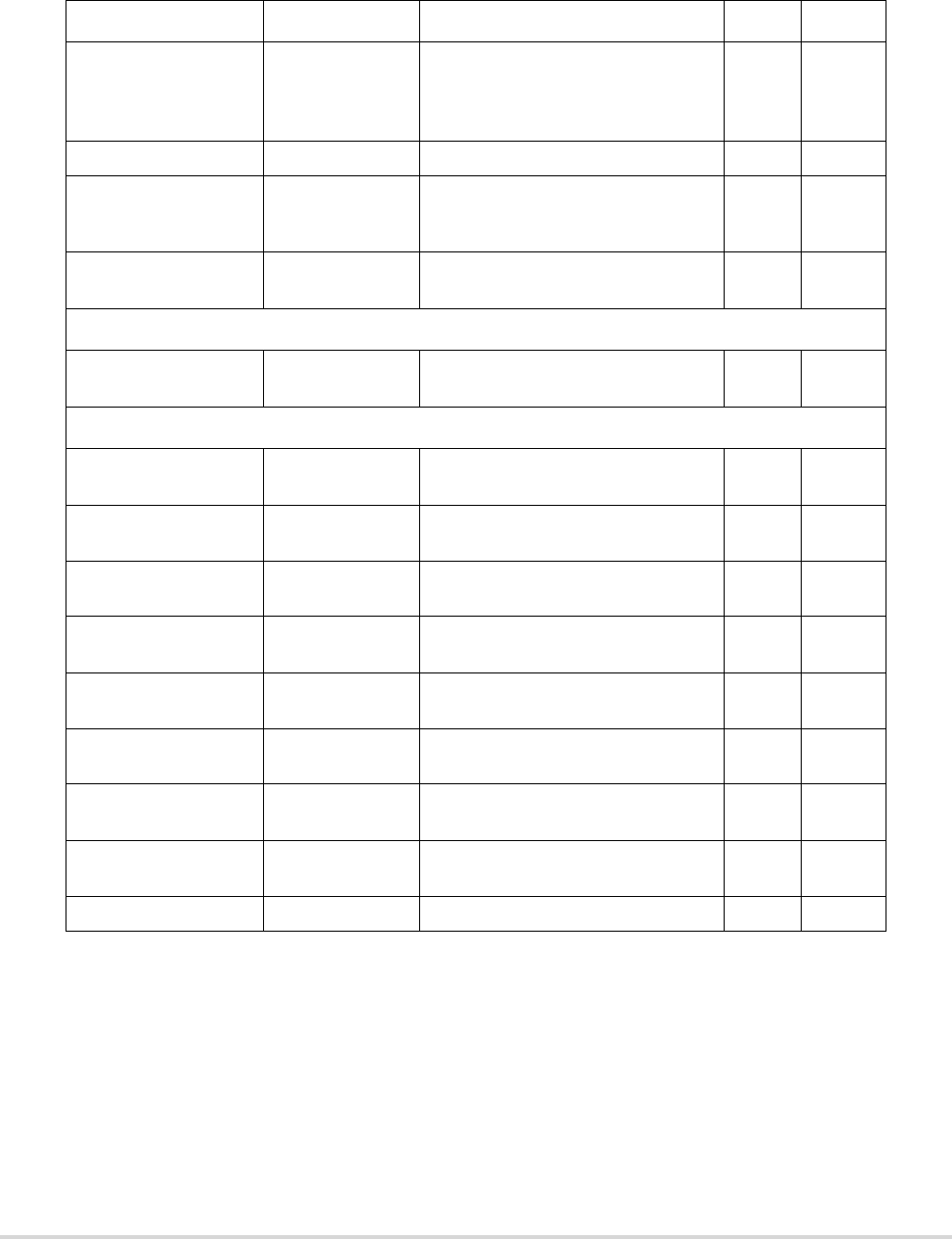

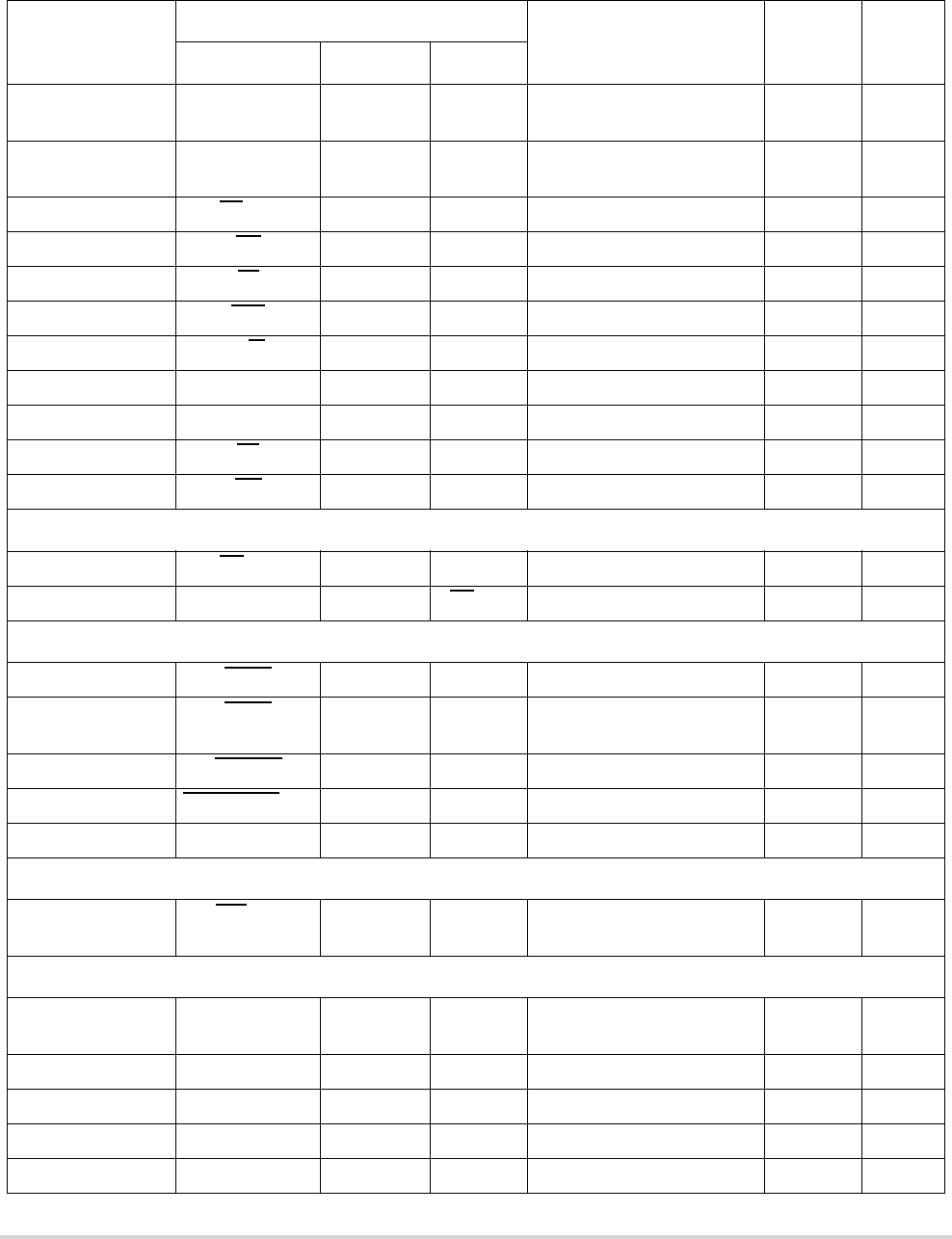

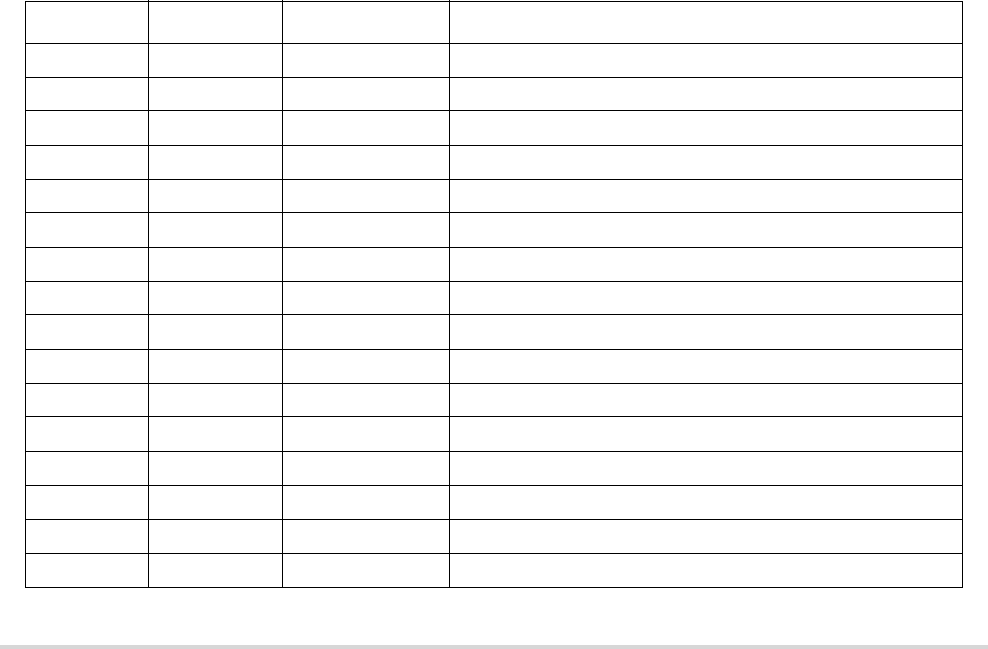

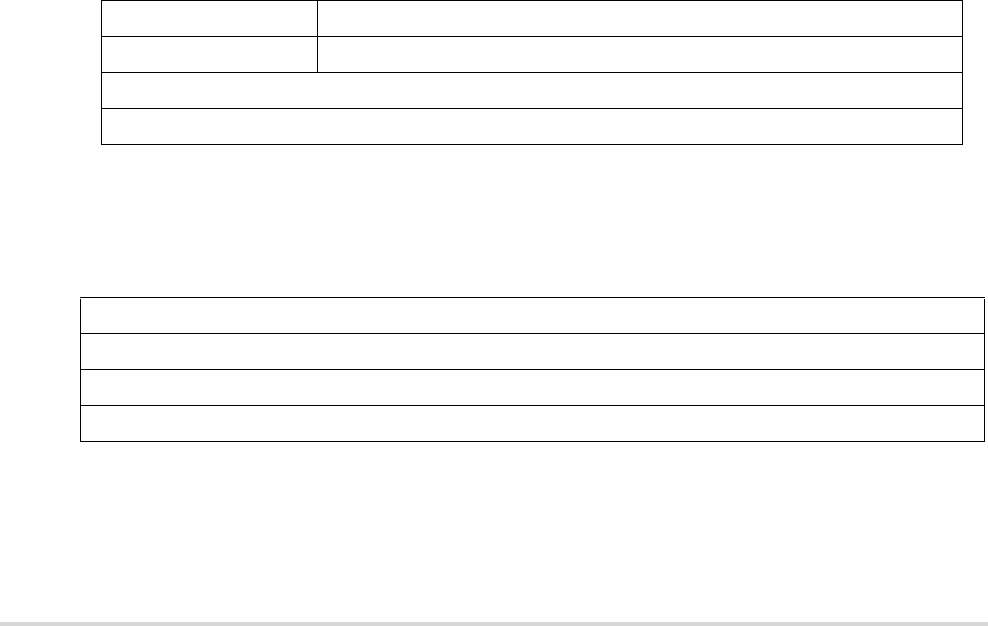

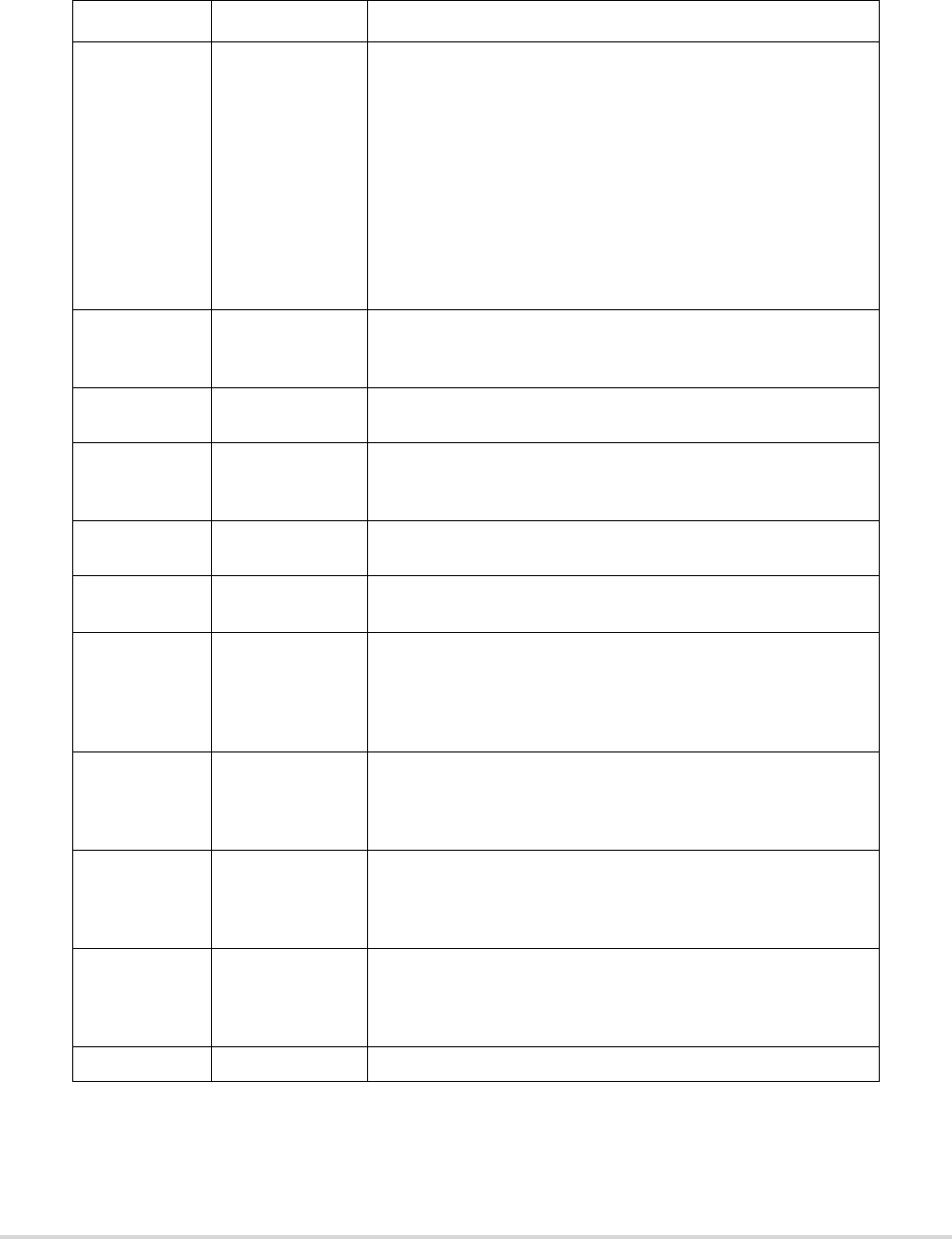

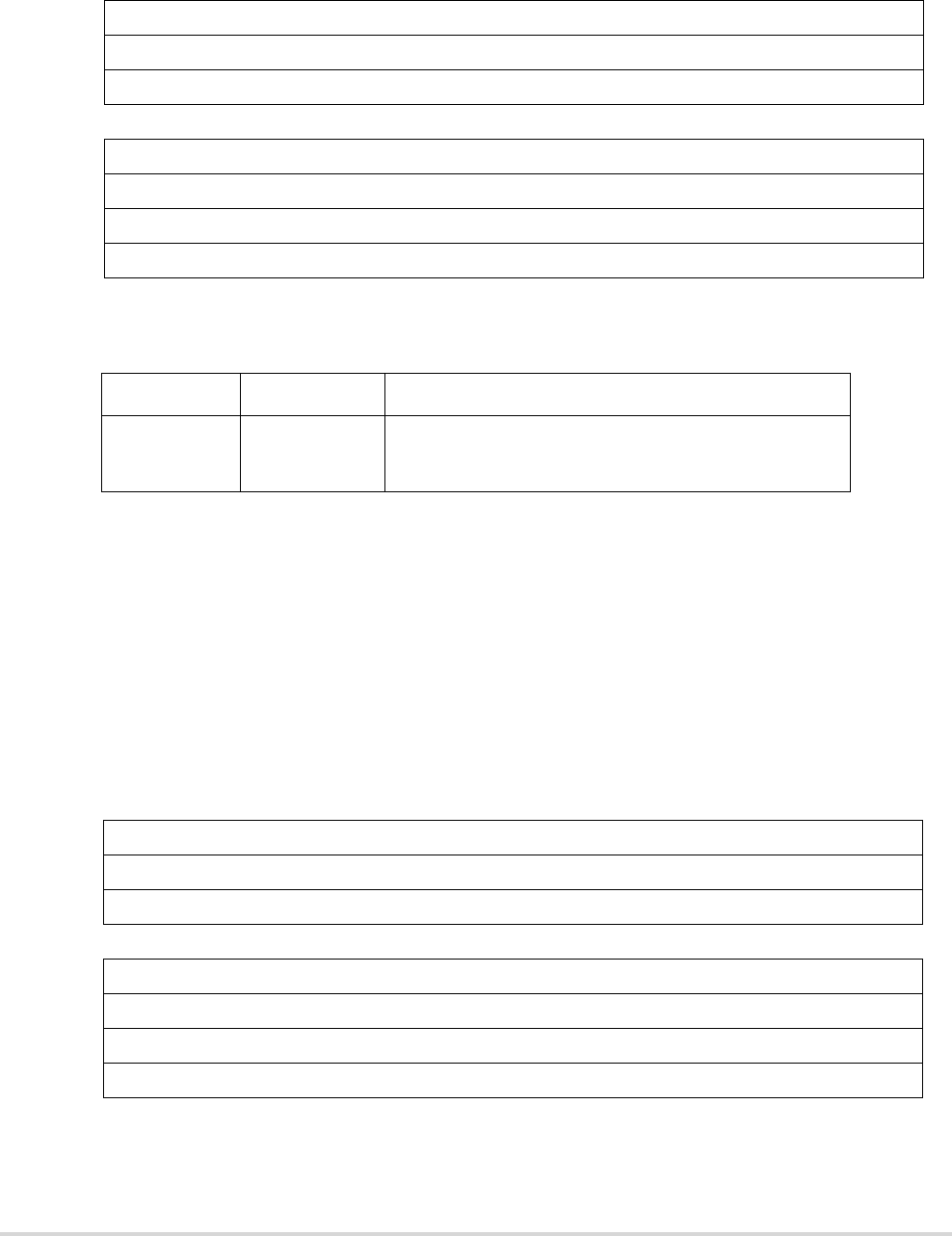

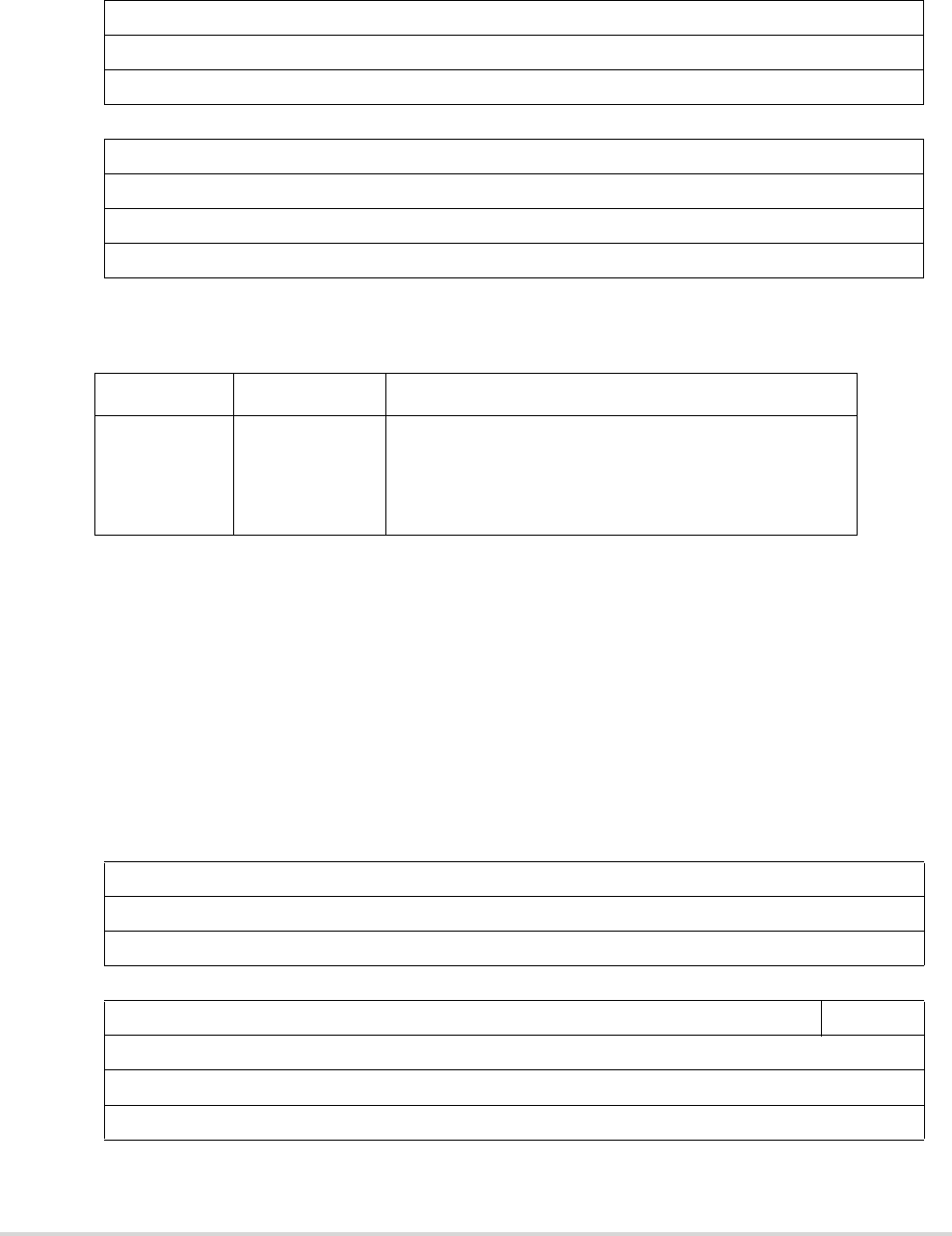

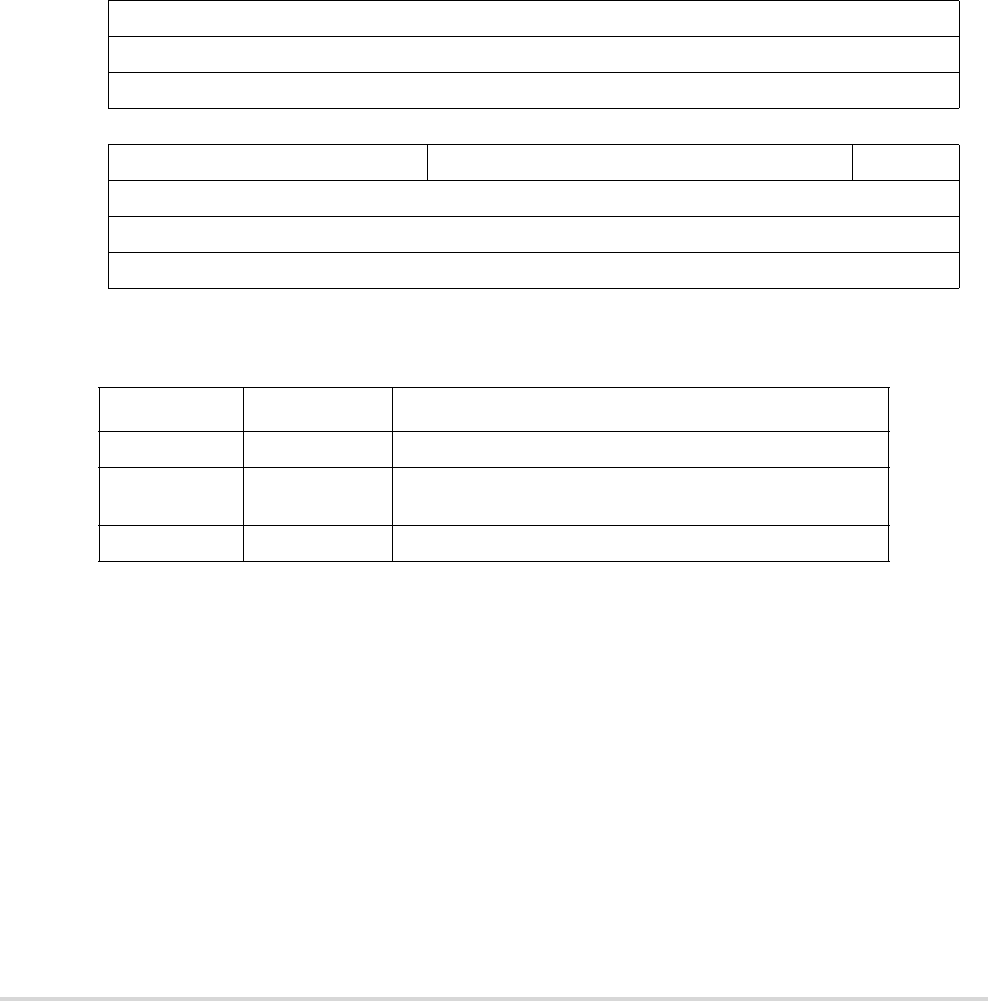

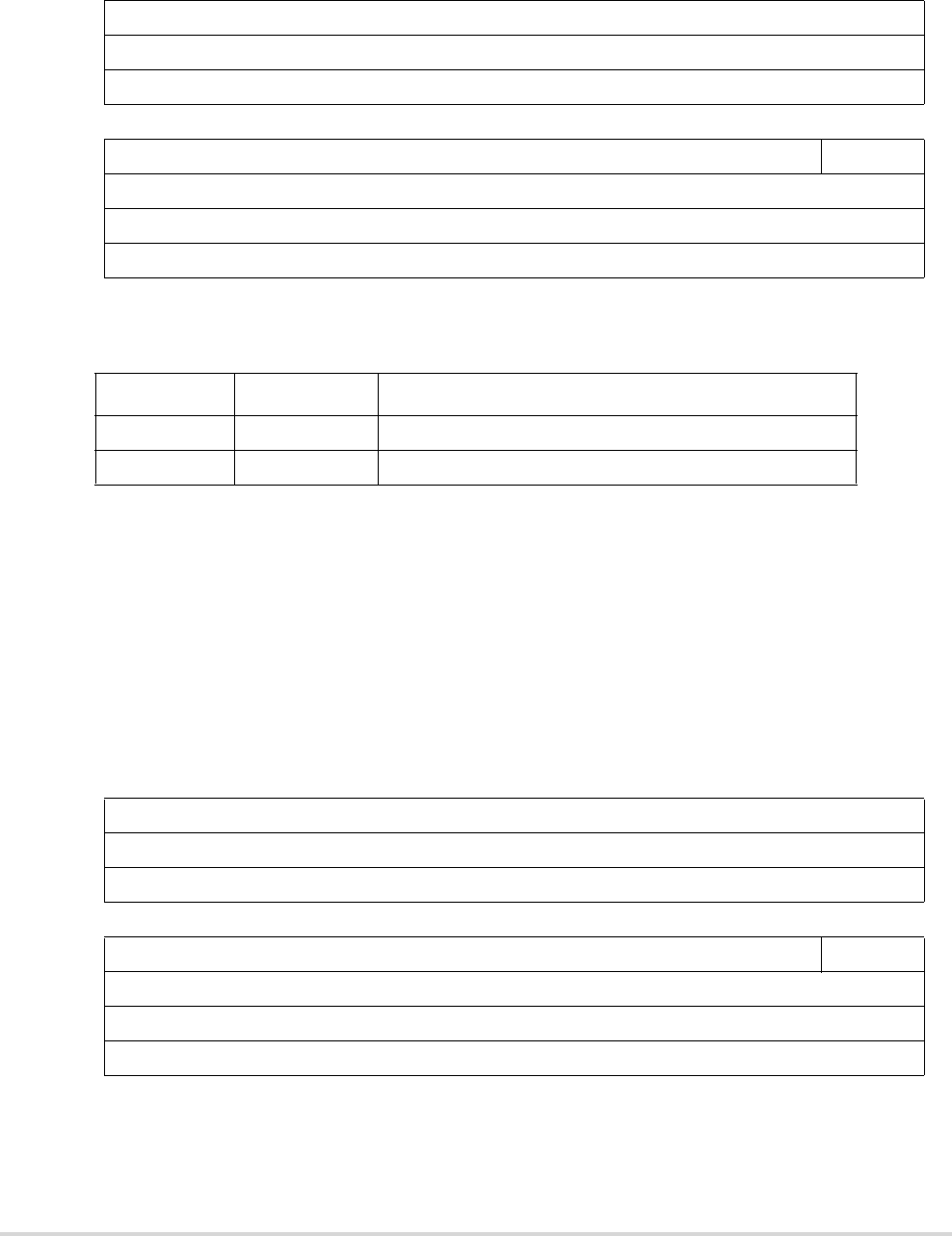

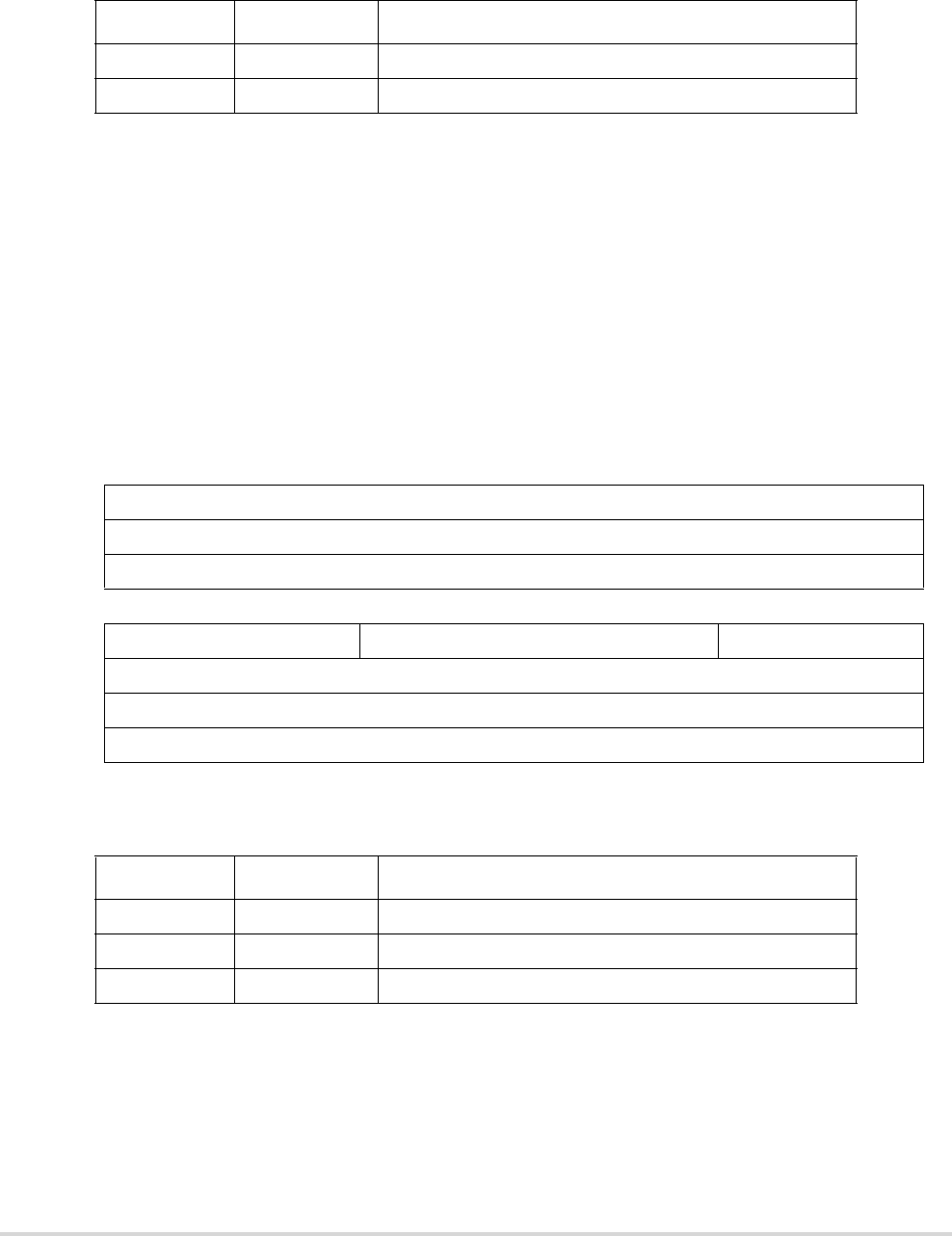

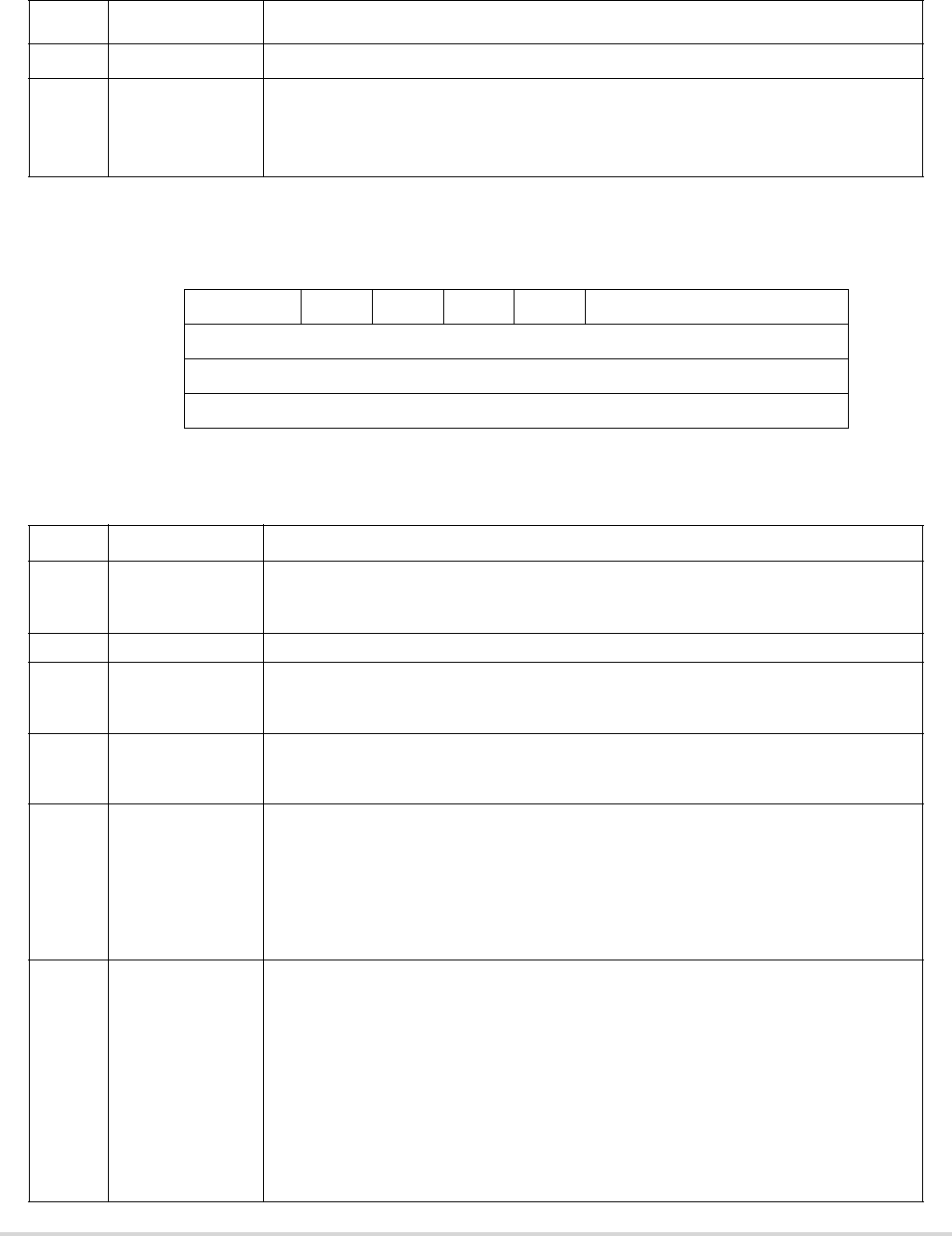

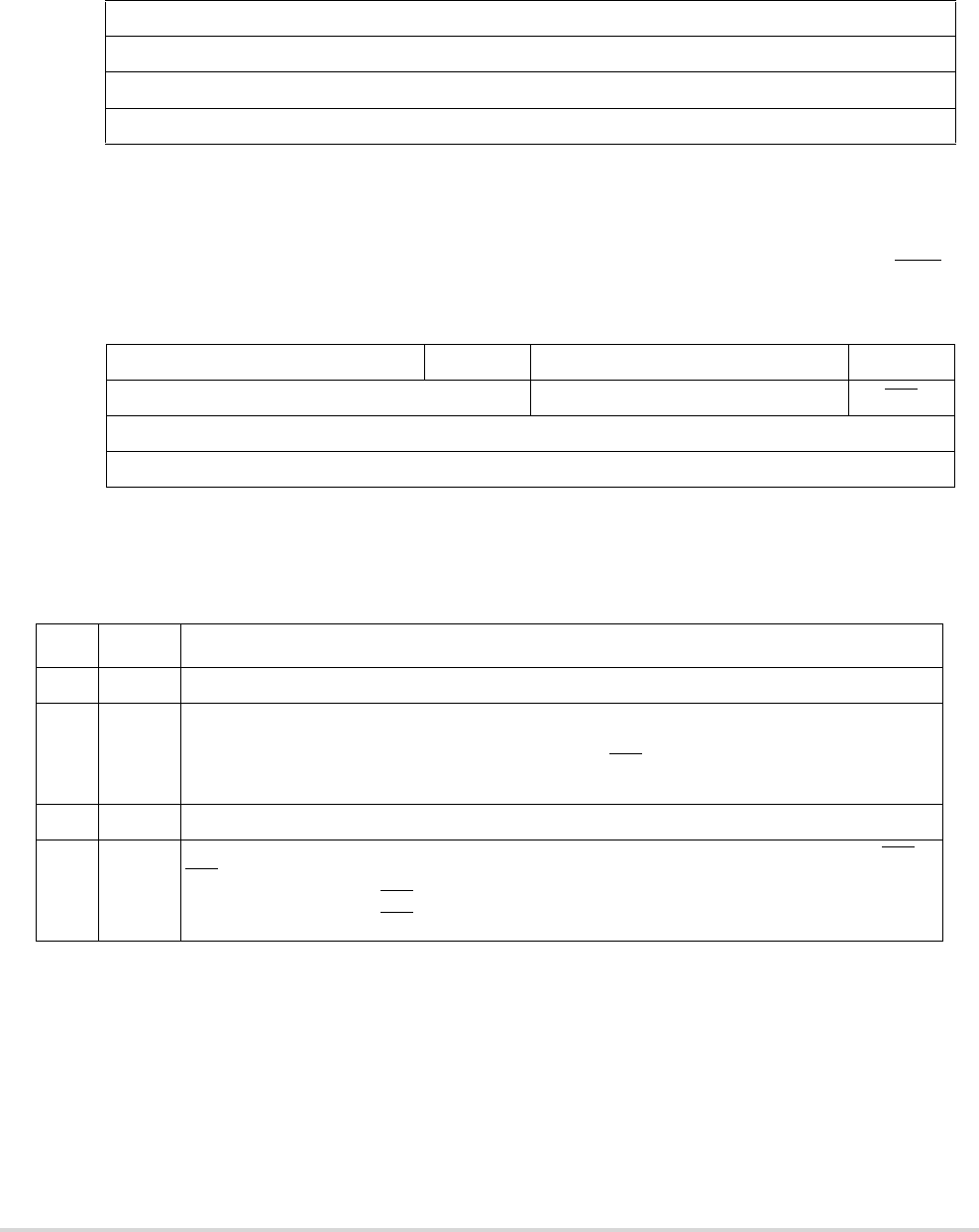

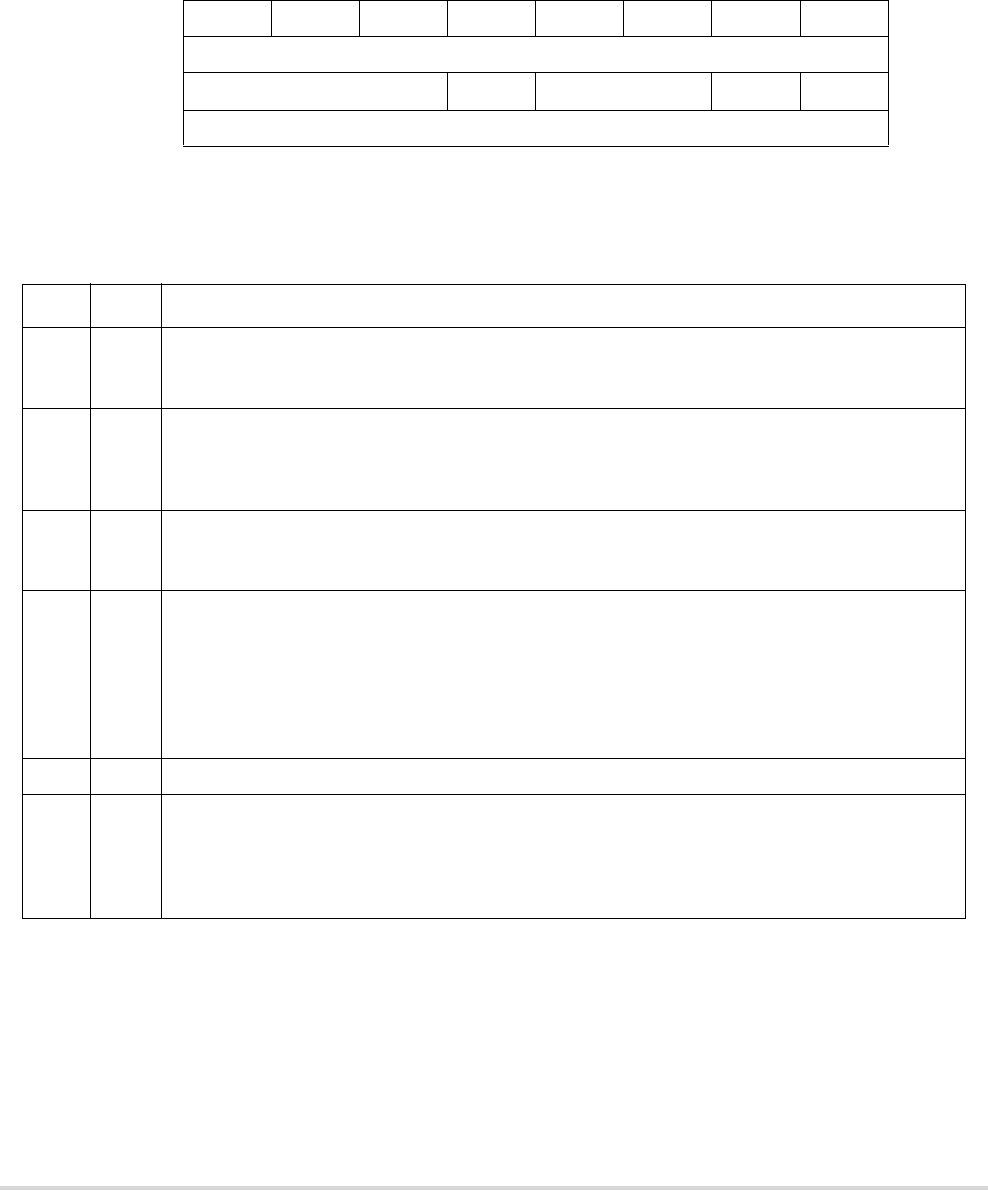

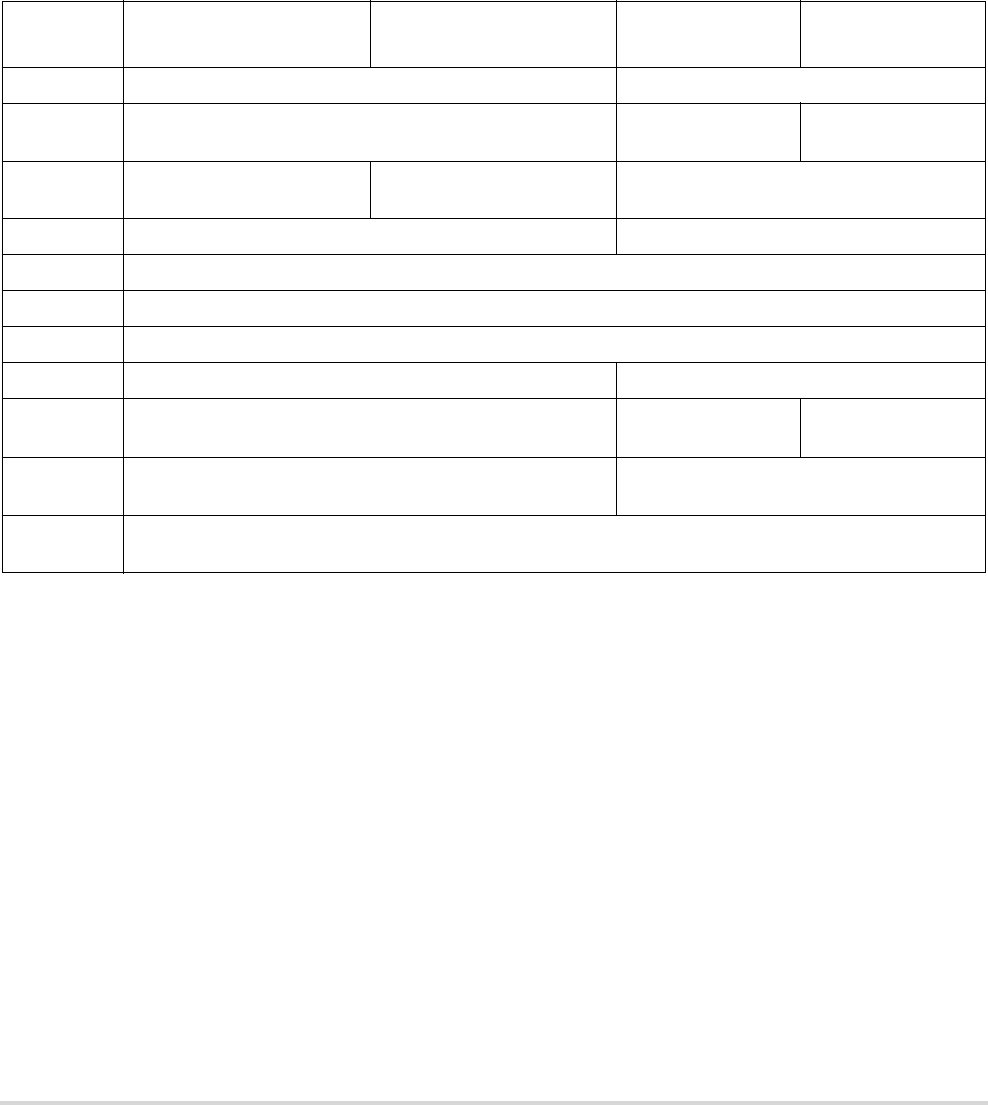

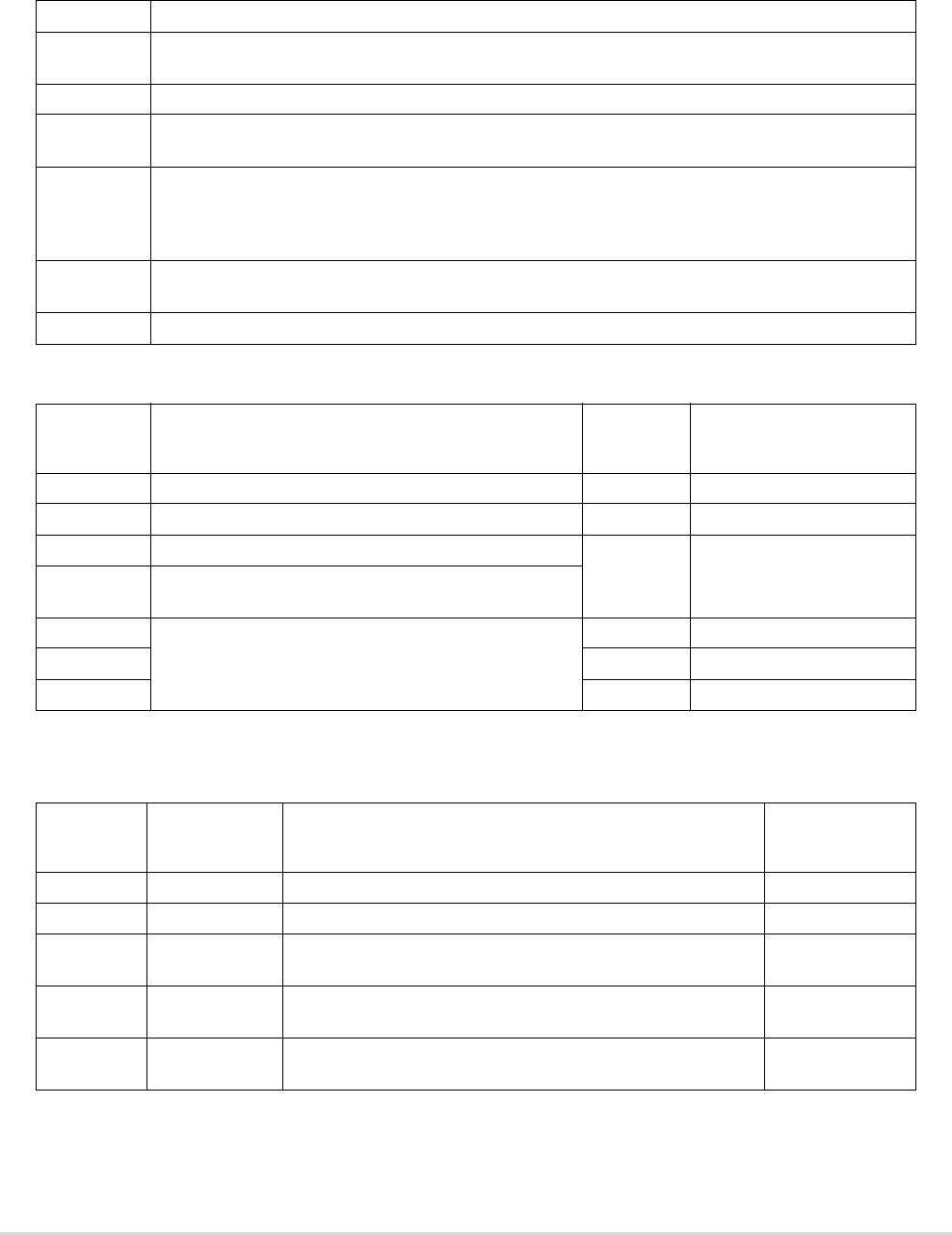

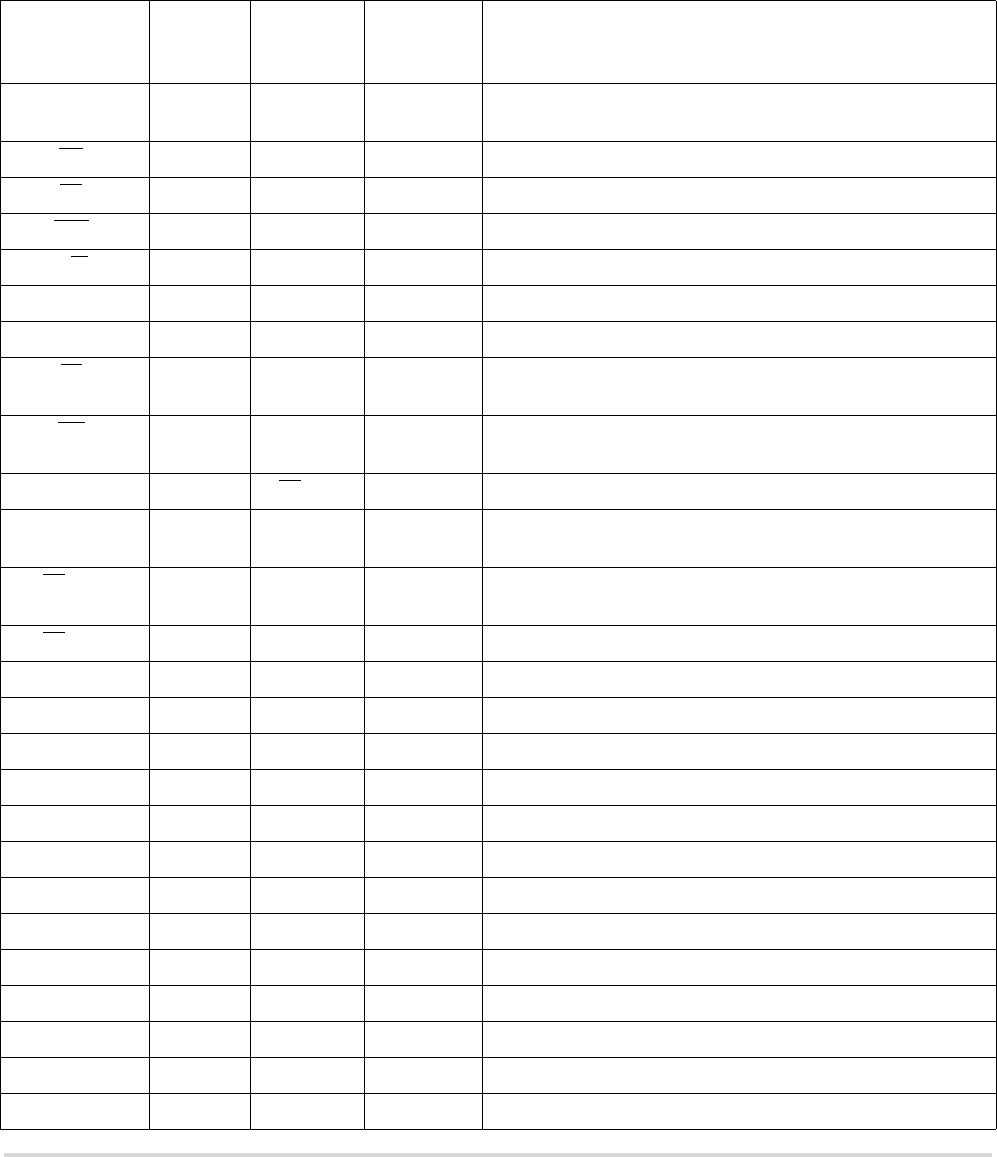

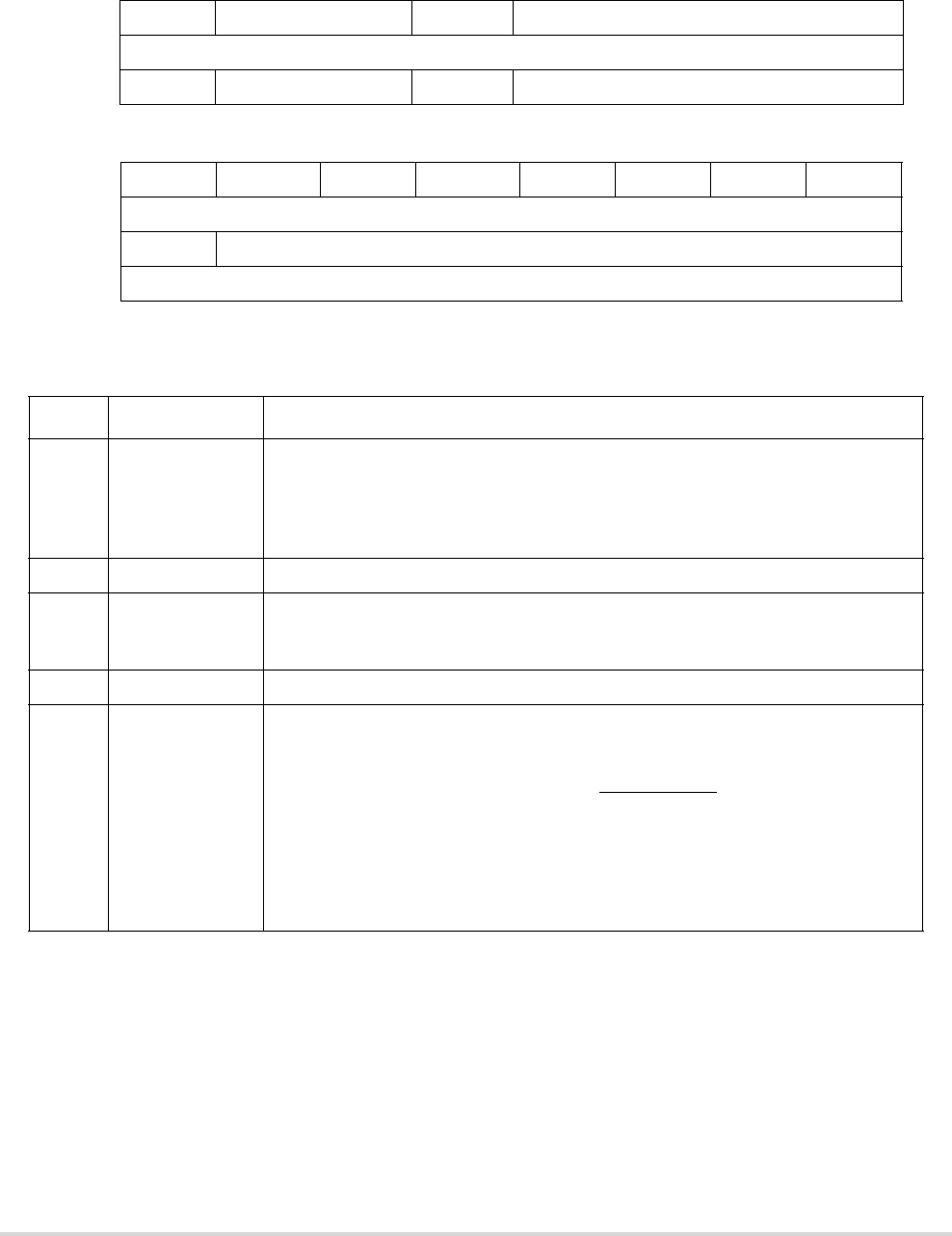

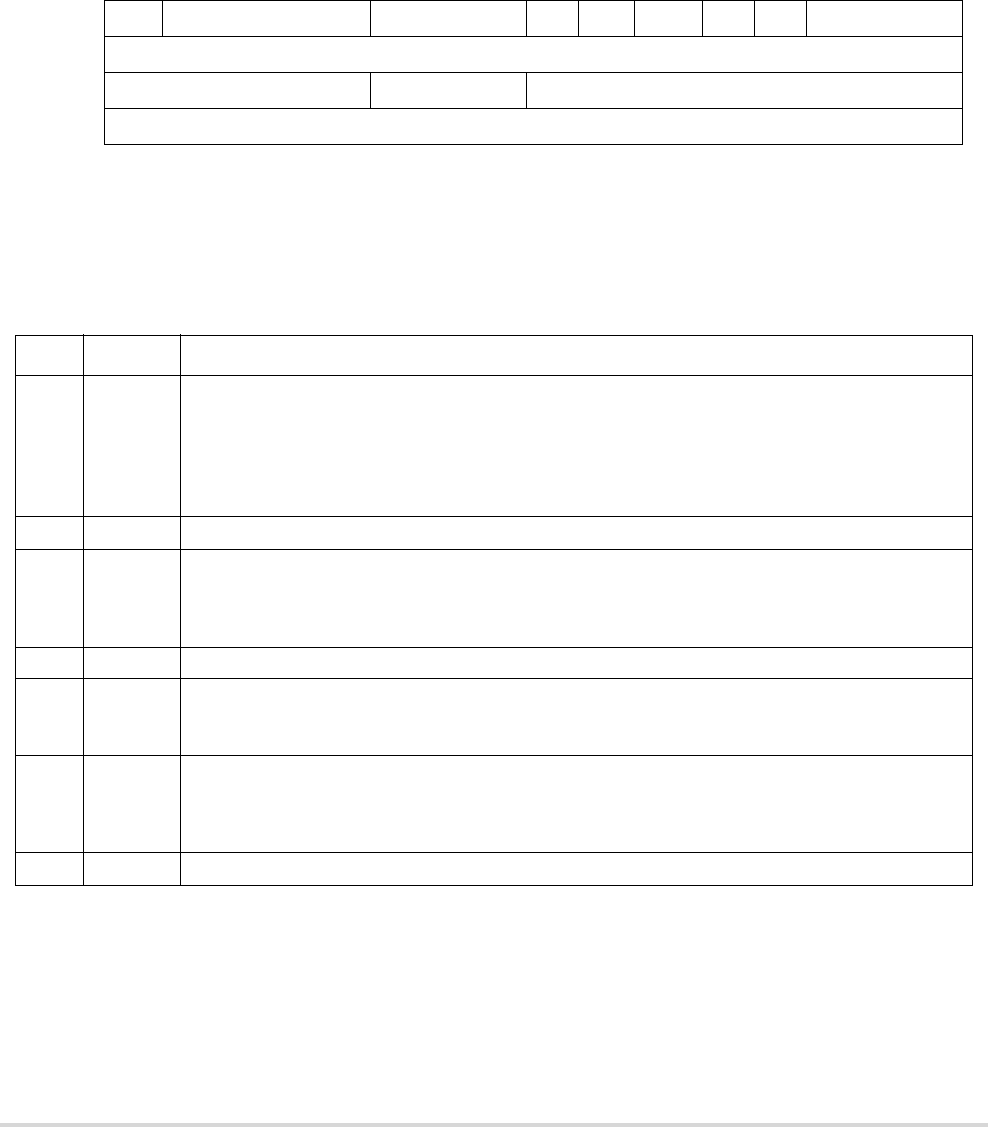

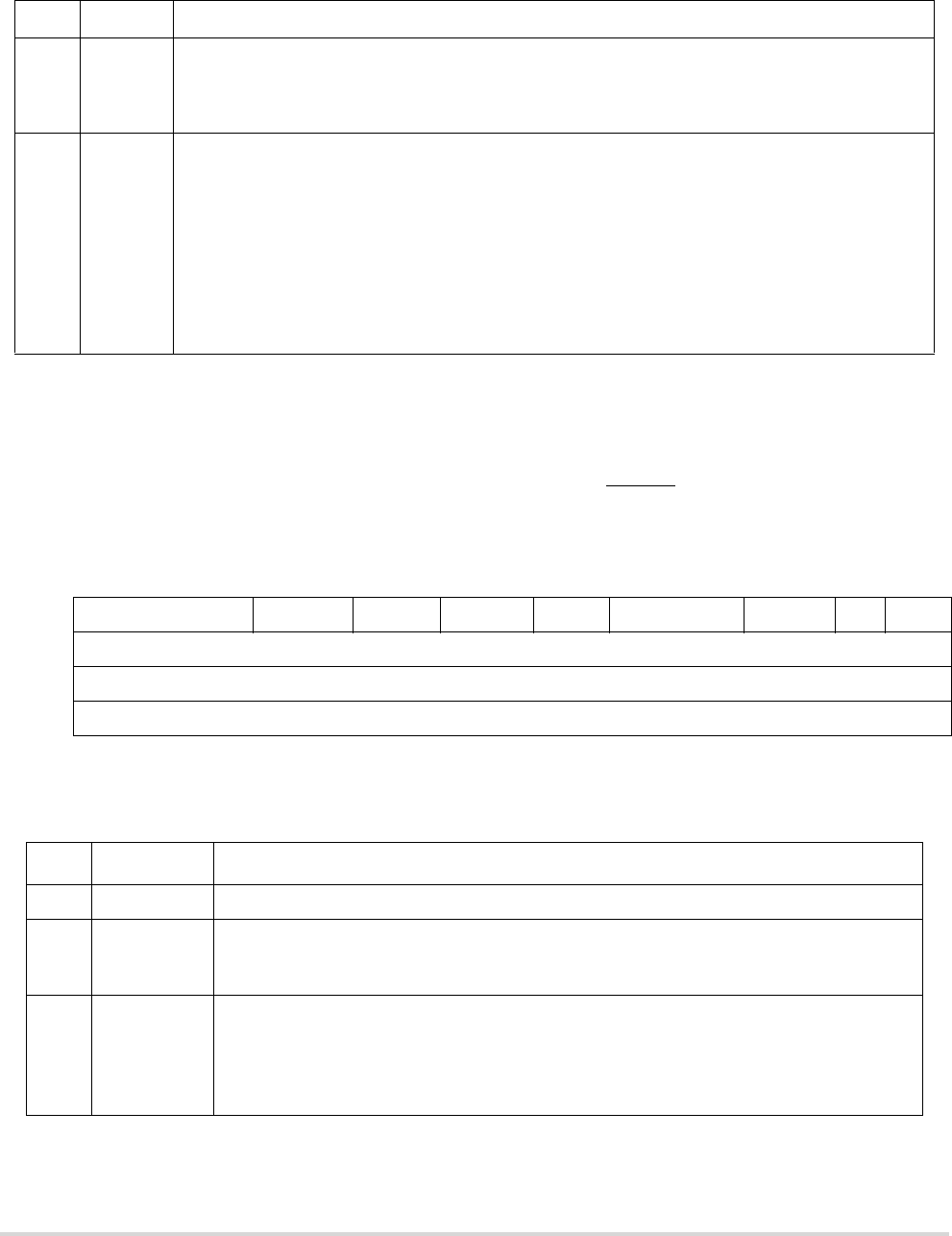

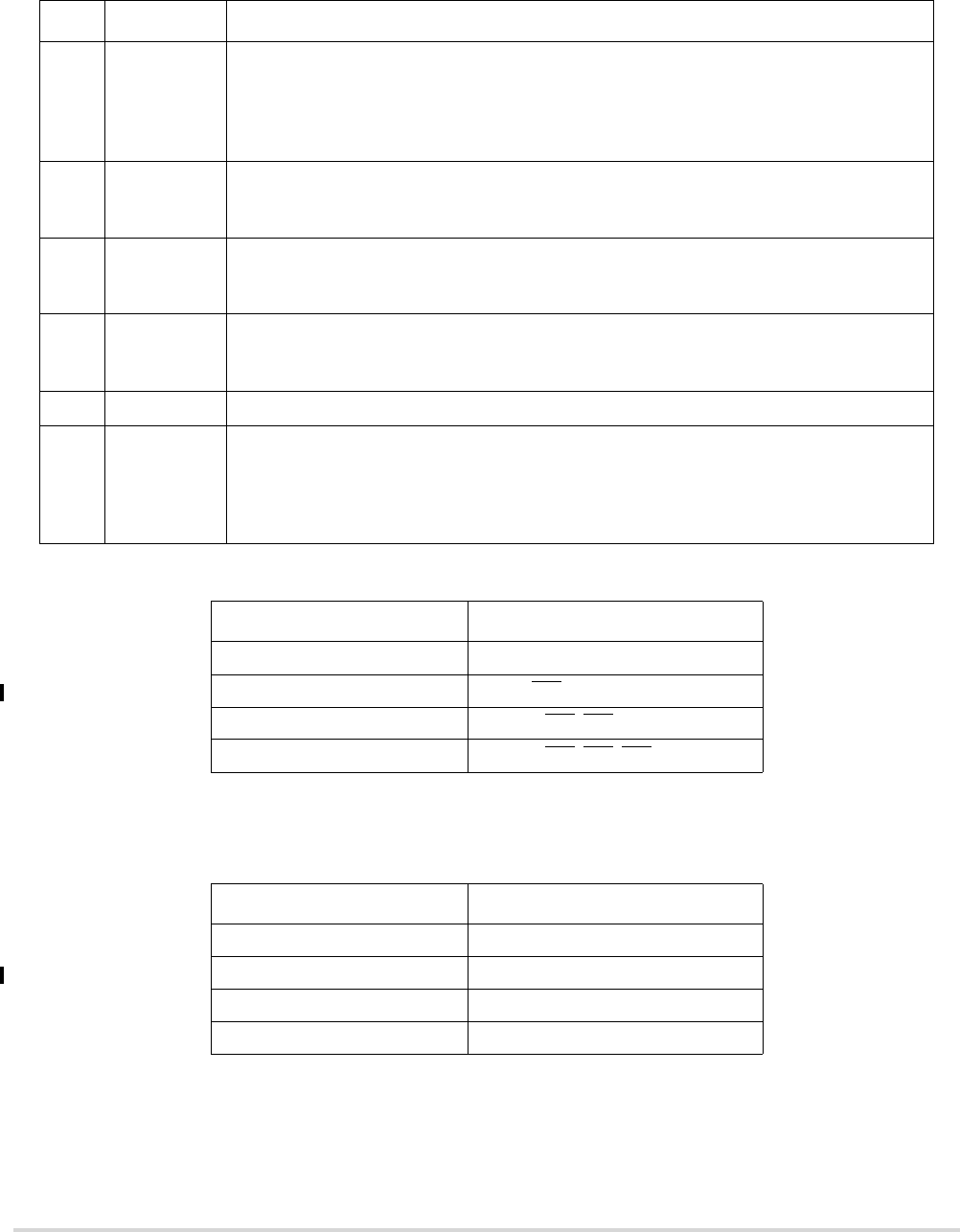

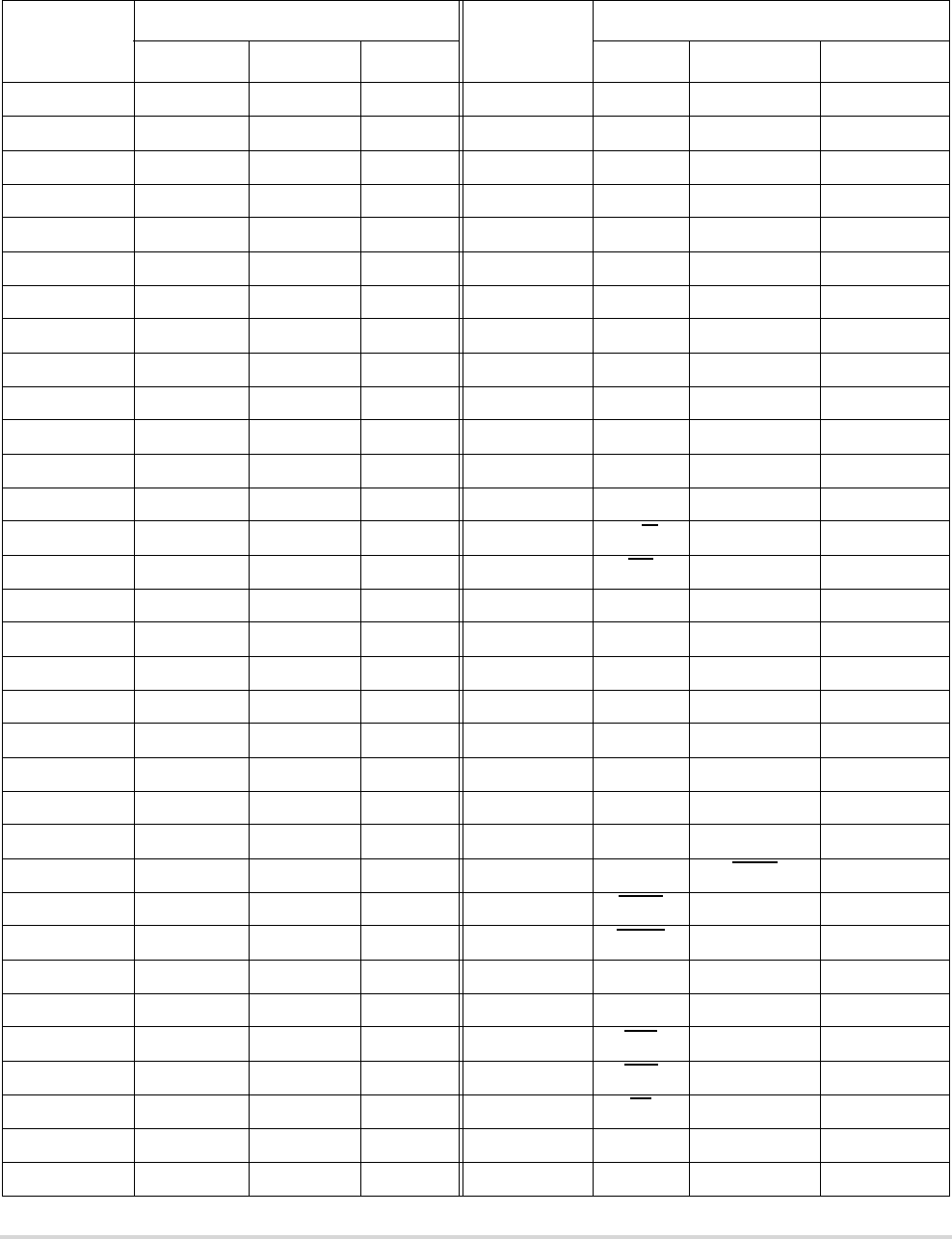

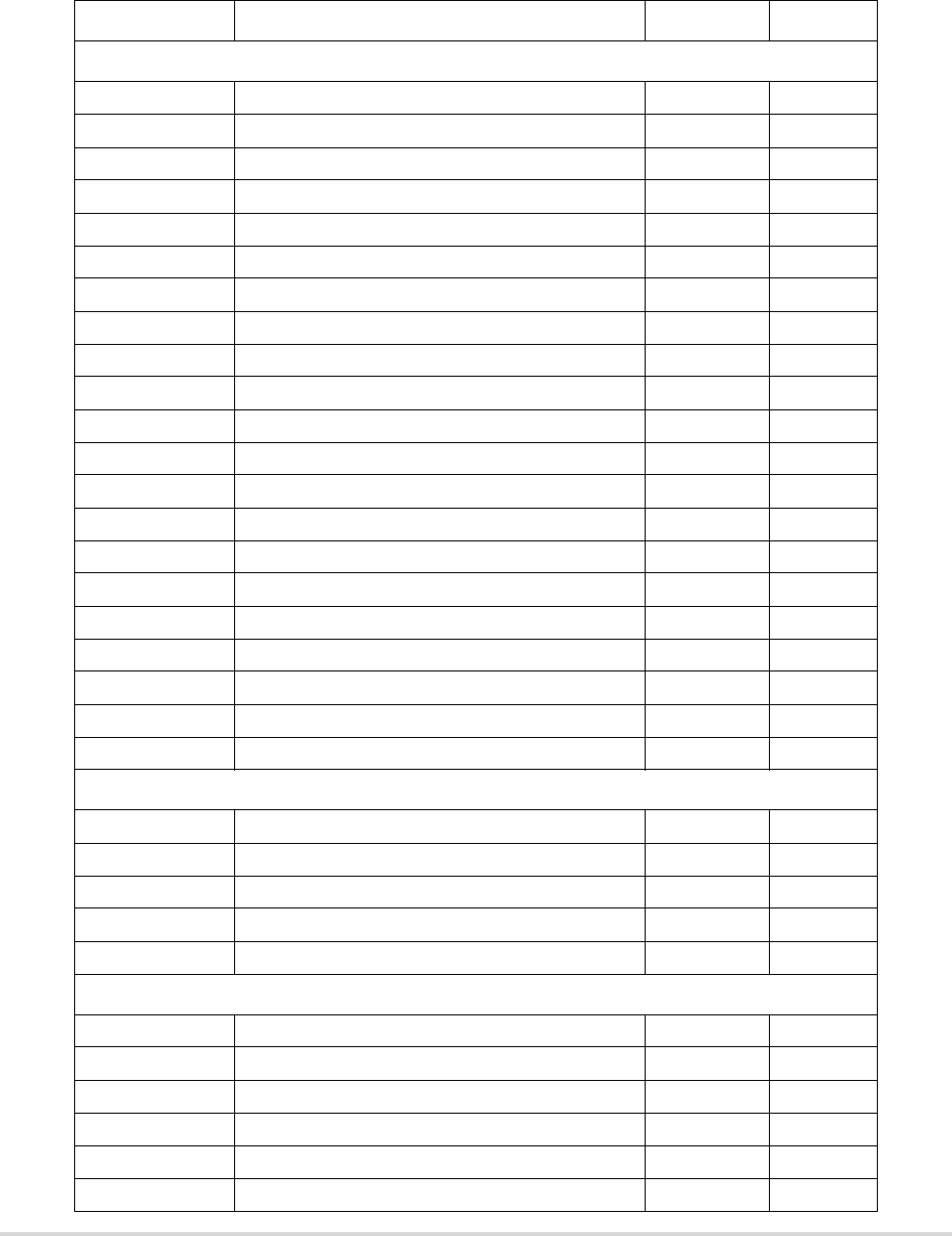

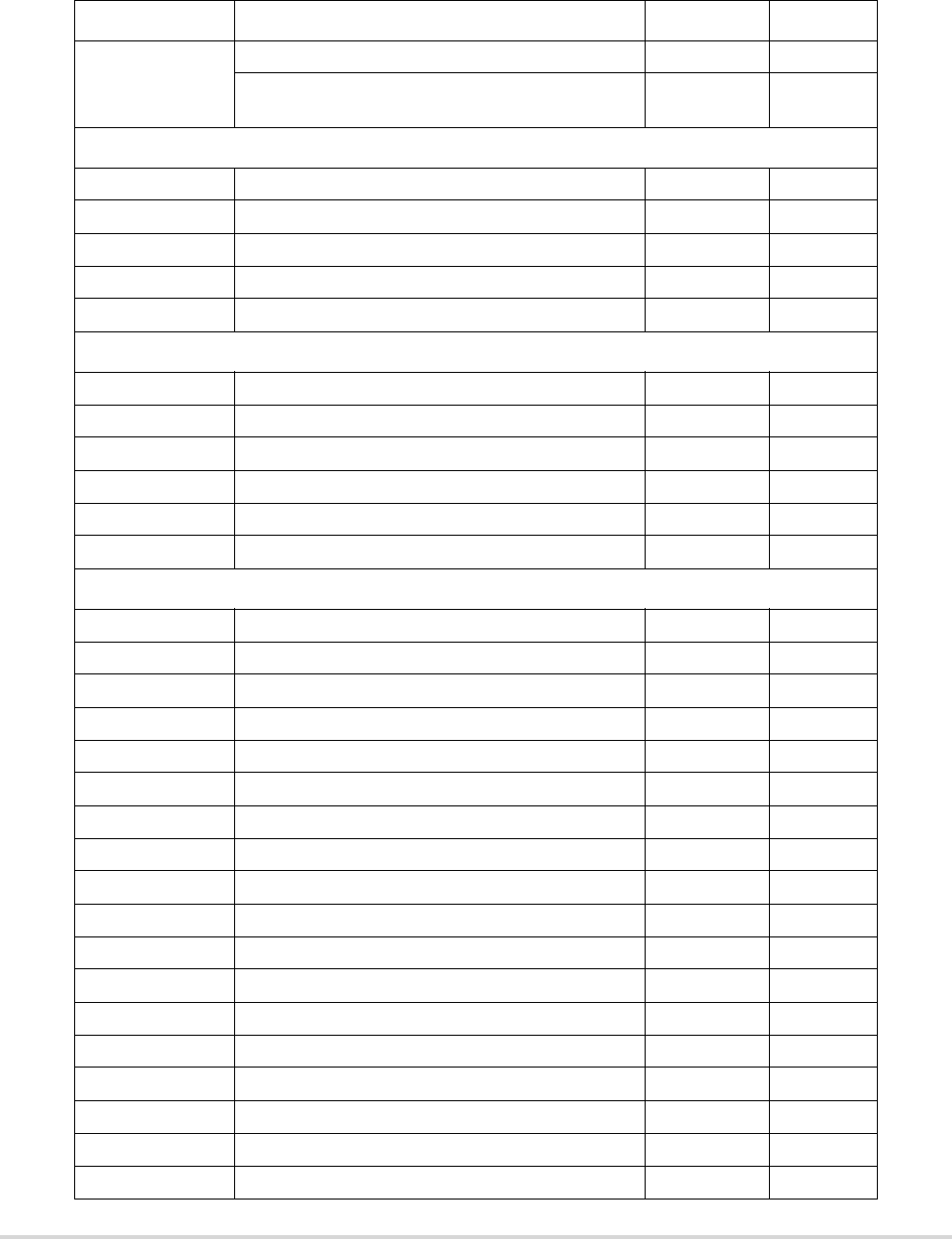

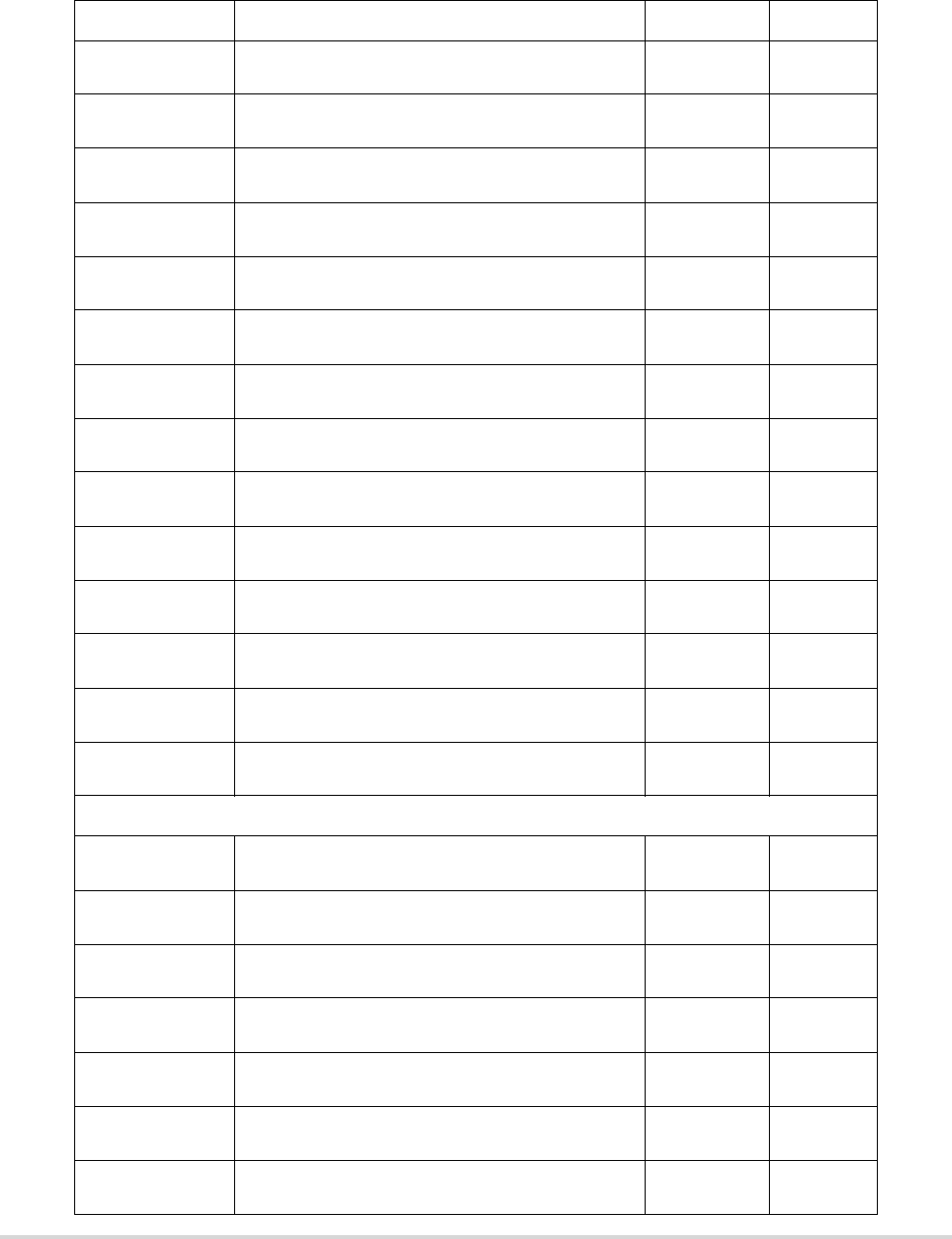

CONTENTS

Paragraph

Number Title Page

Number

MOTOROLA Contents v

Chapter 1

Overview

1.1 MCF5282 Key Features...................................................................................... 1-1

1.1.1 Version 2 ColdFire Core................................................................................. 1-8

1.1.2 System Control Module................................................................................ 1-10

1.1.3 External Interface Module (EIM) ................................................................. 1-10

1.1.4 Chip Select.................................................................................................... 1-11

1.1.5 Power Management ...................................................................................... 1-11

1.1.6 General Input/Output Ports........................................................................... 1-11

1.1.7 Interrupt Controllers (INTC0/INTC1).......................................................... 1-11

1.1.8 SDRAM Controller....................................................................................... 1-11

1.1.9 Test Access Port............................................................................................ 1-12

1.1.10 UART Modules............................................................................................. 1-12

1.1.11 DMA Timers (DTIM0-DTIM3) ................................................................... 1-13

1.1.12 General-Purpose Timers (GPTA/GPTB)...................................................... 1-13

1.1.13 Periodic Interrupt Timers (PIT0-PIT3)......................................................... 1-13

1.1.14 Software Watchdog Timer............................................................................ 1-14

1.1.15 Phase Locked Loop (PLL)............................................................................ 1-14

1.1.16 DMA Controller............................................................................................ 1-14

1.1.17 Reset.............................................................................................................. 1-14

1.2 MCF5282-Specific Features ............................................................................. 1-15

1.2.1 Fast Ethernet Controller (FEC)..................................................................... 1-15

1.2.2 FlexCAN....................................................................................................... 1-15

1.2.3 I2C Bus.......................................................................................................... 1-15

1.2.4 Queued Serial Peripheral Interface (QSPI)................................................... 1-15

1.2.5 Queued Analog-to-Digital Converter (QADC) ............................................ 1-15

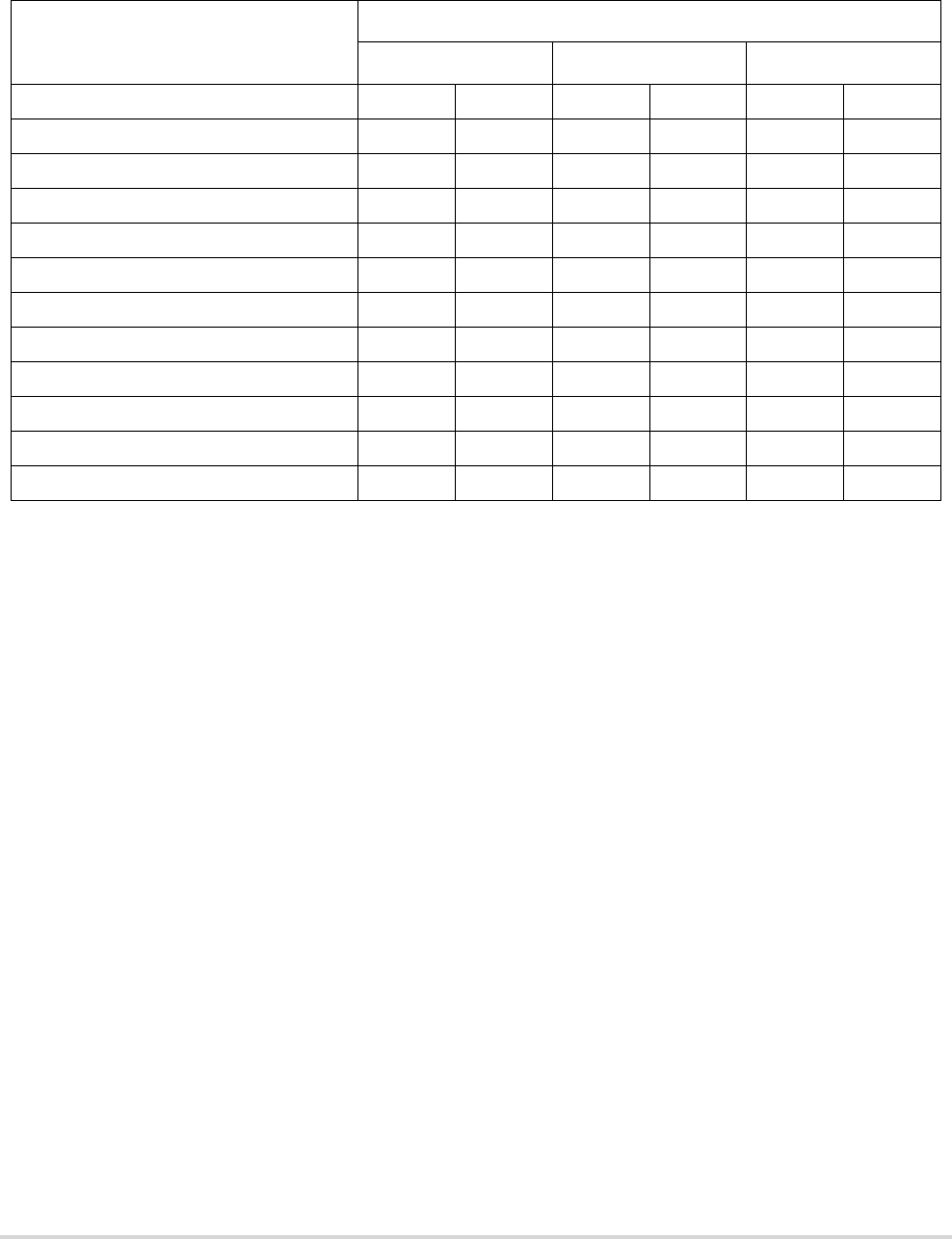

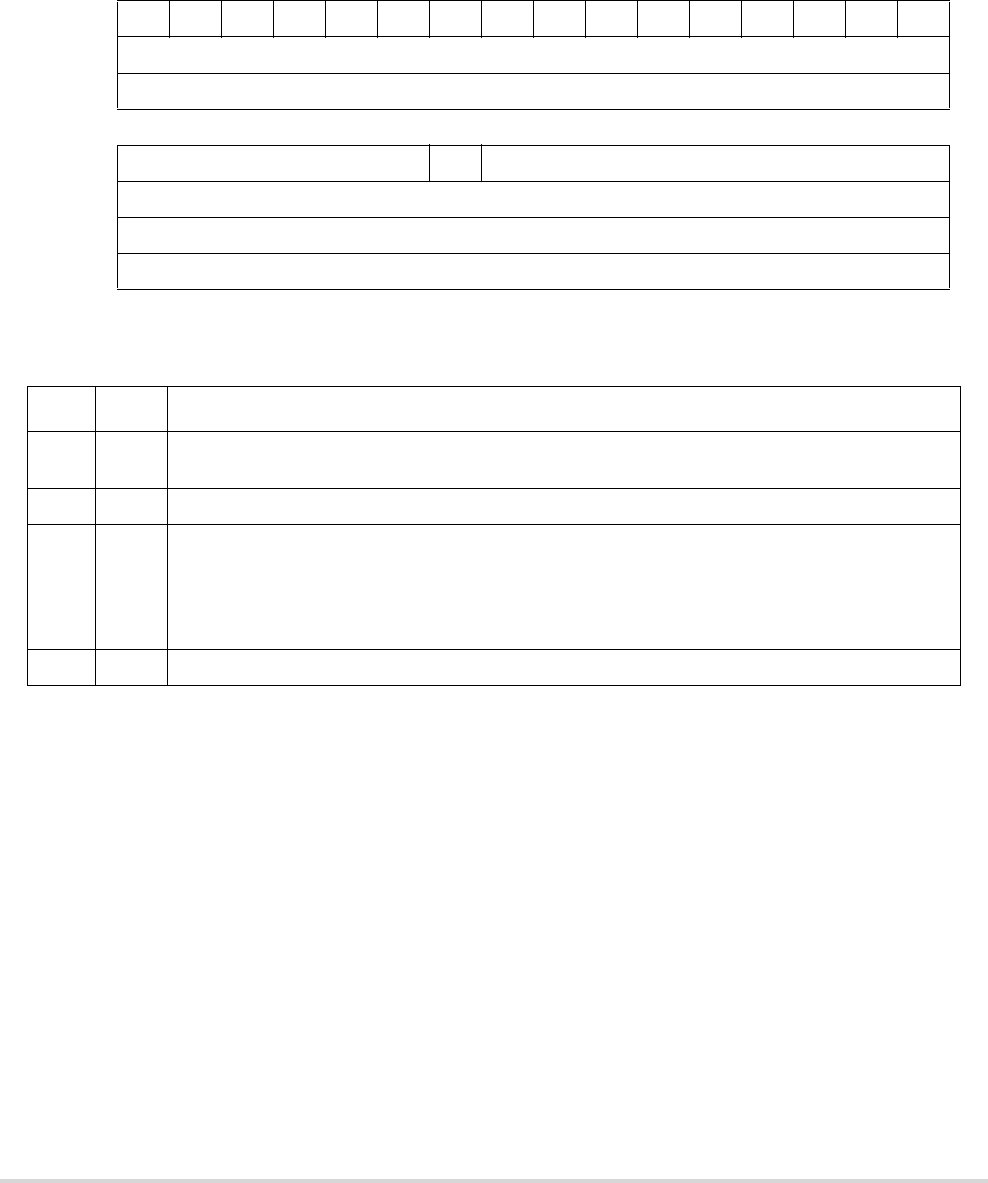

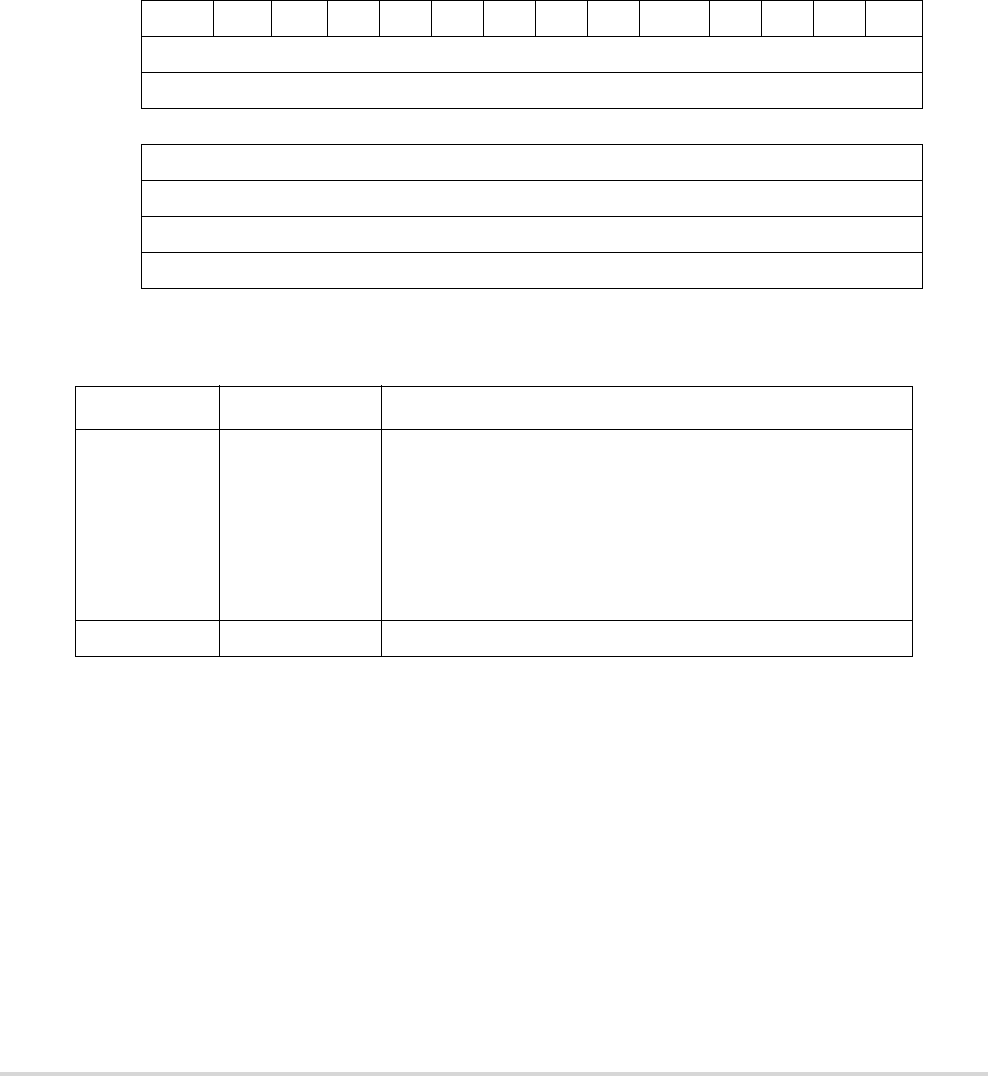

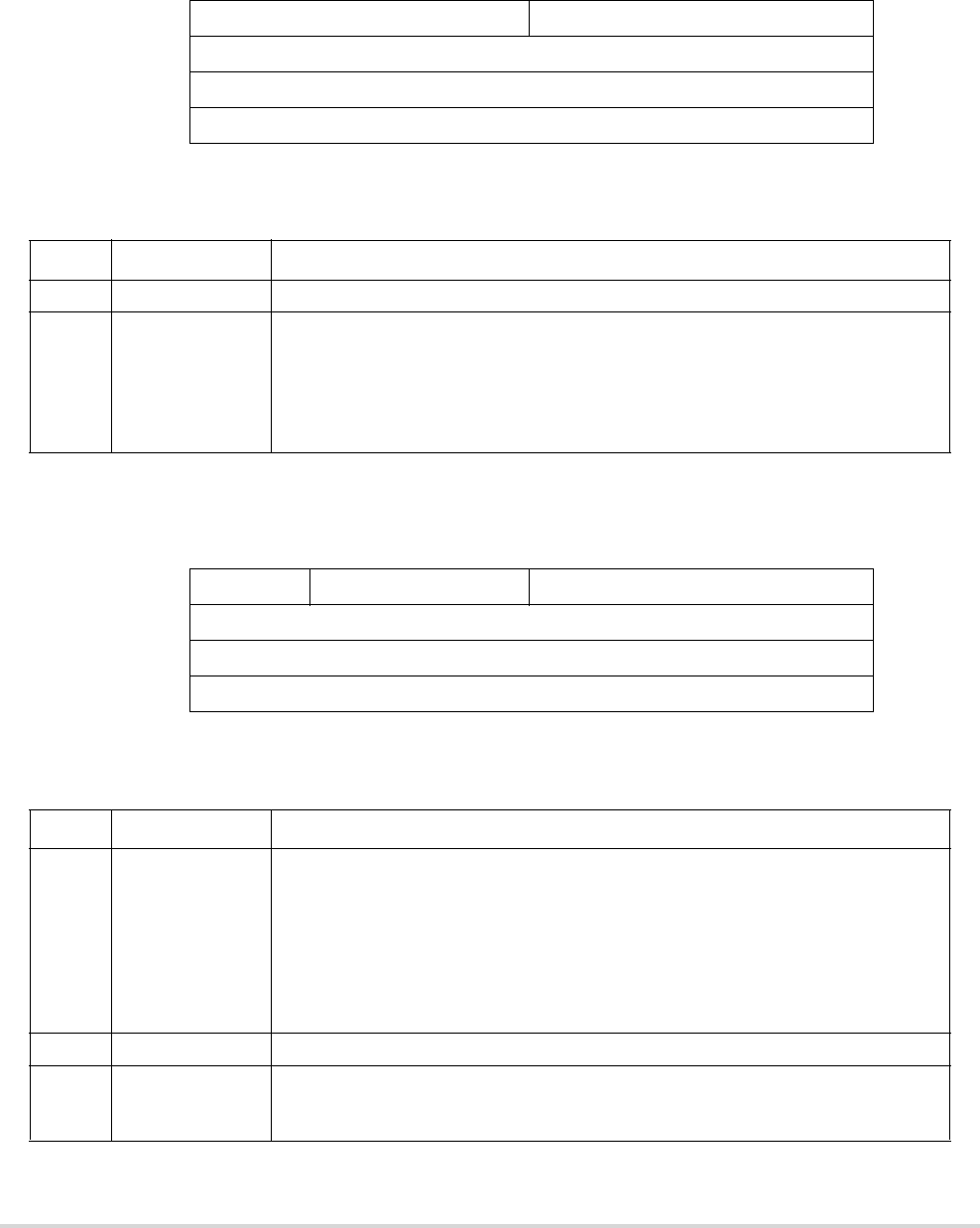

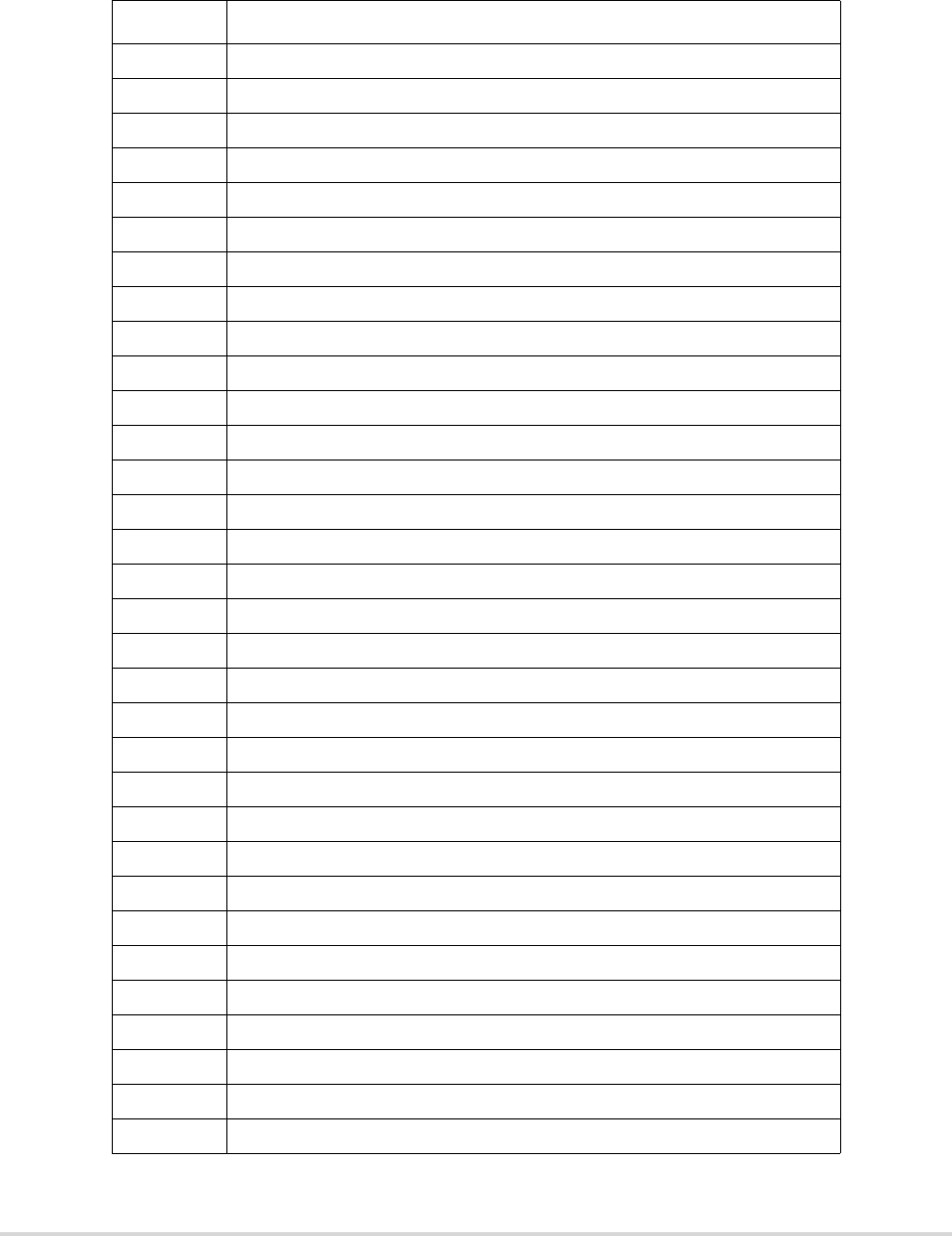

Chapter 2

ColdFire Core

2.1 Processor Pipelines ............................................................................................. 2-1

2.2 Processor Register Description........................................................................... 2-2

2.2.1 User Programming Model .............................................................................. 2-2

2.2.2 EMAC Programming Model ......................................................................... 2-5

2.2.3 Supervisor Programming Model..................................................................... 2-5

vi MCF5282 User’s Manual MOTOROLA

CONTENTS

Paragraph

Number Title Page

Number

2.3 Programming Model ........................................................................................... 2-8

2.4 Additions to the Instruction Set Architecture ..................................................... 2-9

2.5 Exception Processing Overview ....................................................................... 2-10

2.6 Exception Stack Frame Definition.................................................................... 2-12

2.7 Processor Exceptions ........................................................................................ 2-13

2.7.1 Access Error Exception ................................................................................ 2-13

2.7.2 Address Error Exception............................................................................... 2-14

2.7.3 Illegal Instruction Exception......................................................................... 2-14

2.7.4 Divide-By-Zero............................................................................................. 2-14

2.7.5 Privilege Violation........................................................................................ 2-14

2.7.6 Trace Exception ............................................................................................ 2-14

2.7.7 Unimplemented Line-A Opcode................................................................... 2-15

2.7.8 Unimplemented Line-F Opcode ................................................................... 2-15

2.7.9 Debug Interrupt............................................................................................. 2-15

2.7.10 RTE and Format Error Exception................................................................. 2-16

2.7.11 TRAP Instruction Exception......................................................................... 2-16

2.7.12 Interrupt Exception ....................................................................................... 2-16

2.7.13 Fault-on-Fault Halt ....................................................................................... 2-16

2.7.14 Reset Exception ............................................................................................ 2-16

2.8 Instruction Execution Timing ........................................................................... 2-21

2.8.1 Timing Assumptions..................................................................................... 2-21

2.8.2 MOVE Instruction Execution Times ............................................................ 2-22

2.9 Standard One Operand Instruction Execution Times ....................................... 2-24

2.10 Standard Two Operand Instruction Execution Times....................................... 2-24

2.11 Miscellaneous Instruction Execution Times..................................................... 2-26

2.12 EMAC Instruction Execution Times ................................................................ 2-27

2.13 Branch Instruction Execution Times ................................................................ 2-28

2.14 ColdFire Instruction Set Architecture Enhancements ...................................... 2-28

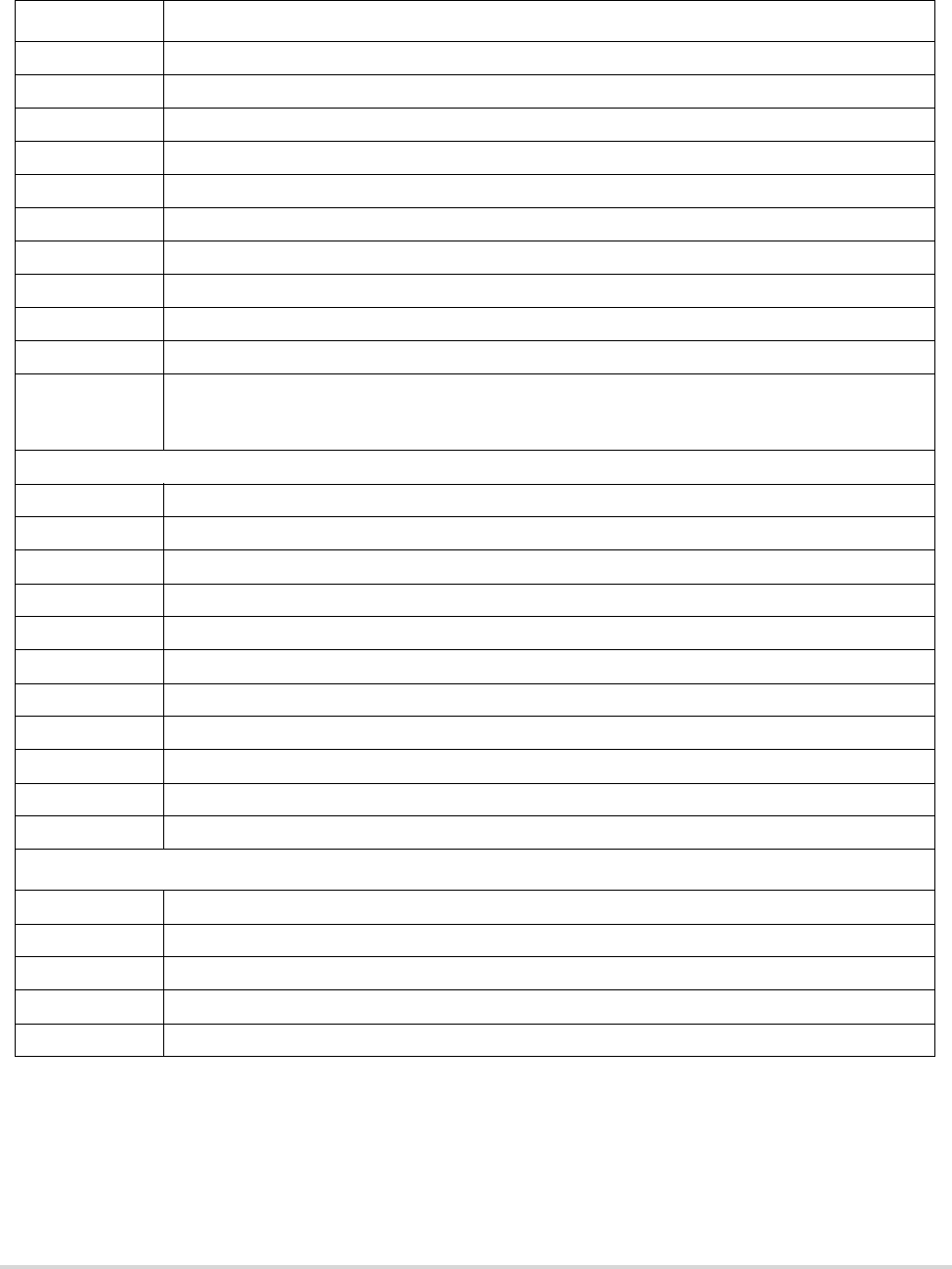

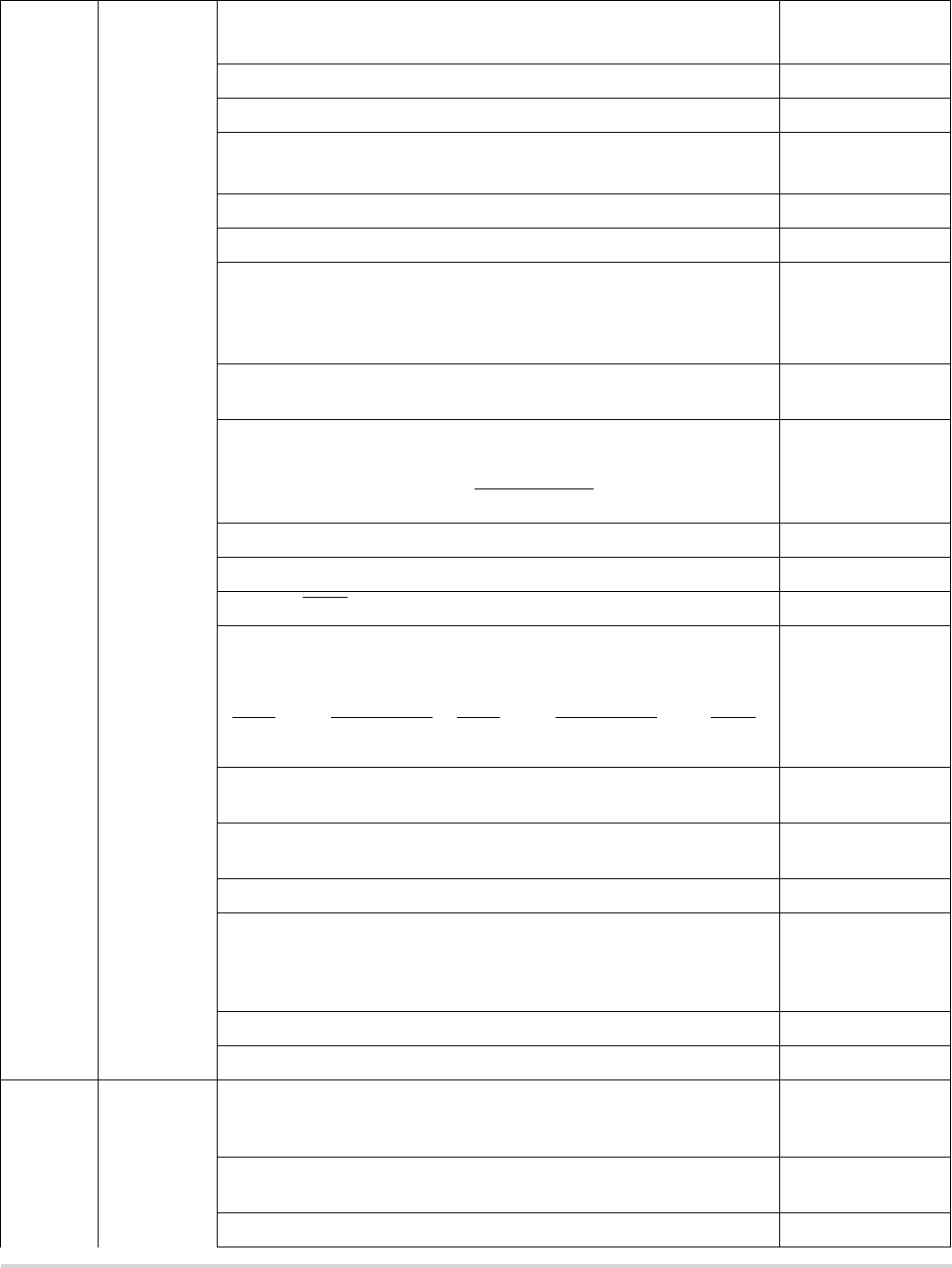

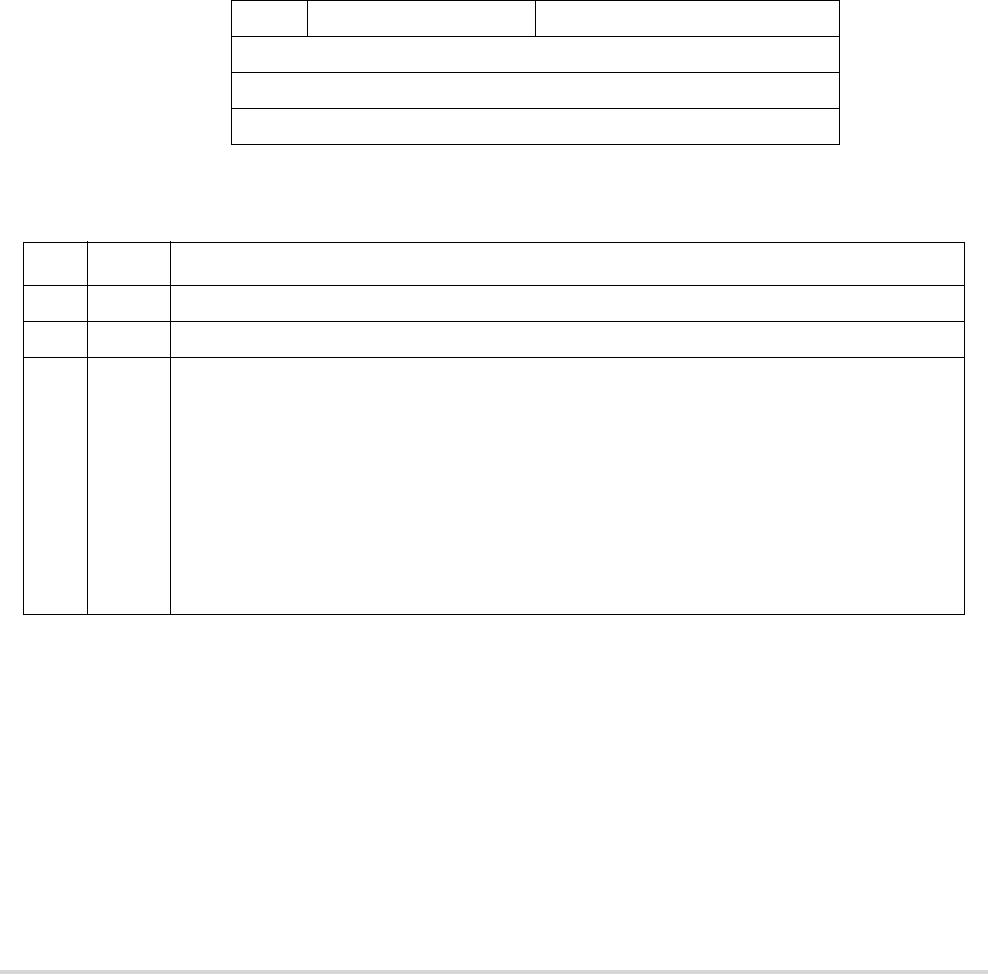

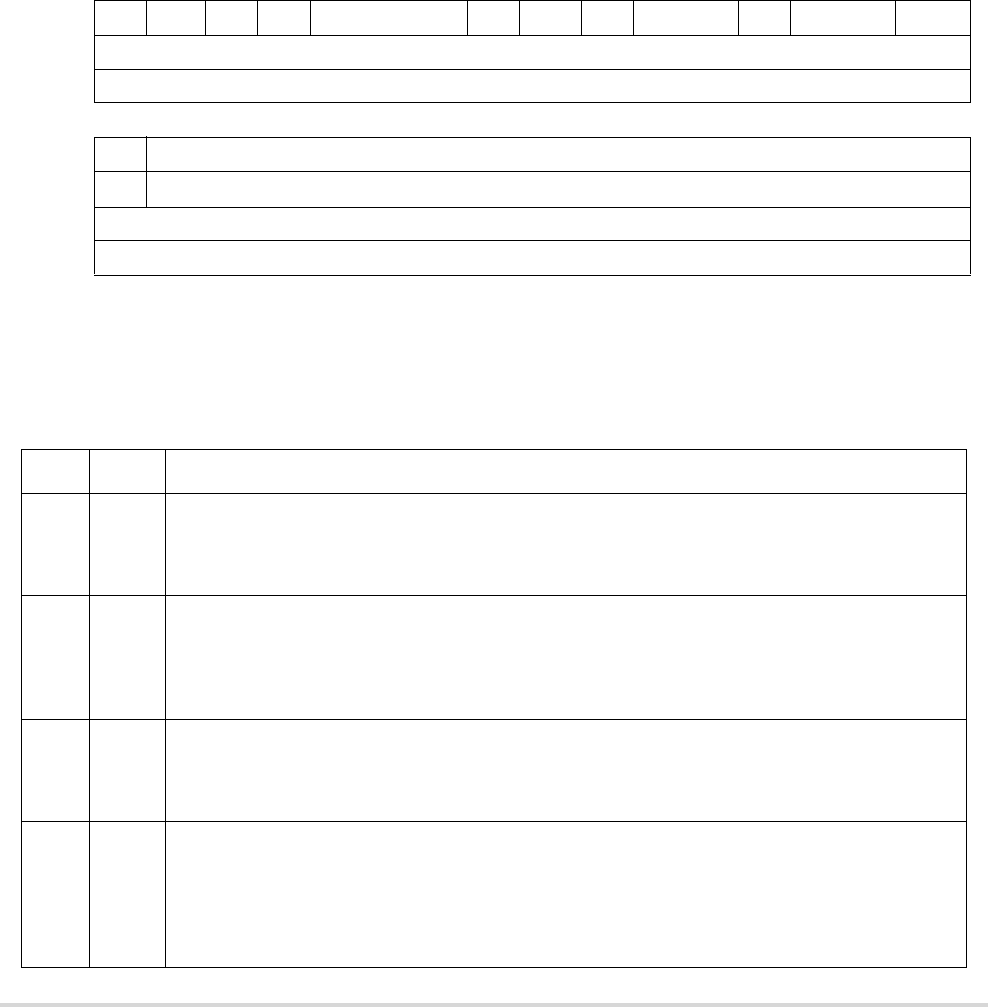

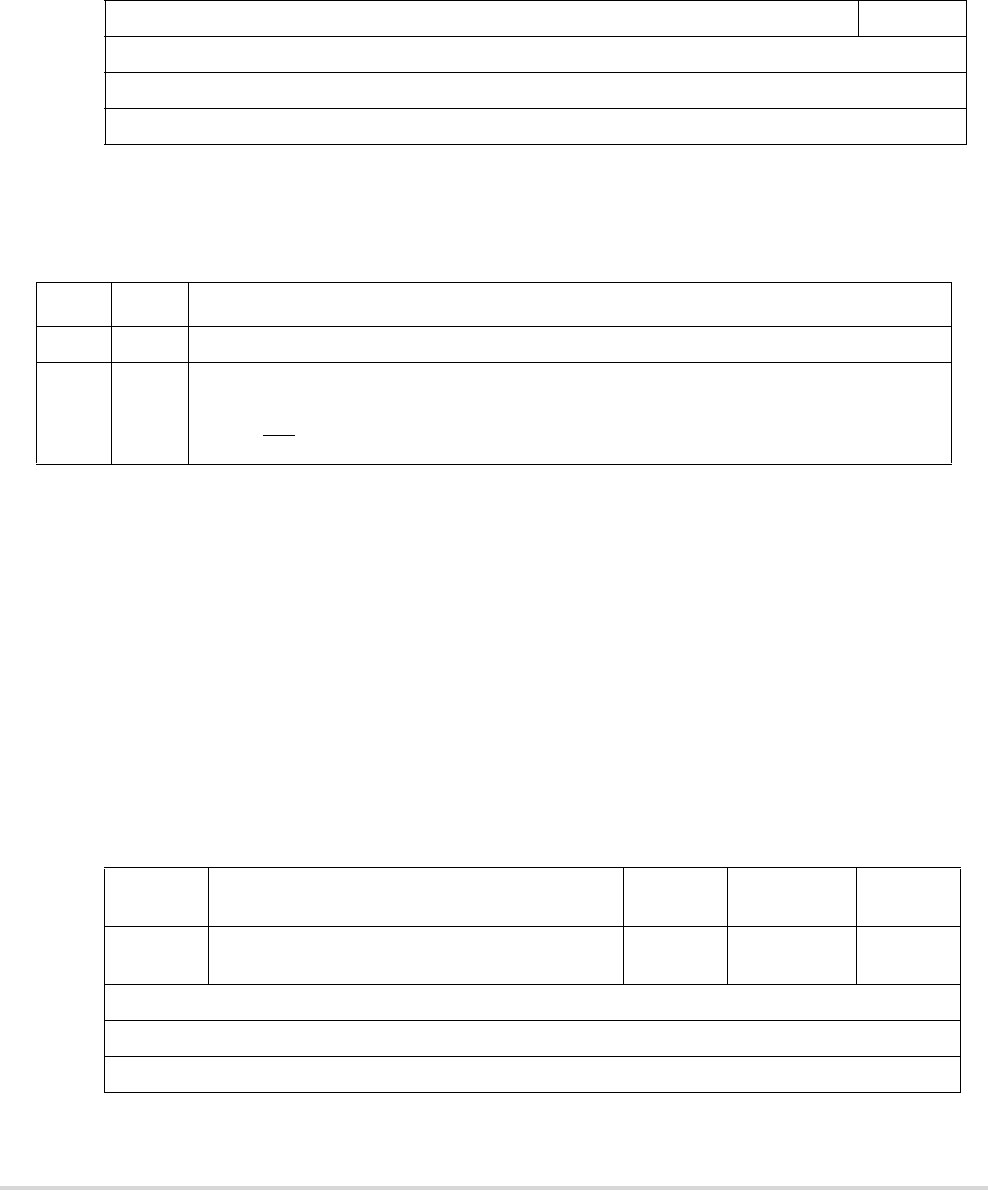

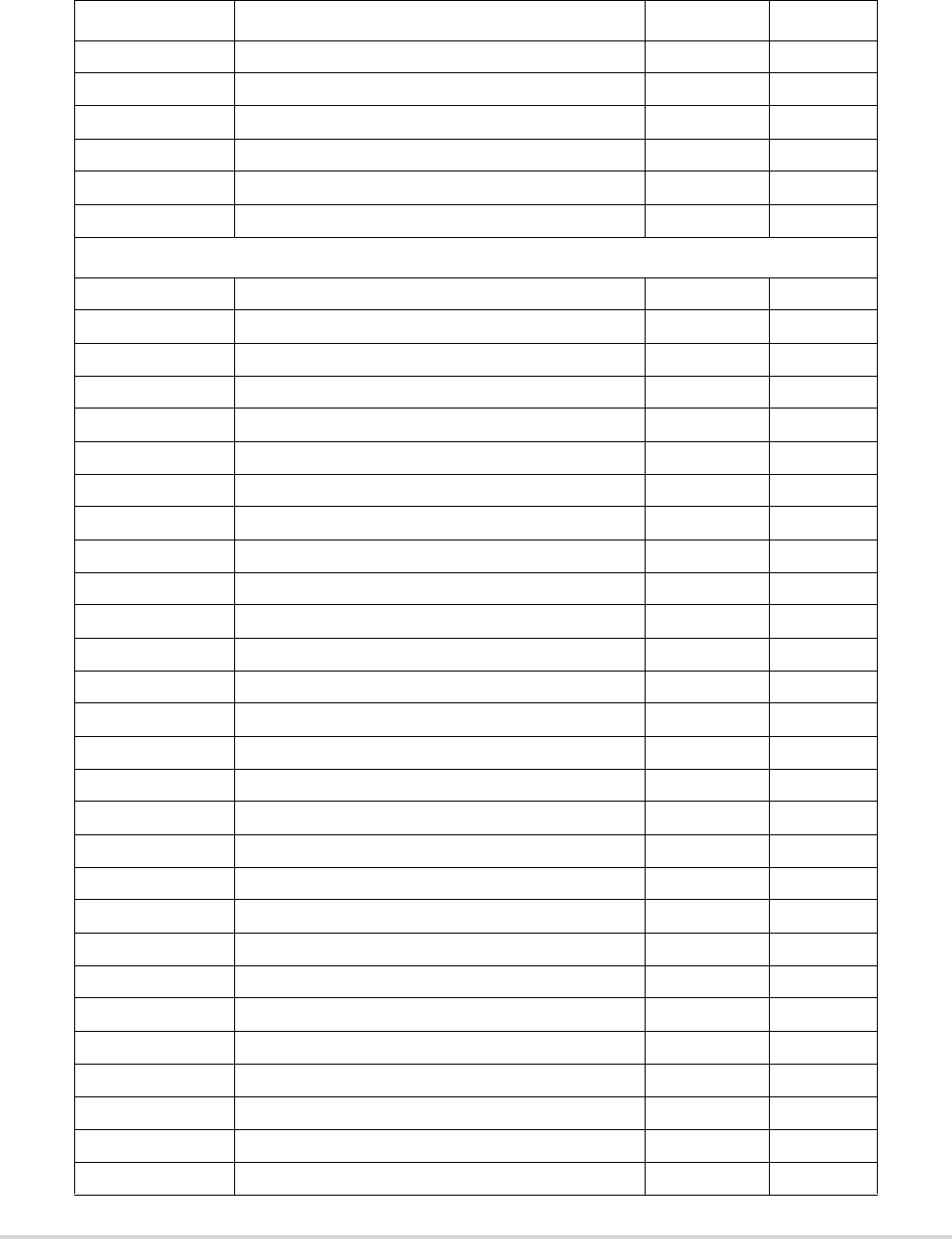

Chapter 3

Enhanced Multiply-Accumulate Unit (EMAC)

3.1 Multiply-Accumulate Unit.................................................................................. 3-1

3.2 Introduction to the MAC..................................................................................... 3-2

3.3 General Operation............................................................................................... 3-3

3.4 Memory Map/Register Set.................................................................................. 3-6

3.4.1 MAC Status Register (MACSR) .................................................................... 3-6

3.4.2 Mask Register (MASK)................................................................................ 3-11

3.5 EMAC Instruction Set Summary...................................................................... 3-12

3.5.1 EMAC Instruction Execution Times ............................................................ 3-12

3.5.2 Data Representation...................................................................................... 3-13

3.5.3 MAC Opcodes .............................................................................................. 3-14

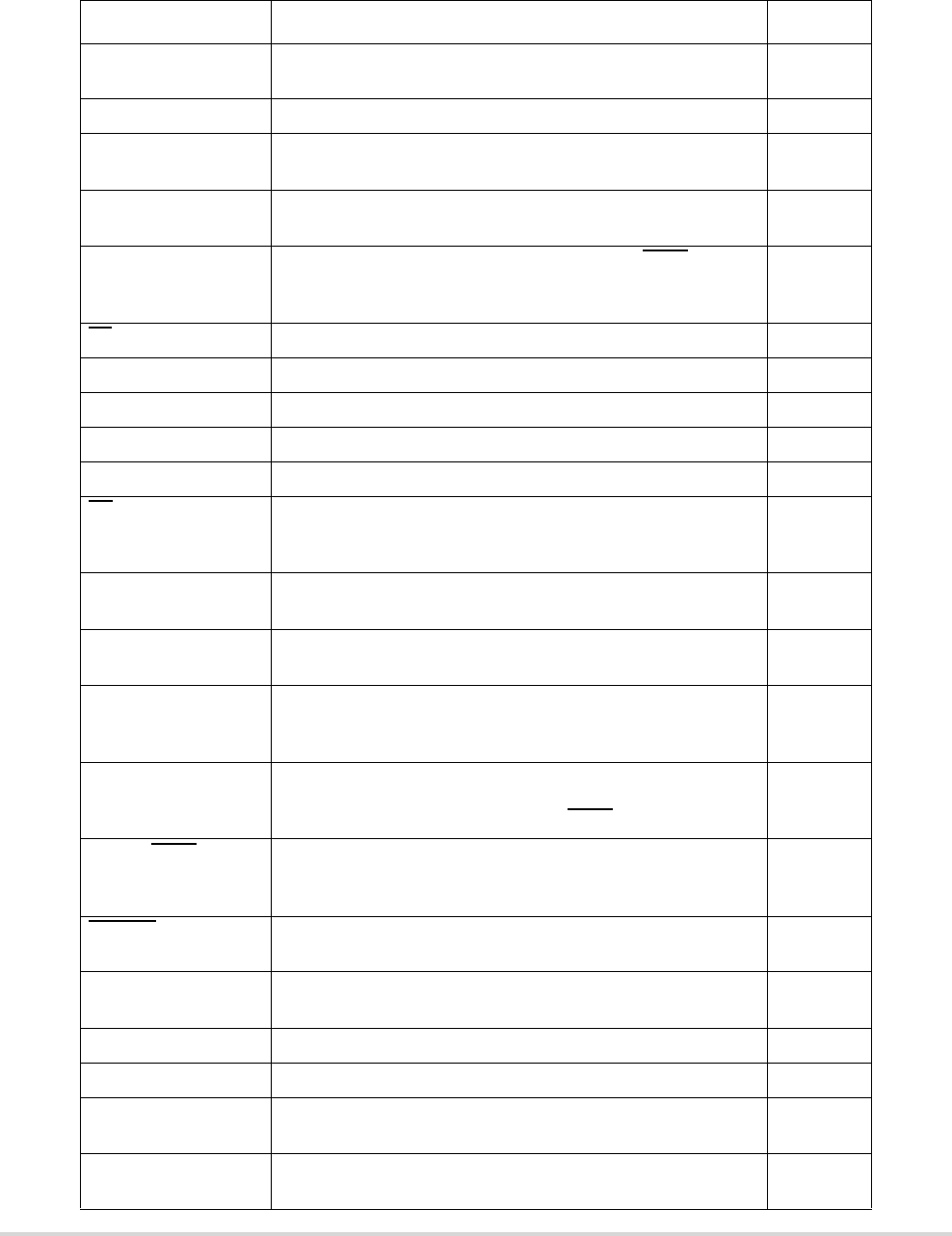

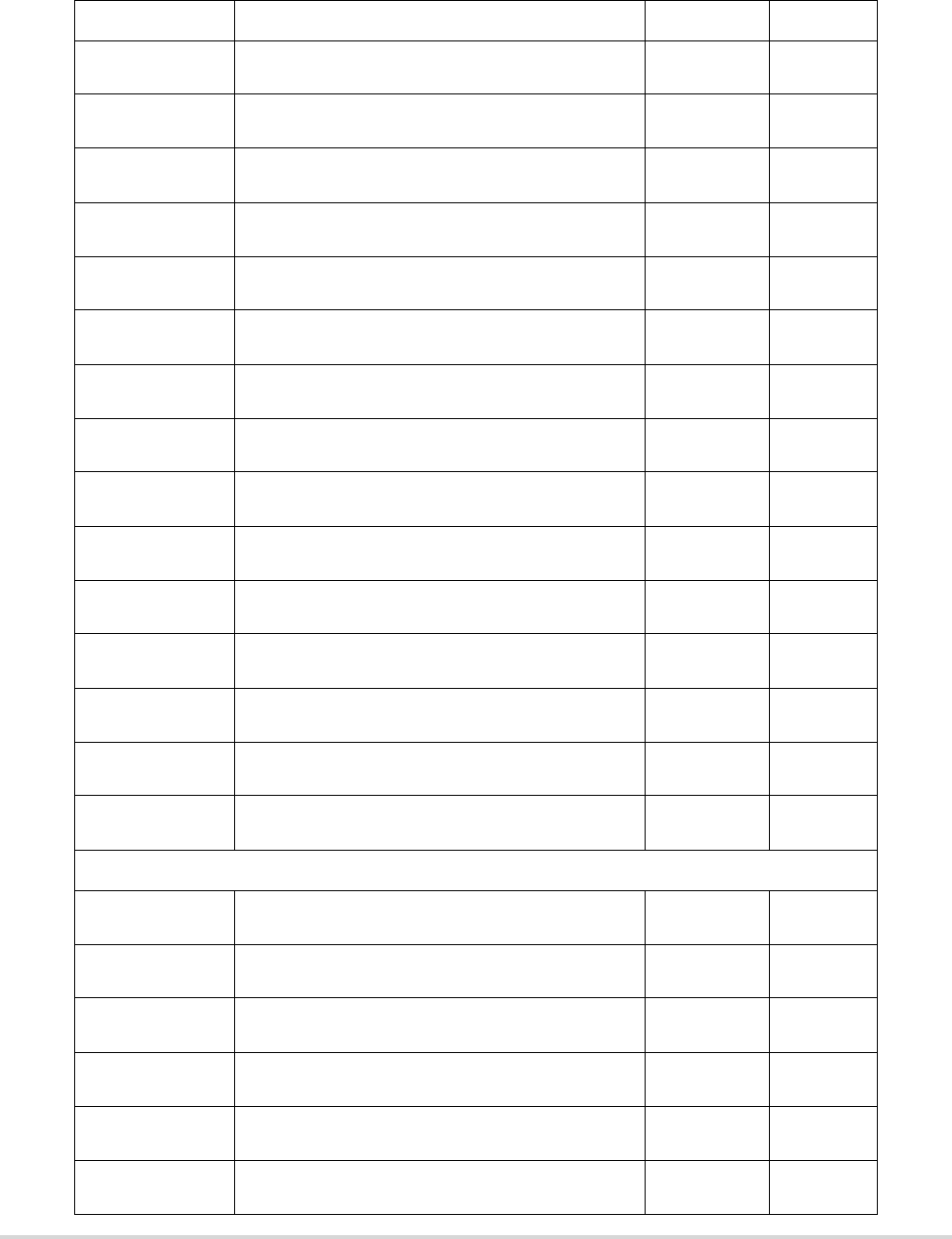

CONTENTS

Paragraph

Number Title Page

Number

MOTOROLA Contents vii

Chapter 4

Cache

4.1 Cache Features.................................................................................................... 4-1

4.2 Cache Physical Organization .............................................................................. 4-1

4.3 Cache Operation ................................................................................................. 4-3

4.3.1 Interaction with Other Modules...................................................................... 4-3

4.3.2 Memory Reference Attributes ........................................................................ 4-4

4.3.3 Cache Coherency and Invalidation................................................................. 4-4

4.3.4 Reset................................................................................................................ 4-5

4.3.5 Cache Miss Fetch Algorithm/Line Fills ......................................................... 4-5

4.4 Cache Programming Model ................................................................................ 4-7

4.4.1 Cache Registers Memory Map ....................................................................... 4-7

4.4.2 Cache Registers............................................................................................... 4-7

Chapter 5

Static RAM (SRAM)

5.1 SRAM Features................................................................................................... 5-1

5.2 SRAM Operation ................................................................................................ 5-1

5.3 SRAM Programming Model............................................................................... 5-1

5.3.1 SRAM Base Address Register (RAMBAR)................................................... 5-2

5.3.2 SRAM Initialization........................................................................................ 5-3

5.3.3 SRAM Initialization Code .............................................................................. 5-4

5.3.4 Power Management ........................................................................................ 5-4

Chapter 6

ColdFire Flash Module (CFM)

6.1 Features............................................................................................................... 6-1

6.2 Block Diagram.................................................................................................... 6-2

6.3 Memory Map ...................................................................................................... 6-4

6.3.1 CFM Configuration Field ............................................................................... 6-5

6.3.2 Flash Base Address Register (FLASHBAR).................................................. 6-5

6.3.3 CFM Registers ................................................................................................ 6-8

6.3.4 Register Descriptions...................................................................................... 6-9

6.4 CFM Operation ................................................................................................. 6-17

6.4.1 Read Operations............................................................................................ 6-17

6.4.2 Write Operations........................................................................................... 6-17

6.4.3 Program and Erase Operations ..................................................................... 6-17

6.4.4 Stop Mode..................................................................................................... 6-22

6.4.5 Master Mode................................................................................................. 6-23

viii MCF5282 User’s Manual MOTOROLA

CONTENTS

Paragraph

Number Title Page

Number

6.5 Flash Security Operation .................................................................................. 6-23

6.5.1 Back Door Access......................................................................................... 6-24

6.5.2 Erase Verify Check....................................................................................... 6-24

6.6 Reset.................................................................................................................. 6-24

6.7 Interrupts........................................................................................................... 6-25

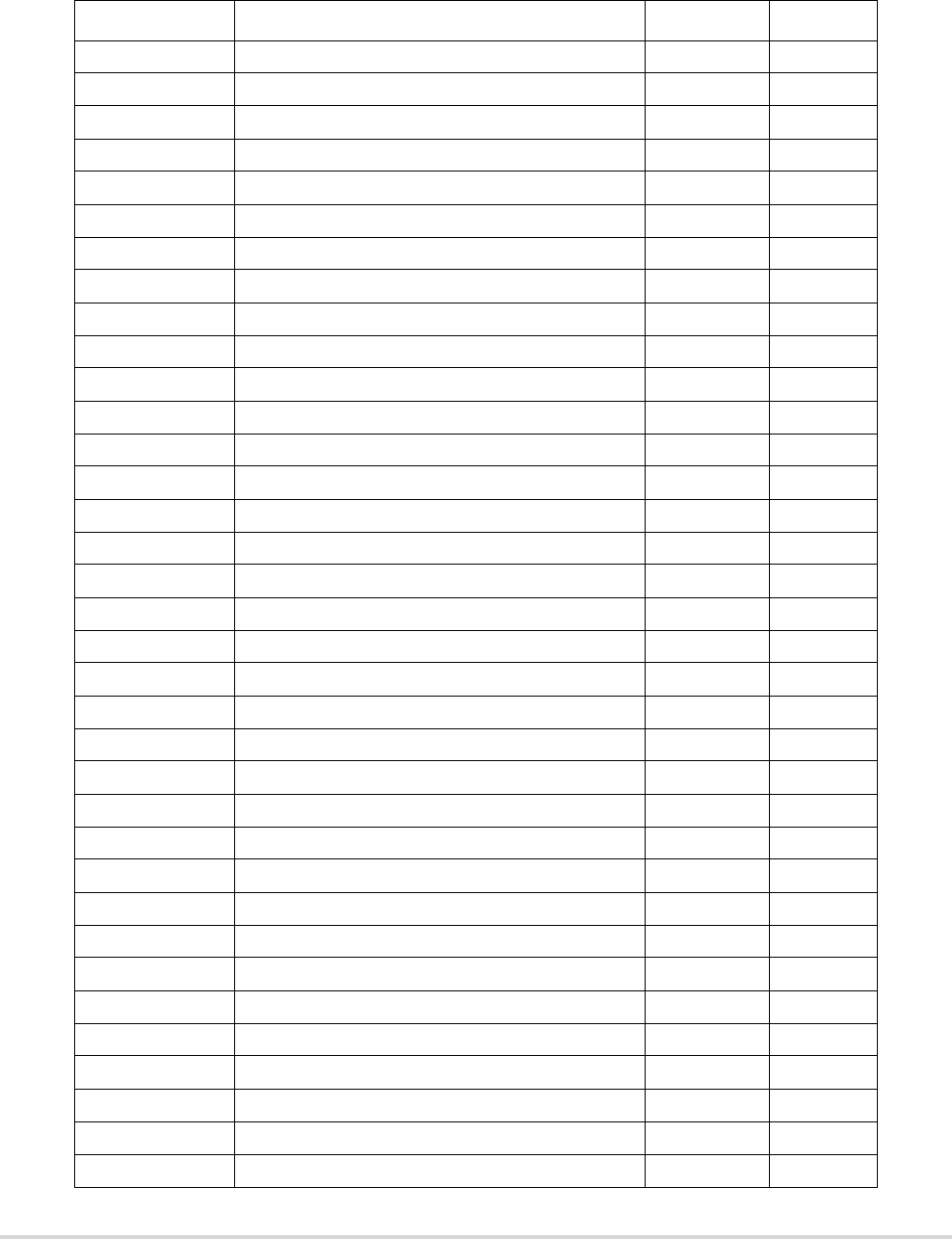

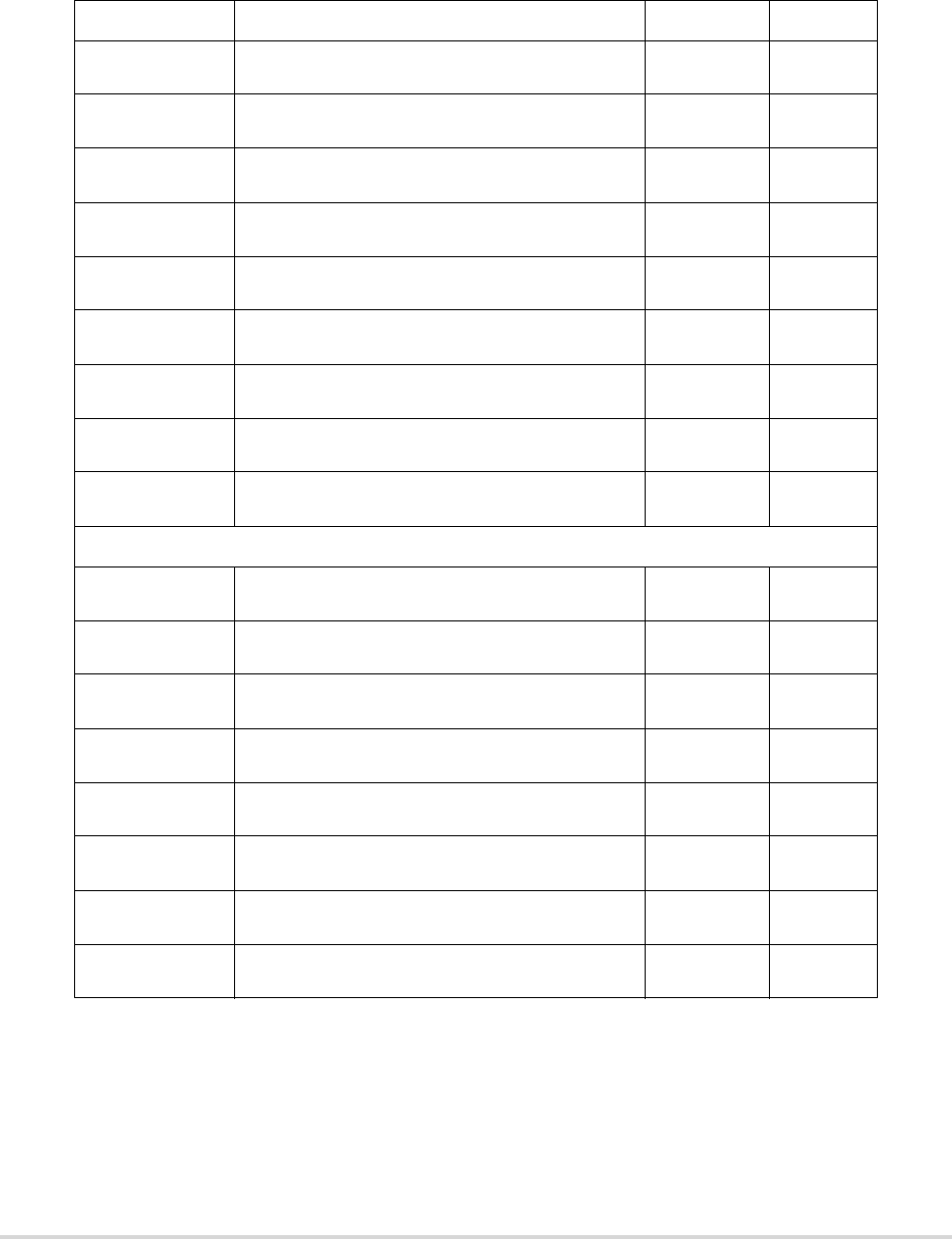

Chapter 7

Power Management

7.1 Features............................................................................................................... 7-1

7.2 Memory Map and Registers................................................................................ 7-1

7.2.1 Programming Model....................................................................................... 7-1

7.2.2 Memory Map .................................................................................................. 7-2

7.2.3 Register Descriptions...................................................................................... 7-2

7.3 Functional Description........................................................................................ 7-5

7.3.1 Low-Power Modes.......................................................................................... 7-5

7.3.2 Peripheral Behavior in Low-Power Modes .................................................... 7-7

7.3.3 Summary of Peripheral State During Low-Power Modes............................ 7-16

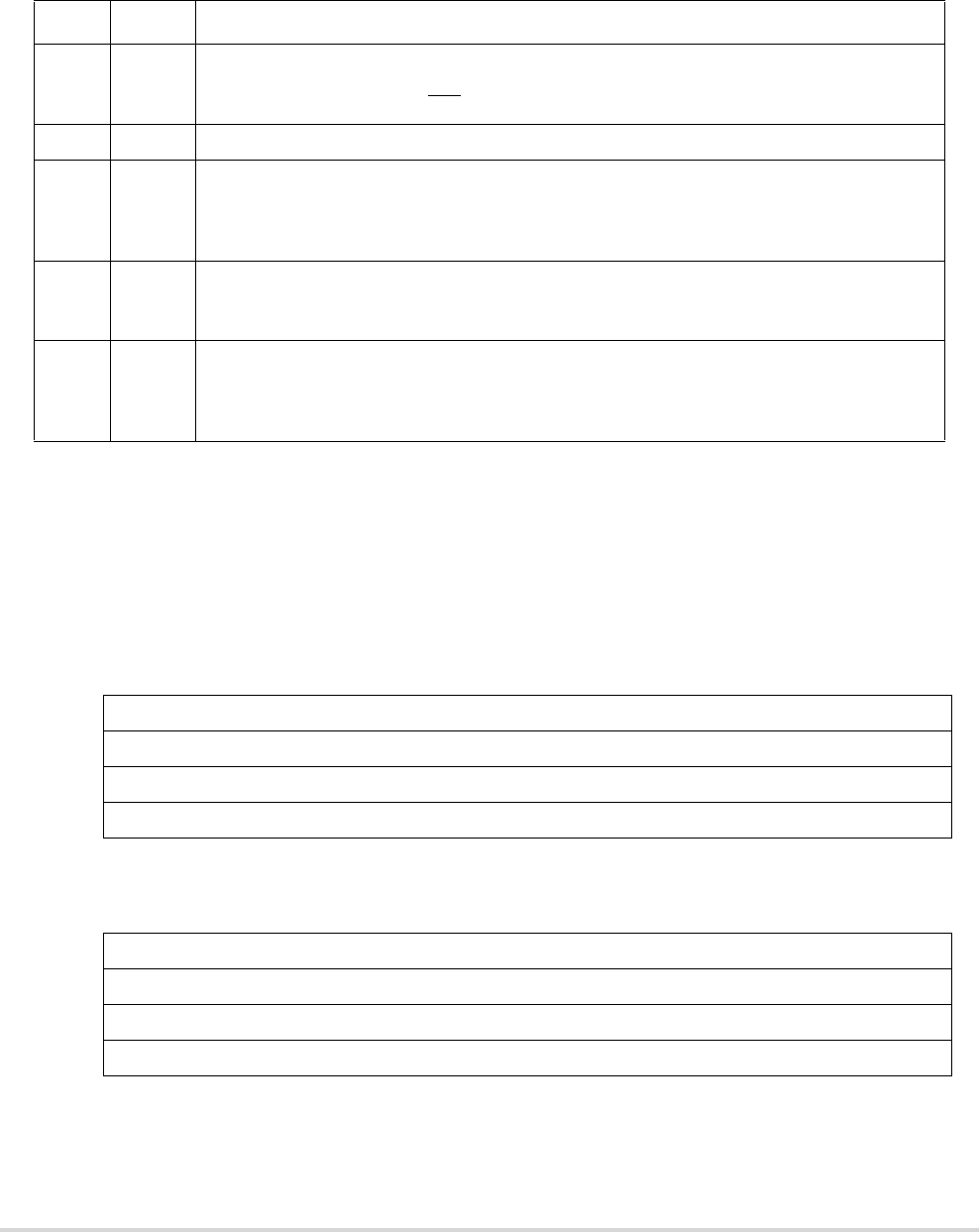

Chapter 8

System Control Module (SCM)

8.1 Overview............................................................................................................. 8-1

8.2 Features............................................................................................................... 8-1

8.3 Memory Map and Register Definition................................................................ 8-2

8.4 Register Descriptions.......................................................................................... 8-3

8.4.1 Internal Peripheral System Base Address Register (IPSBAR)....................... 8-3

8.4.2 Memory Base Address Register (RAMBAR) ................................................ 8-4

8.4.3 Core Reset Status Register (CRSR)................................................................ 8-6

8.4.4 Core Watchdog Control Register (CWCR) .................................................... 8-6

8.4.5 Core Watchdog Service Register (CWSR)..................................................... 8-9

8.5 Internal Bus Arbitration ...................................................................................... 8-9

8.5.1 Overview....................................................................................................... 8-11

8.5.2 Arbitration Algorithms ................................................................................. 8-11

8.5.3 Bus Master Park Register (MPARK)............................................................ 8-12

8.6 System Access Control Unit (SACU)............................................................... 8-14

8.6.1 Overview....................................................................................................... 8-14

8.6.2 Features......................................................................................................... 8-14

8.6.3 Memory Map/Register Definition ................................................................ 8-15

CONTENTS

Paragraph

Number Title Page

Number

MOTOROLA Contents ix

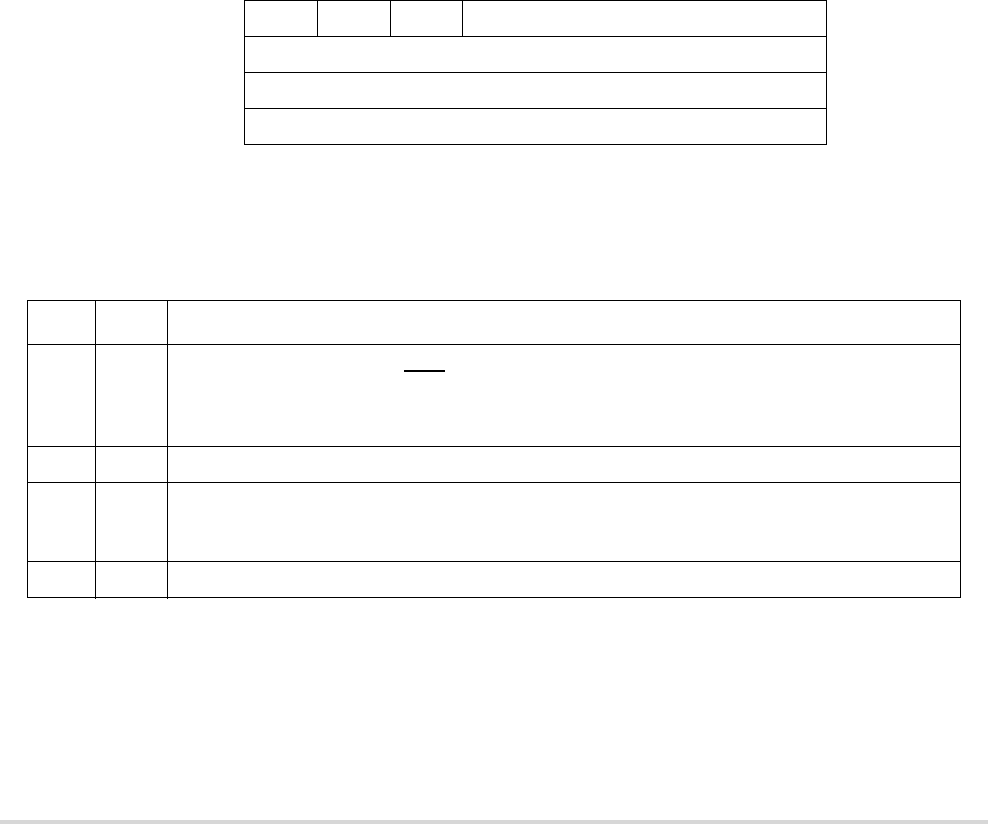

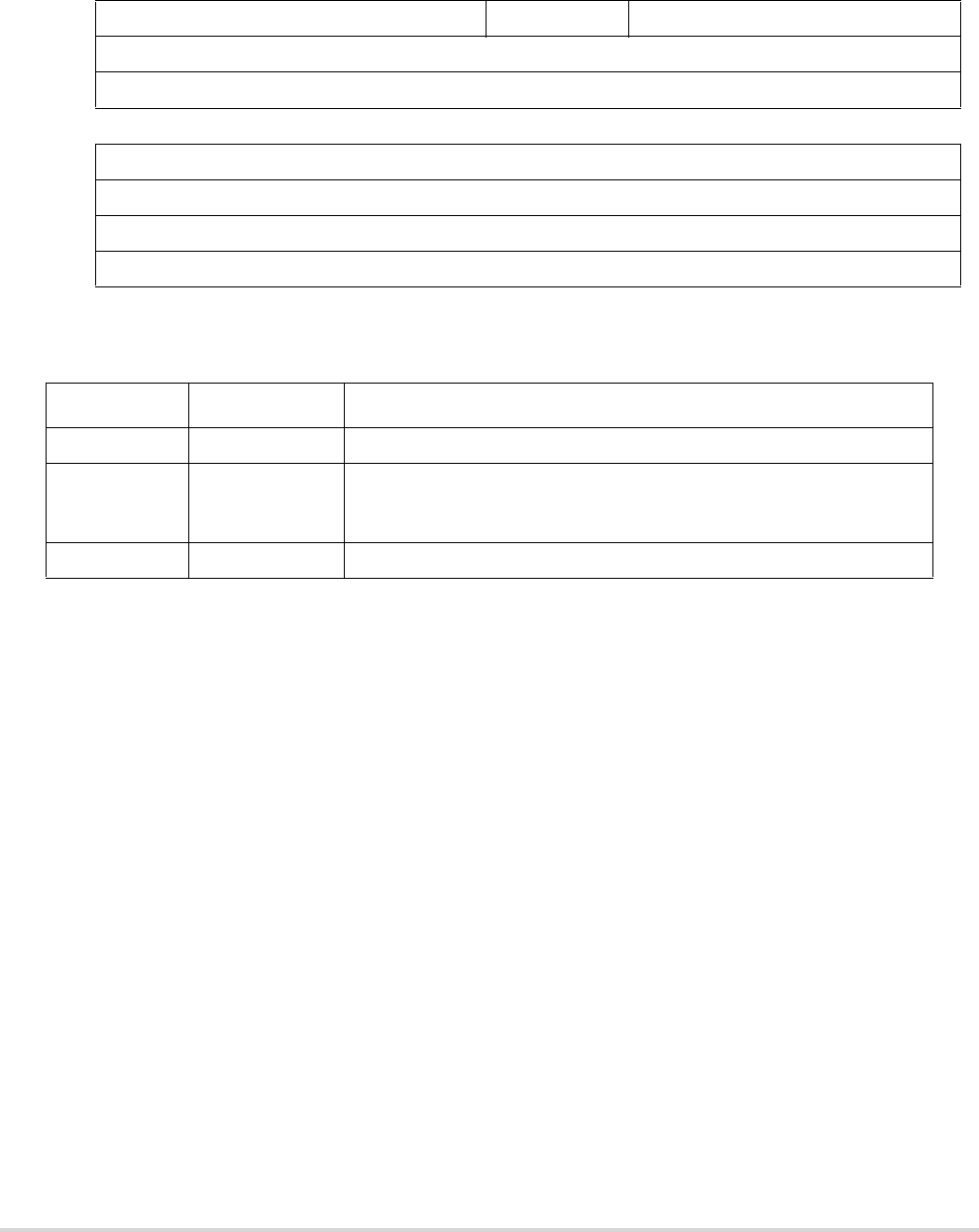

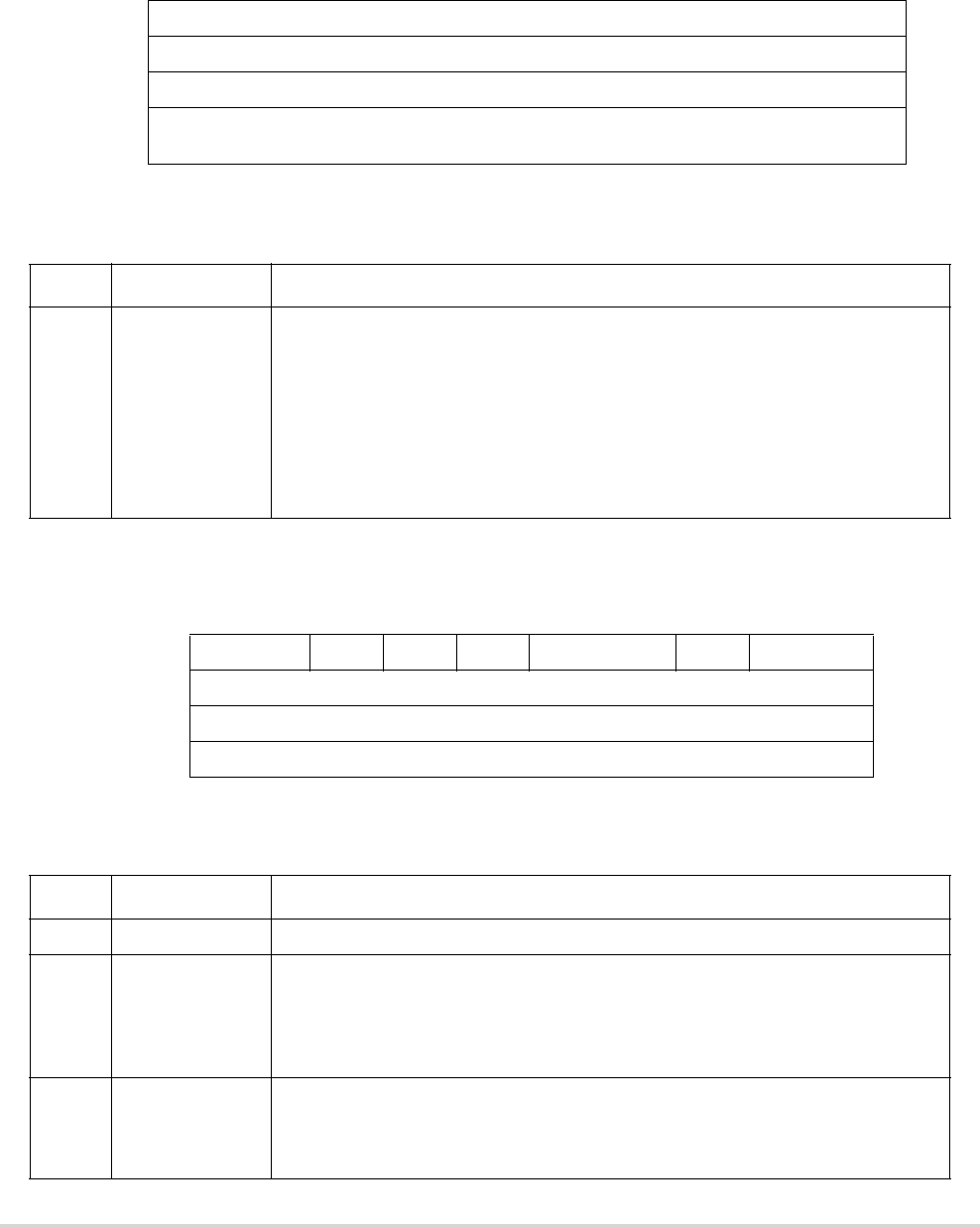

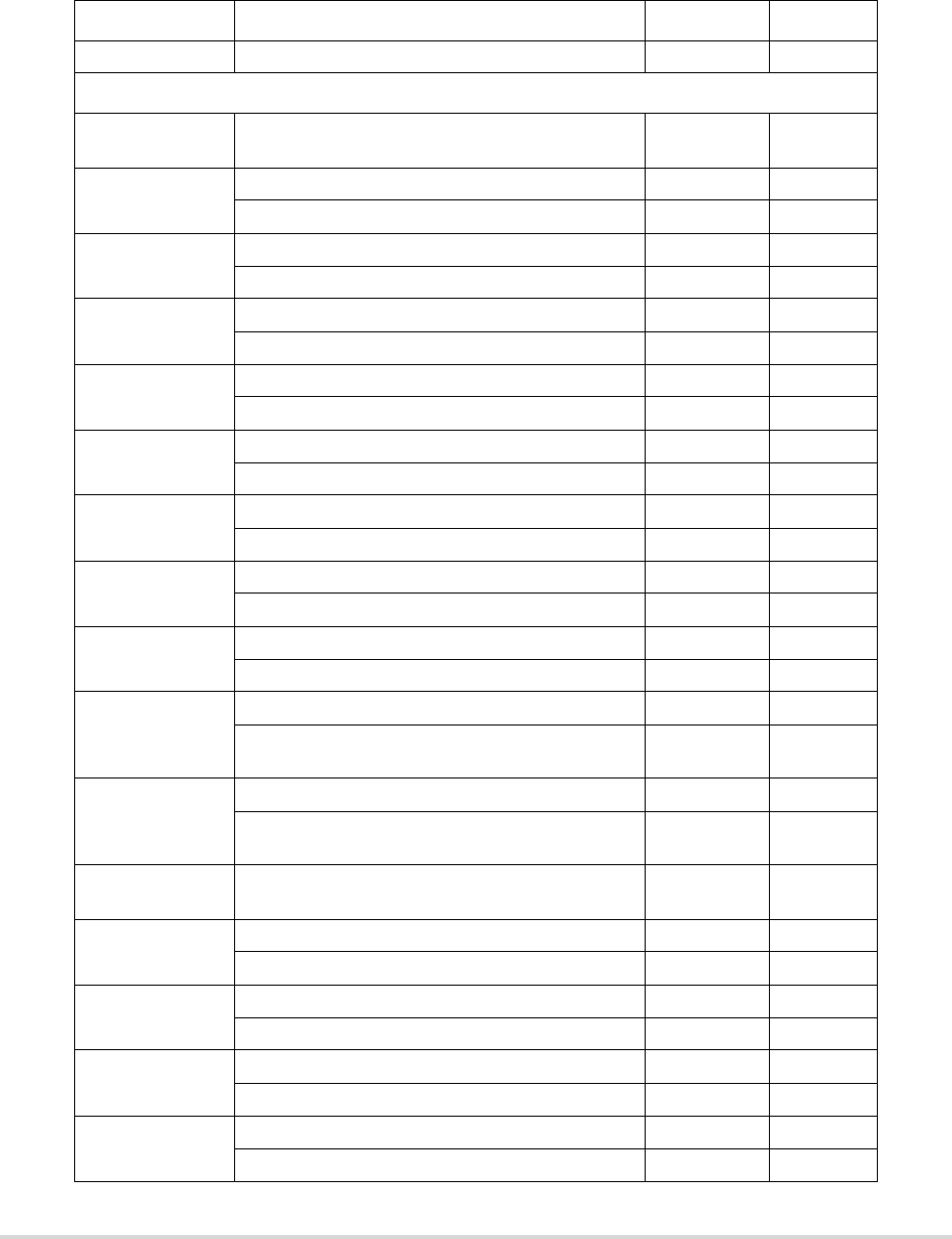

Chapter 9

Clock Module

9.1 Features............................................................................................................... 9-1

9.2 Modes of Operation ............................................................................................ 9-1

9.2.1 Normal PLL Mode.......................................................................................... 9-1

9.2.2 1:1 PLL Mode................................................................................................. 9-2

9.2.3 External Clock Mode...................................................................................... 9-2

9.3 Low-power Mode Operation .............................................................................. 9-2

9.4 Block Diagram.................................................................................................... 9-3

9.5 Signal Descriptions ............................................................................................. 9-4

9.5.1 EXTAL ........................................................................................................... 9-4

9.5.2 XTAL.............................................................................................................. 9-5

9.5.3 CLKOUT ........................................................................................................ 9-5

9.5.4 CLKMOD[1:0] ............................................................................................... 9-5

9.5.5 RSTOUT......................................................................................................... 9-5

9.6 Memory Map and Registers................................................................................ 9-5

9.6.1 Module Memory Map..................................................................................... 9-5

9.6.2 Register Descriptions...................................................................................... 9-6

9.7 Functional Description...................................................................................... 9-10

9.7.1 System Clock Modes .................................................................................... 9-10

9.7.2 Clock Operation During Reset...................................................................... 9-11

9.7.3 System Clock Generation ............................................................................. 9-11

9.7.4 PLL Operation .............................................................................................. 9-12

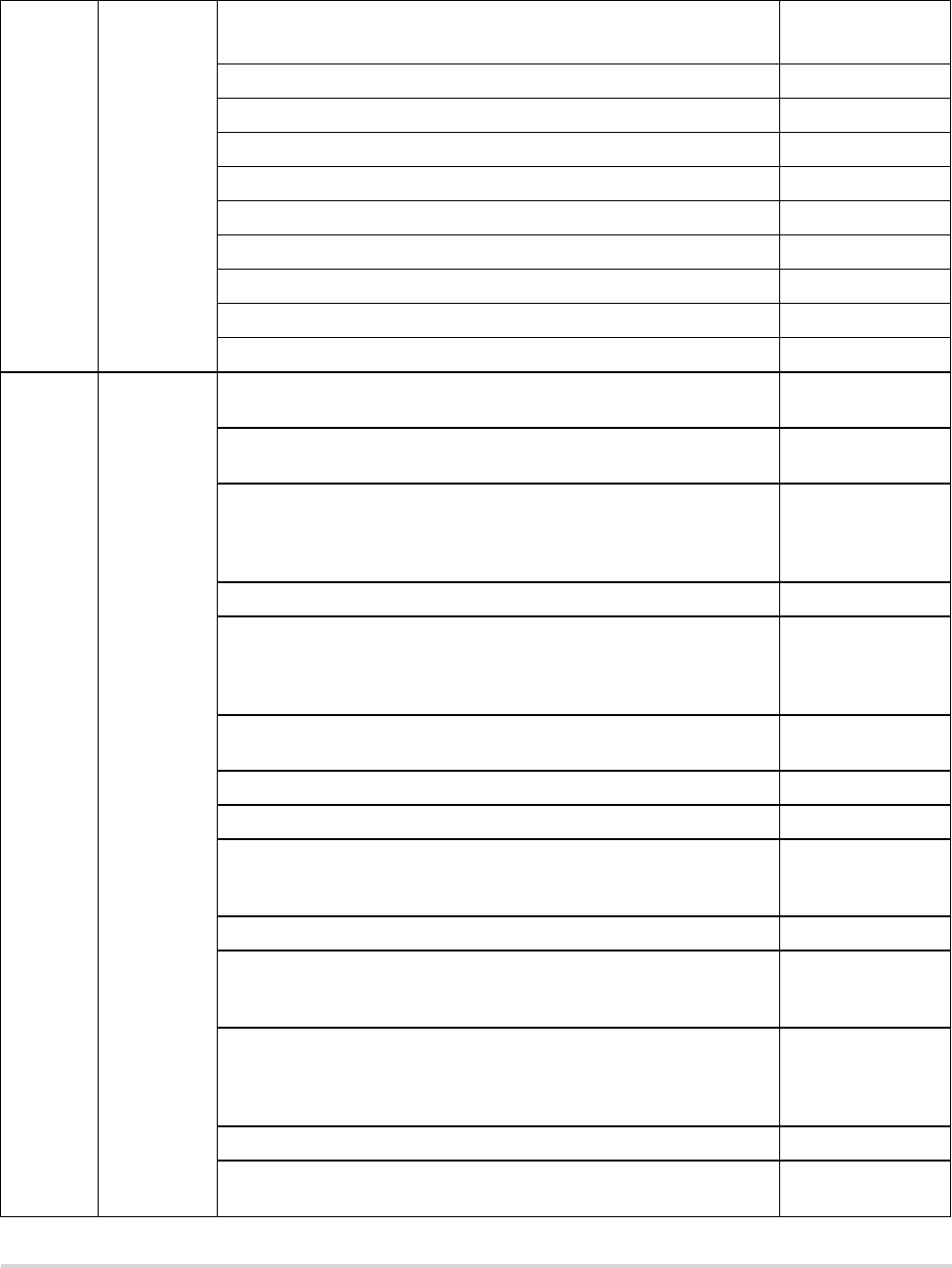

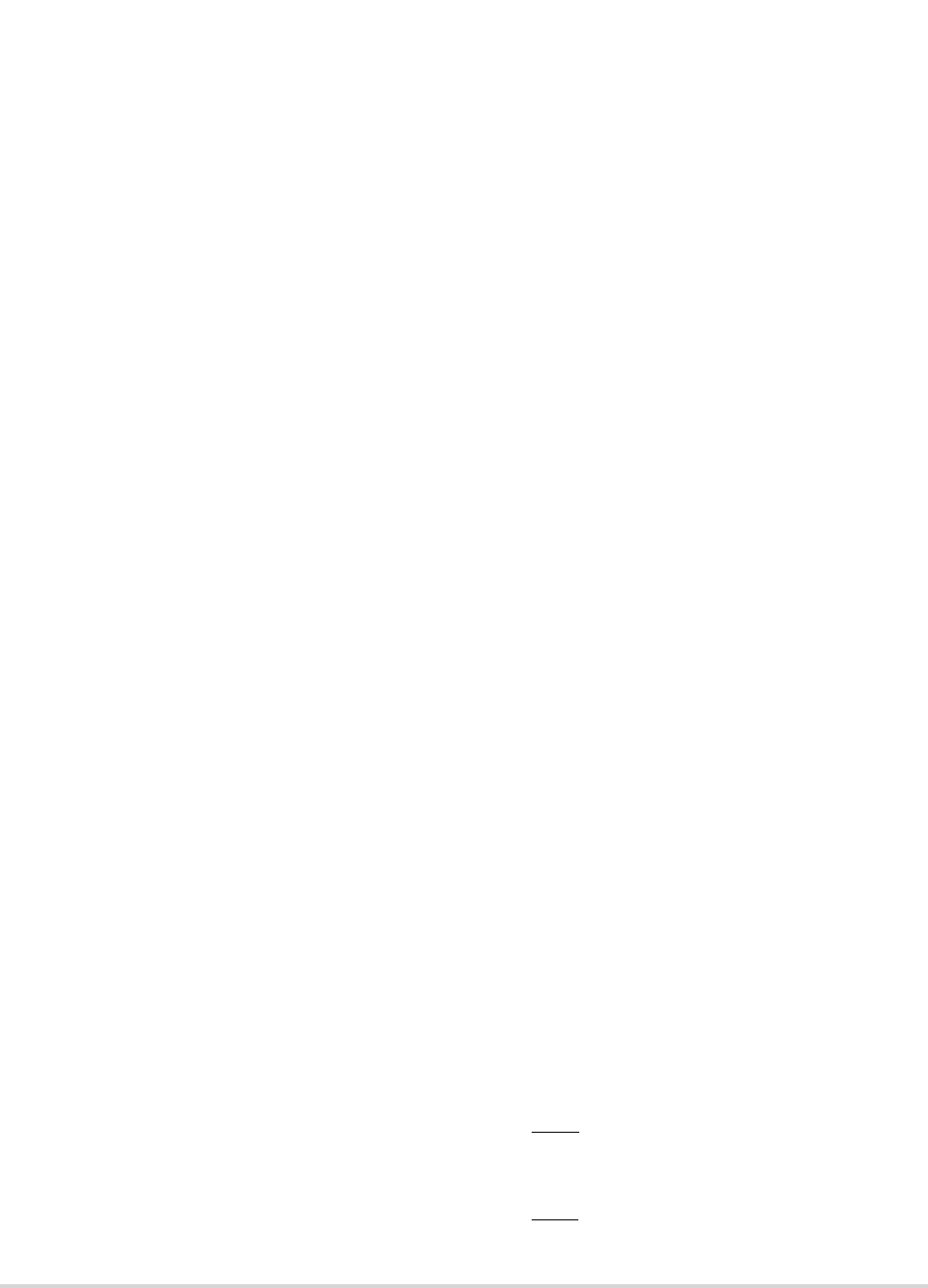

Chapter 10

Interrupt Controller Modules

10.1 68K/ColdFire Interrupt Architecture Overview ............................................... 10-1

10.1.1 Interrupt Controller Theory of Operation ..................................................... 10-3

10.2 Memory Map .................................................................................................... 10-5

10.3 Register Descriptions........................................................................................ 10-6

10.3.1 Interrupt Pending Registers (IPRHn, IPRLn)............................................... 10-6

10.3.2 Interrupt Mask Register (IMRHn, IMRLn) .................................................. 10-8

10.3.3 Interrupt Force Registers (INTFRCHn, INTFRCLn)................................... 10-9

10.3.4 Interrupt Request Level Register (IRLRn) ................................................. 10-10

10.3.5 Interrupt Acknowledge Level and Priority Register (IACKLPRn) ............ 10-11

10.3.6 Interrupt Control Register (ICRnx, (x = 1, 2,..., 63)).................................. 10-11

10.3.7 Software and Level n IACK Registers (SWIACKR, L1IACK–L7IACK). 10-15

10.4 Prioritization Between Interrupt Controllers .................................................. 10-16

10.5 Low-Power Wakeup Operation ...................................................................... 10-17

xMCF5282 User’s Manual MOTOROLA

CONTENTS

Paragraph

Number Title Page

Number

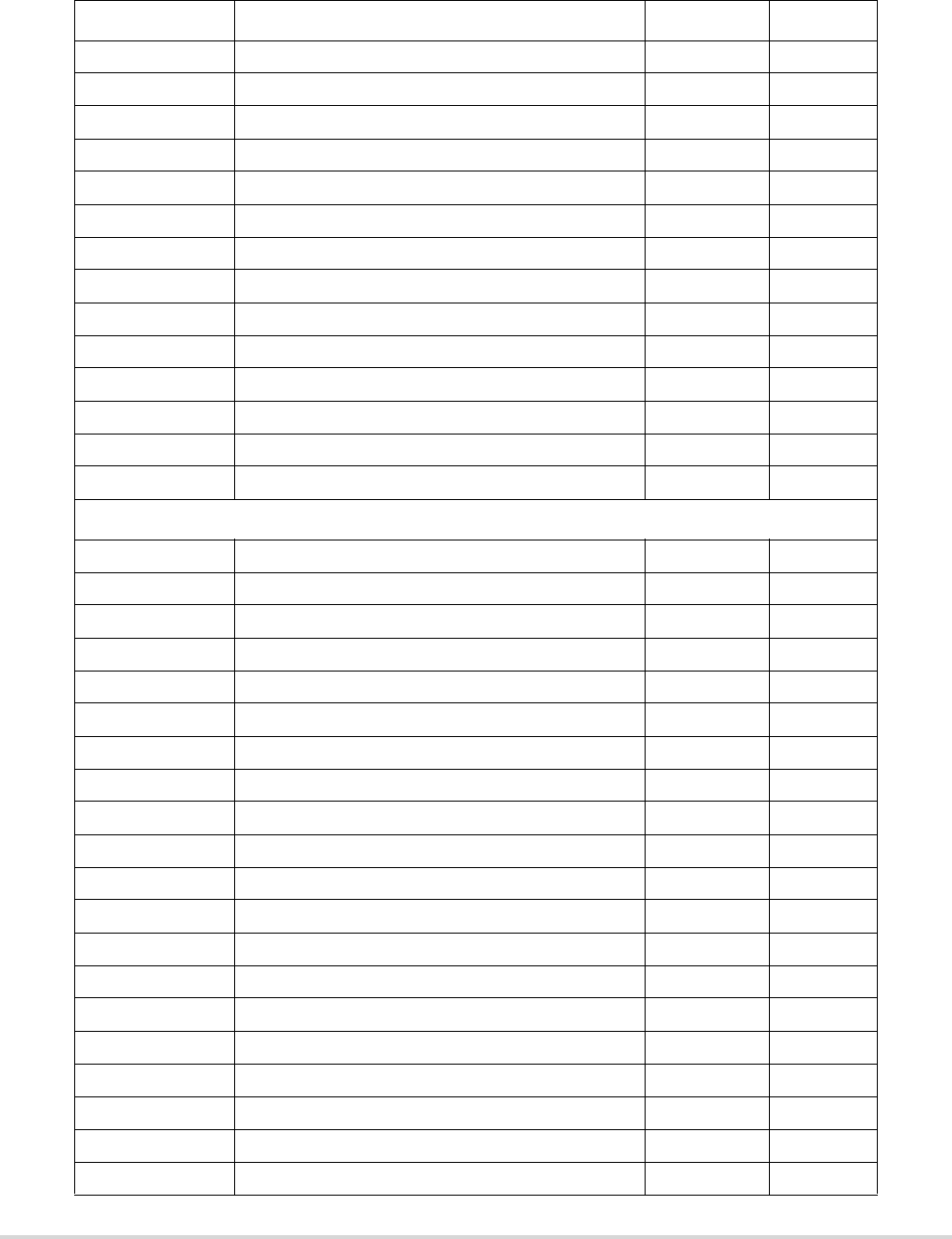

Chapter 11

Edge Port Module (EPORT)

11.1 Introduction....................................................................................................... 11-1

11.2 Low-Power Mode Operation ............................................................................ 11-1

11.3 Interrupt/General-Purpose I/O Pin Descriptions............................................... 11-2

11.4 Memory Map and Registers.............................................................................. 11-3

11.4.1 Memory Map ................................................................................................ 11-3

11.4.2 Registers........................................................................................................ 11-3

Chapter 12

Chip Select Module

12.1 Overview........................................................................................................... 12-1

12.2 Chip Select Module Signals.............................................................................. 12-1

12.3 Chip Select Operation....................................................................................... 12-3

12.3.1 General Chip Select Operation ..................................................................... 12-3

12.4 Chip Select Registers ........................................................................................ 12-5

12.4.1 Chip Select Module Registers....................................................................... 12-6

Chapter 13

External Interface Module (EIM)

13.1 Features............................................................................................................. 13-1

13.2 Bus and Control Signals ................................................................................... 13-1

13.3 Bus Characteristics ........................................................................................... 13-2

13.4 Data Transfer Operation ................................................................................... 13-2

13.4.1 Bus Cycle Execution..................................................................................... 13-3

13.4.2 Data Transfer Cycle States ........................................................................... 13-5

13.4.3 Read Cycle.................................................................................................... 13-6

13.4.4 Write Cycle................................................................................................... 13-8

13.4.5 Fast Termination Cycles ............................................................................... 13-9

13.4.6 Back-to-Back Bus Cycles ........................................................................... 13-10

13.4.7 Burst Cycles................................................................................................ 13-10

13.5 Misaligned Operands ...................................................................................... 13-14

Chapter 14

Signal Descriptions

14.1 Overview........................................................................................................... 14-1

14.1.1 Single-Chip Mode....................................................................................... 14-17

14.1.2 External Boot Mode.................................................................................... 14-17

CONTENTS

Paragraph

Number Title Page

Number

MOTOROLA Contents xi

14.2 MCF5282 External Signals............................................................................. 14-18

14.2.1 External Interface Module (EIM) Signals .................................................. 14-18

14.2.2 SDRAM Controller Signals........................................................................ 14-21

14.2.3 Clock and Reset Signals ............................................................................. 14-22

14.2.4 Chip Configuration Signals ........................................................................ 14-22

14.2.5 External Interrupt Signals ........................................................................... 14-23

14.2.6 Ethernet Module Signals............................................................................. 14-23

14.2.7 Queued Serial Peripheral Interface (QSPI) Signals.................................... 14-25

14.2.8 FlexCAN Signals ........................................................................................ 14-26

14.2.9 I2C Signals .................................................................................................. 14-26

14.2.10 UART Module Signals ............................................................................... 14-26

14.2.11 General Purpose Timer Signals .................................................................. 14-27

14.2.12 DMA Timer Signals.................................................................................... 14-28

14.2.13 Analog-to-Digital Converter Signals.......................................................... 14-29

14.2.14 Debug Support Signals ............................................................................... 14-30

14.2.15 Test Signals................................................................................................. 14-32

14.2.16 Power and Reference Signals ..................................................................... 14-33

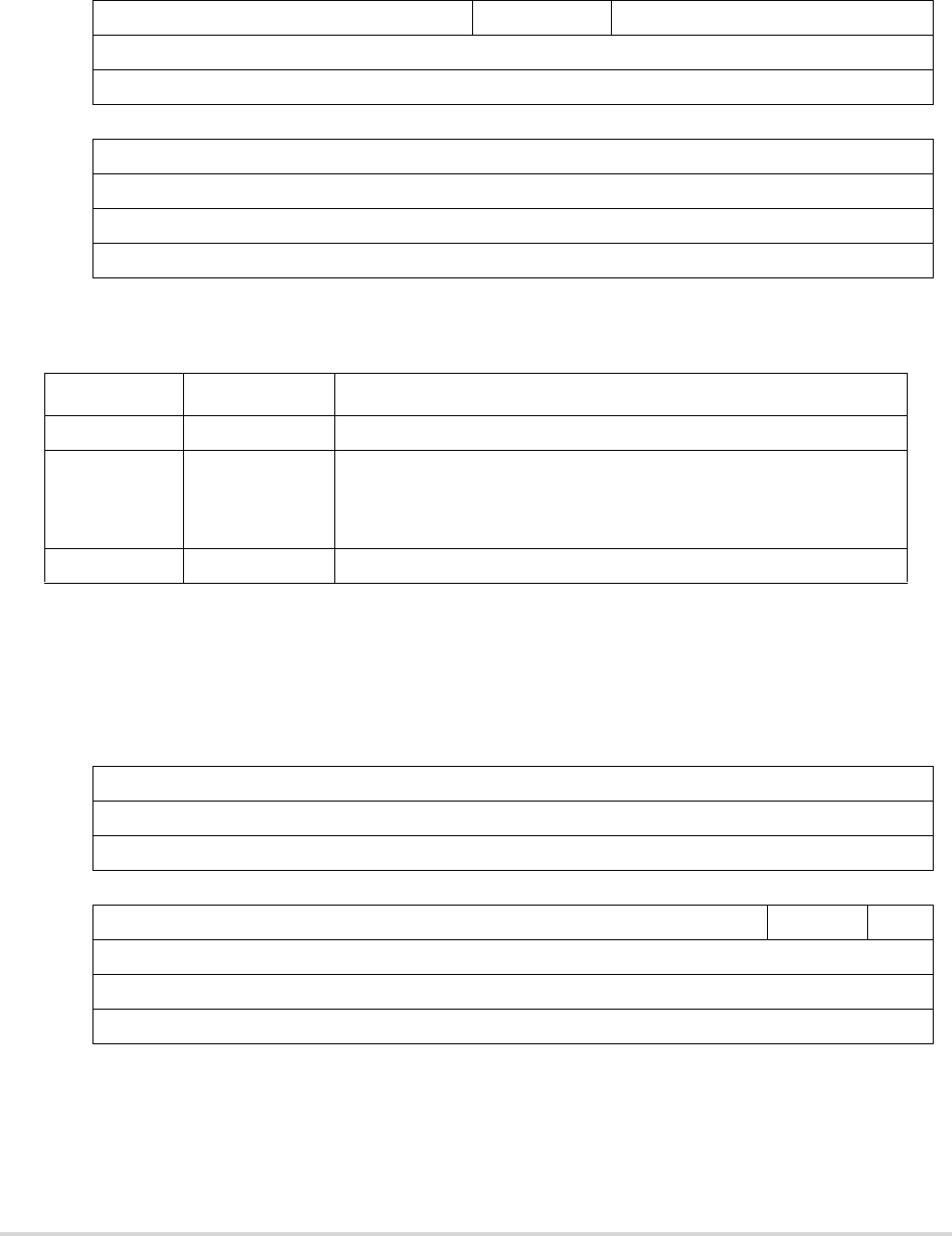

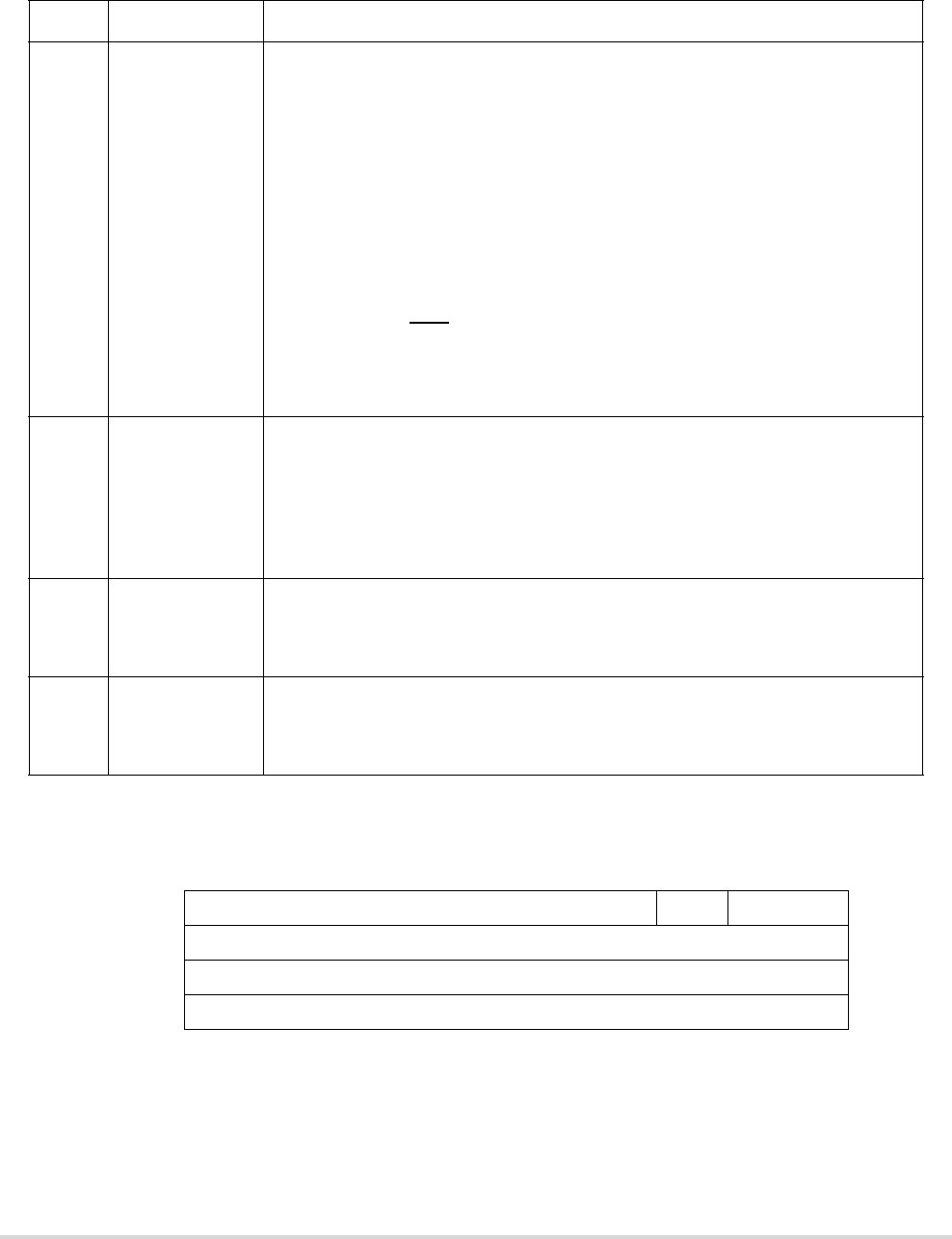

Chapter 15

Synchronous DRAM Controller Module

15.1 Overview........................................................................................................... 15-1

15.1.1 Definitions .................................................................................................... 15-1

15.1.2 Block Diagram and Major Components ....................................................... 15-2

15.2 SDRAM Controller Operation.......................................................................... 15-3

15.2.1 DRAM Controller Signals ............................................................................ 15-4

15.2.2 Memory Map for SDRAMC Registers......................................................... 15-4

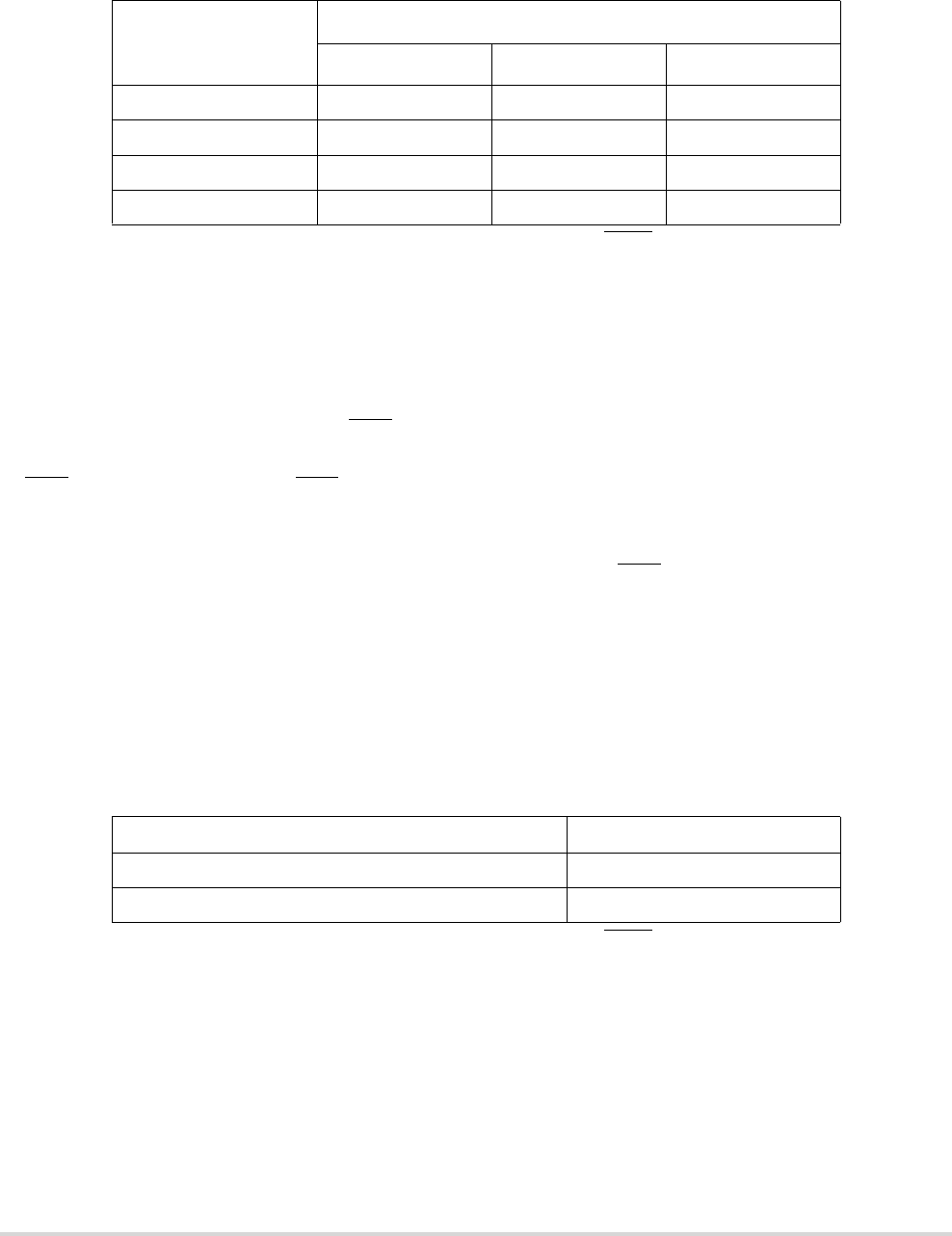

15.2.3 General Synchronous Operation Guidelines................................................. 15-9

15.2.4 Initialization Sequence................................................................................ 15-17

15.3 SDRAM Example ........................................................................................... 15-19

15.3.1 SDRAM Interface Configuration................................................................ 15-20

15.3.2 DCR Initialization....................................................................................... 15-20

15.3.3 DACR Initialization.................................................................................... 15-21

15.3.4 DMR Initialization...................................................................................... 15-22

15.3.5 Mode Register Initialization ....................................................................... 15-23

15.3.6 Initialization Code....................................................................................... 15-24

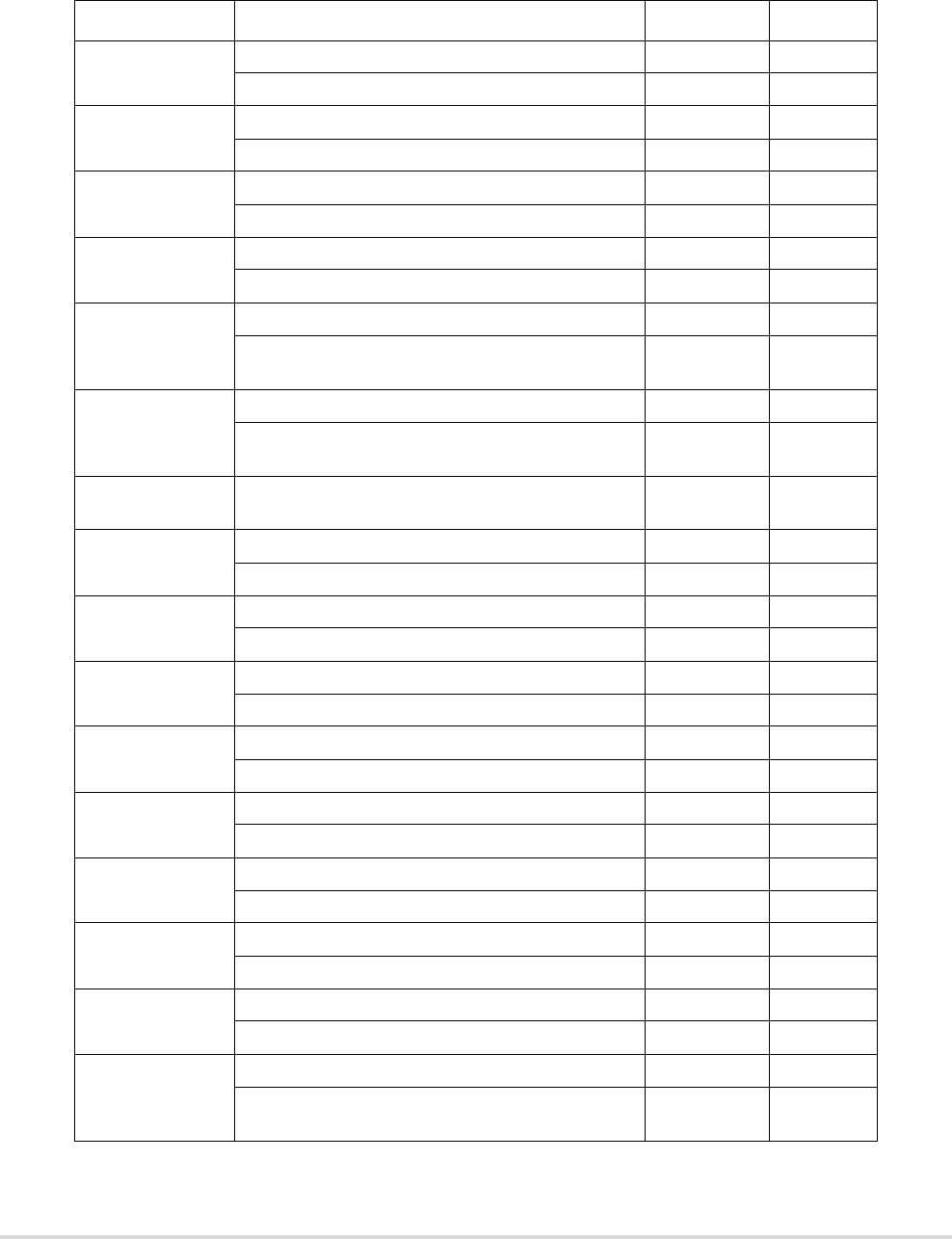

Chapter 16

DMA Controller Module

16.1 Overview........................................................................................................... 16-1

16.1.1 DMA Module Features ................................................................................. 16-2

xii MCF5282 User’s Manual MOTOROLA

CONTENTS

Paragraph

Number Title Page

Number

16.2 DMA Request Control (DMAREQC) .............................................................. 16-3

16.3 DMA Transfer Overview.................................................................................. 16-4

16.4 DMA Controller Module Programming Model................................................ 16-5

16.4.1 Source Address Registers (SAR0–SAR3) .................................................... 16-6

16.4.2 Destination Address Registers (DAR0–DAR3) ........................................... 16-6

16.4.3 Byte Count Registers (BCR0–BCR3) .......................................................... 16-7

16.4.4 DMA Control Registers (DCR0–DCR3)...................................................... 16-8

16.4.5 DMA Status Registers (DSR0–DSR3) ....................................................... 16-10

16.5 DMA Controller Module Functional Description .......................................... 16-11

16.5.1 Transfer Requests (Cycle-Steal and Continuous Modes)........................... 16-11

16.5.2 Data Transfer Modes .................................................................................. 16-12

16.5.3 Channel Initialization and Startup .............................................................. 16-13

16.5.4 Data Transfer .............................................................................................. 16-14

16.5.5 Termination................................................................................................. 16-15

Chapter 17

Fast Ethernet Controller (FEC)

17.1 Overview........................................................................................................... 17-1

17.1.1 Features......................................................................................................... 17-1

17.2 Modes of Operation .......................................................................................... 17-2

17.2.1 Full and Half Duplex Operation ................................................................... 17-2

17.2.2 Interface Options........................................................................................... 17-2

17.2.3 Address Recognition Options ....................................................................... 17-3

17.2.4 Internal Loopback......................................................................................... 17-3

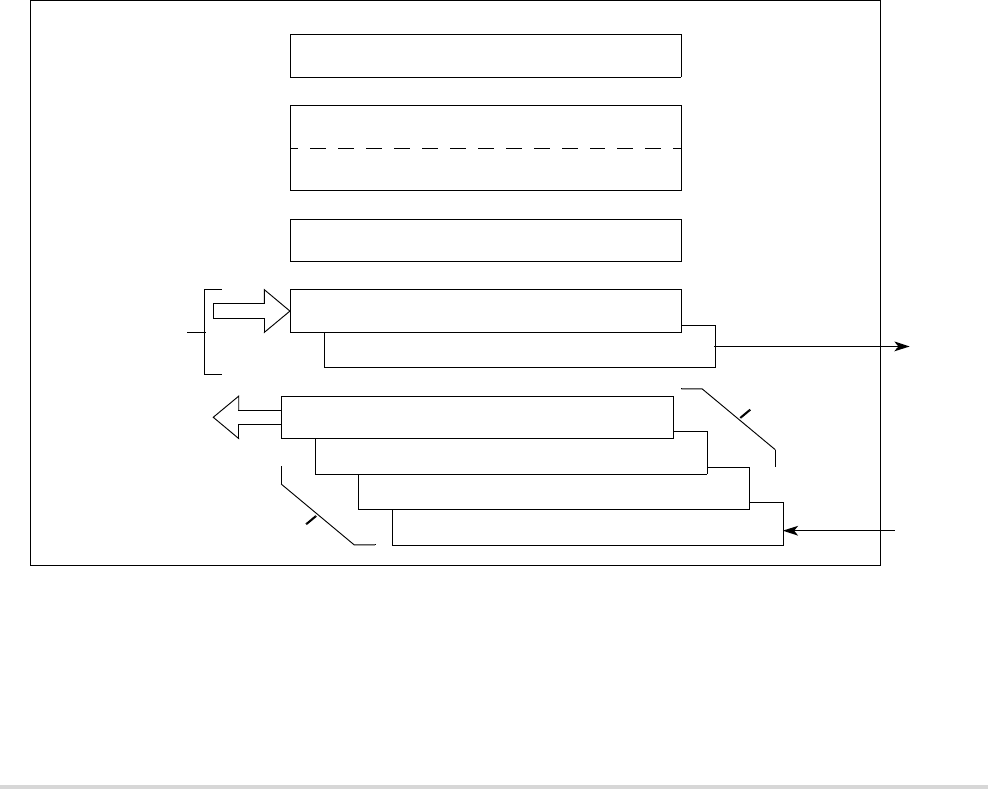

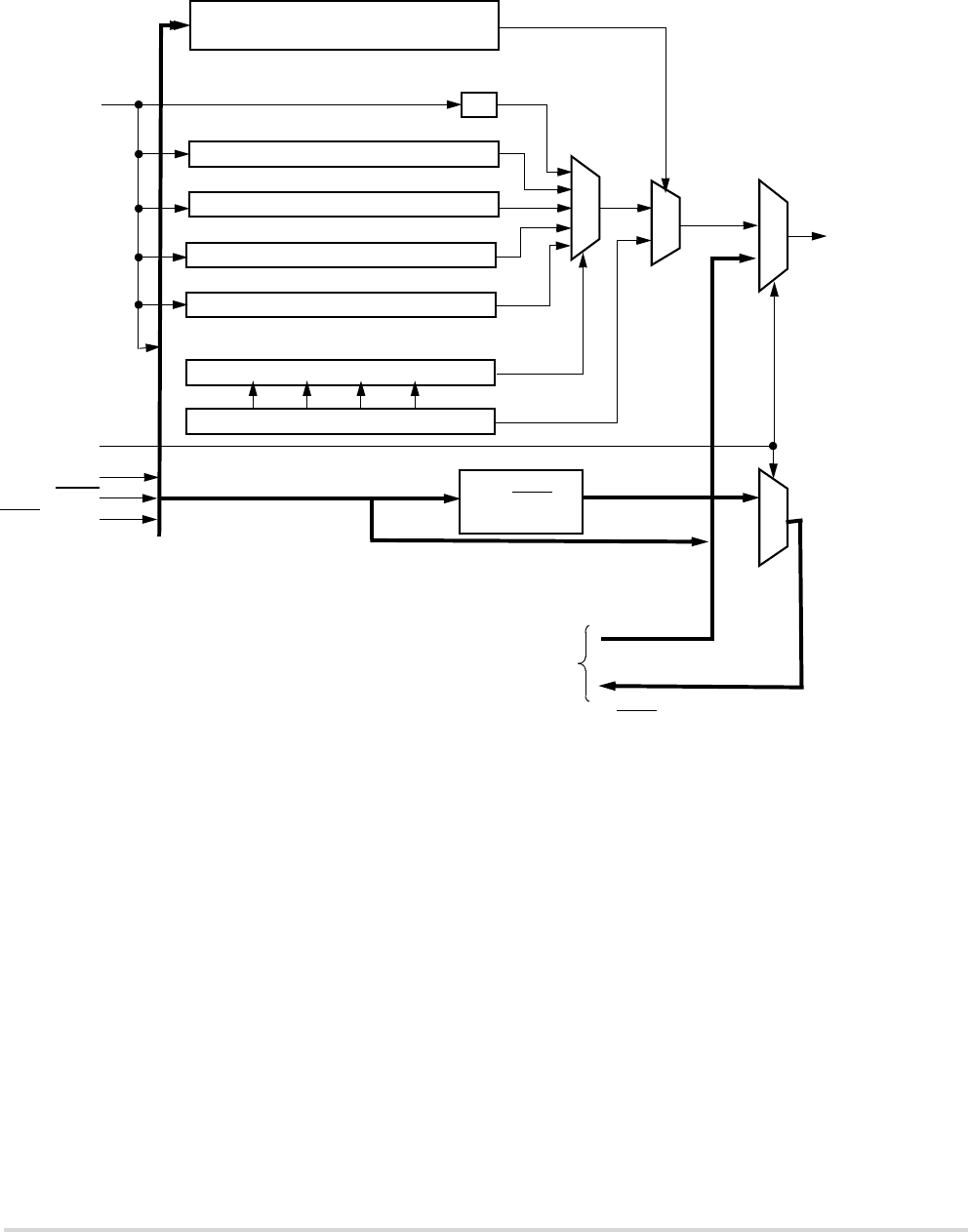

17.3 FEC Top-Level Functional Diagram ................................................................ 17-4

17.4 Functional Description...................................................................................... 17-5

17.4.1 Initialization Sequence.................................................................................. 17-6

17.4.2 User Initialization (Prior to Asserting ECR[ETHER_EN]).......................... 17-6

17.4.3 Microcontroller Initialization........................................................................ 17-7

17.4.4 User Initialization (After Asserting ECR[ETHER_EN]) ............................. 17-7

17.4.5 Network Interface Options............................................................................ 17-8

17.4.6 FEC Frame Transmission ............................................................................. 17-9

17.4.7 FEC Frame Reception................................................................................. 17-10

17.4.8 Ethernet Address Recognition .................................................................... 17-11

17.4.9 Hash Algorithm........................................................................................... 17-13

17.4.10 Full Duplex Flow Control........................................................................... 17-16

17.4.11 Inter-Packet Gap (IPG) Time...................................................................... 17-17

17.4.12 Collision Handling...................................................................................... 17-17

17.4.13 Internal and External Loopback.................................................................. 17-17

17.4.14 Ethernet Error-Handling Procedure............................................................ 17-18

17.5 Programming Model ....................................................................................... 17-20

CONTENTS

Paragraph

Number Title Page

Number

MOTOROLA Contents xiii

17.5.1 Top Level Module Memory Map ............................................................... 17-20

17.5.2 Detailed Memory Map (Control/Status Registers) ..................................... 17-20

17.5.3 MIB Block Counters Memory Map............................................................ 17-21

17.5.4 Registers...................................................................................................... 17-23

17.6 Buffer Descriptors........................................................................................... 17-45

17.6.1 Driver/DMA Operation with Buffer Descriptors........................................ 17-45

17.6.2 Ethernet Receive Buffer Descriptor (RxBD).............................................. 17-47

17.6.3 Ethernet Transmit Buffer Descriptor (TxBD) ............................................ 17-49

Chapter 18

Watchdog Timer Module

18.1 Introduction....................................................................................................... 18-1

18.2 Low-Power Mode Operation ............................................................................ 18-1

18.3 Block Diagram.................................................................................................. 18-2

18.4 Signals............................................................................................................... 18-2

18.5 Memory Map and Registers.............................................................................. 18-2

18.5.1 Memory Map ................................................................................................ 18-2

18.5.2 Registers........................................................................................................ 18-3

Chapter 19

Programmable Interrupt Timer Modules (PIT0–PIT3)

19.1 Overview........................................................................................................... 19-1

19.2 Block Diagram.................................................................................................. 19-1

19.3 Low-Power Mode Operation ............................................................................ 19-2

19.4 Signals............................................................................................................... 19-2

19.5 Memory Map and Registers.............................................................................. 19-3

19.5.1 Memory Map ................................................................................................ 19-3

19.5.2 Registers........................................................................................................ 19-3

19.6 Functional Description...................................................................................... 19-6

19.6.1 Set-and-Forget Timer Operation................................................................... 19-6

19.6.2 Free-Running Timer Operation .................................................................... 19-7

19.6.3 Timeout Specifications ................................................................................. 19-7

19.7 Interrupt Operation ........................................................................................... 19-8

Chapter 20

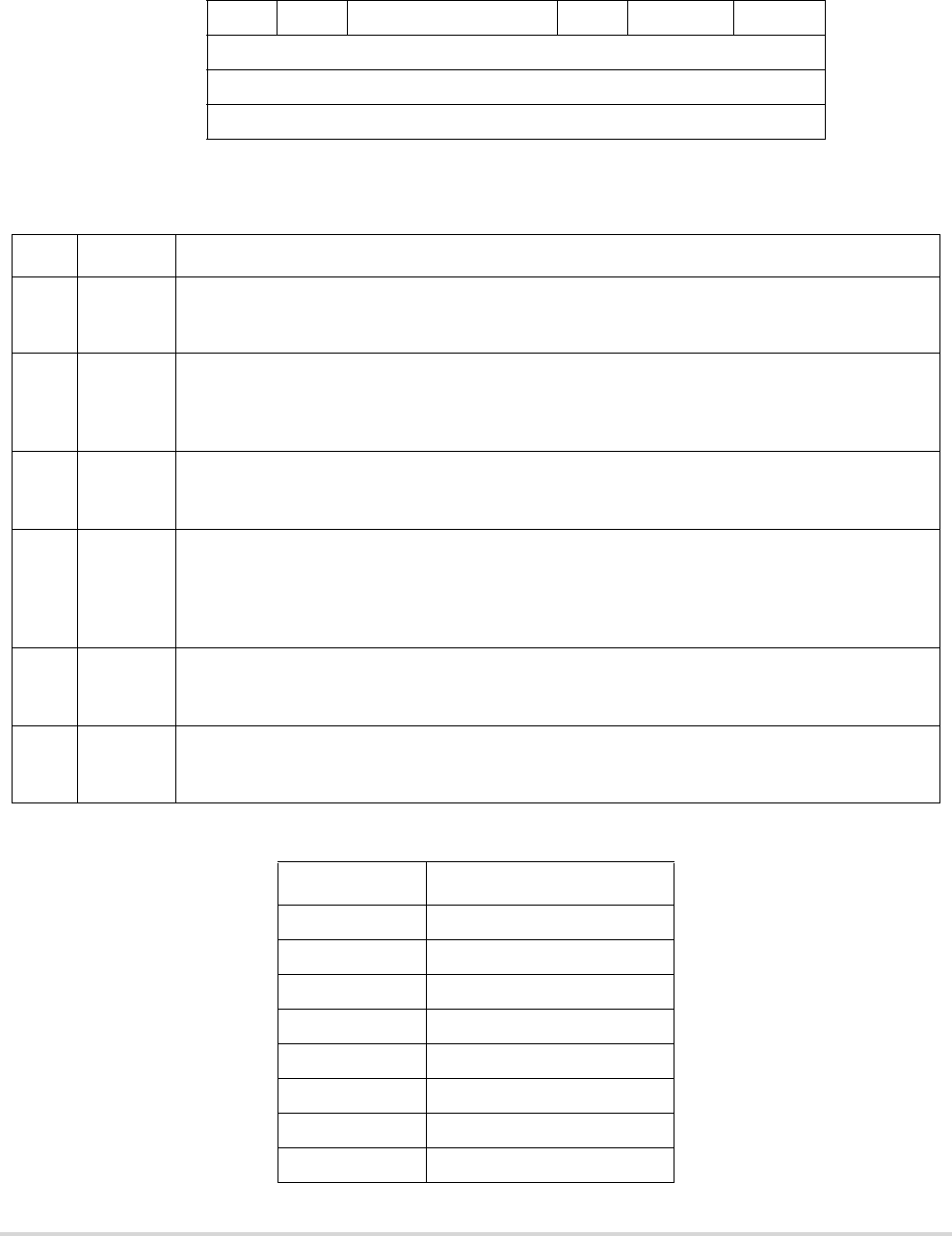

General Purpose Timer Modules

(GPTA and GPTB)

20.1 Features............................................................................................................. 20-1

20.2 Block Diagram.................................................................................................. 20-2

xiv MCF5282 User’s Manual MOTOROLA

CONTENTS

Paragraph

Number Title Page

Number

20.3 Low-Power Mode Operation ............................................................................ 20-3

20.4 Signal Description............................................................................................. 20-3

20.4.1 GPTn[2:0] ..................................................................................................... 20-3

20.4.2 GPTn3........................................................................................................... 20-4

20.4.3 SYNCn.......................................................................................................... 20-4

20.5 Memory Map and Registers.............................................................................. 20-4

20.5.1 GPT Input Capture/Output Compare Select Register (GPTIOS) ................. 20-5

20.5.2 GPT Compare Force Register (GPCFORC)................................................. 20-6

20.5.3 GPT Output Compare 3 Mask Register (GPTOC3M).................................. 20-6

20.5.4 GPT Output Compare 3 Data Register (GPTOC3D).................................... 20-7

20.5.5 GPT Counter Register (GPTCNT) ............................................................... 20-7

20.5.6 GPT System Control Register 1 (GPTSCR1)............................................... 20-8

20.5.7 GPT Toggle-On-Overflow Register (GPTTOV).......................................... 20-9

20.5.8 GPT Control Register 1 (GPTCTL1)............................................................ 20-9

20.5.9 GPT Control Register 2 (GPTCTL2).......................................................... 20-10

20.5.10 GPT Interrupt Enable Register (GPTIE) .................................................... 20-10

20.5.11 GPT System Control Register 2 (GPTSCR2)............................................. 20-11

20.5.12 GPT Flag Register 1 (GPTFLG1)............................................................... 20-12

20.5.13 GPT Flag Register 2 (GPTFLG2)............................................................... 20-12

20.5.14 GPT Channel Registers (GPTCn)............................................................... 20-13

20.5.15 Pulse Accumulator Control Register (GPTPACTL) .................................. 20-13

20.5.16 Pulse Accumulator Flag Register (GPTPAFLG)........................................ 20-14

20.5.17 Pulse Accumulator Counter Register (GPTPACNT) ................................. 20-15

20.5.18 GPT Port Data Register (GPTPORT)......................................................... 20-16

20.5.19 GPT Port Data Direction Register (GPTDDR)........................................... 20-16

20.6 Functional Description.................................................................................... 20-17

20.6.1 Prescaler...................................................................................................... 20-17

20.6.2 Input Capture .............................................................................................. 20-17

20.6.3 Output Compare.......................................................................................... 20-17

20.6.4 Pulse Accumulator...................................................................................... 20-18

20.6.5 Event Counter Mode................................................................................... 20-18

20.6.6 Gated Time Accumulation Mode ............................................................... 20-19

20.6.7 General-Purpose I/O Ports.......................................................................... 20-19

20.7 Reset................................................................................................................ 20-21

20.8 Interrupts......................................................................................................... 20-21

20.8.1 GPT Channel Interrupts (CnF) ................................................................... 20-22

20.8.2 Pulse Accumulator Overflow (PAOVF)..................................................... 20-22

20.8.3 Pulse Accumulator Input (PAIF) ................................................................ 20-22

20.8.4 Timer Overflow (TOF) ............................................................................... 20-22

CONTENTS

Paragraph

Number Title Page

Number

MOTOROLA Contents xv

Chapter 21

DMA Timers (DTIM0–DTIM3)

21.1 Overview........................................................................................................... 21-1

21.1.1 Key Features ................................................................................................. 21-2

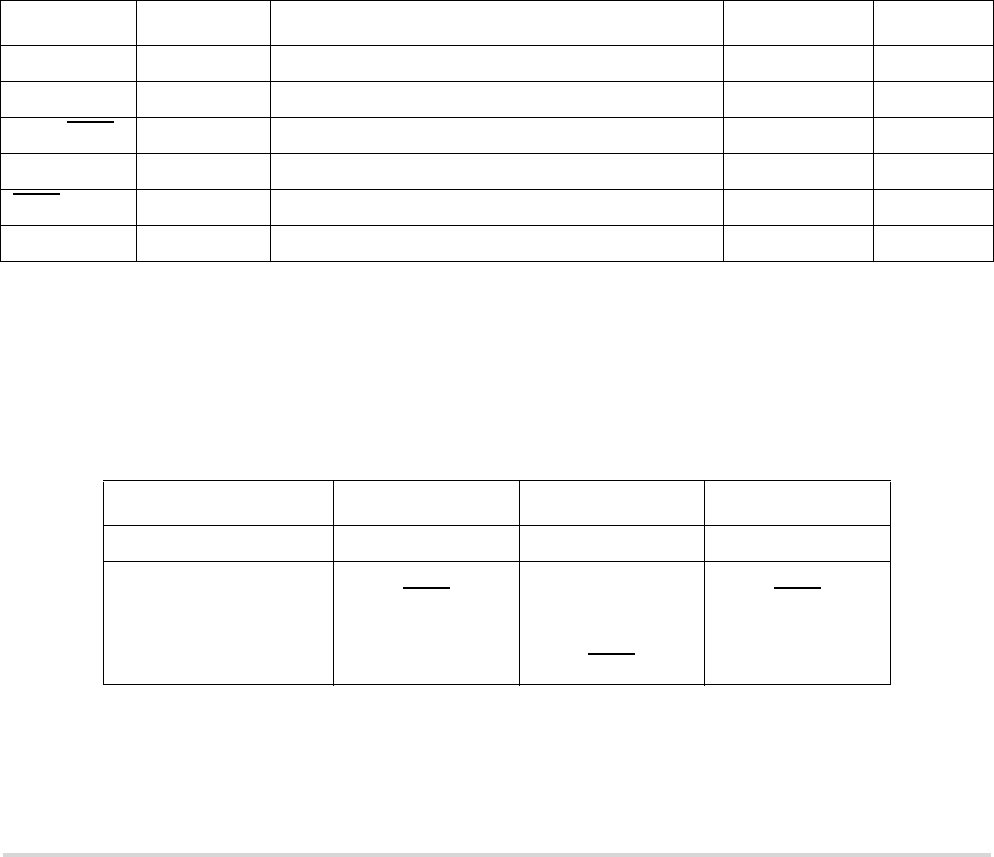

21.2 DMA Timer Programming Model.................................................................... 21-2

21.2.1 Prescaler........................................................................................................ 21-2

21.2.2 Capture Mode ............................................................................................... 21-3

21.2.3 Reference Compare....................................................................................... 21-3

21.2.4 Output Mode................................................................................................. 21-3

21.2.5 Memory Map ................................................................................................ 21-3

21.2.6 DMA Timer Mode Registers (DTMRn)....................................................... 21-4

21.2.7 DMA Timer Extended Mode Registers (DTXMRn).................................... 21-5

21.2.8 DMA Timer Event Registers (DTERn)........................................................ 21-6

21.2.9 DMA Timer Reference Registers (DTRRn)................................................. 21-7

21.2.10 DMA Timer Capture Registers (DTCRn) .................................................... 21-7

21.2.11 DMA Timer Counters (DTCNn) .................................................................. 21-8

21.3 Using the DMA Timer Modules....................................................................... 21-8

21.3.1 Code Example............................................................................................... 21-9

21.3.2 Calculating Time-Out Values ..................................................................... 21-10

Chapter 22

Queued Serial Peripheral Interface

(QSPI) Module

22.1 Overview........................................................................................................... 22-1

22.2 Features............................................................................................................. 22-1

22.3 Module Description .......................................................................................... 22-1

22.3.1 Interface and Signals..................................................................................... 22-2

22.3.2 Internal Bus Interface.................................................................................... 22-3

22.4 Operation .......................................................................................................... 22-3

22.4.1 QSPI RAM.................................................................................................... 22-4

22.4.2 Baud Rate Selection...................................................................................... 22-6

22.4.3 Transfer Delays............................................................................................. 22-7

22.4.4 Transfer Length............................................................................................. 22-8

22.4.5 Data Transfer ................................................................................................ 22-8

22.5 Programming Model ......................................................................................... 22-9

22.5.1 QSPI Mode Register (QMR) ...................................................................... 22-10

22.5.2 QSPI Delay Register (QDLYR) ................................................................. 22-11

22.5.3 QSPI Wrap Register (QWR)....................................................................... 22-12

22.5.4 QSPI Interrupt Register (QIR).................................................................... 22-13

22.5.5 QSPI Address Register (QAR) ................................................................... 22-14

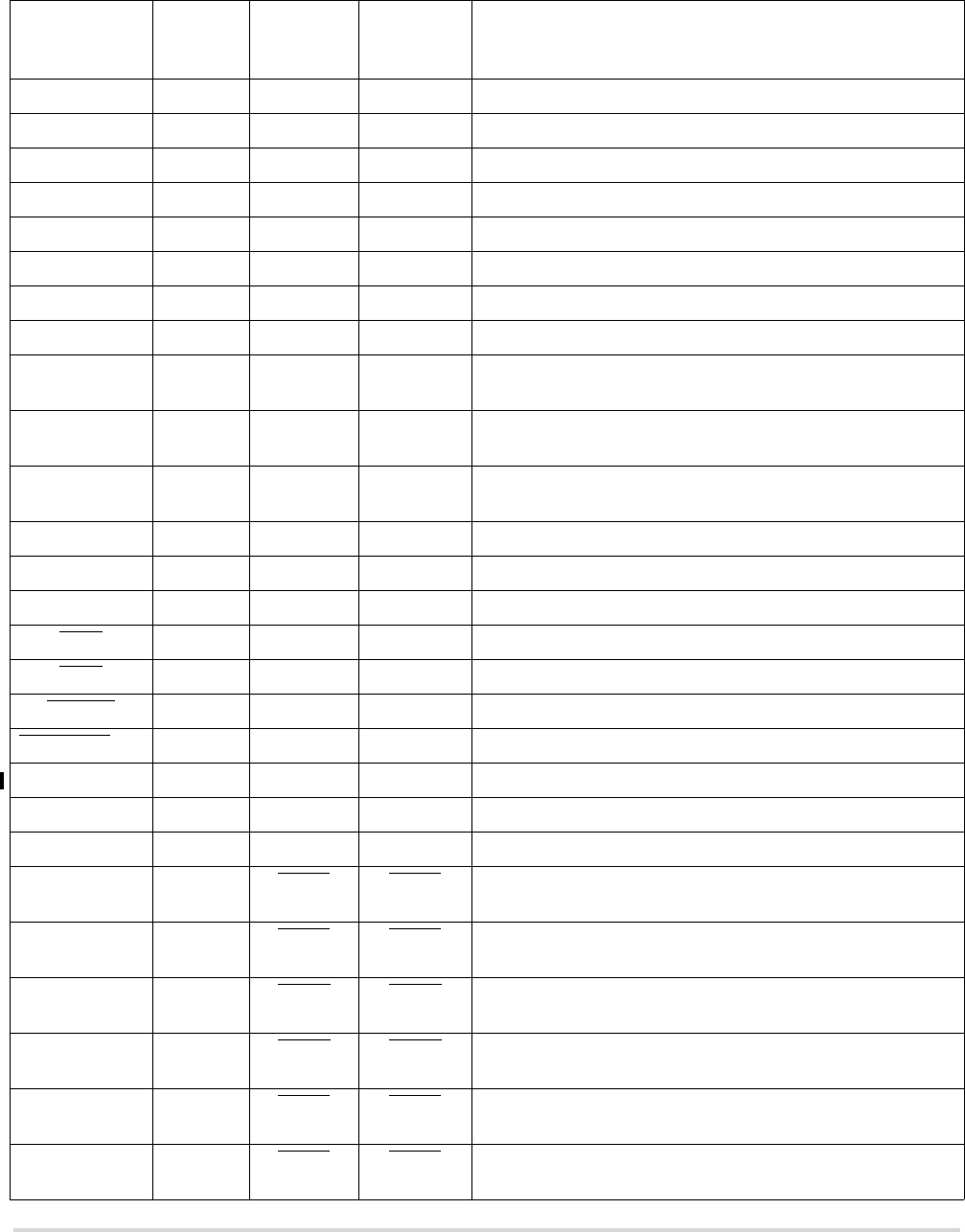

xvi MCF5282 User’s Manual MOTOROLA

CONTENTS

Paragraph

Number Title Page

Number

22.5.6 QSPI Data Register (QDR)......................................................................... 22-14