Quectel Wireless Solutions 201807EG06A LTE-A Cat6 Module User Manual

Quectel Wireless Solutions Company Limited LTE-A Cat6 Module Users Manual

Users Manual

EG06 Manual

LTE-A Module Series

Rev. EG06_Hardware_Design_V1.0

Date: 2018-05-16

Status: Released

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 1 / 89

Our aim is to provide customers with timely and comprehensive service. For any

assistance, please contact our company headquarters:

Quectel Wireless Solutions Co., Ltd.

7th Floor, Hongye Building, No.1801 Hongmei Road, Xuhui District, Shanghai 200233, China

Tel: +86 21 5108 6236

Email: info@quectel.com

Or our local office. For more information, please visit:

http://quectel.com/support/sales.htm

For technical support, or to report documentation errors, please visit:

http://quectel.com/support/technical.htm

Or Email to: support@quectel.com

GENERAL NOTES

QUECTEL OFFERS THE INFORMATION AS A SERVICE TO ITS CUSTOMERS. THE INFORMATION

PROVIDED IS BASED UPON CUSTOMERS’ REQUIREMENTS. QUECTEL MAKES EVERY EFFORT

TO ENSURE THE QUALITY OF THE INFORMATION IT MAKES AVAILABLE. QUECTEL DOES NOT

MAKE ANY WARRANTY AS TO THE INFORMATION CONTAINED HEREIN, AND DOES NOT ACCEPT

ANY LIABILITY FOR ANY INJURY, LOSS OR DAMAGE OF ANY KIND INCURRED BY USE OF OR

RELIANCE UPON THE INFORMATION. ALL INFORMATION SUPPLIED HEREIN IS SUBJECT TO

CHANGE WITHOUT PRIOR NOTICE.

COPYRIGHT

THE INFORMATION CONTAINED HERE IS PROPRIETARY TECHNICAL INFORMATION OF

QUECTEL WIRELESS SOLUTIONS CO., LTD. TRANSMITTING, REPRODUCTION, DISSEMINATION

AND EDITING OF THIS DOCUMENT AS WELL AS UTILIZATION OF THE CONTENT ARE

FORBIDDEN WITHOUT PERMISSION. OFFENDERS WILL BE HELD LIABLE FOR PAYMENT OF

DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT OF A PATENT GRANT OR

REGISTRATION OF A UTILITY MODEL OR DESIGN.

Copyright © Quectel Wireless Solutions Co., Ltd. 2018. All rights reserved

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 2 / 89

About the Document

History

Revision

Date

Author

Description

1.0

2018-04-11

King MA/

Wison HE

Initial

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 3 / 89

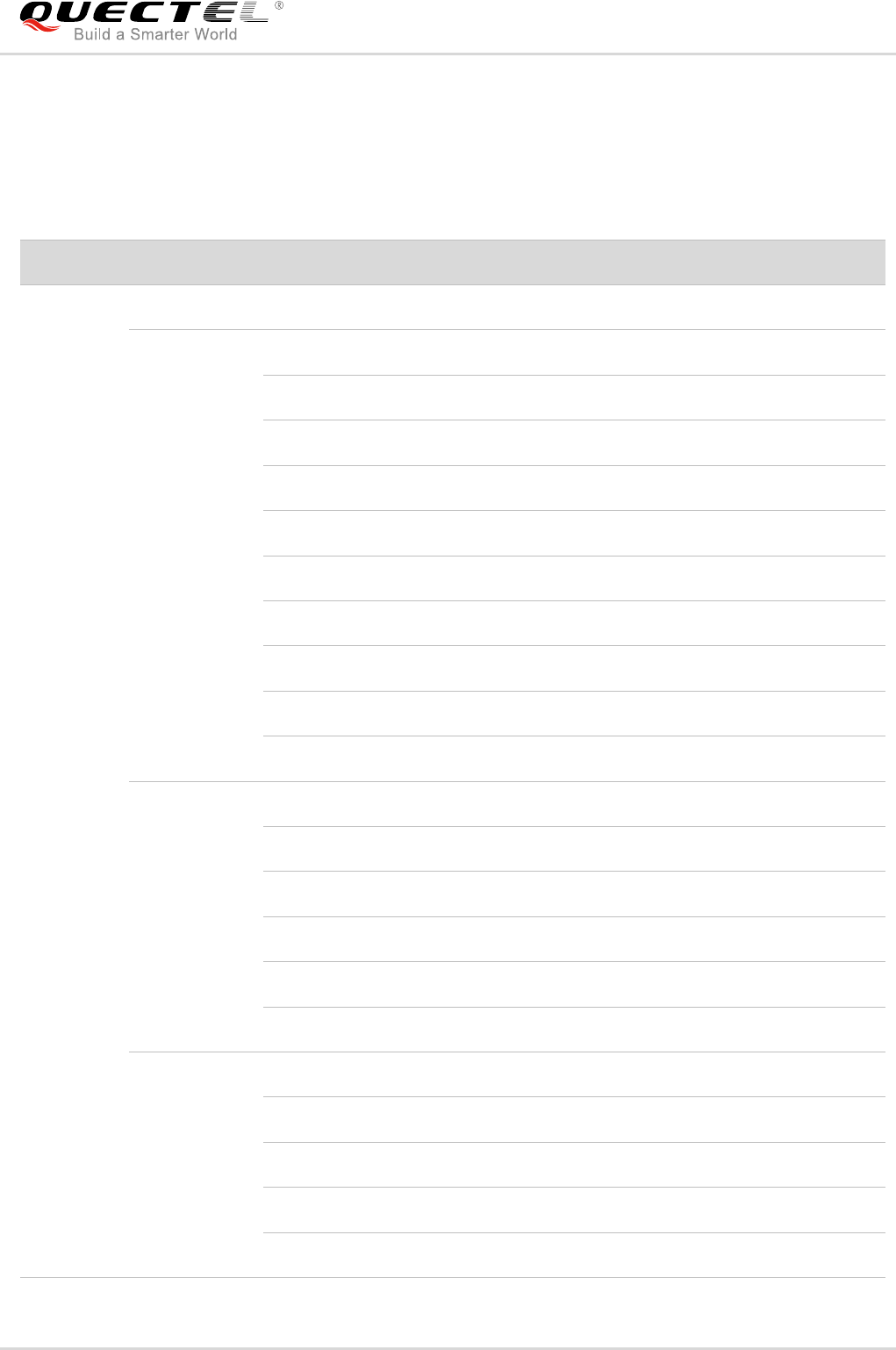

Contents

About the Document ................................................................................................................................... 2

Contents ....................................................................................................................................................... 3

Table Index ................................................................................................................................................... 6

Figure Index ................................................................................................................................................. 8

1 Introduction ........................................................................................................................................ 10

1.1. Safety Information.................................................................................................................... 11

2 Product Concept ................................................................................................................................ 13

2.1. General Description ................................................................................................................. 13

2.2. Key Features ........................................................................................................................... 14

2.3. Functional Diagram ................................................................................................................. 16

2.4. Evaluation Board ..................................................................................................................... 17

3 Application Interface ......................................................................................................................... 18

3.1. General Description ................................................................................................................. 18

3.2. Pin Assignment ........................................................................................................................ 19

3.3. Pin Description ......................................................................................................................... 20

3.4. Operating Modes ..................................................................................................................... 30

3.5. Power Saving ........................................................................................................................... 31

3.5.1. Sleep Mode .................................................................................................................... 31

3.5.1.1. UART Application ................................................................................................. 31

3.5.1.2. USB Application with USB Remote Wakeup Function ........................................ 32

3.5.1.3. USB Application with USB Suspend/Resume and RI Function .......................... 33

3.5.1.4. USB Application without USB Suspend Function ................................................ 33

3.5.2. Airplane Mode ................................................................................................................ 34

3.6. Power Supply ........................................................................................................................... 35

3.6.1. Power Supply Pins ......................................................................................................... 35

3.6.2. Decrease Voltage Drop .................................................................................................. 36

3.6.3. Reference Design for Power Supply .............................................................................. 37

3.6.4. Monitor the Power Supply .............................................................................................. 37

3.7. Turn on and off Scenarios ....................................................................................................... 37

3.7.1. Turn on Module Using the PWRKEY ............................................................................. 37

3.7.2. Turn off Module .............................................................................................................. 39

3.7.2.1. Turn off Module Using the PWRKEY Pin ............................................................ 39

3.7.2.2. Turn off Module Using AT Command .................................................................. 40

3.8. Reset the Module..................................................................................................................... 40

3.9. (U)SIM Interface ...................................................................................................................... 42

3.10. USB Interface .......................................................................................................................... 44

3.11. UART Interfaces ...................................................................................................................... 46

3.12. PCM and I2C Interfaces .......................................................................................................... 49

3.13. ADC Interfaces ........................................................................................................................ 51

3.14. Network Status Indication ........................................................................................................ 52

3.15. STATUS ................................................................................................................................... 53

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 4 / 89

3.16. Behavior of the RI .................................................................................................................... 54

3.17. PCIe Interface* ........................................................................................................................ 55

3.18. WLAN Control Interface* ......................................................................................................... 56

3.19. SD Card Interface .................................................................................................................... 57

3.20. SPI Interface ............................................................................................................................ 59

3.21. USB_BOOT Interface .............................................................................................................. 60

4 GNSS Receiver ................................................................................................................................... 62

4.1. General Description ................................................................................................................. 62

4.2. GNSS Performance ................................................................................................................. 62

4.3. Layout Guidelines .................................................................................................................... 63

5 Antenna Interfaces ............................................................................................................................. 64

5.1. Main/Rx-diversity Antenna Interface ....................................................................................... 64

5.1.1. Pin Definition .................................................................................................................. 64

5.1.2. Operating Frequency ..................................................................................................... 64

5.1.3. Reference Design of RF Antenna Interface ................................................................... 66

5.1.4. Reference Design of RF Layout..................................................................................... 66

5.2. GNSS Antenna Interface ......................................................................................................... 68

5.3. Antenna Installation ................................................................................................................. 69

5.3.1. Antenna Requirement .................................................................................................... 69

5.3.2. Recommended RF Connector for Antenna Installation ................................................. 71

6 Electrical, Reliability and Radio Characteristics ............................................................................ 74

6.1. Absolute Maximum Ratings ..................................................................................................... 74

6.2. Power Supply Ratings ............................................................................................................. 75

6.3. Operation and Storage Temperatures .................................................................................... 75

6.4. Current Consumption .............................................................................................................. 76

6.5. RF Output Power ..................................................................................................................... 78

6.6. RF Receiving Sensitivity .......................................................................................................... 78

6.7. Electrostatic Discharge ............................................................................................................ 79

6.8. Thermal Consideration ............................................................................................................ 80

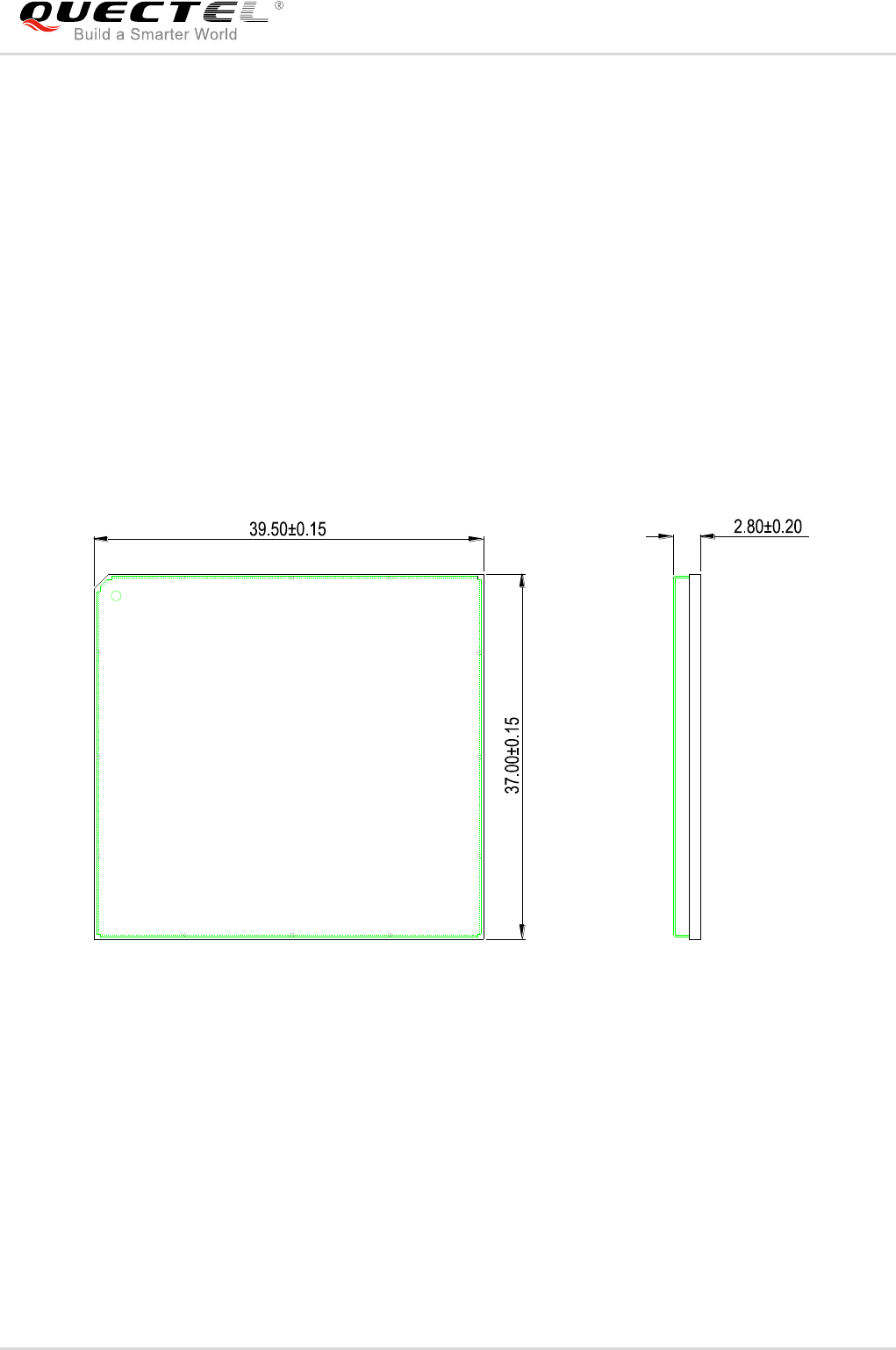

7 Mechanical Dimensions .................................................................................................................... 82

7.1. Mechanical Dimensions of the Module.................................................................................... 82

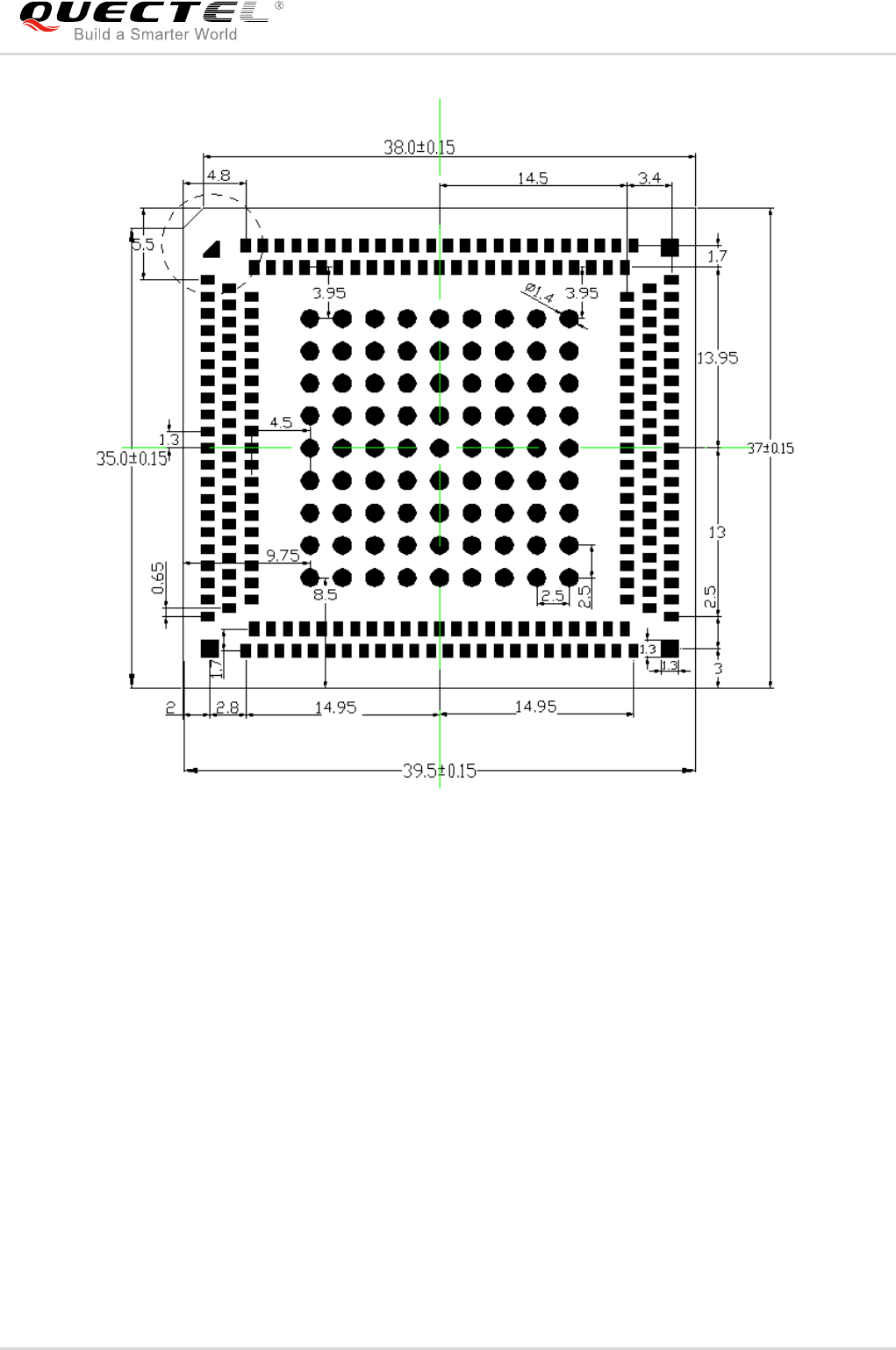

7.2. Recommended Footprint ......................................................................................................... 84

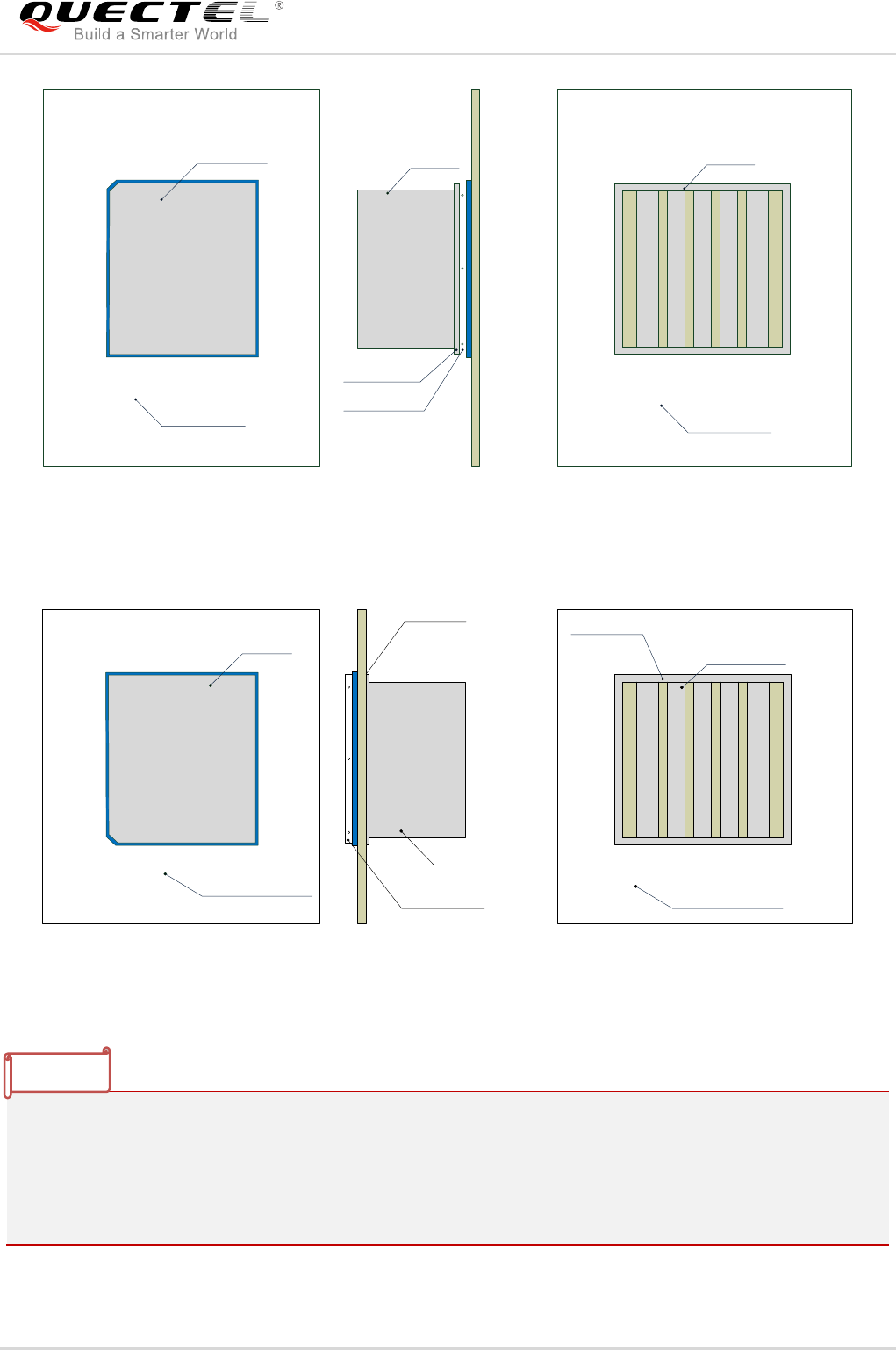

7.3. Design Effect Drawings of the Module .................................................................................... 85

8 Storage, Manufacturing and Packaging .......................................................................................... 86

8.1. Storage .................................................................................................................................... 86

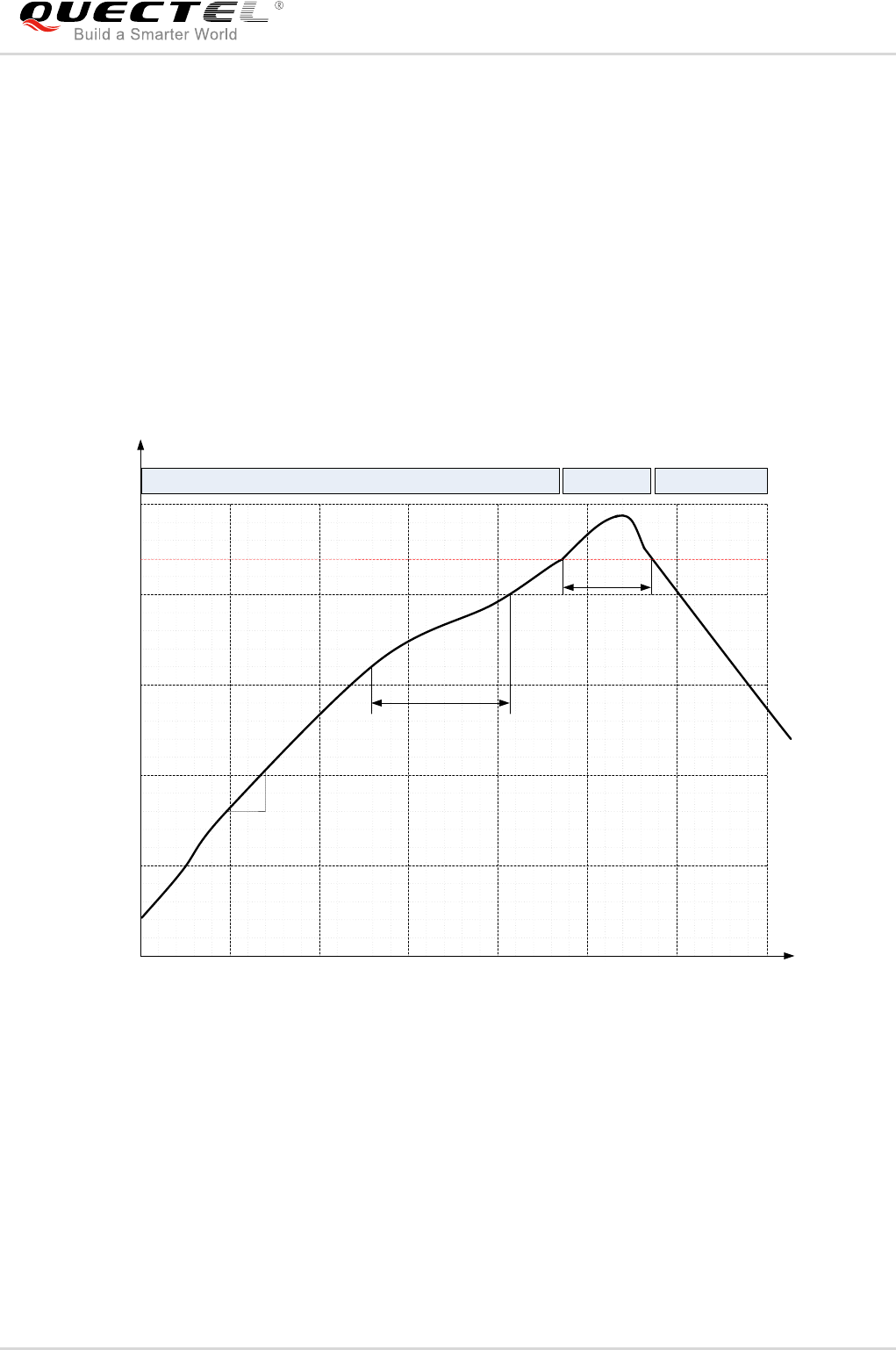

8.2. Manufacturing and Soldering .................................................................................................. 87

8.3. Packaging ................................................................................................................................ 87

9 Appendix A References ..................................................................................................................... 89

10 IC & FCC Requirement ...................................................................................................................... 93

10.1. FCC Regulations: .................................................................................................................... 93

10.2. RF Exposure Information ......................................................................................................... 93

10.3. ISED Notice ............................................................................................................................. 93

10.4. ISED Radiation Exposure Statement ...................................................................................... 94

10.5. IMPORTANT NOTE: ............................................................................................................... 94

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 5 / 89

10.6. USERS MANUAL OF THE END PRODUCT: ......................................................................... 94

10.7. LABEL OF THE END PRODUCT: ........................................................................................... 95

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 6 / 89

Table Index

TABLE 1: FREQUENCY BANDS OF EG06 SERIES MODULE ....................................................................... 13

TABLE 2: KEY FEATURES OF EG06 MODULE .............................................................................................. 14

TABLE 3: I/O PARAMETERS DEFINITION ...................................................................................................... 20

TABLE 4: PIN DESCRIPTION ........................................................................................................................... 20

TABLE 5: OVERVIEW OF OPERATING MODES ............................................................................................ 30

TABLE 6: VBAT AND GND PINS ...................................................................................................................... 35

TABLE 7: PWRKEY PIN DESCRIPTION .......................................................................................................... 38

TABLE 8: RESET_N PIN DESCRIPTION ......................................................................................................... 41

TABLE 9: PIN DEFINITION OF THE (U)SIM INTERFACE ............................................................................... 42

TABLE 10: PIN DESCRIPTION OF USB INTERFACE ..................................................................................... 44

TABLE 11: PIN DEFINITION OF THE MAIN UART INTERFACE .................................................................... 46

TABLE 12: PIN DEFINITION OF THE DEBUG UART INTERFACE ................................................................ 47

TABLE 13: PIN DEFINITION OF THE BT UART INTERFACE......................................................................... 47

TABLE 14: LOGIC LEVELS OF DIGITAL I/O ................................................................................................... 47

TABLE 15: PIN DEFINITION OF PCM AND I2C INTERFACES....................................................................... 50

TABLE 16: PIN DEFINITION OF THE ADC INTERFACES .............................................................................. 51

TABLE 17: CHARACTERISTICS OF ADC INTERFACES ................................................................................ 52

TABLE 18: PIN DEFINITION OF NETWORK CONNECTION STATUS/ACTIVITY INDICATOR .................... 52

TABLE 19: WORKING STATE OF THE NETWORK CONNECTION STATUS/ACTIVITY INDICATOR ......... 52

TABLE 20: PIN DEFINITION OF STATUS........................................................................................................ 53

TABLE 21: BEHAVIOR OF THE RI ................................................................................................................... 54

TABLE 22: PIN DEFINITION OF THE PCIE INTERFACE ................................................................................ 55

TABLE 23: PIN DEFINITION OF WLAN CONTROL INTERFACE ................................................................... 56

TABLE 24: PIN DEFINITION OF THE SD CARDINTERFACE ......................................................................... 57

TABLE 25: PIN DEFINITION OF THE SPI INTERFACE .................................................................................. 59

TABLE 26: PARAMETERS OF SPI INTERFACE TIMING ............................................................................... 60

TABLE 27: PIN DEFINITION OF USB_BOOT INTERFACE ............................................................................. 61

TABLE 28: GNSS PERFORMANCE ................................................................................................................. 62

TABLE 29: PIN DEFINITION OF THE RF ANTENNA ...................................................................................... 64

TABLE 30: MODULE OPERATING FREQUENCIES ....................................................................................... 64

TABLE 31: PIN DEFINITION OF GNSS ANTENNA INTERFACE .................................................................... 68

TABLE 32: GNSS FREQUENCY ...................................................................................................................... 69

TABLE 33: ANTENNA REQUIREMENTS ......................................................................................................... 70

TABLE 34: ABSOLUTE MAXIMUM RATINGS ................................................................................................. 74

TABLE 35: THE MODULE POWER SUPPLY RATINGS.................................................................................. 75

TABLE 36: OPERATION AND STORAGE TEMPERATURES ......................................................................... 75

TABLE 37: EG06-E CURRENT CONSUMPTION ............................................................................................. 76

TABLE 38: RF OUTPUT POWER ..................................................................................................................... 78

TABLE 39: EG06-E CONDUCTED RF RECEIVING SENSITIVITY ................................................................. 79

TABLE 40: ELECTROSTATIC DISCHARGE CHARACTERISTICS ................................................................. 80

TABLE 41: RELATED DOCUMENTS ............................................................................................................... 89

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 8 / 89

Figure Index

FIGURE 1: FUNCTIONAL DIAGRAM ............................................................................................................... 17

FIGURE 2: PIN ASSIGNMENT (TOP VIEW) .................................................................................................... 19

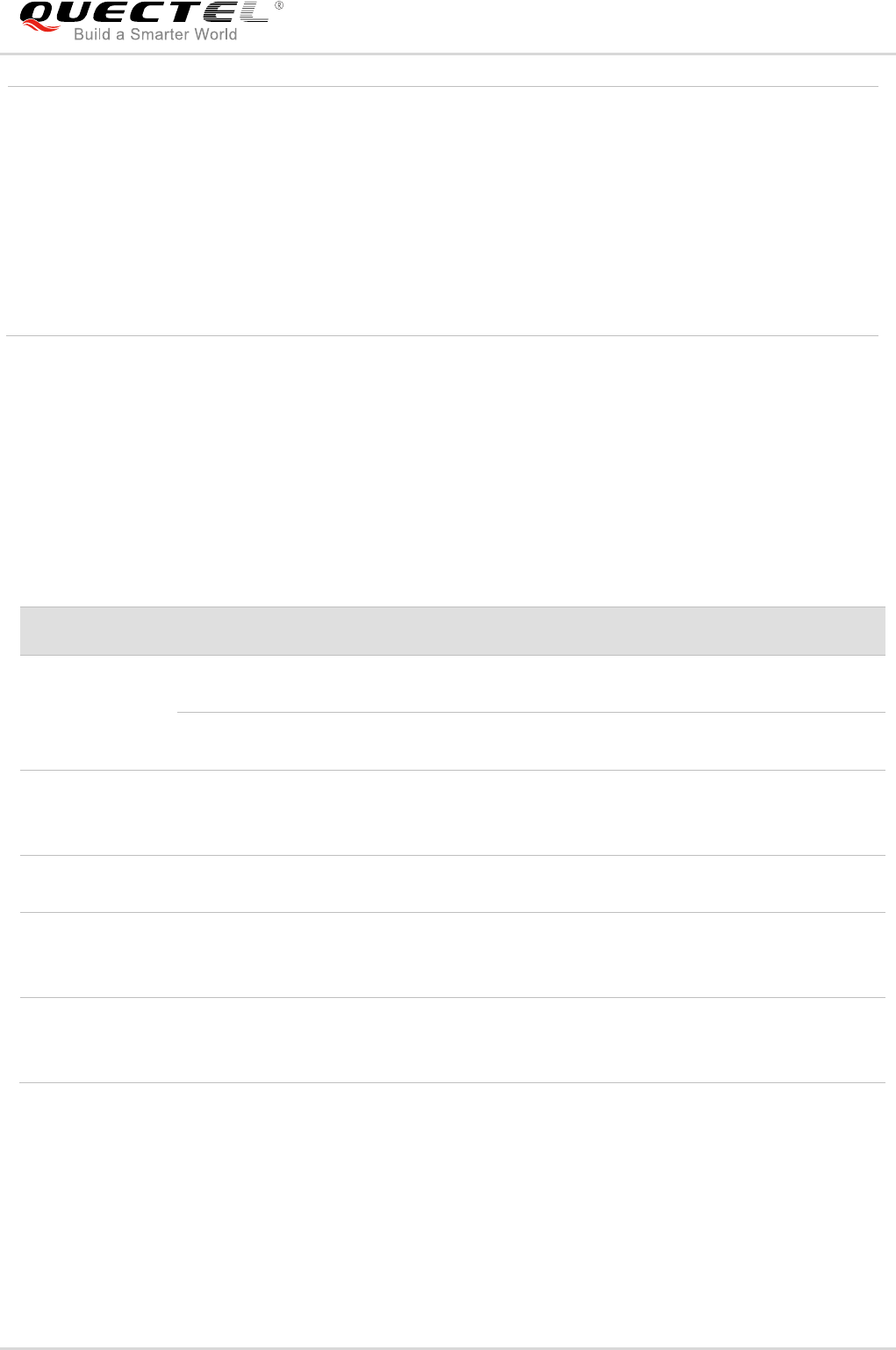

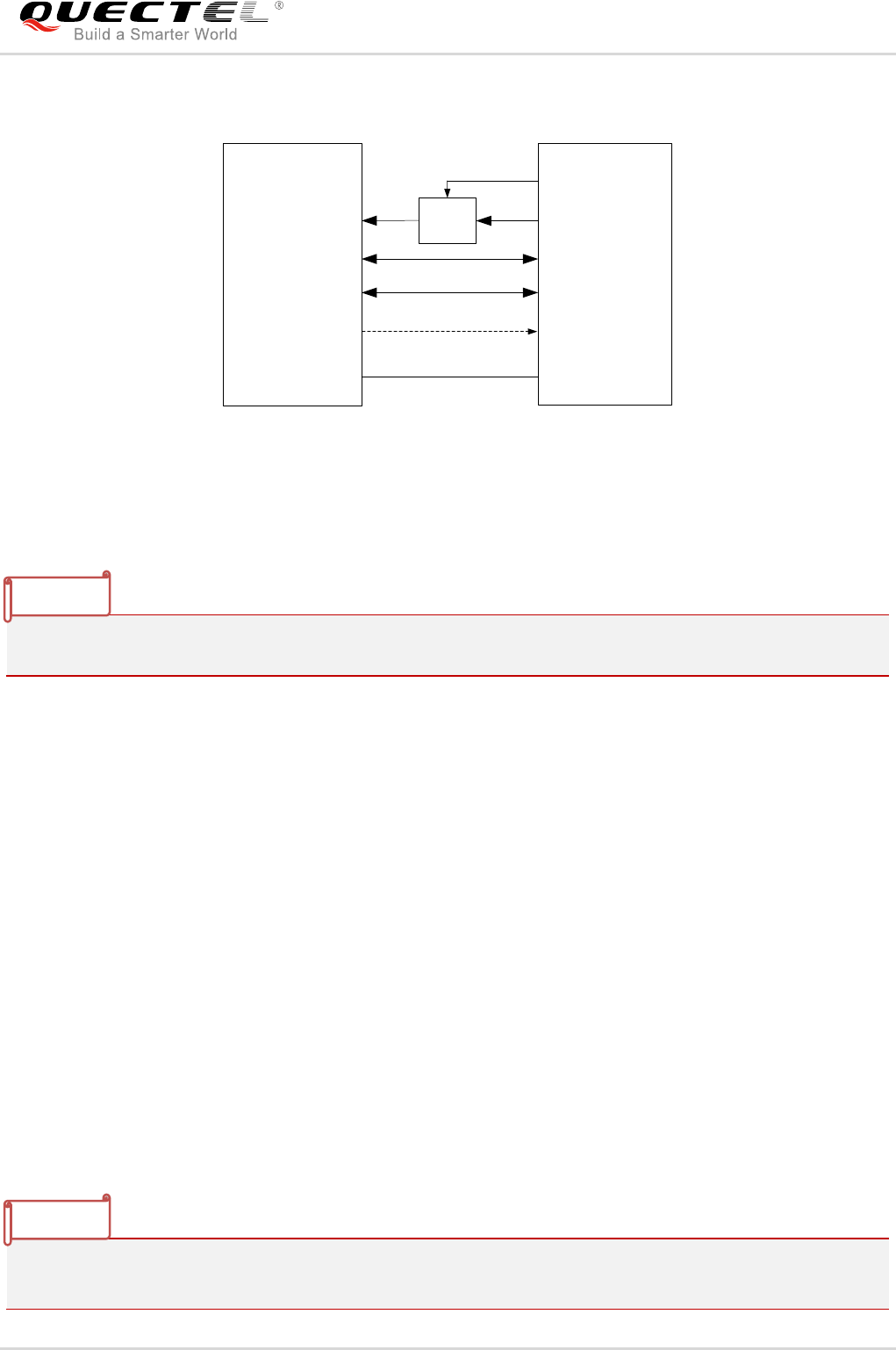

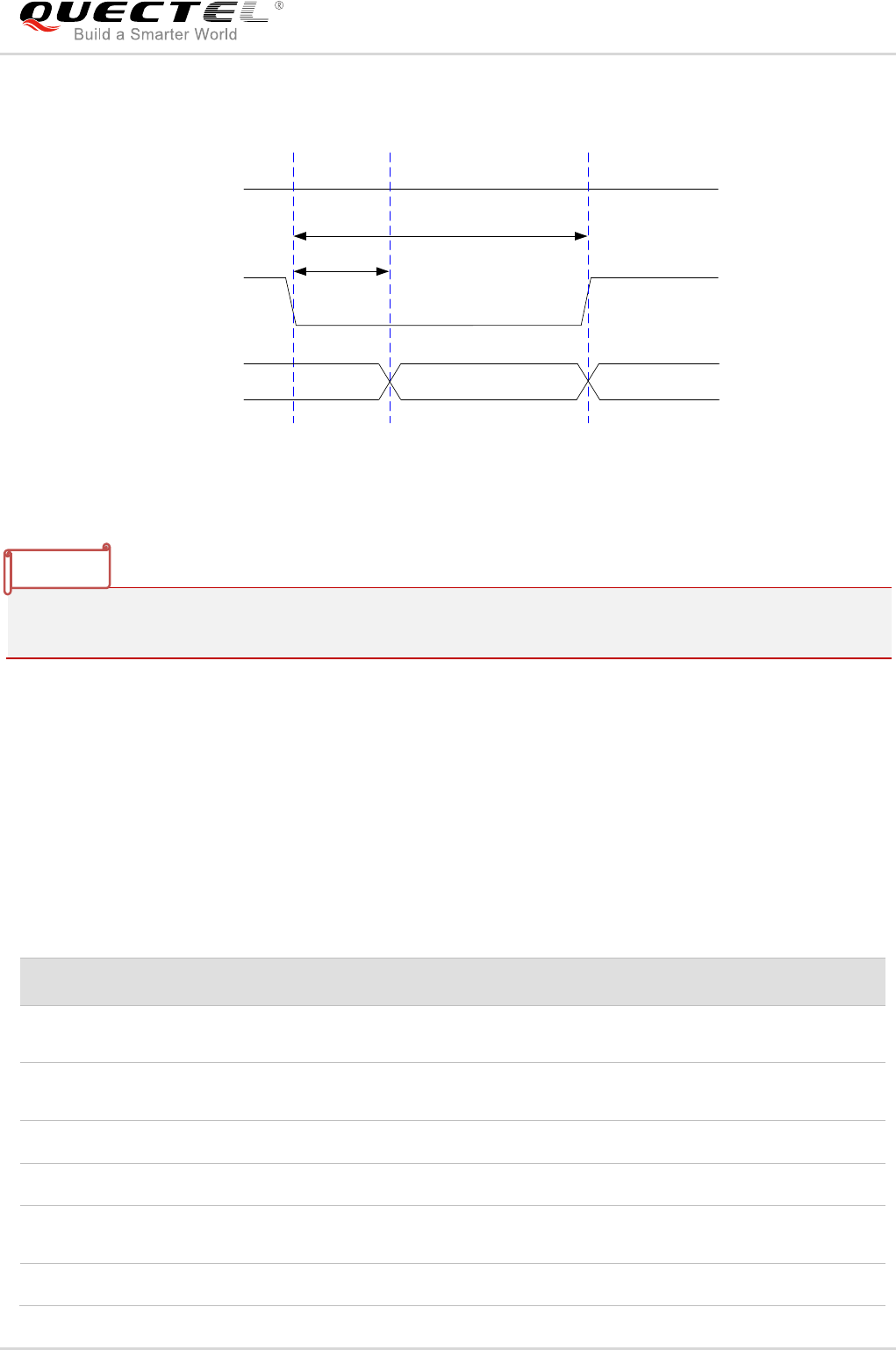

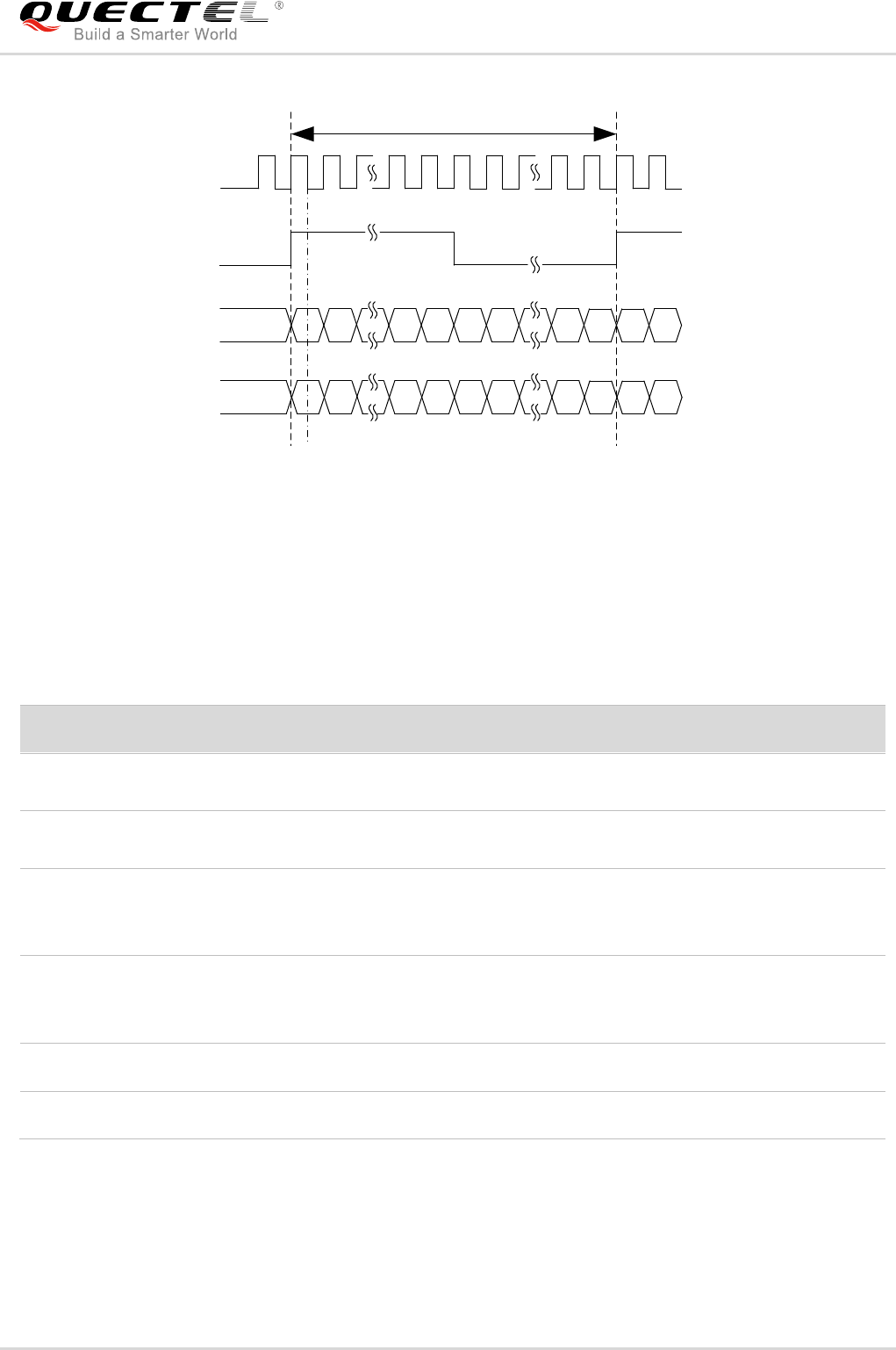

FIGURE 3: DRX RUN TIME AND CURRENT CONSUMPTION IN SLEEP MODE ......................................... 31

FIGURE 4: SLEEP MODE APPLICATION VIA UART ...................................................................................... 32

FIGURE 5: SLEEP MODE APPLICATION WITH USB REMOTE WAKEUP .................................................... 32

FIGURE 6: SLEEP MODE APPLICATION WITH RI ......................................................................................... 33

FIGURE 7: SLEEP MODE APPLICATION WITHOUT SUSPEND FUNCTION................................................ 34

FIGURE 8: POWER SUPPLY LIMITS DURING TX POWER ........................................................................... 36

FIGURE 9: STAR STRUCTURE OF THE POWER SUPPLY ........................................................................... 36

FIGURE 10: REFERENCE CIRCUIT OF POWER SUPPLY ............................................................................ 37

FIGURE 11: TURN ON THE MODULE USING DRIVING CIRCUIT ................................................................. 38

FIGURE 12: TURN ON THE MODULE USING KEYSTROKE ......................................................................... 38

FIGURE 13: TIMING OF TURNING ON MODULE ........................................................................................... 39

FIGURE 14: TIMING OF TURNING OFF MODULE ......................................................................................... 40

FIGURE 15: REFERENCE CIRCUIT OF RESET_N BY USING DRIVING CIRCUIT ...................................... 41

FIGURE 16: REFERENCE CIRCUIT OF RESET_N BY USING BUTTON ...................................................... 41

FIGURE 17: TIMING OF RESETTING MODULE ............................................................................................. 42

FIGURE 18: REFERENCE CIRCUIT OF (U)SIM INTERFACE WITH AN 8-PIN (U)SIM CARD CONNECTOR

................................................................................................................................................................... 43

FIGURE 19: REFERENCE CIRCUIT OF (U)SIM INTERFACE WITH A 6-PIN (U)SIM CARD CONNECTOR 43

FIGURE 20: REFERENCE CIRCUIT OF USB APPLICATION ......................................................................... 45

FIGURE 21: REFERENCE CIRCUIT WITH TRANSLATOR CHIP ................................................................... 48

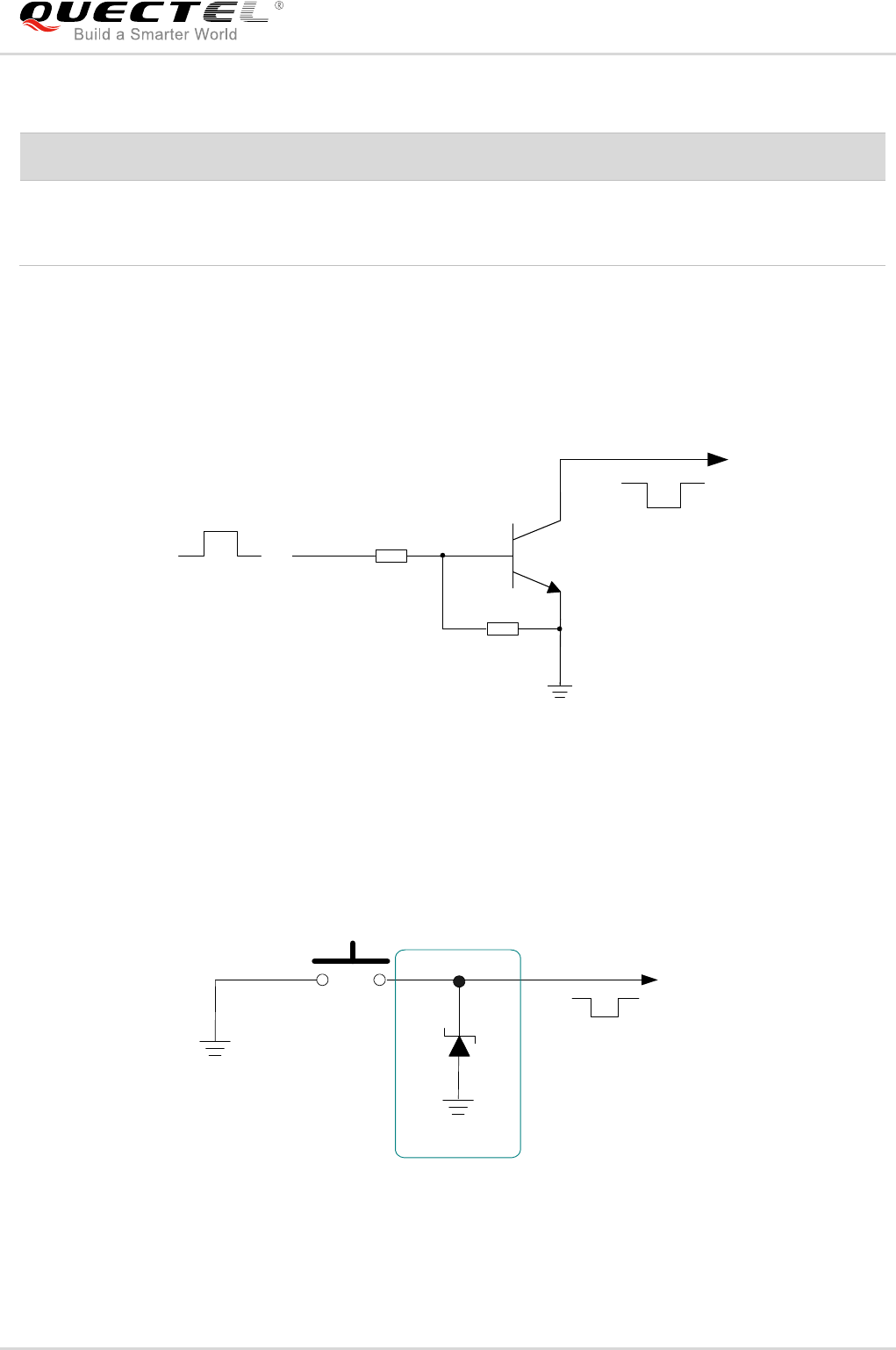

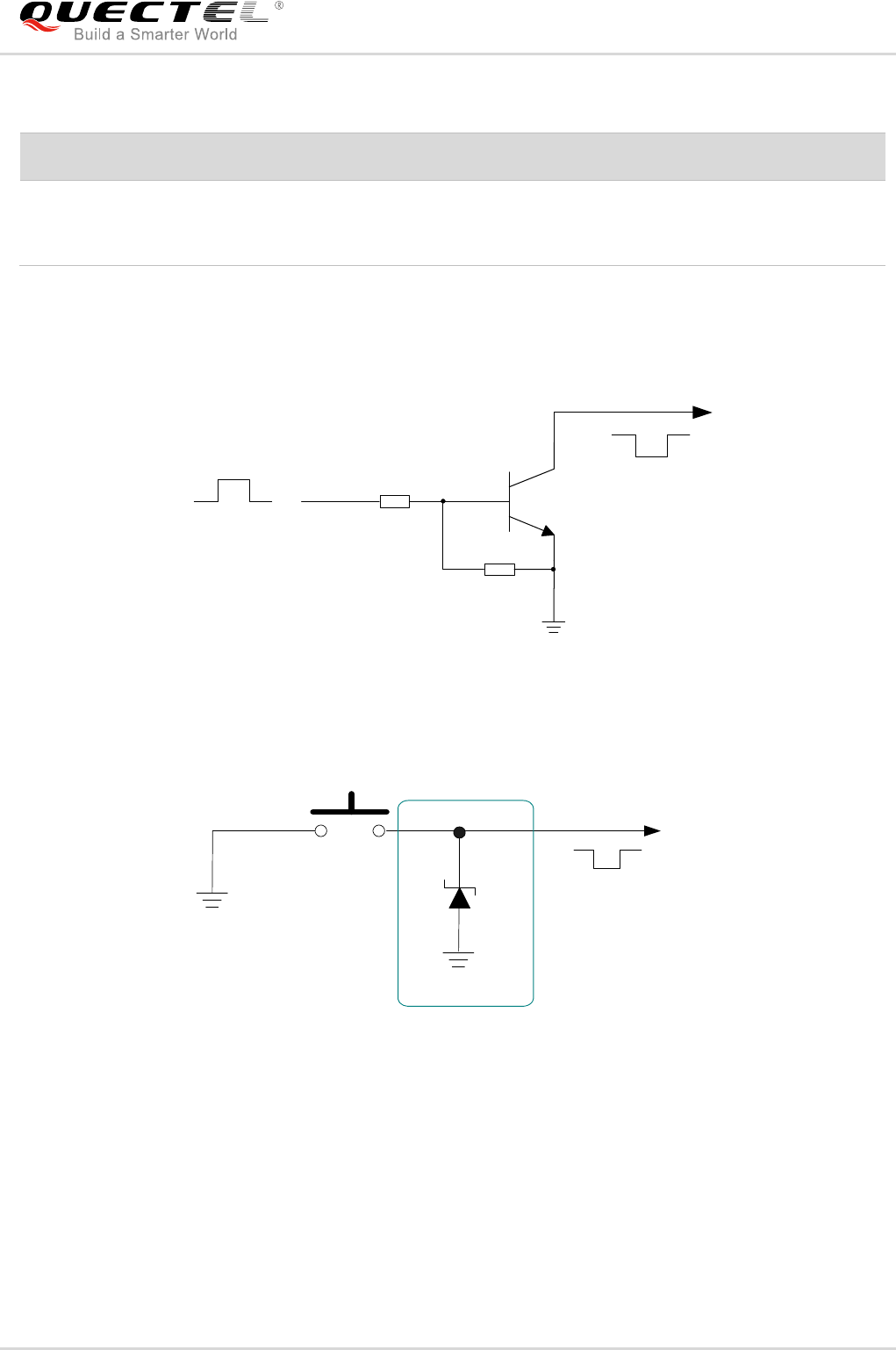

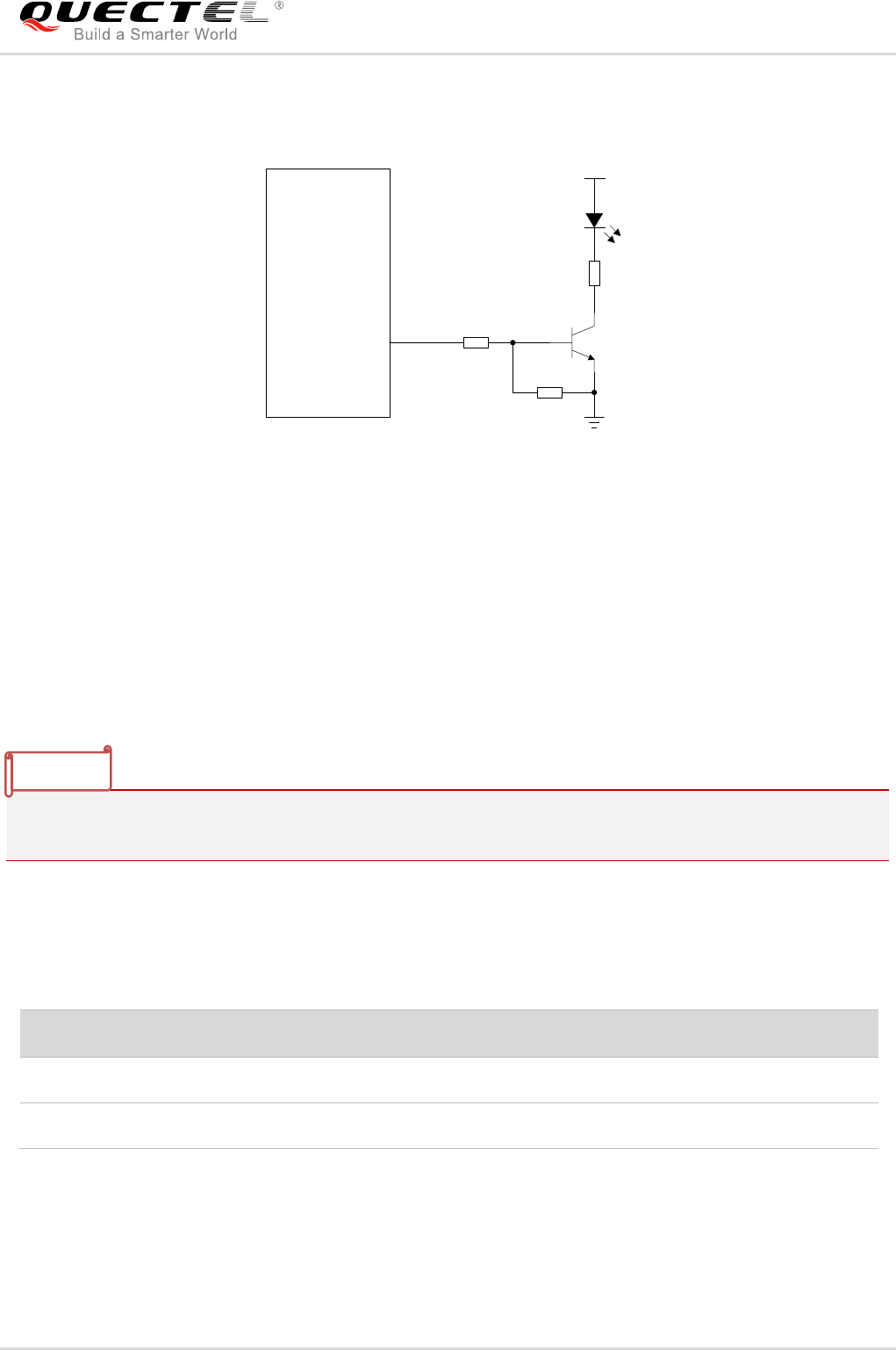

FIGURE 22: REFERENCE CIRCUIT WITH TRANSISTOR CIRCUIT .............................................................. 48

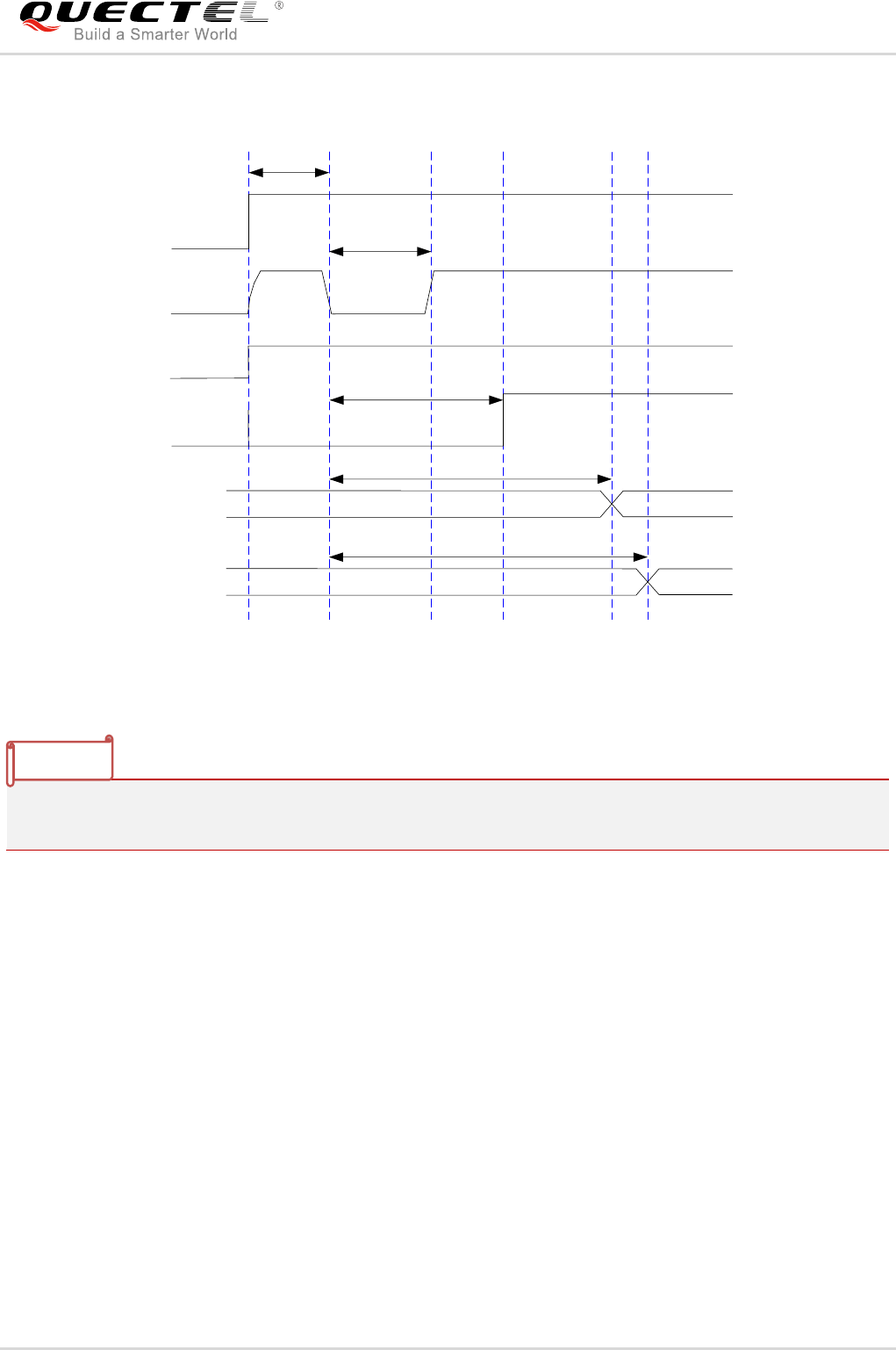

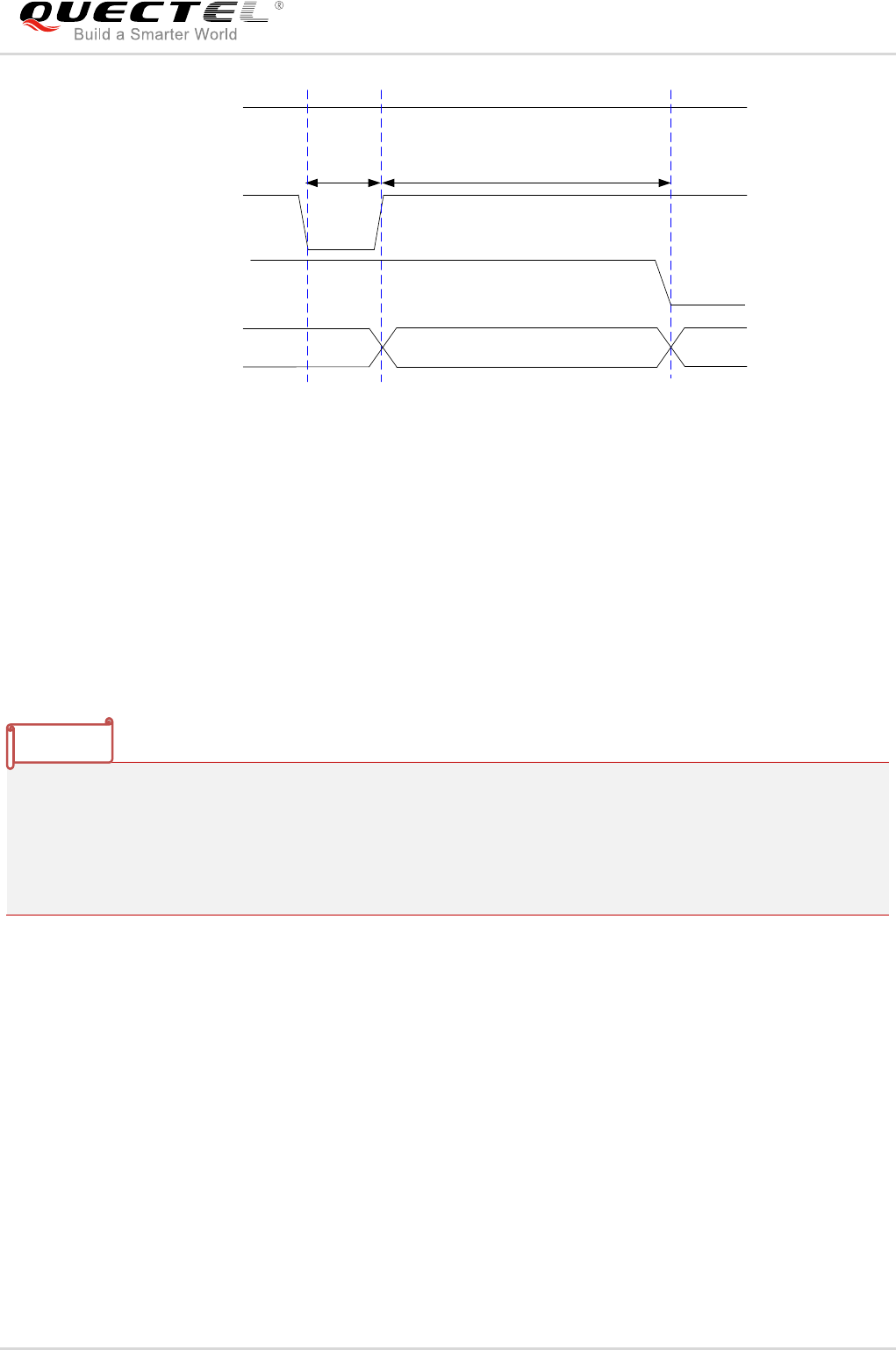

FIGURE 23: PRIMARY MODE TIMING ............................................................................................................ 49

FIGURE 24: AUXILIARY MODE TIMING .......................................................................................................... 50

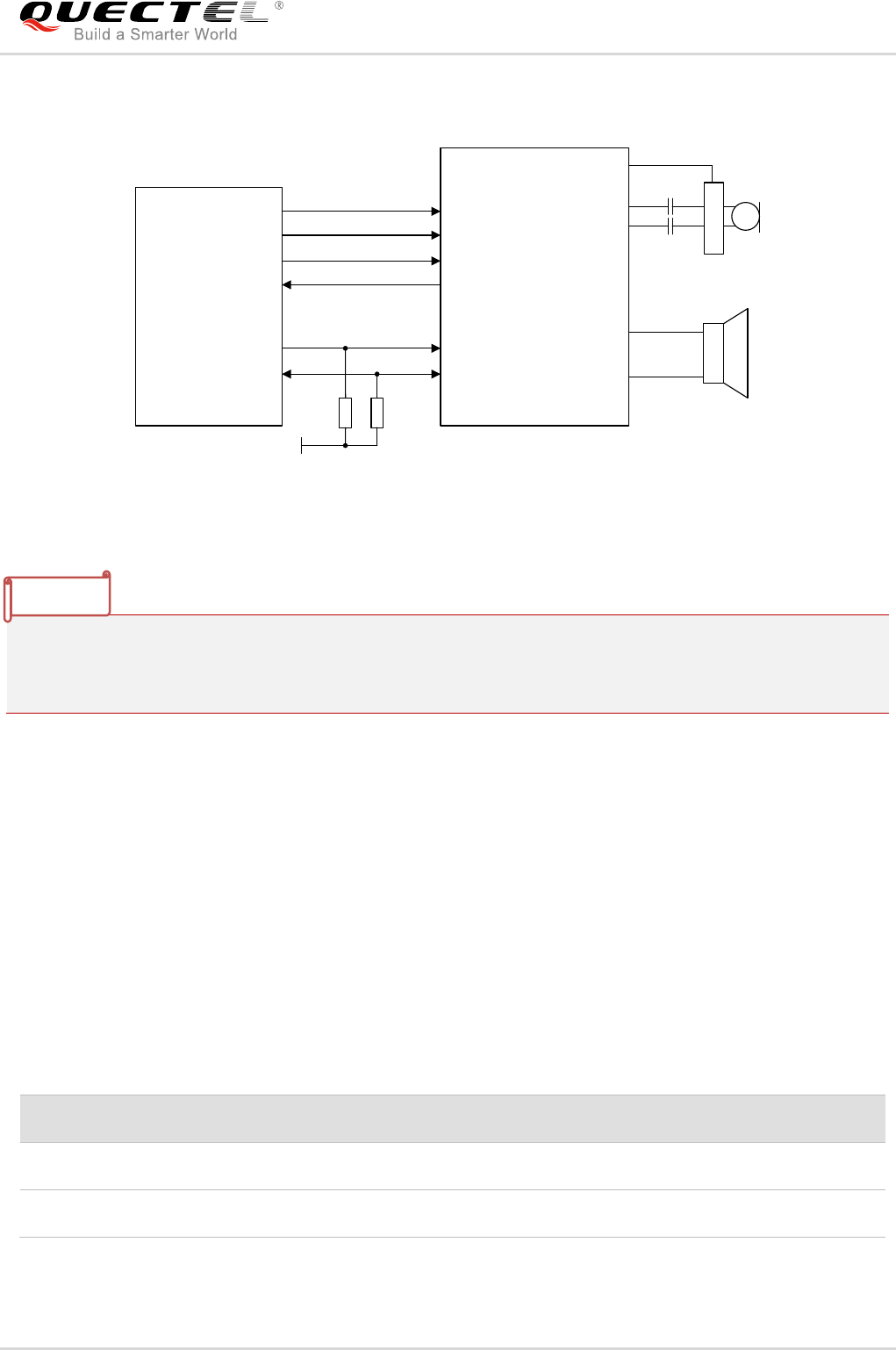

FIGURE 25: REFERENCE CIRCUIT OF PCM APPLICATION WITH AUDIO CODEC ................................... 51

FIGURE 26: REFERENCE CIRCUIT OF THE NETWORK INDICATOR ......................................................... 53

FIGURE 27: REFERENCE CIRCUITS OF STATUS ........................................................................................ 54

FIGURE 28: REFERENCE CIRCUIT OF SD CARD APPLICATION ................................................................ 58

FIGURE 29: SPI INTERFACE TIMING ............................................................................................................. 59

FIGURE 30: SPI INTERFACE REFERENCE CIRCUIT WITH A LEVEL TRANSLATOR ................................ 60

FIGURE 31: REFERENCE CIRCUIT OF USB_BOOT INTERFACE ................................................................ 61

FIGURE 32: REFERENCE CIRCUIT OF RF ANTENNA INTERFACE ............................................................ 66

FIGURE 33: MICROSTRIP LINE DESIGN ON A 2-LAYER PCB ..................................................................... 67

FIGURE 34: COPLANAR WAVEGUIDE LINE DESIGN ON A 2-LAYER PCB ................................................. 67

FIGURE 35: COPLANAR WAVEGUIDE LINE DESIGN ON A 4-LAYER PCB (LAYER 3 AS REFERENCE

GROUND) .................................................................................................................................................. 67

FIGURE 36: COPLANAR WAVEGUIDE LINE DESIGN ON A 4-LAYER PCB (LAYER 4 AS REFERENCE

GROUND) .................................................................................................................................................. 68

FIGURE 37: REFERENCE CIRCUIT OF GNSS ANTENNA............................................................................. 69

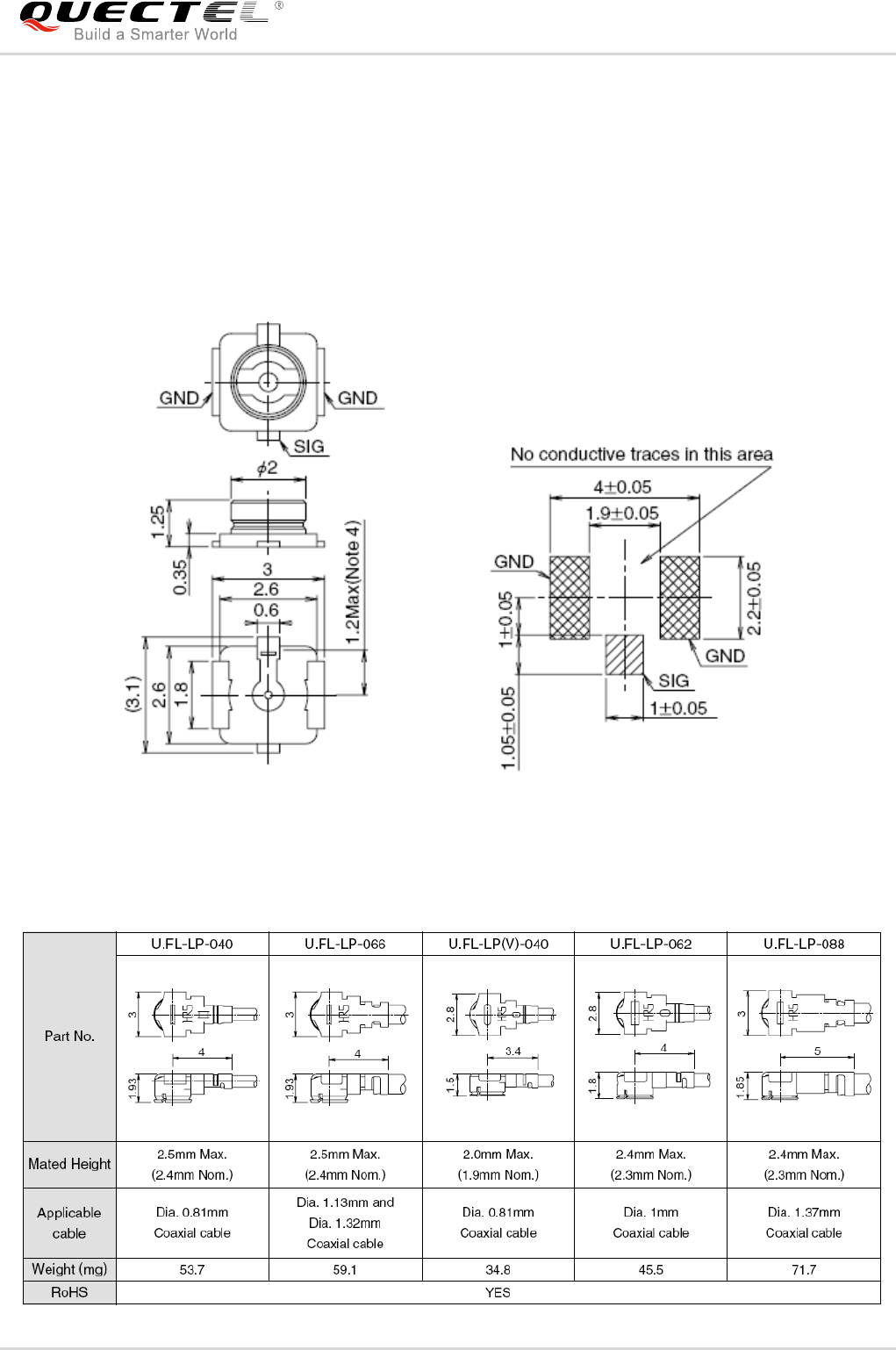

FIGURE 38: DIMENSIONS OF THE U.FL-R-SMT CONNECTOR (UNIT: MM) ............................................... 71

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 9 / 89

FIGURE 39: MECHANICALS OF U.FL-LP CONNECTORS ............................................................................. 72

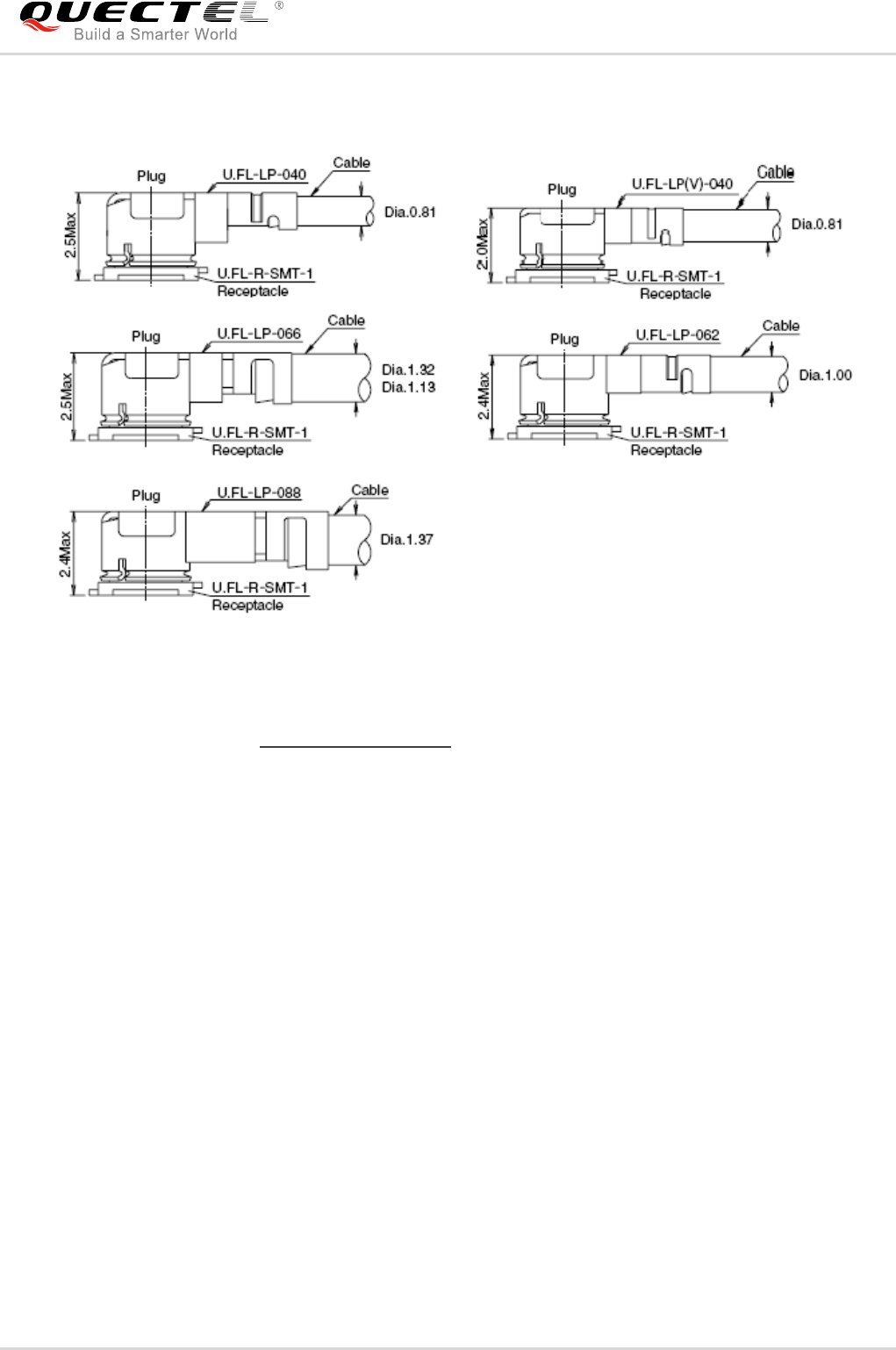

FIGURE 40: SPACE FACTOR OF MATED CONNECTOR (UNIT: MM) .......................................................... 73

FIGURE 41: REFERENCED HEATSINK DESIGN (HEATSINK AT THE TOP OF THE MODULE) ................. 81

FIGURE 42: REFERENCED HEATSINK DESIGN (HEATSINK AT THE BACKSIDE OF CUSTOMERS’ PCB)

................................................................................................................................................................... 81

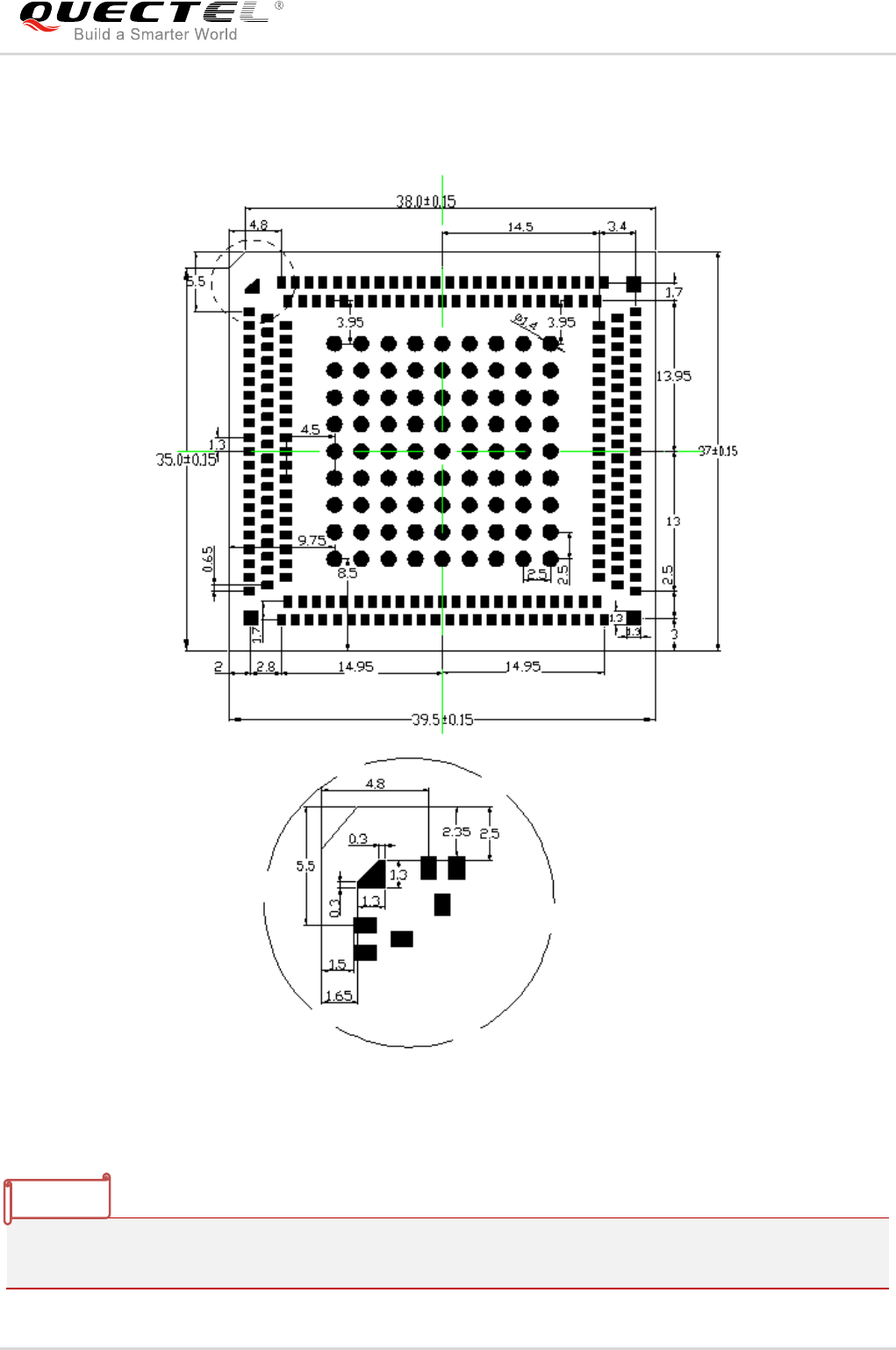

FIGURE 43: MODULE TOP AND SIDE DIMENSIONS .................................................................................... 82

FIGURE 44: MODULE BOTTOM DIMENSIONS (TOP VIEW) ......................................................................... 83

FIGURE 45: RECOMMENDED FOOTPRINT (TOP VIEW) .............................................................................. 84

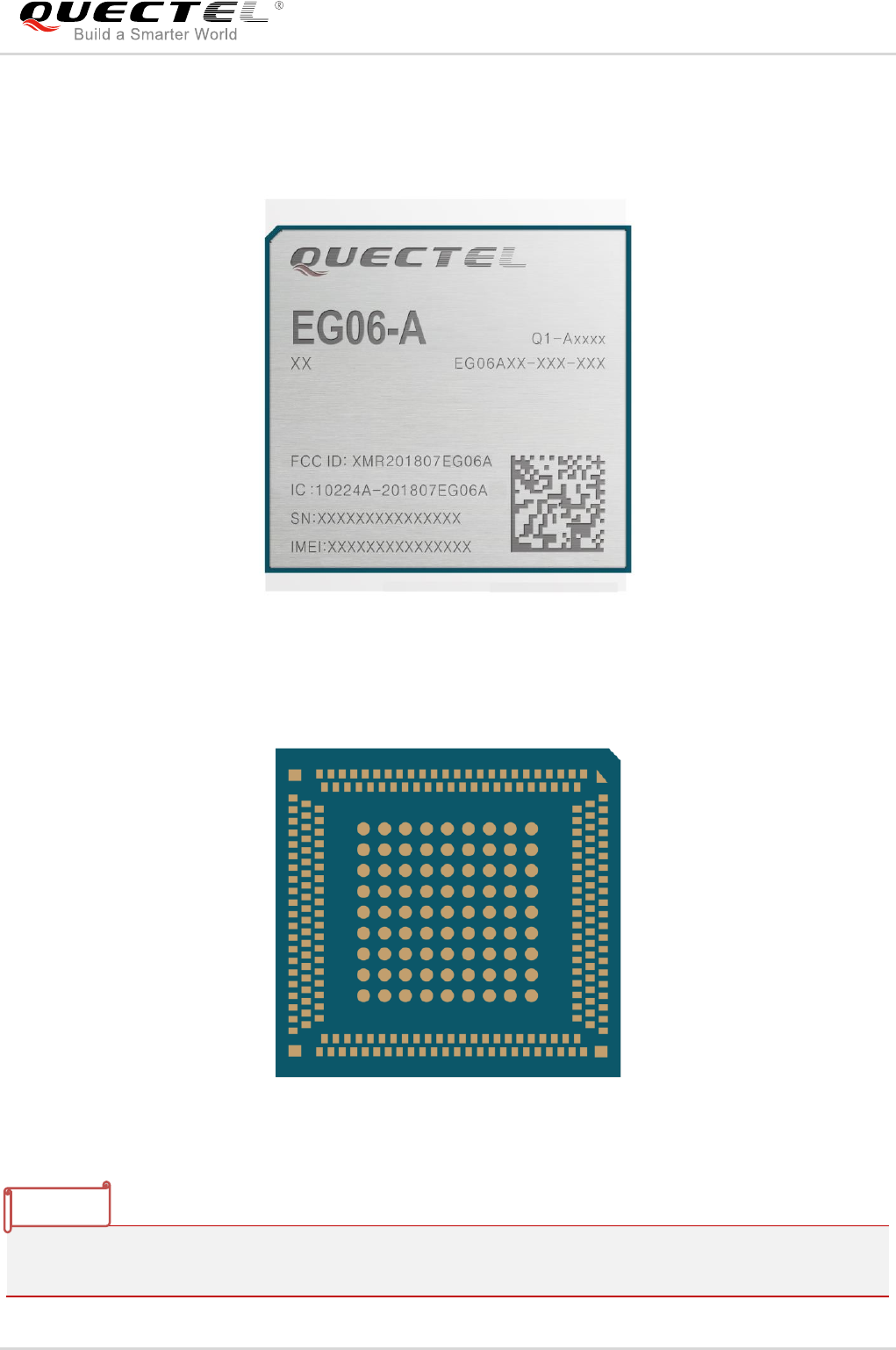

FIGURE 46: TOP VIEW OF THE MODULE ...................................................................................................... 85

FIGURE 47: BOTTOM VIEW OF THE MODULE .............................................................................................. 85

FIGURE 48: REFLOW SOLDERING THERMAL PROFILE .............................................................................. 87

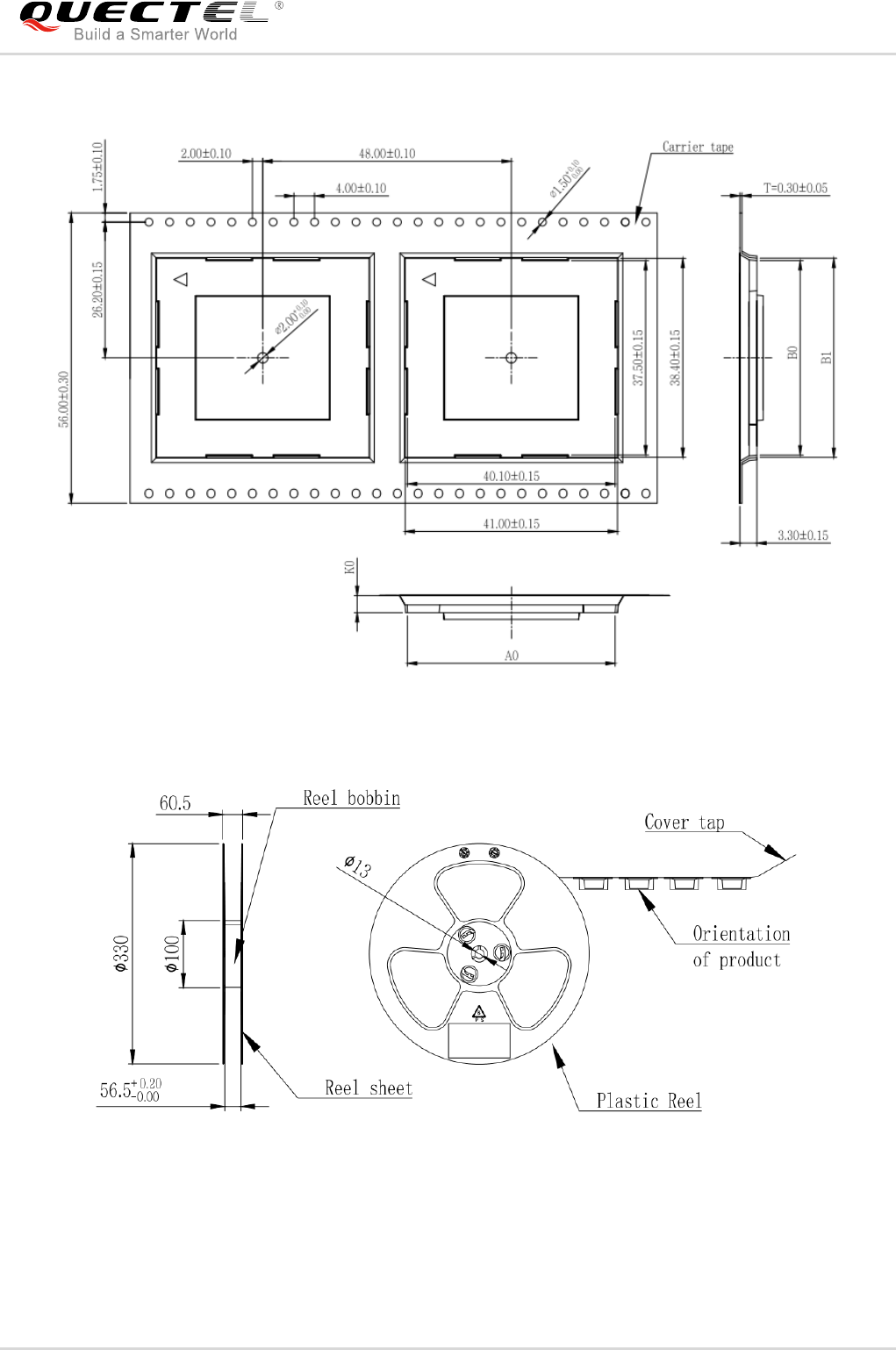

FIGURE 49: TAPE SPECIFICATIONS.............................................................................................................. 88

FIGURE 50: REEL SPECIFICATIONS.............................................................................................................. 88

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 10 / 89

1 Introduction

This document defines the EG06 module and describes its air interface and hardware interface which are

connected with customers’ applications.

This document can help customers quickly understand module interface specifications, electrical and

mechanical details, as well as other related information of EG06 module. Associated with application note

and user guide, customers can use EG06 module to design and set up mobile applications easily.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 11 / 89

1.1. Safety Information

The following safety precautions must be observed during all phases of the operation, such as usage,

service or repair of any cellular terminal or mobile incorporating EG06 module. Manufacturers of the

cellular terminal should send the following safety information to users and operating personnel, and

incorporate these guidelines into all manuals supplied with the product. If not so, Quectel assumes no

liability for the customers’ failure to comply with these precautions.

Full attention must be given to driving at all times in order to reduce the risk of an

accident. Using a mobile while driving (even with a handsfree kit) causes

distraction and can lead to an accident. You must comply with laws and regulations

restricting the use of wireless devices while driving.

Switch off the cellular terminal or mobile before boarding an aircraft. Make sure it is

switched off. The operation of wireless appliances in an aircraft is forbidden, so as

to prevent interference with communication systems. Consult the airline staff about

the use of wireless devices on boarding the aircraft, if your device offers an

Airplane Mode which must be enabled prior to boarding an aircraft.

Switch off your wireless device when in hospitals,clinics or other health care

facilities. These requests are designed to prevent possible interference with

sensitive medical equipment.

Cellular terminals or mobiles operatingover radio frequency signal and cellular

network cannot be guaranteed to connect in all conditions, for example no mobile

fee or with an invalid (U)SIM card. While you are in this condition and need

emergent help, please remember using emergency call. In order to make or

receive a call, the cellular terminal or mobile must be switched on and in a service

area with adequate cellular signal strength.

Your cellular terminal or mobile contains a transmitter and receiver. When it is ON,

it receives and transmits radio frequency energy. RF interference can occur if it is

used close to TV set, radio, computer or other electric equipment.

In locations with potentially explosive atmospheres, obey all posted signs to turn

off wireless devices such as your phone or other cellular terminals. Areas with

potentially explosive atmospheres include fuelling areas, below decks on boats,

fuel or chemical transfer or storage facilities, areas where the air contains

chemicals or particles such as grain, dust or metal powders, etc.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 12 / 89

Please do not discard. Maybe wireless devices have an impact on the environment

so please do not arbitrarily discarded.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 13 / 89

2 Product Concept

2.1. General Description

EG06 is a series of LTE-FDD/LTE-TDD/WCDMA wireless communication module with receive diversity,

which provides data connectivity on LTE-FDD, LTE-TDD, DC-HSDPA, HSPA+, HSDPA, HSUPA, and

WCDMA networks. It also provides GNSS1) and voice functionality2) to meet customers’ specific

application demands. EG06 contains five variants: EG06-E, EG06-A, EG06-LA, EG06-APAC and

EG06-AUTL. Customers can choose a dedicated type based on the region or operator. The following

table shows the frequency bands of EG06 series module.

Table 1: Frequency Bands of EG06 Series Module

Mode

EG06-E

EG06-A

EG06-LA

EG06-APAC

EG06-AUTL

LTE-FDD

(with

Rx-diversity)

B1/B3/B5/B7/

B8/B20/B28/

B323)

B2/B4/B5/B7/

B12/B13/B25/

B26/B293)/B30/

B66

B2/B3/B4/B5/

B7/B8/B20/B28

B1/B3/B5/B7/

B8/B18/B19/

B21/B26

B3/B7/B28

LTE-TDD

(with

Rx-diversity)

B38/B40/B41

Not supported

Not supported

B38/B39/B40/

B41

Not supported

2×CA

B1+B1/B5/B8/

B20/B28;

B3+B3/B5/B7/

B8/B20/B28;

B7+B5/B7/B8/

B20/B28;

B20+B323);

B38+B38;

B40+B40;

B41+B41

B2+B2/B5/B12/

B13/B26/B293);

B4+B4/B5/B12/

B13/B26/B293);

B7+B5/B7/B12/

B13/B26/B293);

B25+B5/B12/

B13/B25/B26/

B293);

B30+B5/B12/

B13/B26/B293);

B66+B5/B12/

B13/B26/B293)/

B66

B2+B2/B5/B8/

B20/B28;

B3+B3/B5/B7/

B8/B20/B28;

B4+B4/B5/B8/

B20/B28;

B7+B5/B7/B8/

B20/B28

B1+B3/B8/B18/

B19;

B3+B5/B19;

B7+B5/B7;

B21+B19;

B38+B38;

B39+B39;

B39+B41;

B40+B40;

B41+B41

B3+B3/B7/B28;

B7+B7/B28

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 14 / 89

1. 1) GNSS function is optional.

2. 2) EG06 series module (EG06-E/EG06-A/EG06-LA/EG06-APAC/EG06-AUTL) contains Telematics

version and Data-only version. Telematics version supports voice and data functions, while

Data-only version only supports data function.

3. 3) B32 and B29 support Rx only, and in 2×CA they are only for secondary component carrier.

With a compact profile of 37.0mm × 39.5mm × 2.8mm, EG06 can meet almost all requirements for M2M

applications such as automotive, metering, tracking system, security, router, wireless POS, mobile

computing device, PDA phone, tablet PC, etc.

EG06 is an SMD type module which can be embedded in applications through its 299-pin LGA pads.

2.2. Key Features

The following table describes the detailed features of EG06 module.

Table 2: Key Features of EG06 Module

WCDMA

(with

Rx-diversity)

B1/B3/B5/B8

B2/B4/B5

B2/B3/B4/B5/

B8

B1/B5/B6/B8/

B9/B19

Not supported

GNSS

GPS,

GLONASS,

BeiDou/

Galileo,

QZSS

GPS,

GLONASS,

BeiDou/

Galileo,

QZSS

GPS,

GLONASS,

BeiDou/

Galileo,

QZSS

GPS,

GLONASS,

BeiDou/Galileo,

QZSS

GPS,

GLONASS,

BeiDou/Galileo,

QZSS

Feature

Details

Power Supply

Supply voltage: 3.3V~4.3V

Typical supply voltage: 3.8V

Transmitting Power

Class 3 (24dBm+1/-3dB) for WCDMA bands

Class 3 (23dBm±2dB) for LTE-FDD bands

Class 3 (23dBm±2dB) for LTE-TDD bands

LTE Features

Support up to CA Cat 6 FDD and TDD

Support uplink QPSK and 16-QAM modulation

Support downlink QPSK, 16-QAM and 64-QAM modulation

Support 1.4MHz to 20MHz (2×CA) RF bandwidth

Support MIMO in DL direction

NOTES

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 15 / 89

FDD: Max 300Mbps (DL)/50Mbps (UL)

TDD: Max 226Mbps (DL)/28Mbps (UL)

UMTS Features

Support 3GPP R8 DC-HSDPA, HSPA+, HSDPA, HSUPA and WCDMA

Support QPSK, 16-QAM and 64-QAM modulation

DC-HSDPA: Max 42Mbps (DL)

HSUPA: Max 5.76Mbps (UL)

WCDMA: Max 384Kbps (DL)/384Kbps (UL)

Internet Protocol Features

Support PPP/QMI/TCP*/UDP*/FTP*/HTTP*/NTP*/PING*/HTTPS*/SMTP*/

MMS*/FTPS*/SMTPS*/SSL* protocols

Support the protocols PAP (Password Authentication Protocol) and CHAP

(Challenge Handshake Authentication Protocol) usually used for PPP

connections

SMS

Text and PDU mode

Point to point MO and MT

SMS cell broadcast

SMS storage: ME by default

(U)SIM Interface

Support (U)SIM card: 1.8V/3.0V

Audio Features

Support one digital audio interface: PCM interface

WCDMA: AMR/AMR-WB

LTE: AMR/AMR-WB

Support echo cancellation and noise suppression

PCM Interface

Used for audio function with external codec

Support 16-bit linear data format

Support long frame synchronization and short frame synchronization

Support master and slave modes, but must be the master in long frame

synchronization

USB Interface

Compliant with USB 3.0 and 2.0 specifications, with maximum transmission

rates up to 5Gbps on USB 3.0 and 480Mbps on USB 2.0.

Used for AT command communication, data transmission, firmware

upgrade, software debugging, GNSS NMEA sentence output and voice

over USB*

Support USB serial drivers for: Windows XP/Vista 7/8/8.1/10;

WinCE 5.0/6.0/7.0*; Linux 2.6/3.x/4.1~4.14; Android 4.x/5.x/6.x/7.x

UART Interface

Main UART:

Used for AT command communication and data transmission

Baud rate reaches up to 921600bps, 115200bps by default

Support RTS and CTS hardware flow control

Debug UART:

Used for Linux console and log output

115200bps baud rate

BT UART:

Used for Bluetooth communication

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 16 / 89

1. 1) Within operation temperature range, the module is 3GPP compliant.

2. 2) Within extended temperature range, the module remains the ability to establish and maintain a

voice, SMS, data transmission, emergency call, etc. There is no unrecoverable malfunction. There

are also no effects on radio spectrum and no harm to radio network. Only one or more parameters like

Pout might reduce in their value and exceed the specified tolerances. When the temperature returns to

the normal operating temperature levels, the module will meet 3GPP specifications again.

3. “*” means under development.

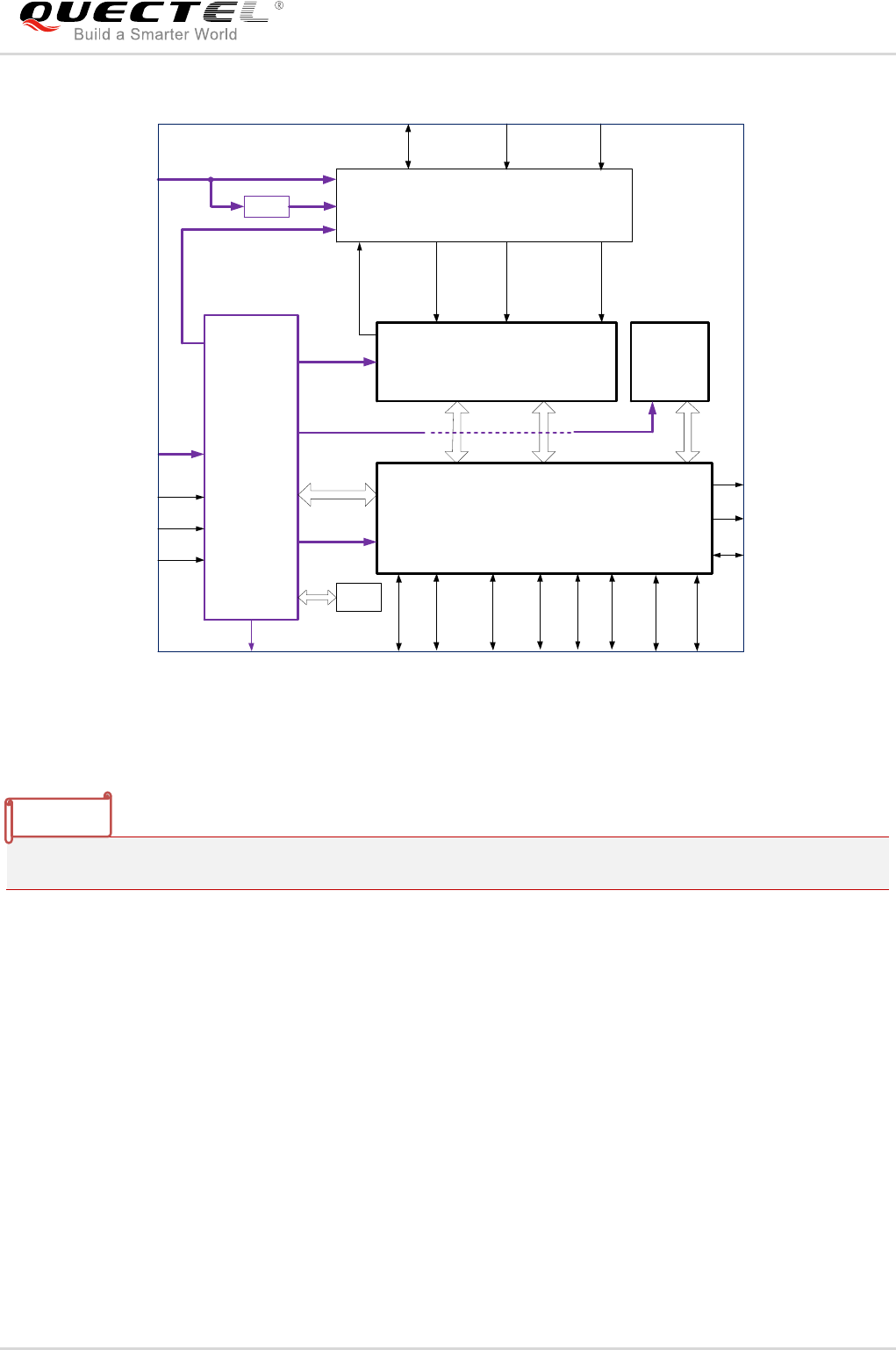

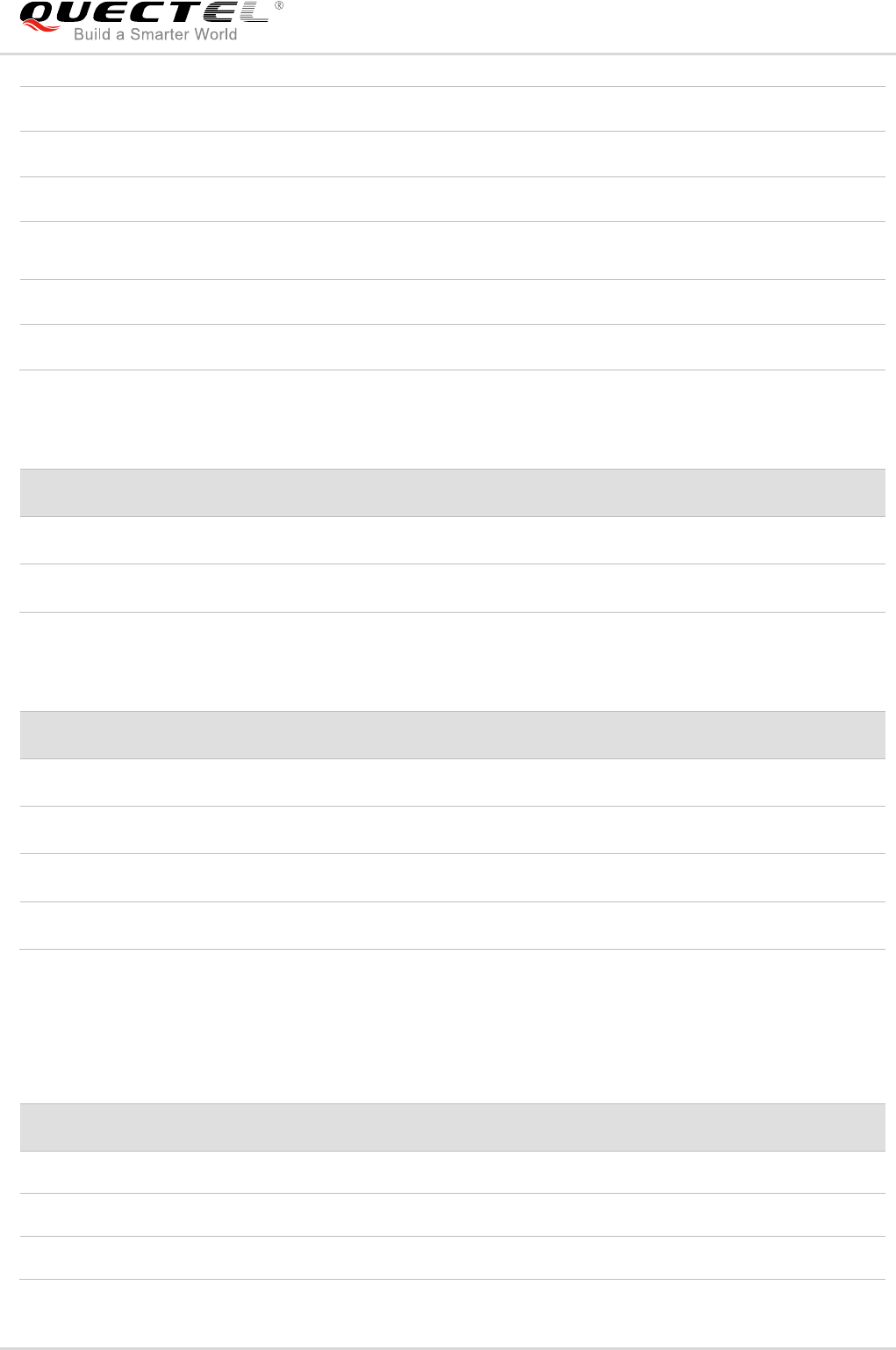

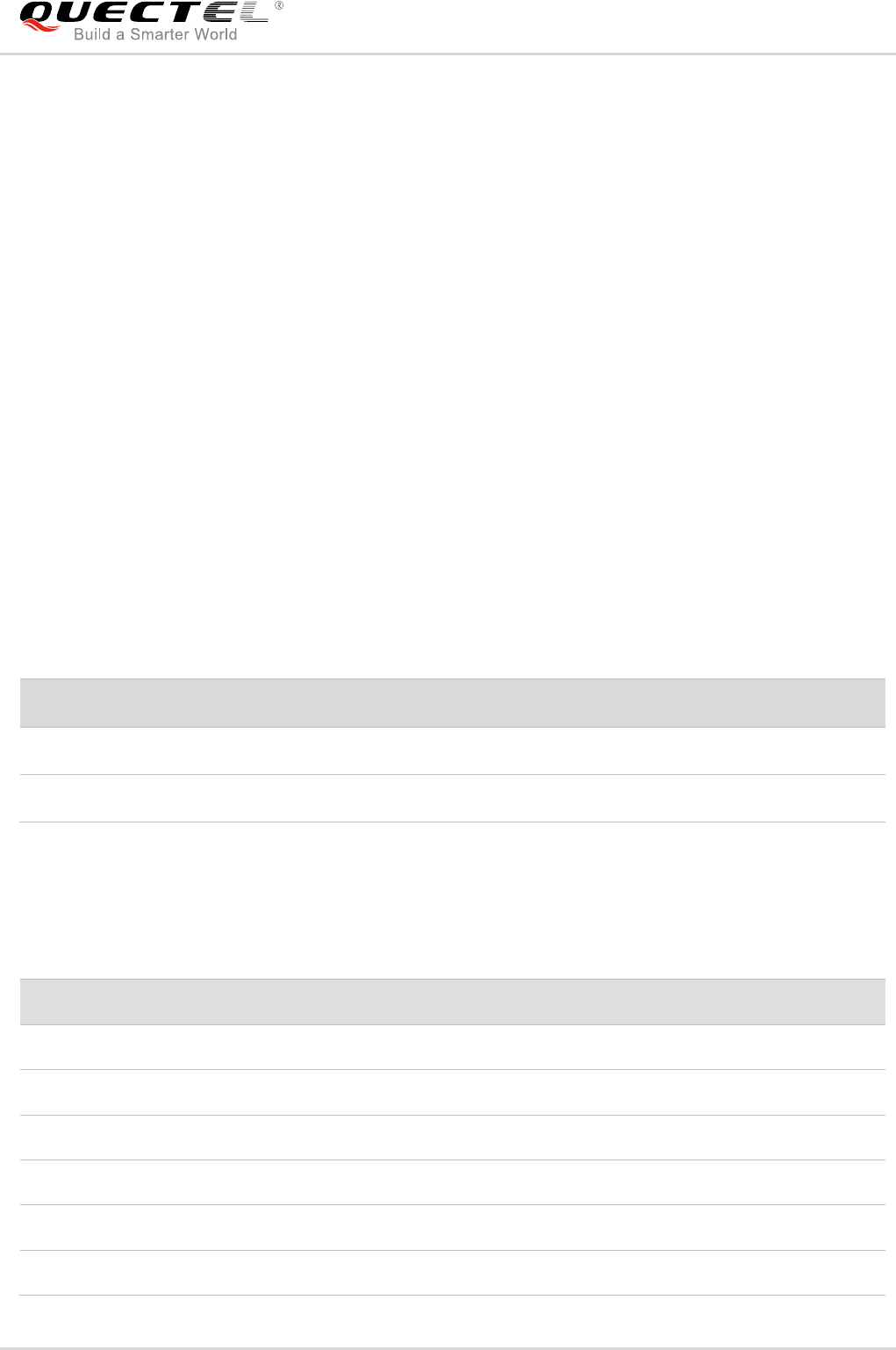

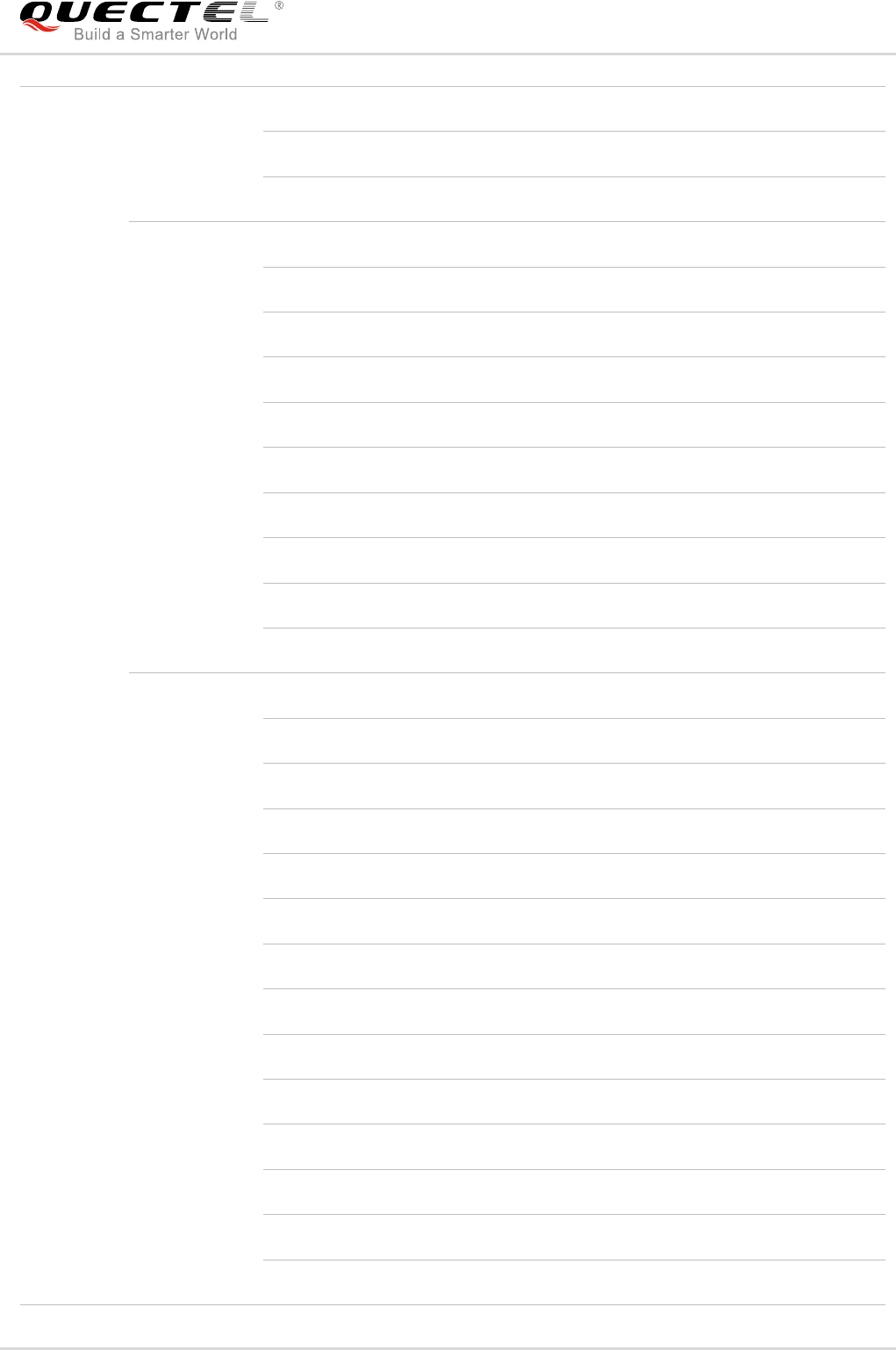

2.3. Functional Diagram

The following figure shows a block diagram of EG06 and illustrates the major functional parts.

Power management

Baseband

DDR+NAND flash

Radio frequency

Peripheral interfaces

PCIe Interface*

Comply with PCI Express Specification Revision 2.1

Used for Ethernet or WLAN communication

Rx-diversity

Support LTE/WCDMA Rx-diversity

GNSS Features

Gen8C-Lite of Qualcomm

Protocol: NMEA 0183

AT Commands

Compliant with 3GPP TS 27.007, 27.005 and Quectel enhanced AT

commands

Network Indication

Two pins including NET_MODE and NET_STATUS to indicate network

connectivity status

Antenna Interface

Including main antenna interface (ANT_MAIN), Rx-diversity antenna

interface (ANT_DIV) and GNSS antenna interface (ANT_GNSS)

Physical Characteristics

Size: (37.0±0.15)mm × (39.5±0.15)mm × (2.8±0.2)mm

Weight: approx. 6.7g

Temperature Range

Operation temperature range: -35°C ~ +75°C1)

Extended temperature range: -40°C ~ +85°C2)

Storage temperature range: -40°C ~ +90°C

Firmware Upgrade

USB2.0 interface and DFOTA*

RoHS

All hardware components are fully compliant with EU RoHS directive

NOTES

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 17 / 89

Baseband

PMIC

Transceiver NAND

DDR2

SDRAM

Tx/Rx Blocks

ANT_MAIN ANT_DIVANT_GNSS

VBAT_BB

VBAT_RF

APT

PWRKEY

ADCs

VDD_EXT USB2.0/3.0 USIM PCM UART

I2C

RESET_N

19.2M

XO

STATUS

GPIOs

Control

IQ Control

Tx

PRx DRx

PCIe*

CLK_OUT

SD

SPI

Figure 1: Functional Diagram

“*” means under development.

2.4. Evaluation Board

In order to help customers develop applications with EG06, Quectel supplies an evaluation board (EVB),

USB to RS-232 converter cable, earphone, antenna and other peripherals to control or test the module.

NOTE

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 18 / 89

3 Application Interface

3.1. General Description

EG06 is equipped with 299-pin LGA pads that can be connected to cellular application platform.

Sub-interfaces included in these pads are described in detail in the following chapters:

Power supply

(U)SIM interface

USB interface

UART interfaces

PCM and I2C interfaces

ADC interfaces

Network status indication

PCIe interface*

WLAN control interface*

SD card interface

USB_BOOT interface

“*” means under development.

NOTE

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 19 / 89

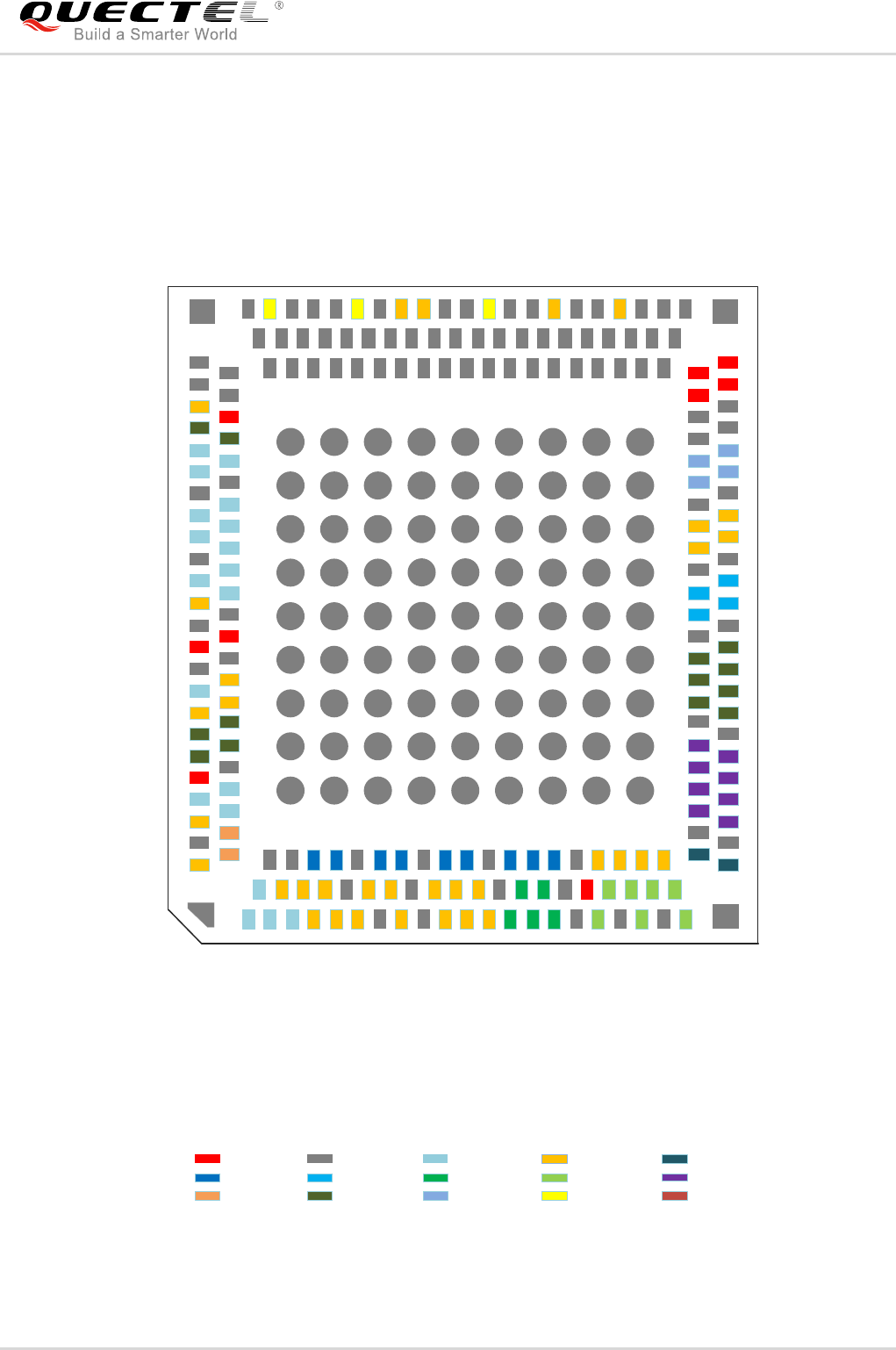

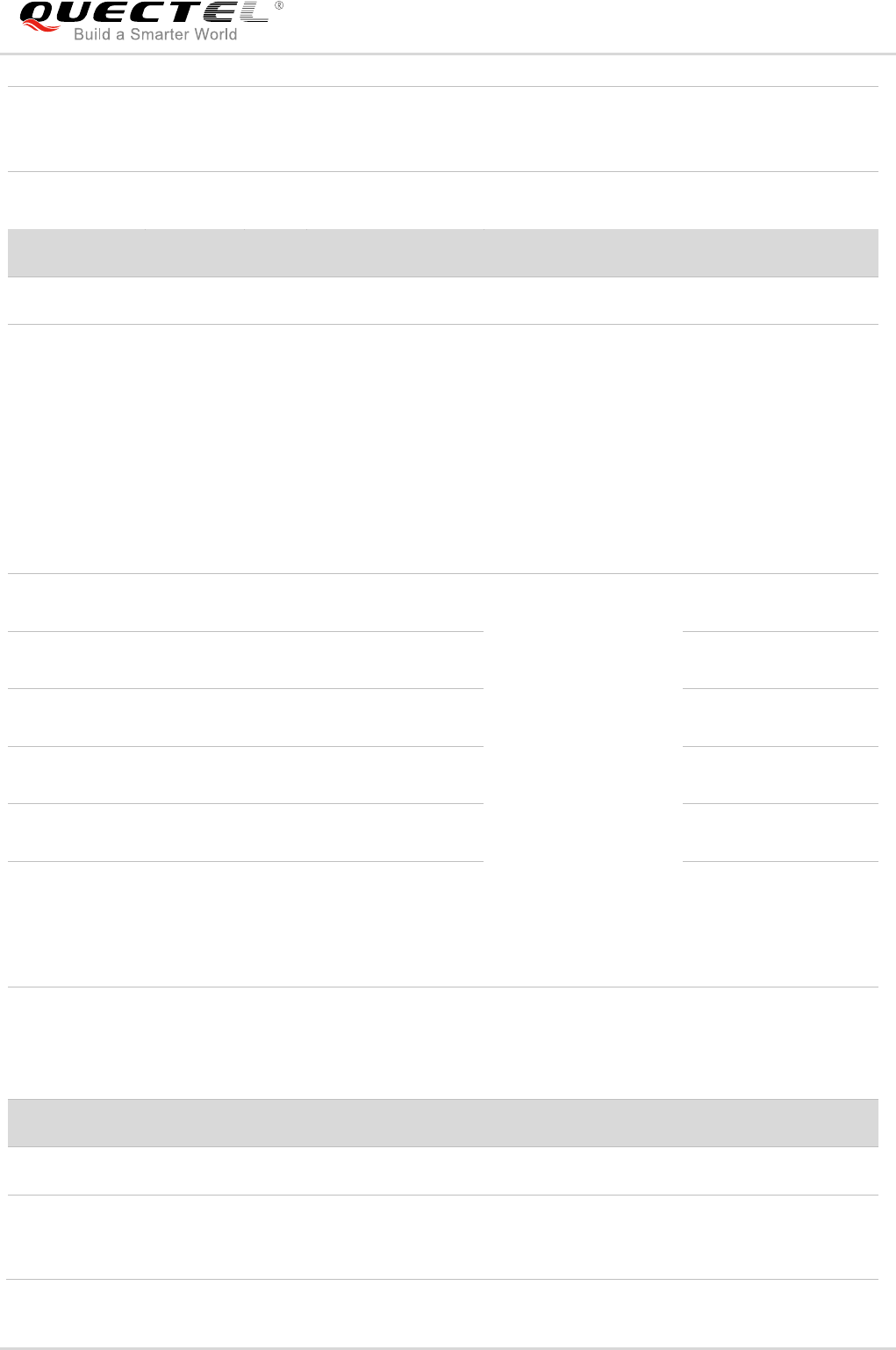

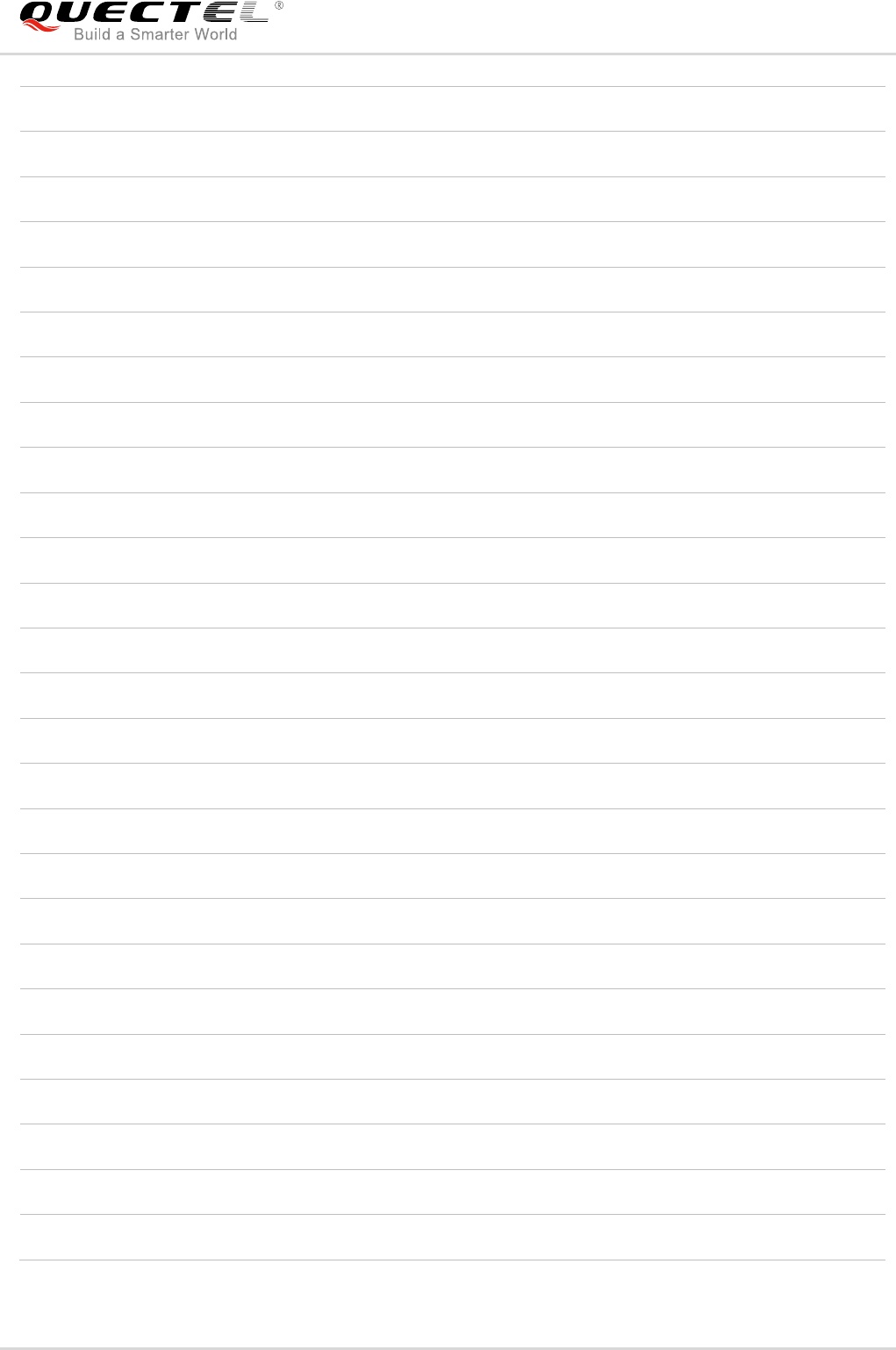

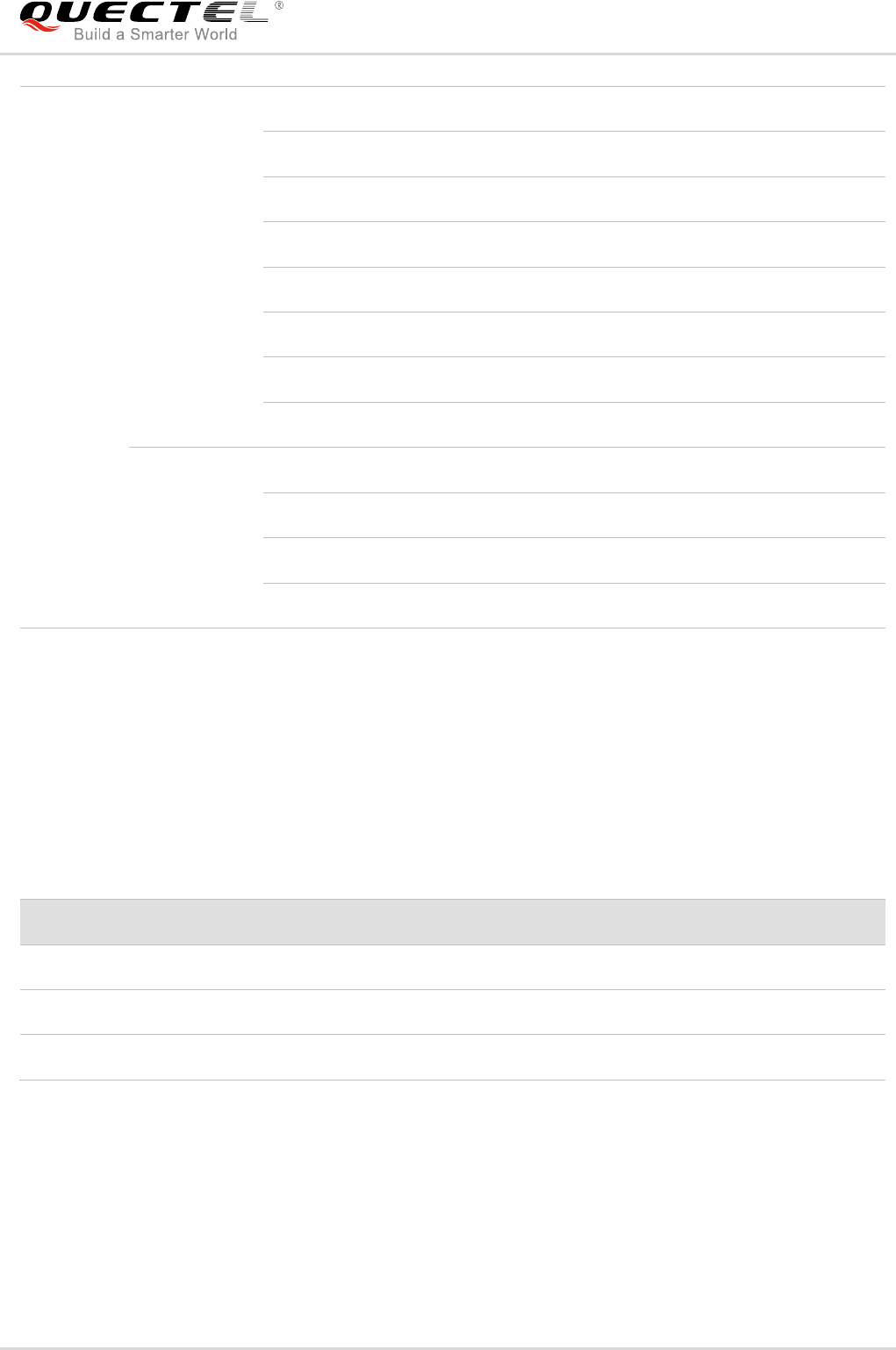

3.2. Pin Assignment

The following figure shows the pin assignment of EG06 module.

299

176

298

174

172

170

168

166

164

162

160

158

156

154

152

150

148

146

144

142

140

138

136

134

132

130

175

173

171

169

167

165

163

161

159

157

155

153

151

149

147

145

143

141

139

137

135

133

131

129

127

125

123

121

119

117

115

111

109

107

105

103

101

99

97

95

128

113

126

124

122

120

118

116

114

112

110

108

106

104

102

100

98

96

214

213

212

211

210

209

208

207

206

205

204

203

202

201

200

199

198

93

91

89

94

92

90

197

196

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

41

39

37

35

33

31

29

27

23

21

19

17

15

13

11

9

7

40

25

38

36

34

32

30

28

26

24

22

20

18

16

14

12

10

8

195

194

193

192

191

190

189

188

187

186

185

184

183

182

181

180

179

5

3

1

6

4

2

178

177

Power Pins GND Pins GPIO and Other Pins RESVRVED Pins

297

296

216 217 218215 219 220 221 222 223

224

233

242

251

260

269

278

287

225

234

243

252

261

270

279

288

226

235

244

253

262

271

280

289

227

236

272

281

290

228

237

273

282

291

229

238

274

283

292

230

239

248

257

266

275

284

293

231

240

249

258

267

276

285

294

232

241

250

259

268

277

286

295

PCIe Pins PCM Pins USIM Pins USB Pins

IIC Pins

SD Pins

ADC Pins UART Pins SPI Pins ANT Pins CLK Pins

RESET_N

PWRKEY

BT_EN

PM_ENABLE

USIM_PRESENCE

USIM_CLK

USIM_DATA

USIM_VDD

USIM_RST

USB_VBUS

USB_DM

USB_DP

USB_ID

USB_SS_TX_M

USB_SS_TX_P

USB_SS_RX_P

USB_SS_RX_M

I2C_SDA

I2C_SCL

SD_VDD

SD_DATA2

SD_DATA3

SD_DATA0

SD_DATA1

SD_CMD

SD_DETECT

SD_CLK

CTS

RTS RXD

DCD TXD

RI DTR

PCM_SYNC

PCM_CLK

PCM_IN

PCM_OUT

SPI_MOSI

SPI_CS

SPI_MISO

SPI_CLK

VBAT_RF

VBAT_RF

VBAT_RF

VBAT_RF

ANT_MAIN

ANT_GNSS

ANT_DIV

RESERVED

DBG_RXD

GPIO1

USB_BOOT

VDD_P2

DBG_TXD

GPIO2

OTG_PWR_EN

COEX_UART_TX

NET_MODE

WLAN_EN

W_DISABLE#

SLEEP_IND

COEX_UART_RX

WAKEUP_IN

RESERVED

VBAT_BB

VBAT_BB

WAKE_ON_WIRELESS

BT_TXD

BT_RXD

BT_CTS

BT_RTS

VDD_EXT WLAN_SLP_CLK

GND

NET_STATUS

STATUS

ADC0

ADC1

GND

GND GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PCIE_REFCLK_P

PCIE_REFCLK_M

PCIE_TX_M

PCIE_TX_P

PCIE_RX_M

PCIE_RX_P

PCIE_CLK_REQ_N

PCIE_RST_N

PCIE_WAKE_N

GND

GND

GND GND

GND

GND

GND

GND

GND

GND

GND GND

GND GND

USIM_GND

245 246 247

254 255 256

263 264 265

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED RESERVED

RESERVED GND

RESERVED

GND RESERVED

RESERVED

GND

RESERVED

RESERVED

RESERVED

GND

GND

GND

GND

RESERVED

RESERVED

RESERVED

GND

RESERVED

GND

GND

GND

GND

GND

GND

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

Figure 2: Pin Assignment (Top View)

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 20 / 89

1. Keep all RESERVED pins and unused pins unconnected.

2. GND pads 215~299 should be connected to ground in the design.

3.3. Pin Description

The following tables show the pin definition and description of EG06 module.

Table 3: I/O Parameters Definition

Type

Description

IO

Bidirectional

DI

Digital input

DO

Digital output

PI

Power input

PO

Power output

AI

Analog input

AO

Analog output

OD

Open drain

Table 4: Pin Description

Power Supply

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

VBAT_BB

155,156

PI

Power supply for

the module’s

baseband part.

Vmax=4.3V

Vmin=3.3V

Vnorm=3.8V

It must be able to

provide sufficient

current up to 0.8A.

VBAT_RF

85, 86,

87, 88

PI

Power supply for

the module’s RF

part.

Vmax=4.3V

Vmin=3.3V

Vnorm=3.8V

It must be able to

provide sufficient

current up to 1.8A in a

transmitting burst.

NOTES

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 21 / 89

VDD_EXT

168

PO

Provide 1.8V for

external circuit.

Vnorm=1.8V

IOmax=50mA

Power supply for

external GPIO’s pull up

circuits.

VDD_P2

135

PI

It is determined by

external circuit.

If an SD card is used,

connect VDD_P2 to

SD_VDD.

If an eMMC* is used,

connect VDD_P2 to

VDD_EXT.

GND

10, 13, 16,

17, 24, 30,

31, 35, 39,

44, 45, 54,

55, 63, 64,

69, 70, 75,

76, 81~84,

89~94,

96~100,

102~106,

108~112,

114, 116,

117, 118,

120~126,

128~133,

141, 142,

148, 153,

154, 157,

158, 167,

174, 177,

178, 181,

184, 187,

191,

196~299

Ground

Turn on/off

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

PWRKEY

2

DI

Turn on/off the

module.

VIHmax=2.1V

VIHmin=1.3V

VILmax=0.5V

The output voltage is

0.8V because it is

pulled up to an

internal voltage

(800mV).

RESET_N

1

DI

Reset the module

VIHmax=2.1V

VIHmin=1.3V

VILmax=0.5V

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 22 / 89

Status Indication

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

STATUS

171

DO

Indicate the

module’s operation

status.

VOHmin=1.35V

VOLmax=0.45V

1.8V power domain.

If unused, keep it

open.

NET_MODE

147

DO

Indicate the

module’s network

registration mode

VOHmin=1.35V

VOLmax=0.45V

1.8V power domain.

If unused, keep it

open.

NET_

STATUS

170

DO

Indicate the

module’s network

activity status

VOHmin=1.35V

VOLmax=0.45V

1.8V power domain.

If unused, keep it

open.

USB Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

USB_VBUS

32

PI

USB connection

detection

Vmax=5.25V

Vmin=3.0V

Vnorm=5.0V

USB_DP

34

IO

USB 2.0 differential

data bus - plus

Compliant with USB

2.0 standard

specifications.

Require differential

impedance of 90Ω.

USB_DM

33

IO

USB 2.0 differential

data bus - minus

Compliant with USB

2.0 standard

specifications.

USB_ID

36

DI

OTG identification

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

If unused, keep it

open.

USB_SS_

TX_P

38

AO

USB 3.0 super

speed

transmission- plus

Compliant with USB

3.0 standard

specifications.

Require differential

impedance of 90Ω.

USB_SS_

TX_M

37

AO

USB 3.0 super

speed

transmission-

minus

USB_SS_

RX_P

40

AI

USB 3.0 super

speed receiving-

plus

Require differential

impedance of 90Ω.

USB_SS_

RX_M

41

AI

USB 3.0

super-speed

receiving- minus

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 23 / 89

OTG_PWR_

EN

143

DO

OTG power control

VOLmax=0.45V

VOHmin=1.35V

(U)SIM Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

USIM_GND

24

Specified ground

for (U)SIM card

USIM_VDD

26

PO

Power supply for

(U)SIM card

For 1.8V (U)SIM:

Vmax=1.9V

Vmin=1.7V

For 3.0V (U)SIM:

Vmax=3.05V

Vmin=2.75V

IOmax=50mA

Either 1.8V or 3.0V is

supported by the

module

automatically.

USIM_

DATA

29

IO

Data signal of

(U)SIM card

For 1.8V (U)SIM:

VILmax=0.36V

VIHmin=1.26V

VOLmax=0.4V

VOHmin=1.45V

For 3.0V (U)SIM:

VILmax=0.57V

VIHmin=2.0V

VOLmax=0.4V

VOHmin=2.3V

USIM_CLK

27

DO

Clock signal of

(U)SIM card

For 1.8V (U)SIM:

VOLmax=0.4V

VOHmin=1.45V

For 3.0V (U)SIM:

VOLmax=0.4V

VOHmin=2.3V

USIM_RST

28

DO

Reset signal of

(U)SIM card

For 1.8V (U)SIM:

VOLmax=0.4V

VOHmin=1.45V

For 3.0V (U)SIM:

VOLmax=0.4V

VOHmin=2.3V

USIM_

PRESENCE

25

DI

(U)SIM card

insertion detection

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

If unused, keep it

open.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 24 / 89

UART Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

RI

61

DO

Ring indicator

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

DCD

59

DO

Data carrier

detection

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

CTS

56

DO

Clear to send

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

RTS

57

DI

Request to send

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

If unused, keep it

open.

DTR

62

DI

Data terminal

ready, sleep mode

control

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

Pull-up by default.

Pulling down to low

level will wake up the

module.

If unused, keep it

open.

TXD

60

DO

Transmit data

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

RXD

58

DI

Receive data

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

If unused, keep it

open.

BT Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

BT_TXD

163

DO

Transmit data

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

BT_RXD

165

DI

Receive data

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

If unused, keep it

open.

BT_RTS

166

DI

Request to send

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

1.8V power domain.

If unused, keep it

open.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 25 / 89

VIHmax=2.0V

BT_CTS

164

DO

Clear to send

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

BT_EN*

3

DO

BT function

enabled

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

Keep it open.

This function is under

development

Debug UART Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

DBG_RXD

136

DI

Receive data

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

If unused, keep it

open.

DBG_TXD

137

DO

Transmit data

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

ADC Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

ADC0

173

AI

General purpose

analog to digital

converter interface

Voltage range:

0.15V to VBAT_BB

If unused, keep it

open.

ADC1

175

AI

General purpose

analog to digital

converter interface

Voltage range:

0.15V to VBAT_BB

If unused, keep it

open.

PCM and I2C Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

PCM_IN

66

DI

PCM data input

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

If unused, keep it

open.

PCM_OUT

68

DO

PCM data output

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

PCM_SYNC

65

IO

PCM data frame

synchronization

signal

VOLmax=0.45V

VOHmin=1.35V

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

1.8V power domain.

In master mode, it is

an output signal. In

slave mode, it is an

input signal.

If unused, keep it

open.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 26 / 89

VIHmax=2.0V

PCM_CLK

67

IO

PCM clock

VOLmax=0.45V

VOHmin=1.35V

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

In master mode, it is

an output signal. In

slave mode, it is an

input signal.

If unused, keep it

open.

I2C_SCL

43

OD

I2C serial clock

Used for external

codec.

1.8V power domain.

An external pull-up

resistor is required.

1.8V only. If unused,

keep it open.

I2C_SDA

42

OD

I2C serial data

Used for external

codec.

1.8V power domain.

An external pull-up

resistor is required.

1.8V only. If unused,

keep it open.

SPI Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

SPI_CS

79

DO

Chip select of SPI

interface

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

SPI_CLK

80

DO

Clock signal of SPI

interface

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

SPI_MOSI

77

DO

Master output

slave input of SPI

interface

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

SPI_MISO

78

DI

Master input

slave output of SPI

interface

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

If unused, keep it

open.

PCIe Interface*

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

PCIE_REF

CLK_P

179

AO

Output PCIe

reference clock -

plus

If unused, keep it

open.

PCIE_REF

CLK_M

180

AO

Output PCIe

reference clock -

minus

If unused, keep it

open.

PCIE_TX_M

182

AO

PCIe transmission

- minus

If unused, keep it

open.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 27 / 89

PCIE_TX_P

183

AO

PCIe transmission

- plus

If unused, keep it

open.

PCIE_RX_M

185

AI

PCIe receiving-

minus

If unused, keep it

open.

PCIE_RX_P

186

AI

PCIe receiving -

plus

If unused, keep it

open.

PCIE_CLK_

REQ_N

188

IO

PCIe clock request

VOLmax=0.45V

VOHmin=1.35V

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

In master mode, it is

an input signal.

In slave mode, it is an

output signal.

If unused, keep it

open.

PCIE_RST_N

189

IO

PCIe reset

VOLmax=0.45V

VOHmin=1.35V

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

In master mode, it is

an output signal.

In slave mode, it is an

input signal.

If unused, keep it

open.

PCIE_WAKE_

N

190

IO

PCIe wake

VOLmax=0.45V

VOHmin=1.35V

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

VIHmax=2.0V

In master mode, it is

an input signal.

In slave mode, it is an

output signal.

If unused, keep it

open.

WLAN Control Interface*

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

PM_ENABLE

5

DO

Enable WLAN

power

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

WAKE_ON_

WIRELESS

160

DI

Wake up the host

(EG06 module) by

Wi-Fi module.

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

Active low.

If unused, keep it

open.

WLAN_EN

149

DO

WLAN function

enable control

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

Active high.

If unused, keep it

open.

COEX_UART_

RX

146

DI

LTE/WLAN

coexistence signal

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

If unused, keep it

open.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 28 / 89

COEX_UART_

TX

145

DO

LTE/WLAN

coexistence signal

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

WLAN_SLP_

CLK

169

DO

WLAN sleep clock

VOLmax=0.45V

VOHmin=1.35V

If unused, keep it

open.

SD Card Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

SD_VDD

46

PO

Power supply for

pull up voltage of

SD card bus

For 1.8V SD:

Vmax=1.9V

Vmin=1.75V

For 3.0V SD:

Vmax=3.05V

Vmin=2.75V

IOmax=50mA

Either 1.8V or 3.0V is

supported by the

module

automatically.

Power supply of SD

card must be

provided by an

external power

supply.

SD_DATA0

49

IO

Secure digital

controller data bit 0

For1.8V SD:

VOLmax=0.45V

VOHmin=1.4V

VILmin=-0.3V

VILmax=0.58V

VIHmin=1.3V

VIHmax=2.0V

For 3.0V SD:

VOLmax=0.35V

VOHmin=2.15V

VILmin=-0.3V

VILmax=0.7V

VIHmin=1.8V

VIHmax=3.15V

If unused, keep it

open.

SD_DATA1

50

IO

Secure digital

controller data bit 1

If unused, keep it

open.

SD_DATA2

47

IO

Secure digital

controller data bit 2

If unused, keep it

open.

SD_DATA3

48

IO

Secure digital

controller data bit 3

If unused, keep it

open.

SD_CMD

51

DO

Command signal

for SD card

If unused, keep it

open.

SD_CLK

53

DO

Serial clock signal

for SD card

If unused, keep it

open.

SD_ DETECT

52

DI

SD card insertion

detection

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

If unused, keep it

open.

RF Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

ANT_DIV

127

AI

Diversity antenna

interface

50Ω impedance.

If unused, keep it

open.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 29 / 89

ANT_MAIN

107

IO

Main antenna

interface

50Ω impedance.

ANT_GNSS

119

AI

GNSS antenna

interface

50Ω impedance.

If unused, keep it

open.

GPIO Pins

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

WAKEUP_IN

150

DI

Sleep mode control

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

Pull-up by default.

Low level wakes up

the module.

If unused, keep it

open.

W_DISABLE#

151

DI

Airplane mode

control

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

Pull-up by default.

In low voltage level,

the module can enter

into airplane mode.

If unused, keep it

open.

GPIO1

138

IO

General purpose

input/output port

VOLmax=0.45V

VOHmin=1.35V

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

If unused, keep it

open.

GPIO2

139

IO

Other Pins

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

USB_BOOT

140

DI

Force the module

to enter into

emergency

download mode

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V power domain.

If unused, keep it

open.

SLEEP_IND

144

DO

Sleep instruction

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain.

If unused, keep it

open.

RESERVED Pins

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

RESERVED

4, 6, 7, 8,

9, 11, 12,

Reserved

Keep these pins

unconnected.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 30 / 89

RESERVED

14, 15,

18~23,

71~74, 95,

101, 113,

115, 134,

152, 159,

161, 162,

172, 176,

192~195

Reserved

Keep these pins

unconnected.

3.4. Operating Modes

The table below briefly summarizes the various operating modes referred in the following chapters.

Table 5: Overview of Operating Modes

Mode

Details

Normal

Operation

Idle

Software is active. The module has registered on the network, and it is

ready to send and receive data.

Talk/Data

Network connection is ongoing. In this mode, the power consumption is

decided by network setting and data transfer rate.

Minimum

Functionality

Mode

AT+CFUN command can set the module to a minimum functionality mode without

removing the power supply. In this case, both RF function and (U)SIM card will be

invalid.

Airplane Mode

AT+CFUN command or W_DISABLE# pin can set the module to airplane mode. In

this case, RF function will be invalid.

Sleep Mode

In this mode, the current consumption of the module will be reduced to the minimal

level. During this mode, the module can still receive paging message, SMS, voice

call and TCP/UDP data from the network normally.

Power Down

Mode

In this mode, the power management unit shuts down the power supply. Software is

not active. The serial interfaces are not accessible. Operating voltage (connected to

VBAT_RF and VBAT_BB) remains applied.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 31 / 89

3.5. Power Saving

3.5.1. Sleep Mode

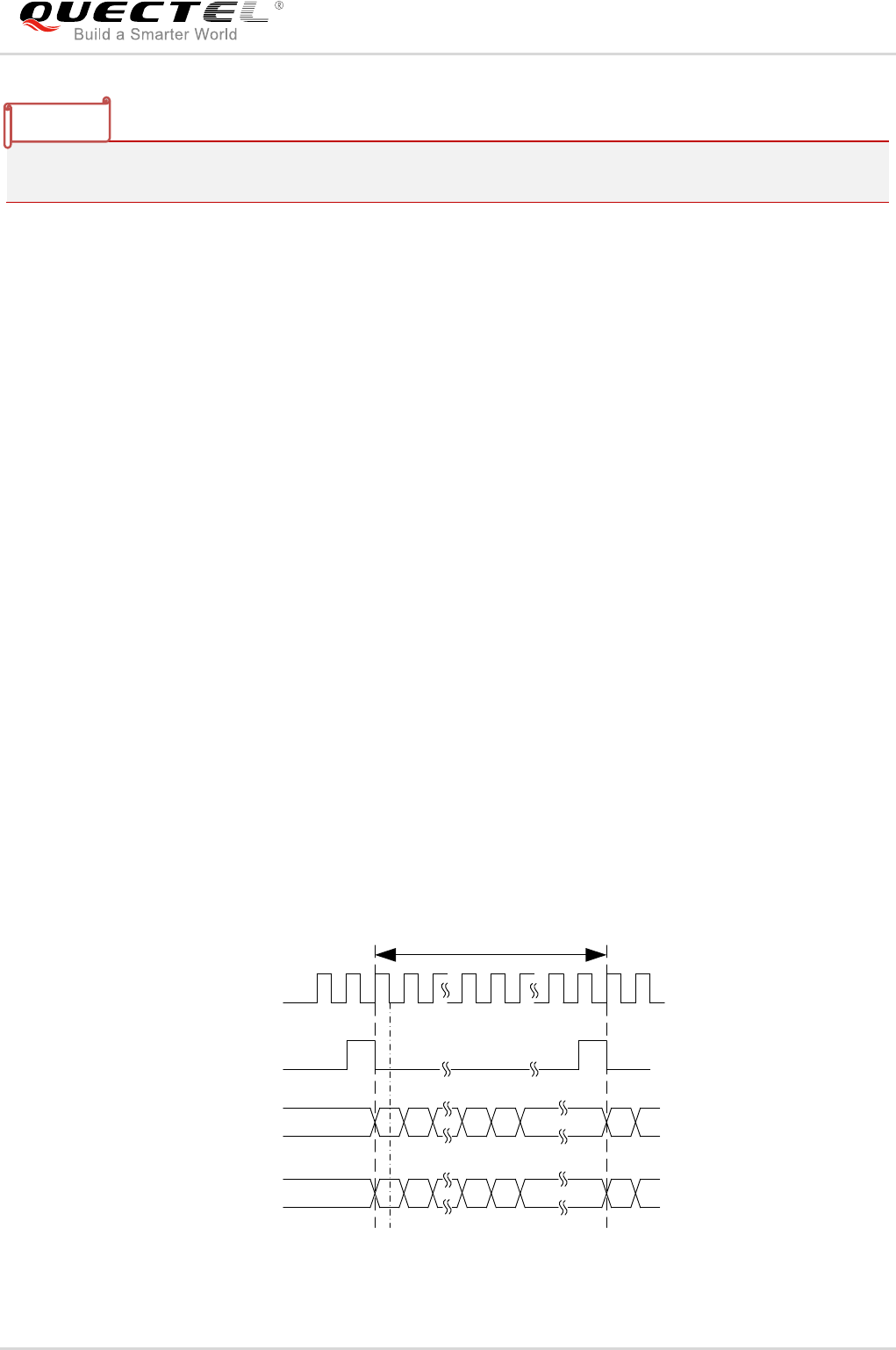

DRX on EG06 is able to reduce the current consumption to a minimum value during the sleep mode, and

DRX cycle index values are broadcasted by the wireless network. The figure below shows the relationship

between the DRX run time and the current consumption in sleep mode. The longer the DRX runs, the

lower the current consumption will be.

Current Consumption

Run Time

DRX OFF ON OFF ON OFF ON OFF ON OFF

Figure 3: DRX Run Time and Current Consumption in Sleep Mode

The following section describes power saving procedure of EG06 module.

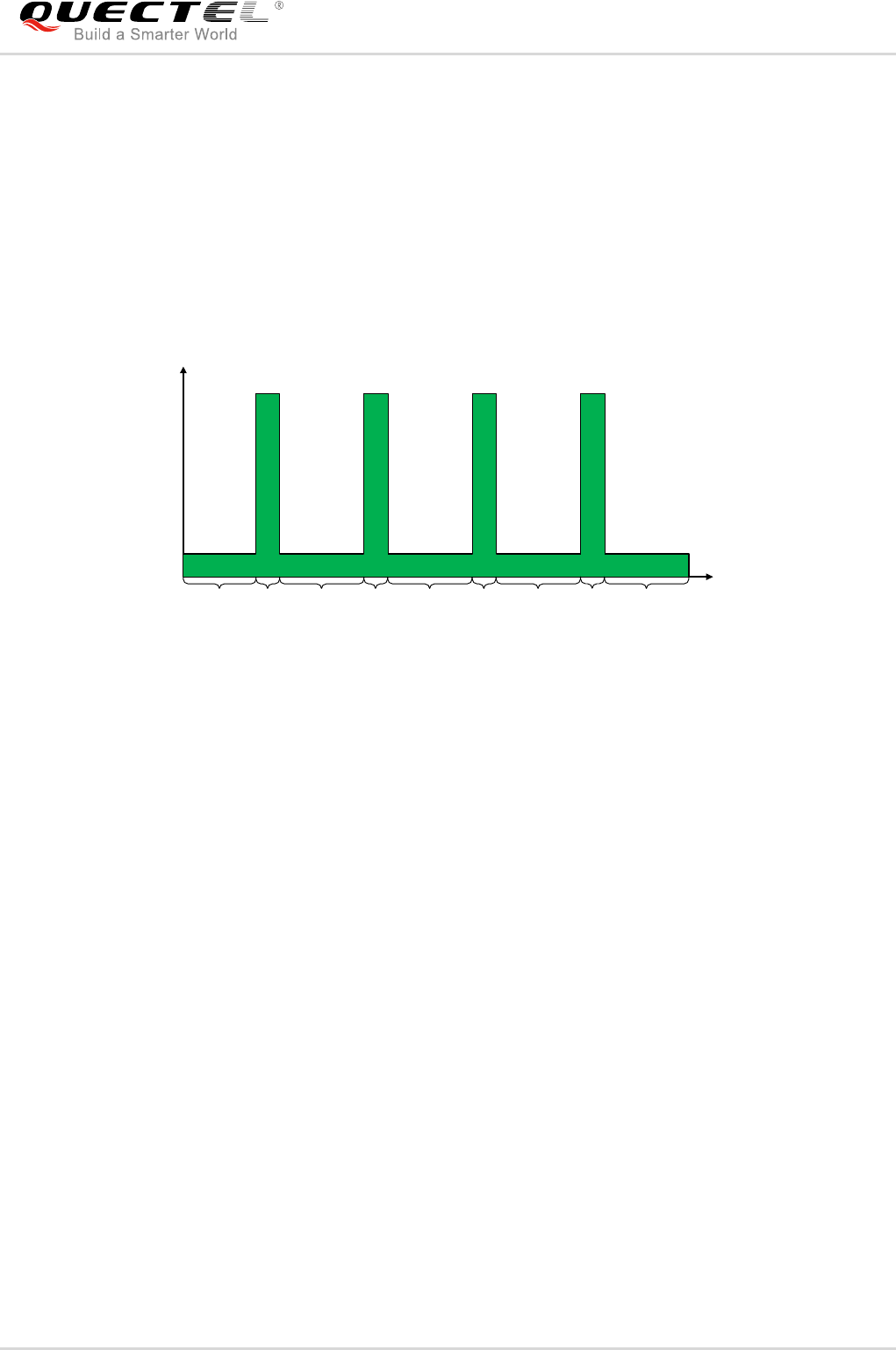

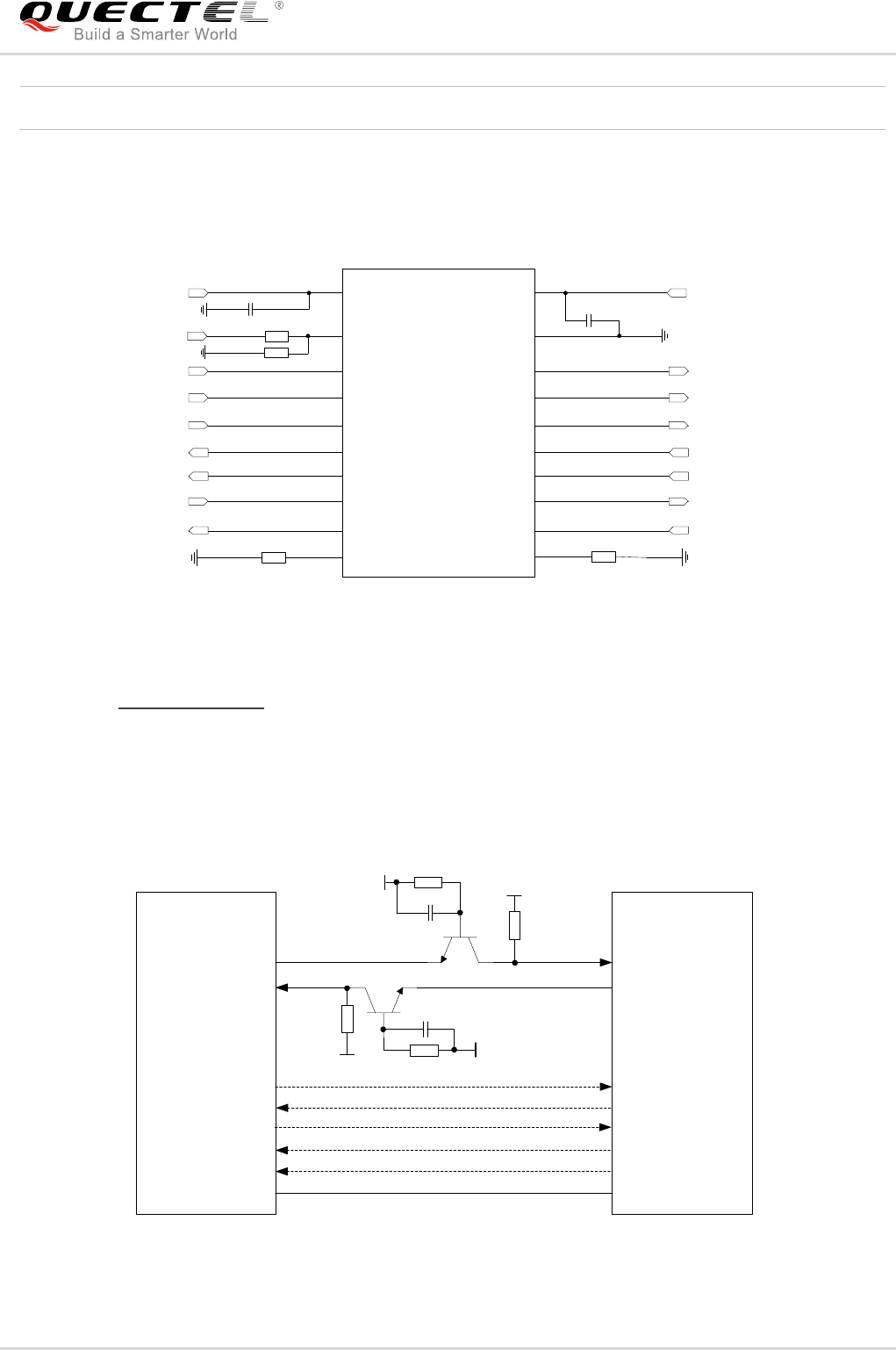

3.5.1.1. UART Application

If the host communicates with the module via UART interface, the following preconditions can let the

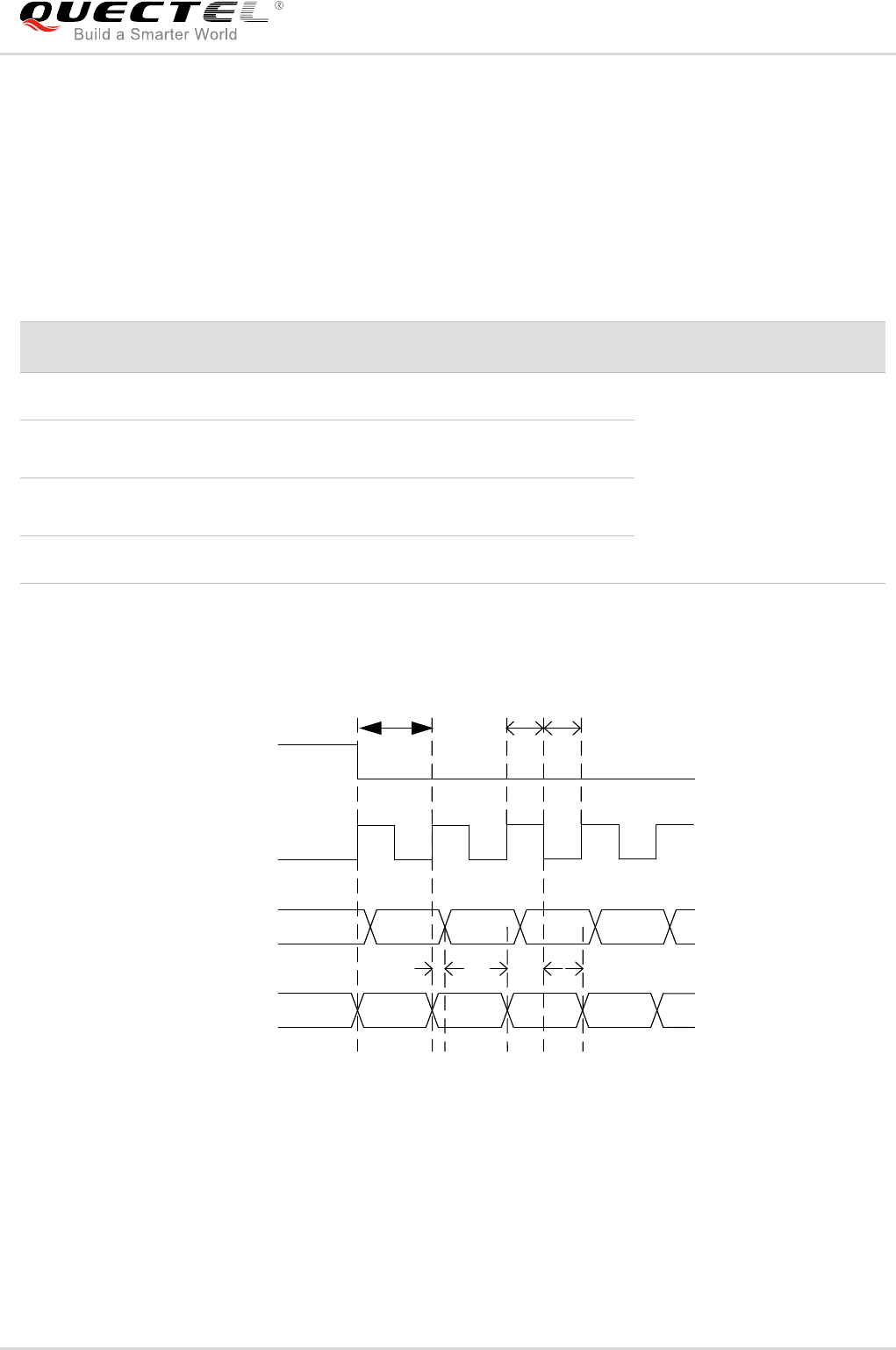

module enter into sleep mode.

Execute AT+QSCLK=1 command to enable sleep mode.

Drive DTR to high level.

The following figure shows the connection between the module and the host.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 32 / 89

RXD

TXD

RI

DTR

TXD

RXD

EINT

GPIO

Module Host

GND GND

Figure 4: Sleep Mode Application via UART

Driving the host DTR to low level will wake up the module.

When EG06 has a URC to report, RI signal will wake up the host. Please refer to Chapter 3.16 for

details about RI behavior.

3.5.1.2. USB Application with USB Remote Wakeup Function

If the host supports USB suspend/resume and remote wakeup function, the following three preconditions

must be met to let the module enter into the sleep mode.

Execute AT+QSCLK=1 command to enable the sleep mode.

Ensure the DTR is held at high level or keep it open.

The host’s USB bus, which is connected with the module’s USB interface, enters into suspended

state.

The following figure shows the connection between the module and the host.

USB_VBUS

USB_DP

USB_DM

VDD

USB_DP

USB_DM

Module Host

GND GND

Figure 5: Sleep Mode Application with USB Remote Wakeup

Sending data to EG06 through USB will wake up the module.

When EG06 has a URC to report, the module will send remote wake-up signals to USB bus so as to

wake up the host.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 33 / 89

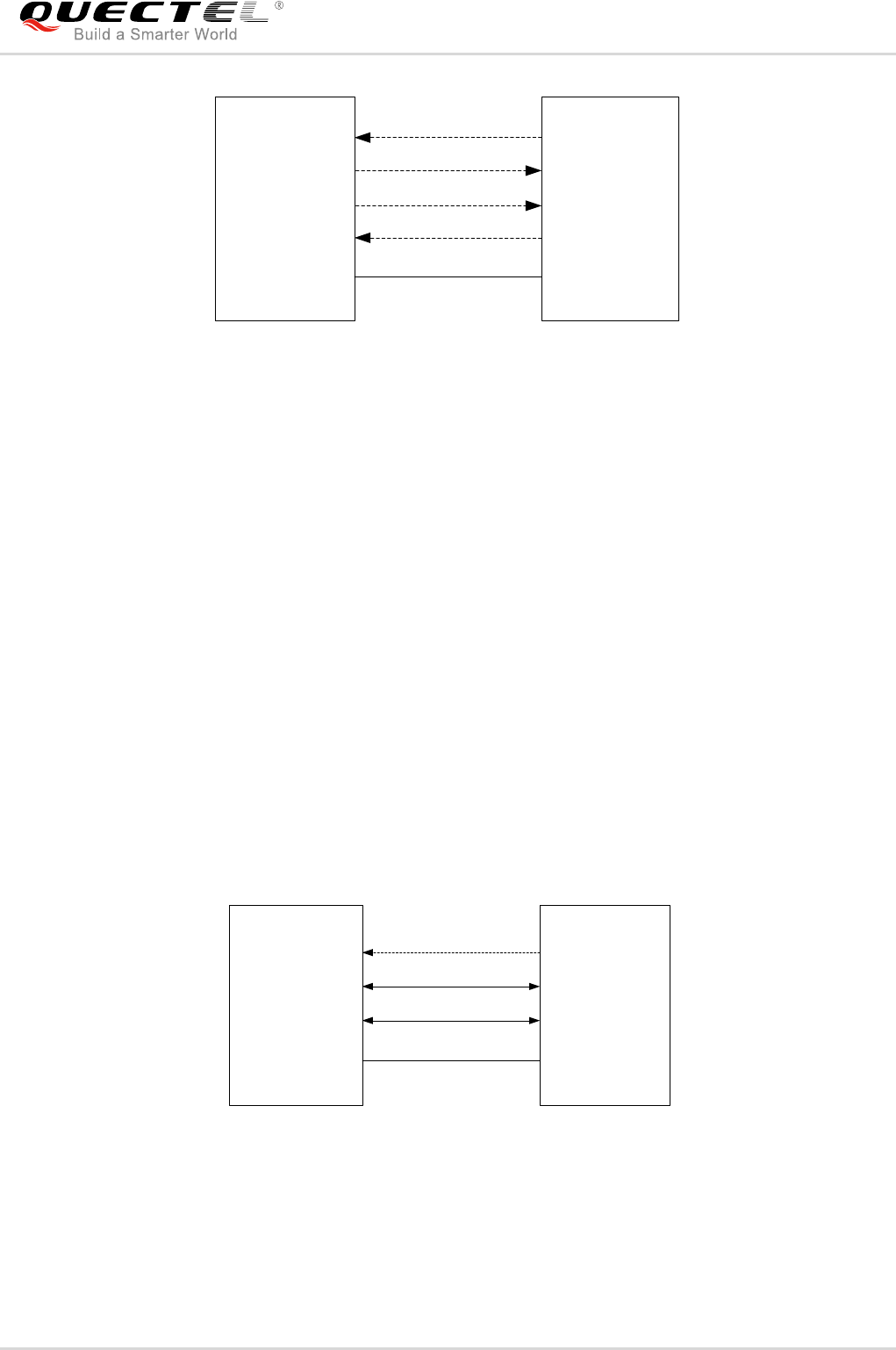

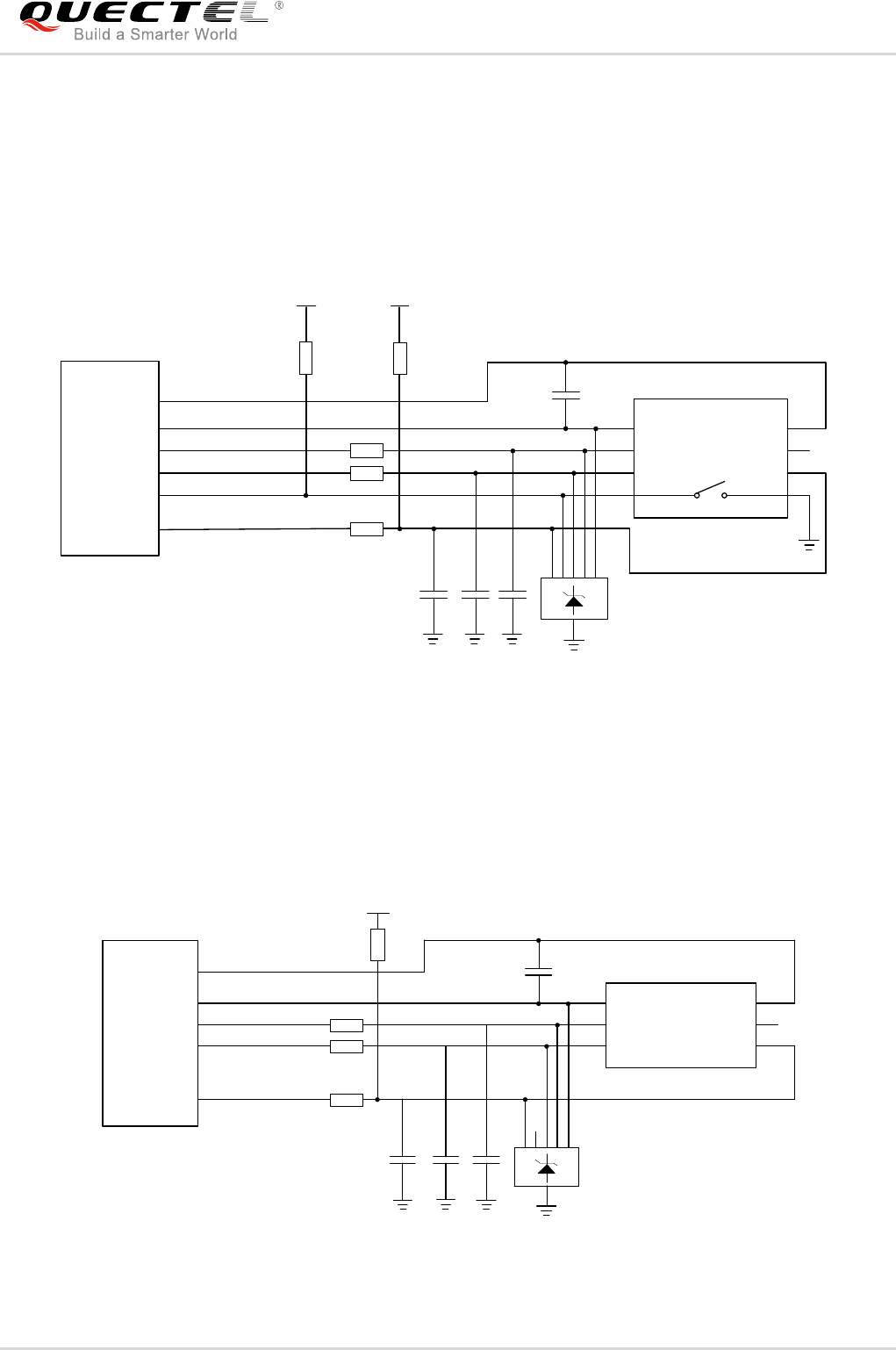

3.5.1.3. USB Application with USB Suspend/Resume and RI Function

If the host supports USB suspend/resume, but does not support remote wake-up function, the RI signal is

needed to wake up the host.

There are three preconditions to let the module enter into the sleep mode.

Execute AT+QSCLK=1 command to enable the sleep mode.

Ensure the DTR is held at high level or keep it open.

The host’s USB bus, which is connected with the module’s USB interface, enters into suspended

state.

The following figure shows the connection between the module and the host.

USB_VBUS

USB_DP

USB_DM

VDD

USB_DP

USB_DM

Module Host

GND GND

RI EINT

Figure 6: Sleep Mode Application with RI

Sending data to EG06 through USB will wake up the module.

When EG06 has a URC to report, RI signal will wake up the host.

3.5.1.4. USB Application without USB Suspend Function

If the host does not support USB suspend function, USB_VBUS should be disconnected with an external

control circuit to let the module enter into sleep mode.

Execute AT+QSCLK=1 command to enable the sleep mode.

Ensure the DTR is held at high level or keep it open.

Disconnect USB_VBUS.

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 34 / 89

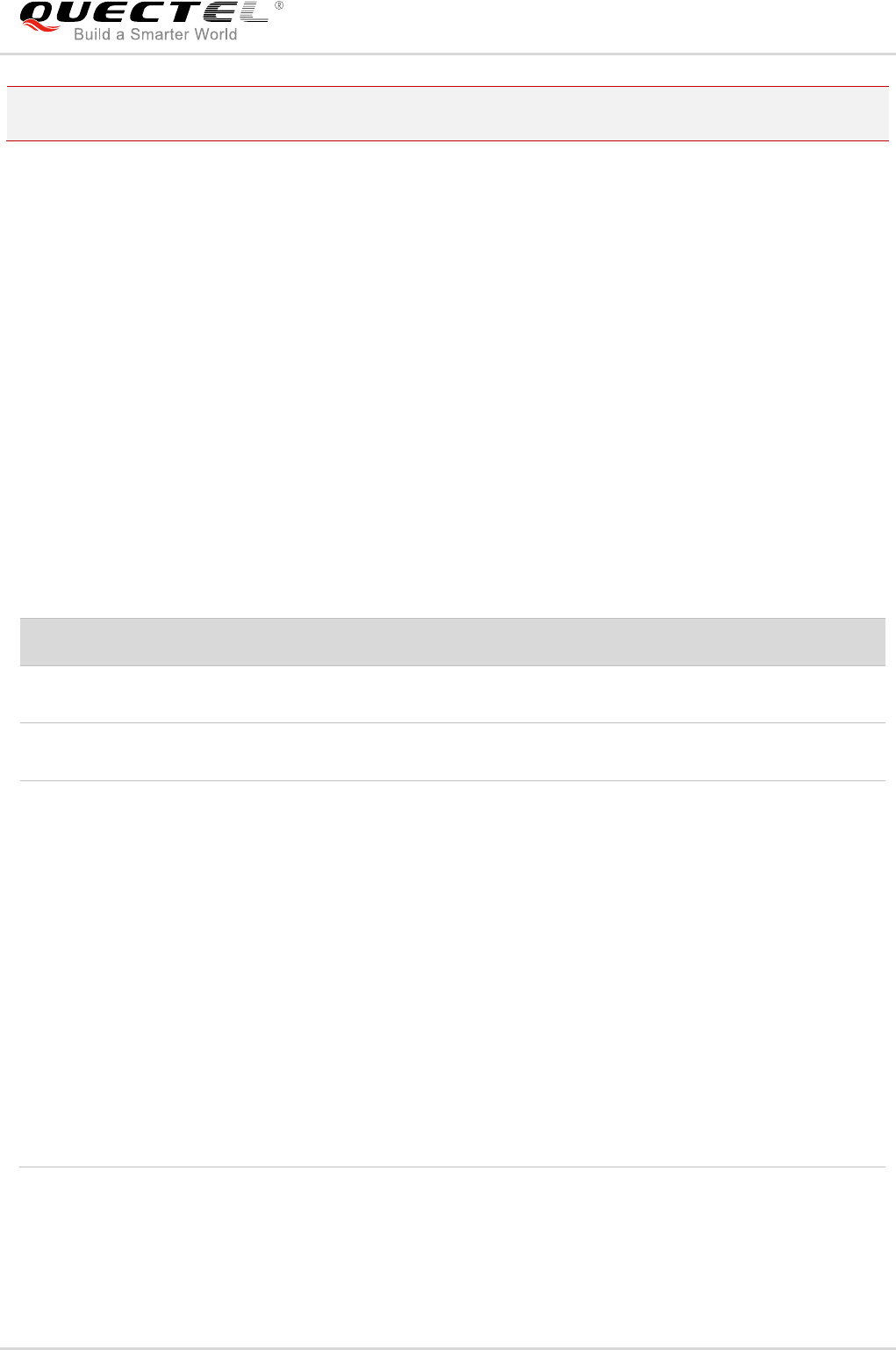

The following figure shows the connection between the module and the host.

USB_VBUS

USB_DP

USB_DM

VDD

USB_DP

USB_DM

Module Host

RI EINT

Power

Switch

GPIO

GND GND

Figure 7: Sleep Mode Application without Suspend Function

Switching on the power switch to supply power to USB_VBUS will wake up the module.

Please pay attention to the level match shown in dotted line between the module and the host.

3.5.2. Airplane Mode

When the module enters into airplane mode, the RF function does not work, and all AT commands

correlative with RF function will be inaccessible. This mode can be set via the following ways.

Hardware:

The W_DISABLE# pin is pulled up by default; driving it to low level will let the module enter into airplane

mode.

Software:

AT+CFUN command provides the choice of the functionality level through setting <fun> into 0, 1 or 4.

AT+CFUN=0: Minimum functionality mode; both (U)SIM and RF functions are disabled.

AT+CFUN=1: Full functionality mode (by default).

AT+CFUN=4: Airplane mode. RF function is disabled.

1. The W_DISABLE# control function is disabled in firmware by default. It can be enabled by

AT+QCFG="airplanecontrol" command, and this command is under development.

NOTES

NOTE

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 35 / 89

2. The execution of AT+CFUN command will not affect GNSS function.

3.6. Power Supply

3.6.1. Power Supply Pins

EG06 provides six VBAT pins dedicated to connect with the external power supply. There are two

separate voltage domains for VBAT.

Four VBAT_RF pins for module’s RF part

Two VBAT_BB pins for module’s baseband part

The following table shows the details of VBAT pins and ground pins.

Table 6: VBAT and GND Pins

Pin Name

Pin No.

Description

Min.

Typ.

Max.

Unit

VBAT_RF

85, 86

87, 88

Power supply for module’s

RF part

3.3

3.8

4.3

V

VBAT_BB

155, 156

Power supply for module’s

baseband part

3.3

3.8

4.3

V

GND

10, 13, 16, 17, 24,

30, 31, 35, 39, 44,

45, 54, 55, 63, 64,

69, 70, 75, 76,

81~84, 89~94,

96~100, 102~106,

108~112, 114,117,

118, 120~126,

128~133, 141,142,

148, 153, 154,157,

158, 167, 174, 177,

178, 181, 184, 187,

191, 217, 196~214,

224~299

Ground

-

0

-

V

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 36 / 89

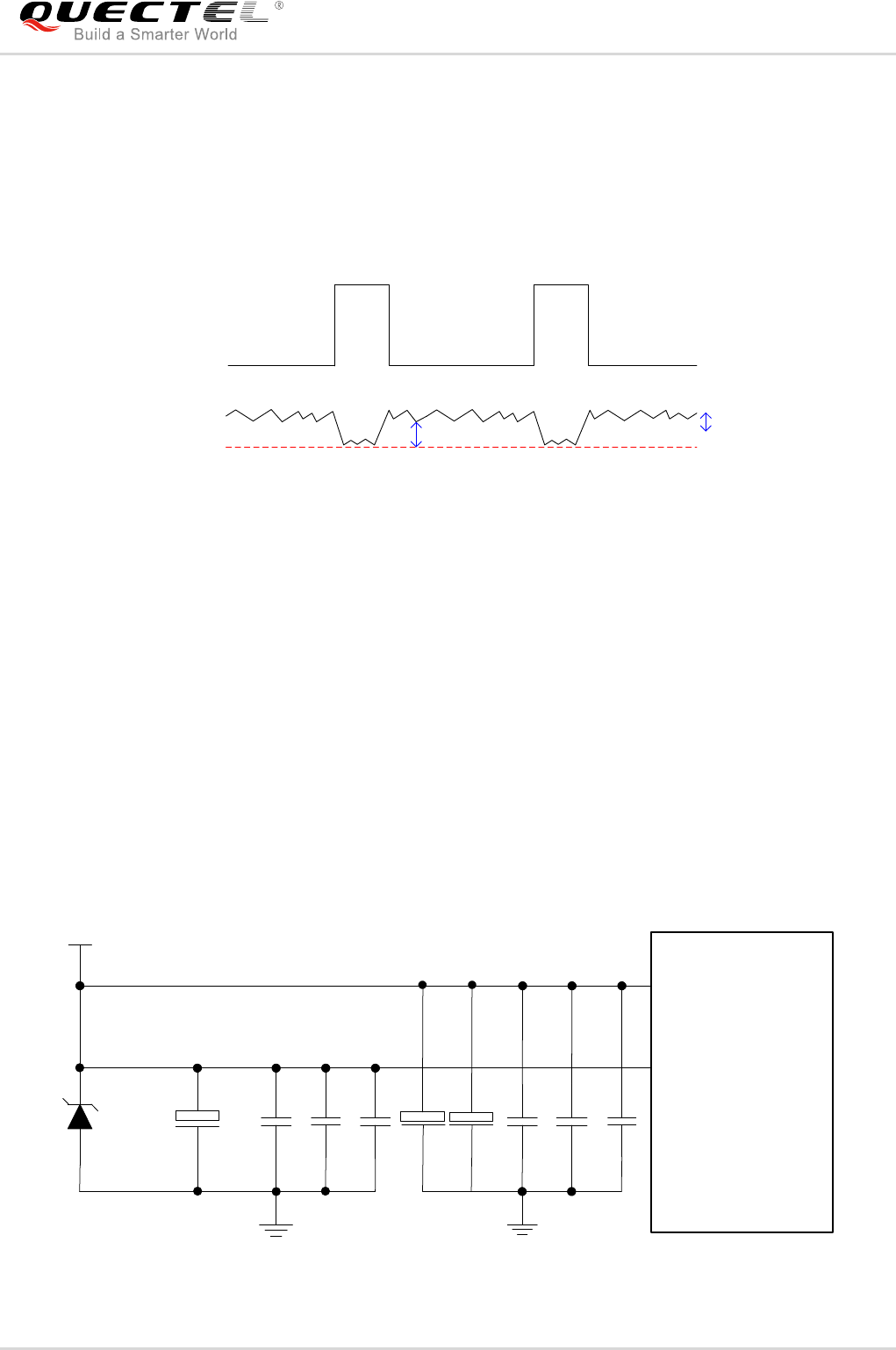

3.6.2. Decrease Voltage Drop

The power supply range of the module is from 3.3V to 4.3V. Please make sure the input voltage will never

drop below 3.3V. The following figure shows the voltage drop during Tx power in 3G and 4G networks.

VCC

Burst

Transmission

Min. 3.3V

Ripple

Drop

Burst

Transmission

Figure 8: Power Supply Limits during Tx Power

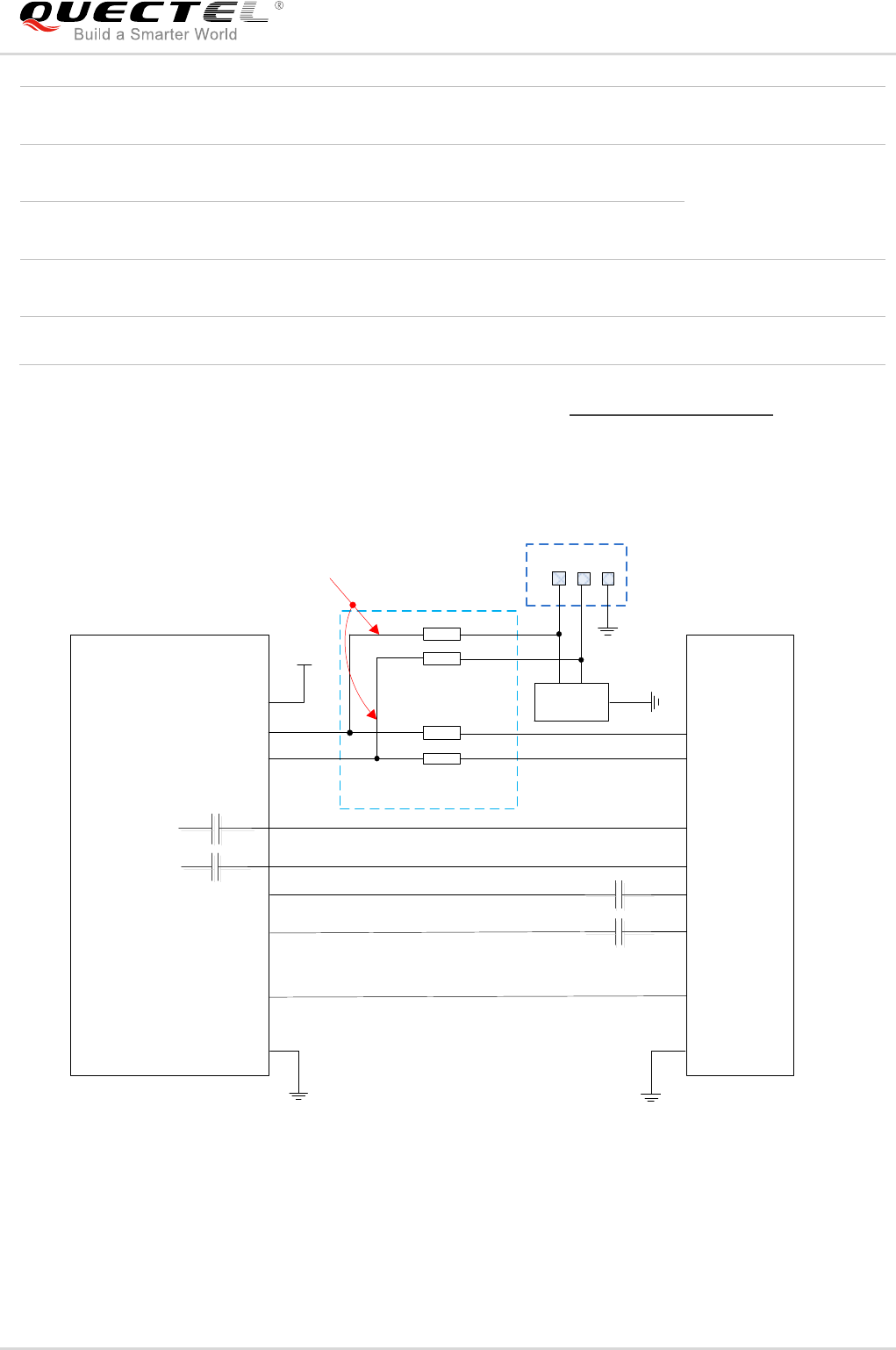

To decrease voltage drop, a bypass capacitor of about 100µF with low ESR should be used, and a

multi-layer ceramic chip (MLCC) capacitor array should also be reserved due to its ultra-low ESR. It is

recommended to use three ceramic capacitors (100nF, 33pF, 10pF) for composing the MLCC array, and

place these capacitors close to VBAT pins. The main power supply from an external application has to be

a single voltage source and can be expanded to two sub paths with star structure. The width of VBAT_BB

trace should be no less than 1mm; and the width of VBAT_RF trace should be no less than 2mm. In

principle, the longer the VBAT trace is, the wider it will be.

In addition, in order to get a stable power source, it is suggested that customers should use a zener diode

of which reverse zener voltage is 5.1V and dissipation power is more than 0.5W. The following figure

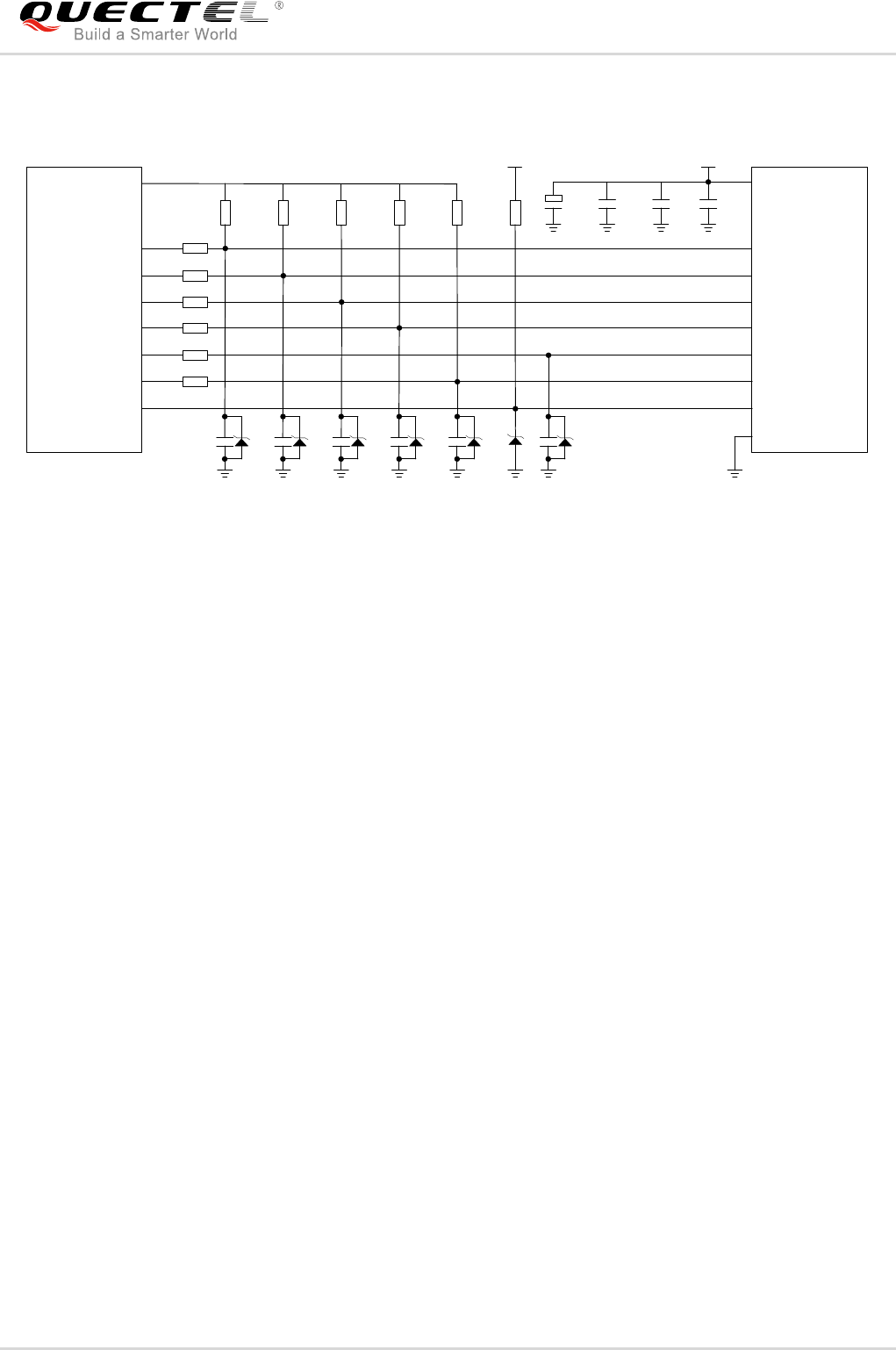

shows the star structure of the power supply.

Module

VBAT_RF

VBAT_BB

VBAT

C1

100uF

C7

100nF

C8

33pF

C9

10pF

+

+

C2

100nF

C5

100 uF

C3

33pF

C4

10pF

D1

5.1V

+

C6

100uF

Figure 9: Star Structure of the Power Supply

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 37 / 89

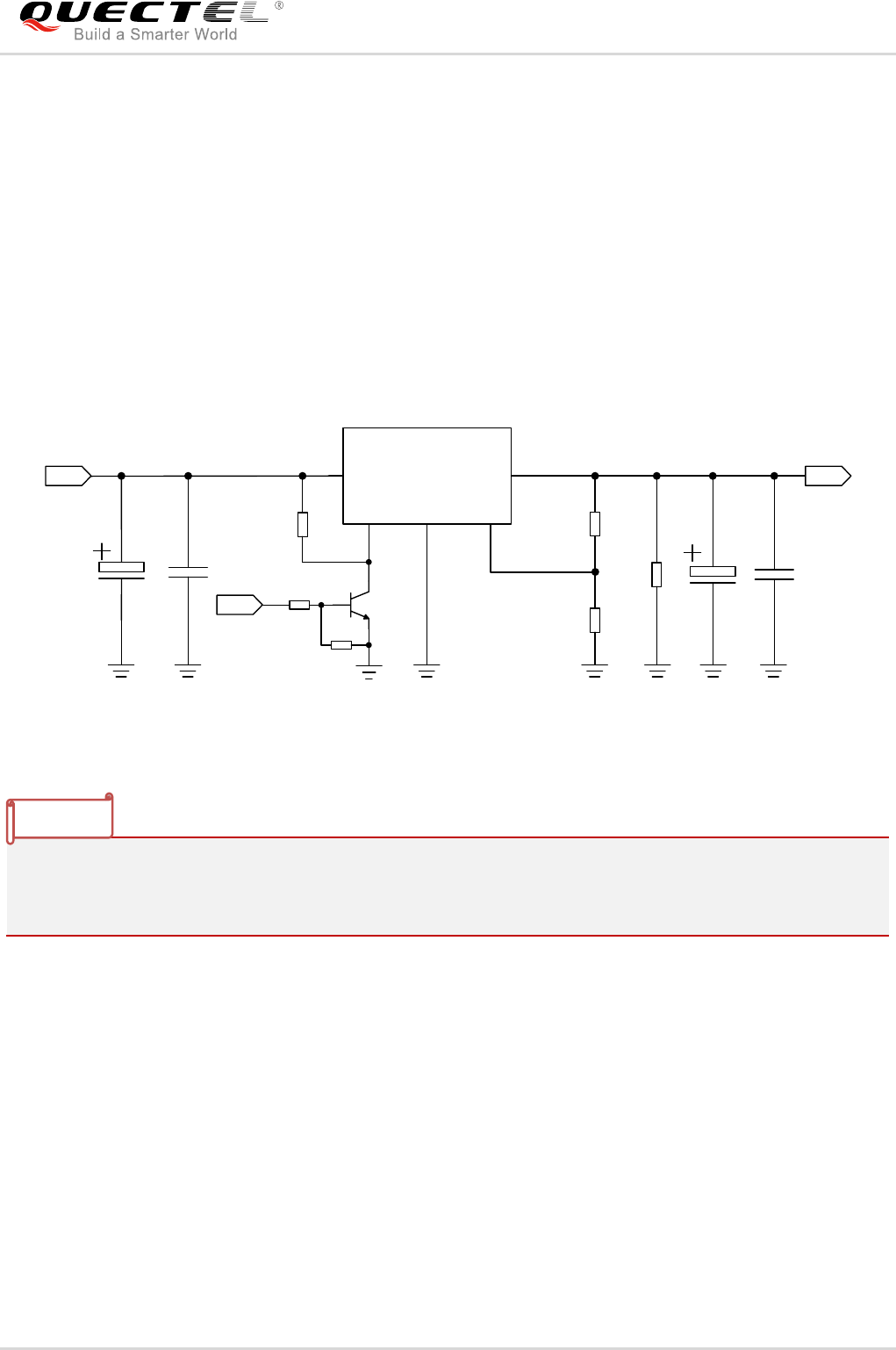

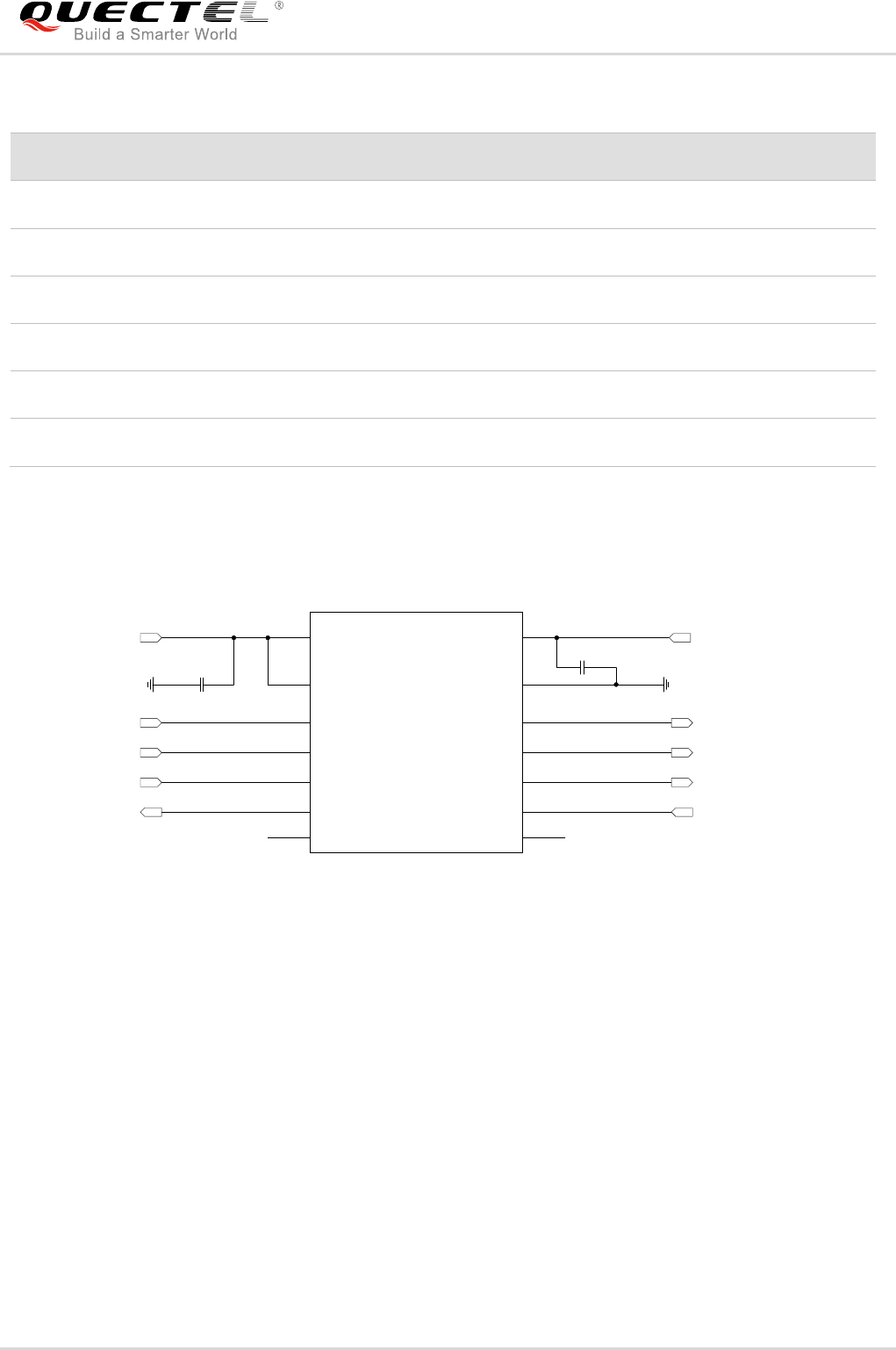

3.6.3. Reference Design for Power Supply

Power design for the module is very important, as the performance of the module largely depends on the

power source. The power supply of EG06 should be able to provide sufficient current up to 2A at least. If

the voltage drop between the input and output is not too high, it is suggested that an LDO should be used

to supply power for the module. If there is a big voltage difference between the input source and the

desired output (VBAT), a buck converter is preferred to be used as the power supply.

The following figure shows a reference design for +5V input power source. The designed output of the

power supply is about 3.8V and the maximum load current is 3A.

DC_IN

MIC29302WU

IN OUT

EN

GND

ADJ

2 4

1

3

5

VBAT

100nF 470uF 100nF

100K

47K

470uF

470R

51K 1%

1%

4.7K

47K

VBAT_EN

Figure 10: Reference Circuit of Power Supply

In order to avoid damaging internal flash, please do not switch off the power supply when the module

works normally. Only after the module is shut down by PWRKEY or AT command, the power supply can

be cut off.

3.6.4. Monitor the Power Supply

AT+CBC command can be used to monitor the VBAT_BB voltage value. For more details, please refer to

document [1].

3.7. Turn on and off Scenarios

3.7.1. Turn on Module Using the PWRKEY

The following table shows the pin definition of PWRKEY.

NOTE

LTE-A Module Series

EG06 Hardware Design

EG06_Hardware_Design 38 / 89

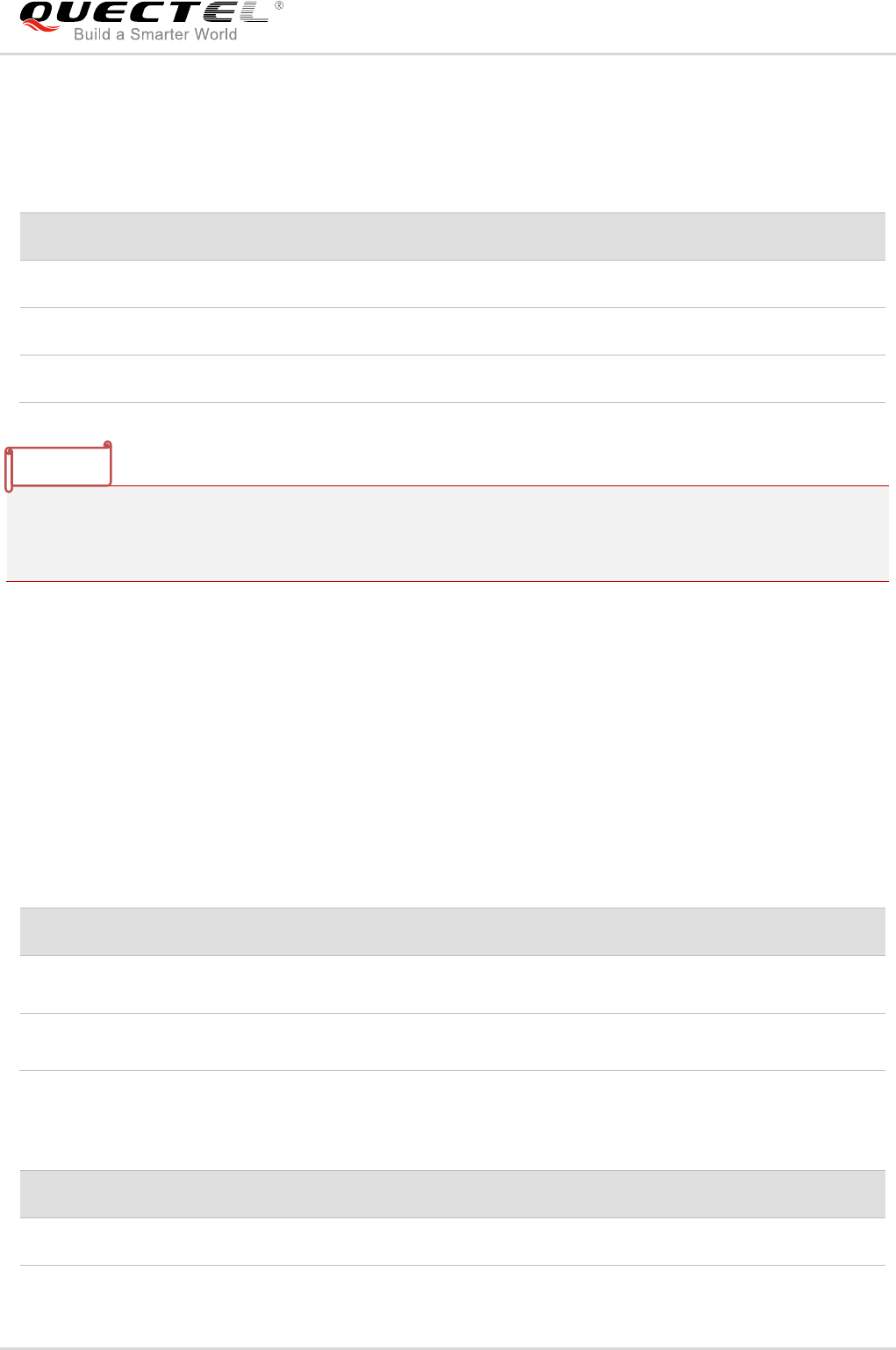

Table 7: PWRKEY Pin Description

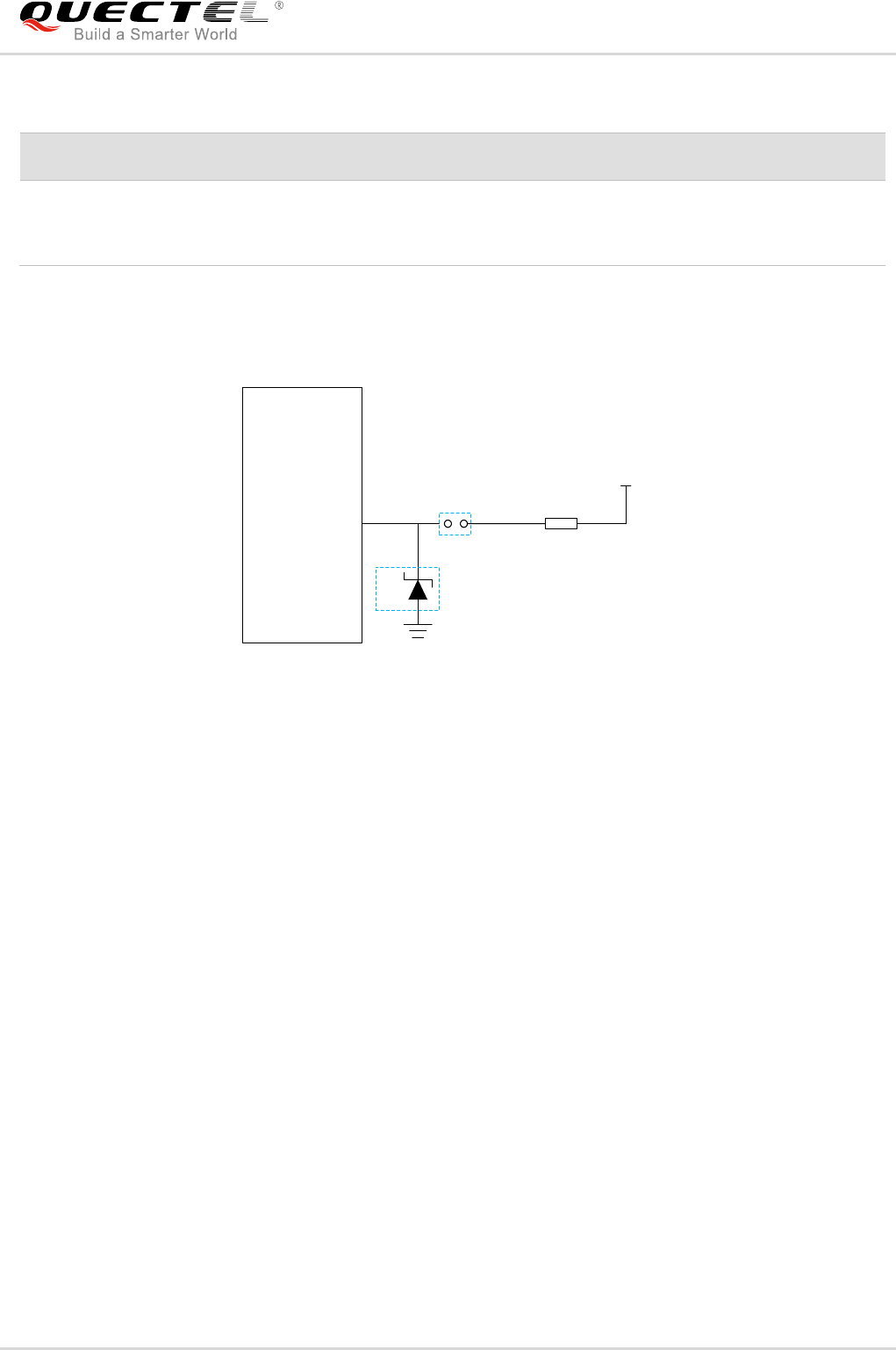

When EG06 is in power down mode, it can be turned on to normal mode by driving the PWRKEY pin to a

low level for at least 500ms. It is recommended to use an open drain/collector driver to control the

PWRKEY. After STATUS pin outputs a high level, PWRKEY pin can be released. A simple reference

circuit is illustrated in the following figure.

Turn on pulse

PWRKEY

4.7K

47K

≥500ms

Figure 11: Turn on the Module Using Driving Circuit

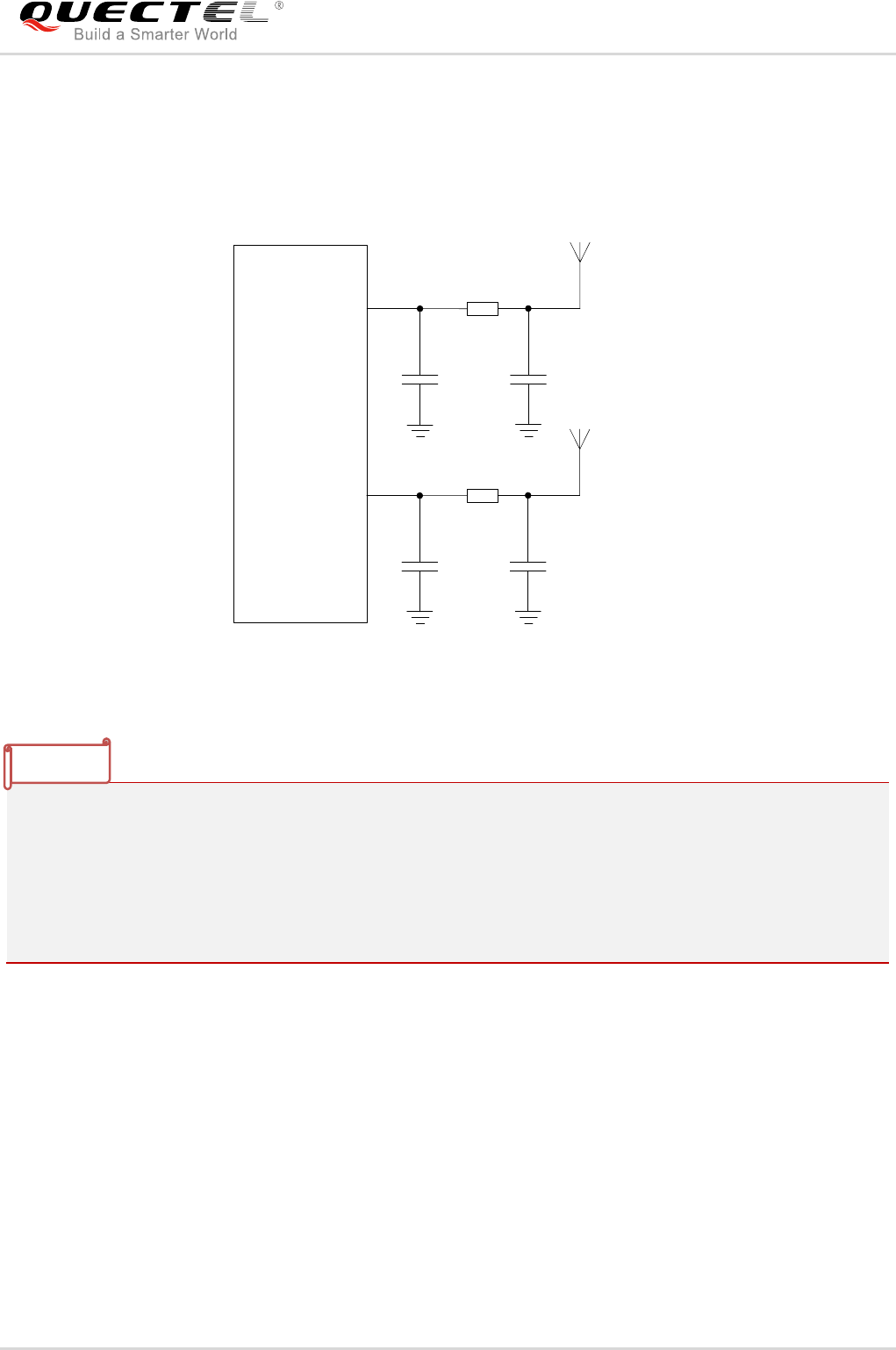

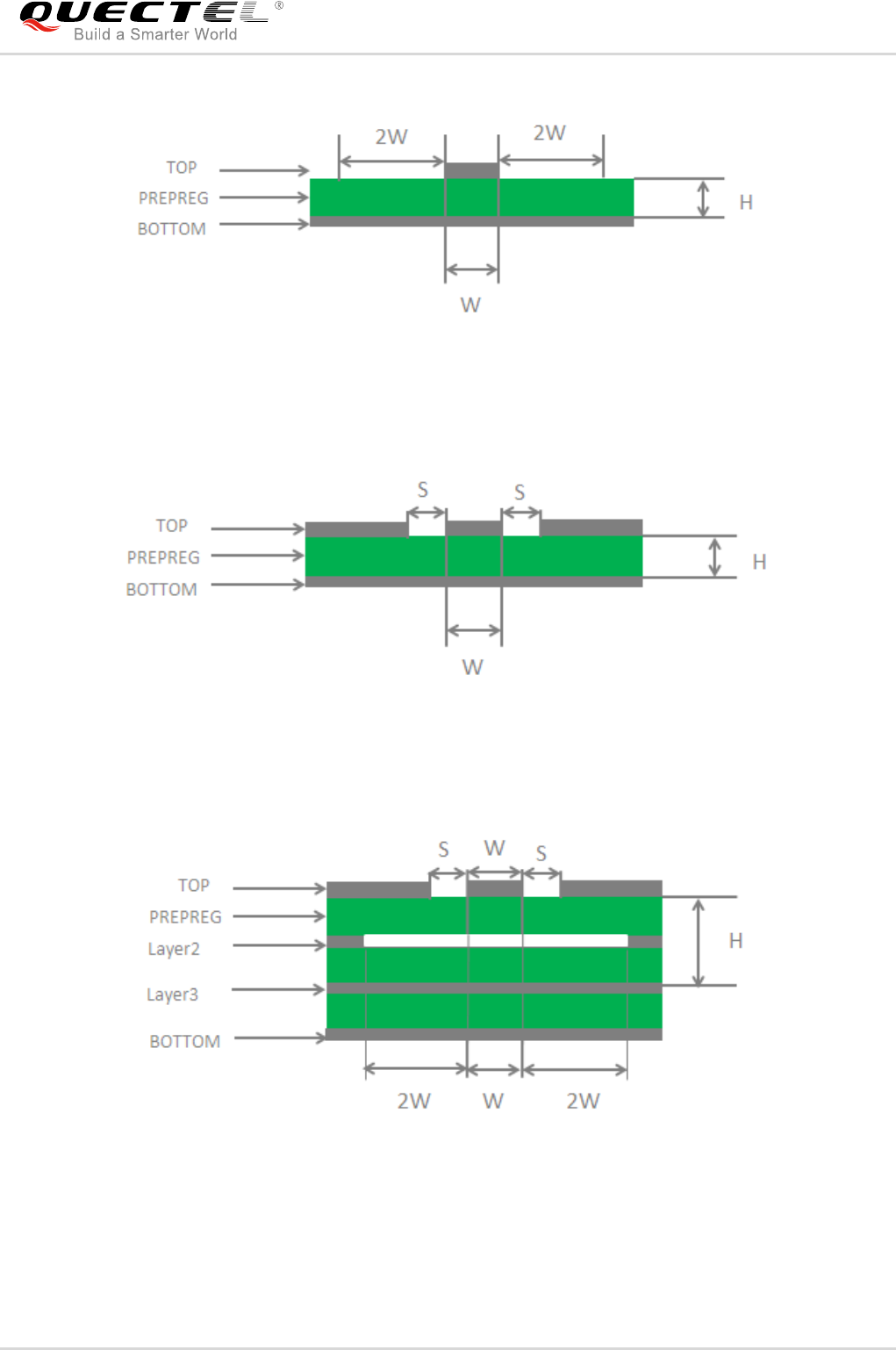

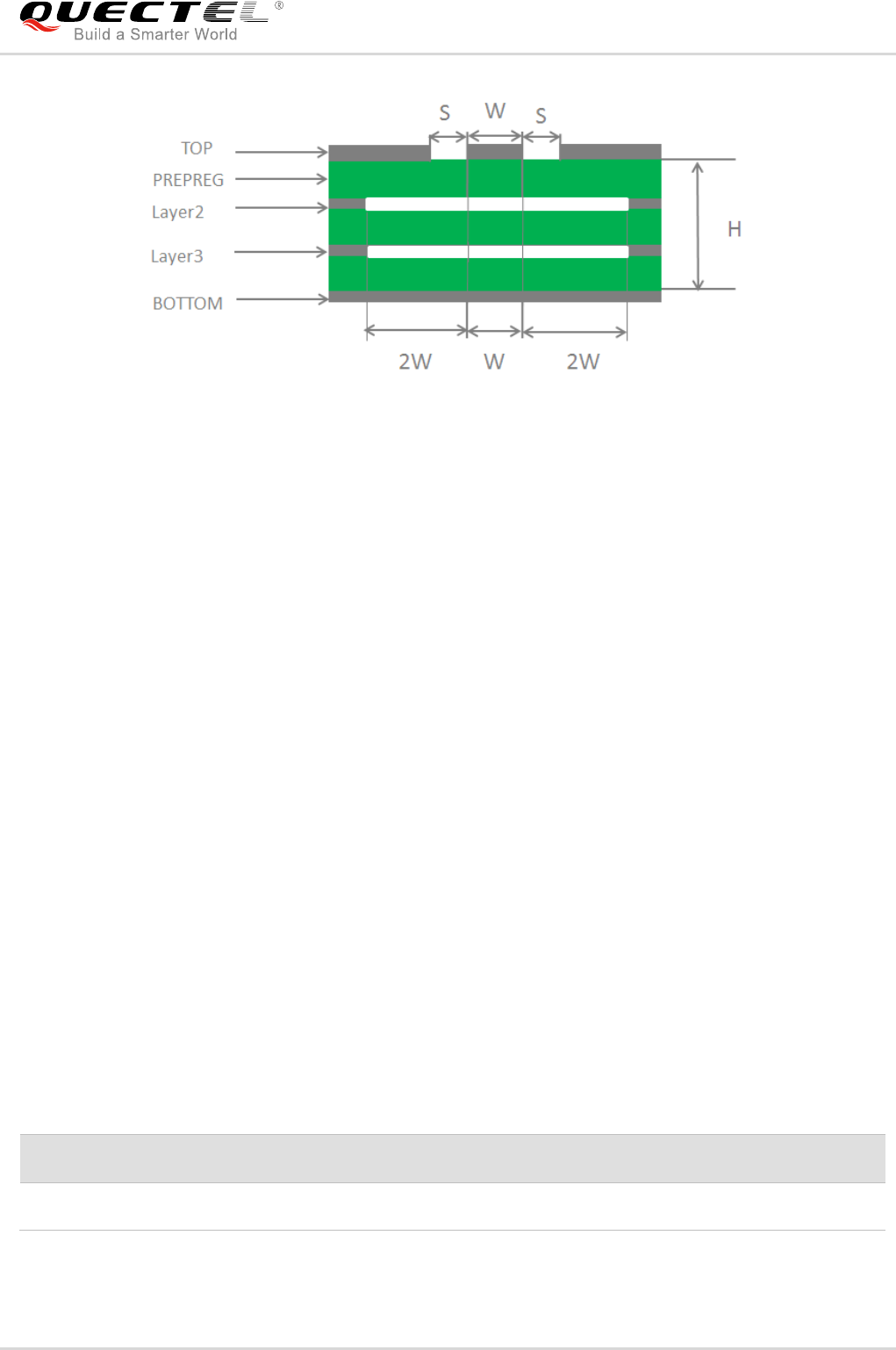

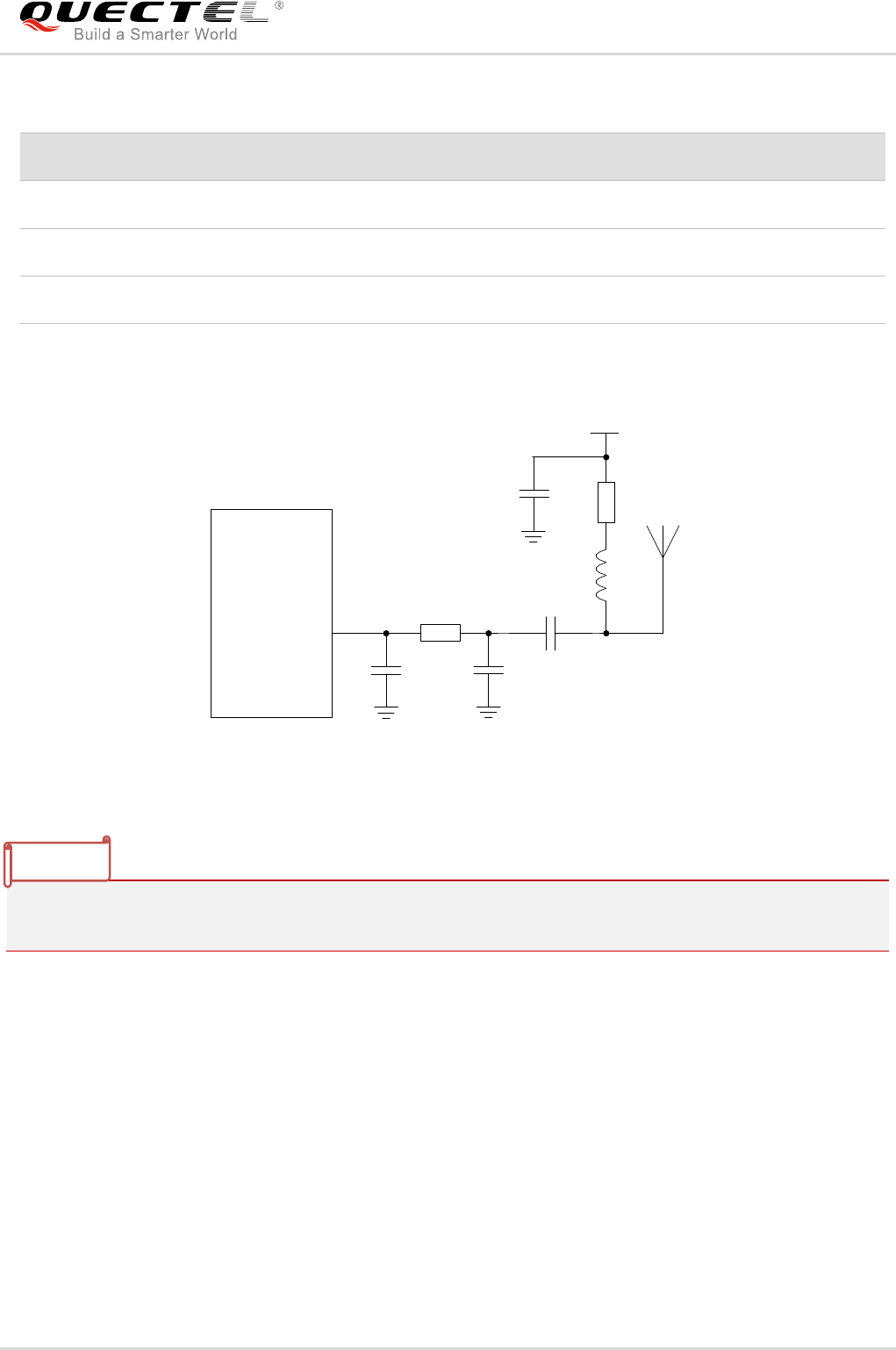

Another way to control the PWRKEY is using a button directly. When pressing the key, electrostatic strike