Trimble 613 HANDHELD GPS WITH BLUETOOTH User Manual WM BG MR 01 22 042805

Trimble Navigation Ltd HANDHELD GPS WITH BLUETOOTH WM BG MR 01 22 042805

Trimble >

Contents

- 1. USERS MANUAL 1 OF 2

- 2. USERS MANUAL 2 OF 2

- 3. users manual 1

- 4. users manual 2

users manual 2

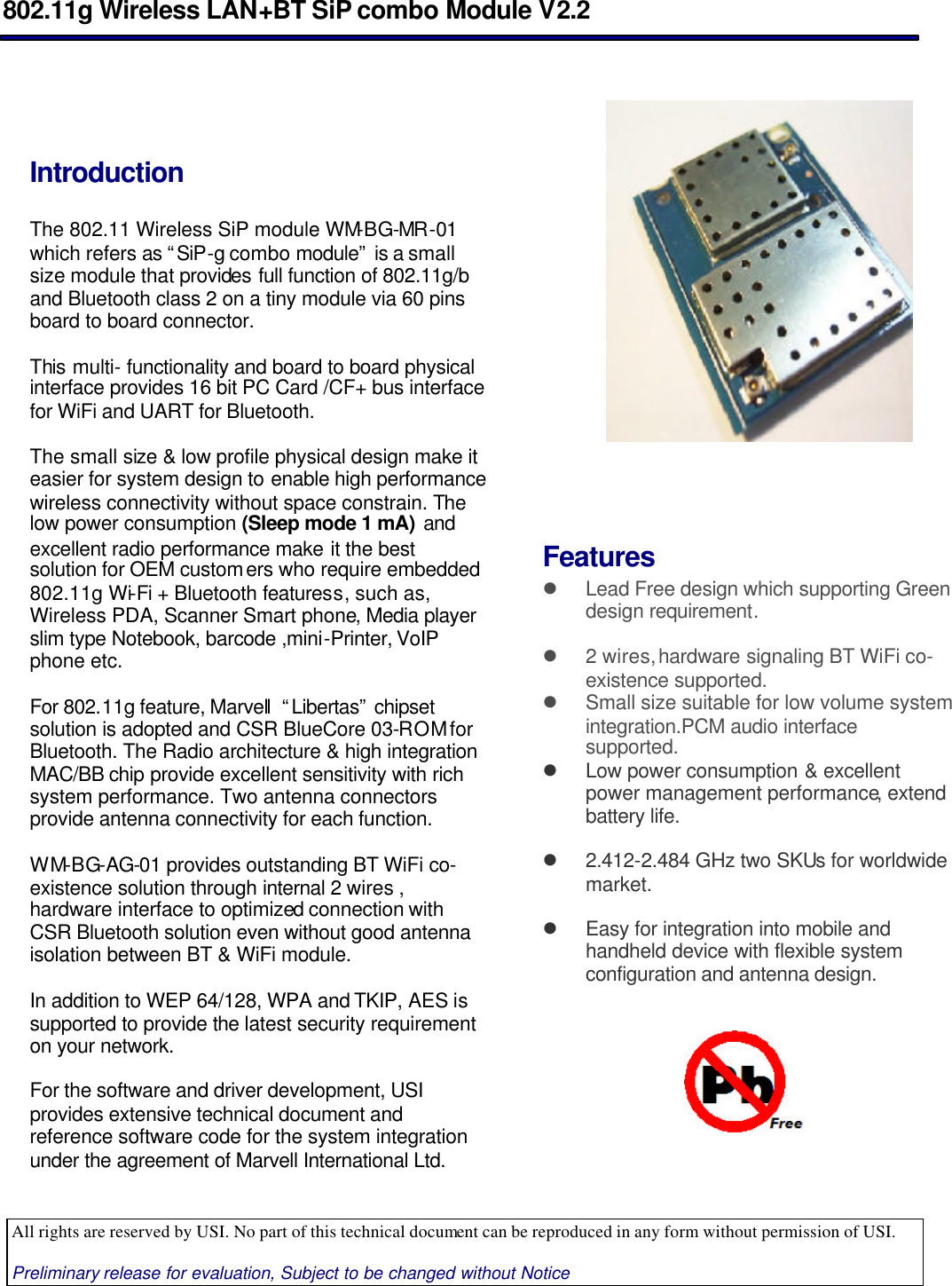

![802.11g Wireless LAN+BT SiP combo Module V2.2 All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI. Preliminary release for evaluation, Subject to be changed without Notice 9.5. PRODUCT MARKING The Module is marked by laser marking which containing the following information: Description: WM-BG-XX-XX Serial number: yyllwkxxxx Revision: format to follow USI revision level in PDM System For the serial number the following format will be followed: yy = last two digits of current year ll = Assembly Location: UT = USI Taiwan UM = USI Mexico UC = USI China wk = current week (week period = starting on Monday) xxxx = consecutive number, starting at 0000 at beginning of each week. 9.6. ENVIRONMENTALLY SAFE MATERIAL RESTRICTIONS The use of polychlorinated biphenyls (PCB’s) is prohibited (specifically) as dielectric in capacitors or transformers. Electrolytic capacitors shall not be composed of any quaternary salt ammonium and/or gamma-butyrolactone (i.e. no el caps allowed). No CFC's (chlorofluorocarbons) shall be used anywhere in the manufacture of this product. The use of tantalum capacitors should be minimized in any product of the product family [including the power-supply]. Where the use of tantalum caps cannot be avoided, provisions must be made in the manufacturing process to prevent reverse polarization. The WM-BG-MR-01 module hardware design should take the safety of operation into consideration and prevent the potential risk on Labor safety for manufacturing process.](https://usermanual.wiki/Trimble/613.users-manual-2/User-Guide-733454-Page-21.png)

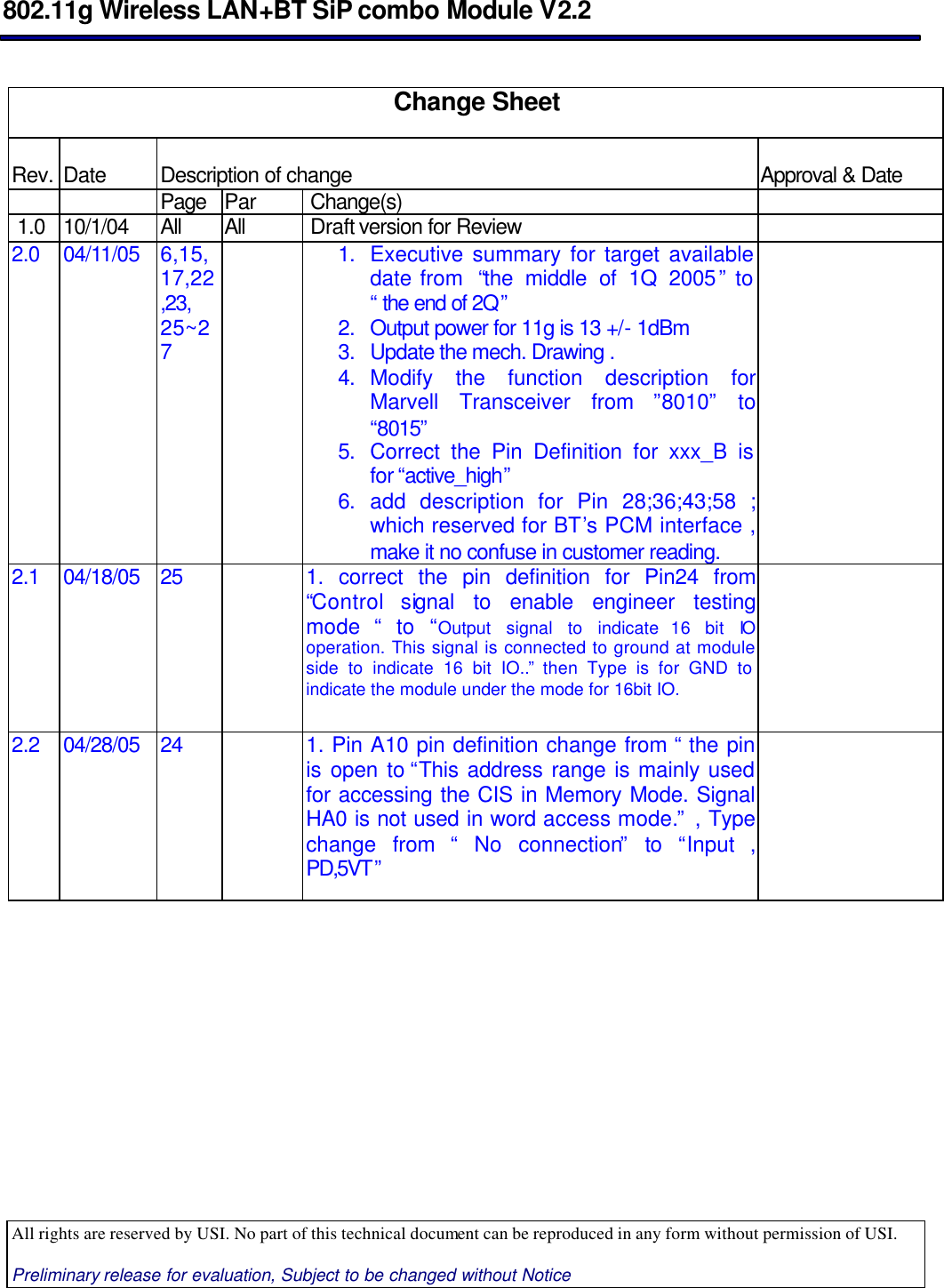

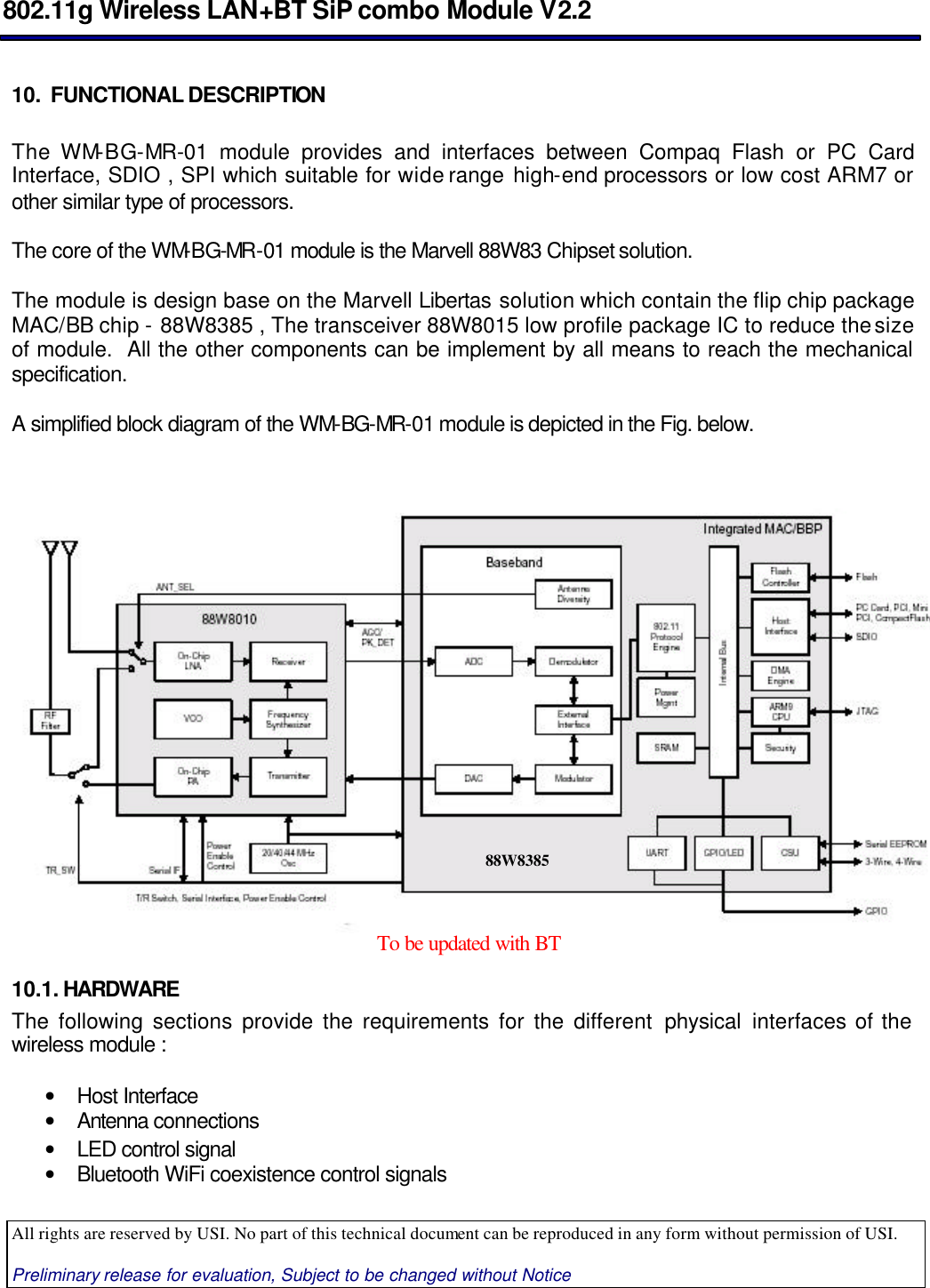

![802.11g Wireless LAN+BT SiP combo Module V2.2 All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI. Preliminary release for evaluation, Subject to be changed without Notice • Power • GND 10.2. HOST INTERFACE The host interface will be compatible with CompactFlash (PCMCIA) standard, 16 bit I/O bus. Signals which are not used won’t be routed to the physical interface (connector). The host interface of Combo SiP Bluetooth portion is compliant with UART interface, the default baud rate setting is 115.2kbps and the optional range is from 9.6kbps to 921.6kbps. On Board connector Molex 53794-0608 or 55560-0607 [Socket, 60 pins, with positioning protection, stack height which is able to support 1.5 mm] Datasheet_Molex_53794-0608.pdf Datasheet_Molex_55560-0607.pdf Host System: Host System Connector Molex 54722-0607 [Header, 60 pins, with positioning protection, stack height 1.5mm] Datasheet_Molex_54722-0607.pdf Pin definition [ …] means optional function of the pin. PD : Signal pull down internally in the chip by 50K ohm while initialization. PU : Signal pull up internally in the chip by 100K ohm while initialization. 5VT: 5 Volt tolerance pin xxx_B : Signal pins end with _B are “active high” Pin Number Definition Draft Description Type WM-BG-MR-01 CF+ interface 1 GND GND GND 2 D03 HD3 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE O, PD, 5VT, 4mA](https://usermanual.wiki/Trimble/613.users-manual-2/User-Guide-733454-Page-23.png)

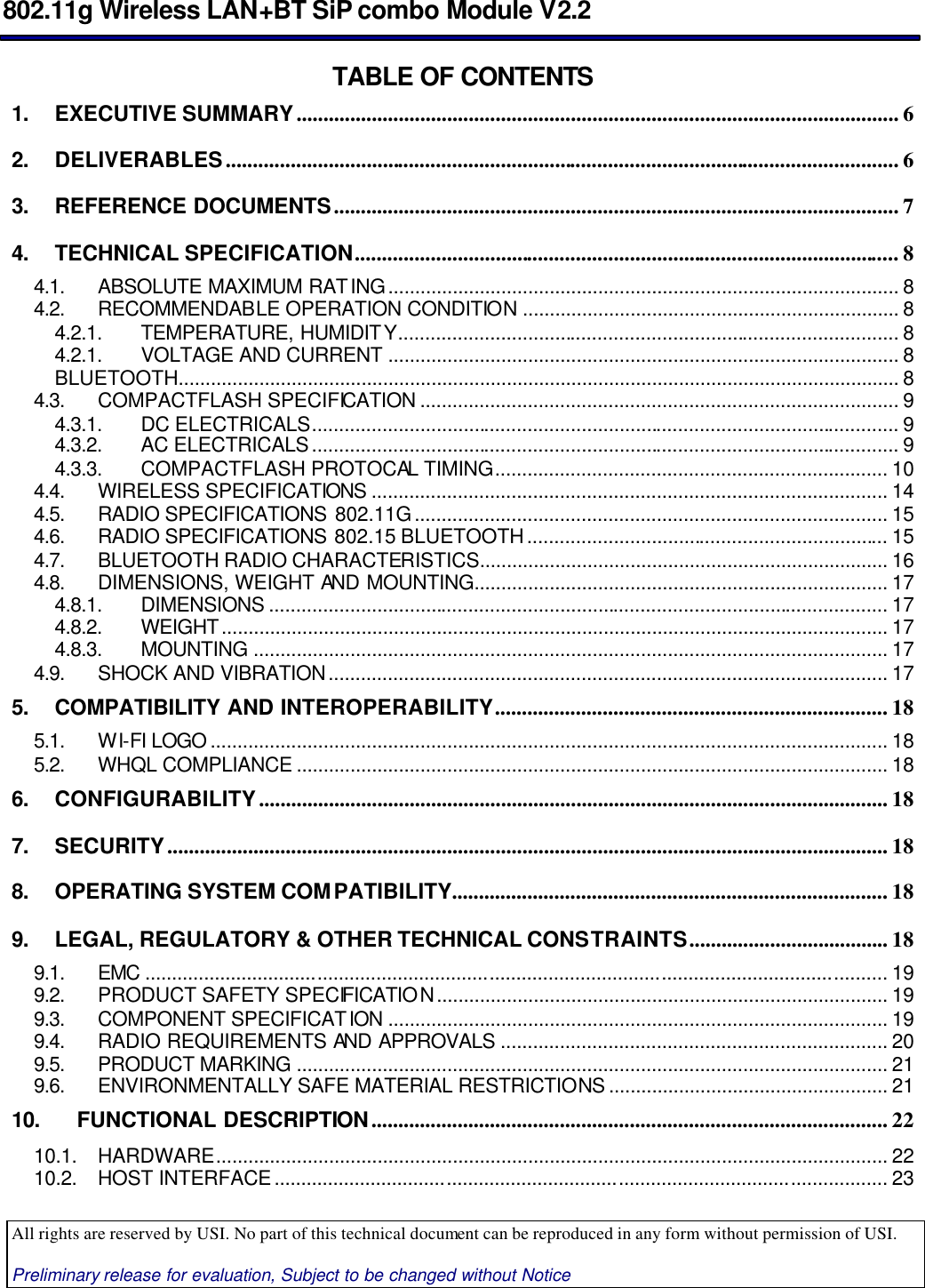

![802.11g Wireless LAN+BT SiP combo Module V2.2 All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI. Preliminary release for evaluation, Subject to be changed without Notice bus. HD[15:0] are used to access the MODULE MAC Host Interface register Databus 3 D04 HD4 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register O, PD, 5VT, 4mA Databus 4 D05 HD5 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA Databus 5 D06 HD6 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA 6 D07 HD7 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA 7 -CE_1 HCE1_B Card Enable1 is driven by the host system and is used as select strobe in both I/O and memory mode. Enables even numbered address bytes. Input, PU, 5VT 8 A10 A10 ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode.The pin is open in B2B module. Input, PD,5VT 9 -OE HOE_B OUTPUT ENABLE is driven by the host during a memory Read Access. Input, PU,5VT 10 A09 HA9 ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. Input, PD,5VT 11 A08 HA8 ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. Input, PD,5VT 12 A07 HA7 ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. Input, PD,5VT 13 VCC VCC_WLAN Power, 3.3V_WLAN Input 14 A06 HA6 ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. Input, PD, 5VT 15 A05 HA5 ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. Input, PD, 5VT 16 A04 HA4 ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for Input, PD, 5VT](https://usermanual.wiki/Trimble/613.users-manual-2/User-Guide-733454-Page-24.png)

![802.11g Wireless LAN+BT SiP combo Module V2.2 All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI. Preliminary release for evaluation, Subject to be changed without Notice within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. 17 A03 HA3 ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC . This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. Input, PD, 5VT 18 A02 HA2 ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. Input, PD, 5VT 19 A01 HA1 ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. Input, PD, 5VT 20 A00 HA0 ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. Input, PD, 5VT 21 D00 HD0 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA 22 D01 HD1 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA 23 D02 HD2 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA 24 -IOIS16 IOIS16_B Output signal to indicate 16 bit IO operation. This signal is connected to ground at module side to indicate 16 bit IO.. GND 25 -CD2 CD2 Normal operation, this pin is functionally for card detection. Out, 6mA, 5VT. 26 N/A TXD_B UART CMOS output data line Output,WPU, 1µA 27 N/A RTS_B UART CMOS output signal, request to sent Output ,WPU, 1µA 28 N/A PCM_In Reserved for BT portion , keep its open on host side if no use. 29 N/A VCC_WLAN Power_WLAN Input 30 GND GND 31 GND GND 32 D10 HD10 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA 33 D09 HD9 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA](https://usermanual.wiki/Trimble/613.users-manual-2/User-Guide-733454-Page-25.png)

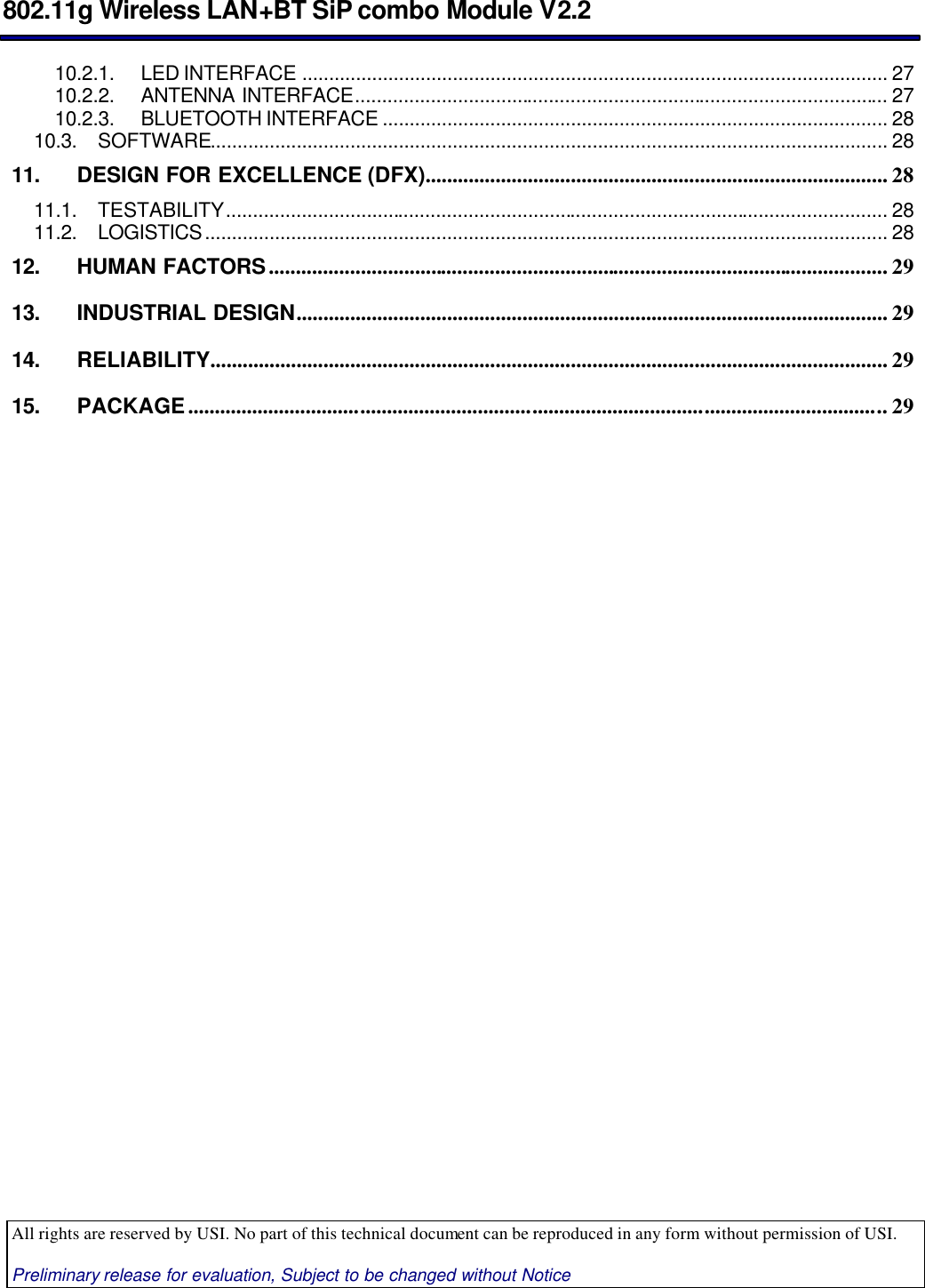

![802.11g Wireless LAN+BT SiP combo Module V2.2 All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI. Preliminary release for evaluation, Subject to be changed without Notice 34 D08 HD8 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA 35 -STSCHG HSTSCHG_B STATUS CHANGE indication to the host. This signal gets active when one of the bits in the PRR or CSR registers are set Output, 4mA 36 -SPKR PCM_Sync Reserved for BT portion , keep its open on host side if no use. 37 -REG HREG_B ATTRIBUTE MEMORY SELECT is driven by the host system and is used to access the Attribute Memory Input, PU, 5VT 38 -INPACK HINPACK_B INPUT ACKNOWLEDGE is driven by MAC. Is asserted when the device is selected and the device is responding to an I/O Read command. Output, 2mA 39 -WAIT HWAIT_B HWAIT_B is driven by MAC and allows for extending the memory or I/O cycle Output, 4mA 40 RESET HRESET Used to asynchronously reset the complete Module Input, PU,5VT 41 -VS2 VS2_B Voltage sense signal Output , 5VT 4mA 42 N/A WLAN_LED_B WLAN LED control signal, driven the LED indicating the link status of WLAN Output, 4mA 43 N/A PCM_OUT Reserved for BT portion , keep its open on host side if no use. 44 IREQ IREQ_B INTERRUPT REQUEST to the host. In Memory mode this pin signifies RDY/BSY_typically used during card initialization immediately after reset or power on. Indicates to the host that the device is not able to transfer data Output, 4mA 45 -WE HWE_B WRITE ENABLE is driven by the host during a memory Write Access Input, PU,5VT 46 -IOWR HIOWR_B I/O Write Strobe is driven by the host and is asserted when the host wants to write to an on-chip I/O register Input, PU,5VT 47 -IORD HIORD_B I/O Read Strobe is driven by the host and is asserted when the host wants to read from an on-chip I/O register Input, PU,5VT 48 -VS1 -VS1 Reserved Output , 5VT 49 -CE2 HCE2_B CARD ENABLE2 is driven by the host system and is used as select strobe in both I/O and memory mode. Enables odd numbered address bytes Input, PU,5VT 50 D15 HD15 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA 51 D14 HD14 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA 52 D13 HD13 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA 53 D12 HD12 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA](https://usermanual.wiki/Trimble/613.users-manual-2/User-Guide-733454-Page-26.png)

![802.11g Wireless LAN+BT SiP combo Module V2.2 All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI. Preliminary release for evaluation, Subject to be changed without Notice 54 D11 HD11 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register IO, PD, 5VT, 4mA 55 N/A BT_LED_B BT LED control signal which drive the LED to indicate the activity of Bluetooth Output 4mA 56 N/A RXD_B UART data line CMOS input signal Input, WPD, 1µA 57 N/A CTS_B UART clear to sent COMS input signal Input, WPD, 1µA 58 N/A PCM_CLK Reserved for BT portion , keep its open on host side if no use. 59 VCC VCC_BT Power 3.3V_BT Input 60 GND GND Fig 1: Pin 1 assignment and indication Drawing ( To be updated with latest design) 10.2.1. LED INTERFACE The Wireless Module will provide two control signals to the host and capable to drive an LED to indicate the connectivity and operating status. The WM-BG-MR -01 have 2 LED’s (output) via 60 pins connector for feedback to the user on the current WLAN activity state. The signaling will reflect status / activity as described in the table below. Those two signals are provided via the board to board connector with the following pin assignment. Pin No Pin description Function description 42 WLAN_LED Link activity of Wireless LAN 55 BT Power status indication LED code to be defined ! 10.2.2. ANTENNA INTERFACE No antenna diversity supported on the Wireless Module. The output impedance of the cable is 50 Ohms. Antenna Connector: Hirose W-FL-R-SMT(10) Pin 1 Pin 59 Pin 60](https://usermanual.wiki/Trimble/613.users-manual-2/User-Guide-733454-Page-27.png)