UBS Axcera LU500AL 500-Watt UHF Translator User Manual 382699

UBS-Axcera 500-Watt UHF Translator 382699

Contents

- 1. Section 5 Users Manual Page

- 2. Title Page External Amplifier

- 3. Table of Contents External Amplifier

- 4. Chapter 1 External Amplifier

- 5. Chapter 2 External Amplifier

- 6. Chapter 3 External Amplifier

- 7. Chapter 4 External Amplifier

- 8. Chapter 5 External Amplifier

- 9. Appendix Pages External Amplifier

- 10. Drawings List External Amplifier

- 11. Title Page Exciter

- 12. Table of Contents Exciter

- 13. Chapter 1 Exciter

- 14. Chapter 2 Exciter

- 15. Chapter 3 Exciter

- 16. Chapter 4 Exciter

- 17. Chapter 5 Exciter

- 18. Appendix Pages Exciter

- 19. Drawings List Exciter

- 20. Data Sheet Exciter and Amplifier

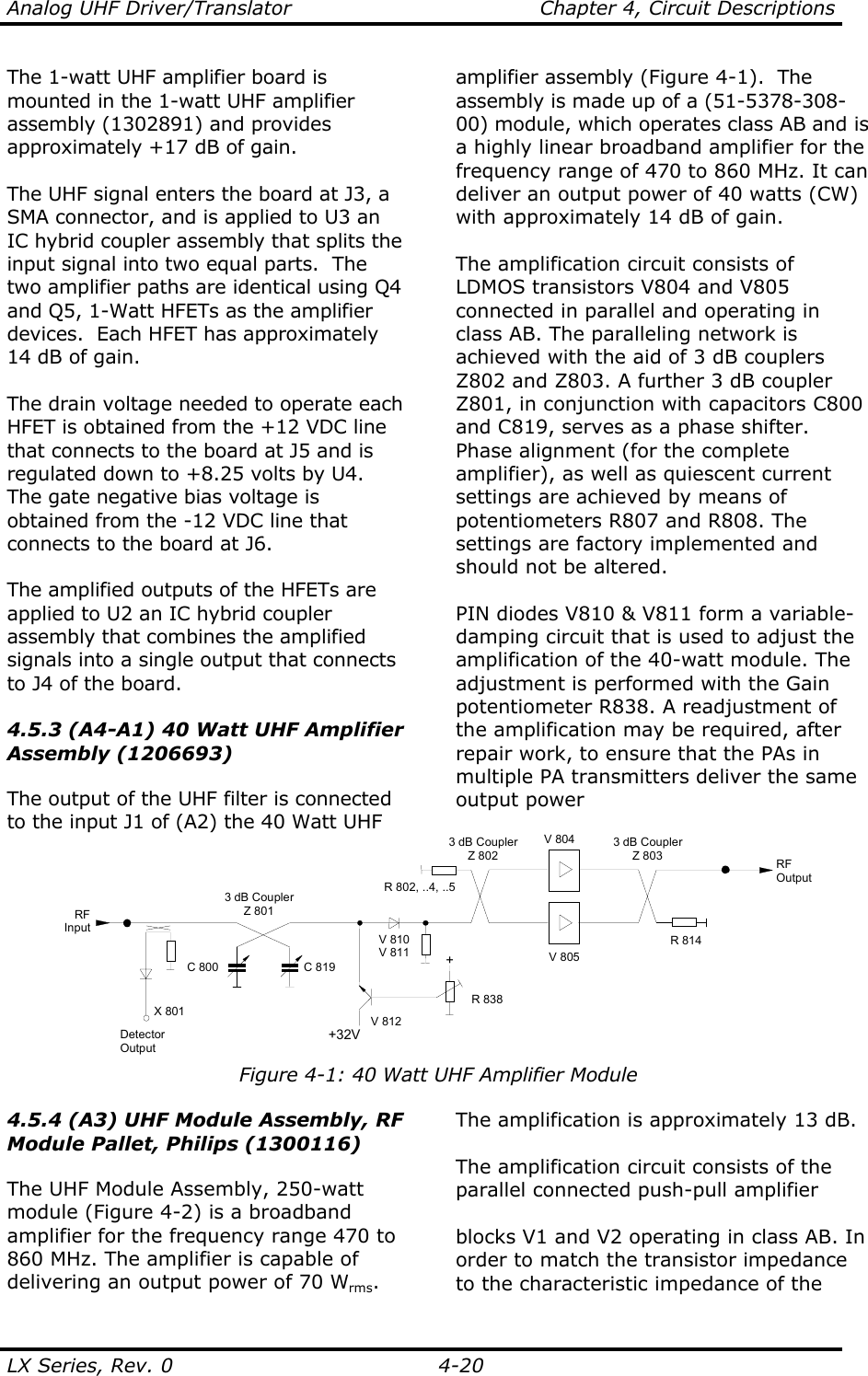

Chapter 4 Exciter