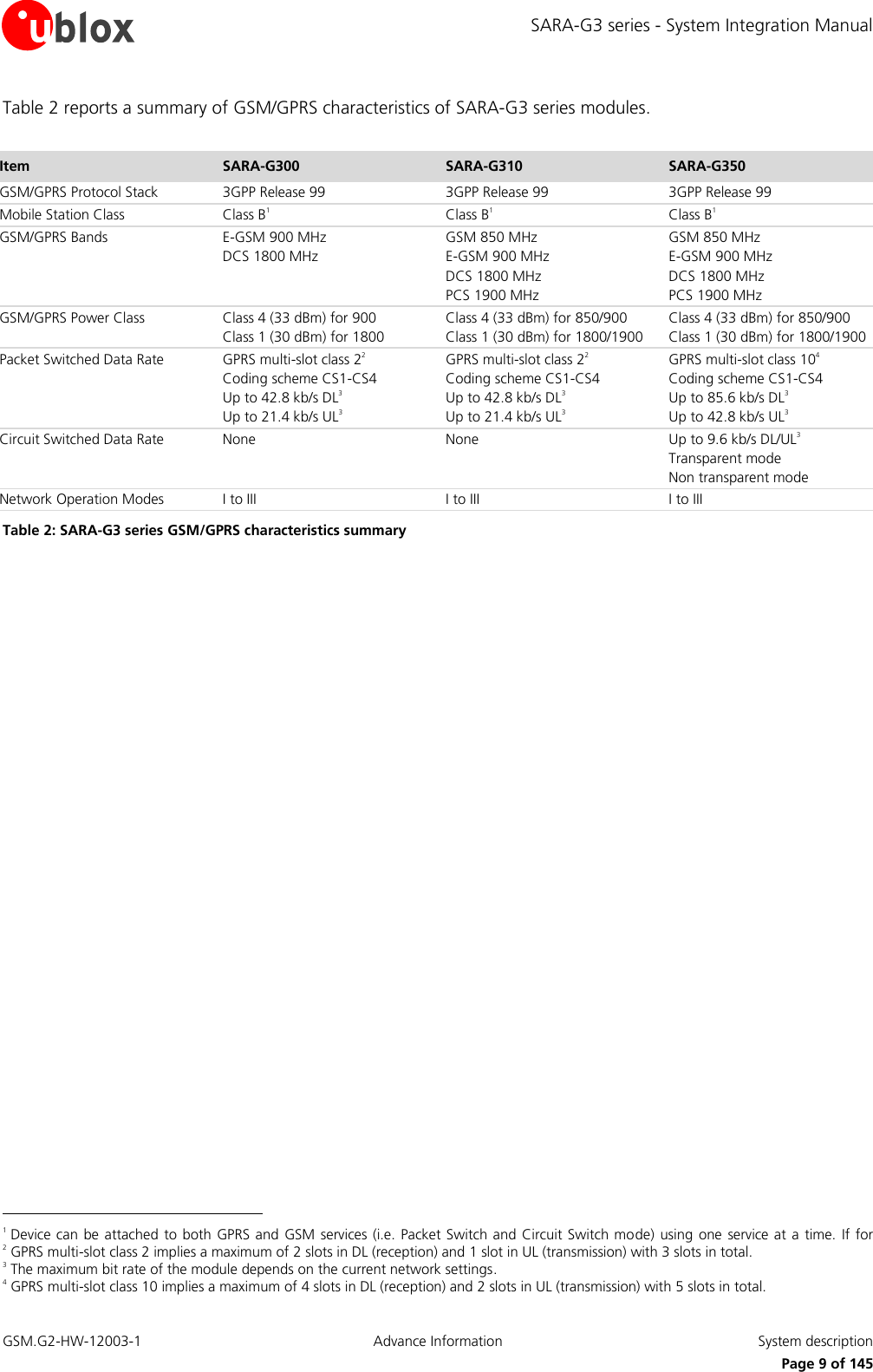

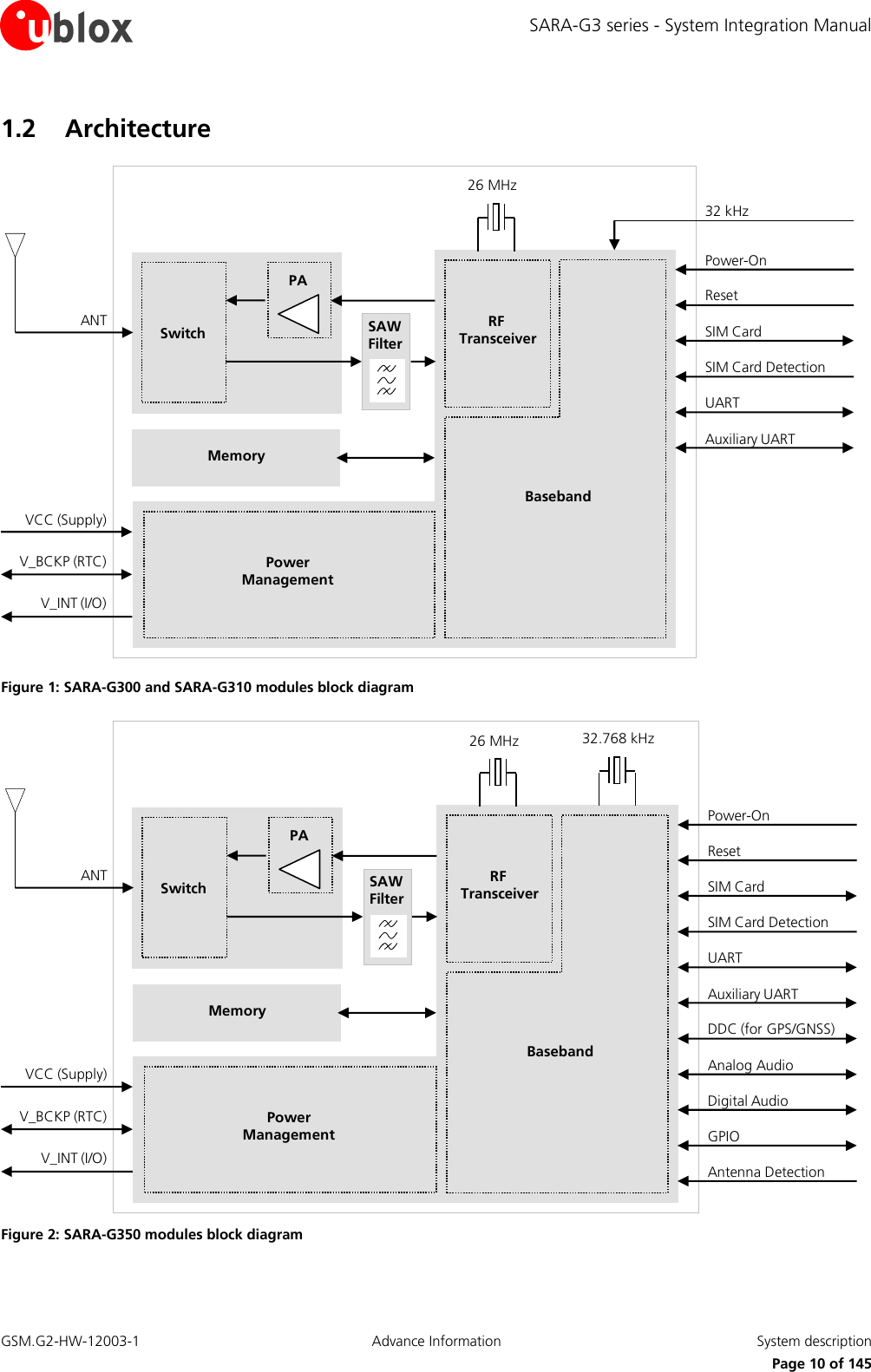

u blox SARAG350 Quad band (GSM850, GSM 900, DCS 1800, PCS 1900) GSM/GPRS module User Manual SARA G3 series

u-blox AG Quad band (GSM850, GSM 900, DCS 1800, PCS 1900) GSM/GPRS module SARA G3 series

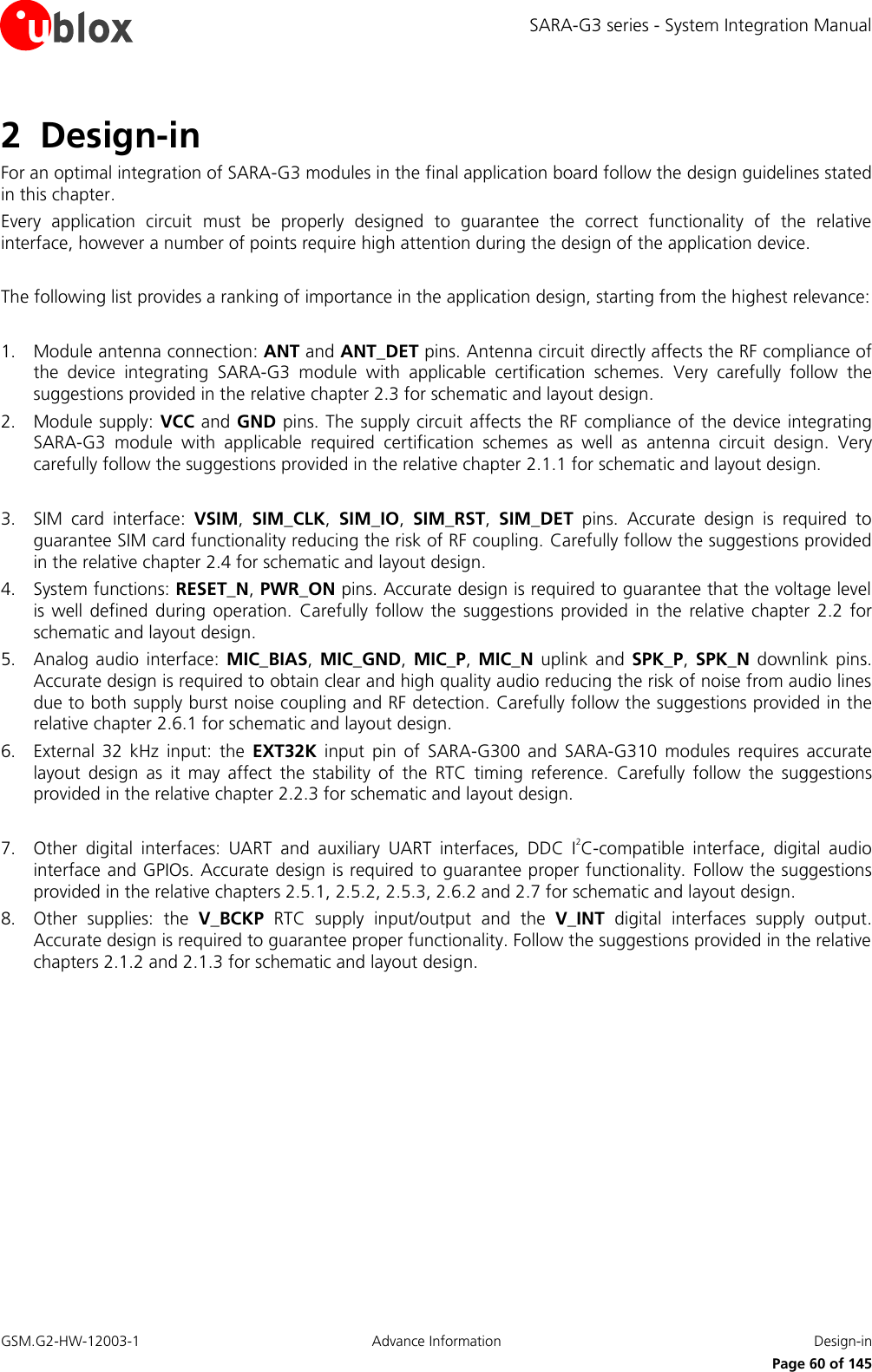

u blox >

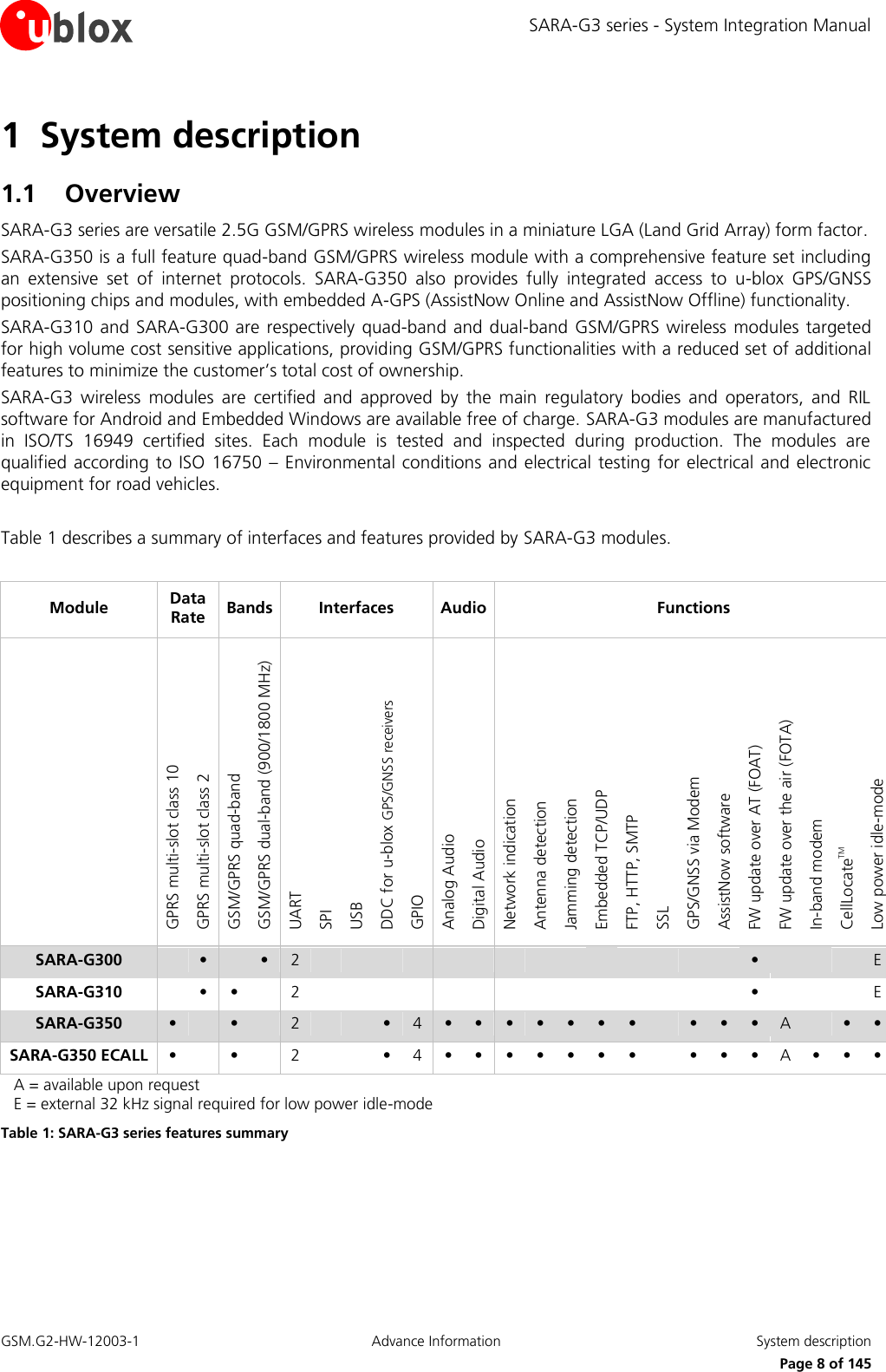

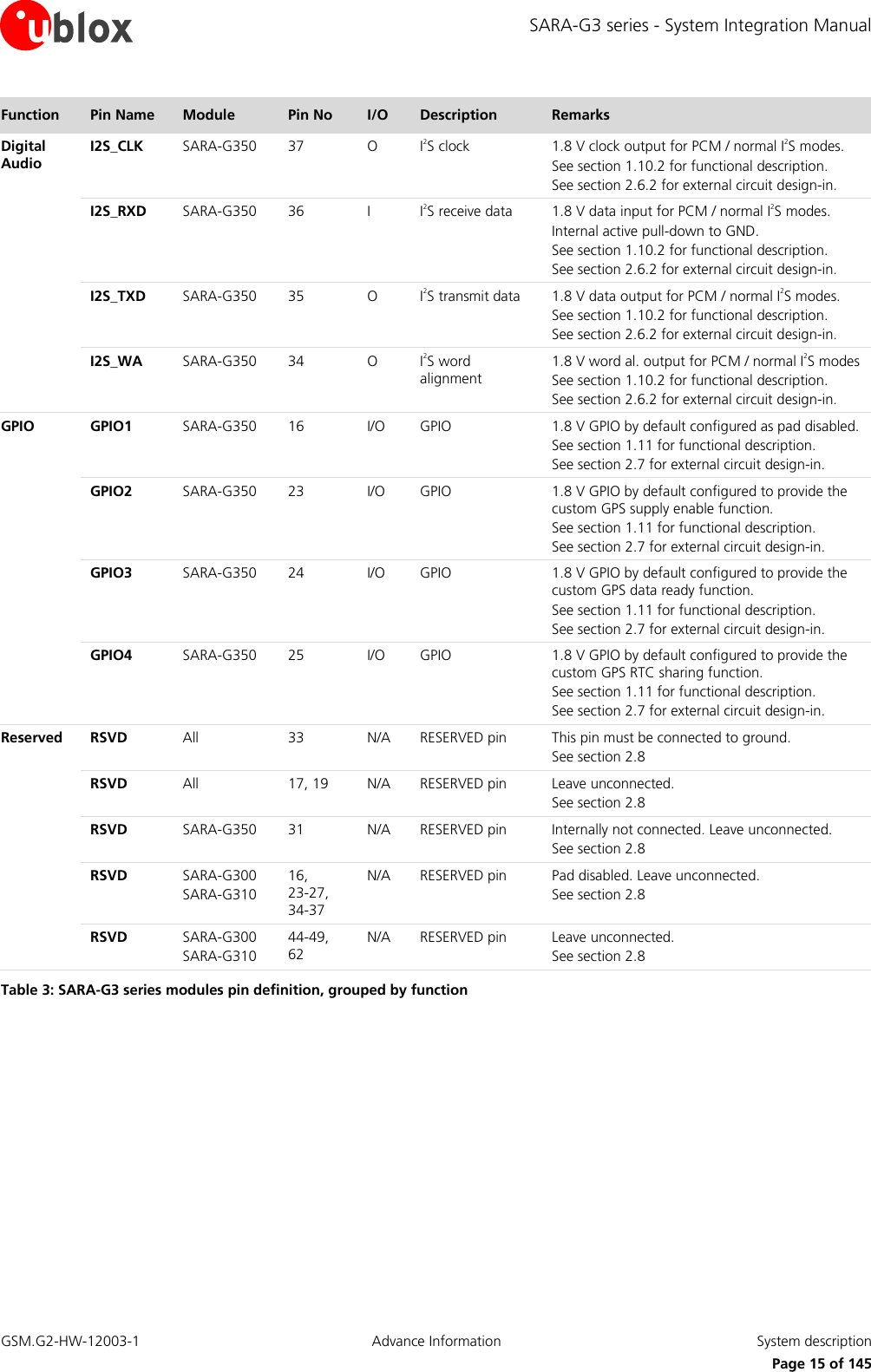

Contents

- 1. Users_manual

- 2. User manual

Users_manual

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 16 of 145 1.4 Operating modes SARA-G3 modules have several operating modes. The operating modes are defined in Table 4 and described in details in Table 5, providing general guidelines for operation. General Status Operating Mode Definition Power-down Not-Powered Mode VCC supply not present or below operating range: module is switched off. Power-Off Mode VCC supply within operating range and module is switched off. Normal Operation Idle-Mode Module processor core runs with 32 kHz reference, that is generated by: The internal 32 kHz oscillator (SARA-G350) The 32 kHz signal provided at the EXT32K pin (SARA-G300 and SARA-G310) Active-Mode Module processor core runs with 26 MHz reference generated by the internal oscillator. Connected-Mode Voice or data call enabled and processor core runs with 26 MHz reference. Table 4: Module operating modes definition Operating Mode Description Transition between operating modes Not-Powered Mode Module is switched off. Application interfaces are not accessible. Internal RTC timer only operates if a valid voltage is applied to V_BCKP pin (necessary for all SARA-G3 modules), and if a valid 32 kHz signal is provided to EXT32K pin (necessary only for SARA-G300 and SARA-G310 modules) When VCC supply is removed, the module enters not-powered mode. When in not-powered mode, the module cannot be switched on by a low level on PWR_ON input or by a preset RTC alarm. When in not-powered mode, the module can be switched on applying VCC supply (refer to 2.2.1) so that the module switches from not-powered to active-mode. Power-Off Mode Module is switched off: normal shutdown by an appropriate power-off event (refer to 1.6.2). Application interfaces are not accessible. Only the internal RTC timer in operation. A valid 32 kHz signal must be provided to EXT32K pin of SARA-G300 and SARA-G310 modules to let RTC timer running that otherwise is in operation (this is not needed for the other SARA-G3 series modules). When the module is switched off by an appropriate power-off event (refer to 1.6.2), the module enters power-off mode from active-mode. When in power-off mode, the module can be switched on by a low level on PWR_ON input or by a preset RTC alarm (refer to 2.2.1): module switches from power-off to active-mode. When VCC supply is removed, the module switches from power-off mode to not-powered mode. Idle-Mode The module is not ready to communicate with an external device by means of the application interfaces since configured to reduce power consumption. The module automatically enters idle-mode whenever possible if power saving is enabled by the AT+UPSV command (refer to u-blox AT Commands Manual [2]), reducing power consumption (refer to 1.5.1.3). The CTS output line indicates when the UART interface is disabled/enabled due to the module idle/active-mode according to power saving and hardware flow control settings (refer to 1.9.1.3, 1.9.1.4). Power saving configuration is not enabled by default: it can be enabled by the AT+UPSV command (see u-blox AT Commands Manual [2]). A valid 32 kHz signal must be provided to EXT32K pin of SARA-G300 and SARA-G310 modules to let idle-mode that otherwise cannot be reached (this is not needed for the other SARA-G3 series modules). The module automatically switches from active-mode to idle-mode whenever possible if power saving is enabled (refer to sections 1.5.1.3, 1.9.1.4 and to the u-blox AT Commands Manual [2], AT+UPSV). The module wakes up from idle-mode to active-mode in the following events: Automatic periodic monitoring of the paging channel for the paging block reception according to network conditions (refer to 1.5.1.3, 1.9.1.4) Automatic periodic enable of the UART interface to receive and send data, if the power saving AT command is set to 1 (refer to 1.9.1.4) RTC alarm occurs (refer to u-blox AT Commands Manual [2], AT+CALA command) Data received on UART interface (refer to 1.9.1.4) RTS input line set to the ON state by the DTE if hardware flow control has been disabled by AT&K3 and the power saving AT command is set to 2 (refer to 1.9.1.4) GPS data ready: when the GPIO3 pin is informed by the connected u-blox GPS/GNSS receiver that it is ready to send data via the DDC (I2C) interface (refer to 1.11, 1.9.3)](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-16.png)

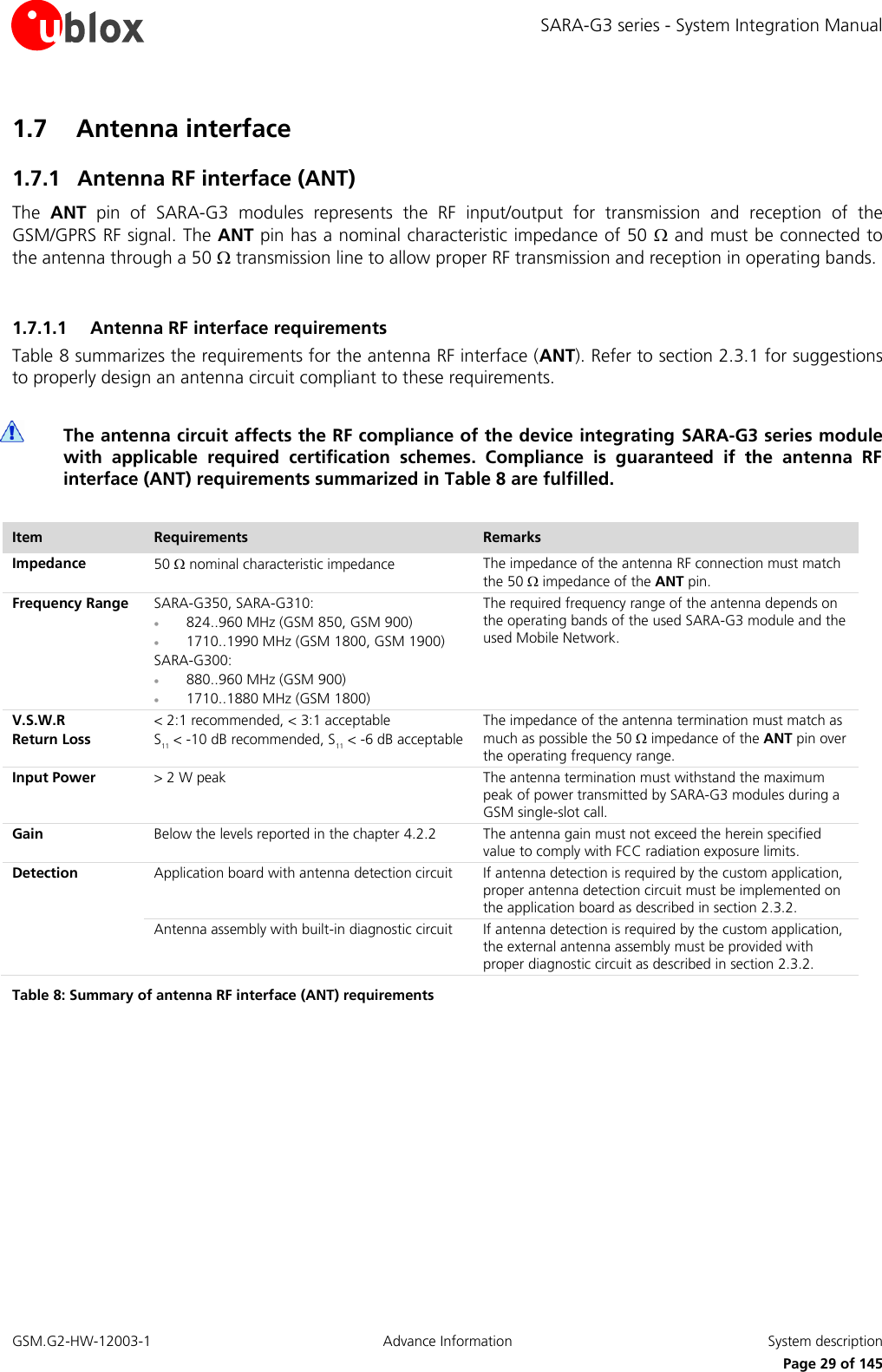

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 17 of 145 Operating Mode Description Transition between operating modes Active-Mode The module is ready to communicate with an external device by means of the application interfaces unless power saving configuration is enabled by the AT+UPSV command (refer to sections 1.5.1.3, 1.9.1.4 and to the u-blox AT Commands Manual [2]). When the module is switched on by an appropriate power-on event (refer to 2.2.1), the module enters active-mode from not-powered or power-off mode. If power saving configuration is enabled by the AT+UPSV command, the module automatically switches from active to idle-mode whenever possible and the module wakes up from idle to active-mode in the events listed above (refer to idle to active transition description). When a voice call or a data call is initiated, the module switches from active-mode to connected-mode. Connected-Mode A voice call or a data call is in progress. The module is ready to communicate with an external device by means of the application interfaces unless power saving configuration is enabled by the AT+UPSV command (see sections 1.5.1.3, 1.9.1.4 and the u-blox AT Commands Manual [2]). When a voice call or a data call is initiated, the module enters connected-mode from active-mode. When a voice call or a data call is terminated, the module returns to the active-mode. Table 5: Module operating modes description Figure 3 describes the transition between the different operating modes. Switch ON:•Apply VCCIf power saving is enabled and there is no activity for a defined time intervalAny wake up event described in the module operating modes summary table aboveIncoming/outgoing call or other dedicated device network communicationCall terminated, communication droppedRemove VCCSwitch ON:•PWR_ON•RTC AlarmNot poweredPower offActiveConnected IdleSwitch OFF:•AT+CPWROFF Figure 3: Operating modes transition](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-17.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 18 of 145 1.5 Supply interfaces 1.5.1 Module supply input (VCC) SARA-G3 modules must be supplied via the three VCC pins that represent the module power supply input. The VCC pins are internally connected to the RF power amplifier and to the integrated Power Management Unit: all supply voltages needed by the module are generated from the VCC supply by integrated voltage regulators, including V_BCKP Real Time Clock supply, V_INT digital interfaces supply and VSIM SIM card supply. During operation, the current drawn by the SARA-G3 series modules through the VCC pins can vary by several orders of magnitude. This ranges from the high peak of current consumption during GSM transmitting bursts at maximum power level in connected-mode (as described in the chapter 1.5.1.2), to the low current consumption during low power idle-mode with power saving enabled (as described in the chapter 1.5.1.3). 1.5.1.1 VCC supply requirements Table 6 summarizes the requirements for the VCC module supply. Refer to chapter 2.1.1 for all the suggestions to properly design a VCC supply circuit compliant to the requirements listed in Table 6. The VCC supply circuit affects the RF compliance of the device integrating SARA-G3 series module with applicable required certification schemes as well as antenna circuit design. Compliance is guaranteed if the VCC requirements summarized in the Table 6 are fulfilled. Item Requirement Remark VCC nominal voltage Within VCC normal operating range: 3.35 V min. / 4.50 V max. The module cannot be switched on if VCC voltage value is below the normal operating range minimum limit. Ensure that the input voltage at VCC pins is above the minimum limit of the normal operating range for at least more than 3 s after the module switch-on. VCC voltage during normal operation Within VCC extended operating range: 3.00 V min. / 4.50 V max. The module may switch off when VCC voltage drops below the extended operating range minimum limit. Operation above extended operating range maximum limit is not recommended and exposure beyond it may affect device reliability. VCC average current Considerably withstand maximum average current consumption value in connected-mode conditions specified in SARA-G3 series Data Sheet [1]. The maximum average current consumption can be greater than the specified value according to the actual antenna mismatching, temperature and VCC voltage. Chapter 1.5.1.2 describes connected-mode current. VCC peak current Withstand the maximum peak current consumption specified in the SARA-G3 series Data Sheet [1]. The specified maximum peak of current consumption occurs during GSM single transmit slot in 850/900 MHz connected-mode, in case of mismatched antenna. Chapter 1.5.1.2 describes connected-mode current. VCC voltage drop during Tx slots Lower than 400 mV VCC voltage drop values greater than recommended during 2G TDMA transmission slots directly affect the RF compliance with applicable certification schemes. Figure 5 describes VCC voltage drop during Tx slots. VCC voltage ripple during Tx slots Lower than 30 mVpp if fripple ≤ 200 kHz Lower than 10 mVpp if 200 kHz < fripple ≤ 400 kHz Lower than 2 mVpp if fripple > 400 kHz VCC voltage ripple values higher than recommended during 2G/3G transmission directly affect the RF compliance with applicable certification schemes. Figure 5 describes VCC voltage ripple during Tx slots.](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-18.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 19 of 145 Item Requirement Remark VCC under/over-shoot at start/end of Tx slots Absent or at least minimized VCC under/over-shoot higher than recommended at the start/end of 2G TDMA transmission slots directly affect the RF compliance with applicable certification schemes Figure 5 describes VCC voltage under/over-shoot at the start/end of Tx slots Table 6: Summary of VCC supply requirements 1.5.1.2 VCC current consumption in connected-mode When a GSM call is established, the VCC consumption is determined by the current consumption profile typical of the GSM transmitting and receiving bursts. The current consumption peak during a transmission slot is strictly dependent on the transmitted power, which is regulated by the network. If the module is transmitting in GSM talk mode in the 850 or 900 MHz bands, at the maximum RF power control level (approximately 2 W or 33 dBm in the allocated transmit slot/burst) the current consumption can reach up to 1900 mA (with a highly unmatched antenna) for 576.9 µs (width of the transmit slot/burst) with a periodicity of 4.615 ms (width of 1 frame = 8 slots/burst), so with a 1/8 duty cycle according to GSM TDMA (Time Division Multiple Access). If the module is in GSM connected-mode in the 1800 or 1900 MHz bands, the current consumption figures are lower than the one in the 850 or 900 MHz bands, due to 3GPP transmitter output power specifications (refer to SARA-G3 series Data Sheet [1]). During a GSM call, current consumption is in the order of 60-130 mA in receiving or in monitor bursts and is about 10-40 mA in the inactive unused bursts (low current period). The more relevant contribution to determine the average current consumption is set by the transmitted power in the transmit slot. Figure 4 shows an example of the module current consumption profile versus time in GSM talk mode. Time [ms]RX slotunused slotunused slotTX slotunused slotunused slotMON slotunused slotRX slotunused slotunused slotTX slotunused slotunused slotMON slotunused slotGSM frame 4.615 ms (1 frame = 8 slots)Current [A]200 mA60-120 mA1900 mAPeak current depends on TX powerGSM frame 4.615 ms (1 frame = 8 slots)1.51.00.50.02.060-120 mA10-40 mA Figure 4: VCC current consumption profile versus time during a GSM call (1 TX slot, 1 RX slot)](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-19.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 20 of 145 Figure 5 illustrates VCC voltage profile versus time during a GSM call, according to the relative VCC current consumption profile described in the Figure 4. TimeundershootovershootrippledropVoltage3.8 V (typ)RX slotunused slotunused slotTX slotunused slotunused slotMON slotunused slotRX slotunused slotunused slotTX slotunused slotunused slotMON slotunused slotGSM frame 4.615 ms (1 frame = 8 slots)GSM frame 4.615 ms (1 frame = 8 slots) Figure 5: Description of the VCC voltage profile versus time during a GSM call When a GPRS connection is established, more than one slot can be used to transmit and/or more than one slot can be used to receive. The transmitted power depends on network conditions, which set the peak current consumption, but following the GPRS specifications the maximum transmitted RF power is reduced if more than one slot is used to transmit, so the maximum peak of current is not as high as can be in case of a GSM call. If the module transmits in GPRS multi-slot class 10, in the 850 or 900 MHz bands, at the maximum power control level, the consumption can reach up to 1600 mA (with highly unmatched antenna). This happens for 1.154 ms (width of the 2 Tx slots/bursts) with a periodicity of 4.615 ms (width of 1 frame = 8 slots/bursts), so with a 1/4 duty cycle, according to GSM TDMA. If the module is in GPRS connected-mode in 1800 or 1900 MHz bands, consumption figures are lower than in the 850 or 900 MHz band, due to 3GPP Tx power specifications. Figure 6 reports the current consumption profiles in GPRS connected-mode, in the 850 or 900 MHz bands, with 2 slots used to transmit and 1 slot used to receive. Time [ms]RX slotunused slotunused slotTX slotTX slotunused slotMON slotunused slotRX slotunused slotunused slotTX slotTX slotunused slotMON slotunused slotGSM frame 4.615 ms (1 frame = 8 slots)Current [A]60-120mAGSM frame 4.615 ms (1 frame = 8 slots)1.51.00.50.02.060-120mA 10-40mA200mAPeak current depends on TX power1600 mA Figure 6: VCC current consumption profile versus time during a GPRS connection (2 TX slots, 1 RX slot)](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-20.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 21 of 145 1.5.1.3 VCC current consumption in cyclic idle/active-mode (power saving enabled) The power saving configuration is by default disabled, but it can be enabled using the appropriate AT command (refer to u-blox AT Commands Manual [2], AT+UPSV command). When power saving is enabled, the module automatically enters idle-mode whenever possible, reducing current consumption. During idle-mode, the module processor runs with 32 kHz reference clock frequency. For SARA-G350 modules, the internal oscillator automatically generates the 32 kHz clock. For SARA-G300 and SARA-G310 modules, a valid 32 kHz signal must be provided to the EXT32K input pin of the module to let idle-mode, that otherwise cannot be reached (this is not needed for the other SARA-G3 series modules). When power saving is enabled, the module is registered or attached to a network and a voice or data call is not enabled, the module automatically enters idle-mode whenever possible, but it must periodically monitor the paging channel of the current base station (paging block reception), in accordance to GSM system requirements. When the module monitors the paging channel, it wakes up to active-mode, to enable the reception of paging block. In between, the module switches to idle-mode. This is known as GSM discontinuous reception (DRX). The module processor core is activated during the paging block reception, and automatically switches its reference clock frequency from 32 kHz to the 26 MHz used in active-mode. The time period between two paging block receptions is defined by the network. This is the paging period parameter, fixed by the base station through broadcast channel sent to all users on the same serving cell. The time interval between two paging block receptions can be from 470.76 ms (DRX = 2, i.e. width of 2 GSM multiframes = 2 x 51 GSM frames = 2 x 51 x 4.615 ms) up to 2118.42 ms (DRX = 9, i.e. width of 9 GSM multiframes = 9 x 51 frames = 9 x 51 x 4.615 ms). Figure 7 shows an example of a module current consumption profile: the module is registered with the network, automatically enters idle-mode and periodically wakes up to active-mode to monitor the paging channel for paging block reception. ~30 msIDLE MODE ACTIVE MODE IDLE MODE400-700 µAActive Mode EnabledIdle Mode Enabled400-700 µA60-120 mA0.44-2.09 sIDLE MODE~30 msACTIVE MODETime [s]Current [mA]100500Time [ms]Current [mA]1005003-6 mA 7-18 mA60-120 mAPLL EnabledRX Enabled20-40 mADSP Enabled Figure 7: Description of VCC current consumption profile versus time when the module is registered the network: the module is in idle-mode and periodically wakes up to active-mode to monitor the paging channel for paging block reception](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-21.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 22 of 145 1.5.1.4 VCC current consumption in fixed active-mode (power saving disabled) Power saving configuration is by default disabled, or it can be disabled using the appropriate AT command (refer to u-blox AT Commands Manual [2], AT+UPSV command). When power saving is disabled, the module does not automatically enter idle-mode whenever possible: the module remains in active-mode. The module processor core is activated during active-mode, and the 26 MHz reference clock frequency is used. Figure 8 shows an example of the module current consumption profile when power saving is disabled: the module is registered with the network, active-mode is maintained, and the receiver and the DSP are periodically activated to monitor the paging channel for paging block reception. ACTIVE MODE7-18 mA60-120 mA0.47-2.12 sPaging periodTime [s]Current [mA]100500Time [ms]Current [mA]1005007-18 mA60-120 mARX Enabled20-40 mADSP Enabled7-18 mA Figure 8: Description of the VCC current consumption profile versus time when power saving is disabled: the active-mode is always held, and the receiver and the DSP are periodically activated to monitor the paging channel for paging block reception](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-22.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 23 of 145 1.5.2 RTC supply input/output (V_BCKP) The V_BCKP pin of SARA-G3 modules connects the supply for the Real Time Clock (RTC) and Power-On internal logic. This supply domain is internally generated by a linear LDO regulator integrated in the Power Management Unit, as described in Figure 9. The output of this linear regulator is always enabled when the main voltage supply provided to the module through the VCC pins is within the valid operating range, with the module switched off or switched on. Baseband Processor51VCC52VCC53VCC2V_BCKPLinear LDO RTCPower ManagementSARA-G35032 kHzBaseband Processor51VCC52VCC53VCC2V_BCKPLinear LDO RTCPower ManagementSARA-G300 / SARA-G31032 kHz31EXT32K Figure 9: SARA-G3 series RTC supply input/output (V_BCKP) and 32 kHz RTC timing reference clock simplified block diagram The RTC provides the module time reference (date and time), also in power-off mode, when the V_BCKP voltage is within its valid range (specified in the “Input characteristics of Supply/Power pins” table in SARA-G3 series Data Sheet [1]). The RTC timing is normally used to set the wake-up interval during idle-mode periods between network paging, but is able to provide programmable alarm functions by means of the 32.768 kHz clock provided by the internal oscillator on SARA-G350 modules or provided by a valid 32 kHz external signal present at the EXT32K input pin of SARA-G300 and SARA-G310 modules. The RTC can be supplied from an external back-up battery through the V_BCKP, when the main voltage supply is not provided to the module through VCC. This lets the time reference (date and time) run until the V_BCKP voltage is within its valid range, even when the main supply is not provided to the module. The RTC oscillator does not necessarily stop operation (i.e. the RTC counting does not necessarily stop) when V_BCKP voltage value drops below the specified operating range minimum limit (1.00 V): the RTC value read after a system restart could be not reliable as explained in the following Table 7. V_BCKP voltage value RTC value reliability Notes 1.00 V < V_BCKP < 2.40 V RTC oscillator does not stop operation RTC value read after a restart of the system is reliable V_BCKP within operating range 0.05 V < V_BCKP < 1.00 V RTC oscillator does not necessarily stop operation RTC value read after a restart of the system is not reliable V_BCKP below operating range 0.00 V < V_BCKP < 0.05 V RTC oscillator stops operation RTC value read after a restart of the system is reliable V_BCKP below operating range Table 7: RTC value reliability as function of V_BCKP voltage value Consider that the module cannot switch on if a valid voltage is not present on VCC even when the RTC is supplied through V_BCKP (meaning that VCC is mandatory to switch on the module). The RTC has very low power consumption, but is highly temperature dependent. For example at 25 °C, with the V_BCKP voltage equal to the typical output value, the power consumption is approximately 2 µA (refer to the](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-23.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 24 of 145 “Input characteristics of Supply/Power pins” table in the SARA-G3 series Data Sheet [1] for the detailed specification), whereas at 70 °C and an equal voltage the power consumption increases to 5-10 µA. If V_BCKP is left unconnected and the module main voltage supply is removed from VCC, the RTC is supplied from the bypass capacitor mounted inside the module. However, this capacitor is not able to provide a long buffering time: within few milliseconds the voltage on V_BCKP will go below the valid range (1 V min). This has no impact on wireless connectivity, as all the module functionalities do not rely on date and time setting. 1.5.3 Interfaces supply output (V_INT) The same 1.8 V voltage domain used internally to supply the digital interfaces of SARA-G3 modules is also available on the V_INT supply output pin, as described in Figure 10. Baseband Processor51VCC52VCC53VCC4V_INTSwitchingStep-DownDigital I/O InterfacesPower ManagementSARA-G3 series Figure 10: SARA-G3 series interfaces supply output (V_INT) simplified block diagram The internal regulator that generates the V_INT supply is a switching step-down converter that is directly supplied from VCC. The voltage regulator output is set to 1.8 V (typical) when the module is switched on and it is disabled when the module is switched off. The switching regulator operates in Pulse Width Modulation (PWM) for greater efficiency at high output loads when the module is in active-mode or in connected-mode. When the module is in low power idle-mode between paging periods and with power saving configuration enabled by the appropriate AT command, it automatically switches to Pulse Frequency Modulation (PFM) for greater efficiency at low output loads. Refer to the u-blox AT Commands Manual [2], +UPSV command.](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-24.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 25 of 145 1.6 System function interfaces 1.6.1 Module power-on The power-on sequence of SARA-G3 series modules is initiated in one of these ways: Rising edge on the VCC pin to a valid voltage as module supply (i.e. applying module supply) Low level on the PWR_ON pin (normally high with external pull-up) for an appropriate time period RTC alarm (i.e. pre-programmed scheduled time by AT+CALA command) 1.6.1.1 Rising edge on VCC When a SARA-G3 module is in the not-powered mode, it can be switched on by applying the VCC supply. The module is switched on when the voltage rises up to the VCC normal operating range minimum limit (3.35 V) starting from a voltage value lower than 2.25 V, and with a proper voltage slope: the voltage at the VCC pins must ramp from 2.5 V to 3.2 V within 4 ms to switch on the module. When the VCC voltage is stabilized at its nominal value within the normal operating range, the module can be switched on by a low level on PWR_ON pin (see section 1.6.1.2) or by RTC alarm (see section 1.6.1.3). If the PWR_ON input pin is held low during the VCC apply phase, the SARA-G3 module switches on when voltage rises up to the VCC normal operating range minimum limit (3.35 V). 1.6.1.2 Low level on PWR_ON When a SARA-G3 module is in the power-off mode (i.e. switched off with valid VCC supply maintained), the module can be switched on by forcing a low level on the PWR_ON input pin at least for 5 ms. The electrical characteristics of the PWR_ON input pin are different from the other digital I/O interfaces. The input voltage thresholds are slightly different since the PWR_ON input pin is tolerant of voltages up to the module supply level. The detailed electrical characteristics are described in SARA-G3 series Data Sheet [1]. There is no internal pull-up resistor on the PWR_ON pin: the pin has high input impedance and is weakly pulled to the high level by the internal circuit. Therefore the external circuit must be able to hold the high logic level stable, e.g. providing an external pull-up resistor (for further design-in guidelines refer to chapter 2.2.1). 1.6.1.3 RTC alarm When a SARA-G3 module is in the power-off mode (i.e. switched off with valid VCC supply maintained) and the RTC timing (32 kHz reference clock) is available, the module can be switched on by an RTC alarm previously programmed by AT command at a scheduled time (refer to the u-blox AT Commands Manual [2], AT+CALA command). The internal RTC block system will then initiate the module boot sequence by instructing the Power Management Unit to turn on power. Also included in this setup is an interrupt signal from the RTC block to indicate to the baseband processor that an RTC event has occurred. The RTC timing is generated by the 32 kHz reference clock provided by the internal oscillator on SARA-G350 modules. A valid 32 kHz external signal must be provided at the EXT32K input pin of the SARA-G300 and SARA-G310 modules to enable RTC timing, otherwise the switch-on of SARA-G300 and SARA-G310 modules by means of a pre-programmed RTC alarm is not possible (refer to the chapter 1.6.4). 1.6.1.4 Additional considerations The module is switched on when the VCC voltage rises to the normal operating range (i.e. applying module supply): the first time that the module is used, it is switched on in this way. SARA-G3 modules can be switched off by means of the AT+CPWROFF command, entering power-off mode. In this state, the digital input-output pads of the baseband chipset (i.e. all the digital pins of the module) are locked in tri-state (i.e. floating). The power down tri-state function isolates the module pins from the environment, when no proper operation of the outputs can be guaranteed.](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-25.png)

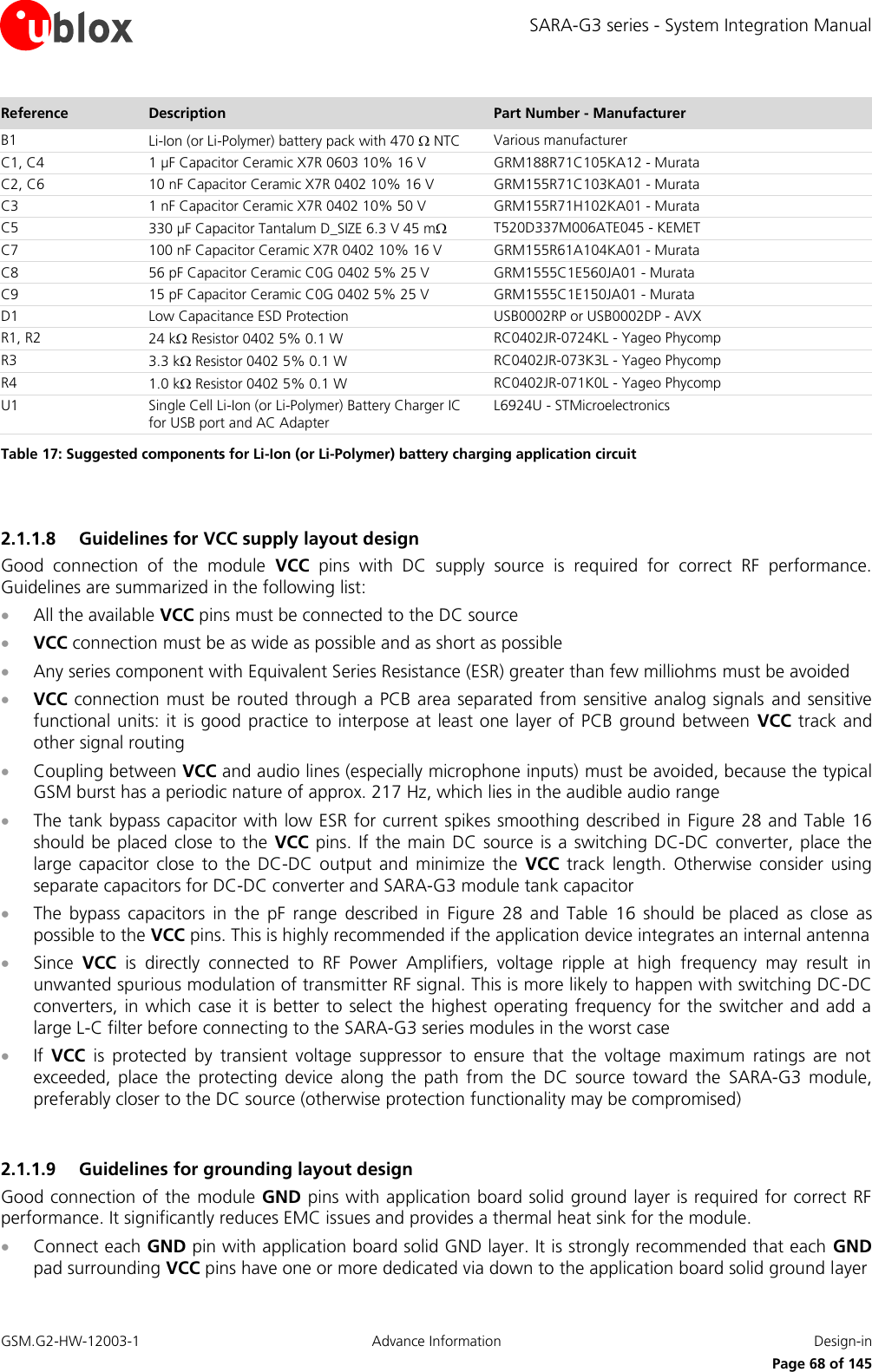

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 26 of 145 The module can be switched on from power-off mode by forcing a proper start-up event (e.g. PWR_ON low). After the detection of a start-up event, all the module digital pins are held in tri-state until all the internal LDO voltage regulators are turned on in a defined power-on sequence. Then, as described in Figure 11, the baseband core is still held in reset state for a time interval: the internal reset signal (which is not available on a module pin) is still low and all the digital pins of the module are held in reset state. The reset state of all the digital pins is reported in the pin description table of SARA-G3 Series Data Sheet [1]. When the internal signal is released, the configuration of the module interfaces starts: during this phase any digital pin is set in a proper sequence from the reset state to the default operational configuration. Finally, the module is fully ready to operate when all interfaces are configured. VCCV_BCKPPWR_ONV_INTInternal ResetSystem StateBB Pads StateInternal Reset → Operational OperationalTristate / Floating Internal ResetOFFONStart-up eventPWR_ON can be set highStart of interface configurationAll interfaces are configured0 ms5 ms~35 ms~3 s8 ms Figure 11: SARA-G3 series power-on sequence description The Internal Reset signal is not available on a module pin, but the application can monitor the V_INT pin to sense the start of the SARA-G3 series power-on sequence. 1.6.2 Module power-off The correct way to switch off SARA-G3 modules is by means of +CPWROFF AT command (more details in u-blox AT Commands Manual [2]): in this way the current parameter settings are saved in the module’s non-volatile memory and a proper network detach is performed. An under-voltage shutdown occurs on SARA-G3 modules when the VCC supply is removed, but in this case the current parameter settings are not saved in the module’s non-volatile memory and a proper network detach cannot be performed. An over-temperature or an under-temperature shutdown occurs when the temperature measured within the wireless module reaches the dangerous area, if the optional Smart Temperature Supervisor feature is activated and configured by the dedicated AT+USTS command. Refer to chapter 1.13.8 and to the u-blox AT Commands Manual [2] for more details. Figure 12 describes the power-off sequence by means of +CPWROFF AT command. When the +CPWROFF AT command is sent, the module starts the switch-off routine replying OK on the AT interface. At the end of the switch-off routine, all digital pins are locked in tri-state by the module and all the internal LDO voltage regulators except the RTC supply (V_BCKP) are turned off in a defined power-off sequence. The module remains in power-off mode as long as a switch on event does not occur (i.e. applying a low level on the PWR_ON pin, or by a pre-programmed RTC alarm), and enters not-powered mode if the supply is removed from the VCC pin. Current parameter settings are stored to the module’s non-volatile memory and a network detach is performed before the OK reply from AT+CPWROFF command.](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-26.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 27 of 145 The duration of the switch-off routine phases can largely differ from the values reported in Figure 12, depending on the network settings and the concurrent activities of the module performing a network detach. VCCV_BCKPPWR_ONV_INTInternal ResetSystem StateBB Pads State OperationalOFFTristate / Floating ONOperational → Tristate / FloatingAT+CPWROFFsent to the module0 s~2.5 s~5 sOKreplied by the module Figure 12: SARA-G3 series power-off sequence description The Internal Reset signal is not available on a module pin, but the application can monitor the V_INT pin to sense the end of the SARA-G3 series power-off sequence. 1.6.3 Module reset A SARA-G3 module reset can be performed in one of two ways. RESET_N input pin: Forces a low level on the RESET_N input pin, causing an “external” or “hardware” reset. This must be for at least 50 ms on SARA-G350 modules or 3000 ms on SARA-G300 and SARA-G310 modules. This causes an asynchronous reset of the module baseband processor, excluding the integrated Power Management Unit and the RTC internal block: the V_INT interfaces supply is enabled and each digital pin is set in its reset state, the V_BCKP supply and the RTC block are enabled. Forcing an “external” or “hardware” reset, the current parameter settings are not saved in the module’s non-volatile memory and a proper network detach is not performed. AT+CFUN command (refer to the u-blox AT Commands Manual [2] for more details): This command causes an “internal” or “software” reset, which is an asynchronous reset of the module baseband processor. The electrical behavior is the same as that of the “external” or “hardware” reset, but in an “internal” or “software” reset the current parameter settings are saved in the module’s non-volatile memory and a proper network detach is performed. After either reset, when RESET_N is released from the low level, the module automatically starts its power-on sequence from the reset state. The reset state of all digital pins is reported in the pin description table in SARA-G3 series Data Sheet [1]. The electrical characteristics of RESET_N are different from the other digital I/O interfaces: the RESET_N input pin is tolerant of voltages up to the module supply level due to the series Schottky diode mounted inside the module on the RESET_N pin. As described in Figure 13, the module has an internal pull-up resistor which pulls the line to the high logic level when the RESET_N pin is not forced low from the external. Detailed electrical characteristics are described in SARA-G3 series Data Sheet [1].](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-27.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 28 of 145 Baseband Processor18RESET_N Reset InputSARA-G3 series10k1.8 V Figure 13: SARA-G3 series reset input (RESET_N) description 1.6.4 External 32 kHz signal input (EXT32K) The external 32 kHz signal input pin (EXT32K) is available on SARA-G300 and SARA-G310 modules to provide the 32 kHz reference clock for the Real Time Clock (RTC) timing, used by the module processor when in the low power idle-mode. Only if a valid 32 kHz external signal is provided at the EXT32K input pin, SARA-G300 and SARA-G310 modules can enter the low power idle-mode (with power saving configuration enabled by the AT+UPSV command) and can provide the RTC functions (as RTC timing by AT+CCLK command and RTC alarm by AT+CALA command). The detailed electrical characteristics are described in SARA-G3 series Data Sheet [1]. The 32 kHz reference clock for the RTC timing is automatically generated by the internal oscillator provided on the SARA-G350 modules: the same pin (31) is a reserved (RSVD) pin internally not connected, since an external 32 kHz signal is not needed to enter the low power idle-mode and to provide the RTC functions.](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-28.png)

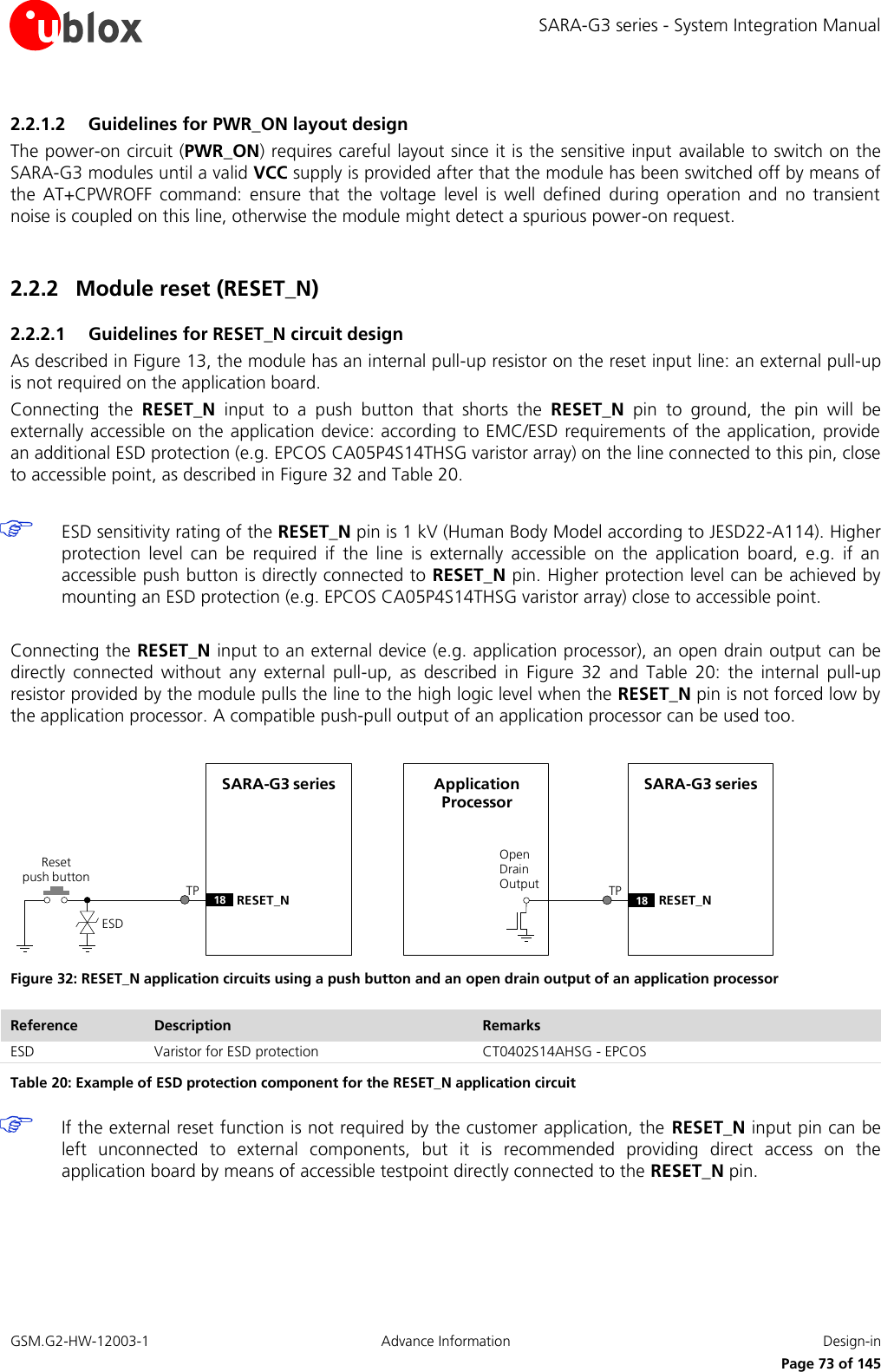

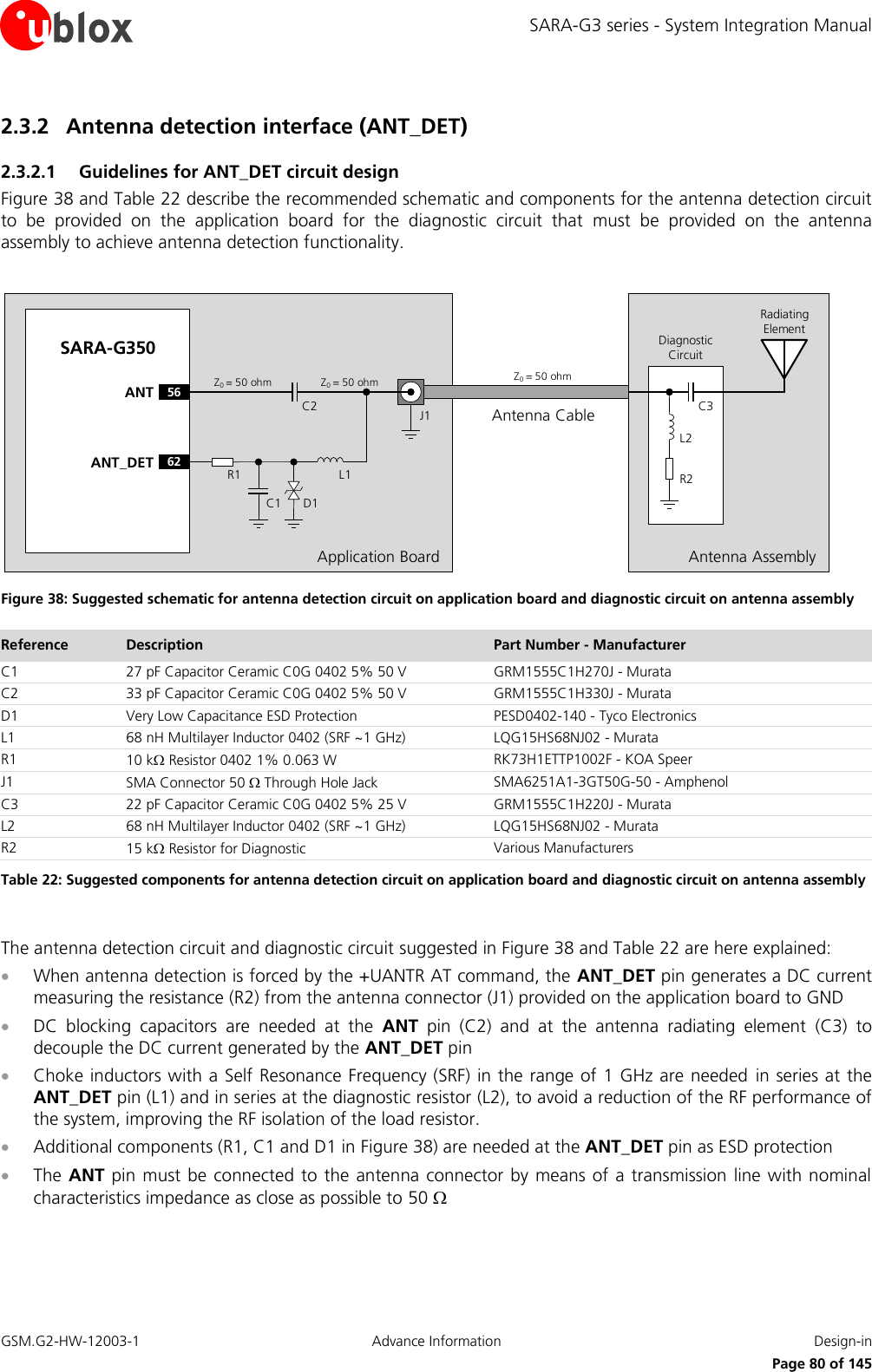

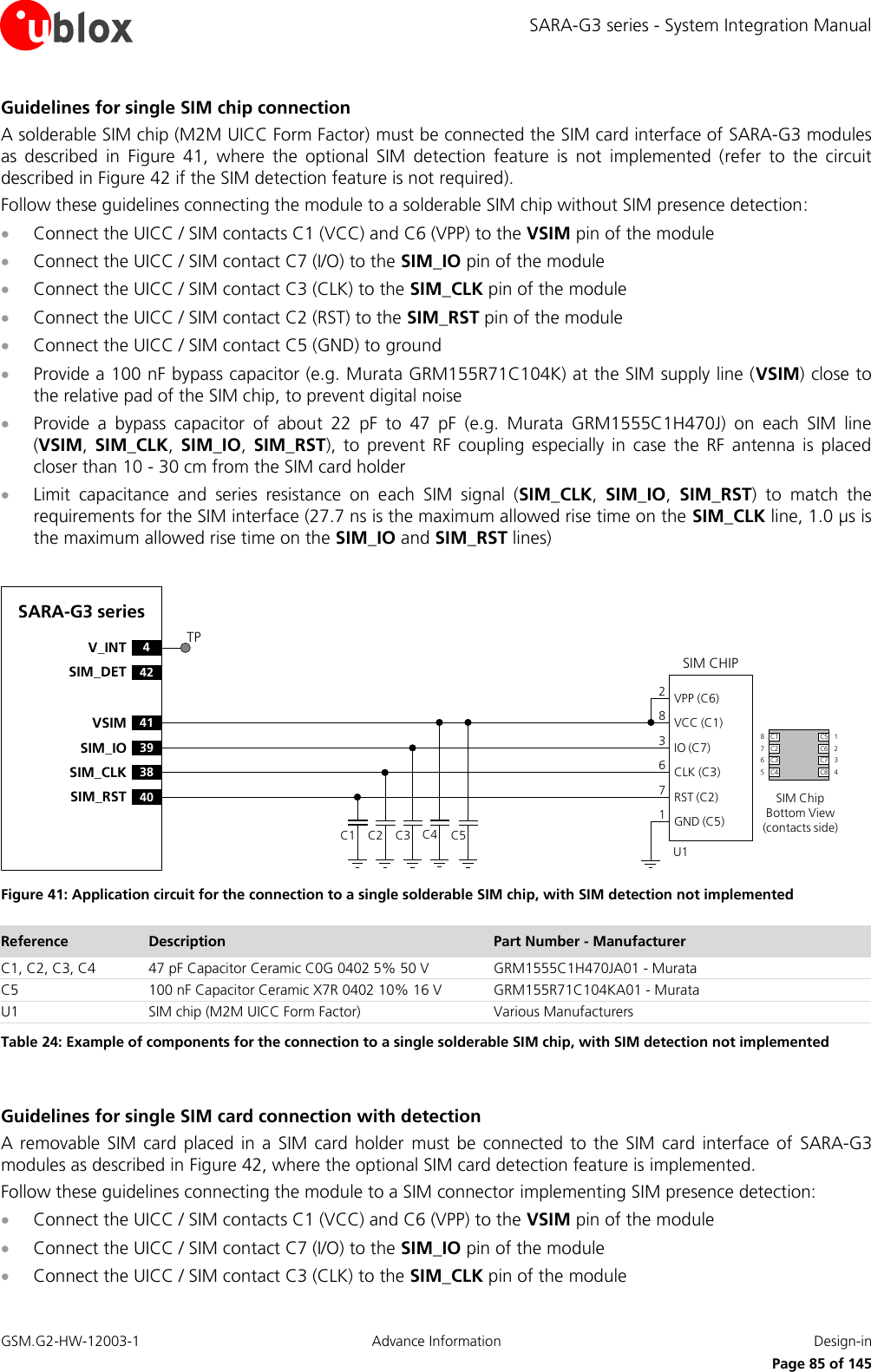

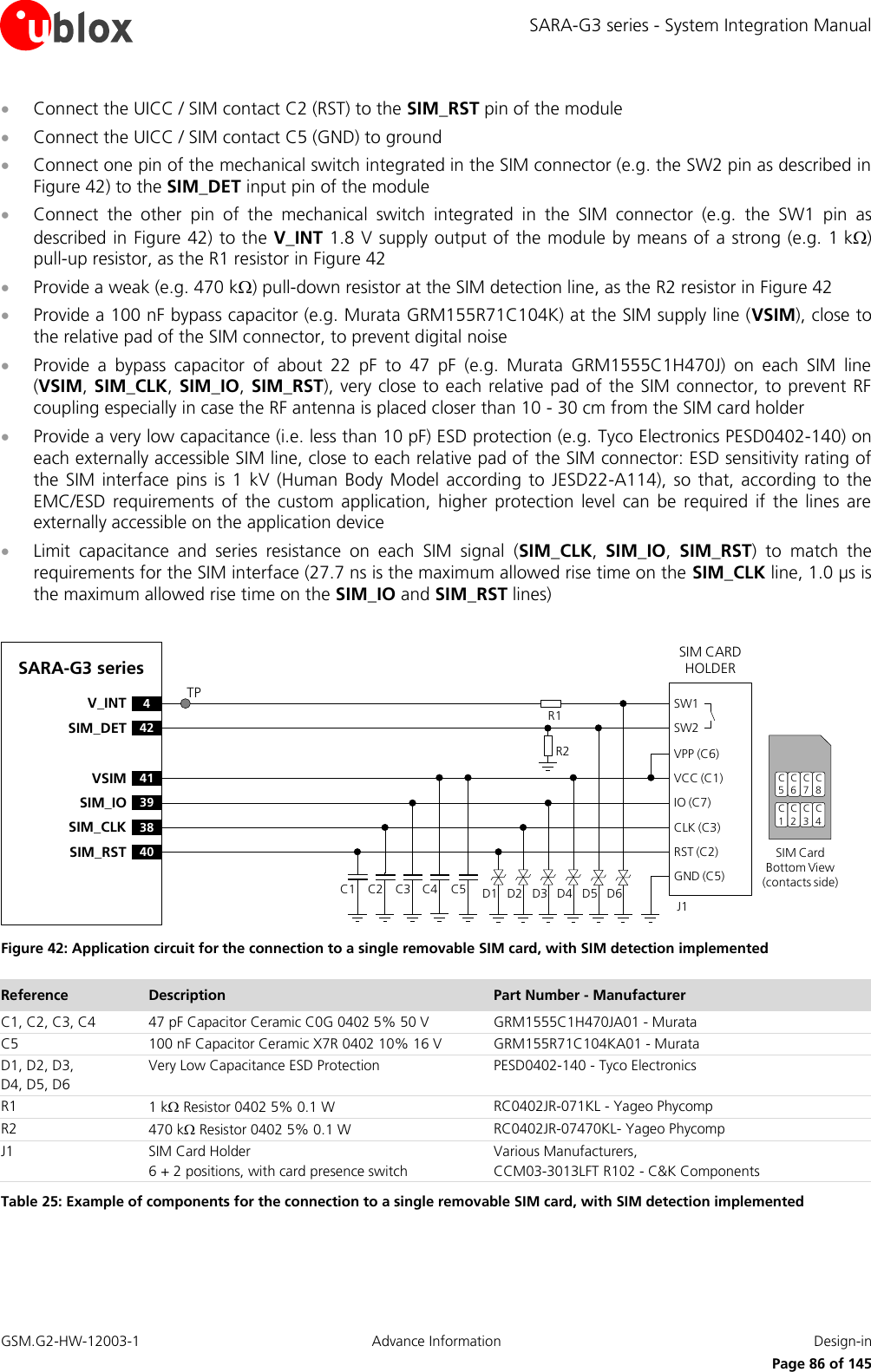

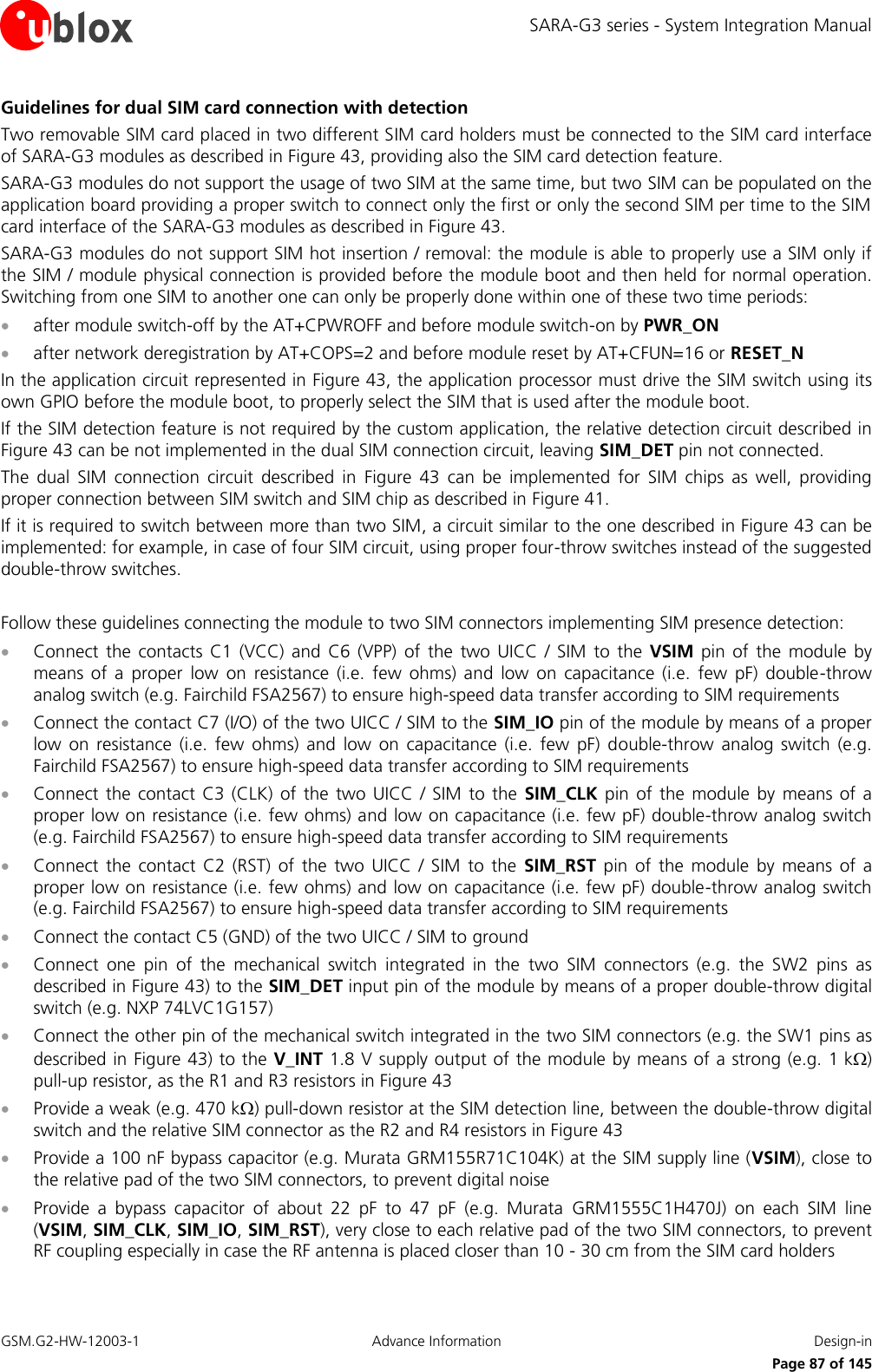

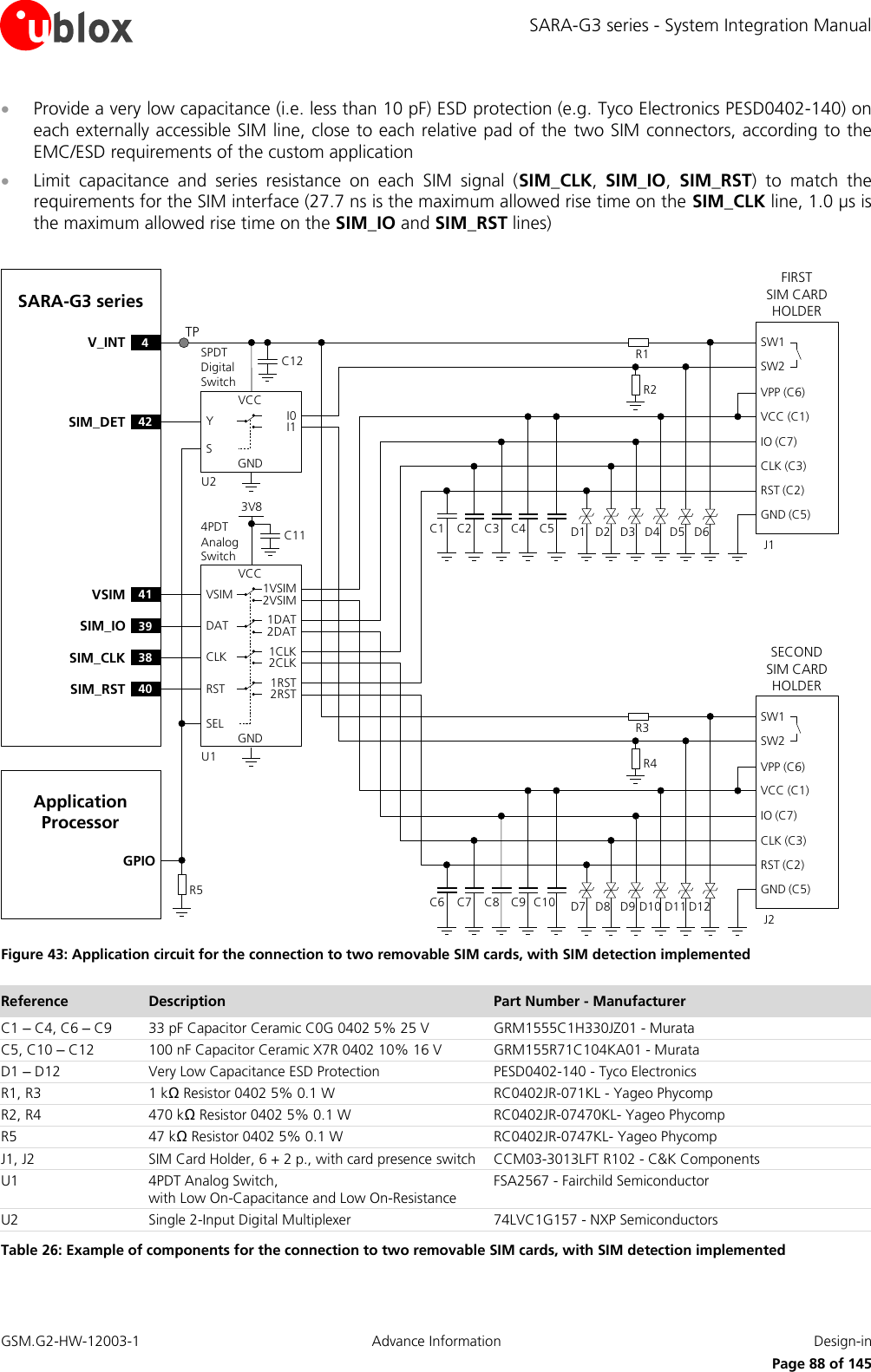

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 30 of 145 1.7.1 Antenna detection interface (ANT_DET) SARA-G300 and SARA-G310 modules do not support antenna detection interface (ANT_DET). The antenna detection is based on ADC measurement. The ANT_DET pin is an Analog to Digital Converter (ADC) provided to sense the antenna presence. The antenna detection function provided by ANT_DET pin is an optional feature that can be implemented if the application requires it. The antenna detection is forced by the +UANTR AT command. Refer to the u-blox AT Commands Manual [2] for more details on this feature. The ANT_DET pin generates a DC current (20 µA for 5.4 ms) and measures the resulting DC voltage, thus determining the resistance from the antenna connector provided on the application board to GND. So, the requirements to achieve antenna detection functionality are the following: an RF antenna assembly with a built-in resistor (diagnostic circuit) must be used an antenna detection circuit must be implemented on the application board Refer to the section 2.3.2 for antenna detection circuit on application board and diagnostic circuit on antenna assembly design-in guidelines. 1.8 SIM interface 1.8.1 SIM card interface SARA-G3 modules provide high-speed SIM/ME interface including automatic detection and configuration of the voltage required by the connected SIM card or chip. Both 1.8 V and 3 V SIM types are supported: activation and deactivation with automatic voltage switch from 1.8 V to 3 V is implemented, according to ISO-IEC 7816-3 specifications. The VSIM supply output pin provides internal short circuit protection to limit start-up current and protect the device in short circuit situations. The SIM driver supports the PPS (Protocol and Parameter Selection) procedure for baud-rate selection, according to the values determined by the SIM Card. SIM Application Toolkit (R99) is supported only by SARA-G350 modules. 1.8.2 SIM card detection interface (SIM_DET) The SIM_DET pin is configured as an external interrupt to detect the SIM card mechanical / physical presence. The pin is configured as input with an internal active pull-down enabled, and it can sense SIM card presence only if properly connected to the mechanical switch of a SIM card holder as described in the chapter 2.4: Low logic level at SIM_DET input pin is recognized as SIM card not present High logic level at SIM_DET input pin is recognized as SIM card present The SIM card detection function provided by SIM_DET pin is an optional feature that can be implemented / used or not according to the application requirements. For more details on SIM detection function refer to the u-blox AT Commands Manual [2], “simind” value of the <descr> parameter of the +CIND and +CMER commands.](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-30.png)

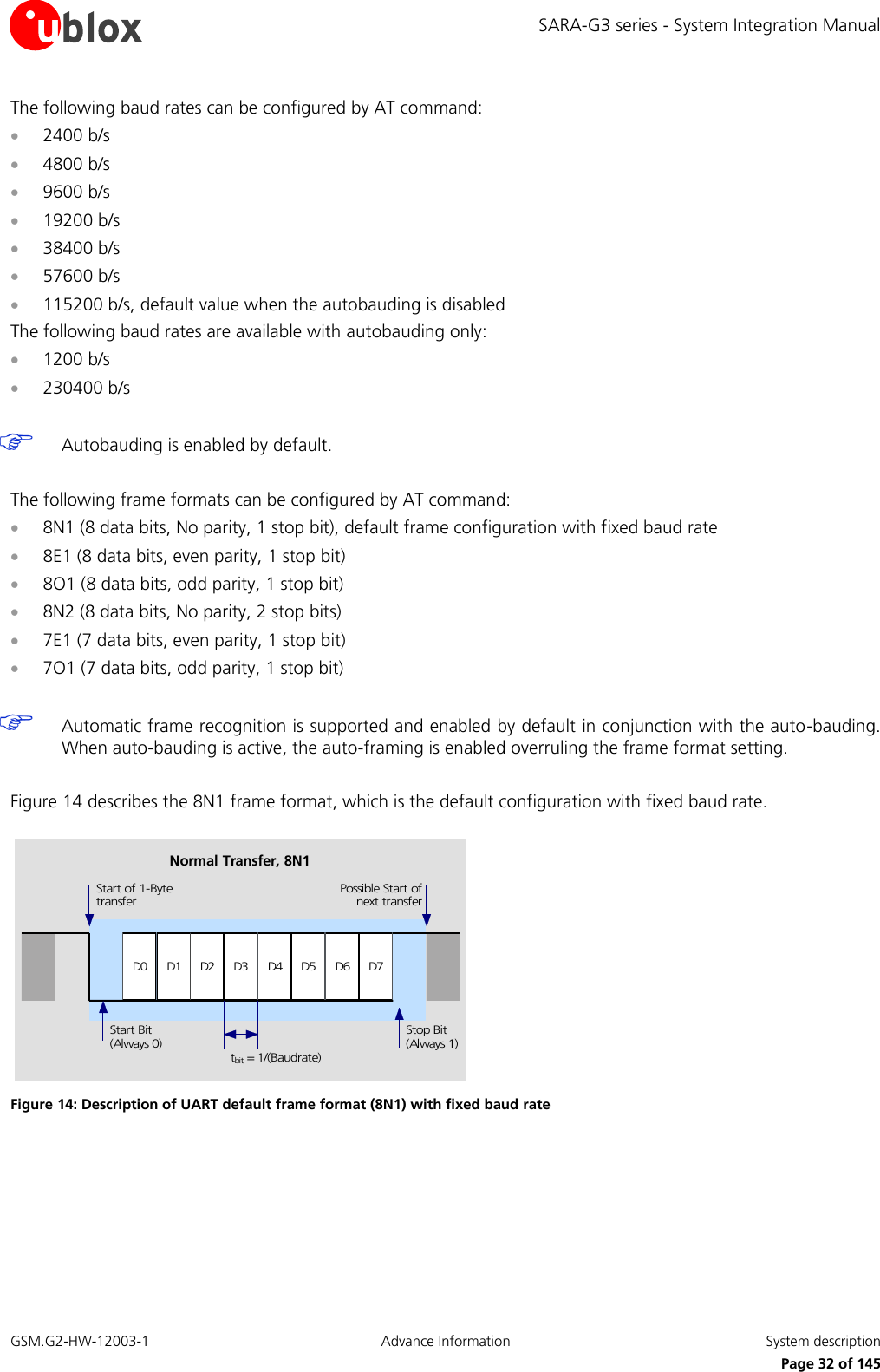

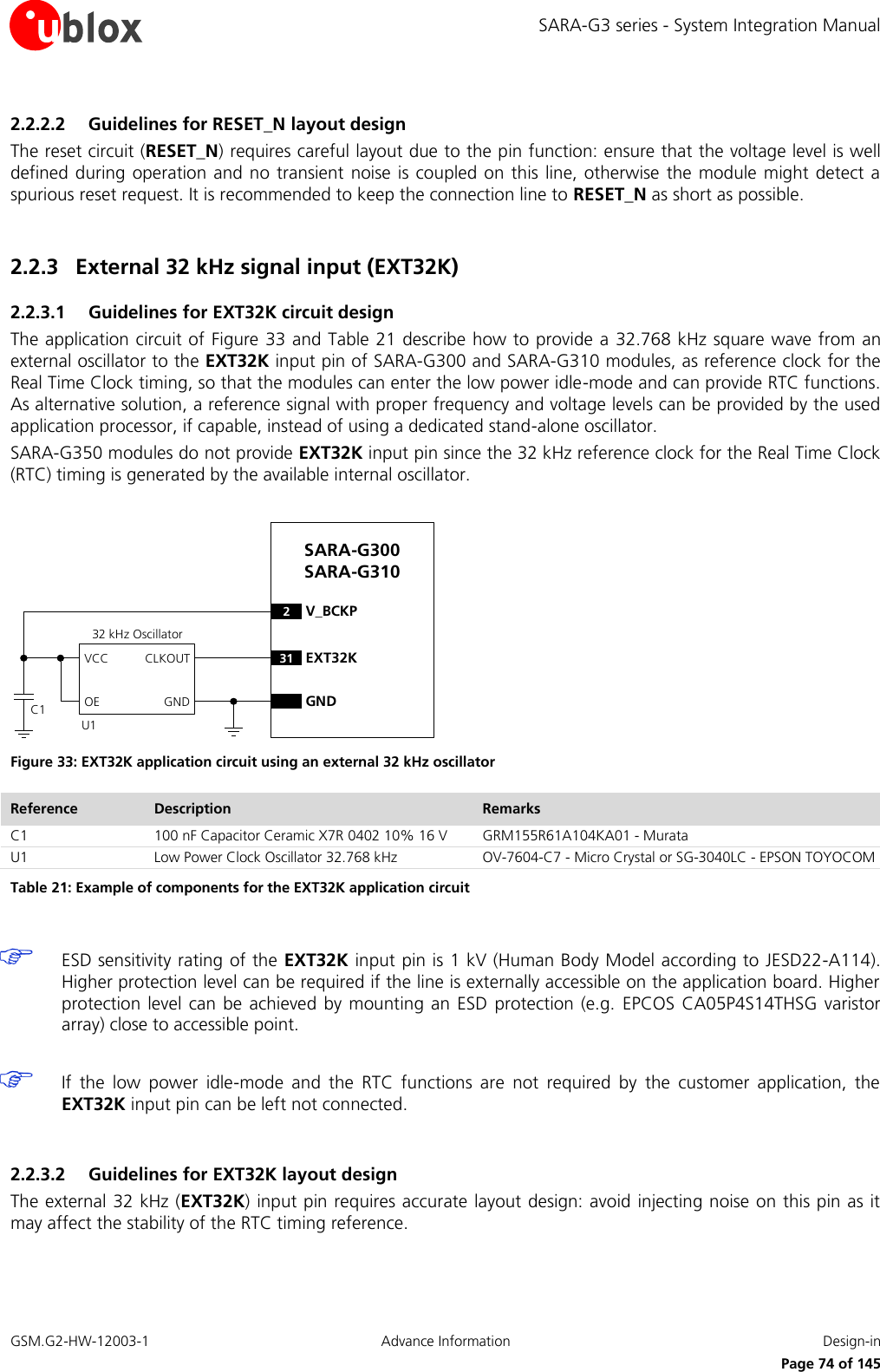

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 31 of 145 1.9 Serial interfaces SARA-G3 series modules provide the following serial communication interfaces: UART interface: 9-wire unbalanced 1.8 V asynchronous serial interface available for AT commands interface, Packet-Switched / Circuit-Switched Data communication, FW upgrades by means of the FOAT feature Auxiliary UART interface: 3-wire unbalanced 1.8 V asynchronous serial interface available only for the FW upgrade by means of the u-blox EasyFlash tool and for the Trace log capture (debug purpose) DDC interface: I2C compatible 1.8 V interface available only for the communication with u-blox positioning chips and modules 1.9.1 Asynchronous serial interface (UART) 1.9.1.1 UART features The UART interface is a 9-wire 1.8 V unbalanced asynchronous serial interface, and it is the only serial interface of the SARA-G3 modules available for an AT command interface and for Packet-Switched / Circuit-Switched Data communication. The module firmware can be upgraded over the UART interface by means of the Firmware upgrade over AT (FOAT) feature only: for more details refer to section 1.13 and Firmware update application note [22]. UART interface provides RS-232 functionality conforming to the ITU-T V.24 Recommendation (more details available in ITU Recommendation [9]), with CMOS compatible signal levels: 0 V for low data bit or ON state, and 1.8 V for high data bit or OFF state. For detailed electrical characteristics refer to SARA-G3 series Data Sheet [1]. SARA-G3 modules are designed to operate as a GSM/GPRS wireless modem, which represents the data circuit-terminating equipment (DCE) as described by the ITU-T V.24 Recommendation [9]. A customer application processor connected to the module through the UART interface represents the data terminal equipment (DTE). The signal names of the UART interface of the SARA-G3 modules conform to the ITU-T V.24 Recommendation [9]: e.g. TXD line represents the data transmitted by the DTE (application processor data output) and received by the DCE (module input). The UART interface is controlled and operated with: AT commands according to 3GPP TS 27.007 [10] AT commands according to 3GPP TS 27.005 [11] AT commands according to 3GPP TS 27.010 [12] u-blox AT commands For the complete list of supported AT commands and their syntax refer to the u-blox AT Commands Manual [2]. All flow control handshakes are supported by the UART interface and can be set by appropriate AT commands (see u-blox AT Commands Manual [2], &K, +IFC, \Q AT commands): hardware flow control (RTS/CTS), software flow control (XON/XOFF), or none flow control. Hardware flow control is enabled by default.](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-31.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 33 of 145 1.9.1.2 UART AT interface configuration The UART interface is the only AT command interface on SARA-G3 series modules. UART is configured as described in Table 9 (for information about further settings, refer to the u-blox AT Commands Manual [2]). Interface AT Settings Comments UART interface AT interface: enabled AT command interface is enabled by default on the UART physical interface AT+IPR=0 Automatic baud rate detection enabled by default AT+ICF=0 Automatic frame format recognition enabled by default AT&K3 HW flow control enabled AT&S1 DSR line set ON in data mode5 and set OFF in command mode5 AT&D1 Upon an ON-to-OFF transition of DTR, the DCE enters online command mode5 and issues an OK result code AT&C1 Circuit 109 changes in accordance with the Carrier detect status; ON if the Carrier is detected, OFF otherwise MUX protocol: disabled Multiplexing mode is disabled by default and it can be enabled by AT+CMUX command. The following virtual channels are defined for SARA-G350 modules: Channel 0: control channel Channel 1 – 5: AT commands / data connection Channel 6: GPS tunneling The following virtual channels are defined for SARA-G300 and SARA-G310 modules: Channel 0: control channel Channel 1 – 2: AT commands / data connection Table 9: Default UART AT interface configuration 1.9.1.3 UART signal behavior (AT commands interface case) At the module switch-on, before the UART interface initialization (as described in the power-on sequence reported in Figure 11), each pin is first tri-stated and then is set to its relative internal reset state.6 At the end of the boot sequence, the UART interface is initialized, the module is by default in active-mode, and the UART interface is enabled. The configuration and the behavior of the UART signals after the boot sequence are described below. See section 1.4 for definition and description of module operating modes referred to in this section. RXD signal behavior The module data output line (RXD) is set by default to OFF state (high level) at UART initialization. The module holds RXD in OFF state until the module does not transmit some data. TXD signal behavior The module data input line (TXD) is set by default to OFF state (high level) at UART initialization. The TXD line is then held by the module in the OFF state if the line is not activated by the DTE: an active pull-up is enabled inside the module on the TXD input. 5 Refer to the u-blox AT Commands Manual [2] for the definition of the interface data mode, command mode and online command mode. 6 See the pin description table in the SARA-G3 series Data Sheet [1].](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-33.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 34 of 145 CTS signal behavior The module hardware flow control output (CTS line) is set to the ON state (low level) at UART initialization. If the hardware flow control is enabled (for more details, refer to u-blox AT Commands Manual [2], AT&K, AT\Q, AT+IFC AT command) the CTS line indicates when the UART interface is enabled (data can be sent and received): the module drives the CTS line to the ON state or to the OFF state when it is either able or not able to accept data from the DTE (refer to chapter 1.9.1.4 for the complete description). If the hardware flow control is not enabled, the CTS line is always held in the ON state after UART initialization. If hardware flow control is enabled, then when the CTS line is ON the UART is enabled and the module is in active-mode. If the CTS line is OFF it does not necessarily mean that the module is in idle-mode, but only that the UART is not enabled (the module could be forced to stay in active-mode for other activities, e.g. network related). When the power saving configuration is enabled and the hardware flow-control is not implemented in the DTE/DCE connection, data sent by the DTE can be lost: the first character sent when the module is in idle-mode will not be a valid communication character (see chapter 1.9.1.4 for complete description). When the multiplexer protocol is active, the CTS line state is mapped to FCon / FCoff MUX command for flow control issues outside the power saving configuration while the physical CTS line is still used as a power state indicator. For more details, refer to Mux Implementation Application Note [20]. RTS signal behavior The hardware flow control input (RTS line) is set by default to the OFF state (high level) at UART initialization. The module then holds the RTS line in the OFF state if the line is not activated by the DTE: an active pull-up is enabled inside the module on the RTS input. If the HW flow control is enabled (for more details, refer to u-blox AT Commands Manual [2] AT&K, AT\Q, AT+IFC command descriptions) the module monitors the RTS line to detect permission from the DTE to send data to the DTE itself. If the RTS line is set to OFF state, any on-going data transmission from the module is immediately interrupted or any subsequent transmission forbidden until the RTS line changes to ON state. The DTE must still be able to accept a certain number of characters after the RTS line is set to OFF state: the module guarantees the transmission interruption within two characters from RTS state change. If AT+UPSV=2 is set and HW flow control is disabled, the module monitors the RTS line to manage the power saving configuration: When an OFF-to-ON transition occurs on the RTS input line, the UART is enabled and the module is forced to active-mode; after ~20 ms from the transition the switch is completed and data can be received without loss. The module cannot enter idle-mode and the UART is keep enabled as long as the RTS input line is held in the ON state If the RTS input line is set to OFF state by the DTE, the UART is disabled (held in low power mode) and the module automatically enters idle-mode whenever possible For more details, refer to chapter 1.9.1.4 and u-blox AT Commands Manual [2], AT+UPSV command. DSR signal behavior If AT&S0 is set, the DSR module output line is set by default to ON state (low level) at UART initialization and is then always held in the ON state. If AT&S1 is set, the DSR module output line is set by default to OFF state (high level) at UART initialization. The DSR line is then set to the OFF state when the module is in command mode or in online command mode and is set to the ON state when the module is in data mode (refer to the u-blox AT Commands Manual [2] for the definition of the interface data mode, command mode and online command mode).](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-34.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 35 of 145 DTR signal behavior The DTR module input line is set by default to OFF state (high level) at UART initialization. The module then holds the DTR line in the OFF state if the line is not activated by the DTE: an active pull-up is enabled inside the module on the DTR input. Module behavior according to DTR status depends on the AT command configuration (see u-blox AT Commands Manual [2], &D AT command). DCD signal behavior If AT&C0 is set, the DCD module output line is set by default to ON state (low level) at UART initialization and is then always held in the ON state. If AT&C1 is set, the DCD module output line is set by default to OFF state (high level) at UART initialization. The module then sets the DCD line in accordance with the carrier detect status: ON if the carrier is detected, OFF otherwise. For voice calls, DCD is set to the ON state when the call is established. For a data call there are the following scenarios (refer to the u-blox AT Commands Manual [2] for the definition of the interface data mode, command mode and online command mode): Packet Switched Data call: Before activating the PPP protocol (data mode) a dial-up application must provide the ATD*99***<context_number># to the module: with this command the module switches from command mode to data mode and can accept PPP packets. The module sets the DCD line to the ON state, then answers with a CONNECT to confirm the ATD*99 command. The DCD ON is not related to the context activation but with the data mode Circuit Switched Data call: To establish a data call, the DTE can send the ATD<number> command to the module which sets an outgoing data call to a remote modem (or another data module). Data can be transparent (non reliable) or non transparent (with the reliable RLP protocol). When the remote DCE accepts the data call, the module DCD line is set to ON and the CONNECT <communication baudrate> string is returned by the module. At this stage the DTE can send characters through the serial line to the data module which sends them through the network to the remote DCE attached to a remote DTE DCD is set to ON during the execution of the +CMGS, +CMGW, +USOWR, +USODL AT commands requiring input data from the DTE: the DCD line is set to ON state as soon as the switch to binary/text input mode is completed and the prompt is issued; DCD line is set to OFF as soon as the input mode is interrupted or completed (for more details refer to the u-blox AT Commands Manual [2]). DCD line is kept to ON state even during the online command mode to indicate that the data call is still established even if suspended, while if the module enters command mode DSR line is set to OFF state. For more details refer to DSR signal behavior description. For scenarios when the DCD line setting is requested for different reasons (e.g. SMS texting during online command mode), the DCD line changes to guarantee the correct behavior for all the scenarios. For instance, in case of SMS texting in online command mode, if the data call is released, the DCD line is kept to ON till the SMS command execution is completed (even if the data call release would request the DCD setting to OFF).](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-35.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 36 of 145 RI signal behavior The RI module output line is set by default to the OFF state (high level) at UART initialization. Then, during an incoming call, the RI line is switched from OFF state to ON state with a 4:1 duty cycle and a 5 s period (ON for 1 s, OFF for 4 s, see Figure 15), until the DTE attached to the module sends the ATA string and the module accepts the incoming data call. The RING string sent by the module (DCE) to the serial port at constant time intervals is not correlated with the switch of the RI line to the ON state. Figure 15: RI behavior during an incoming call The RI line can notify an SMS arrival. When the SMS arrives, the RI line switches from OFF to ON for 1 s (see Figure 16), if the feature is enabled by the proper AT command (refer to the u-blox AT Commands Manual [2], AT+CNMI command). Figure 16: RI behavior at SMS arrival This behavior allows the DTE to stay in power saving mode until the DCE related event requests service. For SMS arrival, if several events coincidently occur or in quick succession each event independently triggers the RI line, although the line will not be deactivated between each event. As a result, the RI line may stay to ON for more than 1 s. If an incoming call is answered within less than 1 s (with ATA or if auto-answering is set to ATS0=1) than the RI line is set to OFF earlier. As a result: RI line monitoring cannot be used by the DTE to determine the number of received SMSes. For multiple events (incoming call plus SMS received), the RI line cannot be used to discriminate the two events, but the DTE must rely on the subsequent URCs and interrogate the DCE with the proper commands. SMS arrives time [s] 0 RI ON RI OFF 1s SMS time [s] 0 RI ON RI OFF 1s 1stime [s]151050RI ONRI OFFCall incomes1stime [s]151050RI ONRI OFFCall incomes](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-36.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 37 of 145 1.9.1.4 UART and power-saving The power saving configuration is controlled by the AT+UPSV command (for the complete description, refer to u-blox AT Commands Manual [2]). When power saving is enabled, the module automatically enters low power idle-mode whenever possible, and otherwise the active-mode is maintained by the module (see section 1.4 for definition and description of module operating modes referred to in this section). The AT+UPSV command configures both the module power saving and also the UART behavior in relation to the power saving. The conditions for the module entering idle-mode also depend on the UART power saving configuration. Three different power saving configurations can be set by the AT+UPSV command: AT+UPSV=0, power saving disabled: module forced on active-mode and UART interface enabled (default) AT+UPSV=1, power saving enabled: module cyclic active / idle-mode and UART enabled / disabled AT+UPSV=2, power saving enabled and controlled by the UART RTS input line The different power saving configurations that can be set by the +UPSV AT command are described in details in the following subchapters. Table 10 summarizes the UART interface communication process in the different power saving configurations, in relation with HW flow control settings and RTS input line status. For more details on the +UPSV AT command description, refer to u-blox AT commands Manual [2]. AT+UPSV HW flow control RTS line Communication during idle-mode and wake up 0 Enabled (AT&K3) ON Data sent by the DTE is correctly received by the module. 0 Enabled (AT&K3) OFF Data sent by the module is buffered by the module and will be correctly received by the DTE when it is ready to receive data (i.e. RTS line is ON). 0 Disabled (AT&K0) ON Data sent by the DTE is correctly received by the module. 0 Disabled (AT&K0) OFF Data sent by the module is correctly received by the DTE if it is ready to receive data, otherwise data is lost. 1 Enabled (AT&K3) ON Data sent by the DTE is buffered by the DTE and will be correctly received by the module when active-mode is entered. 1 Enabled (AT&K3) OFF Data sent by the module is buffered by the module and will be correctly received by the DTE when it is ready to receive data (i.e. RTS line will be ON). 1 Disabled (AT&K0) ON The first character sent by the DTE is lost, but it wakes up the UART (if disabled) and the module (if in idle-mode) after ~20 ms. Recognition of subsequent characters is guaranteed only after the complete wake-up of the UART and the module (i.e. after ~20 ms). 1 Disabled (AT&K0) OFF Data sent by the module is correctly received by the DTE if it is ready to receive data, otherwise data is lost. 2 Enabled (AT&K3) ON Not Applicable: HW flow control cannot be enabled with AT+UPSV=2. 2 Enabled (AT&K3) OFF Not Applicable: HW flow control cannot be enabled with AT+UPSV=2. 2 Disabled (AT&K0) ON Data sent by the DTE is correctly received by the module. 2 Disabled (AT&K0) OFF The first character sent by the DTE is lost, but it wakes up the UART (if disabled) and the module (if in idle-mode) after ~20 ms. Recognition of subsequent characters is guaranteed only after the complete wake-up of the UART and the module (i.e. after ~20 ms). Table 10: UART and power-saving summary AT+UPSV=0: power saving disabled, fixed active-mode The module does not enter idle-mode and the UART interface is enabled (data can be sent and received): the CTS line is always held in the ON state after UART initialization. This is the default configuration.](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-37.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 38 of 145 AT+UPSV=1: power saving enabled, cyclic idle/active-mode The module automatically enters idle-mode whenever possible and, if the module is registered with network, it periodically wakes up from idle-mode to active-mode for at least ~11 ms to monitor the paging channel of the current base station (paging block reception), according to the GSM discontinuous reception (DRX) specification. The idle-mode period depends on the time period between two paging receptions defined by the current base station (i.e. by the network): the paging reception period can vary from ~0.47 s (DRX = 2, i.e. 2 x 51 GSM frames) up to ~2.12 s (DRX = 9, i.e. 9 x 51 GSM frames) When the module wakes up to active-mode for the paging block receptions, the UART interface is enabled for at least ~11 ms concurrently to each paging reception and then, as data has not been received or sent over the UART, the interface is disabled until the next paging reception. During a call, the UART interface is kept enabled, regardless of the AT+UPSV setting. If the module is not registered with a network, the cyclic idle/active-mode configuration is present as well: the module automatically enters idle-mode whenever possible and periodically wakes up to active-mode to enable the UART for at least ~11 ms and then, as data has not been received or sent over the UART, the interface is disabled for a defined period (according to the latest DRX setting) and afterwards the UART is enabled again. When UART interface is disabled, data transmitted by the DTE is lost if hardware flow control is disabled. If hardware flow control is enabled, data is buffered by the DTE and will be correctly received by the module when UART interface is enabled again. When UART interface is enabled, data can be received. When a character is received, it forces the UART interface to stay enabled for a longer time and it forces the module to stay in the active-mode for a longer time. The module active-mode duration depends on: The time period for the paging block reception, which is set by the current base station: ~11 ms minimum The time period where the UART interface is enabled, when the module is not registered with a network: ~11 ms minimum of in absence of data reception by serial interface The time period from the last data received at the serial port during the active-mode: the module does not enter idle-mode until a timeout expires. The second parameter of the +UPSV AT command configures this timeout, from 40 GSM TDMA frames (i.e. 40 x 4.615 ms = ~184 ms) up to 65000 GSM TDMA frames (i.e. 65000 x 4.615 ms = 300 s). Default value is 2000 GSM frames (i.e. 2000 x 4.615 ms = ~9.2 s) The active-mode duration can be extended indefinitely since every subsequent character received during the active-mode, resets and restarts the timer. If HW flow control is enabled, the hardware flow-control output (CTS line) indicates when the UART interface is enabled (data can be sent and received) as illustrated in Figure 17. time [s]CTS ONCTS OFFUART disabled~10 ms (min)UART enabled~9.2 s (default)UART enabledData input0.47- 2.10 s Figure 17: CTS behavior with power saving enabled (AT+UPSV=1) and HW flow control enabled: the CTS output line indicates when the UART interface of the module is enabled (CTS = ON = low level) or disabled (CTS = OFF = high level)](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-38.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 40 of 145 Figure 18 shows the case where the DCE UART is disabled and only a wake-up is forced. In this scenario the only character sent by the DTE is the wake-up character; as a consequence, the DCE UART is disabled when the timeout from last data received expires (2000 frames without data reception, as the default case). CTS OFFCTS ONDCE UART is enabled for 2000 GSM frames (~9.2 s)time Wake up time: ~20 mstime TxD module inputWake up character Not recognized by DCE Figure 18: Wake-up via data reception without further communication Figure 19 shows the case where in addition to the wake-up character further (valid) characters are sent. The wake up character wakes-up the DCE UART. The other characters must be sent after the “wake up time” of ~20 ms. If this condition is satisfied, the DCE recognizes characters. The DCE is allowed to disable the UART and re-enters idle-mode after 2000 GSM frames from the latest data reception. CTS OFFCTS ONDCE UART is enabled for 2000 GSM frames (~9.2s) after the last data receivedtime Wake up time: ~20 mstime TxD module inputWake up character Not recognized by DCEValid characters Recognized by DCE Figure 19: Wake-up via data reception with further communication The “wake-up via data reception” feature cannot be disabled. In command mode7, if autobauding is enabled and the DTE does not implement HW flow control, the DTE must always send a character to the module before the “AT” prefix set at the beginning of each command line: the first character is ignored if the module is in active-mode, or it represents the wake-up character if the module is in idle-mode. 7 Refer to the u-blox AT Commands Manual [2] for the definition of the interface data mode, command mode and online command mode.](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-40.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 41 of 145 In command mode7, if autobauding is disabled, the DTE must always send a dummy “AT” before each command line: the first character is not ignored if the module is in active-mode (i.e. the module replies “OK”), or it represents the wake up character if the module is in idle-mode (i.e. the module does not reply). No wake-up character or dummy “AT” is required from the DTE during a voice or data call since the module UART interface continues to be enabled and does not need to be woken-up. Furthermore in data mode7 a dummy “AT” would affect the data communication. 1.9.1.5 Multiplexer protocol (3GPP 27.010) SARA-G3 modules have a software layer with MUX functionality, 3GPP TS 27.010 Multiplexer Protocol [12], available on the UART physical link. The auxiliary UART and the DDC (I2C) serial interfaces do not support the multiplexer protocol. This is a data link protocol (layer 2 of OSI model) which uses HDLC-like framing and operates between the module (DCE) and the application processor (DTE) and allows a number of simultaneous sessions over the used physical link (UART or SPI): the user can concurrently use AT command interface on one MUX channel and Packet-Switched / Circuit-Switched Data communication on another multiplexer channel. Each session consists of a stream of bytes transferring various kinds of data such as SMS, CBS, PSD, GPS, AT commands in general. This permits, for example, SMS to be transferred to the DTE when a data connection is in progress. The following virtual channels are defined for SARA-G350 modules: Channel 0: control channel Channel 1 – 5: AT commands / data connection Channel 6: GPS tunneling The following virtual channels are defined for SARA-G300 and SARA-G310 modules: Channel 0: control channel Channel 1 – 2: AT commands / data connection For more details, refer to Mux implementation Application Note [20]. 1.9.2 Auxiliary asynchronous serial interface (UART AUX) The auxiliary UART interface is a 3-wire unbalanced 1.8 V asynchronous serial interface (only the RXD_AUX data output and TXD_AUX data input are provided), available for SARA-G3 modules FW upgrade by means of the u-blox EasyFlash tool and for Trace log capture (debug purpose). The AT commands interface is not available on the auxiliary UART interface. 1.9.3 DDC (I2C) interface SARA-G300 and SARA-G310 modules do not support DDC (I2C) interface. An I2C bus compatible Display Data Channel (DDC) interface for communication with u-blox GPS/GNSS receivers is available on SDA and SCL pins of SARA-G350 modules. Only this interface provides the communication between the u-blox wireless module and u-blox positioning chips and modules. The AT commands interface is not available on the DDC (I2C) interface. DDC (I2C) slave-mode operation is not supported: the SARA-G350 wireless module can act as master only, and the connected u-blox GPS/GNSS receiver automatically acts as slave in the DDC (I2C) communication.](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-41.png)

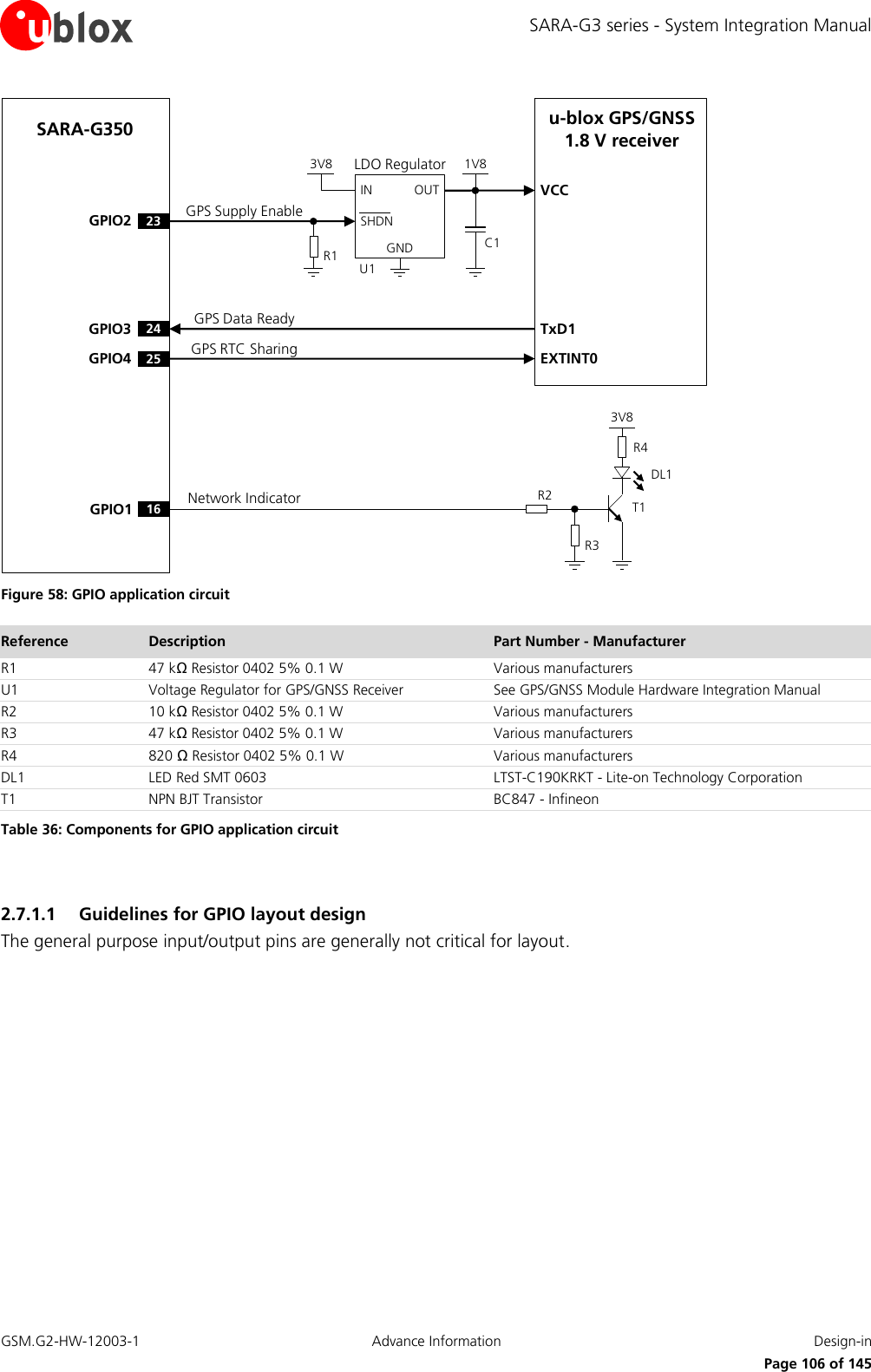

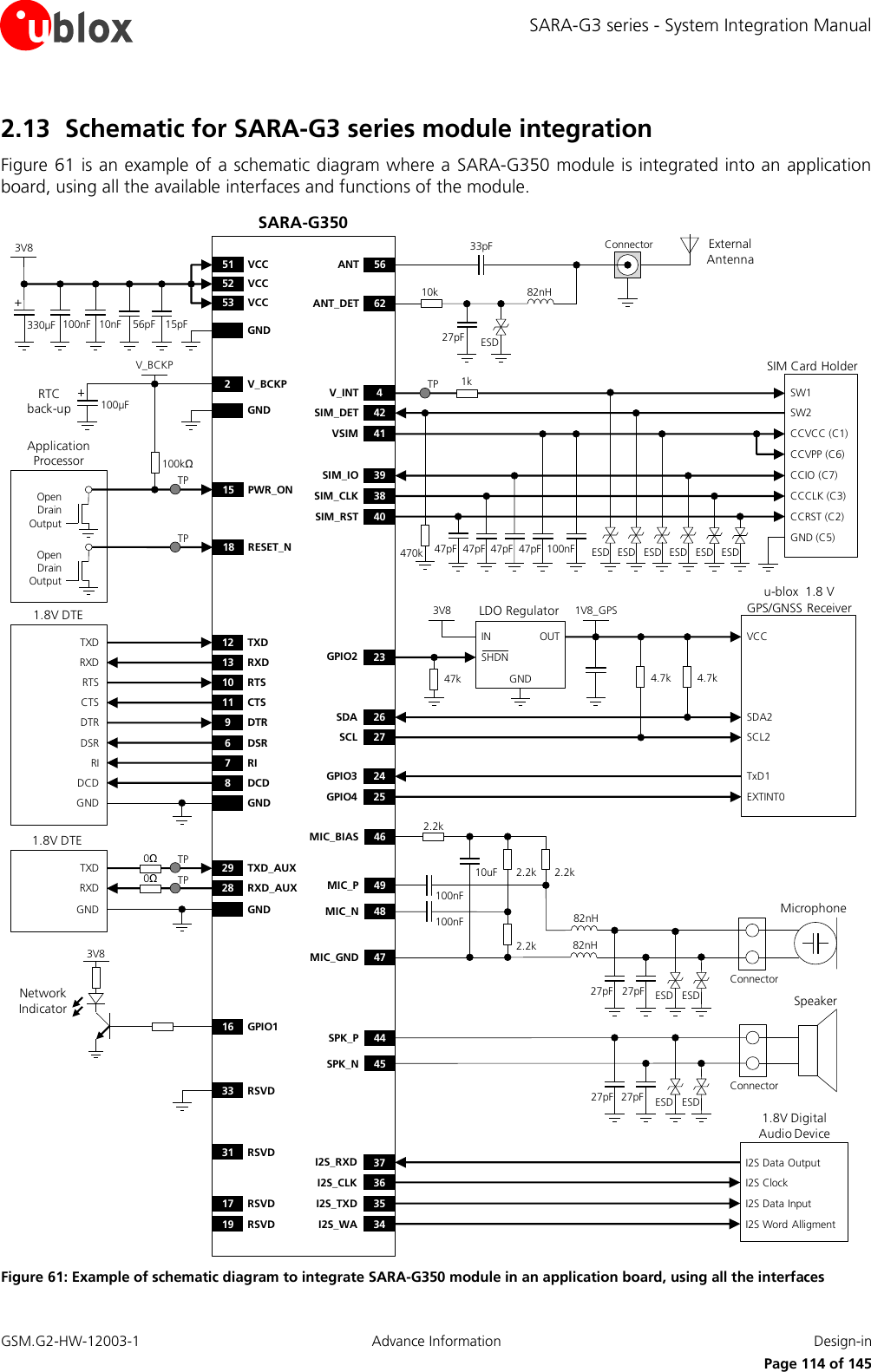

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 42 of 145 Two lines, serial data (SDA) and serial clock (SCL), carry information on the bus. SCL is used to synchronize data transfers, and SDA is the data line. To be compliant to the I2C bus specifications, the module bus interface pads are open drain output and pull up resistors must be used conforming to the I2C bus specifications [13]. u-blox has implemented special features in SARA-G350 wireless modules to ease the design effort required for the integration of a u-blox wireless module with a u blox GPS/GNSS receiver. Combining a u-blox wireless module with a u-blox GPS/GNSS receiver allows designers to have full access to the positioning receiver directly via the wireless module: it relays control messages to the GPS/GNSS receiver via a dedicated DDC (I2C) interface. A 2nd interface connected to the positioning receiver is not necessary: AT commands via the UART serial interface of the wireless module allows a fully control of the GPS/GNSS receiver from any host processor. SARA-G350 modules feature embedded GPS aiding that is a set of specific features developed by u-blox to enhance GPS/GNSS performance, decreasing Time To First Fix (TTFF), thus allowing to calculate the position in a shorter time with higher accuracy. SARA-G350 modules support these GPS aiding types: Local aiding AssistNow Online AssistNow Offline AssistNow Autonomous The embedded GPS aiding features can be used only if the DDC (I2C) interface of the wireless module is connected to the u-blox GPS/GNSS receivers. SARA-G350 wireless modules provide additional custom functions over GPIO pins to improve the integration with u-blox positioning chips and modules. GPIO pins can handle: GPS/GNSS receiver power-on/off: “GPS supply enable” function provided by GPIO2 improves the positioning receiver power consumption. When the GPS/GNSS functionality is not required, the positioning receiver can be completely switched off by the wireless module that is controlled by the application processor with AT commands The wake up from idle-mode when the GPS/GNSS receiver is ready to send data: “GPS data ready” function provided by GPIO3 improves the wireless module power consumption. When power saving is enabled in the wireless module by the AT+UPSV command and the GPS/GNSS receiver does not send data by the DDC (I2C) interface, the module automatically enters idle-mode whenever possible. With the “GPS data ready” function the GPS/GNSS receiver can indicate to the wireless module that it is ready to send data by the DDC (I2C) interface: the positioning receiver can wake up the wireless module if it is in idle-mode, so the wireless module does not lose the data sent by the GPS/GNSS receiver even if power saving is enabled The RTC synchronization signal to the GPS/GNSS receiver: “GPS RTC sharing” function provided by GPIO4 improves GPS/GNSS receiver performance, decreasing the Time To First Fix (TTFF), and thus allowing to calculate the position in a shorter time with higher accuracy. When GPS local aiding is enabled, the wireless module automatically uploads data such as position, time, ephemeris, almanac, health and ionospheric parameter from the positioning receiver into its local memory, and restores this to the GPS/GNSS receiver at the next power up of the positioning receiver For more details regarding the handling of the DDC (I2C) interface, the GPS aiding features and the GPS related functions over GPIOs, refer to the chapter 1.11, to the u-blox AT Commands Manual [2] (AT+UGPS, AT+UGPRF, AT+UGPIOC AT commands) and the GPS Implementation Application Note [21]. “GPS data ready” and “GPS RTC sharing” functions are not supported by all u-blox GPS/GNSS receivers HW or ROM/FW versions. Refer to the GPS Implementation Application Note [21] or to the Hardware Integration Manual of the u-blox GPS/GNSS receivers for the supported features.](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-42.png)

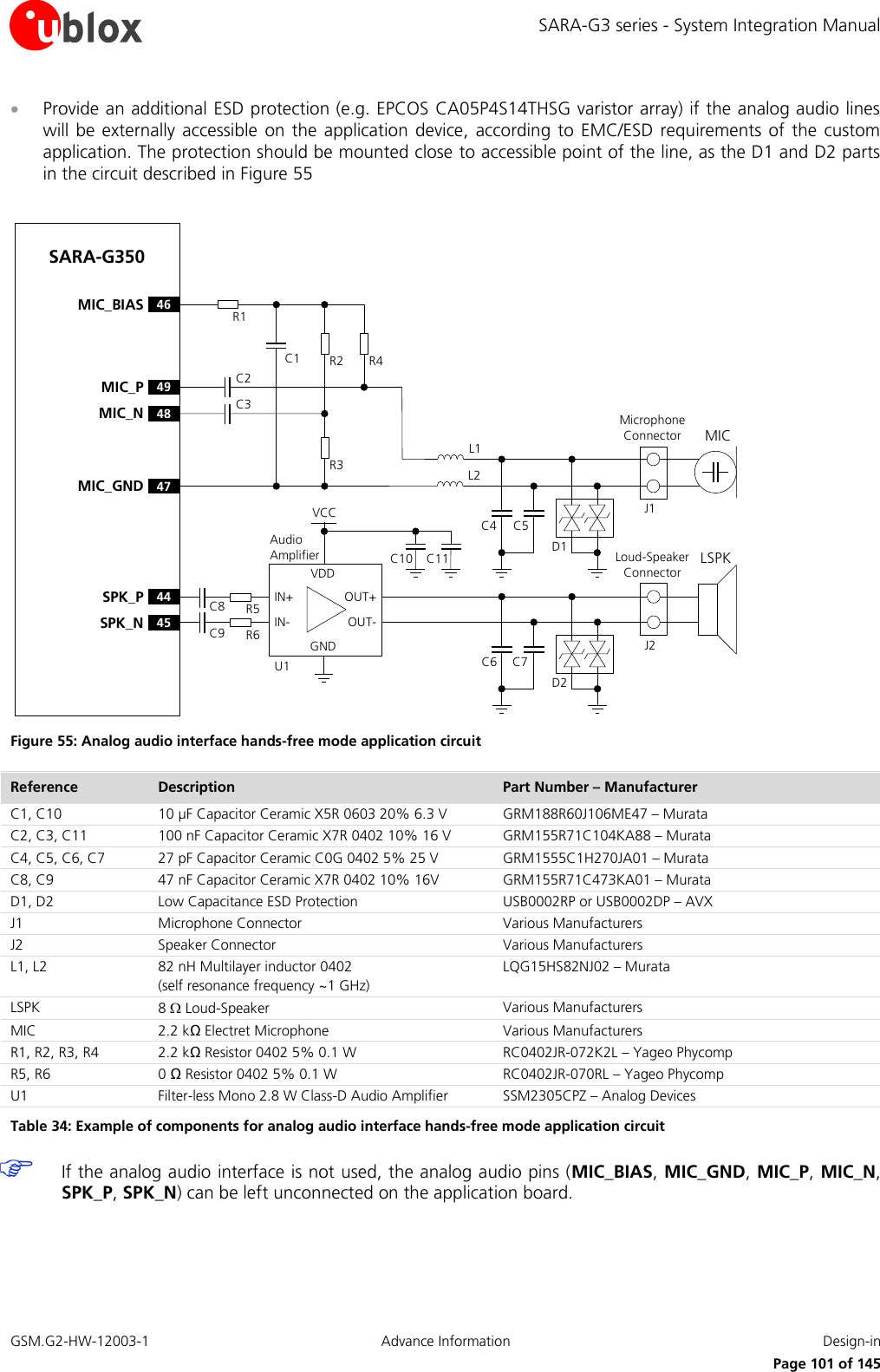

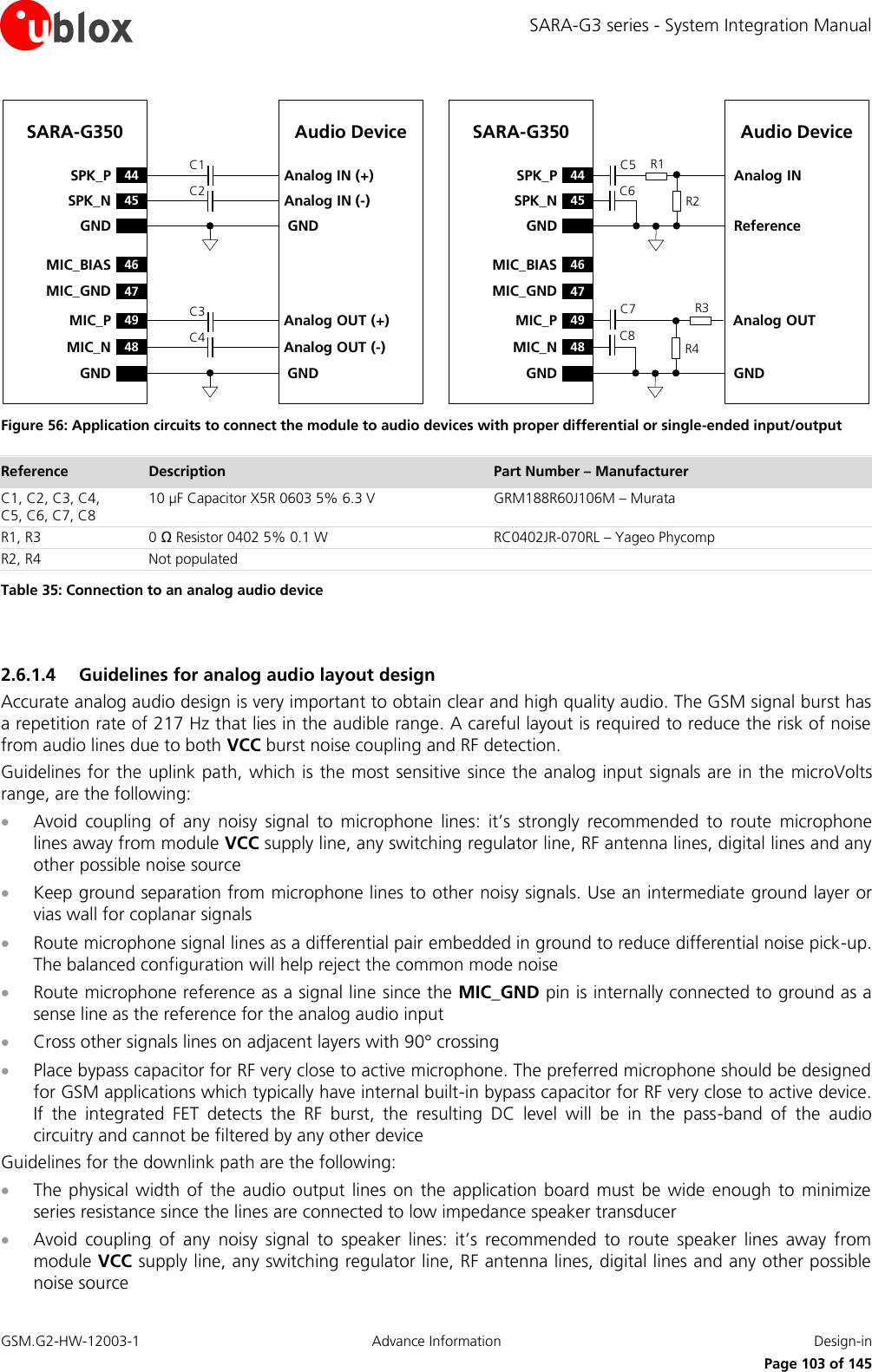

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 43 of 145 As additional improvement for the GPS/GNSS receiver performance, the V_BCKP supply output of SARA-G350 modules can be connected to the V_BCKP backup supply input pin of u-blox positioning chips and modules to provide the supply for the GPS/GNSS real time clock and backup RAM when the VCC supply of the wireless module is within its operating range and the VCC supply of the GPS/GNSS receiver is disabled. This enables the u-blox positioning receiver to recover from a power breakdown with either a hot start or a warm start (depending on the duration of the GPS/GNSS receiver VCC outage) and to maintain the configuration settings saved in the backup RAM. 1.10 Audio interface SARA-G300 and SARA-G310 modules do not support audio interface. SARA-G350 modules provide one analog audio interface and one digital audio interface that can be selected and set by the dedicated AT command +USPM (refer to u-blox AT Commands Manual [2]): this command allows setting the audio path mode, composed by the uplink audio path and the downlink audio path. Each uplink path mode defines the physical input (i.e. the analog or the digital audio input) and the set of parameters to process the uplink audio signal (uplink gains, uplink digital filters, echo canceller parameters). For example the “Headset microphone” uplink path uses the differential analog audio input with the default parameters for the headset profile. Each downlink path mode defines the physical output (i.e. the analog or the digital audio output) and the set of parameters to process the downlink audio signal (downlink gains, downlink digital filters and sidetone). For example the “Mono headset” downlink path uses the differential analog audio output with the default parameters for the headset profile. The set of parameters to process the uplink or the downlink audio signal can be changed with dedicated AT commands for each uplink or downlink path and then stored in two profiles in the non volatile memory (refer to u-blox AT Commands Manual [2] for Audio parameters tuning commands). 1.10.1 Analog audio interface 1.10.1.1 Uplink path SARA-G350 pins related to the analog audio uplink path are: MIC_P / MIC_N: Differential analog audio signal inputs (positive/negative). These two pins are internally directly connected to the differential input of an integrated Low Noise Amplifier, without any internal series capacitor for DC blocking. The LNA output is internally connected to the digital processing system by an integrated sigma-delta analog-to-digital converter MIC_BIAS: Supply output for an external microphone. The pin is internally connected to the output of a low noise LDO linear regulator provided with proper internal bypass capacitor to guarantee stable operation of the linear regulator MIC_GND: Local ground for the external microphone. The pin is internally connected to ground as a sense line as the reference for the analog audio input The analog audio input is selected when the parameter <main_uplink> in AT+USPM command is set to “Headset microphone”, “Handset microphone” or “Hands-free microphone”: the uplink analog path profiles use the same physical input but have different sets of audio parameters (for more details, refer to u-blox AT Commands Manual [2], AT+USPM, AT+UMGC, AT+UUBF, AT+UHFP commands). SARA-G3 series Data Sheet [1] provides the detailed electrical characteristics of the analog audio uplink path.](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-43.png)

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 44 of 145 1.10.1.2 Downlink path SARA-G350 pins related to the analog audio downlink path are: SPK_P / SPK_N: Differential analog audio signal output (positive/negative). These two pins are directly connected internally to the differential output of a low power audio amplifier, for which the input is connected internally to the digital processing system by to an integrated digital-to-analog converter. The analog audio output is selected when the parameter <main_downlink> in AT+USPM command is set to “Normal earpiece”, “Mono headset” or “Loudspeaker”: the downlink analog path profiles use the same physical output but have different sets of audio parameters (for more details, refer to the u-blox AT Commands Manual [2], AT+USPM, AT+USGC, AT+UDBF, AT+USTN commands). The differential analog audio output of SARA-G350 modules (SPK_P / SPK_N) is able to directly drive loads with resistance rating greater than 14 : it can be directly connected to a headset earpiece or handset earpiece but cannot directly drive a 8 or 4 loudspeaker for the hands-free mode. SARA-G3 series Data Sheet [1] provides the detailed electrical characteristics of the analog audio downlink path. Warning: excessive sound pressure from headphones can cause hearing loss. 1.10.1.3 Headset mode Headset mode is the default audio operating mode of the modules. The headset profile is configured when the uplink audio path is set to “Headset microphone” and the downlink audio path is set to “Mono headset” (refer to u-blox AT Commands Manual [2]: AT+USPM command: <main_uplink>, <main_downlink> parameters). 1.10.1.4 Handset mode The handset profile is configured when the uplink audio path is set to “Handset microphone” and the downlink audio path is set to “Normal earpiece” (refer to u-blox AT commands manual [2]: AT+USPM command: <main_uplink>, <main_downlink> parameters). 1.10.1.5 Hands-free mode The hands-free profile is configured when the uplink audio path is set to “Hands-free microphone” and the downlink audio path is set to “Loudspeaker” (refer to u-blox AT commands manual [2]: AT+USPM command: <main_uplink>, <main_downlink> parameters). Hands-free functionality is implemented using appropriate digital signal processing algorithms for voice-band handling (echo canceller and automatic gain control), managed via software (refer to u-blox AT commands manual [2], AT+UHFP command).](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-44.png)

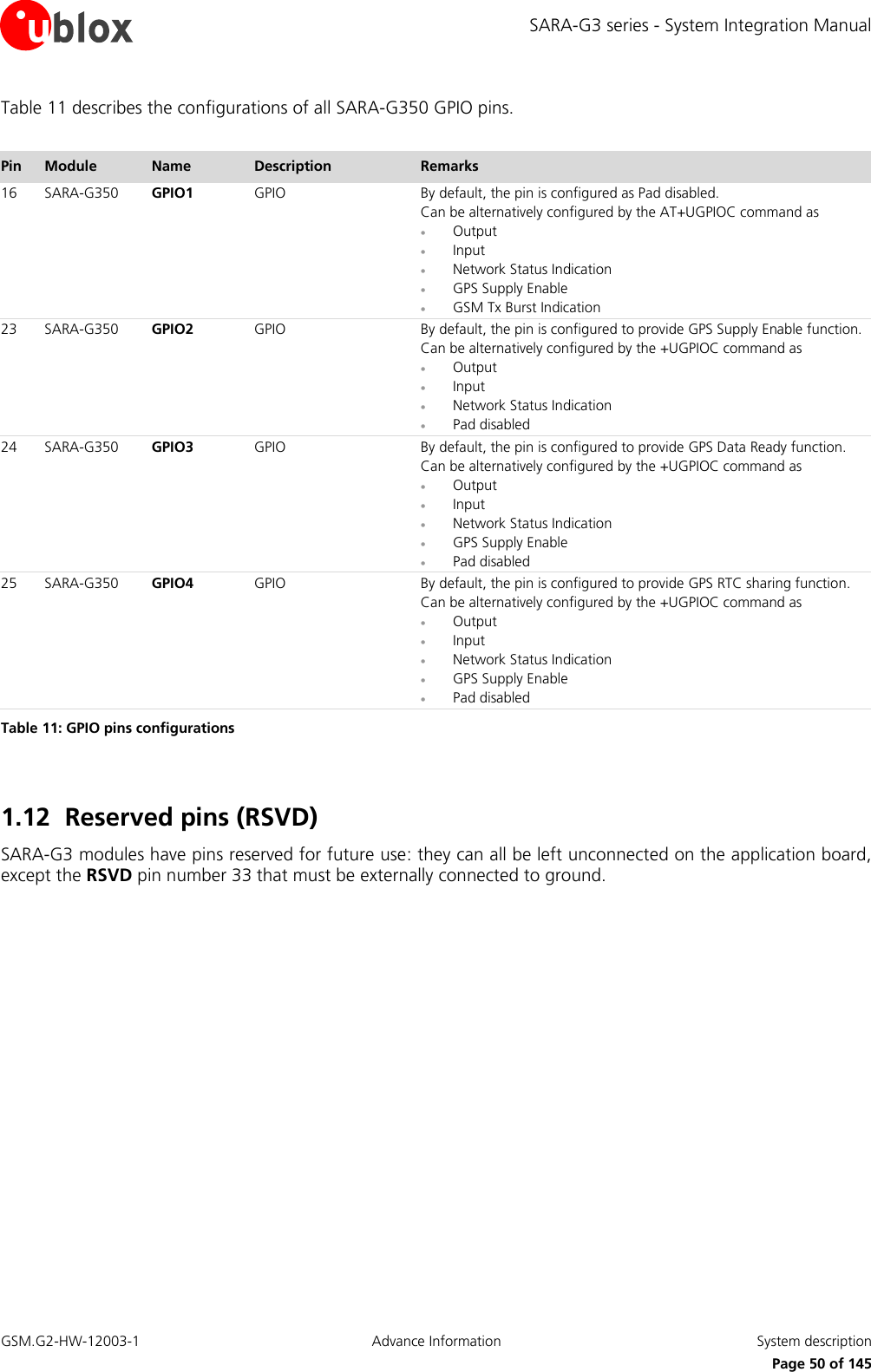

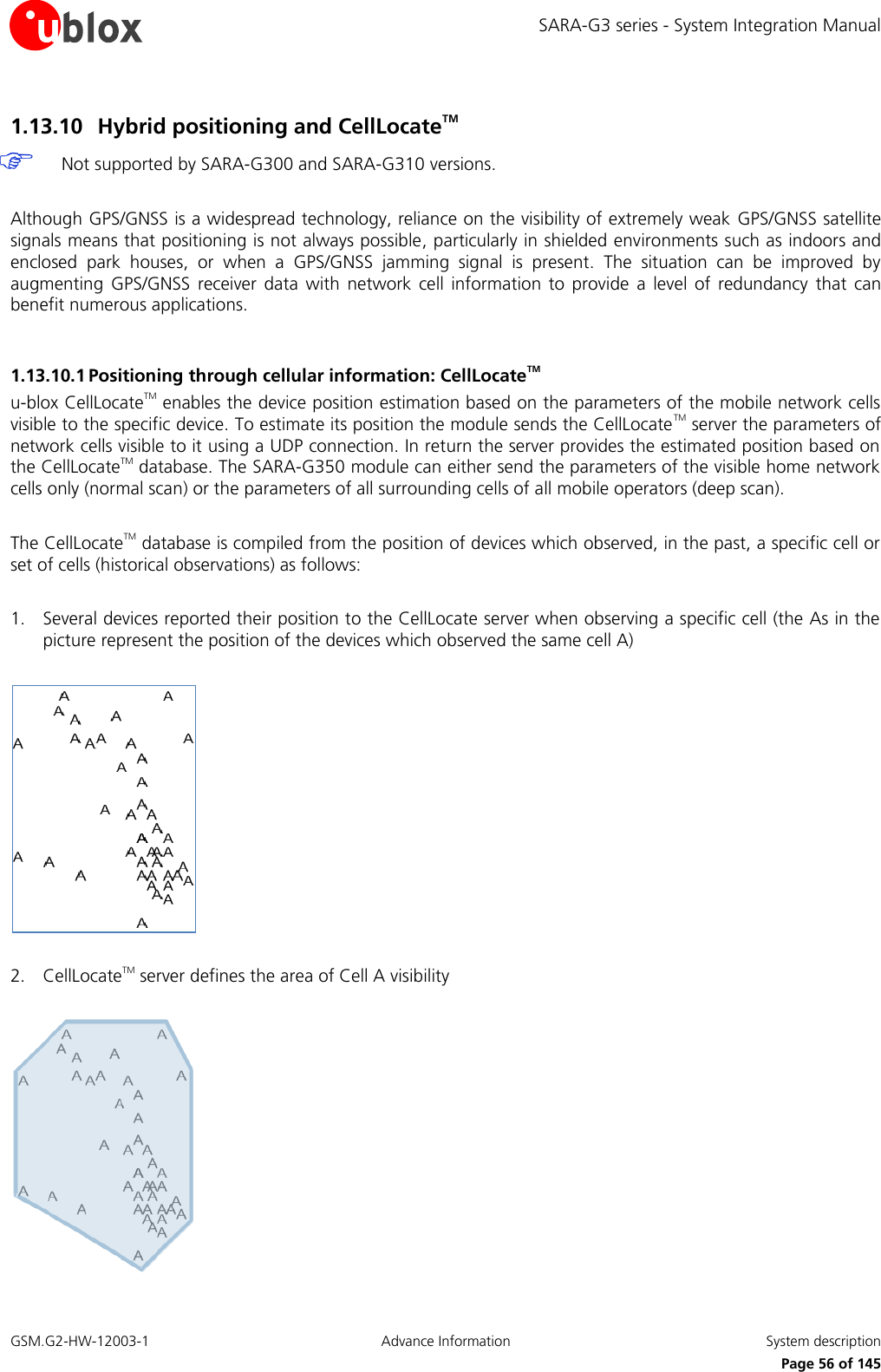

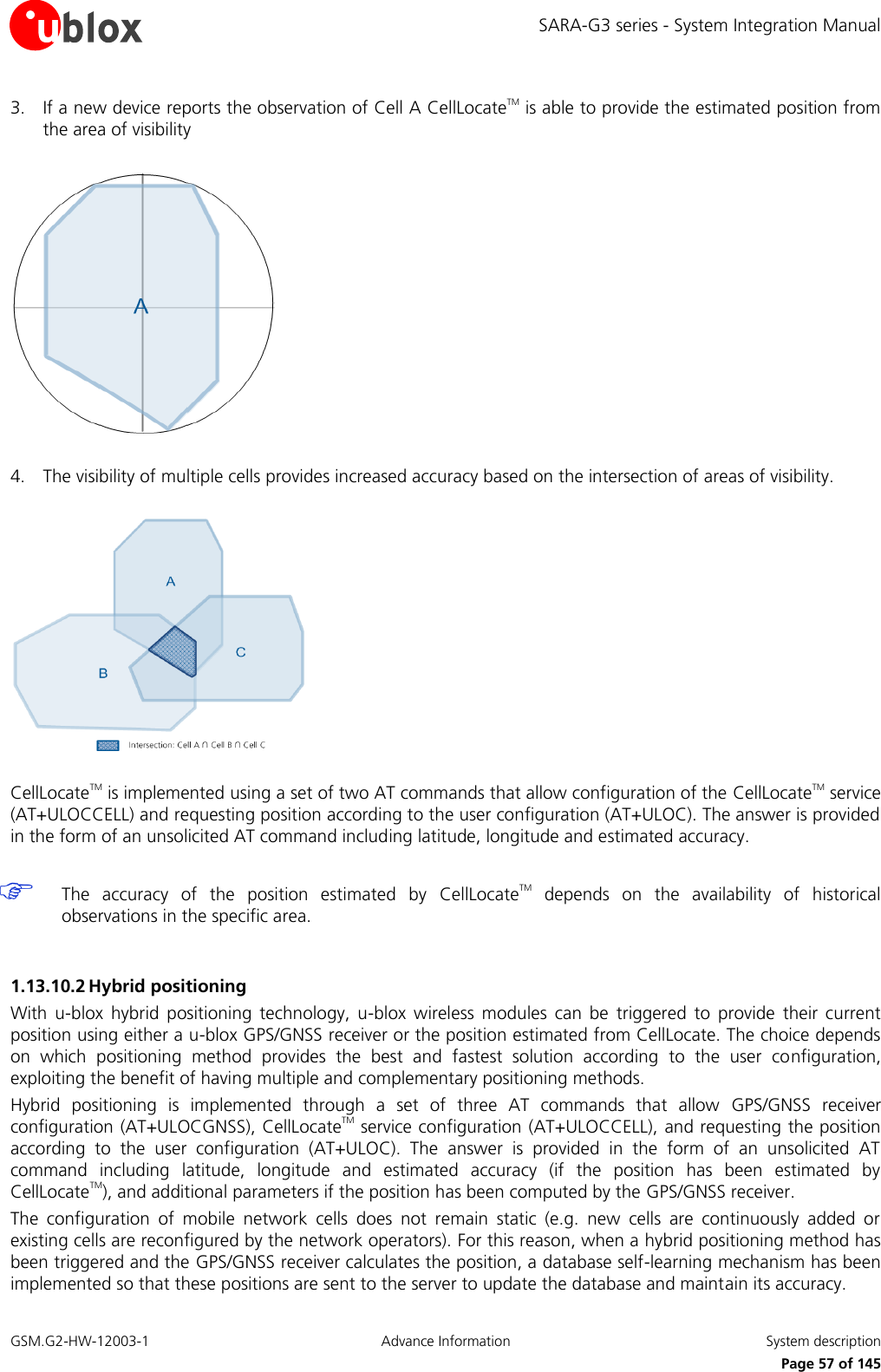

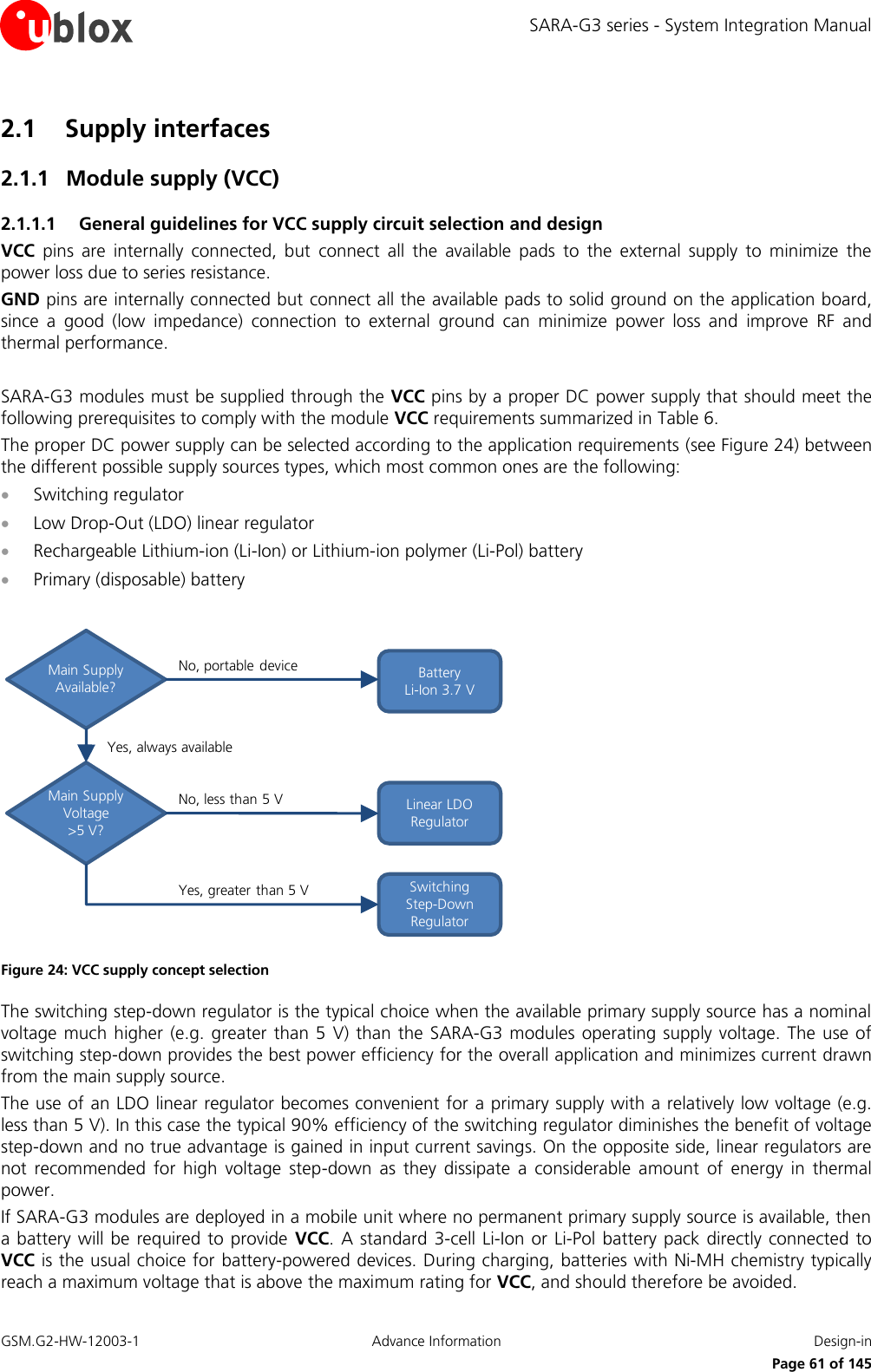

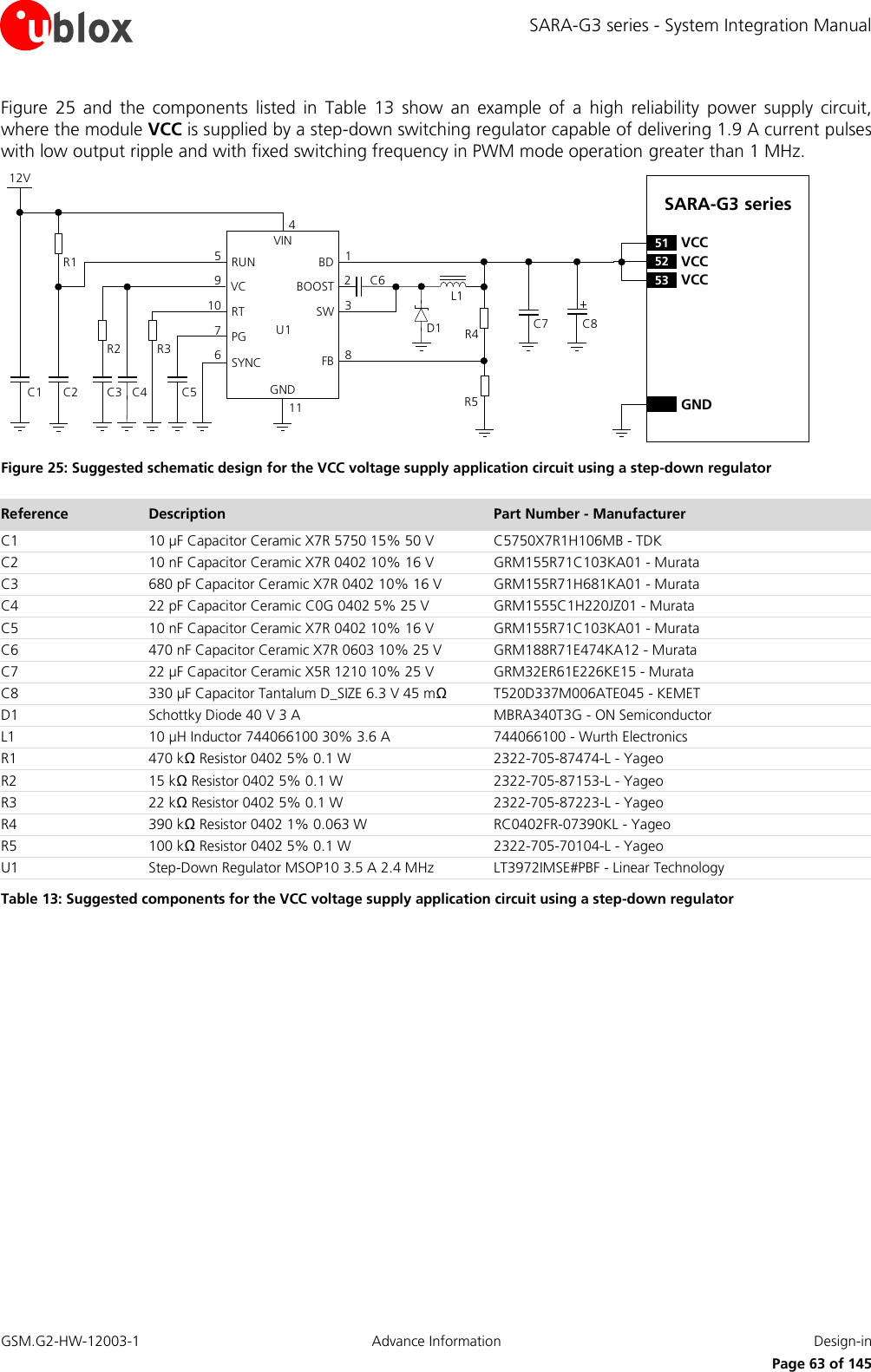

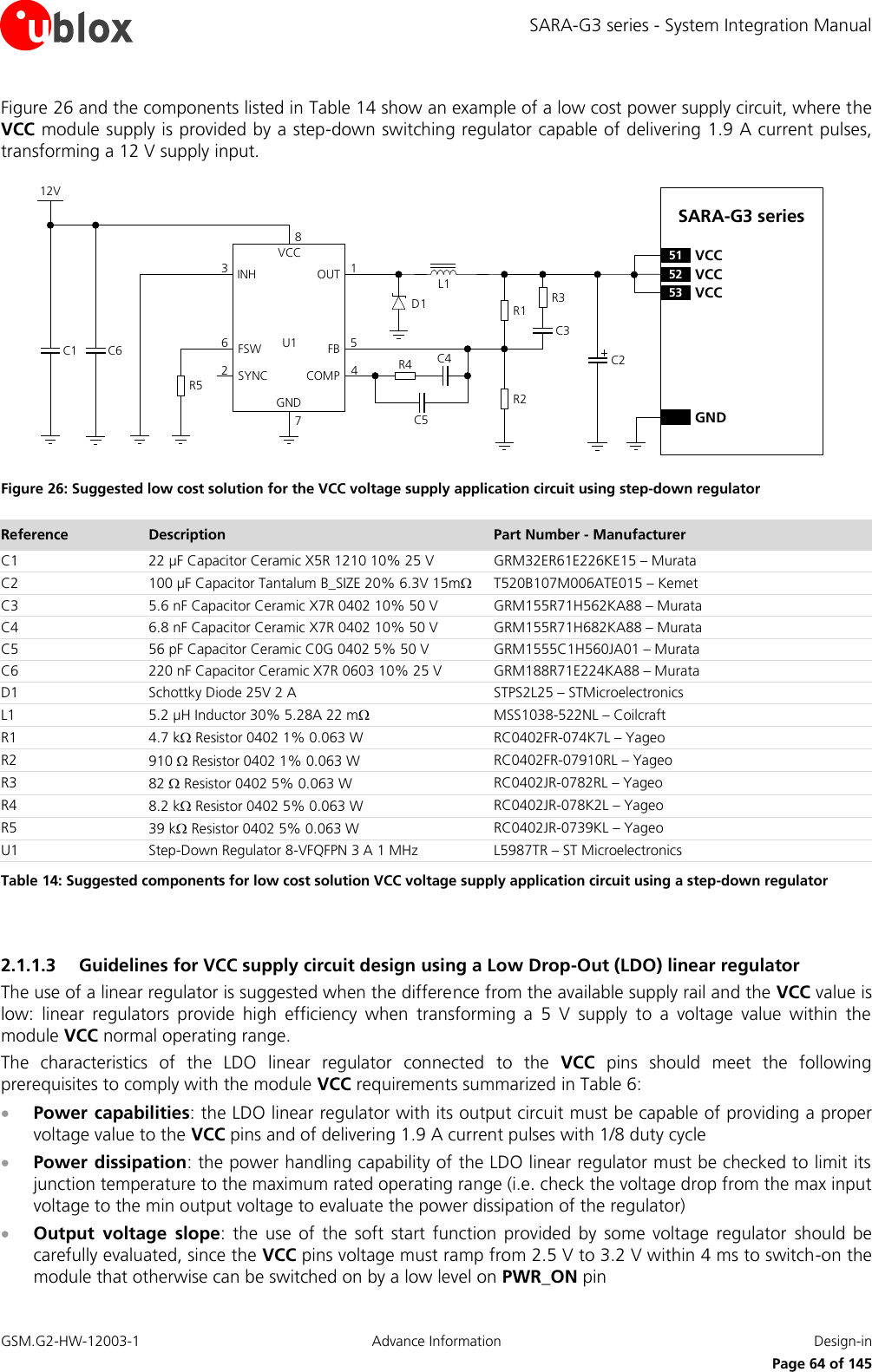

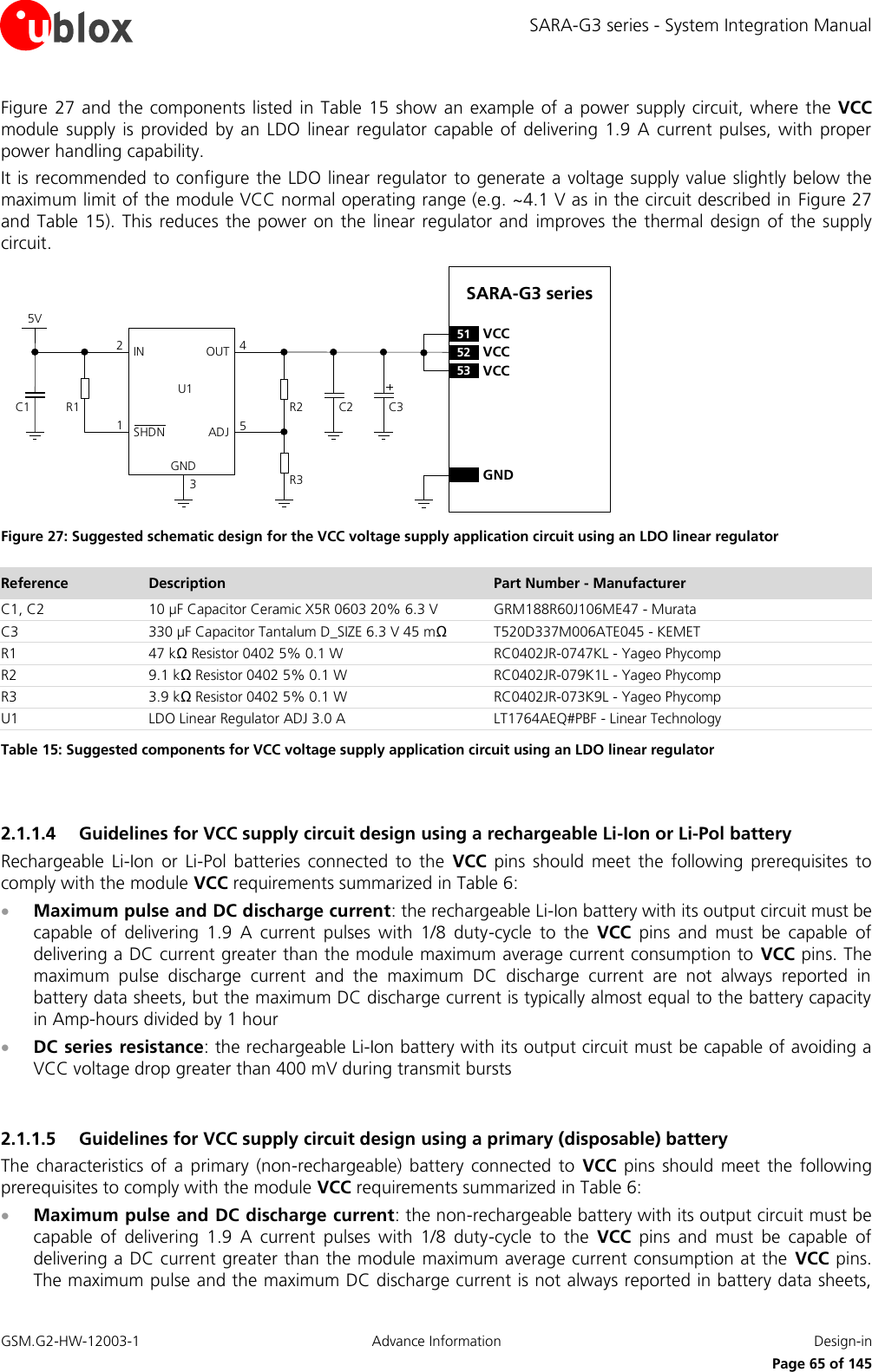

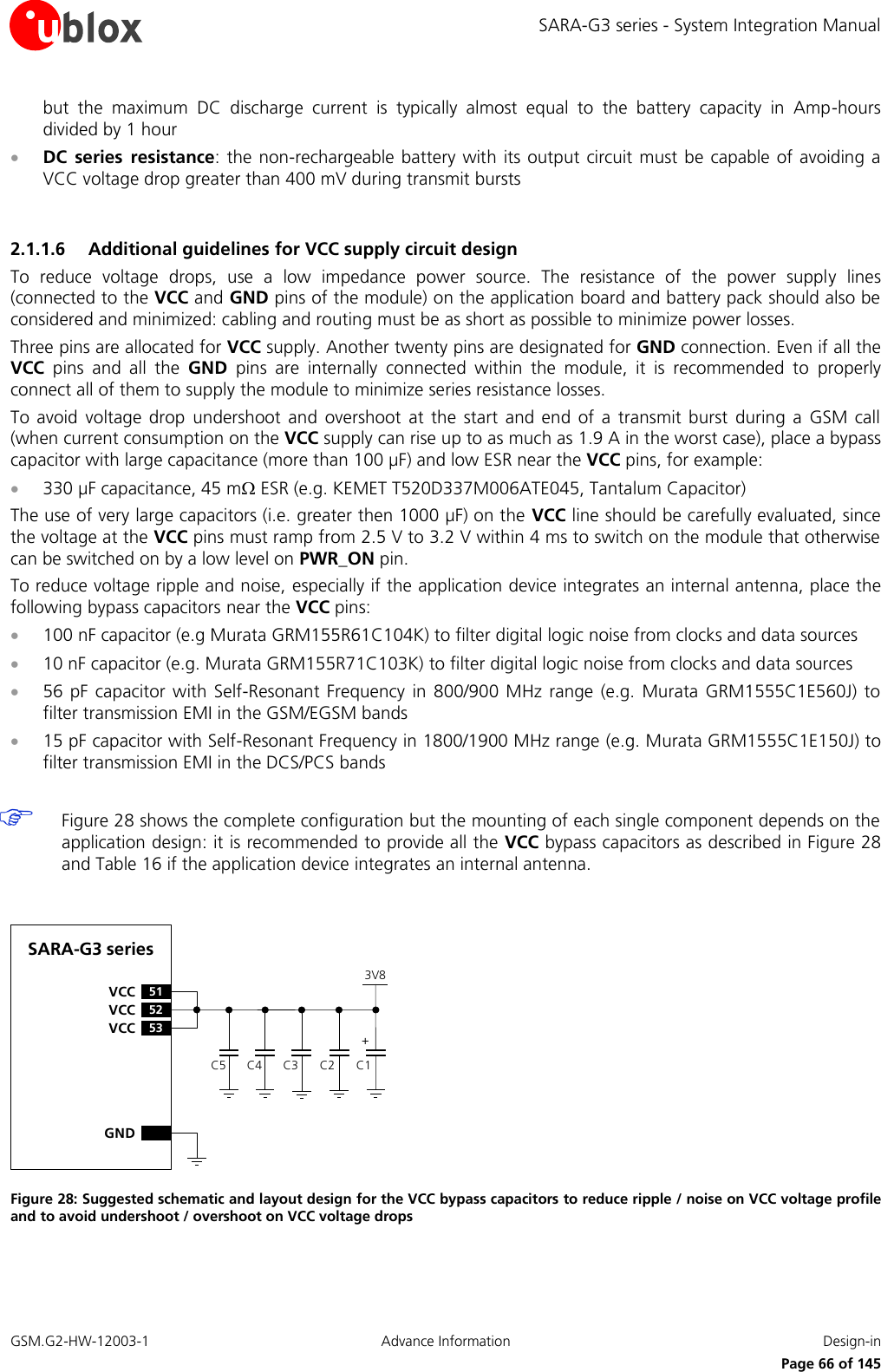

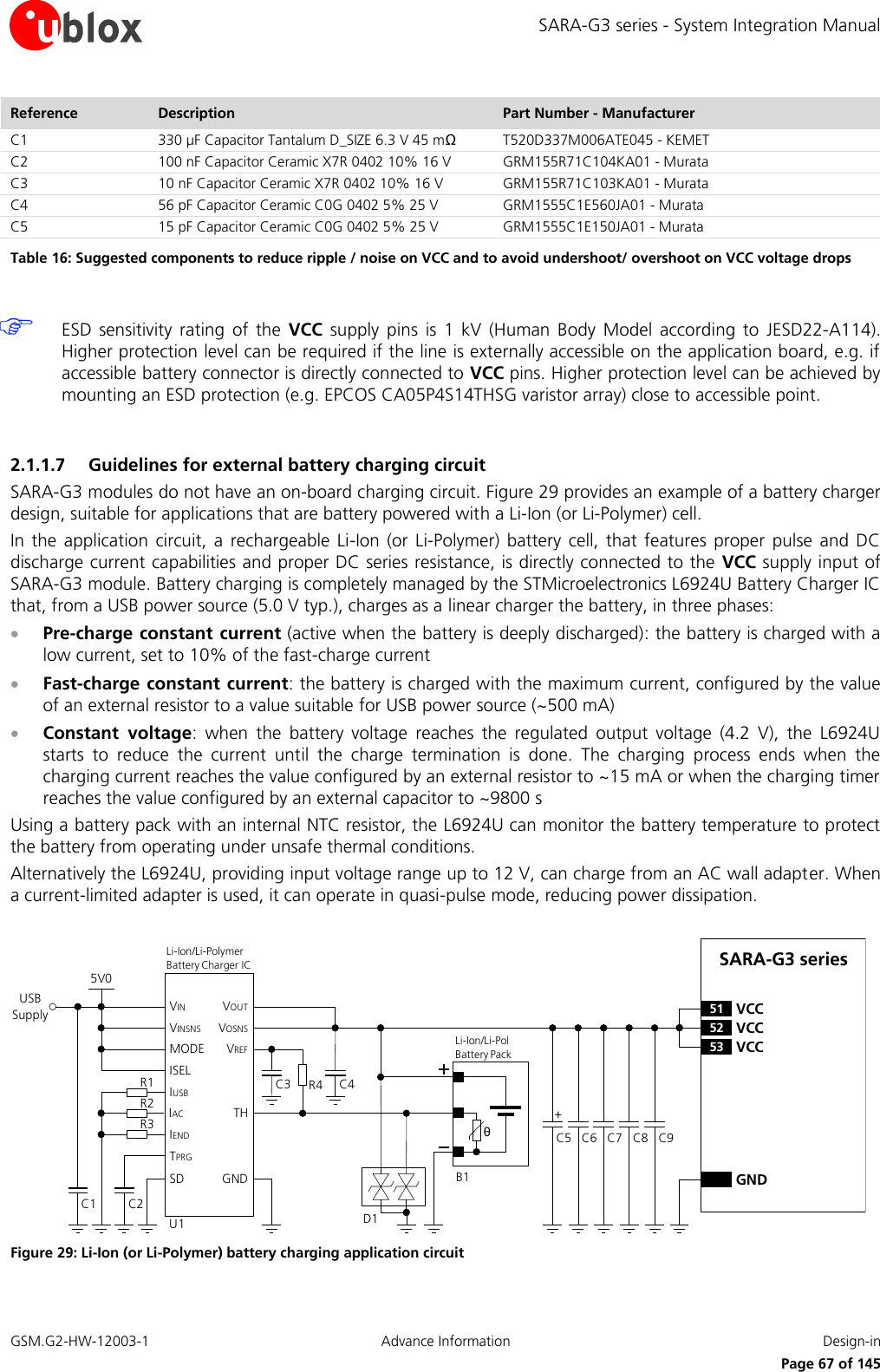

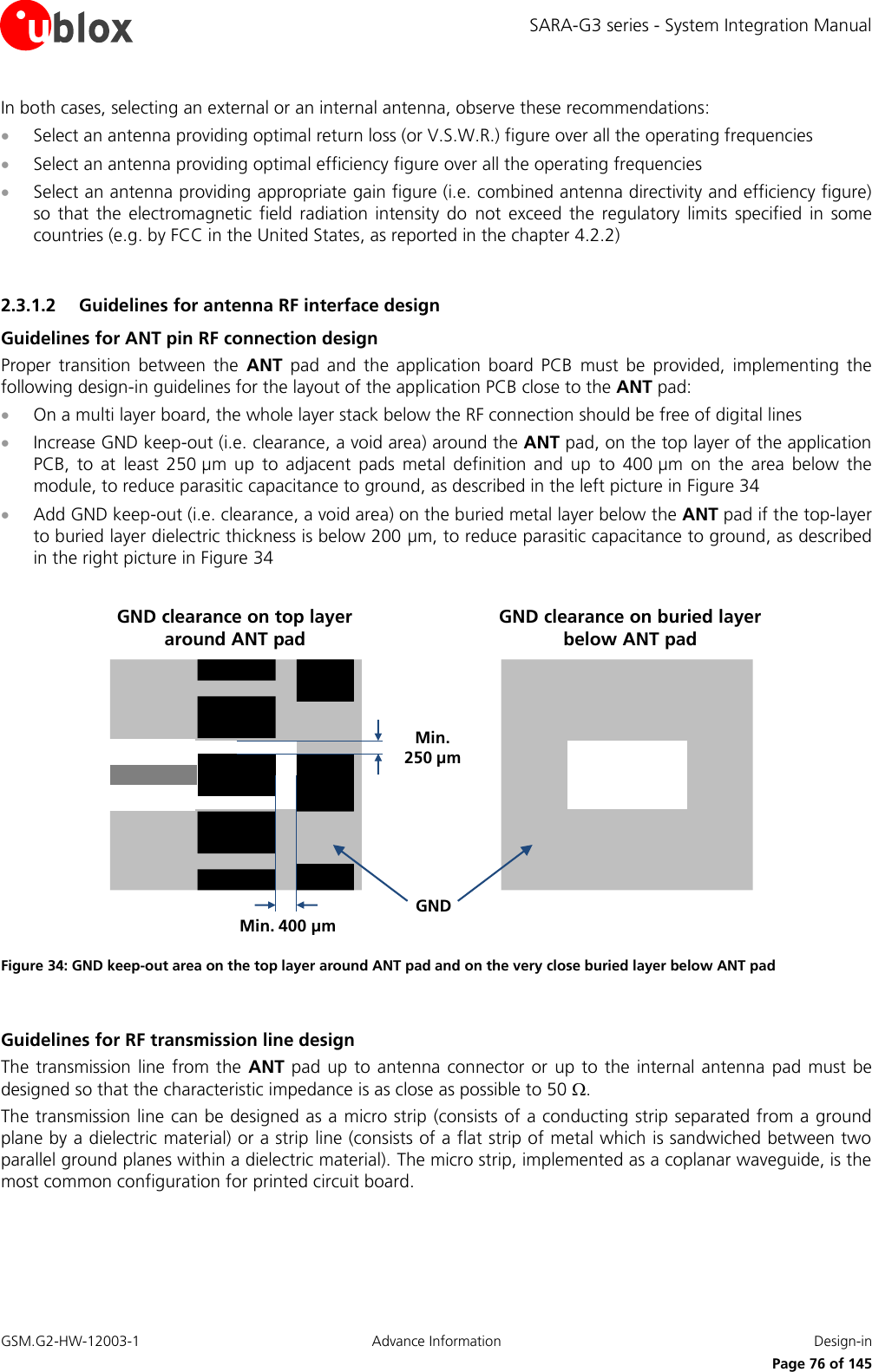

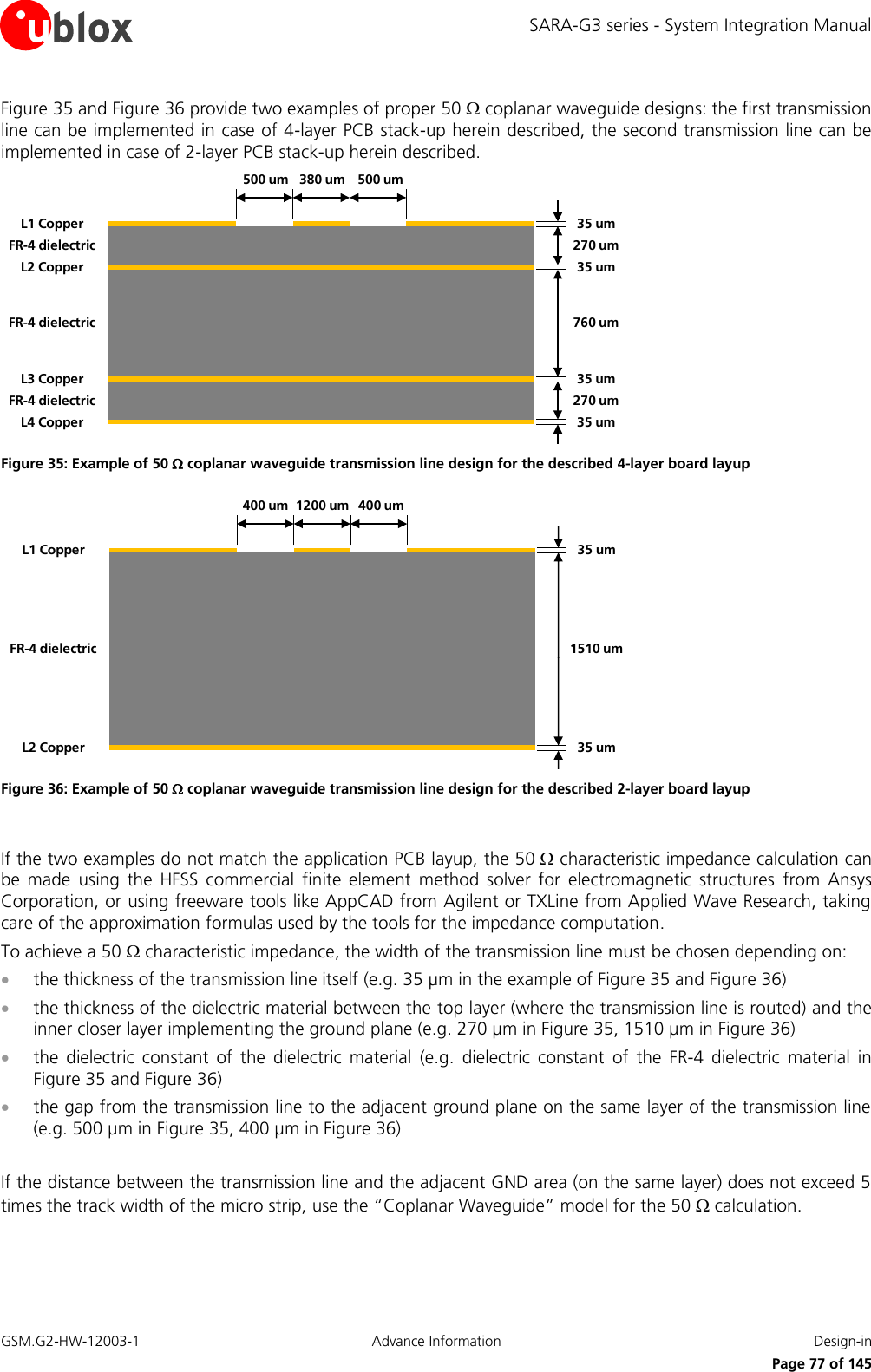

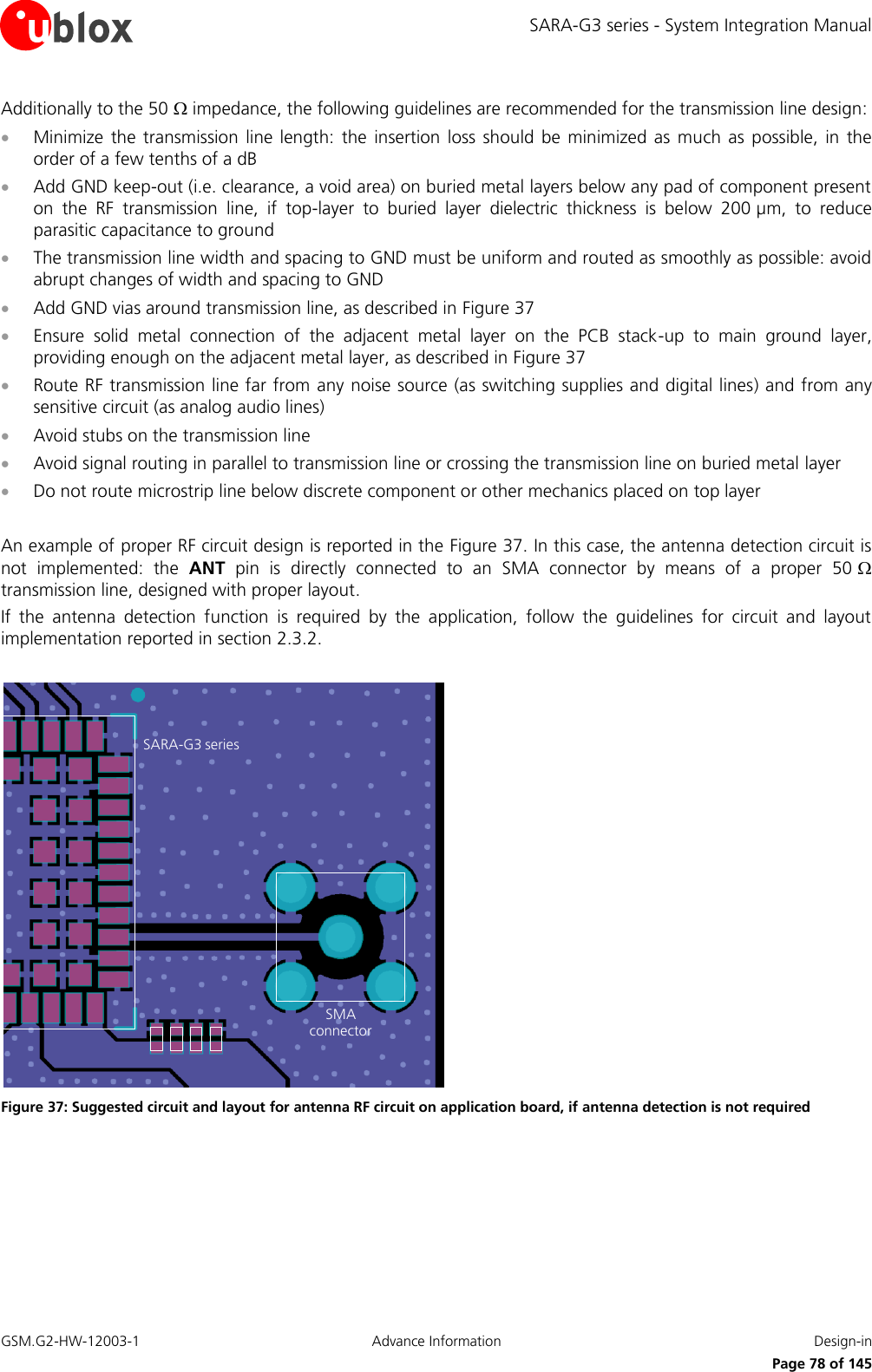

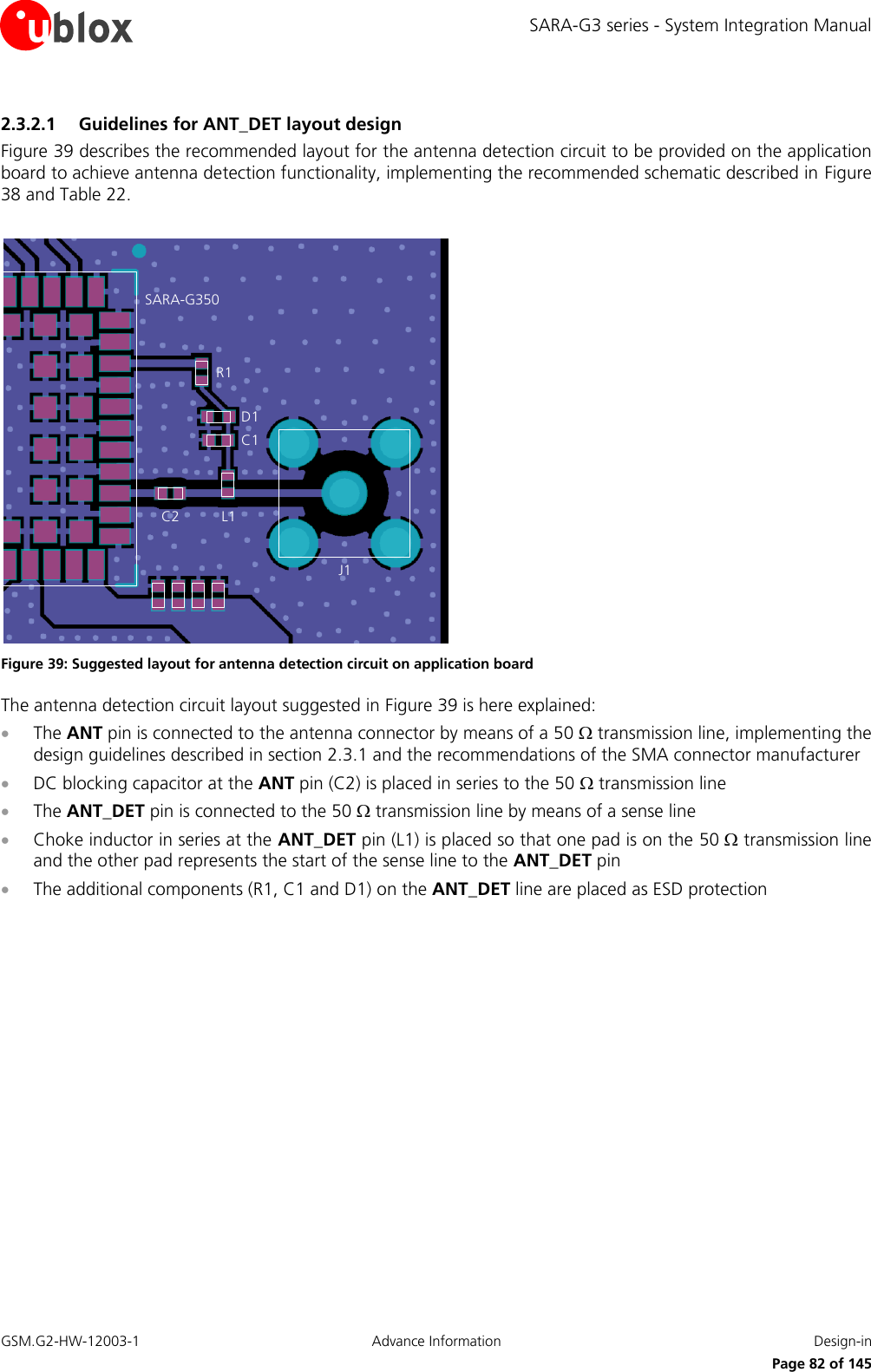

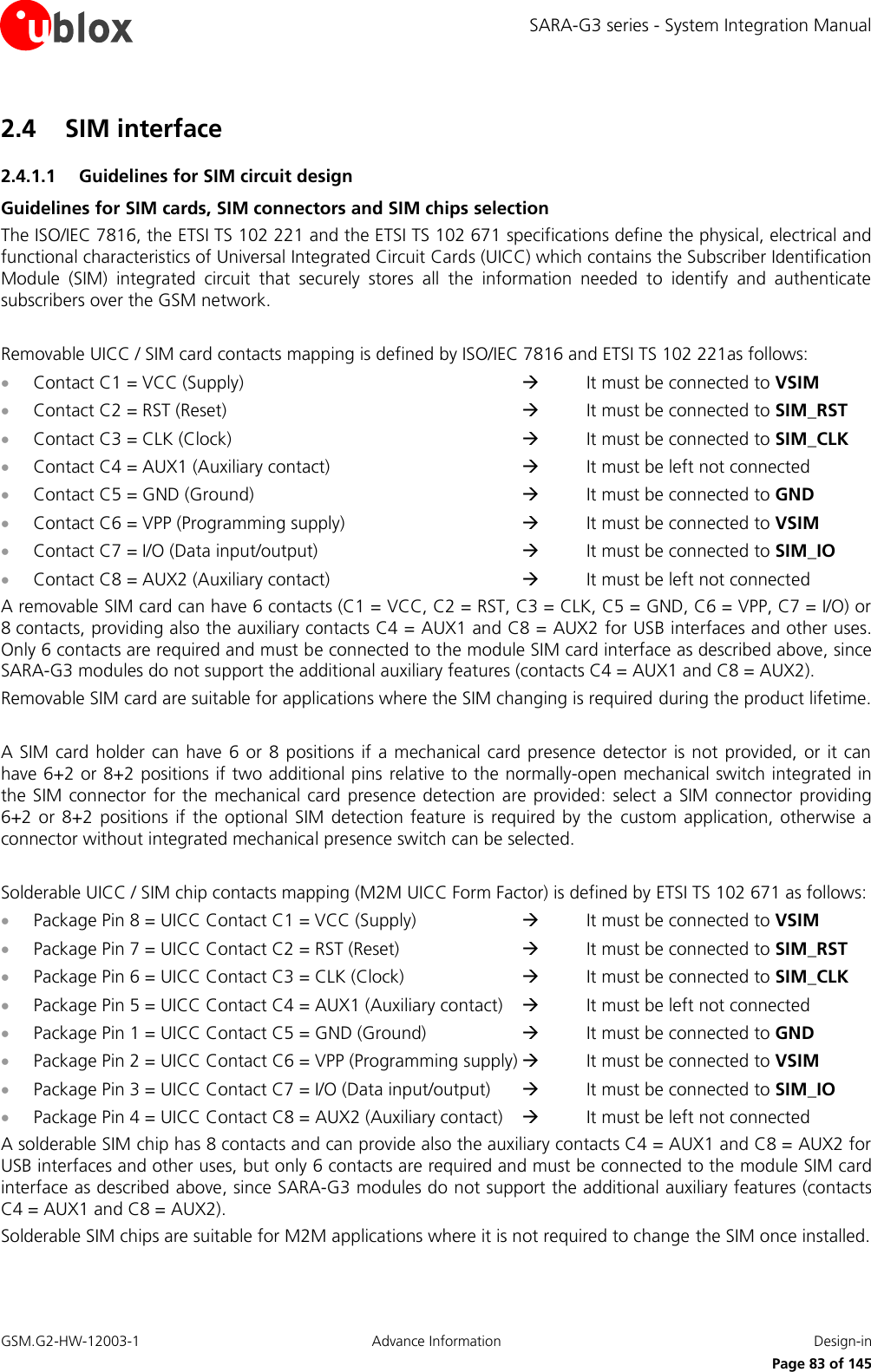

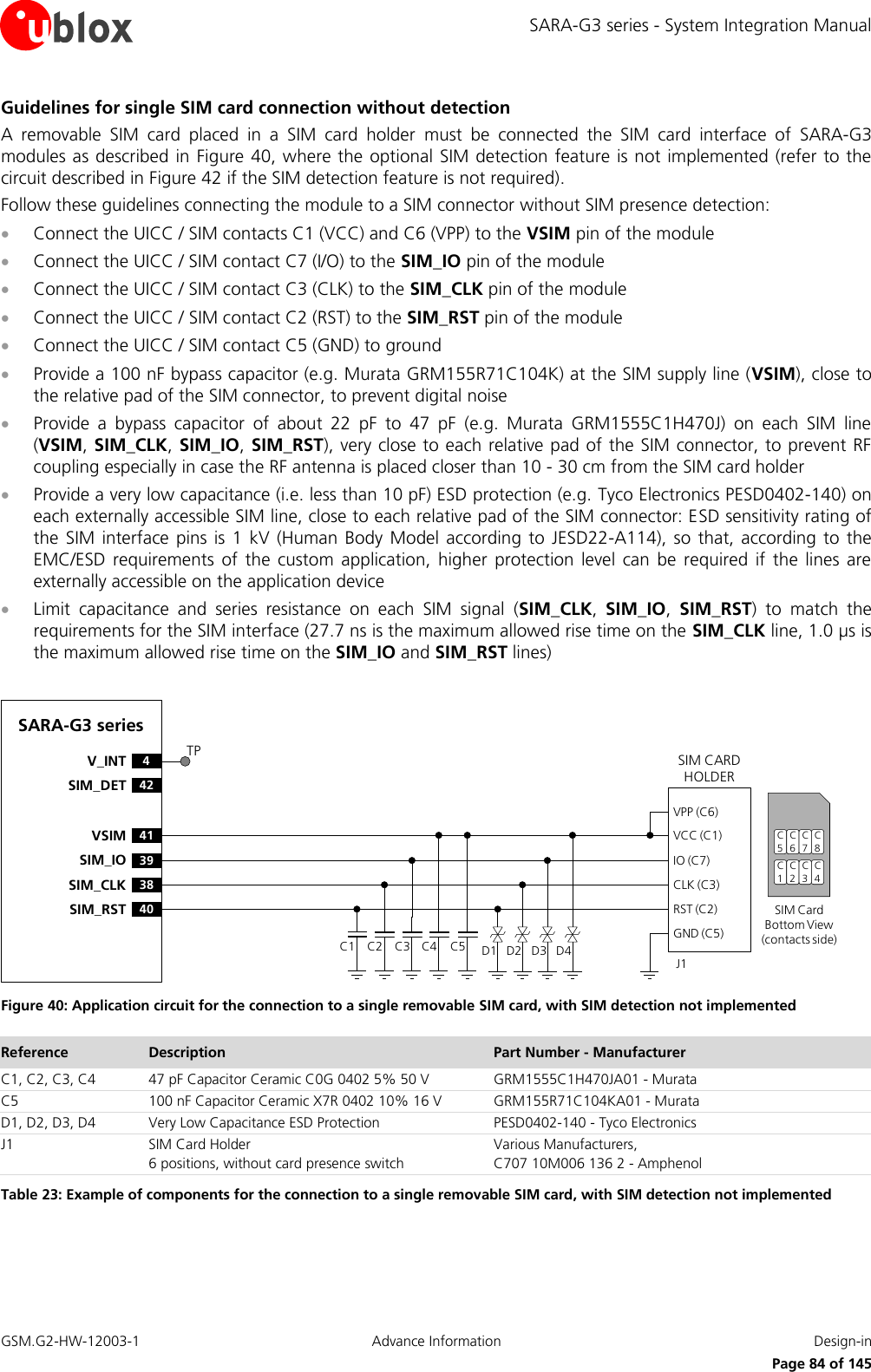

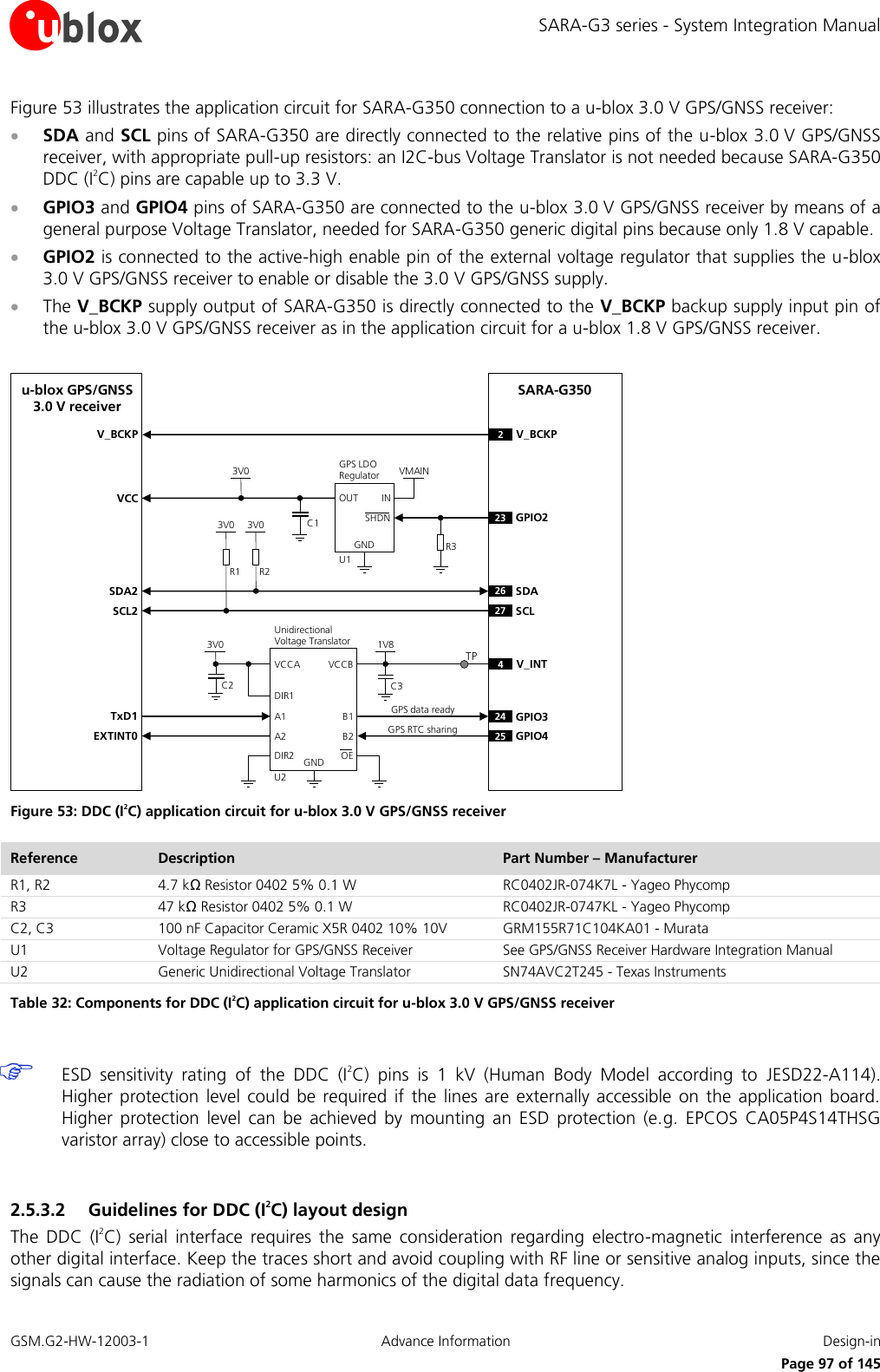

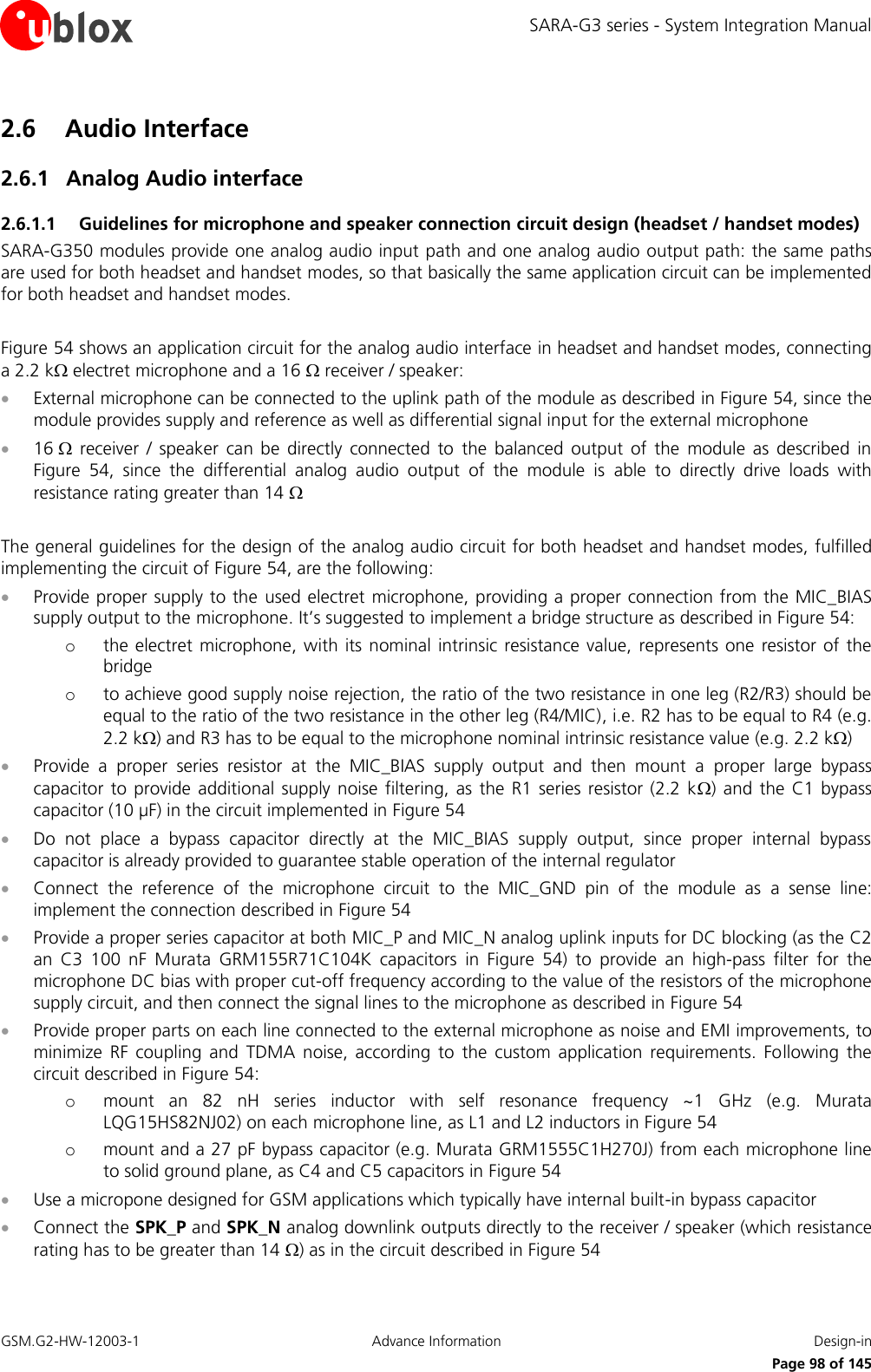

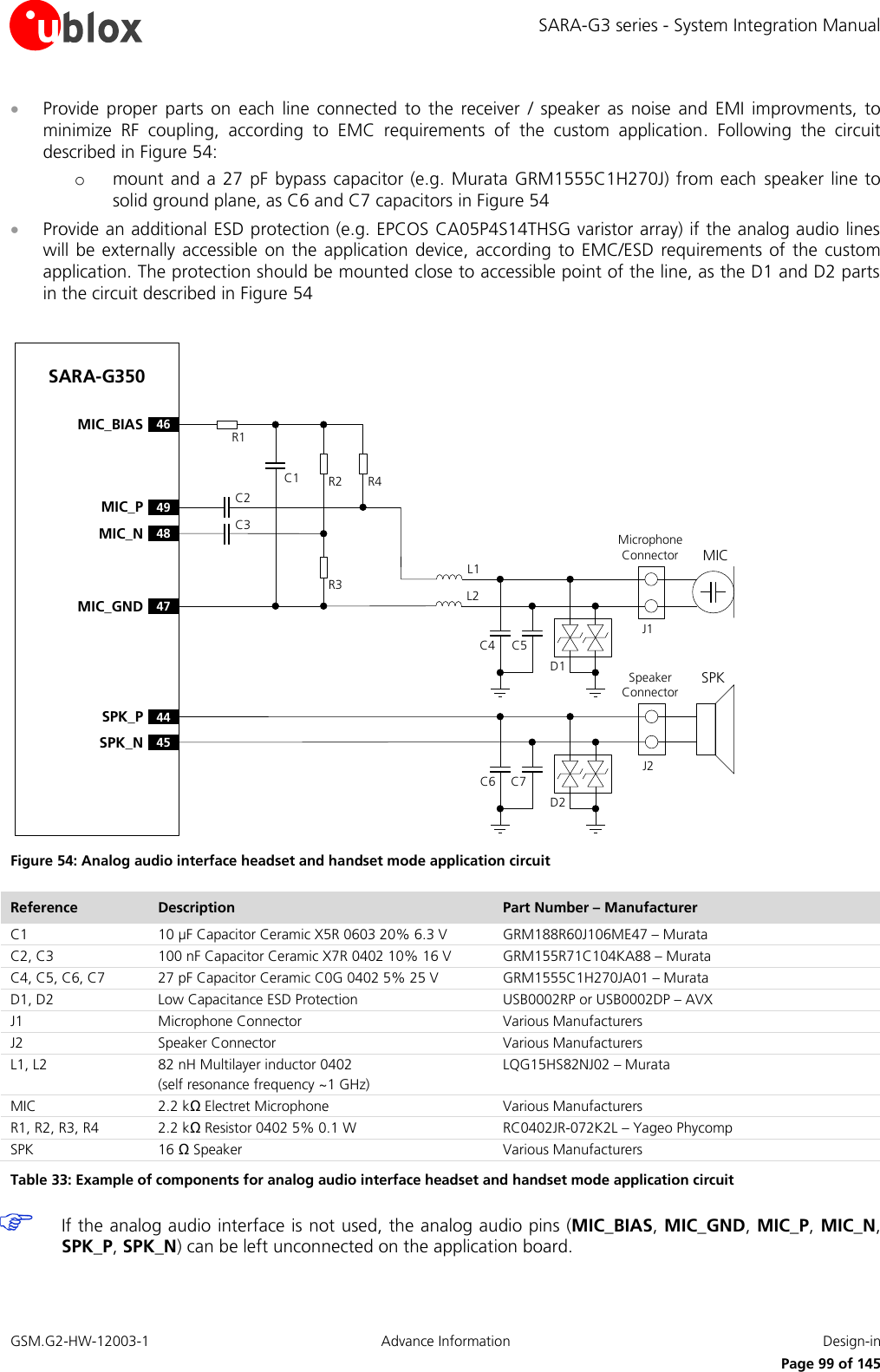

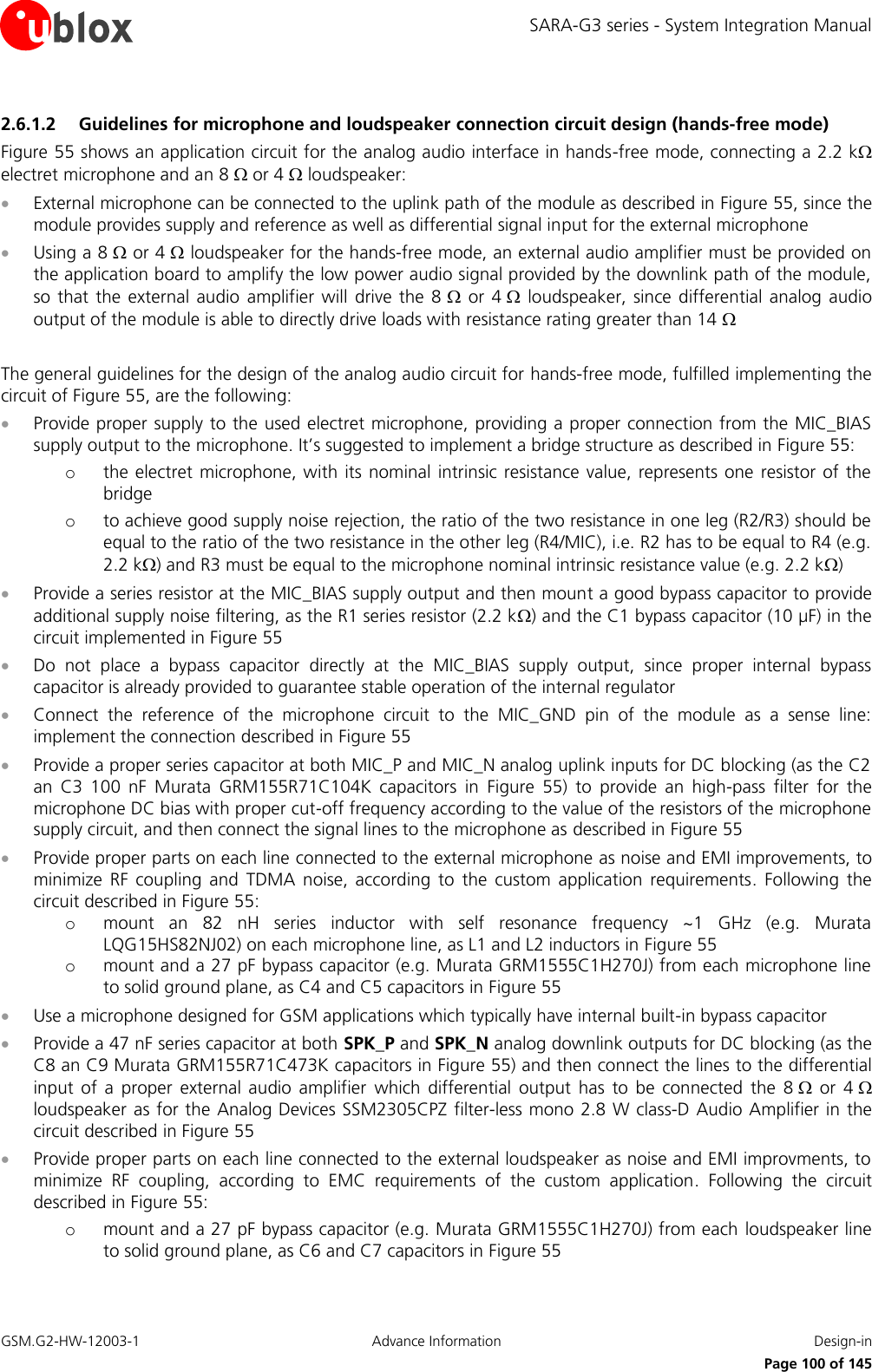

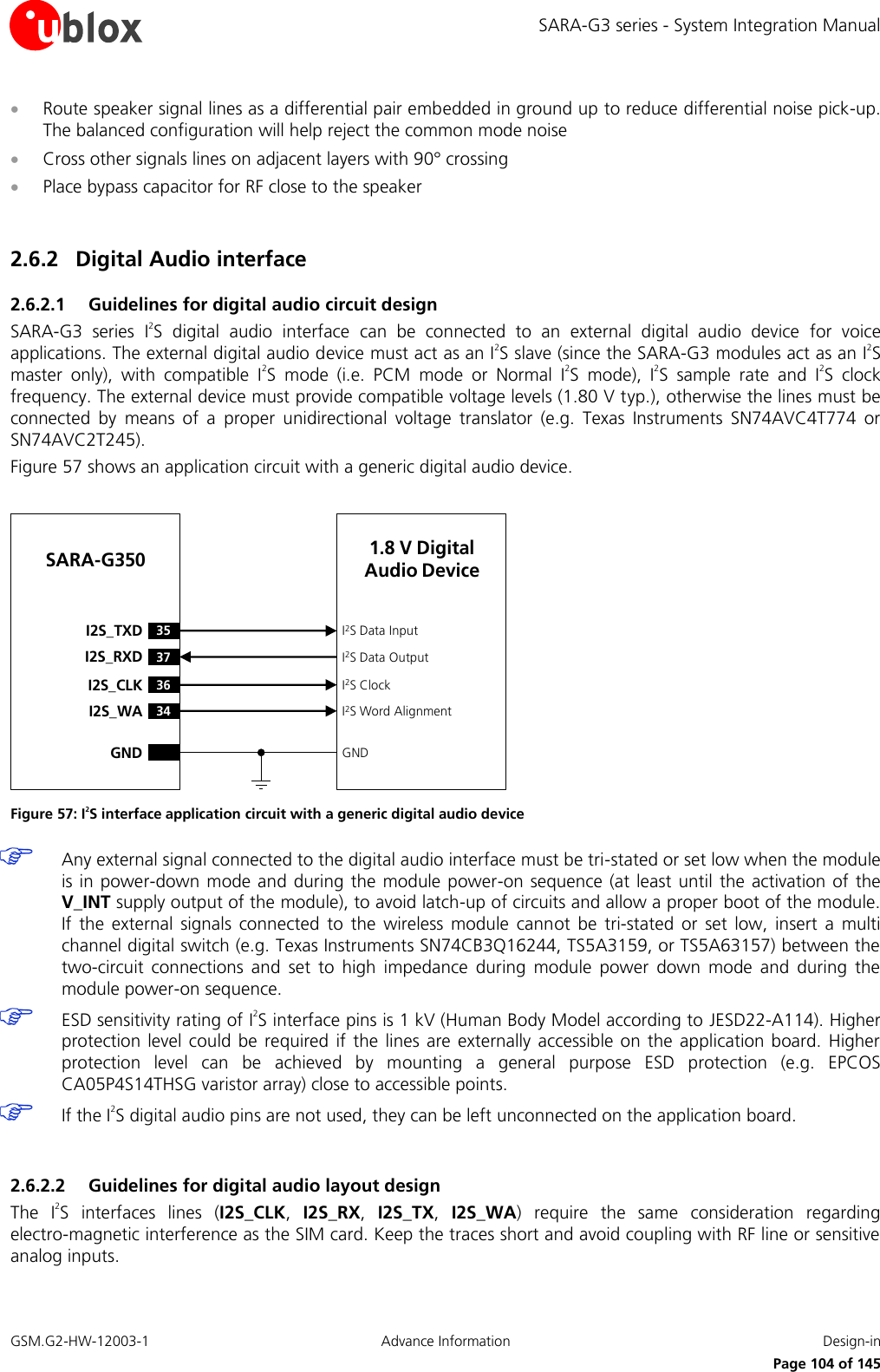

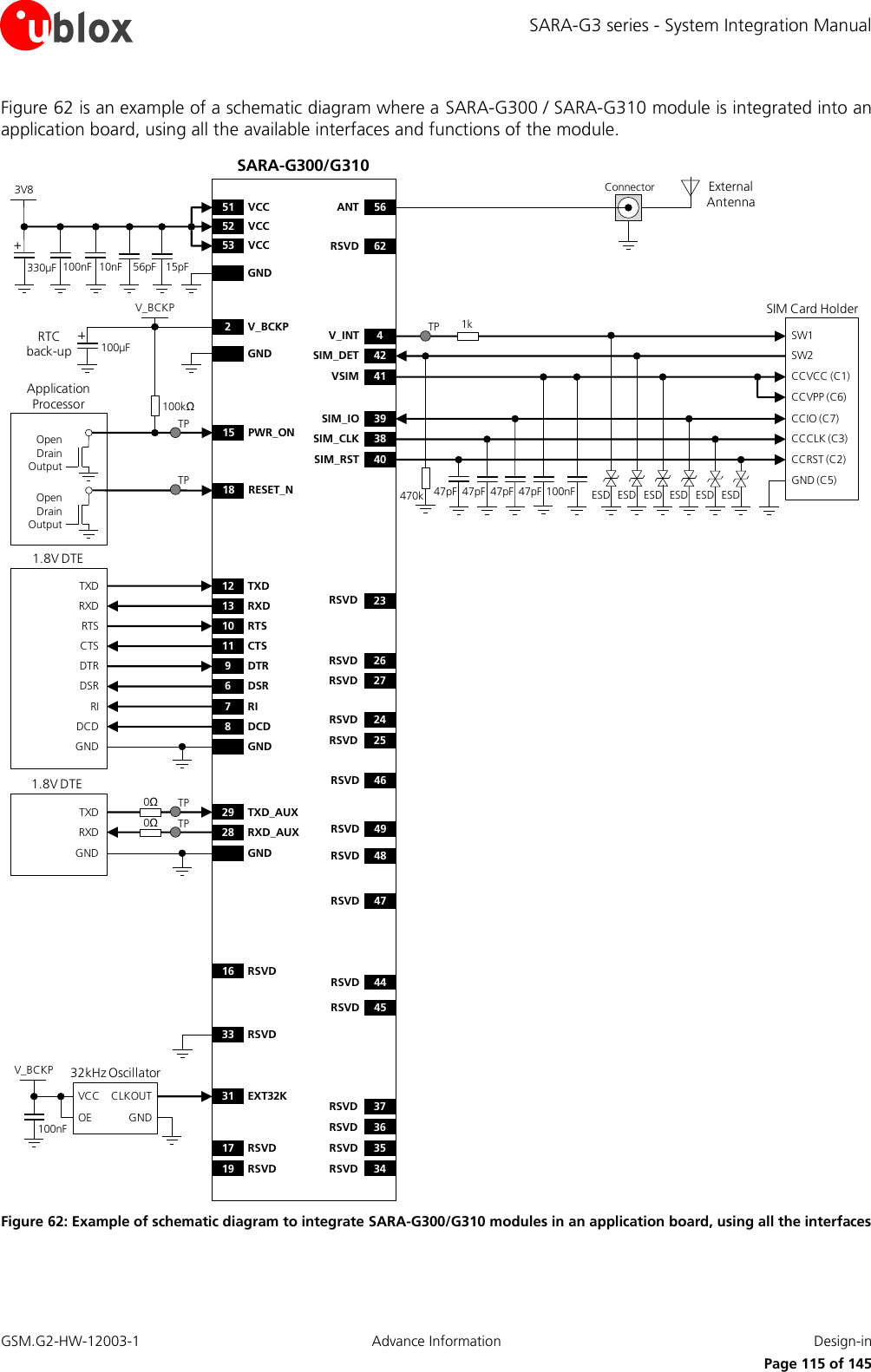

![SARA-G3 series - System Integration Manual GSM.G2-HW-12003-1 Advance Information System description Page 45 of 145 1.10.2 Digital audio interface SARA-G350 modules provide one 4-wire I2S digital audio interface (1.8 V) that acts as an I2S master and can be used for digital audio communication with external digital audio devices that acts as I2S slave. Related pins are: I2S_TXD data output I2S_RXD data input I2S_CLK clock output I2S_WA world alignment output The I2S interface can be set to two modes, by the <I2S_mode> parameter of the AT+UI2S command: PCM mode Normal I2S mode SARA-G350 modules do not support I2S slave mode: module acts as master only. The sample rate is fixed at 8 kHz only: it is not possible to configure the sample rate of transmitted and received words of SARA-G350 modules. The <main_uplink> and <main_downlink> parameters of the AT+USPM command must be properly configured to select the I2S digital audio interfaces paths (for more details, refer to u-blox AT Commands Manual [2]): <main_uplink> must be properly set to select: o the I2S interface (using I2S_RXD module input) <main_downlink> must be properly set to select: o the I2S interface (using I2S_TXD module output) Parameters of digital path can be configured and saved as the normal analog paths, using appropriate path parameter as described in the u-blox AT Commands Manual [2], +USGC, +UMGC, +USTN AT command. Analog gain parameters of microphone and speakers are not used when digital path is selected. The I2S receive data input and the I2S transmit data output signals are respectively connected in parallel to the analog microphone input and speaker output signals, so resources available for analog path can be shared: Digital filters and digital gains are available in both uplink and downlink direction. The AT commands allow to properly configure them Ringer tone and service tone are mixed on the TX path when active (downlink) The HF algorithm acts on I2S path Refer to the u-blox AT Commands Manual [2]: AT+UI2S command for possible settings of I2S interface. 1.10.2.1 I2S interface – PCM mode Main features of the I2S interface in PCM mode: I2S runs in PCM – short alignment mode (configurable by AT commands) I2S word alignment signal is configured to 8 kHz: this is the <sample_rate> parameter I2S word alignment toggles high for 1 or 2 CLK cycles of synchronization (configurable), then toggles low for 16 CLK cycles of sample width. Frame length can be 1 + 16 = 17 bits or 2 + 16 = 18 bits I2S clock frequency depends on frame length and the 8 kHz sample rate. Can be 17 x 8 kHz or 18 x 8 kHz I2S transmit and I2S receive data are 16 bit words long with the same sampling rate as I2S word alignment, mono. Data is in 2’s complement notation. MSB is transmitted first](https://usermanual.wiki/u-blox/SARAG350.Users-manual/User-Guide-1951513-Page-45.png)