Baron Services XDD-1000C C-BAND DOPPLER WEATHER RADAR User Manual

Baron Services Inc C-BAND DOPPLER WEATHER RADAR

Contents

- 1. Modulator Manual

- 2. Users Manual Part 1

- 3. Users Manual Part 2

- 4. Users Manual Part 3

- 5. S10 OPERATION AND MAINTENANCE MANUAL

- 6. S10 FAST TRAC MILLENIUM USERS GUIDE

- 7. S10 TECHNICAL MANUAL

- 8. S10 RECEIVER AND PROCESSOR USERS MANUAL PART 1

- 9. S10 RECEIVER AND PROCESSOR USERS MANUAL PART 2

- 10. S10 RECEIVER AND PROCESSOR USERS MANUAL PART 3

S10 RECEIVER AND PROCESSOR USERS MANUAL PART 1

DRAFT

RVP8

Digital IF Receiver/Doppler Signal Processor

User’s Manual

May 2003

Copyright 2003 SIGMET, Inc.

The designs and descriptions contained in this manual may not be copied, translated or

reproduced in any form without the prior written consent of SIGMET, Inc.

Table of Contents

RVP8 User’s Manual

12 May 2003

i

Table of Contents

Hardware Limited Warranty x . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Preface xi . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1. Introduction and Specifications 1–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 System Configuration Concepts 1–4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.1 IFD IF Digitizer 1–9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.2 Digital Receiver PCI Card (RVP8/Rx) 1–10 . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.3 Mother Board or Single-Board Computer (SBC) 1–13 . . . . . . . . . . . . . . . . . .

1.1.4 Digital Transmitter PCI Card (RVP8/Tx) 1–13 . . . . . . . . . . . . . . . . . . . . . . . .

1.1.5 I/O-62 PCI Card and I/O Panel 1–15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Comparison of Analog vs Digital Radar Receivers 1–17 . . . . . . . . . . . . . . . . . . . . . .

1.2.1 What is a Digital IF Receiver? 1–17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.2 Magnetron Receiver Example 1–18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.3 Klystron or TWT Receiver and Transmit RF Example 1–20 . . . . . . . . . . . . .

1.3 RVP8 IF Signal Processing 1–21 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.1 IFD Data Capture and Timing 1–21 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.2 Burst Pulse Analysis for Amplitude/Frequency/Phase 1–22 . . . . . . . . . . . . . .

1.3.3 Rx Board and CPU IF to I/Q Processing 1–23 . . . . . . . . . . . . . . . . . . . . . . . .

1.4 RVP8 Weather Signal Processing 1–25 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.1 General Processing features 1–26 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.2 RVP8 Pulse Pair Time Domain Processing 1–29 . . . . . . . . . . . . . . . . . . . . . .

1.4.3 RVP8 DFT/FFT Processing 1–29 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.4 Random Phase Processing for 2nd Trip Echo 1–30 . . . . . . . . . . . . . . . . . . . .

1.4.5 Polarization Mode Processing 1–30 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.6 Output Data 1–30 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 RVP8 Control and Maintenance Features 1–31 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5.1 Radar Control Functions 1–31 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5.2 Power-Up Setup Configuration 1–32 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5.3 Built-In Diagnostics 1–32 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.6 Support Utilities and Available Application Software 1–33 . . . . . . . . . . . . . . . . . . . .

1.7 Open Architecture and Published API 1–34 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.8 RVP8 Technical Specifications 1–35 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.8.1 IFD Digitizer Module 1–35 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.8.2 RVP8/Rx PCI Card 1–36 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.8.3 RVP8/Tx PCI Card 1–37 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.8.4 SIGMET I/O-62 PCI Card 1–38 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.8.5 RVP8 Standard Connector Panel 1–39 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.8.6 RVP8 Processing Algorithms 1–40 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table of Contents

RVP8 User’s Manual

12 May 2003

ii

1.8.7 RVP8 Input/Output Summary 1–42 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.8.8 Physical and Environmental Characteristics 1–43 . . . . . . . . . . . . . . . . . . . . . .

2. Hardware Installation 2–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Overview and Input Power Requirements 2–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 IFD IF Digitizer Module Installation 2–2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 IFD Introduction 2–2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.2 IFD Revision History 2–3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.3 IFD Power, Size and Physical Mounting Considerations 2–4 . . . . . . . . . . . .

2.2.4 IFD I/O Summary 2–5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.5 IFD Adjustments and Test/Status Indicators 2–6 . . . . . . . . . . . . . . . . . . . . . .

2.2.6 IFD Input A/D Saturation Levels 2–8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.7 IF Bandwidth and Dynamic Range 2–9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.8 IF Gain and System Performance 2–11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.9 Choice of Intermediate Frequency 2–13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.10 IFD Analog AFC Output Voltage (Optional) 2–14 . . . . . . . . . . . . . . . . . . . .

2.2.11 IFD Reference Clock Input (Optional) 2–15 . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.12 Coax Uplink and Fiber Downlink 2–17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 RVP8 Chassis 2–18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.1 RVP8 Chassis Overview 2–18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.2 Power Requirements, Size and Physical Mounting 2–18 . . . . . . . . . . . . . . . .

2.3.3 Main Chassis Direct Connections 2–19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.4 Connector Panel I/O Connections 2–20 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.5 Power-Up Details (Alan) Draft 2–23 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.6 Socket Interface 2–24 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

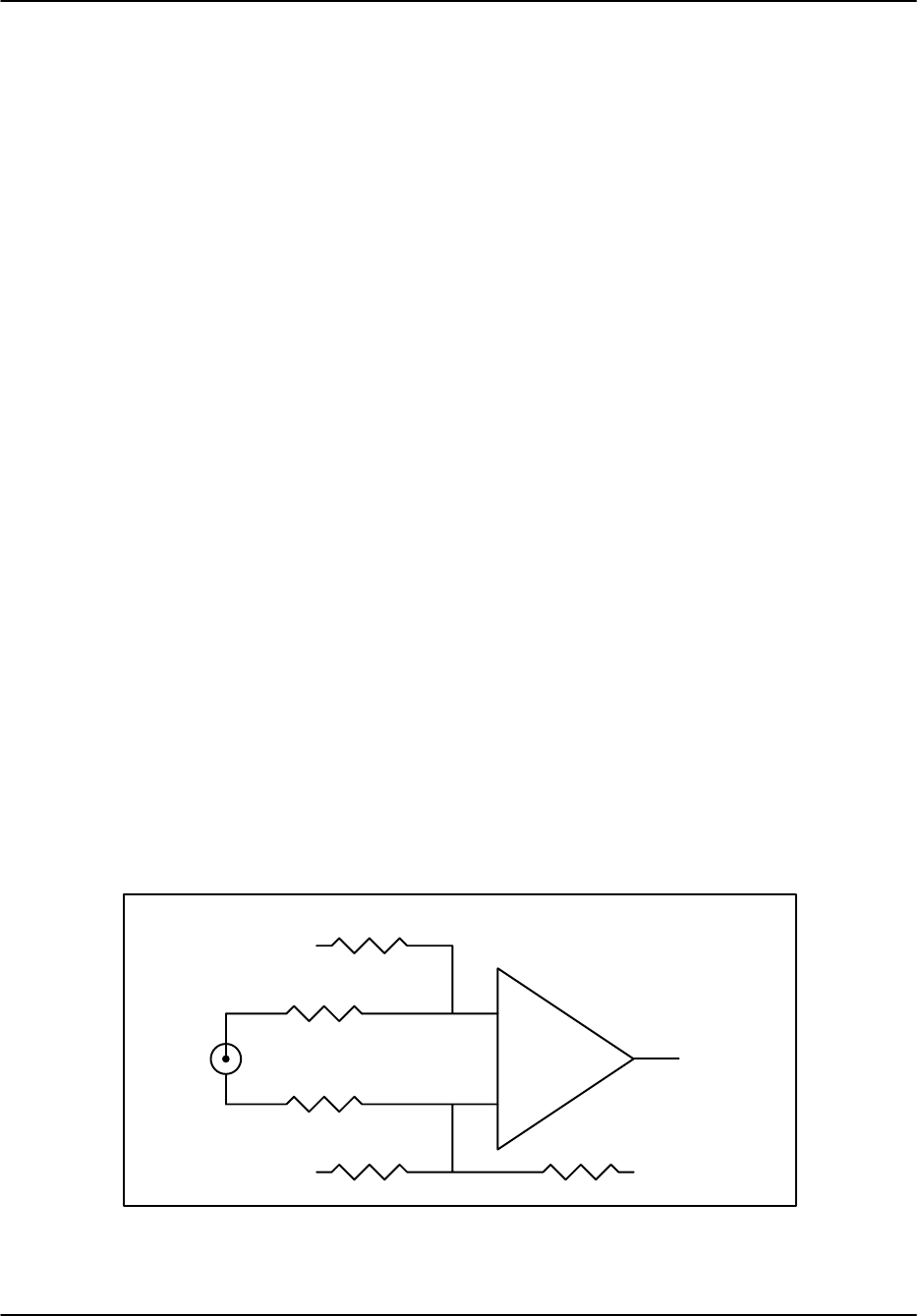

2.4 Digital AFC Module (DAFC) 2–27 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4.1 Example Hookup to a CTI “MVSR-xxx” STALO 2–29 . . . . . . . . . . . . . . . . .

2.4.2 Example Hookup to a MITEQ “MFS-xxx” STALO 2–31 . . . . . . . . . . . . . . .

2.5 RVP8 Custom Interfaces 2–32 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.1 Using the IFD Coax Uplink 2–32 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.2 Using the (I,Q) Digital Data Stream (Alan) 2–35 . . . . . . . . . . . . . . . . . . . . . .

3. TTY Nonvolatile Setups (draft) 3–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Overview of Setup Procedures 3–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.1 Initial Entry and Help List 3–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.2 Factory, Saved, and Current Settings 3–2 . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.3 Processor Reset Command 3–3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.4 V — View Internal Status 3–3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.5 Burst-In / IF-In Swap Command 3–5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Host Computer I/O Debugging 3–7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Physical-Level I/O Examiner 3–7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 Application-Level I/O Examiner 3–7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 View/Modify Dialogs 3–10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table of Contents

RVP8 User’s Manual

12 May 2003

iii

3.3.1 Mc — Board Configuration 3–10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2 Mp — Processing Options 3–13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3 Mf — Clutter Filters 3–16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.4 Mt — General Trigger Setups 3–18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.5 Mt<n> — Triggers for Pulsewidth #n 3–21 . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.6 Mb — Burst Pulse and AFC 3–25 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.6.1 AFC Motor/Integrator Option 3–32 . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.7 M+ — Debug Options 3–33 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.8 Mz — Transmitter Phase Control 3–34 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4. Plot-Assisted Setups 4–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

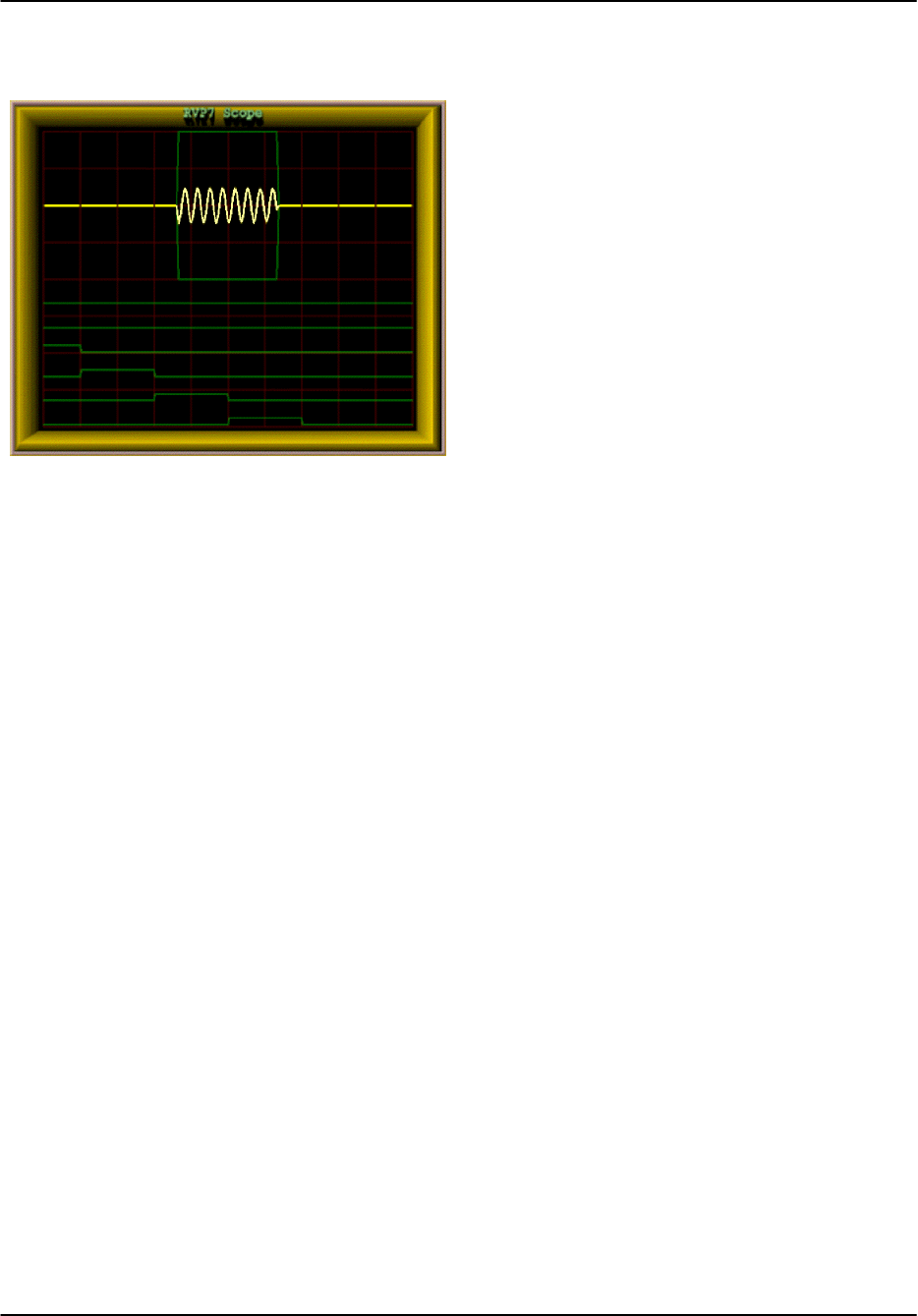

4.1 Oscilloscope Connections 4–2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

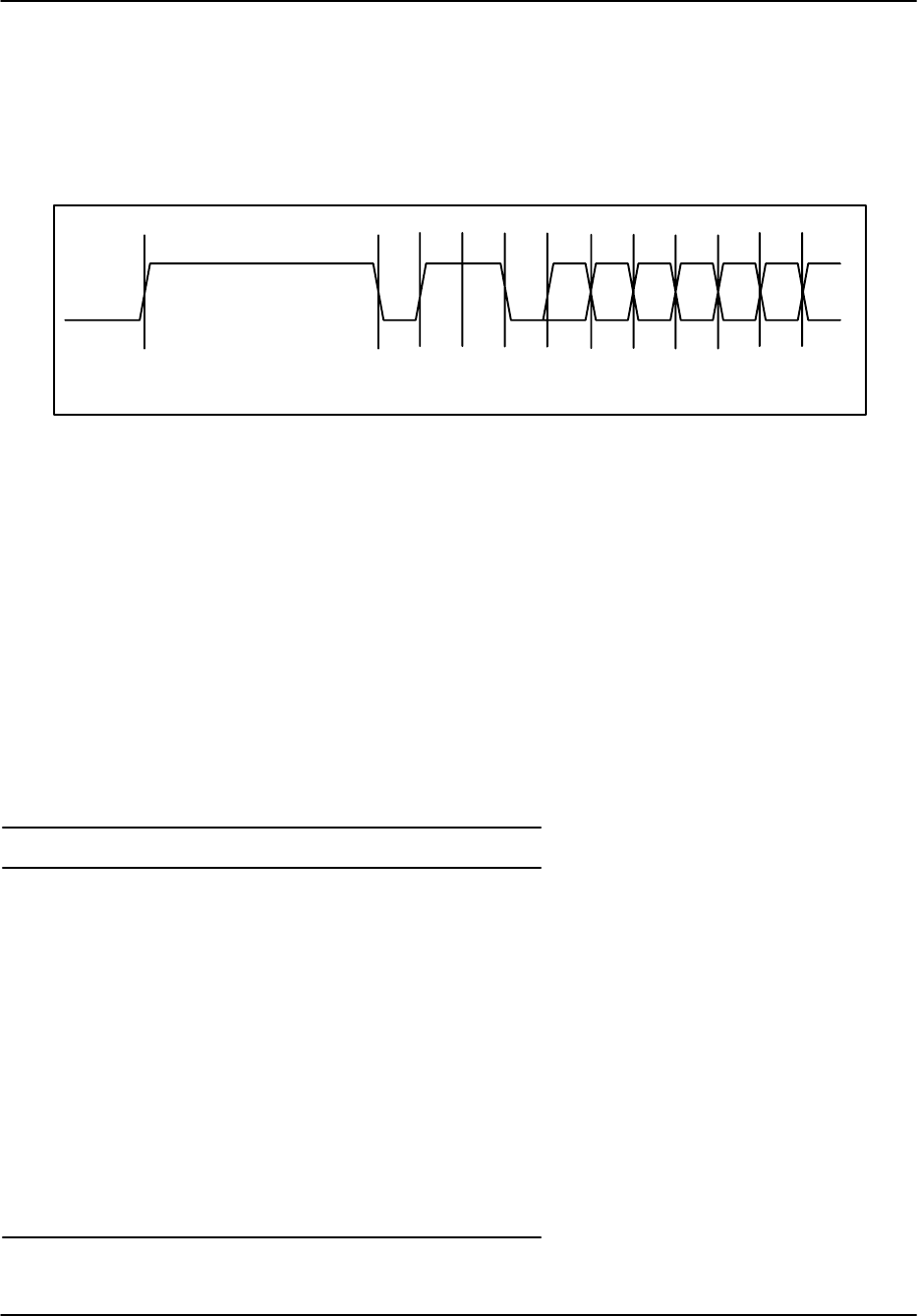

4.2 P+ — Plot Test Pattern 4–3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 General Conventions Within the Plot Commands 4–4 . . . . . . . . . . . . . . . . . . . . . . .

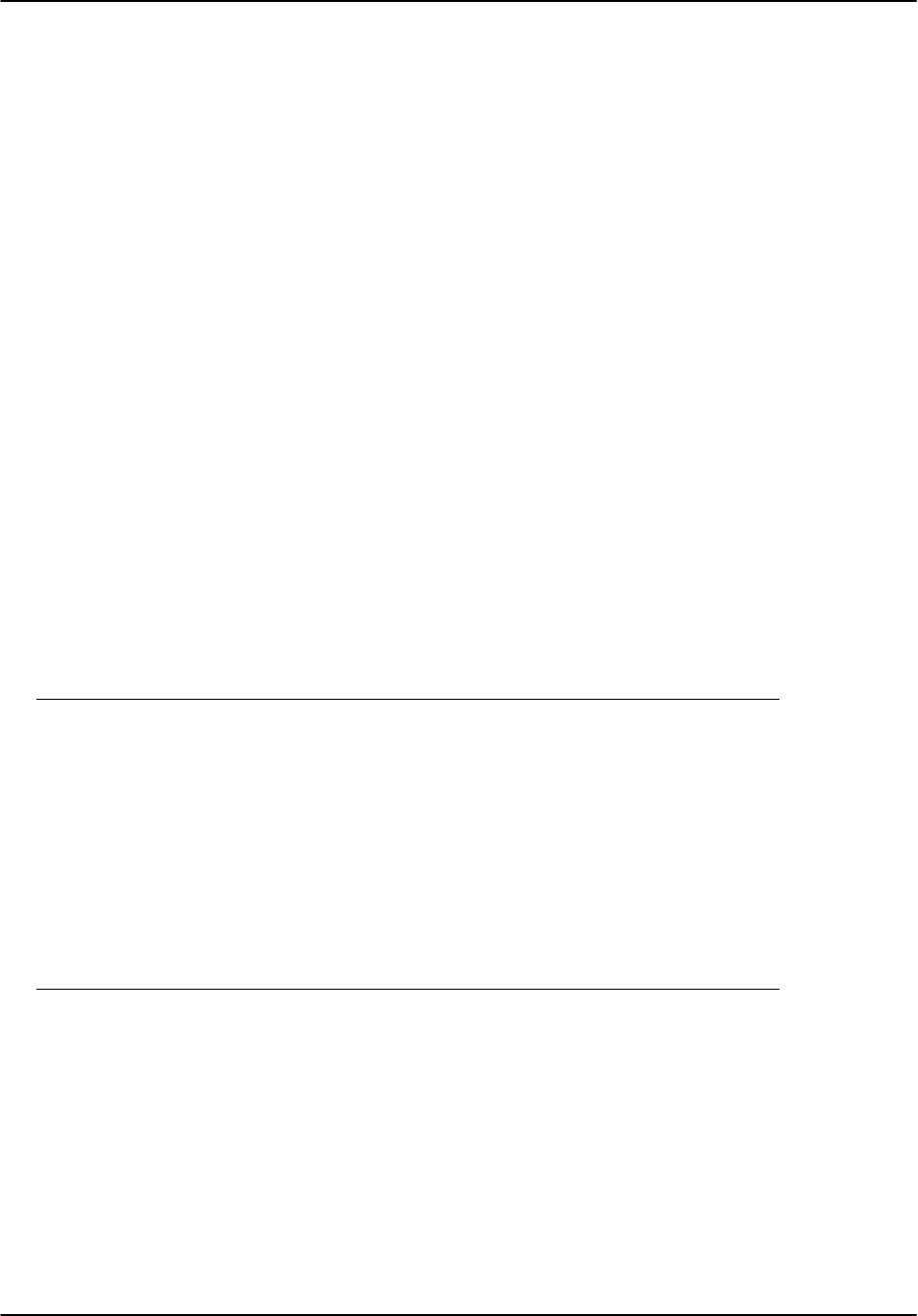

4.4 Pb — Plot Burst Pulse Timing 4–6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.1 Interpreting the Burst Timing Plot 4–6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.2 Available Subcommands Within “Pb” 4–7 . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.3 TTY Information Lines Within “Pb” 4–8 . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.4 Recommended Adjustment Procedures 4–9 . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 Ps — Plot Burst Spectra and AFC 4–11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.1 Interpreting the Burst Spectra Plots 4–11 . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.2 Available Subcommands Within “Ps” 4–13 . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.3 TTY Information Lines Within “Ps” 4–15 . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.4 Computation of Filter Loss 4–17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.5 Recommended Adjustment Procedures 4–20 . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 Pr — Plot Receiver Waveforms 4–23 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.1 Interpreting the Receiver Waveform Plots 4–23 . . . . . . . . . . . . . . . . . . . . . . .

4.6.2 Available Subcommands Within “Pr” 4–25 . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.3 TTY Information Lines Within “Pr” 4–26 . . . . . . . . . . . . . . . . . . . . . . . . . . .

5. Processing Algorithms (draft) 5–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 IF Signal Processing 5–4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.1 FIR (Matched) Filter 5–4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.2 Automatic Frequency Control (AFC) 5–5 . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.3 Burst Pulse Tracking 5–6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.4 Interference Filter 5–7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.5 Large-Signal Linearization 5–9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.6 Correction for Tx Power Fluctuations 5–9 . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Video (“I” and “Q”) Signal Processing 5–11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.1 Time Series 5–11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.2 IIR Clutter Filter for PPP-Mode 5–11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.3 Autocorrelations for PPP-Mode 5–12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.4 Range averaging and Clutter Microsuppression 5–13 . . . . . . . . . . . . . . . . . . .

Table of Contents

RVP8 User’s Manual

12 May 2003

iv

5.2.5 Reflectivity 5–13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.6 Velocity 5–15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.7 Spectrum Width Algorithms 5–15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.8 Signal Quality Index (SQI threshold) 5–16 . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.9 Clutter Correction (CCOR threshold) 5–17 . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.10 Weather Signal Power (SIG threshold) 5–18 . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.11 Signal to Noise Ratio (LOG threshold) 5–18 . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Thresholding 5–19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.1 Threshold Qualifiers 5–19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.2 Adjusting Threshold Qualifiers 5–20 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.3 Speckle Filters 5–21 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 Reflectivity Calibration 5–25 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5 Dual PRT Processing Mode 5–30 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5.1 DPRT-1 Mode 5–30 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5.2 DPRT-2 Mode 5–31 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6 Dual PRF Velocity Unfolding 5–32 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7 Optional Dual Polarization- ZDR, PHIDP, KDP, LDR, ... 5–36 . . . . . . . . . . . . . . . . .

5.7.1 Overview of Dual Polarization 5–36 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.2 Radar System Considerations 5–38 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.3 RVP8 Dual-Channel Receiver Approach 5–40 . . . . . . . . . . . . . . . . . . . . . . . .

5.7.4 Overview of Processing Algorithms 5–42 . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.5 Case 1: Fixed Transmit: Dual-Channel Receiver 5–45 . . . . . . . . . . . . . . . . . .

5.7.6 Case 2: Simultaneous Dual Transmit and Receive (STAR mode) 5–46 . . . . .

5.7.7 Case 3: Alternating H/V Transmit: Single-Channel Receiver 5–47 . . . . . . . .

5.7.8 Case 4: Alternating H/V Transmit: Dual-Channel Receiver 5–48 . . . . . . . . .

5.7.10 KDP Calculation 5–49 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.11 Standard Moment Calculations (T, Z, V, W) 5–50 . . . . . . . . . . . . . . . . . . . .

5.7.12 Thresholding of Polarization Parameters 5–60 . . . . . . . . . . . . . . . . . . . . . . .

5.7.13 Calibration Considerations 5–61 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8 FFT Mode 5–64 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8.1 Overview 5–64 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8.2 FFT Implementation 5–65 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9 Random Phase 2nd Trip Processing 5–70 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.1 Overview 5–70 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.2 Algorithm 5–70 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.3 Tuning for Optimal Performance 5–71 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10 Signal Generator Testing of the Algorithms 5–75 . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10.1 Linear Ramp of Velocity with Range 5–75 . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10.2 Verifying PHIDP and KDP 5–76 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10.3 Verifying RHOH, RHOV, and RHOHV 5–76 . . . . . . . . . . . . . . . . . . . . . . . .

Table of Contents

RVP8 User’s Manual

12 May 2003

v

6. Host Computer Commands 6–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 No-Operation (NOP) 6–2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 Load Range Mask (LRMSK) 6–2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Setup Operating Parameters (SOPRM) 6–4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 Interface Input/Output Test (IOTEST) 6–10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5 Interface Output Test (OTEST) 6–11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6 Sample Noise Level (SNOISE) 6–11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.7 Initiate Processing (PROC) 6–13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.8 Load Clutter Filter Flags (LFILT) 6–21 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.9 Get Processor Parameters (GPARM) 6–22 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.10 Load Simulated Time Series Data (LSIMUL) 6–31 . . . . . . . . . . . . . . . . . . . . . . . . .

6.11 Reset (RESET) 6–33 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.12 Define Trigger Generator Output Waveforms (TRIGWF) 6–33 . . . . . . . . . . . . . . . .

6.13 Define Pulse Width Control Bits and PRT Limits (PWINFO) 6–34 . . . . . . . . . . . . .

6.14 Set Pulse Width and PRF (SETPWF) 6–36 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.15 Load Antenna Synchronization Table (LSYNC) 6–36 . . . . . . . . . . . . . . . . . . . . . . .

6.16 Set/Clear User LED (SLED) 6–38 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.17 TTY Operation (TTYOP) 6–38 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.18 Load Custom Range Normalization (LDRNV) 6–40 . . . . . . . . . . . . . . . . . . . . . . . .

6.19 Read Back Internal Tables and Parameters (RBACK) 6–41 . . . . . . . . . . . . . . . . . . .

6.20 Pass Auxiliary Arguments to Opcodes (XARGS) 6–42 . . . . . . . . . . . . . . . . . . . . . .

6.21 Configure Ray Header Words (CFGHDR) 6–42 . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.22 Configure Interference Filter (CFGINTF) 6–43 . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.23 Set AFC level (SETAFC) 6–44 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.24 Set Trigger Timing Slew (SETSLEW) 6–44 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.25 Hunt for Burst Pulse (BPHUNT) 6–45 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.26 Configure Phase Modulation (CFGPHZ) 6–45 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.27 Set User IQ Bits (UIQBITS) 6–46 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.28 Custom User Opcode (USRINTR and USRCONT) 6–47 . . . . . . . . . . . . . . . . . . . . .

Table of Contents

RVP8 User’s Manual

12 May 2003

vi

A. Software: Basics, Installation and Backup A–1 . . . . . . . . . . . . . . . . . . . . . .

A.1 Overview A–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2 Basics of Login, Logout and Shutdown A–2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.1 Power up procedure A–2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.2 Local and remote login A–2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.3 Default operator and root login passwords A–2 . . . . . . . . . . . . . . . . . . . . . .

A.2.4 Login procedure A–3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.5 Logout procedure A–4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2.6 Poweroff shutdown procedure A–4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3 Software Installation A–5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3.1 When to perform software installation A–5 . . . . . . . . . . . . . . . . . . . . . . . . .

A.3.2 Preparing for the installation A–5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3.3 Installing the system software A–6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.4 System Software Configuration A–10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.4.1 Configuring the softplane.conf file A–11 . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.5 System Backup and Recovery A–17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.5.1 System Backup A–17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.5.2 System Recovery A–21 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.5.3 Transferring a backup file from the RVP8 hard disk A–22 . . . . . . . . . . . . . . .

A.6 Software Upgrade and Support A–24 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.6.1 Where to get software upgrades A–24 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.6.2 When should I upgrade A–24 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.6.3 How should I upgrade A–24 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.6.4 Getting the network upgrade files A–25 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.6.5 Starting the “install” utility A–28 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.6.6 Using the install utility A–29 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.7 Network Basics A–31 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.7.1 Default Out Of The Box Configuration A–31 . . . . . . . . . . . . . . . . . . . . . . . . .

A.7.2 Making Changes to Default Configuration A–32 . . . . . . . . . . . . . . . . . . . . . .

B. RVP8/RCP8 Packaging B–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

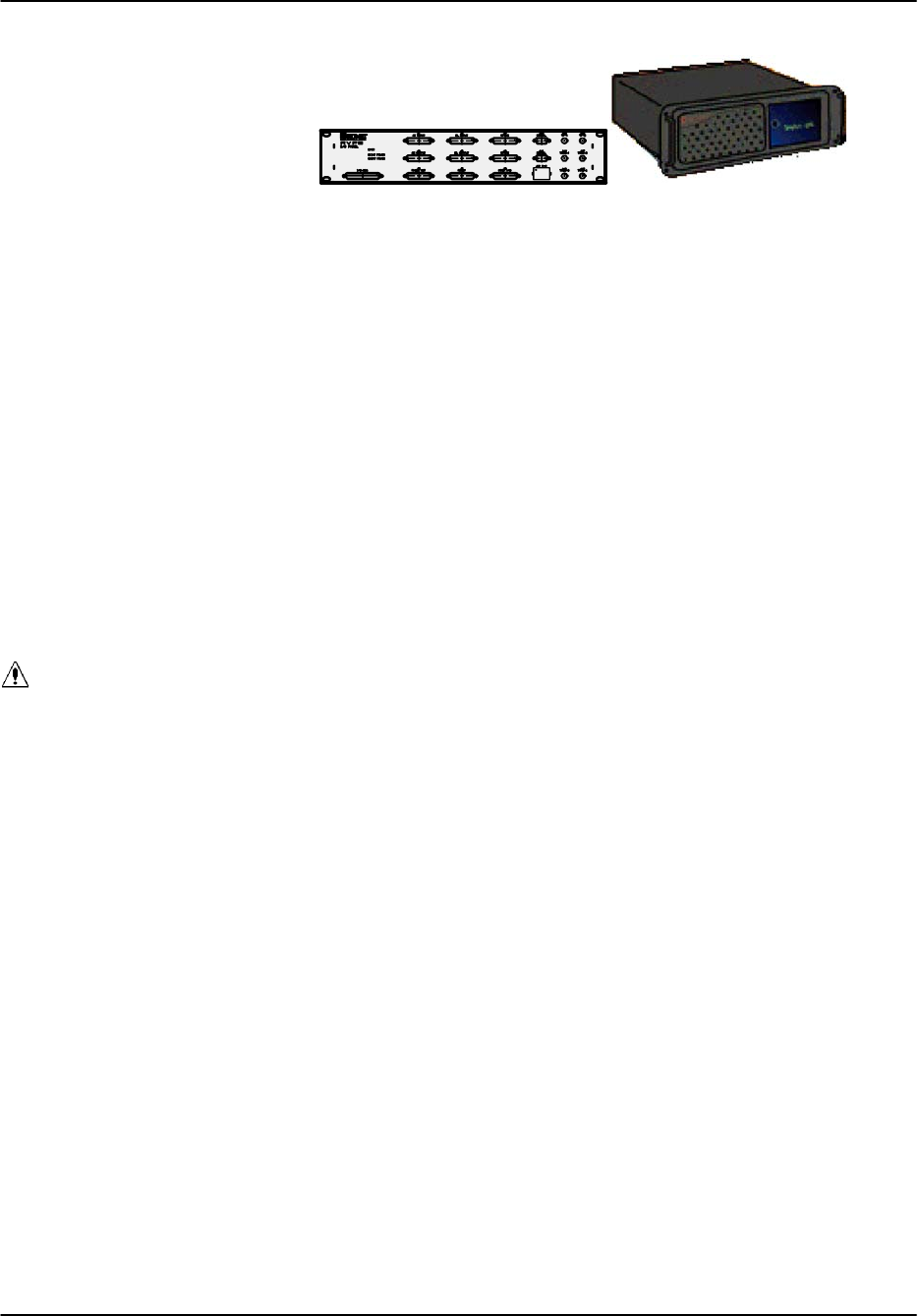

B.1 Main Chassis General Description B–2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1.1 Main Chassis Front Panel B–7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1.2 Main Chassis Back Panel B–8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1.3 Main Chassis Back Panel Power Section B–9 . . . . . . . . . . . . . . . . . . . . . . . .

B.1.4 Main Chassis Back Panel PC I/O Section B–10 . . . . . . . . . . . . . . . . . . . . . . .

B.1.5 Main Chassis Back Panel PCI Card Section B–11 . . . . . . . . . . . . . . . . . . . . .

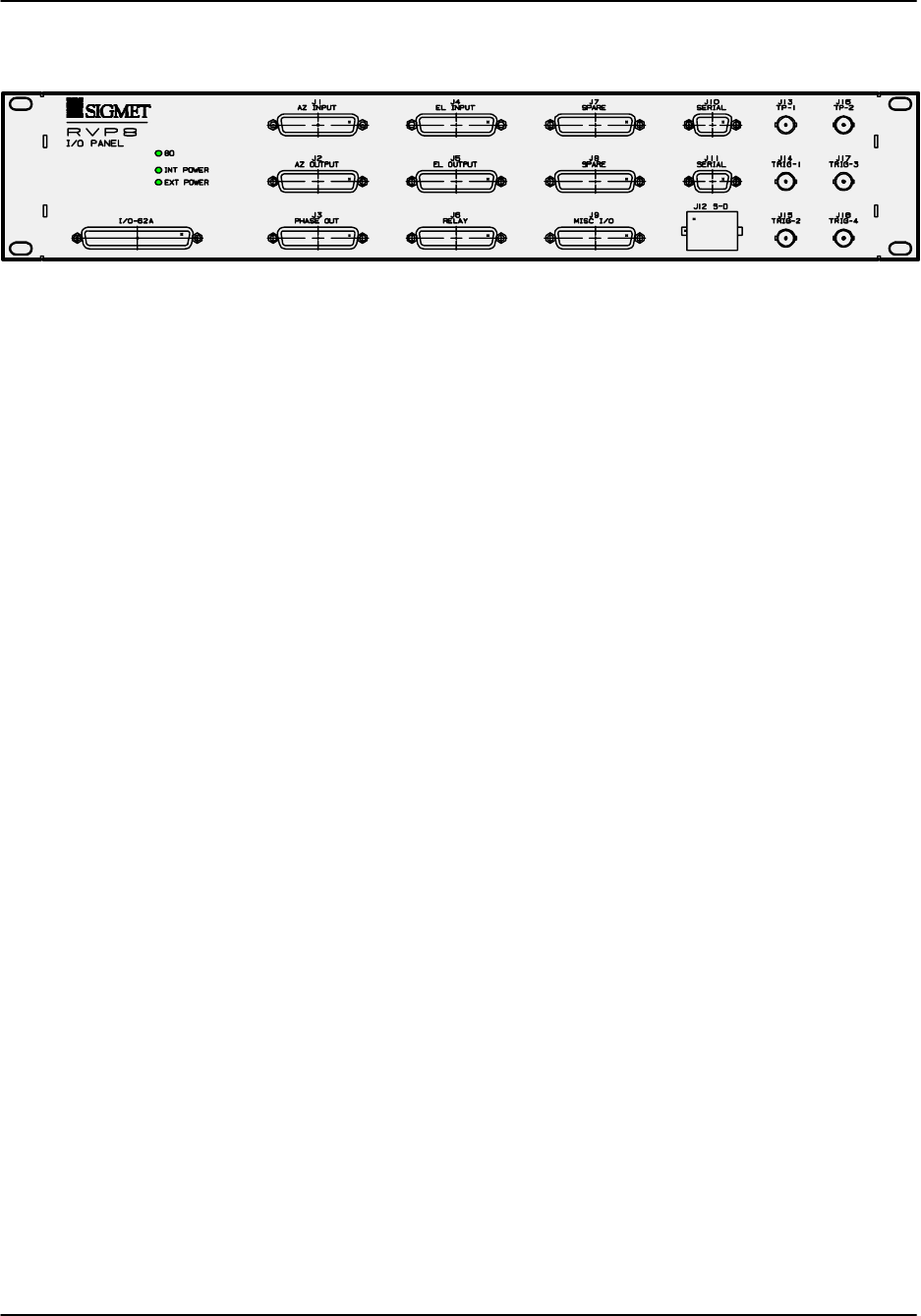

B.2 I/O-62 and Connector Panel B–12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3 IFD Module (RVP8 Only) B–28 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.4 DAFC Module (RVP8 only) B–31 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C. Clutter Filter Characteristics (DRAFT) C–1 . . . . . . . . . . . . . . . . . . . . . . . .

D. References and Credits D–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table of Contents

RVP8 User’s Manual

12 May 2003

vii

E. Installation and Test Procedure (DRAFT) E–1 . . . . . . . . . . . . . . . . . . . . . . .

E.1 Installation Check E–3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.2 Power-Up Check E–4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.3 Setup Terminal E–5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.4 Setup “V” Command (Internal Status) E–6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.5 Setup “Mc” Command (Board Configuration) E–7 . . . . . . . . . . . . . . . . . . . . . . . . .

E.6 Setup “Mp” Command (Processing Options) E–8 . . . . . . . . . . . . . . . . . . . . . . . . . .

E.7 Setup “Mf” Command (Clutter Filters) E–9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.8 Setup “Mt” Command (General Trigger Setup) E–10 . . . . . . . . . . . . . . . . . . . . . . . .

E.9 Initial Setup of Information for Each Pulse Width E–11 . . . . . . . . . . . . . . . . . . . . . .

E.10 Setup “Mb” Command (Burst Pulse and AFC) E–12 . . . . . . . . . . . . . . . . . . . . . . . .

E.11 Setup “M+” Command (Debug Options) E–13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.12 Setup “Mz” Command (Transmitter Phase Control) E–14 . . . . . . . . . . . . . . . . . . . .

E.13 Display Scope Test E–15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.14 Burst Pulse Alignment E–16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.15 Bandwidth Filter Adjustment E–17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.16 Digital AFC Voltage Alignment (Optional) E–18 . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.17 Analog AFC Voltage Alignment (Optional) E–19 . . . . . . . . . . . . . . . . . . . . . . . . . .

E.18 MFC Functional Test and Tuning (Optional) E–21 . . . . . . . . . . . . . . . . . . . . . . . . . .

E.19 AFC Functional Test (Optional) E–22 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.20 Input IF Signal Level Check E–23 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.21 Dynamic Range Check E–24 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.22 Receiver Bandwidth Check E–26 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.23 Receiver Phase Noise Check E–28 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.24 Hardcopy of Final Setups E–29 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.25 IFD Stand-alone SigGen Bench Test E–30 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Index Index–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table of Contents

RVP8 User’s Manual

12 May 2003

viii

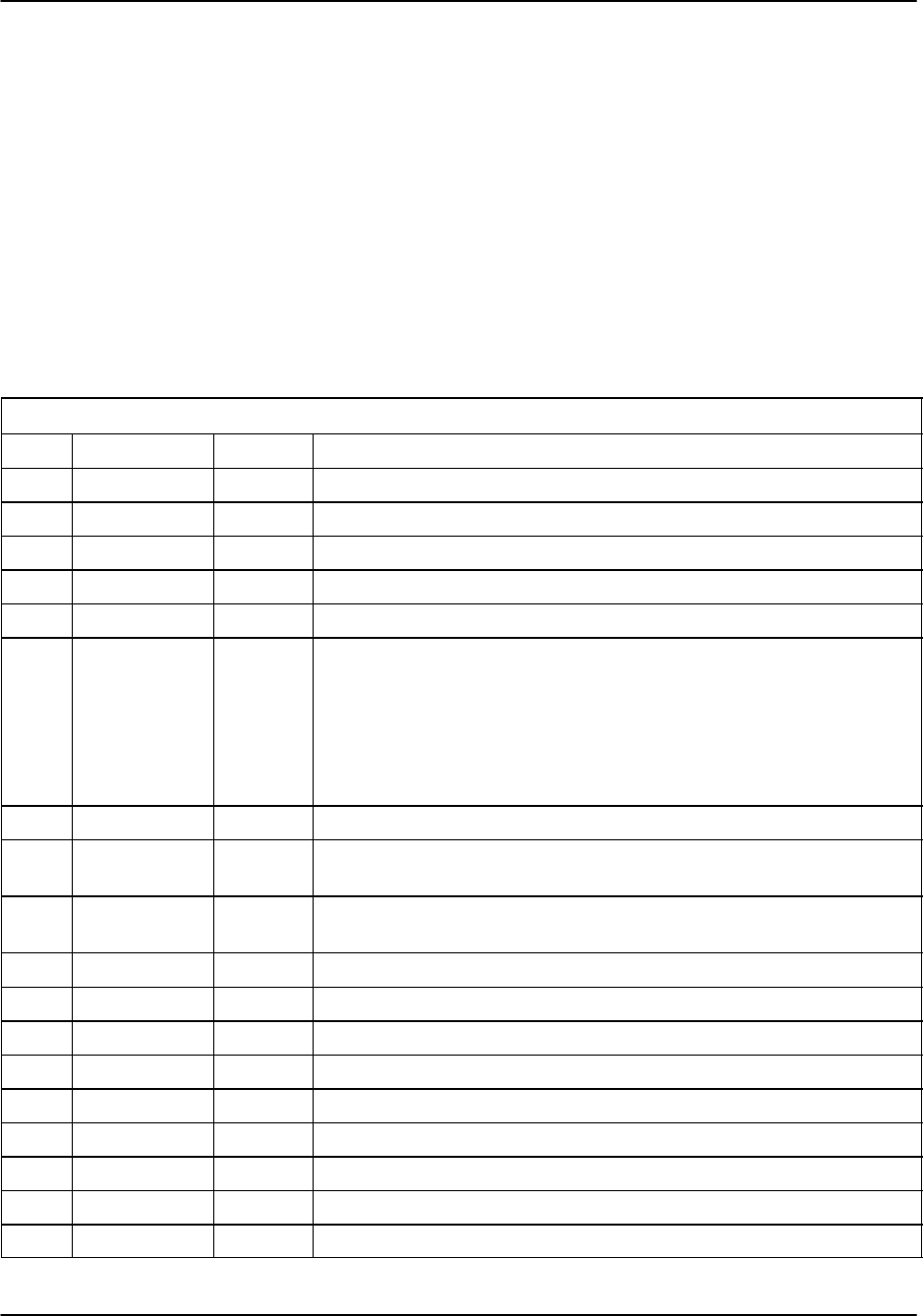

Figures

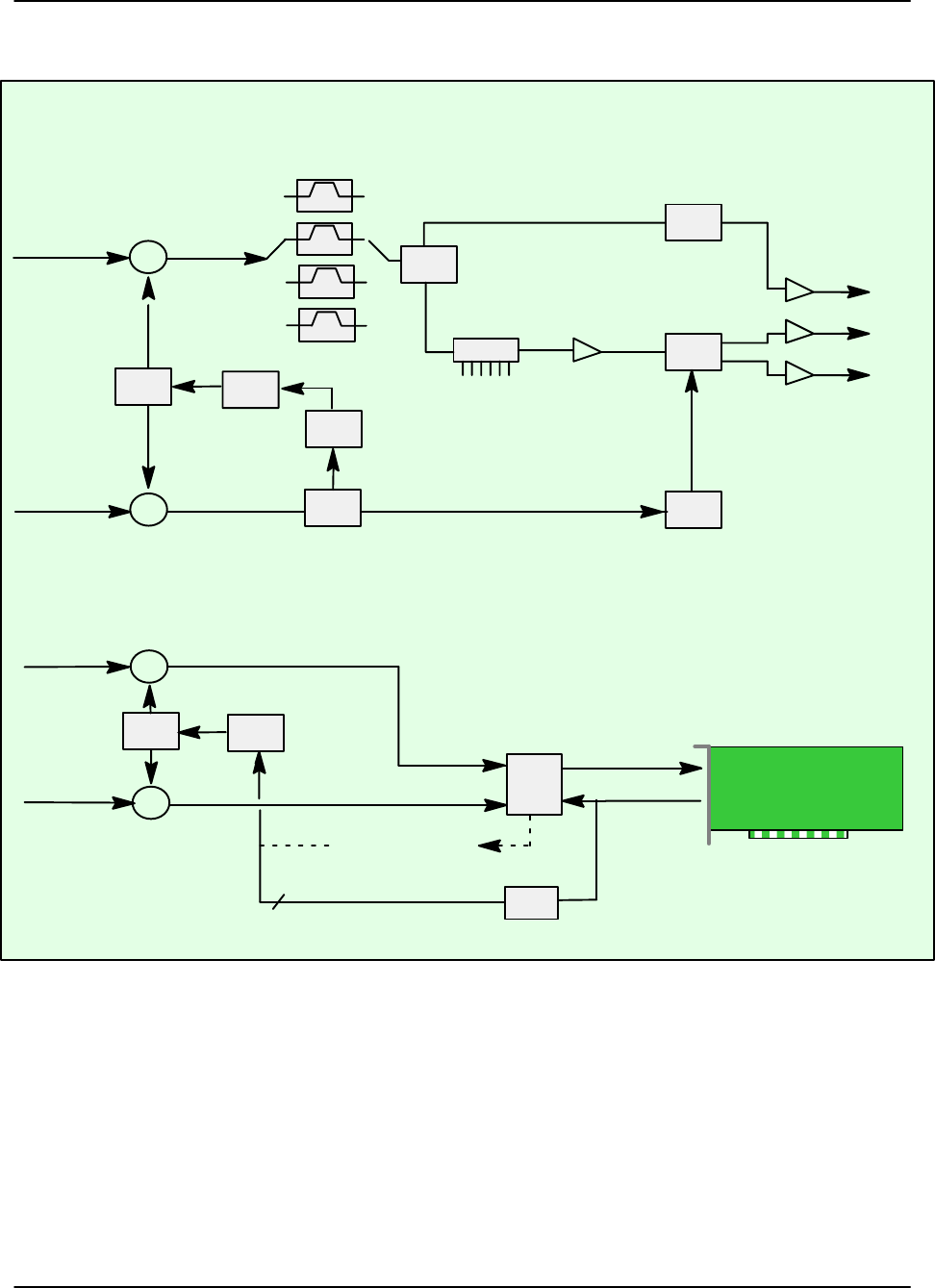

Figure 1–1: Analog vs Digital Receiver for Magnetron Systems 1–19 . . . . . . . . . . . . . .

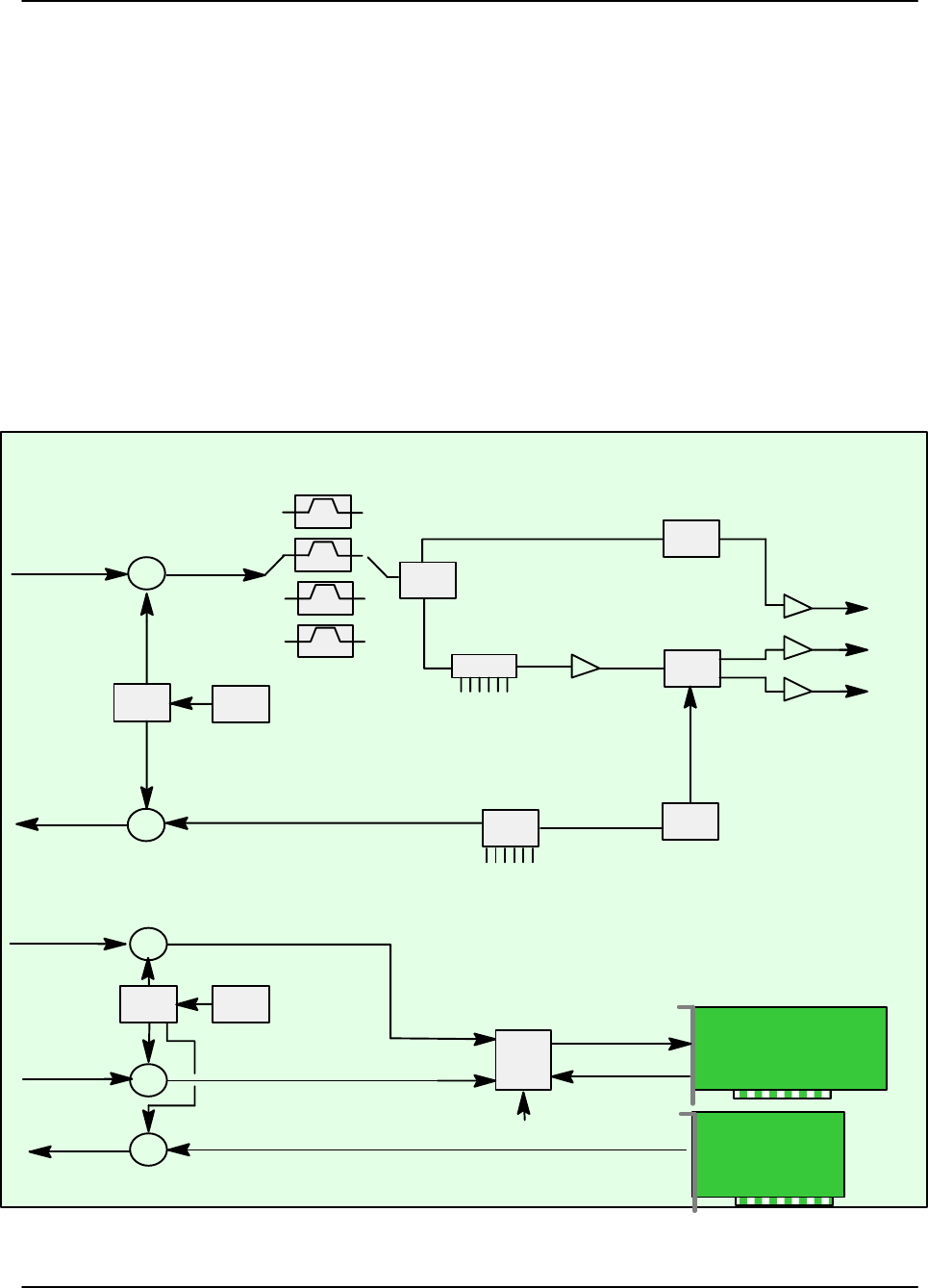

Figure 1–2: Analog vs Digital Receiver for Klystron Systems 1–20 . . . . . . . . . . . . . . . .

Figure 1–3: IF to I/Q Processing Steps 1–23 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 1–4: I/Q Processing for Weather Moment Extraction 1–26 . . . . . . . . . . . . . . . . .

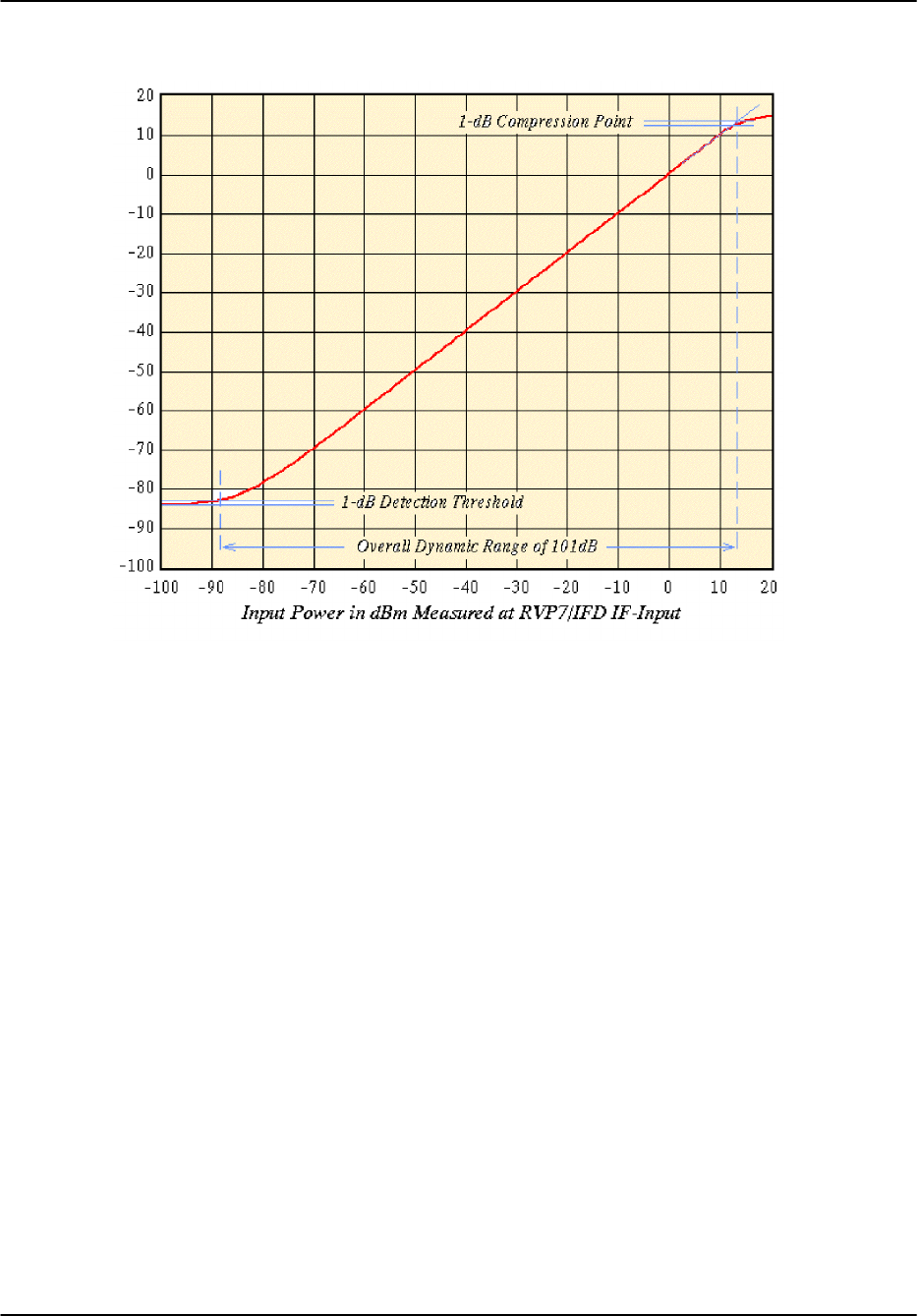

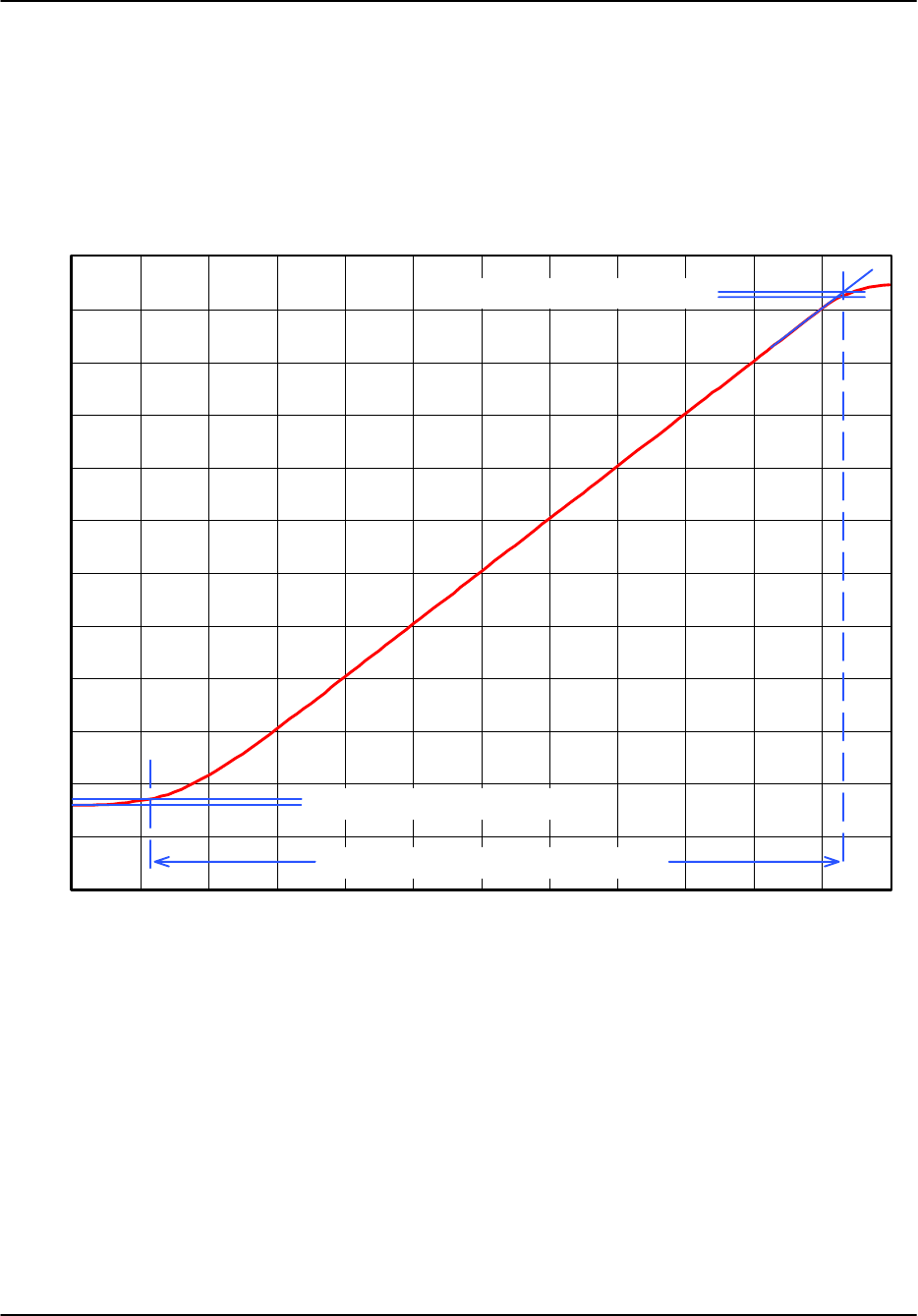

Figure 2–1: Calibration Plot for a Stand-alone 14-Bit IFD 2–10 . . . . . . . . . . . . . . . . . . .

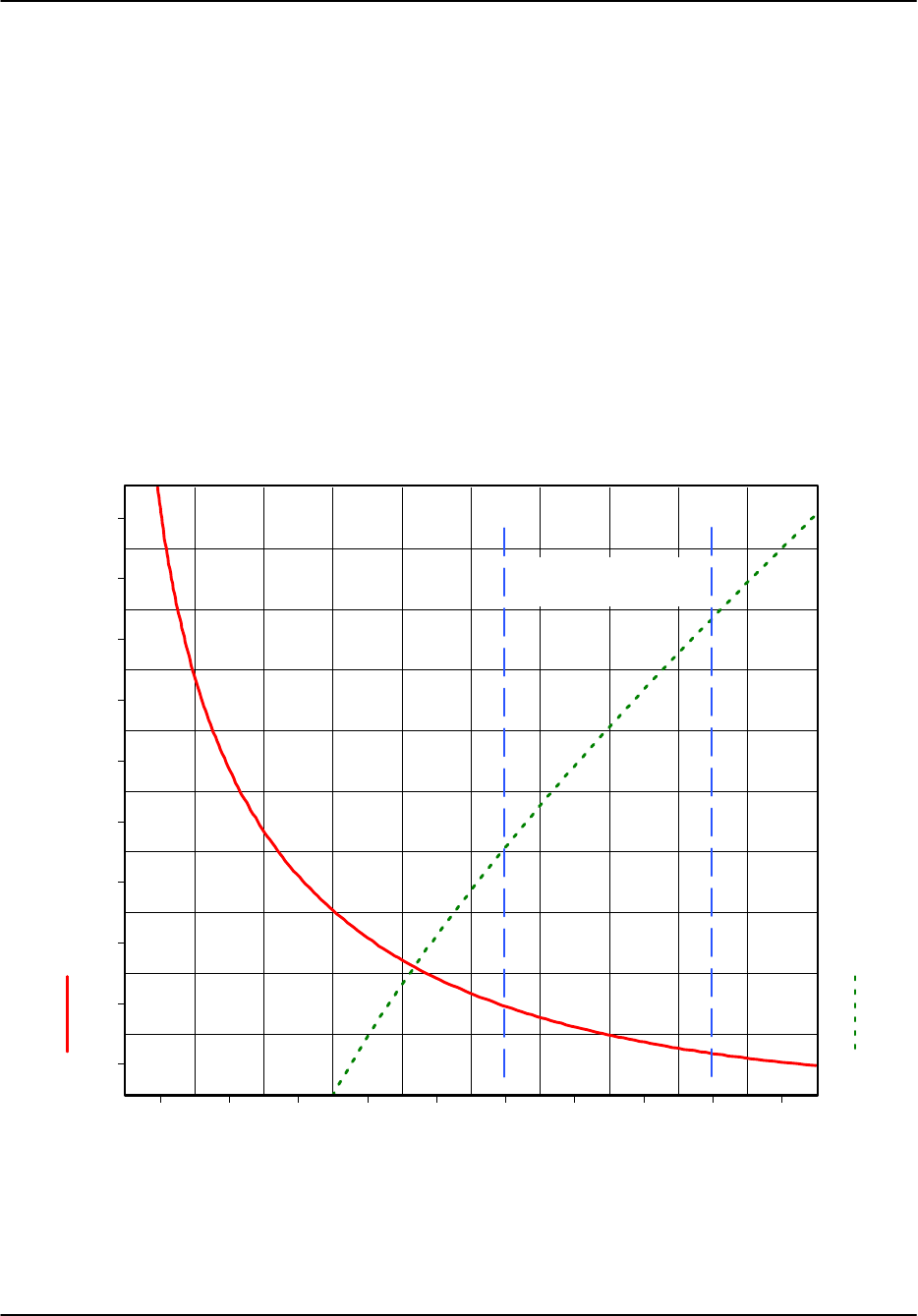

Figure 2–2: Tradeoff Between Dynamic Range and Sensitivity 2–11 . . . . . . . . . . . . . . .

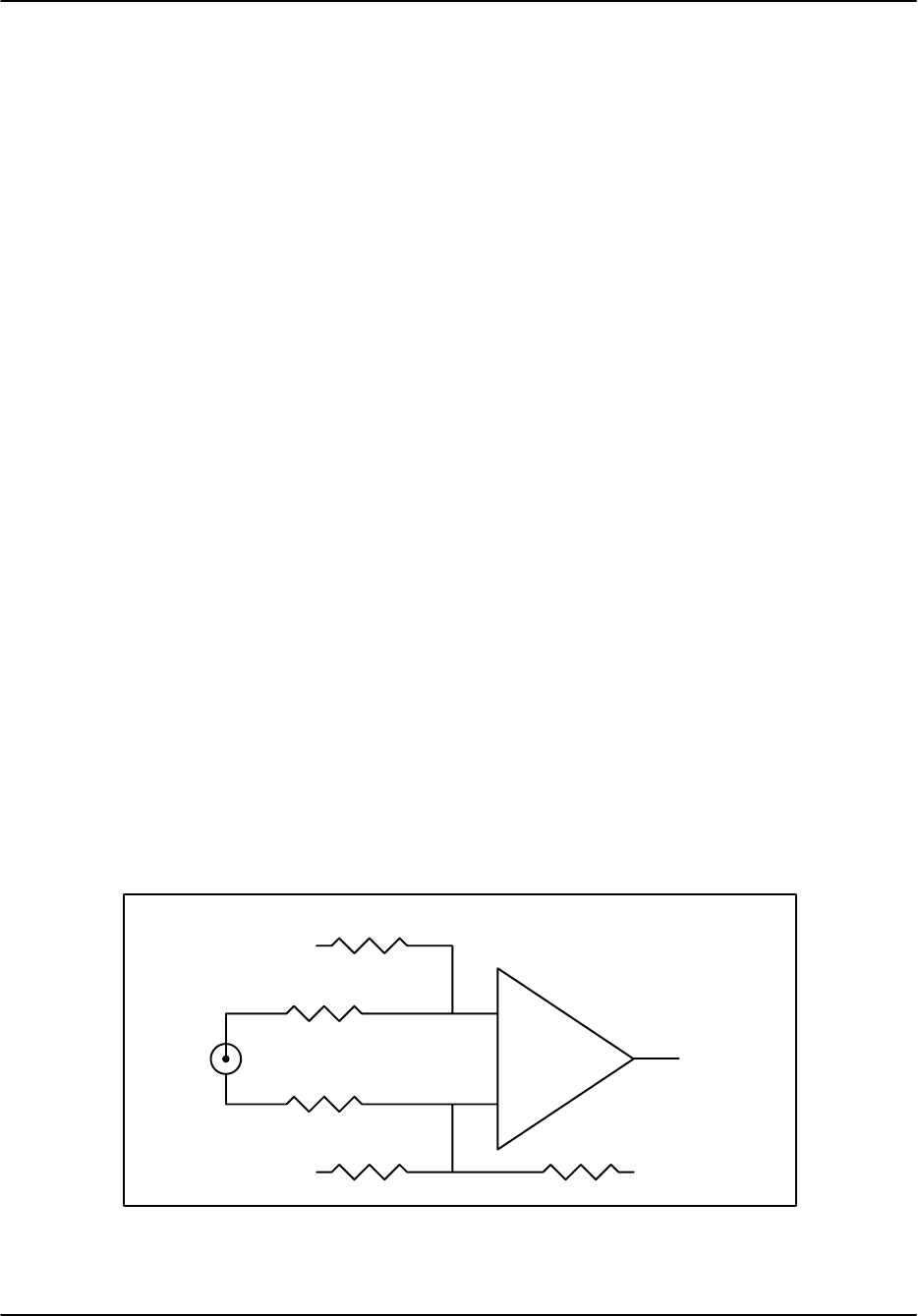

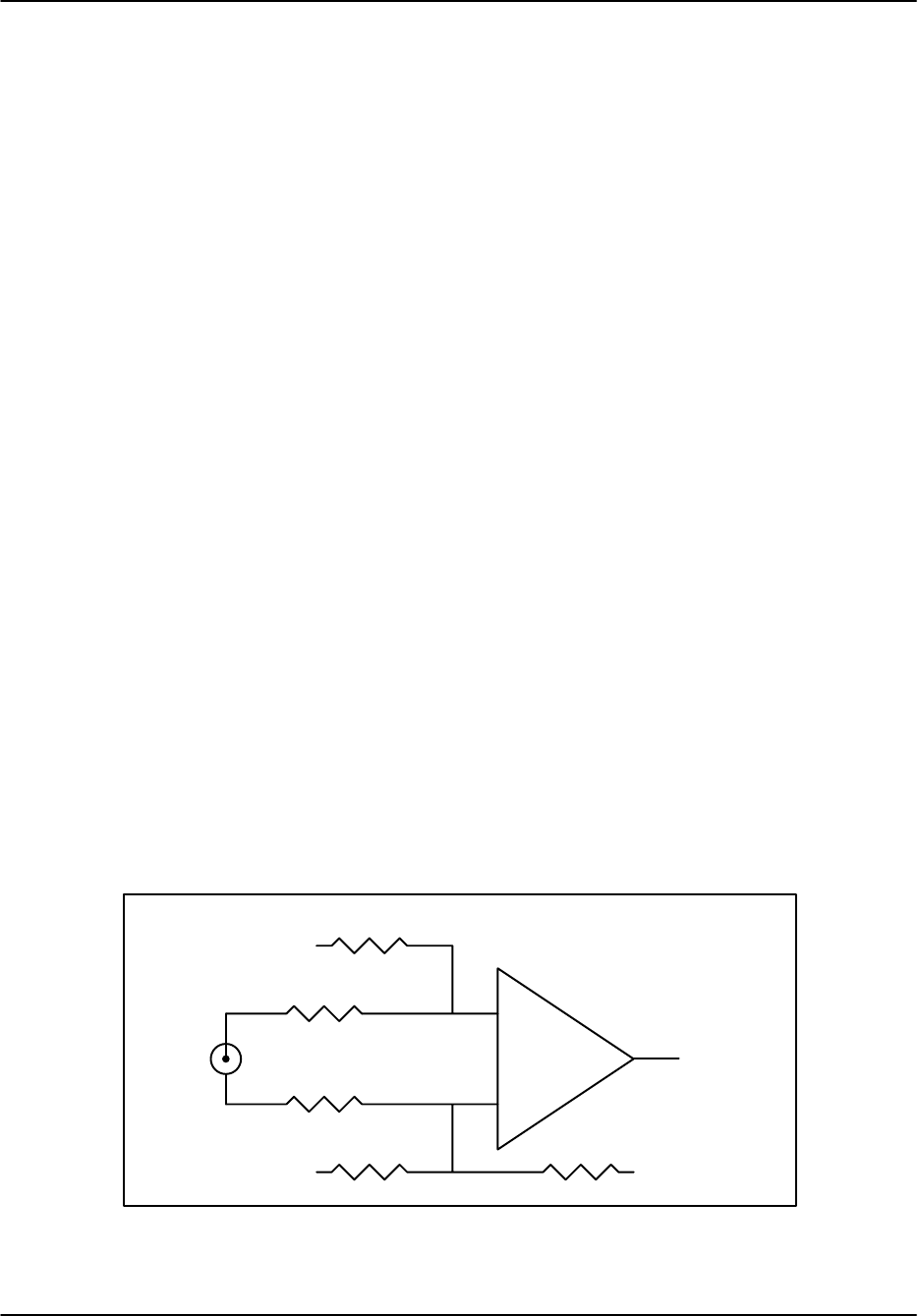

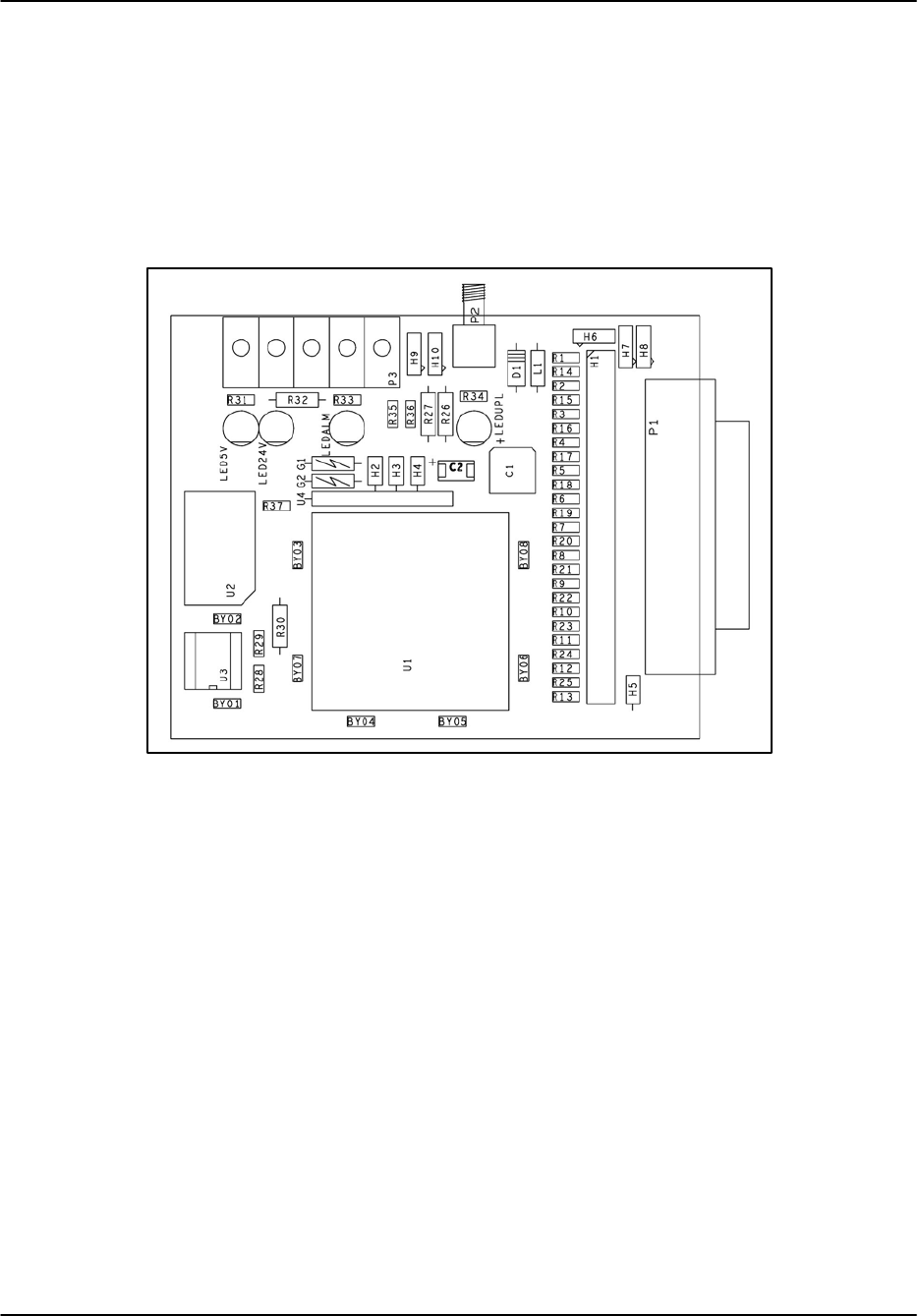

Figure 2–3: Assembly Diagram of the DAFC 2–27 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

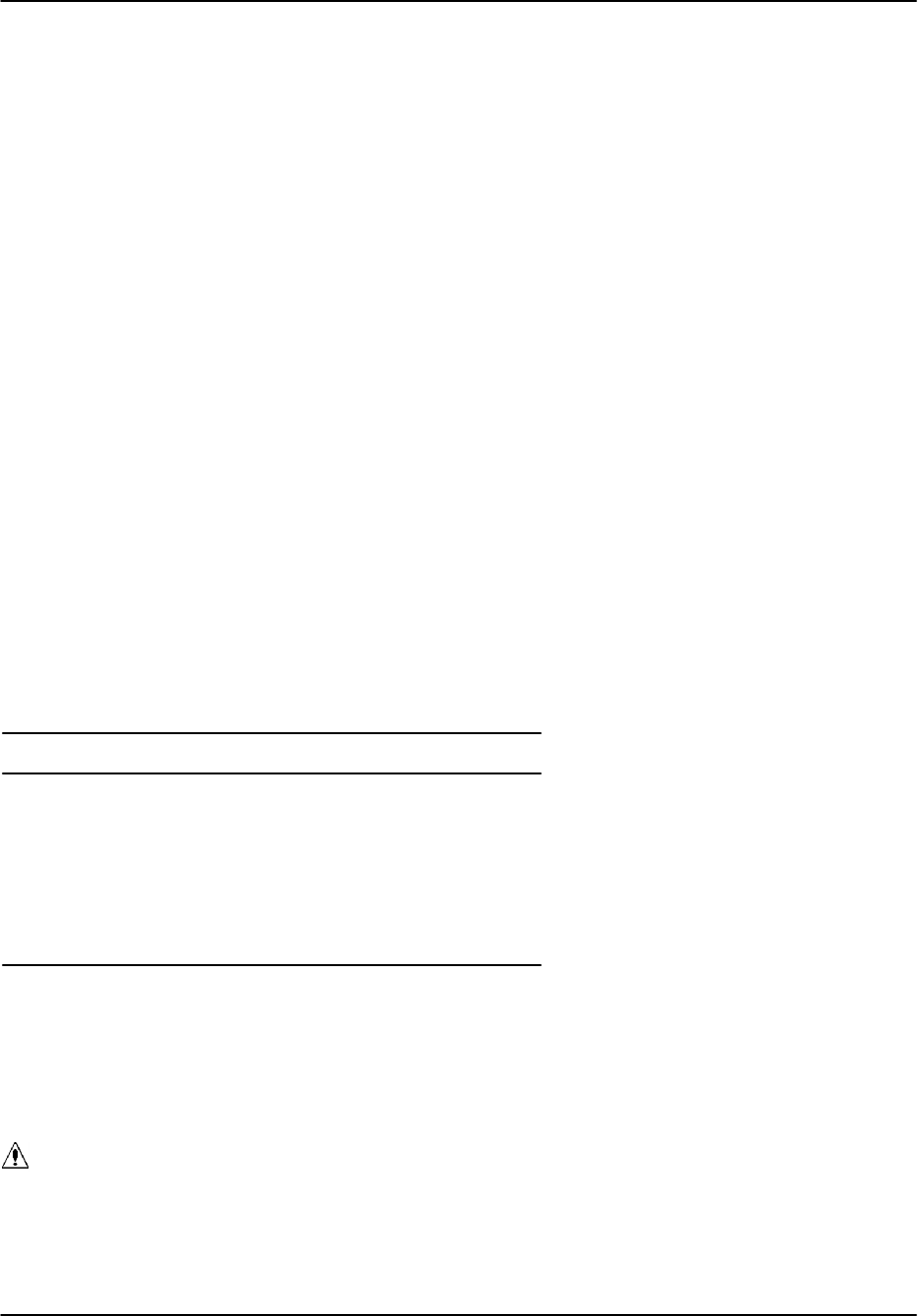

Figure 2–4: Recommended Receiving Circuit for the Coax Uplink 2–32 . . . . . . . . . . . .

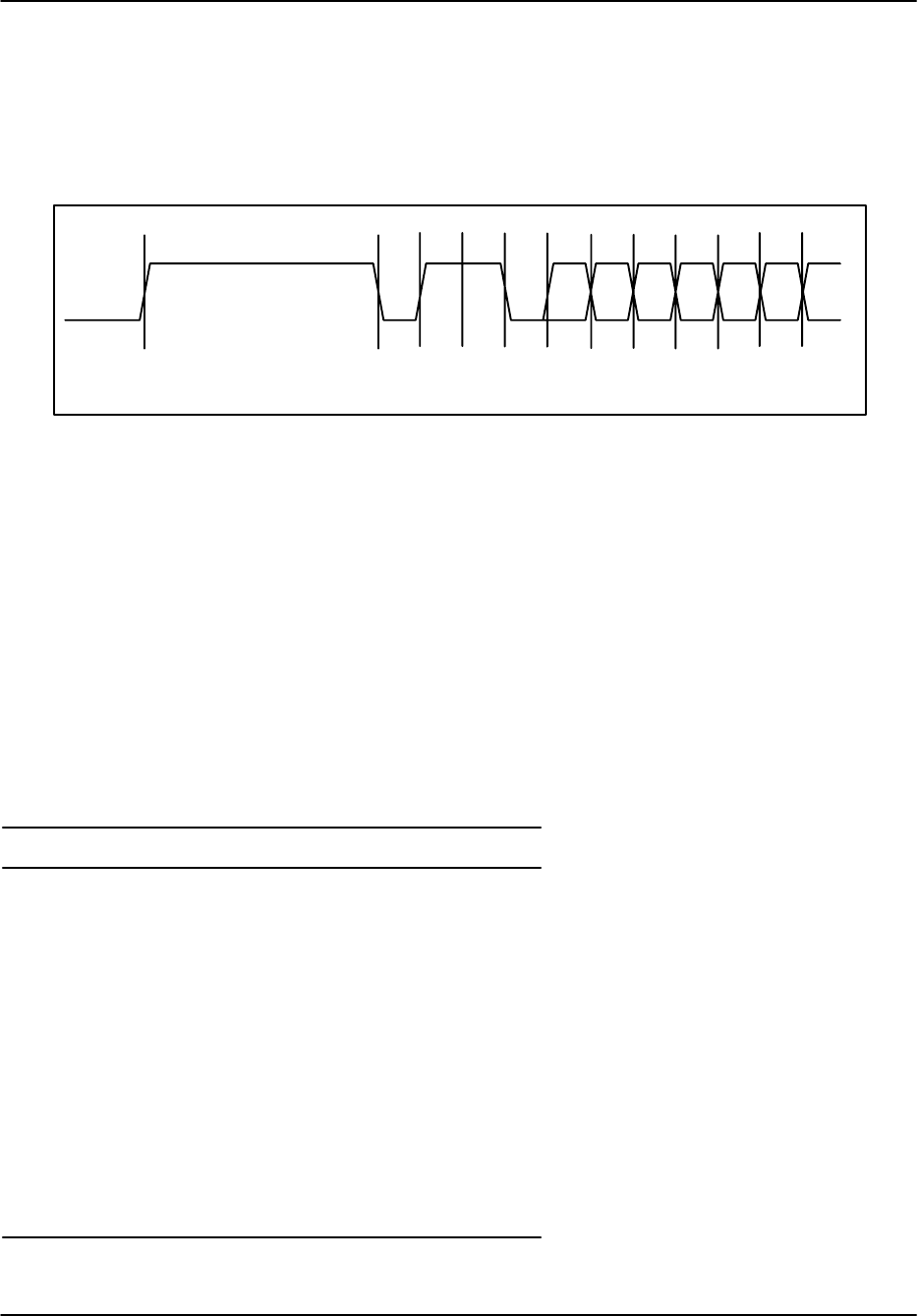

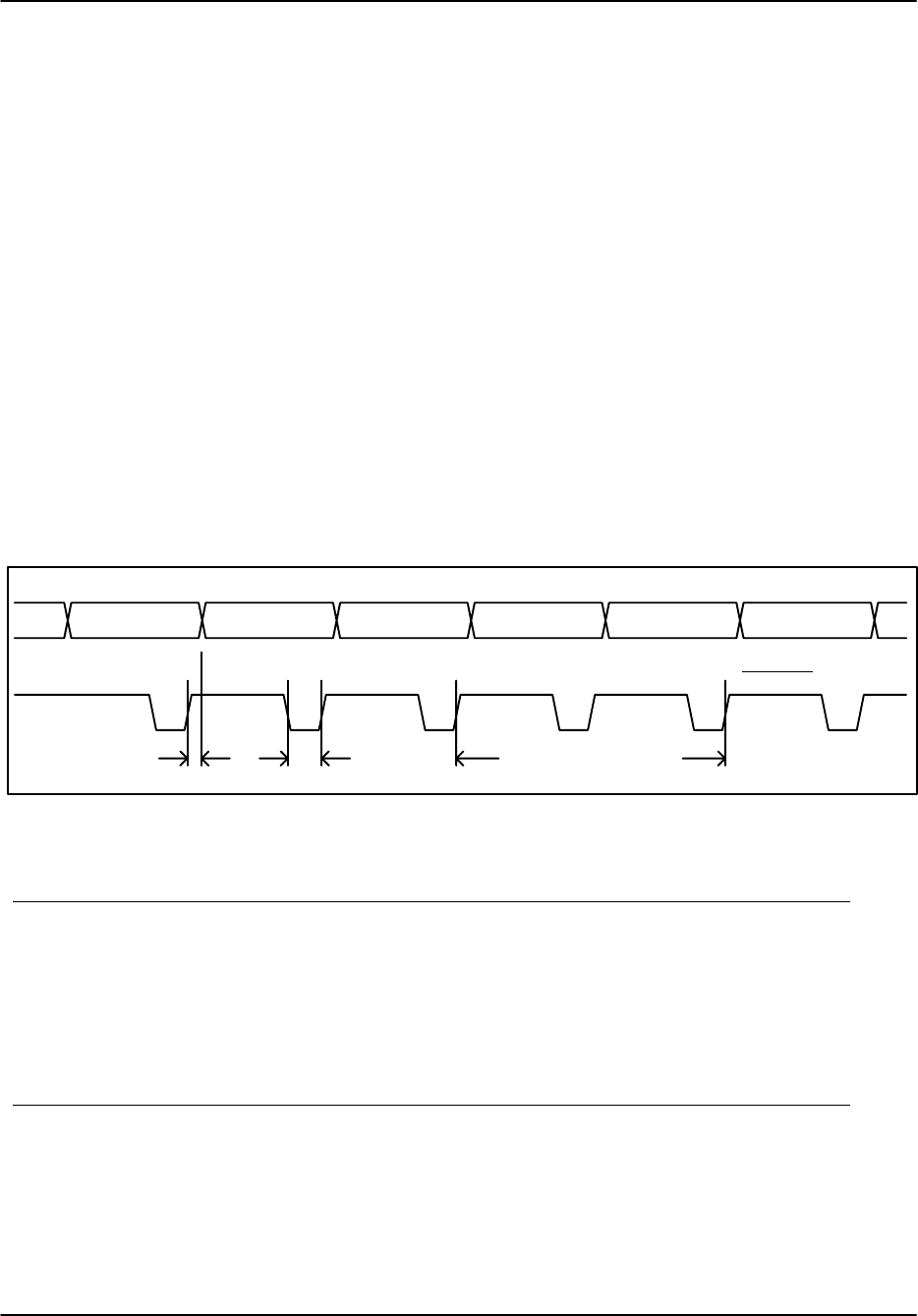

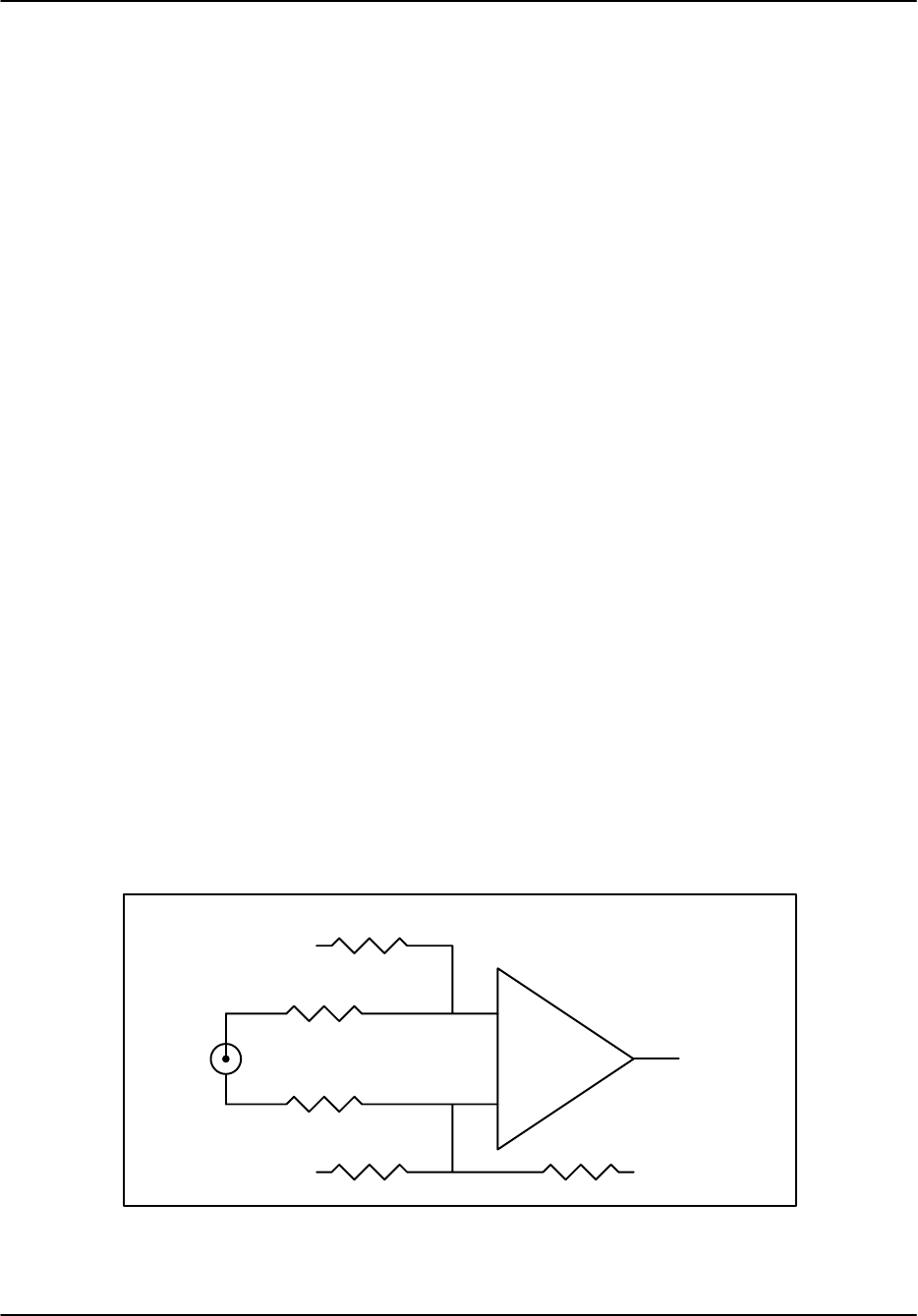

Figure 2–5: Timing Diagram of the IFD Coax Uplink 2–33 . . . . . . . . . . . . . . . . . . . . . .

Figure 2–6: Timing diagram of the (I,Q) Data Stream 2–36 . . . . . . . . . . . . . . . . . . . . . .

Figure 4–1: Oscilloscope Display of Test Pattern 4–3 . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 4–2: Successful Capture of the Transmit Burst 4–6 . . . . . . . . . . . . . . . . . . . . . .

Figure 4–3: Example of a Filter With Excellent DC Rejection 4–11 . . . . . . . . . . . . . . . .

Figure 4–4: Example of a Poorly Matched Filter 4–20 . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 4–5: Example of a Filter With Poor DC Rejection 4–22 . . . . . . . . . . . . . . . . . . .

Figure 4–6: Example of Combined IF Sample and LOG Plot 4–23 . . . . . . . . . . . . . . . .

Figure 4–7: Example of a Noisy High Resolution “Pr” Spectrum 4–25 . . . . . . . . . . . . .

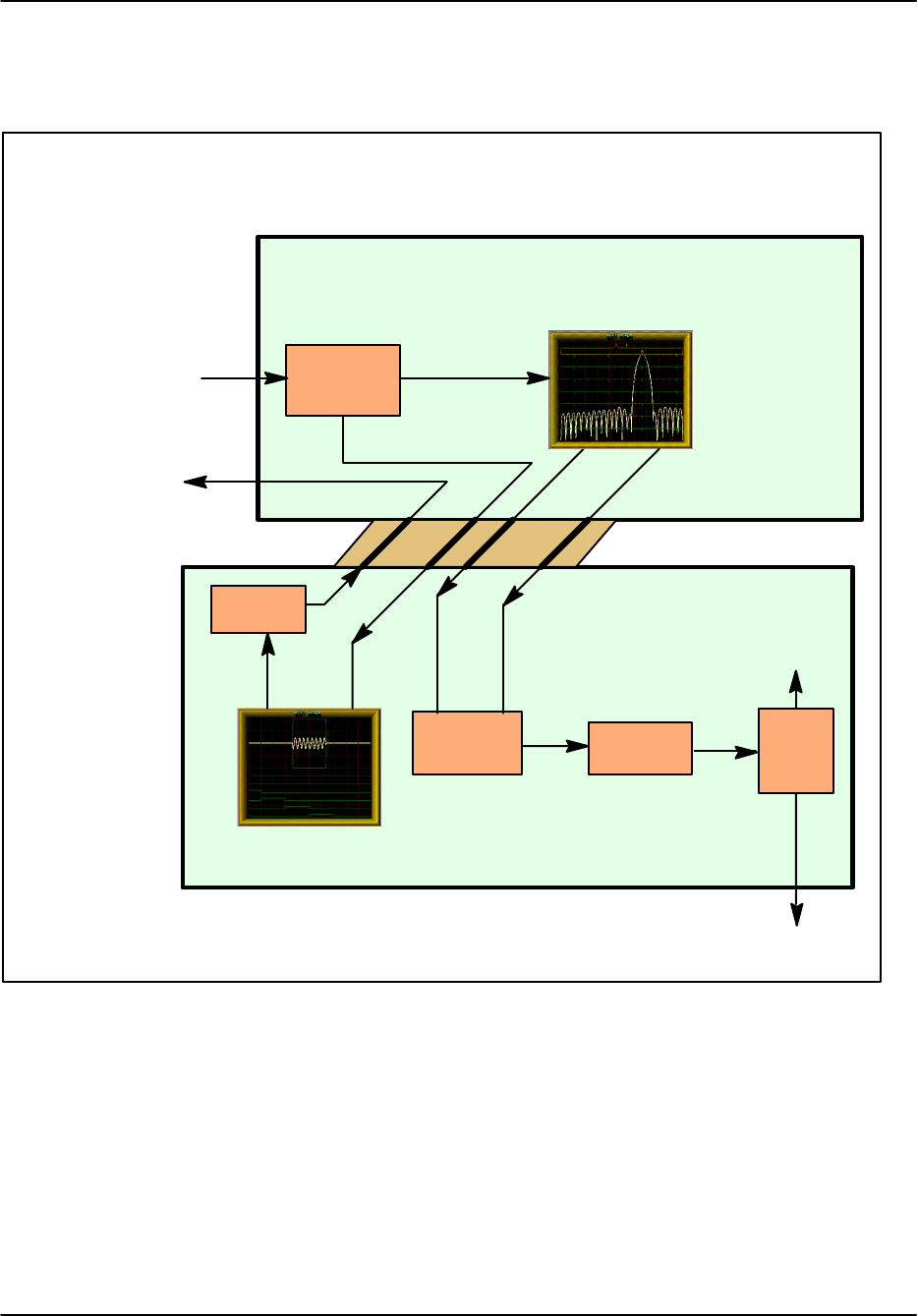

Figure 5–1: Flow Diagram of RVP8 Processing 5–3 . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 5–2: Linearization of Saturated Signals Above +4dBm 5–10 . . . . . . . . . . . . . . .

Figure 5–3: Model Intensity Curve 5–25 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 5–4: Illustration of Losses that Affect LOG Calibration 5–28 . . . . . . . . . . . . . . .

Figure 5–5: Dual PRF Concepts 5–33 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 5–6: Example of Dual PRF Trigger Waveforms 5–35 . . . . . . . . . . . . . . . . . . . . .

Figure 5–7: Dual Receiver Magnetron Case 5–40 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 5–8: Comparison of Pulse Pair and FFT Clutter Filters 5–64 . . . . . . . . . . . . . . .

Figure 5–9: FFT Processing — 50 pulse example 5–66 . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 5–10: Effect of Windowing on FFT Response to Ground Clutter 5–67 . . . . . . . .

Figure 5–11: Example of FFT Clutter Filter in Frequency Domain 5–68 . . . . . . . . . . . .

Figure 5–12: Random Phase Processing Algorithm 5–74 . . . . . . . . . . . . . . . . . . . . . . . .

Figure B–1: Main Chassis- Front Panel B–3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure B–2: Main Chassis- Back Panel B–4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure B–3: Main Chassis- Right Side View B–5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure B–4: Main Chassis Internal Cabling B–6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

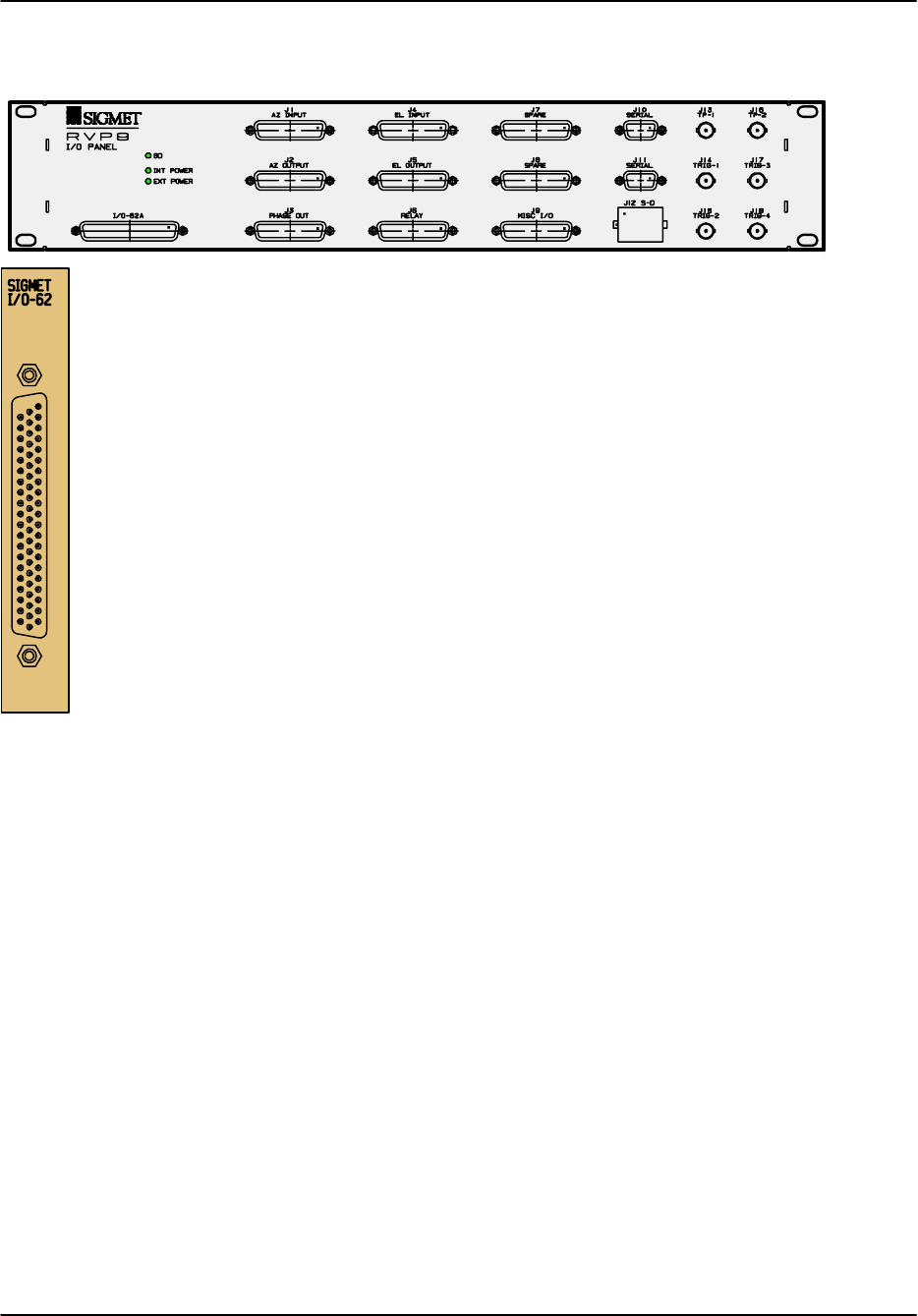

Figure B–5: RVP8 I/O-62 Connector Panel B–14 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure B–6: RCP8 I/O-62 Connector Panel B–15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure B–7: RVP8/IFD Module B–29 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure B–8: IFD Front Panel B–30 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure B–9: View of DAFC Module B–31 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure C–1: 40 dB IIR Clutter Filter Responses C–3 . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure C–2: 50 dB IIR Clutter Filters Responses C–4 . . . . . . . . . . . . . . . . . . . . . . . . . .

Table of Contents

RVP8 User’s Manual

12 May 2003

ix

Tables

Table 1–1: Examples of Dual PRF Velocity Unfolding 1–28 . . . . . . . . . . . . . . . . . . . . .

Table 2–1: Differences Among Versions of the IFD 2–3 . . . . . . . . . . . . . . . . . . . . . . . .

Table 2–2: IFD I/O Connections 2–5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2–3: IFD Toggle Switch Settings 2–6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2–4: IFD LED Indicator Interpretations 2–6 . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2–5: IFD Internal Jumper Settings 2–7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2–6: Direct Connections to RVP8 Main Chassis 2–19 . . . . . . . . . . . . . . . . . . . . . .

Table 2–7: DAFC Protocol Jumper Selections 2–28 . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2–8: Pinout for the CTI “MVSR-xxx” STALO 2–30 . . . . . . . . . . . . . . . . . . . . . . .

Table 2–9: Bit Assignments for the IFD Coax Uplink 2–33 . . . . . . . . . . . . . . . . . . . . . .

Table 5–1: Algebraic Quantities Within the RVP8 Processor 5–2 . . . . . . . . . . . . . . . . .

Table 5–2: Algorithm Results for +16dB Interference 5–8 . . . . . . . . . . . . . . . . . . . . . .

Table 5–3: Algorithm Results for +26dB Interference 5–9 . . . . . . . . . . . . . . . . . . . . . .

Table 6–2: RVP8 Status Output Words 6–22 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table B–1: J1 “AZ INPUT” B–16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table B–2: J2 “AZ OUTPUT” B–17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table B–3: J3 RVP8: “PHASE OUT”; RCP8 “CONTROL” B–18 . . . . . . . . . . . . . . . . .

Table B–4: J4 “EL INPUT” B–19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table B–5: J5 “EL OUTPUT” B–20 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table B–6: J6 “RELAY” B–21 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table B–7: J7: RVP8 “SPARE”; RCP8 “BITE 19:0” B–22 . . . . . . . . . . . . . . . . . . . . . . .

Table B–8: J8: RVP8 “SPARE”; RCP8 “ANALOG IN” B–23 . . . . . . . . . . . . . . . . . . . . .

Table B–9: J9 RVP8: “MISC I/O” ; RCP8: “PED/STATUS” B–24 . . . . . . . . . . . . . . . . .

Table B–10: J10 “SERIAL” B–25 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table B–11: J11 “SERIAL” B–25 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table B–12: J12 “S–D” B–26 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table B–13: RVP8 BNC Connector Pin Assignments B–27 . . . . . . . . . . . . . . . . . . . . . .

Table B–14: RCP8 BNC Connector Pin Assignments B–27 . . . . . . . . . . . . . . . . . . . . . .

Table C–1: Doppler 40dB Clutter Filter Coefficients C–1 . . . . . . . . . . . . . . . . . . . . . .

Table C–2: Doppler 50dB Clutter Filter Coefficients C–2 . . . . . . . . . . . . . . . . . . . . . .

Preface

RVP8 User’s Manual

April 2003

x

Hardware Limited Warranty

SIGMET, Inc. warrants its IRIS hardware (RVP8 and RCP8) to function according to the

hardware User’s Manual documentation for a period of one year following delivery. In the event

of a failure during the warranty period, the customer should notify SIGMET to obtain a Return

Authorization. Upon receiving the Return Authorization from SIGMET, the customer ships the

failed unit to SIGMET by pre-paid freight. SIGMET, at its option, will repair or replace the

defective unit within 30 days and return the unit to the customer.

Damage caused by fire, flood, lightning, or other catastrophe, and damage caused by misuse or

abuse are not covered by this warranty.

In no event shall SIGMET, Inc. be liable for any direct, indirect, special, incidental, or

consequential damages arising out of the use or inability to use the hardware or

documentation provided by SIGMET, Inc. SIGMET, Inc. makes no warranty, either

express or implied, with respect to any of the hardware or documentation, as to the quality,

performance, merchantability, or fitness for a particular purpose.

Preface

RVP8 User’s Manual

April 2003

xi

Preface

This manual provides technical information on the RVP8 digital receiver and Doppler signal

processor.

About This Manual

This manual is used primarily by engineers for installation and troubleshooting, or by users

interested in understanding the signal processing features, algorithms, and control and data

formats.

Chapter 1, Introduction and Specifications, describes the major features of the RVP8 signal

processor and gives its technical specifications.

Chapter 2, Hardware Installation, discusses the electrical issues involved with installing the

RVP8 processor and IFD receiver module. This includes power supply connections, radar

analog and digital signal interfaces and computer interface connections. Software installation is

covered in a separate Appendix.

Chapter 3, TTY Nonvolatile Setups, continues the installation discussion by describing how to

use the local TTY to configure the actual operation of the RVP8. This includes a detailed

description of the (approximately one hundred) setup parameters that affect the operation of the

RVP8.

Chapter 4, Plot-Assisted Setups, completes the installation discussion by using the oscilloscope

plotting modes to configure and align the radar receiver, and measure its performance.

Chapter 5, Processing Algorithms, gives mathematical descriptions of the processing algorithms

implemented in the RVP8 signal processor. This information can be useful to those writing their

own interface to the RVP8, or for those who want to learn more about the internal workings of

the signal processor.

Chapter 6, Host Computer Commands, contains a description of the digital commands that the

host computer must use to set up and control the RVP8 processor. The introductory section

discusses processor I/O in general, and gives an overview of how to set up the RVP8 for

recording data. Each command is then detailed in subsequent sections.

The appendixes give information on software installation and backup, the RVP8 standard

chassis, and clutter filter characteristics.

Preface

RVP8 User’s Manual

April 2003

xii

Where to Find More Information

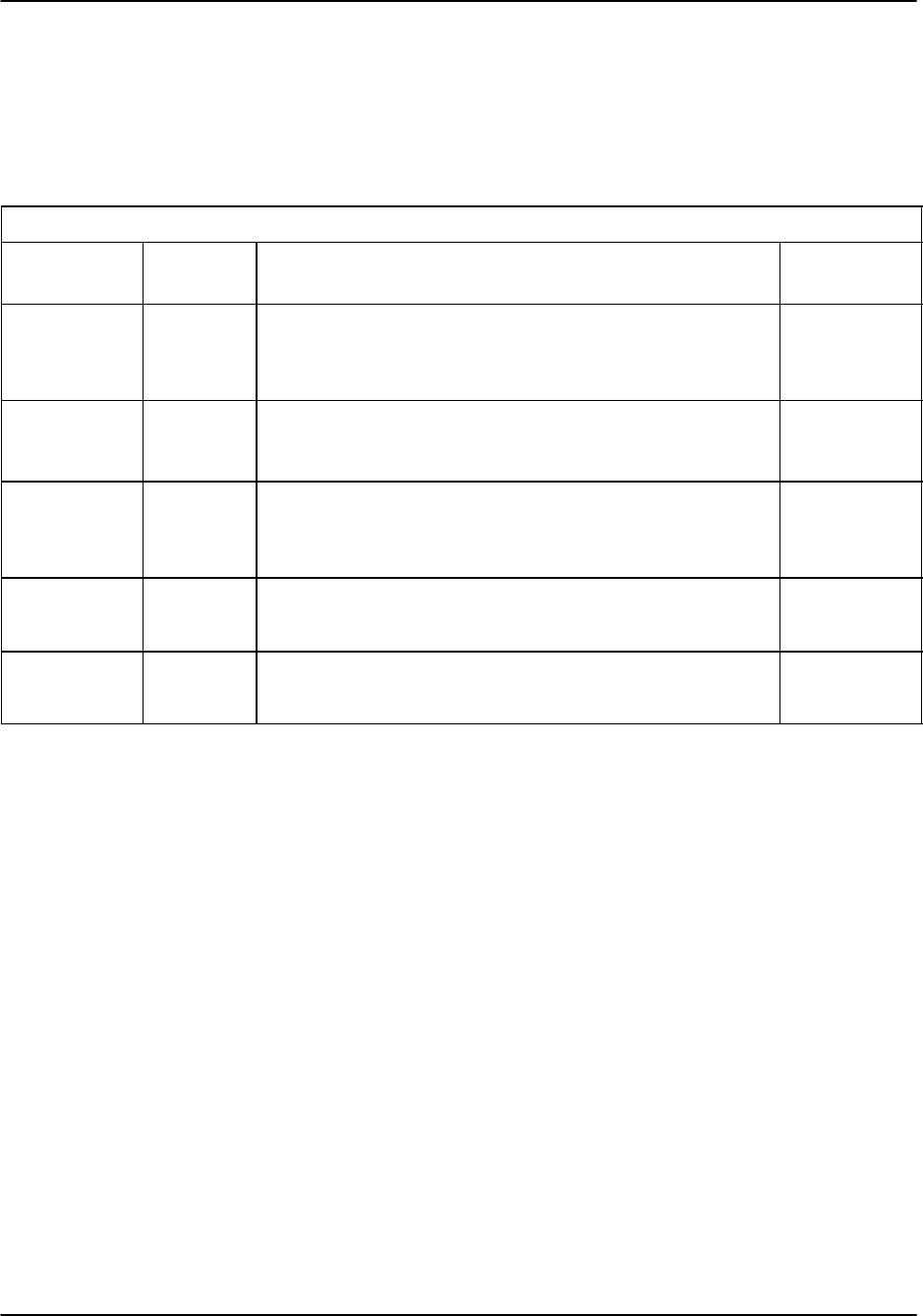

The following manuals are also available from SIGMET, Inc.:

IRIS

Installation Manual Describes the procedures for installing and upgrading IRIS and

the specific hardware and software configuration for your

facility.

IRIS

Radar Manual

Describes the IRIS/Radar software. This manual is for radar

operators.

IRIS

Product & Display Manual Describes the IRIS/Analysis product generation software and the

IRIS/Display software.

IRIS

Utilities Manual Describes the utility programs for system alignment, calibration,

installation and testing.

IRIS

Programmer’s Manual Describes the data formats and library routines used by IRIS.

This manual is for programmers who want to access IRIS data or

interface to IRIS processes.

The RCP8

User’s Manual Describes the installation, operation and technical details of the

Radar Control Processor. The RCP8 is an interface between the

IRIS software and miscellaneous hardware such as the antenna

and transmitter.

SIGMET, Inc. encourages you to send your comments and/or corrections to:

SIGMET, Inc.

2 Park Drive, Suite 1

Westford, Massachusetts 01886

USA

FAX (978)692–9575

EMAIL support@sigmet.com

Documentation Conventions

The following conventions are used throughout this manual:

prompt Some features of the RVP8 operate by displaying questions and

waiting for you to type an answer. The text of prompts is

displayed in bold, monospaced type.

This margin icon indicates a note that may be of interest to the

reader.

This margin icon indicates a note that is important to the reader.

This margin icon indicates a caution or warning to the reader.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–1

1. Introduction and Specifications

The RVP8 Lineage

SIGMET Inc. has a 20-year history of supplying innovative, high-quality signal processing

products to the weather radar community. The history of SIGMET products reads like a history

of weather radar signal processing:

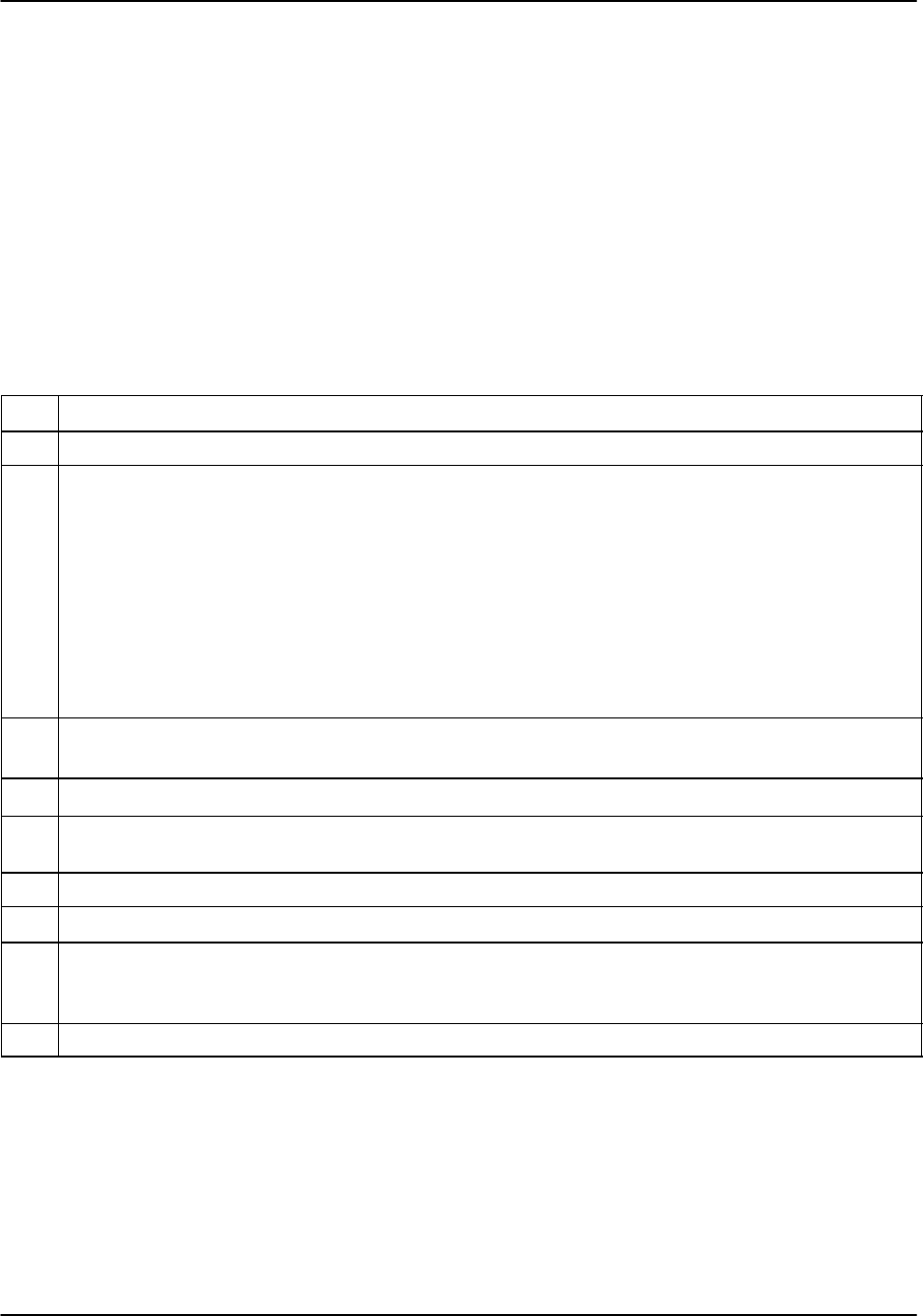

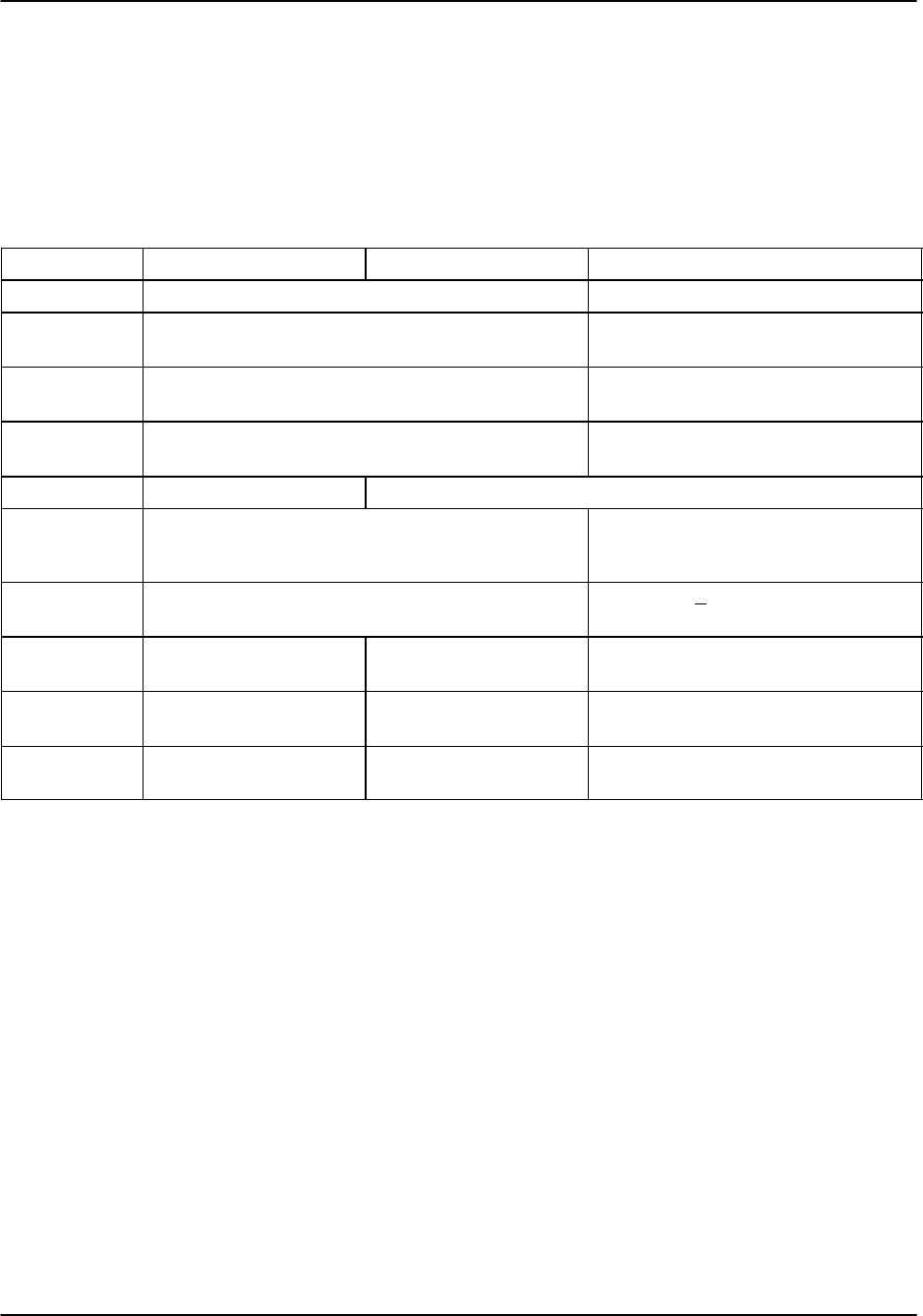

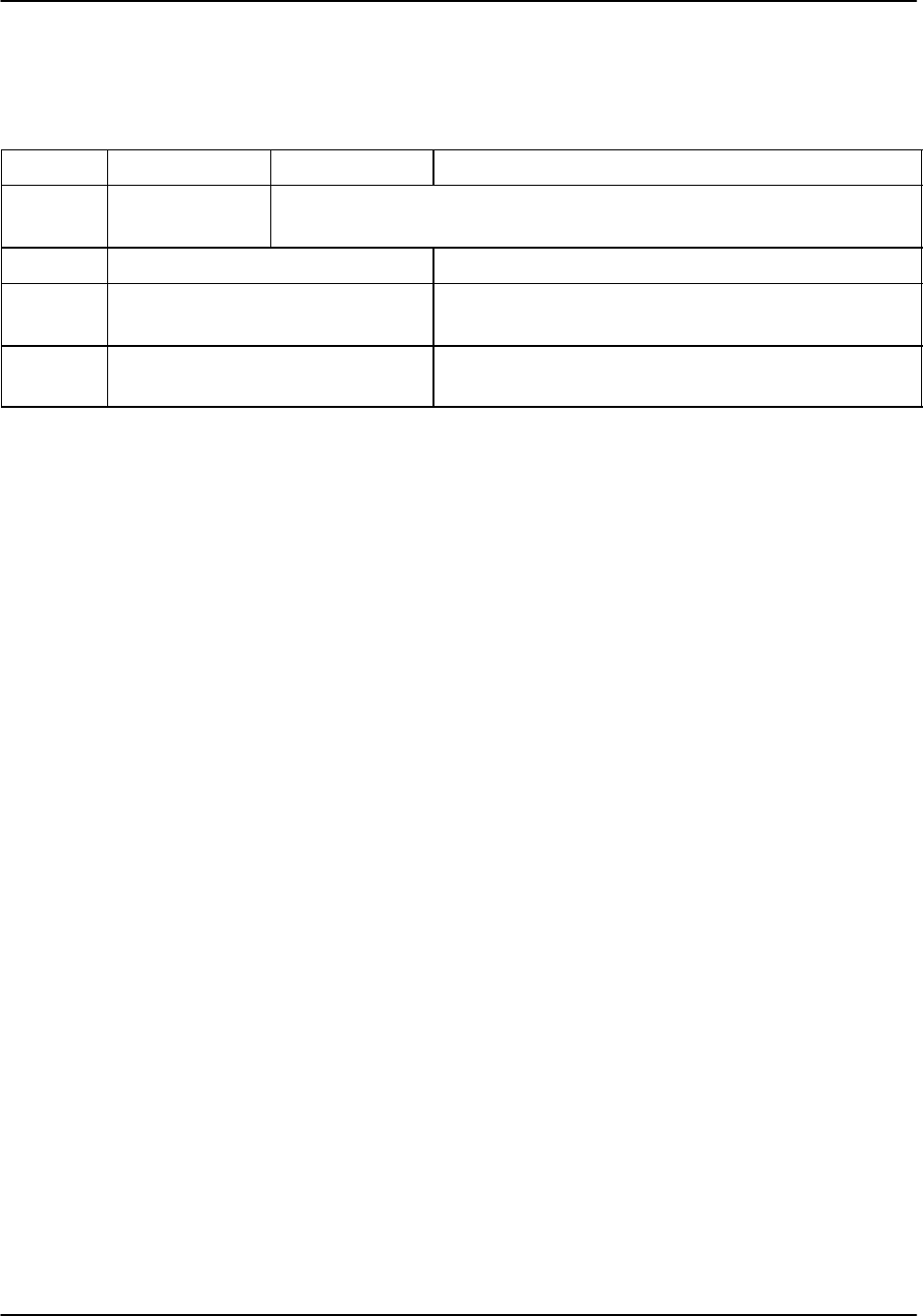

Year Model Units

Sold Major Technical Milestones

1981 FFT 10 First commercial FFT-based Doppler signal processor for weath-

er radar applications. Featured Simultaneous Doppler and inten-

sity processing.

1985 RVP5 161 First single-board low-cost Doppler signal processor. First com-

mercial application of dual PRF velocity unfolding algorithm.

1986 PP02 12 First high-performance commercial pulse pair processor with

18.75-m bin spacing and 1024 bins.

1992 RVP6 150 First commercial floating-point DSP-chip based processor. First

commercial processor to implement selectable pulse pair, FFT or

random phase 2nd trip echo filtering.

1996 RVP7 >200 First commercial processor to implement fully digital IF process-

ing for weather radar.

2003 RVP8 First digital receiver/signal processor to be implemented using an

open hardware and software architecture on standard PC hard-

ware under the Linux operating system. Public API’s are pro-

vided so that customers may implement their own custom proc-

essing algorithms.

Much of the proven, tested, documented software from the highly-successful RVP7 (written in

C) is ported directly to the new RVP8 architecture. This allows SIGMET to reduce

time-to-market and produce a high-quality, reliable system from day one. However, the new

RVP8 is not simply a re-hosting of the RVP7. The RVP8 provides new capabilities for weather

radar systems that, until now, were not available outside of the research community.

Advanced Digital Transmitter Option

For example, the RVP8 takes the next logical step after a digital receiver- a digitally synthesized

IF transmit waveform output that is mixed with the STALO to provide the RF waveform to the

transmitter amplifier (e.g., Klystron or TWT). The optional RVP8/Tx card opens the door for

advanced processing algorithms such as pulse compression, frequency agility and phase agility

that were not possible before, or done in more costly ways.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–2

Open Hardware and Software Design

Compared to previous processors that were built around proprietary DSP chips, perhaps the most

innovative aspect of the RVP8 is that it is implemented on standard PC hardware and software

that can be purchased from a wide variety of sources. The Intel Pentium/PCI approach promises

continued improvement in processor speed, bus bandwidth and the availability of low–cost

compatible hardware and peripherals. The performance of an entry level RVP8 (currently dual

2.4 GHz Pentium processors) is 6 times faster than the fastest RVP7 ever produced (with two

RVP7/AUX boards).

Aside from the open hardware approach, the RVP8 has an open software approach as well. The

RVP8 runs in the context of the Linux operating system. The code is structured and public API’s

are provided so that research customers can modify/replace existing SIGMET algorithms, or

write their own software from scratch using the RVP8 software structure as a foundation on

which to build.

The advantage of the open hardware and software PCI approach is reduced cost and the ability

for customers to maintain, upgrade and expand the processor in the future by purchasing

standard, low cost PC components from local sources.

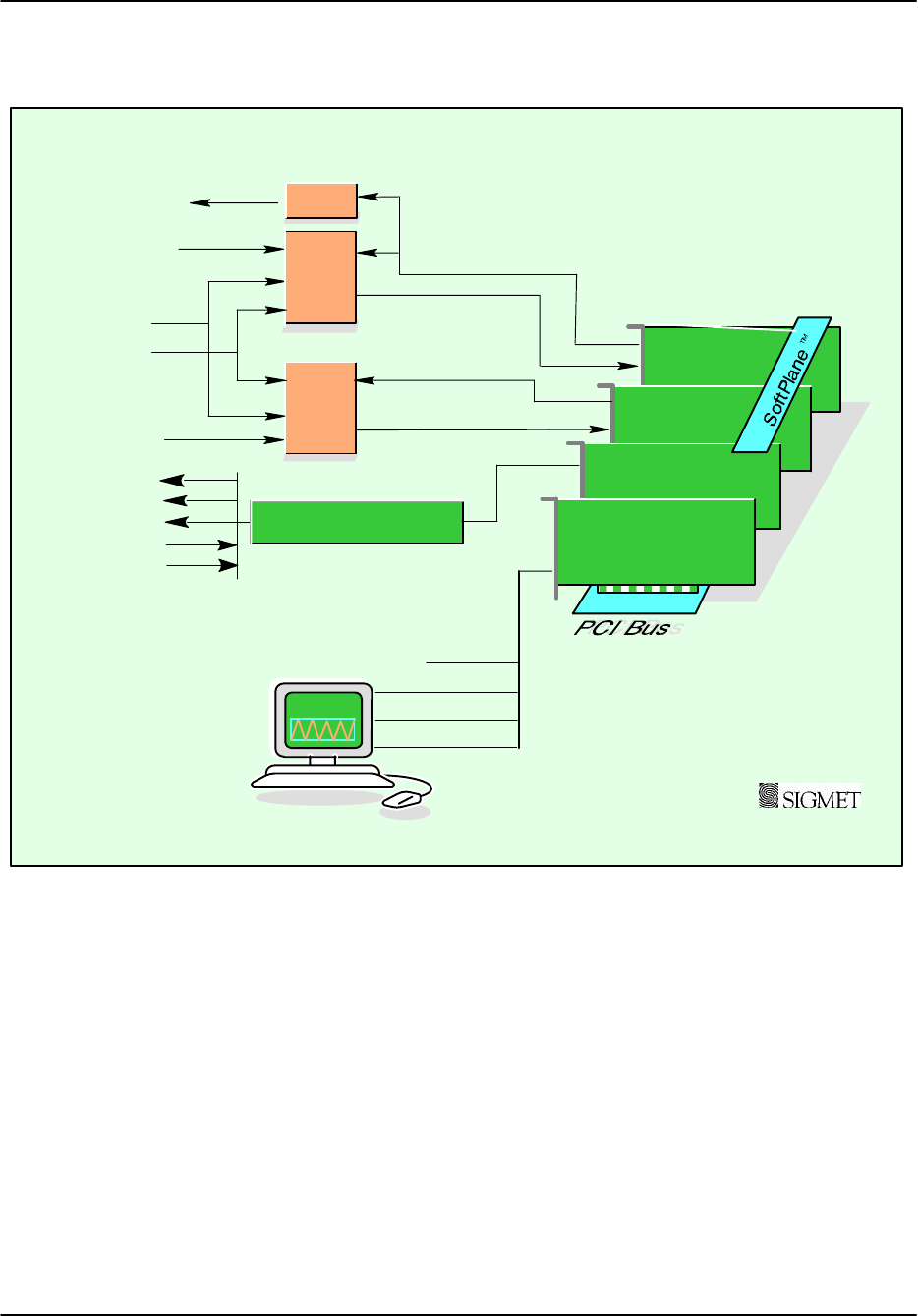

SoftPlane High–Speed I/O Interconnect

There are potentially many different I/O signals emanating from the backpanel of the RVP8.

Most of these conform to well-known electrical and protocol standards (VGA, SCSI, 10–BaseT,

RS-232 Serial, PS/2 Keyboard, etc.), and can be driven by standard commercial boards that are

available from multiple vendors. However, there are other interface signals such as triggers and

clocks that require careful timing. These precise signals cannot tolerate the PCI bus latency. For

signals that have medium–speed requirements (~1 microsec latency) for which the PCI bus is

inappropriate; and others that require a high–speed (~ 1 ns latency) connection that can only be

achieved with a dedicated wire, the RVP8 Softplane provides the solution.

Physically, the Softplane is a 16-wire digital “daisy-chain” bus that plugs into the tops of the

RVP8/Rx, RVP8/Tx, and I/O boards. The wires connect to the FPGA chips on each card, and the

function of each wire is assigned at run–time based on the connectivity needs of the overall

system. The Softplane allocates a dedicated wire to carry each high-speed signal; but groups of

medium-speed signals are multiplexed onto single wires in order to conserve resources. Even

though there are only 16 wires available, the Softplane is able to carry several high-speed signals

and hundreds of medium–speed signals, as long as the total bandwidth does not exceed about

600MBits/sec.

The Softplane I/O is configured at run–time based on a file description rather than custom

wiring such as wirewrap. Neither the PCI backplane nor the physical Softplane are customized

in any way. Since there is no custom wiring, a failed board can be replaced with a generic

off–the–shelf spare, and that spare will automatically resume whatever functions had been

assigned to the original board. Similarly, if the chassis itself were to fail, then simply plugging

the boards into another generic chassis would restore complete operation. Cards and chassis can

be swapped between systems without needing to worry about custom wiring.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–3

Standard LAN Interconnection for Data Transfer or Parallel Processing

For communication with the outside world, the RVP8 supports as standard a 10/100/1000 Base T

Ethernet. For most applications, the 100 BaseT Ethernet is used to transfer moment results (Z, T,

V, W) to the applications host computer (e.g., a product generator). However, the gigabit

Ethernet is sufficiently fast to allow UDP broadcast of the I and Q values for the purpose of

archiving and/or parallel processing. In other words, a completely separate signal processor can

ingest and process the I and Q values generated by the RVP8.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–4

1.1 System Configuration Concepts

The hardware building blocks of an RVP8 system are actually quite few in number:

RVP8/IFD IF Digitizer Unit- This is a separate sealed unit usually mounted in

the receiver cabinet. The primary input to the IFD is the received IF signal. In

addition, the IFD has channels to sample the transmit pulse and to take in an

external clock to phase lock the A/D conversion with the transmit pulse (not used

for magnetron systems).

RVP8/Rx Card- A PCI long format card mounted in the chassis. It connects to

the IFD by a fiberoptic downlink and a coax uplink which can be up to 100m

distant. In addition, there are two BNC trigger input/output (programmable).

I/O-62 Card and Connector Panel- These handle all of the various I/O

associated with a radar signal processor, such as triggers, antenna angles,

polarization switch controls, pulse width control, etc. The Connector Panel is

mounted on either the front or rear of the equipment rack and a cable (supplied)

connects the panel to the I/O-62.

Optional RVP8/Tx card- This supplies two IF output signals with

programmable frequency, phase and amplitude modulation. In the simplest case,

it supplies the COHO which is then mixed up with the STALO to generate the

transmit RF for Klystron or TWT systems. This card is not necessary for

magnetron systems.

PC Chassis and Processor with various peripherals- a robust 6U rack mount

unit with either a mother board or single board computer (SBC) in a passive back

plane. There is a diagnostic front panel display, disk (mechanical or flash),

CDRW, keyboard, mouse and optional monitor for local diagnostic work. Dual or

tri–redundant power supplies are used and there are redundant fans as well.

This modular hardware approach allows the various components to be mixed and matched to

support applications ranging from a simple magnetron system to an advanced dual polarization

system with pulse compression. Typically SIGMET supplies turn-key systems, although some

OEM customers who produce many systems purchase individual components and integrate them

by themselves. This allows OEM customers to put their own custom “stamp” on the processor

and even their own custom software if they so choose.

For the turnkey systems provided by SIGMET, the basic chassis is a 6U rackmount unit as

described above. A 2U chassis can be provided for applications for which space is limited. A

very low cost approach is to use a desk side PC, but this is not recommended for applications

that require long periods of unattended operation.

To illustrate various RVP8 configurations, some typical examples are shown below. For clarity,

all the examples show the single–board computer approach. A mother board approach is

equivalent.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–5

Keyboard

Mouse

Monitor

10/100 BaseT LAN Interface

IFD Fiber Downlink

COAX Uplink

RS232C Antenna Angles

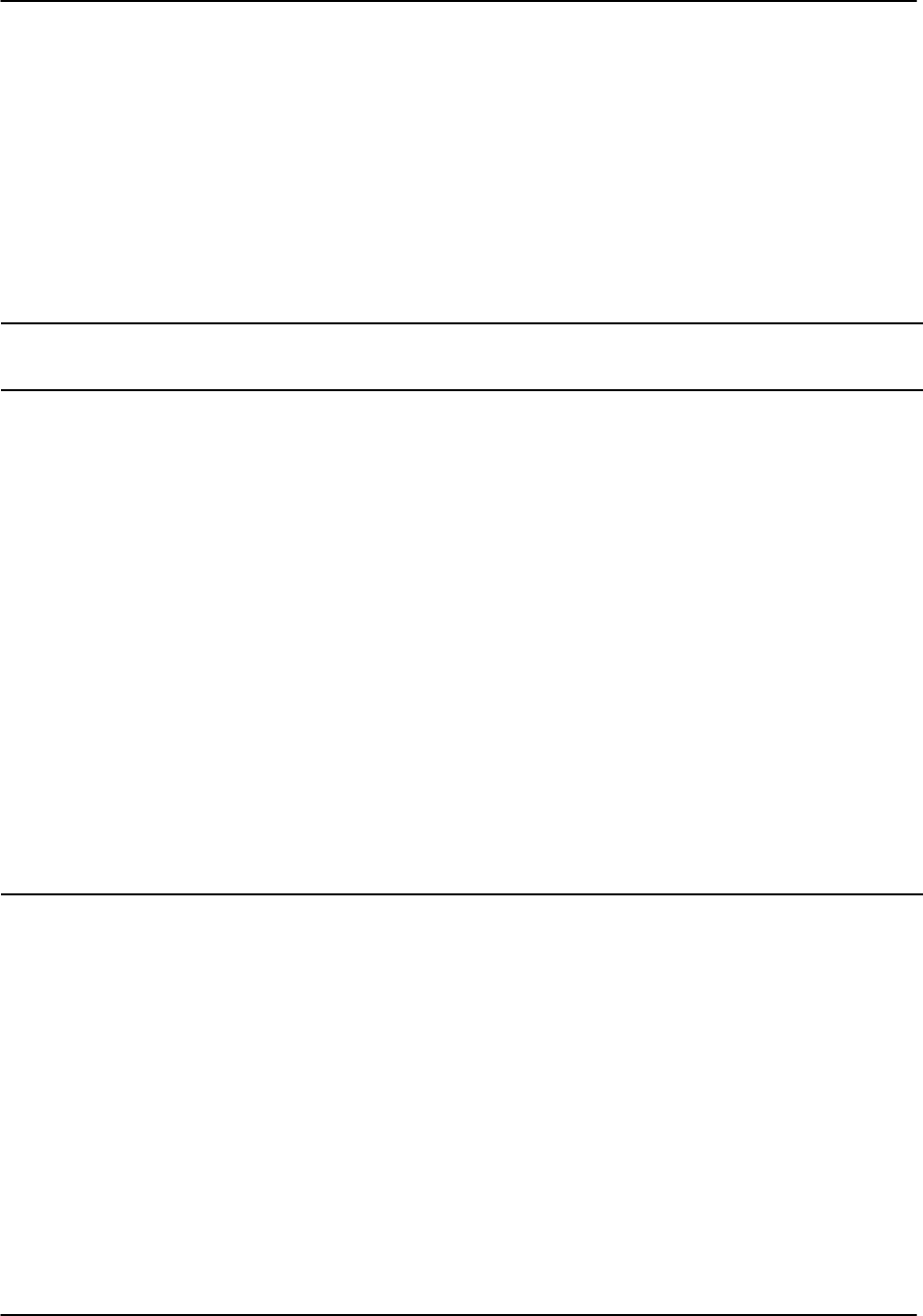

RVP8 Configuration Example: Basic Magnetron System

Triggers

IF Signal

IF Magnetron Burst

DAFCDigital STALO

Optional

Utilities

14-Bit

SBC

RVP8/Rx

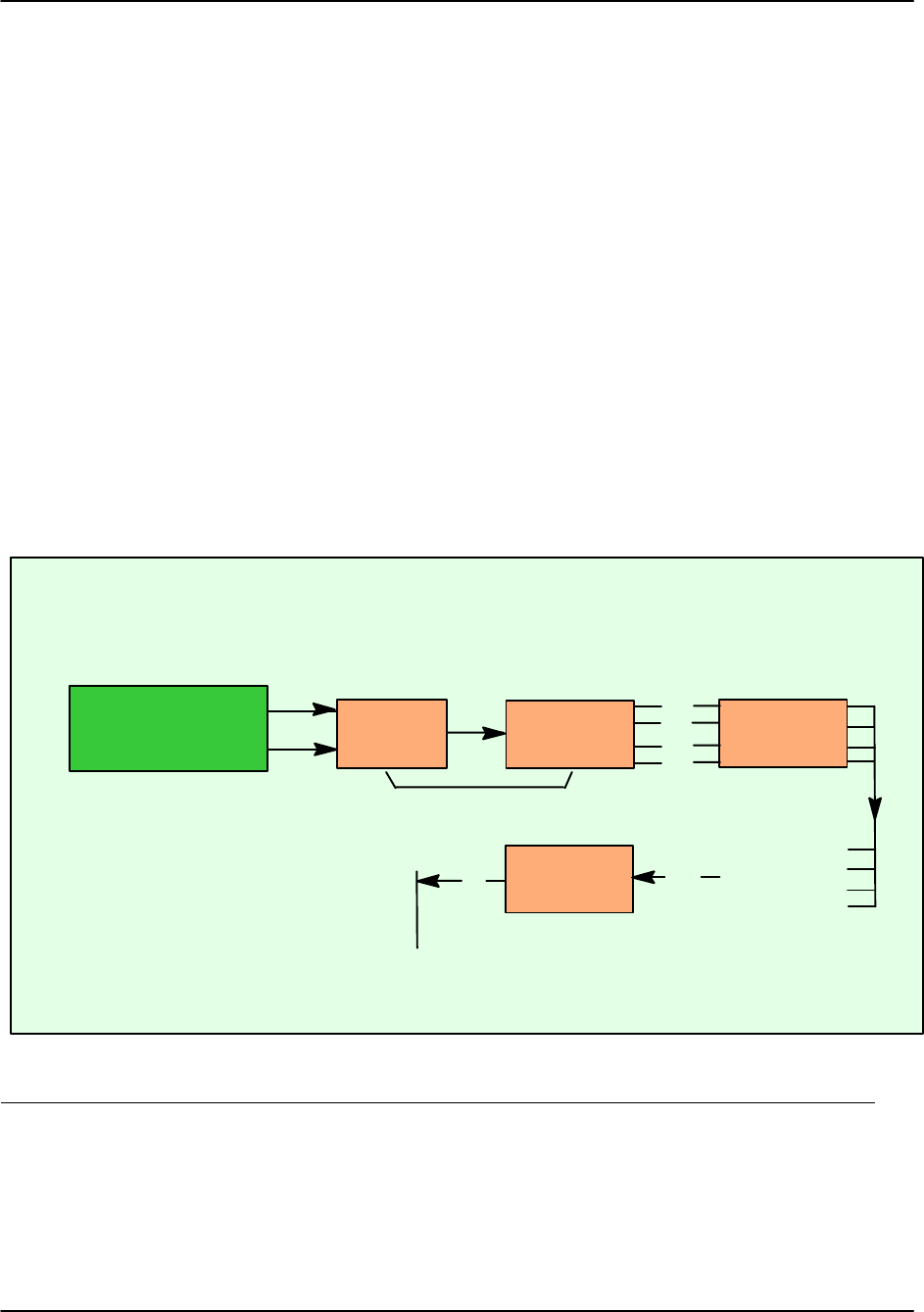

Example 1: Basic Magnetron System

The building blocks required to construct the basic system are:

IFD- IF Digitizer installed in the radar receiver cabinet. This can be located up to 100

meters from the RVP8 main chassis (fiber optic connection). The DAFC (Digital AFC) is

an option to interface to a digitally controlled STALO. Like the RVP7, the RVP8

provides full AFC with burst pulse auto-tracking.

RVP8/Rx- The digital receiver collects digitized samples from the IFD and does the

processing to obtain I/Q. It also provides two trigger connections configurable for input

or output.

SBC Card- Single Board Computer with dual SMP processors (PC) running Linux.

The figure above shows a basic magnetron system constructed with an IFD, and two PCI cards.

A standard RS-232 serial input (included with the SBC) is used for obtaining the antenna angles

and the output/input trigger is provided directly from the Rx card. This system has 5 times the

processing power of the fastest version of the previous generation processor (RVP7/Main board

plus 2 RVP7/AUX boards) so that it is capable of performing DFT processing in 2048 rangebins

with advanced algorithms such as random phase 2nd trip echo filtering and recovery.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–6

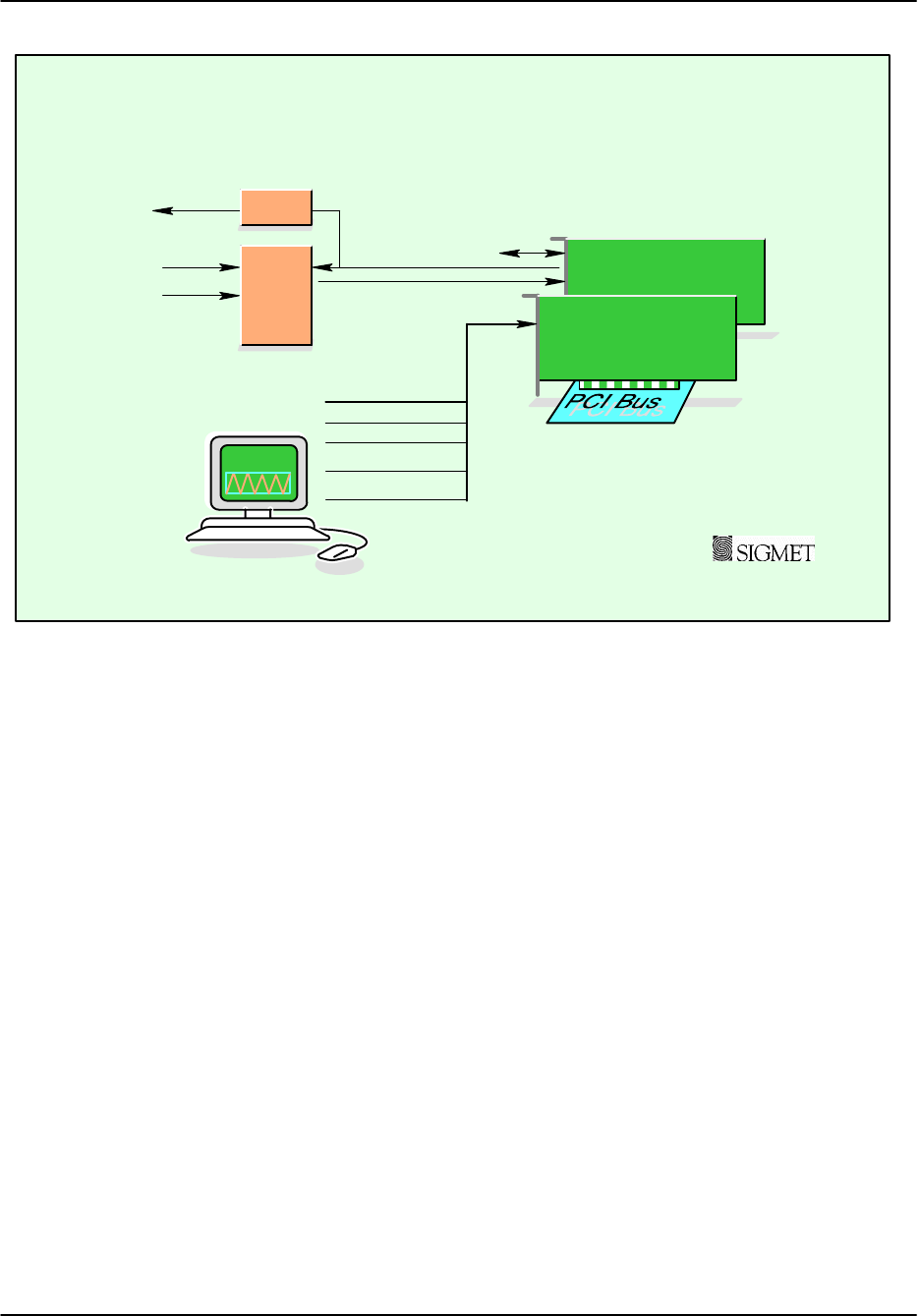

RVP8 Configuration Example: High Performance Klystron

Keyboard

Mouse

Monitor

10/100/1000 Base T

IFD

Fiber Downlink

COAX Uplink

Triggers

IF Signal

Reference Clock

Digitally Synthesized COHO

Parallel or Synchro AZ

Parallell or Synchro EL

Pulse width IF Tx Waveform

Utilities

IF Tx Waveform

14-Bit

I/O62

SBC

RVP8/Tx

RVP8/Rx

Connector Panel

Example 2: Klystron System with Digital Tx

In this case, the IFD can receive a master clock from the radar system (e.g., the COHO). This

ensures that the entire system is phase locked. As compared to the previous example there are

two additional cards shown in this example:

RVP8/Tx- The digital transmitter card provides the digital Tx waveform. A second

output can be used to provide a COHO in the event that the RVP8 is used to provide the

system master clock. In any case, the IF transit waveform and the A/D sampling are

phase locked.

SIGMET I/O-62 card for additional triggers, parallel, synchro or encoder AZ and EL

angle inputs, pulse width control, spot blanking control output, etc. These signals are

brought in via the connector panel.

The figure shows the SIGMET SoftPlane which carries time-critical I/O such as clock and

trigger information which is not appropriate for the PCI bus. These signals are limited to the

cards provided by SIGMET, i.e., the SoftPlane is not connected to any of the standard

commercial cards.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–7

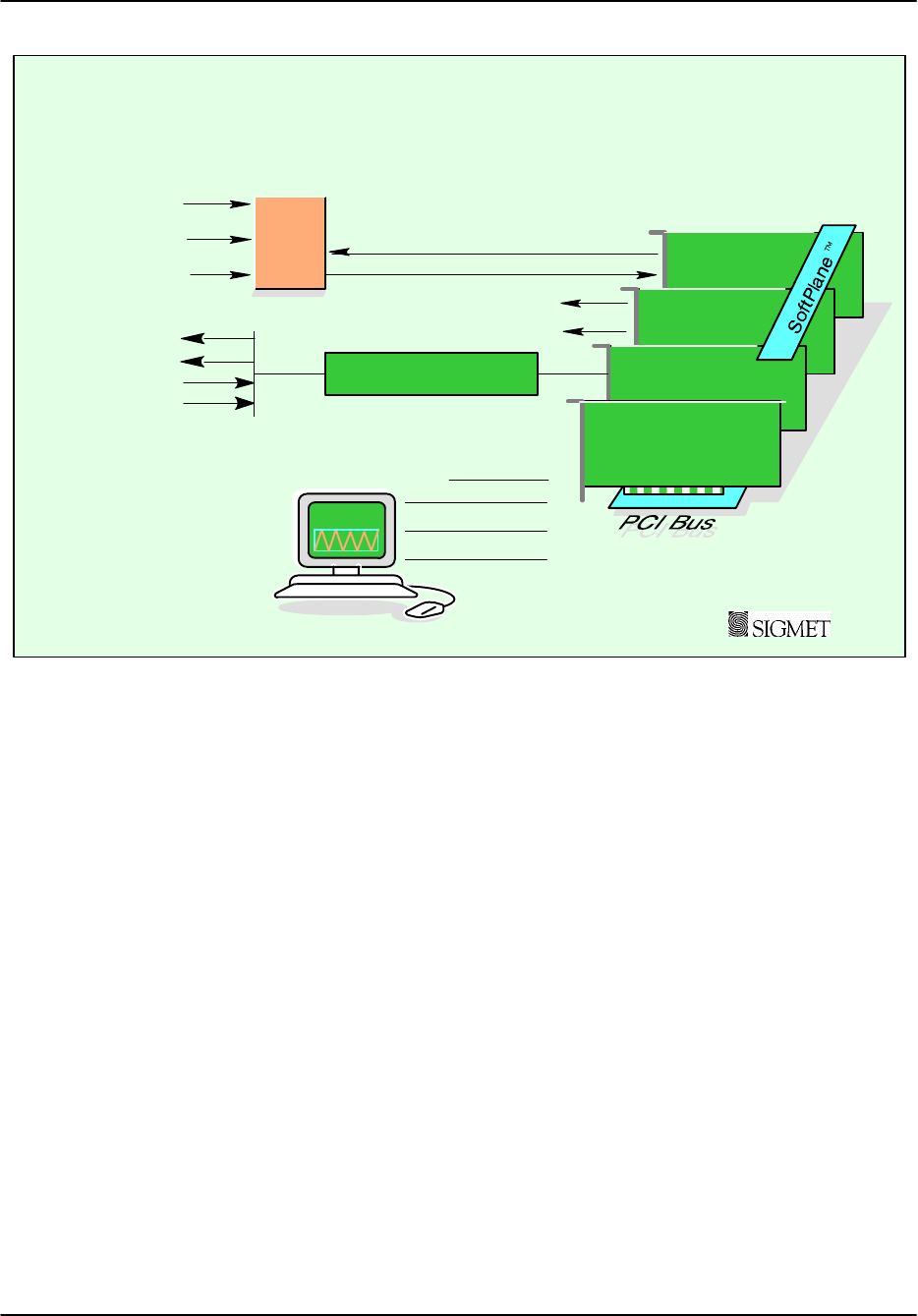

IFD

Fiber Downlink

COAX Uplink

RVP8 Configuration Example: Dual Polarization Magnetron System

Keyboard

Mouse

Monitor

10/100/1000 BaseT LAN

IFD

Horizontal IF Signal

DAFCDigital STALO

Optional

Vertical IF Signal

Utilities

14-Bit

14-Bit

IF Magnetron Burst

Synch Clock

Fiber Downlink

Horz

Vert I/O62

SBC

RVP8/Rx

RVP8/Rx

COAX Uplink

Triggers

Parallel or Synchro AZ

Parallell or Synchro EL

Pulse Width Control

Connector Panel

Polarization Control

Example 3: Dual Polarization Magnetron System

In this system 2 IFD’s and two RVP8/Rx cards are used for the horizontal and vertical channels

of a dual-channel receiver. The legacy RVP7 technique of using a single IFD and two IF

frequencies for the horizontal and vertical channels (e.g., 24 and 30 MHz) is also supported by

the RVP8. In the case of either dual or single IFD’s, there is a synch clock provided by either the

STALO reference frequency (e.g., 10 MHz) or by the RVP8 itself.

The RVP8 supports calculation of the complete covariance matrix for dual pol, including ZDR,

PHIDP (KDP), RHOHV, LDR, etc. Which of these variables is available depends on whether the

system is a single–channel switching system (alternate H and V), a STAR system (simultaneous

transmit and receive) or a dual channel switching system (co and cross receivers). Note that for

the special case of a single channel switching system, only one IFD is required.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–8

COTS Accessories

Aside from the basic PCI cards required for the radar application, there are additional cards that

can be installed to meet different customer requirements, e.g.,

10/100–BaseT Ethernet card for additional network I/O (e.g., a backup network).

RS-232/RS-422 serial cards for serial angles, remote TTY control, etc.

Sound card to synthesize audio waveforms for wind profiler applications.

GPS card for time synch.

IEEE 488 GPIB card for control of test equipment.

The bottom line is that the PCI open hardware approach provides unparalleled hardware

flexibility. In addition, the availability of compatible low-cost replacement or upgrade parts is

assured for years into the future.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–9

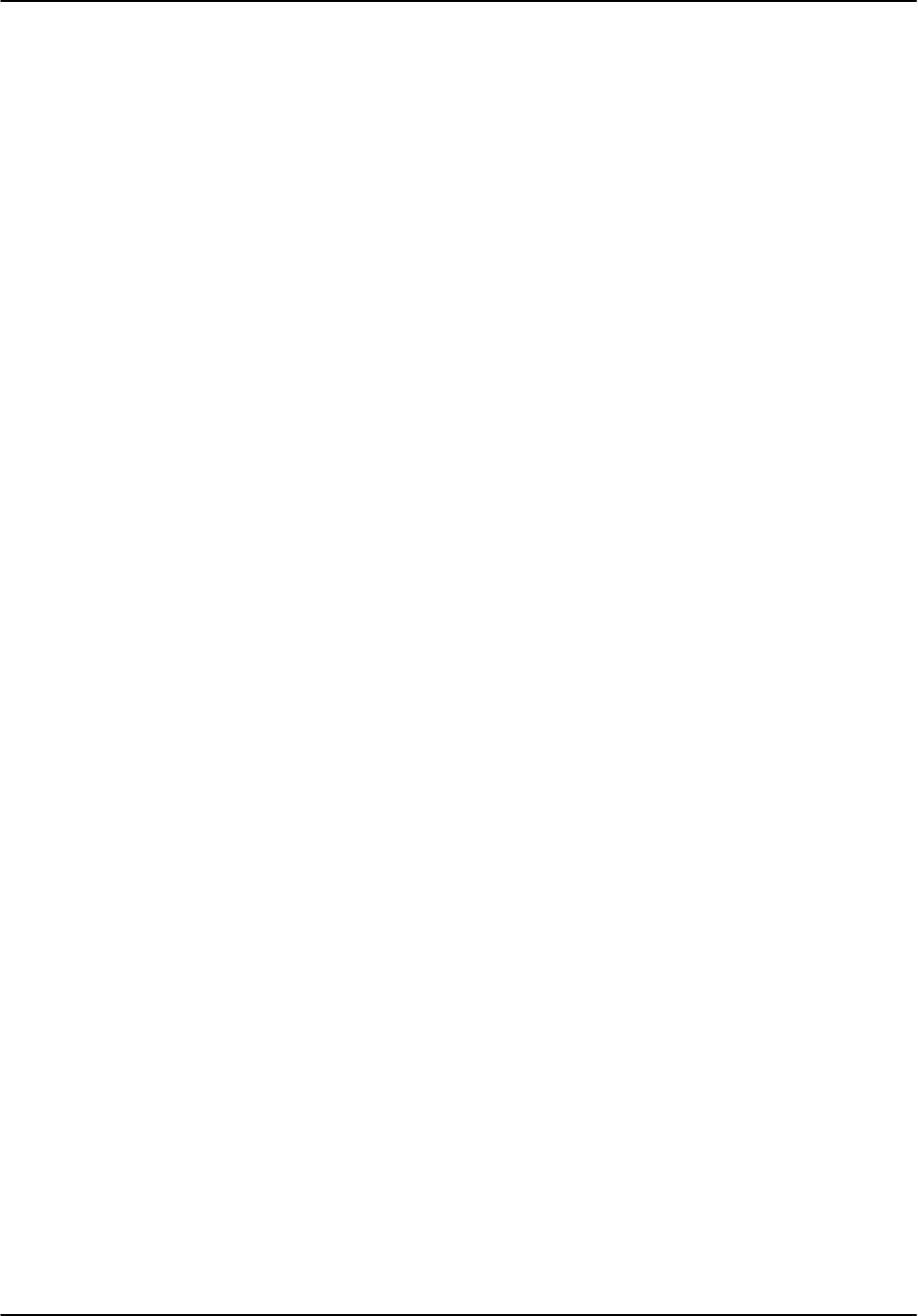

1.1.1 IFD IF Digitizer

The IFD 14–bit IF digitizer is a totally sealed unit for optimum low–noise per-

formance. The use of digital components within the IFD is minimized and the

unit is carefully grounded and shielded to make the cleanest possible digital

capture of the input IF signal. Because of this, the IFD achieves the theoretical

minimum noise level for the A/D convertors.

There are 3 inputs to the IFD:

IF signal in the nominal ranges of 20 -34, 38-52 and 56-70 MHz. The user

simply enters the system IF frequency as a setup parameter.

IF Burst Pulse for magnetron or IF COHO for Klystron.

Optional reference clock for system synchronization. For a Klystron system,

the COHO can be input. Magnetron systems do not require this signal. This

clock can even come from the RVP8/Tx card itself.

All of these inputs are on SMA connectors. The IF signal input is made imme-

diately after the STALO mixing/sideband filtering step of the receiver where

a traditional log receiver would normally be installed. The required signal lev-

el for both the IF signal and burst is +6.5 dBm for the strongest expected input

signal. A fixed attenuator or IF amplifier may be used to adjust the signal level

to be in this range.

Digitizing is performed for both the IF signal and burst/COHO channels at

approximately 36 MHz to 14–bits. This provides 92 to 102 dB of dynamic

range (depending on pulse width) without using complex AGC, dual A/D

ranging or down mixing to a lower IF frequency.

The uplink from the RVP8/Rx is an SMA input on 75–Ohm shielded cable.

This carries timing and AFC information back to the IFD. The data downlink

to the RVP8/Rx card is a fiber optic cable. The IFD may be separated from

the Rx Board by up to 100 meters.

The RVP8 provides comprehensive AFC support for tuning the STALO of a magnetron system.

Alternatively, the magnetron itself can be tuned by a motorized tuning circuit controlled by the

RVP8. Both analog (+–10V) and digital tuning (with optional DAFC to 24 bits) are supported.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–10

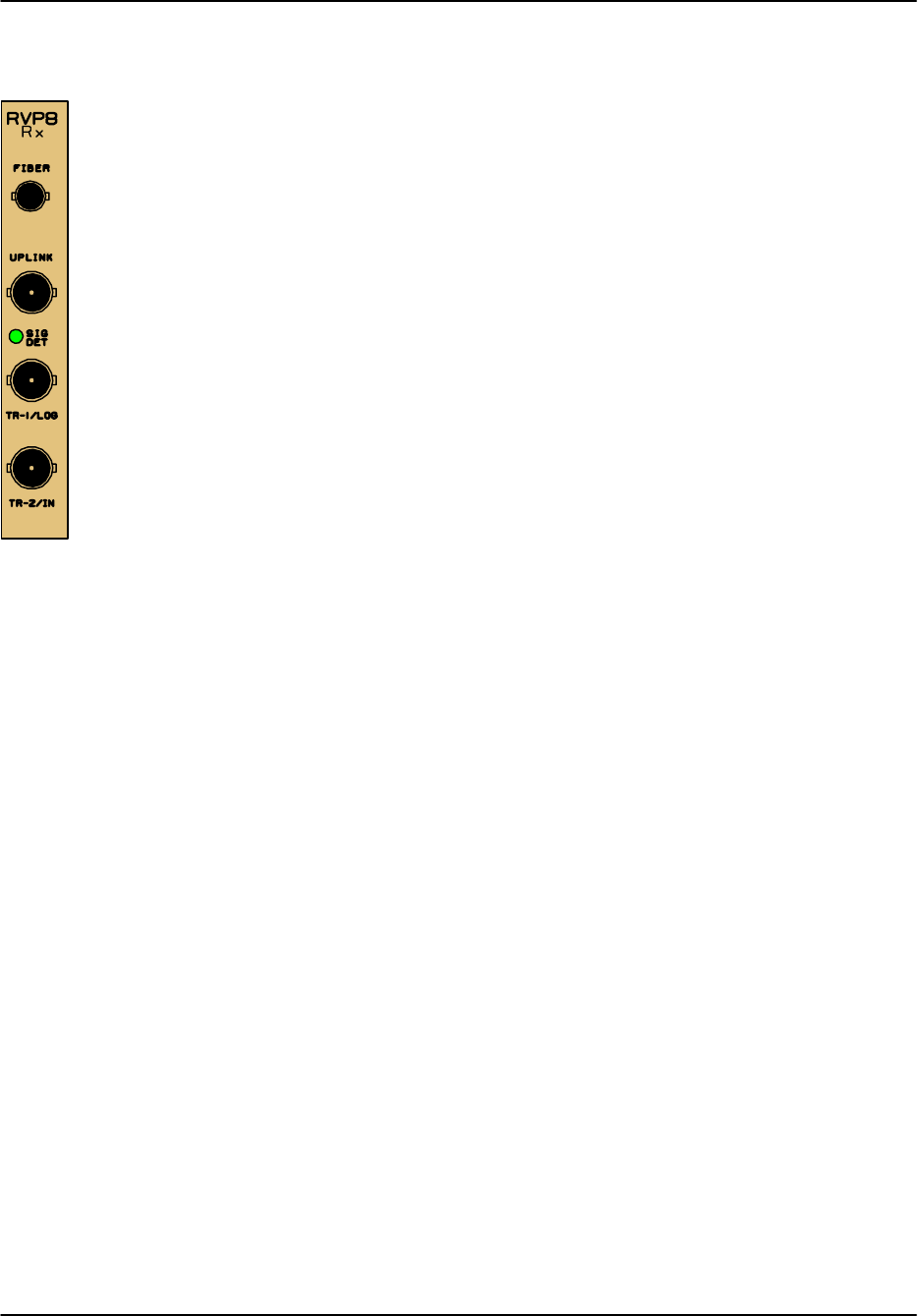

1.1.2 Digital Receiver PCI Card (RVP8/Rx)

The RVP8/Rx card receives the digitized IF samples from the IFD via the fiber optic

link. The advantage of this design is that the receiver electronics (LNA, RF mixer,

IF preamp, and IFD) can be located as far as 100–meters away from the RVP8 main

chassis. This makes it possible to choose optimum locations for both the IFD and the

RVP8, e.g., the IFD could be mounted on the antenna itself, and the processor box

in a nearby equipment room.

The RVP8/Rx is 100% compatible with the 14–bit RVP7/IFD, but it also includes

hooks for future IFD’s operating at higher sampling clock rates. Two additional BNC

connectors are included on the board’s faceplate. These can be used for trigger input,

programmable trigger output, or a simple LOG analog ascope waveform.

A remarkable amount of computing power is resident on the receiver board, in the

form of an FIR filter array that can execute 6.9 billion multiply/accumulate cycles

per second. These chips serve as the first stage of processing of the raw IF data sam-

ples. Their job is to perform the down–conversion, bandpass, and deconvolution

steps that are required to produce (I,Q) time series. The time series data are then trans-

ferred over the PCI bus to the SBC for final processing.

The FIR filter array can buffer as much as 80 microsec of 36MHz IF samples, and then compute

a pair of 2880–point dot products on those data every 0.83 microsec. This could be used to

produce over-sampled (I,Q) time series having a range resolution of 125–meters and a

bandwidth as narrow as 30Khz. The same computation could also yield independent 125–meter

time series data from an 80 microsec compressed pulse whose transmit bandwidth was

approximately 1MHz.

Finer range resolutions are also possible, down to a minimum of 25–meters. A special feature of

the RVP8/Rx is that the bin spacing of the (I,Q) data can be set to any desired value between 25

and 2000 meters. Range bins are placed accurately to within +2.2 meters of any selected grid,

which does not have to be an integer multiple of the sampling clock. However, when an integer

multiple (N x 8.333–meters) is selected, the error in bin placement effectively drops to zero.

Dual polarization radars that are capable of simultaneous reception for both horizontal and

vertical channels can be interfaced to the RVP8 using a separate RVP8/Rx and IFD for each

channel. Note that the multiplexed dual IF approach used for the RVP7 with a single IFD can

also be used.

One of the primary advantages of the digital receiver approach is that wide linear dynamic range

can be achieved without the need for complex AGC circuits that require both phase and

amplitude calibration.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–11

Calibration Plot for RVP8/IFD

The figure above shows a calibration plot for a 14–bit IFD with the digital filter matched to a 2

microsecond pulse. The performance in this case is >100 dB dynamic range– fully linear.

The RVP8 performs several real time signal corrections to the I/Q samples from the Rx,

including:

Amplitude Correction- A running average of the transmit pulse power in the magnetron burst

channel is computed in real-time by the RVP8/Rx. The individual received I/Q samples are

corrected for pulse–to–pulse deviations from this average. This can substantially improve the

“phase stability” of a magnetron system to improve the clutter cancelation performance to near

Klystron levels.

Phase Correction- The phase of the transmit waveform is measured for each pulse (either the

burst pulse for magnetron systems or the Tx Waveform for coherent systems). The I/Q values

are adjusted for the actual measured phase. The coherency achievable is better than 0.1 degrees

by this technique.

Large Signal Linearization- When an IF signal saturates, there is still considerable information

in the signal since only the peaks are clipped. The proprietary large signal linearization

algorithm used in the RVP8 provides an extra 3 to 4 dB of dynamic range by accounting for the

effects of saturation.

The RVP8/Rx card provides the same comprehensive configuration and test utilities as the

RVP7, with the difference that no external host computer is required to run the utilities. These

utilities can be run either locally or remotely– over the network! Some examples are shown

below:

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–12

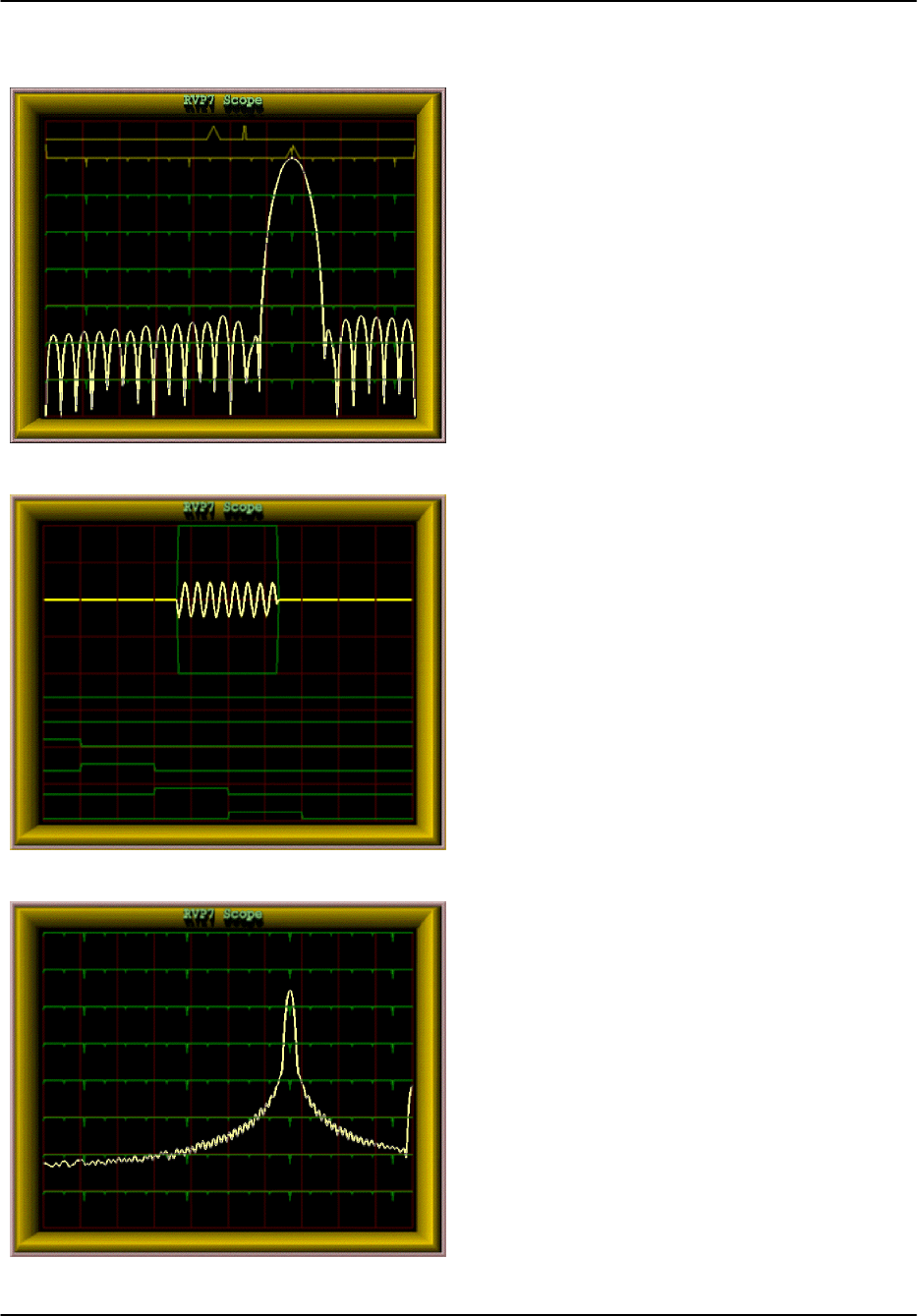

Digital IF Band Pass Design Tool

The built–in filter design tool makes it easy for

anyone to design the optimal IF filter to match

each pulse width and application. Simply specify

the impulse response and pass band and the filter

appears. The user interface makes it easy to wid-

en/narrow the filter with simple keyboard com-

mands. There is even a command to automatical-

ly search for an optimal filter.

This display can also show the actual spectrum

of the transmit burst pulse for quality control and

comparison with the filter.

Burst Pulse Alignment Tool

The quality assessment of the transmit burst

pulse and its precise alignment at range zero

are easy to do, either manually using this tool

and/or automatically using the burst pulse

auto-track feature. This performs a 2D search

in both time and frequency space if a valid

burst pulse is not detected. The automatic

tracking makes the AFC robust to start–up

temperature changes and pulse width changes

that can effect the magnetron frequency.

AFC alignment/check is now much easier

since it can be done manually from a central

maintenance site or fully automatically.

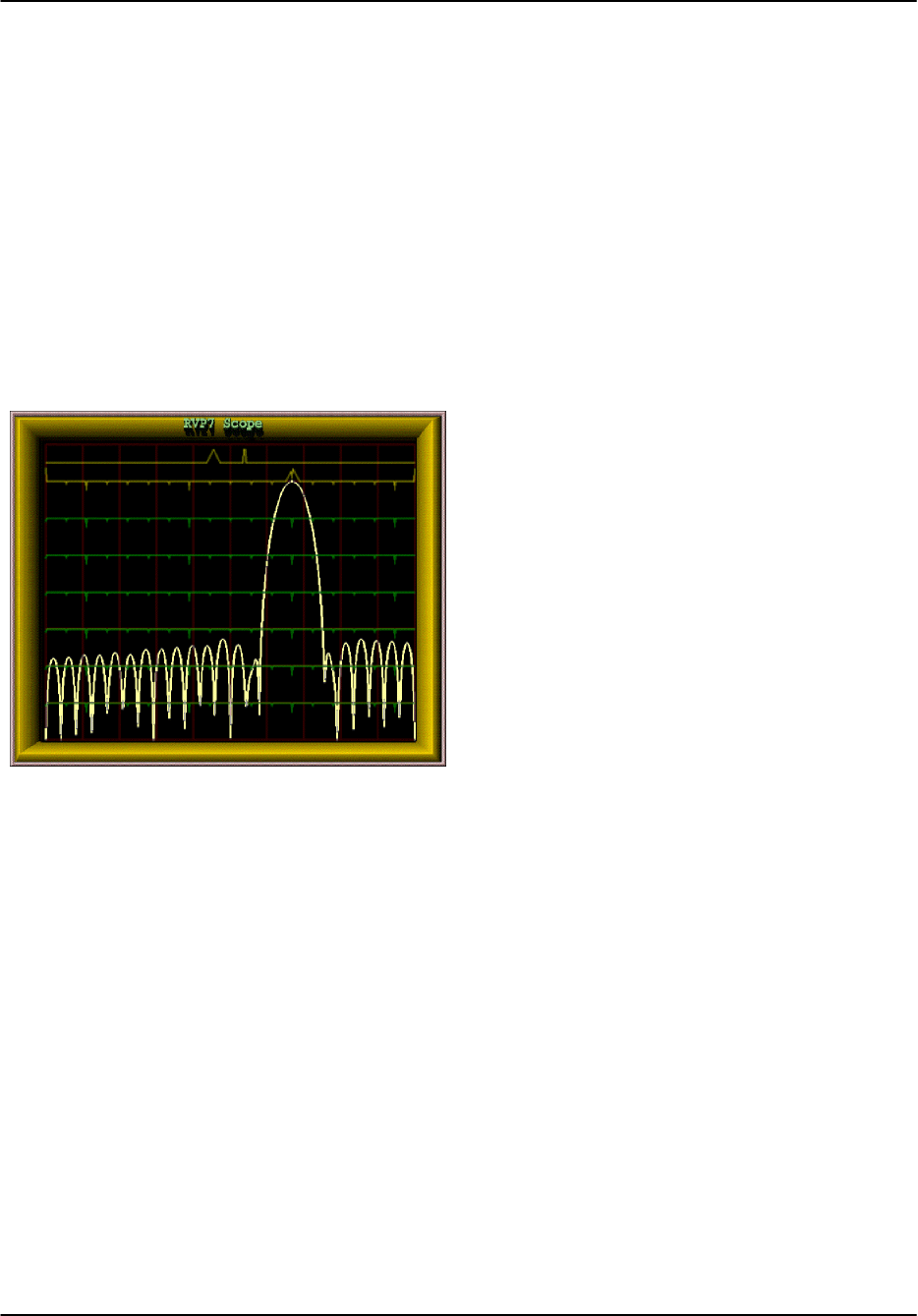

Received Signal Spectrum Analysis Tool

The RVP8 provides plots of the IF signal versus

range as well as spectrum analysis of the signal

as shown in this example.

In the past, these types of displays and tools re-

quired that a highly-skilled engineer transport

some very expensive test equipment to the radar

site. Now, detailed analysis and configuration

can all be done from a central maintenance facil-

ity via the network. For a multi-radar network

this results in substantial savings in equipment,

time and labor.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–13

1.1.3 Mother Board or Single-Board Computer (SBC)

The dual-CPU Pentium mother board or single-board computer (SBC) acts as the host

to the Linux operating system and provides all of the compute resources for processing

the I/Q values that are generated by the RVP8/Rx card. Standard keyboard, mouse and

monitor connections are on the Rx backpanel, along with a 10/100/1000 BaseT Ether-

net port. The system does not require that a keyboard, mouse or monitor be connected

which is typically the case at an unattended site. An SBC example is shown on the left.

Motherboards and SBC’s are available from many vendors, at various speeds Typical-

ly the SBC is equipped with 128 MB RAM. The RVP8 chassis has a front bay for either

a >20 GB hard disk or a Flash Disk. The Flash Disk approach is well suited to applica-

tions where high–reliability is important. CDRW is also provided for software mainte-

nance. Note that the latest versions of the RVP8 software and documentation can al-

ways be down-loaded from SIGMET’s web site for FREE.

The SBC also plays host for SIGMET’s RVP8 Utilities which provide test, configura-

tion, control and monitoring software as well as built–in on-line documentation.

1.1.4 Digital Transmitter PCI Card (RVP8/Tx)

Many of the exciting new meteorological applications for the RVP8 are made possible

by its ability to function as a digital radar transmitter. The RVP8/Tx PCI card synthe-

sizes an output waveform that is centered at at the radar’s intermediate frequency. This

signal is filtered using analog components, then up–converted to RF, and finally am-

plified for transmission. The actual transmitter can be a solid state or vacuum tube de-

vice. The RVP8 can even correct for waveform distortion by adaptively “pre–distort-

ing” the transmit waveform, based on the measured transmit burst sample.

The Tx card has a BNC output for the IF Tx waveform. In addition, there is a second

output for an auxiliary signal or clock, or for a clock input. At the bottom of the card

is a 9–pin connector for arbitrary I/O (e.g., TTL, RS422, additional clock).

The RVP8 digital transmitter finds a place within the overall radar system that exactly

complements the digital receiver. The receiver samples an IF waveform that has been

down–converted from RF, and the transmitter synthesizes an IF waveform for up–con-

version to RF. The beauty of this approach is that the RVP8 now has complete control

over both halves of the radar, making possible a whole new realm of matched Tx/Rx

processing algorithms. Some examples are given below:

Phase Modulation- Some radar processing algorithms rely on modulating the phase of

the transmitter from pulse to pulse. This is traditionally done using an external IF phase

modulator that is operated by digital control lines. While this usually works well, it

requires additional hardware and cabling within the radar cabinet, and the

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–14

phase/amplitude characteristics may not be precise or repeatable. In contrast, the

RVP8/Tx can perform precise phase modulation to any desired angle, without requiring

the use of external phase shifting hardware.

Pulse Compression- There is increasing demand for siting radars in urban areas

that also happen to have strict regulations on transmit emissions. Often the peak

transmit power is limited in these areas; so the job for the weather radar is to

somehow illuminate its targets using longer pulses at lower power. The problem,

of course, is that a simple long pulse lacks the ability (bandwidth) to discern

targets in range. The remedy is to increase the Tx bandwidth by modulating the

overall pulse envelope, so that a reasonable range resolution is restored. The

exceptional fidelity of the RVP8/Tx waveform can accomplish this without

introducing any of the spurious modulation components that often occur when

external phase modulation hardware is used.

Frequency Agility- This has been well studied within the research community,

but has remained out of the reach of practical weather radars. The RVP8/Tx

changes all of this, because frequency agility is as simple as changing the center

frequency of the synthesized IF waveform. Many new Range/Doppler unfolding

algorithms become possible when multiple transmit frequencies can coexist.

Frequency agility can also be combined with pulse compression to remedy the

blind spot at close ranges while the long pulse is being transmitted.

COHO synthesis- The RVP8/Tx output waveform can be programmed to be a

simple CW sine wave. It can be synthesized at any desired frequency and

amplitude, and its phase is locked to the other system clocks. If you need a

dedicated oscillator at some random frequency in the IF band, this is a simple

way to get it.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–15

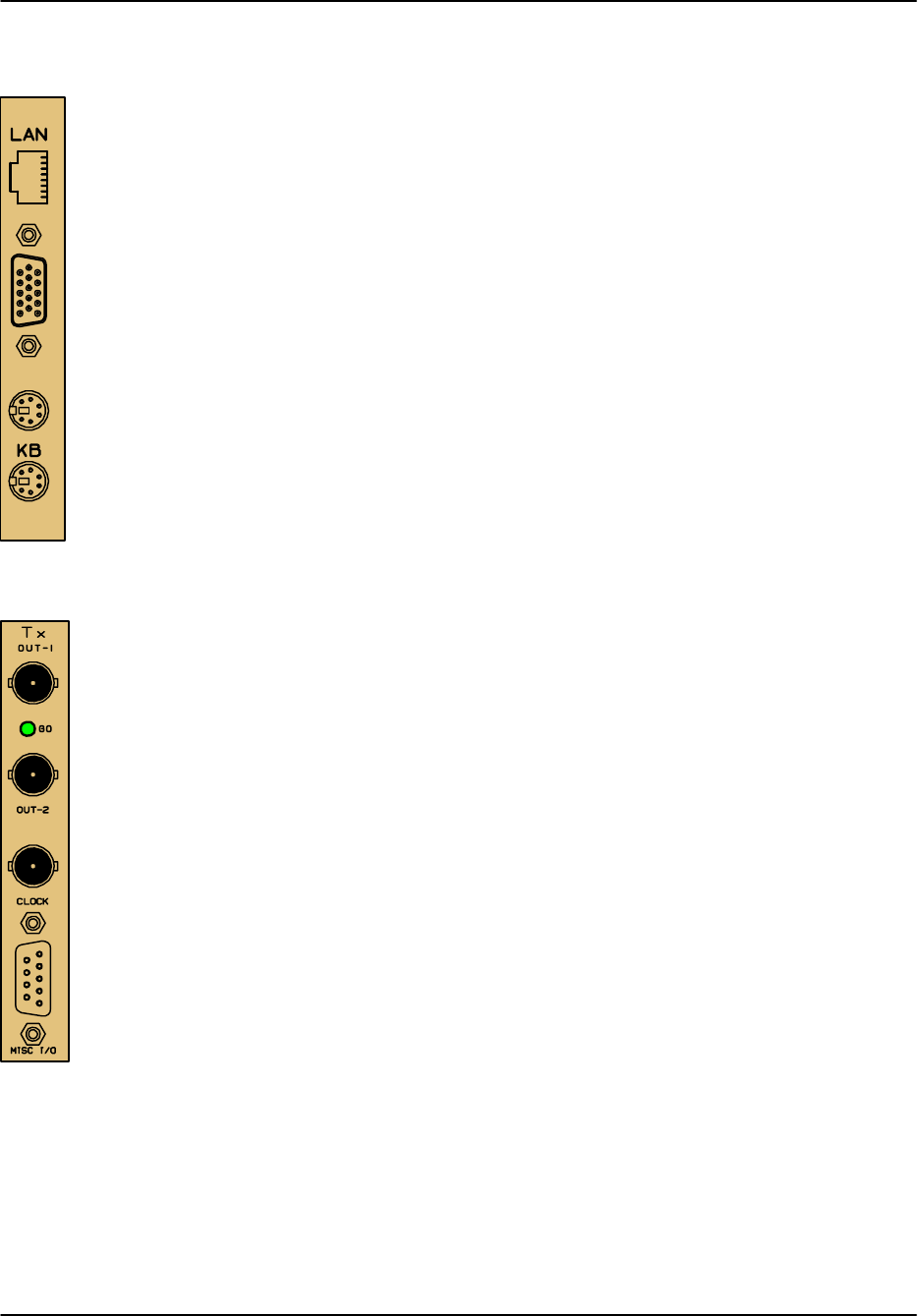

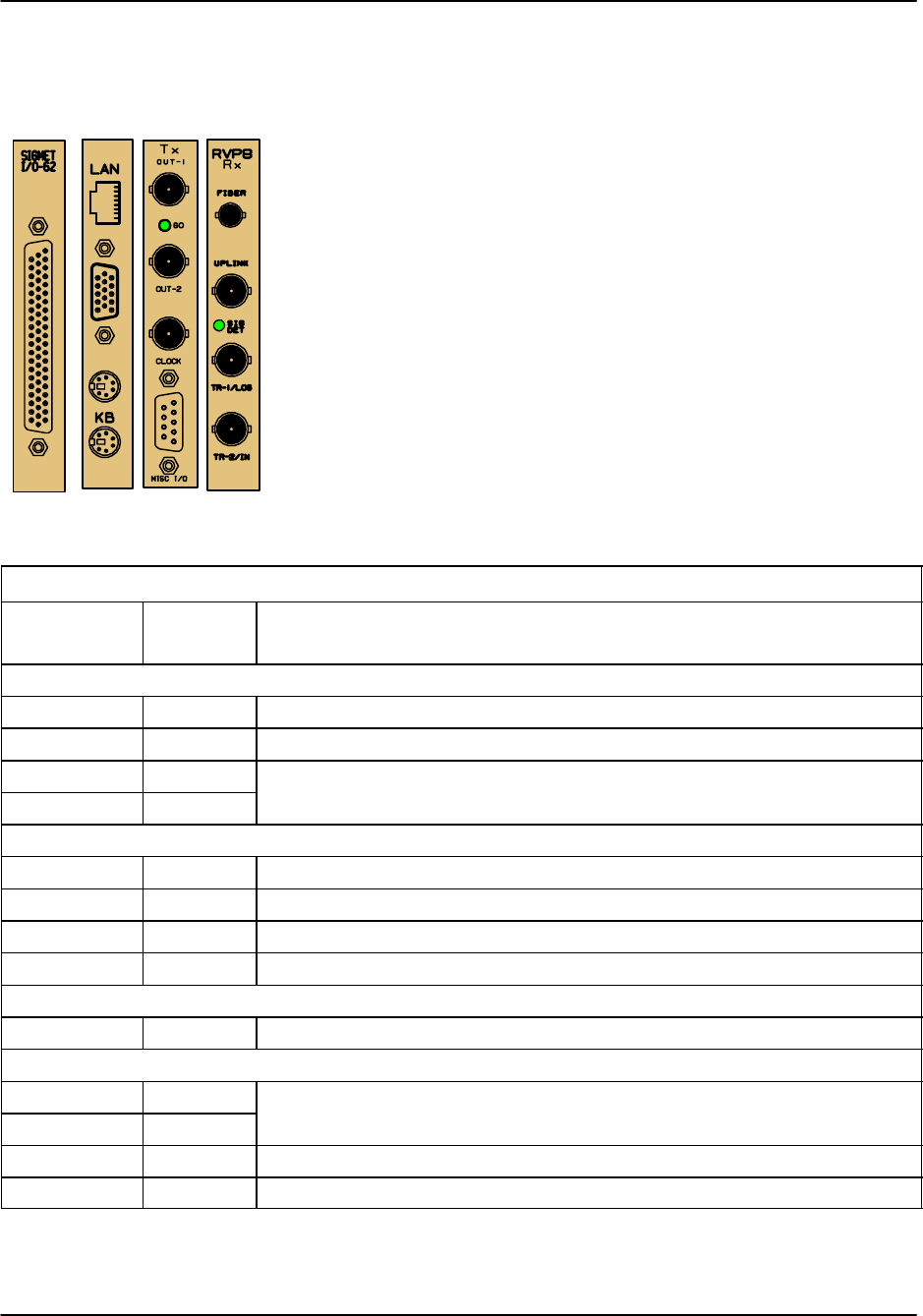

1.1.5 I/O-62 PCI Card and I/O Panel

The SIGMET I/O-62 is a short format PCI card that provides extensive I/O capabilities

for the RVP8. A typical installation would have one I/O-62 and an RVP8 Connector

Panel shown above. The Softplane is used to interconnect the I/O 62 with other SIG-

MET PCI cards. Note that the identical card is used in the SIGMET RCP8 radar/anten-

na control processor which in general does not use the Softplane connection. The

I/O-62 has a single 62-position, high-density “D” connector. This is attached to the

RVP8 Connector Panel (typically mounted on the front or back of the rack which holds

the RVP8). A standard 1:1 cable connects the remote panel to the I/O-62 card in the

RCP8 chassis. The standard connector panel provided by SIGMET meets the needs of

most radar sites.

The best part is that the I/O-62 is configurable in software, i.e., there is no need to open

the chassis to configure jumpers or switches. This means that when a spare board is

added, there is no need to perform hardware configuration or custom wiring.

The physical I/O lines are summarized in the system specifications section.

ESD Protection Features

Since the I/O lines are connected to the radar system, there is a potential for lightning or other

ESD type damage. This is addressed aggressively by the I/O-62 in two ways:

Every wire is protected by a Tranzorb diode which transitions from an open to

a full clamp between ±27 to ±35 VDC. Additionally, the Connector Panel uses

Tranzorb diodes on every I/O line for double protection.

High-voltage tolerant front-end receivers/drivers are used. All components

connected to the external pins can tolerate up to ±40V. For example, the TTL

and wide range inputs use protectors that normally look like 100 Ohm resistors,

but open at high voltage.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–16

Run Time FPGA Configuration

The SIGMET I/O-62 card is built around a 100K–Gate FPGA which, in addition to driving the

I/O signals on the 62-position connector, also coordinates the PCI and Softplane traffic. These

chips are SRAM–based, meaning that they are configured at run time. This allows the FPGA

code to be automatically upgraded during each RVP8 code release without needing to physically

reprogram any parts.

The board’s basic I/O services use up only 40% of the complete FPGA. The leftover space

makes it possible to add smart processing right on the I/O-62 board to handle custom needs. For

example the 16–bit floating–point (I,Q) data in the previous example could be reformatted into a

32–bit fixed–point stream. Other examples include generating custom serial formats, data

debouncing, and signal transition detection. In general, I/O functions that would either be

tedious or inappropriate for the host computer SBC can likely be moved onto the I/O-62 card

itself.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–17

1.2 Comparison of Analog vs Digital Radar Receivers

1.2.1 What is a Digital IF Receiver?

A digital IF receiver accepts the analog IF signal (typically 30 MHz), processes it and outputs a

stream of wide dynamic range digital “I” and “Q” values. These quantities are then processed to

obtain the moment data (e.g., Z, V, W or polarization variables). Additionally, the digital

receiver can accept the transmit pulse “burst sample” for the purpose of measuring the

frequency, phase and power of the transmit pulse. The functions that can be performed by the

digital receiver are:

IF band pass filtering

“I” and “Q” calculation over wide dynamic range

Phase measurement and correction of transmitted pulse for magnetron systems –

from burst sample

Amplitude measurement and correction of transmitted pulse – from burst sample

Frequency measurement for AFC output – from burst sample

The digital approach replaces virtually all of the traditional IF receiver components with flexible

software-controlled modules that can be easily adapted to function for a wide variety of radars

and operational requirements.

The digital receiver approach made a very rapid entry into the weather radar market. Up until

the about 1997 weather radars were not supplied with digital receivers. Today in 2003 nearly all

new weather radars and weather radar upgrades use the digital receiver approach. Much of this

rapid change is attributed to the previous generation RVP7 which is the most widely sold

weather radar signal processor of all time.

The number one advantage of a digital receiver is that it achieves a wide linear dynamic range

(e.g., >95dB depending on pulse width) without having to use AGC circuits which are complex

to build, calibrate and maintain. However, there are other advantages as well:

Lower initial cost by eliminating virtually all IF receiver components.

Lower life cycle cost do to reduced maintenance.

Selectable IF frequency.

Software controlled AFC with automatic alignment.

Programmable band pass filter

Dual or multiple IF multiplexing

Improved remote monitoring down to the IF level.

The following sections compare the digital receiver approach to the analog receiver approach.

This illustrates the advantages of the digital approach and what functions are performed by a

digital receiver.

Introduction and Specifications

RVP8 User’s Manual

May 2003

1–18

1.2.2 Magnetron Receiver Example

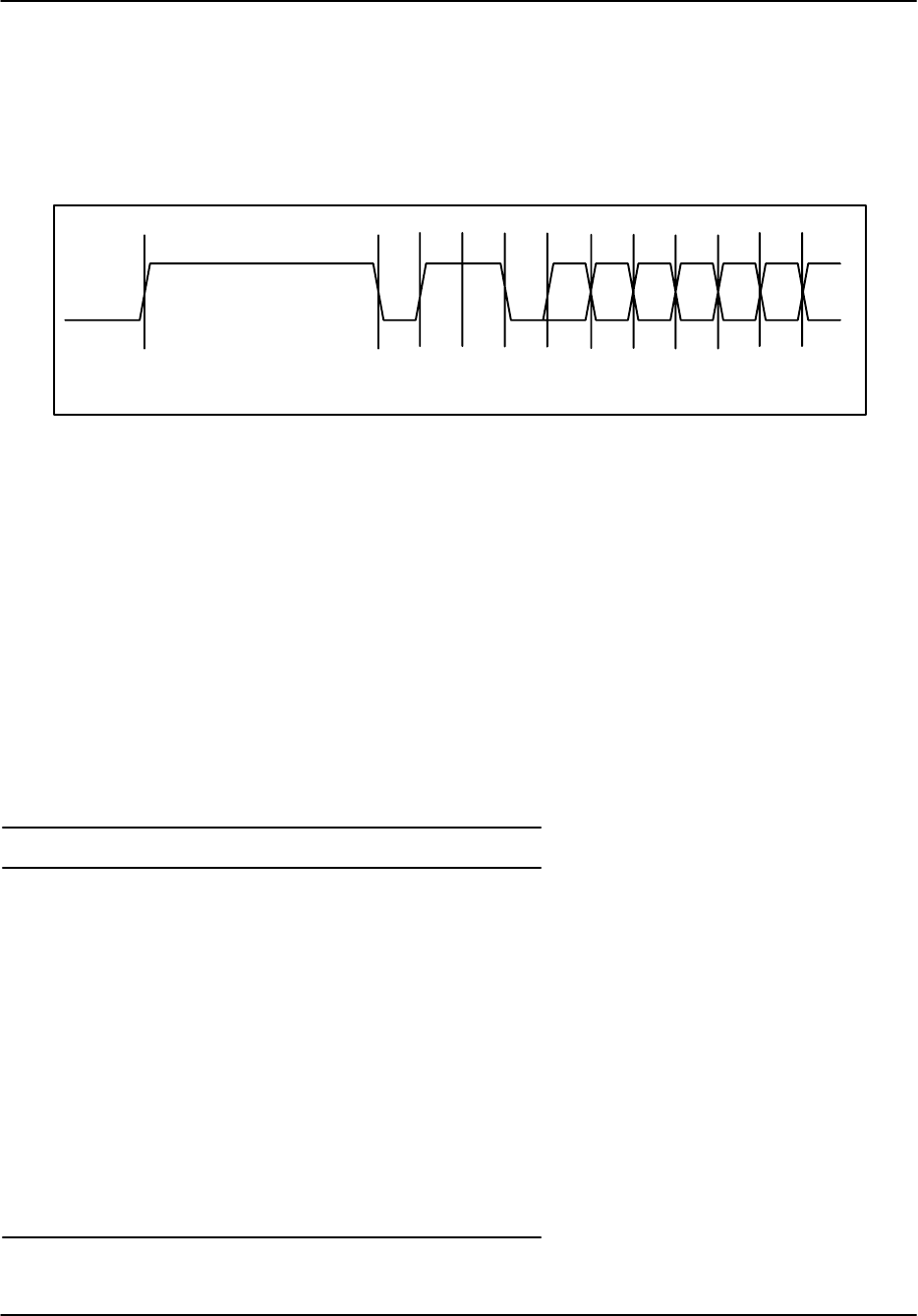

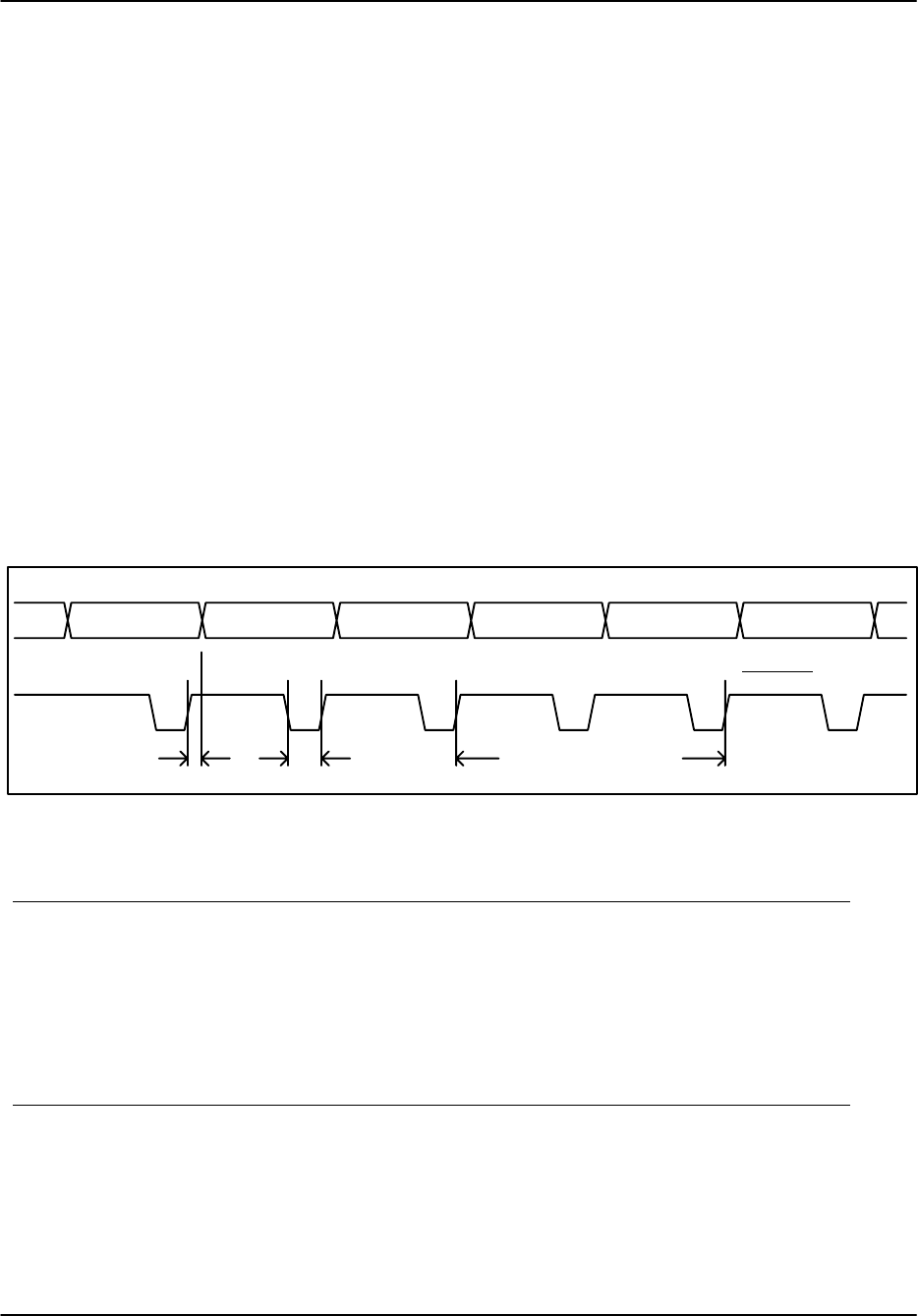

A typical analog receiver for a magnetron system is shown in the top portion of Figure 1–1. The

received RF signal from the LNA is first mixed with the STALO (RF–IF) and the resulting IF

signal is applied to one of several bandpass filters that match the width of the transmitted pulse.

The filter selection is usually done with relays. The narrow band waveform is then split. Half is

applied to a LOG amplifier having a dynamic range of 80–100dB, from which a calibrated