HARRIS TR-0017-E Sitepro Base Station User Manual Site Pro Manual Part 1

HARRIS CORPORATION Sitepro Base Station Site Pro Manual Part 1

HARRIS >

Contents

Site Pro Manual Part 1

Maintenance Manual

MM101271V1 R2A

SitePro™ Controller

Shelf Assembly EA101209V1

ADDENDUM NUMBER 1 TO SITEPRO MAINTENANCE MANUAL

MM101271V1 R2A

This addendum adds an improved high-speed data (HSD) adjustment procedure to the following manuals:

• SitePro Controller Maintenance Manual MM101271V1 R2A

• SitePro Simulcast Controller Card Maintenance Manual MM101509V1 R1A

• GPS Simulcast Systems (with SIM and SitePro Controllers)

System Alignment and Field Testing Procedures MM101724V1 R1A

This improved procedure allows the adjustment to be made on-the-fly without the need to put the SitePro

Controller into Test Mode. The adjustment range is the same as with the earlier procedure [two hexadecimal

digits 00-FF]. The values entered will take effect immediately. By writing these values to EEprom they will

persist through a reset. From a hyper-terminal connected to the SitePro Controller serial port1 perform the

following:

HIGH-SPEED DATA ADJUSTMENT PROCEDURE

Adjust HSD by modifying the pot setting. Once the correct level is found it must be stored in permanent

memory.

1. Adjust the 'real time' high-speed level:

SI2C 50 1 5 <rtn> sets slave device for all subsequent read/write operations (50 is EE pot)

2. Read current data from the HSD pot:

RI2C A9 A9 <rtn> reads current data at specified address range (A9 is location of the HSD pot)

3. Write new values to the HSD pot. The value from step 2 provides an initial set point. The command to

write a value is:

WI2C A9 xx <rtn> were xx is the hexadecimal value written to the HSD pot. Write new values

until the desired deviation is achieved.

4. Store the new value which achieves the desired deviation into permanent memory (novRAM) using the

following commands:

SI2C A6 2 5 <rtn> sets slave device for all subsequent read/write operations (A6 is EEprom)

WI2C 03 xx <rtn> writes new value of the HSD Pot in EEprom (03 is location of HS level)

RI2C 03 03 <rtn> reads current value of the HSD Pot from EEprom (to check if written

correctly)

1 This procedure can also be performed through an ethernet port. Refer to the applicable manual for instructions.

2MM101271V1 R2A

NOTICE!

This manual covers products manufactured and sold by M/A-COM Private Radio Systems, Inc.

NOTICE!

Repairs to this equipment should be made only by an authorized service technician or facility designated by the supplier. Any

repairs, alterations or substitution of recommended parts made by the user to this equipment not approved by the

manufacturer could void the user's authority to operate the equipment in addition to the manufacturer's warranty.

NOTICE!

The software contained in this device is copyrighted by M/A-COM Private Radio Systems, Inc. Unpublished rights are

reserved under the copyright laws of the United States.

This manual is published by M/A-COM Private Radio Systems, Inc. without any warranty. Improvements and changes to this manual necessitated by

typographical errors, inaccuracies of current information, or improvements to programs and/or equipment, may be made by M/A-COM Private Radio

Systems, Inc., at any time and without notice. Such changes will be incorporated into new editions of this manual. No part of this manual may be

reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the

express written permission of M/A-COM Private Radio Systems, Inc.

EDACS is a registered trademark, and Aegis, ProVoice, GETC and SitePro are trademarks of M/A-COM Private Radio Systems, Inc.

Copyright 2002, M/A-COM Private Radio Systems, Inc. All rights reserved.

TABLE OF CONTENTS

MM101271V1 R2A 3

TABLE OF CONTENTS

Page

1.0 SPECIFICATIONS ................................................................................................................................................3

2.0 RELATED PUBLICATIONS................................................................................................................................3

3.0 SAFETY SYMBOLS AND INFORMATION......................................................................................................3

4.0 INTRODUCTION ..................................................................................................................................................3

4.1 OVERVIEW.............................................................................................................................................................3

4.2 OPERATIONAL FEATURES ......................................................................................................................................3

4.3 OPTIONS AND ACCESSORIES ..................................................................................................................................3

4.4 SUMMARY..........................................................................................................................................................3

5.0 MAINTENANCE AND SERVICE .......................................................................................................................3

5.1 APPLICATIONS ..................................................................................................................................................3

5.2 COMPATIBILITY AND MIGRATION ..............................................................................................................3

5.3 SYSTEM EXTERNAL INTERFACES................................................................................................................3

5.3.1 Station Control ............................................................................................................................................3

5.3.2 Simulcast Control........................................................................................................................................3

5.3.3 Conventional Control..................................................................................................................................3

5.3.4 Voter Control...............................................................................................................................................3

5.3.5 Asynchronous Serial Ports ..........................................................................................................................3

5.3.6 Synchronous Serial Ports ............................................................................................................................3

5.3.7 Power ..........................................................................................................................................................3

6.0 DESCRIPTION ......................................................................................................................................................3

6.1 INDICATORS AND CONTROLS.......................................................................................................................3

6.1.1 Indicators ....................................................................................................................................................3

6.1.2 Controls.......................................................................................................................................................3

6.2 ROCKWELL MODEM ........................................................................................................................................3

6.3 LOW SPEED AND HIGH SPEED DATA FILTERS..........................................................................................3

6.3.1 Low Speed Data Decode Filter ...................................................................................................................3

6.3.2 High Speed Data Encode Filter...................................................................................................................3

6.4 INTERFACE CONNECTIONS ...........................................................................................................................3

6.5 COMMUNICATION LINKS ...............................................................................................................................3

7.0 CIRCUIT ANALYSIS............................................................................................................................................3

7.1 SHELF ASSEMBLY ............................................................................................................................................3

7.2 INTERCONNECT BOARD (A1).........................................................................................................................3

7.3 CONTROLLER BOARD (A2).............................................................................................................................3

7.3.1 Block Diagram ............................................................................................................................................3

7.3.2 System I/O ...................................................................................................................................................3

7.3.3 Backplane....................................................................................................................................................3

7.3.4 CPU.............................................................................................................................................................3

7.3.5 SitePro Modem Board Connector ...............................................................................................................3

7.3.6 Electrically Programmable Logic Device (EPLD)......................................................................................3

7.3.7 Ethernet Ports..............................................................................................................................................3

7.3.8 I2C Bus.........................................................................................................................................................3

7.3.9 Memory........................................................................................................................................................3

7.4 SITEPRO MODEM BOARD..................................................................................................................................3

7.4.1 Modems .......................................................................................................................................................3

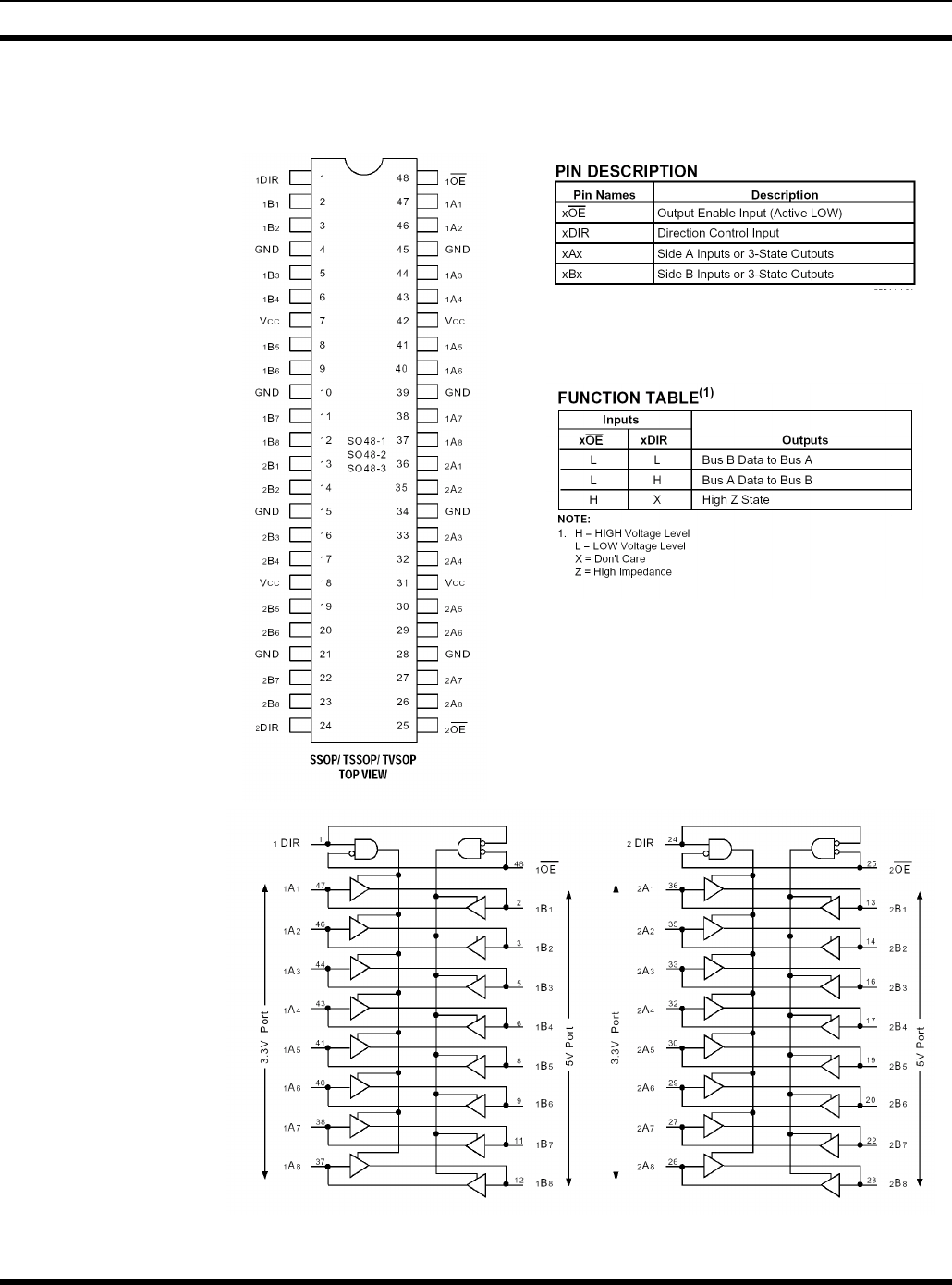

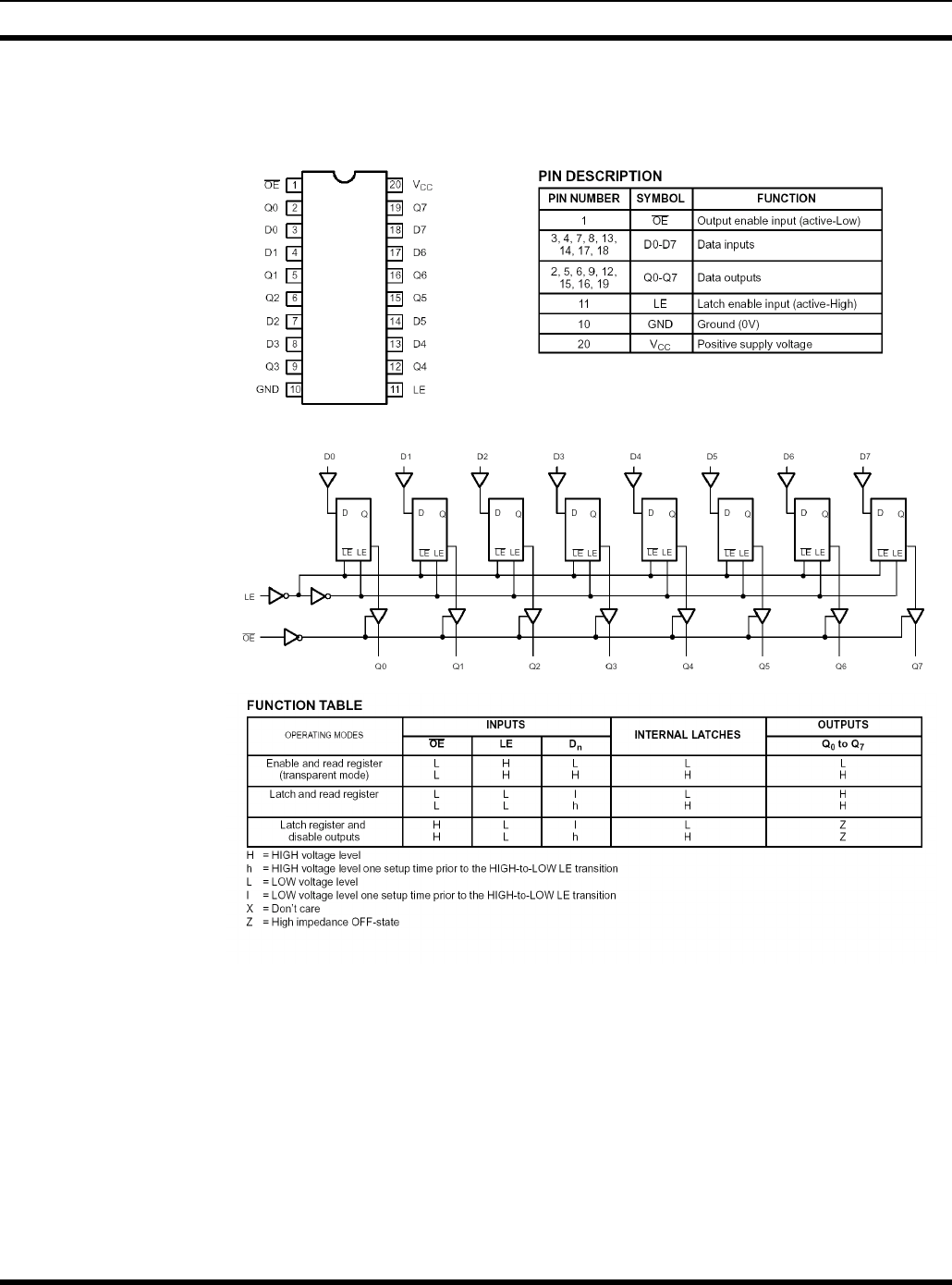

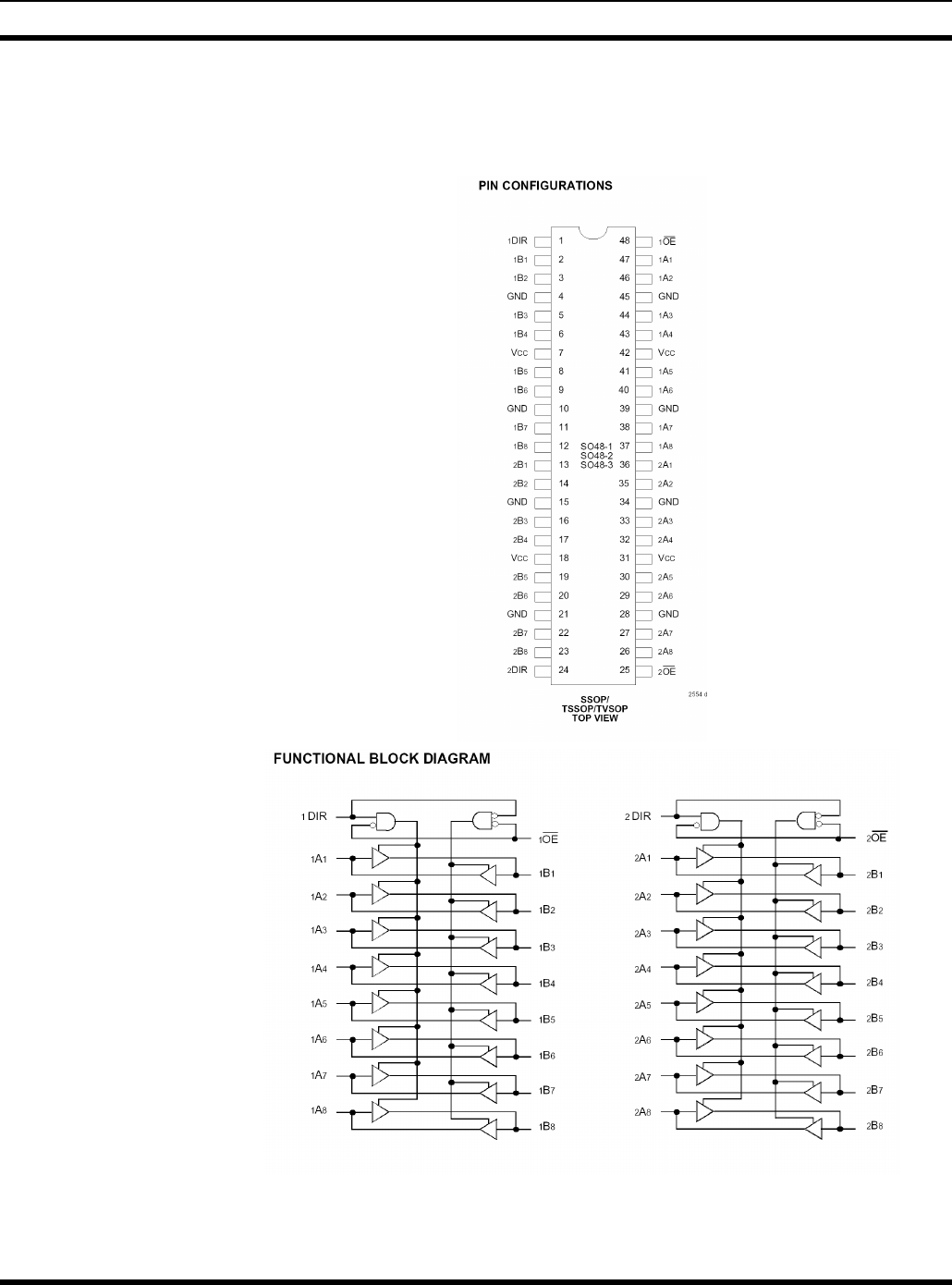

7.4.2 3.3V/5V Interface.........................................................................................................................................3

7.4.3 Microprocessor ...........................................................................................................................................3

7.4.4 Code Memory ..............................................................................................................................................3

7.4.5 Data Memory...............................................................................................................................................3

TABLE OF CONTENTS

4MM101271V1 R2A

TABLE OF CONTENTS

Page

7.4.6 Dual Port Ram............................................................................................................................................ 3

7.4.7 Troubleshooting Aids.................................................................................................................................. 3

7.5 ROCKWELL MODEM INTERFACE CARD (A3) ............................................................................................ 3

7.6 ANALOG BOARD (A4) ..................................................................................................................................... 3

7.6.1 Quad ADC and Single DAC ....................................................................................................................... 3

7.6.2 8-Bit I/O Expander for I2C Bus................................................................................................................... 3

7.6.3 –5 Volt Generation ..................................................................................................................................... 3

7.6.4 High-Speed Data Transmit Filters.............................................................................................................. 3

7.6.5 Clock Generation........................................................................................................................................ 3

7.6.6 Low -Speed Data Decode Filters and Slicer............................................................................................... 3

7.6.7 Low Speed Data Encode Filter................................................................................................................... 3

7.6.8 Simulcast Control Circuits.......................................................................................................................... 3

7.7 POWER SUPPLY (A5) PS101328V1 ................................................................................................................. 3

7.8 MISCELLANEOUS INFORMATION................................................................................................................ 3

7.8.1 Serial Port Data Format............................................................................................................................. 3

8.0 PERSONALITY PROGRAMMING ................................................................................................................... 3

8.1 PROGRAMMING A PERSONALITY ............................................................................................................... 3

9.0 TROUBLESHOOTING ........................................................................................................................................ 3

9.1 ON SITE TROUBLESHOOTING....................................................................................................................... 3

9.2 IN CASE OF DIFFICULTY ................................................................................................................................ 3

9.3 SITEPRO SHELF TEST...................................................................................................................................... 3

9.3.1 Equipment Needed...................................................................................................................................... 3

9.3.2 RF Data Loop Test...................................................................................................................................... 3

9.3.3 Modem Loop Test ....................................................................................................................................... 3

9.3.4 Loopback Connectors ................................................................................................................................. 3

9.4 FIELD TROUBLESHOOTING GUIDE ............................................................................................................. 3

9.4.1 SitePro Controller Board ........................................................................................................................... 3

9.4.2 SitePro Modem Board Tests From The 860 ............................................................................................... 3

9.4.3 Modem Board Tests Using Simon............................................................................................................... 3

9.4.4 Analog Board.............................................................................................................................................. 3

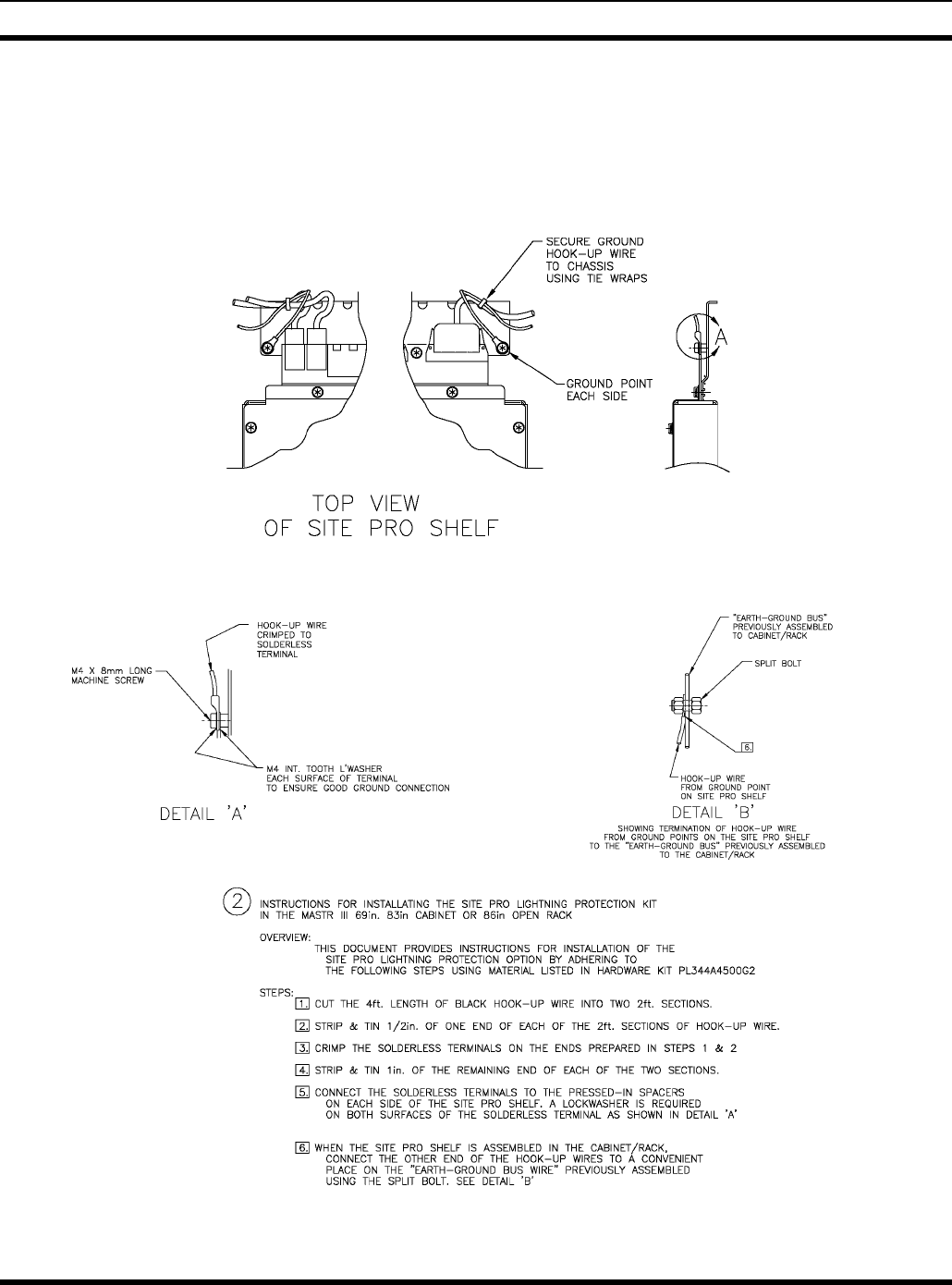

10.0 LIGHTNING PROTECTION GROUNDING .................................................................................................... 3

11.0 PARTS LIST .......................................................................................................................................................... 3

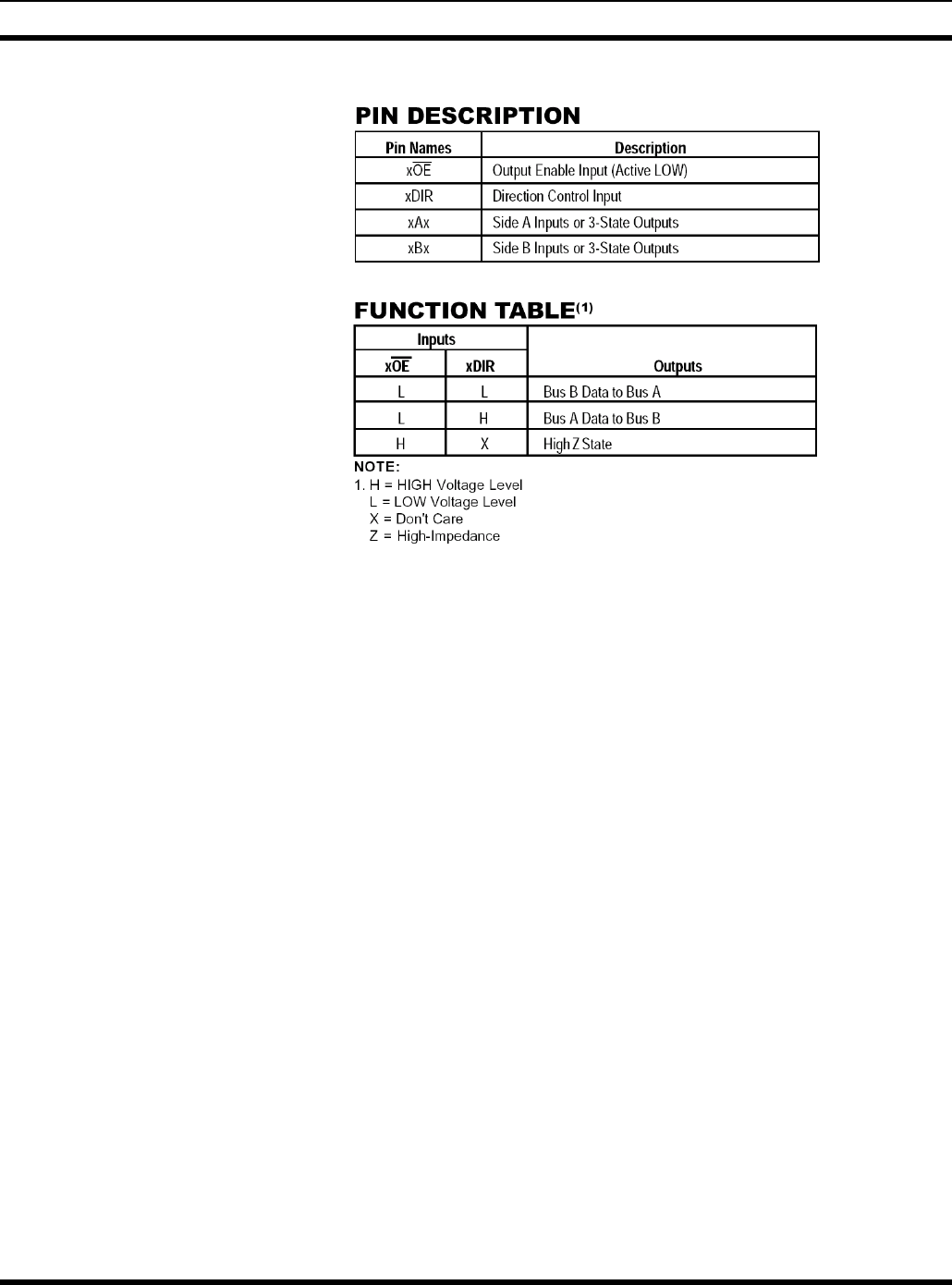

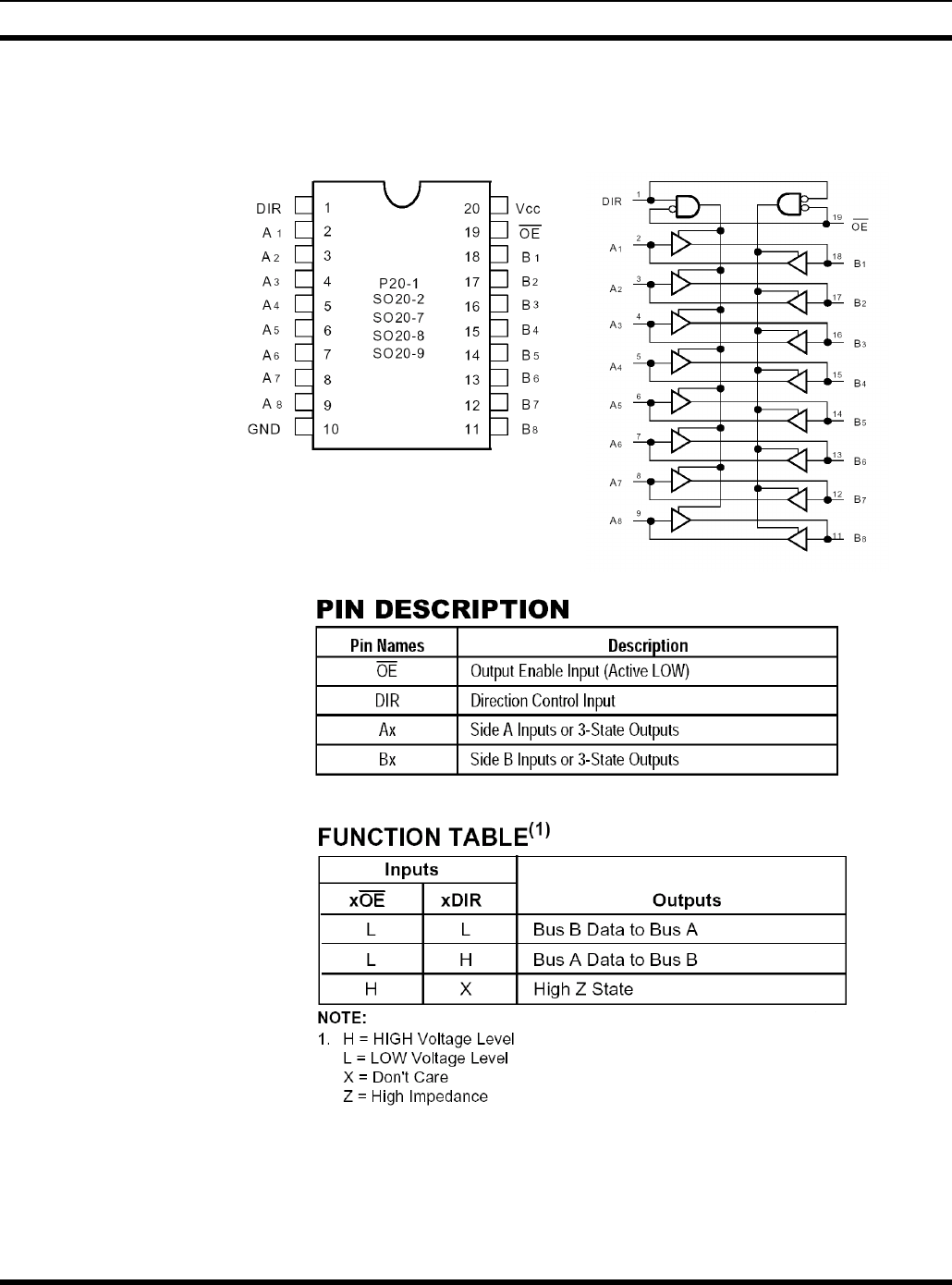

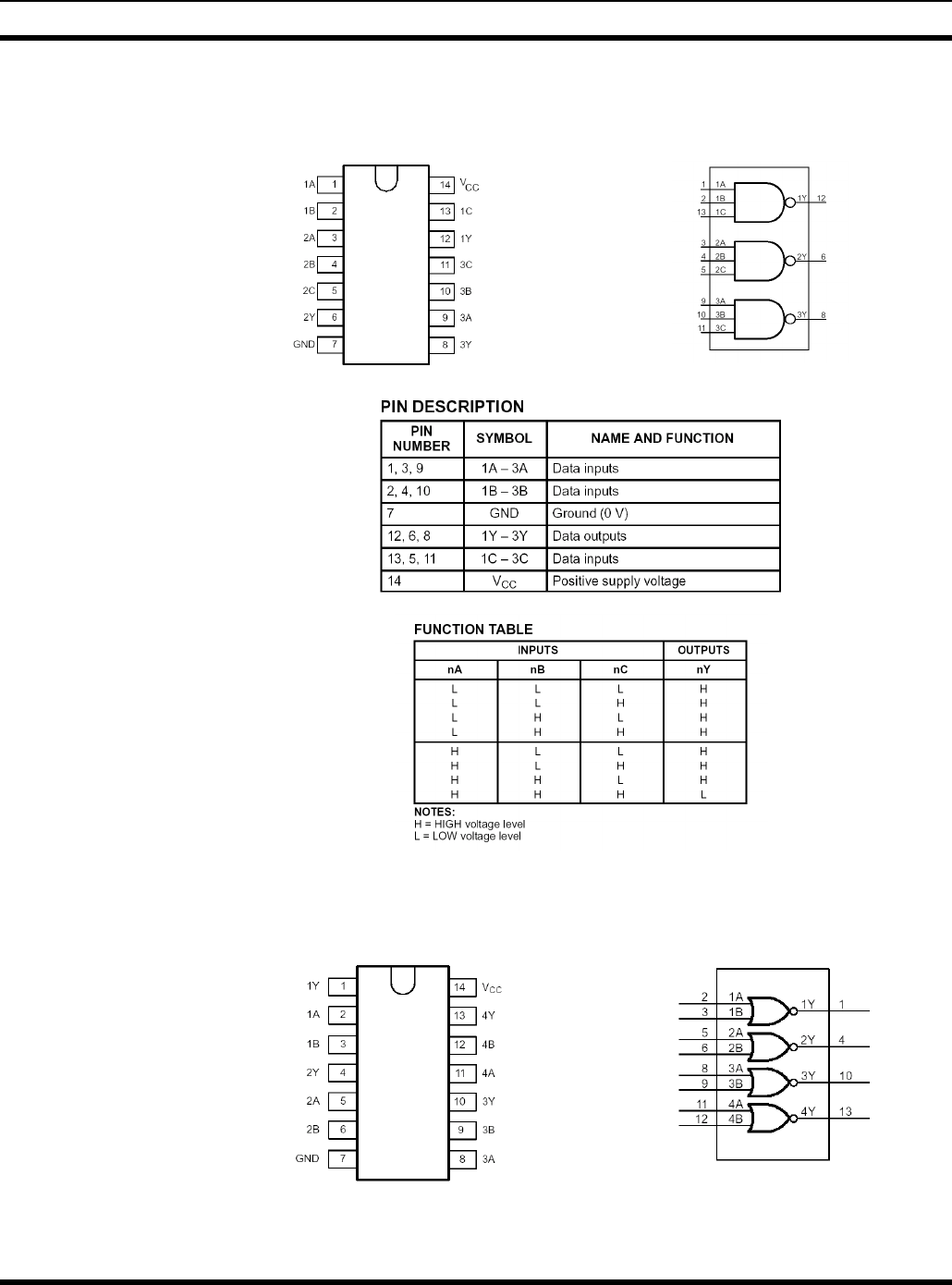

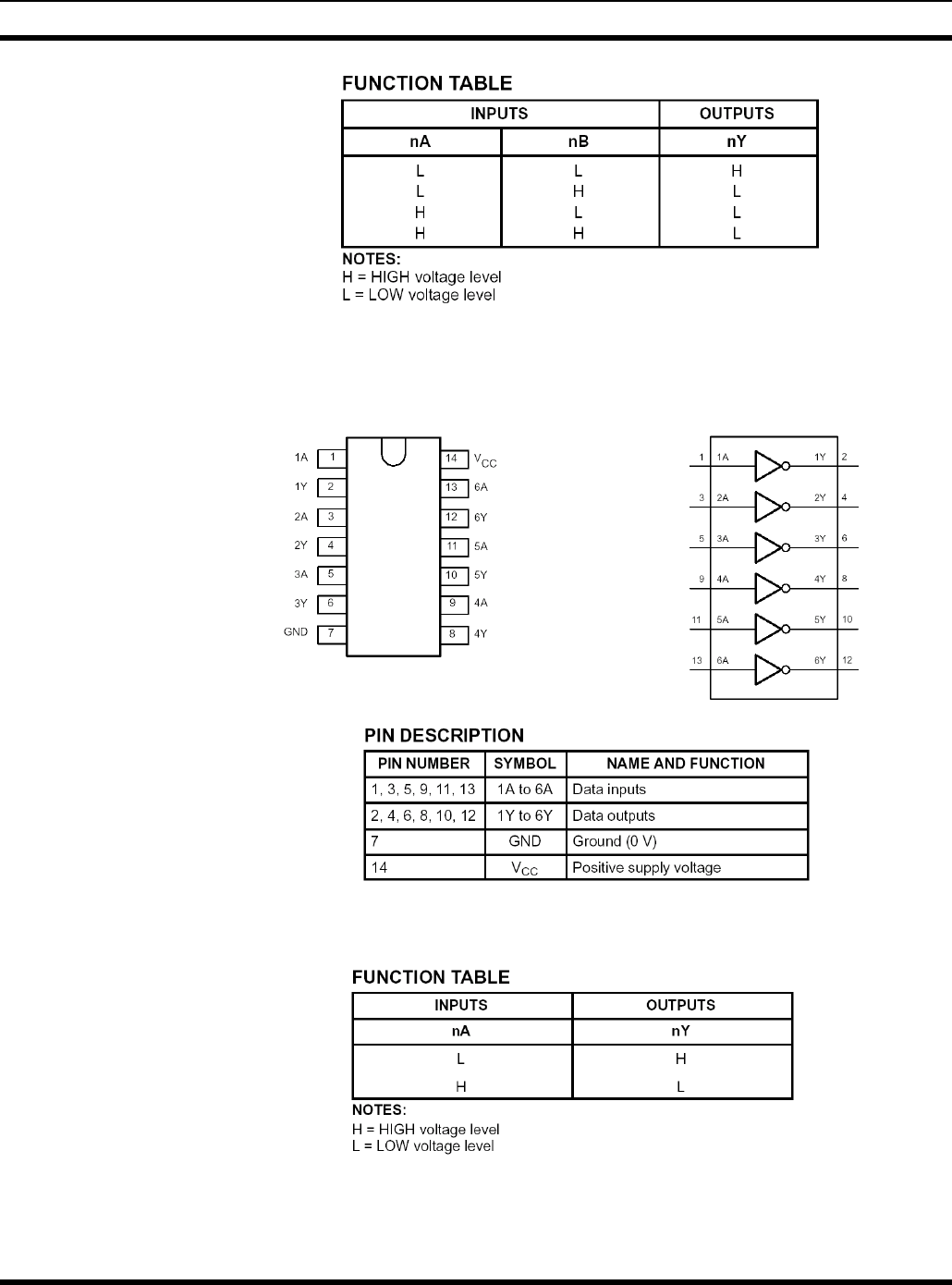

12.0 IC DATA................................................................................................................................................................. 3

12.1 CONTROLLER BOARD (A2)............................................................................................................................ 3

12.2 SITEPRO MODEM BOARD (A2-A1) .................................................................................................................. 3

12.3 ANALOG FILTER BOARD (A4)....................................................................................................................... 3

12.4 DISPLAY MODULE ASSEMBLY (A6) ............................................................................................................ 3

13.0 PRODUCT STRUCTURE ................................................................................................................................ 147

14.0 INTERCONNECTION DIAGRAM ................................................................................................................ 148

15.0 ASSEMBLY DIAGRAM .................................................................................................................................. 149

16.0 OUTLINE DIAGRAMS.................................................................................................................................... 150

16.1 INTERCONNECT BOARD (A1) CB101073V1............................................................................................. 150

16.2 CONTROLLER BOARD (A2) CB101069V1................................................................................................. 151

16.3 SITEPRO MODEM BOARD (A2-A1) CB101074V1 ....................................................................................... 152

16.4 ANALOG BOARD (A4) CB101070V1 .......................................................................................................... 153

16.5 DISPLAY MODULE (A6-A1) CB101077V1 ................................................................................................. 154

TABLE OF CONTENTS

MM101271V1 R2A 5

TABLE OF CONTENTS

Page

17.0 SCHEMATIC DIAGRAMS ..............................................................................................................................155

17.1 INTERCONNECT BOARD (A1) CB101073V1 .............................................................................................155

17.2 CONTROLLER BOARD (A2) CB101069V1..................................................................................................159

17.2.1 SitePro Board Title Page ........................................................................................................................159

17.2.2 Block Diagram ........................................................................................................................................160

17.3 SYSTEM I/O ....................................................................................................................................................161

17.3.1 Backplane................................................................................................................................................162

17.3.2 CPU.........................................................................................................................................................166

17.3.3 Modem Board Connector ........................................................................................................................168

17.3.4 EPLD.......................................................................................................................................................169

17.3.5 Ethernet 10 (10 Mbit PHY)......................................................................................................................170

17.3.6 Ethernet 10/100 (10/100 Mbit PHY) .......................................................................................................171

17.3.7 I2C Bus.....................................................................................................................................................172

17.3.8 Memory....................................................................................................................................................173

17.3.9 QUART ....................................................................................................................................................175

17.4 SITEPRO MODEM BOARD (A2-A1) CB101074V1........................................................................................176

17.5 ANALOG FILTER BOARD (A4) CB101070V1.............................................................................................178

17.6 DISPLAY BOARD (A6-A1) CB101077V1.....................................................................................................181

18.0 CABLE DIAGRAMS .........................................................................................................................................182

18.1 DISPLAY BOARD (A6-W1) DATA CABLE CA101222V1..........................................................................182

18.2 13.8V INPUT POWER CABLE (W1) (INPUT) CA101211V1.........................................................................183

18.3 POWER CABLE (W2) (OUTPUT) CA101212V1.............................................................................................184

18.4 ETHERNET CABLES CA101301V1 THRU V8.............................................................................................185

19.0 EPLD DRAWINGS ............................................................................................................................................186

19.1 SITEPRO TOP LEVEL ....................................................................................................................................186

19.2 LBSW ...............................................................................................................................................................187

19.3 FSL ...................................................................................................................................................................188

19.4 SYNCHRO .......................................................................................................................................................189

19.5 PIN NAMES .....................................................................................................................................................190

FIGURES

Page

Figure 1 - SitePro/Site Interface Module (SIM) Controller......................................................................................... 3

Figure 2 - SitePro Controller Shelf Assembly............................................................................................................. 3

Figure 3 - SitePro Shelf Assembly Block Diagram..................................................................................................... 3

Figure 4 - Controller Board Block Diagram................................................................................................................ 3

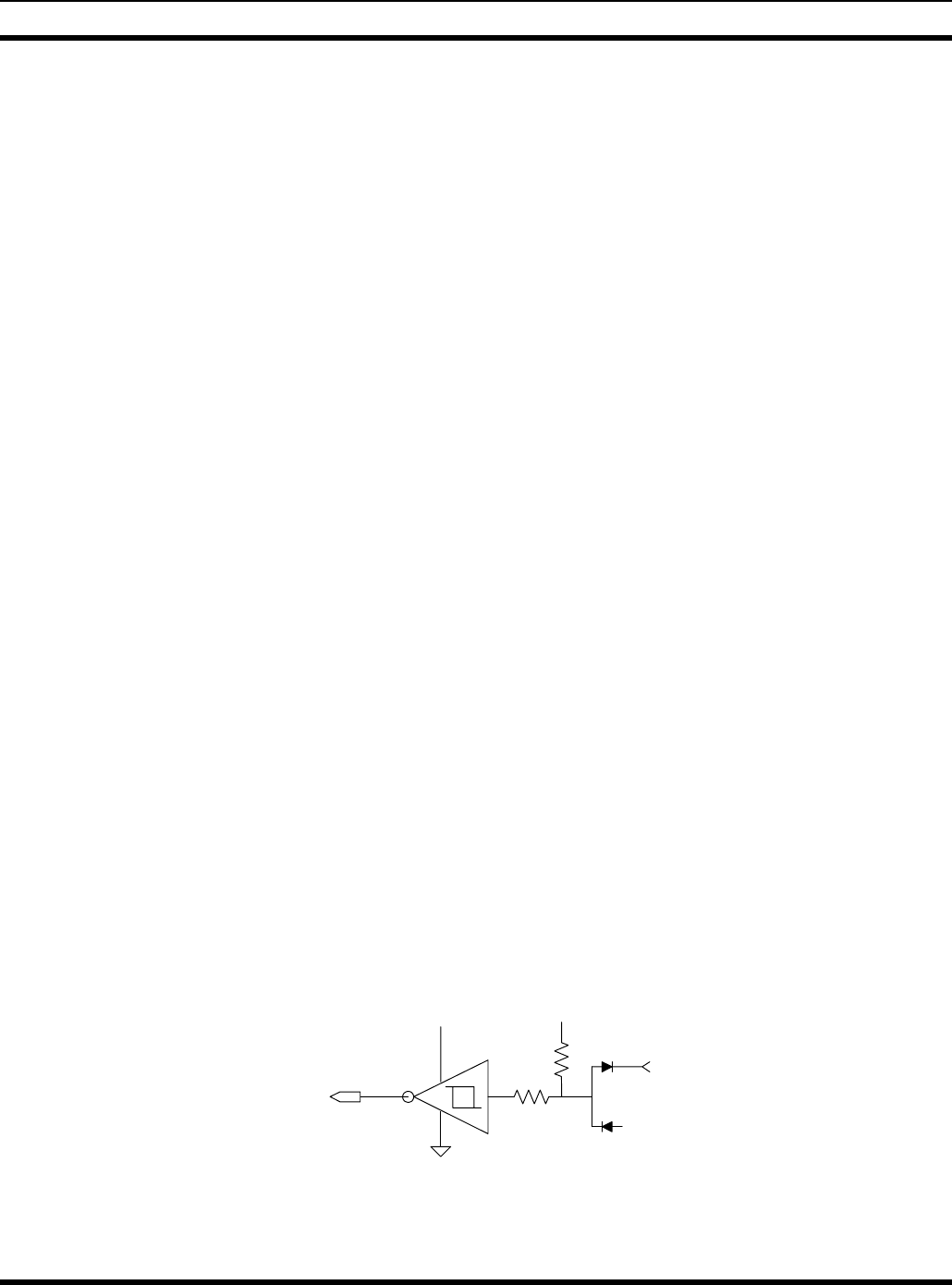

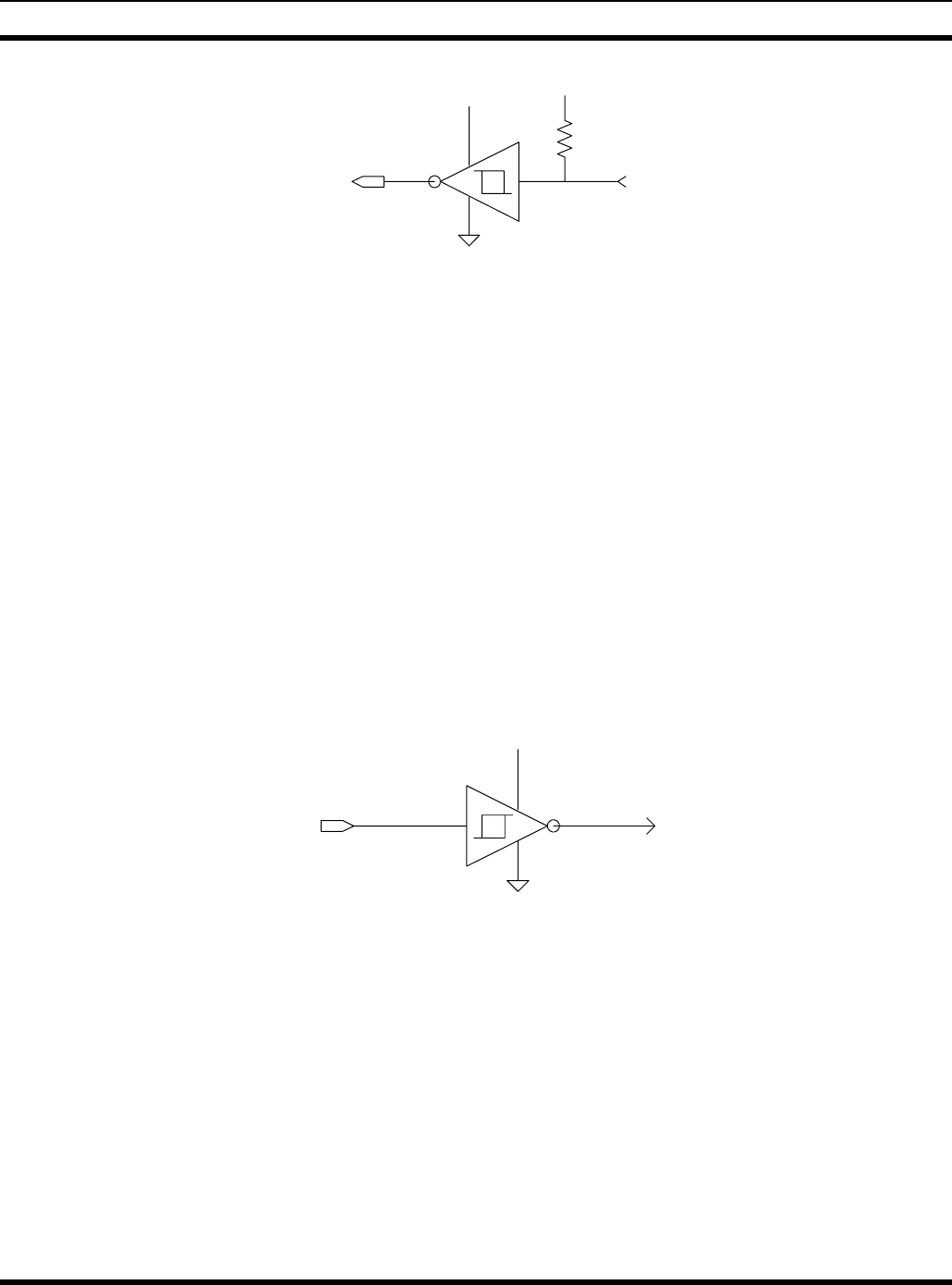

Figure 5 - Input Circuits U18A thru F, U22B thru D and U23C thru F....................................................................... 3

Figure 6 - Input Circuits U22A, E, F, U29D and U32B .............................................................................................. 3

Figure 7 - Output Circuits U29B, C, E & F, U33C, E & F and U34A thru F.............................................................. 3

Figure 8 - Output Circuits U33B, C, E, F, U34A, B, C, D, E, F and U35C, D, E & F................................................3

Figure 9 - Site Pro Modem Board Block Diagram ...................................................................................................... 3

Figure 10 - I2C Address............................................................................................................................................... 3

Figure 11 - Analog Board Block Diagram................................................................................................................... 3

Figure 12 - Programming Hook-Up ............................................................................................................................ 3

Figure 13 - Location of Serial Programming Port J8 (Front Left of SitePro Controller with Hinged Door Open) ..... 3

Figure 14 - RF Data Signal Path.................................................................................................................................. 3

Figure 15 - Phone Line Data Signal Path .................................................................................................................... 3

Figure 16 - Loopback Test Connectors ....................................................................................................................... 3

TABLE OF CONTENTS

6MM101271V1 R2A

TABLE OF CONTENTS

Page

TABLES

Table 1 –Asynchronous Serial Ports............................................................................................................................3

Table 2 - Synchronous Serial Ports..............................................................................................................................3

Table 3 - Interface Connections...................................................................................................................................3

Table 4 - External Processor Interrupt Signals ............................................................................................................3

Table 5 - External Chip Select Signals ........................................................................................................................3

Table 6 - 10 Mbit Ethernet Connections......................................................................................................................3

Table 7 - I2C Bus Addresses ........................................................................................................................................3

Table 8 - DRAM Bank Memory Ranges ..................................................................................................................... 3

Table 9 - Memory Map................................................................................................................................................ 3

Table 10 - 9600 Baud WB Filter Response .................................................................................................................3

Table 11 - 4800 Baud NB Filter Response ..................................................................................................................3

Table 12 - 9600 Baud WB ETSI Filter Response ........................................................................................................3

Table 13 - 4800 Baud NB ETSI Filter Response.........................................................................................................3

Table 14 - 9600 Baud NB Filter Response ..................................................................................................................3

Table 15 - HSD Selection ............................................................................................................................................3

Table 16 - Low Speed Data Decode Filter Response ..................................................................................................3

Table 17 - Acquisition Rates .......................................................................................................................................3

Table 18 - Low-Speed Data Encode Filter Response ..................................................................................................3

Table 19 -Minimum Operating System Requirements ................................................................................................3

Table 20 - Cable Connections......................................................................................................................................3

Table 21 - Current (I) Limits .......................................................................................................................................3

Table 23 - SIMON Commands....................................................................................................................................3

Table 24 - I/O Signal Paths..........................................................................................................................................3

Table 25 - FactoryTest Manual Mode Commands ......................................................................................................3

Table 26 - I/O Output Group A Paths..........................................................................................................................3

Table 27 - FactoryTest Manual Mode Commands (Group B).....................................................................................3

Table 28 - I/O Outputs Group B Paths.........................................................................................................................3

Table 29 - FactoryTest Manual Mode Commands (Group C)..................................................................................... 3

Table 30 - I/O Outputs Group C Paths......................................................................................................................... 3

Table 31 - FactoryTest Command Mode READ Commands ...................................................................................... 3

Table 32 - Group A I/O Input Paths.............................................................................................................................3

Table 33 - READ Commands and Expected Results................................................................................................... 3

Table 34 - I/O Input Group B Paths.............................................................................................................................3

Table 35 - Test Point Levels........................................................................................................................................3

Table 36 - Frequency Response at LSDTX .................................................................................................................3

Table 37 - Circuit Levels .............................................................................................................................................3

Table 38 - High Speed Data Signal Levels..................................................................................................................3

SPECIFICATIONS

MM101271V1 R2A 7

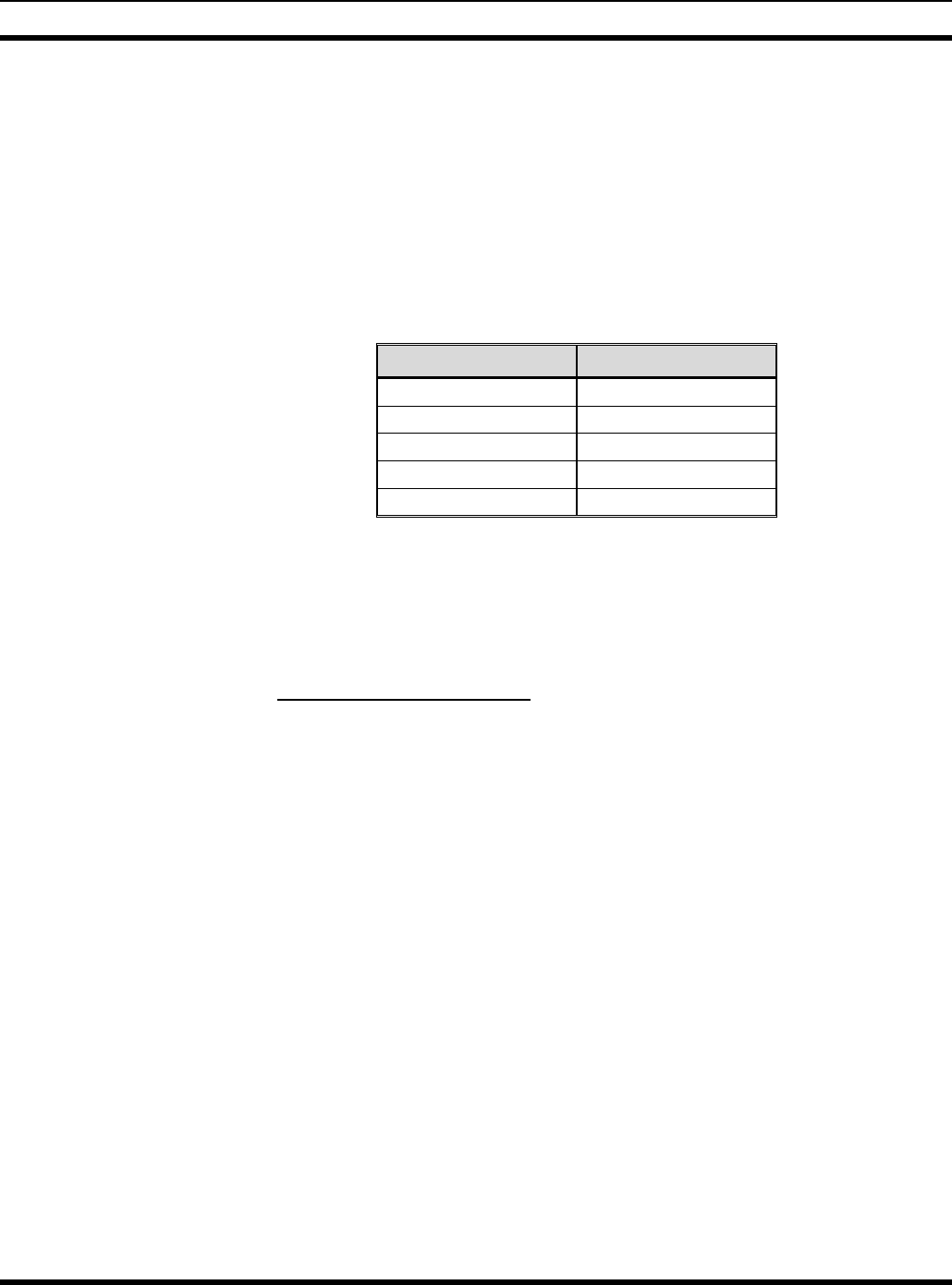

1.0 SPECIFICATIONS1

INPUT VOLTAGE +13.8±20% VDC

CURRENT DRAIN

Without 9600 baud modem 900mA (typical), 1.5 Amps (maximum)

With 9600 baud modem 1.5 Amps (typical), 2 Amps (maximum)

OPERATING TEMPERATURE -22°F to +140°F (-30°C to +60°C)

DIMENSIONS (H x W x D) 1.75 x 17.12 x 15.625 inches

(4.44 x 43.48 x 39.69 cm)

DATA TRANSMISSION

High Speed (RF and phone line) 9600 ±1bps (EDACS Wideband)

Low Speed 150 ±1bps

COMMUNICATION INTERFACE

Redundant Communication Link

Data Levels 0 to 13.8 VDC (nominal)

Data Format 1 start bit, 1 stop bit, and 8/9 data bits

Data Rate 38.4 kbaud

Ethernet Interfaces 10 Mbit

1 These specifications are intended to be used by the service technician during servicing. Refer to the appropriate

Specification Sheet for the complete Specification.

RELATED PUBLICATIONS

8MM101271V1 R2A

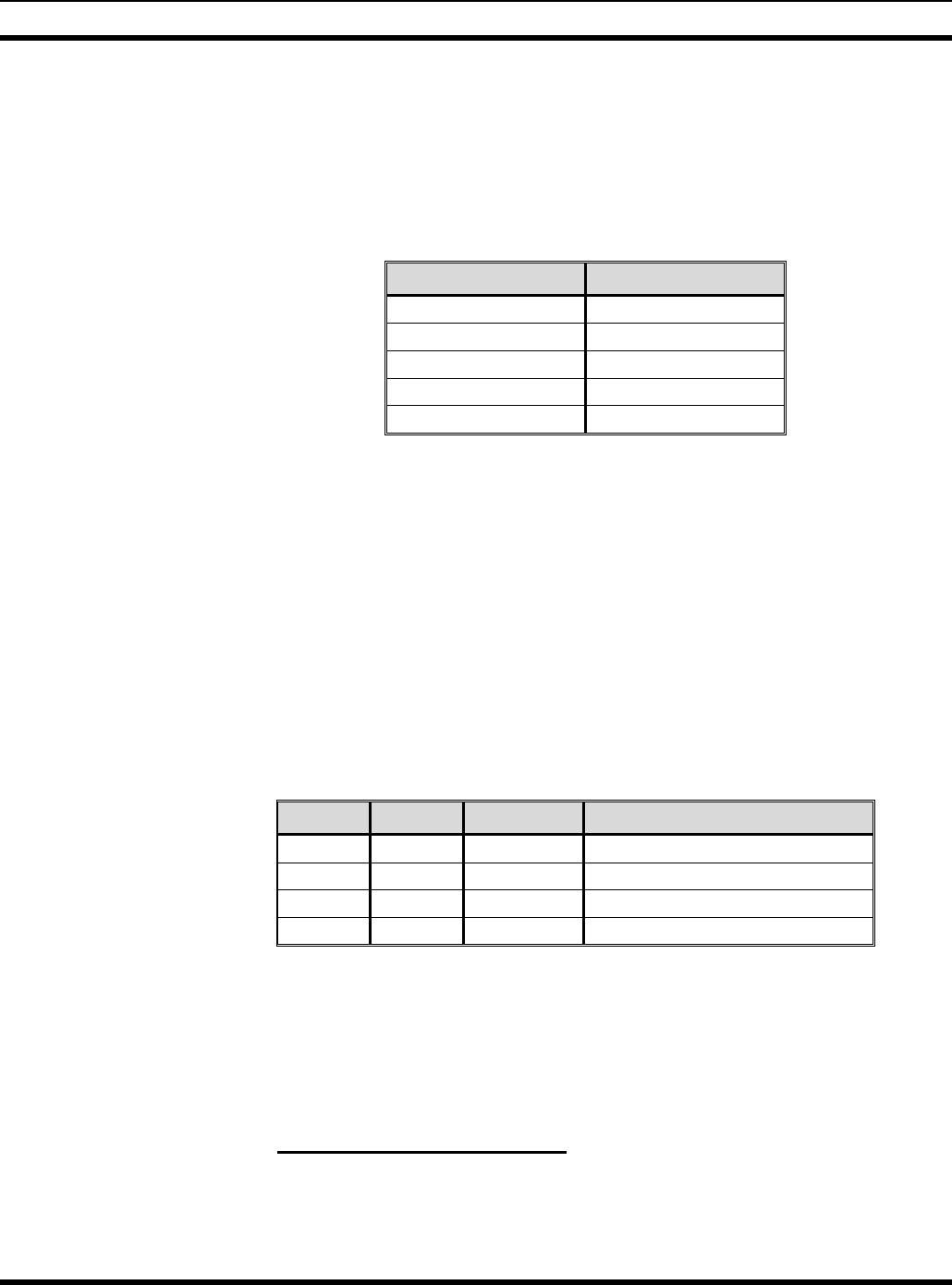

2.0 RELATED PUBLICATIONS

Publication Title

LBI-39152 Rockwell Modem Interface Card ROA 117 2247/1

Rockwell Modem Assembly, RYTUA 921 01/1

RS-232 INTERFACE CARD, ROA 117 2247/2

MM101343V1 SitePro Controller Installation and Configuration Manual

MM101461V1 SitePro Personality Programming Manual

SAFETY SYMBOLS

MM101271V1 R2A 9

3.0 SAFETY SYMBOLS AND INFORMATION

WARNING

The WARNING symbol calls attention to a procedure, practice, or the like,

which, if not correctly performed or adhered to, could result in personal

injury. Do not proceed beyond a WARNING symbol until the conditions

identified are fully understood or met.

CAUTION

The CAUTION symbol calls attention to an operating procedure, practice, or

the like, which, if not performed correctly or adhered to, could result in

damage to the equipment or severely degrade the equipment performance.

NOTE

The NOTE symbol calls attention to supplemental information, which may

improve system performance or clarify a process or procedure.

The ESD symbol calls attention to procedures, practices, or the like, which

could expose equipment to the effects of Electro-Static Discharge. Proper

precautions must be taken to prevent ESD when handling circuit modules.

• The means of disconnecting power from a station cabinet is the cabinet power supply

plug.

• When conducting repair/maintenance, disconnect the cabinet power supply plug from

the AC source.

• In European applications, equipment must be installed in a closed cabinet.

• Only replace components with components specified by M/A-COM Private Radio

Systems.

INTRODUCTION

10 MM101271V1 R2A

4.0 INTRODUCTION

The SitePro Controller was developed by M/A-COM Private Radio Systems as the next

generation trunking controller. This GETC replacement increases site reliability and

security, and enables new site features.

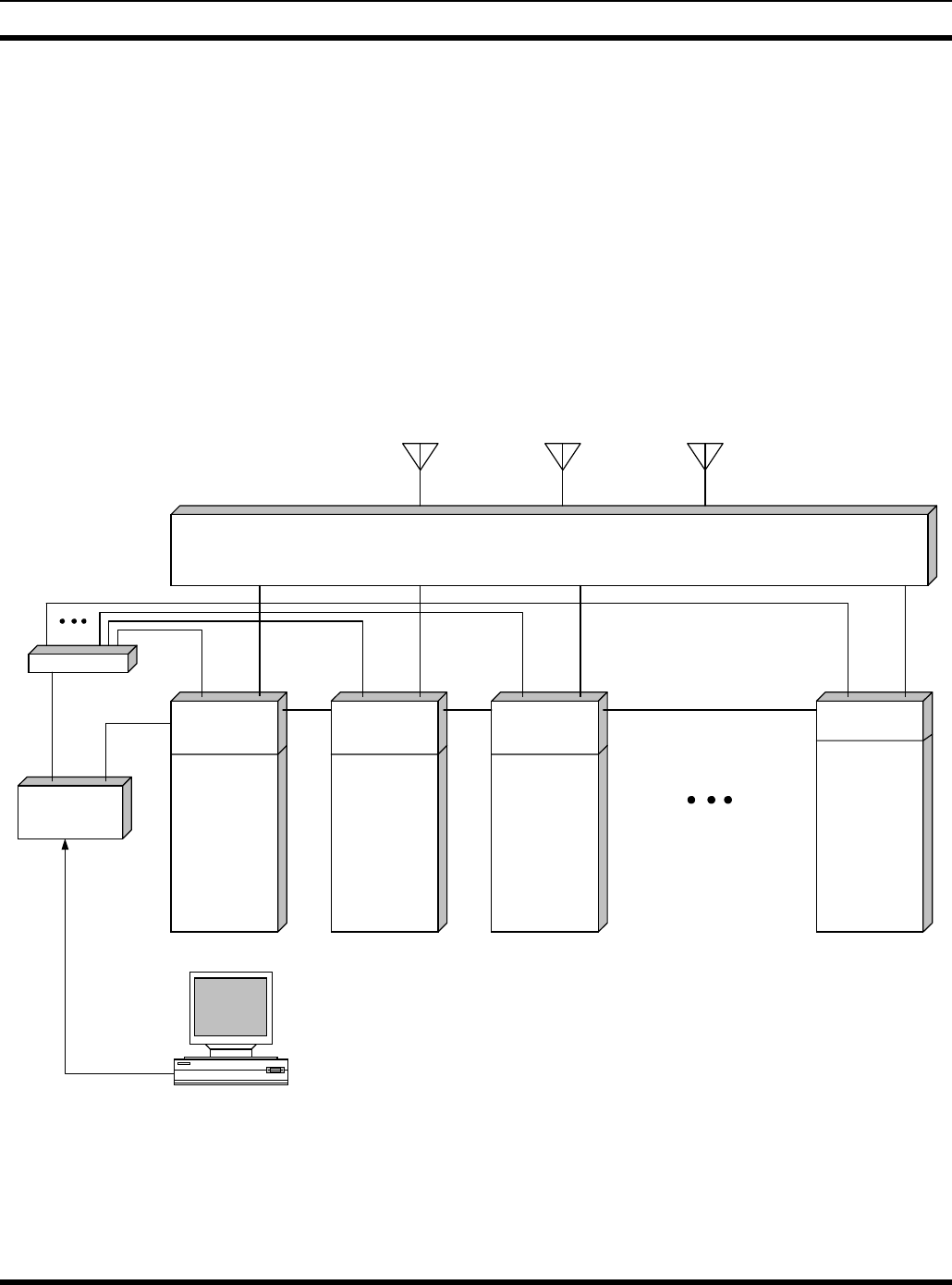

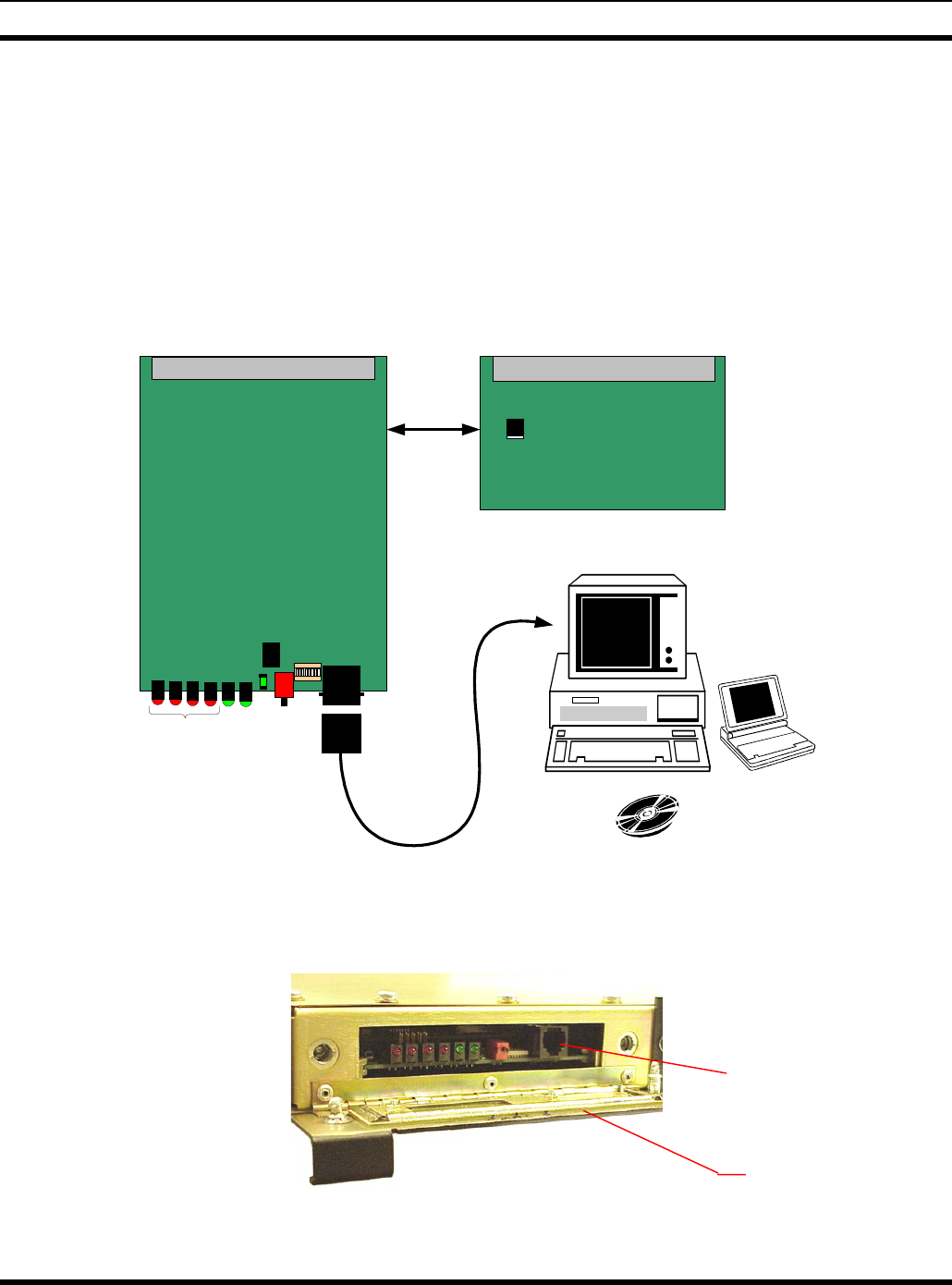

4.1 Overview

SitePro Controller EA101209V1 is the distributed control equipment used at the base

station of an EDACS® or ProVoiceTM communication system. The SitePro Controller

interprets and directs inbound calls, processes these calls, and issues appropriate

commands about how calls are handled. The SitePro Controller is the heart of an EDACS

or ProVoice critical communications system (Figure 1 - SitePro/Site Interface Module

(SIM) Controller).

SitePro

EDACS

Channel

SitePro

EDACS

Channel

SitePro

EDACS

Channel

SitePro

EDACS

Channel

BSL BSL BSL

RF Equipment (Combiner/Multicoupler)

Up to 24

Channels

~V.T

Optional Communications

System Director

Ethernet Hub

Site Interface

Module

BSL

Figure 1 - SitePro/Site Interface Module (SIM) Controller

INTRODUCTION

MM101271V1 R2A 11

4.2 Operational Features

The CSD allows access to the user and site database utilized by the SitePro Controller.

The SitePro Controller offers the following features:

1. Eight Priority Levels – The SitePro Controller prioritizes calls from a list of

individual and group identification numbers (LIDs and GIDs) for use during queuing.

This prioritized list ensures that higher priority calls are processed first for critical

communications.

2. Call Validation – The SitePro Controller checks the ID of every radio attempting to

access the system. An invalid ID attempting to use the system will be denied access,

eliminating system security breeches.

3. Unit Enable/Disable – The SitePro Controller has the capability to disable and

enable radios over the air. This feature prevents intruders from accessing the system

with stolen or misplaced radios.

4. Dynamic Regroup – This feature allows the SitePro Controller to reconfigure radio-

operating groups in response to critical emergency situations.

5. Recent Priority Increments – The SitePro Controller is able to increase the priority

level of ID’s that have recently placed calls. This allows ongoing conversations to

have a higher priority.

6. Local Telephone Interconnect – The SitePro Controller supports local telephone

interconnect. Calls can be made to and from an individual or to a group in an EDACS

or ProVoice system.

7. Multiple Channel Partition (MCP) – Using MCP, the SitePro Controller is capable

of segregating sets of channels for exclusive use by select users. Up to 15 distinct

partitions may be defined to ensure channel availability for critical communications.

8. Toll Call Restriction - The SitePro Controller is able to restrict Hotline telephone

access by radio for both local and long distance calls.

9. Patch and Simulselect - The SitePro Controller allows console dispatchers to

"patch" together different talkgroups. This feature allows maximum response to

emergency situations.

10. Site Configuration - The SitePro Controller is the repository for critical site

configuration data resident on the Communications Systems Director (CSD).

11. Redundant Downlink GETCTM (Optional) - A Downlink GETC shelf provides the

9600-baud Integrated Multisite and Console Controller (IMC) link for

communications control from the repeater site to the dispatch center site or multisite

switch.

4.3 Options and Accessories

Site Sentry Alarm and Control System – The Site Sentry alarm and control equipment

enables the SitePro Controller to monitor key aspects of the site operation, including the

following:

1. Remote reporting of inputs from customer-specific alarm sensors.

2. Remote control of relays that operate customer-specific devices.

INTRODUCTION

12 MM101271V1 R2A

3. Diagnostic testing of system operation.

4. Local display of system status

The Site Sentry also keeps track of transmitter performance and the antenna system. The

parameters monitored to verify the system health are transmitter power, forward and

reflected antenna power, and antenna Voltage Standing Wave Ratio (VSWR).

Site SureCall Test Call System – Site SureCall allows remote channel monitoring and

testing of repeater stations via a Test Unit (TU) radio.

Hotline Local Telephone Interconnect – The SitePro Controller provides the processing

for Hotline. Calls can be made from the Public Switched Telephone Network (PSTN) to

an individual or group as well as from a radio to the PSTN.

4.4 SUMMARY

The SitePro Controller provides the latest control technology to ensure that the EDACS

or ProVoice critical communication system is unmatched in system performance. The

SitePro Controllers are capable of maintaining the following critical communication

features even if the SIM, due to a temporary failure, is taken out or service:

1. Eight Priority Levels

2. Call Validation

3. Recent Priority Increment

4. Multiple Channel Partition

5. Patch and Simulselect

MAINTENANCE AND SERVICE

MM101271V1 R2A 13

5.0 MAINTENANCE AND SERVICE

This manual provides maintenance and servicing information for M/A-COM SitePro

Controller Shelf Assembly EA101209V12. Production versions of this shelf consist of the

following components:

• Shelf Assembly MA101080V1

• Interconnect Board Assembly (A1) CB101073V1

• Controller Board Assembly (A2) CD101069V1

• SitePro Modem Board (A2-A1) CB101074V1

• Rockwell Modem Interface

Card Assembly (A3) ROA 117 2247

Rockwell Modem Assembly (A7) RYTUZ 921 01/1

• Analog Board (A4) CB101070V1

• Power Supply Module (A5) PS-PS101328V1

• Display Module (A6) MA101082V1

Display Board Assembly (A6-A1) CB101077V1

Cable (A6-W1) CA101222V1

• Input Cable to the Power Supply (W1) CA101211V1

• Output Cable from the Power Supply (W2) CA101212V1

5.1 APPLICATIONS

The SitePro Controller can be installed and configured for several different station

applications. Initially the basic configuration is for the EDACS Station Trunking Shelf.

This shelf enables the station to function as part of an EDACS trunked communication

system by providing digital signaling and control of the associated base station. In

addition, the SitePro Controller provides an interface between the base station repeater,

the Site Interface Module (SIM) and other channel SitePro Controller(s) at the same

time.

5.2 COMPATIBILITY AND MIGRATION

The SitePro Controller, with the exception of the Site Controller, is compatible with

GETC compatible devices as follows:

• Downlink GETC

• SIM

• SureCall

• Hotline

• Site Sentry

2 The Service Technician(s) should always consult any application manuals, Software Release Notes (SRN), and Specific

Customer information provided with the system whenever the equipment requires service or repair.

MAINTENANCE AND SERVICE

14 MM101271V1 R2A

The requirements for compatibility and migration are that:

1. The SitePro Controller will only switch modes if the Control Channel fails or a

configuration command is received. The SitePro Controller will, however, change

modes as currently implemented by the GETC. For example, the SitePro Controller

Control Channel can switch modes, without failure or configuration command, if it

detects carrier.

2. For High Speed Data Modulation, the SitePro Controller has a separate Analog Board

(A4) providing software configurable filtering, which is compatible with high-speed

data types.

5.3 SYSTEM EXTERNAL INTERFACES

(SitePro Trunked Interface Specification)

The following is a description of all electrical connections to the SitePro Controller. All

input/output definitions are relative to the SitePro Controller. This configuration supports

EDACS, Simulcast and Voted systems. The analog and digital control signals provide an

interface to a variety of base stations and are grouped by functionality.

5.3.1 Station Control

• LocRxAudio - Analog input

MASTR III level = 1 Vrms, Zin = 100Kohm, bias = ac coupled

This signal is unfiltered local receiver audio from the base station also called

Volume/Squelch or VolSqHi and carries either High Speed Data (control

signaling/digital audio) or Low Speed Data with analog audio. The two components

are internally separated.

• RUS - Digital TTL active high input

This signal is the Receiver UnSquelch signal from the base station and is activated

when a carrier of sufficient signal strength (as determined by the squelch pot setting)

is present.

• LSD - Analog output

level = 300 mVrms

Zout = 100ohm, bias = 0 volts

This signal is the Low Speed Data output to the base station. The signal is

conditioned through a low pass filter to remove frequency components above 300 Hz

to allow multiplexing with analog voice audio.

• HSD - Analog output

level = 1.1 Vrms

Zout = 100ohm, bias = 0 volts

This signal is the High Speed Data output to the base station modulator. The signal is

conditioned through a specially designed filter needed to meet precise RF modulation

bandwidth limitations.

MAINTENANCE AND SERVICE

MM101271V1 R2A 15

• LocPTT - Digital active low open drain output

This signal is the Local PTT control. This line, when low, will key up the base station

transmitter and select the local receiver audio source for transmission.

• RemPTT - Digital active low open drain output

This signal is the Remote PTT control. This line, when low, will key up the base

station transmitter and select the remote audio source for transmission.

• A/DmodCtrl - Digital output TTL

This is the Analog/Digital Modulation Control signal. When high, HSD is routed to

the base station transmit. When low, LSD/audio is routed to the base station transmit.

• HSAcq - Digital output open drain output

This is the High-Speed Acquisition control signal. A high or low signal produces a

corresponding high or low time constant in the limiter circuit.

• LocRxMute - Digital active low output (8.5 volt low Z source)

This signal is the Local Receiver Mute control. This line, when low, blocks the

routing of receiver audio to the base station transmitter and line out. Muting occurs

during HSD transmission, no valid carrier present, or no valid LSD present.

• Walsh1/Walsh2 - Digital output TTL

These two signals are combined to form a two bit Walsh Function DAC. This signal

is the Low Speed Data source.

• Synth_Clk – Digital open drain output

This signal provides the clock source for loading the base station frequency

synthesizer (required for MIIe). Data is clocked on the negative edge of the clock.

The baud rate is approximately 2.4Kbaud.

• Synth_Data – Digital open drain output

This signal provides the data source for loading the base station frequency

synthesizer (required for MIIe). Data is clocked on the negative edge of the clock.

The baud rate is approximately 2.4Kbaud.

• Synth_LdEn – Digital open drain output

This signal is the Synthesizer Load Enable control. This line, when high, permits the

base station frequency synthesizer to be loaded and is used for protection against

invalid transitions on the clock and data lines.

• Synth_Locked – Digital TTL active high input

This is the Synthesizer Locked signal. This line, when high, indicates that the base

station synthesizer is locked. This is used for verifying successful synthesizer loading

and is also continuously monitored as a failure mode.

• PAFail - Digital TTL active high input diode isolated with pull-up

This is the Power Amp Failure indicator. This line, when high, indicates that the base

station PA has failed. A floating line asserts PA Fail.

MAINTENANCE AND SERVICE

16 MM101271V1 R2A

• RemAudioFlag - Digital TTL active low input, diode isolated

This is the Remote Audio Present indicator. This line, when low, indicates that

remote audio from the IMC is present. This is generated by the base station in

response to 2175Hz or E&M from the IMC.

• FSL - Digital open drain bi-directional

output: 300-mA sink (low), 10mA source (high)

input: Zin = 1k ohm

This is the bi-directional Frame Sync Line. The line is used as an output in the

Control Channel and as an input in the Working Channel.

• ADCin – Analog input

level = 0 to 5 volts, Zin = 100Kohm

This is the 8-bit Analog to Digital Converter (ADC) input. This may be used to

monitor station PA power.

5.3.2 Simulcast Control

• ext_PTT - Digital TTL active low input, diode isolated

This is the external source for Local PTT and is only active in a Simulcast

configuration.

• ext_A/Dmodctrl - Digital TTL active low input, diode isolated

This is the external source for the Analog/Digital modulation control and is only

active in a Simulcast configuration.

• ext_150 - RS422 input

This is the external source for Low Speed Data and is only active in a Simulcast

configuration.

• ext_9600baud - RS422 input

This is the external source for High Speed Data and is only active in a Simulcast

configuration.

• bypass - Digital TTL active low input, diode isolated

This is the Simulcast bypass control signal. This line, when low, forces the site to

operate in non-Simulcast mode and is driven by the Simulcast control equipment.

• inhibit - Digital TTL active low input, diode isolated

This signal is the Simulcast alarm indicator. This line, when low, indicates the

presence of a Simulcast alarm and is driven by the Simulcast control equipment.

• txclk_in - Digital TTL active low input, diode isolated

This is the external source for High Speed Clock and is only active in a Simulcast

configuration.

• txclk_alarm - Digital TTL active high output

This signal is the Simulcast Tx Clock alarm indicator. This line, when high, indicates

MAINTENANCE AND SERVICE

MM101271V1 R2A 17

that the external source for High Speed Clock is missing and is only active in a

Simulcast configuration.

• 9.6 REF - External source of systems clock (RS422 input). Only active with

Simulcast

5.3.3 Conventional Control

• CPTT – Digital open drain output

This signal is the Combined PTT control. This line, when low, will key up the base

station transmitter.

• TxCGDis – Digital open drain output

This signal is the Transmit Channel Guard Disable control. This line, when low,

prevents the transmission of Channel.

• CGMon - Digital TTL active low input, diode isolated

This signal is the Channel Guard Monitor control.

5.3.4 Voter Control

• vot_emsq - Digital open collector output

This is the Voter E&M Squelch signal. This line, when pulled up to +12V through a

4.7k ohm pull-up resistor, indicates the presence of E&M from the Voter. Open

output indicates no E&M.

• vot_rcvng - Digital active low input

This is the Voter Receiving signal. This line, when low, indicates that the Voter is

receiving.

5.3.5 Asynchronous Serial Ports

The following asynchronous serial ports provide control links to the SitePro Controller.

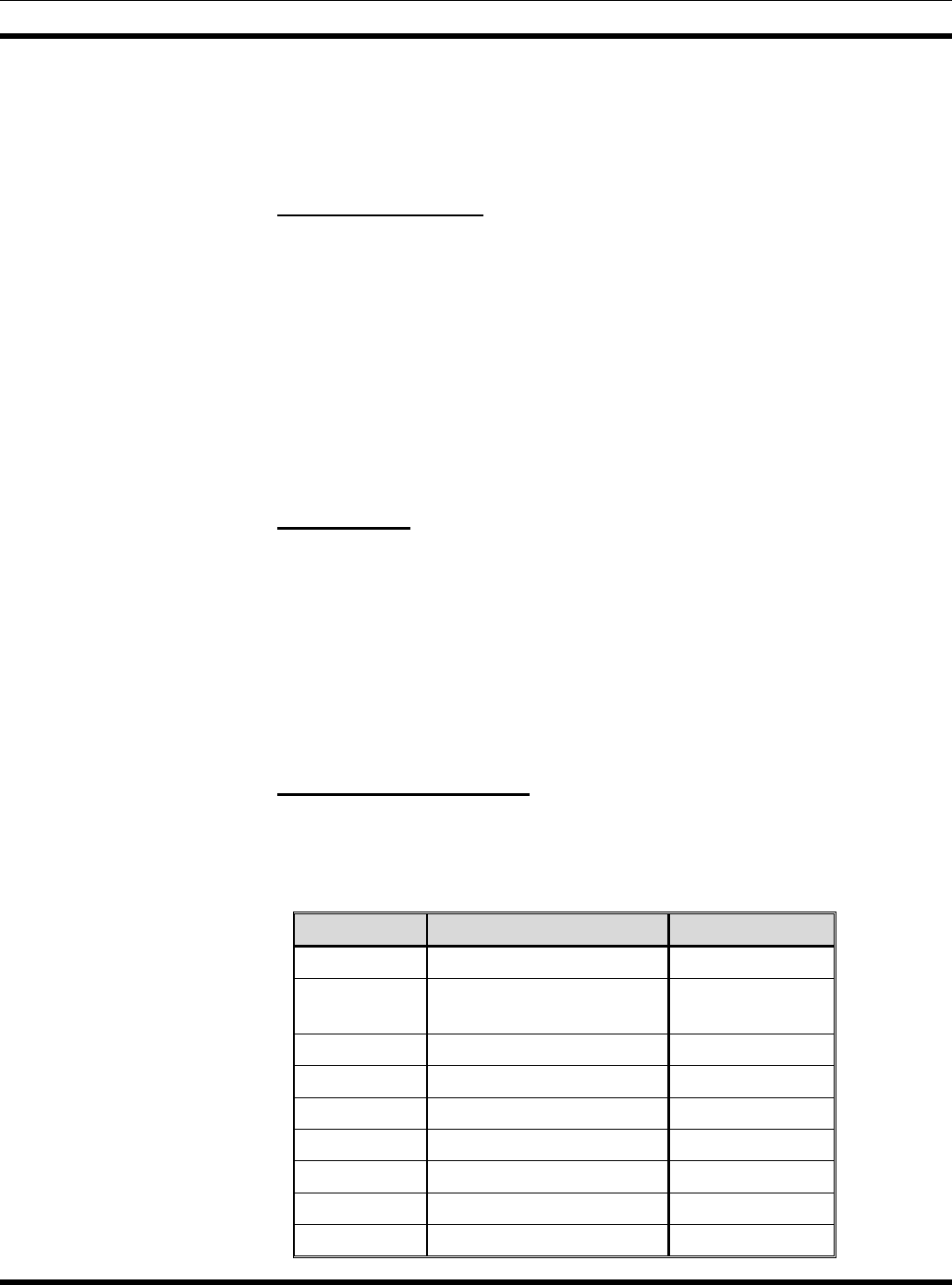

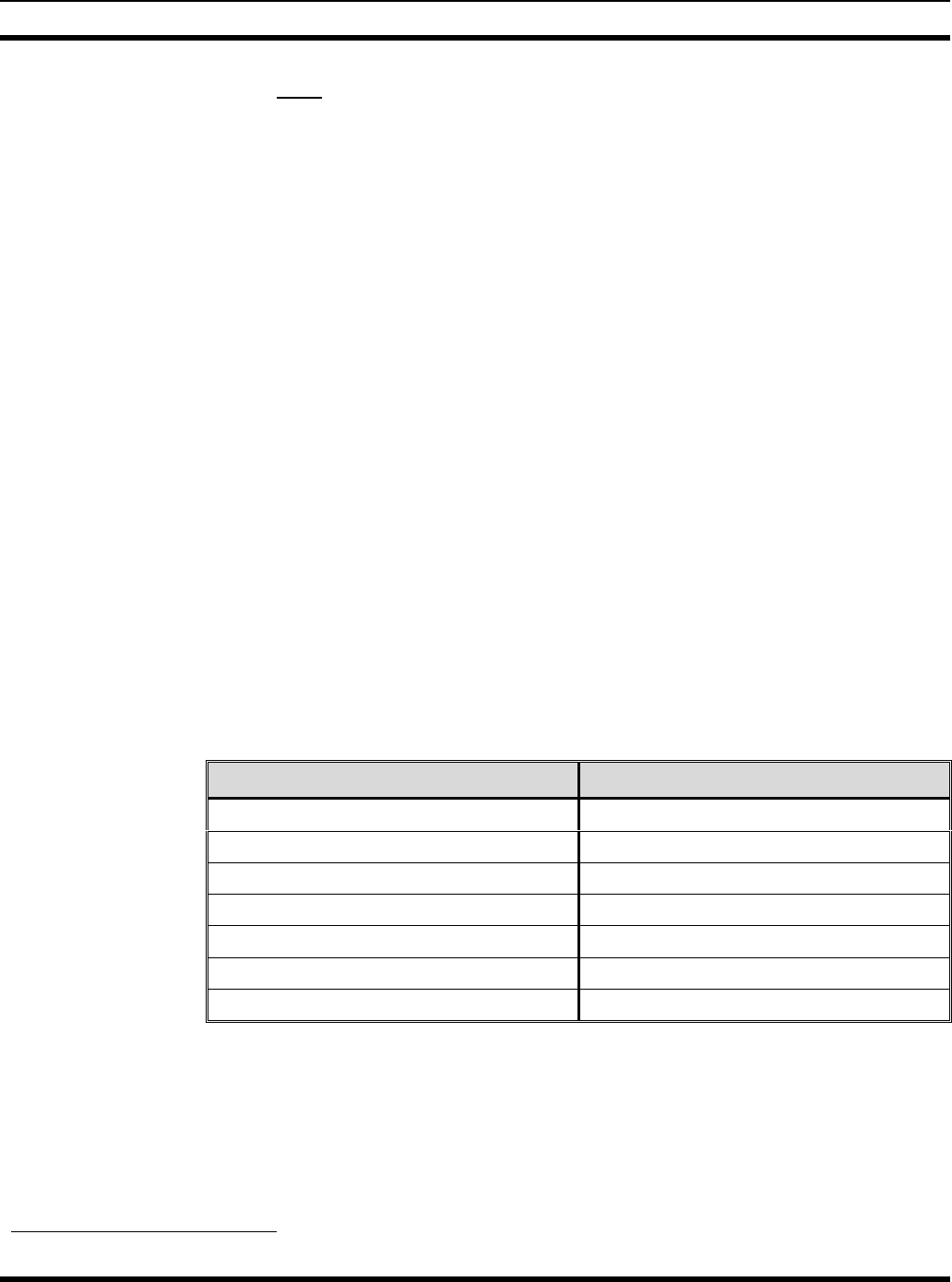

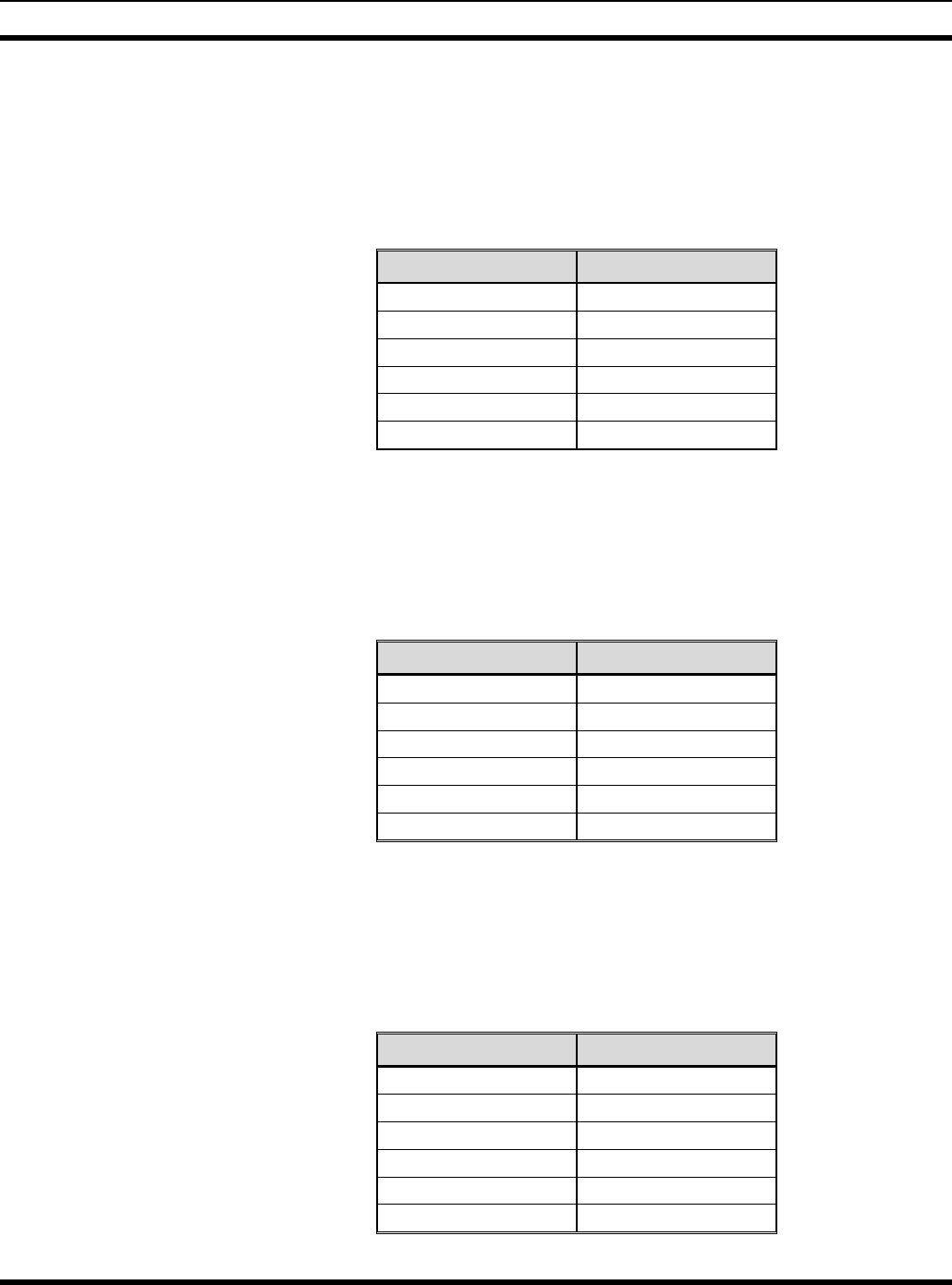

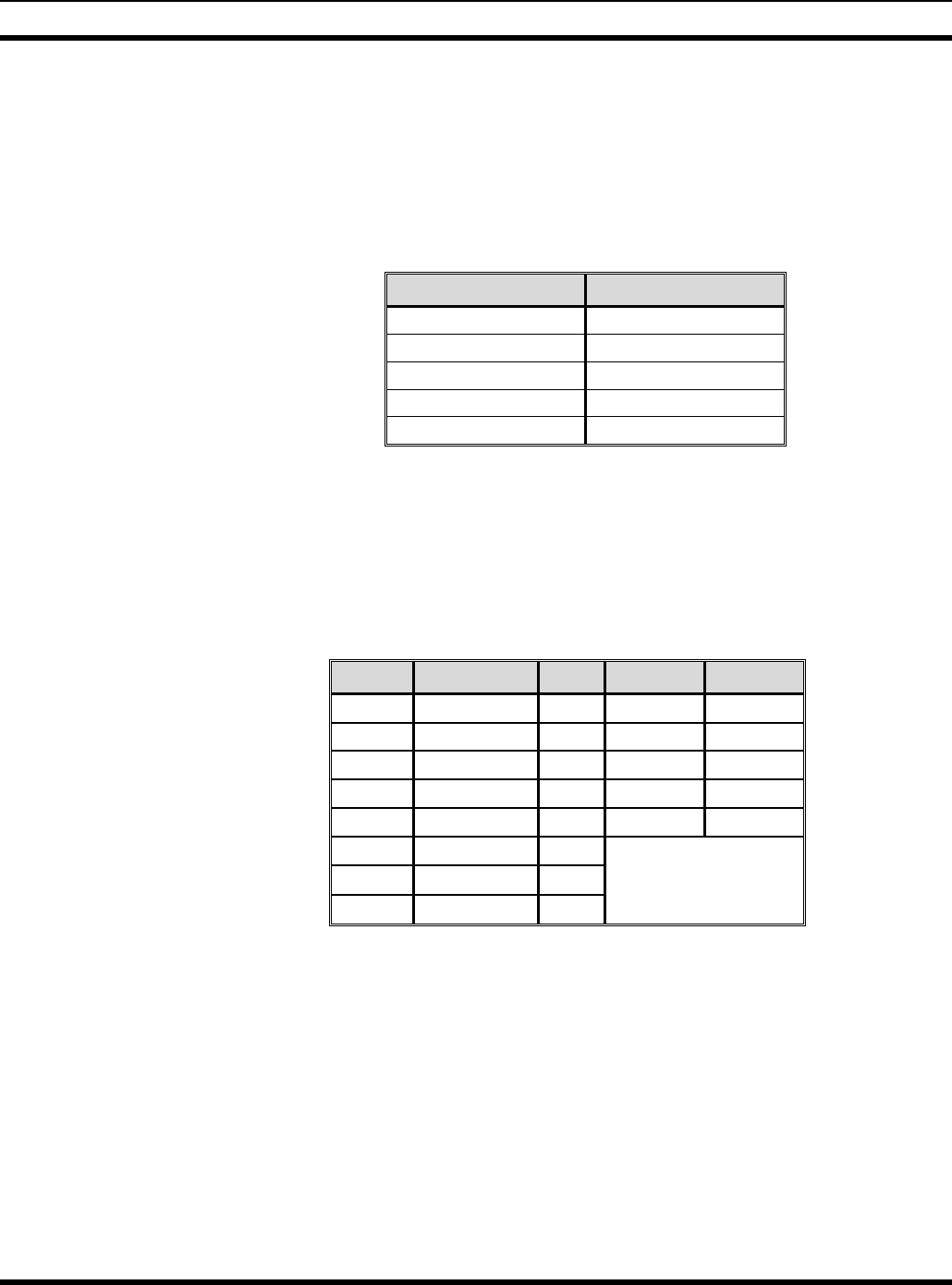

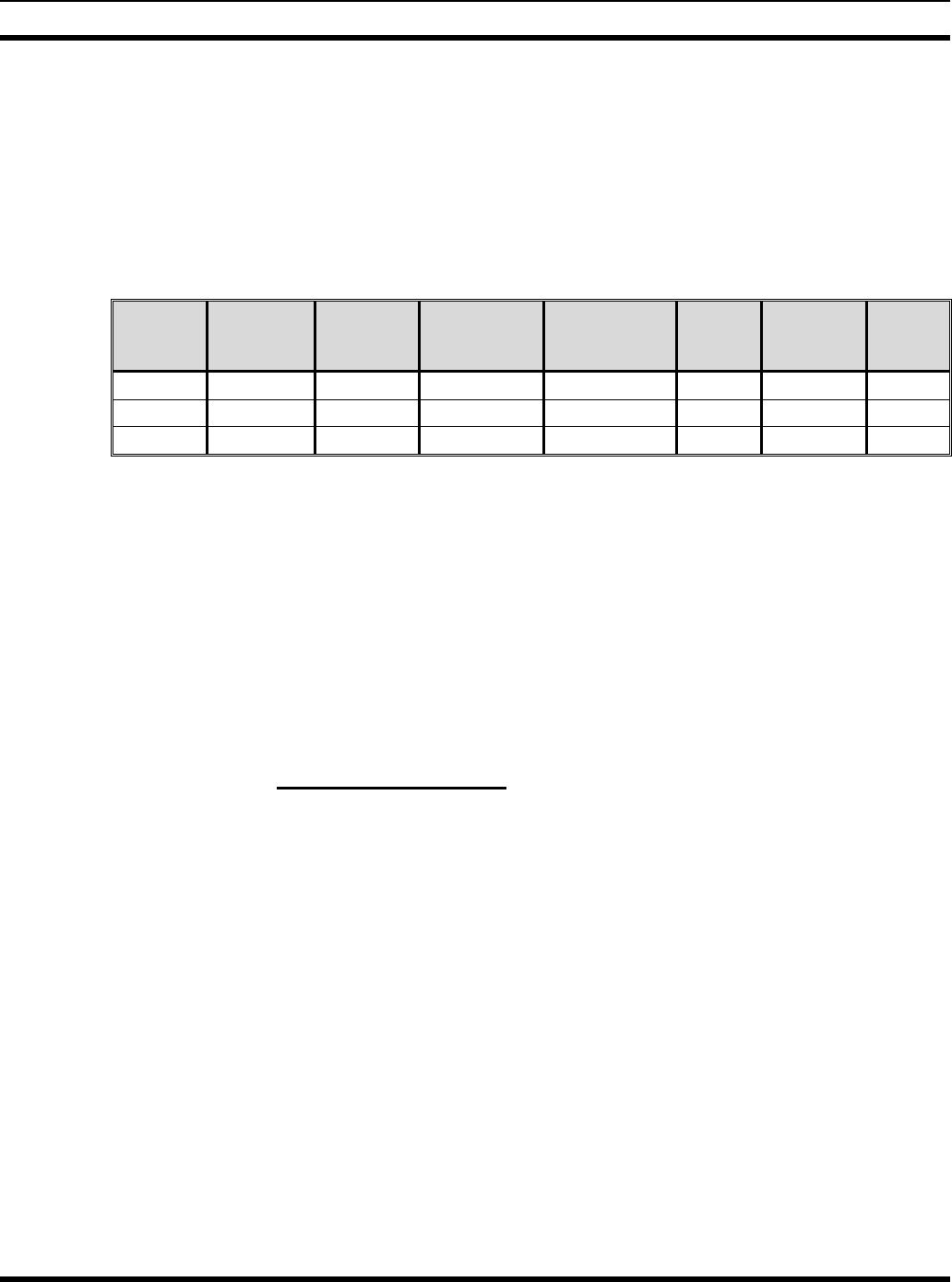

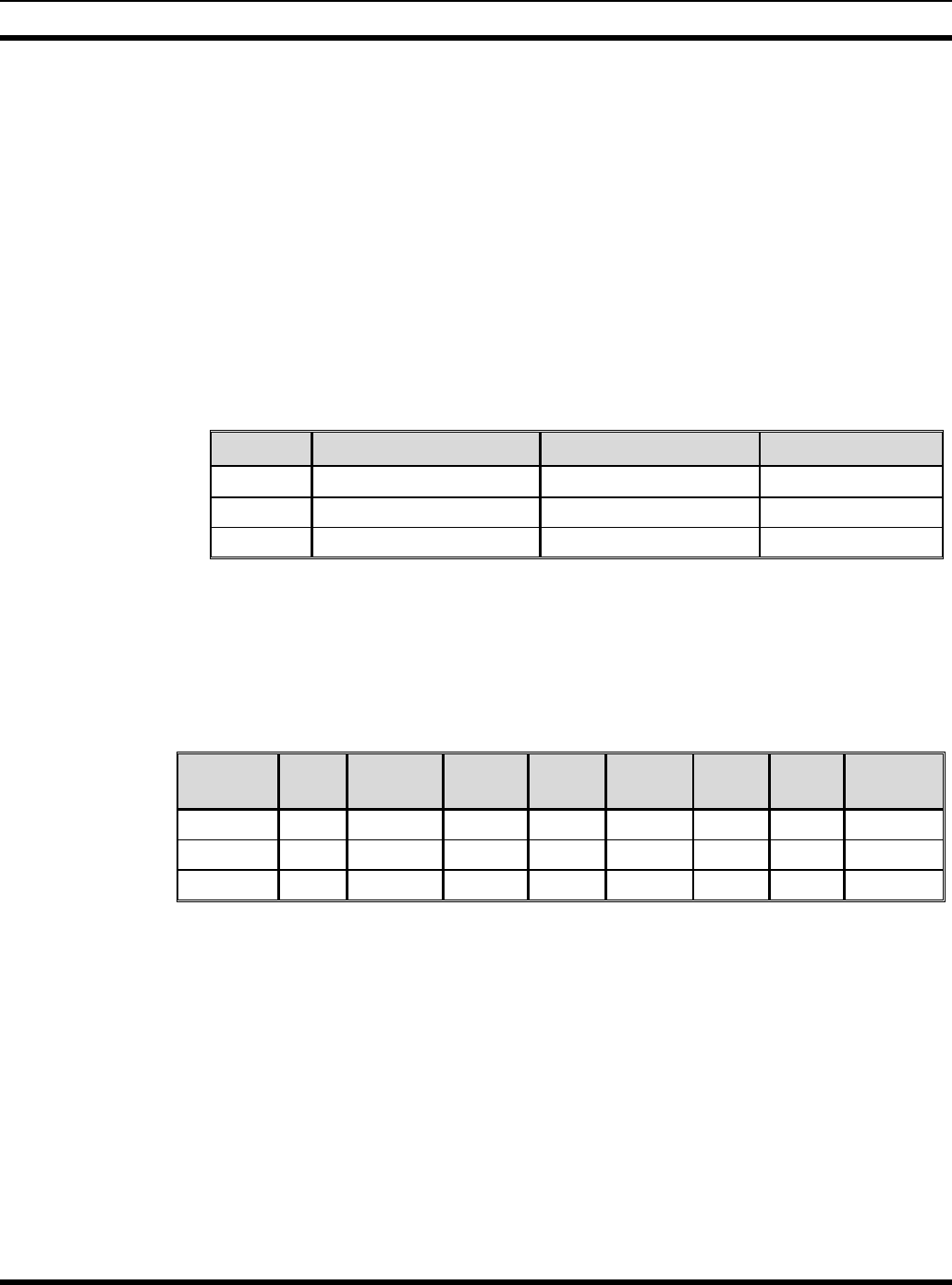

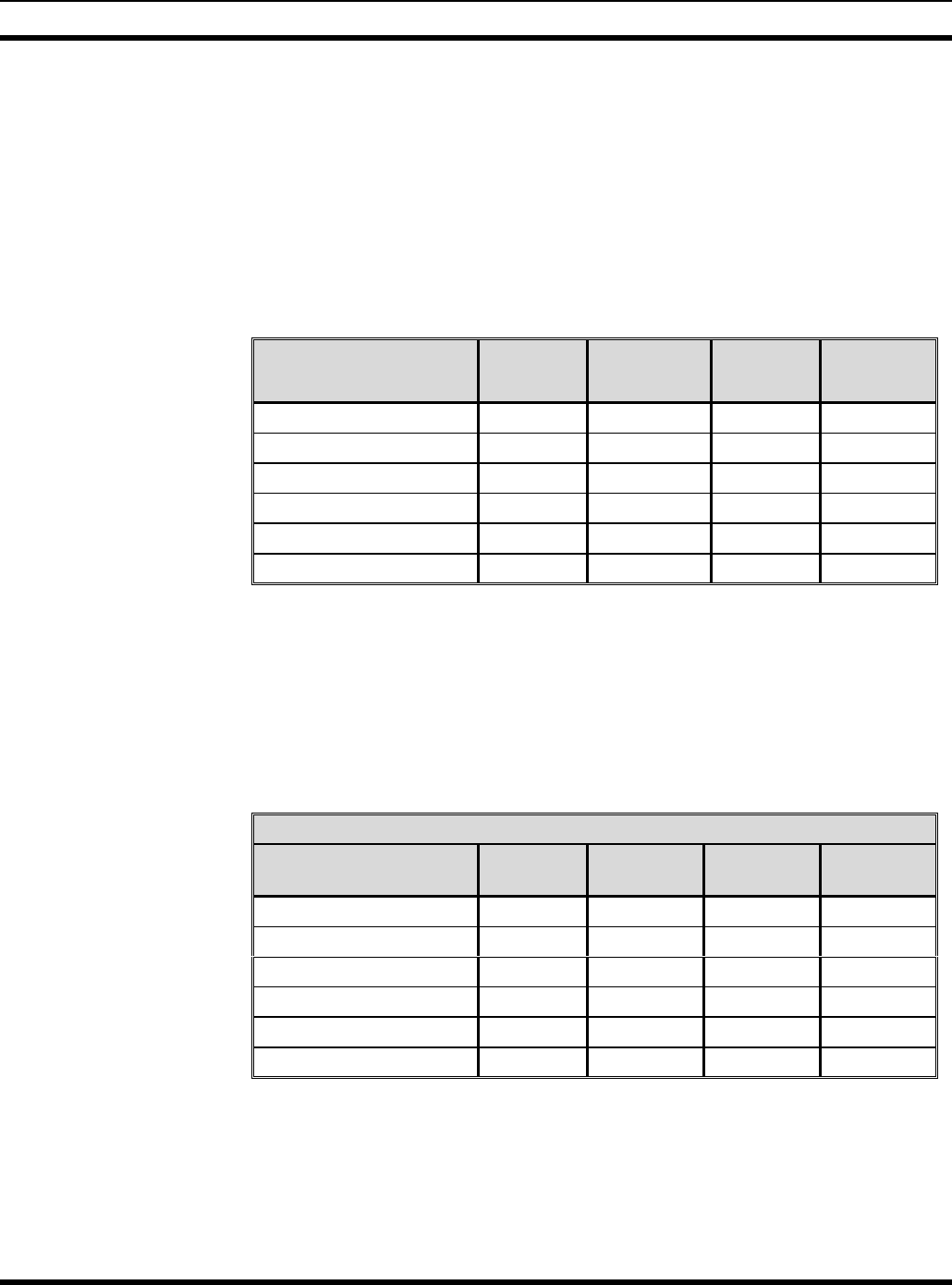

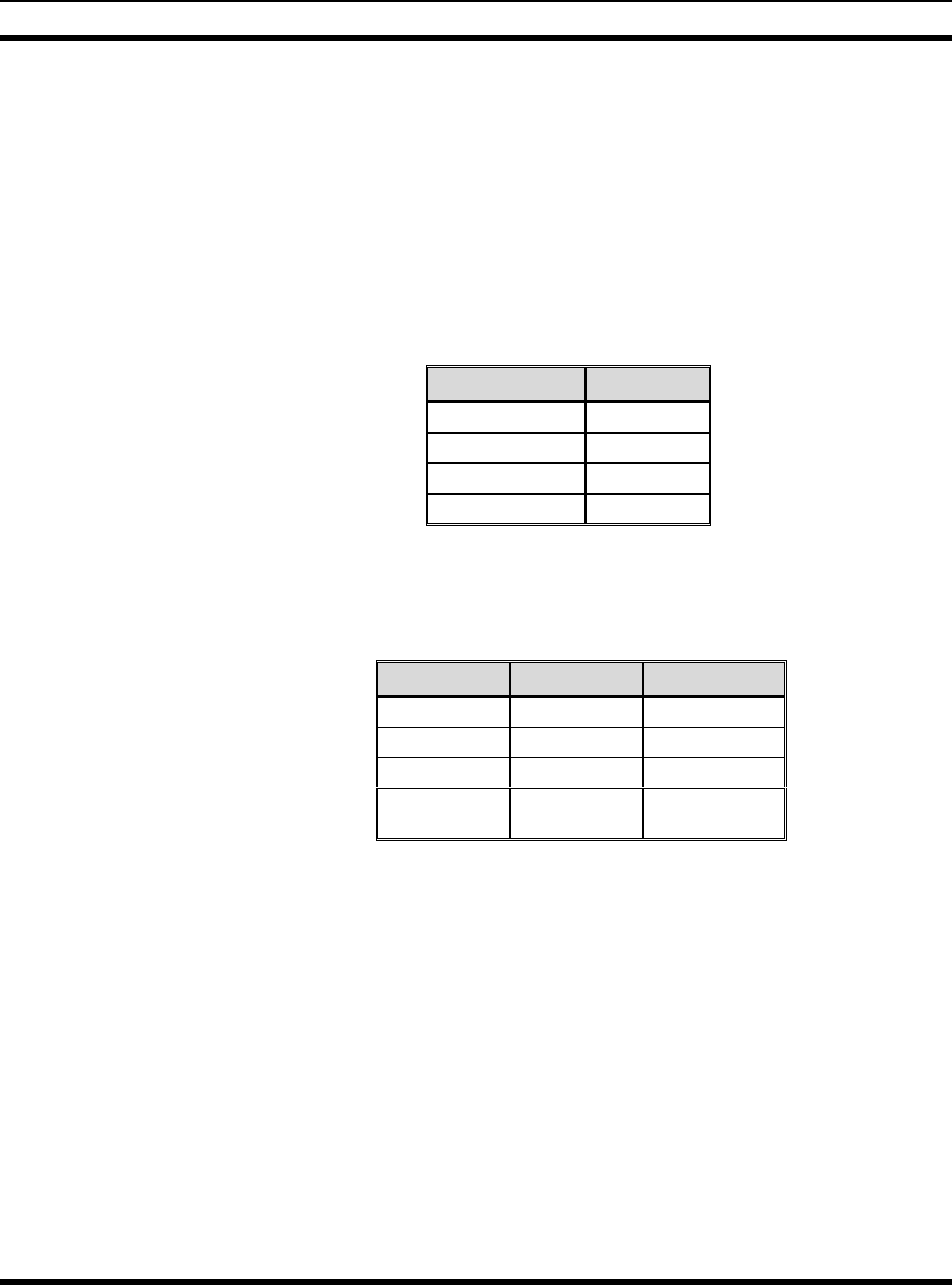

Table 1 –Asynchronous Serial Ports

PORT FORMAT FUNCTION

ENet0 Ethernet 10baseT Management

ENet1

(SCC1)

Ethernet 10baseT Spare

SCC2 RS232 Spare

SCC3 RS232 Spare

SCC4 RS485 Spare

QUART A 38400 baud BSL0

QUART B 38400 baud BSL1

QUART C RS232 Spare

QUART D RS232 Spare

MAINTENANCE AND SERVICE

18 MM101271V1 R2A

PORT FORMAT FUNCTION

SMC1 RS232 (38400 baud (8N1)) Program/Debug

SMC2 RS232 Spare

80C323 SP0 RS232 (38400 baud (8N1)) Debug

80C323 SP1 RS232 (38400 baud (8N1)) Spare

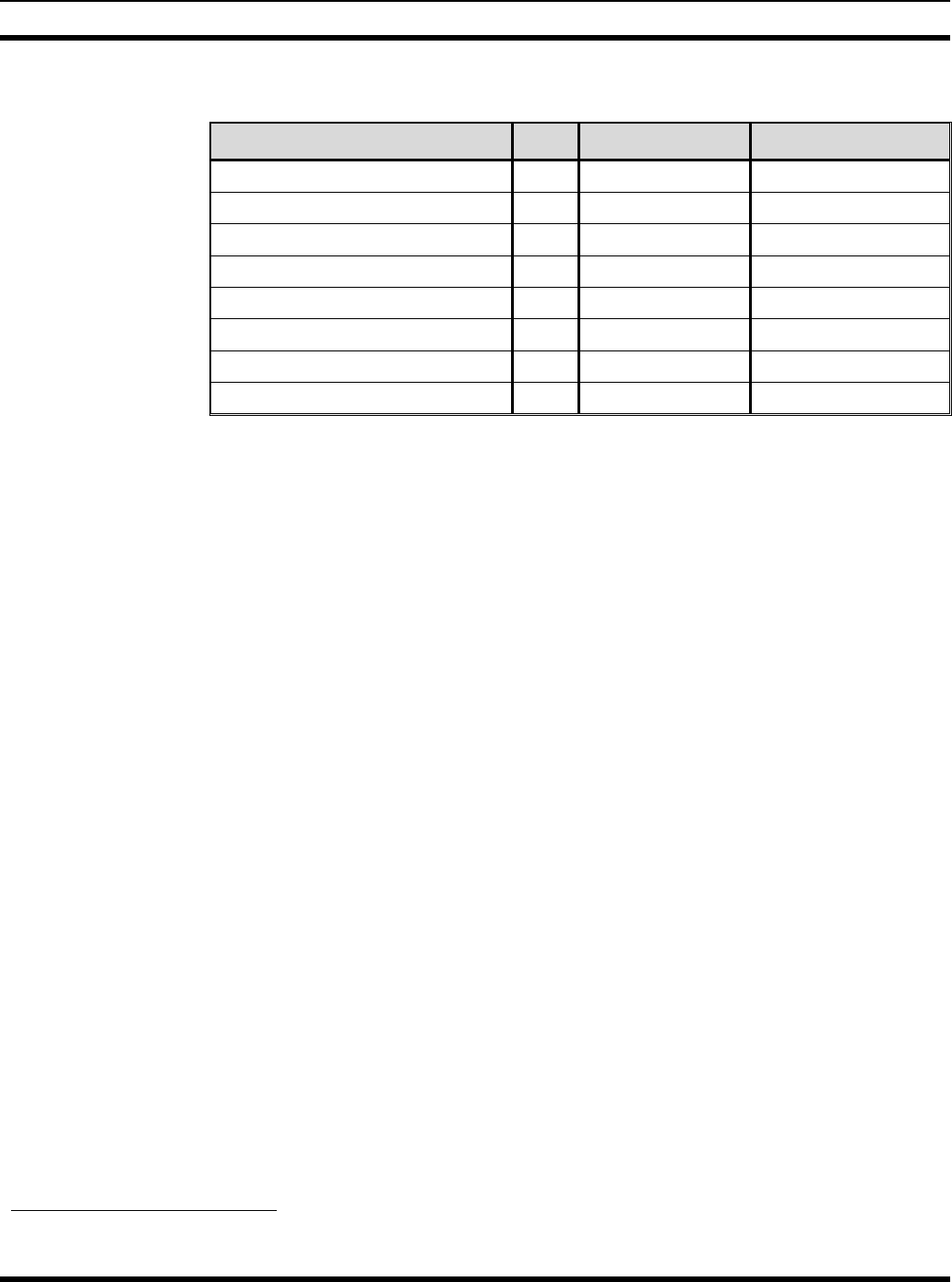

5.3.6 Synchronous Serial Ports

The following synchronous serial ports provide data and control paths from the SitePro

Controller to the base station (High Speed Data), to the IMC (Phone Line), and to

optional Voter equipment (VDI).

Table 2 - Synchronous Serial Ports

PORT FORMAT FUNCTION SIGNALS

SSP0 4800/9600 baud Local (RF)

Comm Link

TxData, TxClock

RxData, RxClock

SSP1 9600 baud Remote (PL)

Comm Link

TxData, TxClock

RxData, RxClock

CTS, RTS

SSP2 9600 baud Voter (VDI)

Comm Link

TxData, TxClock

RxData, RxClock

CTS, RTS

5.3.7 Power

• +13.8V - power supply input

+13.8 volts, 1.5 amps (nominal)

This signal is the positive voltage supply for the SitePro Controller and should be

externally fused. An internal switching DC-DC converter will be used to supply +/-

12 and +5volts to the SitePro Controller sub-components.

• GND – power supply input

This signal is the ground connection for the SitePro Controller.

DESCRIPTION

MM101271V1 R2A 19

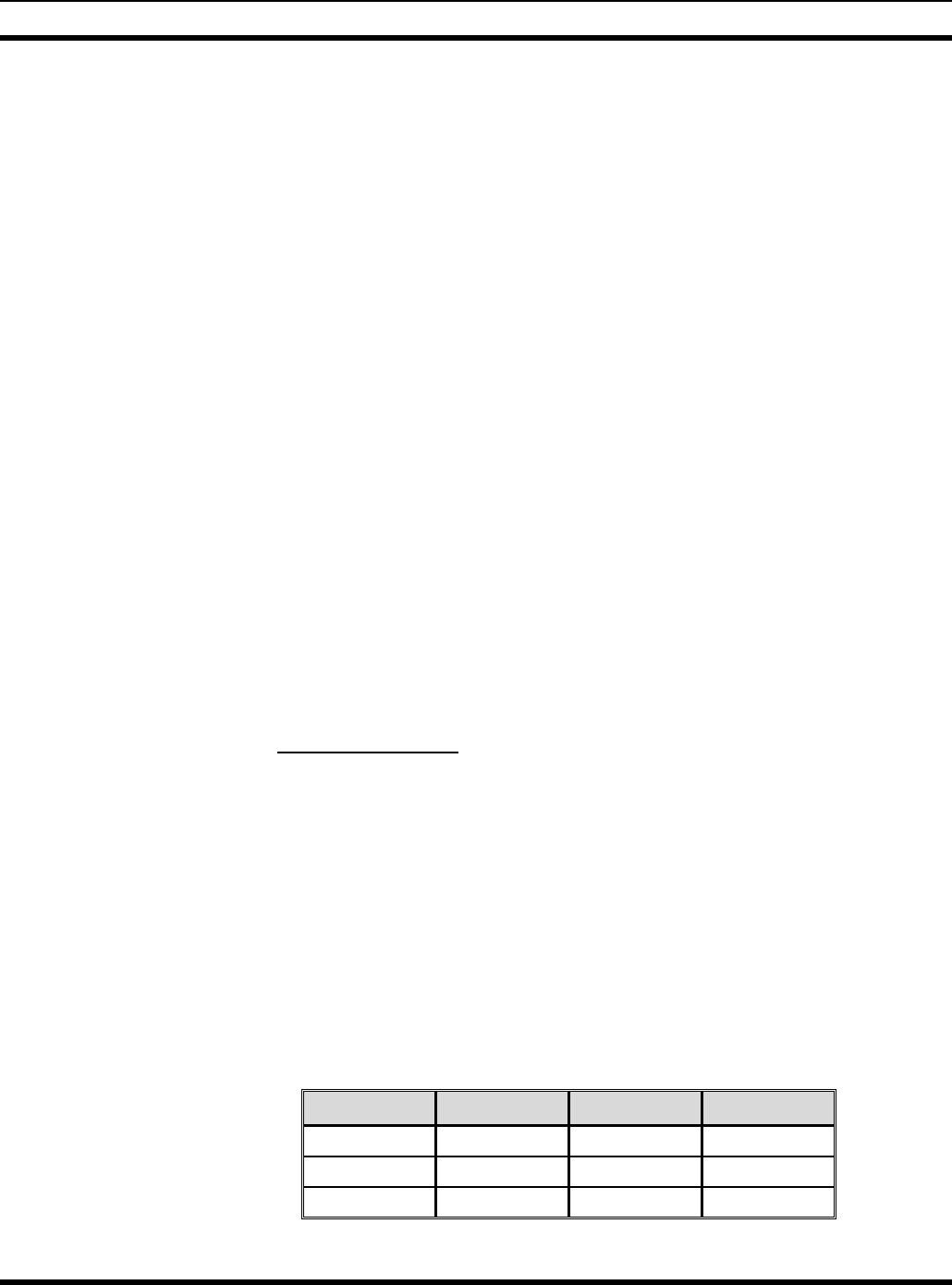

6.0 DESCRIPTION

The SitePro Controller is essentially a processor with audio filtering and specialized I/O

capability. Flexibility in design allows the SitePro Controller to be configured to function

in many applications as suggested in the APPLICATIONS section. The SitePro

Controller software is stored in flash memory. Configuration Data is stored in

NOnVolatile Random Access Memory (NOVRAM).

The Controller Board, Rockwell Modem, Analog Board, Power Supply, Display Module,

and Display Board are mounted on a tray and enclosed in shelf (Figure 2 - SitePro

Controller Shelf Assembly). The SitePro Controller shelf is a one-rack unit assembly

(1.75-inches x 19-inches), which mounts in a standard 19-inch wide equipment

cabinet/rack. This shelf does not slide out, but by reversing the mounting ears can be

mounted approximately 2/3 of the way out of the cabinet for troubleshooting.

Controller Board A2 uses Dual High Speed Diodes BAV99’s for surge protection on all

TTL inputs. However, maximum surge protection is achieved when the SitePro

Controller is grounded to the cabinet earth-ground using Lightning Protection Circuitry

Ground Kit 344A4500 and the Cabinet Grounding strap Kit 344A4730. Specific details

for installing these grounding kits are found in the LIGHTNING PROTECTION

section 10.0 of this manual.

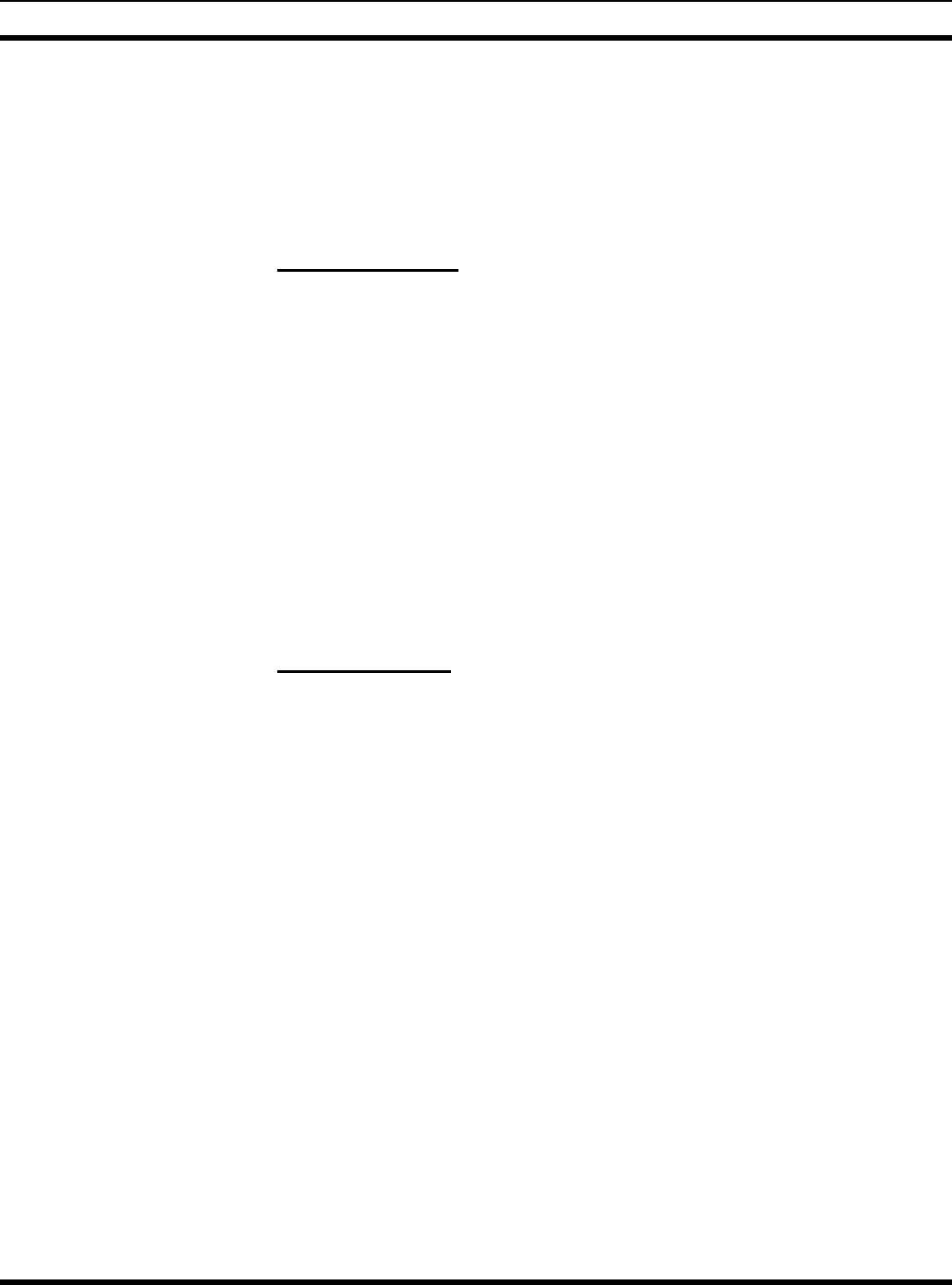

6.1 INDICATORS AND CONTROLS

This section describes the indicators and controls visible and accessible from the front

panel of the SitePro Controller Shelf Assembly.

There are two hinged doors on the front panel of the shelf assembly. Each door has a

window so that indicators mounted on Control Board A2 and Rockwell Modem Interface

Card A3 can be seen. Opening the Controller Board door provides access to Reset

Pushbutton switch S1. This door also provides access to PROGRAMMING and

DIAGNOSTIC SERIAL PORT J8. Programming is available through this port.

The circuit boards can be removed from the shelf assembly through these doors.

6.1.1 Indicators

6.1.1.1 Controller Board Power Indicator

Green LED indicator D12 provided on the Controller Board indicates when power is

applied to the shelf. This indicator is visible by looking diagonally through the window in

the hinged door on the front panel of the shelf.

6.1.1.2 Controller Board Status Indicators

Four Red LED status indicators L1 thru L4 (D1 thru D4) are visible through the window

in the hinged door. These indicators show the state of operation of the SitePro Controller.

The interpretation of these indicators depend on the system application (refer to the

SitePro Controller configuration manual for the specific application).

DESCRIPTION

20 MM101271V1 R2A

Green ETHERNET indicators ETH0 and ETH1 are also visible through the window in

the hinged door. These indicators indicate when a compatible source is connected to

ETHERNET 1 or ETHERNET 2 ports.

There are six other LED indicators on the Controller Board that are not visible from the

front panel. Yellow LEDs D7 and D10 indicate when there is transmit activity on ETH0

and ETH1. Yellow LEDs D6 and D9 indicate when there is receive activity on ETH0

and ETH1. Green LEDs D5 and D8 indicate when there is link activity (refer to Ethernet

Ports, section 7.3.7).

6.1.1.3 Rockwell Modem Interface Card Indicators

There are five Red LED indicators on Rockwell Modem Interface Card A3. These LEDs

are visible through the window in the hinged door and indicate +5V, +12V, -12V, RLSD

and CTS respectively. Received Line Signal Detect (RLSD) indicates data is being

received. Clear-To-Send (CTS) indicates a control signal is being sent to the CPU

selector.

6.1.1.4 Display

Eight-character LED Display Board A6-A1 mounts between the two hinged doors on the

front panel of the SitePro Controller Shelf Assembly. Green LED D1 indicates POWER

ON to the shelf. This display displays Channel Status and Channel Information.

6.1.2 Controls

Reset Pushbutton Switch S1 is the only control available on the front panel of the

SitePro Controller Shelf Assembly. It is used to reboot the SitePro Controller.

6.2 ROCKWELL MODEM

The 9600 Baud Rockwell Modem Board RYTUZ 921 01/1 mounts on top of Modem

Interface Card A3 (ROA 117 2247). This Modem Board is used to generate a 9600 baud,

fast-train, synchronous, serial data stream suitable for transmission over audio (phone)

line or microwave link. The data stream is sent over a full-duplex, four-wire, dedicated

3002 grade telephone line.

Receive and Transmit Phone Data Lines are two balanced pairs carrying Modem data to

and from the station where the data is combined with station audio (voice) and routed to

the Remote Line input and Line output.

In addition to transformer isolation and conditioning provided by the SitePro Controller,

the modem provides automatic adaptive signal equalization. The Rockwell Modem

demodulates the input signal and the resulting data is transferred using a serial interface

between the Rockwell Modem and the controller.

The modem senses a received signal by initiating a training state upon detecting an

increase in the input signal level. The modem begins processing data at the end of the

training state if the input signal is still above the nominal -40 dBm receiving threshold

value. Otherwise, the modem returns to an idle mode at the end of the training state if the

input signal is below the nominal receiving threshold value.

DESCRIPTION

MM101271V1 R2A 21

6.3 LOW SPEED AND HIGH SPEED DATA FILTERS

6.3.1 Low Speed Data Decode Filter

The Low Speed Data (LSD) Decode Filter, part of Analog Board A4, provides additional

filtering to remove voice-audio from the receiver unfiltered audio (vol/sq/hi), thus leaving

only the low-speed subaudible data for input to the microprocessor.

6.3.2 High Speed Data Encode Filter

The High Speed Data (HSD) Encode Filter, part of Analog Board A4, is configurable

based on personality data and shapes the data for the most efficient RF transmission. This

data can be control signaling or digital voice. The data is generated by the RF modem

under control of the 80C323 microprocessor.

6.4 INTERFACE CONNECTIONS

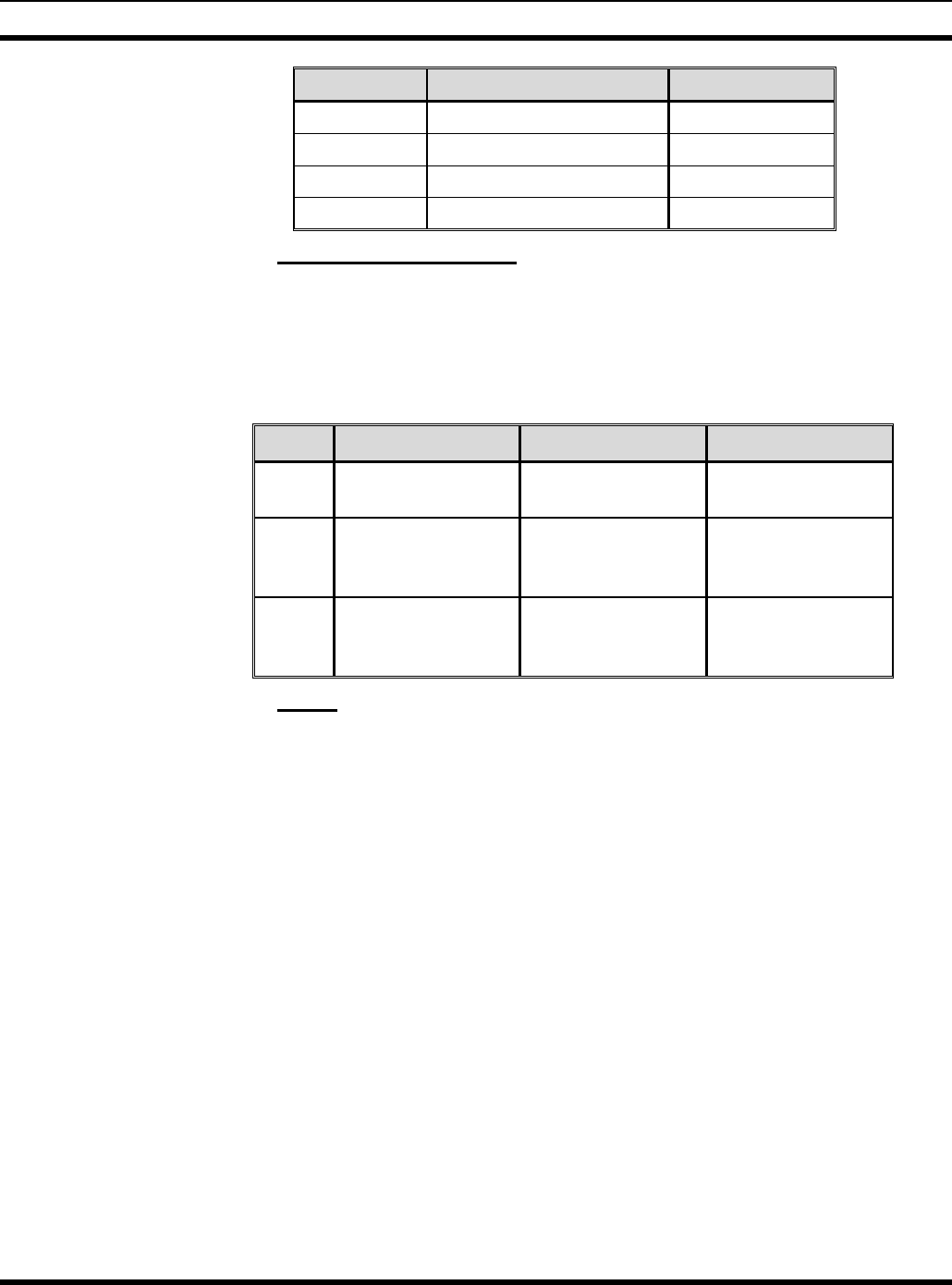

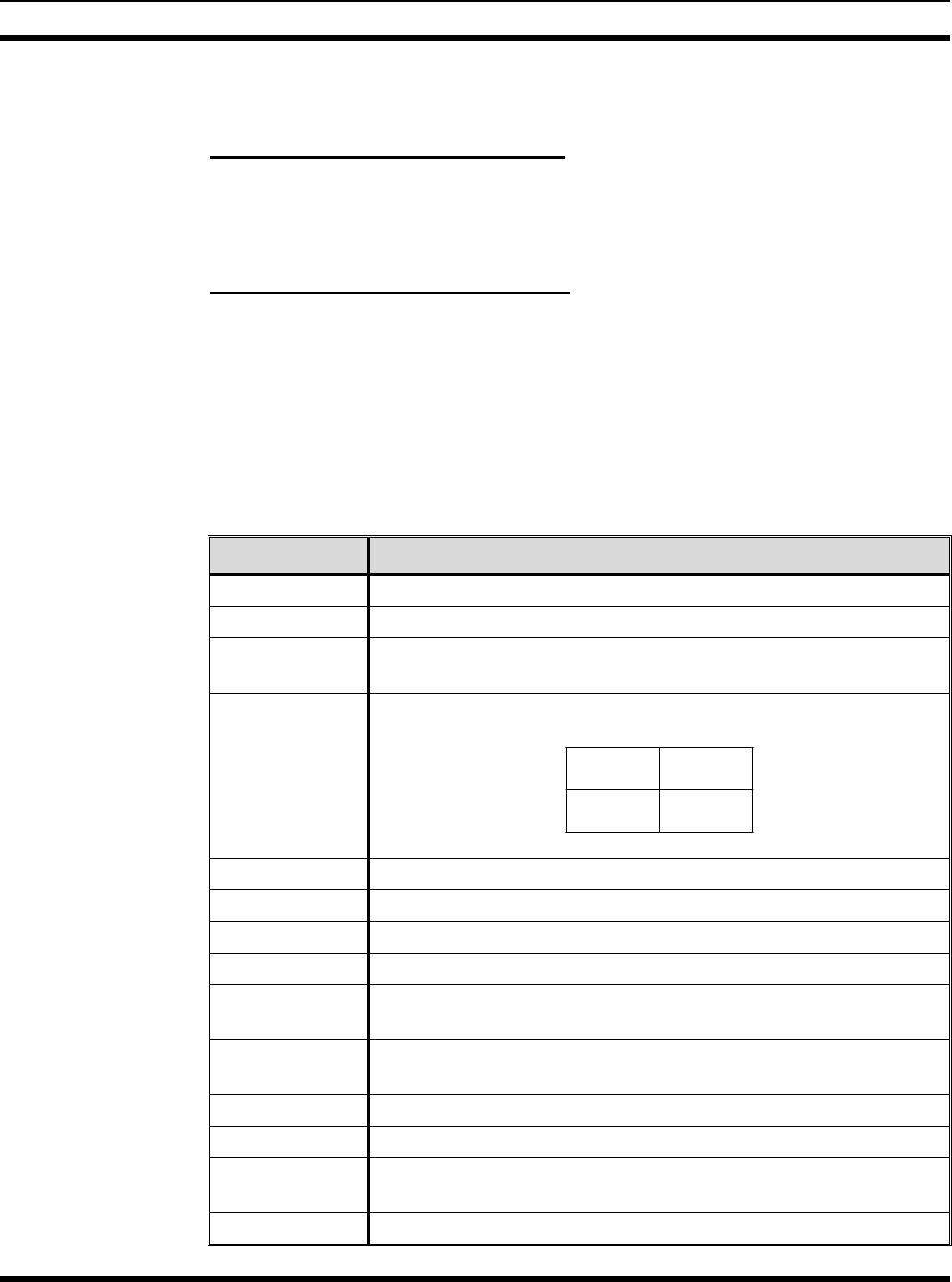

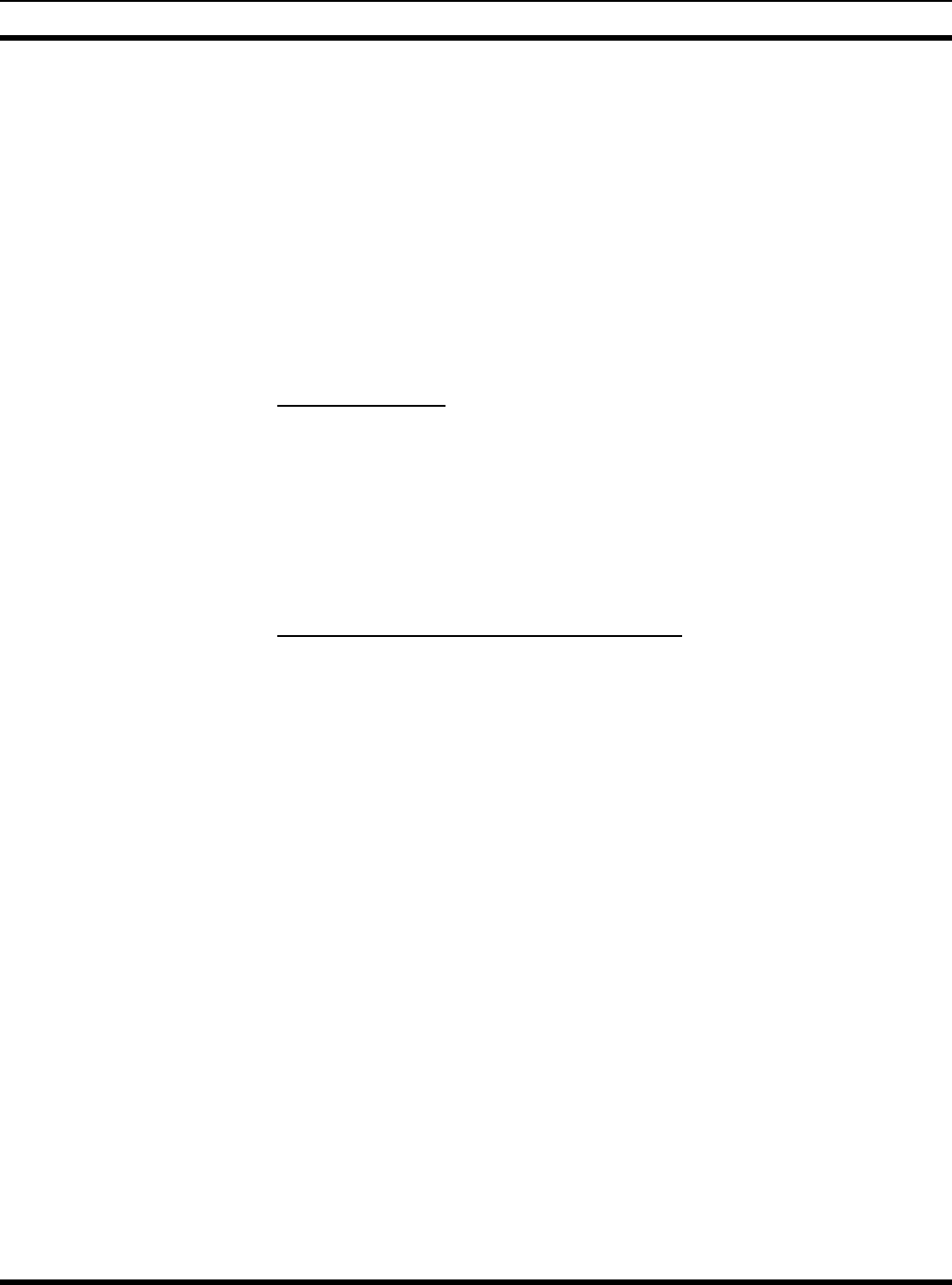

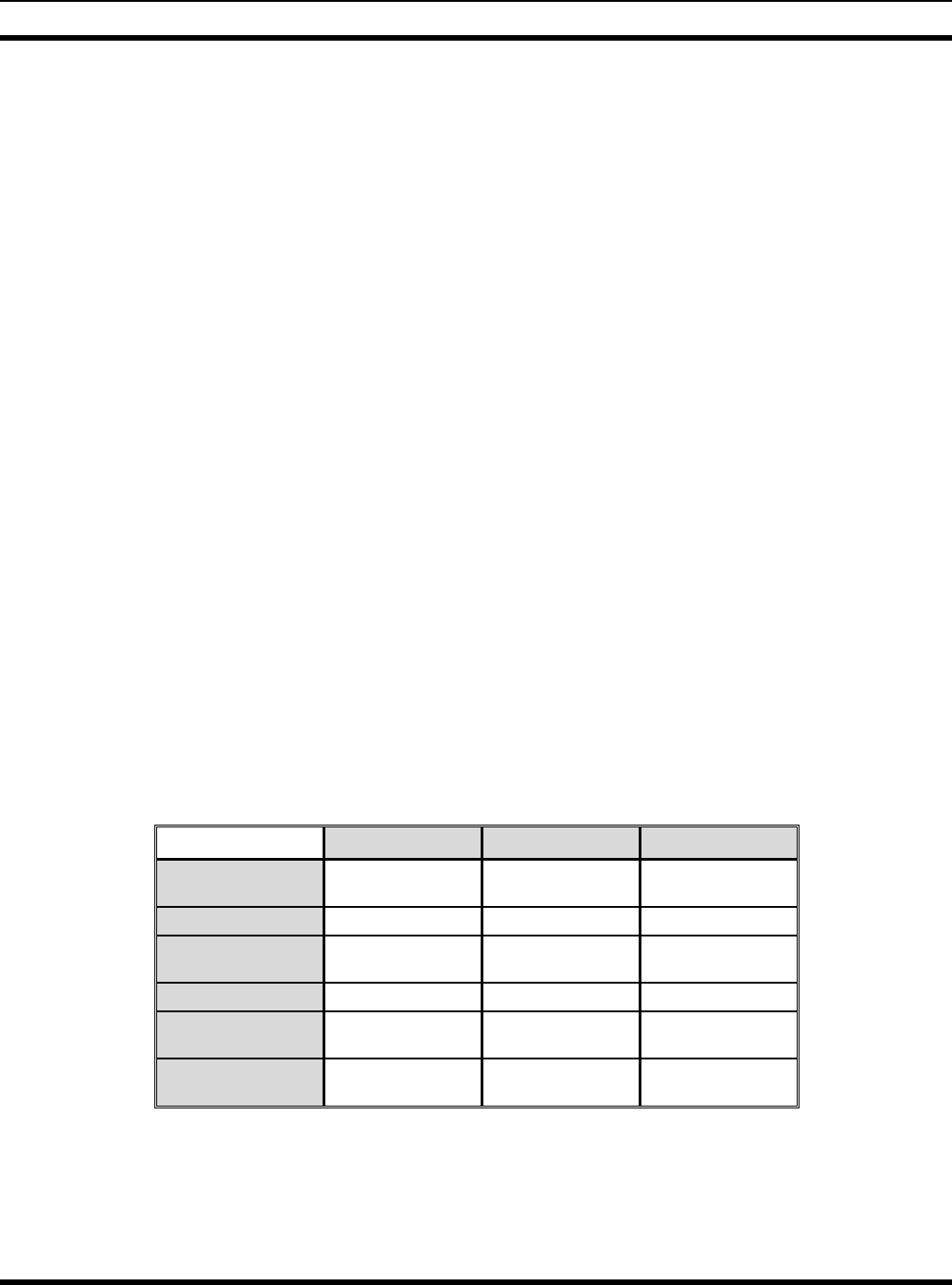

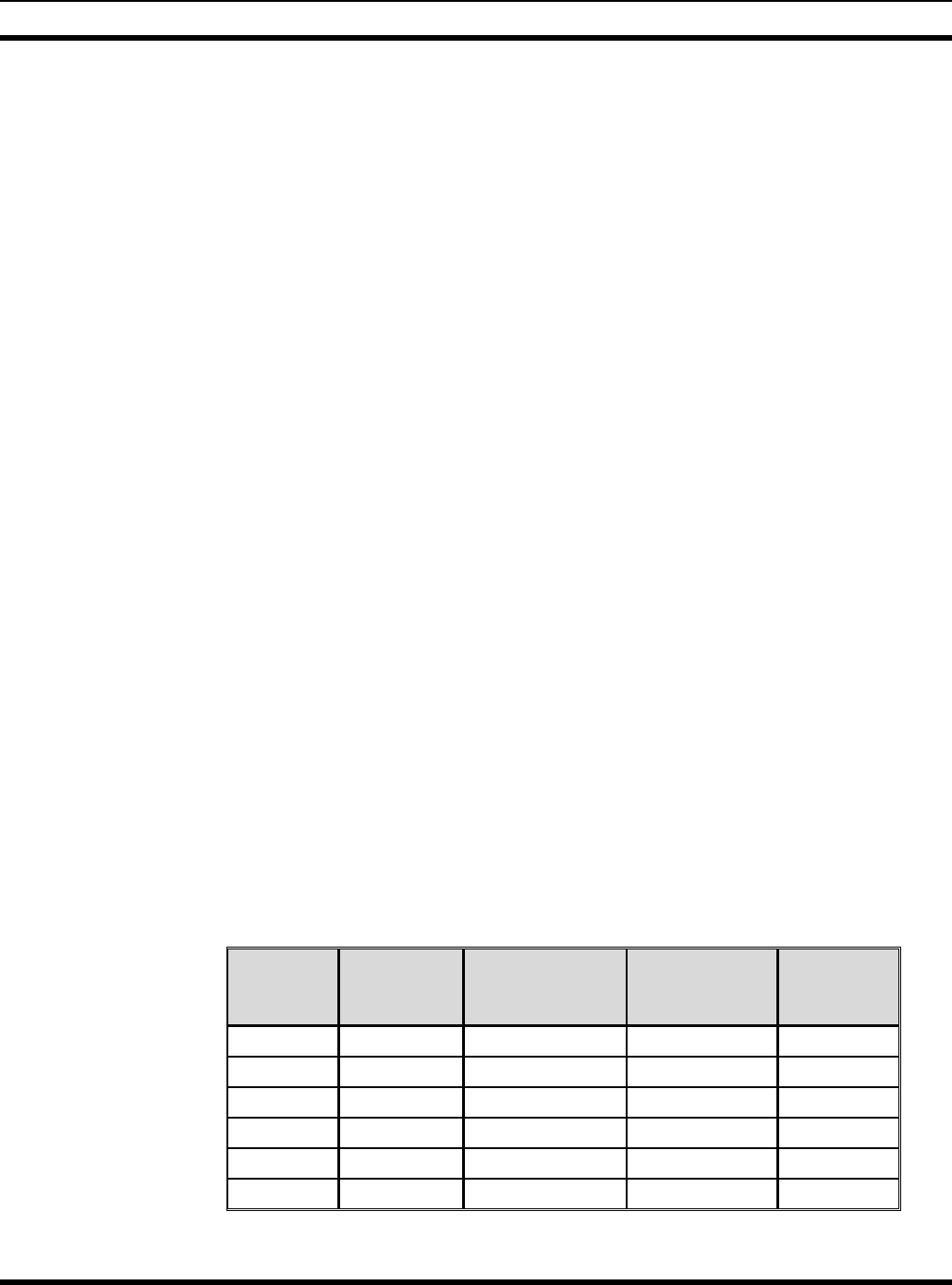

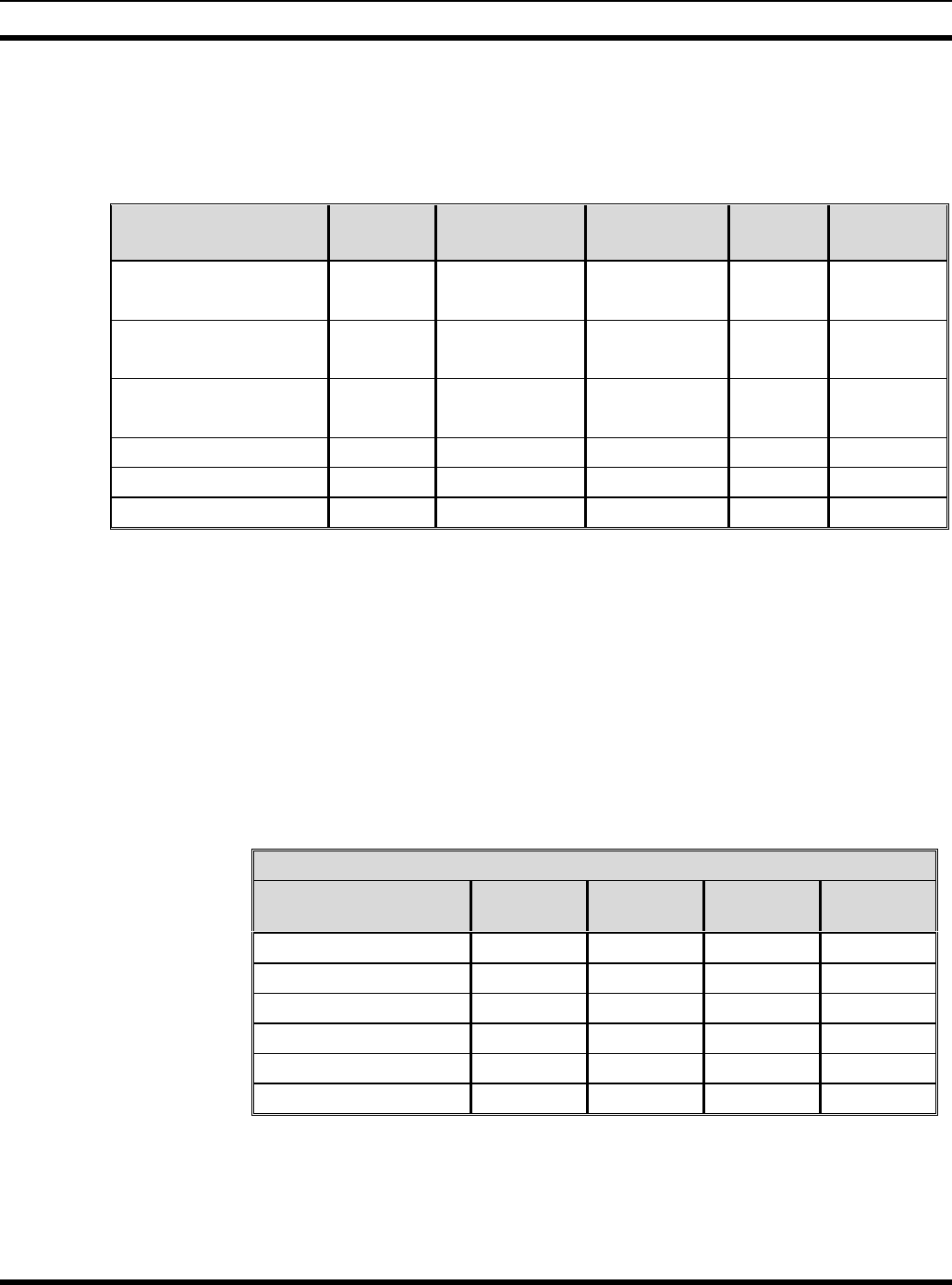

Table 3 - Interface Connections

CONNECTOR INTERFACE CONNECTIONS

J1 96 Pin connector interfaces with Controller Board CB101069V1.

J2 96 Pin connector interfaces with Analog Board CB101070V1.

J3 96 Pin connector interfaces with Rockwell Modem Interface Card

ROA 117 2247.

J4 2 over 2 BSL/RM (Rockwell Modem). This connector consist of

four RJ11 connectors as follows:

RM 0 BSL 1

QUART A

RM 1 BSL 0

QUART B

J5 Ethernet 0

J6 Ethernet 1

J7 4 Pin Power connector (+13.8 VDC).

J8 (Controller) Programming connector on the front of Controller Board A2

J8 (Interconnect) Connects +13.8 VDC from Interconnect Board A1 to power supply

module A5 input through cable W1

J9 Power Supply Output +12V, -12V and +5V. Cable W2 connects

between J9 and J2 on Power Supply Module A5

J10 Connects through cable A6-W1 to Display Module A6.

J11 20 Pin connector for interfacing with a Conventional/DSP system.

J12 24 Pin connector for connecting to an Enhanced Digital Access

Communication System (EDACS)

J13 26 Pin connector for interfacing with a Simulcast System.

DESCRIPTION

22 MM101271V1 R2A

CONNECTOR INTERFACE CONNECTIONS

J14 6 over 6 phone lines and serial ports. This connector consists of

twelve RJ11 connectors as follows:

RM 0 QUART C SCC4

RS 485

SCC3 80C323

PORT 0

N/U

RM 1 QUART D SCC2 SMC2 80C323

PORT 1

N/U

6.5 COMMUNICATION LINKS

Communication Modes available to the SitePro Controller are:

1. The SitePro Controller can communicate with other devices such as the

Communication System Director (CSD), IMC, and RF Station. Communication

occurs primarily through an RS-232C serial interface normally operating at 38.4

kilobaud. For a SitePro Controller interfacing with a Site Interface Module (SIM)

this is set to 38.4 kilobaud.

2. The SitePro Controller can communicate with other SitePro Controllers in the normal

mode of operation, over a Backup Serial Link (BSL). The link uses 0-13.8 VDC

levels and operates at 38.4 kilobaud and is ordinarily used in a bus configuration. For

a SitePro Controller interfacing with a SIM this is set to 38.4 kilobaud.

3. A timing signal called the Frame Sync Line (FSL) helps arbitrate the use of the BSL

serial bus. The FSL is also used for timing purposes. In the station configuration, FSL

signals use 0-13 VDC levels to produce a periodic negative going pulse (2.5 ms wide

every 30 ms).

4. A 9600/4800 baud full duplex, synchronous communication interface over an RF

channel.

5. A 9600 baud phone line or microwave communication interface (this may be RS-232

or modem data) through a Rockwell Modem.

NOTE

SitePro Controller interface functions vary from application to application and between

EDACS systems using MASTR III repeaters. It is necessary to refer to the Application

Configuration Manual for details regarding the specific hardware and software

configuration of the SitePro Controller.

DESCRIPTION

MM101271V1 R2A 23

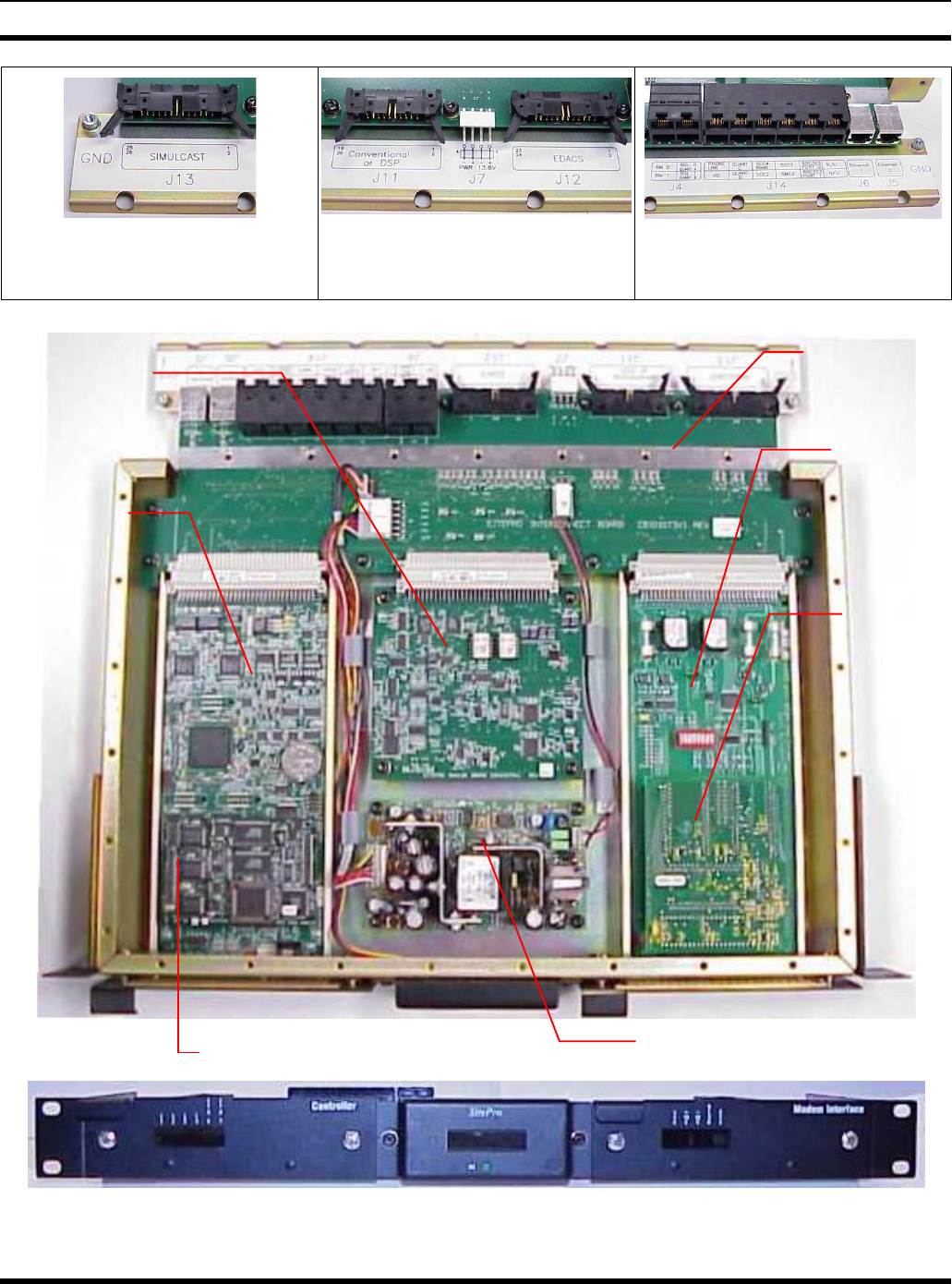

Left Rear

20-Pin SIMULCAST Connector

Center Rear

24-Pin EDACS, 4-Pin POWER & 20-

Pin CONV/DSP Connectors

Right Rear

Ethernet, SERIAL PORT &

BSL/RM Connectors

Rear Views

Top View

Front View

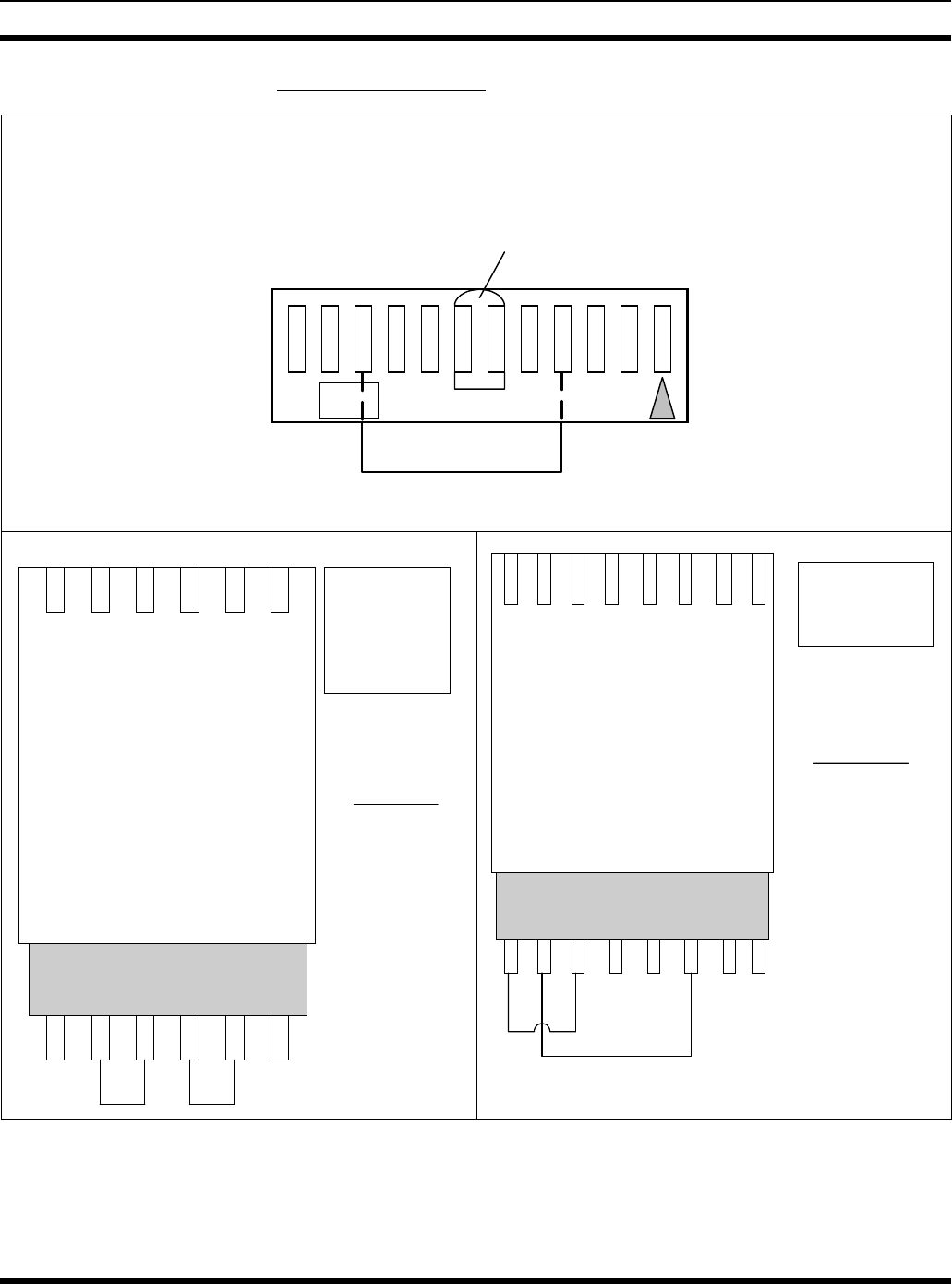

Figure 2 - SitePro Controller Shelf Assembly

DC/DC Power Supply (A5)

SitePro Modem Board (A2-A1)

Interconnect

Board (A1)

Rockwell

Modem

Interface

Card (A3)

Rockwell

Modem

Controller

Board (A2)

Analog

Board (A4)

CIRCUIT ANALYSIS

24 MM101271V1 R2A

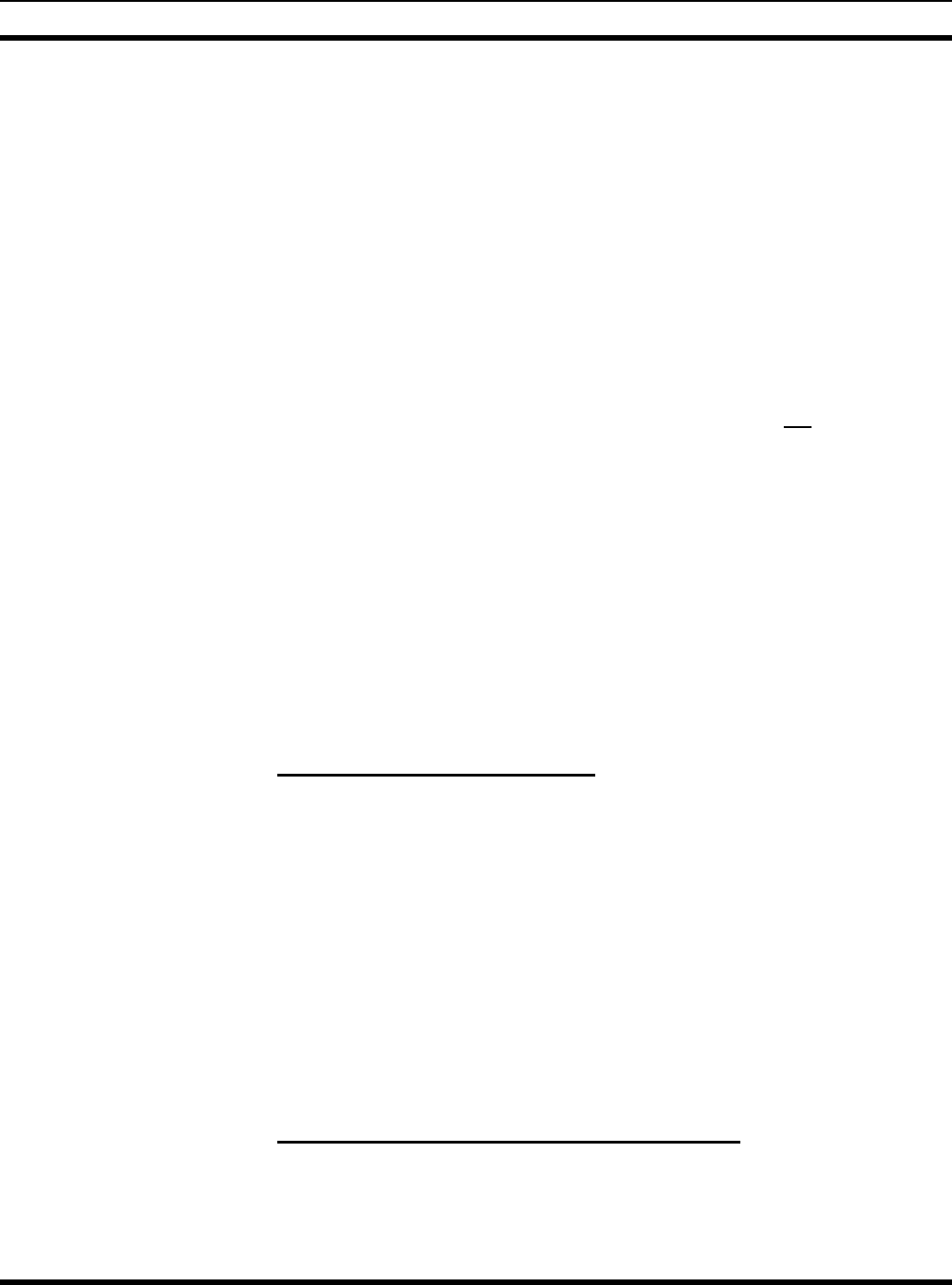

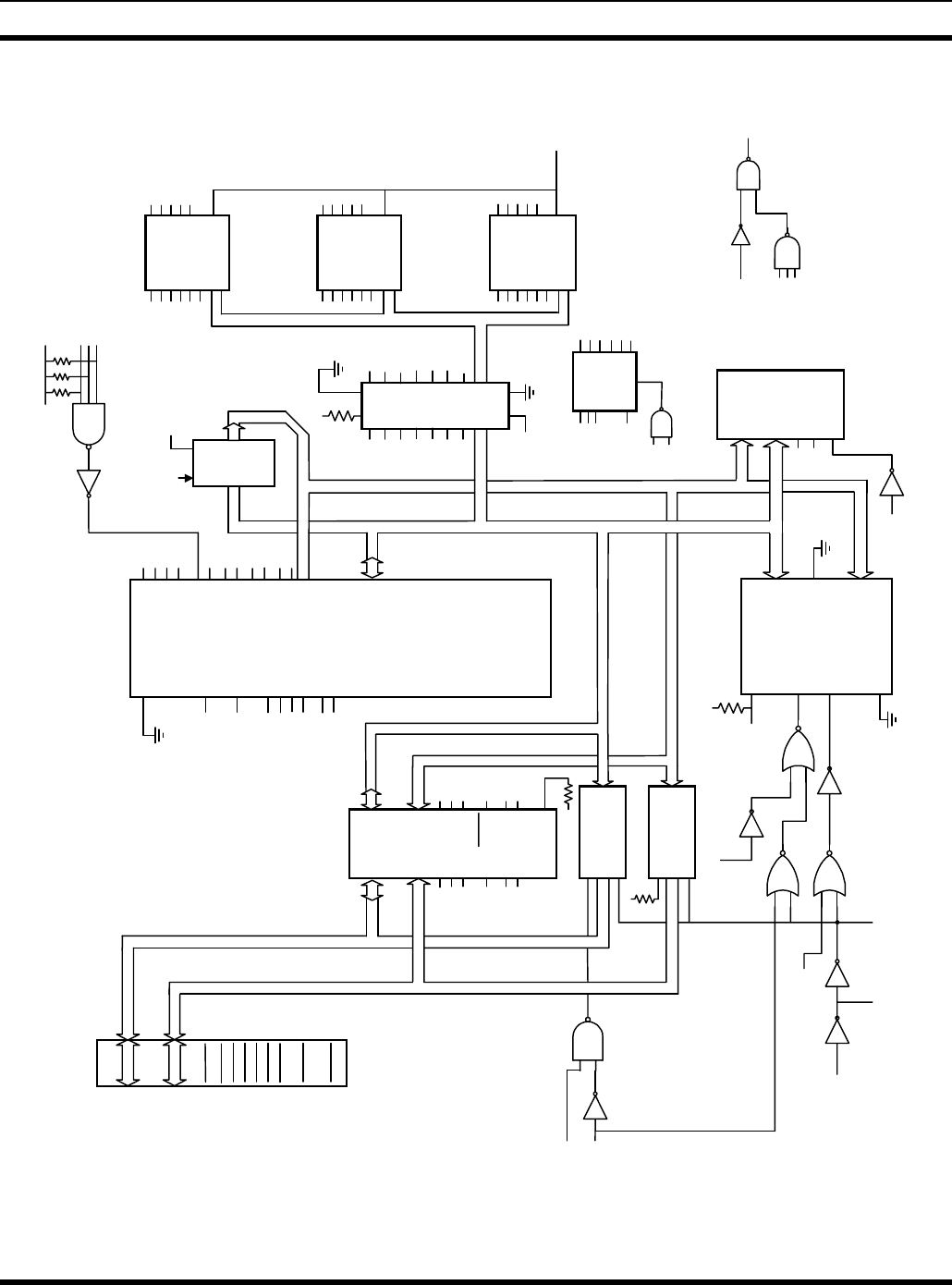

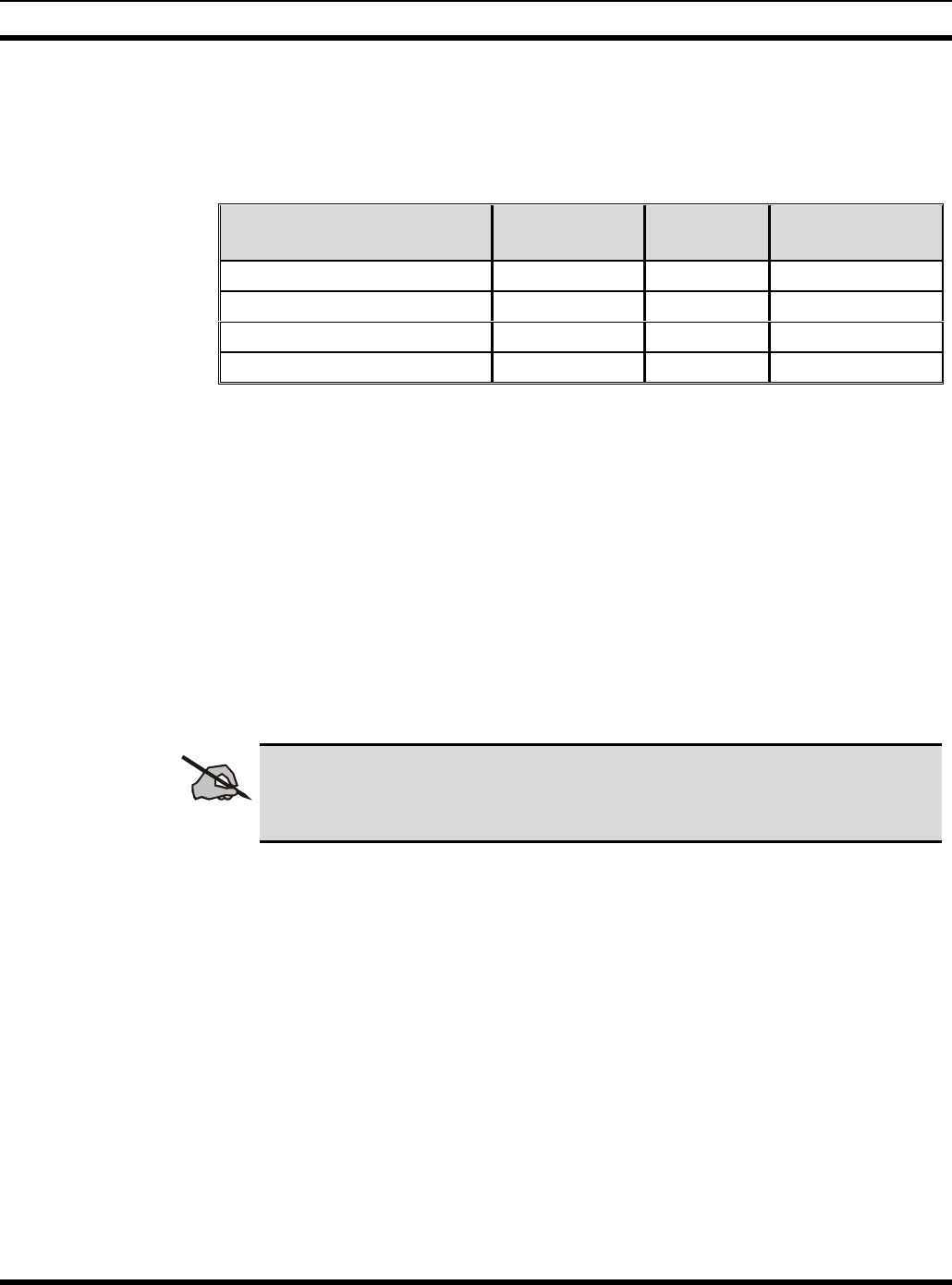

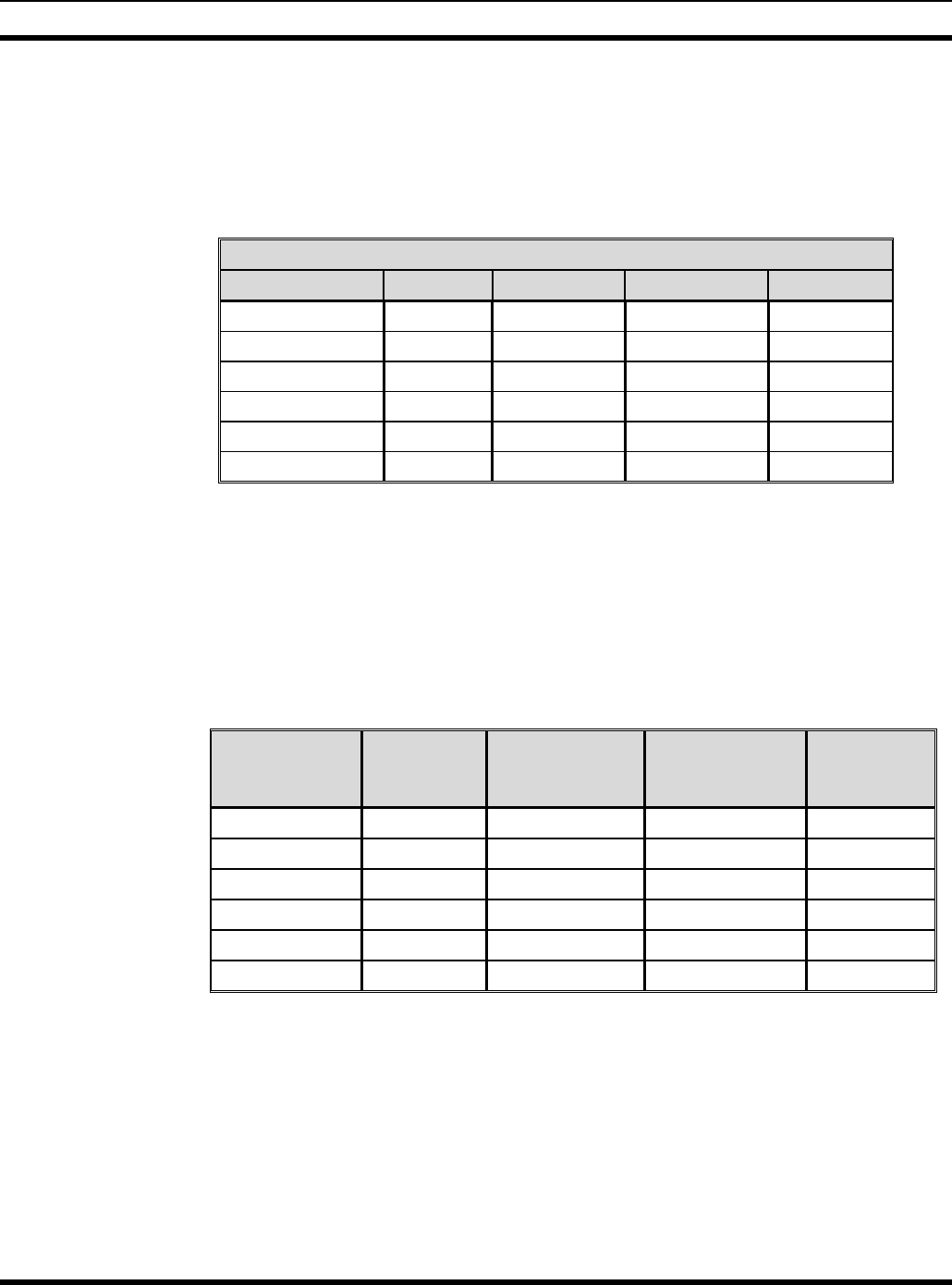

7.0 CIRCUIT ANALYSIS

The Theory of operation of each circuit board/card and module used in SitePro Controller

Shelf Assembly EA101209V1 is described in the following paragraphs. Refer to the

Block Diagram in Figures 3 and 4 and Outline and Schematic Diagrams as listed in the

TABLE OF CONTENTS.

The SitePro Controller is a Base Station Controller with redundant communication links

[Backup Serial Links (BSL’s)]. The BSL’s provide for inter-channel communication.

Two 10Mbit Ethernet Ports provide system level communication. The BSL’s provide

trunking communications as well as site configuration and database messaging. One

Ethernet port is dedicated to Management System information. The second Ethernet Port

is not supported at this time.

The SitePro Controller and System Interface Module (SIM) will use the primary BSL for

trunking information and limited management system information. The secondary link

will ensure continued trunking operation in the event of a primary BSL failure.

The SitePro Controller/base station interface for digital information, both receive and

transmit, is 9.6k baud synchronous data. Additional digital control information is

provided via discrete I/O at both the base station and controller. The following diagram

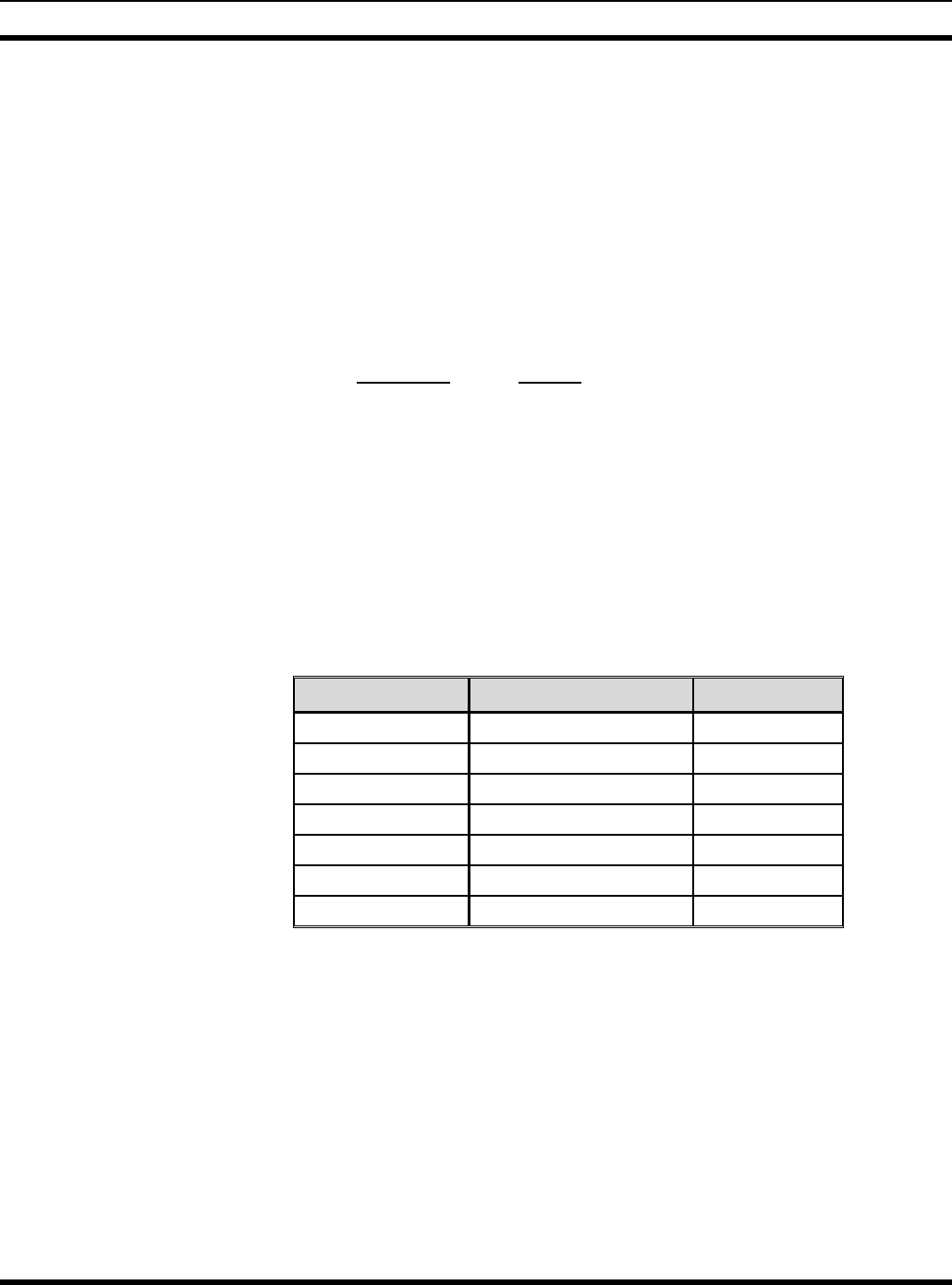

(Figure 2) is a high level picture of the SitePro Controller and external interfaces.

7.1 SHELF ASSEMBLY

SitePro Controller shelf Assembly EA101209V1 is a 19” Rack Mount, one Rack Unit

device. It is enclosed to reduce emissions and interference with other devices. Serial

ports, Ethernet, power, and I/O connections are accessible at the back of the shelf (Figure

1). The serial port connections (6 OVER 6 PHONE LINES & SERIAL PORTS) are

stacked two high using RJ45 type connectors (J14) and RJ11 type connectors (J4). The

Ethernet connectors J5 & J6 (ETHERNET 0 & ETHERNET 1) are single height RJ45

connectors. The power connector (J7) and I/O connectors (J11, J12 & J13) are Molex

type.

The front panel has two hinged access doors for insertion/removal of the Controller

Board and the Rockwell Modem card for troubleshooting and ease of maintenance. These

doors have RF fingers to reduce emissions. Diagnostic LEDs and the eight-character

display are viewable from the front panel.

The Shelf Assembly consists of Interconnect Board A1, which provides connectors to

accommodate:

• Controller Board CB101069V1 (A2)

• Rockwell Modem Interface Card Assembly ROA 117 2247 (A3)

• Analog Board CB101070V1 (A4)

• Power Supply PS101328V1 (A5)

• Display Module MA101082V1 (A6)

CIRCUIT ANALYSIS

MM101271V1 R2A 25

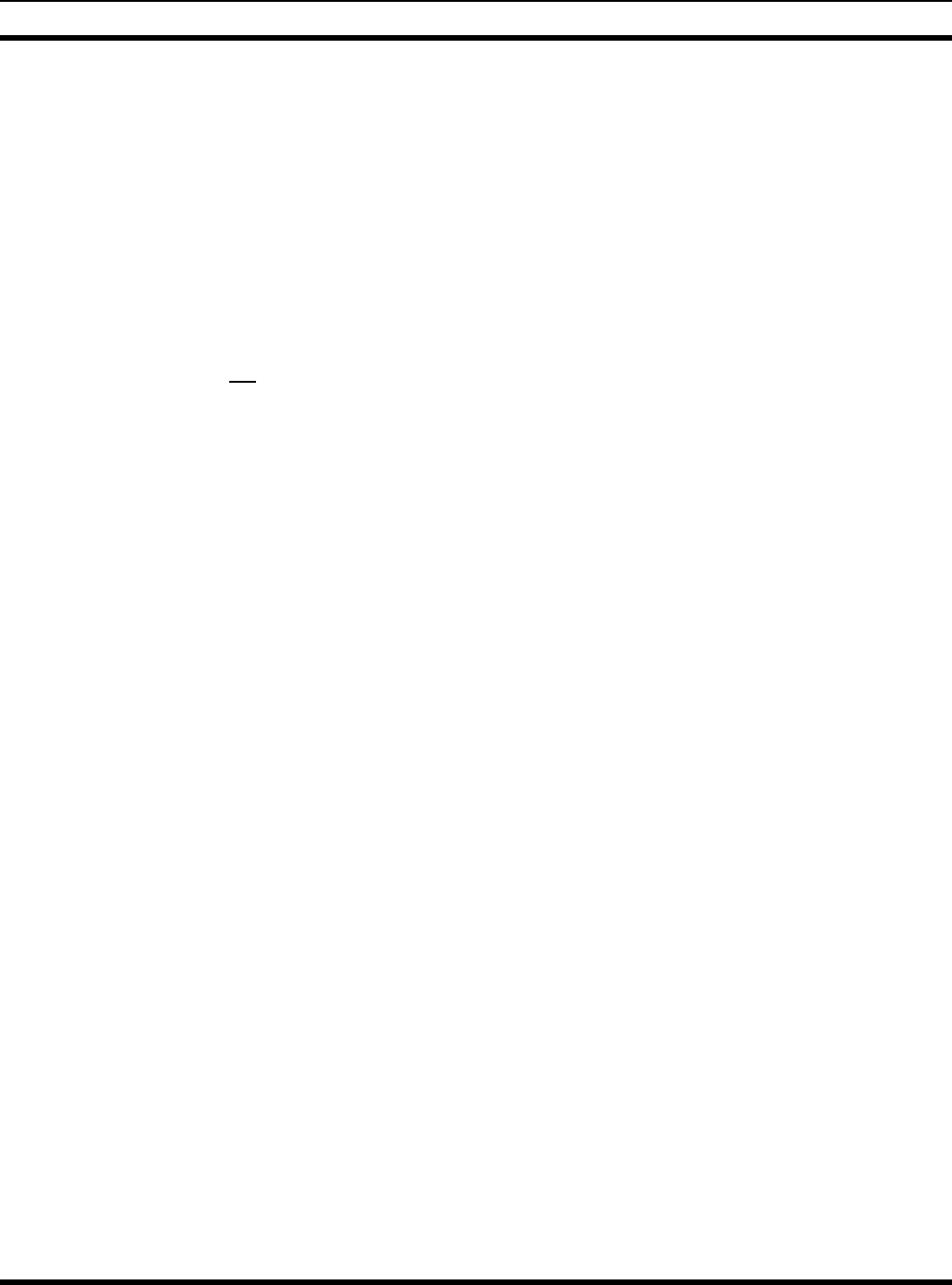

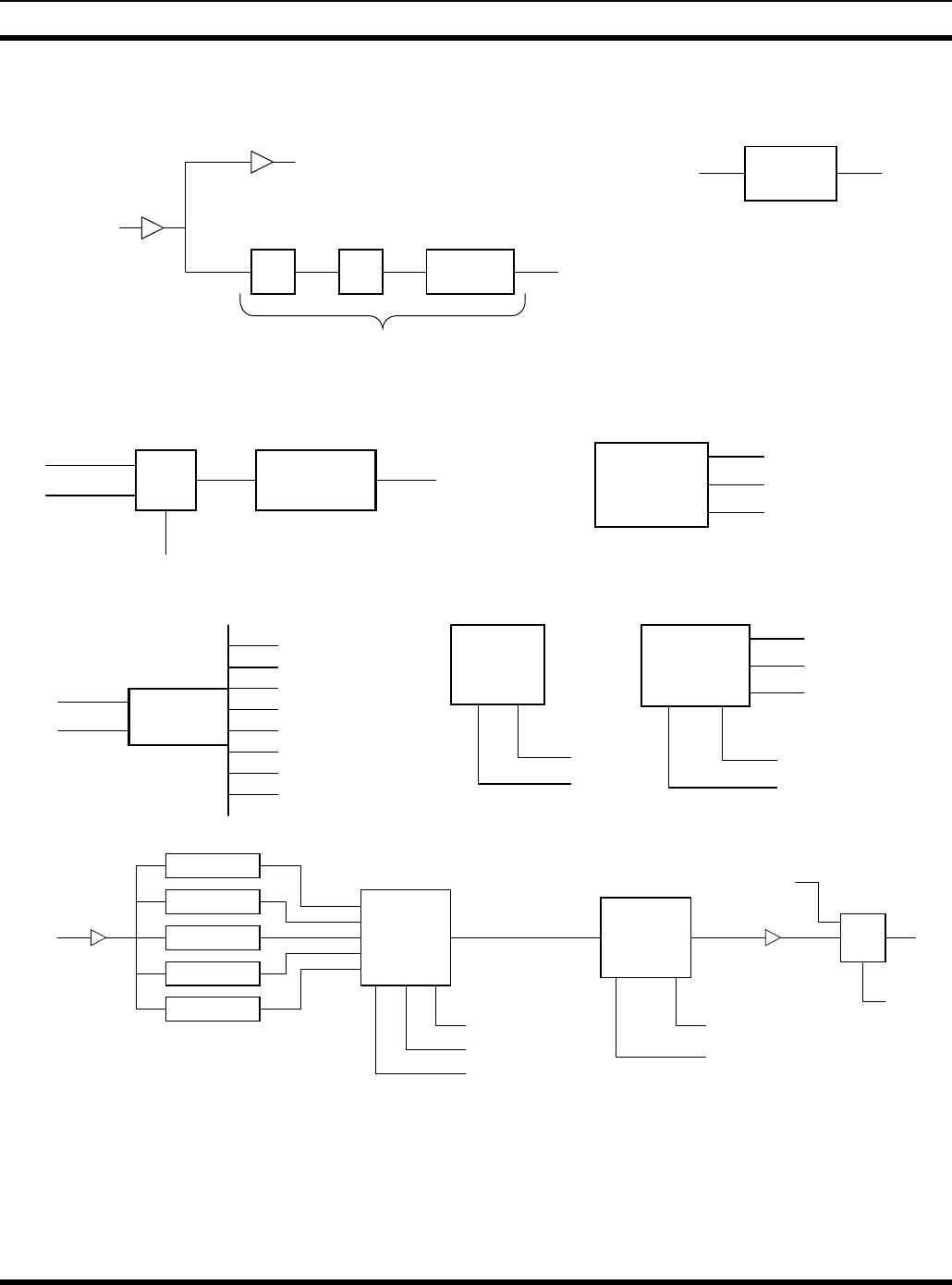

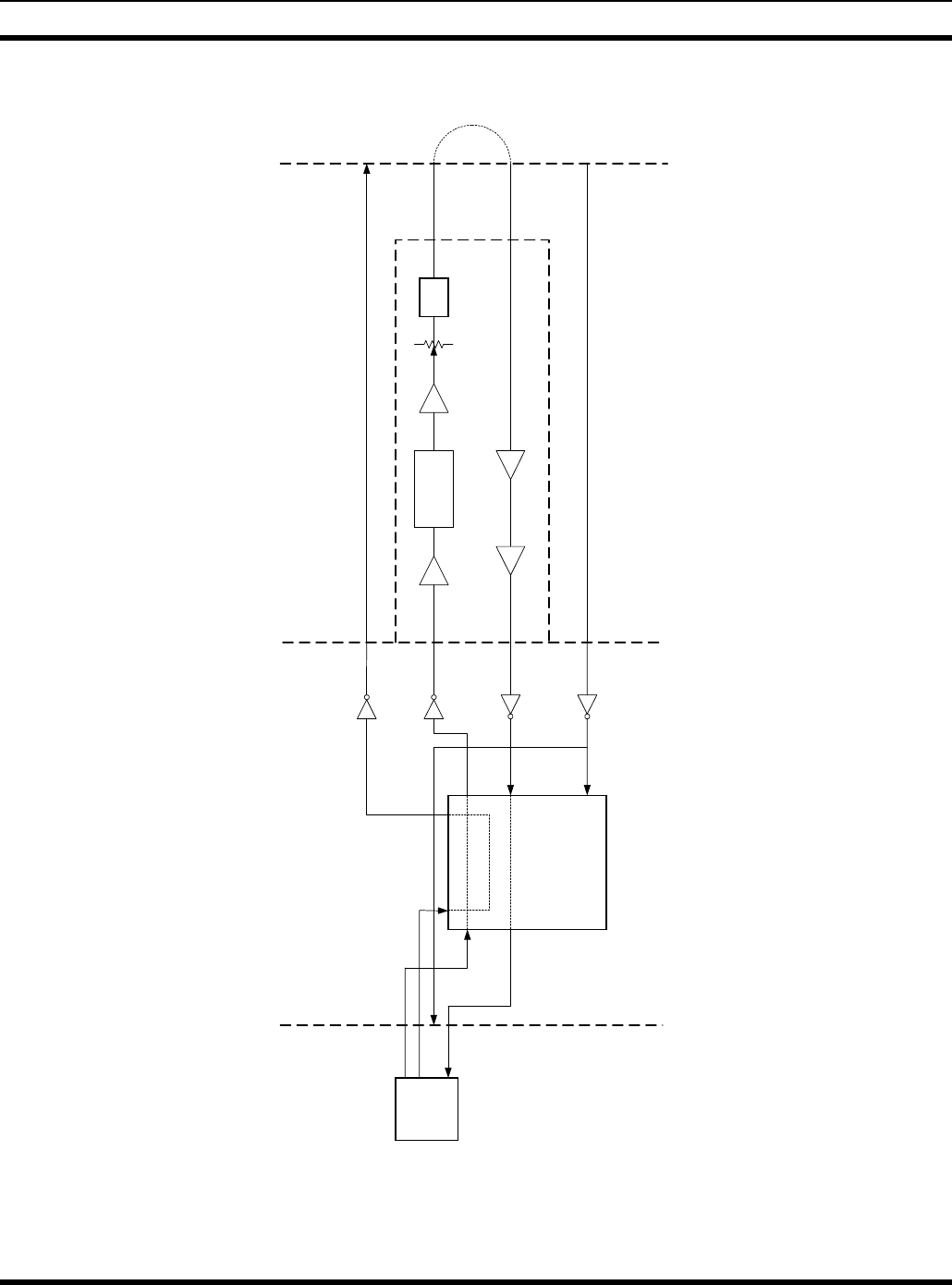

Loc PTT

Rem PTT

A/D ModCtrl

HSD

LSD

PA Fail

Local Rx Audio

Local Tx Audio

RUS

Rem Audio Flag

Local Rx Mute

Synth_Locked

Synth_Clk

Synth_Data

Synth_LdEn

ADCin

bypass

inhibit

ext_PTT

ext_ADModCTrl

ext_150

ext_HSD

TxClk_in

TxClk_alarm

E0

E1

SCC1

SCC2

SCC3

SMC1

BSL/FSL0

BSL/FSL1

Com3

Com4

SP0

SP1

Controller

Analog

Power Supply

(switch mode)

SSP0

SSP1

SSP2

External (simulcast)

Signals and Control

Conventional

Signals and Control

Local (station)

Signals and Control

Voter

Signals and Control

Local (RF) HSD

SitePro Interface

FILTERS

LINE DRIVERS

ANALOG SWITCHES

ADC

MPC860

DS80C323

QUART

USRT

PLD

+5v @2a

+/- 12v

EtherNet Ports

Asynchronous

Serial Ports

RMIC

ROCKWELL MODEM

LINE DRIVERS

ANALOG SWITCHES

Voted (VDI) HSD

Remote (PL) HSD

CPTT

TxCGDis

CGMon

Vot_emsq

Vot_rcvng

Figure 3 - SitePro Shelf Assembly Block Diagram

CIRCUIT ANALYSIS

26 MM101271V1 R2A

7.2 INTERCONNECT BOARD (A1)

Interconnect Board CB101073V1 is a passive printed circuit board that provides

interconnections between all internal components of the SitePro Controller shelf and

interfaces the SitePro Controller shelf with the outside world (Refer to Table 3 -

Interface Connections, and Interconnection, Outline and Schematic Diagrams). Pi

filters U1 thru U29 reduce any Electro Mechanical Interference (EMI).

7.3 CONTROLLER BOARD (A2)

Controller Board CB101069V1 contains all SitePro Controller logic and control functions

except the power supply and Rockwell Modem (Refer to the Outline and Schematic

Diagrams for the Controller Board as listed in the TABLE OF CONTENTS).

This Controller Board is based on an MPC860 microprocessor, the primary responsibility

being message processing. This board has multiple high-speed serial ports, two of, which

are used for primary and secondary BSL’s. It has hardware and dual port RAM to support

the SitePro Modem Board and a 10/100 Mbit ethernet port. This port is available for

Voice Over IP traffic. A second 10 Mbit ethernet port is available for management

functions.

This board has sufficient memory to support 1M LIDs and 64k GIDs. It has LID and GID

validation for all calls.

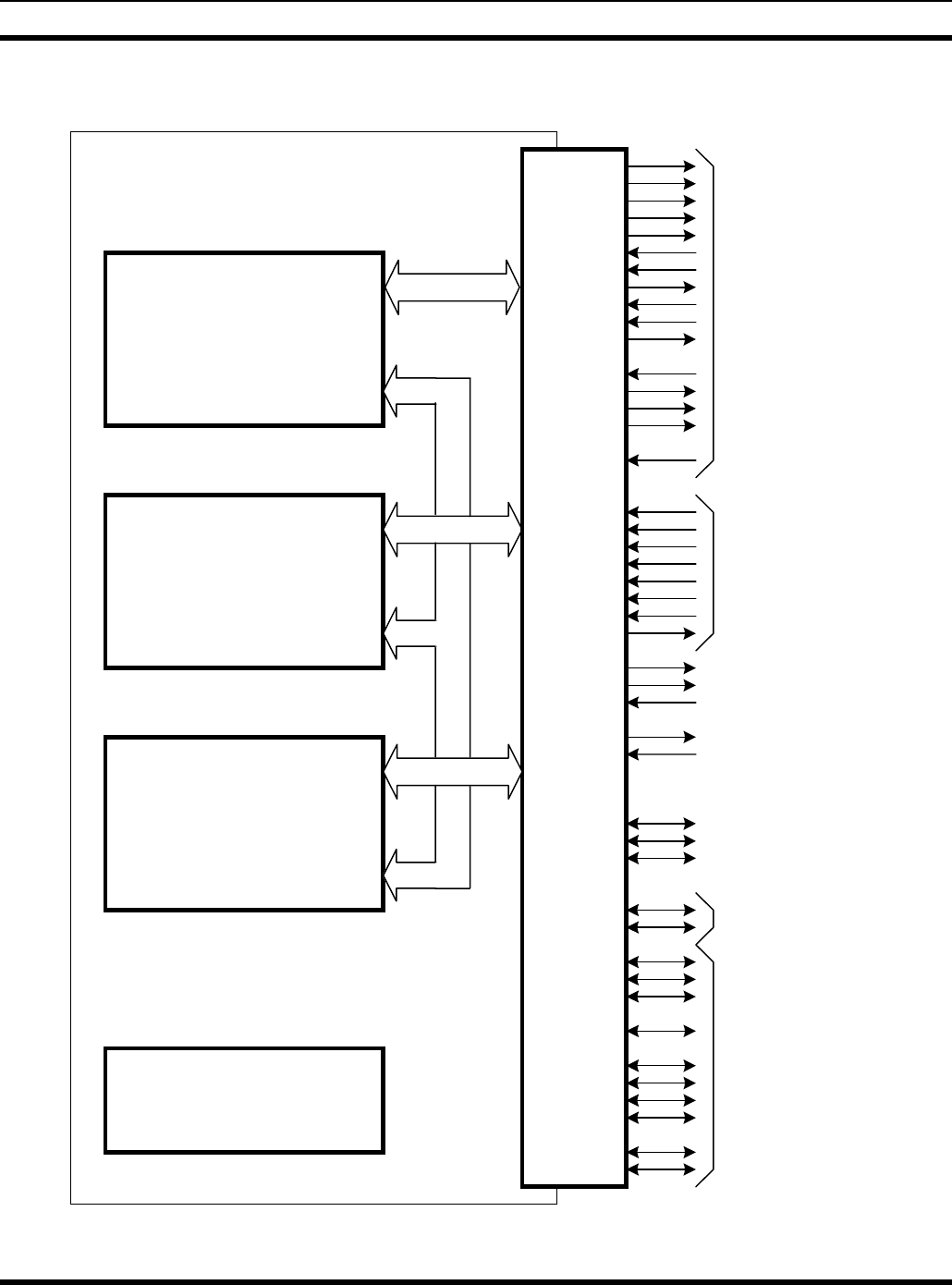

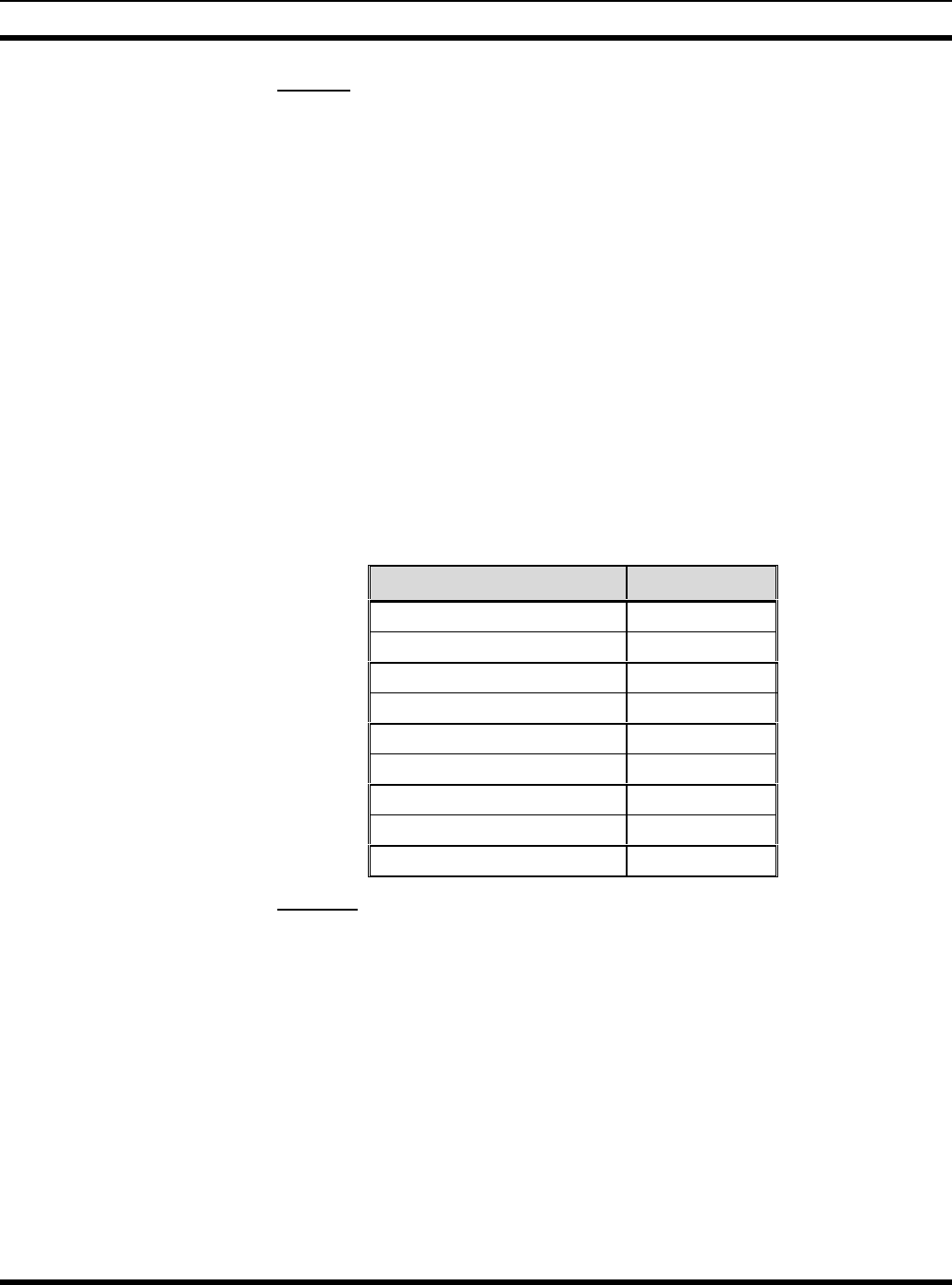

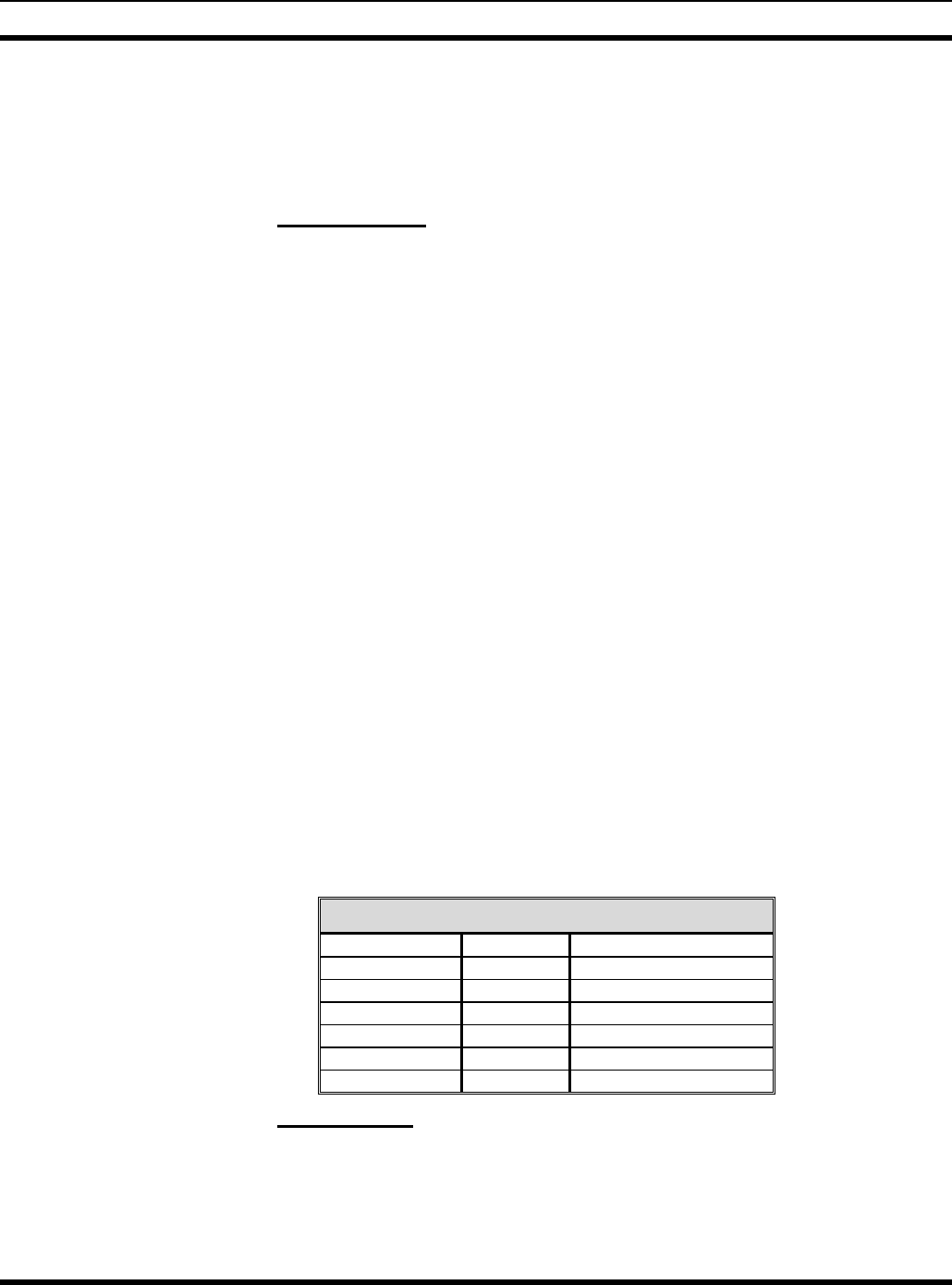

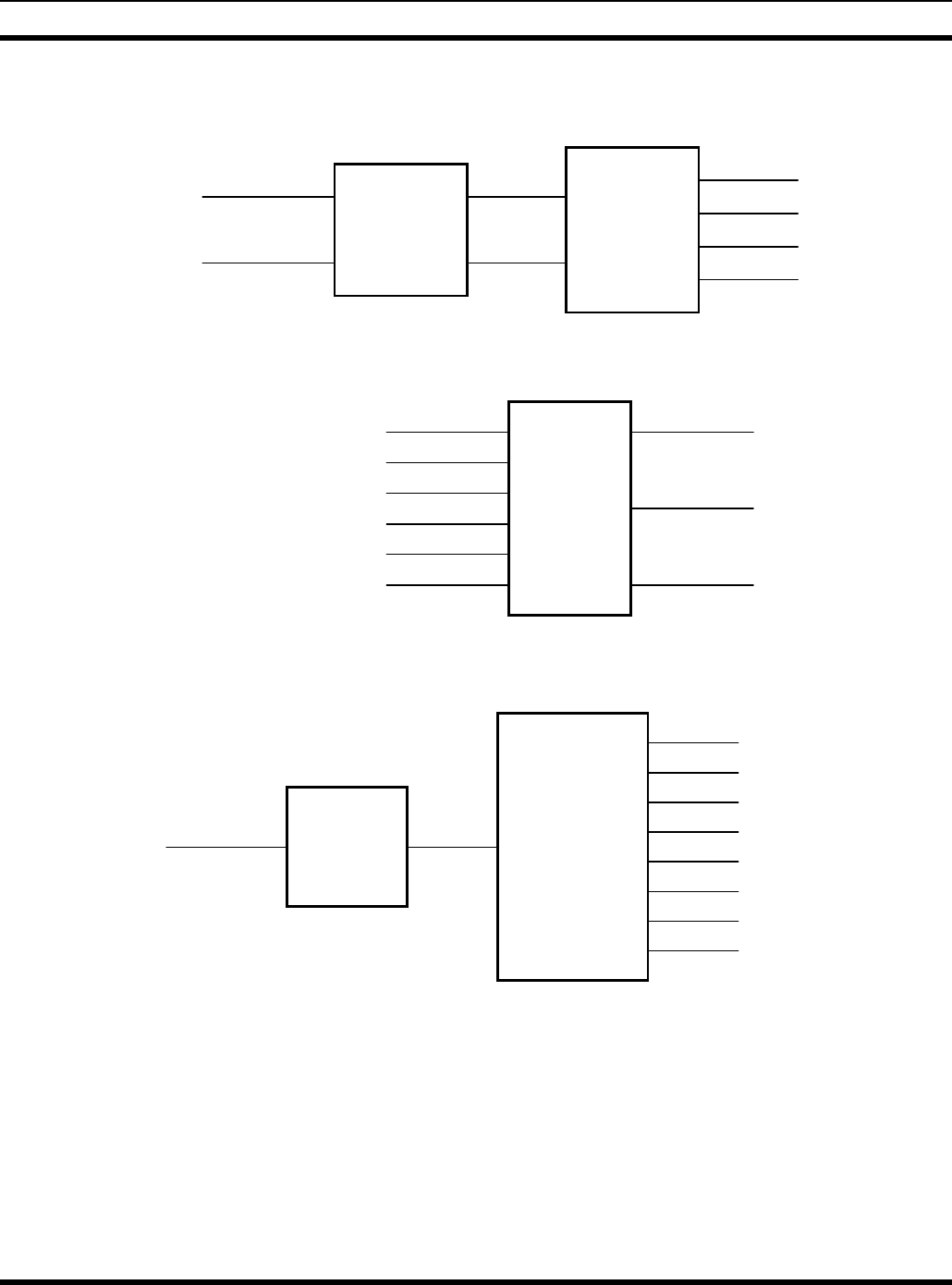

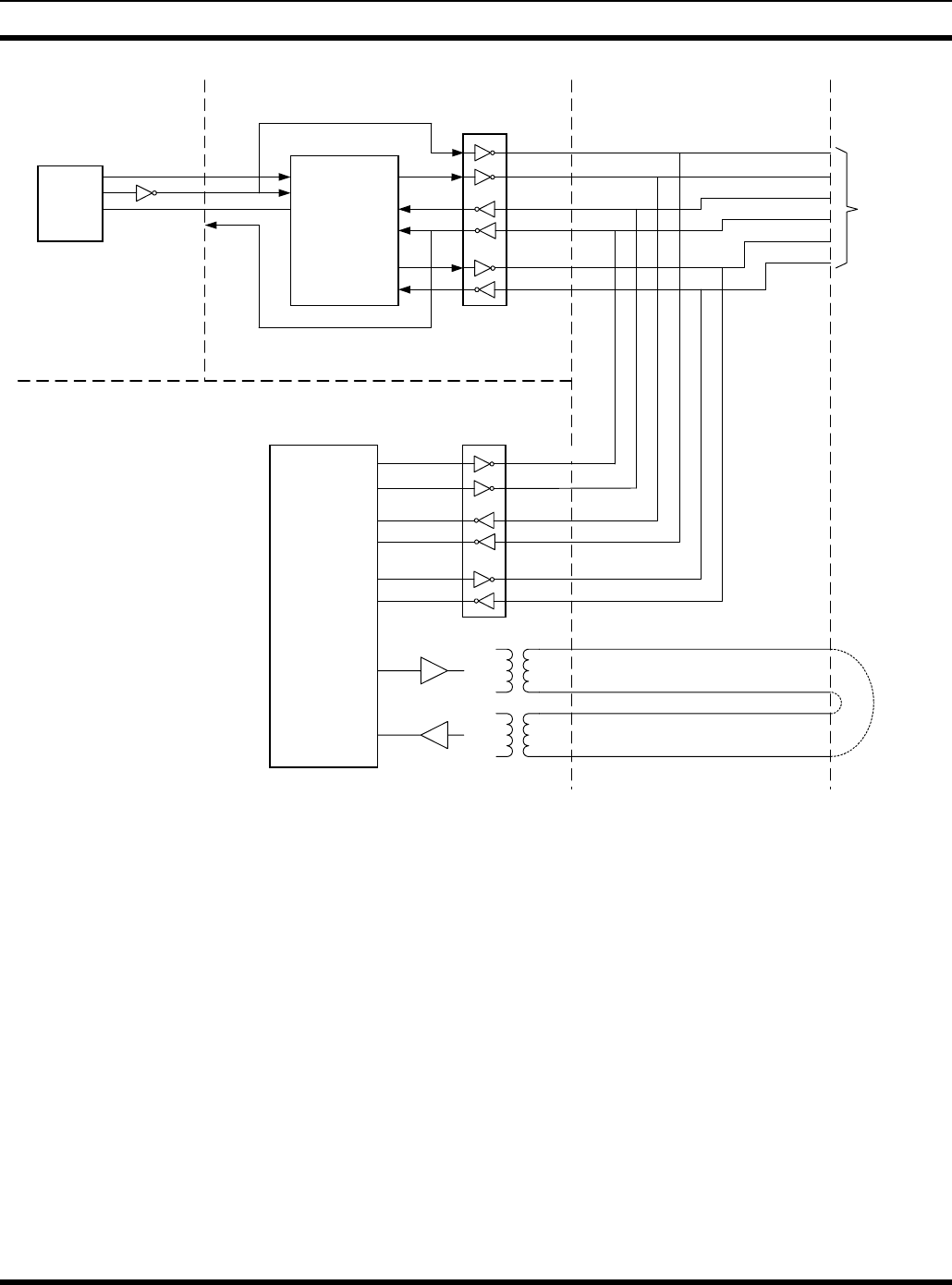

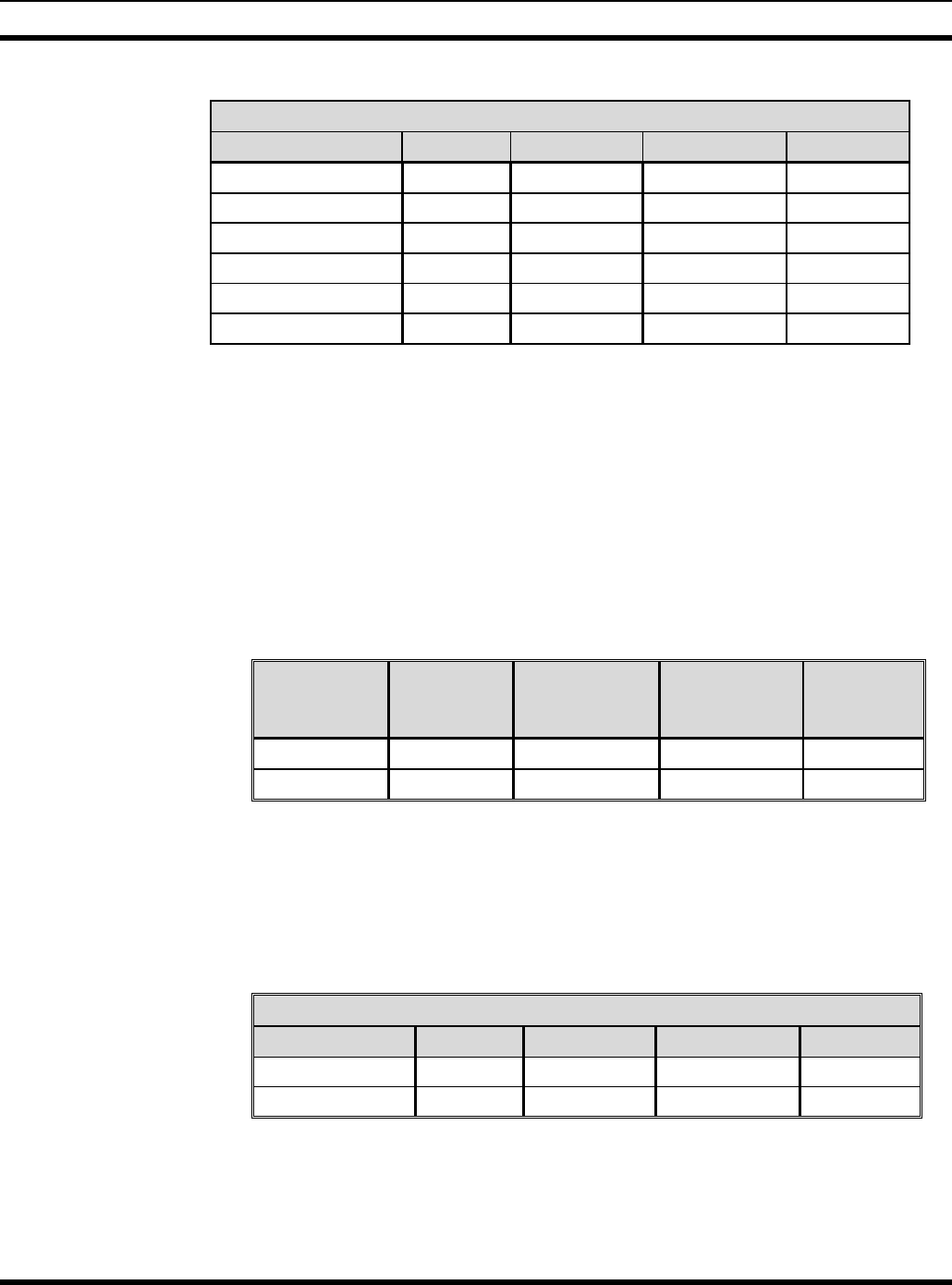

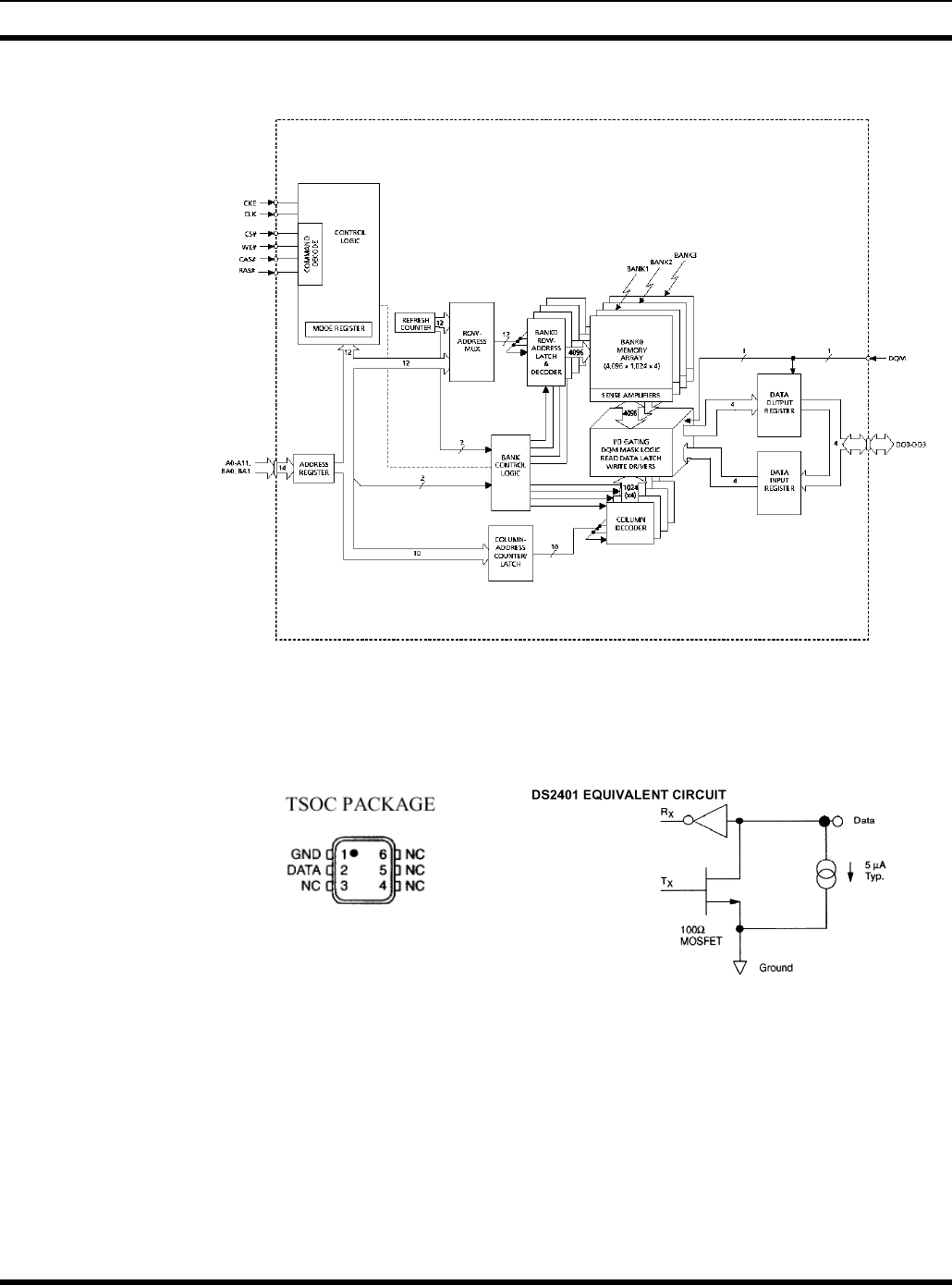

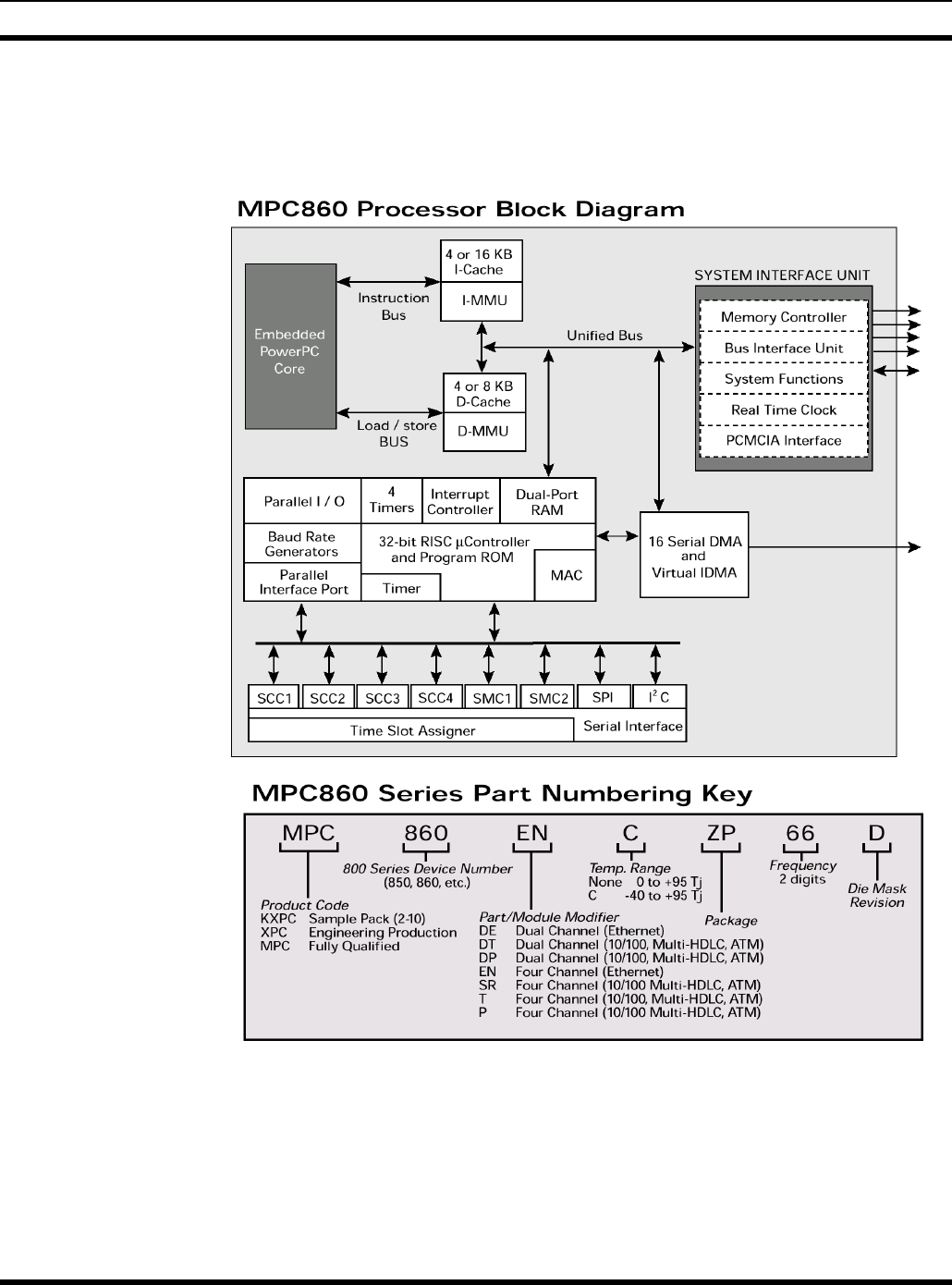

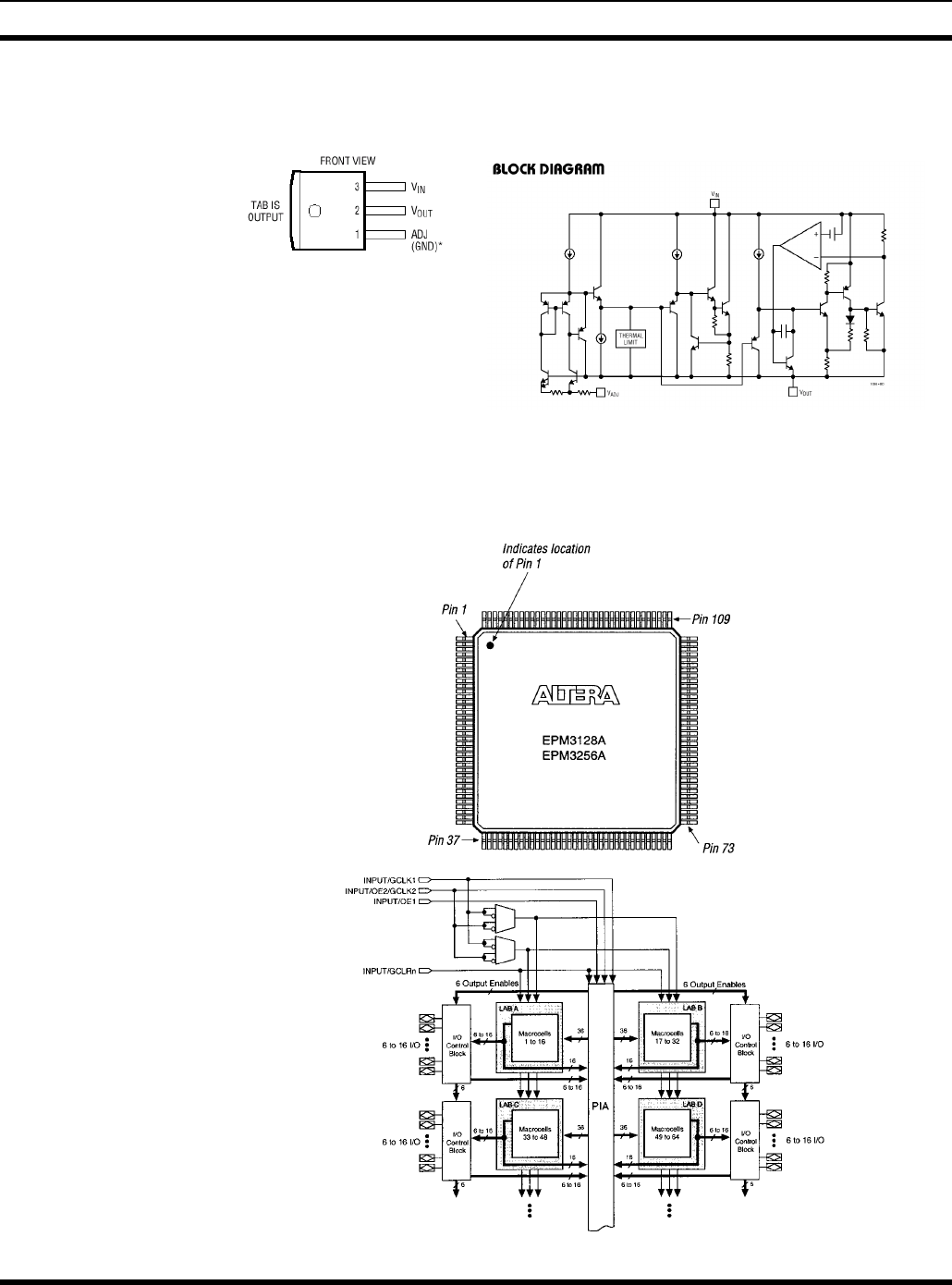

7.3.1 Block Diagram

Figure 4 - Controller Board Block Diagram shows the connection of major components

from a high level viewpoint. Schematic Diagram WD-CB101069V1, Sheet 2 also

provides a Block Diagram for the Controller Board. These diagrams show the major

components of this board as:

• CPU (MPC860P)

• Ethernet 10 Base T

• Ethernet 10/100 Base T

• EEPROM

• Modem Board

• Memory:

⇒ FLASH

⇒ DRAM

• Electronically Programmable Logic

Device (EPLD)

• Quad UART (QUART)

• LEDS

• DIPSWITCH

• I2C Real-Time-Clock (RTC)

• Serial Ports

• Regulator

• Hot Swap Controller (HSC)

• Interconnect Board (Backplane)

7.3.2 System I/O

The System I/O circuits for the Controller Board are shown on Schematic Diagram WD-

CB101069V1, Sheet 3 and include:

• Oscillator For PHYs • 3.3V Power Monitor

• JTAG Port • Test Points

• Board Insert Detection Circuit • Programming Serial Port J8

• Hot Swap Controller • Decouplers

• 3.3V Regulator

CIRCUIT ANALYSIS

MM101271V1 R2A 27

MPC860P

59 MHz

MII

Enet PHY

10/100 BaseT

1:1 1:1

SDRAM

8M x 32

FLASH

1M x 32

I2C

EEPROM

32K x 8

32.768

kHz

RTC

29.4912

MHz

SMC1

SMC2

SCC4

BDM

QUART

RS-232

RS-232

EPLD RS-232

I/O Backplane

1

2

3

4

RS-232

RS-232

SitePro Modem Board

OUTs

INs

32

32

32

8

JTAG

INTsDATA

REG

5V

3.3V

PL

JTAG

JTAG

I/O

+12V

Enet PHY

10 BaseT

1:1 1:1

SCC1

LEDs

VDIRF

RS-232

RS-232

DIP SW

RS-232SCC2

RS-232

SCC3

I/O

Serial

Number

RS-485

BSL

BSL

XCVR

JTAG

5V

HSC

JTAG

I2C RTC

3.0V

Batt

32.768

kHz

DIAGNOSITC

PORT

Figure 4 - Controller Board Block Diagram

CIRCUIT ANALYSIS

28 MM101271V1 R2A

7.3.2.1 Oscillator For Ethernet PHYs

This circuit consists of crystal oscillator circuit Y1 powered by 3.3 V applied to Y1, Pin

4, Vcc. Oscillator circuit Y1 is biased on by resistor R49 connected to Y1, Pin 3, CTRL

and produces 25 MHz on the output at Pin 3 through resistor R51 (OSC 25MHz). This

output connects to the CLK25 inputs to the Ethernet 10 and Ethernet 10/100 Mbit

PHYs3.

7.3.2.2 JTAG Port

This JTAG PORT circuit consists of buffer U1 (NC7SZ125M5). This circuit allows

programming directly to the microprocessor through connector J4. This circuitry is not

presently used.

7.3.2.3 Board Insert Detection Circuit

This circuit consists of NPN transistors Q6 and Q7. When the Controller Board is

inserted into a live Interconnect Board, the base circuits of these transistors are connected

to ground through connector J1B, Pins B1 and B32 at either end of J2. Connector J1B,

Pin B1 is MATE-DETECT-A and J1B, Pin B32 is MATE-DETECT-B. With the base of

both transistors at ground, they are held in the off state. This allows POWER ON to cycle

high if the output of U41 is high. The POWER ON voltage is applied to Pin 2 of Hot

SwapTM Controller U37. If the base of either transistor (Q6 or Q7) is not connected to

ground, POWER ON will not be applied to the HotSwap Controller. Therefore, if the

card is not seated properly, power will not turn ON.

7.3.2.4 Hot Swap™ Controller

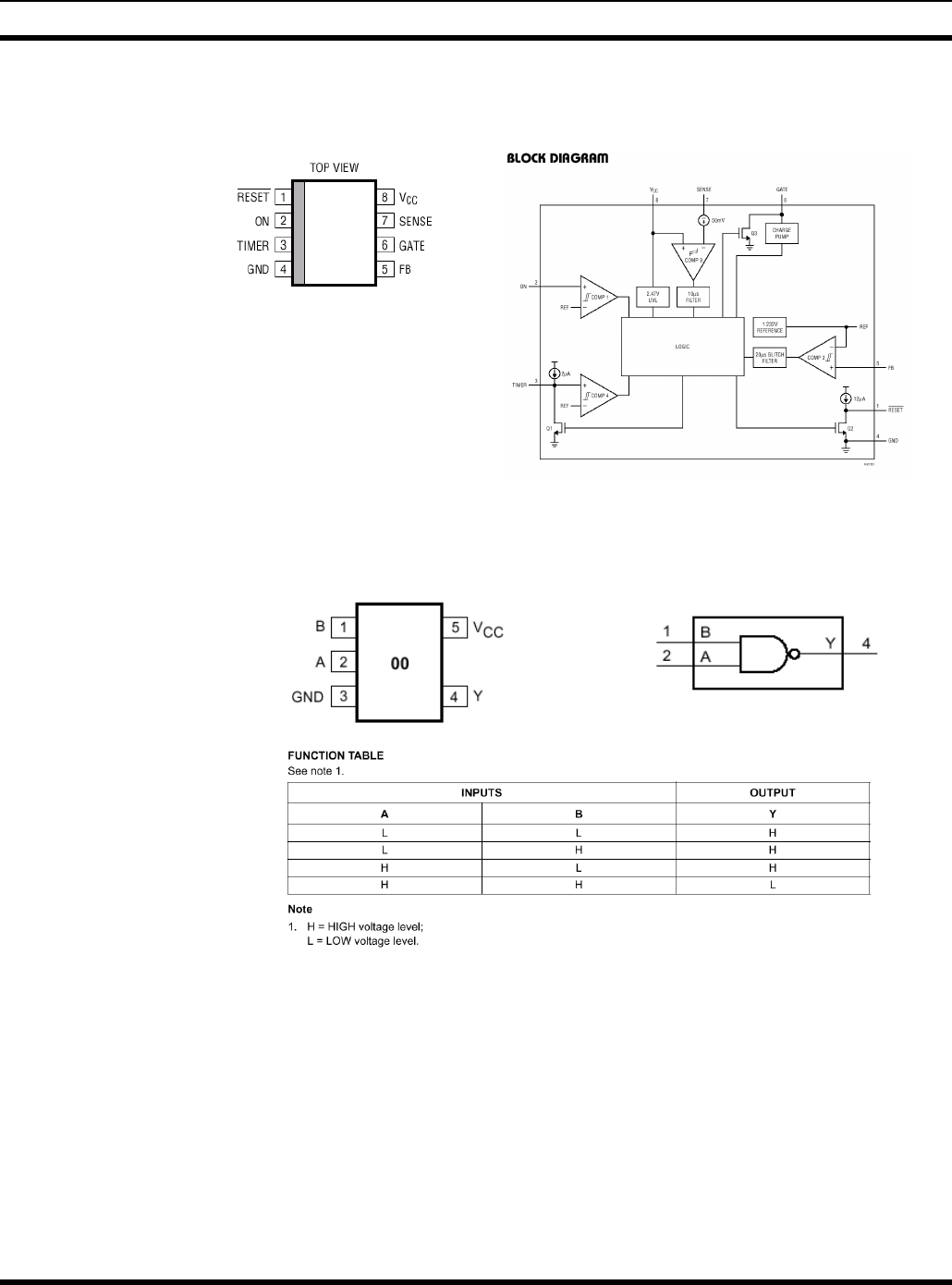

Hot Swap™ controller (HSC) U37 allows Controller Board CB101069V1 to be safely

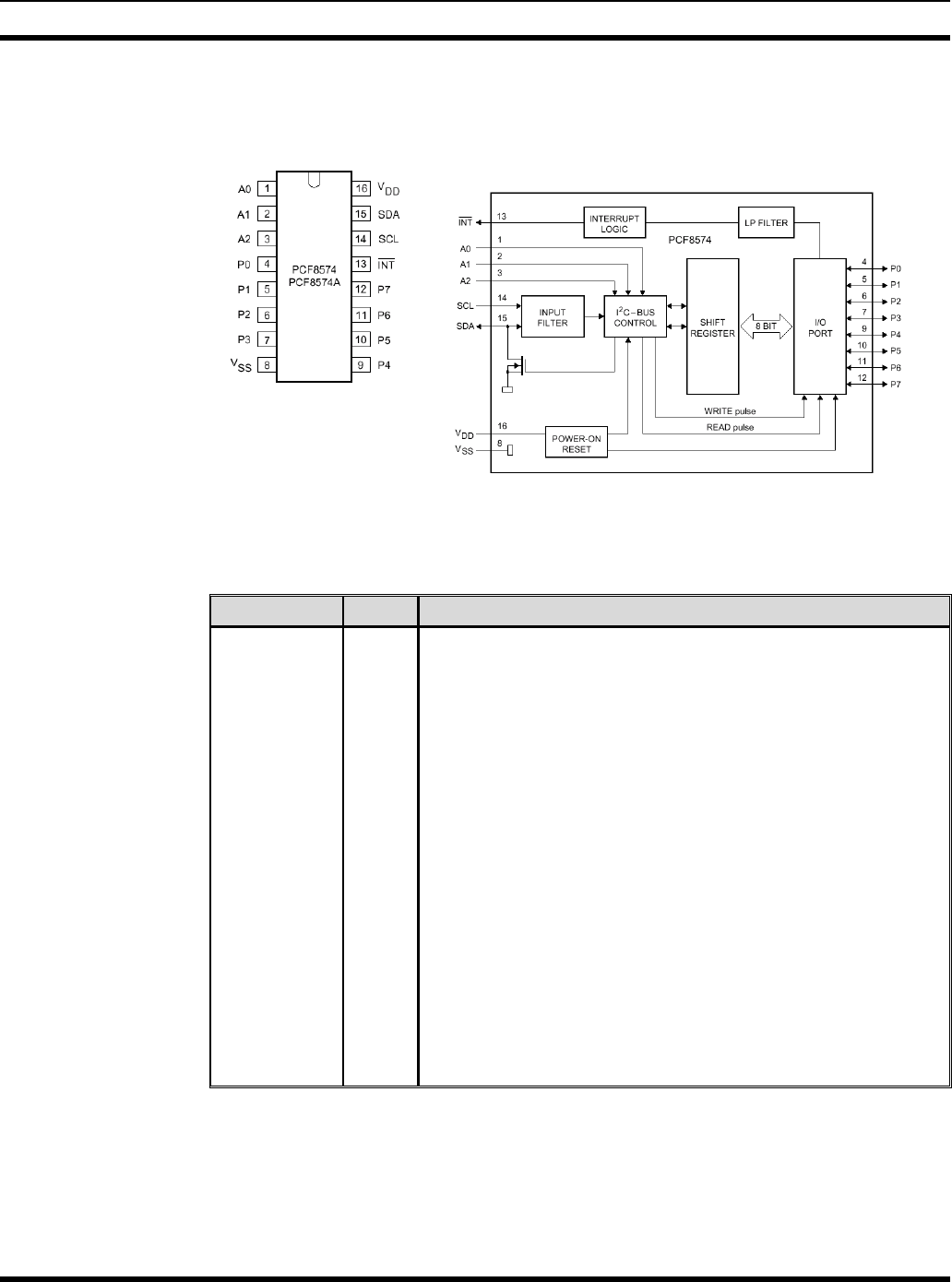

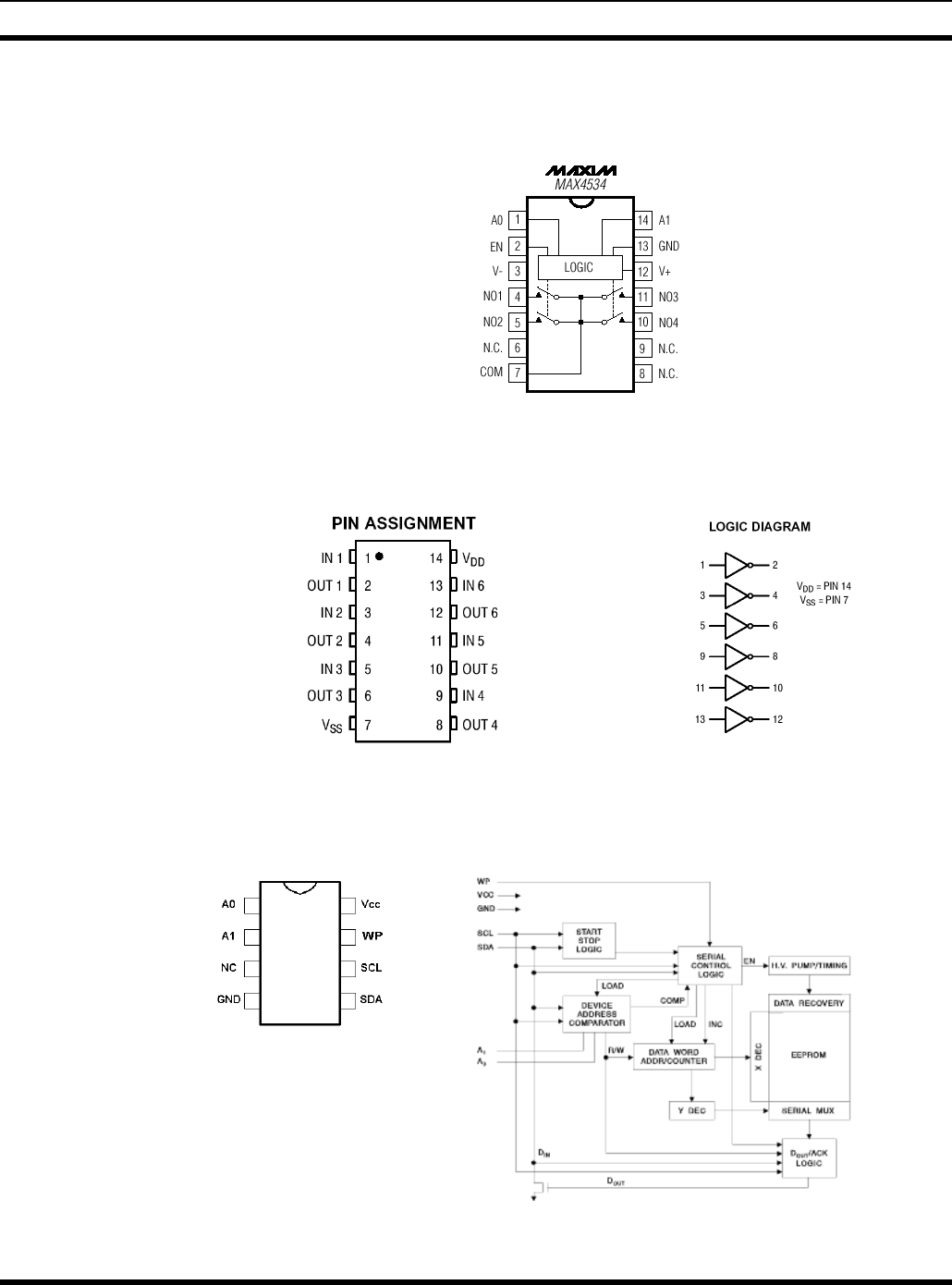

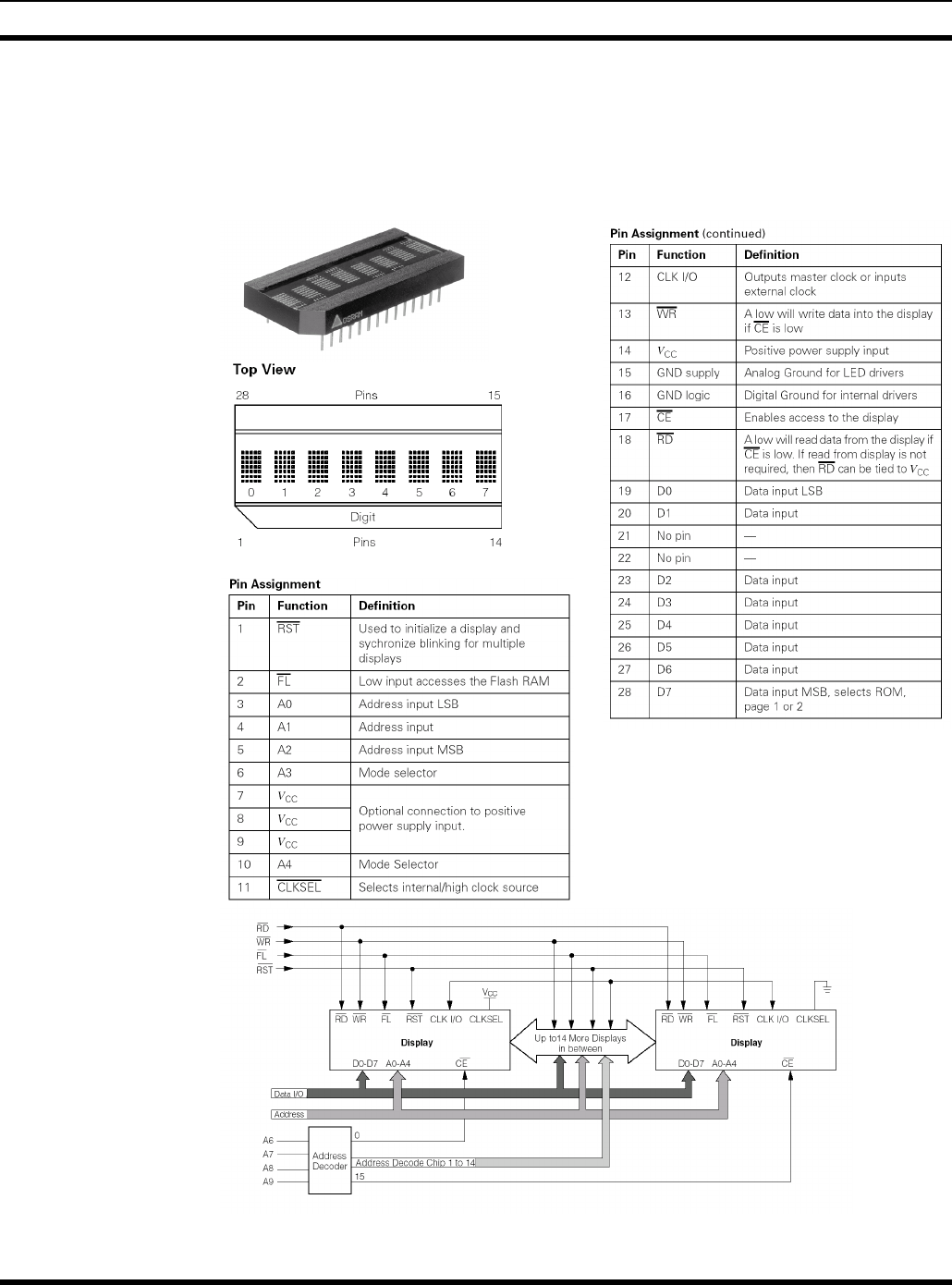

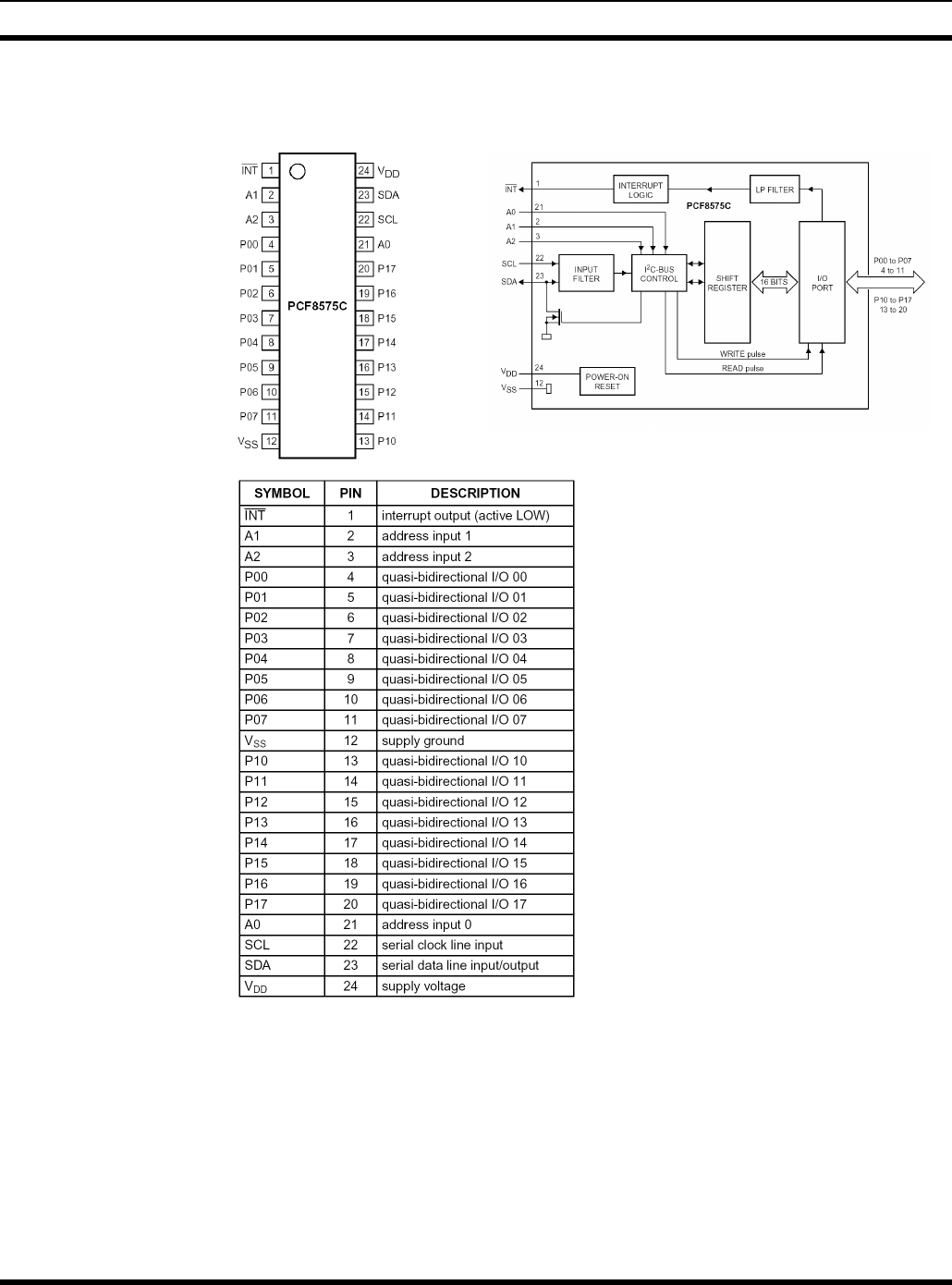

inserted in or removed from Interconnect Board CB101073V1 while voltage is applied.

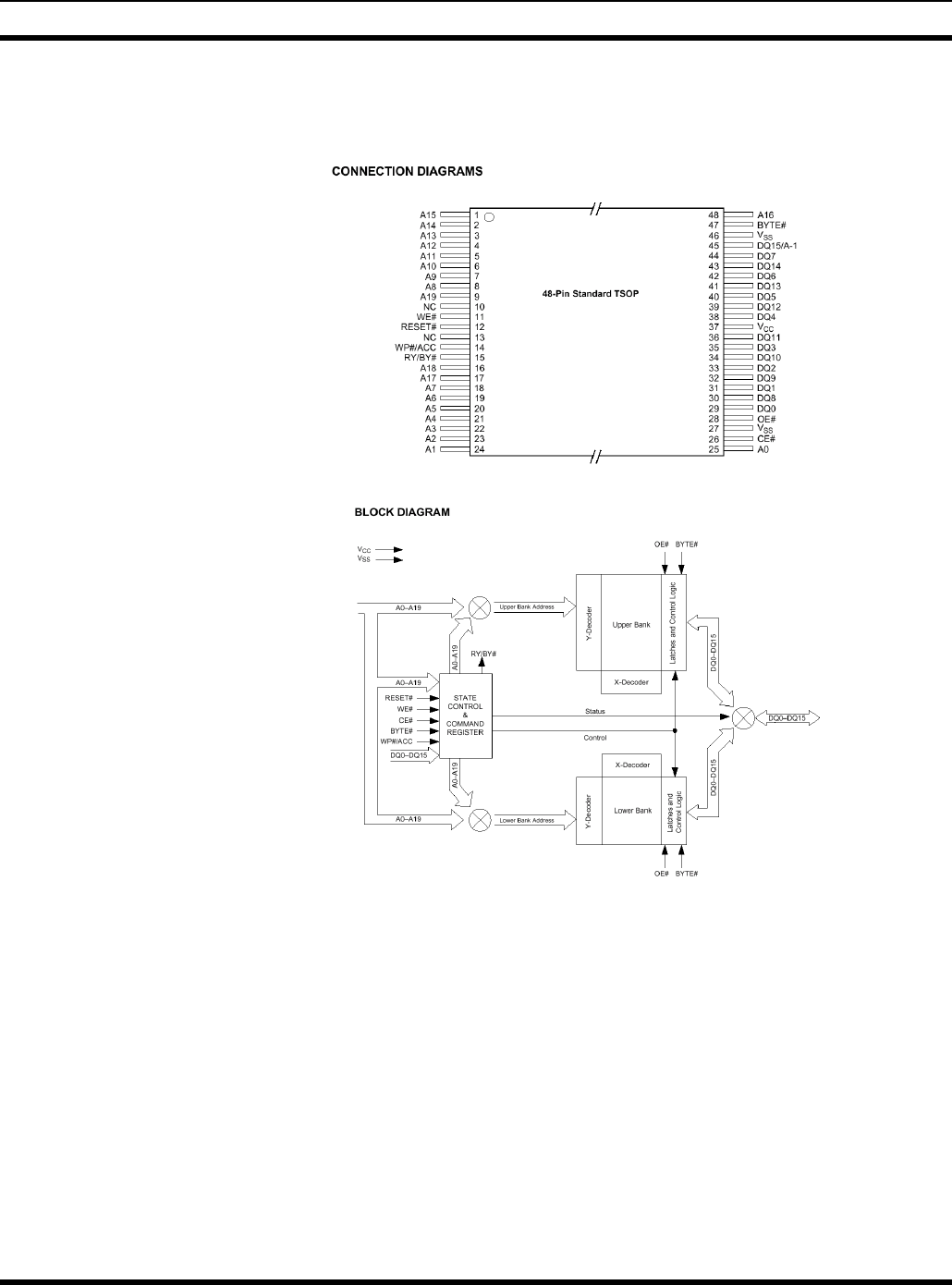

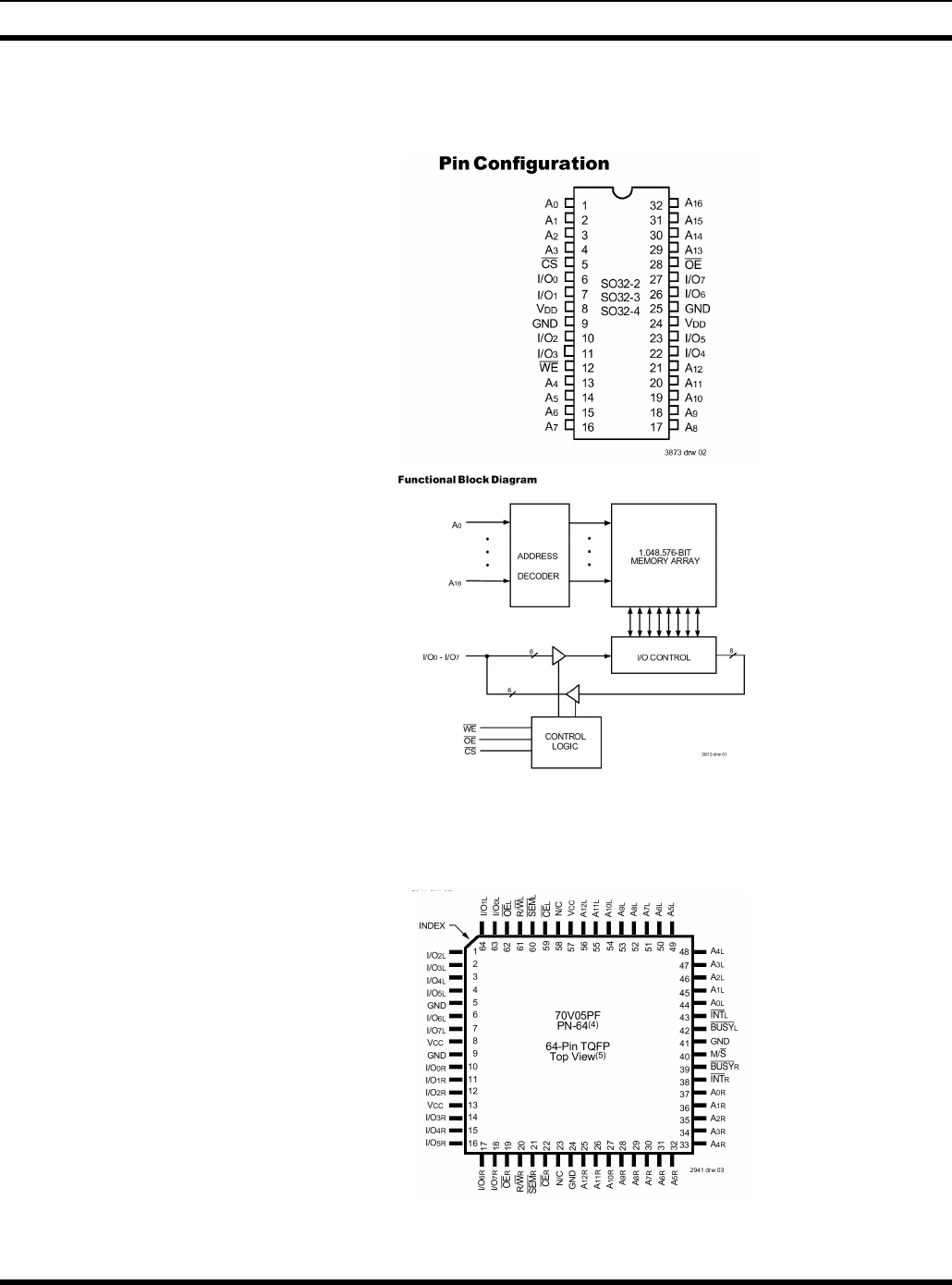

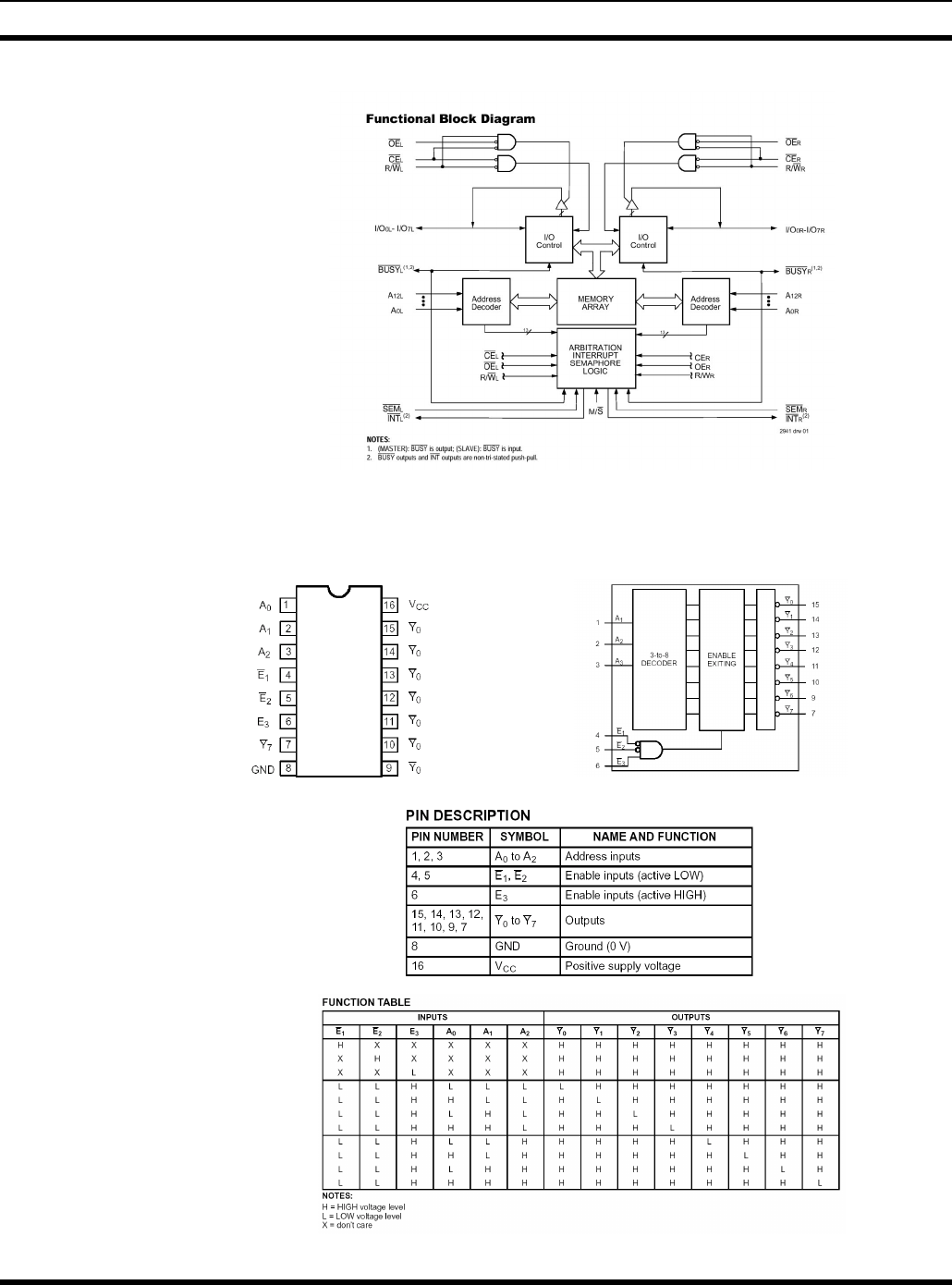

Using external N-channel pass transistor Q5, the supply voltage to the Controller Board is

ramped up at a controlled rate. Hot Swap switch driver U37, Pin 6 controls the N-channel

gate. A programmable electronic circuit breaker detecting over current by sensing voltage

across 15 milliohm resistor R153 protects against shorts. The RESET output (U37, Pin 1)

is used to generate a system reset when the supply voltage falls below the voltage preset

by resistors R167 and R168. The POWER ON input to U37, Pin 2 is used to cycle the

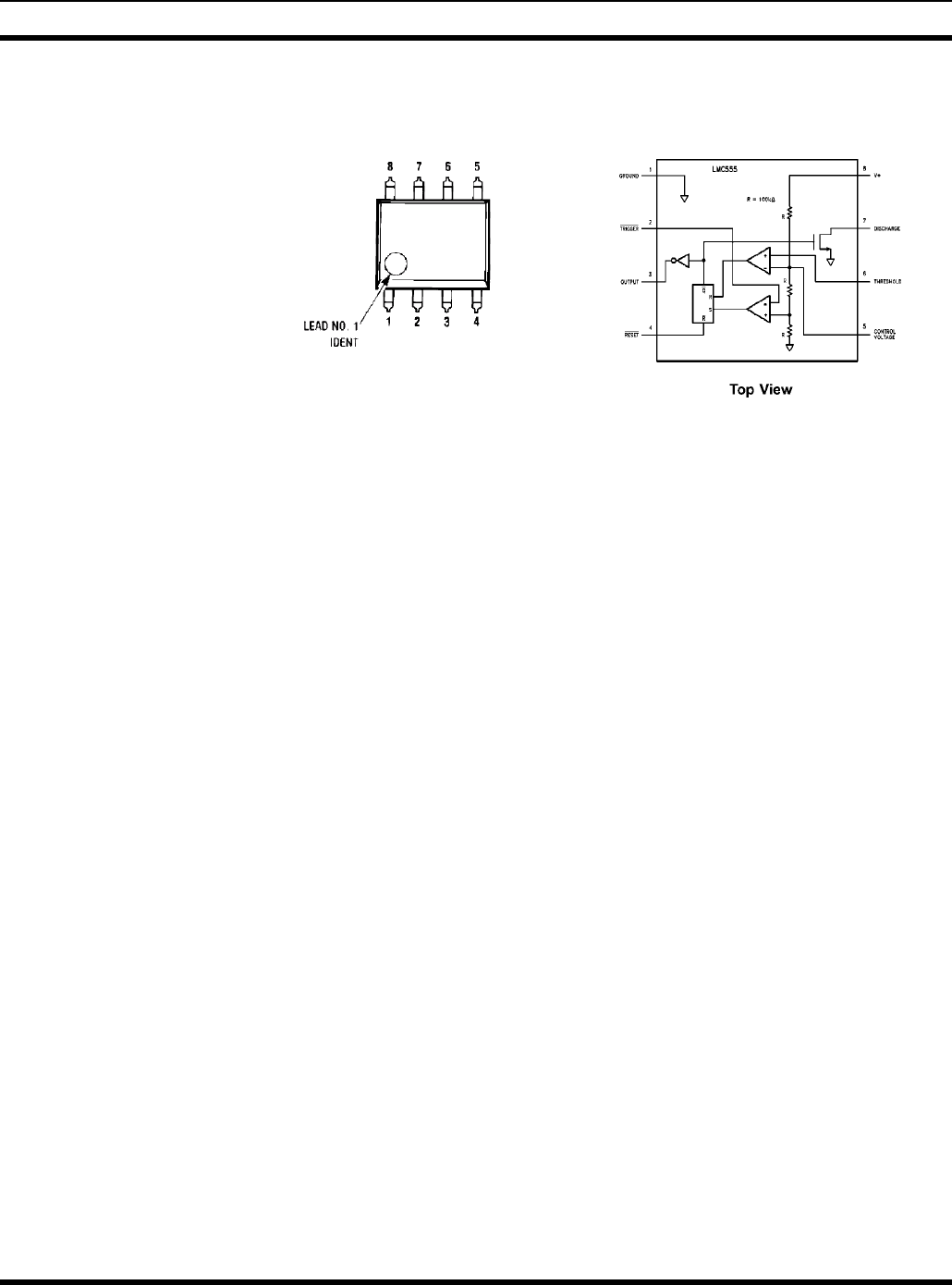

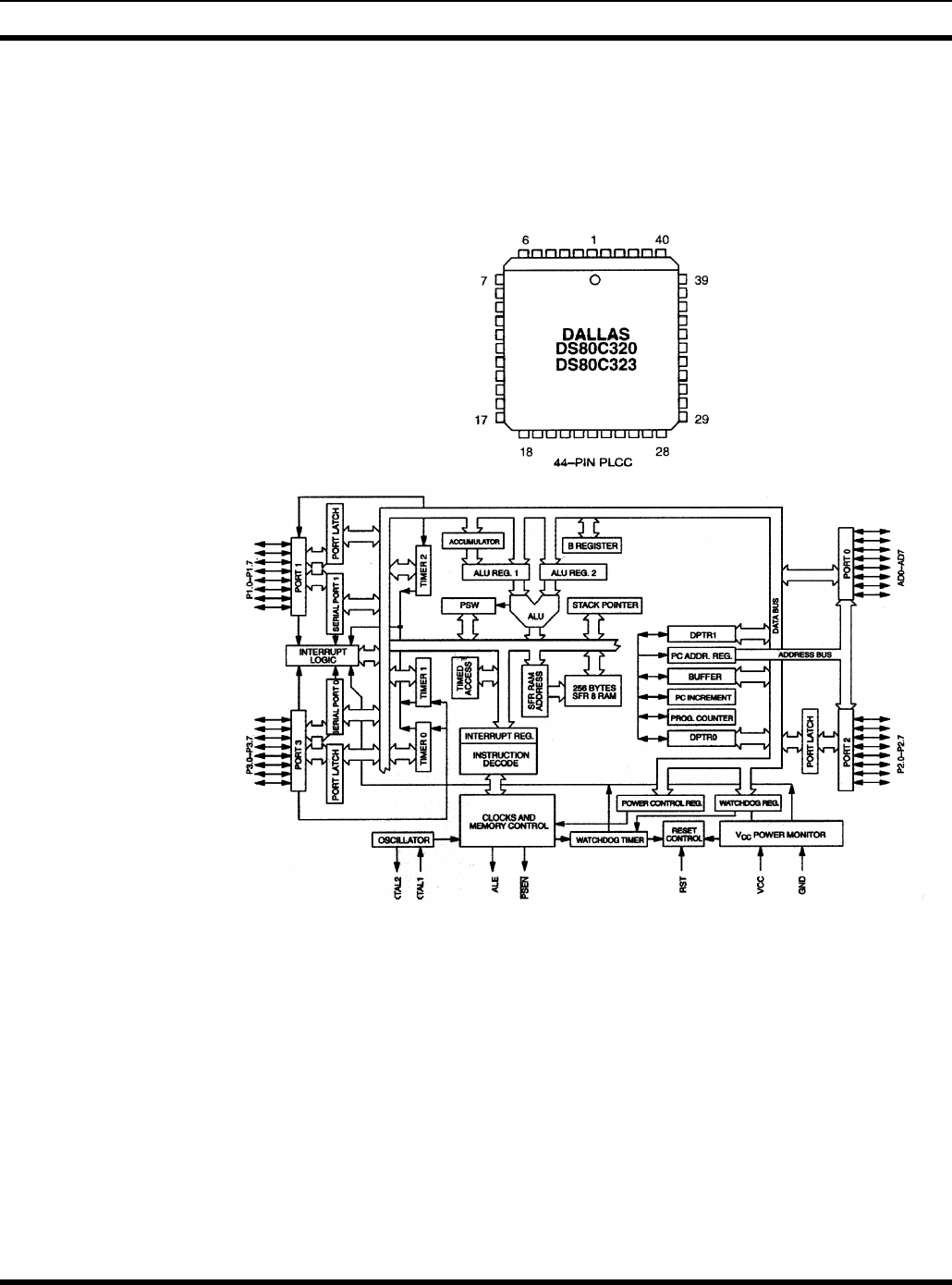

Controller Board power. The 555 timer circuit (U40) is connected to the HSC chip so that

the HSC can be automatically reset in the case of a circuit breaker fault.

Because the Hot Swap Controller, U37, latches OFF if it senses an overload, a timer

circuit has been added to occasionally turn it back ON. If the overload still exists, it turns

off immediately but if the overload is not present, normal operation is restored. This

circuit is needed for unattended operation.

The 555 timer is powered any time 5V is applied to the board since it is connected ahead

of the Hot Swap Controller. As long as the HSC is ON, 5V is fed to inverter U42-2

through D34. The resulting low on U42-4 holds U40 at reset.

When the HSC turns power OFF, U42-4 goes high and the reset is removed. The timer

now free runs with about a 1.1 second cycle time. U40-3 is high for about 0.7 sec and low

3 PHY is an Industry Standard for “Physical Interface.”

CIRCUIT ANALYSIS

MM101271V1 R2A 29

for about 0.4 sec. U40-3 is inverted by U41. During the high part of the cycle, the

resulting low at U41-4 holds the HSC ON pin low keeping the HSC OFF.

When U40-3 switches low, U37-2, the HSC ON pin is allowed to go high through D35,

pulled up by resistor R157. The HSC turns ON, but if the fault is still present, it turns

OFF within 40µs and the cycle continues. If the fault is gone, the 555 is held reset and the

Controller Board resumes normal functioning.

Capacitor C119 and resistor R191 act as a slugging filter on the FB input to prevent fast

transients on the 5V from causing the HSC to generate a reset. Likewise, capacitor C118

and resistor R190 prevent large transients on the input 5V, i.e. when the RMIC is hot

swapped, from causing the HSC to generate a reset due to a transient on the ON pin.

7.3.2.5 3.3V Regulator

The controller board is provided with 5 Volts and ±12 Volts from the Interconnect Board.

Linear regulator U25 is used to provide 3.3 volts to be used by the majority of digital

logic on the Controller Board and the Board.

The Hot Swap Controller (HSC) is used to ramp up the 5V-power rail at a controlled

rate. This, in addition to other considerations, will allow the Controller Board to be hot

swappable. The 5V output from this circuit will also power the 3.3-Volt regulator, thus

causing the 3.3 V power rail to also ramp up at a controlled rate. As mentioned above, the

HSC has a built-in electronic circuit breaker.

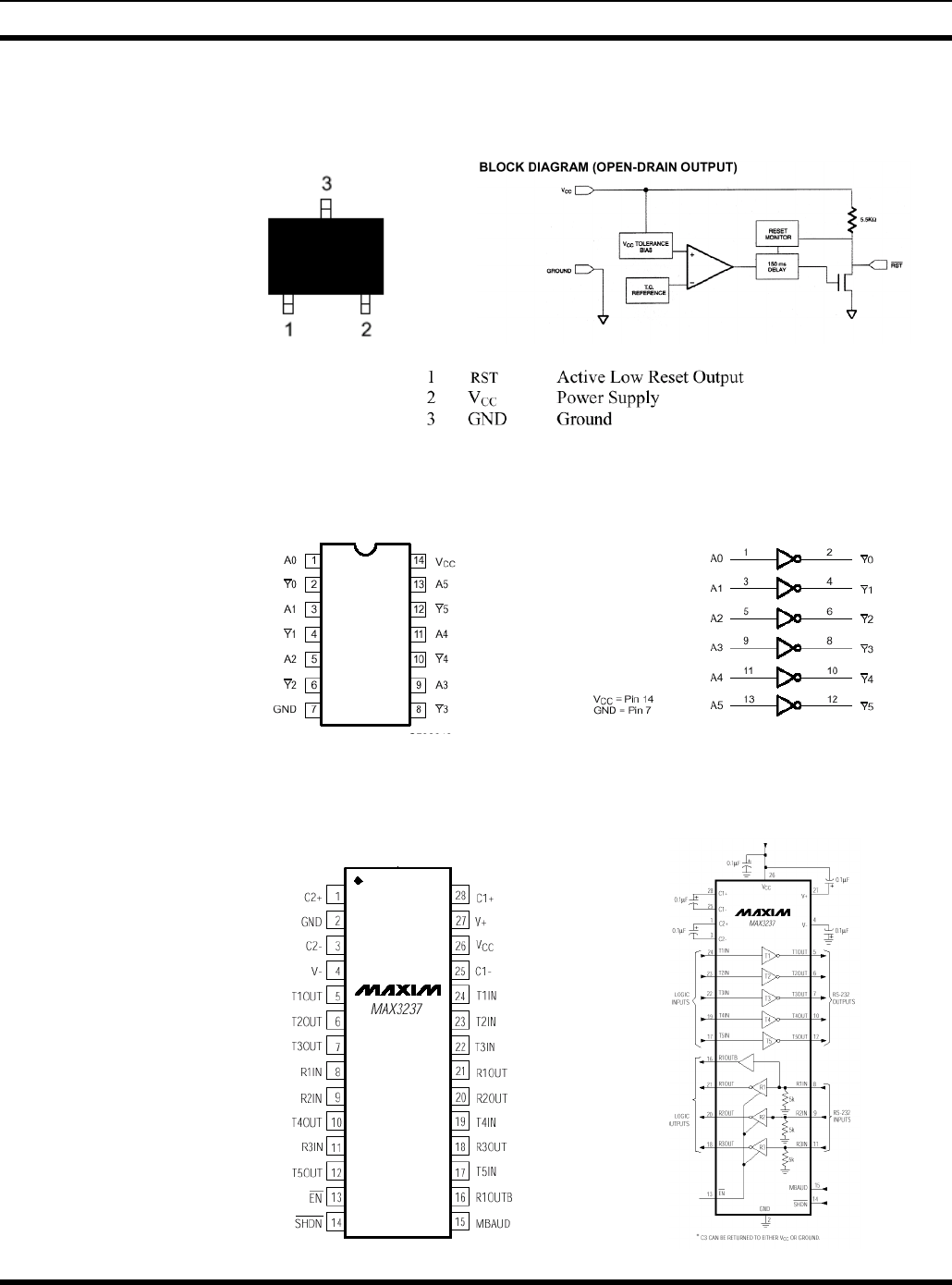

7.3.2.6 3.3V Power Monitor

The 3.3V Power Monitor (U31) uses a precision temperature-compensated reference and

comparator circuit to monitor the status of the 3.3V supply. If a loss of power is detected

an internal power-fail signal forces reset to the active state, which is low. When the 3.3V

supply returns to a normal state, the reset signal is kept active for approximately 150 ms

to allow the power supply and microprocessor to stabilize. This 3.3V Power Monitor

circuit also monitors Reset Pushbutton S1 on the reset output, U31, Pin 1. If the reset is

pulled low, by pressing S1, a reset signal is generated upon release. The output of U31 is

held in reset output (low) for approximately 150 ms.

7.3.2.7 Test Points

Test Points TP1 thru TP10 are provided on the Controller Board as follows:

• TP1 thru TP3, TP7, TP8 and TP10 are ground connections

• TP4 is +12V

• TP5 is +3.3V

• TP6 is +5.0V

• TP9 is WALSHCLK

7.3.2.8 Programming Serial Port J8

This port (J8) is located at the front of the Controller Board just behind the hinged door.

It is provided so that a programmer can easily program the microprocessor from the front

of the SitePro Controller without removing it from the cabinet.

CIRCUIT ANALYSIS

30 MM101271V1 R2A

7.3.2.9 Decouplers

Decoupling capacitors (Decouplers) are used to eliminate high-speed transient noise in

high-speed digital circuits. There are many decoupling capacitors used on the Controller

Board. These capacitors are connected between a source and ground. For example, on

sheet 3 of Schematic Diagram WD-CB101069V1 there are two 3.3V decoupling

capacitors, C2 and C87.

7.3.3 Backplane

The Controller Board to Interconnect Board A1 (Backplane) connector circuits are shown

on Schematic Diagram WD-CB101069V1, Sheets 4-7 and include:

• Board Connections • I/O (1)

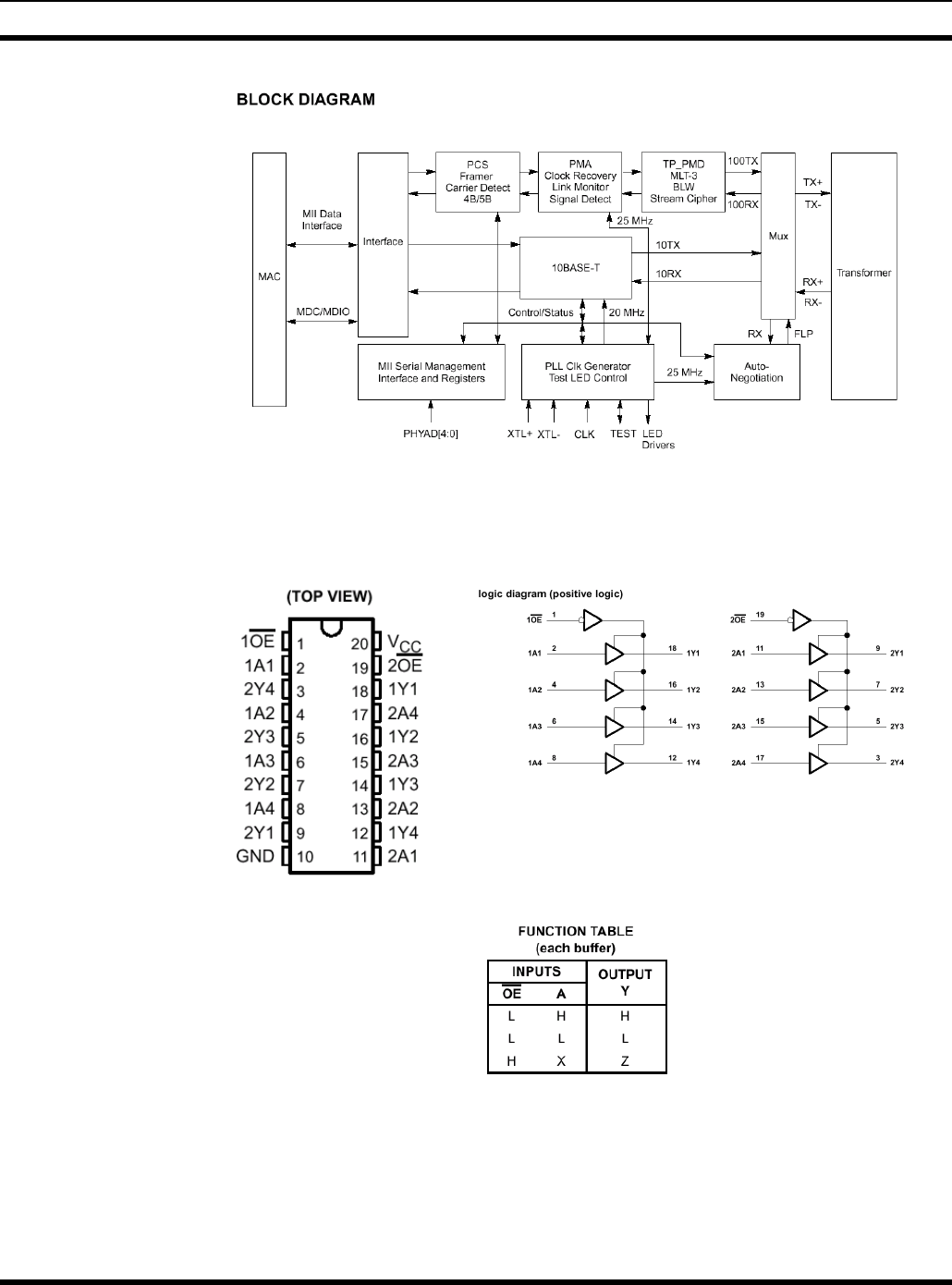

• Serial I/O • I/O (2)

7.3.3.1 Board Connections

Schematic Diagram WD-CB101069V1, Sheet 4 shows the single DIN96 connector, J7.

This 96-pin connector has three layers of pins, J7A, J7B and J7C. Each layer consists of

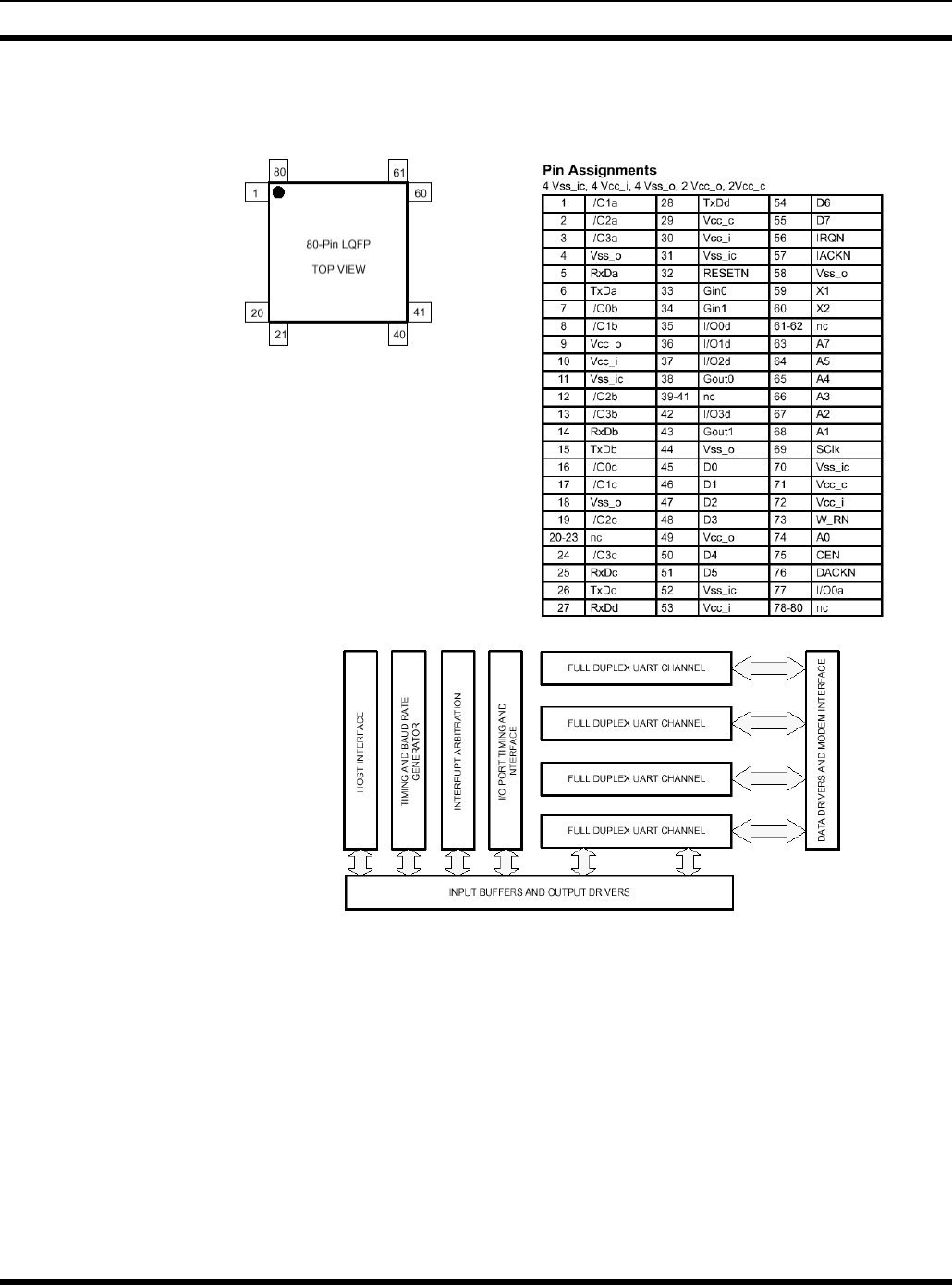

32 pins. J7B, Pins 1 and 32 are the MATE-DETECT-A and MATE DETECT-B

connections. These two connections are used with the Board Insertion Detection circuit.

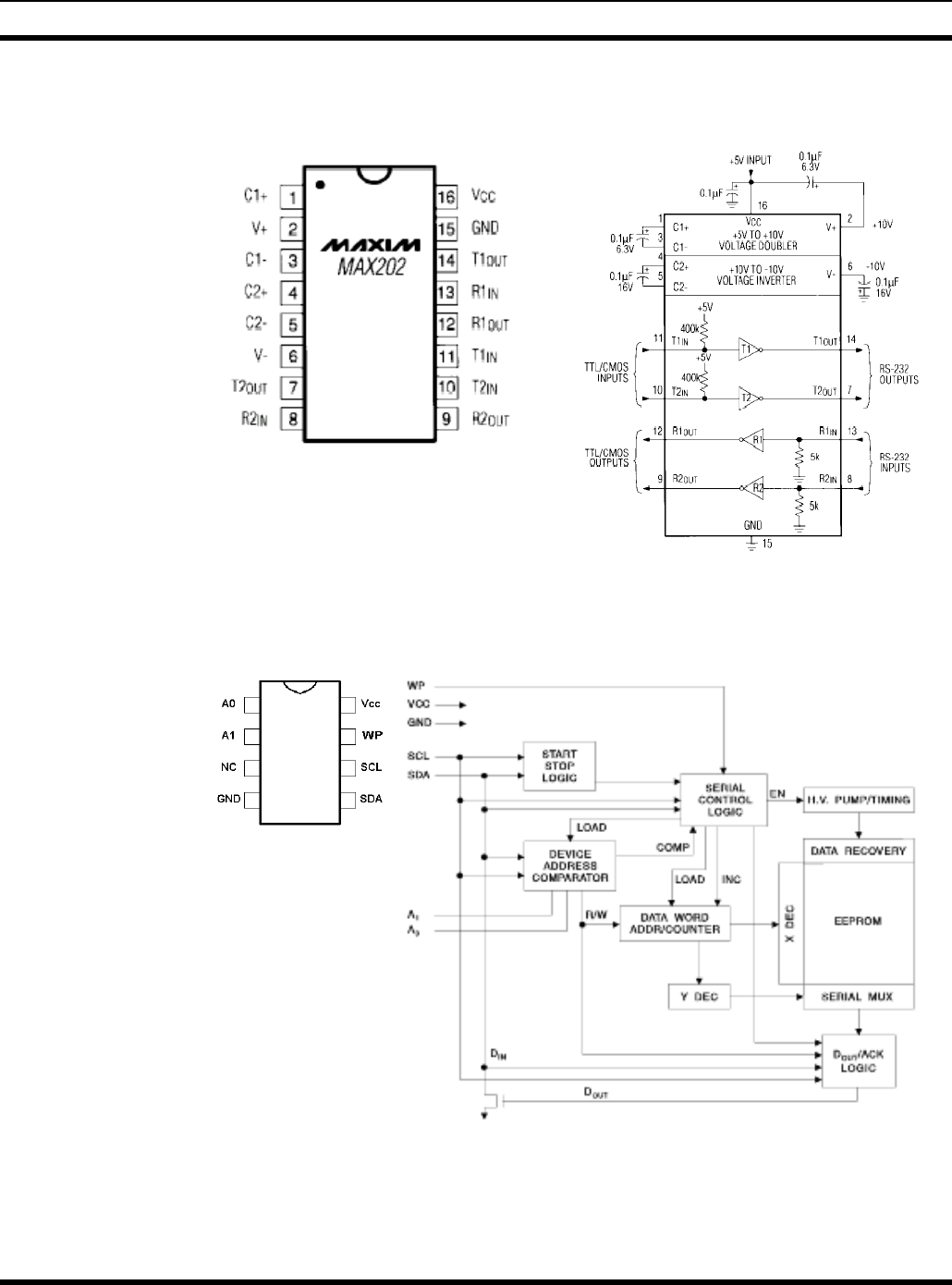

Pins J7B; Pins 27 and 28 are the SCL and SDA connections. SCL and SDA make up the

I2C bus. CPU I/O SIGNAL PROTECTION DIODES D27, D29 connected to SCL and

SDA provide surge protection for the I2C bus.

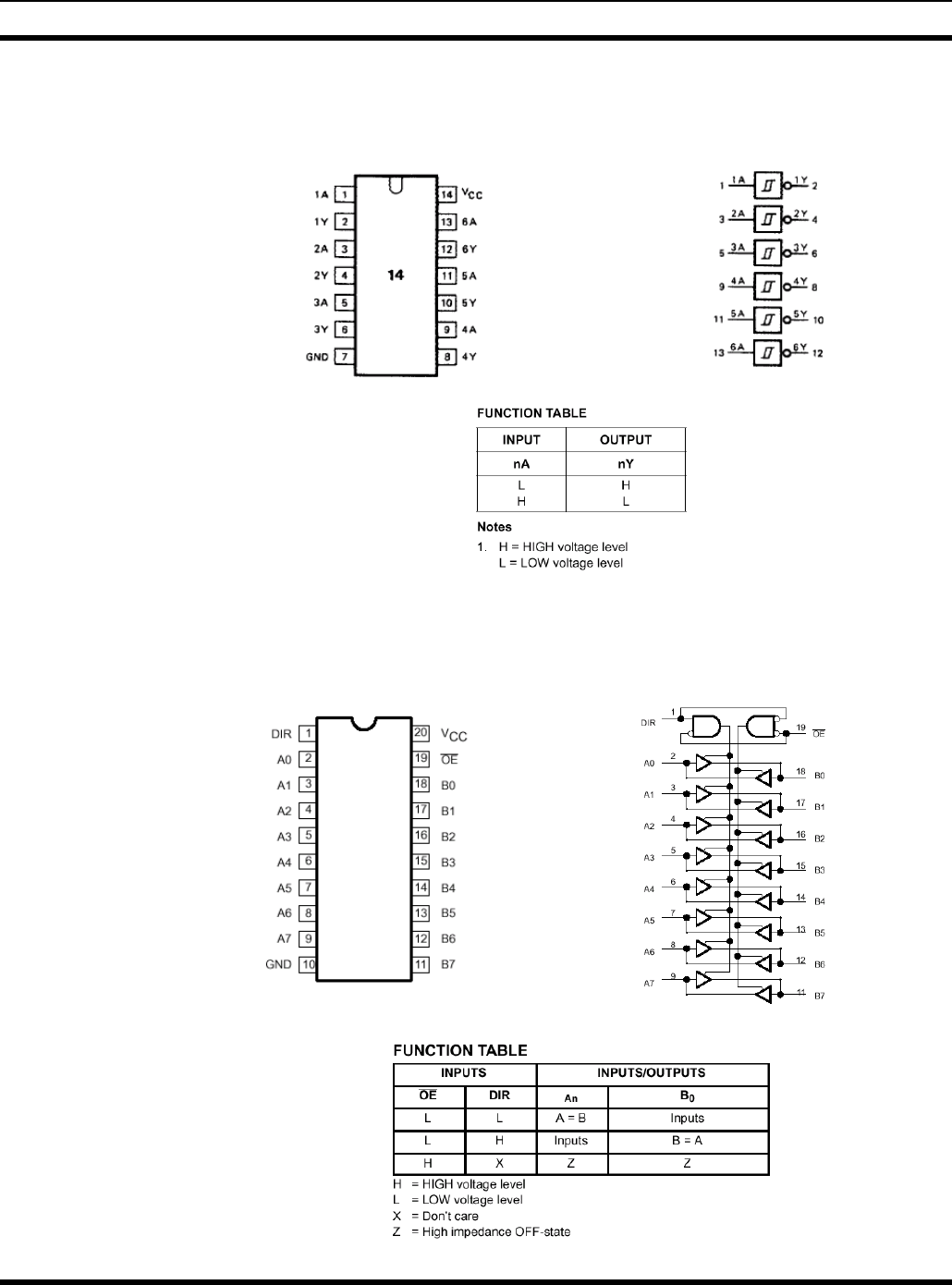

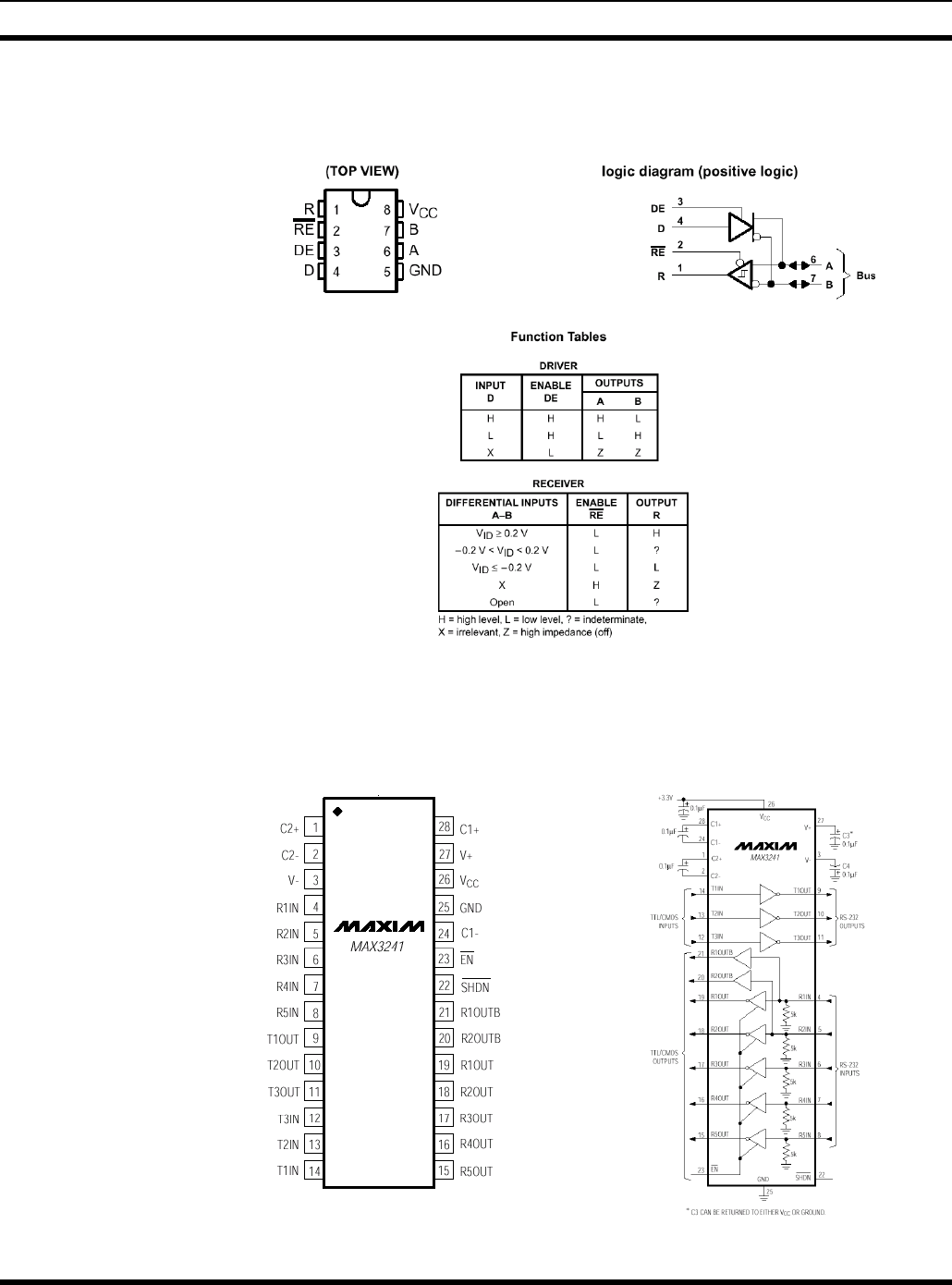

7.3.3.2 Serial I/O

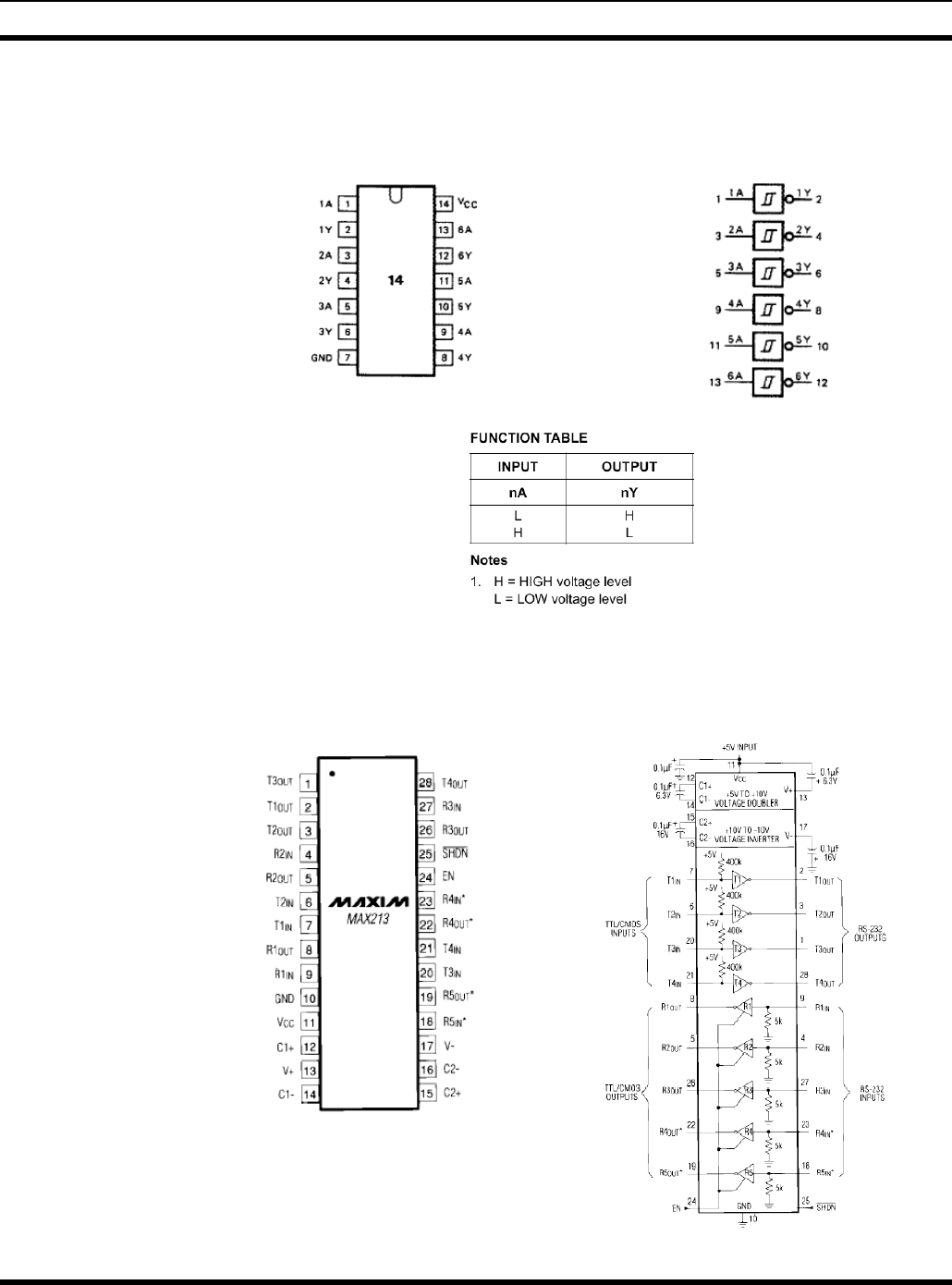

Numerous asynchronous and synchronous serial ports are brought to the Interconnect

Board (Backplane) from the microprocessor, Modem Board and QUART. Most serial

ports convert to standard RS-232 levels using RS-232 transceivers U13, U24, U30 &

U36. Serial port U21 converts to RS-485 differential signal levels and supports a

multidrop network. One microprocessor RS-232 port is used as a diagnostic or local

programming port and is brought to RJ-11 connector J8 on the front of the board. Two

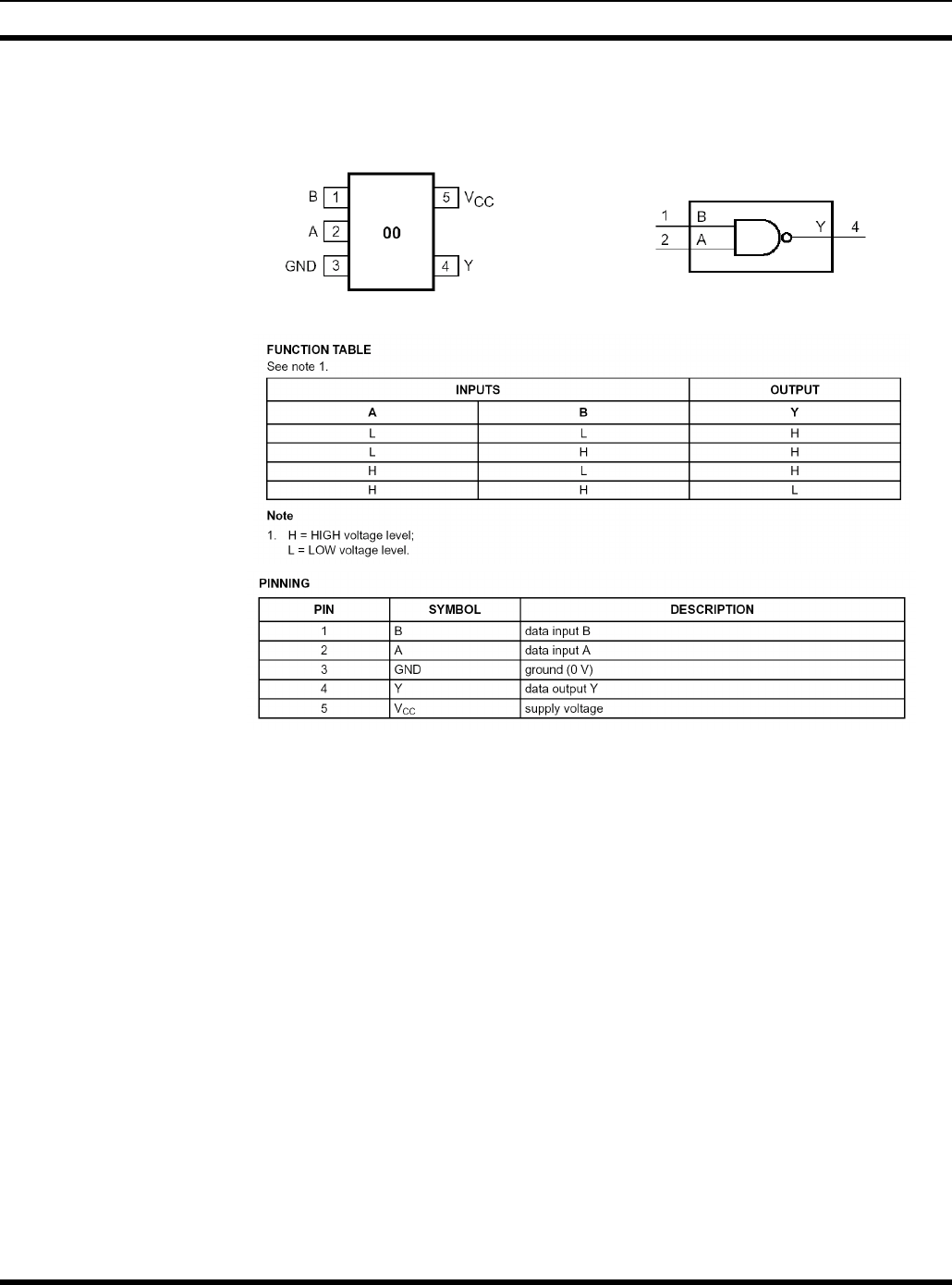

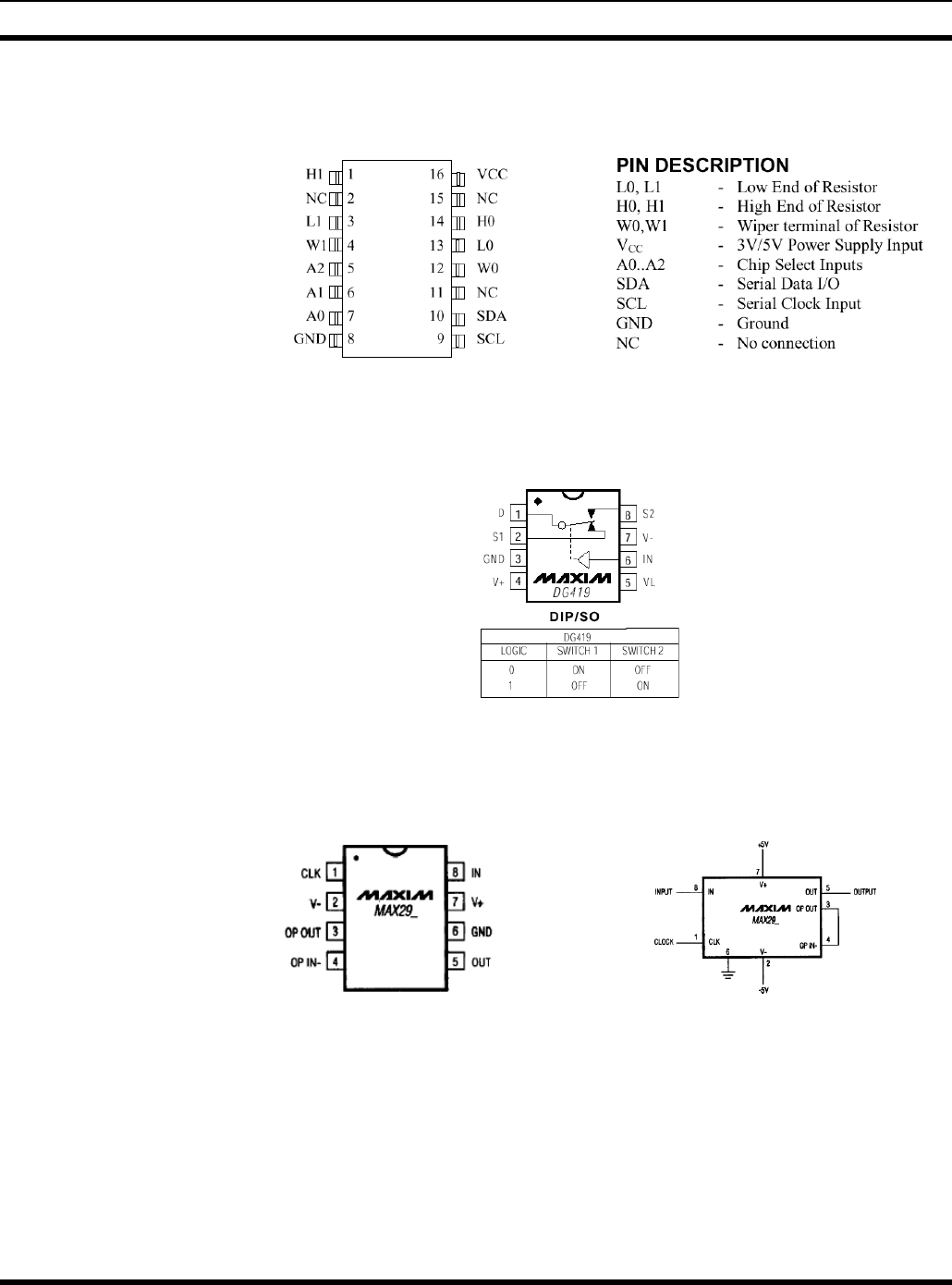

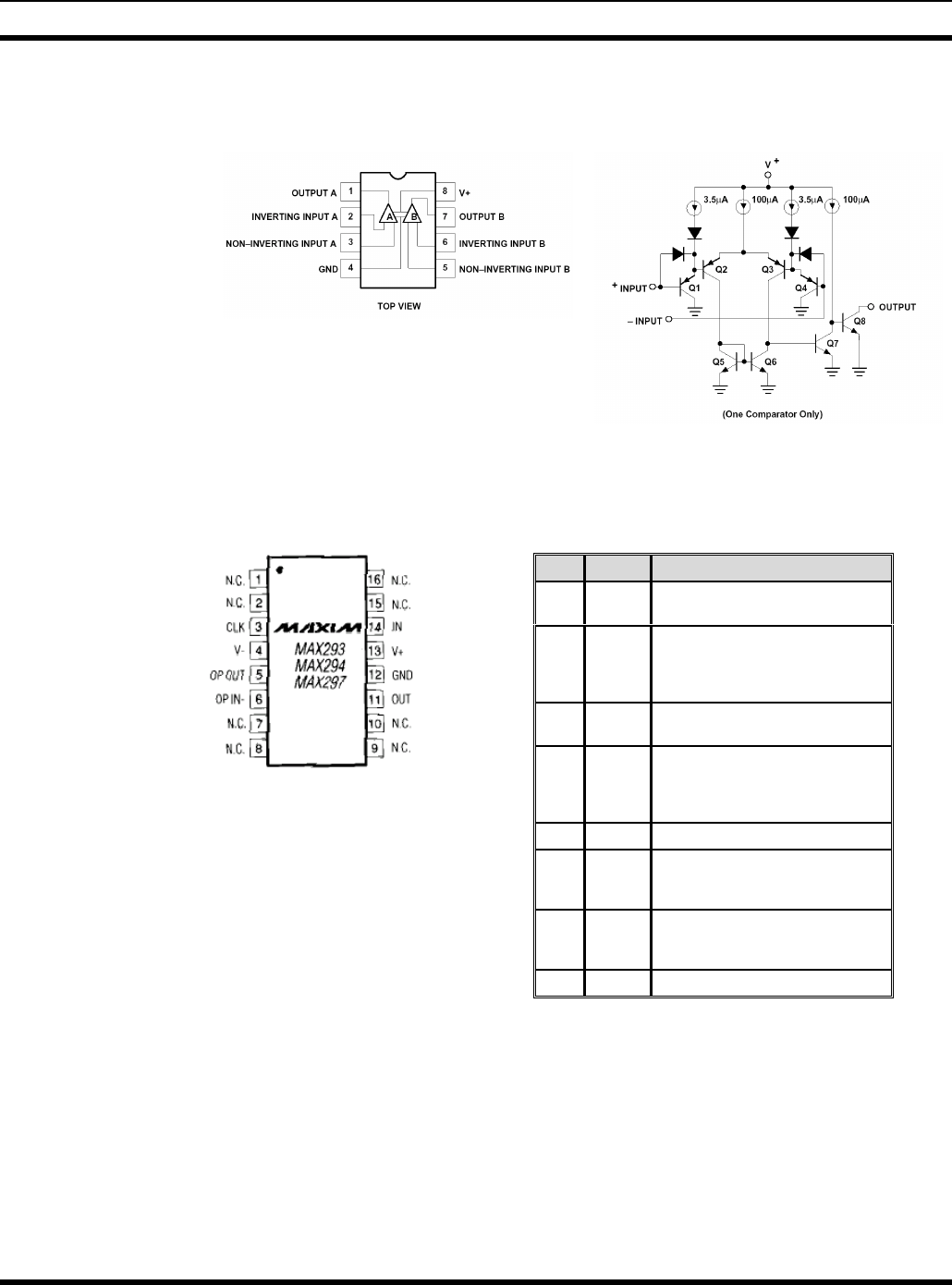

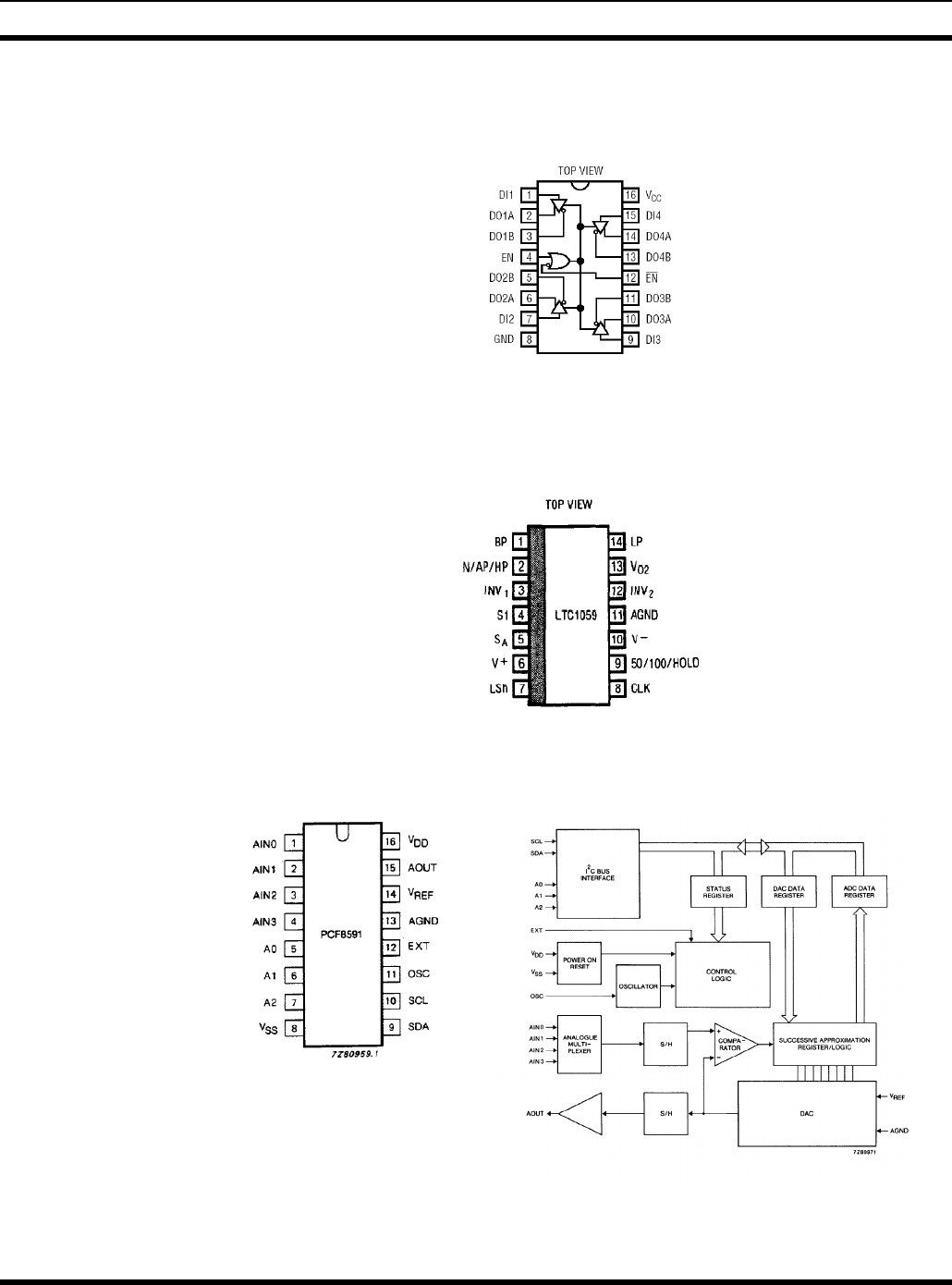

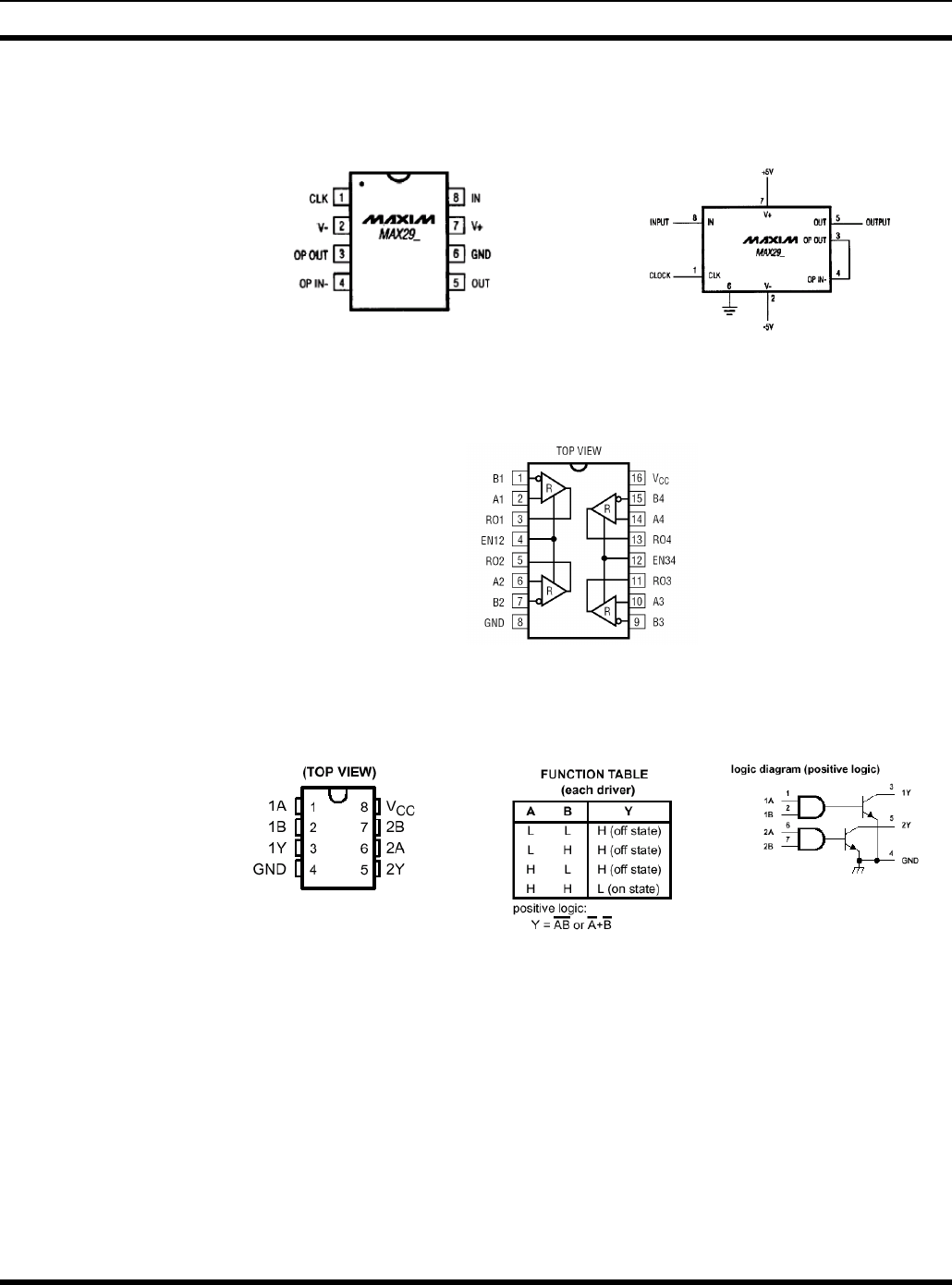

ports from the QUART use BSL signaling.